# Polycrystalline CdSeTe/CdTe Absorber Cells with 28 mA/cm<sup>2</sup> Short-Circuit Current

Amit Munshi<sup>1</sup>, Jason Kephart<sup>1</sup>, Ali Abbas<sup>2</sup>, John Raguse<sup>3</sup>, Jean-Nicolas Beaudry<sup>4</sup>, Kurt Barth<sup>1</sup>, James Sites<sup>3</sup>, John Walls<sup>2</sup>, Walajabad Sampath<sup>1</sup>

<sup>1</sup> NGPV (Next Generation PV Center), Department of Mechanical Engineering, Colorado State University, Fort Collins, CO 80523, United States

<sup>2</sup>CREST (Centre for Renewable Energy Systems Technology), Loughborough University, Leicestershire, LE11 3TU, United Kingdom

<sup>3</sup>Department of Physics, Colorado State University, Fort Collins, CO 80523, United States <sup>4</sup>5N Plus Inc., Montreal, Quebec, H4R 2B4, Canada

Abstract — An 800-nm CdSeTe layer was added to the CdTe absorber used in high-efficiency CdTe cells to increase the current and produce an increase in efficiency. The CdSeTe layer employed had a band gap near 1.41 eV, compared to 1.5 eV for CdTe. This lower band-gap allowed a current increase from approximately 26 to over 28 mA/cm<sup>2</sup>. Voltage same as earlier demonstrated high efficiency CdTe-only device was maintained. The fill-factor was not significantly affected. Improving the short-circuit current and maintaining the open-circuit voltage lead to device efficiency over 19%. QE implied that the approximately half the current was generated in the CdSeTe layer and half in the CdTe. Cross-section STEM and EDS showed good grain structure throughout and diffusion of Se into the CdTe layer was observed. To the best of authors' knowledge this is the highest efficiency polycrystalline CdTe photovoltaic device demonstrated amongst universities and national labs.

## I. INTRODUCTION

Thin-film CdTe photovoltaic panels have demonstrated very low cost of photovoltaic electricity generation, particularly for utility scale applications [1]. With improvements in fabrication processes, research scale small devices have recorded efficiencies as high as 22.1% [2] while commercial modules have achieved upto 18.6% [3]. The average production efficiency of such modules has increased from 13.5% to 16.2% between 2014 and 2016 [4], [5].

Improving the efficiency of photovoltaics without substantially increasing the manufacturing cost is key to further reductions in the cost/Wp of photovoltaic modules for commercial applications. One way of increasing the efficiency of thin-film photovoltaic devices is to improve the shortcircuit current. This can be achieved in several ways including the use of more transparent window-layers, anti-reflection coatings and a more transparent glass/TCO substrate. The authors have previously demonstrated 18.7% efficiency for polycrystalline thin-film CdTe devices using higher deposition temperatures, a Te layer in the back contact, and the use of anti-reflection coating[6][7]. This study demonstrates the use of a CdSeTe/CdTe absorber structure to further improve shortcircuit current for II-VI photovoltaic devices.

Lowering the band-gap of the absorber material can increase the photon fraction above the band-gap of the material leading to improved short-circuit current. Previous studies using these alloys for this purpose [8][9] have shown promise for the use of CdSeTe in PV cells. This study demonstrates the results from utilization of CdSe<sub>1-x</sub>Te<sub>x</sub>/CdTe absorber structure to improve the short-circuit current and thus improve the overall efficiency.

#### II. EXPERIMENTAL DETAILS

The cells used in the study were deposited on NSG TEC 10 soda lime glass coated with fluorine-doped tin oxide (FTO), a transparent conducting oxide (TCO). A Mg<sub>x</sub>Zn<sub>1-x</sub>O (MZO) buffer layer instead of the more common CdS was deposited using RF sputter deposition. CdSeTe films were sublimated using an optimized deposition process followed by sublimation of the CdTe layer. The CdSe<sub>x</sub>Te<sub>1-x</sub> (CdSeTe) and CdTe depositions were followed by CdCl<sub>2</sub> passivation, performed in-line without breaking vacuum [10]. The substrate was heated to about 540°C before starting the sublimation of CdSeTe. The temperature of the substrate was measured in-situ using a pyrometer located outside the preheating station.

The CdSeTe vapor source was heated to 575°C and CdSeTe films of 800 nm thickness were deposited. The CdSeTe composition used for this study had 20% Se in the source material. Band-gap of as-deposited film was measured to be 1.41 eV using transmission measurements and Tauc Plot. After deposition of CdSeTe, the sample was moved to the CdTe sublimation vapor source and a film ~3.4 µm thick was deposited. The CdTe sublimation source temperature was maintained at 555°C. CdCl<sub>2</sub> treatment is known to promote grain growth in CdTe films[11]-[14]. An aggressive CdCl<sub>2</sub> passivation treatment was performed for CdSeTe/CdTe films to promote inter-diffusion between these layers and avoid an abrupt interface. In addition to this, CdCl<sub>2</sub> treatment also is known to passivate the grain boundaries that leads to higher device performance[15]. For CdCl<sub>2</sub> passivation treatment, after deposition of CdSeTe and CdTe layers the substrate was transferred to the CdCl<sub>2</sub> treatment station without breaking vacuum. The CdCl<sub>2</sub> deposition source was maintained at

450°C while the substrate heater for this source was maintained at 425°C. The passivation treatment was performed for 600 seconds. This temperature gradient was maintained to ensure a thin film of  $CdCl_2$  got deposited on the substrate. After the  $CdCl_2$  treatment, the film was allowed to cool under vacuum for 180 seconds and then removed from the deposition chamber. After removing the film from the deposition chamber, the films were rinsed with deionized water to remove residual  $CdCl_2$  from the surface and surfaced dried using ultra-high purity  $N_2$  gas.

Thereafter, the films were heated to ~140°C, and CuCl was deposited on the film surface for 110 seconds[16]. The CuCl deposition source was maintained at 200°C while the substrate heater for the CuCl station was maintained at 170°C. This was followed by 220 seconds of annealing at 220°C in continued vacuum to form a Cu back contact. A 20-nm Te film was evaporated to improve the back-contact[17]. Carbon and nickel paint in a polymer binder where then sprayed on these films to form the back electrode.

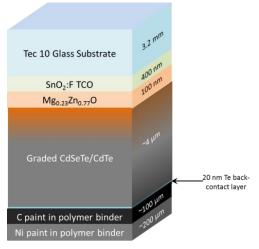

Figure 1 shows a schematic of the full device structure. The individual cells were delineated using a mask and bead blasting using plastic medium to fabricate 16 small scale devices on the substrate. The devices each had an area of  $\sim$ 1 cm<sup>2</sup>. The area of the aperture after masking the best performing device was measured to be 0.777 cm<sup>2</sup>.

Fig. 1. Schematic of the CdSeTe/CdTe graded absorber device. (not to scale).

#### III. PERFORMANCE

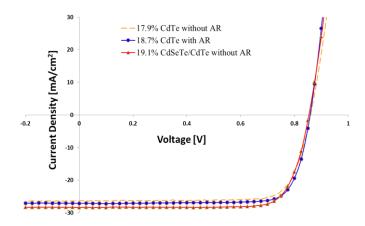

Figure 2 shows the current-density vs voltage comparison of a high efficiency device with CdTe absorber, with and without anti-reflection coating, earlier demonstrated by the authors. These high efficiency CdTe devices are compared to the device with CdSeTe/CdTe absorber described in section II. Table I shows the performance parameters of these 3 devices. The device with 19.1% efficiency demonstrated here is the

highest efficiency polycrystalline CdTe device demonstrated by any academic institution to the best of authors' knowledge.

With the addition of Se alloy at the front of the device, a higher  $J_{SC}$  is achieved. This is due to the formation of a lower band-gap absorber layer at the front interface leading to higher absorption. The band-gap measured for this ~800 nm CdSeTe layer was 1.41 eV before device completion. Current density of 28.4 mA/cm² was measured for this cell. This was over 1 mA/cm² higher than the current density measured for the high efficiency CdTe device with anti-reflection coating.

TABLE I

ELECTRICAL PERFORMANCE OF HIGH PERFORMING DEVICES

SHOWING IMPROVEMENT IN EFFICIENCY THROUGH IMPROVED

ABSORPTION AND INCREASE IN SHORT-CIRCUIT CURRENT

| Device Structure       | V <sub>OC</sub> (mV) | $J_{SC}$ (mA/cm <sup>2</sup> ) | FF<br>(%) | % η   |

|------------------------|----------------------|--------------------------------|-----------|-------|

| CdTe without AR        | 860                  | 26.3                           | 78.9%     | 17.9% |

| CdTe with AR           | 858                  | 27.1                           | 80.5%     | 18.7% |

| CdSeTe/CdTe without AR | 854                  | 28.4                           | 79.1%     | 19.1% |

Fig. 2. J-V graph comparing the performance of a CdSeTe/CdTe device against a CdTe reference device

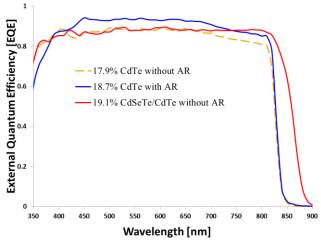

The external quantum efficiency (EQE) of the CdSeTe/CdTe and high efficiency device without antireflection coating (Fig. 3) was essentially identical below 700 nm, and after correction for reflection, the internal quantum efficiency in both cases was very close to unity. Above 700 nm, there appeared to be two differences between the CdTe device without anti-reflection coating and the CdSeTe/CdTe. The QE of the CdTe-only absorber showed a slight decrease below the band-gap cut-off, presumably due to reduced collection caused by higher recombination. Above 700 nm the response in CdSeTe/CdTe device was seen to be substantially higher and this device was found to absorb wavelengths above 850 nm up to about 900 nm.

Fig. 3. Comparison of the quantum efficiency for CdSeTe/CdTe devices against high efficiency CdTe device.

The second difference above the CdTe cutoff clearly showed current contribution from the CdSeTe layer and was consistent with its 0.1-eV reduction in band-gap. The slant in that part of the curve followed directly from absorption of approximately half of the longer wavelength photons in the CdSeTe layer. The CdTe device with anti-reflection coating demonstrated increased response between 400 nm and 850 nm that resulted in higher  $J_{SC}$  (27.1 mA/cm²) for this device. However, this improvement was still lower than the device with CdSeTe/CdTe absorber. This suggests large portion of the higher wavelength light was effectively utilized with the use of lower bang-gap CdSeTe. It is eminent that including an anti-reflection coating with the CdSeTe/CdTe absorber would lead to further improvement in short-circuit current.

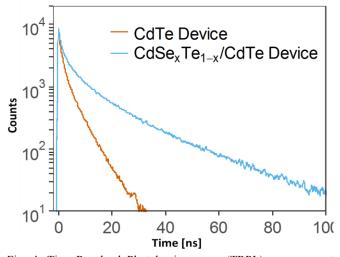

Fig. 4. Time-Resolved Photoluminescence (TRPL) measurement showing improved carrier lifetime with CdSeTe in the absorber.

Time-Resolved Photoluminescence (TRPL) measurements were performed for the high efficiency device with CdSeTe/CdTe absorber and compared to a high efficiency CdTe-only device. About 4-times higher carrier life-time of

21.9 ns was measured for the devices with CdSeTe/CdTe absorber as compared to CdTe-only absorber that demonstrated a carrier life-time of 5.5 ns. Carrier life-time as high as ~39 ns has been measured in similar devices with CdSeTe/CdTe absorber within this study. The cause of this improvement in carrier life-time is understood to be due to improved quality of the front interface between MgZnO and CdSeTe. Presence of lower band-gap CdSeTe adjacent to high band-gap MgZnO appears to produce a better band-alignment to give higher carrier life-time. In addition to this, presence of a higher band-gap CdTe at the back of CdSeTe maybe producing an effect similar to electron reflector [7], [18]–[20] which maybe partly responsible improvement in carrier life-time. The suggested electron reflection-like behavior of CdTe for CdSeTe requires further verification.

## IV. MATERIALS CHARACTERIZATION

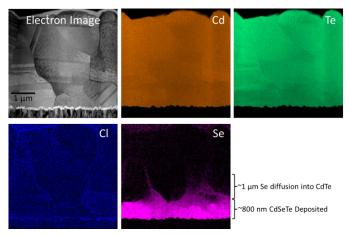

In-depth microstructure characterization of the CdTe film was carried out using Transmission Electron Microscopy (TEM) and High Resolution Transmission Electron Microscopy (HRTEM). TEM samples were prepared using Focused Ion Beam (FIB) milling using dual beam FEI Nova 600 Nanolab. A standard in-situ lift out method was used to prepare the cross section sample through the film stack into the glass substrate. A platinum overlay was deposited on the top of the film to define the area of interest on surface of the sample, homogenize the final thinning of the samples and to avoid damage to the CdTe film surface from the ion beam. STEM bright-field images and high resolution TEM images were collected using a FEI Tecnai F20 (S)TEM operating at 200 kV Cross-section (S)TEM images and corresponding EDS maps revealed the grain-structure and elemental distribution for these devices. The (S)TEM image showed large CdTe

Fig. 5. A Cross-section STEM image with EDS maps for Cd, Te and Se along with over layered image showing distribution of elements in the thin-film CdSeTe/CdTe device.

grain. No stacking faults were present in the CdSeTe/CdTe absorber layer, although twin boundaries are visible. Coverage of CdSeTe/CdTe appears to be conformal over MgZnO buffer layer and no voids or abnormalities were observed in the

growth of the absorber layer. A 100 nm thick MgZnO buffer layer was deposited on the substrate prior to deposition of the CdSeTe layer. This MgZnO layer appeared to be preserved through the fabrication process and no diffusion of Mg, Zn and O into the absorber was detected within the limits of EDS. There appeared to be an abrupt interface between MgZnO and CdSeTe layer further reinforcing diffusion between these layers to be negligible, if any.

Authors in another study had shown that presence of grain boundaries that are perpendicular to the path of charges has a detrimental effect on device performance[6], [14]. Similarly, large grains in the absorber that grow along the thickness of the absorber correspond to better device performance. Improvement in device performance from such grain structure with large grains and fewer grain boundaries had a substantial positive impact on fill-factor. This behavior was observed with these CdSeTe/CdTe films as well. TEM cross-section shows large grains covering most of the thickness of the film. These devices demonstrate fill-factor over 79%. However, few grain boundaries that were formed perpendicular to the direction of charge conduction are observed. Reducing area of such grain boundaries may result in higher fill-factor and thus better device performance.

The EDS elemental maps (figure 5) showed that Cd and Te were retained in the absorber film. The Se concentration at the glass side of the film appears to be high up to a thickness of ~800 nm and it diffused up to about 1 μm into the following CdTe. EDS elemental map also showed Cl distinctly decorating the CdSeTe/CdTe absorber grain boundaries and CdSeTe/MgZnO interface. It had been demonstrated in the by Lee *et al* that Cl at the grain boundaries in CdTe films plays an important role in electronic performance of the devices[15]. This appeared to hold true for CdSeTe/CdTe devices. There appeared to be Cl present is some of the MgZnO grain

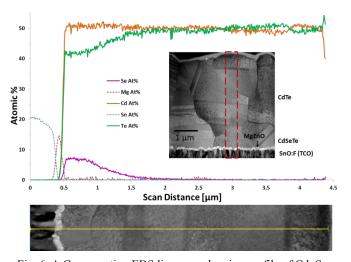

Fig. 6. A Cross-section EDS line-scan showing profile of Cd, Se, Te, Mg and Sn along the depth of thin-film CdSeTe/CdTe device. TEM image shows region where the scan has been performed.

boundaries but no such presence of Cl was detected at the interface of MgZnO and SnO:F (TCO). In addition, TEM images and EDS maps did not show Se being confined to certain grains closer to CdSeTe/MgZnO interface. Se was found to be present in grains that were graded from CdSeTe to CdTe. This suggested the growth of CdTe was epitaxial over CdSeTe that further helped in avoiding formation of an abrupt interface between CdSeTe and CdTe.

EDS line scan along the thickness of the absorber was performed that is shown in Figure 6. Region of the TEM cross section where the line scan was performed can also be seen in the figure. EDS line scan confirms the observation from the EDS elemental map that there was no substantial interdiffusion between the MgZnO and CdSeTe layers. However, it reaffirmed higher concentration of Se in the first ~800 nm of the absorber and its gradual diffusion into the CdTe layer over next 1.5  $\mu m-2~\mu m$ . This helped in formation of a graded interface between the CdSeTe and CdTe layers which was believed to be advantageous for photovoltaic device performance.

#### V. DISCUSSION

The external quantum efficiency indicated an improved absorption of light at higher wavelengths however, the effective band-gap of this material was still measured to be ~1.45 eV. Lowering the band-gap further to achieve higher short-circuit current density while maintaining higher voltage as well as fill-factor would be the logical next steps to achieve higher conversion efficiency. External quantum efficiency comparison showed that improving absorption between 700 nm and 900 nm wavelengths using lower band-gap CdSeTe has a greater impact on short-circuit current generation than increasing absorption between 400 nm and 850 nm using anti-reflection coating.

The elemental maps suggest that the process of grading the absorber material with Se was successful. Better grading of the absorber may be achieved by further optimization of CdCl<sub>2</sub> passivation treatment that may prove to be advantageous for device performance. Higher fill-factors may be achieved using more optimized CdCl<sub>2</sub> passivation treatment that would allow growth of larger grains in absorber that may lead to higher fill-factor and thus higher conversion efficiency.

Authors have currently been able to only maintain the open-circuit voltage when compared to earlier demonstrated high efficiency devices. However, TRPL results in this study showed about 4 times higher carrier life-time. This provides a basis to improve open-circuit voltage of the devices. Passivation of the front interface as well as reducing the back-surface recombination for such devices with CdSeTe/CdTe absorber may be necessary to achieve higher open-circuit voltage.

## VI. CONCLUSIONS

To best of authors' knowledge, device performance demonstrated here is amongst the highest efficiency CdTe based photovoltaic device demonstrated by any university or national lab. Improvement in short-circuit current density of photovoltaic devices by using CdSeTe has been successfully demonstrated. Further refinement of the process is necessary to exploit the full potential of using Se in the absorber material. Long and high temperature CdCl<sub>2</sub> passivation treatment leads to the diffusion of Se into the CdTe film. However, this does not negatively affect the MgZnO buffer layer and the interfaces remain intact. External quantum efficiency measurements showed that the improvement in short-circuit current is due to improved absorption. From external quantum efficiency comparison it is evident that including an anti-reflection coating to the device demonstrated here would lead to devices with short-circuit current greater than 29 mA/cm<sup>2</sup>. This along with improved fill-factor using more optimized CdCl<sub>2</sub> passivation treatment may be necessary to achieve device efficiencies in excess of 20%. High carrier life-time measured using TRPL provide basis for improving the open-circuit voltage that has been a major deficit with CdTe based photovoltaics. CdSeTe material used for fabrication of these devices contained 20% Se, however, from EDS line scan it can be observed that much lower i.e. ~8% is incorporated into the film. CdSeTe material with much higher Se composition may be necessary to further achieve higher absorption as well as further improve carrier life-time.

#### VII. ACKNOWLEDGEMENTS

The CSU authors thank support from NSF's Accelerating Innovation Research, DOE's SunShot and NSF's Industry/University Cooperative Research Center programs. The Loughborough authors are grateful to EPSRC for funding through the Supergen SuperSolar Hub. Authors gratefully acknowledge help from 5N Plus for providing CdSeTe material for deposition.

## REFERENCES

- [1] N. M. Haegel, R. Margolis, T. Buonassisi, D. Feldman, A. Froitzheim, R. Garabedian, M. Green, S. Glunz, H.-M. Henning, B. Holder, I. Kaizuka, B. Kroposki, K. Matsubara, S. Niki, K. Sakurai, R. A. Schindler, W. Tumas, E. R. Weber, G. Wilson, M. Woodhouse, and S. Kurtz, "Terawatt-scale photovoltaics: Trajectories and challenges," *Science* (80-.)., vol. 356, no. 6334, 2017.

- [2] D. E. D. Green Martin A., Emery Keith, Hishikawa Yoshihiro, Warta Wilhelm, "Solar cell efficiency tables (Version 45)," *Prog. Photovoltaics*, vol. 23, no. 1, pp. 1–9, 2015.

- [3] W. Eric, "Exclusive: First Solar's CTO Discusses Record 18.6% Efficient Thin-Film Module," *Greentech Media*, 2015. [Online]. Available:

- http://www.greentechmedia.com/articles/read/Exclusive-First-Solars-CTO-Discusses-Record-18.6-Efficient-Thin-Film-Mod.

- [4] S. K. David Brady, Steve Haymore, "First Solar, INC. Announces First Quarter 2014 Financial Results," Tempe, AZ, 2014.

- [5] S. K. Steve Haymore, "First Solar, Inc. 2016 First Quarter Financial Results," Tempe, AZ, 2016.

- [6] A. Munshi, "Investigation of Processing, Microstructures and Efficiencies of Polycrystalline CdTe Photovoltaic Films and Devices," Colorado State Univeristy, 2016.

- [7] W. S. Sites, James R, Munshi, Amit M, Kephart, Jason M., Swanson, Drew E., Sampath, "Progress and Challenges with CdTe Cell Efficiency," in *43rd IEEE Photovoltaics Specialists Conference (PVSC)*, 2016.

- [8] N. R. Paudel and Y. Yan, "Enhancing the photocurrents of CdTe thin-film solar cells in both short and long wavelength regions," *Appl. Phys. Lett.*, vol. 105, no. 18, 2014.

- [9] D. E. Swanson, J. R. Sites, and W. S. Sampath, "Solar Energy Materials & Solar Cells Co-sublimation of CdSe x Te 1 À x layers for CdTe solar cells," Sol. Energy Mater. Sol. Cells, vol. 159, pp. 389–394, 2017.

- [10] D. E. Swanson, J. M. Kephart, P. S. Kobyakov, K. Walters, K. C. Cameron, K. L. Barth, W. S. Sampath, J. Drayton, and J. R. Sites, "Single vacuum chamber with multiple close space sublimation sources to fabricate CdTe solar cells," *J. Vac. Sci. Technol. A Vacuum, Surfaces, Film.*, vol. 34, no. 2, p. 21202, 2016.

- [11] W. S. S. Ali Abbas, Geoff D. West, Jake W. Bowers, Piotr M. Kaminski, B. Maniscalco, John M. Walls, Kurt L. Barth, "Cadmium Chloride Assisted Re-Crystallization of CdTe: The Effect of Varying the Annealing Time," MRS Proc., vol. 1638, 2014.

- [12] A. Munshi, A. Abbas, J. Raguse, K. Barth, W. S. Sampath, and J. M. Walls, "Effect of varying process parameters on CdTe thin film device performance and its relationship to film microstructure," pp. 1643–1648, 2014.

- [13] W. S. S. Ali Abbas, Geoff D. West, Jake W. Bowers, Piotr M. Kaminski, John M. Walls, Kurt L. Barth, "Cadmium Chloride Assisted Re-Crystallisation of CdTe: The Effect on the CdS Window Layer," MRS Proc., vol. 1738, 2015.

- [14] W. S. Munshi, Amit H., Kephart, Jason M., Abbas Ali, Shimpi, Tushar M., Barth Kurt L., Walls, John M., Sampath, "Effect of Varying Deposition and Substrate Temperature on Sublimated CdTe Thin-Film Photovoltaics," in 43rd IEEE Photovoltaics Specialists Conference (PVSC), 2016.

- [15] C. Li, Y. Wu, J. Poplawsky, T. J. Pennycook, N. Paudel, W. Yin, S. J. Haigh, M. P. Oxley, A. R.

- Lupini, M. Al-Jassim, S. J. Pennycook, and Y. Yan, "Grain-Boundary-Enhanced Carrier Collection in CdTe Solar Cells," *Phys. Rev. Lett.*, vol. 112, no. 15, p. 156103, 2014.

- [16] R. A. Barth, Kurt L; Sampath, Walajabad S; Enzenroth, "Apparatus and Processes for the Mass Production of Photovoltaic Modules," 2002.

- [17] W. Xia, H. Lin, H. Ning, C. W. Tang, I. Irfan, C. Wang, and Y. Gao, "Solar Energy Materials & Solar Cells Te / Cu bi-layer: A low-resistance back contact buffer for thin fi lm CdS / CdTe solar cells," vol. 128, pp. 411–420, 2014.

- [18] S. W. S. Swanson Drew E., Geisthardt Russell M., Kobyakov Pavel S., Raguse John M., Drayton

- Jennifer, Sites James R., "Reduction of Carrier Recombination in CdTe Solar Cells by the Addition of a Cd1-xMgxTe Electron Reflector Film.," in 40th IEEE Photovoltaics Specialists Conference, 2014.

- [19] S. W. S. Swanson Drew E., Abbas Ali, Munshi Amit H., Drayton Jennifer A., Raguse John M., Gristhardt Russell M., Sites James R., "Incorporation of Cd1xMgx Te as an Electron Reflector for Cadmium Telluride Photovoltaic Cells," MRS Proc., vol. 1771, 2015.

- [20] K.-J. Hsiao, "Electron-Reflector Strategy for CdTe Thin-Film Solar Cells," Colorado State University, 2010.