This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<u>https://dspace.lboro.ac.uk/</u>) under the following Creative Commons Licence conditions.

| COMMONS DEED                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Attribution-NonCommercial-NoDerivs 2.5                                                                               |  |  |  |

| You are free:                                                                                                        |  |  |  |

| <ul> <li>to copy, distribute, display, and perform the work</li> </ul>                                               |  |  |  |

| Under the following conditions:                                                                                      |  |  |  |

| <b>Attribution</b> . You must attribute the work in the manner specified by the author or licensor.                  |  |  |  |

| Noncommercial. You may not use this work for commercial purposes.                                                    |  |  |  |

| No Derivative Works. You may not alter, transform, or build upon this work.                                          |  |  |  |

| <ul> <li>For any reuse or distribution, you must make clear to others the license terms of<br/>this work.</li> </ul> |  |  |  |

| <ul> <li>Any of these conditions can be waived if you get permission from the copyright<br/>holder.</li> </ul>       |  |  |  |

| Your fair use and other rights are in no way affected by the above.                                                  |  |  |  |

| This is a human-readable summary of the Legal Code (the full license).                                               |  |  |  |

| Disclaimer 🖵                                                                                                         |  |  |  |

|                                                                                                                      |  |  |  |

For the full text of this licence, please go to: <u>http://creativecommons.org/licenses/by-nc-nd/2.5/</u>

.

•

. а, ۱.

• • • •

.

. . •

### 'Self-Tuning Digital Controllers for Servo Systems'

by

Ghassan Mohammad Al-Sadigi, B.Sc, M.Sc.

A doctoral thesis submitted in partial fulfilment of the requirements of Loughborough University of Technology

April 1987

### Supervisors

J. E. Cooling B.Sc., C.Eng., MIEE. Electronic and Electrical Engineering Dept.

Dr. A. H. Whitfield

Engineering Mathematics Dept.

.

Dete Jue 87 Clars Acc. 013110/02

## Acknowledgement

I wish to express my sincere thanks to Mr. Jim Cooling, of Electronic and Electrical Engineering Dept. and Dr. Allen Whitfield, of Engineering Mathematics Dept., for their invaluable help and guidance during my period of research. Their supervision has been excellent throughout and I am indebted to them both for the inspiration and encouragement they have given me.

I would also like to thank Mr. Mark Morgan Lloyd for his technical advice concerning the software work involved in the thesis. I am thankful to the staff and student members and technicians for their assistance.

### SYNOPSIS

### Self-tuning Digital Controllers for Servo Systems.

Adaptive self-tuning systems have been the subject of a great deal of research effort in recent years. Practical applications have lagged behind such work, in the main being applied in the process industries. Few servo applications have been reported, the wide bandwidths and demanding performance specifications raising problems not found in the process world. The research project described here is concerned with the use of self-tuning digital controllers applied to servosystems, specifically an electro-mechanical actuation unit. Practical limitations, such as stiction, friction and velocity saturation effects are taken into account. The following factors are considered within this thesis;

\* Plant identification and modelling using off-line identification techniques.

\* Plant identification and modelling using on-line methods.

\* Control strategies based on statistical and deterministic principles.

A \* Mathematical methods to achieve optimal plant models through the use of model reduction techniques.

$\mu$  \* Self-tuning strategy evaluation via simulation procedures.

\* Self-tuning strategy evaluation via plant testing.

\* Development and use of a mechanical simulator for the evaluation of control strategies.

\* Hardware design and development of a 16 bit microprocessor based digital controller.

A\* Software design of the identification, control and self-tuning algorithms.

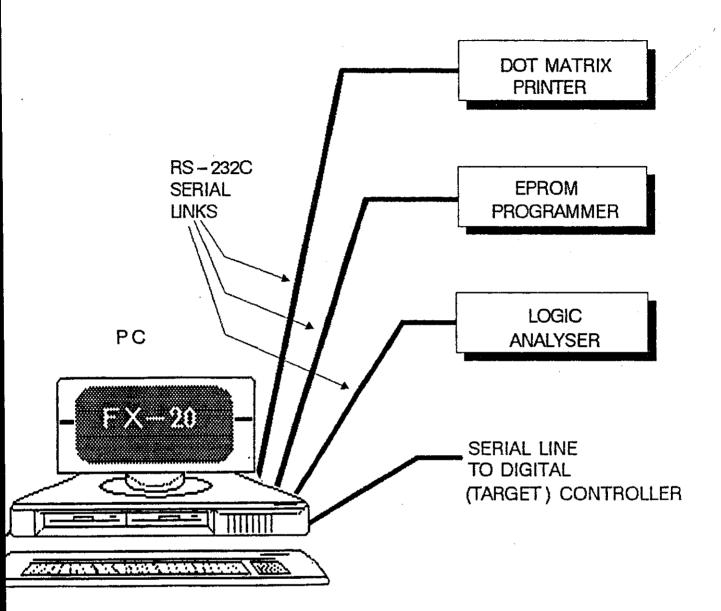

\* The use of a PC based integrated work-station as a tool for the development of embedded control systems.

Significant improvements in mathematical methods for model order reduction are presented, their validity being demonstrated in practical testing.

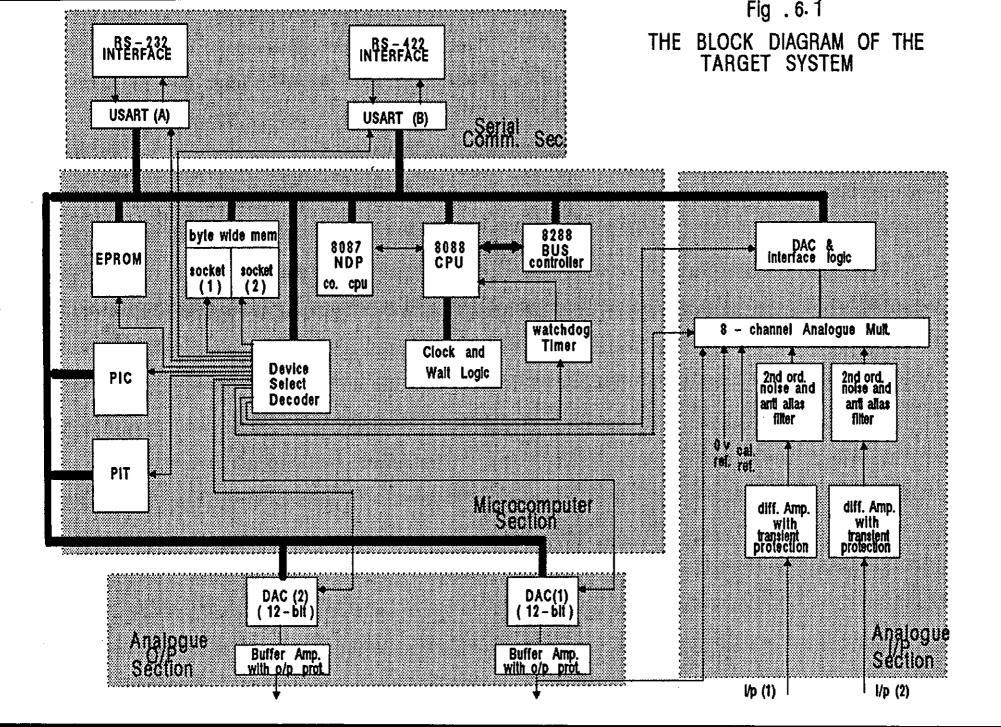

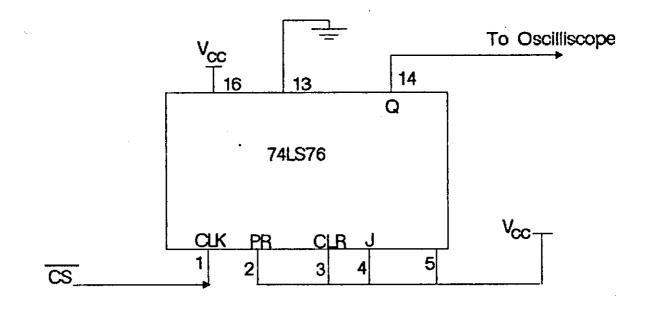

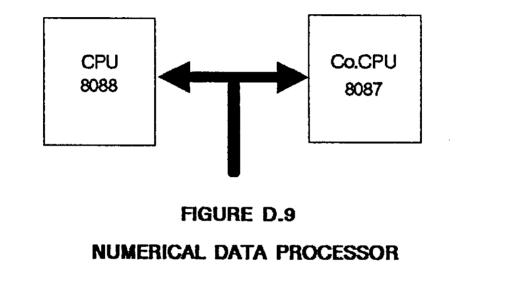

The digital controller described here uses an Intel 8088 processor augmented by an 8087 Numeric Data Processor, plant interfacing being carried out using analogue to digital and digital to analogue converters. Controller software is written in ASM86 and Pascal/MT+, that for the simulation being produced in Fortran 77.

## CONTENTS

## CHAPTER 1: INTRODUCTION

| 1.1 Control Systems                   | 1 - 1      |

|---------------------------------------|------------|

| 1.1.1 General                         | 1 - 1      |

| 1.1.2 Control System Design Methods   | 1 - 1      |

| 1.1.3 Self-Tuning Systems             | 1 - 2      |

| 1.2 The Controlled Plant              | 1 - 3      |

| 1.3 System Development in a PC Enviro | onment 1-3 |

| 1.4 Thesis Objective and Organisation | 1 - 4      |

CHAPTER 2: THE DEVELOPMENT OF THE THEORY OF CONTROL

| 2.1 | History of Control             | 2 - 1 |

|-----|--------------------------------|-------|

| 2.2 | Approaches to Adaptive Control | 2 - 5 |

### CHAPTER 3: MODEL DETERMINATION

| 3.1 Int                                            | Introduction                                 |       |  |

|----------------------------------------------------|----------------------------------------------|-------|--|

| 3.2 Ap                                             | 3.2 Approaches to Model Determenation 3      |       |  |

| 3.3 Functional Testing and System Identification 3 |                                              |       |  |

| 3.3.1                                              | Overview                                     | 3 - 4 |  |

| 3.3.2 Plant Testing 3                              |                                              | 3 - 4 |  |

| 3.3.3 Off-line Identification                      |                                              | 3 - 5 |  |

| 3.4 Mo                                             | del Order Reduction                          | 3 - 8 |  |

| 3.4.1                                              | Overview                                     | 3 - 8 |  |

| `3.4.2                                             | The Effect of Choosing Different Model Order | 3 - 8 |  |

| 3.4.3                                              | The Pole/Zero Cancellation Technique         | 3 - 9 |  |

| 3.4.4 | Static Gain Correction          | 3 -12 |

|-------|---------------------------------|-------|

| 3.4.5 | Model Trimming                  | 3 -14 |

| 3.4.6 | Model Order Reduction Technique | 3 -14 |

## CHAPTER 4: IMPLEMENTATION OF THE DIGITAL CONTROL ALGORITHM

| 4.1 In | troduction                         | 4 - 1 |

|--------|------------------------------------|-------|

| 4.2 Pu | lse Transfer Function              | 4 - 2 |

| 4.3 Th | e Control Law                      | 4 - 4 |

| 4.4 Im | plementation Considerations        | 4 - 6 |

| 4.4.1  | Introduction                       | 4 - 6 |

| 4.4.2  | Choice of Sampling Rate            | 4 - 6 |

| 4.4.3  | Computational Delay                | 4 - 9 |

| 4.4.4  | Practical Constraints              | 4 -11 |

| 4.5 Co | ntrol Design Techniques            | 4 -14 |

| 4.5.1  | Overview                           | 4 -14 |

| 4.5.2  | One-Step-Ahead Prediction          | 4 -14 |

| 4.5.3  | Weighted One-Step-Ahead Prediction | 4 -17 |

| 4.5.4  | Pole/Zero Cancellation             | 4 -19 |

| 4.5.5  | PID Controller                     | 4 -21 |

## CHAPTER 5: SELF-TUNING CONTROLLER

| 5.1             | Introduction                         | 5 - 1 |

|-----------------|--------------------------------------|-------|

| 5.2             | Basics of The Adaptive (Self-Tuning) | 5 - 1 |

| Control Systems |                                      |       |

| 5.3             | Implementation Considerations        | 5 - 3 |

| 5.              | 3.1 The Control Function             | 5 - 3 |

| 5.              | 3.2 The Identification Process       | 5 - 3 |

| 5.4 | Ger | neral Description of Self-Tuning Systems   | 5   | - | 4 |

|-----|-----|--------------------------------------------|-----|---|---|

| 5.5 | Imp | plementation of The Self-Tuning Controller | 5   | - | 6 |

|     | Alg | gorithm                                    |     |   |   |

| 5.8 | 5.1 | Pole/Zero Cancellation Self-Tuning         | 5 · | - | 6 |

| 5.9 | 5.2 | PID Self-Tuning                            | 5 · | - | 9 |

CHAPTER 6: DIGITAL CONTROLLER - ELECTRONIC HARDWARE

| 6.1 | General Description   | 6 - 1 |

|-----|-----------------------|-------|

| 6.2 | CPU Section           | 6 - 1 |

| 6.3 | Analogue I/O Section  | 6 - 2 |

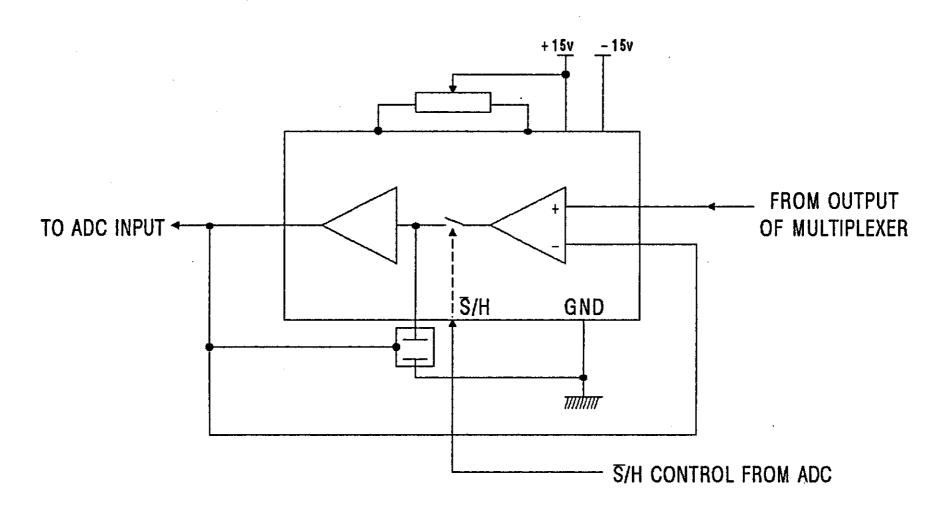

| 6.4 | Serial Communications | 6 - 3 |

## CHAPTER 7: SOFTWARE DESIGN AND DEVELOPMENT

| 7.1 The Host Development System                                                                                    | 7 - 1          |

|--------------------------------------------------------------------------------------------------------------------|----------------|

| 7.2 Design Techniques                                                                                              | 7 - 1          |

| 7.3 The Rules of Structured Programming                                                                            | 7 - 2          |

| 7.4 Programming Language                                                                                           | 7 - 3          |

| 7.5 Program Structure and Development                                                                              | 7 - 4          |

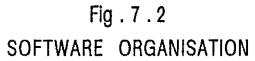

| 7.6 The Software Functions                                                                                         | 7 - 5          |

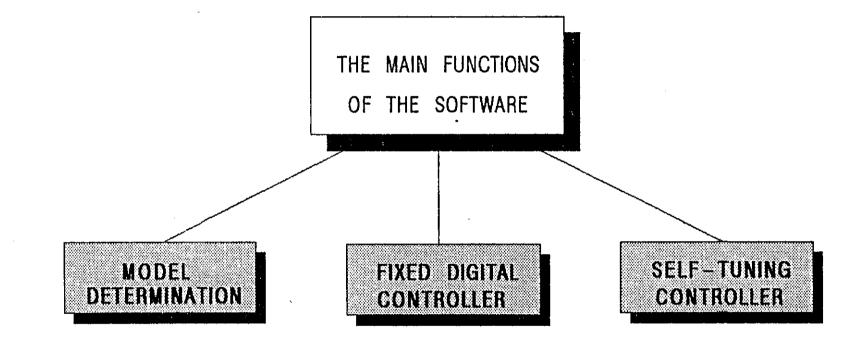

| 7.7 Model Determination                                                                                            | 7 - 5          |

| 7.7.1 Overview                                                                                                     | 7 - 5          |

|                                                                                                                    |                |

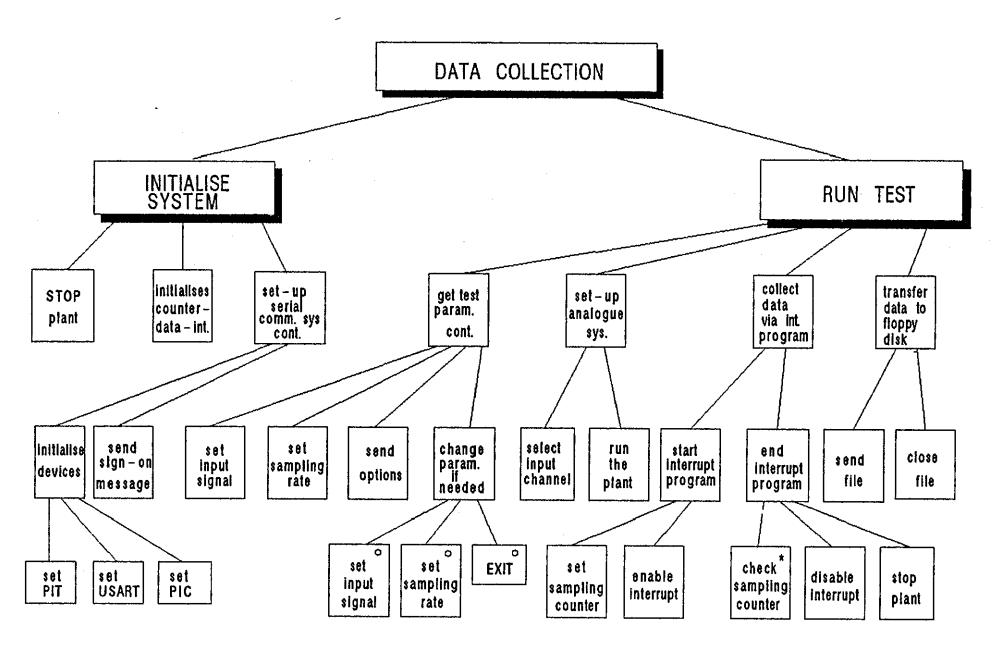

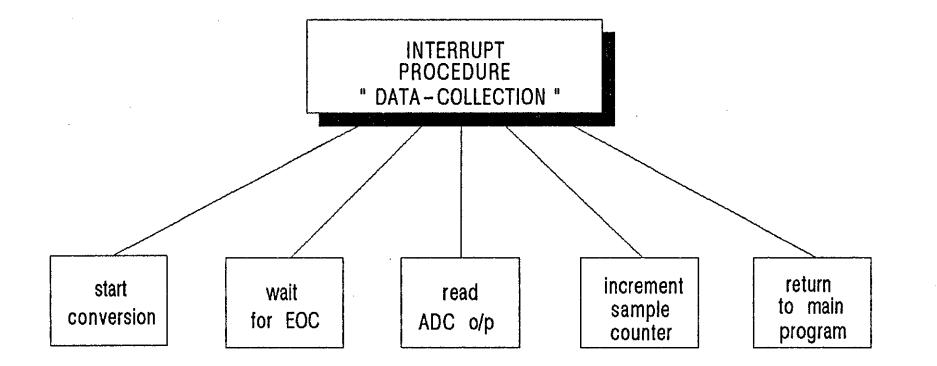

| 7.7.2 Data Collection - General Description                                                                        | 7 - 6          |

| <ul><li>7.7.2 Data Collection - General Description</li><li>7.7.3 Data Collection - Detailed information</li></ul> | 7 - 6<br>7 - 9 |

|                                                                                                                    |                |

| 7.7.3 Data Collection - Detailed information                                                                       | 7 - 9          |

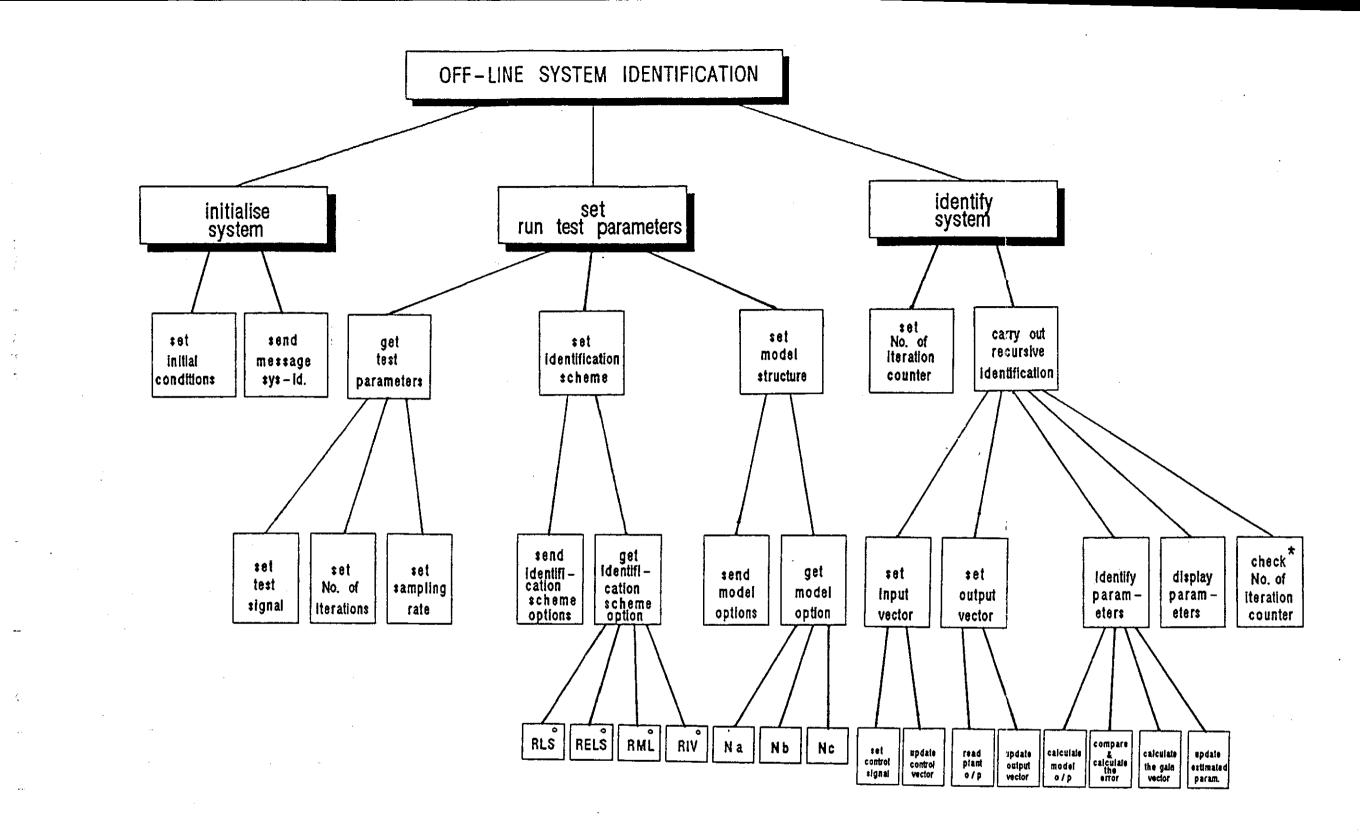

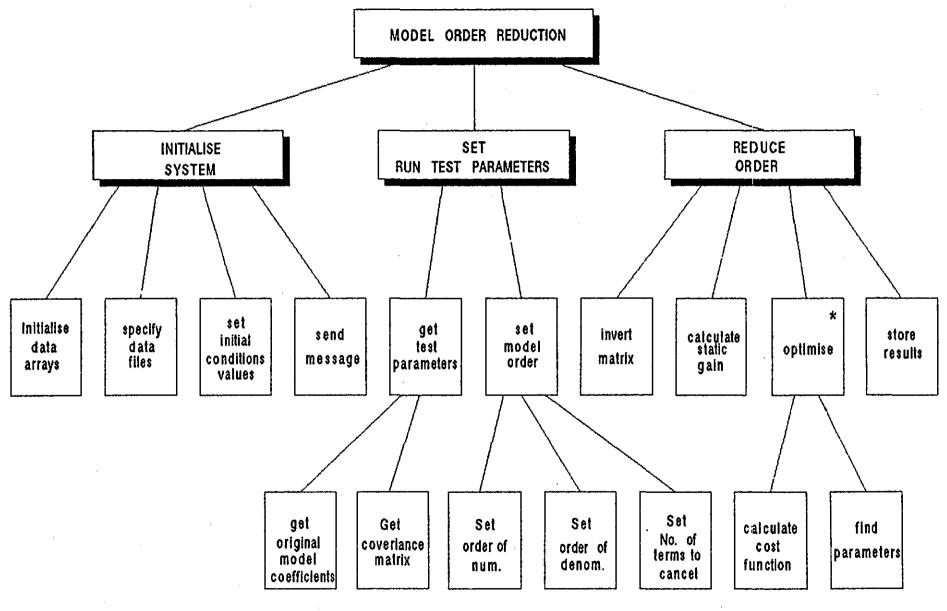

| <ul><li>7.7.3 Data Collection - Detailed information</li><li>7.7.4 Off-Line System Identification</li></ul>        | 7 - 9<br>7 -11 |

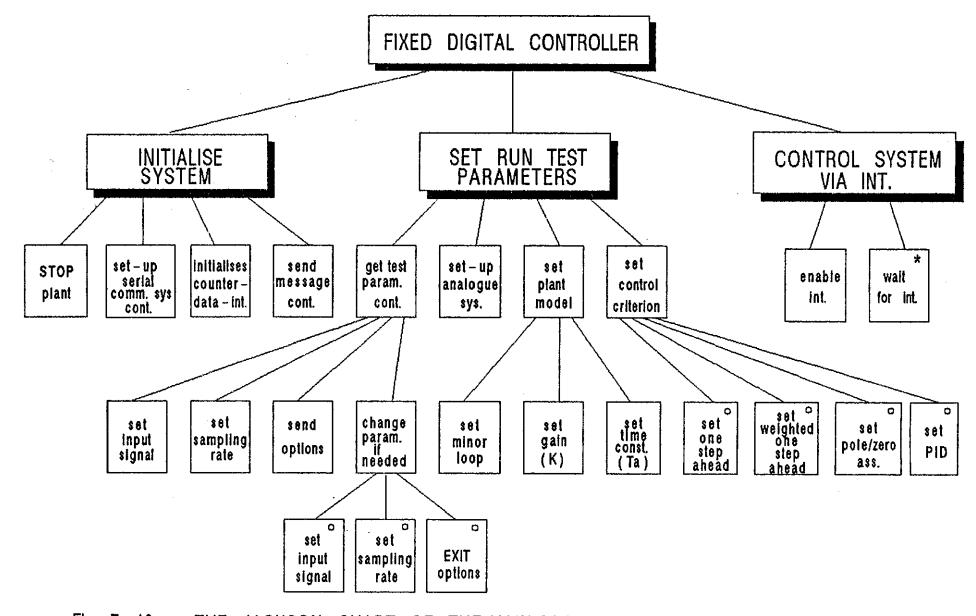

| 7.8.1 | Overview                          | 7 -19 |

|-------|-----------------------------------|-------|

| 7.8.2 | Initialise System Procedure       | 7 -20 |

| 7.8.3 | Set Test Parameters Procedure     | 7 -20 |

| 7.8.4 | Control System Via Int. Procedure | 7 -21 |

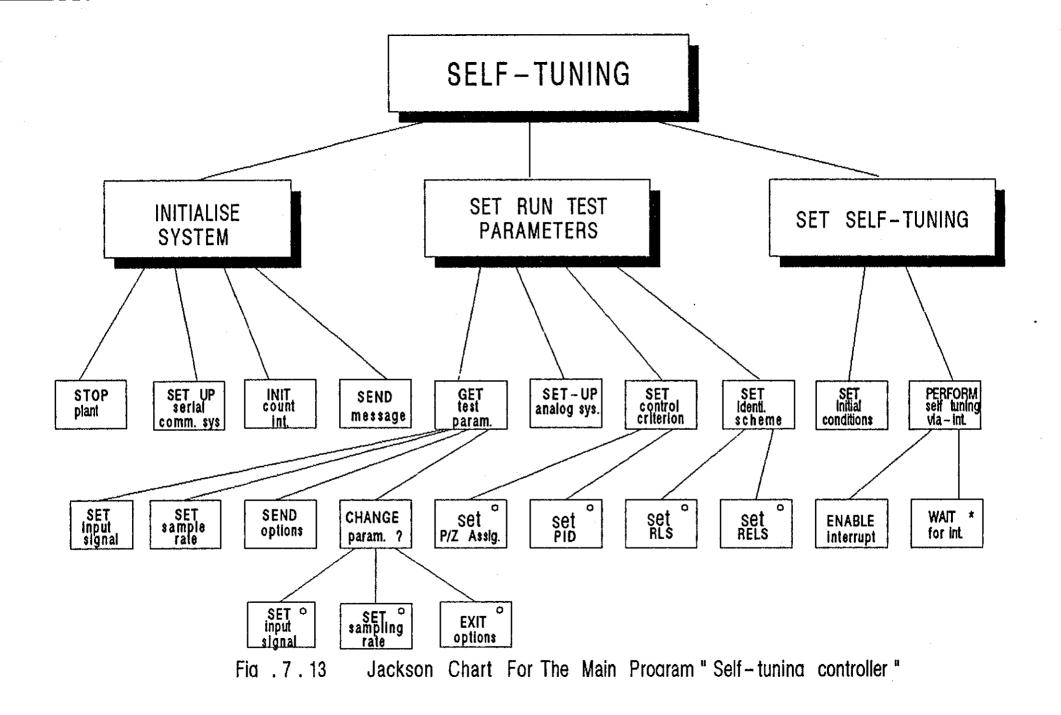

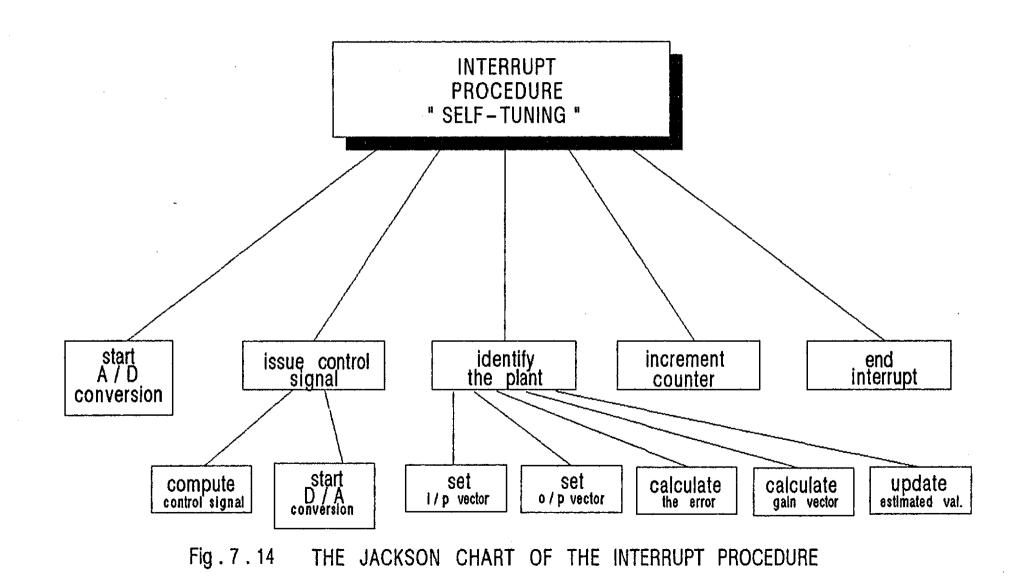

| 7.9 8 | Self-Tuning Controller            | 7 -22 |

| 7.9.1 | Overview                          | 7 -22 |

| 7.9.2 | Initialise System Procedure       | 7 -23 |

| 7.9.3 | Set Run Test Parameters           | 7 -23 |

| 7.9.4 | Run Self-Tuning Procedure         | 7 -24 |

| CHAPTER 8: MODEL DETERMINATION PERFORMANCE - ACTUAL AND SIMULATED |       |  |  |  |

|-------------------------------------------------------------------|-------|--|--|--|

| 8.1 Overview                                                      | 8 - 1 |  |  |  |

| 8.2 The Mathematical Model                                        | 8 - 1 |  |  |  |

| 8.3 Model Order Reduction                                         | 8 - 2 |  |  |  |

| 8.3.1 Overview                                                    | 8 - 2 |  |  |  |

| 8.3.2 Practical Results                                           | 8 - 2 |  |  |  |

| 8.3.3 Simulated Results                                           | 8 - 2 |  |  |  |

| 8.4 Model Trimming 8 - 3                                          |       |  |  |  |

| 8.5 Discussion 8 - 4                                              |       |  |  |  |

|     |     | CHAPTER 9: CLOSED LOOP PERFORMANCE   | TES' | <u>TS</u> |

|-----|-----|--------------------------------------|------|-----------|

| 9.1 | Ove | erview                               | 9 -  | 1         |

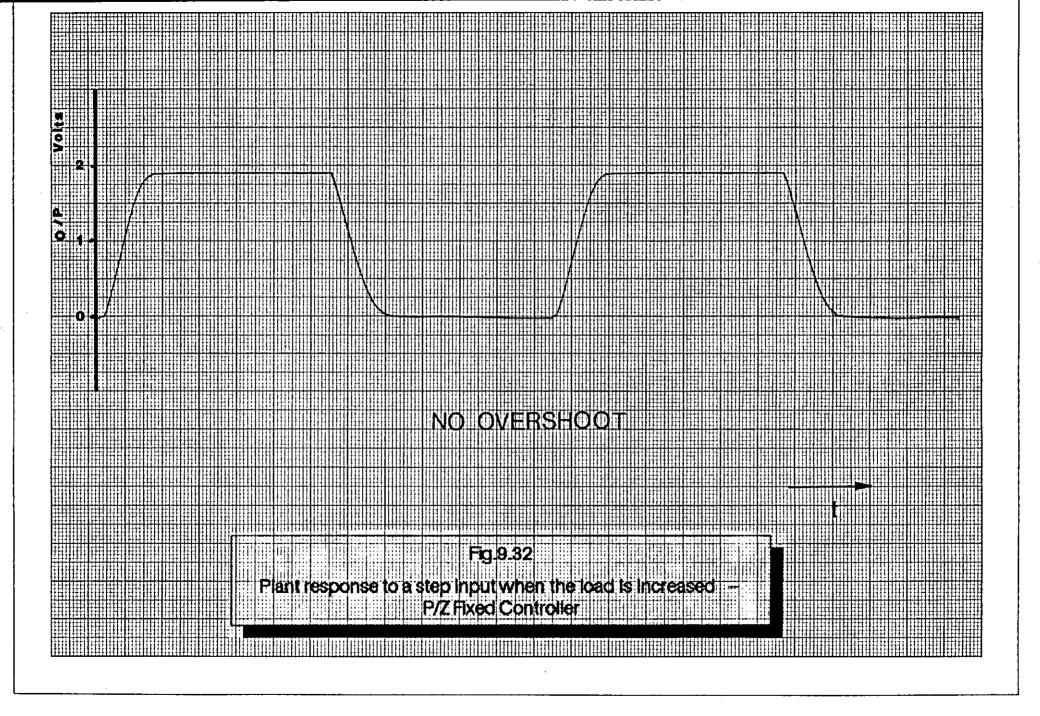

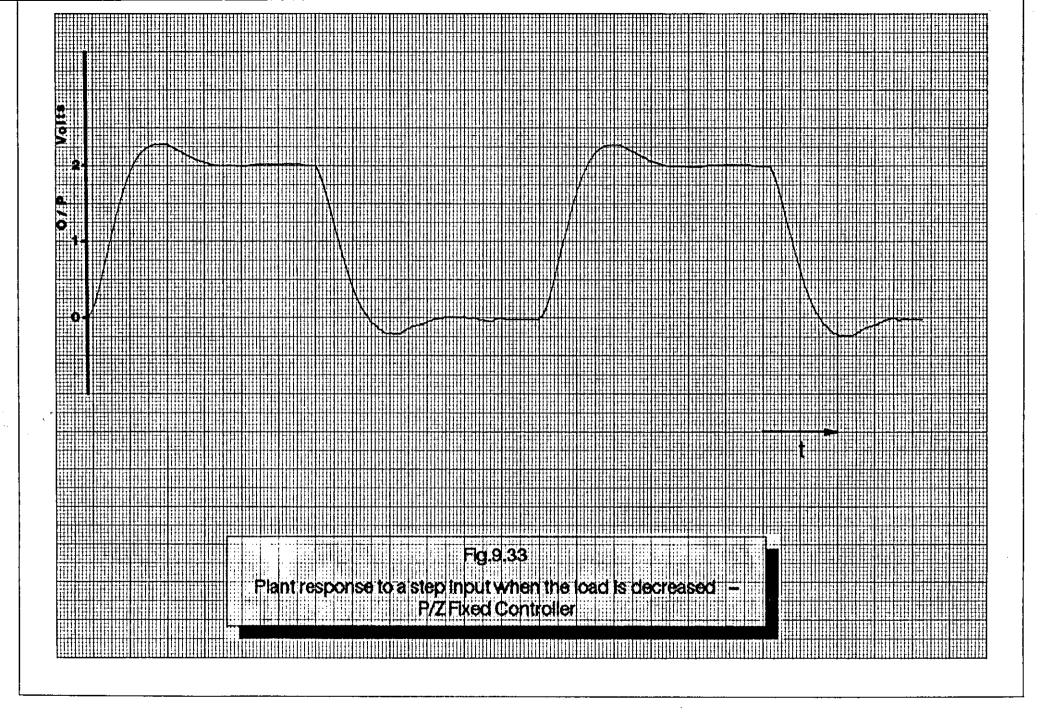

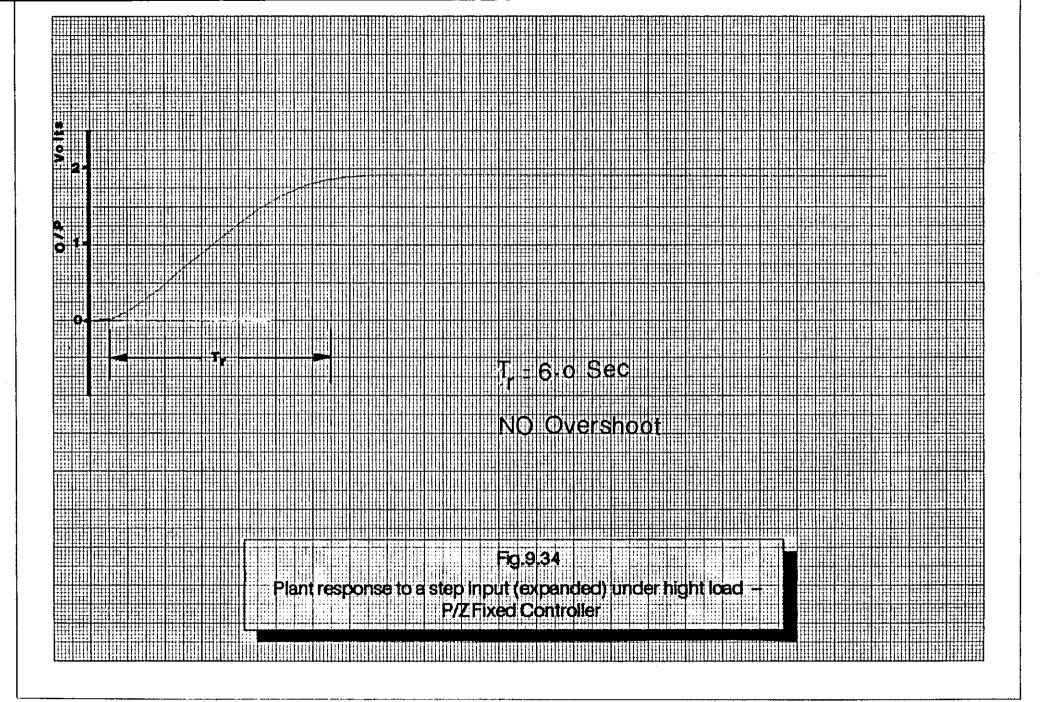

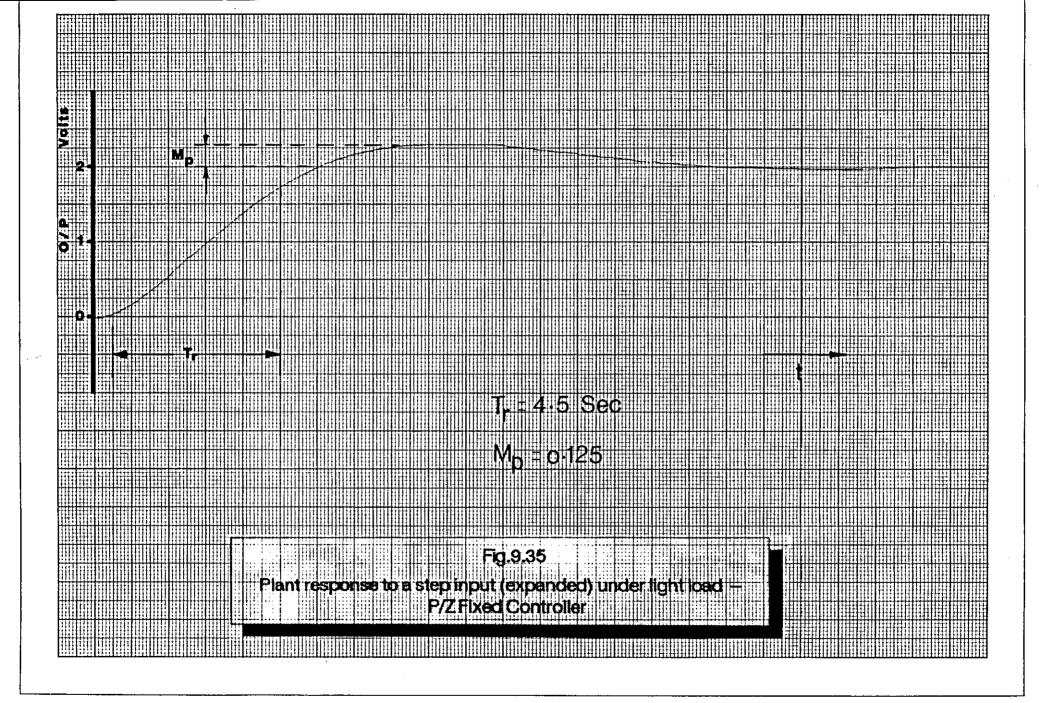

| 9.2 | Tes | t Results – Fixed Digital Controller | 9 -  | 1         |

| 9.  | 2.1 | Overview                             | 9 –  | 1         |

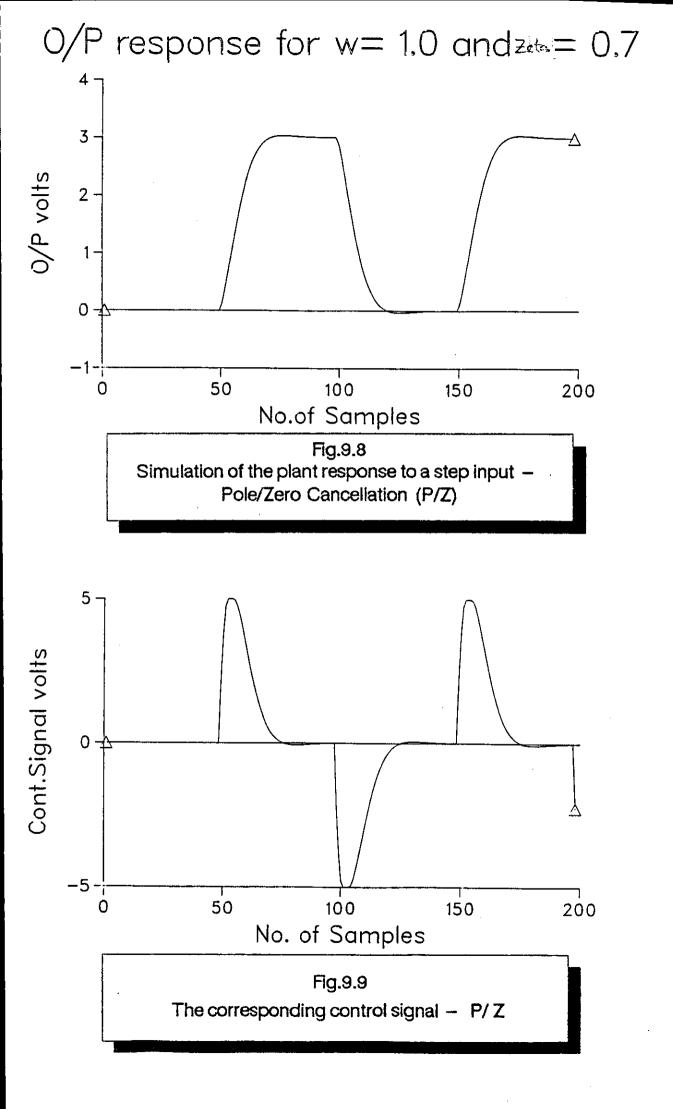

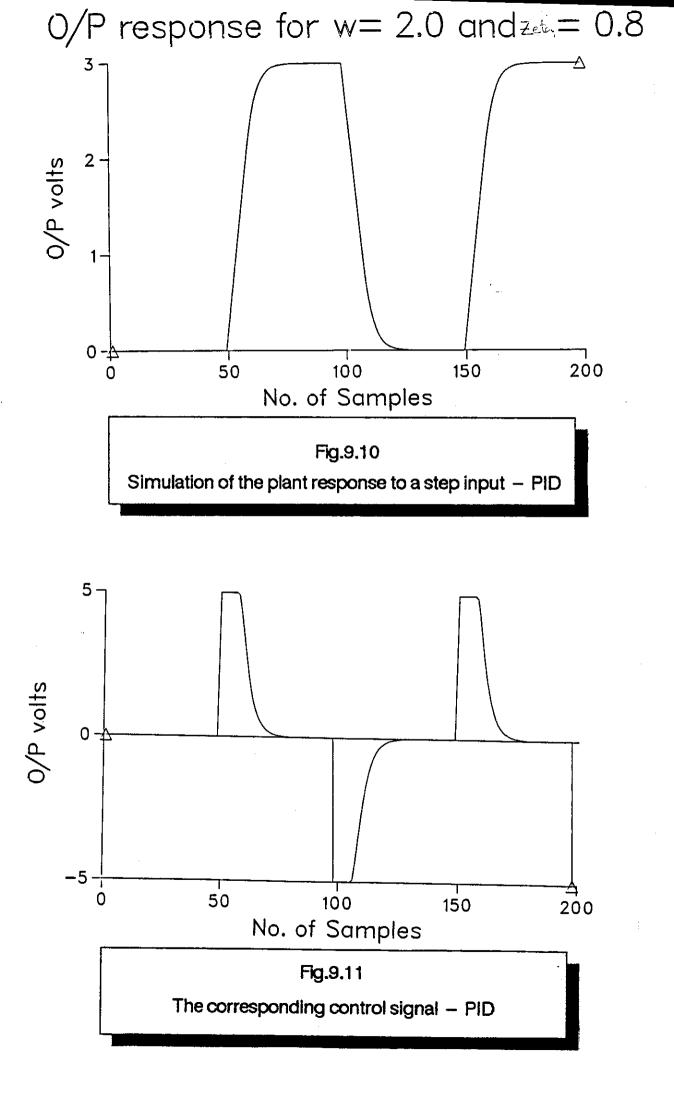

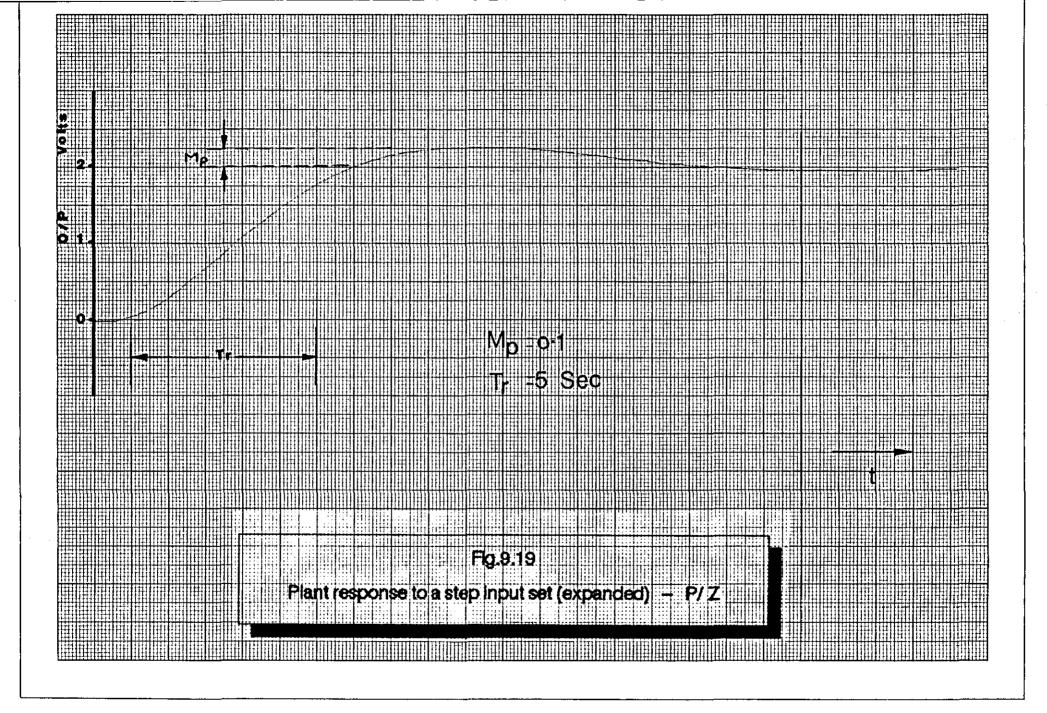

| 9.: | 2.2 | Simulated Results                    | 9 -  | 2         |

| 9.  | 2.3 | Practical Results                    | 9 -  | 4         |

| 9.  | 2.4 | Discussion                           | 9 -  | 5         |

\*

| 9.2.5   | Conclusion                          | 9 - 6 |

|---------|-------------------------------------|-------|

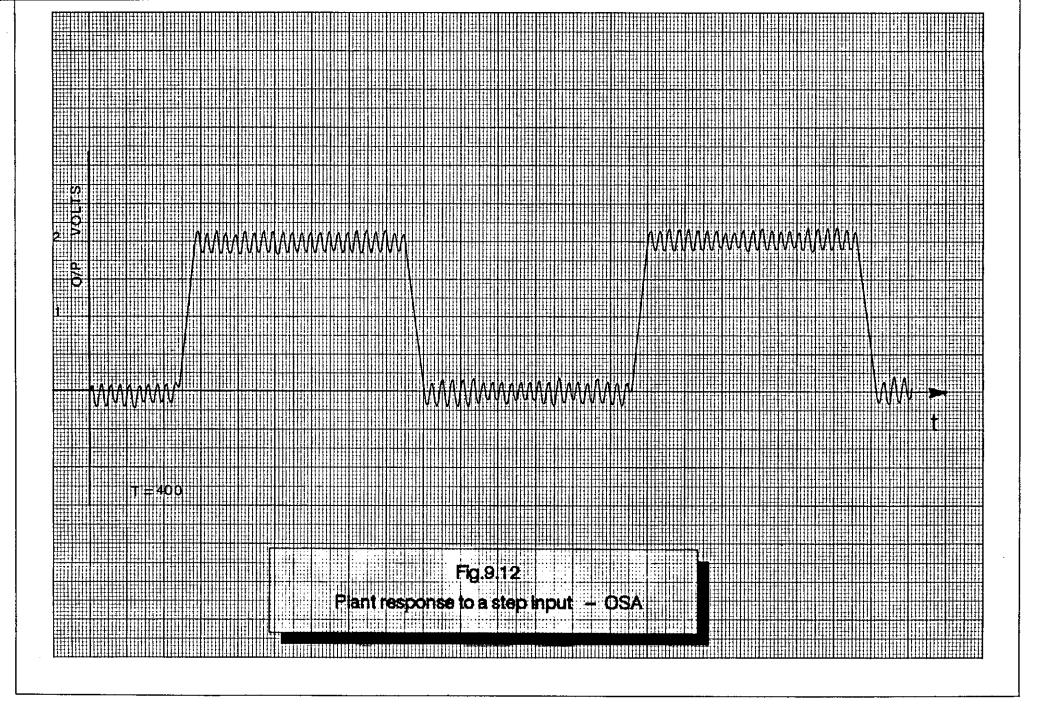

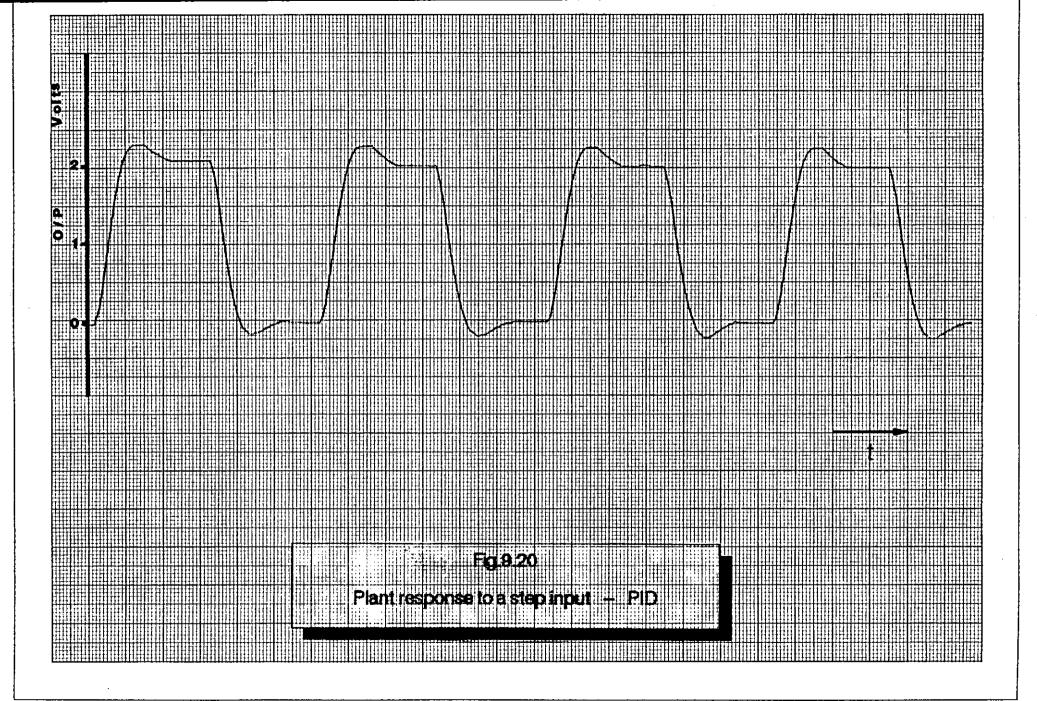

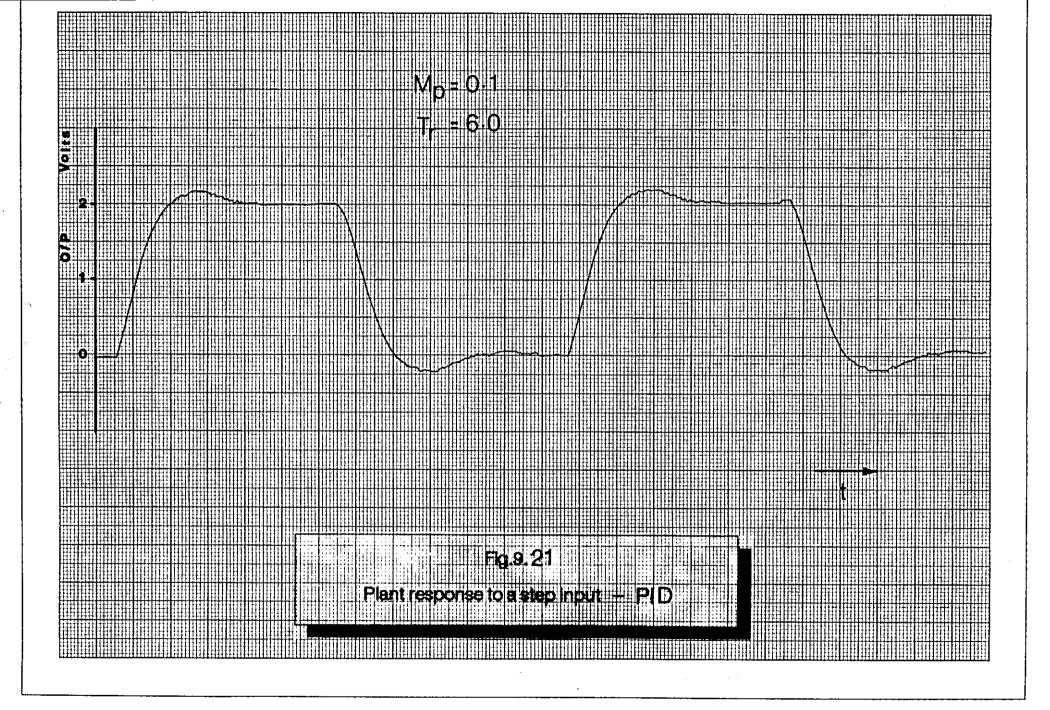

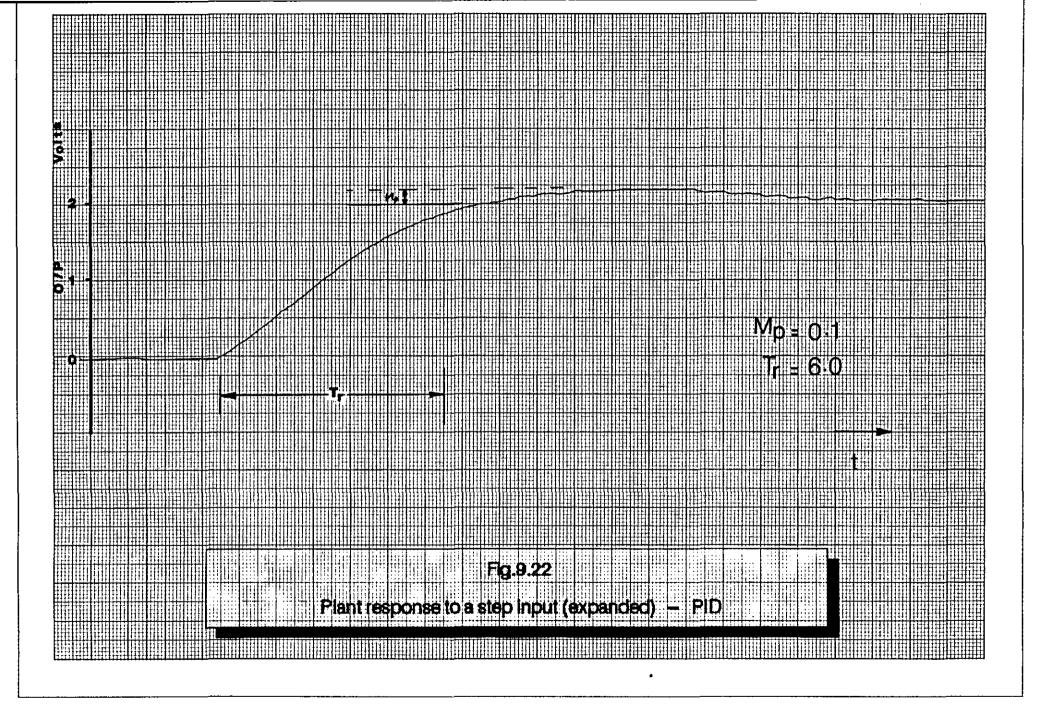

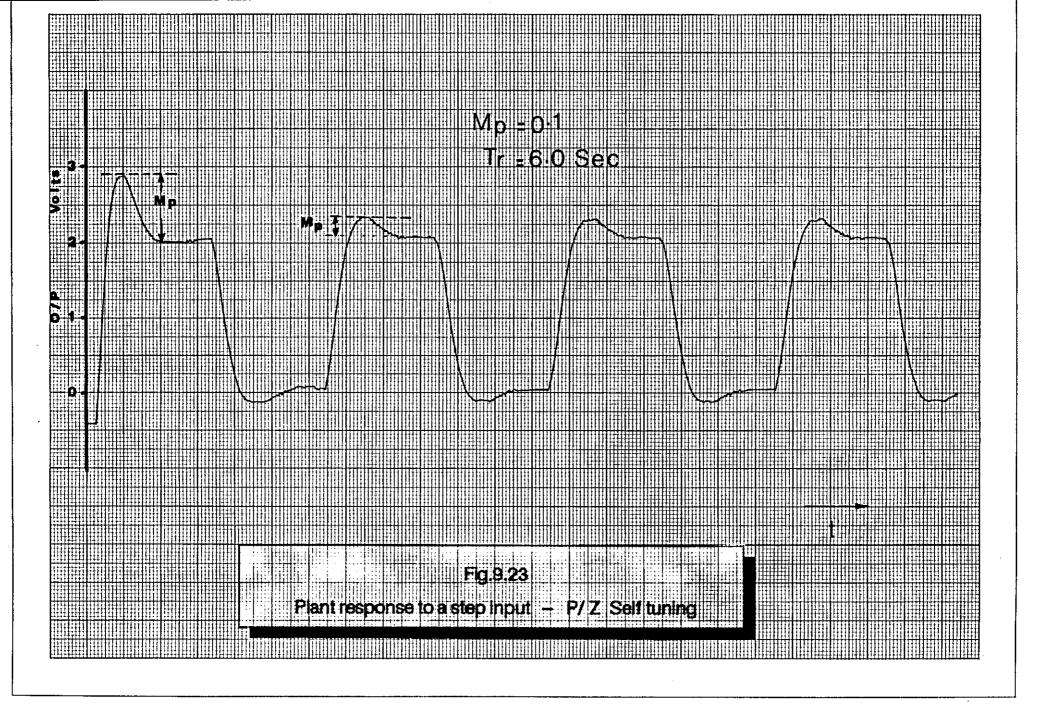

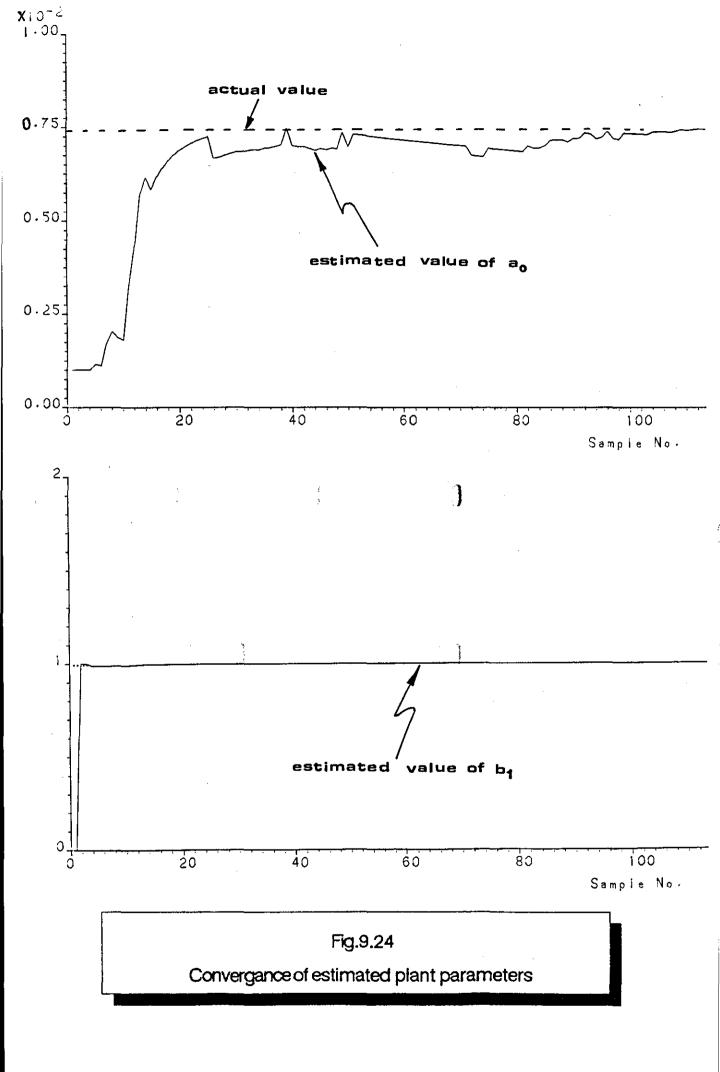

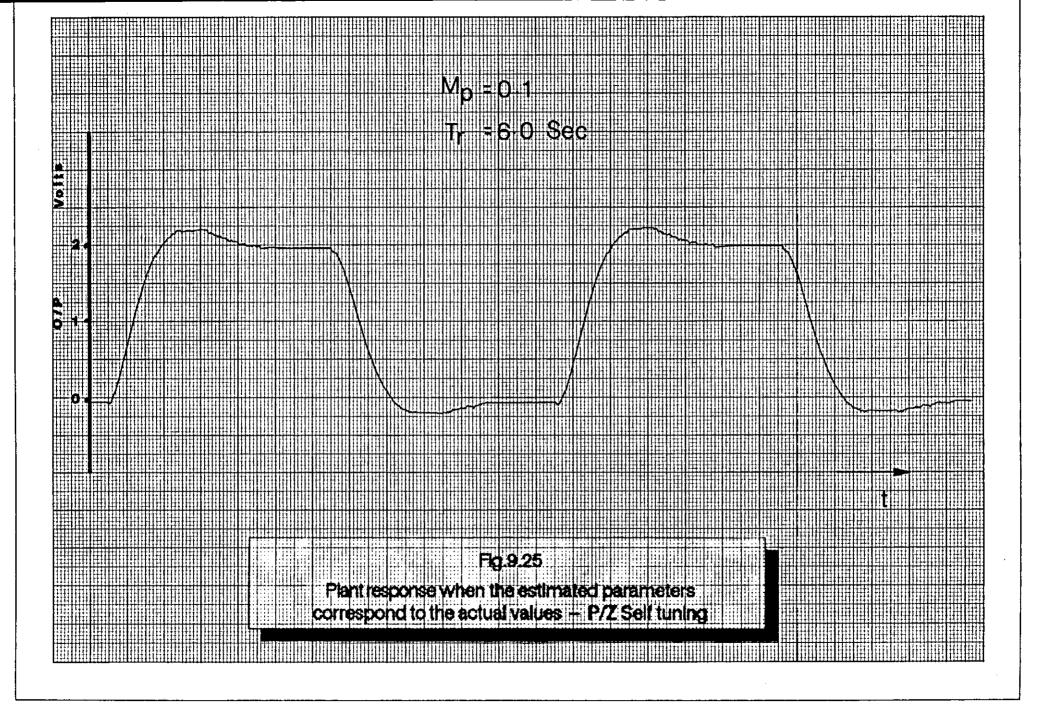

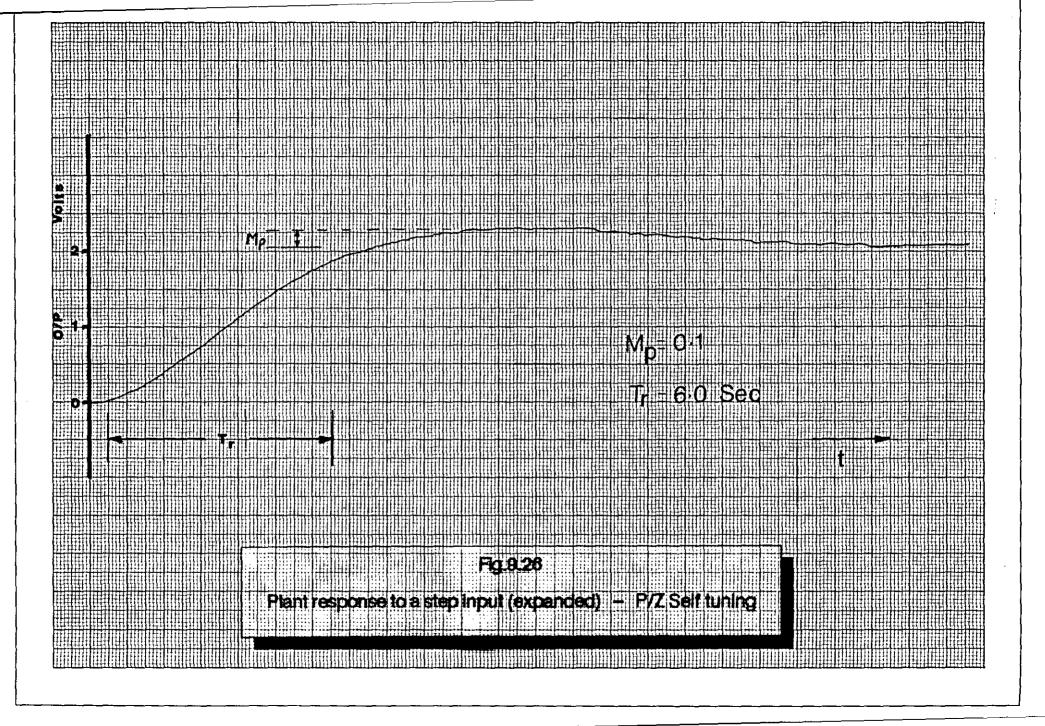

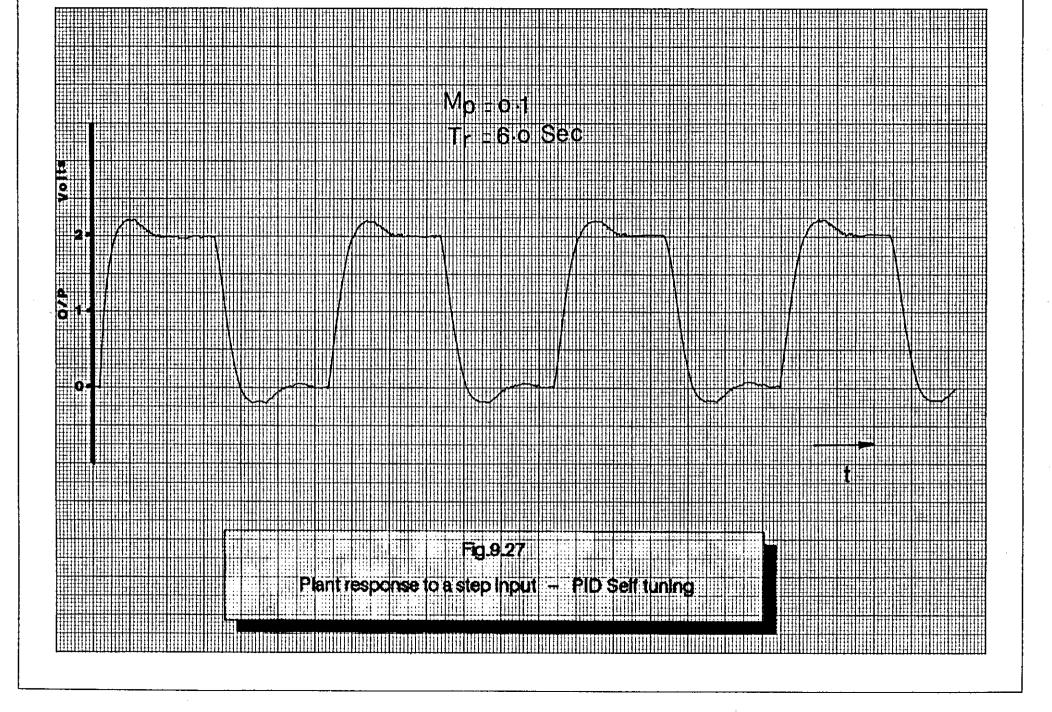

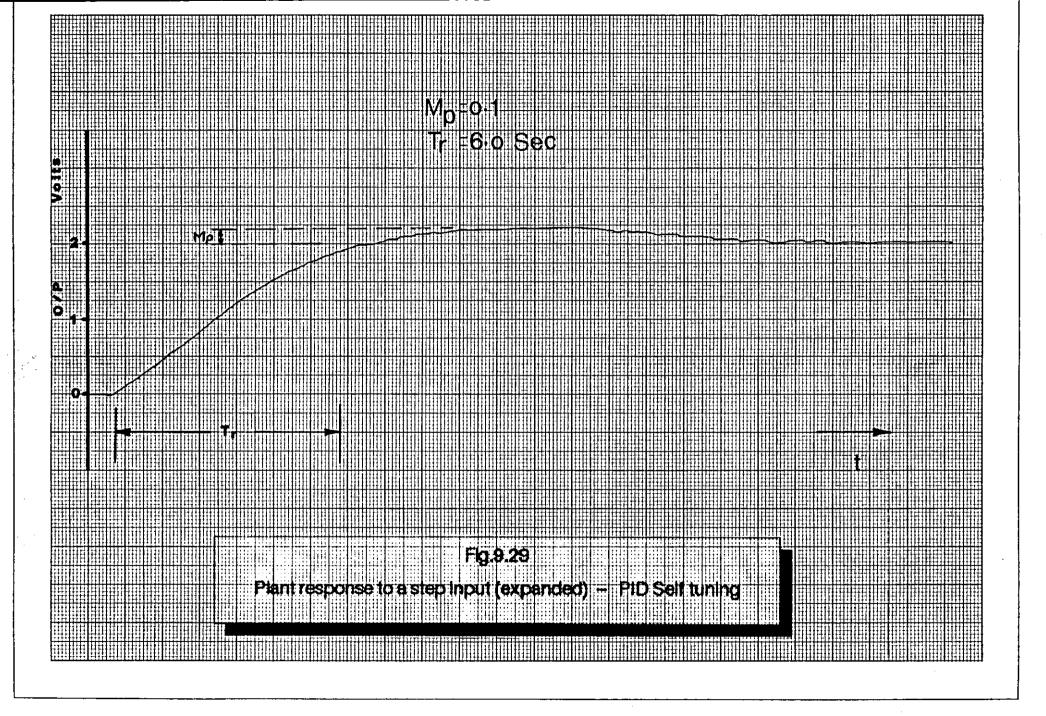

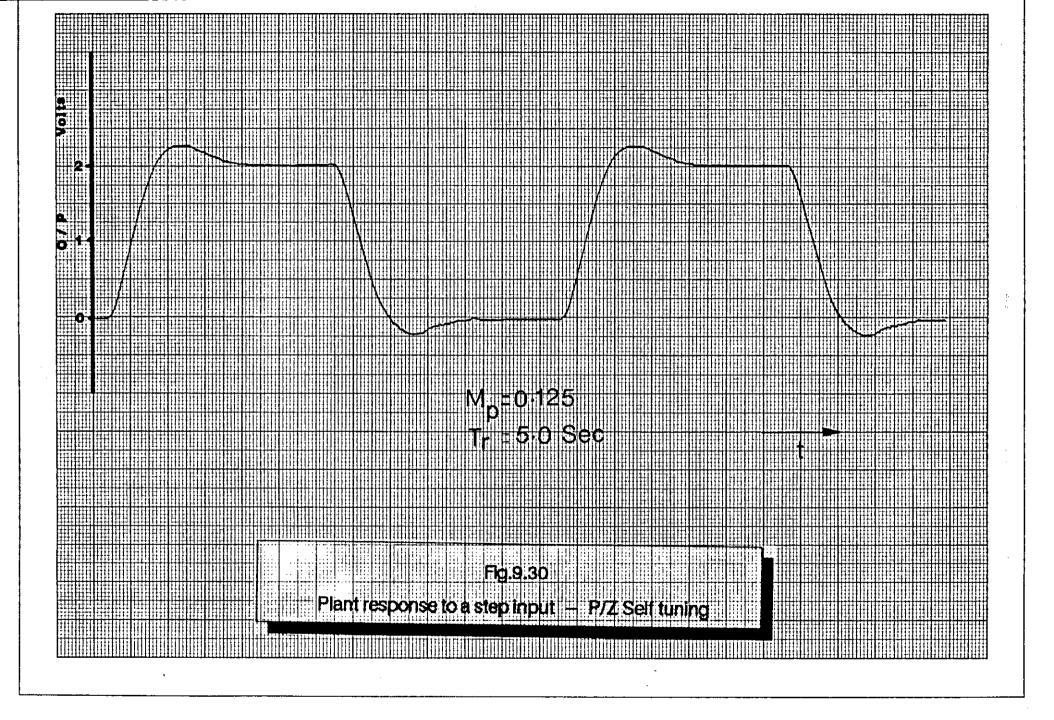

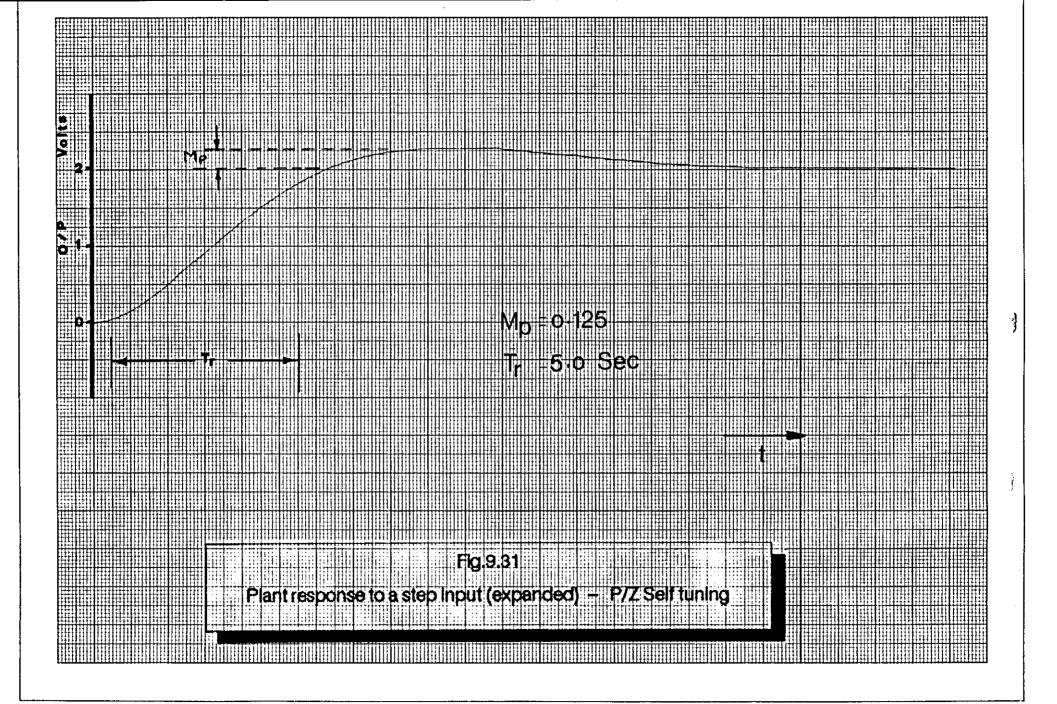

| 9.3 Tes | st Results – Self-Tuning Controller | 9 - 7 |

| 9.3.1   | Overview                            | 9 - 7 |

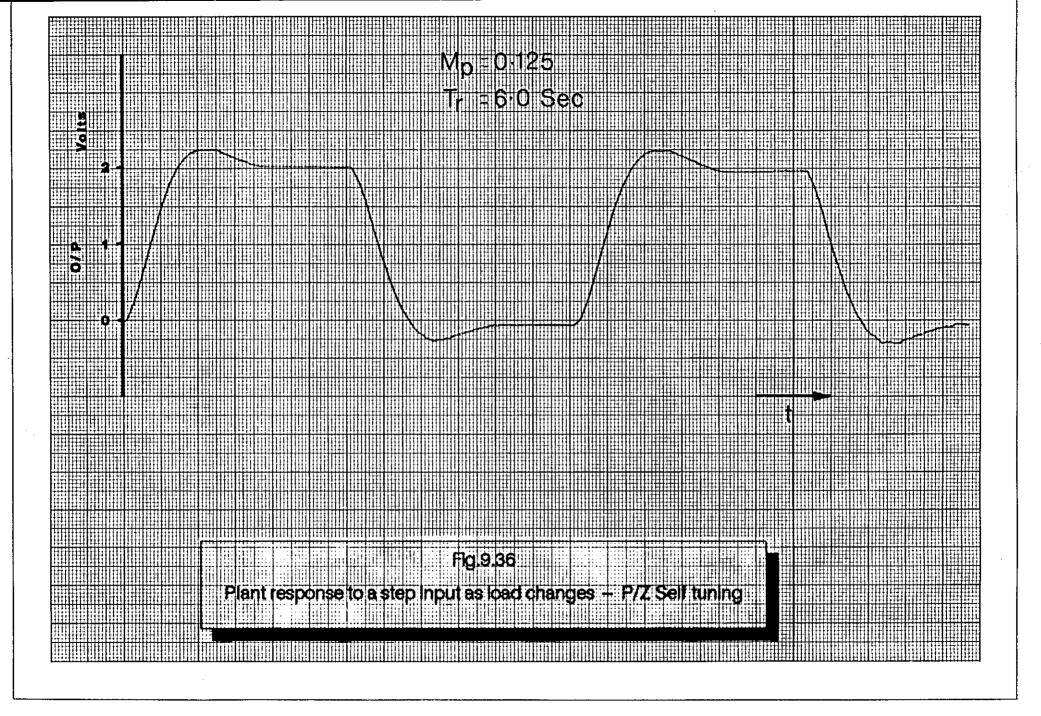

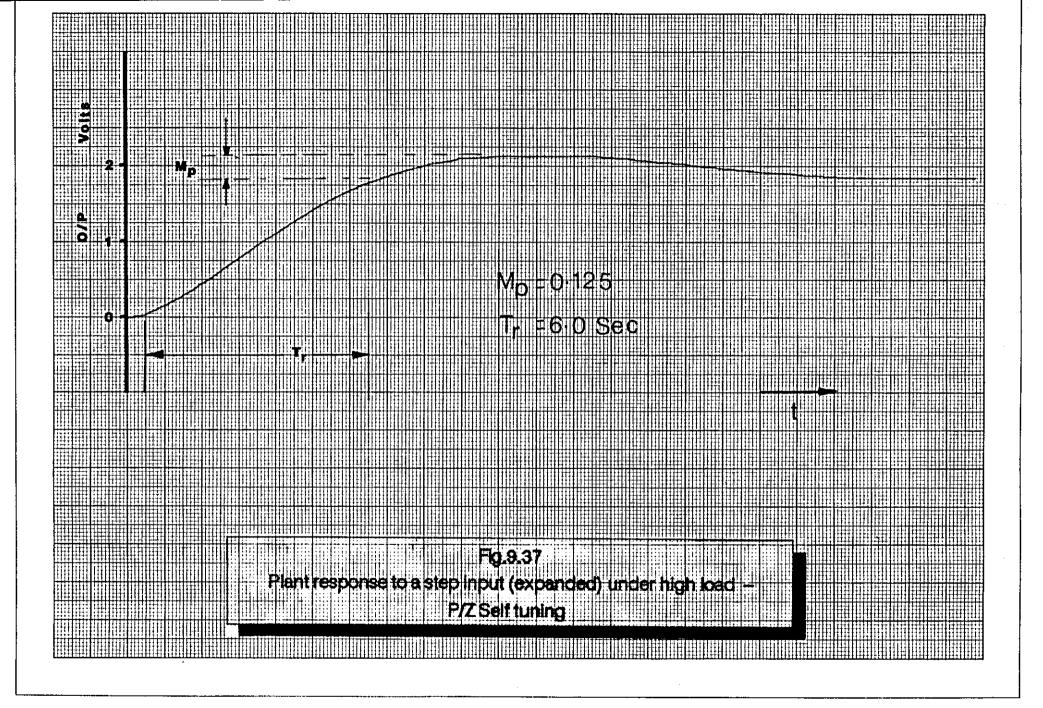

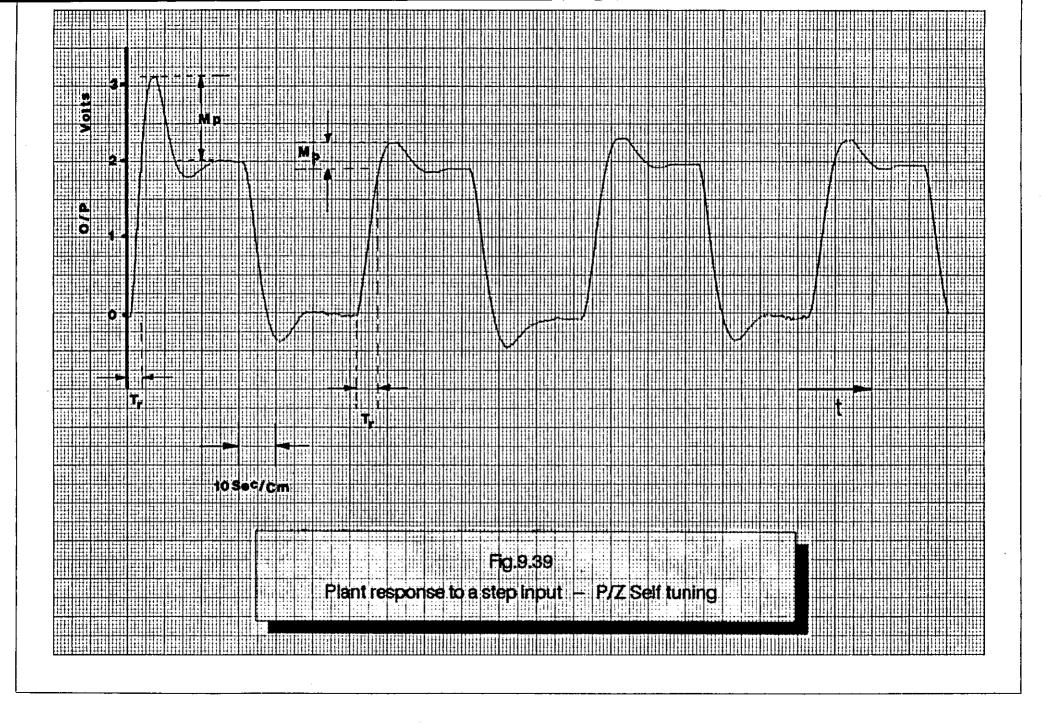

| 9.3.2   | Fixed Load                          | 9 - 7 |

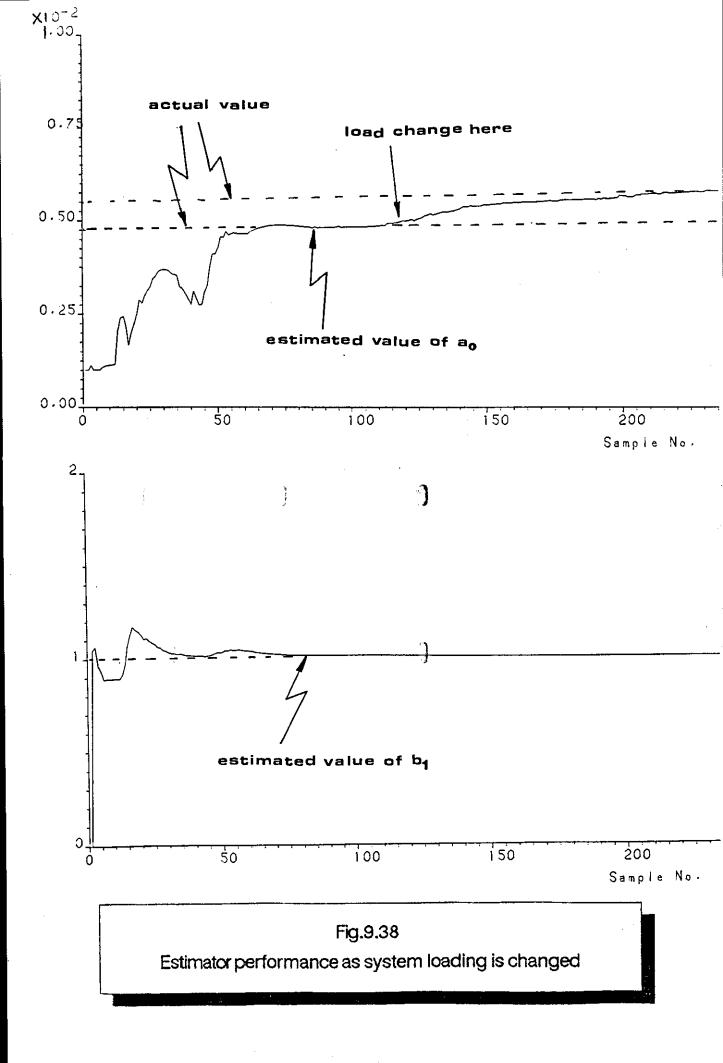

| 9.3.3   | Variable Load                       | 9 - 8 |

| 9.3.4   | Discussion                          | 9 - 8 |

## CHAPTER 10: CONCLUSION

| 10.1 | A General Comment           | 10- 1 |

|------|-----------------------------|-------|

| 10.2 | Conclusions                 | 10- 2 |

| 10.3 | Suggestion For Further Work | 10- 2 |

## APPENDIX A: THE CONTROLLED PLANT

| A.1 | Gei | neral Description           | A | - | 1 |

|-----|-----|-----------------------------|---|---|---|

| A.2 | Me  | chanical Description        | A |   | 2 |

| A.3 | Ele | ctronics                    | A | - | 3 |

| А.  | 3.1 | Analogue Interface Board    | A | - | 4 |

| А.  | 3.2 | Inverter/Actuator Structure | A | - | 5 |

## APPENDIX B: SYSTEM IDENTIFICATION

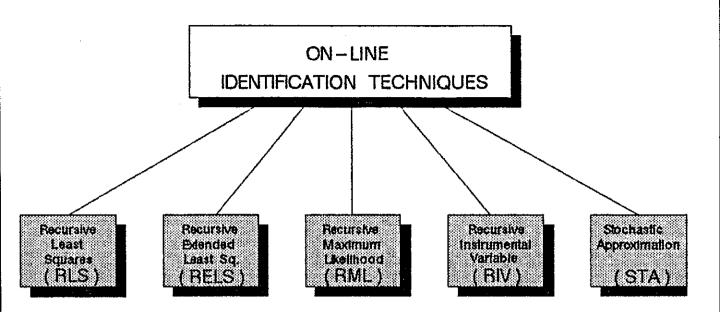

| B.1 Parameter Estimation Methods            | B - 1 |

|---------------------------------------------|-------|

| B.2 Models                                  | B - 2 |

| B.3 A General Criterion                     | B - 3 |

| B.4 Recursive Least Squares (RLS)           | в – 7 |

| B.4.1 General                               | B - 7 |

| B.4.2 The Algorithm                         | B - 8 |

| B.5 Recursive Extended Least Squares (RELS) | в –10 |

| B.5.1   | General                               | B -10        |

|---------|---------------------------------------|--------------|

| B.5.2   | The Algorithm                         | B -11        |

| B.3 Re  | cursive Maximum Likelihood (RML)      | B -13        |

| B.3.1   | General                               | B -13        |

| в.3.2   | The Algorithm                         | в -14        |

| B.4 Re  | cursive Instrumental Variable (RIV)   | B -15        |

| B.4.1   | General                               | в <b>-15</b> |

| B.4.2   | The Algorithm                         | B -16        |

| B.5 Sto | ochastic Approximation (STA)          | B -18        |

| B.5.1   | General                               | в -18        |

| B.5.2   | The Algorithm                         | B -18        |

| B.6 Ini | tial Values                           | в -20        |

| B.7 Rea | al Time Version                       | в -20        |

| B.8 Imp | provement of The Convergence Rate     | в -22        |

| B.9 Cor | nparisons                             | B -23        |

| B.9.1   | Overall Comparison of The Performance | в -23        |

| B.9.2   | Properties of Each Method             | в -23        |

| в.9.3   | Conclusion                            | B -24        |

APPENDIX C: CONTROLLER DESIGN TECHNIQUES

| C.1 One-Step-Ahead Control               | C - 1 |

|------------------------------------------|-------|

| C.2 Weighted One-Step-Ahead Control      | C - 3 |

| C.3 Pole/Zero Cancellation               | C - 5 |

| C.3.1 General                            | C - 5 |

| C.3.2 The Design of The Plant Controller | C - 8 |

| C.3.3 The Design Algorithm               | C -12 |

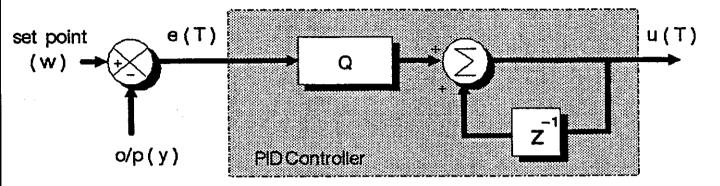

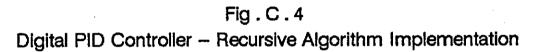

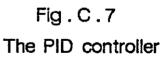

| C.4 PID Controller                       | C -14 |

C.5 Execution Times

C -19

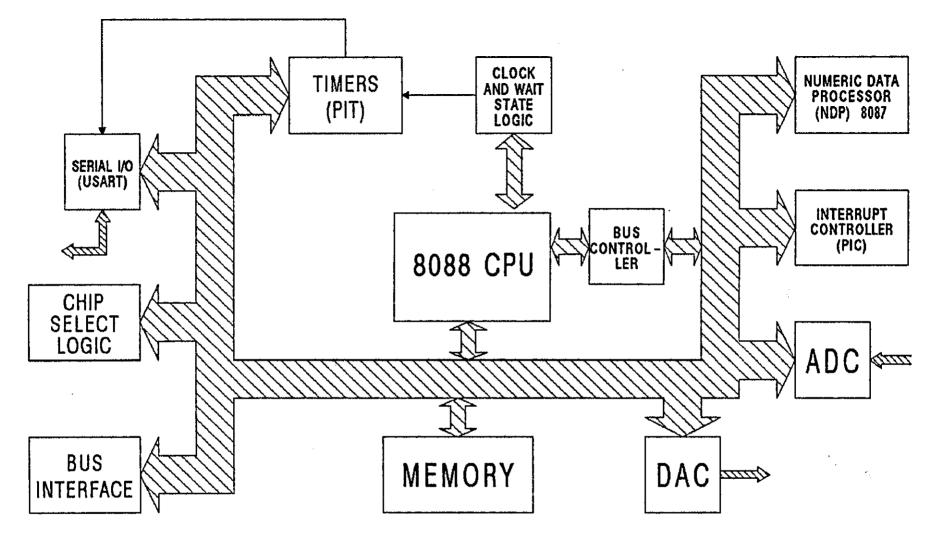

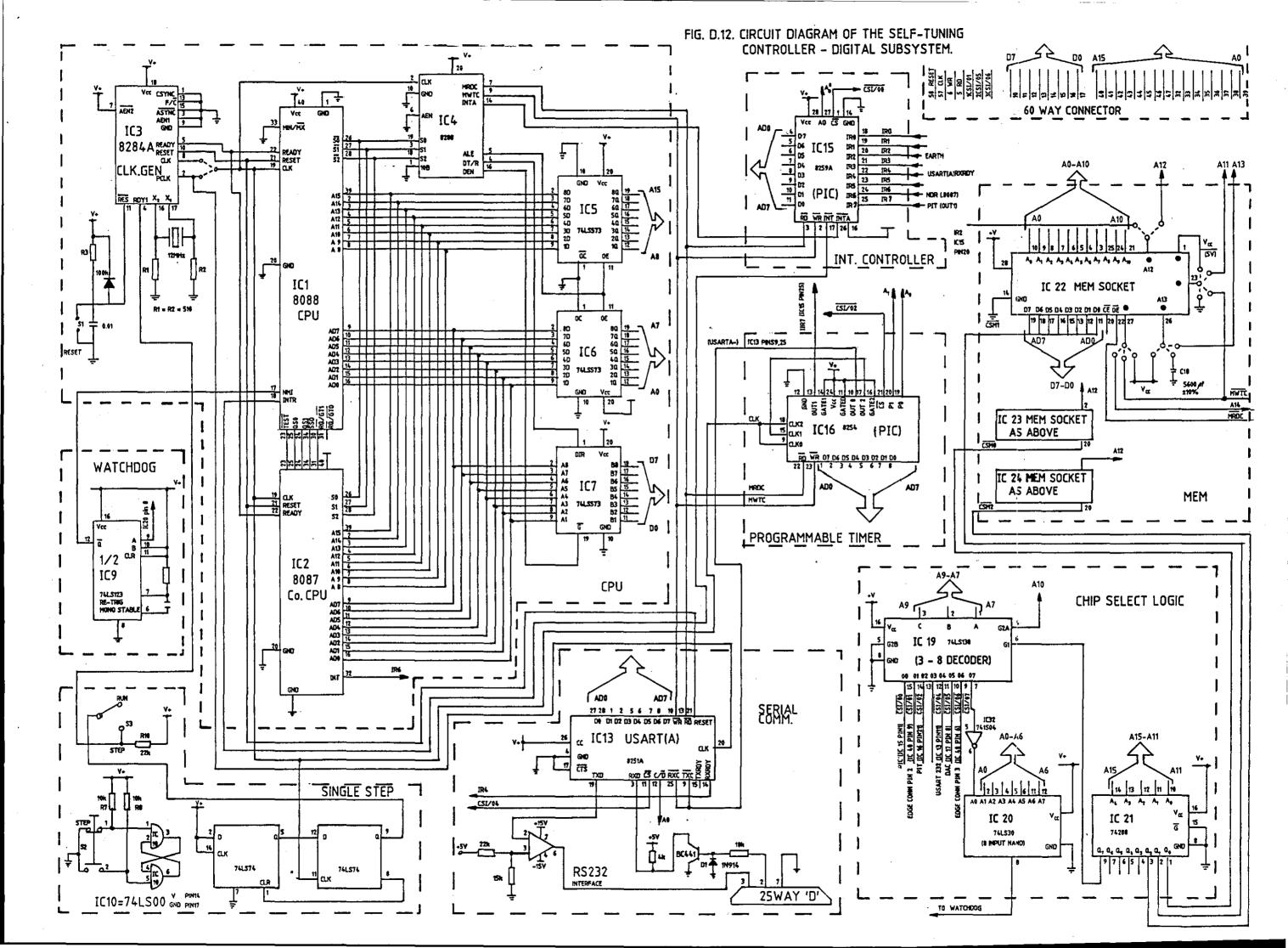

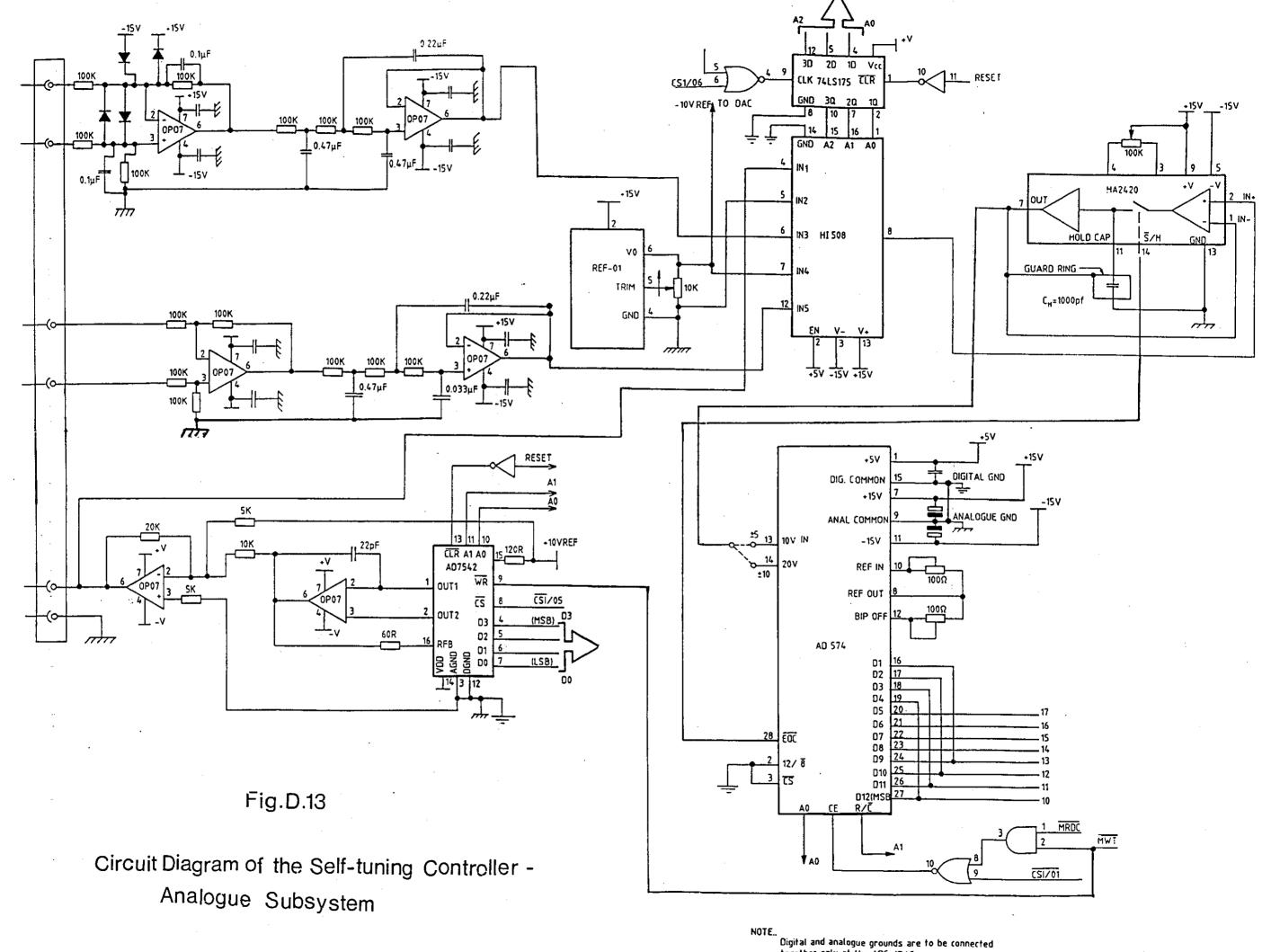

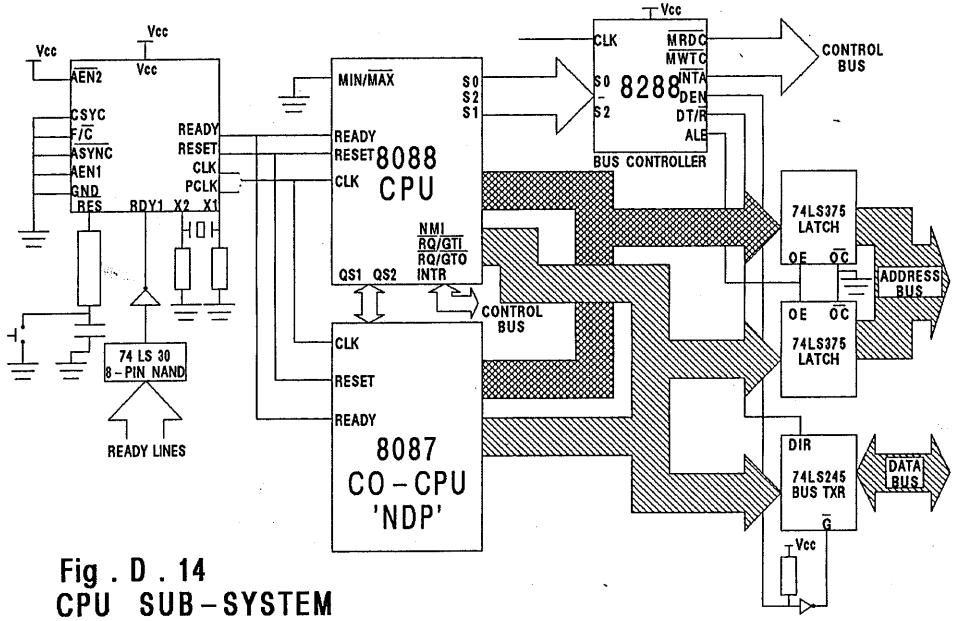

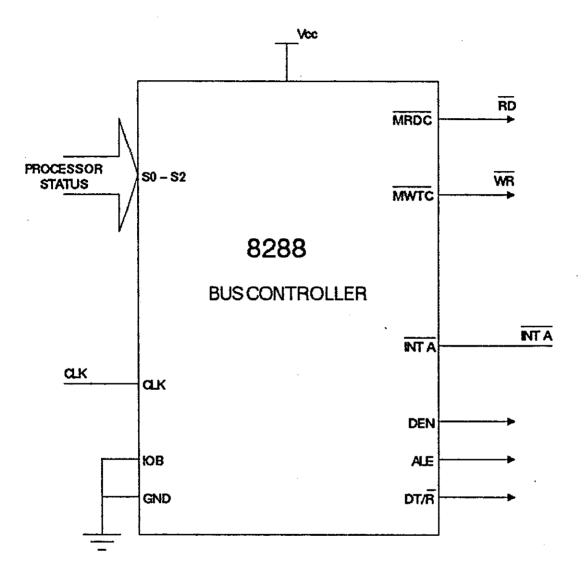

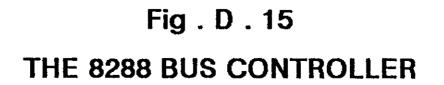

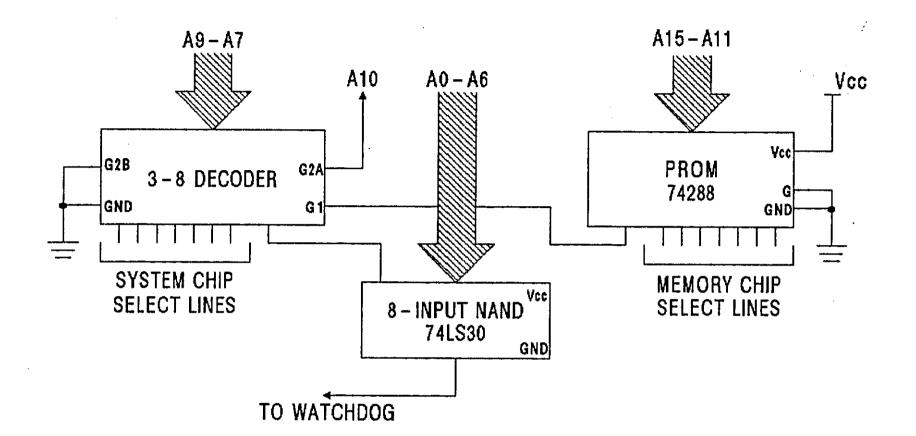

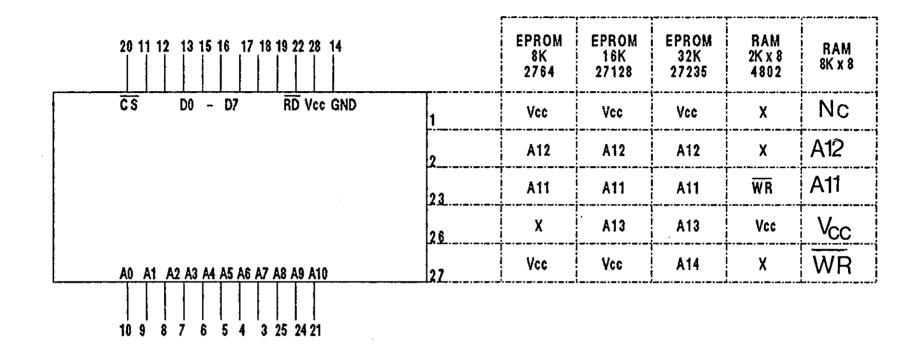

|        | APPENDIX D: SELF-TUNING CONTROLLER - | HARDWARE |

|--------|--------------------------------------|----------|

| D.1 Ta | rget Board System Description        | D - 1    |

| D.1.1  | Overall Structure                    | D - 1    |

| D.1.2  | System Design - Details              | D - 4    |

| D.2 Ha | rdware Design                        | D -13    |

| D.2.1  | Overview                             | D -13    |

| D.2.2  | Central Processing Unit              | D -13    |

| D.2.3  | Numeric Data Processor               | D -15    |

| D.2.3  | Memory                               | D -15    |

| D.2.4  | Interrupts                           | D -16    |

| D.2.5  | Programmable Timer                   | D -18    |

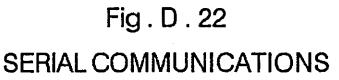

| D.2.6  | Serial Communications Port           | D -19    |

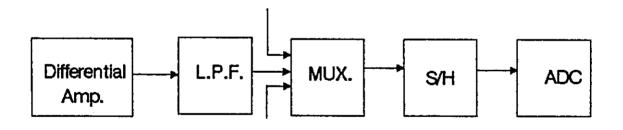

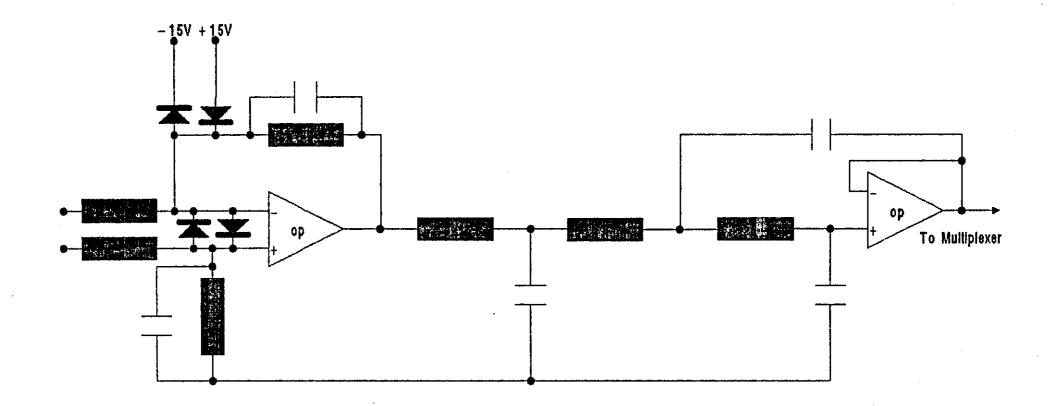

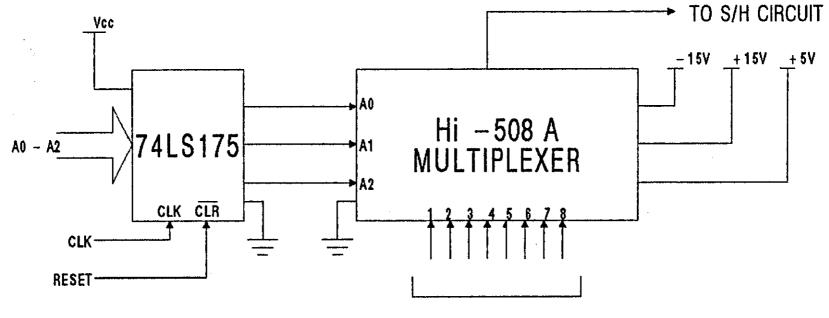

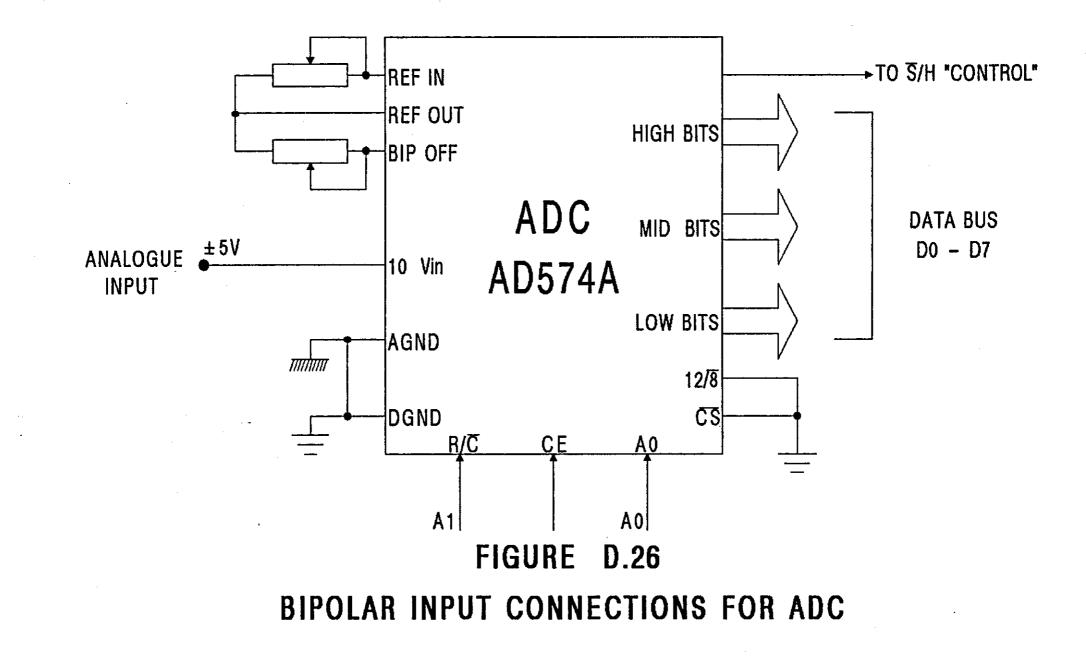

| D.2.7  | Analogue Input                       | D -20    |

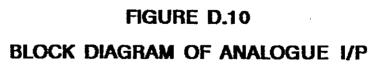

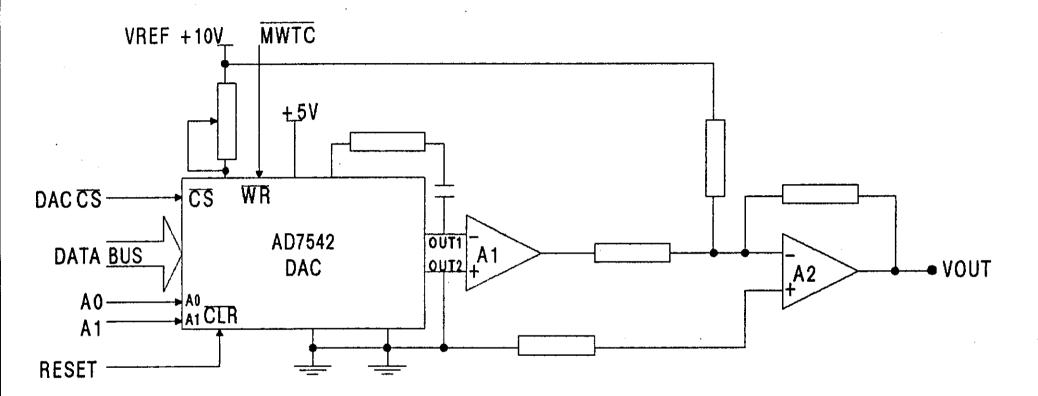

| D.2.8  | Analogue Output                      | D -22    |

| D.2.9  | Power Supplies                       | D -23    |

### APPENDIX E: MODEL DETERMINATION

| E.1 Ov | verview                                    | E | - | 1 |

|--------|--------------------------------------------|---|---|---|

| E.2 Th | e Effect of Assuming a Higher Order Model  | E | - | 1 |

| E.2.1  | Simulation Results                         | Е |   | 2 |

| E.2.2  | Practical Results                          | Е | - | 3 |

| E.3 St | atic Gain                                  | Ε | - | 4 |

| E.4 Te | chniques To Improve Pole/Zero cancellation | E | - | 5 |

| E.4.1  | Scale The Reduced Order Model              | Ε | - | 5 |

| E.4.2  | Retain Static Gain During Optimisation     | Е | - | 6 |

| E.4 | 1.3 Amend a Zero or a Pole        | E - | . ' | 7 |

|-----|-----------------------------------|-----|-----|---|

| E.5 | Effect of Negligible Coefficients | E - |     | 7 |

| E.6 | Model Trimming                    | E - |     | € |

## REFERENCES

# CHAPTER-1

### **1** INTRODUCTION

### 1.1 CONTROL SYSTEMS

### 1.1.1 General

Control systems vary considerably. At one extreme are fast high performance systems such as weapon stabilisers. In such applications many aspects of the design are new and unique, the related control design effort being considerable. At the other end are process systems where the control engineer is asked merely to supply a three-term controller. Here the control design is minimal (though the system design may be considerable).

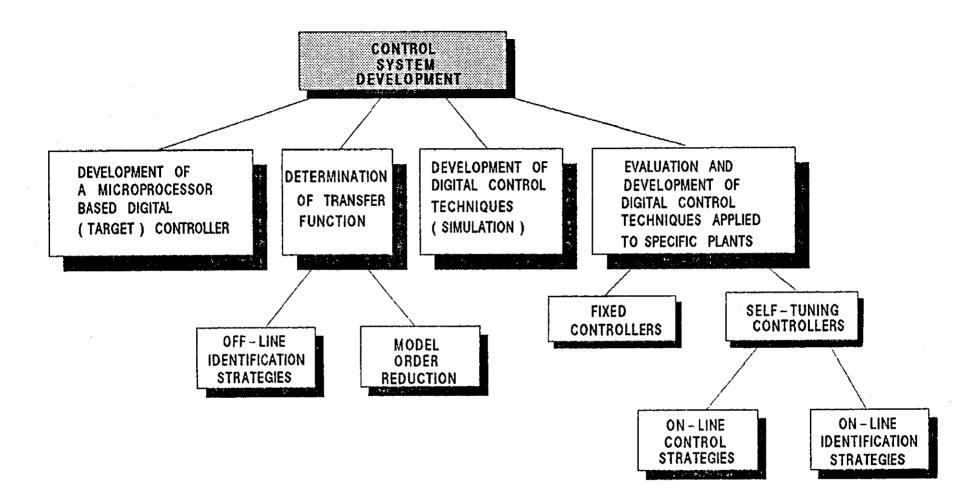

The system described here, together with relevant research and design techniques, falls into the first category. Fig.1.1 shows the main objectives of the programme, these being the development of the target system controller and the development of appropriate control techniques. The target system ("plant") is a real as opposed to a simulated one, being described in section 1.2

### 1.1.2 Control system design methods

Numerous control techniques are available for use in the design of control systems [1.1]. These are divided into two major categories, optimal control techniques [1.2] and classical control techniques [1.3].

In optimal control, widely used in the aerospace industries, the objective is to minimise a specified cost function. These methods are highly mathematical. As a result most practical engineers do not understand optimal methods; neither can they specify their system performance requirements in a relatively straightforward

manner. Highly skilled and specialised engineers are needed in such situations. It is therefore not surprising that these techniques are not widely accepted in control system work.

In contrast classical control techniques are widely used because;

- \* they are relatively simple,

- \* they are well understood by practical engineers,

- \* performance criteria can be specified simply and unambiguously in both the time and frequency domains.

Here the tuning of the controller is adjusted as required by the plant engineer, controller settings being based on both experience and trial and error techniques [1.4].

Self-tuning designs using classically specified performance criteria are serious contenders for use in modern control systems. In such systems the controller is adjusted automatically until (hopefully) the specified performance is achieved. Therefore tuning does not require operator experience or involvement, an added feature of self-tuning controllers.

### <u>1.1.3 Self-tuning systems</u>

Adaptive self-tuning systems have been the subject of a great deal of research effort in recent years, a major review being given by Warwick [1.5]. Practical applications have lagged behind such work, in the main being applied in the process industries (1.6,1.7,1.8,1.9). Few servo applications have been reported, though the advantages of self-tuners in these areas have been shown by Daley [1.10] and Hope [1.11]. The wide bandwidths and demanding performance specifications raise problems not found in the process world. In fact such problems have lead researchers to develop alternative adaptive control techniques [1.12].

### 1.2 THE CONTROLLED PLANT

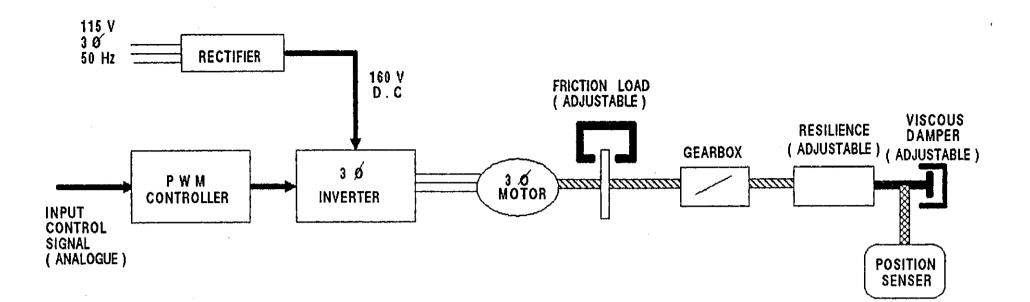

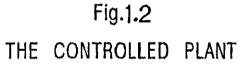

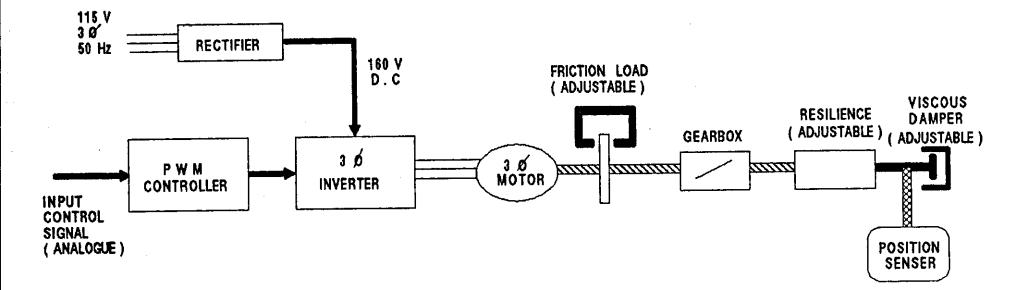

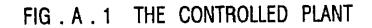

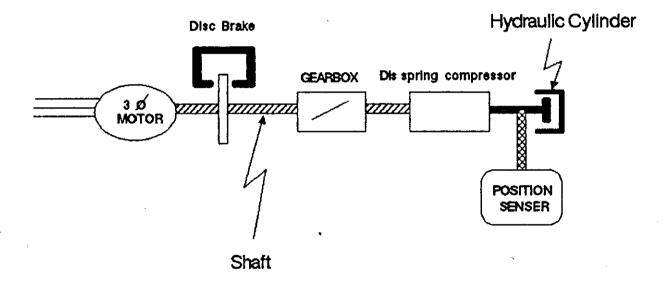

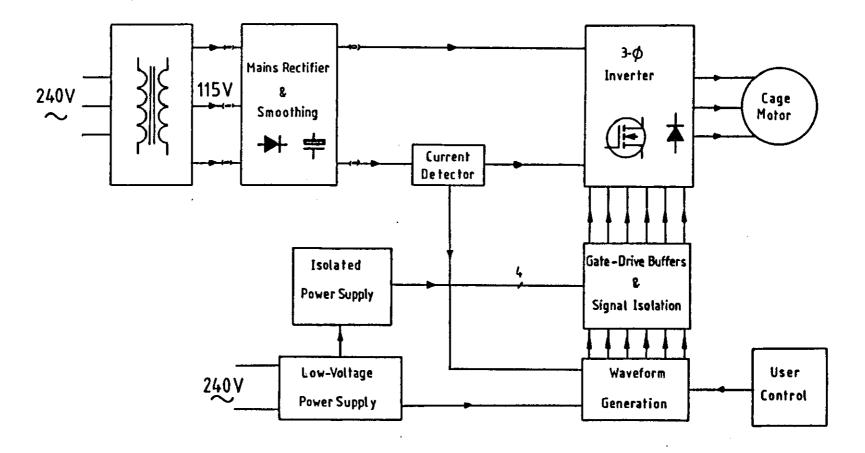

A block diagram of the "plant" used for control system development is shown in Fig.1.2, Fig.1.3 being a photo of the actual test rig. This is an electromechanical actuator (suitable for the use with process control valves) coupled to a mechnical load simulator. The actuator motor and associated control/power electronics are considered to be part of the plant itself, as is the load shaft position sensor.

The drive unit of the actuator is a 1/6 horse power induction motor, originally designed for 115v. 60 Hz. 3 phase operation. It is powered from a static inverter which, when used with its controller, provides full linear speed control from zero to maximum speed in both directions.

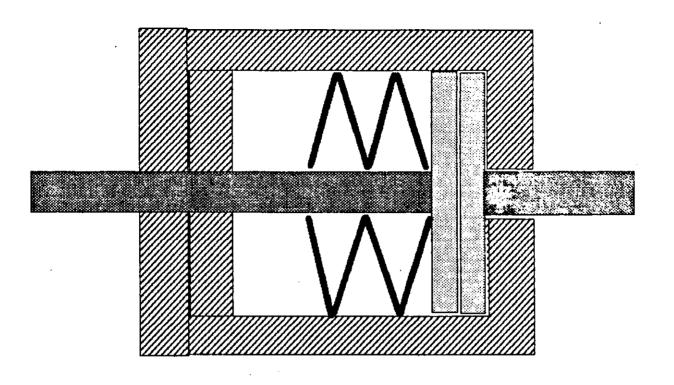

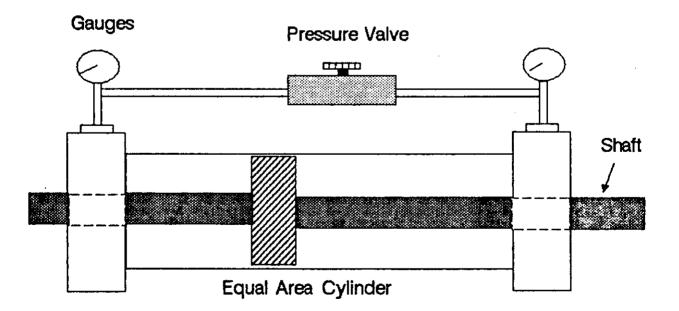

A gearbox is used to translate motor shaft rotary motion to linear motion of the load shaft. Both the load resilience and viscous forces can be varied by the rig operator. Further, the effect of valve loading is simulated using a coulomb damper (actually a disc brake) on the motor shaft; this, too, is adjustable. Position sensing is carried out using a continuous track rectilinear potentiometer.

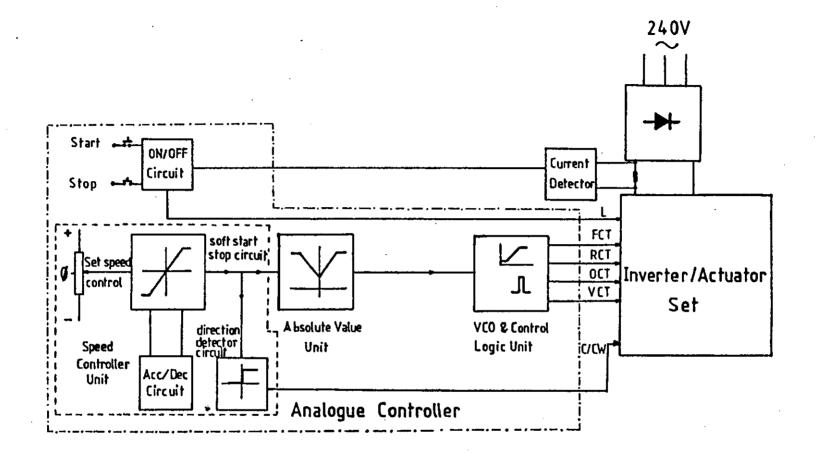

Motor speed control is carried out by a pulse width modulated (PWM) controller in conjunction with a 3 phase static inverter [1.13]. Motor speed is determined by the analogue input signal to the controller. A detailed description of the plant is shown in Appendix-A.

### 1.3 SYSTEM DEVELOPMENT IN A PC ENVIRONMENT

Computerised tools for the analysis, synthesis and development of control systems have generally been based on the use of Mainframe and Mini computers. Typical of such packages are CAD on PRIME [1.14] and MATRIXX on the VAX [1.15]. Recently, however, much attention has been focussed on low cost alternatives using

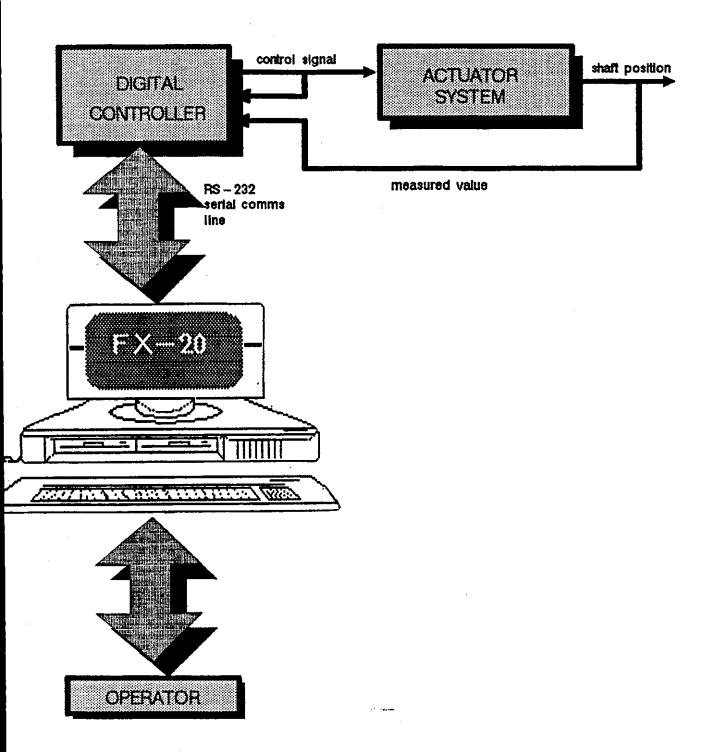

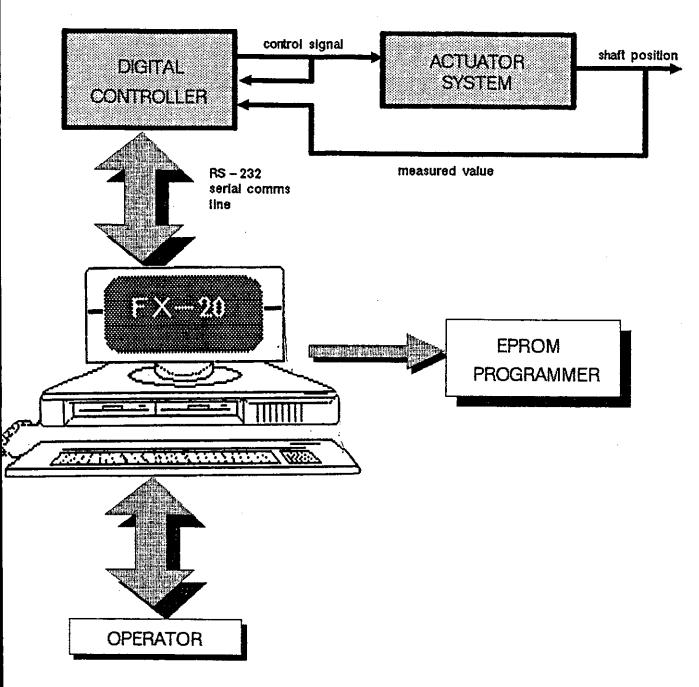

personal computers (PCs). In many cases the emphasis has been on training, analysis and theoretical synthesis [1.16]. Little has been reported concerning their use in the development of practical embedded systems, typified by servo applications. Yet the PC can provide many facilities needed for all phases of the research and design activity. Central to this research work is a general purpose PC based work-station (Fig.1.4) which has been developed specifically for the design of microprocessor based control systems. The use of this forms a topic in its own right as it had a major impact on the design methods adapted during the research programme.

### 1.4 THESIS OBJECTIVE AND ORGANISATION

This thesis describes the development of a microprocessor-based selftuning controller. The performance of "conventional" self-tuning techniques applied to electro-mechanical systems in presence of stiction, friction and velocity saturation are evaluated with respect to fixed digital controllers.

Off-line analysis is carried out to model the plant transfer function and determine the minimum model order.

A digital computer simulation for the plant is carried out using the derived model to evaluate its performance under various control algorithms.

In this thesis it is also shown how a PC based development environment satisfies the requirements of the control engineer, from hardware design to system testing.

The thesis organisation is as follows:

In Chapter 2 a brief general history of control is given, the development of adaptive control being described in more detail. An overview of adaptive control is given here.

Chapter 3 describes an off-line identification technique used as a means to determine the tansfer function of the controlled plant (via the PC). A number of mathematical techniques are presented which seek to improve the model order reduction technique proposed by Soderstrom. Further, a new mathematical method designed to improve reduced order model structures is also given in this chapter.

In Chapter 4 implementation considerations in digital control systems such as computational delay, choice of sampling rate, practical constraints, and numerical accuracy are discussed. This chapter also describes the design of the digital control algorithm using a number of different control criteria.

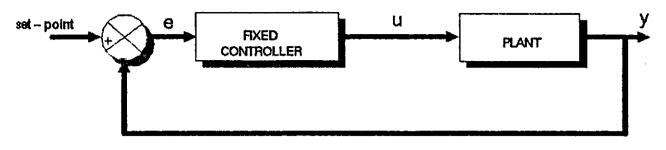

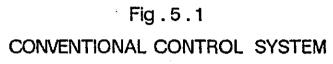

Chapter 5 deals specifically with the implementation of self-tuning algorithms. It describes the basic structural blocks of self-tuning systems and evaluates the practical implementation aspects of self-tuners. The design of a Pole/Zero cancellation self-tuner and a PID self-tuner is shown in this chapter.

Chapter 6 describes the electronic control system used as the target digital controller. The target board functions and facilities are explained. A detailed description of the electronic hardware is included in this chapter.

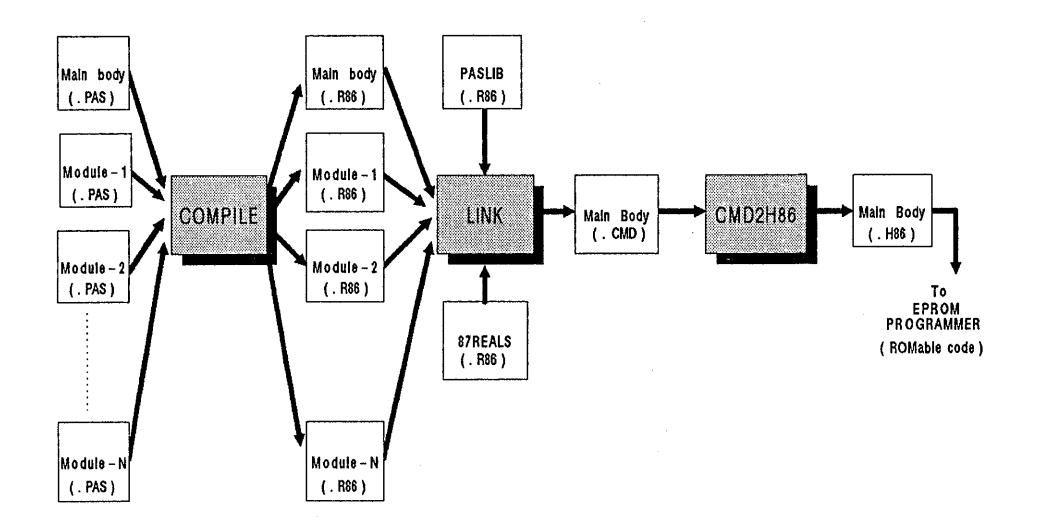

Chapter 7 explains the software structure and the software design technique. The role of the PC in developing both the off-line (computing) and online (plant controller) code is illustrated. In this chapter the implementation of the self-tuning controller (STC) is shown, the functions of the software used on both the PC and the microprocessor being explained in detail.

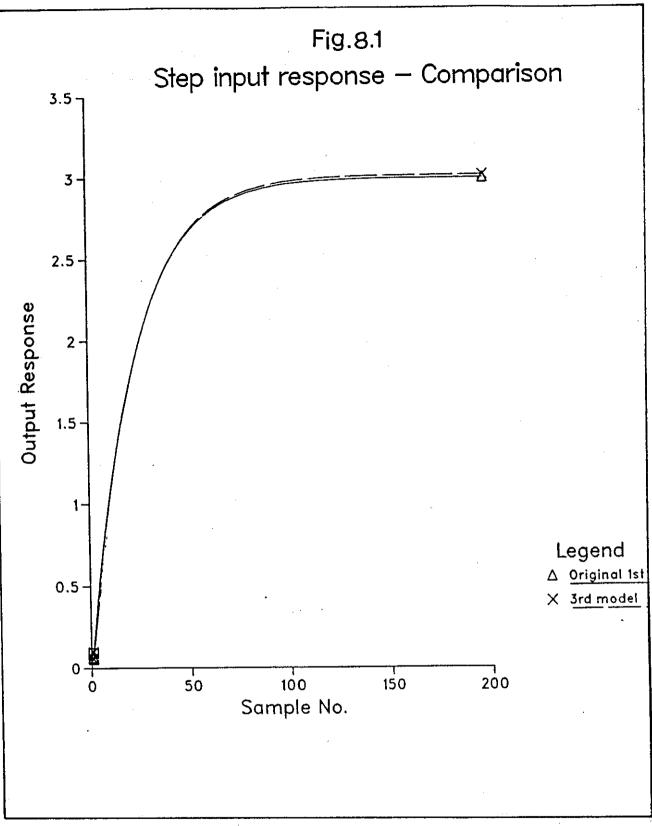

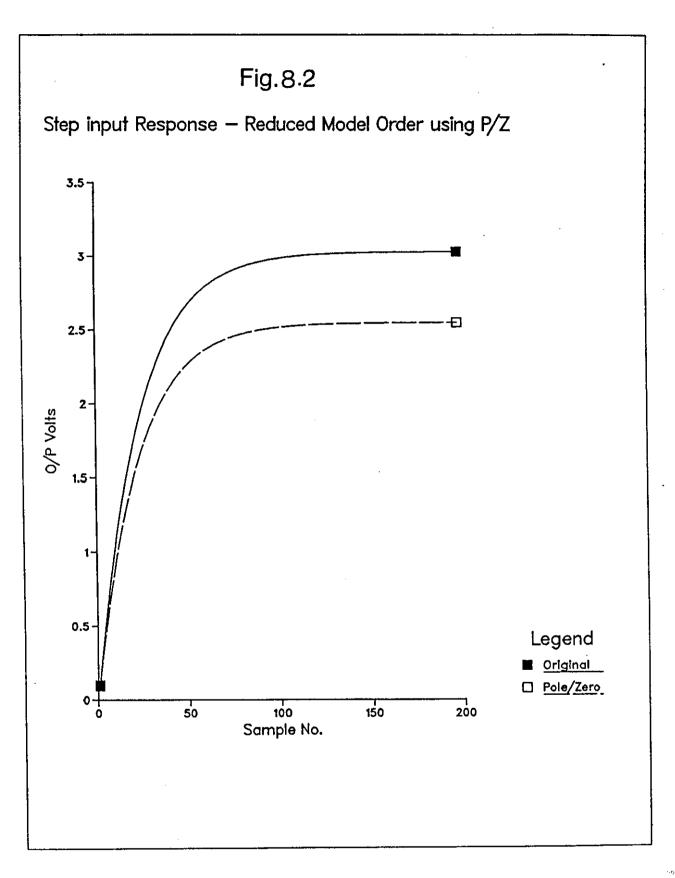

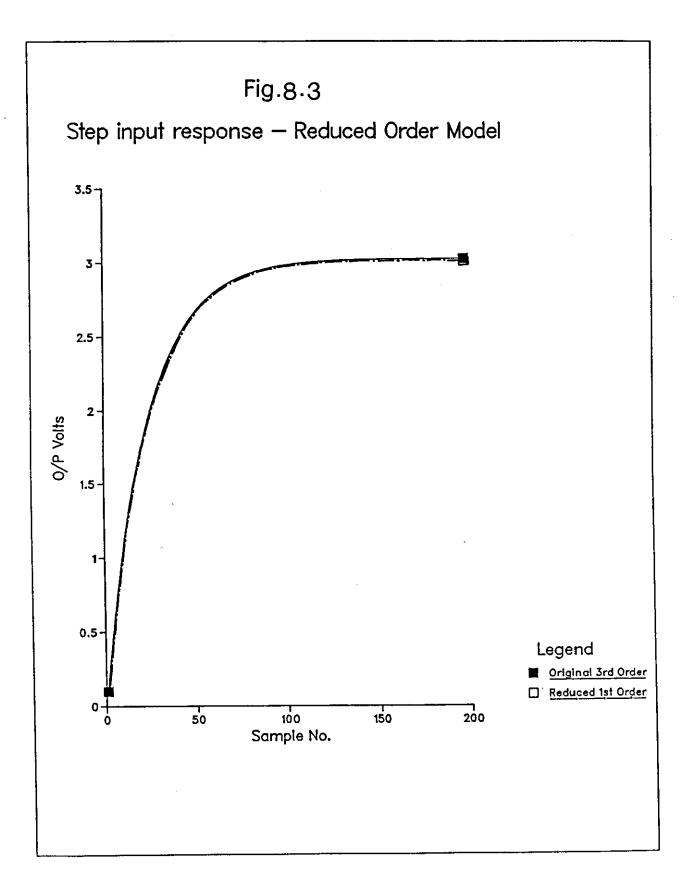

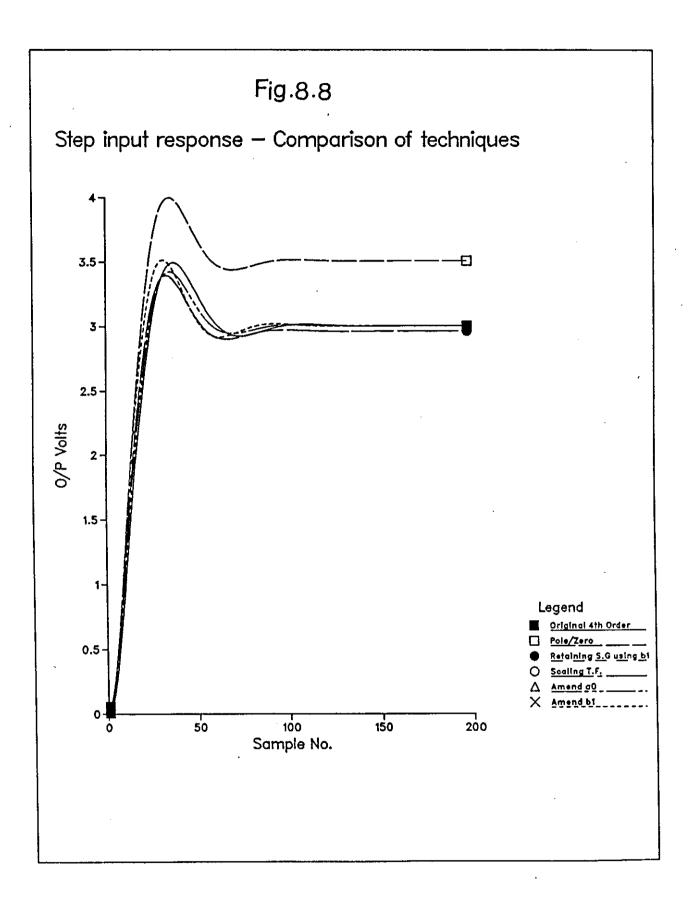

In Chapter 8 the advantages of using the improved transfer function reduction technique are shown using test results obtained for models of different order. The plant transfer functions used are for both real plants and simulated ones.

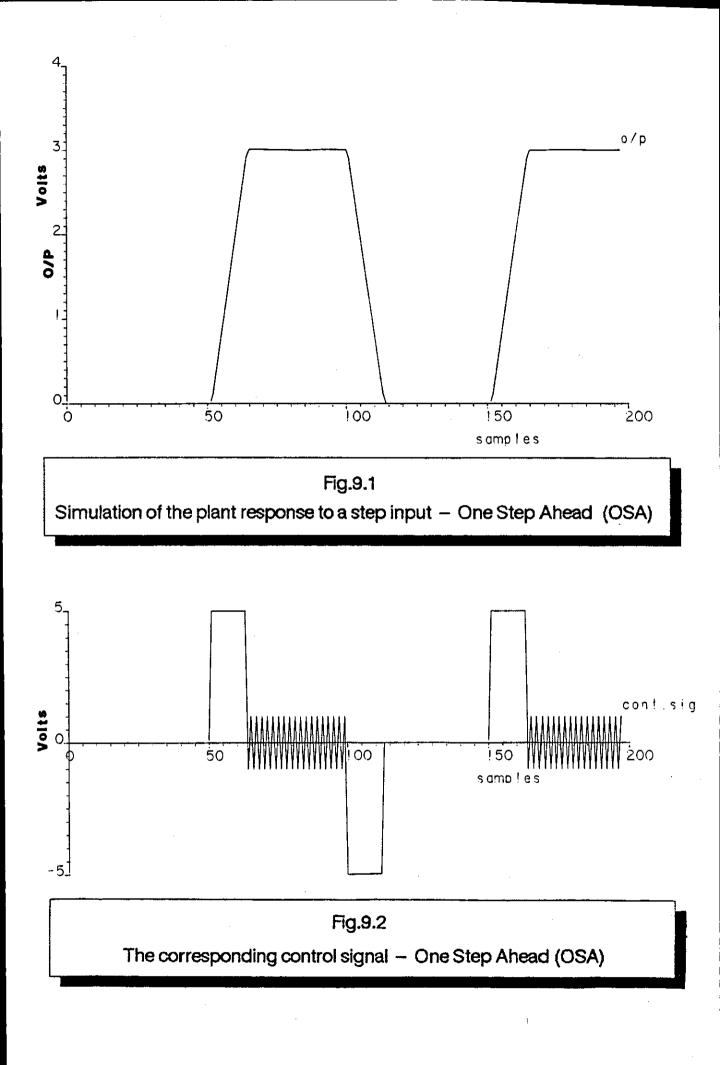

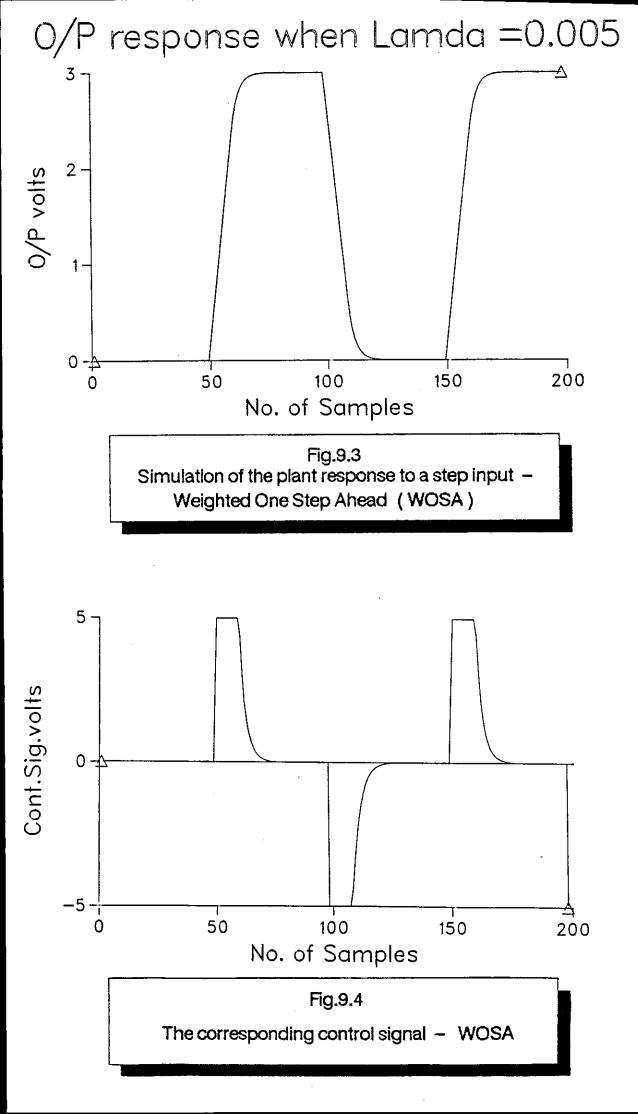

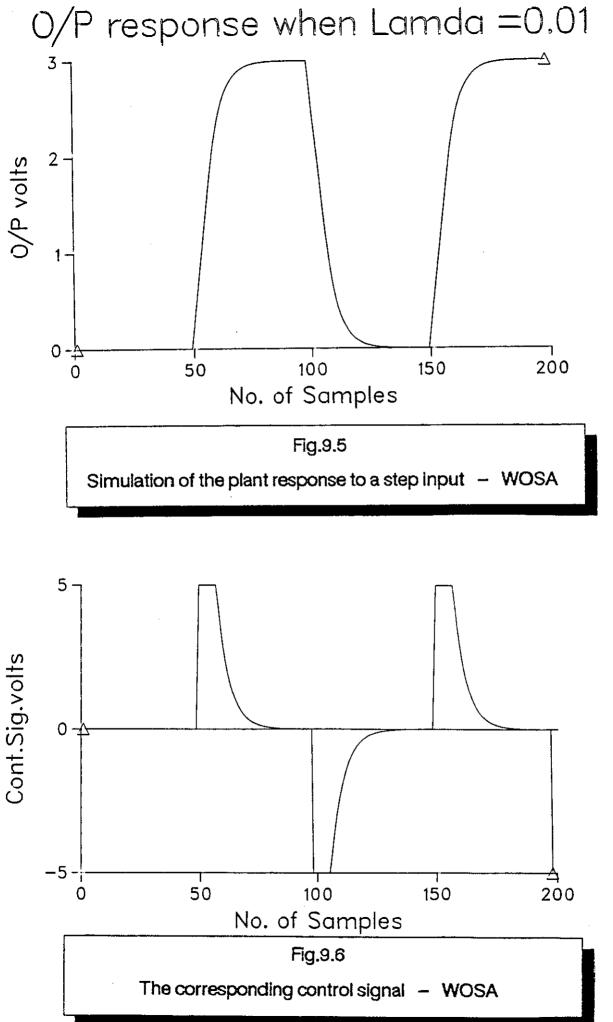

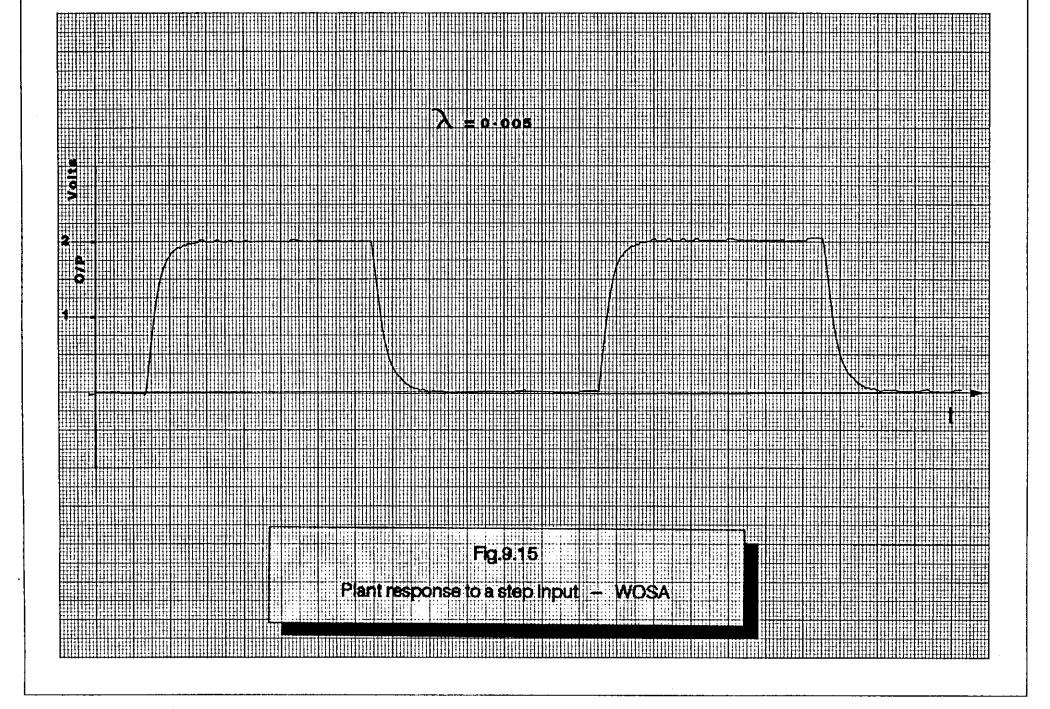

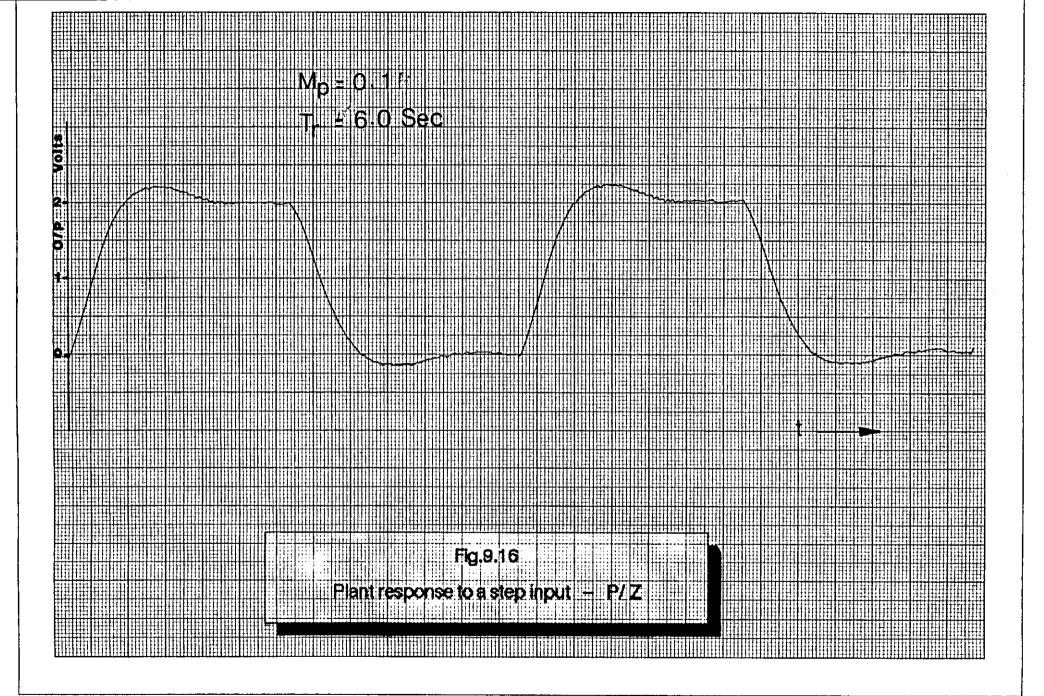

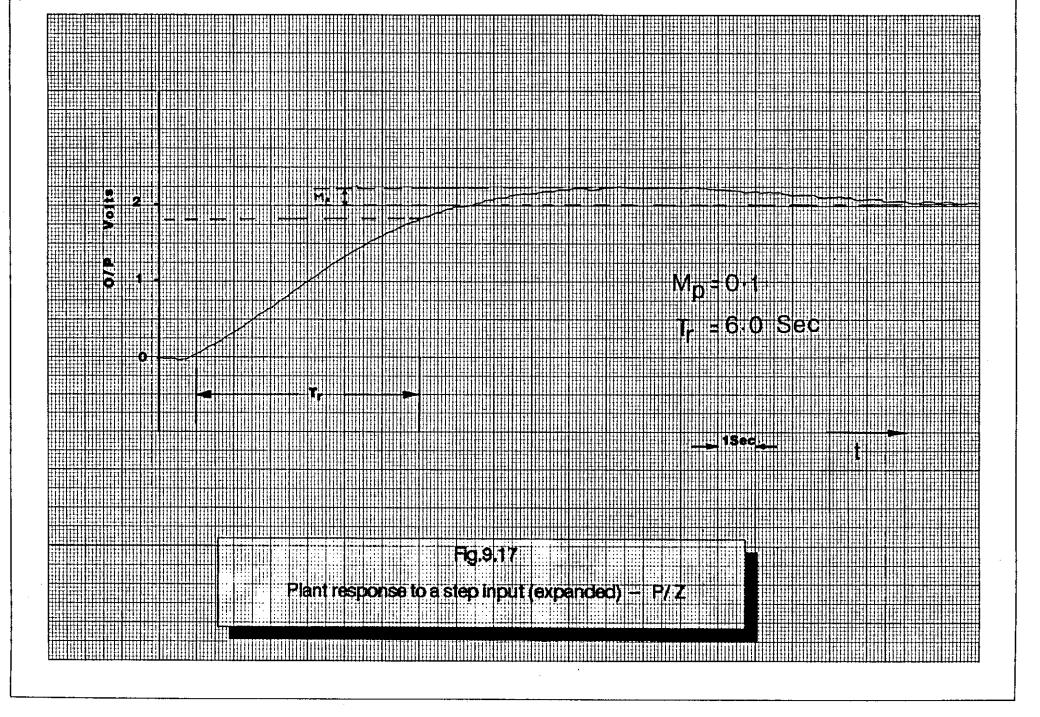

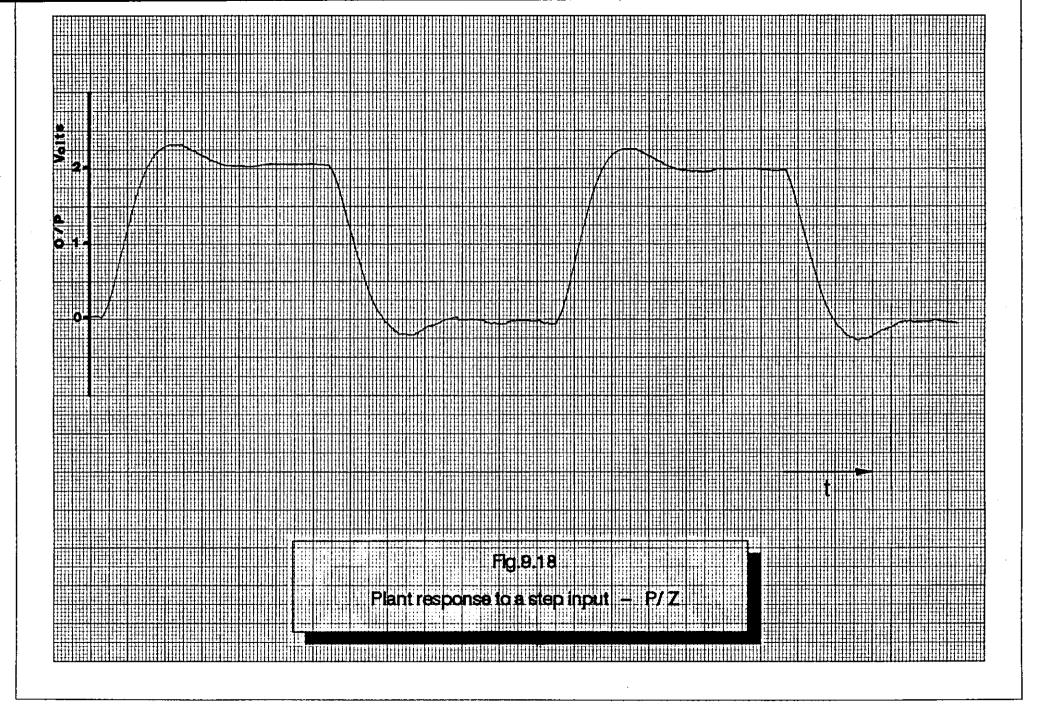

In Chapter 9 both simulated and actual test results for the plant control system are presented, different control techniques being used in these tests. The

actual response of system under self-tuning control (STC) is compared with that under the fixed digital controller. The evaluation and implication of these results are discussed.

In Chapter 10 the conclusions and comments arising from this work are outlined.

## SYSTEM DEVELOPMENT PROGRAMME

## CHAPTER-2

۱

### **2 THE DEVELOPMENT OF THE THEORY OF CONTROL**

### 2.1 HISTORY OF CONTROL

Fig.2.1 shows some events in the history of control. The basic concepts of automatic control and their analysis in terms of ordinary differential equations were well established by the beginning of the twentieth century [2.1]. These techniques were consolidated in review papers by Hort [2.2] and Von Mises [2.3], and in early textbooks on automatic control by Tolle [2.4] and Trinks [2.5]. Important studies carried out by Minorsky [2.6], and by Hazen [2.7] produced further development in the field. Minorsky proposed the use of a proportional-plus-derivative-plusintegral control action in the automatic steering of ships. His work was of particular significance in being practically tested in a famous series of trials on the automatic steering of the USS New Mexico in 1922-23 [2.8]. Hazen's studies were on shaft-positioning servomechanisms. Both Minorsky's and Hazen's work was explained in terms of ordinary differential equations, and their success with practical devices led to the widespread use of this approach for the analysis of automatic control systems [2.1].

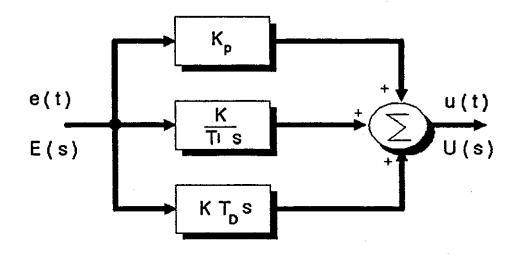

In 1936 Callender, Hartree, and Porter published the first paper [2.9] describing the application of the PID controller on an analogue computer [2.10]. Zieglar and Nichols [2.11] made an important study which led to simple rules for tuning the PID controller [2.22].

By the late 1930's there were thus two separate but well-developed methods of analysing feedback system behaviour [2.12]:

(a) The "time-response approach" which involved ordinary differential equations and their associated characteristic algebraic equations. This

approach was much used in mechanical, naval, aeronautical, and chemical engineering studies of automatic control systems; and

(b) the "frequency-response approach" which involved Nyquist and Bode plots, transfer functions, etc.. This approach was used in the studies of feedback amplifiers [2.12].

The frequency-response approach describes systems in terms of their input/output relationships in the frequency domain. In practice this proved to be a very flexible and general way of representing systems [2.1]. The use of transfer functions in analysing feedback systems was introduced by Harris [2.13]. The idea of Harris enabled a mechanical servomechanism or a chemical process control system to be represented in terms of a block diagram [2.12].

The demands of World War II greatly accelerated work in the field of automatic control. In particular the need for precise and rapid control of ships, aircraft, and radar antenna systems led to significant advances in theory and practice. With the lifting of wartime security restrictions in 1945 [2.10], rapid progress took place in the control field, many books and innumerable articles and papers being written in the post-war period. This has resulted in the widespread dissemination and adoption of frequency-response ideas [2.1] and the application of control systems in industrial and military fields almost without limit [2.10].

The development of frequency response techniques was soon followed by another approach to control system design [2.15]. This was introduced in 1948 by W. R. Evans, who was working in the field of guidance and control of aircraft. Many of his problems had unstable or neutrally stable dynamics, and he suggested a return to the study of the characteristic equation that had been the basis of work of Maxwell and Routh nearly 70 years earlier. However, Evans developed techniques and rules allowing one to follow graphically the paths of the roots of the

characteristic equation as a parameter was changed. His method, the root locus, is suitable for design as well as for stability analysis and remains an important technique today.

Until the beginning of the second world war work concentrated mainly on either linear systems or simple "bang-bang" controllers. However, the need arose at this time to control the performance of systems which provided "plant" information at, and only at, discrete time intervals. For instance, the rotating aerial of a radar system illuminates its target intermittently; hence data is available only in pulsed or sampled form. Therefore, many of the fire-control systems developed during the Second World War had to be designed to deal with data available in this form [2.1]. Hurewicz laid the basis for an effective treatment of sampled-data automatic control systems [2.14], extending the Nyquist stability criterion to sampled-data systems. Digital controllers operating on continuoustime plants required analysis techniques which relate both discrete-time and continuous-time systems. Linvill discussed this problem from the transfer point of view, including a consideration of the Nyquist approach to closed-loop stability [2.15]. Tsypkin used frequency-response methods to analyse sampled-data systems [2.16]. A "Z-transform" theory for systems described by difference equations emerged to match the "S-transform" theory for systems described by differential equations [2.17]. This theory was treated in textbooks by Ragazzini and Franklin [2.17], Jury [2.18], [2.19], Freeman [2.20], and others.

The effect of random disturbances on automatic control systems was also studied during the Second World War [2.14]. Wiener studied the relationship between the time-response and frequency-response descriptions of a stochastic process [2.21]. His books had the important effect of propagating feedback control ideas in general, and frequency-response methods in particular, into the field of stochastic system theory [2.1].

The emergence of the digital computer by the late 1950's as a widely availabe engineering device was a necessary prerequisite for the next developments in automatic control systems. The computing power and versatility of the big scientific machines made the lengthy and intricate calculations involved a practicable proposition [2.22]. During the decade of the 1950's several authors including Bellman, Kalman, and Pontryagin began again to consider the ordinary differential equations (ODE) as a model for control systems [2.10]. The new methods considered the simultaneous control of a number of interacting variables; these also assessed the use of different types of controller objectives, such as the minimisation of fuel consumption. As with the previous major developments in automatic control theory, the next advances arose out of an important technical problem, in this case the launching, manoeuvering, guidance, and tracking of space vehicles [2.1]. This development was supported by digital computers, which could be used to carry out calculations that would have been unthinkable 10 years earlier. The study of optimal controls begun and much of this work was presented at the first conference of the newly formed International Federation of Automatic Control (IFAC) held in Moscow in 1960. This work did not use the frequency response or the characteristic equation but instead worked directly with the ordinary differential equation. Generally such methods required the extensive use of computers [2.10]. This approach is now often called "modern control", as opposed to the methods of Bode et. al, which are termed "classical".

In the late 1950's, the control world became deeply involved in so called adaptive systems [2.23]. As Truxal noted [2.24] these are nonlinear feedback systems derived from an identification viewpoint. In the 1950's and early 1960's, such advanced techniques were seen as a means to substantially improve control performance in parameter varying systems. Unfortunately on-line digital computers with sufficient speed and computation capability were not available at

that time [2.25]. Analogue computers of that time period did not have either adequate accuracy or reliability to perform in the adaptive control mode [2.25]. Adaptive control has been a challenge to control engineers for a long time, many schemes having been proposed [2.26]. In spite of this, progress in the field has been comparatively slow. One reason is that it is difficult to understand how adaptive systems work because they are inherently nonlinear. Another reason is that it has been costly and fairly complicated to implement adaptive controllers. Computer control was still out of reach for many control problems until the development of the microcomputer in 1970 [2.22]. The situation changed dramatically with the advent of powerful low-cost microprocessors, making the implementation of adaptive controllers feasible and economical. Recently there has also been significant progress in the theory of adaptive control [2.27].

### 2.2 APPROACHES TO ADAPTIVE CONTROL

During the past few years the field of adaptive control has become increasingly active. Major advances in microprocessor technology have also made sophisticated algorithms more feasible for practical applications.

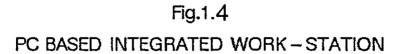

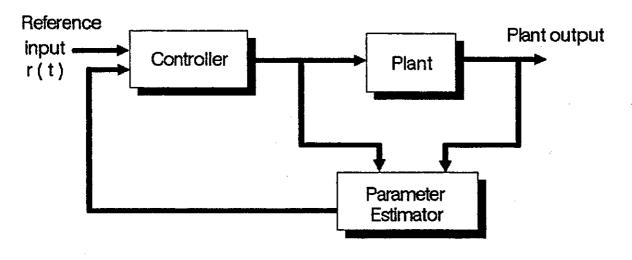

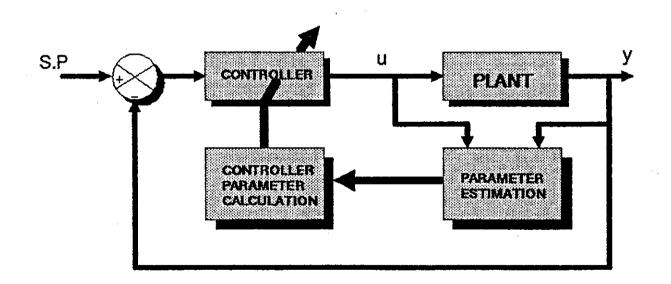

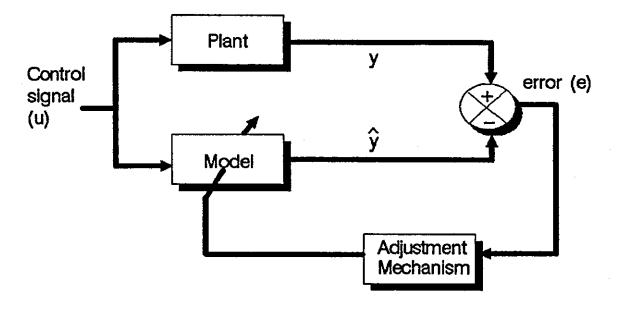

Self-Tuning Controllers (STC) and Model Reference Adaptive Control (MRAC) are the two principal solutions to the adaptive control problem [2.28,2.29]. <u>N STC is derived for discrete time systems while MRAC is derived for deterministic</u> continuous control systems [2.30].

In MRAC the objective is to force the response of the closed loop control system to follow that generated by some defined model. In STC a design procedure for known plant parameters is first chosen and this is applied to the unknown plant using recursively estimated values of these parameters.

Figs.2.2 and 2.3 represent the adaptive control problem using MRAC and

STC approaches respectively. In MRAC (Fig.2.2) the input and the output of a linear plant are u and  $y_p$  respectively. A linear model and reference input r are specified which result in a model output  $y_m$ . From all the available data (u,  $y_p$ , r and  $y_m$ ) it is desired to determine a control input (u) such that the error (e) between  $y_p$  and  $y_m$  tends to zero asymtotically [2.31].

In the STC approach (Fig.2.3) the first step is the selection of an appropriate known procedure for the design of a controller when the plant parameters are known. The second step is to estimate the unknown plant parameters; from these the control algorithm coefficients are modified (up-dated) in accordance with the defined control criterion [2.27]. Identification carried out continuously by the controller as the plant runs is known as "on-line" identification. Off-line identification is done on recorded data by transfering this data to a host computer where it is processed.

According to Clarke [2.27] a "good" adaptive controller should be characterised by:

- \* Closed loop performance criteria easily understood by control engineers.

- \* Simplicity of coding.

- \* Robustness when applied to as broad a class of plants as possible.

In MRAC the zeros of the plant must lie in the interior unit circle (i.e. a nonminimum phase plant is not allowed) [2.29]. The general approach of MRAC yields a relatively complicated adaptive control law [2.44] while STC is, in a sense, the simplest possible adaptive control algorithm [2.30]. STC can use "conventional" control techniques that are robust and well known. The selection of an appropriate control scheme removes the restriction on the type of plant in STC.

Although STC and MRAC techniques are based on different design

principles, it has recently been shown [2.32,2.33,2.34,2.35] that both control schemes are very similar and in some special cases even identical [2.35].

| Period     | Year | Control Theory                                                                         | Control Application                                                                                             | Background                                          |  |

|------------|------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| I.<br>Art  |      |                                                                                        |                                                                                                                 |                                                     |  |

|            | 1900 | * Book on speed<br>control<br>*Use of differential<br>equations and<br>Routh - Hurwitz | Instrument and regulators<br>for process and power<br>industries<br>Control for communication<br>Servomechanism | World War I<br>Progress in<br>Industry              |  |

| Transition |      | criteria on some<br>simple systems<br>*Zlegter – Nichols'                              | Controls for weapon                                                                                             |                                                     |  |

|            | 1950 | method<br>*Laplace domain<br>approach and<br>frequency response                        | Electronic controllers                                                                                          | World War I I                                       |  |

|            | 1960 | method<br>*Root locus<br>* z-transform method<br>* State space approach                | Plant and processes<br>with controls as<br>essential part<br>Data —togging                                      | Nuclear power<br>Computers                          |  |

| 111.       | 1000 | Lyapunov concept,<br>optimum control<br>theory, and math –<br>ematical theory of       | Digital computer for<br>computing control<br>Direct digital control                                             | Automation<br>Space projects<br>Systems and         |  |

| Science    |      | control processes<br>(Adaptive control)<br>* Detailed analyses of                      | Progress towards<br>dynamic optimisation                                                                        | control<br>concepts in<br>biomedical<br>and various |  |

|            | 1970 | * Self - tuning control                                                                | Software developments<br>Microprocessors for                                                                    | other fields<br>Man on the<br>moon                  |  |

|            | 1987 |                                                                                        | on + line control                                                                                               |                                                     |  |

| Ţ          |      |                                                                                        |                                                                                                                 |                                                     |  |

.

Some events in the history of control

Fig.2.3 Self-Tuning Adaptive Controller

CHAPTER-3

I

,

# **<u>3 MODEL DETERMINATION</u>**

## 3.1 INTRODUCTION

A model may be defined as "a representation of the essential aspects of a system which presents knowledge of that system in a usable manner" [3.8]. In order to design a controller for a dynamic system it is necessary in many cases to develop a model that adequately describes the system's behaviour. The mathematical model forms an important part of the design cycle, engineers thereby gaining an understanding of the nature of the dynamic behaviour of the system [3.1].

For a model to be useful it must not be so complicated that it cannot be understood and thereby be unsuitable for analysis; at the same time it must not be oversimplified to the extent that predictions of the behaviour of the system based on this model are inadequate [3.8].

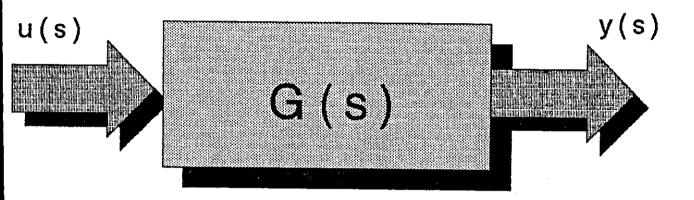

The system model is usually represented by a transfer function, shown in the form of a block diagram, Fig.3.1. Note that the block is "unidirectional". The input may be regarded as the "cause" and the output as the "effect". The block diagram is unidirectional since the "effect" cannot produce the "cause" [3.3]. The transfer function G(s) relates the Laplace transform Y(s) of the output y(t) to the Laplace transform U(s) of the input u(t) through the relationship

$$Y(s) = G(s)U(s)$$

(3.1)

This chapter describes the methods used to obtain a mathematical model of the controlled plant. These are based on established statistical test methods, using an assumed high order model in the identification process. Once the "best" estimate of the plant model is obtained its order is reduced to a minimum acceptable

level.

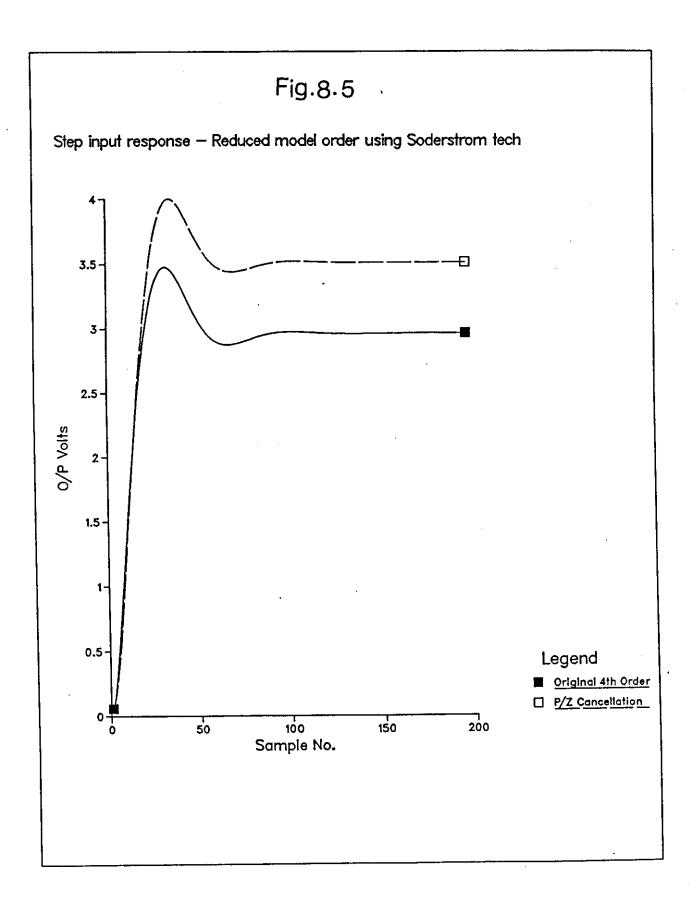

The model order reduction technique developed here, although based on that proposed by Soderstrom [3.9], offers significant improvements on earlier methods; furthermore several concepts involved are new and original. Its effectiveness is demonstrated in a series of practical tests, leading to fast identification combined with satisfactory closed-loop control.

# 3.2 APPROACHES TO MODEL DETERMINATION

There are two approaches to the problem of determining a mathematical model of a given system [3.1].

- (a) <u>Physics:</u> Many systems can be analysed in terms of laws of physics, thermodynamics etc. and expressed in mathematical terms by looking directly at the mechanism that generates signals within the system. Equations are then assembled to form a mathematical model, based on the physical laws and relationships that govern the system's behaviour [3.3]. An advantage of model-building from physics is that the variables have physical interpretations [3.1].

- (b) <u>Identification</u>: System identification is the experimental approach to plant modelling in which data obtained from the system is used to model that system [3.5]. Many methods are suitable for analysing data obtained from such experiments [3.2,3.8] [Appendix-B], one basic approach being the principle of Least Squares (LS) [Appendix-B].

In many situations direct modelling using physical knowledge may not be possible [3.6]. One reason may be that knowledge of the system's mechanism is incomplete, since this method needs insight. A further reason is that the system may be subject to on-line changes in an unpredictable manner, as occurs when the environment of the system changes (e.g. an aircraft changes altitude, a paper machine is given a different composition of fibre, etc.). The first approach can also be quite time-consuming, furthermore it may lead to models that are complex and of high order which in turn require order reduction [3.1]. In these circumstances the designer may turn to an identification method. These methods are also especially

useful when plant dynamics change with time or with operating conditions. On these occasions the control parameters need to be changed to "tune" the controller [3.4] for best performance. In order to achieve this it is necessary to obtain a plant model under the new conditions. Deriving this from experimental data is often the most effective (if not the only) way to do this.

### 3.3 FUNCTIONAL TESTING AND SYSTEM IDENTIFICATION

### 3.3.1 Overview

The ultimate objective of this test is to produce a mathematical model of the plant based on measurements of the plant input (control) and output (measured value) signals. Therefore it is necessary for the experimenter to control the test procedures, setting conditions such as signal type and duration, sampling rates and number of measurement points. The set-up used for these tests is shown in Fig.3.2, the use of the PC being self-evident from the following text. Note there are two distinct aspects of this operation. In the first place the plant has to be perturbed to obtain data; subsequently the information so obtained is used as part of the model identification process. This is carried out within the PC.

### 3.3.2 Plant testing

The control program which actually runs the plant and collects data measurements sits within the target controller in Eprom. For this, the source code is written in MT+ Pascal, details being given the software development chapter. Program development, i.e. code writing, compilation, linkage and PROM blowing,

takes place within the PC environment. For the duration of the plant test the PC functions as a terminal having data storage facilities. It communicates with the target controller using its RS232 serial data line.

To start the test procedure the controller and plant are powered up. The PC must be connected to the controller and placed in terminal mode. Instructions from the controller to the operator are displayed on the PC screen, responses being entered at the keyboard. These include plant test data and designation of the PC data file (on floppy disk) which is to be used to hold the plant measurements. A typical test procedure is shown in Fig.3.3 where, once the test parameters are entered by the operator, the controller runs the plant through its test sequence. During this, measurements are made of control signal and measured value, these being stored within the controller memory. At the end of the test this data is transferred to the named disk file in the PC. If required, the information can also be printed out for evaluation and review.

### 3.3.3 Off-line identification

The purpose of the off-line identification process is twofold. First, using the data recorded during the test run, it enables a mathematical model of the plant to be generated. Second, using this same set of data, a number of models can be obtained by applying various identification schemes. Details of several identification schemes are given in Appendix-B.

Evaluation of several identification schemes was carried out, including Recursive Least Squares (RLS), Recursive Extended Least Squares (RELS), Recursive Maximum Likelihood (RML) and Recursive Instrumental Variable (RIV) methods [Appendix-B]. The process of plant identification can be better understood by considering one of these in more details, RLS being a suitable

candidate.

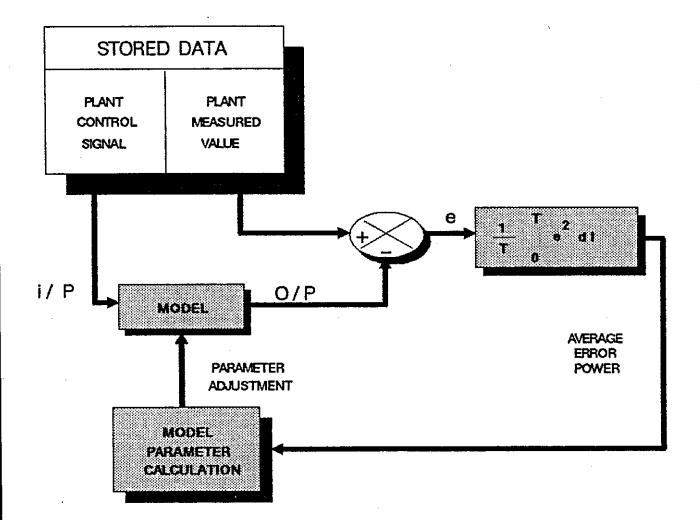

Fig.3.4 illustrates the concept involved in identification and model generation using RLS techniques. Here a program running under the PC operating system performs the following actions;

- (a) Set up a preliminary (guessed) model of the plant using information supplied by the operator.

- (b) Read the recorded plant control signal at a specific sample instant, apply this to the model, and calculate the resulting output.

- (c) Read the recorded plant measured value at the same sample instant and calculate the error between this and the model output.

- (d) Compute the average error power.

- (e) Adjust the model parameters to reduce the absolute value of the power gradient.

- (f) Repeat the above steps (b) to (e) for all recorded values, working iteratively towards a condition of a minimum error power.

As this program is executed sample by sample the model parameters (hopefully) converge toward those of the plant itself. What we are left with is a best estimate of the plant transfer function, this information being used in the implementation of an appropriate control scheme. Also, the results may be stored at each calculation interval, thus allowing the experimenter to review the convergence rate and accuracy of the identification process. It is, of course, necessary to design and write the identification program in the first case. This process is covered under software development (chapter.9).

The identification process is repeated to obtain models of different orders. These are then adjusted until a minimum order model is obtained which adequately

represents the plant. Details of the model order reduction process are given in the following section.

### 3.4 MODEL ORDER REDUCTION

### 3.4.1 Overview

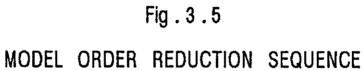

In a self-tuning controller the time required to execute the identification scheme is very significant and is usually the limiting factor on system sample rates. As the order of the assumed model increases the execution time rapidly increases (as shown in Table.3.1). A balance needs to be struck between the order of a transfer function and its effect on control system performance. Increasing the order of a model may produce only a marginal change in closed-loop performance; it may, though, produce a major increase in the time taken to run the identification process. What is needed is a minimum order model that adequately represents the plant for control purposes.

The objective here is to investigate the performance of lower order plant transfer functions derived from the transfer function produced by the identification process. By comparing this with the model derived from frequency response testing of the plant the relative performance of the models can be assessed. This test can be repeated for models of various orders.

# 3.4.2 The effect of choosing different model orders

If the order of the assumed model in the identification scheme is higher than the order of the plant, the following will occur:

(a) Zero coefficients will occur in the numerator polynomial of the transfer function when it is in the rational expansion form in the s-domain. This will take place until the ratio of the numerator to the denominator of the assumed model is equal to the ratio of the numerator to the denominator of the plant. Then, (b) Pole-Zero cancellation will take place until the assumed model matches the plant. This is very clear when the model is in factored form.

Therefore from the theoretical point of view the choice of a higher model order does not affect the estimated model since it will match the real plant as simulated in Appendix-E.

In practice this does not occur, but instead negligible, rather than zero, coefficients appear in the numerator and poles and zeros that should cancel are not exactly equal. This is due to the fact that there are different noise sources in the system (e.g. quantisation effect).

Numerous model order reduction techniques have been proposed in the literature, these being reviewed in [3.10]. In general these techniques have different objectives. Model reduction using pole-zero cancellation is the aim of our tests; hence the pole-zero cancellation method proposed by Soderstrom [3.9] is used.

### 3.4.3 The Pole-Zero cancellation technique

## (a) The problem formulation

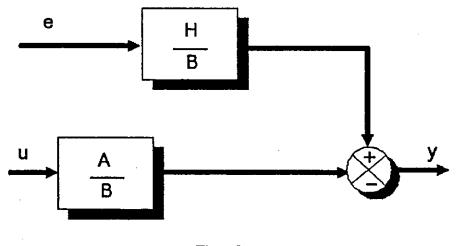

The objective of this method is to test possible pole-zero cancellations in order to reduce a model order. The identification technique (e.g. Recursive Least Squares (RLS)) used in section 3.3.3 forms the basis for this method.

The problem that is considered can be formulated as follows: The two polynomials that form the plant transfer function (A/B) are

$A(z^{-1}) = a_0 + a_1 z^{-1} + \dots a_{na} z^{-na}$

$B(z^{-1})=1 + b_1 z^{-1} + \dots b_{nb} z^{-nb}$

where the values of parameters are those estimated in the previous test (section 3.3.3). To account for the uncertainty of the parameters estimated the covariance matrix (P) of these estimates produced from the identification technique is used. The problem now is to test whether the polynomials A and B have common factors or not. The test is carried out for N common factors by starting with N=1, repeat the test for N=2,3,..., etc. as long as common factors are found.

### (b) The criterion

Let the n-dimensional vector  $\underline{\hat{x}}$  consist of the estimated values of the coefficients of the polynomials  $\widehat{A}$  and  $\widehat{B}$ . Introduce a vector  $\underline{x}$  that has the same dimension as  $\underline{\hat{x}}$  corresponding to two polynomials A and B. The problem now is to look for a vector  $\underline{x}$  in the same domain of  $\underline{\hat{x}}$  such that the corresponding polynomials (A and B) have at least N common factors.

The technique achieves this by minimising a cost function  $J(\underline{x})$  of the form

$$J(\underline{x}) = (\underline{x} - \underline{\hat{x}})^T P^{-1} (\underline{x} - \underline{\hat{x}})$$

(3.1)

Notice that the error criterion (Eq.3.1) uses  $P^{-1}$  as a weighting matrix. Each element in the covariance (P) matrix reflects the uncertainty of each estimate; a large uncertainty means large variance which in turn implies that the corresponding element in the P matrix is large. Therefore  $P^{-1}$  gives approximate relative weighting in the error criterion (Eq.3.1) because in  $P^{-1}$  large variance generates small weighting on the corresponding error.

(c) The algorithm

Introduce the polynomials  $\widetilde{A}(z^{-1})$ ,  $\widetilde{B}(z^{-1})$  and  $\widetilde{C}(z^{-1})$  where

Ã(z-1)= ão + ãi z-1+ ... + ãna-N z-(na-N)

$\tilde{B}(z^{-1})=b_0 + \tilde{b}_1 z^{-1} + ... + \tilde{b}_{ab-N} z^{-(ab-N)}$

$\widetilde{C}(z^{-1}) = 1 + \widetilde{c_1} + \dots + \widetilde{c_N} z^{-N}$

where N is the number of common factors. Consider the polynomials  $A(z^{-1})$  and  $B(z^{-1})$  have the following form

$$A(z^{-1}) = \widetilde{A}(z^{-1}) \widetilde{C}(z^{-1})$$

,

$B(z^{-1}) = \widetilde{B}(z^{-1}) \widetilde{C}(z^{-1})$ .

Thus the polynomial  $\widetilde{C}(z^{-1})$  represents the pole/zero cancellation factors.

The coefficients of these three polynomials ( $\tilde{A}$ ,  $\tilde{B}$ , and  $\tilde{C}$ ) are collected in a vector <u>y</u>. Thus <u>x</u> can be written as a function of <u>y</u>, <u>x</u> = f(<u>y</u>). Then the optimisation problem is to find the global minimum without constraints of

$$V[f(\underline{y})] = [f(\underline{y}) - \underline{\hat{x}}]^T P^{-1} [f(\underline{y}) - \underline{\hat{x}}]$$

The resulting coefficients of  $\tilde{A}$  and  $\tilde{B}$  represent the coefficients of the reduced model while the coefficients of  $\tilde{C}$  represent the common factors in the numerator and the denominator of the original model.

This is a non-linear optimisation problem which may yield several minima,

therefore the selection of the initial values of the  $\underline{y}$  vector is important. A reasonable set of initial values can be found by using the values of the original model. This is done by looking at the poles and zeros of the original transfer function and using the ones that are close to each other as the initial value for the C polynomial while the rest of the coefficients are used as initial values for A and B polynomials.

Several methods are available to solve a non-linear optimisation problem [3.12]. The quasi-Newton method is one of the powerful techniques used in such optimisation problems and is available in the NAG library on the Honeywell MULTICS main frame computer. For these reasons it is used to handle the optimisation process involved in model order reduction.

### 3.4.4 Static gain correction

The static gain of a discrete transfer function is simply its value when z is set equal to 1. Looking at a typical transfer function produced from the optimisation for one common factor

$$\frac{(\tilde{a}_0 + \tilde{a}_1 z^{-1} + \dots + \tilde{a}_{na-1} z^{-(na-1)})(1 + \tilde{c}_1 z^{-1})}{(1 + \tilde{b}_1 z^{-1} + \dots + \tilde{b}_{nb-1} z^{-(nb-1)})(1 + \tilde{c}_1 z^{-1})}$$

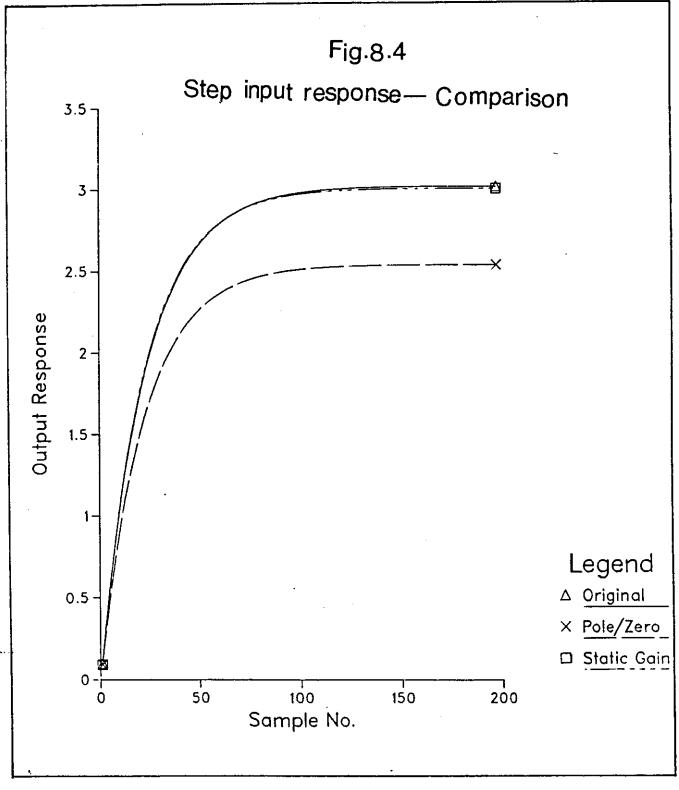

There is one too many degree of freedom in the  $\tilde{A}$  polynomial. Therefore the optimisation may yield numerator estimates which are incorrect by a scaling factor and hence give rise to a static gain difference between the original model and the reduced model. This was found in practice as will be shown in Chapter 8.

Several solutions to this problem are introduced:

(a) Using the above method as proposed by Soderstrom, then multiplying the

reduced order model by a scaling factor. The resultant model has the following form

$$G_{new}(z^{-1}) = \frac{G_o}{G_r} \quad G_r(z^{-1})$$

where  $G_{new}(z^{-1})$  is the new model,  $G_0$  is the static gain of the original model, and  $G_r$  is the static gain of the reduced order model using the Soderstrom method.

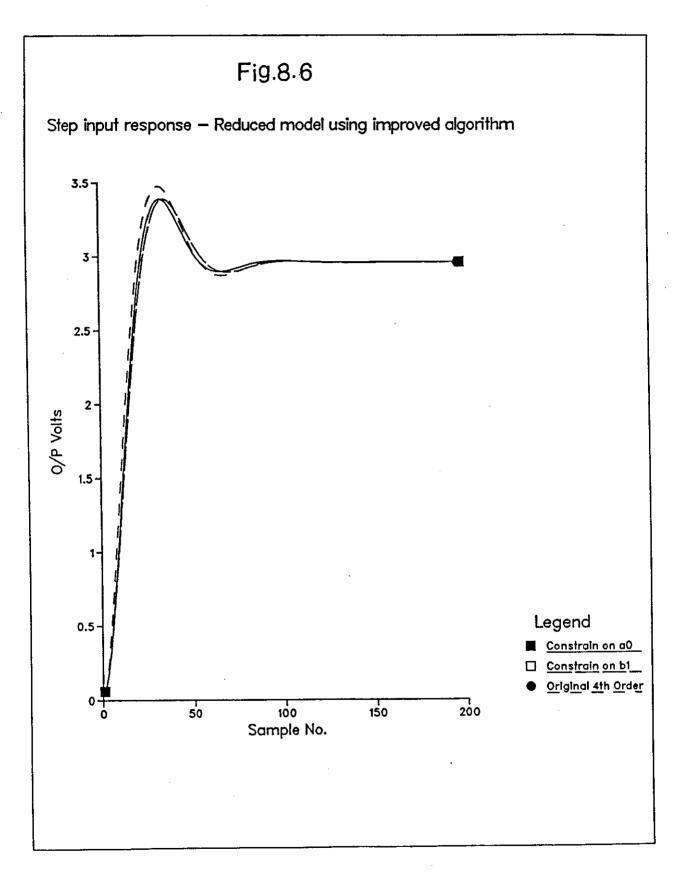

(b) Modifying the algorithm to retain the static gain during the optimisation  $\tilde{b}_1$  to have the value

$$\widetilde{\mathbf{b}}_{1} = \frac{1}{\mathbf{G}_{0}} \sum_{i=0}^{n} \widetilde{\mathbf{a}}_{i} - \sum_{j=2}^{n} \widetilde{\mathbf{b}}_{j} - 1$$

where Go is the static gain of the original model.

(c) Retaining the static gain during the optimisation procedure by forcing  $\tilde{a}_0$  to have the following value

$$\widetilde{\mathbf{a}}_0 = \mathbf{G}_0 \sum_{i=0}^n \widetilde{\mathbf{b}}_i - \sum_{i=1}^m \widetilde{\mathbf{a}}_i$$

instead of b<sub>1</sub>.

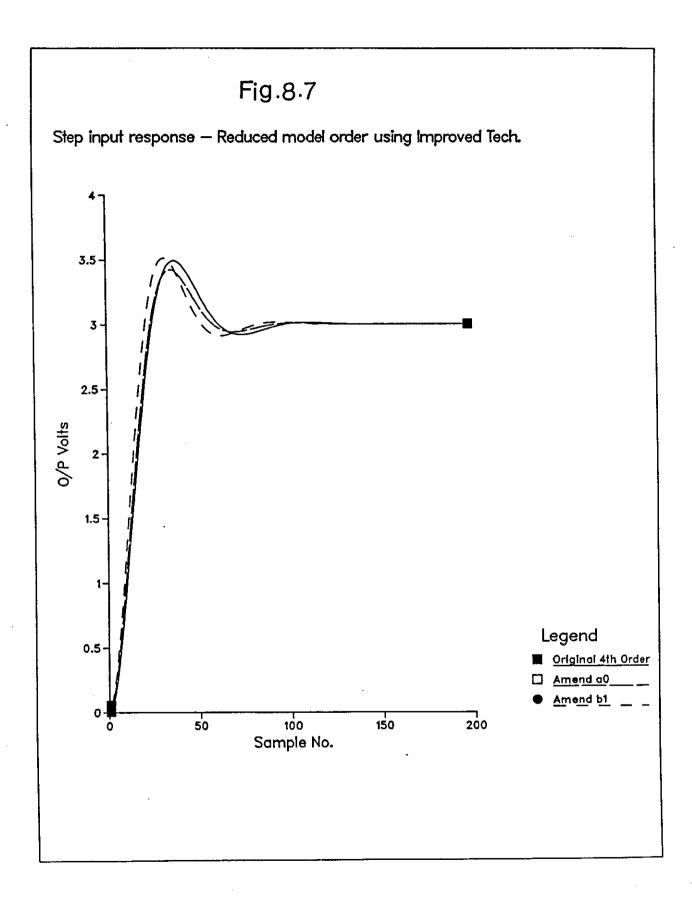

(d) Produce a reduced order model using the Soderstrom method and then amend the value of either  $\tilde{a}_0$  or  $\tilde{b}_1$  so that the static gain is equal to the original model.

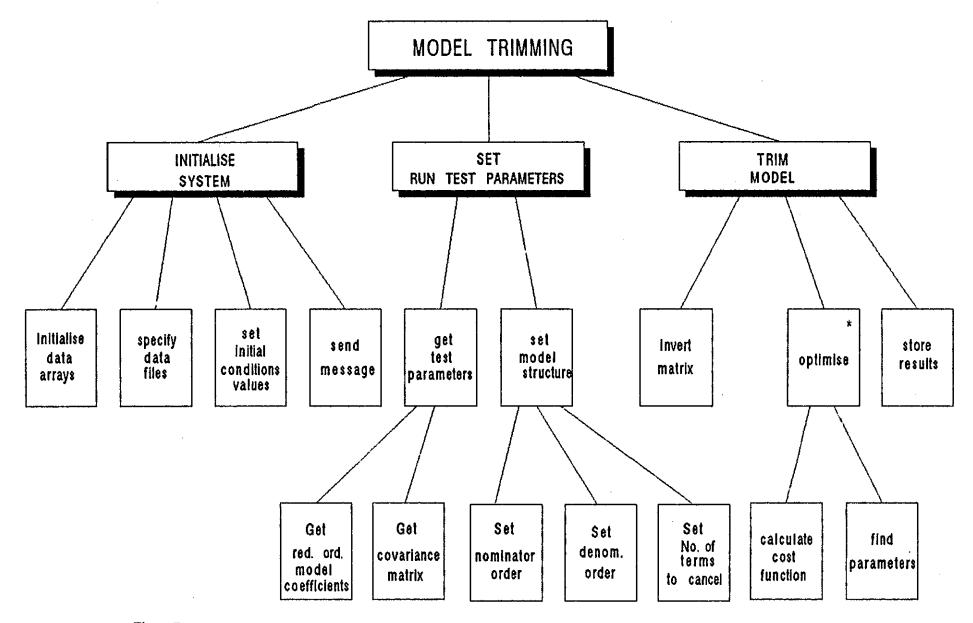

## 3.4.5 Model trimming

The method proposed by Soderstrom tests for pole-zero cancellation but does not test for negligible numerator coefficients that could appear if the order of the model produced from system identification is over estimated as mentioned in section 3.4.2. Therefore the structure of the continuous reduced order model may not match the actual model of the continuous plant. It is shown in Appendix-E that it is not possible to eliminate these coefficients if the model is in the Z-domain since they contribute to each coefficient, but if the model is in the S-domain these small coefficients appear as separate coefficients in the numerator.

A technique is introduced to test for negligible coefficients after performing model order reduction. This trimming method uses the same error criterion (Eq.3.1) used above and the quasi-Newton method is used as the optimisation method. Details are given in Appendix-E.

### 3.4.6 Model order reduction technique

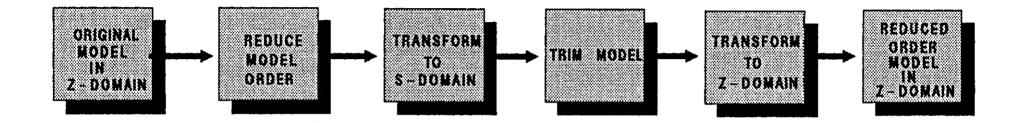

Fig.3.5 shows the procedure to produce a reduced order model, these being

- \* Reduce the model order using the improved method a, b, c or d (Section 3.4.5)

- \* Transform the model to the S-domain.

- \* Trim the model using model trimming technique (Section 3.4.6)

- \* Transform the model back to the Z-domain.

# THE TRANSFER FUNCTION BLOCK DIAGRAM

# Fig.3.2

# SYSTEM ORGANISATION - FUNCTIONAL TESTING

A)B:OFLIBOT ENTER THE NOT OF YOUR OFFICE. HELLO. 105 ENTER THE STEP VOLT PRESS THE SPACE BAD 145 ча -5V) ENTER. TRE 3000 OUTPUT\_VOLTRGEIISISET=3000.0 ENTER ANOTHER OPTION. 3 HOH MANY ITERATION 200\_ Console=0-Dinitale=107.1901 Line free <01/01/64 00:24:03>

Fig . 3 .3

# A TYPICAL TEST SEQUENCE

PLANT OFF-LINE IDENTIFICATION PROCESS

Time Required To Excute System Identification Procedure

# CHAPTER-4

.

### 4 IMPLEMENTATION OF THE DIGITAL CONTROL ALGORITHM

### 4.1 INTRODUCTION

Numerous control algorithms have been proposed for use in digital controllers [4.1,4.2,4.3]. In this chapter a number of algorithms are implemented in order to evaluate their effectiveness in controlling the plant. The ones evaluated here are those which have (or appear to have) given satisfactory results in practical situations. These algorithms are related to the performance specification methods, being expressed either in statistical or deterministic form. However performance effectiveness is not the only criterion for evaluation. In an on-line adaptive controller for servo applications the control action, and especially adaptation of the algorithms, must be carried out quickly. Thus simple algorithms which require only a small computing effort are desirable.

Once the performance specification (criterion) and control algorithm are defined then the algorithm coefficients are adjusted until the closed loop performance specification is met. However the loop includes the plant; hence its dynamics must be taken into account when computing the coefficient values. This requires us to evaluate the plant transfer function in discrete form (i.e. to derive its pulse transfer function) before calculating the controller settings. Finally practical considerations involving system non-linearities and quantisation effects have to be considered before actually running the control loop.

The performance actually achieved depends to some extent on the controller hardware and software. In this case a 16-bit microprocessor with 12-bit Analogue to Digital and Digital to Analogue converters is used; the software is written in PASCAL, calculations being carried out in floating-point form.

### 4.2 PULSE TRANSFER FUNCTION

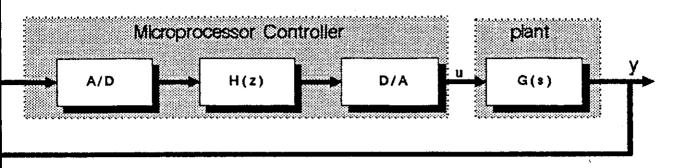

Fig.4.1 shows the system diagram of the microprocessor controller together with the plant. The analogue and the digital parts of the system are connected via D/A and A/D converters respectively.

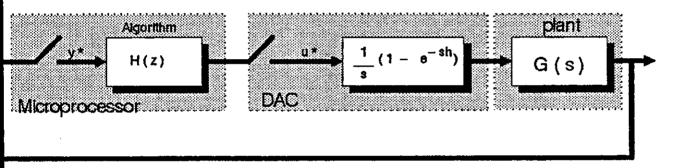

To develop a form of a sampled system as shown in Fig.4.2 the system is depicted as follows. Each A/D converter is represented by an ideal sampler [4.4]. Each D/A converter is represented by a sampler followed by Zero Order Hold (ZOH) circuit having the following transfer function [4.5]:

$$h_{zoh} = \frac{1}{\frac{1}{s}} (1 - e^{-sh})$$

(4.1)

where h is the sample time.

The plant is modelled by its linear transfer function, which, in this case is

$$G(s) = \frac{k}{\sigma s}$$

(4.2)

and the calculations in the microprocessor are expressed by their pulse transfer function H(z) as shown in Fig.4.2 [4.2].

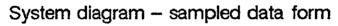

Fig.4.3 is obtained by first combining the analogue parts (the hold, sampler and plant [4.3,4.4,4.6]) to give a combined transfer function of;

$$G(s) = \frac{1}{s} (1 - e^{-sh}) G(s)$$

(4.3)

The discrete equivalent of this is obtained using invariant impulse transform tables [4.5]:

$$G(z) = (1 - z^{-1}) Z[G(s)/s]$$

$$G(z) = \frac{kh z^{-1}}{\tau(1 - z^{-1})}$$

where h is the sampling time.

In more general terms this transfer function can be written as:

$$G(z) = \frac{a_1 \ z^{-1}}{(1+ \ b_1 \ z^{-1})}$$

(4.4)

where  $a_1 = kh/\gamma$ , and  $b_1 = -1$

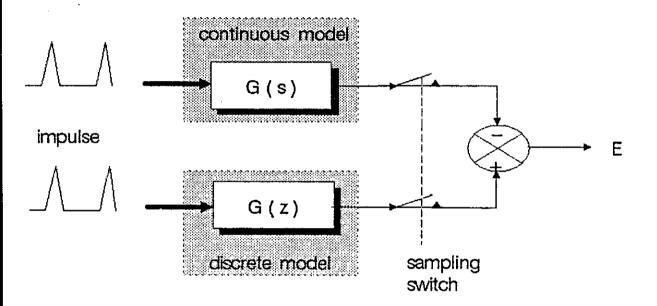

This method of representing the continuous plant as a discrete model is used for the following reason: If at sampling instants, as shown in Fig.4.4, E is zero then the continuous and discrete models are identical (note this does restrict us to the sample instants). Using the impulse invariant transform technique the resulting discrete model has a pulse response which is identical to that of the impulse response of the continuous model.

### 4.3 THE CONTROL LAW

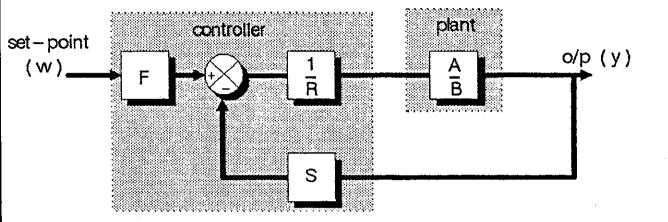

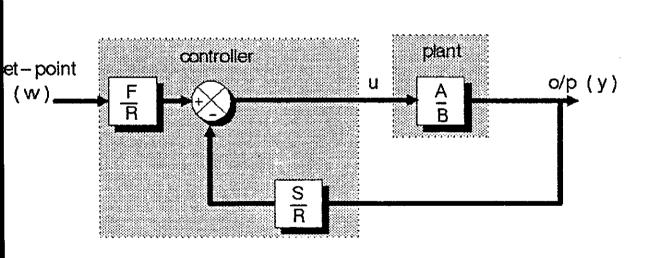

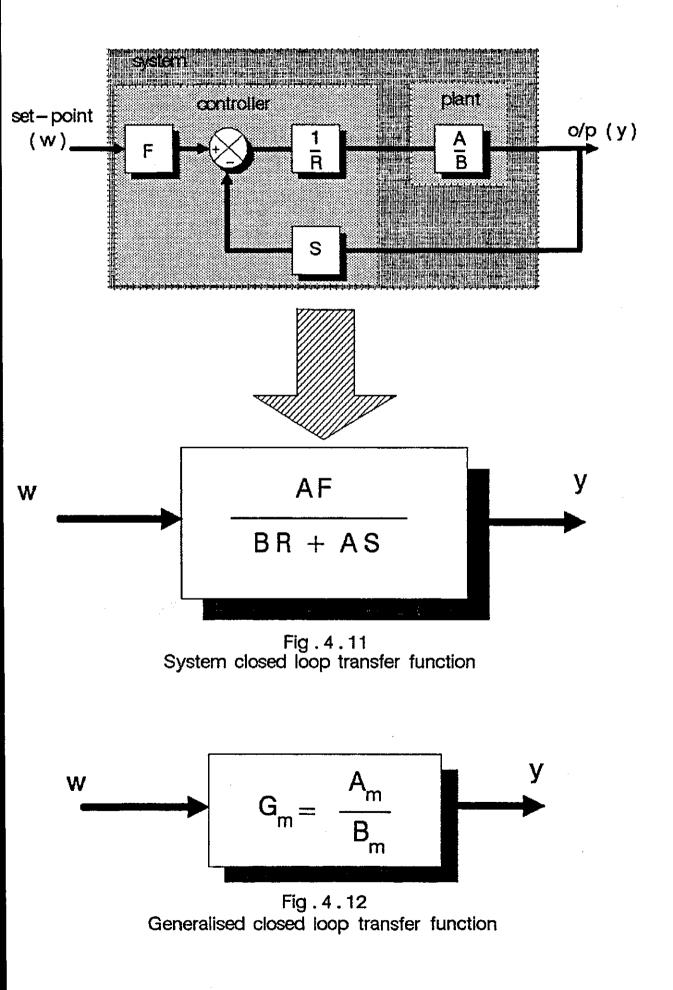

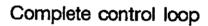

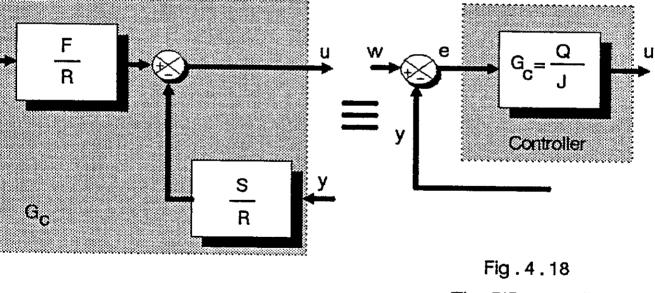

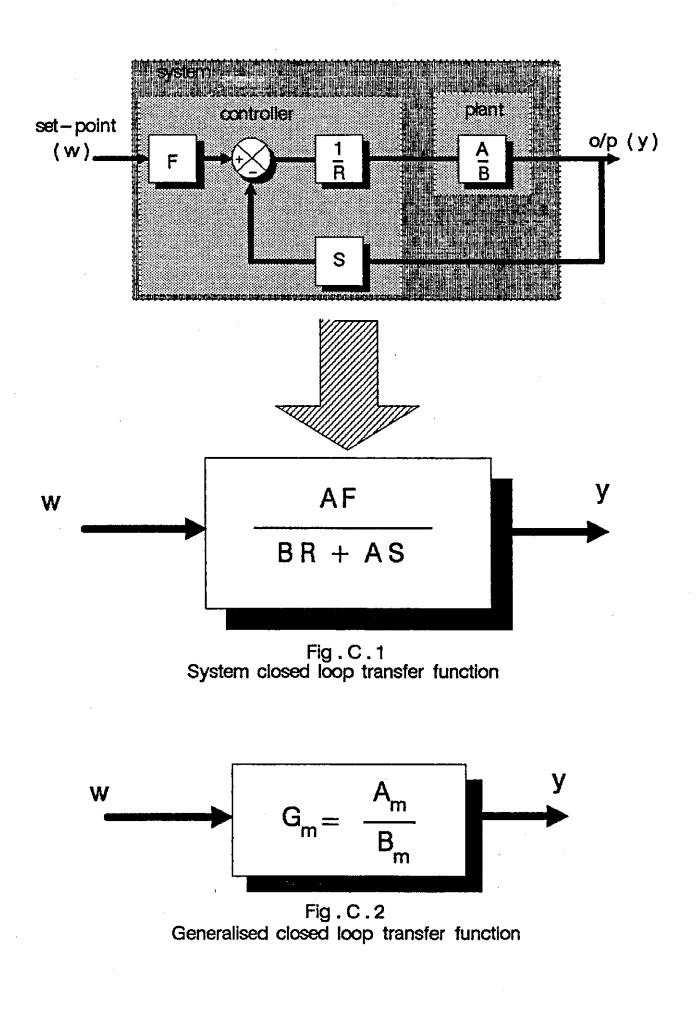

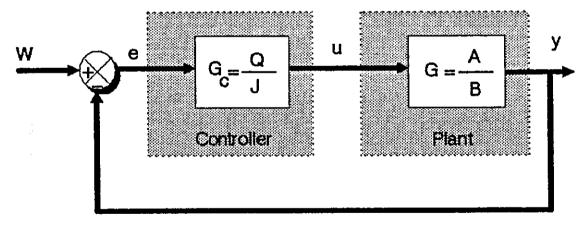

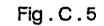

Fig.4.5 and Fig.4.6 show the most general form of a system controller, F, S and 1/R representing individual processing functions. Any closed loop controller can be represented by this structure. For instance with F=1, S=1, and R=0.01 the unit is a simple proportional (P) controller having a gain of 100.

Note that the symbology (F,S,1/R) is used for mathematical convenience only and has no other significance. From this structure the control law can be written in a general form [4.3] as:

Loop error =

$$F(z)w(t) - S(z)y(t)$$

i.e.

$$R(z)u(t) = F(z)w(t) - S(z)y(t)$$

(4.5a)

or

$$u(t) = \frac{F}{R} w(t) - \frac{S}{R} y(t) \qquad (4.5b)$$

where R, F and S are polynomials in the Z domain.

The control law (4.5) represents a combination of a feedforward from the command signal w with the pulse-transfer function [4.2]:

$$G_{ff} = \frac{F}{R}$$

and a feedback from the measured output y with the pulse transfer function:

$$G_{fb} = \frac{S}{R}$$

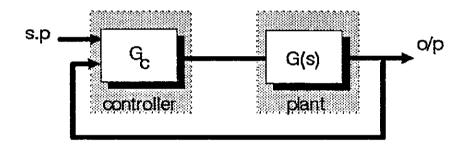

For a digital controller  $G_c$  to be physically realisable, the power series expansion of the controller transfer function  $G_c$  must not contain any positive power in z [4.10]. Any positive power in z in the series expansion of  $G_c$  indicates that the

output precedes the input to  $G_c$ . This cannot be implemented since it requires a knowledge of future values of the input to the controller [4.11]. Therefore, the feedforward and the feedback transfer functions should satisfy the causality conditions [4.2]:

deg  $R \ge deg F$ deg  $R \ge deg S$

# 4.4 IMPLEMENTATION CONSIDERATIONS

# 4.4.1 Introduction

When implementing a digital controller the following are considered:

- \* Choice of sampling rate

- \* Computational delay

- **\*** Practical constraints

- \* Numerical accuracy

# 4.4.2 Choice of sampling rate

The selection of the best sample rate for a digital control system is the compromise of many factors. The basic motivation to lower the sample rate  $\omega_s$  is cost. A decrease in rate means more time is available for the control calculations; hence slower microprocessors can be used for a given control function and the cost per function is lowered. Alternatively the original processor can perform extra tasks above that of controlling the plant. For systems with A/D converters, less demand on conversion speed will also lower cost. These economical arguments indicate that the best engineering choice is the slowest possible sample rate that still meets all performance specifications [4.7].

Factors that provide a lower limit to the acceptable sample rate are:

- \* Tracking effectiveness

- \* Disturbance rejection

- \* Prefilter design

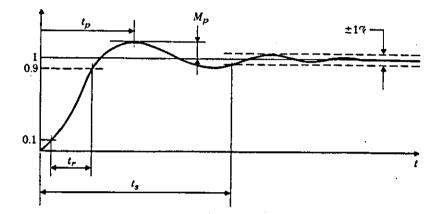

### (a) Tracking effectiveness

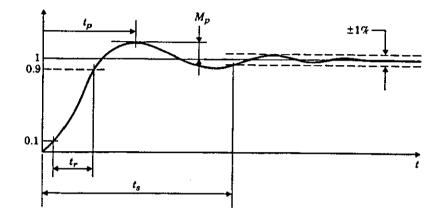

This is defined in terms of closed-loop bandwidth or transient time response performance, such as rise time and settling time. The lowest bound to the sample rate is set by a specification to track a command input with certain frequency (the system bandwidth) [4.7]. The sampling theorem states that in order to reconstruct a continuous signal from samples of that signal, one must sample at least twice as fast as the highest frequency contained in the signal [4.8].

This is likely to be significantly higher than the closed loop bandwidth. In practice test results show that this theoretical lower bound of sampling is not sufficient in terms of the quality of the desired time responses, and a sample rate of 4-20 times  $\omega_{BW}$  is reasonable [4.4]. This is done mainly to reduce the delay between the set-point and the system response to that set-point change [4.7]. Furthermore it smooths the system output response to the control steps coming out of the DAC since, as sampling rates are increased, the step change in DAC output amplitude reduces. Consequently control action becomes less abrupt and control roughness is reduced at high sampling rates [4.4].

It is important to distinguish between closed-loop bandwidth and the highest frequencies present in the open-loop system. In the majority of cases closed-loop bandwidths are significantly higher than their corresponding open-loop values.

0.L.T.F =

$$\frac{1}{1 + \gamma_s}$$

= G(s)

For Gc=10 as shown in Fig.4.7, then

C.L.T.F =

$$\frac{G_cG(s)}{1 + G_cG(s)} = \frac{10/1 + \gamma' s}{1 + 10/1 + \gamma' s}$$

$$= \frac{10}{1 + \tau s + 10} = \frac{10}{11 + \tau s}$$

$$= \frac{10}{11} \frac{1}{1 + \tau/11 s}$$

This may, however, be complicated by resonance effects within the loop which have high natural frequencies.

The situation is further complicated if the controller is likely to experience high frequency electrical interference. Here sampling rates are determined by the input filter design (see paragraph (c)); the resulting performance aspects may lead to the use of multi-rate sampling techniques [4.3] in conjunction with digital low pass filtering of the input signal.

### (b) Disturbance rejection

Disturbance rejection is an important aspect in control systems. If the sample rate is very fast compared with the frequencies contained in the noise disturbance, the noise rejection will be high [4.5]. However, if the sample time is very long compared with the characteristic frequencies of the noise, the response of the system to the noise is essentially the same as if there were no control at all [4.7].

Although the best choice of sample rate is dependent on the frequency characteristics of the noise and the degree to which random disturbance rejection is important to the quality of the controller, sample rate requirements of 10-20 times

$\omega_{BW}$  are common [4.4,4.7].

# (c) Prefilter design

Digital control systems with analogue sensors typically include an analogue prefilter between the sensor and the A/D converter as an antialiasing device. The prefilters are low-pass, typically 3rd to 6th order filters being used in fast systems [4.9]. The simplest transfer function is [4.7]:

$$H_P(s) = \frac{a}{s+a}$$

so that the noise above the prefilter breakpoint a is attenuated [4.10]. The design goal is to provide enough attenuation at half the sample rate ( $\omega_s/2$ ) so that the noise above  $\omega_s$ , when aliased into lower frequencies by the sampler, will not be detrimental to the control system performance [4.4]. A conservative design procedure is to select the breakpoint and  $\omega_s$  sufficiently higher than the system bandwidth so that the phase lag from the prefilter does not significantly alter the system stability. Thus the prefilter can be ignored in the basic control system design [4.7]. Furthermore, for a good reduction in the high frequency noise at  $\omega_s/2$ , the sample rate is selected about 5 or 10 times higher than the prefilter breakpoint [4.7]. This selection is related to the order of the filter [4.9]. The implication of this prefilter design procedure is that the sample rates need to be of the order of 20 to 100 times faster than the system bandwidth. This means that the prefilter specification determines the lower bound of the sample rate.

△ The rise time of the actuator system is approximately 4.3 Sec. A sampling time of 0.1 Sec, roughly 40 times faster than the rise time, is used in the controller.

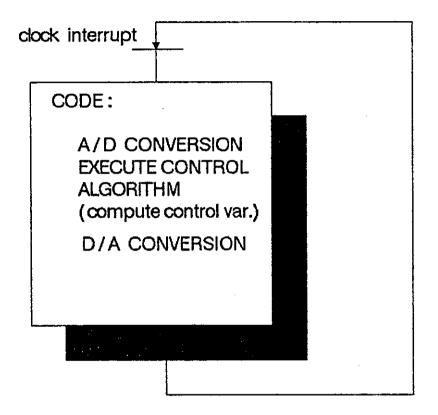

### 4.4.3 Computational delay

There is always time delay when implementing a control algorithm using

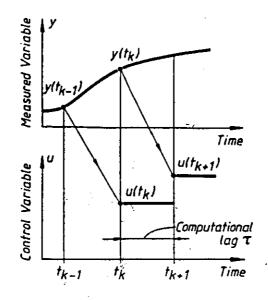

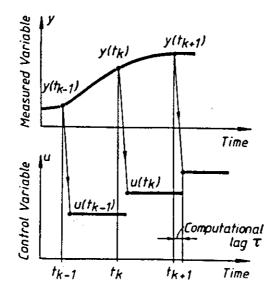

microprocessors [4.10]. This delay is due to A/D and D/A conversion times and the time required to carry out the control calculations. The A/D and D/A conversion time is usually negligible (e.g. 25 uSec.), the significant time being the computational time. This is called the computational delay which is determined mainly by how the control algorithm is implemented.  $\Delta$  There are two ways to implement the control algorithm as shown in Fig.4.8 and Fig.4.9 [4.11].

In Fig.4.8 the measured value is read at time t and used to compute the control signal which is then applied at time t+1. This means that there is a time delay in the controller of one sample interval. In Fig.4.9 the measured value is read at time t, the control signal computed immediately, and the result output via the D/A converter as soon as possible. This means that the control signal is delayed only a fraction of the sample time [4.11].

The advantage of the second case is that the computation time can be ignored if it is very small. This delay is variable, depending upon the programming and mathematical floating point operations [4.5]. In many situations this variability can be ignored. However if it is significant when compared with the sampling time it may cause problems in the control loop [4.3]. The disadvantage of the first case is that the control signal is delayed one sample, but the advantage is that, as the delay time is constant, it is a straightforward to include one time-delay in the controller.

<u>The effect of having one time-delay in the controller is the same as having</u> one extra time-delay in the plant model [4.11]. Thus system performance can be evaluated by including the sample time delay in the plant model [4.11].

In servo systems the response should be virtually instantanous. Therefore it is unacceptable for the controller to have any time delay at all; hence the second implementation only is considered in this work.

The execution times obtained for different algorithms are shown in Appendix-C. In this system the slight delay between the y(t) sample and the u(t)

output has negligible effect on the actual response of the system. A rule of thumb would be to keep the delay in the order of 1/20th of the system rise time [4.7].

## 4.4.4 Practical constraints

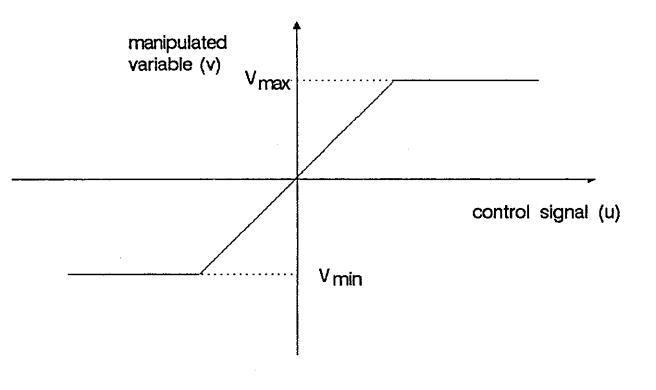

The non-linearity produced by system saturation (Fig.4.10) represents the practical behaviour of many actuators and final control elements [4.12]. For example, a motor-amplifier combination can produce a torque proportional to the input voltage over limited range. However, no amplifier can supply an infinite current; there is a maximum current and thus a maximum torque that any practical system can produce [4.8]. The final control element is said to be overdriven when commanded by the controller to do something beyond its capabilities. The performance of all control elements is ultimately limited by the rate at which they can supply energy. Therefore it is important that all system performance specifications and controller designs be consistent with the energy-delivery capabilities of real devices [4.8,4.13].

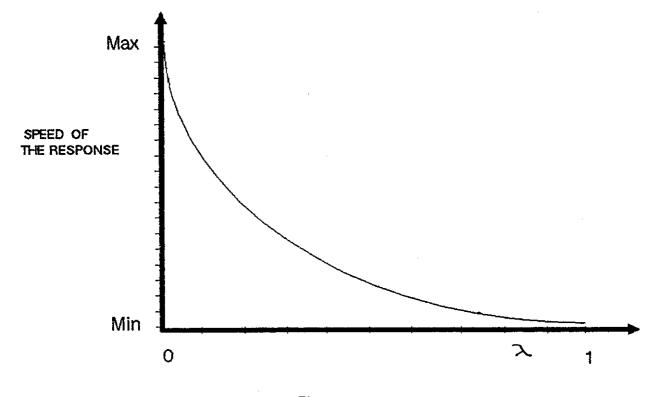

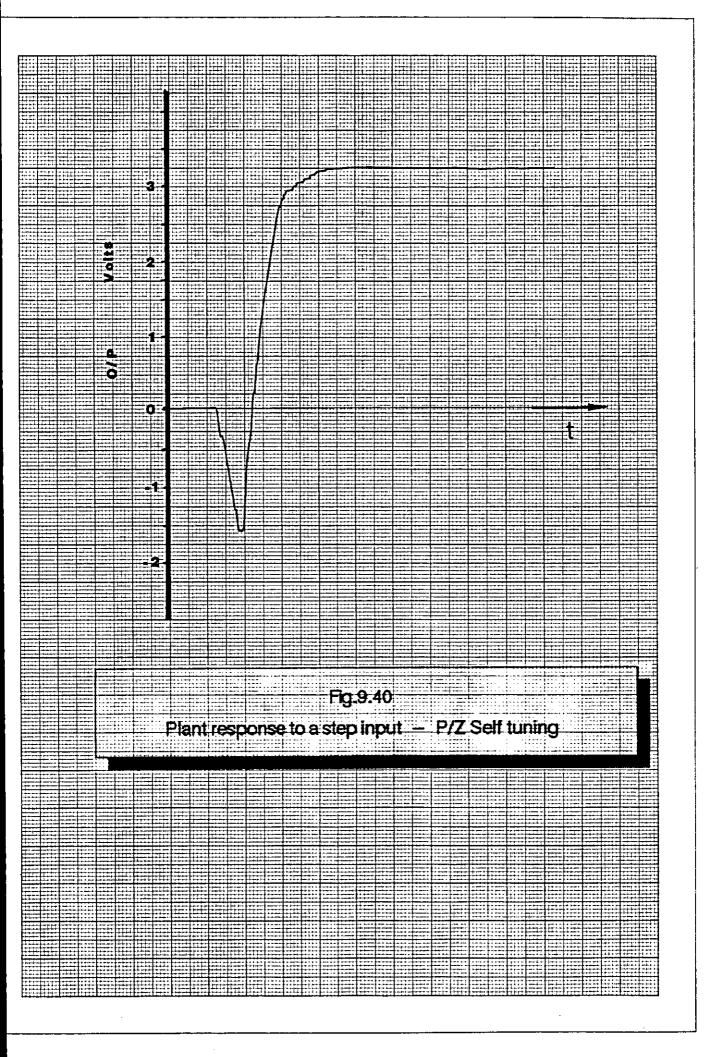

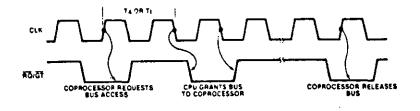

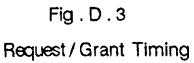

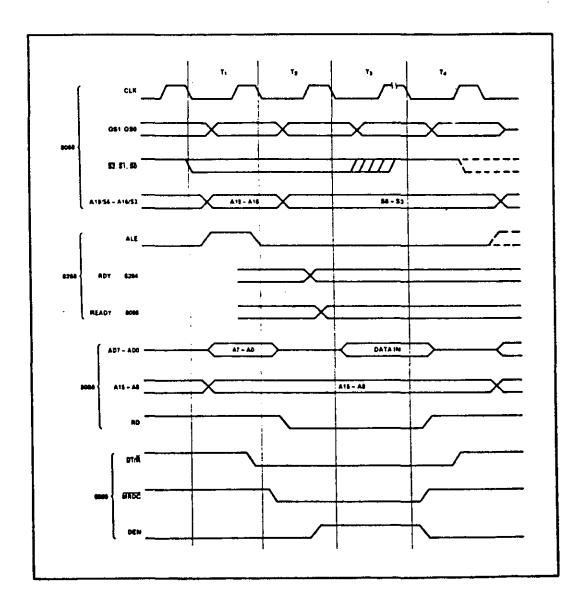

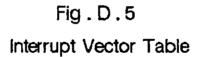

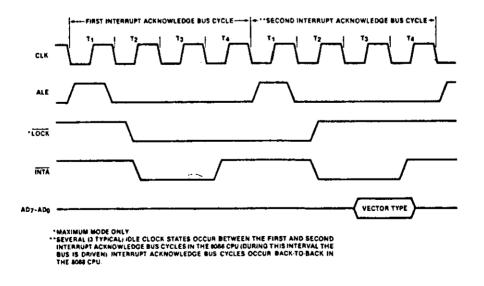

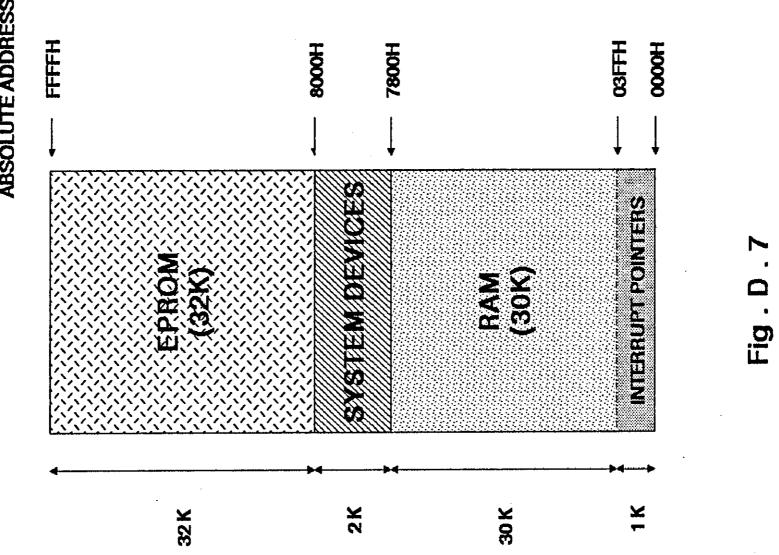

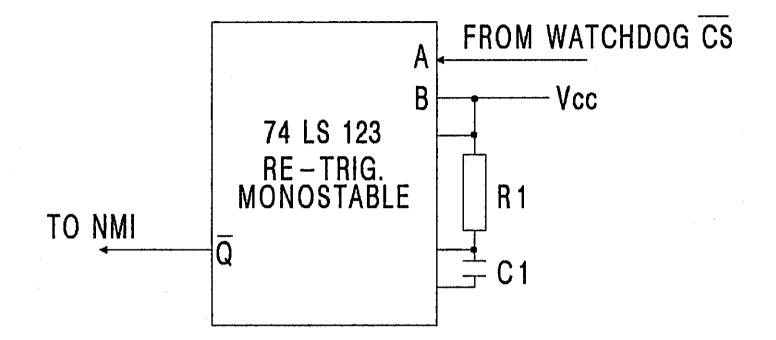

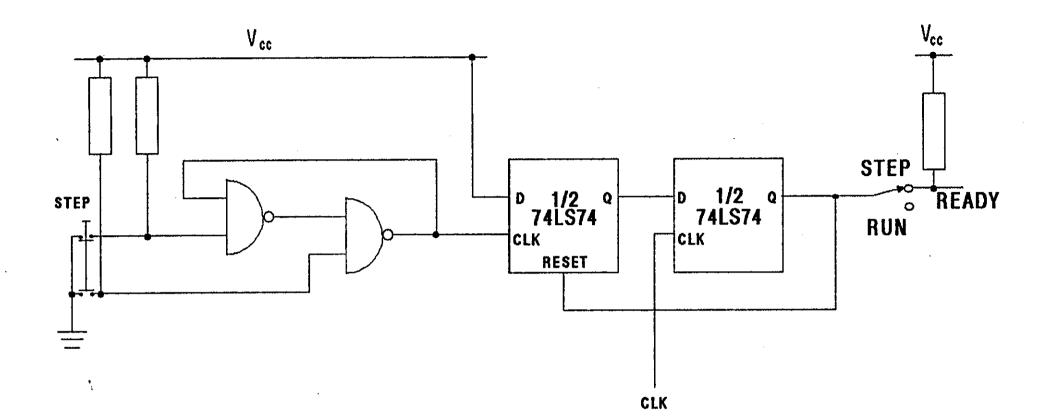

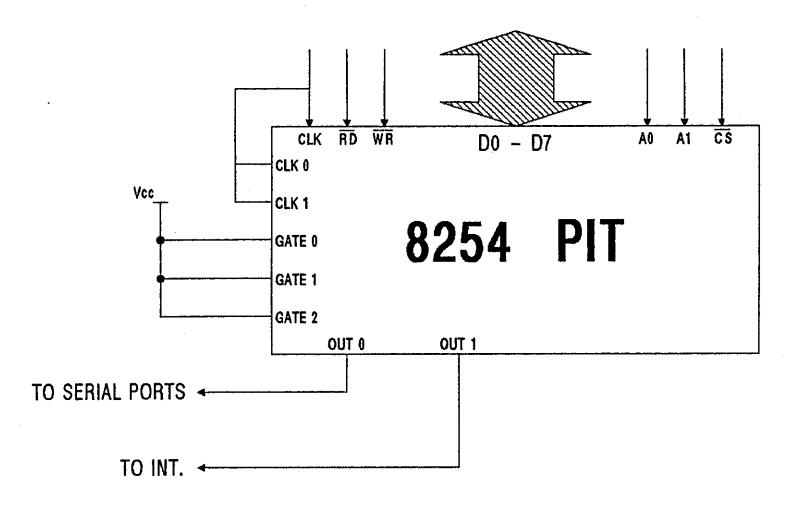

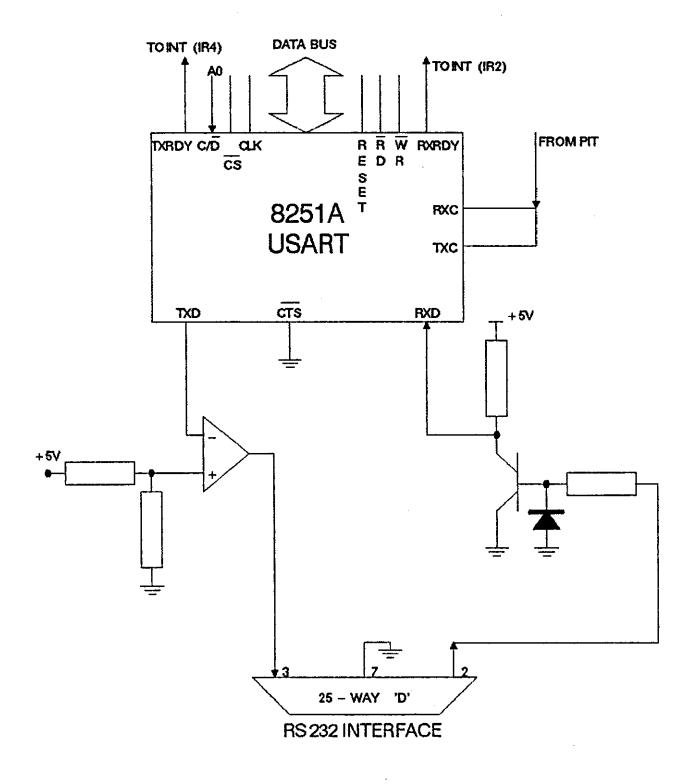

In this work system identification is part of the self-tuning controller. Therefore, the system identification may fail to identify the system if it saturates. This is due to the fact that the identification algorithm will identify a saturating plant as having a very low gain. Consequently a controller with an unsuitable high gain will be implemented [4.14]. It is therefore essential to make sure that the controller never allows the plant to saturate. There are two ways to achieve this [4.8]: