BLDSC no :- DX 79585

|                                       | UNIVE                                                                                                                 | LOUGHBOROUG<br>RSITY OF TECH<br>LIBRARY |                                |                                              |             |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------|----------------------------------------------|-------------|

|                                       | AUTHOR/FILING                                                                                                         |                                         |                                |                                              |             |

|                                       | AL                                                                                                                    | KHAYATT,                                | <u>55</u>                      |                                              | - 5         |

|                                       |                                                                                                                       | ······································  |                                |                                              |             |

|                                       | ACCESSION/COP                                                                                                         |                                         | <u></u>                        |                                              |             |

|                                       |                                                                                                                       | 036000755                               | •                              | ,                                            |             |

|                                       | VOL. NO.                                                                                                              | CLASS MARK                              |                                | <b>- - - -</b>                               |             |

|                                       | •                                                                                                                     |                                         | •                              |                                              | •           |

|                                       | ·<br>                                                                                                                 |                                         | T                              |                                              |             |

|                                       |                                                                                                                       | LOAN COPY                               |                                | ÷<br>•                                       |             |

| - <b>1</b>                            |                                                                                                                       |                                         |                                | :                                            | -           |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                | :                                            | · .         |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         | · *                            |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                | ÷                                            | ,           |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       | ł                                       |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         | •                              |                                              | ,           |

|                                       |                                                                                                                       |                                         | a para la para de              |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              | ·           |

|                                       | an<br>An an an Anna a | _ · ·                                   |                                | ·                                            |             |

|                                       | •                                                                                                                     |                                         | •                              |                                              | •           |

|                                       |                                                                                                                       |                                         | e and an in<br>An anti-Anna an | an a     |             |

|                                       | n an                                                                              |                                         |                                |                                              |             |

|                                       | 03<br>Nili 1                                                                                                          |                                         |                                |                                              |             |

|                                       |                                                                                                                       |                                         |                                |                                              | :           |

|                                       | urfi <b>a (</b>                                                                                                       | *** =********************************** | 11410                          | •                                            |             |

|                                       |                                                                                                                       |                                         | •                              | THIS BOOK W                                  | AS BOUND BY |

|                                       |                                                                                                                       |                                         |                                | THIS BOOK W<br>BADMINTO<br>18 THE HA<br>SYST | ON          |

| · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·                                                                                 | . · · · ·                               |                                | LEICESTER<br>0533 6                          | LE7 BLD     |

• ئ

. . T 1 I. 7 1 1

### FUNCTIONAL PARTITIONING OF MULTI-PROCESSOR ARCHITECTURES

by

SAMIR S. AL-KHAYATT, BSc, MSc

A Doctoral Thesis submitted in partial fulfilment of the requirements for the award of the degree of Doctor of Philosophy of the Loughborough University of Technology

July 1990

Supervisor: J.E. Cooling, BSc, CEng, MIEE, MIEEE

Department of Electronic and Electrical Engineering Loughborough University of Technology

© Samir S. Al-Khayatt

· · ·

.

## 3991123X

# To My Family

.

#### SYNOPSIS

#### FUNCTIONAL PARTITIONING OF MULTI-PROCESSOR ARCHITECTURES

Many real-time computations such as process control and robotic applications may be naturally distributed in a functional manner. One way of ensuring good performance, reliability and security of operation is to map or distribute such tasks onto a distributed, multi-processor system. The time critical task is thus functionally partitioned into a set of cooperating sub-tasks. These sub-tasks run concurrently and asynchronously on different nodes (stations) of the system. The software design and support of such a functional distribution of sub-tasks (processes) depends on the degree of interaction of these processes among the different nodes.

The research work carried out is concerned with the following points:

- \* The design and implementation of a loosely coupled multi-processor system that has been designed and implemented for use in faulttolerant, real-time applications. Each processing unit (station) consists of a single board computer, where the communication and processing tasks are decoupled on each board. It uses a single shared parallel bus for communication between these stations, bus control being fully distributed.

- \* The development of software environment to support functional partitioning. This consists mainly of:

- i) A real-time kernel structure to support and manage partitioned sub-tasks on various processing sections of the system.

i

- ii) A communication software protocol that supports communication between the different processing sections of the system. This is performed using message passing techniques based on token passing.

- iii) A run-time support system for the operation of the communication protocol.

The communication and real-time kernel software have been written mainly in Modula-2. This required the use of two different compilers. A small amount of assembly language programming was also used. This software is hosted on a multi-processor demonstrator system which has been developed as part of the research programme.

#### ACKNOWLEDGEMENTS

I wish to express my deep sense of gratitude to my supervisor Mr J E Cooling for his guidance, inspiration, stimulating discussions, and most of all encouragement during the preparation of this work.

Thanks are also due to the following:

- \* The staff, and technicians for their valuable assistance.

- \* My wife for her endurance and support throughout the project.

#### TABLE OF CONTENTS

| Synopsis | 3      |                                               | i   |

|----------|--------|-----------------------------------------------|-----|

| Acknowle | edgeme | ents                                          | iii |

| List of  | Figur  | res                                           | xi  |

| List of  | Chart  | ts                                            | xv  |

| List of  | Abbre  | eviations                                     | vii |

| CHAPTER  | 1:     | INTRODUCTION                                  | 1   |

|          | 1.1    | Overview                                      | 1   |

|          | 1.2    | Research Objectives                           | 2   |

|          | 1.3    | Thesis Organisation                           | 3   |

|          |        | Figures                                       | 5   |

| CHAPTER  | 2:     | METHODS OF TASK MANAGEMENT IN DISTRIBUTED     |     |

|          |        | SYSTEMS                                       | 7   |

|          | 2.1    | General                                       | 7   |

|          | 2.2    | Partitioning Schemes for Distributed          |     |

|          |        | Environments                                  | 7   |

|          |        | 2.2.1 Overview                                | 7   |

|          |        | 2.2.2 Designing a Distributed System as a     |     |

|          |        | Single Program                                | 8   |

|          |        | 2.2.3 Functional Partitioning Schemes         | 10  |

|          | 2.3    | Task Allocation Strategies                    | 12  |

|          | 2.4    | Inter-Process Communication in Distributed    |     |

|          |        | Systems                                       | 13  |

|          |        | Figures                                       | 15  |

| CHAPTER  | 3:     | FUNDAMENTAL ASPECTS OF DISTRIBUTED CONCURRENT |     |

|          |        | PROGRAMS                                      | 20  |

|          | 3.1    | Concurrent Programs (Use of Processes)        | 20  |

|          |        | 3.1.1 General                                 | 20  |

|          |        | 3.1.2 Processes                               | 20  |

|          |        | 3.1.3 Process Interaction                     | 21  |

| 3.2        | Specifying Concurrent Execution              | 23         |

|------------|----------------------------------------------|------------|

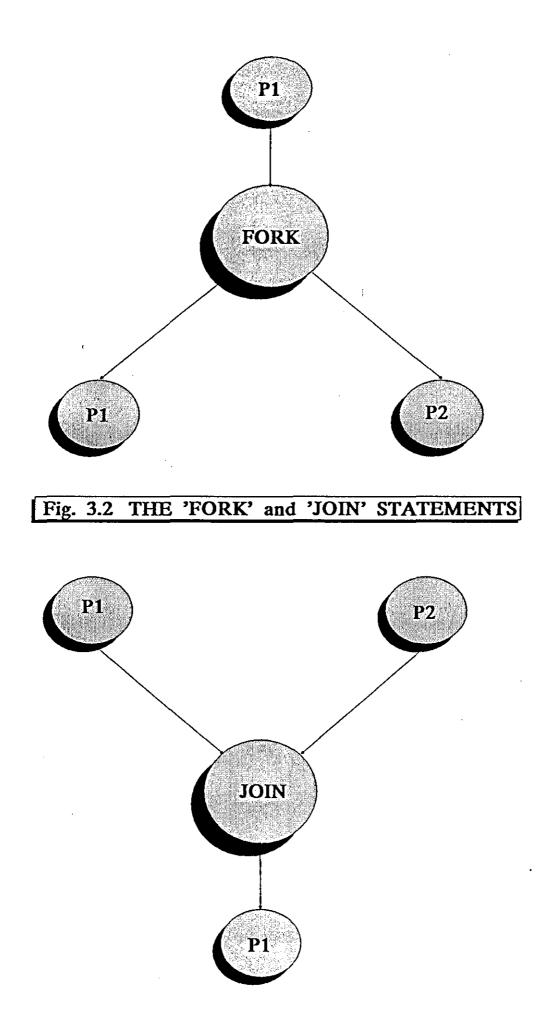

|            | 3.2.1 The Fork and Join Statements           | 23         |

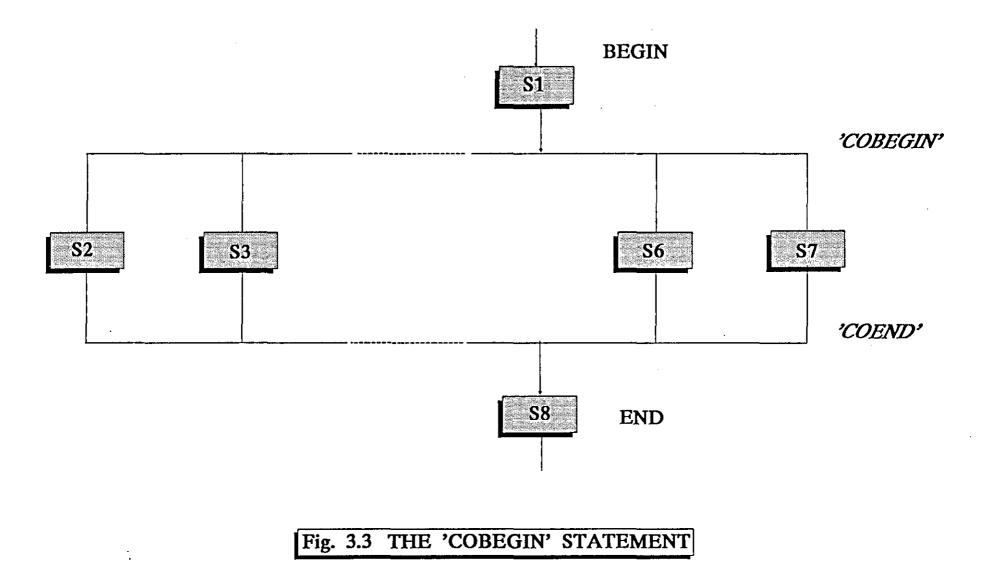

|            | 3.2.2 The Cobegin Statement                  | 24         |

|            | 3.2.3 Coroutines                             | 24         |

| 3.3        | Introduction to Synchronisation Techniques . | 25         |

|            | 3.3.1 Critical Sections                      | 25         |

|            | 3.3.2 Semaphores                             | 25         |

|            | 3.3.3 Synchronisation Techniques and         |            |

|            | Language Classes                             | 27         |

| 3.4        | Procedure-Oriented Synchronisation Method    | 28         |

|            | 3.4.1 Monitors                               | 28         |

|            | 3.4.2 Nested Monitor Calls                   | 31         |

| 3.5        | Message-Passing Synchronisation Primitives . | 32         |

|            | 3.5.1 General                                | 32         |

|            | 3.5.2 Specifying Channels for Communication  | 32         |

|            | 3.5.3 Synchronisation                        | 35         |

| 3.6        | 'Operation-Oriented' Synchronisation Methods | 37         |

|            | 3.6.1 General                                | 37         |

|            | 3.6.2 The Remote Procedure Call (RPC)        | 37         |

|            | 3.6.3 Rendezvous                             | 38         |

|            | 3.6.4 Messages in Distributed Systems        | 42         |

|            | Figures                                      | 44         |

| CHAPTER 4: | A MULTI-PROCESSOR STRUCTURE TO SUPPORT       |            |

|            | FUNCTIONAL PARTITIONING                      | 55         |

| 4.1        | System Overview                              | 55         |

| 4.2        | Functional Description                       | 56         |

| 4.3        | Inter-Processor Communication                | 57         |

| 4.4        | Operating System Support - the Distributed   |            |

|            | Program Kernel                               | 59         |

|            | 4.4.1 General                                | 59         |

|            | 4.4.2 Distributed-Program Kernel             | 5 <b>9</b> |

| 4.5        | Programming Language Issues - Modula-2       | 61         |

|            | 4.5.1 General                                | 61         |

.

.

|            | 4.5.2  | Assessment of Competitors               | 62 |

|------------|--------|-----------------------------------------|----|

|            | 4.5.3  | Possible Competitors of the Future      | 63 |

|            | 4.5.4  | Why Modula-2?                           | 64 |

|            | Figure | s                                       | 65 |

|            |        |                                         |    |

| CHAPTER 5: | MULTI- | PROCESSOR SYSTEM - HARDWARE STRUCTURE . | 68 |

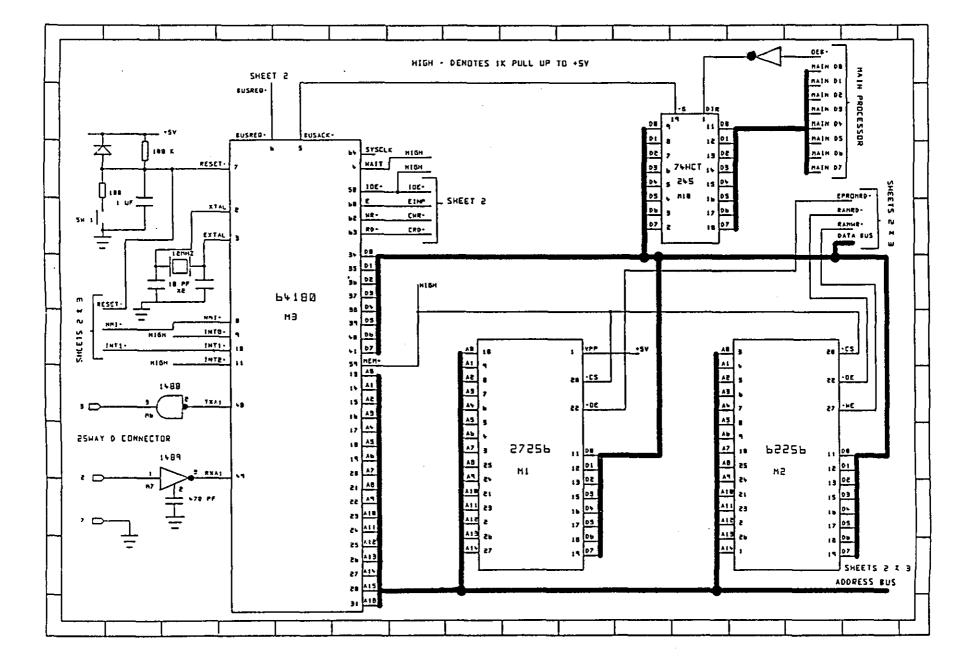

| 5.1        | Overvi | ew                                      | 68 |

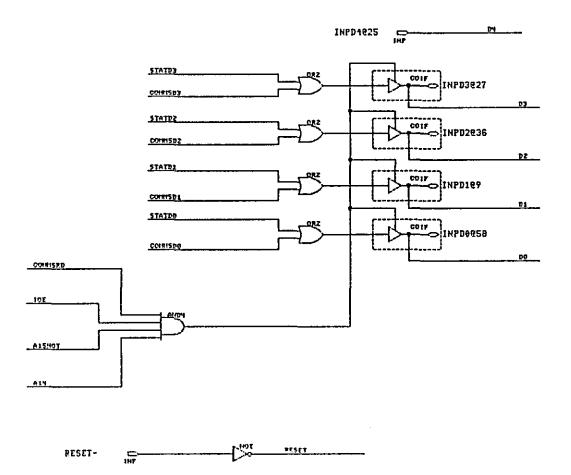

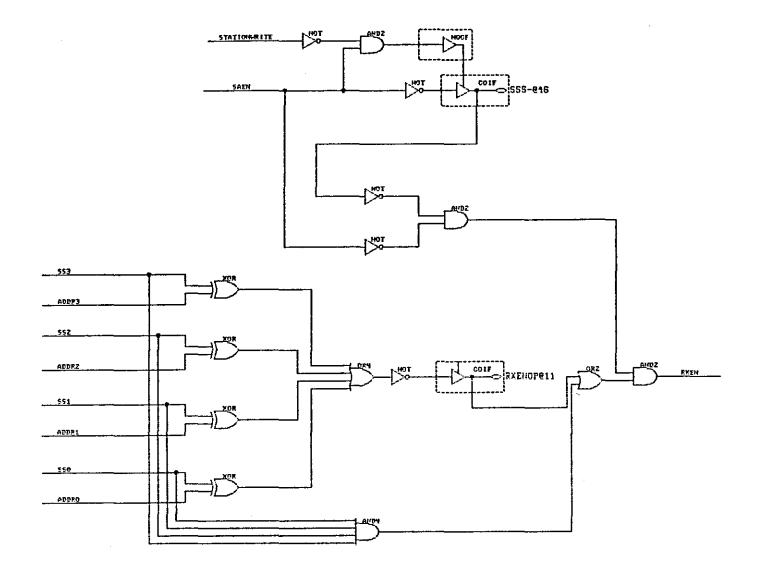

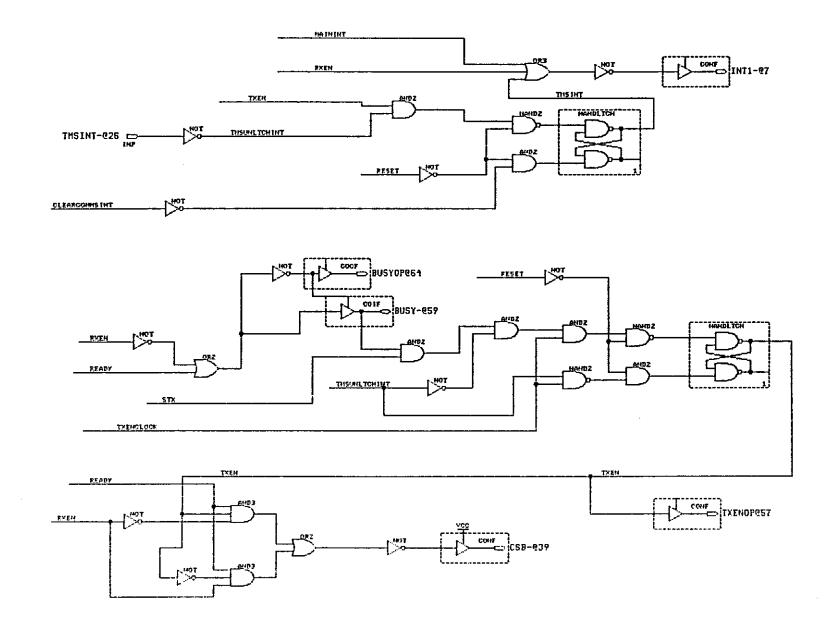

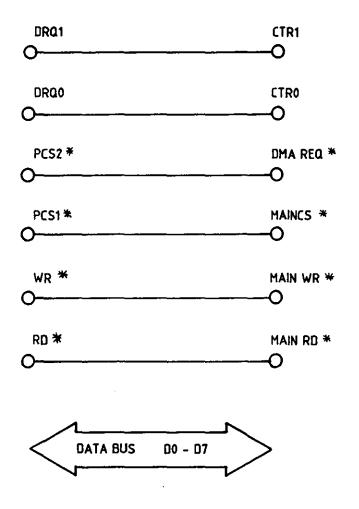

| 5.2        | System | Interfacing                             | 68 |

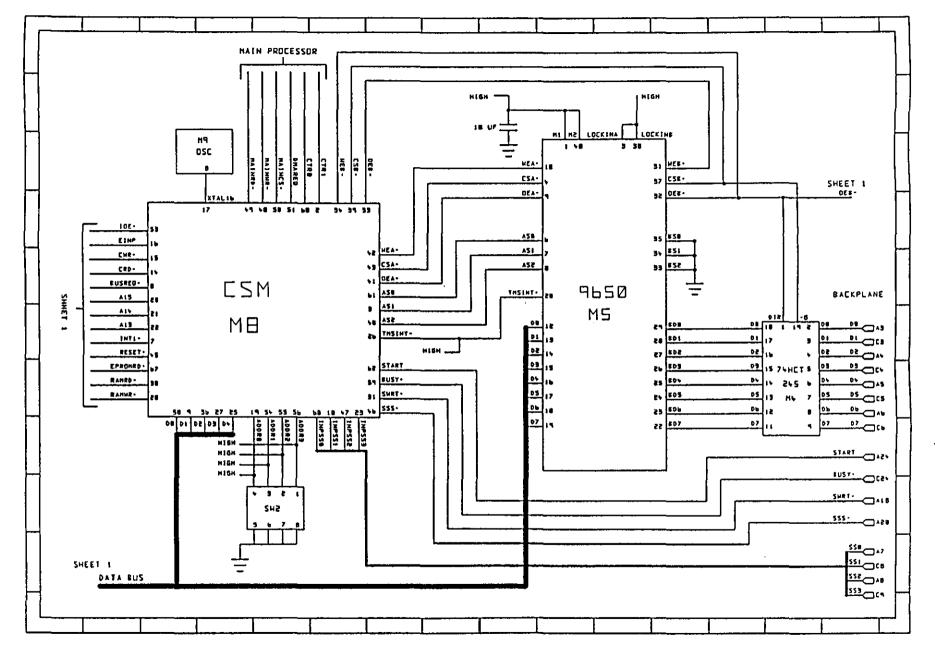

| 5.3        | Commun | ication Section                         | 70 |

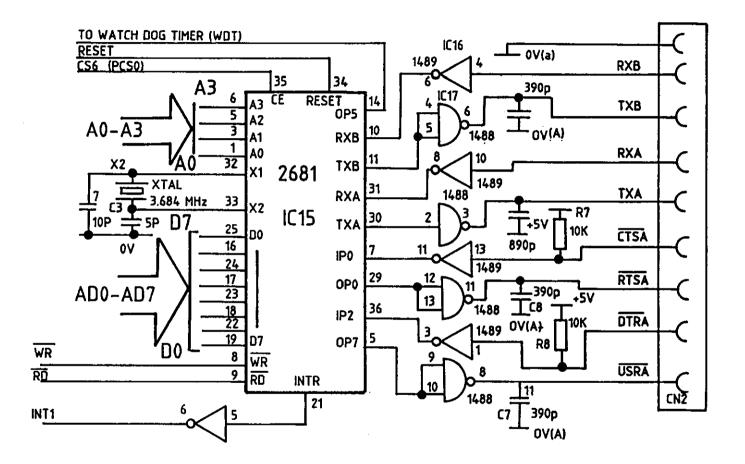

|            | 5.3.1  | Communication Processor                 | 71 |

|            | 5.3.2  | Communication Support Module (CSM)      | 71 |

|            | 5.3.3  | Temporary Memory Store (TMS)            | 73 |

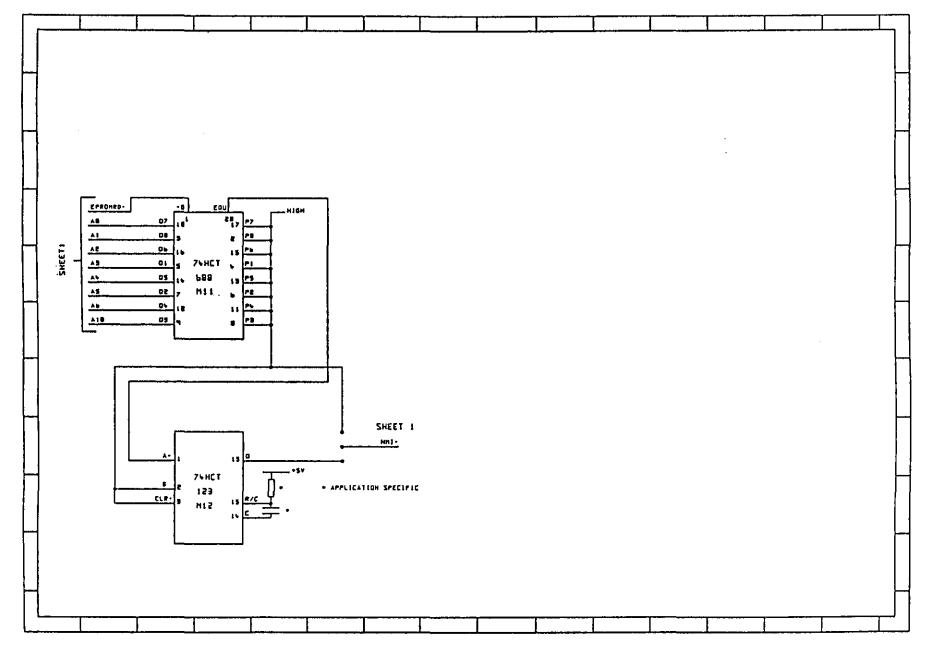

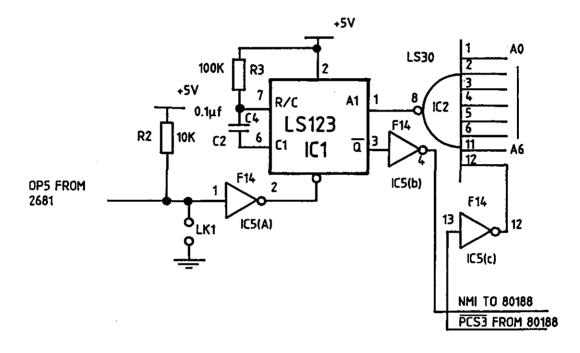

|            | 5.3.4  | A Watchdog Timer                        | 74 |

|            | 5.3.5  | System Bus Buffers                      | 74 |

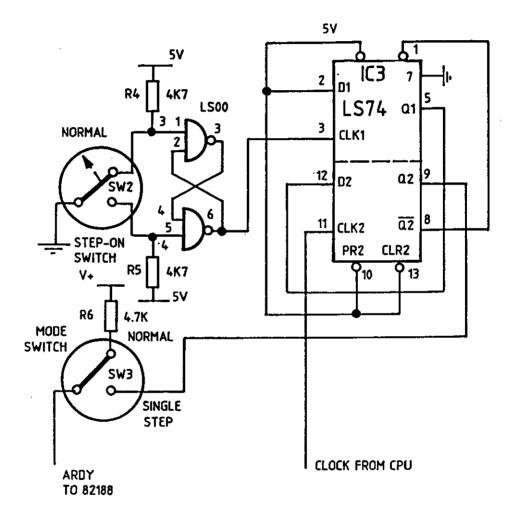

|            | 5.3.6  | Power-on Reset Circuitry                | 74 |

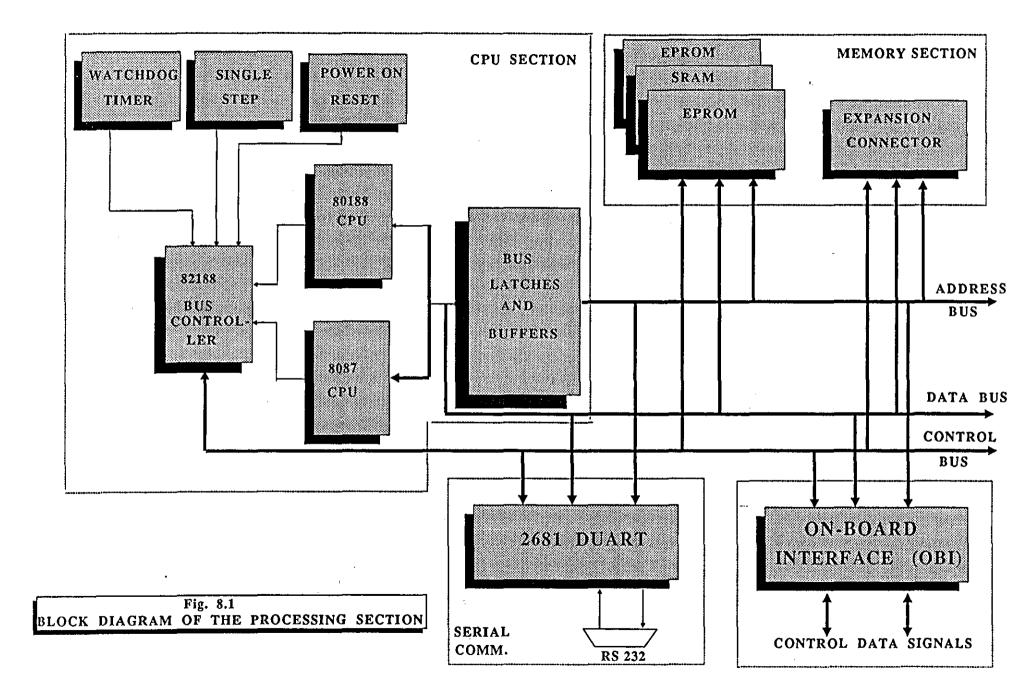

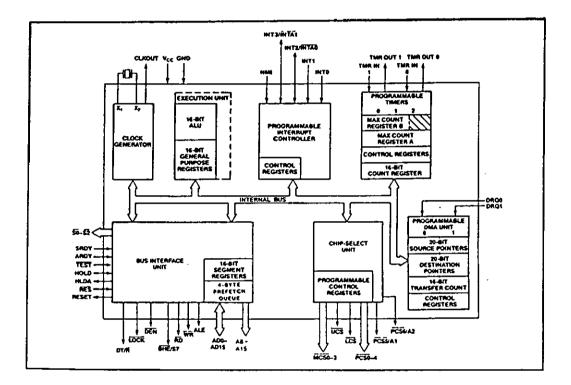

| 5.4        | Proces | sing Section                            | 75 |

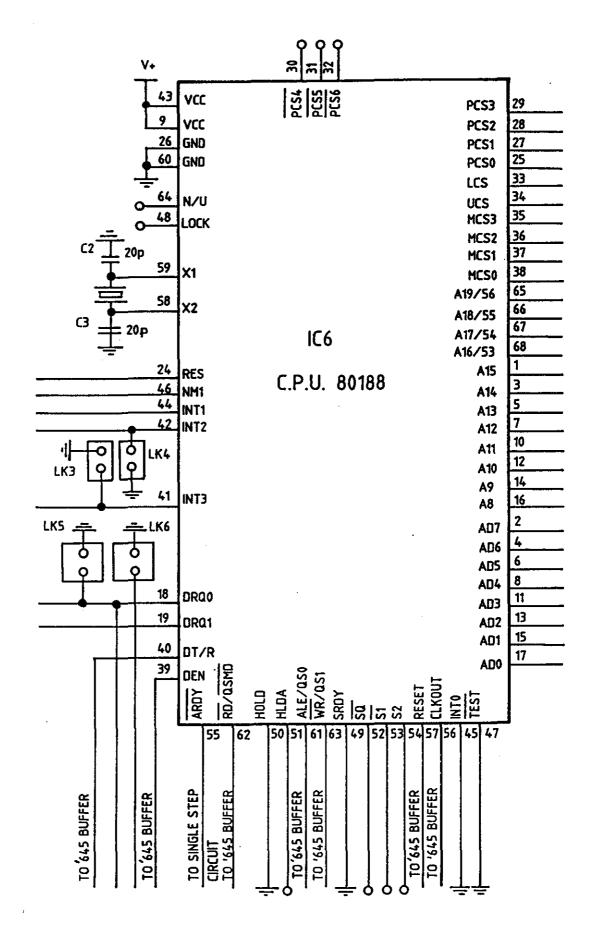

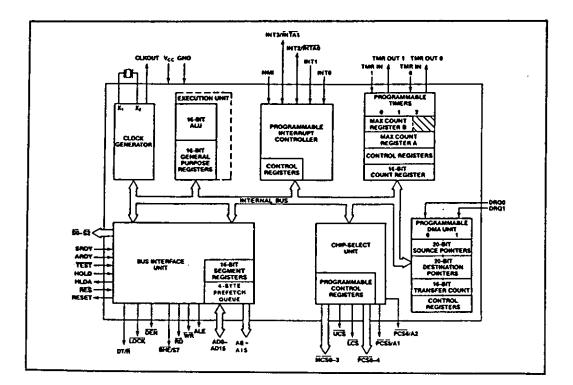

|            | 5.4.1  | CPU Section                             | 75 |

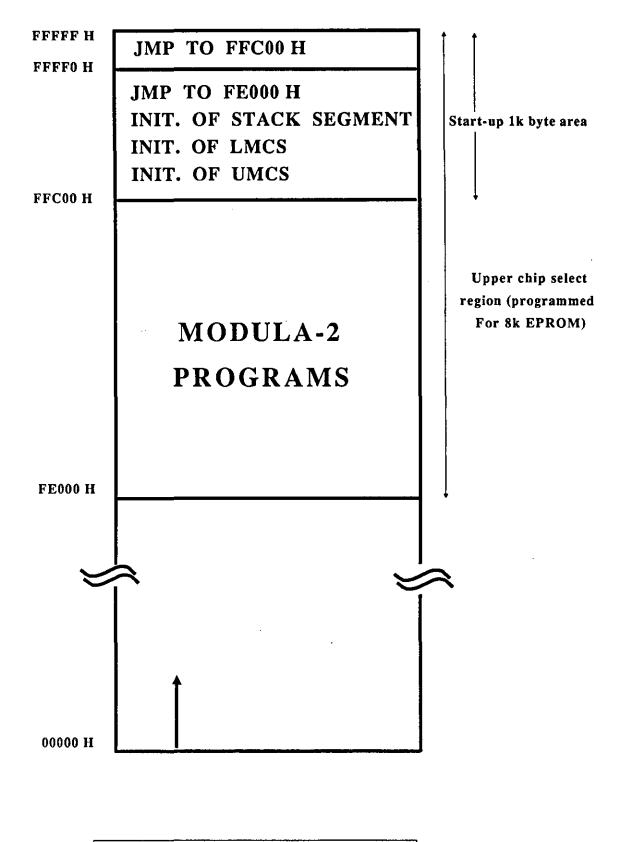

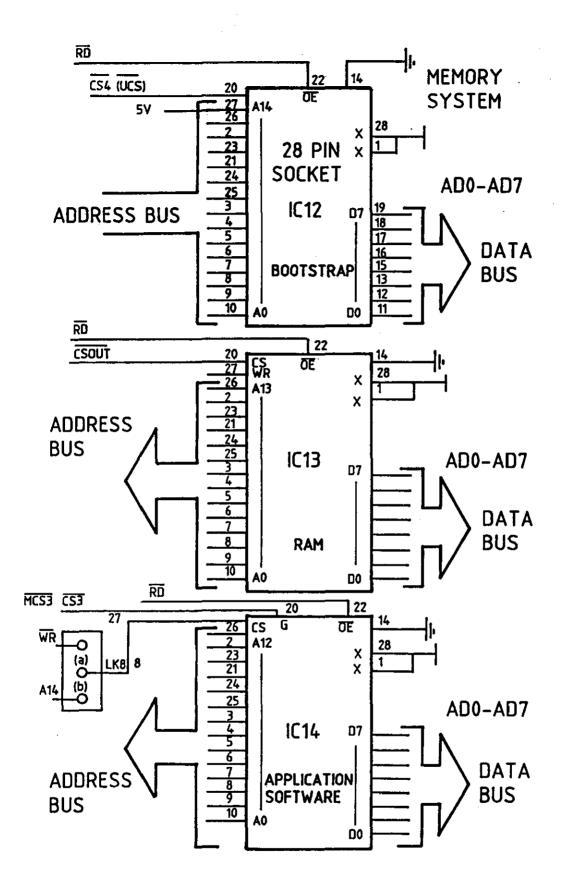

|            | 5.4.2  | Memory                                  | 77 |

| 5.5        | Hardwa | re-System Operation                     | 77 |

|            | 5.5.1  | Power-up                                | 78 |

|            | 5.5.2  | Initialisation                          | 78 |

|            | 5.5.3  | Operational Mode (Steady State)         | 79 |

|            |        | 5.5.3.1 Transmission of a Message       | 79 |

|            |        | 5.5.3.2 Reception of a Message          | 80 |

|            | Tables |                                         | 82 |

|            | Figure | s                                       | 84 |

|            |        |                                         |    |

| CHAPTER 6: | MULTI  | -PROCESSOR SYSTEM - COMMUNICATION       |    |

|            | SOFTWA | RE                                      | 96 |

| 6.1        | Softwa | re Requirements                         | 96 |

| 6.2        | Design | Techniques                              | 97 |

| 6.3        | Implem | entation of the Communication Protocol  | 98 |

|            | 6.3.1  | Software Module Structure - Overview    | 98 |

|            | 6.3.2                                                                                    | Communication Software (Main Module -                                                                                                                                                                                                           |                                                             |

|------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|            |                                                                                          | Run Comms)                                                                                                                                                                                                                                      | 100                                                         |

|            | 6.3.3                                                                                    | Second Level Modules                                                                                                                                                                                                                            | 102                                                         |

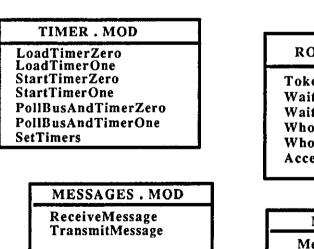

| ,          | 6.3.4                                                                                    | Service Modules                                                                                                                                                                                                                                 | 103                                                         |

|            |                                                                                          | 6.3.4.1 Control-Frame Modules                                                                                                                                                                                                                   | 103                                                         |

|            |                                                                                          | 6.3.4.2 Message-Exchange Modules                                                                                                                                                                                                                | 104                                                         |

|            |                                                                                          | 6.3.4.3 Hardware Related Module -                                                                                                                                                                                                               |                                                             |

|            |                                                                                          | 'Signals'                                                                                                                                                                                                                                       | 106                                                         |

| 6.4        | Implem                                                                                   | entation of the Run-Time Support System                                                                                                                                                                                                         | 109                                                         |

|            | 6.4.1                                                                                    | General                                                                                                                                                                                                                                         | 109                                                         |

|            | 6.4.2                                                                                    | CPM100 Module                                                                                                                                                                                                                                   | 109                                                         |

| 6.5        | System                                                                                   | Development and Operation                                                                                                                                                                                                                       | 110                                                         |

|            | 6.5.1                                                                                    | Compiling and Linking                                                                                                                                                                                                                           | 111                                                         |

|            | 6.5.2                                                                                    | Downloading into EPROMS                                                                                                                                                                                                                         | 111                                                         |

|            | 6.5.3                                                                                    | System Start-up Operation                                                                                                                                                                                                                       | 112                                                         |

|            | Figure                                                                                   | s                                                                                                                                                                                                                                               | 113                                                         |

|            |                                                                                          |                                                                                                                                                                                                                                                 |                                                             |

| CHAPTER 7: | MULTI-                                                                                   | -PROCESSOR SYSTEM - KERNEL SOFTWARE                                                                                                                                                                                                             |                                                             |

|            | STRUCT                                                                                   | URE                                                                                                                                                                                                                                             | 118                                                         |

| 7.1        | Introd                                                                                   | uction                                                                                                                                                                                                                                          | 118                                                         |

| 7.2        | The Re                                                                                   | al-Time Kernel Structure                                                                                                                                                                                                                        | 119                                                         |

| 7.3        |                                                                                          |                                                                                                                                                                                                                                                 | 117                                                         |

|            | Implem                                                                                   | entation of the Real-Time Kernel                                                                                                                                                                                                                | 123                                                         |

|            | -                                                                                        |                                                                                                                                                                                                                                                 |                                                             |

|            | 7.3.1                                                                                    | entation of the Real-Time Kernel                                                                                                                                                                                                                | 123                                                         |

|            | 7.3.1<br>7.3.2                                                                           | entation of the Real-Time Kernel<br>Software Module Structure - Overview .                                                                                                                                                                      | 123<br>123                                                  |

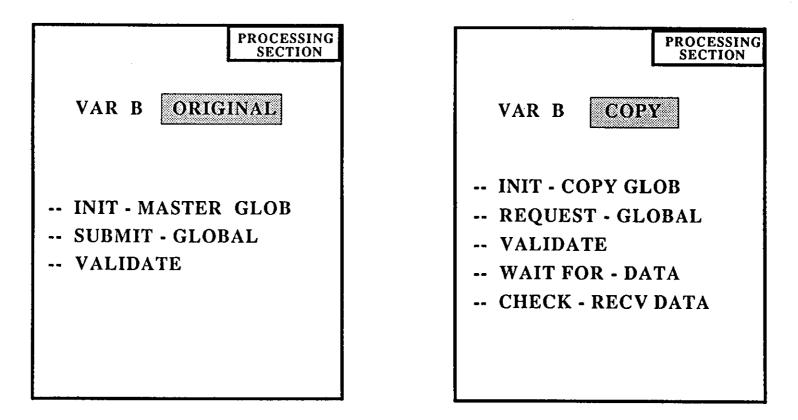

|            | 7.3.1<br>7.3.2<br>7.3.3                                                                  | entation of the Real-Time Kernel<br>Software Module Structure - Overview .<br>Distributed Variables Management                                                                                                                                  | 123<br>123<br>124                                           |

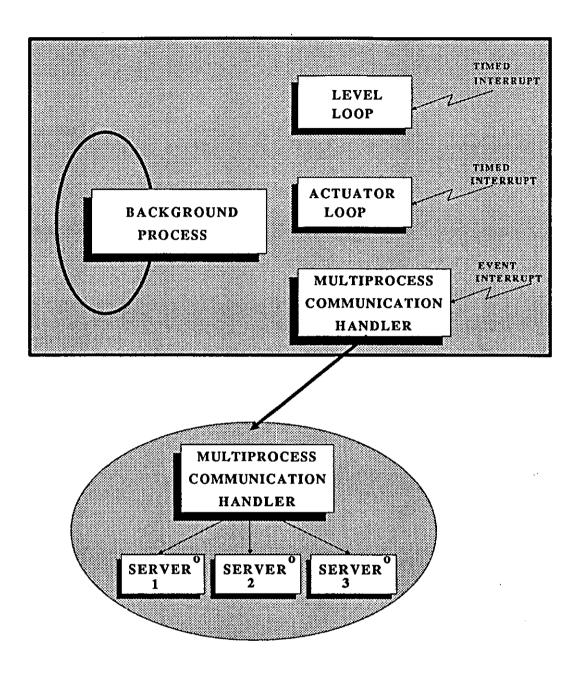

|            | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                         | entation of the Real-Time Kernel<br>Software Module Structure - Overview .<br>Distributed Variables Management<br>Communication Management                                                                                                      | 123<br>123<br>124<br>127                                    |

|            | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5                                                | entation of the Real-Time Kernel<br>Software Module Structure - Overview .<br>Distributed Variables Management<br>Communication Management<br>Message Management                                                                                | 123<br>123<br>124<br>127<br>129                             |

| 7.4        | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6                                       | entation of the Real-Time Kernel<br>Software Module Structure - Overview .<br>Distributed Variables Management<br>Communication Management<br>Message Management                                                                                | 123<br>123<br>124<br>127<br>129<br>130                      |

| 7.4        | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>The Bo                             | entation of the Real-Time Kernel<br>Software Module Structure - Overview .<br>Distributed Variables Management<br>Communication Management<br>Message Management<br>Time Management<br>Hardware-Related Routines                                | 123<br>123<br>124<br>127<br>129<br>130<br>131               |

| 7.4        | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>The Bo<br>7.4.1                    | entation of the Real-Time KernelSoftware Module Structure - OverviewDistributed Variables ManagementCommunication ManagementMessage ManagementTime ManagementHardware-Related Routinesotstrap Routine                                           | 123<br>123<br>124<br>127<br>129<br>130<br>131<br>133        |

|            | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>The Bo<br>7.4.1<br>7.4.2           | entation of the Real-Time KernelSoftware Module Structure - OverviewDistributed Variables ManagementCommunication ManagementMessage ManagementTime ManagementHardware-Related Routinesotstrap RoutineAssembler Routine                          | 123<br>123<br>124<br>127<br>129<br>130<br>131<br>133<br>133 |

|            | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>The Bo<br>7.4.1<br>7.4.2<br>System | entation of the Real-Time Kernel.Software Module Structure - OverviewDistributed Variables Management.Communication Management.Message Management.Time Management.Hardware-Related Routines.otstrap Routine.Assembler Routine.Modula-2 Routine. | 123<br>123<br>124<br>127<br>129<br>130<br>131<br>133<br>133 |

ł

| CHAPTER 8: | SYSTEM TEST AND VALIDATION                   | 140         |

|------------|----------------------------------------------|-------------|

| 8.1        | General                                      | 140         |

| 8.2        | Processing Section - Test Procedures         | 140         |

|            | 8.2.1 Basic Processor Test                   | 141         |

|            | 8.2.2 Chip Select Unit Test                  | 141         |

|            | 8.2.3 Programmable Timer Test                | 14 <b>1</b> |

|            | 8.2.4 Serial Line Test (DUART)               | 142         |

|            | 8.2.5 SRAM Test                              | 142         |

|            | 8.2.6 DMA Controller Test                    | 142         |

|            | 8.2.7 Numeric Processor Extension (NPE 8087) |             |

|            | Test                                         | 143         |

|            | 8.2.8 On-Board Interface (OBI) Test          | 144         |

|            | 8.2.9 Initial Bootstrap Test                 | 144         |

| 8.3        | Communication Section - Test Procedures      | 145         |

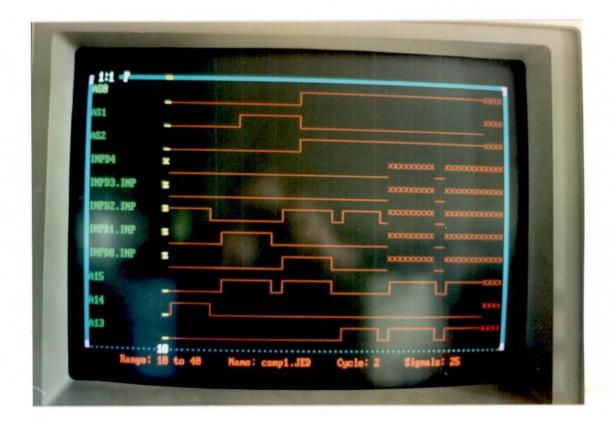

|            | 8.3.1 Simulation                             | 145         |

|            | 8.3.2 PCB Checking                           | 148         |

|            | 8.3.3 Software Testing                       | 149         |

| 8.4        | Overall System Test                          | 150         |

|            | Figures                                      | 153         |

|            |                                              |             |

| CHAPTER 9: | COMMENTS AND CONCLUSIONS                     | 158         |

| 9.1        | Architecture                                 | 158         |

|            | 9.1.1 Loosely-Coupled Systems                | 158         |

|            | 9.1.2 Functional Partitioning                | 159         |

|            | 9.1.3 Communication Features                 | 160         |

| 9.2        | Hardware Structure                           | 161         |

| 9.3        | Software Structure                           | 162         |

| 9.4        | Applicability of Modula-2                    | 163         |

| 9.5        | Overall Comments                             | 164         |

| 9.6        | Future Work                                  | 166         |

| 9.7        | A Final Summary                              | 168         |

| REFERENCES |                                              | 169         |

| APPENDIX A: | SYST  | EM HARDWARE DESIGN                       | 182 |

|-------------|-------|------------------------------------------|-----|

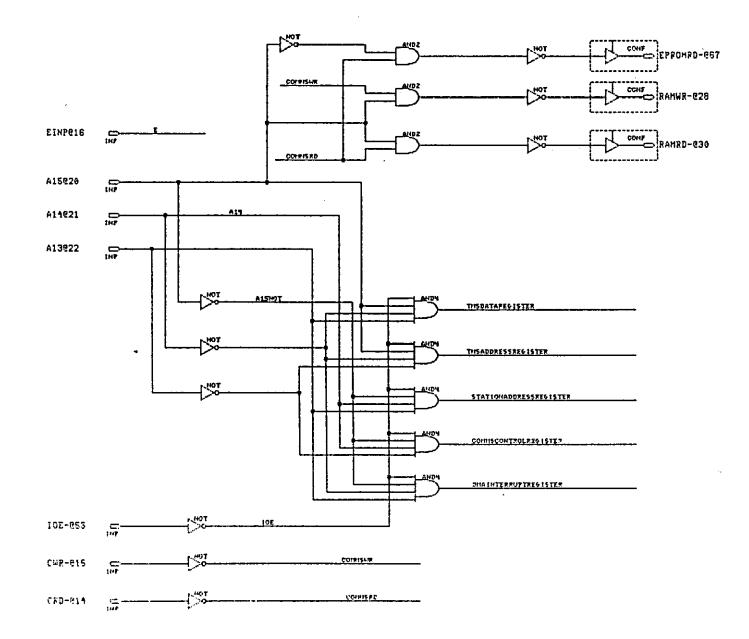

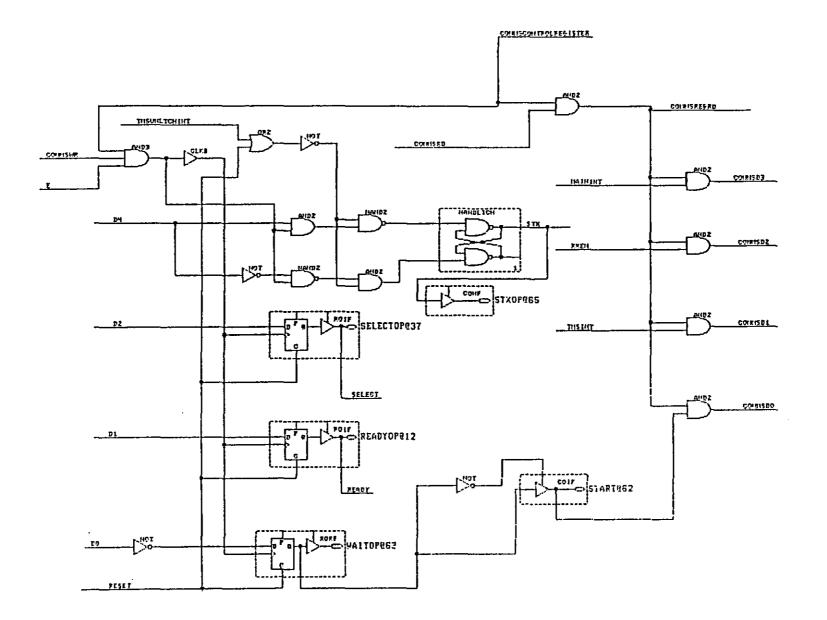

|             | A.1   | Communication Section Design             | 182 |

|             | A.2   | CSM Module Description                   | 191 |

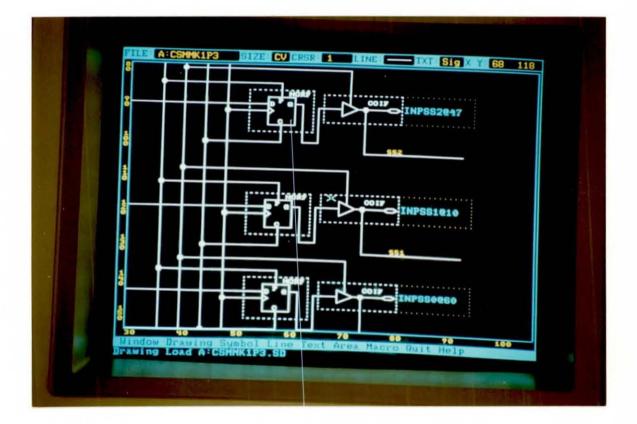

|             | A.3   | Altera Design Report                     | 217 |

|             | A.4   | Processing Section Design                | 240 |

| APPENDIX B: | COMM  | UNICATION SECTION'S MODES OF OPERATION . | 259 |

|             | B.1   | General                                  | 259 |

|             | в.2   | Initialisation                           | 259 |

|             | в.3   | No Operation - Idle                      | 261 |

|             | в.4   | Reception                                | 262 |

|             | в.5   | Transmission                             | 263 |

|             | в.б   | Data Exchange with the OBI Interface     | 265 |

| APPENDIX C: | MU    | ITI-PROCESSOR SYSTEM - COMMUNICATION     |     |

|             | SOFT  | WARE STRUCTURE                           | 270 |

|             | C.1   | Ring Configuration and Maintenance       | 270 |

|             | C.2   | Control Frames                           | 275 |

|             | C.3   | Timers                                   | 276 |

|             | C.4   | Software Development and Structure       | 278 |

| APPENDIX D: | CPM 1 | ENVIRONMENT EMULATOR - CPM100 MODULE     | 314 |

|             | D.1   | Overview                                 | 314 |

|             |       | CPM Compatibility                        | 316 |

|             |       | Limitations                              | 317 |

| APPENDIX E: | MULT  | I-PROCESSOR SYSTEM - KERNEL SOFTWARE     |     |

|             | STRU  | CTURE                                    | 319 |

|             | E.1   | Introduction                             | 319 |

|             | E.2   | Real-Time Kernel Structure               | 319 |

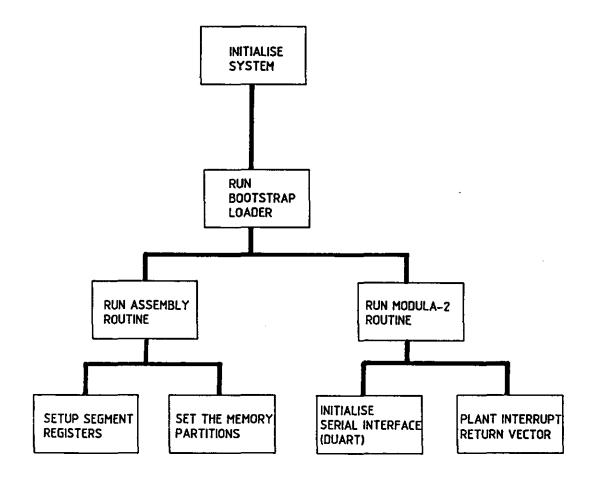

|             | E.3   | Power-Up                                 | 320 |

|             |       | Initialise System                        | 320 |

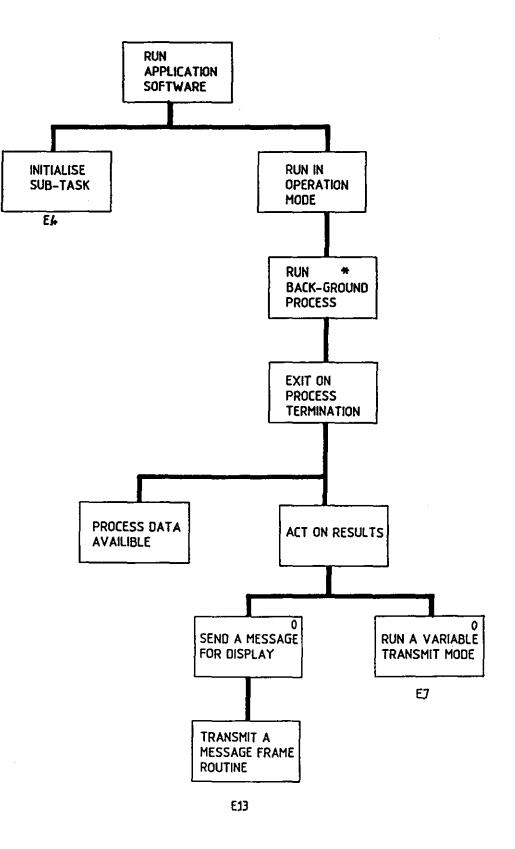

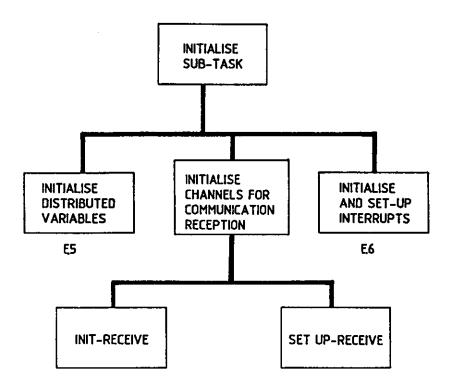

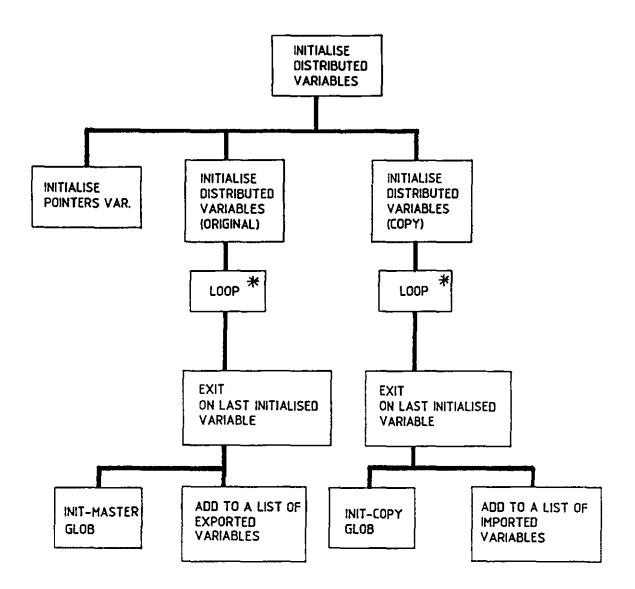

|             |       | Run Application Software                 | 322 |

|             |       | Transmission Mode                        | 324 |

| E.7 | Reception Mode    | • | • | • | • | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | 3 | 24 |

|-----|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|----|

| E.8 | Repeated Routines | • | • | • | • | ٠ | ٠ | • | • | ٠ | ٠ | • | 3 | 26 |

,

.

#### LIST OF FIGURES

#### Page No

#### CHAPTER 1

| Fig. | 1.1: | System Configuration                        | 5 |

|------|------|---------------------------------------------|---|

| Fig. | 1.2: | Multi-Processor Node - Functional Structure | 6 |

#### CHAPTER 2

| Fig. 2.1: | Software Development Incorporating Program   |    |

|-----------|----------------------------------------------|----|

|           | Post-Partitioning                            | 15 |

| Fig. 2.2: | Steps in Software Development in Distributed |    |

|           | Application (Pre-Partitioning)               | 16 |

| Fig. 2.3: | Functional Partitioning (Pipeline)           | 17 |

| Fig. 2.4: | Functional Partitioning                      | 18 |

| Fig. 2.5: | E-Mode and T-Mode Messages                   | 19 |

|           |                                              |    |

#### CHAPTER 3

•

| Fig. | 3.1:  | Process State Transitions                   | 44         |

|------|-------|---------------------------------------------|------------|

| Fig. | 3.2:  | The 'Fork' and 'Join' Statements            | 45         |

| Fig. | 3.3:  | The 'Cobegin' Statement                     | 46         |

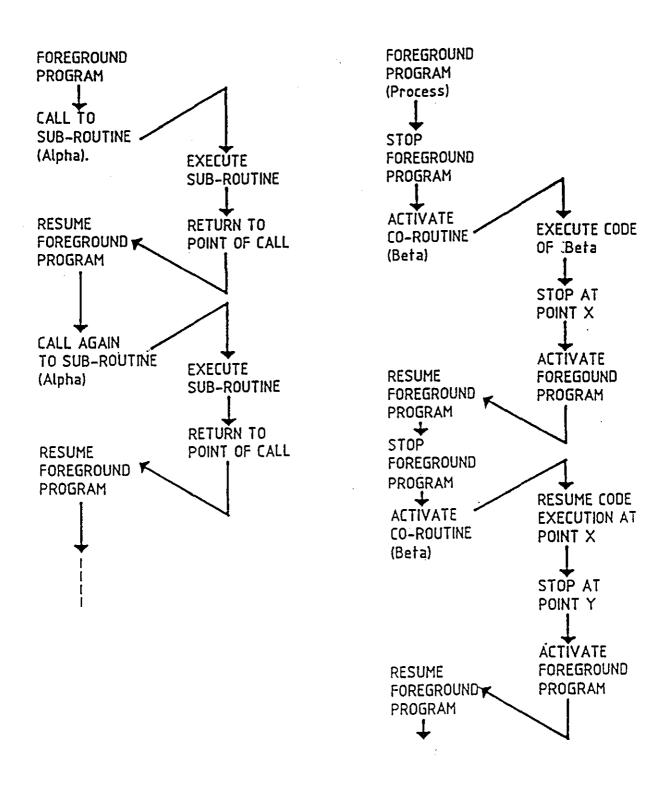

| Fig. | 3.4:  | Subroutines v's Coroutines - Conceptual     |            |

|      |       | Differences                                 | 47         |

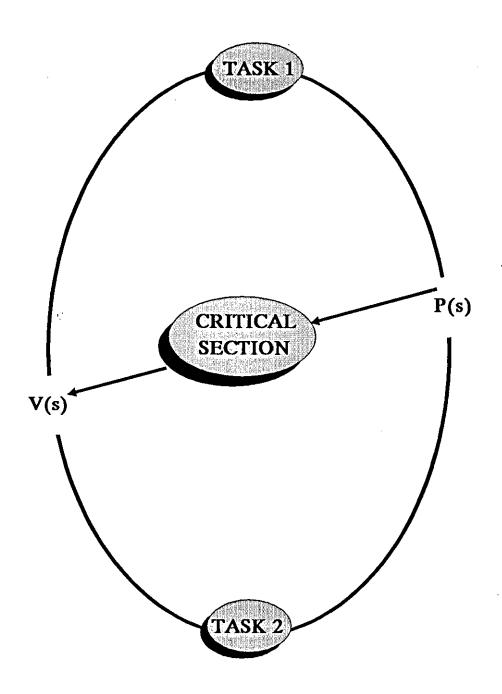

| Fig. | 3.5:  | Task Communication with 'Semaphores'        | 48         |

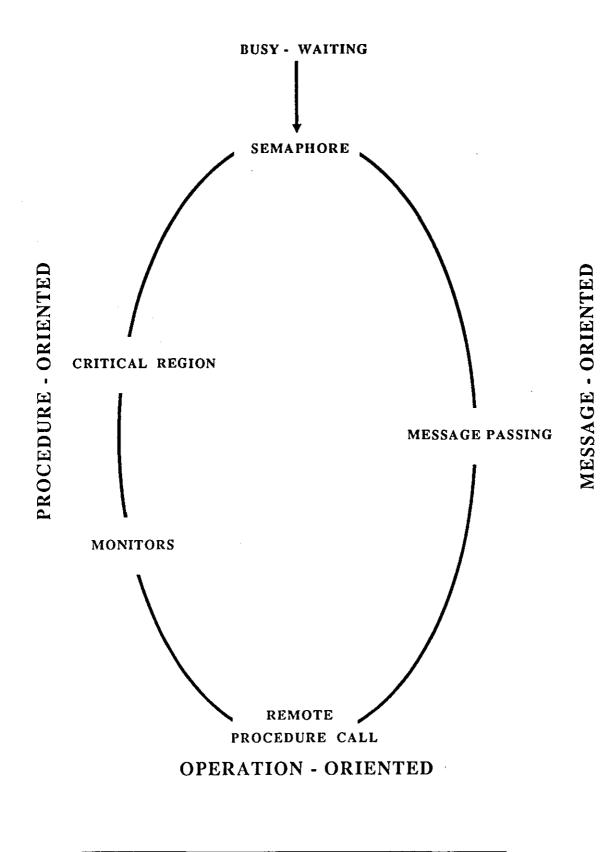

| Fig. | 3.6:  | Software Methodologies                      | 49         |

| Fig. | 3.7:  | Monitor Structure                           | 5 <b>0</b> |

| Fig. | 3.8:  | The Monitor Concept                         | 51         |

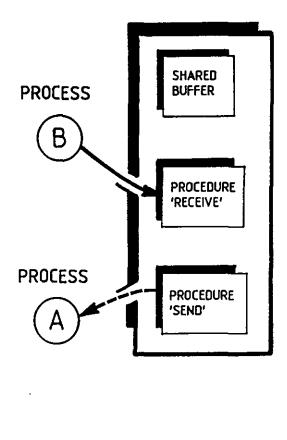

| Fig. | 3.9:  | Remote Procedure Calls (RPC)-Implementation | 52         |

| Fig. | 3.10: | Rendezvous Transactions                     | 53         |

| Fig. | 3.11: | E-Mode and T-Mode Messages                  | 54         |

#### CHAPTER 4

| Fig. | 4.1: | System Configuration                        | 65 |

|------|------|---------------------------------------------|----|

| Fig. | 4.2: | Multi-Processor Node - Functional Structure | 66 |

| Fig. | 4.3: | Token Passing on a Logical Ring             | 67 |

#### CHAPTER 5

| Fig. | 5.1:  | Functional Block Diagram of a Station          | 84 |

|------|-------|------------------------------------------------|----|

| Fig. | 5.2:  | System Interfacing                             | 85 |

| Fig. | 5.3:  | The Communication Section - Detailed Structure | 86 |

| Fig. | 5.4:  | Communication Support Module (CSM)             | 87 |

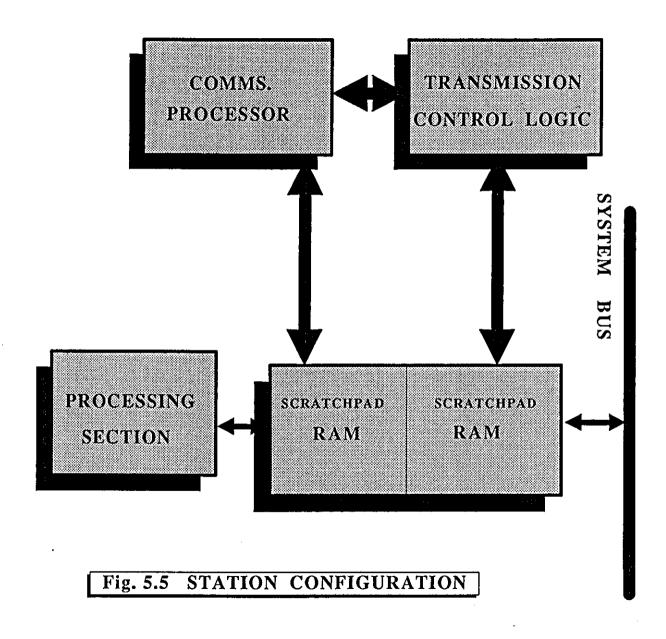

| Fig. | 5.5:  | Station Configuration                          | 88 |

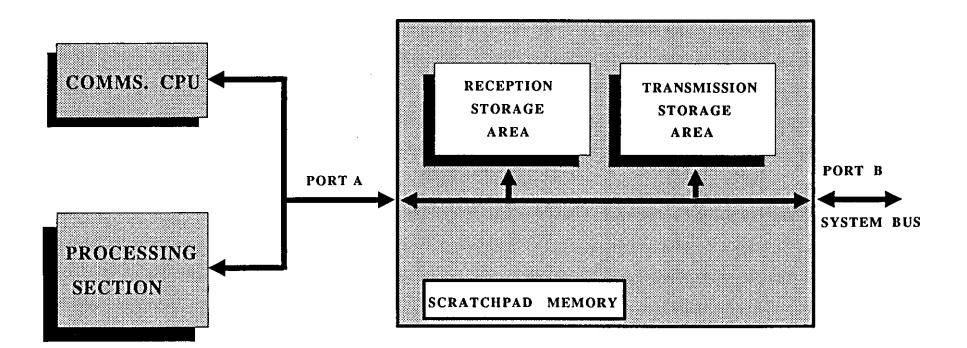

| Fig. | 5.6:  | Block Diagram of the Scratchpad Memory         | 89 |

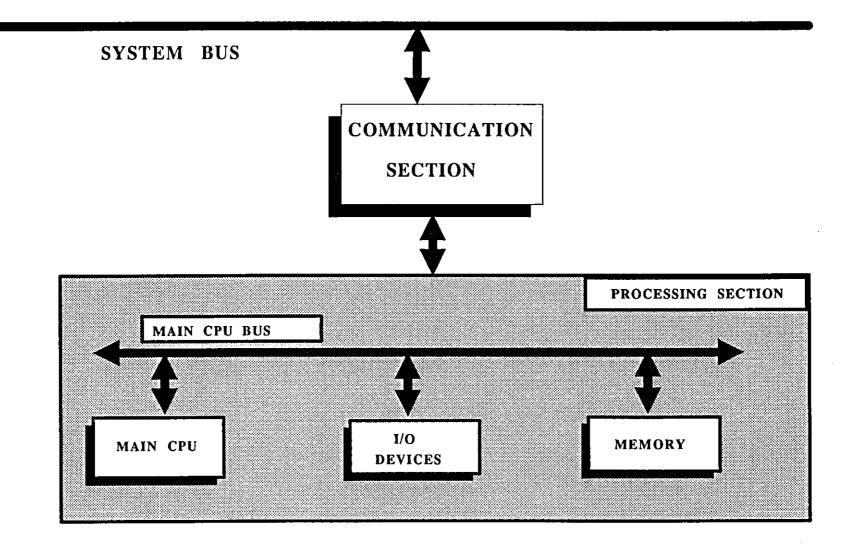

| Fig. | 5.7:  | Processing Section - Overall Structure         | 90 |

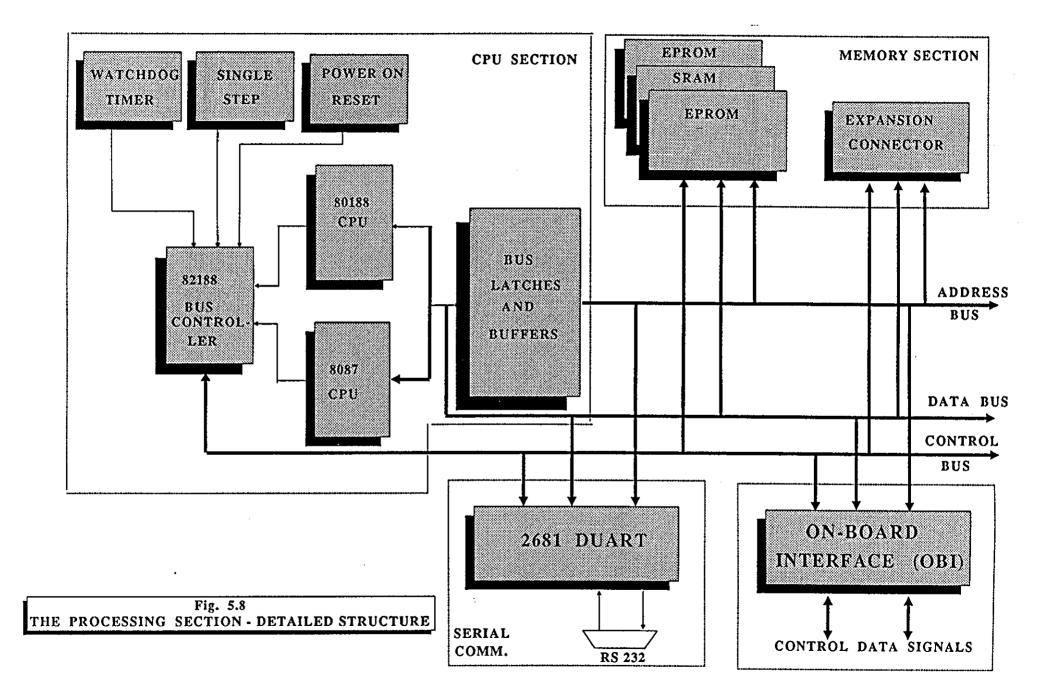

| Fig. | 5.8:  | The Processing Section - Detailed Structure    | 91 |

| Fig. | 5.9:  | Initialisation - Stage 1                       | 92 |

| Fig. | 5.10: | Initialisation - Stage 2                       | 93 |

| Fig. | 5.11: | Transmission of a Message                      | 94 |

| Fig. | 5.12: | Reception of a Message                         | 95 |

#### CHAPTER 6

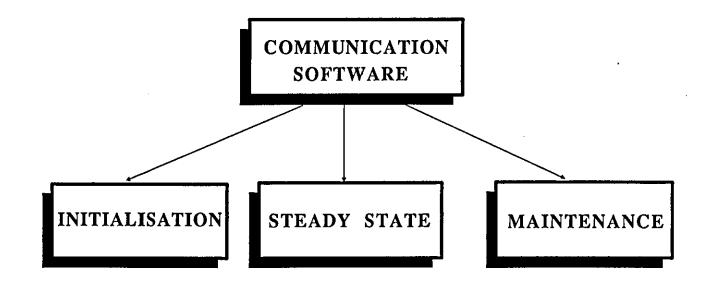

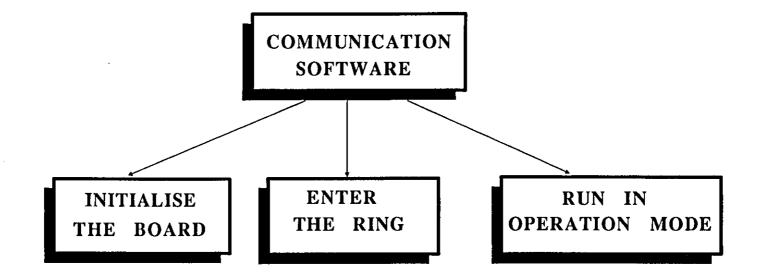

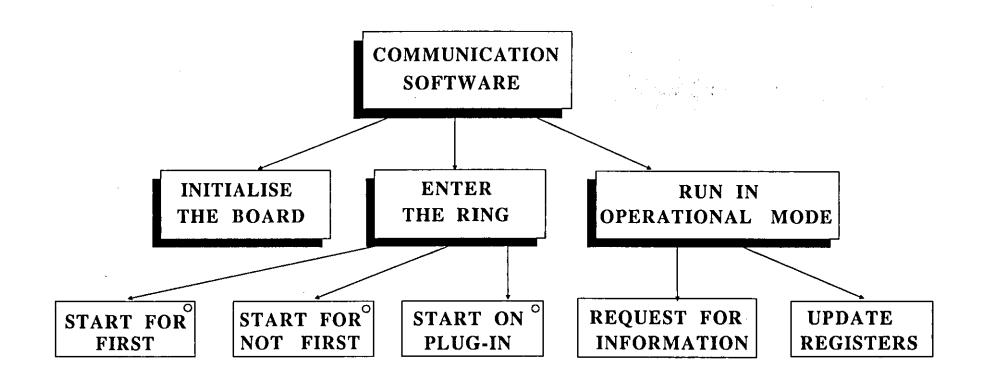

| Fig. | 6.1: | Communication Software - Network's View | 113 |

|------|------|-----------------------------------------|-----|

| Fig. | 6.2: | Communication Software - Station's View | 114 |

| Fig. | 6.3: | Communication Software - Station's View | 115 |

| Fig. | 6.4: | Implemented System Modules              | 116 |

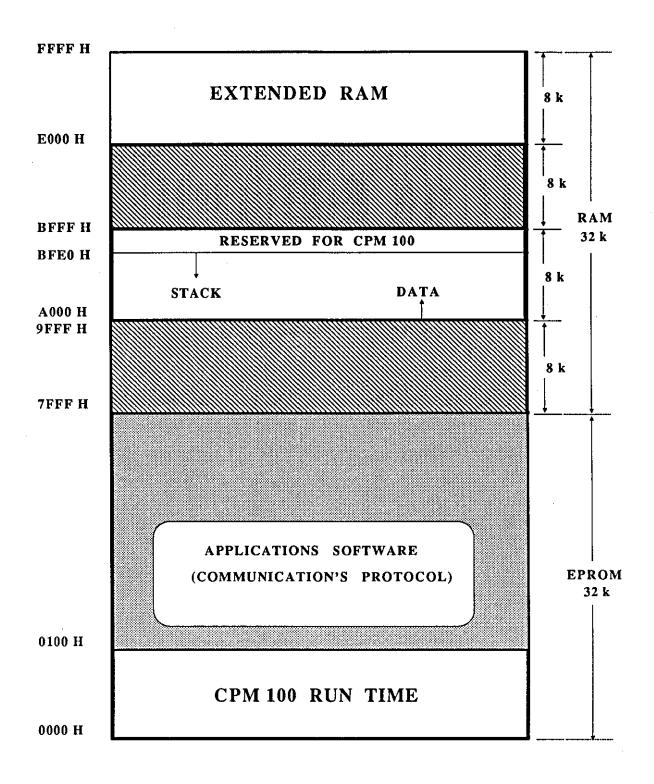

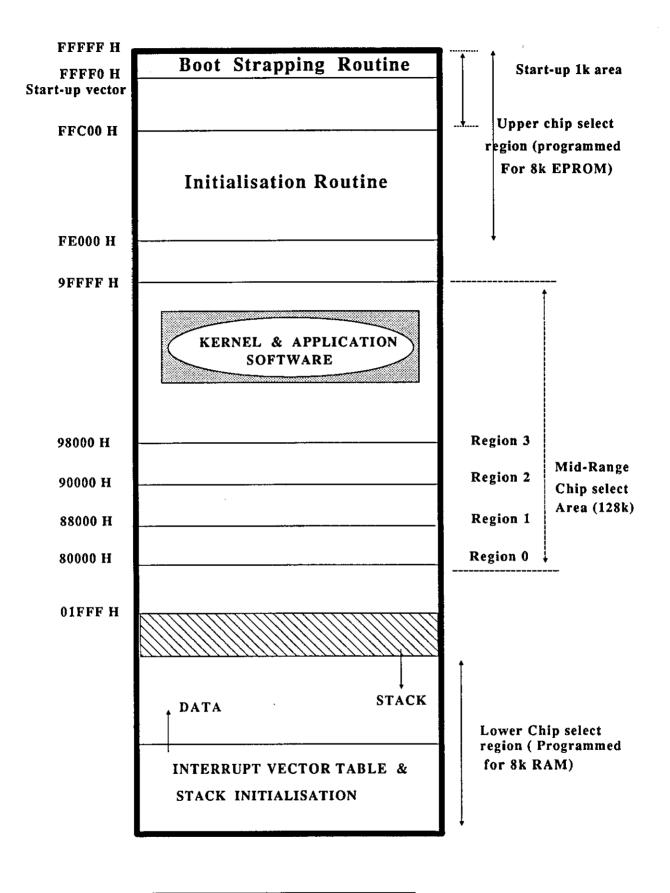

| Fig. | 6.5: | System Memory Map                       | 117 |

#### CHAPTER 7

| Fig. | 7.1: | Functional Partitioning          | 136 |

|------|------|----------------------------------|-----|

| Fig. | 7.2: | Distributed Variables Management | 137 |

| Fig. | 7.3: | Functional Scheduling            | 138 |

| Fig. | 7.4: | System Memory Map                | 139 |

#### CHAPTER 8

| Fig. 8.1: | Block Diagram of the Processing Section        | 153 |

|-----------|------------------------------------------------|-----|

| Fig. 8.2: | Minimum CPU Configuration                      | 154 |

| Fig. 8.3: | 80188 CPU Block Diagram                        | 155 |

| Fig. 8.4: | Initial System Memory Map                      | 156 |

| Fig. 8.5: | The Communication Section - Detailed Structure | 157 |

#### APPENDIX A

.

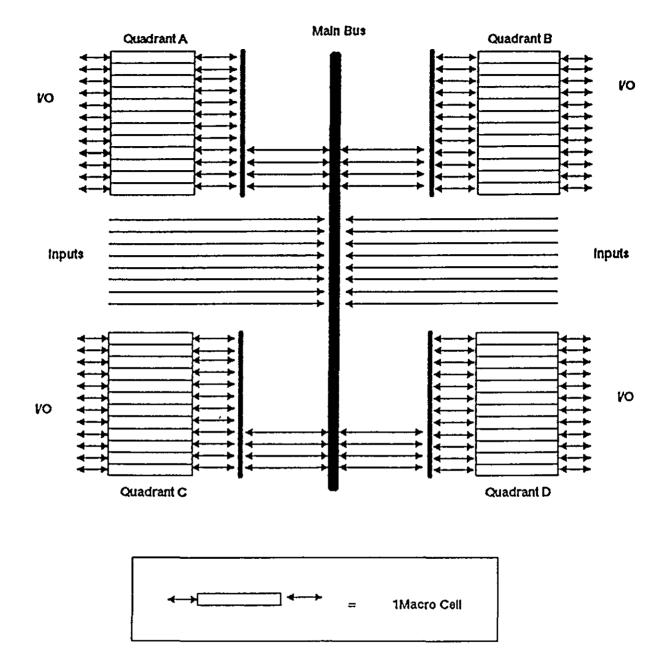

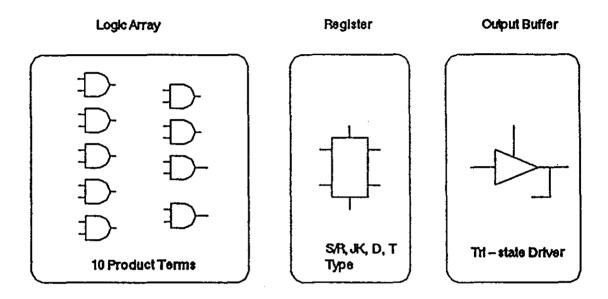

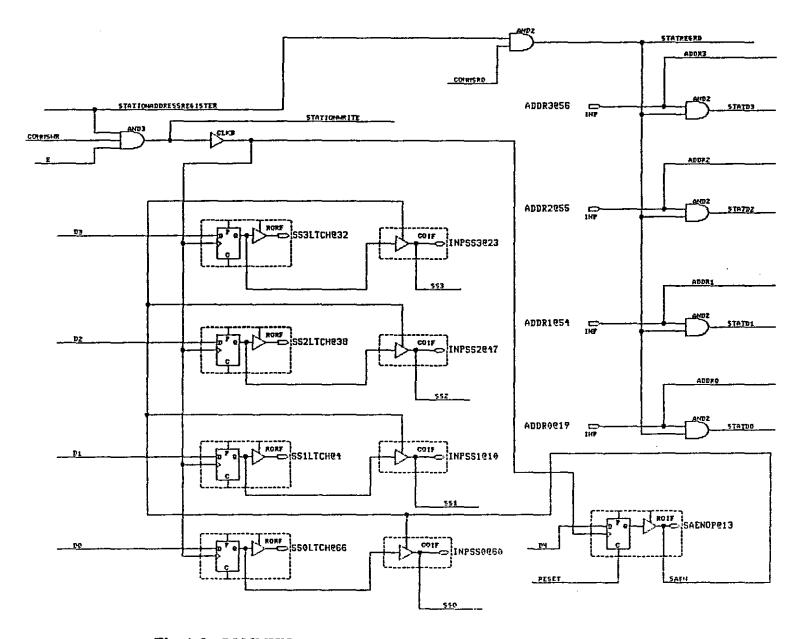

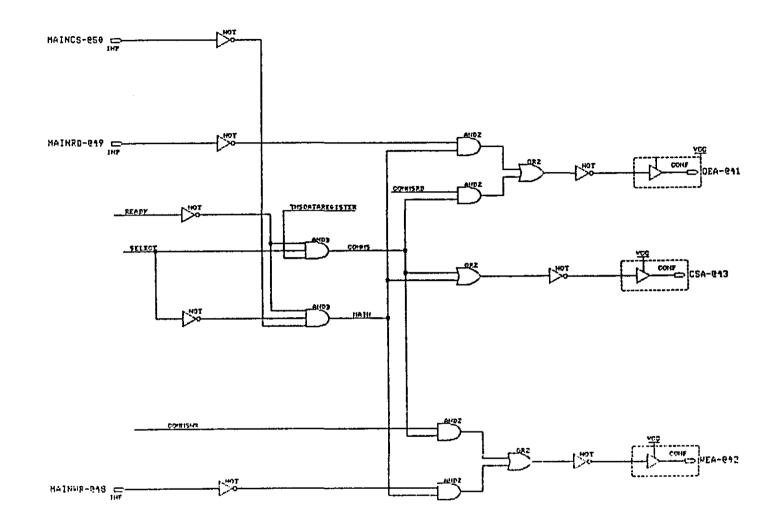

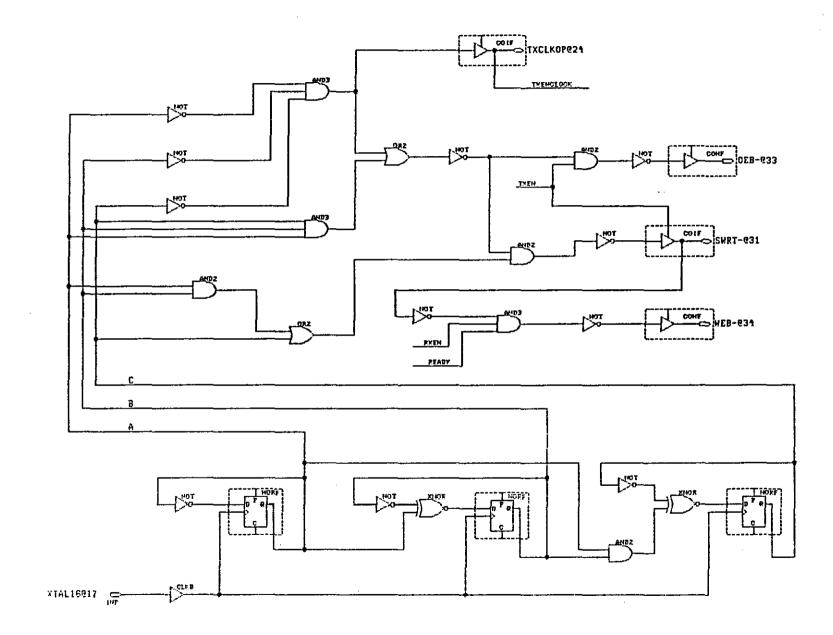

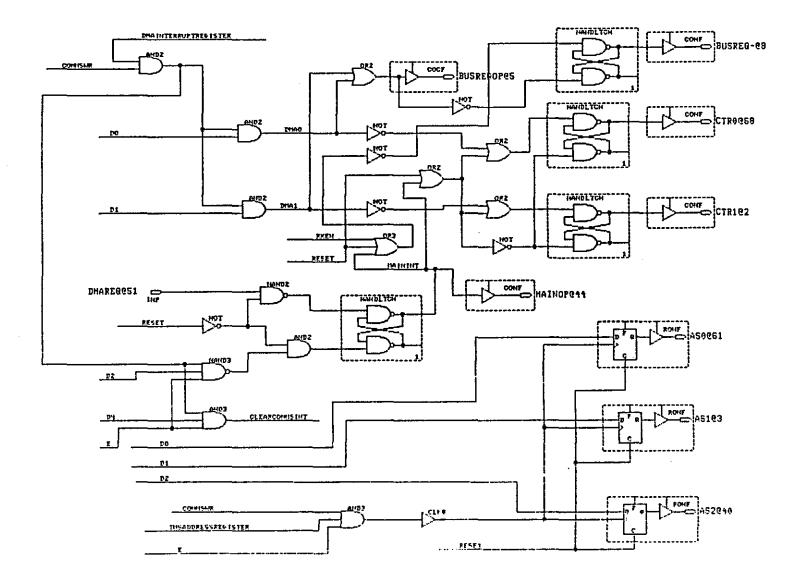

| Fig. A.2:Communication Section Hardware Design - Sheet 2189Fig. A.3:Communication Section Hardware Design - Sheet 3190Fig. A.4:EP 1800 Macro Cell Structure206Fig. A.5:Macro Cell Components207Fig. A.6:Communication Support Module (CSM) Design - Sheet 1208Fig. A.7:Communication Support Module (CSM) Design - Sheet 2209 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. A.4:EP 1800 Macro Cell Structure206Fig. A.5:Macro Cell Components207Fig. A.6:Communication Support Module (CSM) Design - Sheet 1208                                                                                                                                                                                      |

| Fig. A.5:Macro Cell Components207Fig. A.6:Communication Support Module (CSM) Design - Sheet 1208                                                                                                                                                                                                                              |

| Fig. A.6: Communication Support Module (CSM) Design - Sheet 1 208                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                               |

| Fig. A.7: Communication Support Module (CSM) Design - Sheet 2 209                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                               |

| Fig. A.8: Communication Support Module (CSM) Design - Sheet 3 210                                                                                                                                                                                                                                                             |

| Fig. A.9: Communication Support Module (CSM) Design - Sheet 4 211                                                                                                                                                                                                                                                             |

| Fig. A.10: Communication Support Module (CSM) Design - Sheet 5 212                                                                                                                                                                                                                                                            |

| Fig. A.11: Communication Support Module (CSM) Design - Sheet 6 213                                                                                                                                                                                                                                                            |

| Fig. A.12: Communication Support Module (CSM) Design - Sheet 7 214                                                                                                                                                                                                                                                            |

| Fig. A.13: Communication Support Module (CSM) Design - Sheet 8 215                                                                                                                                                                                                                                                            |

| Fig. A.14: Communication Support Module (CSM) Design - Sheet 9 216                                                                                                                                                                                                                                                            |

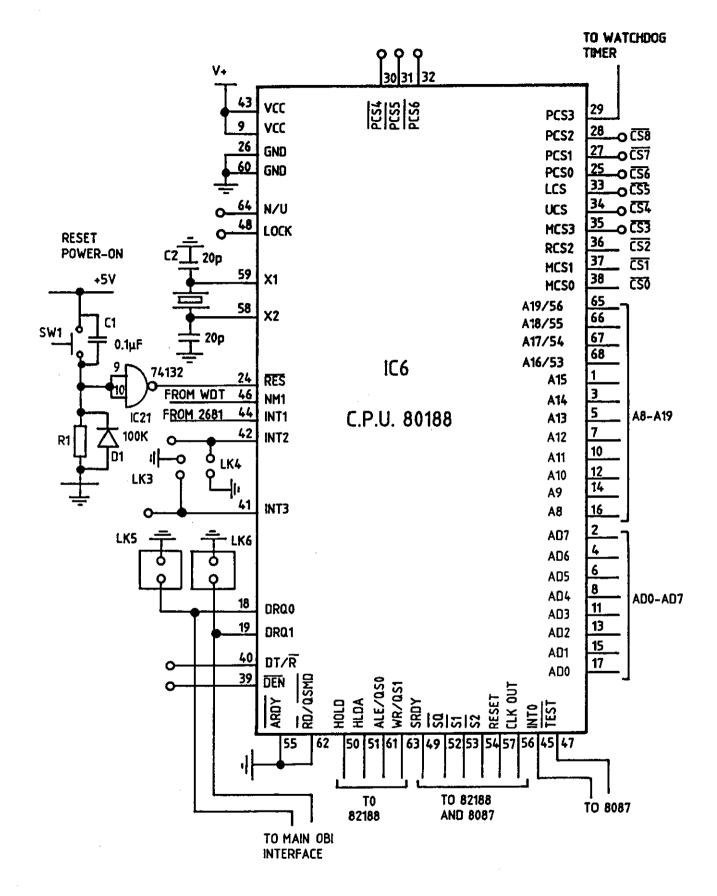

| Fig. A.15:80188 CPU Block Diagram250                                                                                                                                                                                                                                                                                          |

| Fig. A.16:80188 CPU Configuration251                                                                                                                                                                                                                                                                                          |

•

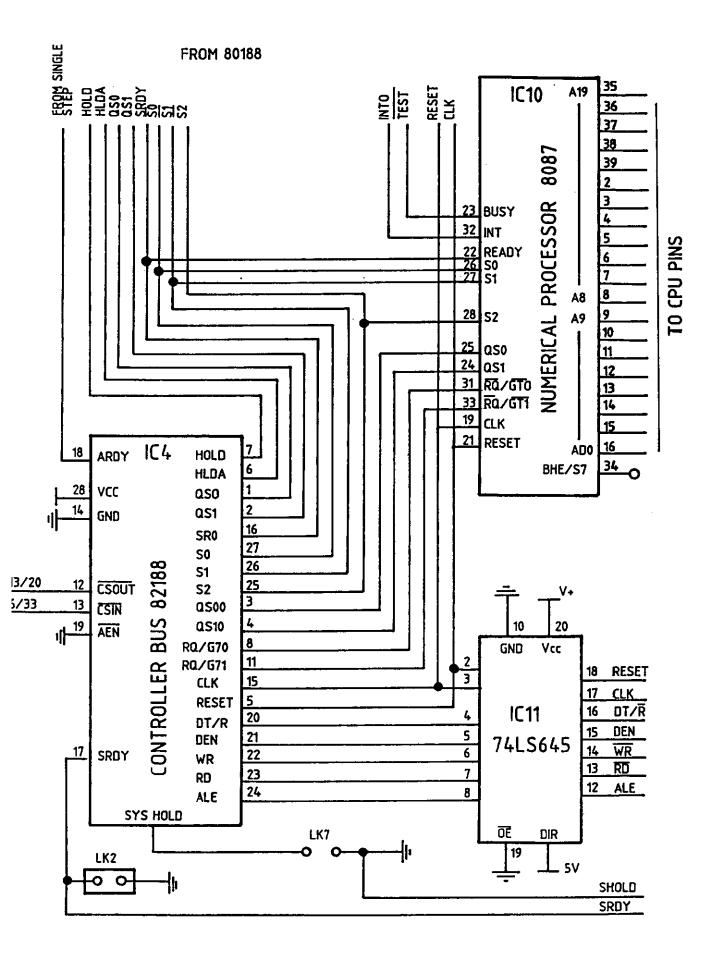

| Fig. A.17: | 82188 Controller and 8087 Numerical Processor | 252 |

|------------|-----------------------------------------------|-----|

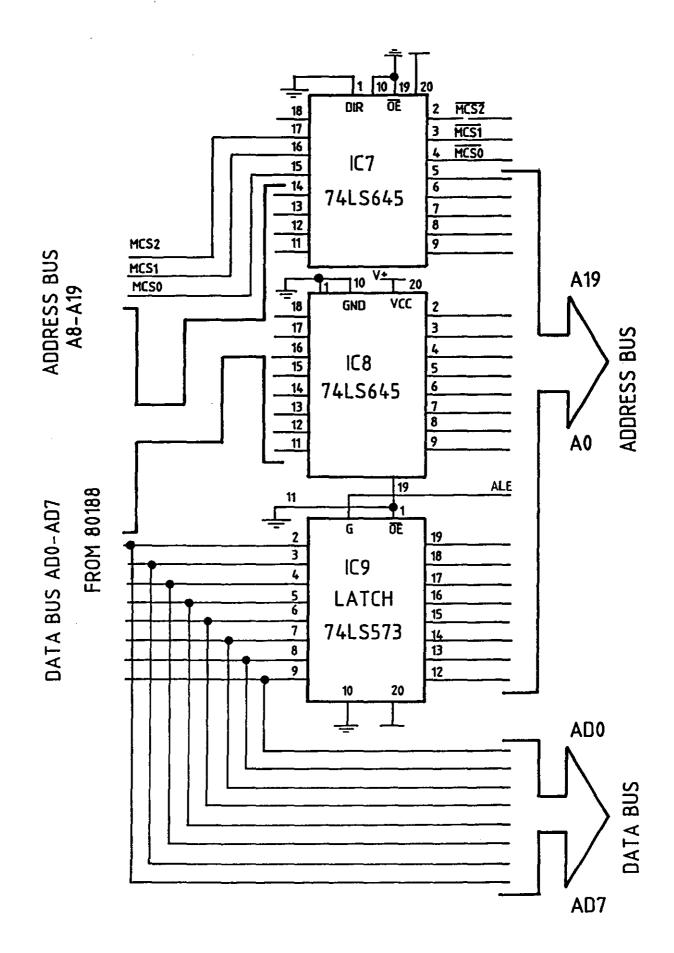

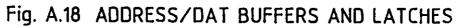

| Fig. A.18: | Address/Data Buffers and Latches              | 253 |

| Fig. A.19: | Memory System                                 | 254 |

| Fig. A.20: | Serial Communication System                   | 255 |

| Fig. A.21: | On-Board Interfacing Block (OBI)              | 256 |

| Fig. A.22: | Single Step Circuit                           | 257 |

| Fig. A.23: | Watchdog Timer                                | 258 |

#### APPENDIX B

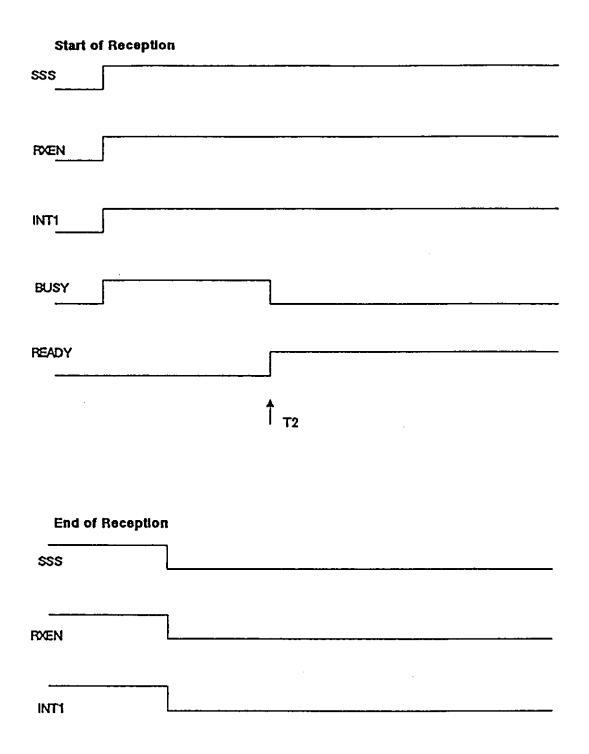

| Fig. B.1: | Data Reception Mode - Signal Timing    | 267 |

|-----------|----------------------------------------|-----|

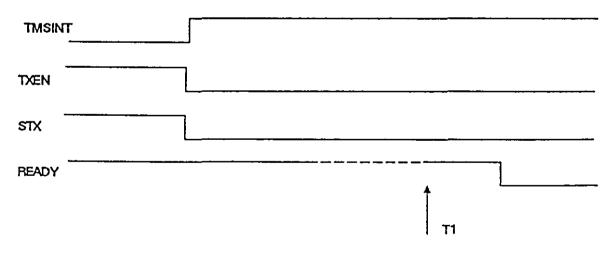

| Fig. B.2: | Data Transmission Mode - Signal Timing | 268 |

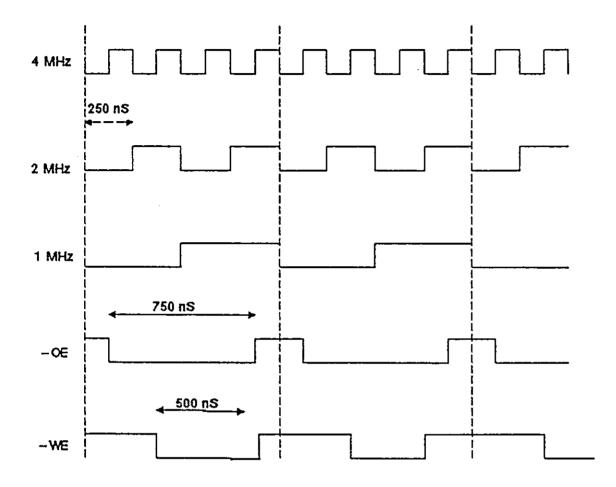

| Fig. B.3: | Transmission Clock Signals             | 269 |

#### APPENDIX C

| Fig. | C.1: | Token Passing on a Logical Ring | 293 |

|------|------|---------------------------------|-----|

| Fig. | C.2: | Ring Configuration Process      | 294 |

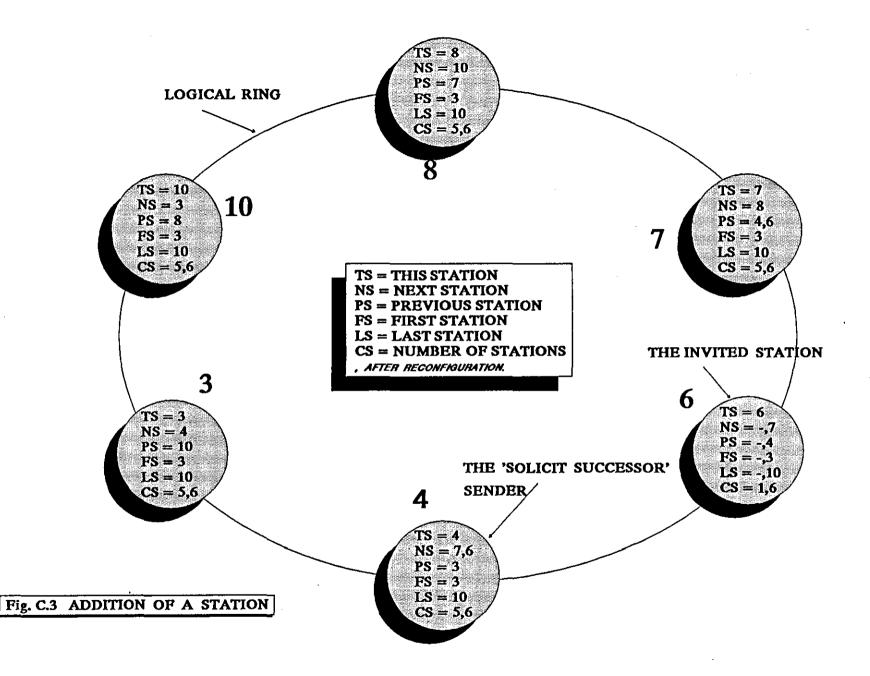

| Fig. | c.3: | Addition of a Station           | 295 |

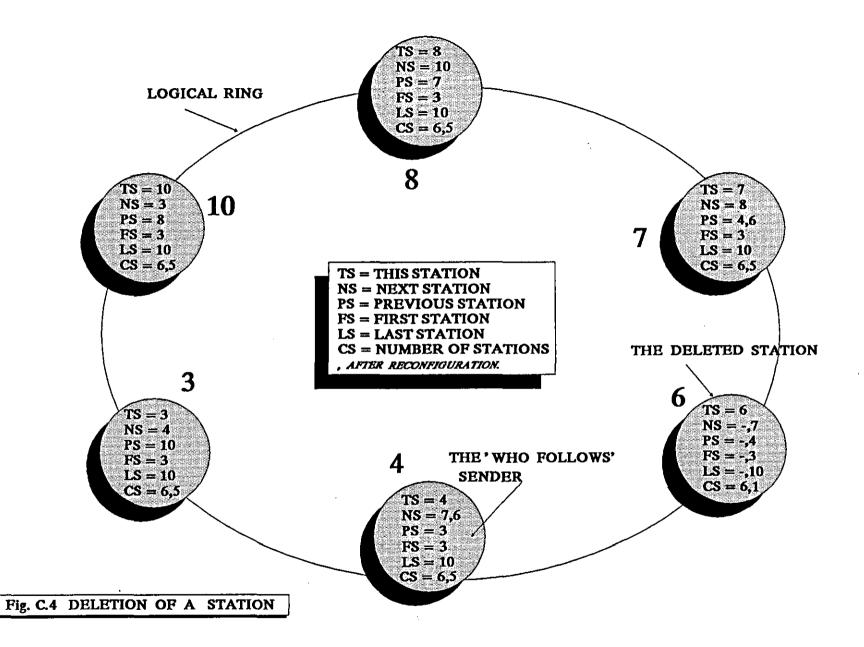

| Fig. | C.4: | Deletion of a Station           | 296 |

#### LIST OF CHARTS

Page No

#### CHART NUMBER

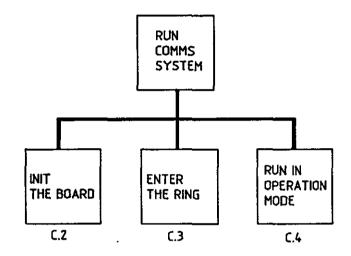

| C.1:  | Run Comms System                 | 297 |

|-------|----------------------------------|-----|

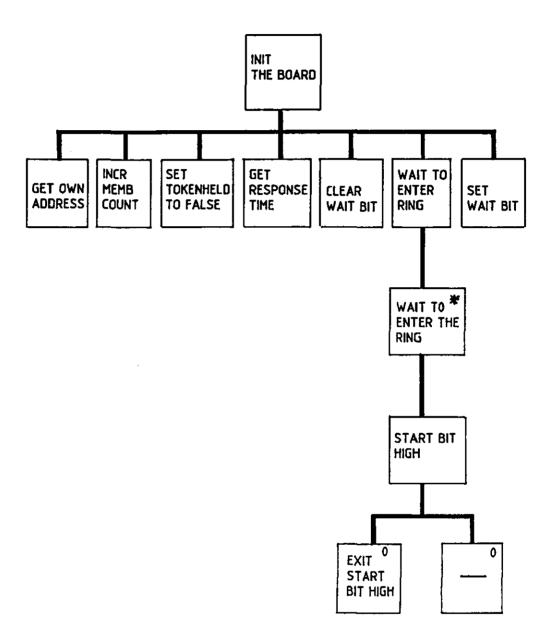

| C.2:  | Init the Board                   | 298 |

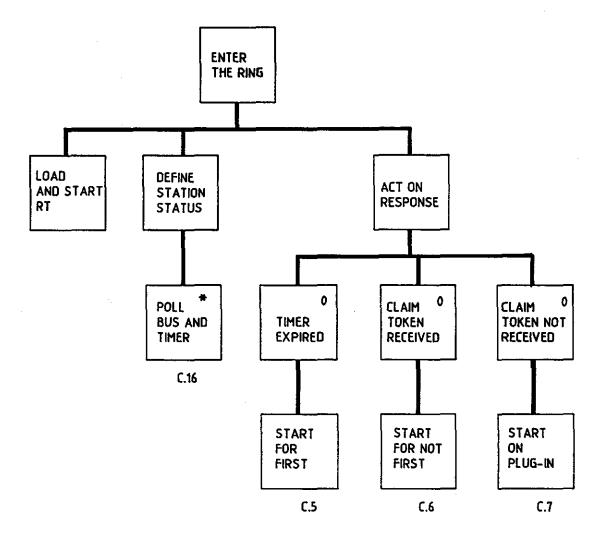

| C.3:  | Enter the Ring                   | 299 |

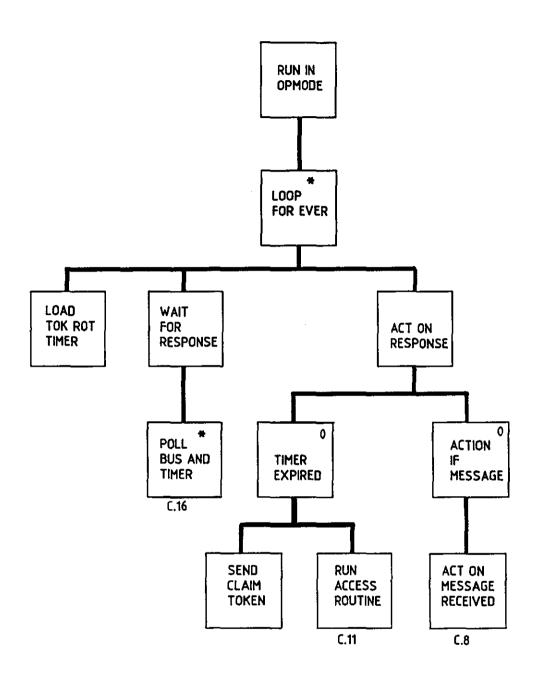

| C.4:  | Run in Op-Mode                   | 300 |

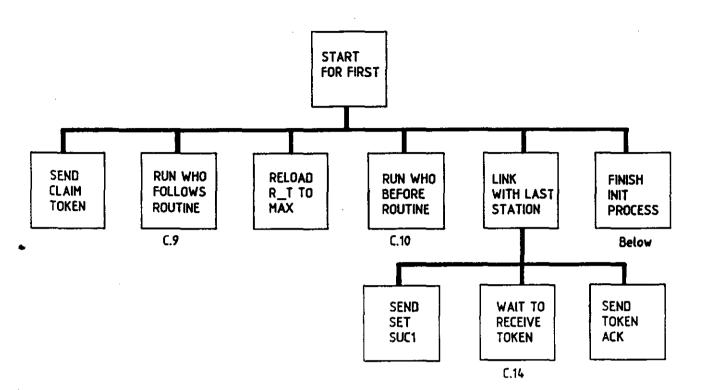

| C.5:  | Start for First                  | 301 |

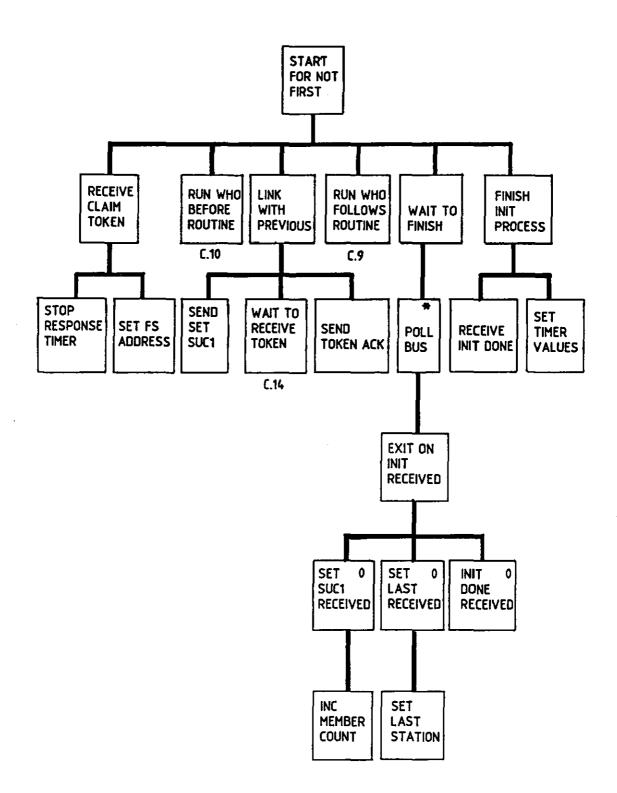

| C.6:  | Start for not First              | 302 |

| C.7:  | Start on Plug-In                 | 303 |

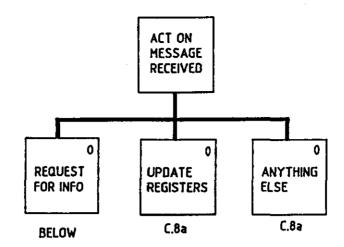

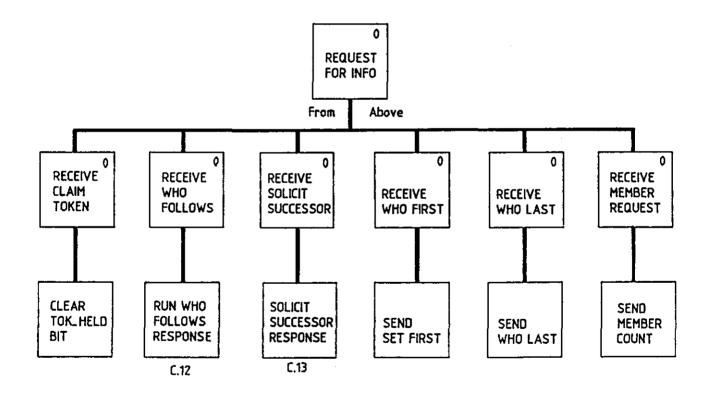

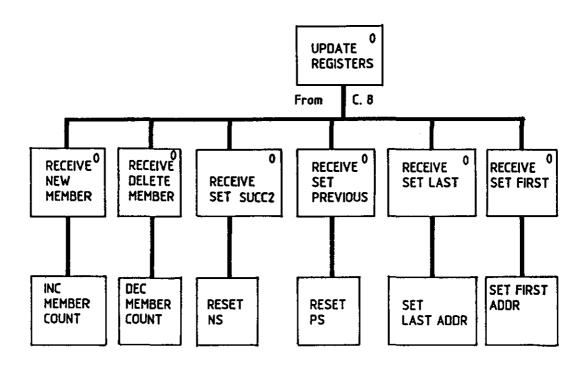

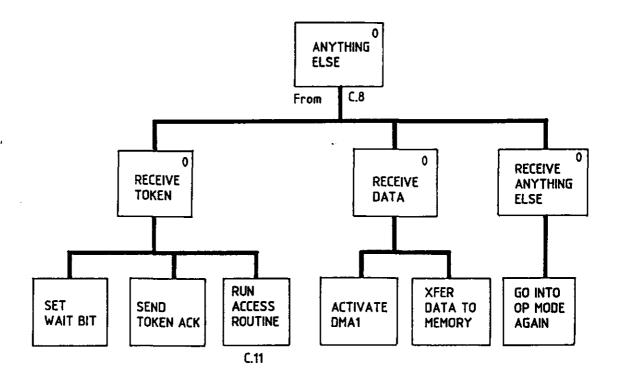

| C.8:  | Act on Message Received          | 304 |

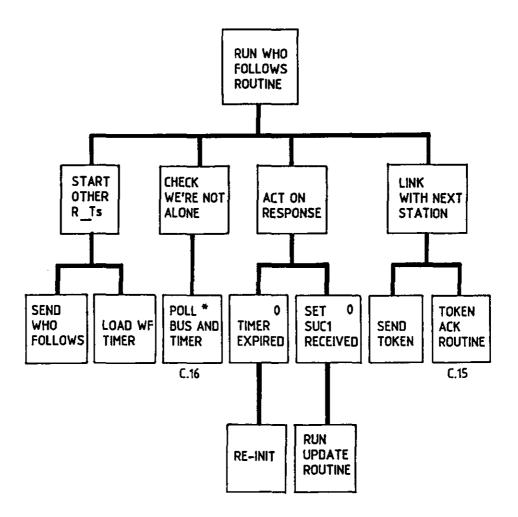

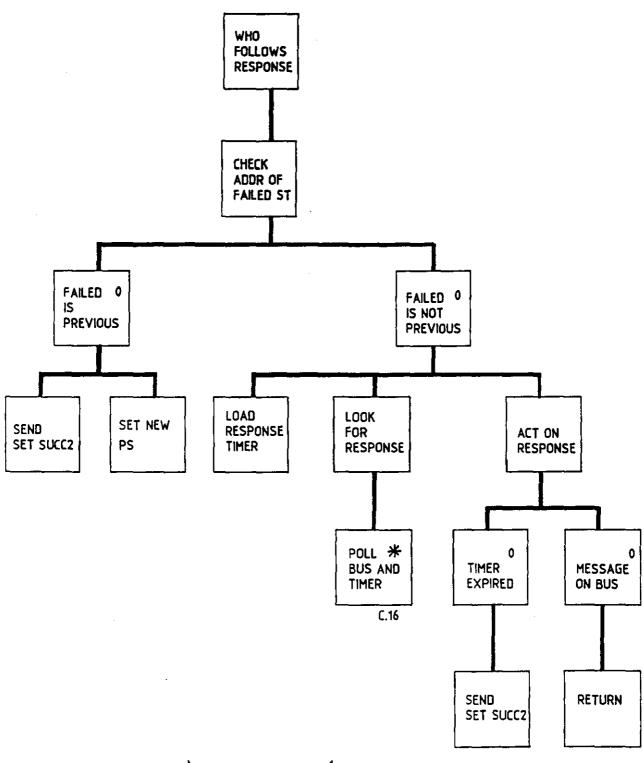

| C.9:  | Run 'Who Follows' Routine        | 306 |

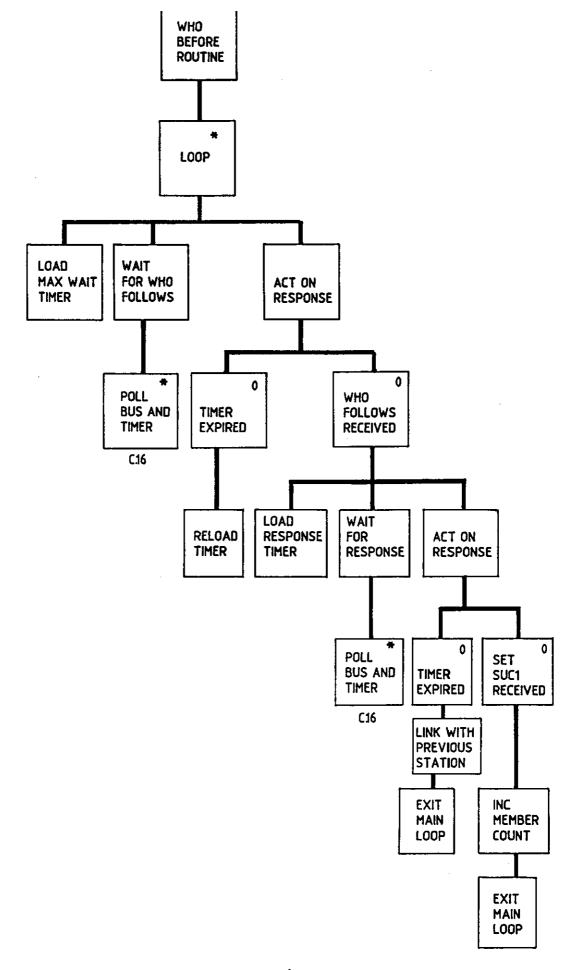

| C.10: | Run 'Who Before' Routine         | 307 |

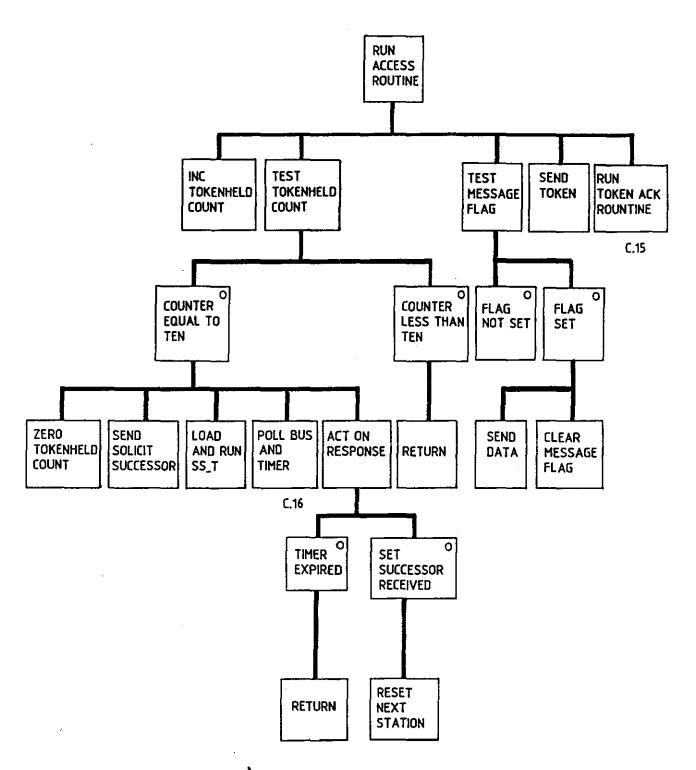

| C.11: | Run 'Access' Routine             | 308 |

| C.12: | 'Who Follows' Routine            | 309 |

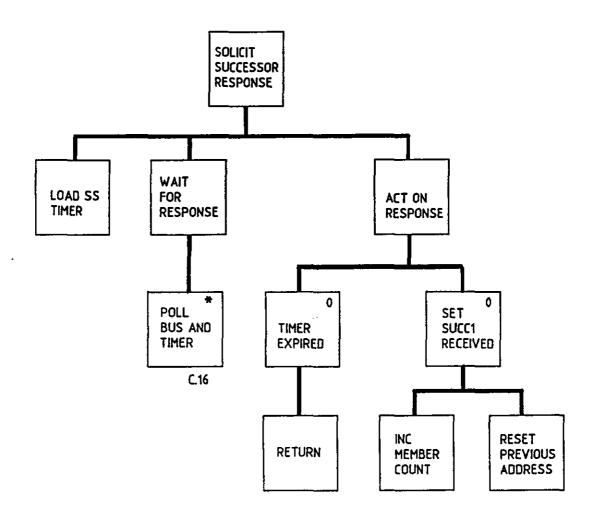

| C.13: | 'Solicit Successor' Response     | 310 |

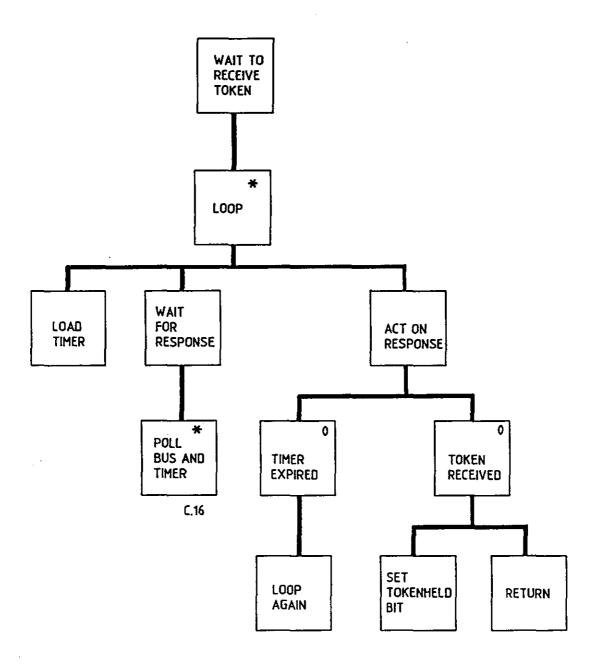

| C.14: | Wait to Receive Token            | 311 |

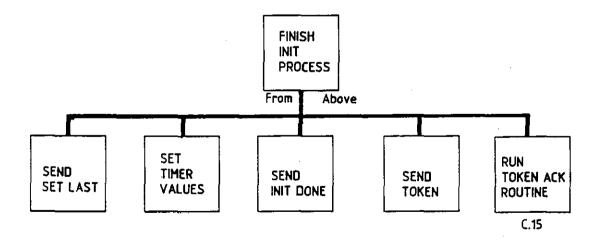

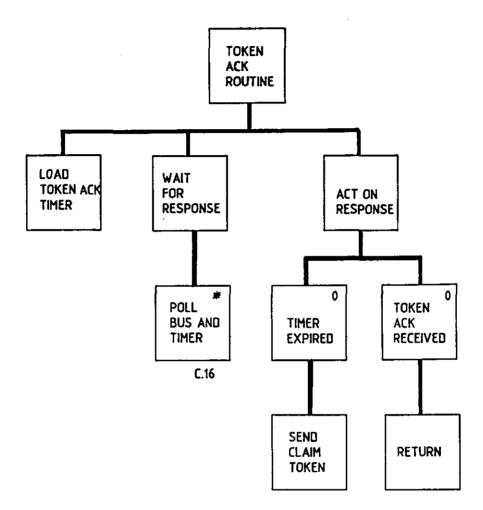

| C.15: | 'Token Ack' Routine              | 312 |

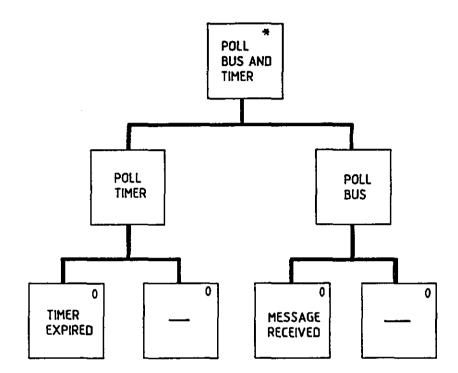

| C.16: | Poll Bus and Timer               | 313 |

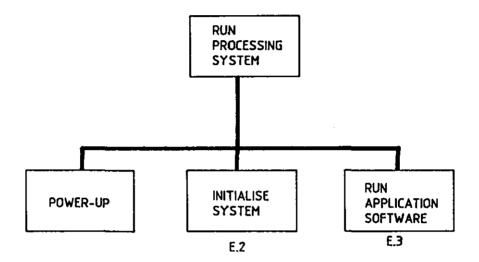

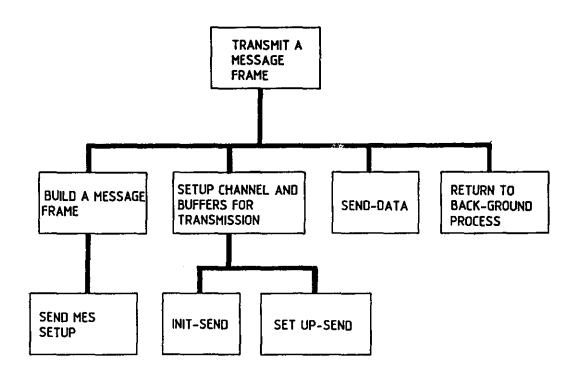

| E.1:  | Run Processing System            | 329 |

| E.2:  | Initialise System                | 330 |

| E.3:  | Run Application Software         | 331 |

| E.4:  | Initialise Sub-Task              | 332 |

| E.5:  | Initialise Distributed Variables | 333 |

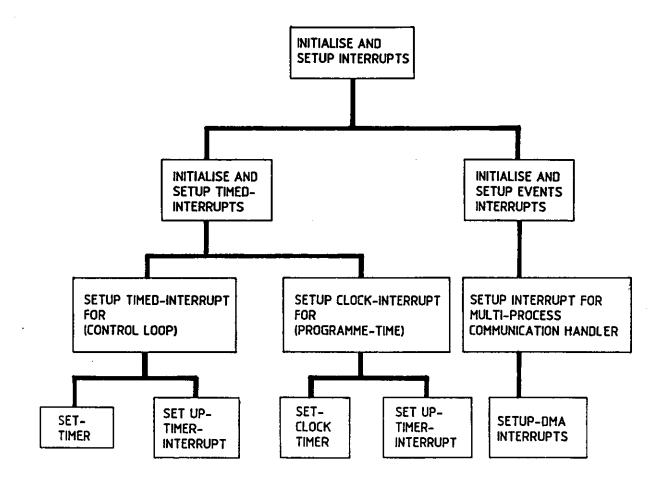

| E.6:  | Initialise and Set-up Interrupts | 334 |

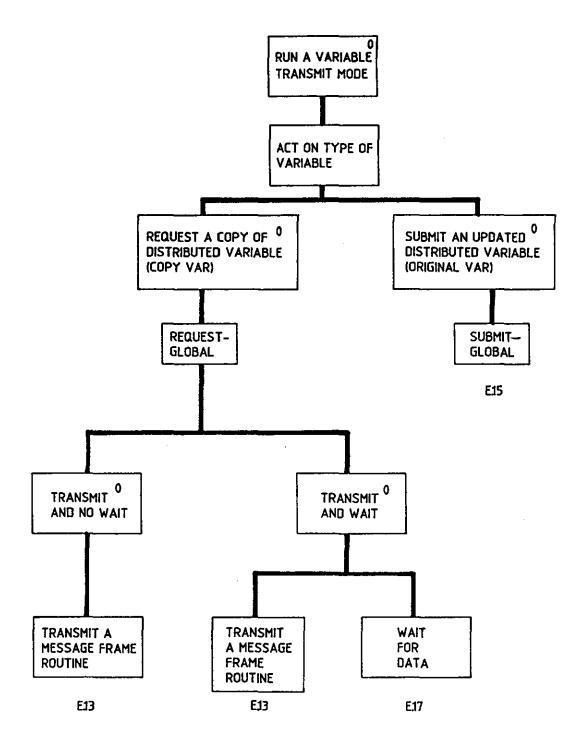

| E.7:  | Run a Variable Transmit Mode     | 335 |

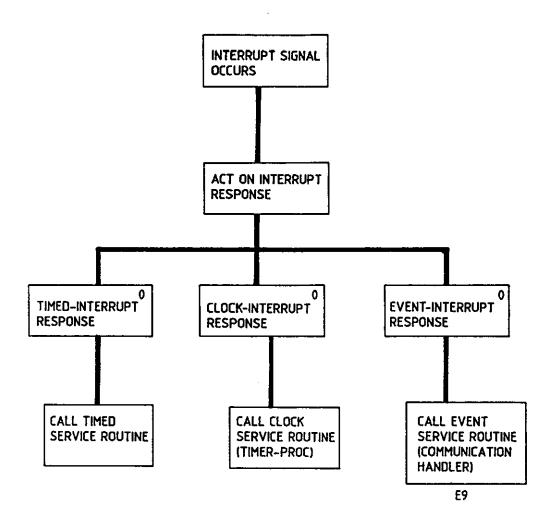

| E.8:  | Interrupts                       | 336 |

| E.9:  | Event Service Routine            | 337 |

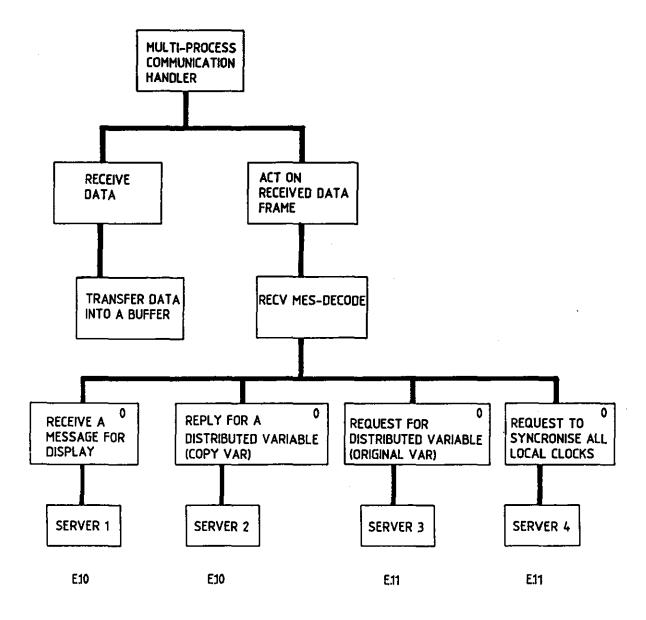

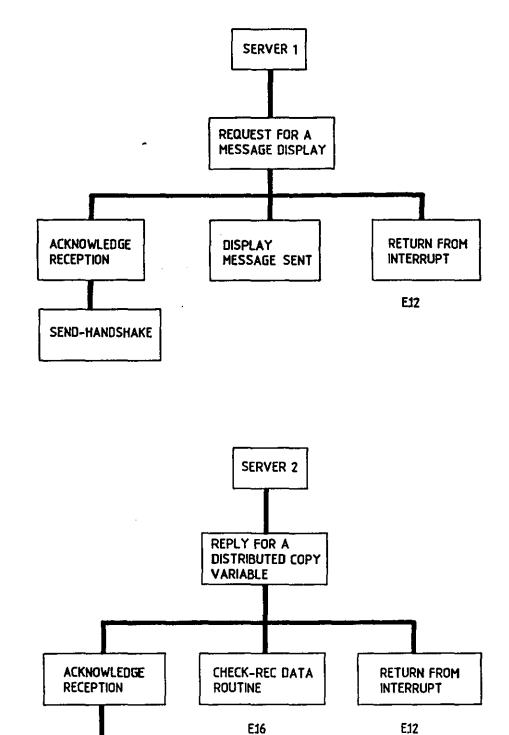

| E.10: | Server 1 and Server 2            | 338 |

| E.11: | Server 3 and Server 4            | 339 |

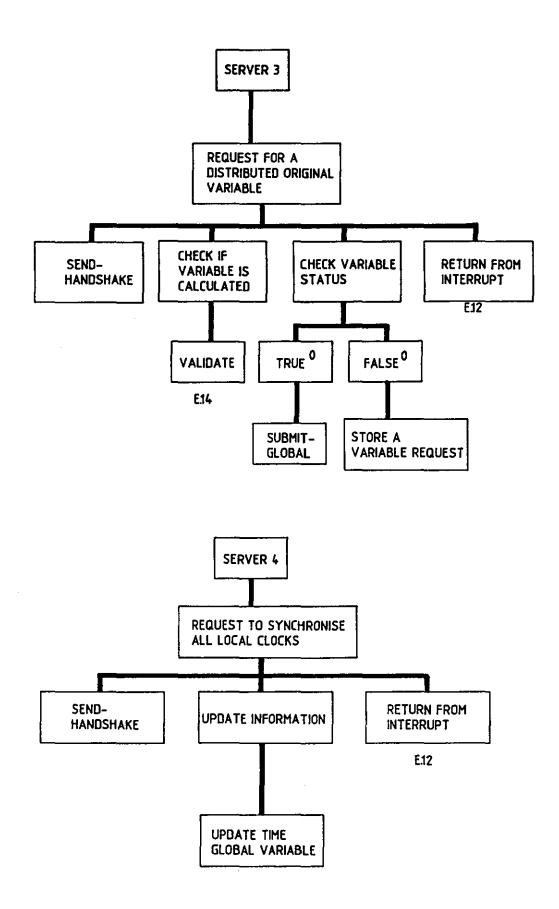

| E.12: | 'Return From Interrupt' Routine    | 340 |

|-------|------------------------------------|-----|

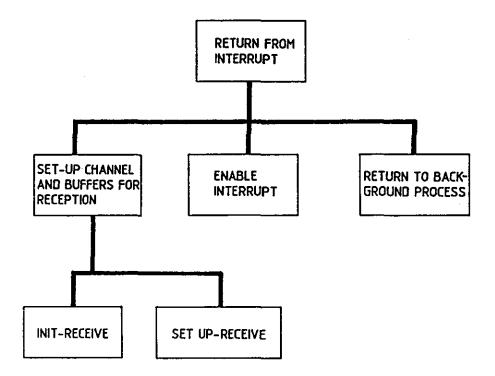

| E.13: | 'Transmit a Message Frame' Routine | 341 |

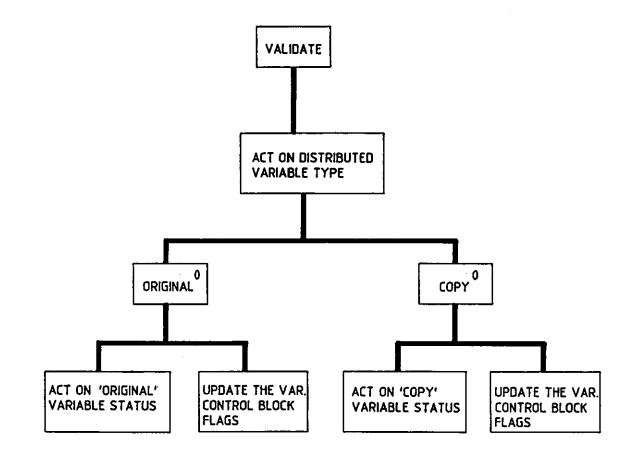

| E.14: | 'Validate' Routine                 | 342 |

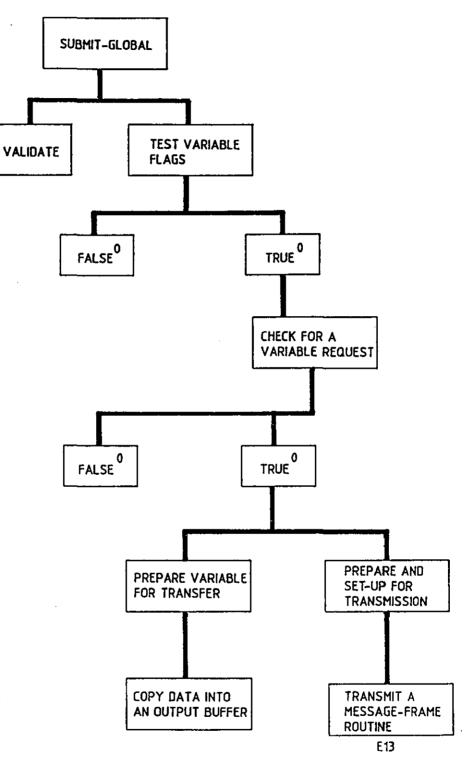

| E.15: | 'Submit-Global' Routine            | 343 |

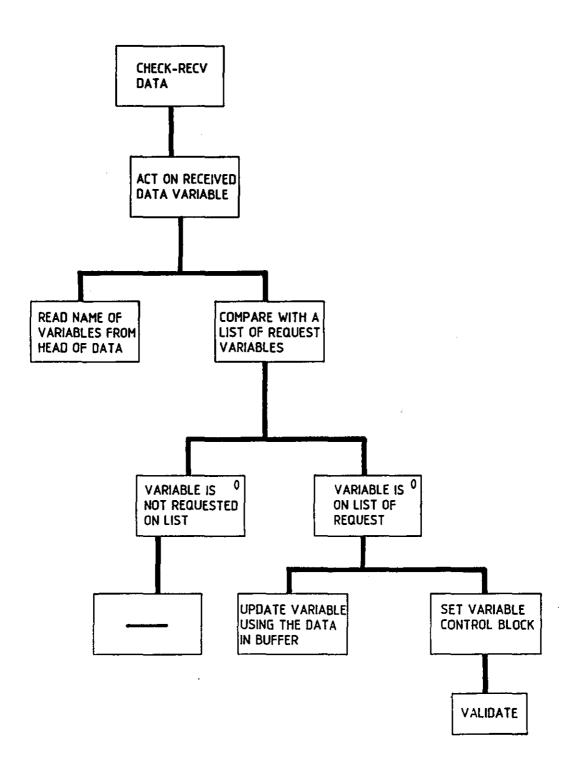

| E.16: | 'Check-RecvData' Routine           | 344 |

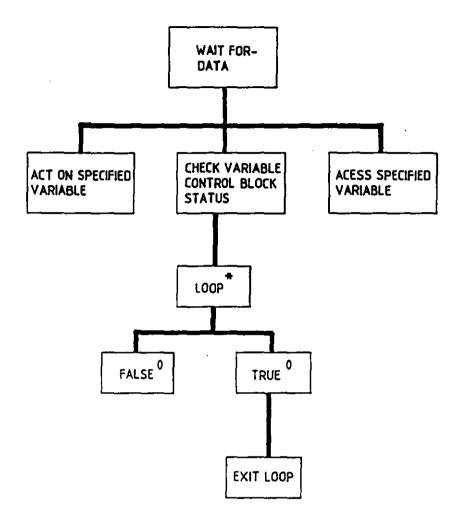

| E.17: | 'Wait For-Data' Routine            | 345 |

#### LIST OF ABBREVIATIONS

#### GENERAL

| ASCII | - | American Scientific Code for Information Interchange. |

|-------|---|-------------------------------------------------------|

| 1100B | - | Binary number.                                        |

| BIT   |   | Binary Digit.                                         |

| BYTE  | - | 8 bits.                                               |

| CAD   | - | Computer Aided Design.                                |

| CPU   | - | Central Processing Unit (80188/64180).                |

| cs    | - | Count of Stations.                                    |

| DMA   | - | Direct Memory Access.                                 |

| DRAM  | - | Dynamic Random Access Memory.                         |

| DUART | - | Dual Universal Asynchronous Receiver Transmitter.     |

| EPLD  | - | Erasable Programmable Logic Devices.                  |

| EPROM | - | Erasable Programmable Read Only Memory.               |

| OFDH  | - | Hexadecimal number.                                   |

| FS    | - | First Station.                                        |

| I/0   |   | Input/Output.                                         |

| JSP   | - | Jackson's Structured Program.                         |

| LS    | ~ | Last Station.                                         |

| NPE   | - | Numerical Processor Extension (8087).                 |

| NS    | - | Next Stations.                                        |

| OBI   | - | On-board Interfacing.                                 |

| PCB   | - | Printed Circuit Board.                                |

| PDF   | - | Program Design Facility.                              |

| PS    | - | Previous Station.                                     |

| ROM   | - | Read Only Memory.                                     |

|       |   |                                                       |

- RPC Remote Procedure Call.

- SRAM Static Random Access Memory.

- IMS Temporary Memory Store.

- TPBAM Token Passing Bus Access Method.

- TS This Station.

- VCB Variable Control Block.

- VDU Visual Display Unit.

#### SIGNALS

| (*)  | - | Active low signal.                 |

|------|---|------------------------------------|

| ALE  |   | Address Latch Enable.              |

| ACK  | - | Acknowledge.                       |

| CLK  | - | Clock.                             |

| DT/R | - | Data Transmit/Receive.             |

| DRQ  | - | DMA Request.                       |

| EDT  | - | End of Data Transmission.          |

| LMCS | - | Lower Memory Chip Select.          |

| M/IO | - | Memory access/Input-Output access. |

| MMCS | - | Medium Memory Chip Select.         |

| PCS  | - | Peripheral Chip Select.            |

| RD   | - | Read signal.                       |

| RDT  | - | Request Data Transmission.         |

| RDY  | - | Ready.                             |

| UMCS | - | Upper Memory Chip Select.          |

| WR   | - | Write signal.                      |

# CHAPTER 1

.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 OVERVIEW

Recent advances in hardware computer technology, combined with component cost reductions, have spurred on the development of new distributed hardware systems. Eventually, future real-time applications will be targeted toward highly distributed, multiprocessor environments because of their attractive cost-to-performance ratios compared to single processor systems.

As new high performance distributed architectures are explored and exploited, the nature of software developed for these new generations will tend to shift from being sequential in nature to being more parallel.

Developing software for such systems will be even more troublesome than it is for traditional computer systems due to synchronisation issues, new algorithms and languages. Yet, there is currently little software support for distributed environments.

Some vendors have succeeded in developing quality software for nonsequential structures using conventional technologies. However, lack of specialised support is already hindering long scale development of systems with this class of architectures. Successful software development, however, will only stem from a better understanding of distributed systems. The design and synthesis of software for distributed systems requires the use of a design methodology and programming language which builds on the inherent parallel nature of such systems. Thus, an adequate software base (design tools, run time environments, dedicated operating systems, compilers, etc) and better software engineering techniques must be available before future needs, for high quality software, can be met.

Intense research activity in recent years has led to a more mature understanding of the problems of a distributed environment [1]. Still, however, the following points need to be resolved to facilitate advances in software development for distributed architectures [2]:

- \* Approaches to problem decomposition for mapping applications to the proper distributed architecture.

- \* Techniques for software design partitioning and allocation.

- \* Language issues for distributed architectures for future systems (e.g. language constructs to address parallel issues).

- \* Algorithm design and evaluation.

- \* Problem visualisation and animation techniques.

- \* Software testing to attain high reliability levels.

#### 1.2 RESEARCH OBJECTIVES

Real-time, multi-processor, embedded systems are one application area where response times, throughput, reliability and fault-tolerance constitute the major design criteria [3]. Hence the distribution and management of the application software is a critical function.

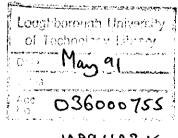

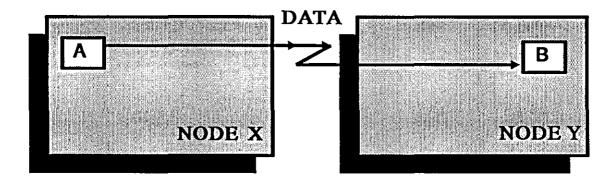

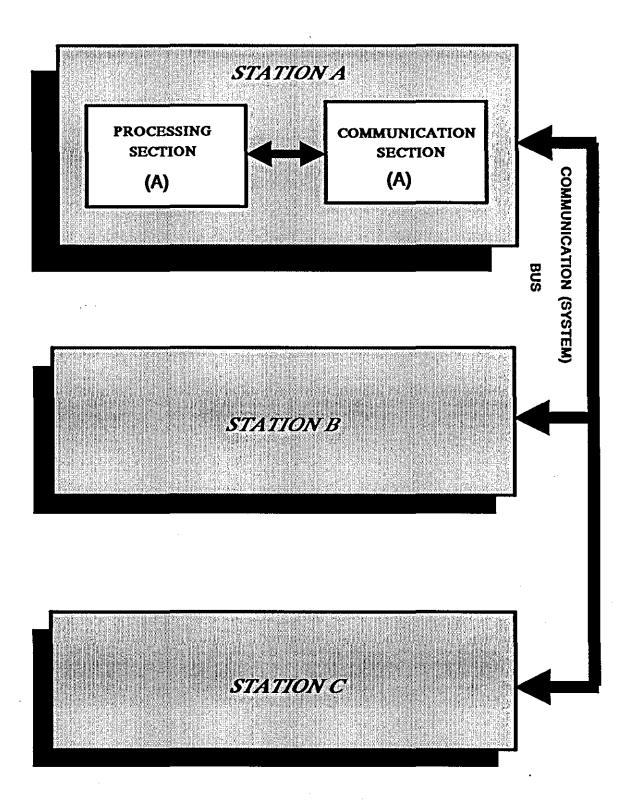

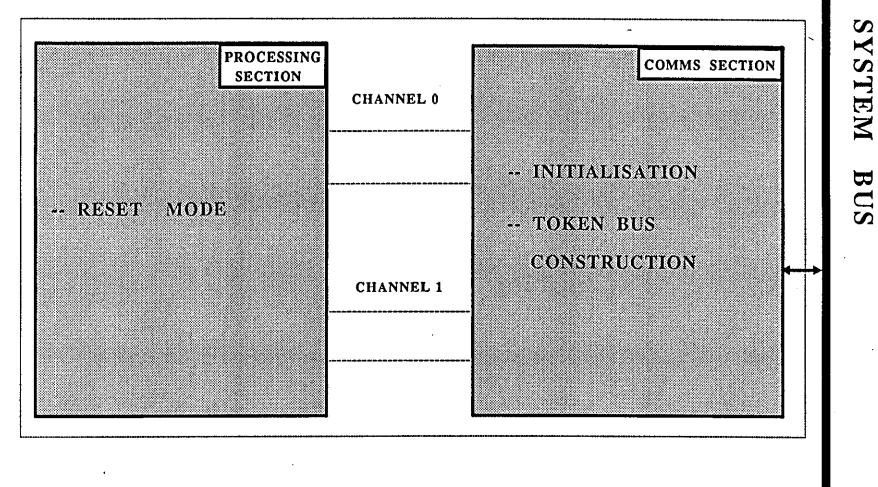

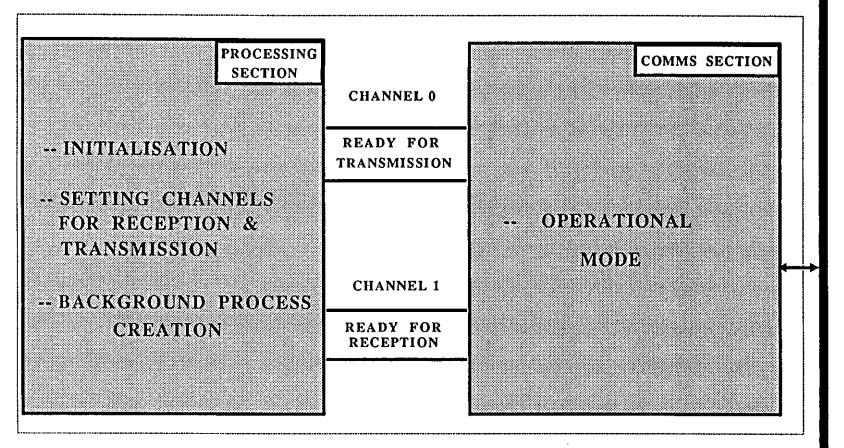

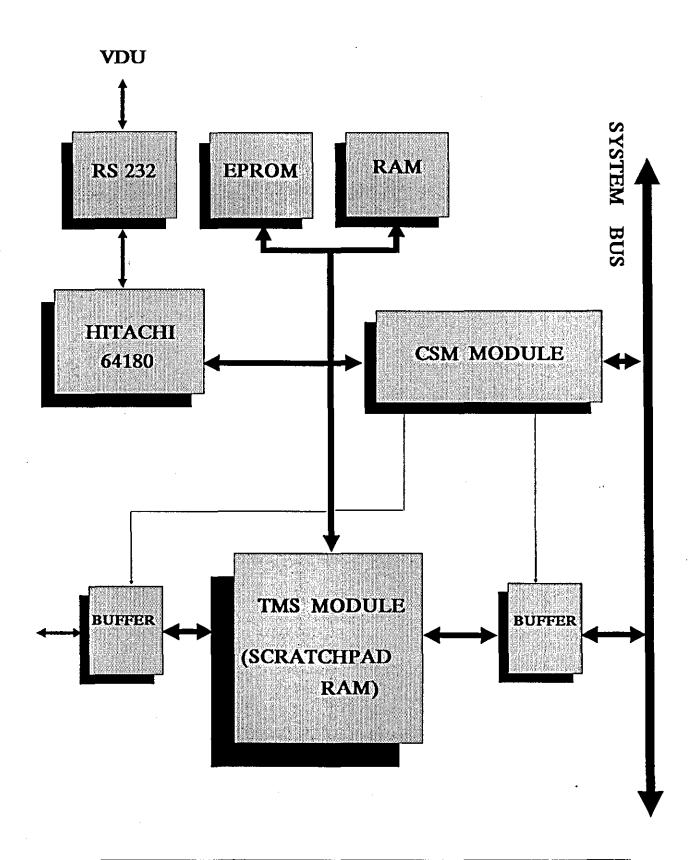

A prototype loosely-coupled multi-processor system has been designed and implemented for use in fault-tolerant real-time applications (Figs. 1.1 and 1.2).

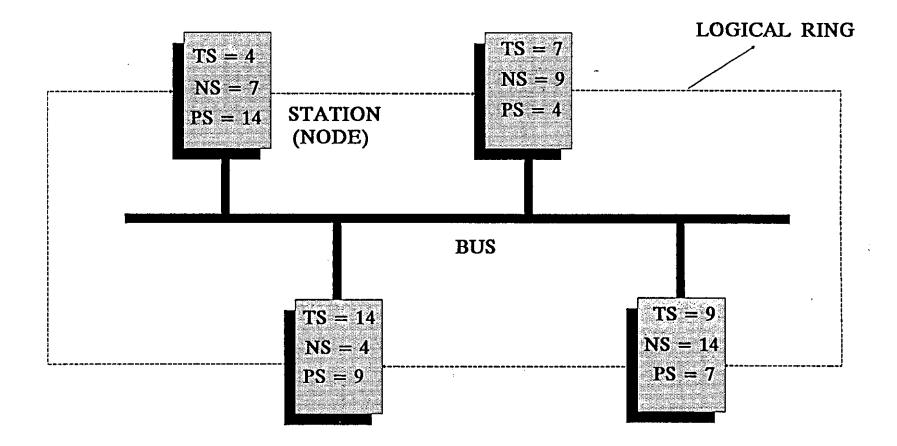

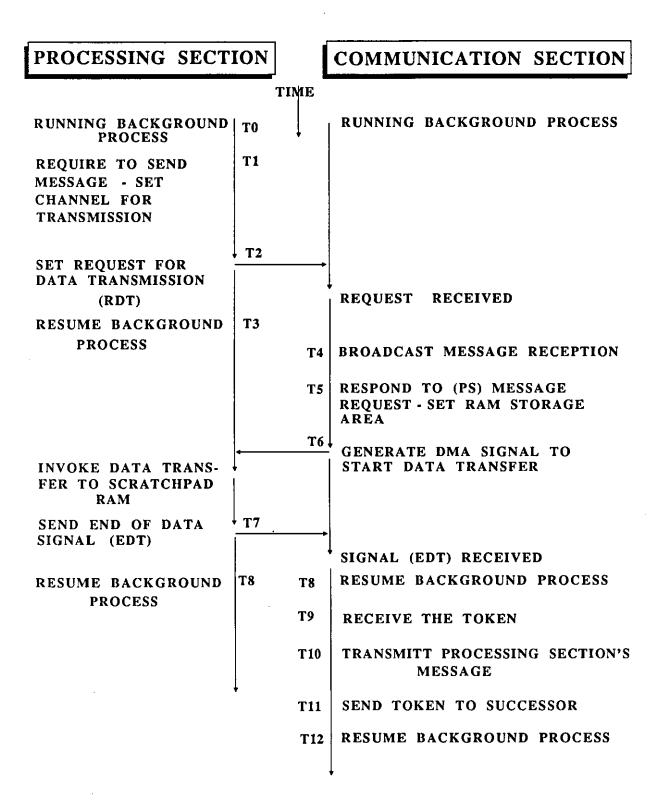

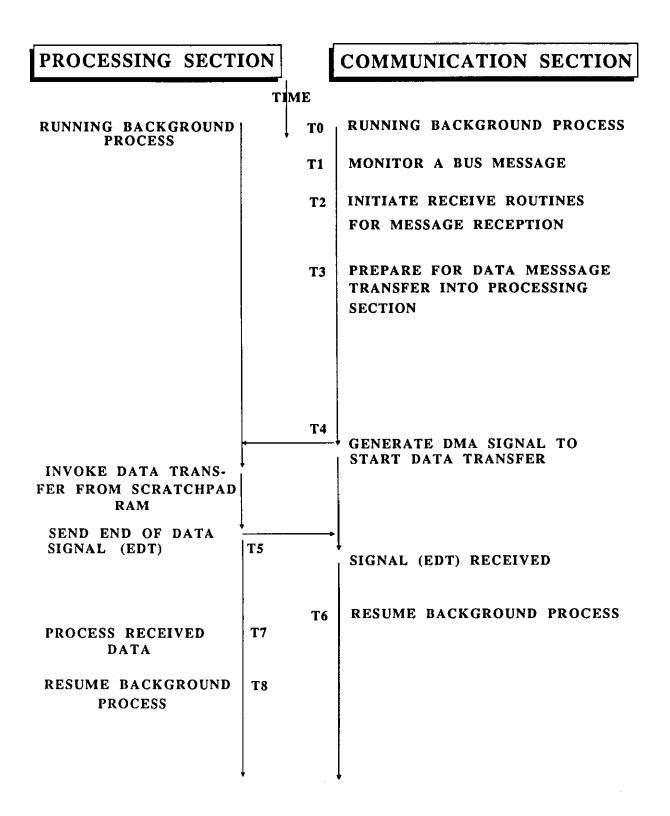

This thesis discusses the organisation and structure of the total system, concentrating in particular on the software environment that has been developed to support functional partitioning [4,5]; i.e. the communication and executive (kernel) functions. The communication system is based on a token passing bus protocol for use with single board computers connected via a fast parallel bus. The kernel is designed to support functional partitioning of application programs, and can be implemented using standard compilers. No special multiprocessing features are required. Most of the software for this system has been written in a high level, structured language (Modula-2), though assembly language programming has been used in a few specialised areas.

#### 1.3 THESIS ORGANISATION

Chapter 2 presents methods of task management in distributed environments. Partitioning schemes and allocation strategies are highlighted in particular.

Chapter 3 gives a general review of distributed, concurrent programming techniques. Different classifications and methods are presented together with the evaluation of each method.

Chapter 4 is devoted to the functional description of a multiprocessor structure that is designed to support functional partitioning. Supporting issues such as inter-processor communication, operating system constructs, and choice of programming language are discussed within this chapter.

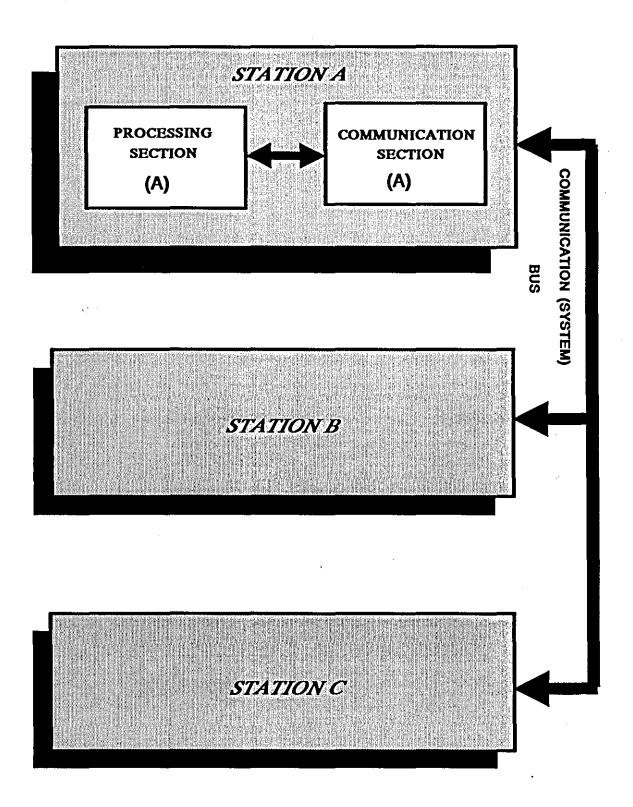

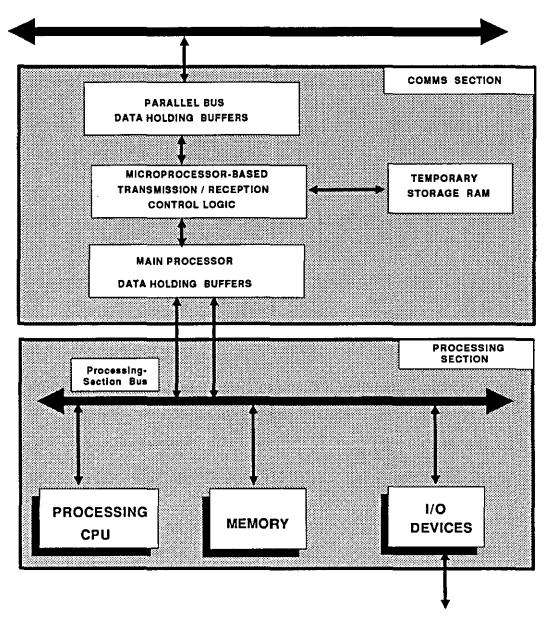

Chapter 5 describes the implementation of the multi-processor system developed in this research project at building block level. The function of each block and its role in the system is demonstrated. It introduces the idea of using two separate sub-systems; the communication sub-system for handling communication with the network and the processing sub-system for the execution of application tasks.

Chapter 6 and Chapter 7 concentrate on the design of the software environment which has been developed to support functional partitioning. Chapter 6 describes the implementation of the communication protocol and its run-time support system. Chapter 7, on the other hand, describes the structure and implementation of an operating system kernel for the support of functional partitioning. Software structure diagrams for Chapter 6 and Chapter 7 are given in Appendices C and E respectively.

Chapter 8 introduces the different approaches and techniques for the testing and validation of both the hardware system, and the implemented system software modules.

Finally, Chapter 9 reviews and assesses the different achievements of the research work. It also highlights areas for future research.

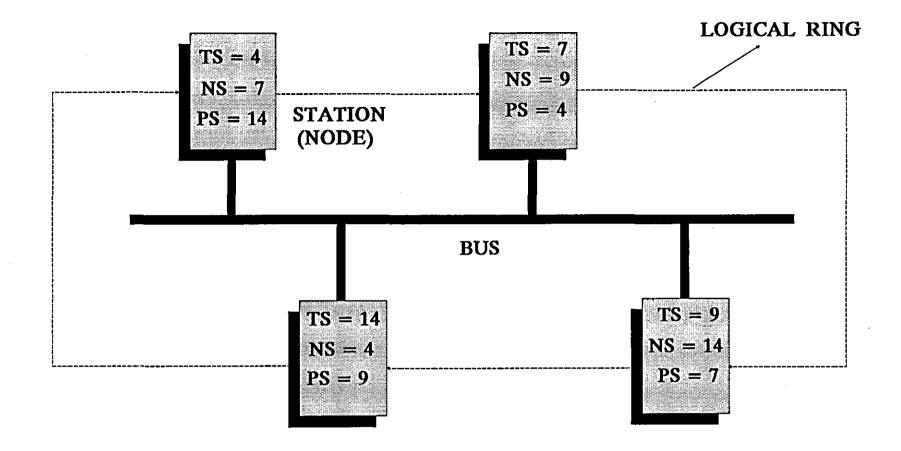

### Fig. 1.1 SYSTEM CONFIGURATION

#### SYSTEM BUS

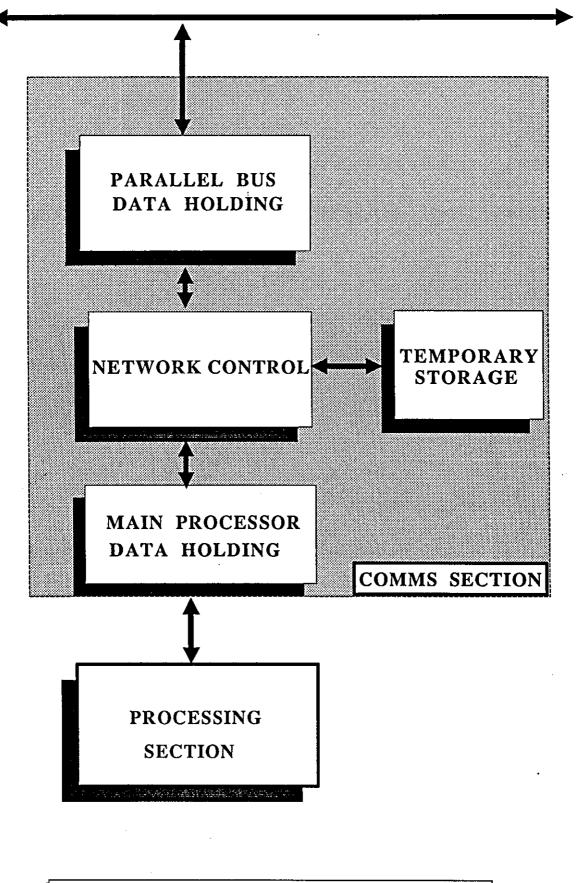

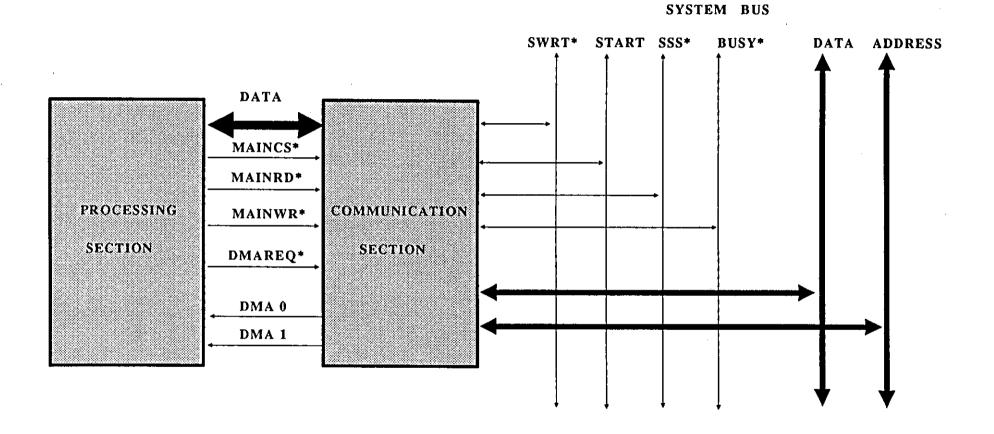

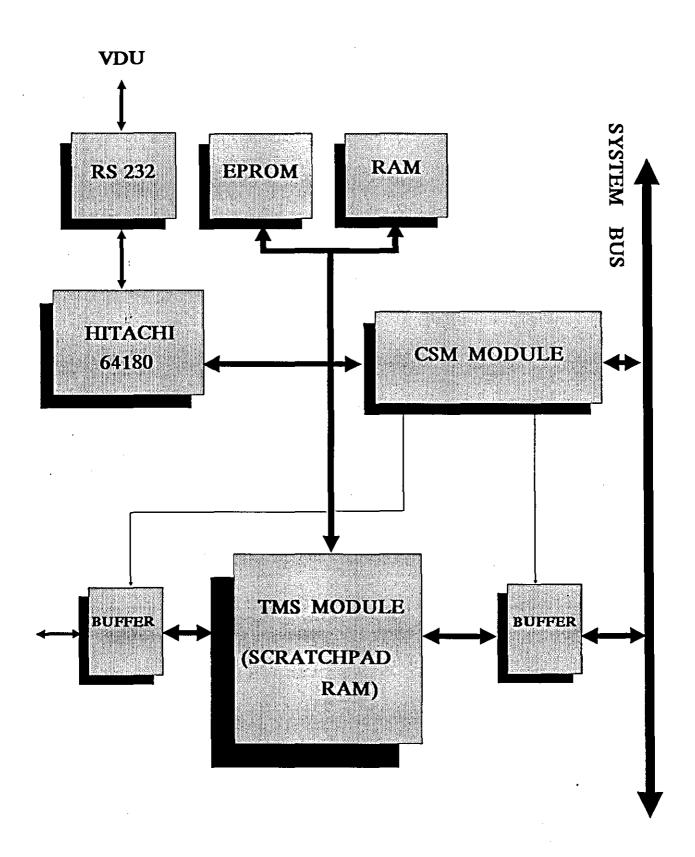

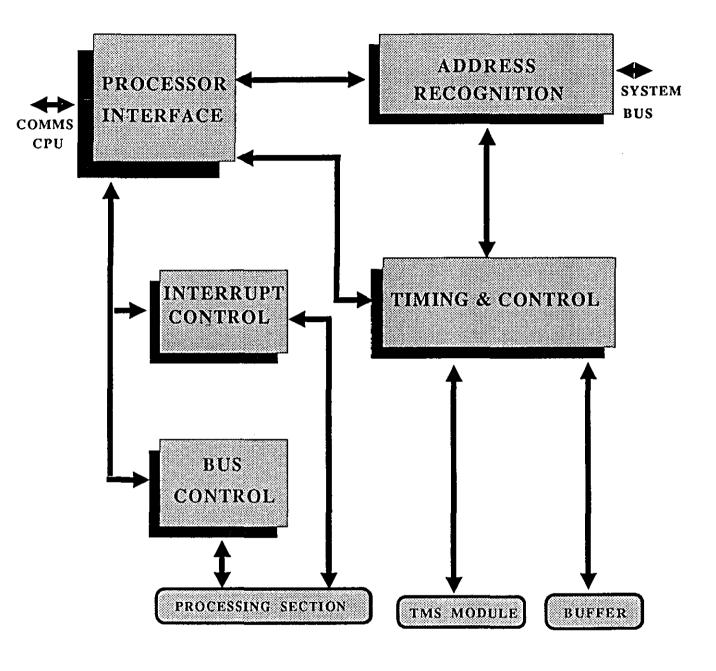

Fig. 1.2 MULTIPROCESSOR NODE - FUNCTIONAL STRUCTURE

# CHAPTER 2

ı

#### CHAPTER 2

#### METHODS OF TASK MANAGEMENT IN DISTRIBUTED SYSTEMS

#### 2.1 GENERAL

Distributed systems have inherent problems which must be overcome by different concurrent programming methodologies. Certain demands and requirements have to be met in the design of distributed programs. Issues such as the complexity of the underlying hardware, partitioning and allocation schemes, the supporting constructs of the programming languages and the availability of the software environment tools play major roles in task management within a distributed environment. This chapter highlights the main issues relating to such environments i.e. those of partitioning, allocation, and communication aspects.

#### 2.2 PARTITIONING SCHEMES FOR DISTRIBUTED ENVIRONMENTS

#### 2.2.1 Overview

Partitioning is the process of breaking down a task into smaller tasks (sub-tasks), or a program into smaller programs called fragments or segments.

In many cases the partitions lead to an apparent reduction in the complexity of the system and reduces the problem at hand to manageable pieces. The partitioning unit or construct used (called granularity) should be carefully chosen as this will affect the type of system implementation. For instance, as the number of parallel processes into which a computational task is partitioned is increased, so the volume

of inter-process communications for control and data interchange also increases. This leads to a closely coupled system implementation.

Language constructs play an important part in simplifying partitioning schemes. For instance, the language StarMod [1] allows the programmer to partition a computation into a collection of processes and also to define the details of communication paths between the processors. Ada [2] has been criticised for not providing a suitable partitioning constructs; help is required from other tools in the support environment to provide such a scheme [3,4,5].

Two basic approaches may be identified for partitioning distributed software [6]:

- Distribute fragments of a single program across processors and use a normal intra-program communication mechanisms for interaction;

- ii) Write a separate program for each processor and devise a means for inter-program interaction. This method is not so applicable in distributed environments since the introduction of hardware specifications into a design at an early stage restricts program portability. It also leads to a change in the partitioned program structure whenever the configuration (say number of processors) changes.

#### 2.2.2 Designing a Distributed System as a Single Program

The fundamental concept here is that the application software is viewed as a single program, distributed across the target system. Its main advantage is that all the interfaces between the distributed

fragments can be type checked for compatibility by the compiler. Within this approach two general strategies can be identified: postpartitioning and pre-partitioning [5,7,8]:

#### i) Post-Partitioning

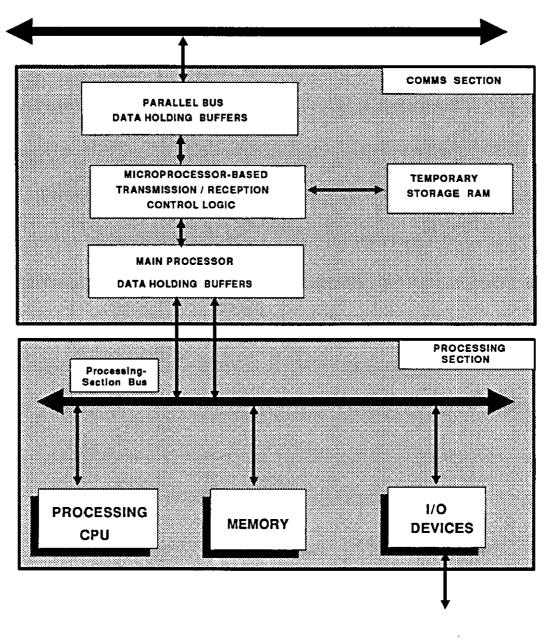

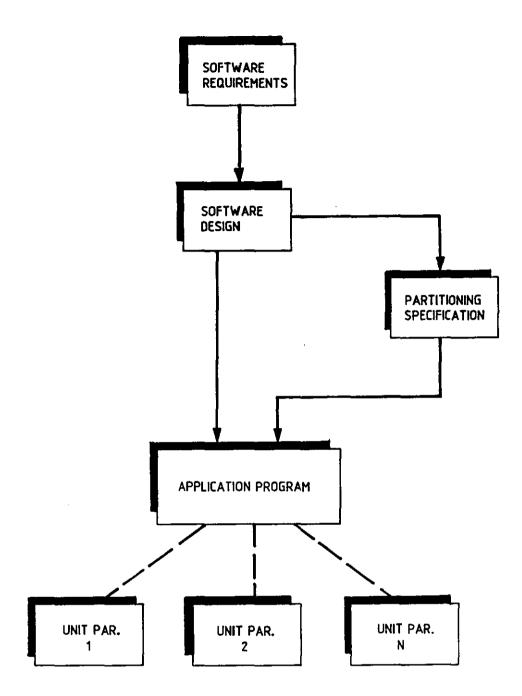

In this strategy, partitioning of an application program is expressed after the design of the software is complete. The partitioning process does not attempt to force changes in the software design in order to achieve the required partitioning. Fig. 2.1 illustrates a typical ordering of system development steps. Partitioning is performed concurrently with and independently of coding.

The programmer produces an appropriate solution to the problem at hand. It is left to the partitioning specification software (Fig. 2.1) to:

- \* Describe the target configuration,

- \* Partition the program into components for distribution, and

- \* Distribute the components to individual nodes.

This method promotes portable software, i.e the same program can be mapped onto different hardware configurations. However, it needs a language that contains facilities for configuration management.

#### ii) Pre-Partitioning

This strategy is to select a particular construct as the sole unit of partitioning, to be used throughout the design and programming process (see Fig. 2.2). The notion underlying this strategy is that of a 'virtual node', which is an abstraction of a physical node in the distributed system [4,9]. A virtual node consists of one or more units

(which may share memory) communicating with other virtual nodes via some form of message passing over a communication sub-system. More than one virtual node, however, can be mapped onto a single physical node.

Note that the programmer must accept any constraints the choice of constructs entails (e.g. it might affect inter-process communication or system performance).

The notion of virtual nodes is found in most languages which have been designed specifically for supporting distributed programming (e.g. the 'guardian' of Argus [10] and the 'processor module' of StarMod [1]).

For a language construct to be effective as a virtual node it must be supported by [4]:

- \* Separate compilation.

- \* Library units or modules.

- \* Exception handling facilities to cope with process failures.

#### 2.2.3 Functional Partitioning Schemes

Many real-time applications and tasks may be naturally distributed in a functional manner. Functionally distributed systems are often modelled and controlled as a set of communicating, distributed subtasks (processes) [11]. The software for such systems invariably reflects the distributed nature of the application.

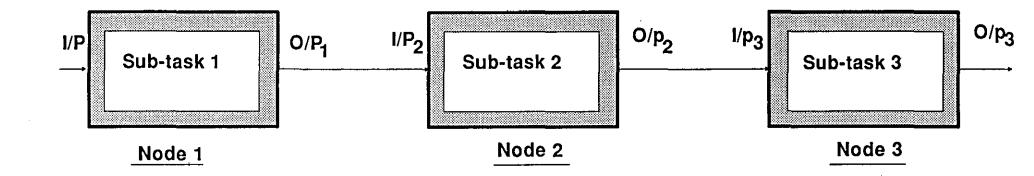

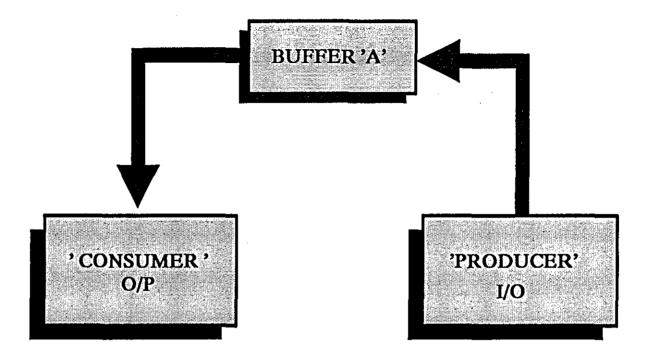

The software design and support of such a functional distribution of sub-tasks (processes) depends on the degree of interaction of these processes among the different processors. A simple implementation of functional partitioning may consist of functional or pipelining partitioning [12] (see Fig. 2.3). Here, the distributed processes interact occasionally, usually for transferring data results, using message-passing techniques.

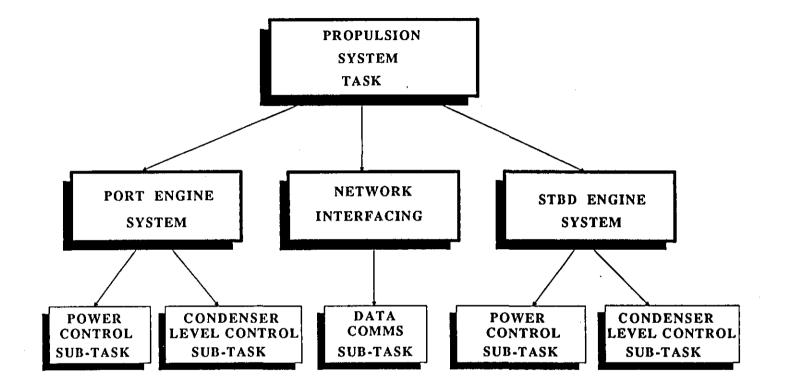

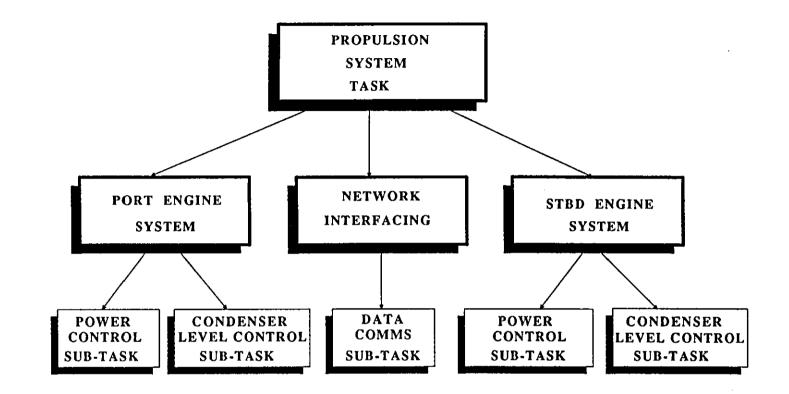

Fig. 2.4 shows a more realistic approach to, and understanding of, functional partitioning within real-time environments. The total system task is partitioned into a number of functional sub-tasks which are then mapped onto the various nodes of a distributed system. In real-time systems such sub-tasks involve plant interfacing, network control, computation of digital control algorithms, etc. These run asynchronously and concurrently within the distributed system. Distributed processes, however, have to communicate and interact occasionally in order to achieve a common goal [13,14]. Management and interaction of distributed processes is usually achieved by supporting software embedded in each node of the system [15,16]. Some of the main advantages in using this method are:

- \* The software structures mirror the application structure, this being especially suitable for real-time application tasks.

- \* The individual software units (sub-tasks) can be implemented, type checked and compiled using uni-processor compilers.

- \* The granularity (unit of partitioning or sub-task), may be further divided and partitioned into other functional sub-tasks (see Fig. 2.4). These sub-tasks can be mapped, in turn, to one or more nodes of the distributed system.

- \* Finally, each sub-task can be considered as a unit sole of partitioning. This means, it can be separately processed, coded, and compiled using structured languages suited or even adapted for distributed environment.

#### 2.3 TASK ALLOCATION STRATEGIES

Allocation assumes the existence of well partitioned or predefined units or modules, and discusses how to effectively map or allocate these units or modules to different nodes. The method of allocation chosen should allow for an efficient and reliable implementation of inter-process communication mechanism [17,18].

In distributed systems this effectively means 'how different program segments reside on different processors, and how they interact' [5,19].

The unit of allocation depends, among other things, on the constructs of the language use for the implementation. For instance, in Ada two main constructs have been considered as the basis of allocation; the 'task' and the 'package' [4,9]. The task is unable to encapsulate data in the same way as a package, and cannot be a library unit, hence its usefulness as a unit of distribution is limited. The package, however, is supported, by separate compilation and library units and thus favoured as a distribution unit.

Similarly, in Modula-2 [19] a 'co-routine' and a 'module' are two constructs that may be suggested as units for allocation [20]. Again, a co-routine fails to encapsulate data in the same way a module does, also it cannot be a library unit or even separately compiled. But most important, for a distributed application, the coroutine mechanism should be modified in order to allow for remote procedure invocations and resumptions. The semantics of remote coroutines appear to be applicable to Modula-2 [21]. A module, on the other hand, is inherently suitable for use as a distribution unit. Apart from

separate compilation, and use of library units, there are two main reasons for using a module as a distribution unit [9]:

- \* Procedures of a module need efficient access to the local shared data of the module. Hence, it is not possible to achieve efficiency if the module is split over several nodes or processors.

- \* Modules often form monitors [22], where mutual exclusion of processes is to be maintained. This is difficult to implement if a module itself is spread over several nodes.

#### 2.4 INTER-PROCESS COMMUNICATION IN DISTRIBUTED SYSTEMS

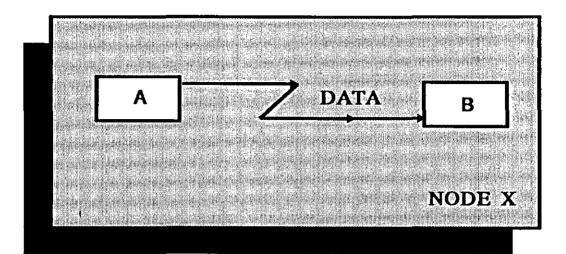

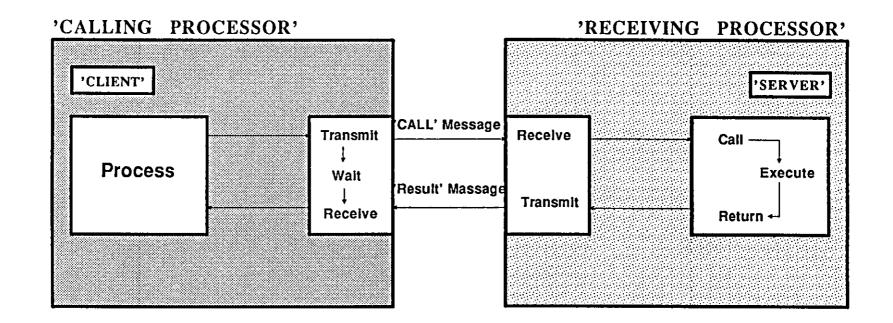

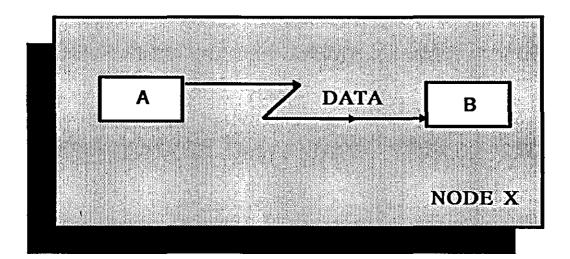

Communication constructs fall into two groups; those designed to support processes which reside on the same node, and those used where processes reside on different nodes (processors). For processes on the same node, a typical and standard form of inter-process communication mechanism is the use of shared variables (using monitors for implementing mutual exclusion). Whereas for processes on different nodes, inter-processor communication is frequently implemented using the remote procedure call mechanism (RPC) [23] (this relationship can be viewed as a 'client-server' model).

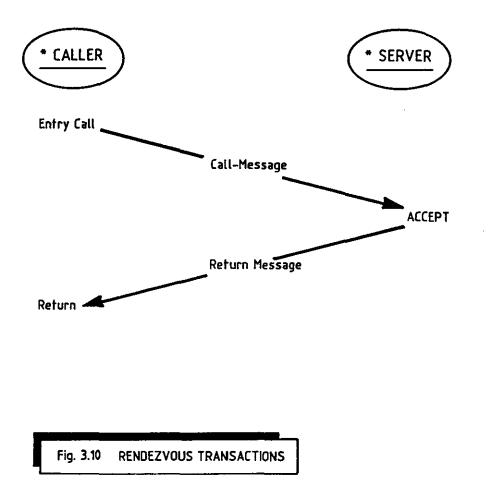

However, a more constructive way of communication between processes in a distributed environment is through the use of message-passing techniques. Process communication may be implemented in both (or either) asynchronous and synchronous forms, using channels [24] or the rendezvous [2]. In a distributed environment, process communication must be transparent, i.e, the programmer is unaware as to whether processes reside on the same or different nodes. It is left to the

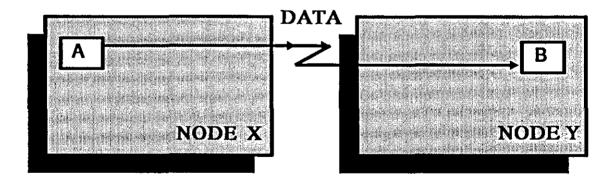

supporting software (operating system kernel) to decide whether processes need inter-process or inter-processor communication. To implement this structure, two types of messages can be executed in a distributed system, E-mode and T-mode messages [25] (Fig. 2.5):

- \* E-mode message refer to message transactions between various processes of a user program (inter-process communication).

- \* T-mode message refer to messages exchanged between the kernels or operating systems of two different nodes (inter-processor communication).

Usually all communication between the different processes are issued first as E-mode messages. These messages are subsequently interpreted by the underlying software (usually called a filter process) as to whether the source and destination processes reside on the same or different processors. If they reside on the same processor, then an Emode message is adequate for communication. However, if they turn out to be on different processors, then a kernel process (usually called a communication process) issues a T-mode message to exchange data between the different nodes. These modes of message communication help constructing a 'naming' scheme in a distributed system.

#### Fig. 2.1 SOFTWARE DEVELOPMENT INCORPORATING PROGRAM POST-PARTITIONING

## FIG. 2.2 STEPS IN SOFTWARE DEVELOPMENT IN DISTRIBUTED APPLICATION (PRE-PARTITIONING)

:

## Fig. 2.3 FUNCTIONAL PARTITIONING (PIPELINE)

Fig. 2.4 FUNCTIONAL PARTITIONING

.

•

## Fig. 2.5A E - MODE MESSAGE

## Fig. 2.5B T - MODE MESSAGE

# CHAPTER 3

#### CHAPTER 3

#### FUNDAMENTAL ASPECTS OF DISTRIBUTED CONCURRENT PROGRAMS

#### 3.1 CONCURRENT PROGRAMS (USE OF PROCESSES)

#### 3.1.1 General

The nature of concurrent programming has changed substantially in the past ten years. First, theoretical research activities have prompted the definition of new programming notations that express concurrent computations simply and make synchronisation requirements explicit. Second, the advances in hardware technology, and hence the availability of inexpensive processors, have made possible the construction of distributed systems and multi-processors that were previously uneconomical.

Thus, implementations of concurrent programming are no longer limited to use in operating systems only. They are implemented in the design of database management systems, parallel scientific computations and real-time, embedded control systems.

#### 3.1.2 Processes

A 'sequential program' specifies sequential execution of a list of statements; its execution is frequently called a 'process' [1].

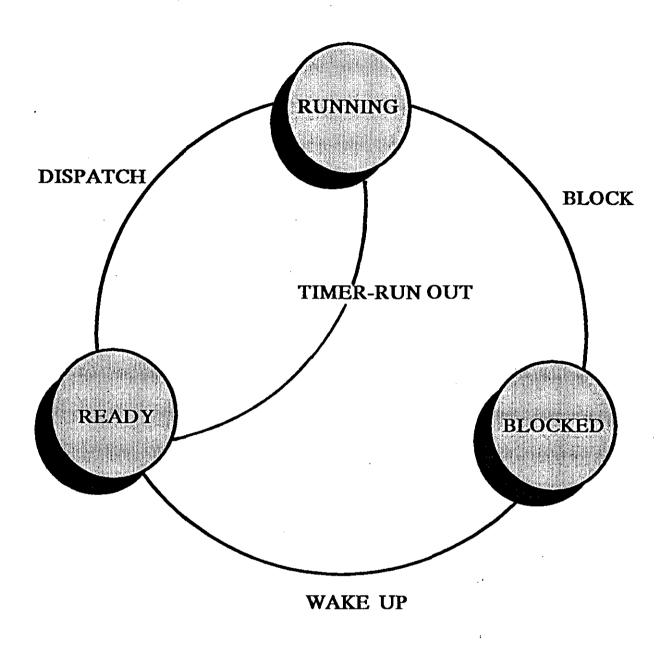

A process may be in three main states (see Fig. 3.1):

- i) Running: Instructions are being executed.

- ii) Blocked: The process is waiting for some event to occur (such as input/output completion).

- iii) Ready: The process is waiting to be assigned a processor.

A concurrent program, however, specifies two or more sequential programs which may be executed concurrently as 'parallel processes'. It can be executed by two methods:

- Running more than one process on an individual processor. This is referred to as 'multi-tasking'. It has to be mentioned here, however, that 'quasi-concurrency' is the name referred to when processes share only one processor [2].

- ii) Running each process on its own processor. This is referred to as 'multiprocessing' if processors share a common memory, or as 'distributed processing' if the processors are connected by a communications network [3]. A concurrent program that is executed in this latter way is often called 'a distributed program'.

#### 3.1.3 Process Interaction

In order for concurrent processes to cooperate, they must communicate and possibly synchronise. 'Communication' is the transfer of data values from one process to another. Inter-process communication is based either on the use of 'shared variables' (variables referred by more than one process) or on 'message passing'.