## LOUGHBOROUGH UNIVERSITY OF TECHNOLOGY LIBRARY

|                                         | LIBHARY    | A = A      |

|-----------------------------------------|------------|------------|

| AUTHOR/FILING                           | TITLE      |            |

| D                                       | DNG, L     |            |

|                                         |            |            |

| ACCESSION/COP                           | Y NO.      |            |

| Of                                      | 0101744    | •          |

| VOL. NO.                                | CLASS MARK | ********** |

|                                         |            |            |

|                                         | LUAN CORY  | ·          |

| 17 MAR 1995                             |            |            |

| 21 MAR 1997                             |            |            |

| 2 1 max 1997                            |            |            |

| 1 3 JUN 1997                            |            |            |

| • • • • • • • • • • • • • • • • • • • • |            |            |

|                                         |            | ·          |

|                                         | l          |            |

|                                         |            |            |

|                                         |            |            |

|                                         | /          |            |

# Gate Oxide Failure in MOS Devices

by

Liqin Dong B.Sc

A Master Thesis

Submitted in partial fulfilment of the requirements for the award of the Degree of Master of Philosophy of Loughborough University of Technology

August 1994

<sup>©</sup> by L. Dong, 1994.

| Loug       | hborough University<br>Technology Ubrary |

|------------|------------------------------------------|

| Ci         | EECHHERA STATION                         |

| Date       | July 98                                  |

| Class      | ,                                        |

| Acc<br>No. | 040101544                                |

v8913473

# **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks to my supervisor, Dr. Vincent Dwyer for providing me the opportunity of this work, for his encouragement and support throughout the work, and for his help and time he put into the final preparation and production of this thesis.

All members in the International Electronics Reliability Institute would have helped me in some ways, their friendship is appreciated. In particular, I would like to thank Dr. Martin Tunnicliffe for the many rewarding discussions I have had with him, for the help on experiments and reading this thesis. Thanks also go to Mr. Paul Donaldson for all his advice and help in experiments and in English. Thanks to Jonathan and Susan for their helps in many ways.

I am greatly indebted my husband, Zaiqing, for his love, encourage and tremendous support throughout many years.

To Zaiqing, I dedicate this work.

# **ABSTRACT**

The thesis presents an experimental and theoretical investigation of gate oxide breakdown in MOS networks, with a particular emphasis on constant voltage overstress failure. It begins with a literature search on gate oxide failure mechanisms, particularly time-dependent dielectric breakdown, in MOS devices.

The experimental procedure is then reported for the study of gate oxide breakdown under constant voltage stress. The experiments were carried out on MOSFETs and MOS capacitor structures, recording the characteristics of the devices before and after the stress. The effects of gate oxide breakdown in one of the transistors in an nMOS inverter were investigated and several parameters were found to have changed.

A mathematical model for oxide breakdown, based on physical mechanisms, is proposed. Both electron and hole trapping occurred during the constant voltage stress. Breakdown appears to take place when the trapped hole density reach a critical value.

PSPICE simulations were performed for the MOSFETs, nMOS inverter and CMOS logic circuits. Two models of MOSFET with gate oxide short were validated. A good agreement between experiments and simulations was achieved.

# SYMBOLS AND NOMENCLATURE

A Ampere.

Å Angstrom (10-8cm).

a.c. Alternating current.

AF Accelerate factor.

Al Aluminium.

B Bulk of MOS device.

C Capacitance, Coulomb.

cm Centimetre.

CMOS Complementary metal oxide semiconductor.

Cr Chromium.

CV Capacitance vs. voltage.

CT1 Tektronix current transformer probe.

°C Centigrade.

CAD Computer aided design.

Cox Oxide capacitance.

CR Capacitance resistance.

Drain electrode of MOSFET.

DC, d.c. Direct current.

D-mode Depletion mode.

DUT Device under test.

E Energy.

E<sub>a</sub> Activation energy.

Energy required to support oxide breakdown.

Energy of conduction band edge.

E<sub>f</sub> Fermi level.

E<sub>G</sub> Energy of band gap.

E<sub>i</sub> Intrinsic Fermi level.

E<sub>T</sub> Ionization energy.

E-mode Enhancement mode.

EOS Electrical overstress.

EPROM Erasable programmable read only memory.

ESD Electrostatic discharge.

E<sub>T</sub> Energy associated with defect. E<sub>v</sub> Energy of valance band edge.

eV Electron-volt.

F Electric field, farad.

f Frequency.

F<sub>an</sub>, F<sub>cat</sub> Anode and cathode electric fields.

Field threshold for dielectric breakdown.

FET Field effect transistor.

F-N Fowler-Nordheim.

Giga (10<sup>9</sup>), gate of MOS device.

G, g Trap generation rate.

g<sub>m</sub> Transconductance (or 'mutual conductance').

GOS Gate oxide short.

H Hydrogen.

h Planck's constant.

$\hbar$  Reduced Planck's constant  $(h/2\pi)$ .

HCL Hydrochloric Acid.

HPIB Hewlett-Packard interface bus.

Hz Hertz. I Current.

Imaginary part of complex number.

$I_0, I_1$  Modified Bessel functions.

IC Integrated circuit.

IGFET Insulated gate field effect transistor.

IR Impact recombination.

I/V Current vs. voltage.

J Current density.

k Kilo  $(10^3)$ .

L MOSFET channel length, correlation length for fluctuation.

L-C-R Inductance-capacitance-resistance.

LO Longitudinal optic (phonon mode).

LSI Large scale integration.

M Mega (10<sup>6</sup>).

m Metre, Milli (10<sup>-3</sup>).

MESFET Metal semiconductor field effect transistor.

MOS Metal oxide semiconductor.

MOS-C Metal oxide semiconductor capacitance.

MOSFET Metal oxide semiconductor field effect transistor.

MSI Medium scale integration.

m<sub>0</sub> Electron rest mass.

m\* Effective electron mass.

n Electron density, Nano (10<sup>-9</sup>).

Na Sodium.

n-type Semiconductor with majority electrons.

NMOS Technology based on n-channel MOSFET.

NXOR Not exclusive-OR logic.

O Oxygen.

P Phosphorus.

p Pico (10<sup>-12</sup>).

PMOS Technology based on p-channel MOSFET.

PSG Phosphosilicate glass.

p-type Semiconductor with majority holes.

Q Charge.

$egin{array}{ll} q & & Electron \ charge. \ Q_{bd} & & Charge \ to \ breakdown. \end{array}$

$Q_d$  Total charge of depletion layer.  $Q_n$  Electron charge of inversion layer.  $Q_{ox}$  Effective oxide space-charge density.

Q<sub>ss</sub> Surface-state charge density.

R Resistance.

$\begin{array}{ll} \Re & \quad & \text{Real part of complex number.} \\ R_b & \quad & \text{Resistance of bulk silicon.} \\ \text{RAM} & \quad & \text{Random access memory.} \\ \text{S} & \quad & \text{Source of MOSFET.} \end{array}$

SEM Scanning electron microscope.

Si Silicon.

SiO<sub>2</sub> Silicon dioxide.

SMU Source/measure unit.

SPICE Simulation program with integrated circuits emphasis.

SSI Small scale integration.

T Temperature.

t Time.

$t_{bd}$  Time to breakdown.

$t_c$  Charge time.  $t_d$  Discharge time.

TDDB Time-dependent dielectric breakdown.

$T_{ox}$  Oxide thickness.

ULSI Ultra large scale integration.

V Voltage, Volt.

V<sub>dd</sub> Drain supply voltage.

VLSI Very large scale integration.

$V_{ss}$  Source supply voltage.

V<sub>T</sub> Threshold voltage of MOS device.

W MOSFET channel width.

W<sub>d</sub> Depletion layer width.

x Position coordinate.

XOR Exclusive-OR logic.

Z MOSFET channel width.

Z<sub>d</sub> Impendance.

$\alpha$  Hole generation efficiency, temperature coefficient of resistance.

$\beta$  Field acceleration factor.

$\Delta$  R.m.s. height of the fluctuation in the interface.

$\epsilon_0$ Permittivity of free space.  $\epsilon_{ox}$ Dielectric constant of SiO<sub>2</sub>.  $\epsilon_s$ Dielectric constant of Si.  $\mu$ Carrier mobility, micro (10<sup>-6</sup>).

$\sigma$  Trap capture cross section, standard deviation.

$\phi$  Electric flux.

$\Phi_{ms}$ ,  $\phi_{ms}$  Effective work-function difference between gate and substrate.

$\phi_{\rm F}$  Fermi potential in the bulk Si.

**E** Deformation potential.

$\rho$  Crystal density.

$au_{ms}$  Function time, relaxation time. Effective electron affinity.

$\Omega$  Ohm.

# **CONTENTS**

|         |                                                     | Page No.    |

|---------|-----------------------------------------------------|-------------|

| ACKNOW  | LEDGEMENTS                                          | (i)         |

| ABSTRAC | T                                                   | (ii)        |

| SYMBOLS | AND NOMENCLATURE                                    | (iii)       |

| CHAPTER | 1: INTRODUCTION                                     | 1           |

| 1.1     | Historical Background                               | 1           |

| 1.2     | Reliability and Quality Assurance                   |             |

|         | 1.2.1 Bathtub Curve                                 | 3           |

|         | 1.2.2 Screening                                     | 2<br>3<br>4 |

|         | 1.2.3 Accelerated Testing                           | 4           |

| 1.3     | Instabilities and Failure Mechanisms in MOS Devices |             |

| 1.4     | Study Synopsis                                      | 6           |

| 1.5     | References                                          | 7           |

| CHAPTER | 2: GATE OXIDE FAILURE MECHANISM                     | <b>AS</b> 8 |

| 2.1     | Introduction                                        | 8           |

| 2.2     | Physics of Silicon Dioxide                          | 8           |

|         | 2.2.1 Properties of SiO <sub>2</sub>                | 8           |

|         | 2.2.2 Atomic Structure                              | 9           |

|         | 2.2.3 Band Structure                                | 11          |

|         | 2.2.4 Defects in SiO <sub>2</sub>                   | 11          |

|         | 2.2.5 The Si-SiO <sub>2</sub> Interface             | 11          |

|         | 2.2.6 The Gate-SiO <sub>2</sub> Interface           | 13          |

| 2.3     | Dielectric Breakdown                                | 14          |

|         | 2.3.1 Phenomenology of Dielectric Breakdown         | 14          |

|         | 2.3.2 Time Dependent Dielectric Breakdown           | 16          |

|         | 2.3.2.1 The Acceleration of TDDB                    | 17          |

| 2.4     | Charge Trapping during Oxide Wearout                | 18          |

| 2.5     | Effects of Oxide Breakdown and GOS upon Circuits    | 19          |

| 2.6     | Summary                                             | 19          |

| 2.7     | References                                          | 19          |

| CHAPTER     | 3: EXPER               | IMENTAL APPARATUS AND                          |    |

|-------------|------------------------|------------------------------------------------|----|

|             | PROCE                  | DURE                                           | 24 |

| 3.1         | Experimental A         | pparatus                                       | 24 |

|             |                        | afer Chuck and Microprober System              | 24 |

|             |                        | ectrical Instruments                           | 25 |

|             |                        | 1.2.1 HP4145B Parametric Analyzer              | 25 |

|             |                        | 1.2.2 Programmable Voltage Source              | 26 |

|             |                        | 1.2.3 L-C-R Meter                              | 26 |

|             | 3.                     | 1.2.4 HP54111D Digital Oscilloscope            | 26 |

|             |                        | 1.2.5 TG102 Signal Generator                   | 27 |

| 3.2         | Test Samples           | Č                                              | 27 |

|             | 3.2.1 De               | evices on the Wafers                           | 27 |

|             | 3.2.2 Ch               | naracterization of Samples                     | 29 |

|             | 3.2                    | 2.2.1 C-V Curve Measurement                    | 29 |

|             | 3.2                    | 2.2.2 Extraction of Oxide Thickness            | 29 |

|             | 3.2                    | 2.2.3 The Measurement of Bulk Resistance       | 31 |

| 3.3         | <b>Experiments on</b>  | <b>MOS-C Structures and MOSFET Networks</b>    | 34 |

|             | 3.3.1 Int              | troduction                                     | 34 |

|             | 3.3.2 Fig              | eld Accelerated TDDB Life Test                 | 34 |

|             | 3.3.3 Te               | emperature Accelerated TDDB Life Test          | 35 |

|             | 3.3.4 Ex               | sperimental Results                            | 35 |

|             | 3.3                    | 3.4.1 Time-dependent Failure Distributions     | 35 |

|             | 3.3                    | 3.4.2 Injection Current                        | 37 |

| 3.4         | <b>Experiments on</b>  | nMOS Inverter                                  | 39 |

|             | 3.4.1 Ch               | naracterisation of the Pull-down Transistor    | 39 |

|             | 3.4.2 Ch               | naracterisation of the nMOS Inverter           | 40 |

|             | 3.4.3 Co               | onstant Voltage Stress on Gate Oxide of the    |    |

|             | Pu                     | ll-down Transistors                            | 41 |

|             | 3.4.4 Re               | c-characterisation of the Pull-down Transistor | 41 |

|             | 3.4.5 Re               | e-measurement of the Characteristics of the    |    |

| •           | Inv                    | verter                                         | 43 |

| 3.5         | <b>Experimental Co</b> | onclusions                                     | 43 |

| 3.6         | References             |                                                | 43 |

| CII A DYTED | A. ANIAT S7            | CIC OF THE EVENTERINGS OF A                    |    |

| CHAPTER     | 4: ANALY<br>RESUL      | SIS OF THE EXPERIMENTAL TS                     | 44 |

|             |                        |                                                |    |

| 4.1         | Introduction           |                                                | 44 |

| 4.2         | ~                      | Oxide Breakdown                                | 44 |

|             | 4.2.1 Int              |                                                | 44 |

|             |                        | e Mechanisms of Oxide Wearout                  | 45 |

|             |                        | 2.2.1 The Entry of Charges into Oxide          | 45 |

|             |                        | 2.2.2 Charge Trapping in Oxides                | 45 |

|             |                        | 2.2.3 Electric Field Change due to Trapped     |    |

|             | Ch                     | arges in Oxides                                | 48 |

|         | 4.2.2.4 The Breakdown                | n of Oxide             | 49 |

|---------|--------------------------------------|------------------------|----|

|         | 4.2.3 Mathematical Model             |                        | 49 |

|         | 4.2.3.1 Physical Mecha               | anisms                 | 49 |

|         | 4.2.3.2 Quantitative M               |                        | 51 |

|         | 4.2.3.3 Calculated Res               |                        | 53 |

| 4.3     | The Assessment of the MOS-C as A     | n Oxide-integrity      |    |

|         | Test Vehicle                         |                        | 54 |

| 4.4     | The Distributions of the Oxide Faile | ure                    | 57 |

| 4,5     | Degradation of Transconductivity o   | f MOSFET               | 59 |

|         | 4.5.1 The Important Scattering       |                        | 60 |

|         | 4.5.2 Scattering Rates and M         | <u> </u>               | 61 |

| 4.6     | References                           | ,                      | 62 |

| CHAPTER | 5: PSPICE SIMULATION                 |                        | 64 |

| 5.1     | Introduction                         |                        | 64 |

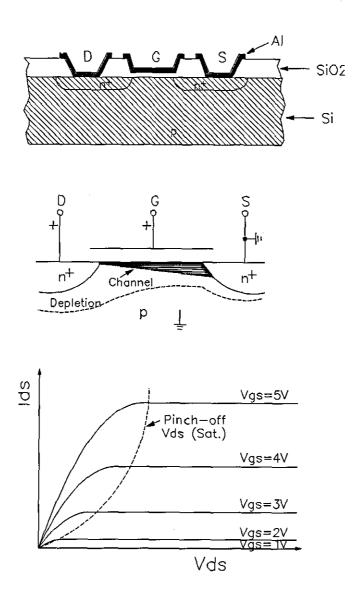

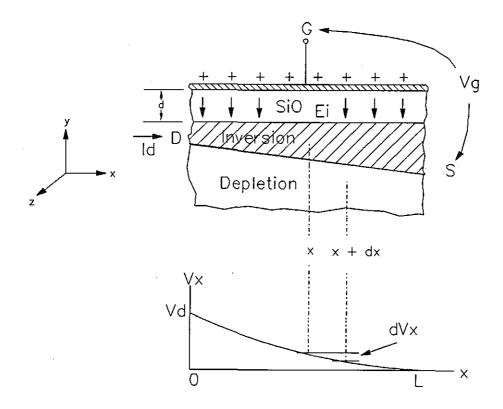

| 5.2     | MOSFET Theory                        |                        | 64 |

|         | 5.2.1 Introduction                   |                        | 64 |

|         | 5.2.2 Basic Operation of MO          | SFET                   | 64 |

|         | 5.2.3 A Mathematical Model           |                        | 66 |

|         | 5.2.3.1 Threshold Volt               |                        | 66 |

|         | 5.2.3.2 Drain Current                |                        | 67 |

|         | 5.2.3.3 Transconductan               | nce and Conductance in |    |

|         | MOSFET                               |                        | 69 |

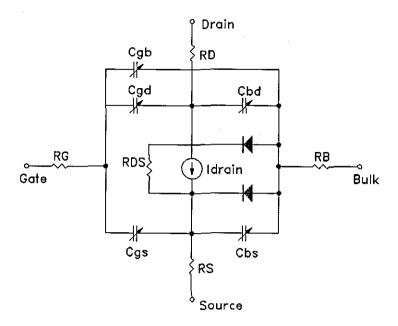

| 5.3     | MOSFET Models in PSPICE              |                        | 71 |

|         | 5.3.1 Introduction to PSPICE         | E Simulator            | 71 |

|         | 5.3.2 MOSFET Models                  |                        | 72 |

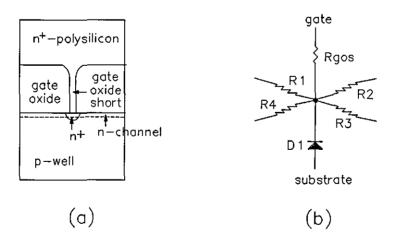

| 5.4     | Simulation Results for MOSFETs w     | ith GOS                | 75 |

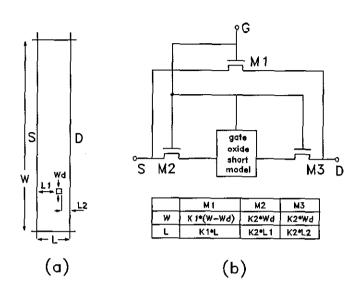

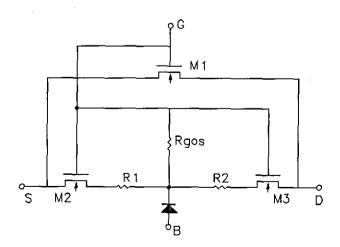

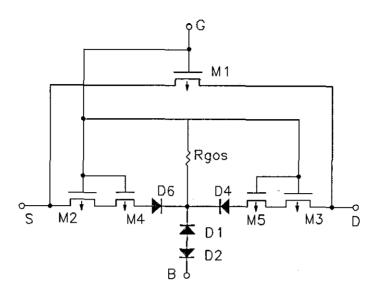

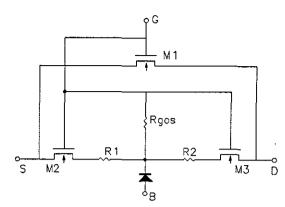

|         | 5.4.1 Models for MOSFETs             |                        | 75 |

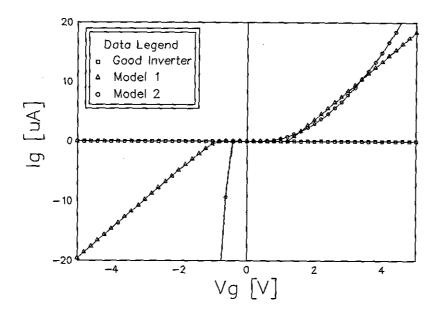

|         | 5.4.2 Simulation Results for         |                        | 78 |

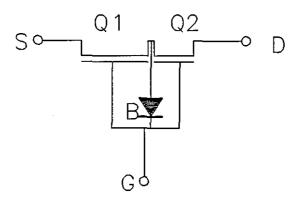

| 5.5     | Simulation Results of the nMOS Inv   |                        | 81 |

|         | 5.5.1 Introduction to Inverter       | · -                    | 81 |

|         | 5.5.2 Delay and Power                |                        | 81 |

|         | 5.5.3 Simulation Results of nl       | MOS Inverter           | 84 |

|         | 5.5.4 Conclusion                     |                        | 85 |

| 5.6     | Test Considerations of MOS circuits  | s with GOS             | 86 |

|         | 5.6.1 CMOS Inverter                  |                        | 86 |

|         | 5.6.2 NMOS Inverter                  |                        | 87 |

|         | 5.6.3 Other CMOS Logic Cir           | cuits                  | 88 |

|         | 5.6.4 Confusion                      |                        | 89 |

| 5.7     | References                           |                        | 89 |

|         | -                                    |                        | -  |

| CHAPTER | 6: CONCLUSIONS                       |                        | 91 |

| <b>APPENDIX:</b> | REPRODUCTIONS OF PUBLISHED         |     |

|------------------|------------------------------------|-----|

|                  | PAPERS                             | 93  |

| Paper I          | (Proc. 5th ESREF, 1994)            | 94  |

| Paper II         | (Proc. 5th ESREF, 1994)            | 99  |

| Paper III        | (Journal of Electroceramics, 1993) | 105 |

#### **CHAPTER 1**

# Introduction

# 1.1. Historical Background

The evolution of electronic technology has been so rapid that it is sometimes described as a revolution. It is not an exaggeration to say that most of the technological achievements of the past two decades have depended on microelectronics. Small and reliable sensing and control devices are essential elements in complex systems from spacecraft, communications satellites to handheld calculators and digital watches. Somewhat subtler, but perhaps eventually more significant, is the effect of microelectronics development upon the computer.

The earliest transistor design was patented in the United States and Canada by J.E.Lillenfeld in 1925 [1]. According to Lillenfeld's proposal, the current flowing in a copper sulphide channel between gold 'drain' and 'source' electrodes was controlled by a voltage applied to an aluminium 'gate' electrode. In 1928, Lillenfeld patented the earliest insulated gate field effect transistor (IGFET) design, in which the conductivity of a copper sulphide channel was controlled by the voltage on an isolated gate, separated from the channel by a layer of aluminium oxide [1,2]. The IGFET was also patented by Heil in Great Britain in 1935 [3]. These designs were the forerunners of the modern MESFET and MOSFET transistors. It is extremely doubtful, however, that any workable transistors were constructed at this time.

The first known operational transistor, a germanium bipolar device, was developed in 1947 by Shockley, Bardeen and Brattain [4,5]. By the late 1950's, small-scale bipolar integrated circuits (SSI) were manufactured, but these were limited by high power dissipation and complicated fabrication processes.

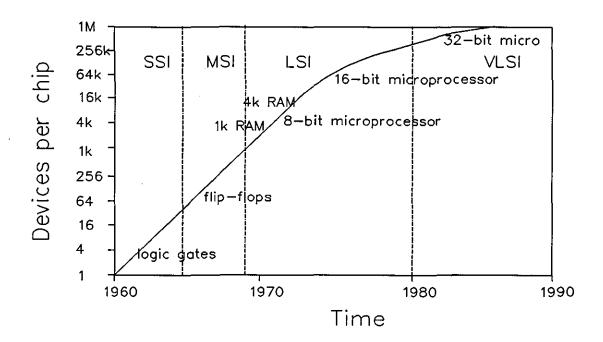

To overcome these problems, the manufacture of the conceptually simpler metaloxide-semiconductor (MOS) device was perfected in the mid 1960's, and it is this technology that has permitted the production of today's highly complex microprocessor and large capacity memory circuits. From the evolution of circuit complexity shown in Fig.1.1, it can be seen that to a first approximation the number of components per integrated circuit has been increasing exponentially - a phenomenon usually referred to as Moore's Law. Small-scale integration (SSI) was the state of art in the early 1960's when the circuits were built using bipolar technology. The introduction of MOS technology allowed circuits of medium-scale integration (MSI) to be produced in the mid to late 1960's and the large-scale integration (LSI) of circuits in the 1970's.

Very large scale integration (VLSI) followed in the 1980's, with the fabrication of 32 bit microprocessors and 256K RAMs. Such scales of integration can approach one million devices per chip [6].

Figure 1.1: Integrated circuit complexity as a function of time (Moore's law).

# 1.2 Reliability and Quality Assurance

This thesis is concerned with reliability and failure mechanisms in small-dimension

MOS devices. This section presents a general discussion of semiconductor reliability theory. The specific failure mechanisms associated with MOS devices are considered in Section 1.3.

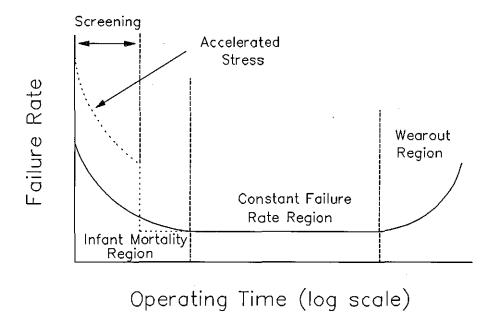

#### 1.2.1 Bathtub Curve

A well-known graphical reliability model, which has been universally accepted since the beginning of the reliability discipline is the 'bathtub' curve [8] shown in Fig.1.2. This curve has three distinct regions, each with its own unique characteristics. The first region with a rapidly decreasing failure rate from a high initial value represents 'infant mortality'. The second region, with almost a constant failure rate, extends well beyond the useful life of most components. The third region, marked by a steep rise in failure rate, is the final 'wearout' period.

Figure 1.2: The bathtub curve.

The initial high failure rates in the infant mortality region arise from the fact that a small fraction of the population is inherently defective (weak) and fails in a very short

period of time. Most of the weak devices fail during this period. The region of constant (or nearly constant) failure-rate corresponds to normal operation of electronic equipment. Eventually, the ICs begin to fail at a rapid rate as a result of intrinsic failure mechanisms such as dielectric breakdown or electromigration.

#### 1.2.2 Screening

In principle, *screening* is a process of eliminating defective components from the production batch. Reliability screening requires acceleration of the mechanisms that give rise to infant mortality. The aim of the screening process is to accelerate the failure rate for a limited period of time, such that the surviving population would begin its effective operational life within the middle steady region of the bathtub curve as shown in Fig.1.2.

Temperature, bias or a combination of the two are often used to accelerate failures within the screening period. The most commonly used screening procedure is burn-in, which combines the effects of voltage and temperature. The ICs with weak oxides, defective metallization, and contamination are typically eliminated by this screen.

## 1.2.3 Accelerated Testing

Failure rates in today's VLSI circuits tend to be so low in normal operation that it takes many years for the steep rise in failure rates due to wearout to begin. However, systems manufacturers require an assurance that the component failure rates remain low and steady over the intended operating life of the equipment. Therefore, it is an industry-wide practice to test ICs under conditions that accelerate wearout in order to provide statistically sufficient data and meaningful estimates of failure rates in an economically reasonable period of time. From the test results, acceleration factors (AF) and activation energies (E<sub>a</sub>) are derived which permit the estimation of failure rates under any set of conditions of operation in the field.

Temperature, voltage, humidity, mechanical shocks and vibrations and radiation are amongst the types of stresses used to accelerate failures. Since the accelerated testing of IC's tends to be destructive, tests have to be performed on a small representative sample size drawn from the total population.

Interpretation of the test results requires an understanding of the accelerating effects of the applied stresses. Since the main purpose of these tests is to quantify all the possible known failure mechanisms under accelerated-stress conditions, an accurate model is necessary in order to extrapolate these mechanisms to normal operating conditions.

#### 1.3 Instabilities and Failure Mechanisms in MOS Devices

Although in 1960, MOS devices with good characteristics were demonstrated, they did not become commercially reliable until the end of the decade. This was because the early devices were plagued with instability problems arising from charges in the oxide or at the semiconductor interface, e.g. ionic contamination, dipole polarization and carrier injection into the oxides.

Oxides can become contaminated by processing and handling. The environment, materials, machines, and operators are the main sources of contamination. In MOSFETs, the effect of ionic contamination is manifested as a drift in the strong-inversion threshold voltage, although this is usually negligible in the state-of-the-art technology.

The phosphosilicate glass (PSG) that immobilizes sodium ions can have a destabilizing effect on active devices because of its polarizability. These dipoles create image charges that can invert the silicon surface and produce effects on devices similar to those by mobile ions, however, the effects of dipole polarization are much less pronounced than those of mobile ions [8].

In order to meet the demands of increased packing density, the feature sizes are continuously being scaled down. With decreasing MOSFET dimensions, the ICs are becoming increasingly susceptible to drift as a result of the injection of carriers. Electrons and holes can enter the oxide by either tunnelling through or by surmounting the barrier. These injected carriers, when trapped in the oxide, are capable of changing the I-V characteristics of MOSFET. Meanwhile, latchup is a key concern to CMOS circuits. It stems from parasitic bipolar transistors, which are structurally inherent to bulk CMOS [9]. As CMOS technologies are scaled down, the protection against latchup will become more difficult.

Although metal electromigration, packaging and interconnections are among the

common failure mechanisms in MOS circuits, oxide breakdown is a great threat to MOS VLSI circuits and has been a subject of research since the mid 1920's [10]. Numerous theories have been proposed, however, no consensus has ever been reached concerning the physical mechanisms involved [11].

The effects of oxide breakdown upon circuits are also concerned by many researchers. Latent failure is a great threaten to reliability, moreover, 'gate oxide shorts (GOS)', i.e. short circuit paths across the insulator [12] can cause distortion of the transistor I/V characteristics and/or loss of transistor action [13].

## 1.4 Study Synopsis

The aims of this study are twofold: (i) develop a physical model to explain the experimental data and understand the oxide breakdown mechanism; (ii) examine the effects of Gate Oxide Shorts upon devices and circuits and try to find a way to detect them.

The remainder of thesis is divided into the following five chapters.

- Chapter 2 outlines the properties of SiO<sub>2</sub>, introduces oxide breakdown mechanism with emphasis on time-dependent dielectric breakdown.

- Chapter 3 describes the apparatus and test samples used for the experimental work, together with the experimental procedures and results.

- Chapter 4 develops a mathematical model based on the charge trapping mechanism in order to understand the physical mechanisms behind the experimental results, analyzes the main results from Chapter 3.

- Chapter 5 focuses on the changes in the device characteristics and circuits after gate oxide breakdown, compares two different GOS equivalent circuits using PSPICE simulator and validates techniques for the detection of GOS in MOS digital circuits.

- Chapter 6 draws conclusions from the results of the thesis.

# 1.5 References

- [1] Gosling, W., Townsend, W.G., Watson, J., "Field-Effect Electronics", Butterworth, London, 1971.

- [2] Lillenfeld, J.E., U.S. Patent No. 1745175, 1930.

- [3] Heil,O, British Patent No.439137, 1935.

- [4] Bardeen, J, Brattain, W.H., "The Transistor, A Semiconducting Triode", Physical Review, 74, p.230, 1948.

- [5] Shockley, W, "The Theory of p-n Junctions in Semiconductors and p-n Transistors", Physical Review, 80, p.467, 1950.

- [6] Russell, G, Kinniment, D.J., Chester, E.G., McLauchlan, M.R., "Chapter 2: Technology and Design", CAD for VLSI, Van Nostrand Reinhold (UK) Co. Ltd. 1985.

- [7] Forester, T, "The Microelectronics Revolution", Basil Blackwell, Oxford, 1980.

- [8] Sabnis, A.G., "VLSI Reliability", Academic Press, Inc., 1990.

- [9] Troutman, R.R., "Latchup in CMOS Technology: The Problem and Its Cure", Kluwer Academic Publishers, 1986.

- [10] Amerasekera, E.A., "Failure Mechanisms in MOS Devices", Ph.D Thesis, 1986.

- [11] Tunnicliffe, M.J., Dwyer, V.M., "Monitoring the Integrity of MOS Gate Oxides: A Preliminary Study", International Journal of Electronics, 1993.

- [12] Soden, J.M., Hawkins, C.F., "Test Considerations for Gate Oxide Shorts in CMOS ICs", IEEE Design and Test, August, pp.56-64, 1986.

- [13] Tunnicliffe, M.J., Dwyer, V.M., Campbell, D.S., "Parametric Drift in Electrostatically Damaged MOS Transistors", Proc. 14th Electrical Overstress/Electrostatic Discharge Symposium, Dallas, Texas, pp.112-120, 1992.

#### **CHAPTER 2**

# **MOS Gate Oxide Failure Mechanisms**

#### 2.1 Introduction

Silicon dioxide plays vital roles in MOS integrated circuits: firstly as a 'passivating' layer and secondly as the MOSFET gate dielectric. The quality of the gate oxide is a crucial factor in determining the performance of an MOS transistor. MOS ICs depend upon the dielectric integrity of thin oxide layers for the high input impedance of MOSFETs and the charge storage ability of MOS capacitors.

Oxide breakdown is probably the most widely recognized failure mechanism in MOS VLSI circuits and has indeed become a serious reliability problem in electronic equipment. The breakdown strength of gate oxide layers usually varies between 7 and 14MV/cm [1,2] depending on stress conditions and method of preparation. An understanding of the silicon dioxide breakdown behaviour is extremely important for prediction and estimation of IC failure rates in field operation.

Charge generation and trapping in SiO<sub>2</sub> has long been suspected to be responsible for the time-dependent dielectric breakdown of MOS structures. Degradation of MOSFETs by trapped electrons and/or holes in the SiO<sub>2</sub> films is the most serious technical problem in assurance of reliability in Si VLSI circuits. It is therefore extremely important to investigate the charge trapping and trap generation mechanisms.

# 2.2 Physics of Silicon Dioxide

# 2.2.1 Properties of Silicon Dioxide

SiO<sub>2</sub> or 'silica' is the native oxide of crystalline silicon. It grows rapidly on clean

silicon surfaces to a depth of about 2nm on exposure to room temperature air. Since such thin layers have little practical use, thicker oxides are grown at about  $1000^{\circ}$ C in oxidation furnaces over periods of time between 15 minutes to 2 hours [3]. The oxidising ambient can be pure  $O_2$  for 'dry' oxides or steam for 'wet' oxides, the wet oxide having a considerably faster growth rate at the expense of electrical stability. Since electrical stability of the passivation is not normally of paramount importance, and since it is usually thick (of the order of  $1\mu$ m), 'wet' oxides are generally used for this application [3].

Although thermally grown SiO<sub>2</sub> is the best known material for a gate insulator, its properties are far from perfect. 'Dry' oxidation is usually used, as the gate oxide integrity and stability is of importance to the circuit performance and reliability [3]. Strategies have been developed to improve the electrical properties of gate oxides, including the addition of HCL in the oxidising ambient [4] and the deposition of an additional yttrium oxide or silicon nitride dielectric layer [5,6]. The techniques used to grow (or deposit) such layers on silicon substrates have been extensively reviewed by S. Rigo in ref. [7].

#### 2.2.2 Atomic Structure

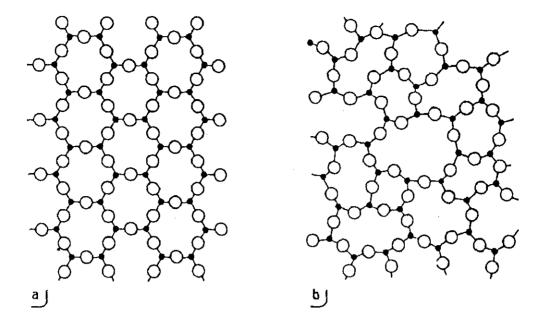

Although thermally grown SiO<sub>2</sub> is chemically identical to crystalline quartz (see Fig.2.1(a)), its atomic structure is vitreous, containing a high degree of short-range order and chemical homogeneity but without any long-range organization (Fig.2.1(b)).

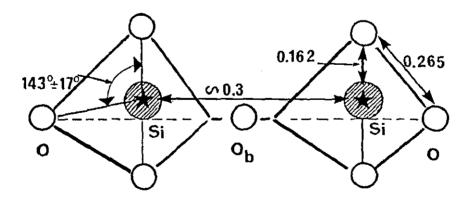

In the classical model of vitreous silica, the SiO<sub>4</sub> tetrahedra are linked via bridging O atoms to form a continuous network of Si-O-Si bonds. Bond angles and interatomic distances are shown in Fig.2.2.

Figure 2.1: Two-dimensional representation of:

a) the lattice of 'perfect' quartz, b) the network of 'perfect' vitreous silica (black dots represent Si atoms, circles represent O atoms) [7].

Figure 2.2: Typical dimension of the SiO<sub>4</sub> tetrahedra of vitreous silica. Dimensions are in nm, angles in degree [7].

#### 2.2.3 The Band Structure of Vitreous Silica

Despite the lack of long-range order, vitreous silica has sufficient short-range regularity to diffract the electron wave functions into a valance and a conduction band. Optical absorption measurements performed on vitreous silica show that a band gap exists, which depends on the degree of perfection of the oxide network: the band gap is found to decrease when disorder increases. The most commonly measured  $E_G$  value for vitreous silica is 8.1eV, which agrees well with computed values based on one-dimensional theoretical models [7].

#### 2.2.4 The Defects in Silica

Defects in silica can be classified into three categories: *point defects* which exist at single atomic sites, *complex defects* which are clusters of point defects, and *microheterogenities* which are devitrified regions in an otherwise non-crystalline oxide [7].

The presence of defects leads to a loss of the translational symmetry of the network and thus introduces supplementary energy levels. These levels may be located in the conduction band, and/or in the valence band, and/or in the band gap. Only those levels introduced in the band gap are of interest for instability phenomena [7].

A fundamental level  $E_T$  associated with a defect can be computed theoretically [7], and the ionization energy of the defect  $E_I$  (defined as  $E_I = E_C - E_T$ ) can be measured by IR absorption or by thermally-stimulated conductivity measurements for shallow levels [7].

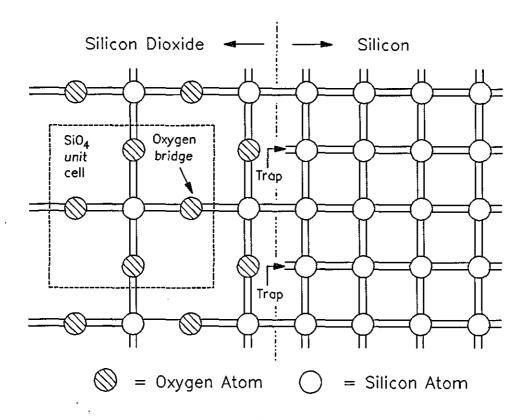

# 2.2.5 The Si-SiO<sub>2</sub> Defects

A cleaved Si crystal has a high density of surface trap states introduced by incomplete or 'dangling' orbitals. These behave as interband surface states or traps and have the same areal density as the surface atoms (i.e.  $\sim 10^{15}$  traps/cm<sup>2</sup>). Although a thermally grown SiO<sub>2</sub> layer passivates the surface, completing most of the surface orbitals, the periodic mismatch between the Si and SiO<sub>2</sub> networks implies that some Si bonds remain incomplete as shown in Fig.2.3.

Figure 2.3: Schematic two-dimensional representation of Si-SiO<sub>2</sub> interface.

Stretched, twisted and dangling bonds do indeed appear on passivated Si-SiO<sub>2</sub> interfaces, introducing an 'interface' trap density of the order of  $10^{12}$  traps/cm<sup>2</sup> [8]. Extrinsic defects associated with ionic contaminants can also exist [9] and although both donor and acceptor species exist at the interface, the donors are more numerous and the net surface charge is positive [10]. Hence the extrinsic surface state charge can be modelled by a positive charge density  $Q_{ss}$  (C/cm<sup>2</sup>).

Interface state density is affected by the type and density of Si dopants, boron giving a higher trap density than phosphorus or arsenic due to an introduced oxygen deficiency [10]. Interface states can sometimes be annealed away by post-oxidation low-temperature thermal processing [10], although this can sometimes increase rather than decrease the defect density [11,12]. This is in some cases due to void formation under the deoxidation reaction (Si + SiO<sub>2</sub>  $\rightarrow$  2SiO↑) across the Si-SiO<sub>2</sub> interface. It can be prevented by

increasing the  $O_2$  content of the annealing ambient, thereby causing compensatory reoxidisation [13]. Interface traps are also generated under electric field stress, although these may have slightly different properties from those of the pre-existing defects [14].

The charged interface states, together with unoxidised Si<sup>+</sup> ions, present a charge storage capacity at the interface, which can be detected using charge-pumping analysis [15], a.c. conductance measurements [16] or deep-level transient spectroscopy [17]. Carriers in MOSFET channel could enter the trap sites in oxide through a tunnelling mechanism, causing 1/f fluctuations in the channel conductance, and therefore the density of interface traps can be measured using a 1/f noise model [18].

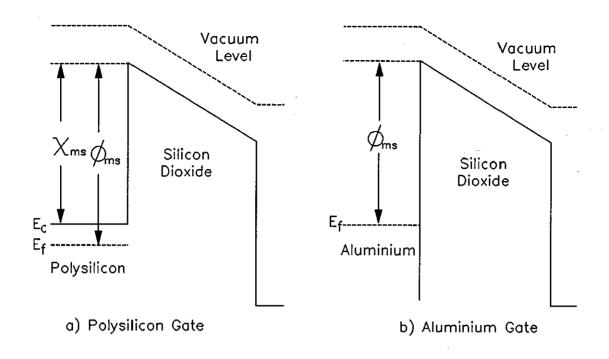

# 2.2.6 The Gate-SiO<sub>2</sub> Interface

The most common materials used for gate fabrication are aluminium and polysilicon (polycrystalline silicon). Both materials are applied to the  $SiO_2$  by vapour deposition, and exhibit a polycrystalline structure. The polysilicon/ $SiO_2$  junction can be considered to display similar properties to the thermal  $Si/SiO_2$  interface. The energy barrier between the polysilicon gate and the  $SiO_2$  can be characterised in terms of the effective work function  $\phi_{ms}$ , i.e. the potential difference between the silicon Fermi-level and the oxide conduction band. Alternatively the effective electron affinity  $\chi_{ms}$ , i.e. the potential difference between the oxide and silicon conduction band edges can be used. Both parameters, shown schematically in Fig.2.4, can be measured using the internal photoemission technique [10,19]. The  $Si-SiO_2$  interface appears to have a  $\phi_{ms}$  of approximately 3.15eV, a value which varies slightly with the Si crystal orientation [10]. If the gate material is metallic, the effective electron affinity is meaningless since the conduction band edge bears little relation to the energy of cathode electrons. The effective work function is therefore the only meaningful parameter, equalling 4.1eV for an aluminium gate material.

Figure 2.4: Energy band diagrams for poly-Si/SiO<sub>2</sub> and Al/SiO<sub>2</sub> MOS structures.

#### 2.3 Dielectric Breakdown

# 2.3.1 Phenomenology of Dielectric Breakdown

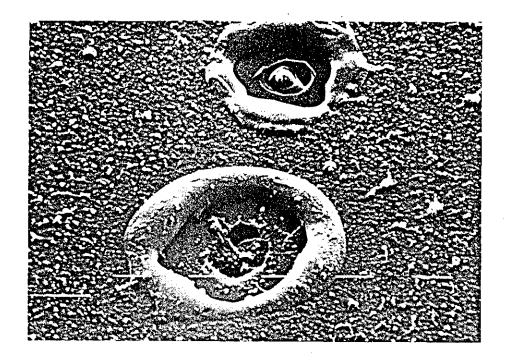

The breakdown of thin silica films is usually studied through electrical tests performed on capacitor-like structures. At breakdown, a large localised current flows in the dielectric, melting a region of gate material and producing a visible crater (see Fig.2.5). The breakdown site can be located by electron microscopy [20,21] or by electroluminescence under current injection [22]. If the gate electrode is thin then the heat dissipated by breakdown may evaporate the gate material in the vicinity of the crater, isolating the defect and *self healing* the oxide [20]. However, either the molten gate material or an air discharge may form a conduction path between the gate and the underlying silicon, sustaining the breakdown current and causing damage propagation across the gate area [20]. Alternatively the current path across the oxide may fuse under

further stress, providing another mechanism for self healing [23].

Figure 2.5: A SEM photograph of two breakdown spots. The polysilicon electrode has melted away over  $\sim 20\mu\text{m}^2$ . The polysilicon is spread over a large area in the form of dust and little globules. The size of a dash is  $1\mu\text{m}$ .

Although the definitions of what constitutes a damaged oxide varies in the literature, a typical example is a leakage current of  $10\mu$ A at 5V bias [24]. However, the rapid resistivity change at breakdown (typically from  $1000G\Omega$  to  $1K\Omega$  in less than  $1\mu$ s) appears to render the exact definition somewhat unimportant. Some recent experiments on ultrathin  $SiO_2$  (about 55Å) show that nondestructive multiple breakdown events can occur prior to final breakdown as the oxide switches between these high and low conductance levels [25]. Later studies have uncovered the existence of multiple conduction levels in the oxide, between which the dielectric may switch prior to breakdown [26,27].

# 2.3.2 Time Dependent Dielectric Breakdown (TDDB)

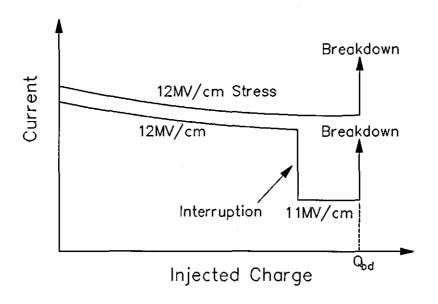

The present consensus maintains that SiO<sub>2</sub> wearout is driven by Fowler-Nordheim tunnelling injection of electrons from the cathode into the dielectric. Such wearout tends to be characterised either by the time-to-breakdown t<sub>bd</sub> or by the charge Q<sub>bd</sub> injected prior to breakdown. Fig.2.6 illustrates the causal nature of wearout. It shows the Fowler-Nordheim current J plotted against the injected charge Q for two oxides, one stressed at a continuous 12MV/cm, the other stressed first at 12MV/cm and then at 11MV/cm after an indefinite interruption. Clearly only a small additional charge is required to push the oxide into breakdown at 11MV/cm after the injection it has already sustained. This is called time-dependent dielectric breakdown (TDDB).

Figure 2.6: Illustration of time-dependent dielectric wearout (after Wolters et al. [28]).

Time-dependent dielectric breakdown (TDDB) is judged to be a potential failure mode for MOS integrated circuits and has received considerable attention [29-37]. Early investigations centred around the effects of mobile ions on enhanced conduction via ionic drift to the Si-SiO<sub>2</sub> interface [31,32], or on the effects of radiation damage on dielectric breakdown [33,34]. More recently, with improved processing, oxides have become

relatively free from both Na<sup>+</sup> contamination and radiation damage; thus TDDB attention has turned to intrinsic breakdown [30, 35]. The occurrences of TDDB, experimentally observed on test capacitors and actual memory devices, appear to be lognormally distributed (i.e. with the logarithm of time) [30] or to follow a Weibull distribution [36,37].

#### 2.3.2.1 The Acceleration of Time-dependent Dielectric Breakdown

The occurrences of TDDB can be accelerated thermally and electrically. The temperature dependence has been found to follow the Arrhenius relationship, i.e.

$$t_{bd}(T) \propto \exp\left(\frac{E_{tbd}}{kT}\right)$$

(2.1)

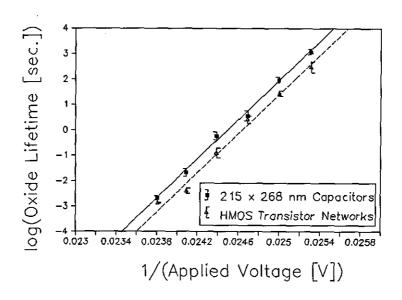

where  $t_{bd}$  is the time-to-breakdown,  $E_{tbd}$  is an activation energies, although a wide range of values has been reported [30,38-41]. The field dependence of TDDB follows the equation

$$t_{bd} \propto \exp\left(\frac{G}{F_{cr}}\right)$$

(2.2)

where G is a constant and  $F_{ox}$  is the oxide electric field. In order to characterize or project the lifetime of oxides, the concept of 'Electric-field acceleration factor'  $\beta$  is widely used.  $\beta$  is defined as:

$$\beta = \frac{dlog(t_{bd})}{dF_{ox}} \tag{2.3}$$

Using the acceleration factor  $\beta$ , oxide life time under normal (low-field) operation conditions would be extrapolated from the high-field acceleration test data. However,

again, many  $\beta$  values have been reported in the literature, varying from 7 to 1.5 decade/MV/cm [30,42,43].

# 2.4 Charge Trapping during the Oxide Wearout

Any defect in the SiO<sub>2</sub> which introduces an energy level in the band gap can act as a carrier trap. The current decay evident in Fig.2.6 may indicate electron trapping, making the oxide more negative and reducing the cathode field which supports tunnelling. Current increase has also been observed [31,44,45], possibly caused by mobile positive ions drifting towards the cathode or by hole trapping increasing the cathode field.

Charge trapping in thermally grown SiO<sub>2</sub> on silicon has been studied extensively [45-52]. Both electron and hole trapping have been observed experimentally [45,49-51]. Electron trapping depends on current density (therefore the field) [50], temperature [46,52], thickness of the oxide [46], and the conditions of oxidation process [46,49].

Traps in SiO<sub>2</sub> can be classified by the following three types with respect to their origin: (1) extrinsic trap states related to impurities such as sodium and heavy metals, (2) semi-intrinsic trap states generated by water- or hydrogen-related species, (3) intrinsic trap states induced by Si-Si stretched bonds or oxygen vacancies in SiO<sub>2</sub>. The first type of trap states can be neglected in modern oxidation processing, although the second and third types remain important.

Both electron and hole trapping have been observed experimentally [45,49-51]. It has been suggested that the generation of electron traps during high-field stress may occur at either the gate-SiO<sub>2</sub> or the SiO<sub>2</sub>-bulk Si interfaces, depending on the polarity of the stress [51], Other workers suggest that the negative charges in oxide are distributed more or less uniformly and that the positive charges are located near the Si-SiO<sub>2</sub> interface [45,49]. Although ultra-dry oxide films have a very small density of electron traps (less than  $10^{11}/\text{cm}^2$ ), they have twice as many hole traps as wet oxide films [49]. Electron trapping and hole trapping are strongly dependent on the stressing conditions and a wide range of trap cross sections have been reported.

## 2.5 Effects of Oxide Breakdown and GOS upon Circuits

Amerasekera et al. [53] experimentally studied the characteristic changes of n-channel MOSFET after ESD pulse. Both parametric degradation and catastrophic failure were observed. Greason et al. [54] showed experimental evidence of latent failure on devices after the gate oxide was subjected to ESD stress, thermal shock or exposed to ultraviolet light, and concluded that latent failure are mainly related to the instability of the silicon-silicon dioxide system in MOS devices and charge trapping appears to be a key factor in the phenomenon. Tunnicliffe et al. [55] found that the threshold voltage  $V_T$  and transconductance  $g_m$  of the MOSFET drifted before the catastrophic failure, showed the effects of a 'walking-wounded' MOSFET upon the circuitry characteristics of CMOS inverter.

Gate oxide failure and their resulting shorts greatly affect MOS IC reliability. Gate oxide defects usually cannot be detected by stuck-at fault model test sets. In CMOS circuits, this problem can be solved by accompanying the each test vector with an  $I_{DD}$  measurement [56].

# 2.6 Summary

Although numerous theories have been proposed to explain oxide breakdown, no consensus has ever been reached concerning the physical mechanisms involved. New experiments are needed to further study the physical mechanisms of oxide breakdown.

Test for the gate oxide failure in CMOS ICs has been proposed, however, it is not effective universally. Alternative ways are needed.

#### 2.7 References

- [1] Scatterfield, H.W., Werber, R.F., "Statistical and Graphical Analysis of Oxide Thickness and ESD Failure Modes", Proc. 9th. EOS/ESD Symp., pp.258-264, 1987.

- [2] Osburn, C.M., Ormond, D.W., "Dielectric Breakdown in Silicon Dioxide Films, Part II: Influence

- of Processing and Materials", J. Electrochem. Soc., 119(5), pp.597-603, 1972.

- [3] Davis, J.R., "Instabilities in MOS Devices", Electrocomponent Science Monographs Volume 1, Gordon and Breach, New York, 1981.

- [4] Hamasaki, M, "Effect of Adding HCL to the Oxidizing Ambient on Characteristics of Metal-Oxide-Semiconductor Capacitors", J. Appl. Phys., 52(5), pp.3484-3490, 1981.

- [5] Manchanda, L, Gurvitch, M, "Yttrium Oxide/Silicon Dioxide: A New Dielectric Structure for VLSI/ULSI Circuits", IEEE Electron Dev. Lett., 9(4), pp.180-182, 1988.

- [6] Moslehi, M.M., Saraswat, K.C., "Thermal Nitridation of Si and SiO<sub>2</sub> for VLSI", IEEE Trans. Electron Dev., ED32(2), pp.106-123, 1985.

- [7] Barbottin, G, Vapaille, A, "Instabilities in Silicon Devices", Vol. I, Elsevier Science Publishers B.V., 1986.

- [8] Goetzberger, A, Klausmann, E, Schulz, M.J., "Interface States on Semiconductor/Insulator Surfaces", CRC Critical Reviews in Solid State Science, 6, pp.1-43, 1976.

- [9] Rosencher, E, Coppard, R, "Transient Capacitance Spectroscopy of Na<sup>+</sup>-Induced Surface States at the Si/SiO<sub>2</sub> Interface", J. Appl. Phys., 55(4), pp.971-979, 1984.

- [10] Verwey, J.F., Amerasekera, E.A., Bisschop, J, "The Physics of SiO<sub>2</sub> Layers", Rep. Prog. Phys., 53, pp.1297-1331, 1990.

- [11] Reed,M,L., Plummer,J.D., "Si-SiO<sub>2</sub> Interface Trap Production by Low-Temperature Thermal Processing" Appl. Phys. Lett., **51**(7), pp.514-516, 1987.

- [12] Burte, E.P., Matthies, P, "Time-Resolved Thermal Annealing of Interface Traps in Aluminium Gate

Silicon Oxide Silicon Devices", IEEE Trans. Nuc. Sci., NS35(5), pp.1113-1120, 1988.

- [13] Hofmann, K, Rubloff, G.W., Liehr, M, Young, D.R., "High Temperature Reaction and Defect Chemistry at the Si/SiO<sub>2</sub> Interface", Appl. Surf. Sci., 30, pp.25-31, 1987.

- [14] Vuillaume, D, Goguenheim, D, Bourgoin, J.C., "Nature of the Defects Generated by Electric Field Stress at the Si-SiO<sub>2</sub> Interface", Appl. Phys. Lett., 55(5), pp.490-492, 1991.

- [15] Elliot, A.B., "The Use of Charge Pumping Currents to Measure Surface State Densities in MOS Transistors", Sol. State Electron, 19, pp.241-247, 1976.

- [16] Noras, J.M., "Parameter Estimation in MOS Conductance Studies", Sol. State Electron, 31(5), pp.981-987, 1988.

- [17] Bauza, D, Morfouli, P, Pananakakis, G, "Detection of Interface and Volume Traps in Very Thin Oxide MOS Structures using DLTS, Quazi-Static and Conductance Measurements", Sol. State Electron, 43(9), pp.933-936, 1991.

- [18] Celik-Butler, Z, Hsiang, T.Y., "Determination of Si-SiO<sub>2</sub> Interface Trap Density by 1/f Noise Measurements", IEEE Trans. Electron Dev., ED35(10), pp.1651-1655, 1988.

- [19] Williams, R, "Photoemission of Electrons from Silicon into Silicon Dioxide". Phys. Rev., 140(2A), pp. A569-575, 1965.

- [20] Klein, N, Gafni, H, "The Maximum Dielectric Strength of Thin Silicon Oxide Films", IEEE Trans.

- Electron Dev., ED12(12), pp.281-289, 1966.

- [21] Klein, N, "Switching and Breakdown in Films", Thin Solid Films, 7, pp.149-177, 1971.

- [22] Hansel, G, Villareal, E, "Cost Effective Failure Analysis Method for Detection Failure Site Associated with Extremely Small Leakage", Proc. 9th, EOS/ESD Symp., pp.71-77, 1987.

- [23] Taylor, R.G., Woodhouse, J., "Junction Degradation and Dielectric Shorting: Two Mechanisms for ESD Recovery", Proc. 8th. EOS/ESD Symp., pp.92-99, 1986.

- [24] Amerasekera, E.A., Campbell, D.S., "Charge Limited Breakdown in MOS Capacitors", Proc. 17th. Annual Solid State Device Research Conference, pp.733-741, 1987.

- [25] Neri,B, Olivo,P, Riccò, "Low-frequency Noise in Silicon-gate Metal-Oxide-Silicon Capacitors Before Oxide Breakdown", Appl. Phys. Lett., 51(25), pp.2167-2169, 1987.

- [26] Suñè, J, Farrès, E, Placencia, I, Barniol, N, Martín, F, Aymerich, X, "Nondestructive Multiple Breakdown Events in Very Thin SiO<sub>2</sub> Films", Appl. Phys. Lett., 55(2), pp.128-130, 1989.

- [27] Saletti, R, Neri, B, Olivo, P, Modelli, A, "Correlated Fluctuations and Noise Spectra of Tunnelling and Substrate Currents Before Breakdown in Thin-Oxide MOS Devices", IEEE Trans. Electron Dev., ED37(11), pp.2411-2413, 1990.

- [28] Hamano, K, "Breakdown Characteristics in Thin SiO<sub>2</sub> Film", Jap. J. Appl. Phys., 13(7), pp.1085-1092, 1974.

- [29] Wood, M.H., Euzent, B.L., "Reliability in MOS Integrated Circuits", IEDM Tech. Dig., p.50, 1984.

- [30] Crook,D,L, "Method of Determining Reliability Screens for Time Dependent dielectric Breakdown", Proc. Int. Reliability Phys. Symp., pp.1-7, 1979.

- [31] Raider, S.I., "Time Dependent Breakdown of SiO<sub>2</sub> Films", Appl. Phys. Lett., 23(15), pp.34-36, 1973.

- Osburn, C.M., Ormond, D.W., "Na-induced Barrier Height Lowering and Dielectric Breakdown in SiO<sub>2</sub> Films on Silicon", J. Electrochem Soc., 121, pp.1195-1198, 1974.

- [33] Li,S.P., Maserjian,J, "Electron Radiation Effects on Time Dependent Dielectric Breakdown in SiO<sub>2</sub> Films", Solid State Electronics, 18, pp.287-288, 1975.

- [34] Li,S.P., "Ion Implantation Effect on Time Dependent Breakdown in SiO<sub>2</sub>", J. Appl. Phys., 46, pp.4833-4834, 1975.

- [35] Anolick, E.S., Nelson, G.R., "Low Field Time Dependent Dielectric Integrity", Proc. 17th Annual IEEE Rel. Phys. Symp., pp.8-12, 1979.

- [36] Vollertsen, R., P., "Statistical Modelling of Time Dependent Oxide Breakdown Distributions", Microelectronics Reliab., 33(11), pp.1665-1677, 1993.

- [37] Tunnicliffe, M.J., Dong, L., Dwyer, V.M., "Monitoring the Integrity of MOS Gate Oxides", Int. Electroceramics, 1993.

- [38] Baglee, D.A., "Characteristics and Reliability of 100Å Oxides", Proc. Int. Reliability Phys. Symp., pp.152-155, 1984.

- [39] Yamabe, K, Taniguchi, K, "Time-dependent Dielectric Breakdown of Thin Thermal Grown SiO<sub>2</sub> Films", IEEE Trans. Electron Devices, ED-32(2), pp.423-428, 1985.

- [40] Chen, C.F., Wu, C.Y., Lee, M.K., Chen, C.N., "The Dielectric Reliability of Intrinsic Thin SiO<sub>2</sub> Films Thermally Grown on a Heavily Doped Si Substrate-Characterization and Modeling", IEEE Trans. Electron Devices, **ED-34(07)**, pp.1540-1552, 1987.

- [41] Hokari, Y, Baba, T, Kawamura, N, "Reliability of 6-10nm Thermal SiO<sub>2</sub> Films Showing Intrinsic Dielectric Integrity", IEEE Trans. Electron Devices, ED-32(11), pp.2485-2491, 1985.

- [42] Hirayama, M, Matsukawaa, T, Tsubouchi, N, Nakata, H, "Time Dependent Dielectric Breakdown Measurement of High Pressure Low Temperature Oxidized Film", Proc. Int. Reliability Phys. Symp., pp.146-151, 1984.

- [43] McPherson, J.W., Baglee, D.A., "Acceleration Factors for Thin Gate Oxide Stressing", Proc. Int. Reliability Phys. Symp., pp.1-5.

- [44] Osburn, C.M., Weitzman, E.J., "Electrical Conduction and Dielectric Breakdown in Silicon Dioxide Films on Silicon", J. Electrochem Soc., 119, pp.603-609, 1972.

- [45] Jeno, C.S., Ranganath, T.R., Huang, C.H., Jones, H.S., Chang, T.L., "High-field Generation of Electron Traps and Charge Trapping in Ultra-thin SiO<sub>2</sub>", IEDM Tech. Digest, pp.388-391, 1981.

- [46] Young, D.R., Irene, E.A., DiMaria, D.J., De Keersmaecker, R.F., "Electron Trapping in SiO<sub>2</sub> at 295 and 77°K", J. Appl. Phys., **50**(10), pp.6366-6372, 1979.

- [47] Dutoit, M, Fazan, P, Benjelloun, A, Ilegems, M, "Charge Trapping and Breakdown in Thin SiO<sub>2</sub> Polysilicon-gate MOS Capacitors", Appl. Surface Science, 30, pp.333-338, 1987.

- [48] Liang, M-S, Hu, C, "Electron Trapping in Very Thin Thermal Silicon Dioxides", IEDM, pp. 396-399, 1981.

- [49] Miki, H, Noguchi, M, Yokogawa, K, Kim, B-W, Asada, K, Sugano, T, "Electron and Hole Traps in SiO<sub>2</sub> Films Thermally Grown on Si Substrates in Ultra-Dry Oxygen", IEEE Trans. Electron Devices, 35(12), pp.2245-2251.

- [50] Haddad, S, Liang, M-S, "The Nature of Charge Trapping Responsible for Thin-Oxide Breakdown Under a Dynamic Field Stress", IEEE Trans. Electron Lett., EDL-8(11), pp.524-527, 1987.

- [51] Heyns, M.M., "Degradation and Wearout of Thin Dielectric Layers during Charge Injection", ESSDERC, pp.361-368, Sept., 1990.

- [52] Avni, E, Loev, L, Shappir, J, "Temperature Effects on Electron Trap Generation and Occupation in SiO<sub>2</sub>", J. Appl. Phys., 63(8), pp.2700-2703, 1988.

- [53] Amerasekera, E.A., Campbell, D.S., "Electrostatic Pulse Breakdown in NMOS Devices", Quality and Reliability Engineering International, 2, pp.107-116, 1986.

- [54] Greason, W.D., Kucerovsky, Z, Chum, K.W.K., "Latent Effects Due to ESD in CMOS Integrated Circuits: Review and Experiments", IEEE Trans. Industry Applications, 29(1), pp.88-97, 1993.

- [55] Tunnicliffe, M.J., Dwyer, V.M., Campbell, D.S., "Latent Damage and Parametric Drift in Electrostatically Damaged MOS Transistors", Journal of Electrostatics, 31, pp.91-110, 1993.

[56] Hawkins, C.F., Soden, J.M., "Electrical Characteristics and Test Considerations for Gate Oxide Shorts in CMOS ICs", Proc. International Test Conf., pp.544-555, 1985.

### **CHAPTER 3**

# **Experimental Apparatus and Procedure**

# 3.1 Experimental Apparatus

# 3.1.1 Wafer Chuck and Microprober System

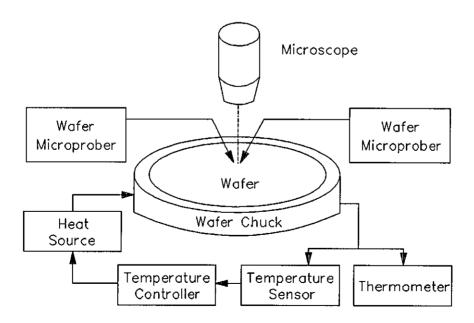

Two different wafer chucks were used to mount the silicon wafers. The first, intended for 4" wafers, was made of brass and held the wafer in place by means of a vacuum pump system. The second type, designed for 3" wafers, was made of aluminium and held the wafers in position using a system of mechanical clips arranged around the wafer periphery. The 3" chuck was heated by a series of wire-wound resistors, embedded in the body of the chuck, while its temperature was monitored by a Cr/Al thermocouple. This system accurately stabilised the chuck (and hence the wafer) at any user-defined temperature between ambient and 200°C. Temperature was independently monitored via a second thermocouple by a Comark Type 1602-2 electronic thermometer.

Figure 3.1: Wafer microprober station (together with temperature control system).

Electrical contact to the device structures was made using adjustable  $20\mu m$  tip microprobes, by which the device bond pads were manually probed under microscopic observation. Substrate contact was made using the chuck itself, which was in contact with the metallised wafer base. The overall arrangement is shown in Fig.3.1.

### 3.1.2 Electrical Instruments

Various electronic instruments were used to study the semiconductor wafers, all of which are described below.

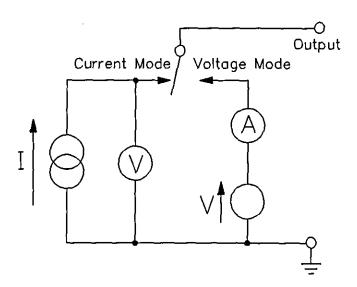

### 3.1.2.1 HP4145B Parametric Analyzer

Parametric analysis of the devices was performed using a Hewlett Packard HP4145B semiconductor parametric analyzer, which is capable of performing a number of different functions. The HP4145B is basically a programmable d.c. measurement system consisting of two voltage sources, two voltage monitors and four source-monitor units (SMUs). The latter are two-mode devices which can source current and monitor voltage or source voltage and monitor current. The arrangements is shown schematically in Fig.3.2.

Figure 3.2: Schematic diagram of Source-Measure Unit (SMU).

The parametric analyzer can measure the static I/V characteristics of a device or alternatively measure current or voltage as a function of time. Accuracy is ultimately limited by system noise, and measurements to within 10mV/10nA are readily attainable. The instrument also has a range of analytical functions (e.g. measurement of the slope/intercept of a tangent to an I/V characteristic), enabling the user to extract device parameters from the measured characteristics.

Measured data were stored on 3½" floppy disks for future retrieval. Hard copies of characteristics were also obtained using a Hewlett Packard HP7475A plotter.

### 3.1.2.2 Programmable Voltage Source

The Keithley 230 programmable voltage source provides precision d.c. voltages between 0 and 100V in both polarities with a resolution below 10mV and an output current limit between 2mA and 100mA. The unit has an internal program memory, allowing it to generate a user-defined voltage waveform.

### 3.1.2.3 L-C-R Meter

The Wayne-Kerr 4210 L-C-R bridge was used to measure high frequency circuit elements. This instrument measures resistance, capacitance and inductance in parallel or series configuration using sampling frequencies of 100Hz, 1kHz and 10kHz. It also incorporates a "suppress" function, which allows the parasitic circuit elements of the test probes and leads to be eliminated from the measurements.

### 3.1.2.4 HP 54111D Digital Oscilloscope

The Hewlett Packard 54111D digital oscilloscope can observe single-shot events and transfer the captured waveform to a computer via an HPIB interface. The controlling software, developed by Dr.A.J.Franklin [1], runs on a Walters 286 AT compatible desktop computer and allows the waveform data to be stored on a disk or transferred to the Mathcad software for analysis. The maximum speed of the oscilloscope is 10<sup>9</sup> samples per second, allowing the measurement of frequency components up to 500MHz.

The signals monitored by the oscilloscope were either voltages, measured by the HP10431A ( $1M\Omega/6.5pF$ ) and 10440A ( $10M\Omega/2.5pF$ ) voltage probes, or electrical currents, measured by the Tektronix CT1 current-transformer probe.

The signals from the voltage and current probes needed very little in the way of mathematical processing. Although probe attenuations were corrected by the oscilloscope itself, a problem was experienced with the zero level, whose value tended to drift. For this reason, the computer was programmed to calculate its own zero-voltage level by averaging the leading tenth of the waveform (prior to the beginning of the pulse) and then subtracting this value from the signal, i.e.

$$V(t) = V_{sc}(t) - \frac{10}{T_{sc}} \int_0^{T_{sc}/10} V_{sc}(\tau) d\tau$$

(3.1)

where  $V_{sc}(t)$  is the voltage signal from the oscilloscope and  $T_{sc}$  is the time duration of the waveform.

### 3.1.2.5 TG102 Signal Generator

A THANSAR TG102 pulse generator was used to provide an a.c. input to the test circuits. This generator has a frequency range of 0.2Hz-2MHz and a maximum output level of 20V peak-peak from  $50\Omega$  source impedance. It can generate sine, square and triangle waveforms with variable DC offset.

# 3.2 Test Samples

### 3.2.1 Devices on the Wafers

4" wafers which were composed of  $<100>40-55\Omega$ cm, p-type bulk silicon were used throughout the experiments. The wafers contained a selection of E-mode and D-mode nMOS transistor network, capacitor structures, various resistors, EPROM device arrays

and nMOS inverter circuits. All devices had gate-oxides of nominal thickness 40nm, and  $n^+$ -doped polysilicon gate electrodes.

All the MOSFETs on the arrays within each die were interconnected with common source and gate contacts and individual drain terminals, such that gate-stress was applied to the entire network at once. The total gate-area of the network was approximately  $3\cdot10^4$ cm<sup>2</sup>. Channel lengths of both E-mode and D-mode transistors varied between approximately 1 and  $50\mu m$ .

Although various capacitors were fabricated on the wafers, only the rectangular gate oxide capacitors with two different dimensions  $(215x268\mu m, and 416x553\mu m)$  were used in the experiments. Some of these capacitors were unimplanted, while others had received preferential p-type doping. The MOS-C gate inputs were isolated from all other devices on the die.

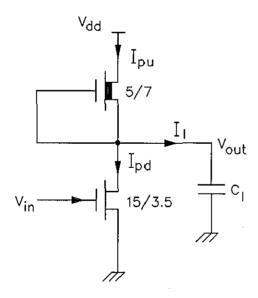

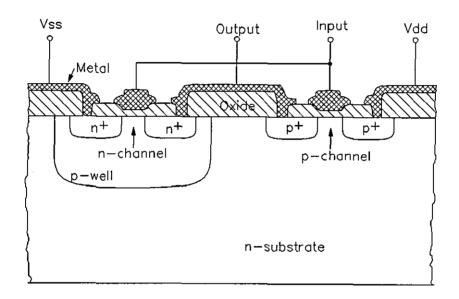

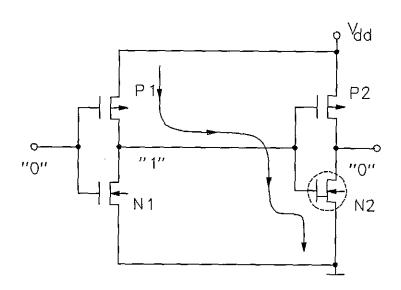

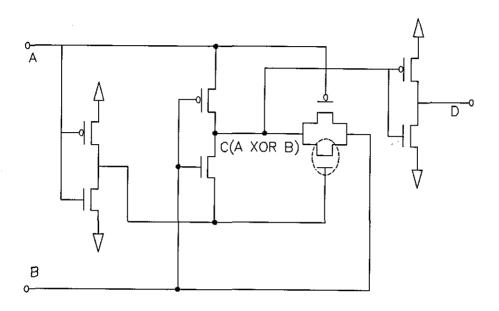

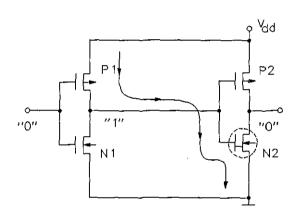

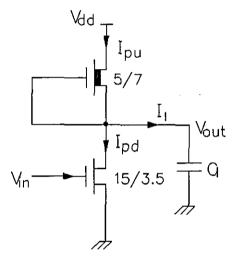

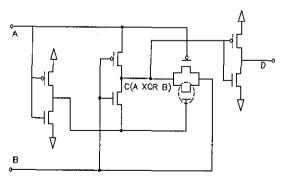

An nMOS inverter (see Fig.3.3) consisted of an E-mode nMOS transistor and a D-mode nMOS transistor was fabricated on each die of the wafers. The dimensions of the transistors are  $15x3.5\mu m$  and  $5x7\mu m$  respectively.

Figure 3.3: The nMOS inverter on wafers.

# 3.2.2 Characterization of Samples

### 3.2.2.1 C-V Curve Measurement

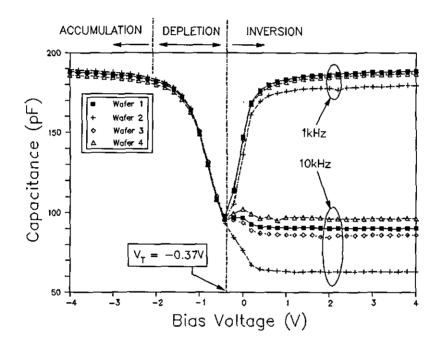

The Wayne-Kerr 4210 L-C-R meter was configured to monitor the capacitance of the MOS-C structures while a external voltage bias was linear increased from -4V to +4V. The measurement was carried out at two different frequencies 1kHz and 10kHz. The results are shown in Fig.3.4.

Figure 3.4: Capacitance versus voltage curves for the MOS-C structures.

### 3.2.2.2 Extraction of Oxide Thickness

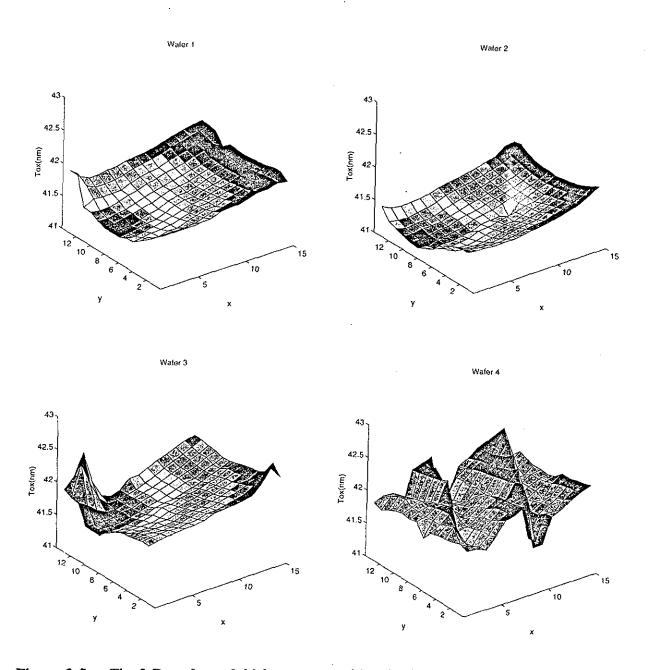

Although all the devices have a nominal oxide thickness of 400Å, a more accurate measurement of local thickness was taken for each die using the wide-area  $416x553\mu m$  MOS-C structure. It is assumed that all the other devices in the same die have the same oxide thickness.

The thickness  $(T_{ox})$  for each die was gauged by measuring the capacitance  $(C_{ox})$  of the wide-area capacitors. Measurement was performed at 10kHz using a Wayne-Kerr 420 L-C-R meter, with a -10V bias potential to ensure carrier accumulation at both oxide surfaces and this was guaranteed from the C-V curve shown in Fig.3.4. The oxide thickness for each die, estimated from the formula  $T_{ox} = \epsilon_0 \epsilon_{ox} \cdot \text{Area}/C_{ox}$  (where  $\epsilon_0 \epsilon_{ox} = 0$  oxide permittivity).

The results of thickness measurement for all the wafers are shown in Fig.3.5.

Figure 3.5: The 3-D surface of thickness vs. position (x,y).

### 3.2.2.3 The Measurement of Bulk Resistance

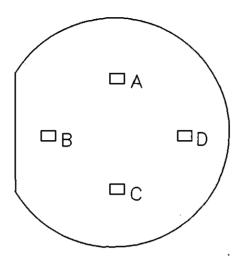

Four samples were chosen at different geographical positions for each wafer as shown in Fig.3.6.

Figure 3.6: The positions of samples for bulk resistance measurement.

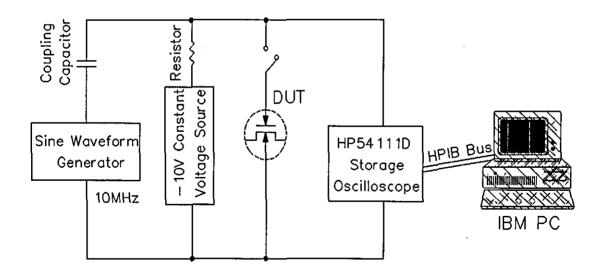

Figure 3.7: The apparatus for measuring bulk resistance of the MOS-C structures.

The apparatus shown in Fig.3.7 was used for the measurement of bulk resistance for the MOS-C structures and MOSFET, since the CR time constant is too small to be measured by L-C-R meter at 10KHz. A 10MHz Sine-wave signal was applied via a coupling capacitor to the DUT, together with a -10V d.c. bias to drive the Si surface into strong accumulation. Voltage and current profiles were captured by the HP54111D oscilloscope and downloaded to a Walters 286 computer, where the impedance  $Z_d$  of the structure was calculated. The capacitance and resistance were then extracted using the formulae:

$$R_b = \Re(Z_d)$$

$C_{ox} = \frac{1}{2\pi f |\Im(Z_d)|}$  (3.2)

where f is the 10MHz sampling frequency,  $\Re(Z_d)$  and  $\Im(Z_d)$  are the real and imaginary parts of the impedance.

Table 3.1: Bulk resistance for MOS-C structures (Ohms).

| Wafer No. |             | Sample A | Sample B | Sample C | Sample D | Average |

|-----------|-------------|----------|----------|----------|----------|---------|

| 1         | Unimplanted | 332.8    | 342.3    | 344.0    | 336.4    | 338.9   |

|           | Implanted   | 346.6    | 352.3    | 347.3    | 327.5    | 343.4   |

| 2         | Unimplanted | 250.6    | 239.7    | 248.7    | 244.7    | 245.9   |

|           | Implanted   | 249.3    | 255.3    | 256.9    | 251.3    | 253.2   |

| 3         | Unimplanted | 294.1    | 294.4    | 291.8    | 289.2    | 292.8   |

|           | Implanted   | 284.1    | 282.5    | 290.6    | 280.9    | 284.6   |

The bulk resistance in ohms are shown in Table 3.1 above, and average bulk resistance for each wafer was used in later data analysis since the difference between inwafer measurements was negligible and well below the error in the measurement technique.

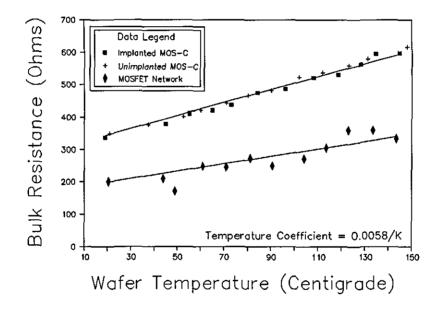

The bulk resistance of Wafer No.4 was measured as a function of temperature. The wafer was mounted on the 3" heated chuck and resistances were measured for temperatures between 20 and 150°C. The results are shown in Fig.3.8. The data appear to follow the standard linear law  $R = R_0(1+\alpha(T-T_0))$  where  $T_0$  is room temperature,  $R_0$  is room temperature resistance and  $\alpha \approx 0.0058$ /°C is the temperature coefficient of resistance.

Figure 3.8: Bulk resistance for different devices on wafer No.4 as a function of temperature.

# 3.3 Experiments on MOS-C Structures and MOSFET Networks

### 3.3.1 Introduction

The general aims of these experiments were providing new data for the development of a gate-oxide dielectric breakdown model and the assessment of the MOS capacitor (MOS-C) as an oxide-integrity test vehicle. The TDDB experiments were performed on implanted and unimplanted MOS-C structures with dimensions of  $215x268\mu m$  and nMOSFET networks on four different wafers. The  $416x553\mu m$  dimension MOS-C structures were reserved for the measurement of gate oxide thickness. The TDDB experimental apparatus is shown in Fig.3.9.

Figure 3.9: The apparatus used for TDDB experiments.

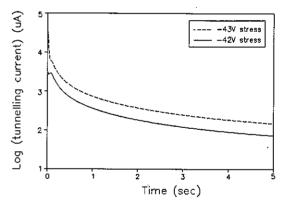

### 3.3.2 Field Accelerated TDDB Life Test

The MOS capacitor structures were subjected to constant voltage stress between gate and substrate at room temperature. The injection current to the gate oxide was monitored as a function of time by the HP4145B analyzer and voltage across the oxide was recorded

using the HP54111D storage oscilloscope. The oxide breakdown was easily detected as a rapid increase of injection current for large-time breakdown ( $t_{bd} > 1$  sec.). The most accurate indication of breakdown for small-time breakdown ( $t_{bd} < 1$  sec.) was a sudden drop of voltage across the oxide as measured by the oscilloscope. Devices stressed at each particular voltage were spread as uniformly as possible across the wafer in order to eliminate any positional dependencies.

The parameters  $t_{bd}$ ,  $I_{max}$  (the maximum recorded injected current) and  $I_{stop}$  (injection current immediately prior to breakdown) were recorded for each capacitor, together with the stress voltage and the position of the die on the wafer.

# 3.3.3 Temperature Accelerated TDDB Life Test

MOS-C structures were subjected to -41.5V stress at four different temperatures,  $50^{\circ}$ C,  $100^{\circ}$ C,  $150^{\circ}$ C and room temperature. The 3" chuck with the temperature controlled heat source was used in the same instrument configuration as that of Section 3.3.2. The 4" wafer was initially divided into four quarters, each of which was mounted upon the 3" chuck. Die position, stress temperature,  $t_{bd}$ ,  $I_{max}$  and  $I_{stop}$  were recorded for later analysis.

# 3.3.4 Experimental Results

This section describes the experimental results from MOS-C structures and MOSFETs. For each die, the measured results of  $t_{bd}$ ,  $I_{max}$ ,  $I_{stop}$ , together with the capacitance of the wide-area  $416x553\mu m$  MOS-C structure were input on to a LOTUS 1-2-3 spreadsheet. Then the thickness of the die was calculated from the formula  $T_{ox} = \epsilon_0 \epsilon_{ox} \cdot \text{Area/C}_{ox}$ , and the oxide fields were estimated from  $F_{ox} = (V_s - I_{ox}R)/T_{ox}$ . The results are shown below.

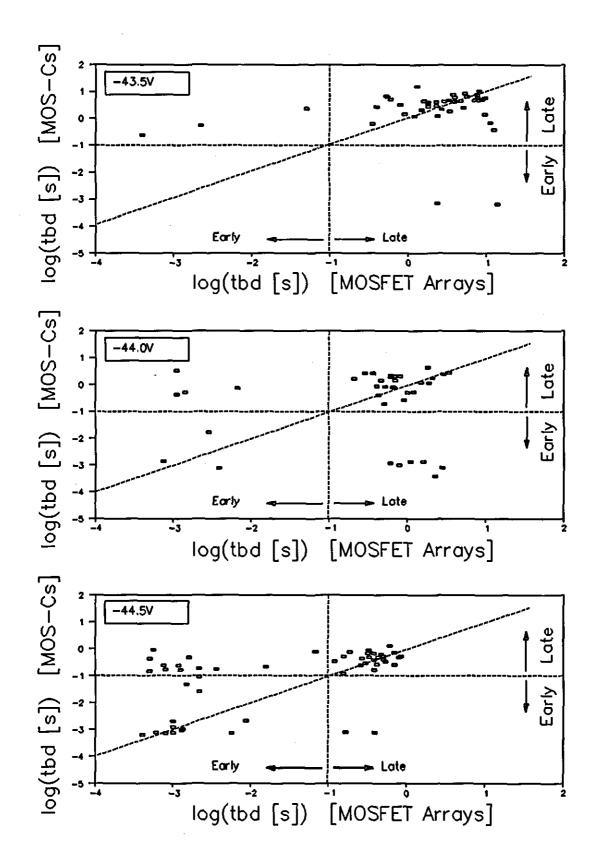

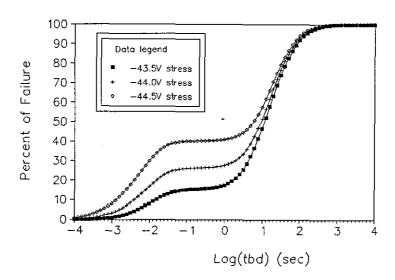

### 3.3.4.1 Time-dependent Failure Distributions

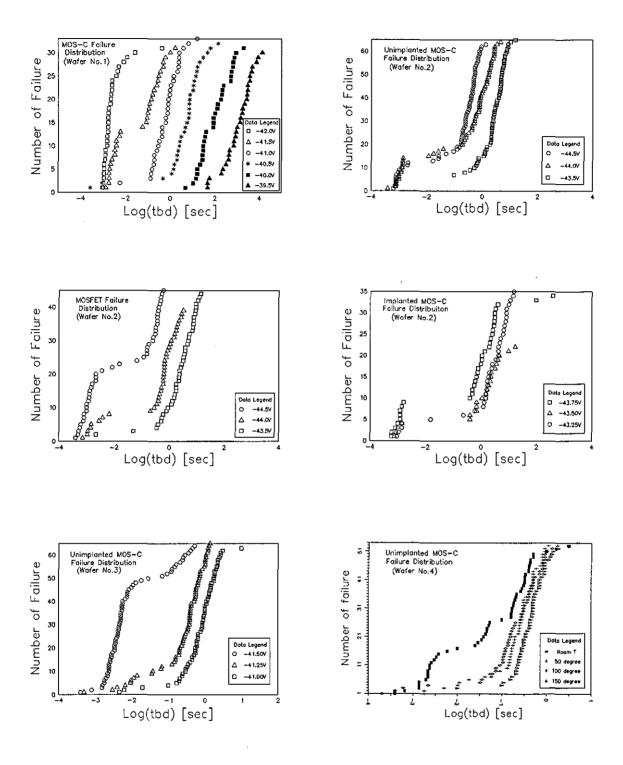

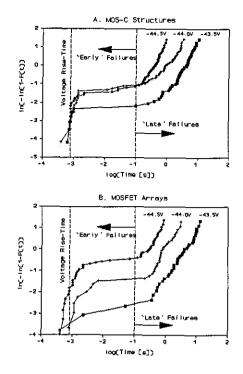

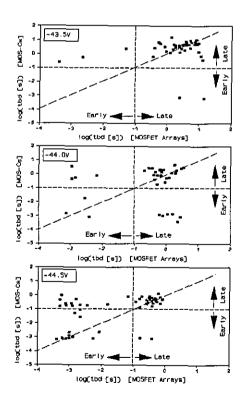

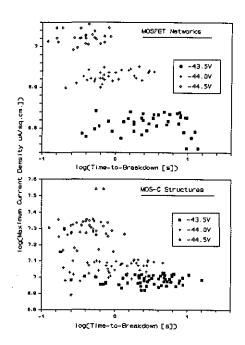

The failure distributions of the unimplanted MOS-C structures for the four wafers are shown in Fig.3.10 together with the failure distributions for the implanted MOS-Cs and

Figure 3.10: Failure distributions for unimplanted MOS-C structure (wafer No.1,2,3,4) under constant voltage stress, implanted MOS-C structures and MOSFETs (wafer No.2 only).

It is clearly shown that the failure distributions are bi-modal, consisting of 'early' failures ( $t_{bd} < 100$ ms) and 'late' failures ( $t_{bd} > 100$ ms). The ratio of the numbers of 'early' and 'late' failures generally increases with the stress voltage.

### 3.3.4.2 Injection Current

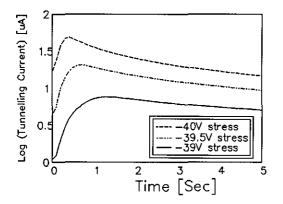

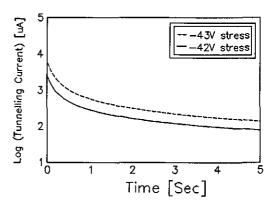

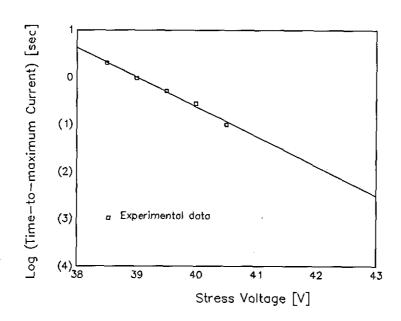

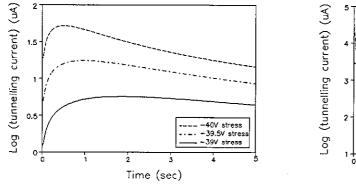

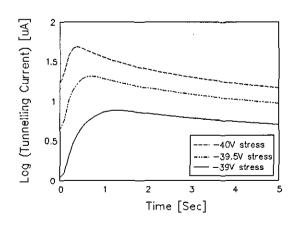

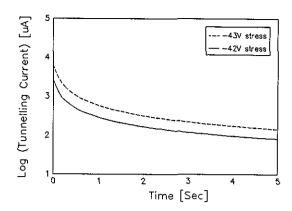

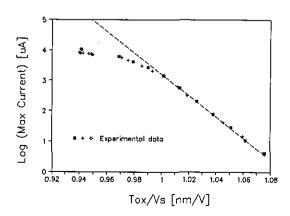

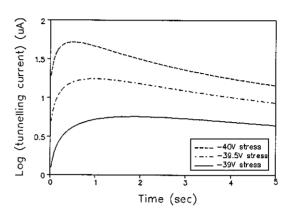

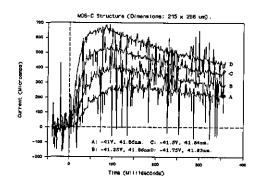

The injection current profiles were monitored using HP4145B parametric analyzer during the stresses. Typical current profiles are shown in Fig.3.11.

Figure 3.11: The injection current profiles of different constant voltage stresses for wafer No.2.

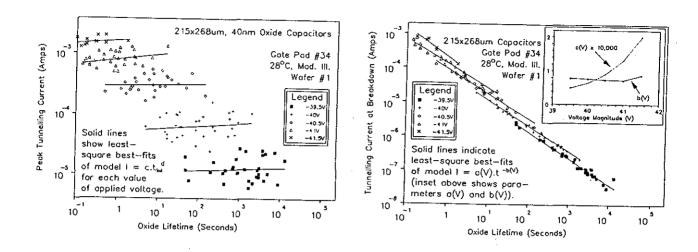

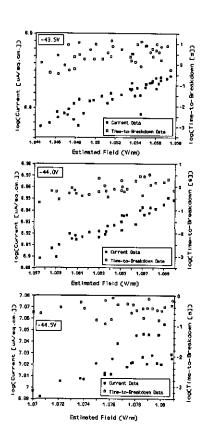

Fig.3.12 and 3.13 show the initial and final injection currents (the injection current at breakdown) plotted against  $t_{bd}$ . In the case of initial current data, there is little correlation between log(current) and log( $t_{bd}$ ), although both are strong function of voltage. Least-square analysis suggested a slight increase in current with  $t_{bd}$ , although the correlation fails to meet the criterion for the 95% confidence level. The final current data can be satisfactorily fitted to a model of the form  $I_{bd} = a(V) \cdot t_{bd}^{-b(V)}$ , where  $I_{bd}$  is the final current and a(V) and b(V) are parameters which depend only upon voltage (see inset). It is clear that the majority of the voltage dependence appears in a(V), while b(V) remains mostly between 0.7 and 0.8 throughout the voltage range.

Figure 3.12 & 3.13: The initial and final injection current as a function of time-to-breakdown.

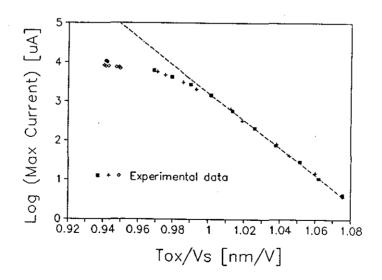

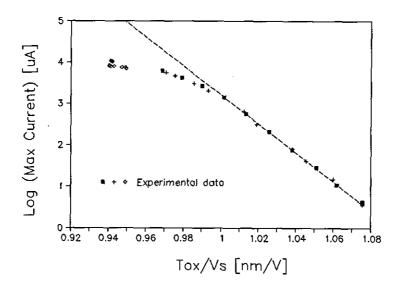

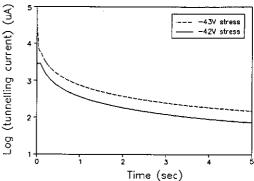

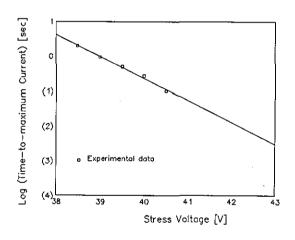

The logarithm of the maximum injection currents were found to decrease linearly with 1/F at lower fields and saturates at higher fields (Fig.3.14).

Figure 3.14: The relationship between maximum injection current and stress field.

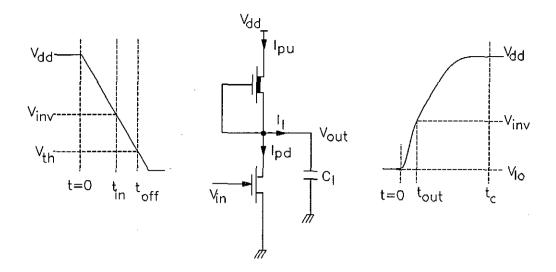

# 3.4 Experiments on nMOS Inverter

The following experiments investigate the effects of the parametric drift caused by gate oxide breakdown upon circuit operation, with an aim to develop a technique for detecting its existence. The experiments were performed on the nMOS inverter (see Fig.3.3). The wafer was held on the 4" brass chuck (described in section 3.1.1) under room temperature and moderate illumination.

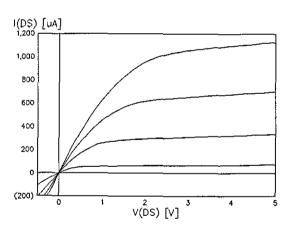

### 3.4.1 Characterisation of the Pull-down Transistor

A wafer level transistor characteristics can be easily measured by connecting the HP4145B analyzer's SMUs through a test fixture 16058A to the microprobe station. During the measurement, the drain electrode of the pull-up transistor was left floating in order to ensure current accuracy. The characterisations were performed using three SMUs connected to the source, drain and gate electrode of the pull-down transistor. The substrate of the transistor was connected to the source.

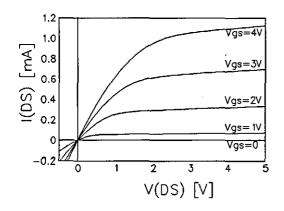

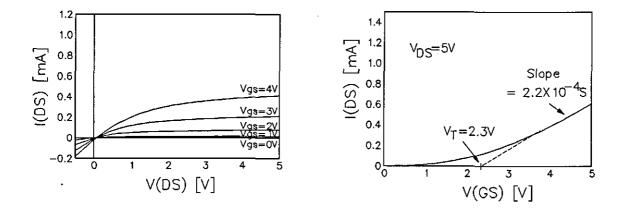

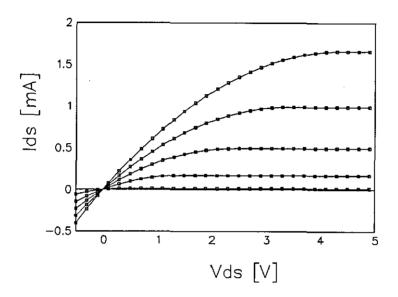

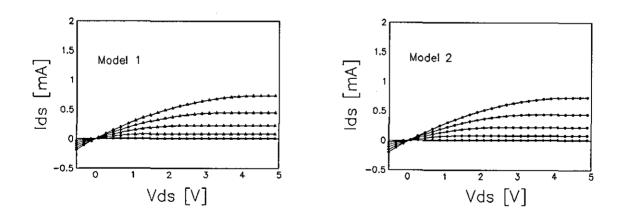

The  $I_G$  -  $V_G$  characteristics of the pull-down transistor remained below the 20pA level throughout the sweep indicating that the gate oxide worked well as a dielectric (its resistance is around 250G $\Omega$ ). The  $I_{DS}$ - $V_{DS}$  and  $I_{DS}$ - $V_{GS}$  characteristics of the pull-down transistor nMOS inverter are shown in Fig.3.15 and Fig.3.16 respectively.

Figure 3.15 & 3.16:  $I_{DS} - V_{DS}$  &  $I_{DS} - V_{GS}$  characteristics of the pull-down transistor.

### 3.4.2 Characterisation of the nMOS Inverter

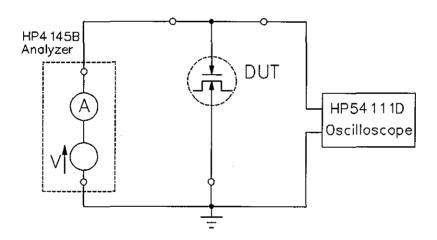

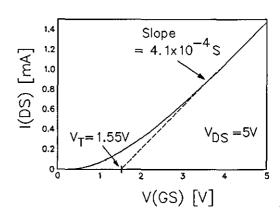

Figure 3.17 & 3.18: The apparatus used for characterisation of the inverter.

Fig.3.17 and 3.18 show the apparatus used to extract the DC and transient characteristics of the inverter.

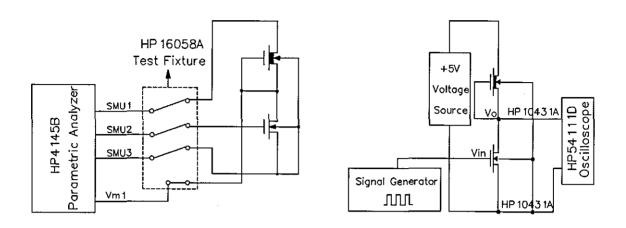

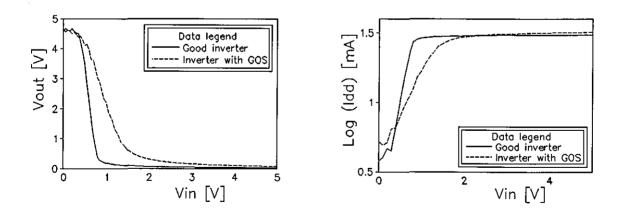

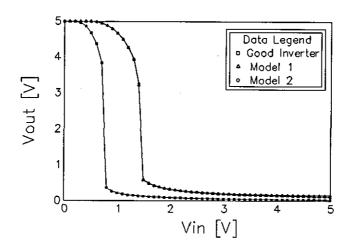

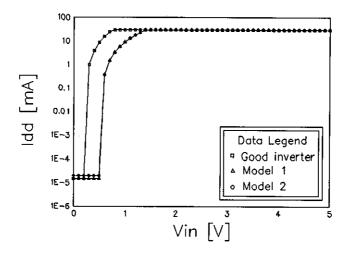

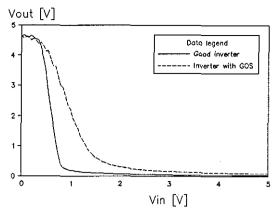

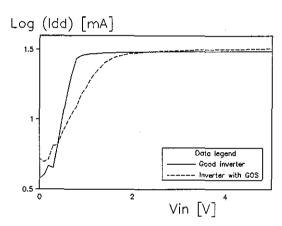

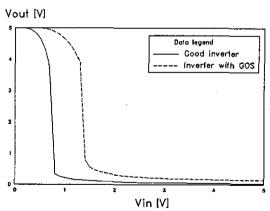

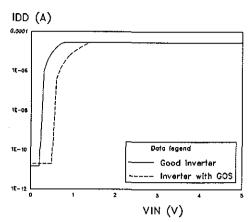

The DC voltage transfer characteristics and the supply current ( $I_{dd}$ ) characteristics are shown in Fig.3.19 and 3.20 by the solid lines.

Figure 3.19 & 3.20: The DC transfer curves for the nMOS inverter.

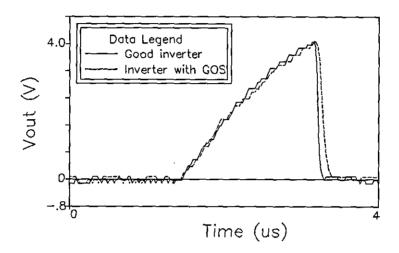

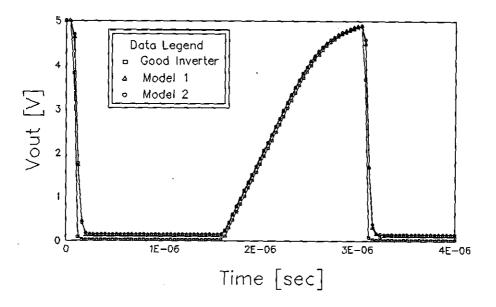

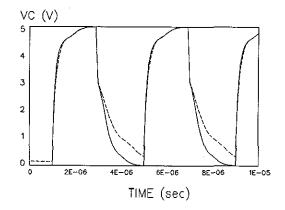

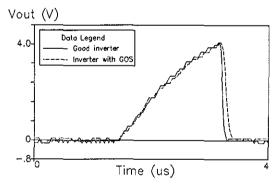

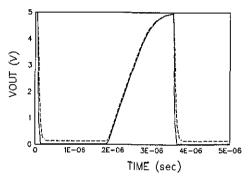

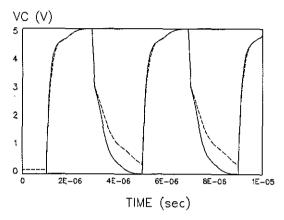

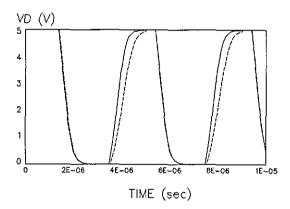

The transient response of the inverter (whose d.c. characteristics are shown in Fig.3.19 & 3.20 by the solid lines) to a 250kHz square input waveform from the THANSAR TG102 generator was captured by HP54111D digital oscilloscope and is shown in Fig.3.21 by the solid line.

Figure 3.21: The transient response of the inverter.

# 3.4.3 Constant Voltage Stress on Gate Oxide of the Pull-down Transistors

The pull-down transistors were then subjected to constant voltage stress from HP4145B analyzer. The -43V stress was applied between the gate electrode and the substrate of the transistors in order to cause gate dielectric breakdown. The injection current profile was monitored by the analyzer and breakdown was detected by a rapid rise in the injection current. The stress was removed immediately after the oxide breakdown.

### 3.4.4 Re-characterisation of the Pull-down Transistors

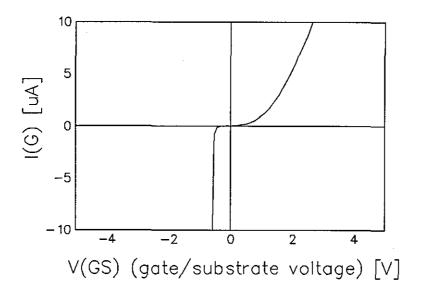

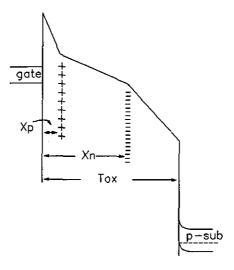

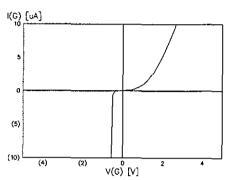

After the gate oxide breakdown, the pull-down transistors were re-characterised. The occurrence of gate oxide breakdown was confirmed by the  $I_G$  -  $V_G$  characteristics shown in Fig.3.22. The existence of a tens-of- $\mu A$  gate current meant that a gate oxide short was

induced during the constant voltage stress.

Figure 3.22: The  $I_G$  -  $V_G$  characteristics of the pull-down nMOSFET with a GOS.

Figure 3.23 & 3.24: The  $I_{DS}$  -  $V_{DS}$  and  $I_{DS}$  -  $V_{GS}$  characteristics of the pull-down nMOSFET with a gate oxide breakdown.