| UNIV         | LOUGHBOROU<br>ERSITY OF TEC<br>LIBRARY | GH<br>HNOLOGY |  |

|--------------|----------------------------------------|---------------|--|

| AUTHOR/FILIN | G TITLE                                |               |  |

|              | AKSEL, A                               |               |  |

| ACCESSION/C  |                                        | 31/01         |  |

| VOL. NO.     | CLASS MARK                             |               |  |

|              | ARCHIVES                               |               |  |

| FOR          | REFERENCE                              | ONLY          |  |

|              |                                        |               |  |

|              |                                        |               |  |

## A DELTA-SIGMA MODULATED SPEED CONTROL

### SYSTEM FOR INDUCTION MOTORS

by

ALPASLAN AKSEL, B.Sc.

#### A Doctoral Thesis

Submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of the Loughborough University of Technology August, 1978.

Supervisor: I.R. Smith, D.Sc., C.Eng., FIEE

Department of Electronic and Electrical Engineering

© by Alpaslan AKSEL, 1978.

| Loughborough University |

|-------------------------|

| of Technology Library   |

| Date Oct.78             |

| Class                   |

| Acc. 152001/01          |

· · · ·

"To AKSEL and DEVELIOGLU Families"

0

3 B

### ACKNOWLEDGEMENTS

The author wishes to express his sincere gratitude to Professor I.R. Smith who supervised the project, for the help he provided by every possible means.

The author is indebted to his wife for her endurance throughout the project and her assistance with the drawings.

Finally thanks are due to Miss J.M. Briers and Mrs. S.A. Moore who patiently carried out the typing of the thesis.

### SYNOPSIS

The electronic control techniques used in static frequency changers differ considerably, depending on the type of system considered and the particular specifications and requirements. Mark-space ratio control and pulse-width modulation are among techniques already well-established for use with induction motors to provide a variable-speed a.c. drive.

The project is concerned with the applicability of delta-sigma modulation as the basis of a novel method of electronic speed control. The techniques involved are well-known in communication systems, where they are extensively used in the transmission of speech signals. With a sine wave at the input, a delta-sigma modulator produces an output quantised in both voltage and frequency, which enables power control to be achieved from a fixed d.c. supply using only a single power controller. This feature is of considerable potential importance in the field of a.c. drives, as is the fact that the harmonic components of the voltages and currents in the circuit are much lower than obtained with most existing techniques. Since the frequency of encoding is high, a transistor inverter is more suitable than a thyristor inverter for amplifying the control signal before feeding to the motor.

The project aims to outline the main features of a delta-sigma modulated speed-control system. Characteristics of induction motors and different speed control methods are discussed. Delta modulation techniques are investigated, with consideration given to their potential use for speed control purposes. A computer simulation is employed to investigate the characteristics of delta-sigma modulation, and the design and performance of delta-sigma modulators are outlined. The problems associated with the design of the inverter and the driving circuitry are discussed. Experimental results are presented from a prototype equipment, which provides continuous and reversible speed variation, with controllable acceleration and deceleration. Results are discussed and suggestions for future research are included.

ii

# LIST OF PRINCIPAL SYMBOLS

| <sup>s</sup> (m)      | =        | slip, for maximum torque                                            |

|-----------------------|----------|---------------------------------------------------------------------|

| p                     | =        | number of poles                                                     |

| V                     | =        | voltage                                                             |

| I                     | =        | current                                                             |

| Т                     | =        | torque developed by motor, time constant of RC integrator           |

| It                    | =        | stator current per phase                                            |

| f                     | = :      | frequency                                                           |

| ω                     | =        | angular frequency                                                   |

| R <sub>r</sub>        | =        | rotor resistance                                                    |

| ω <sub>s</sub>        | =        | supply frequency in rad/sec.                                        |

| N <sub>s</sub>        | <b>=</b> | supply frequency in rev/min, secondary turns ratio of a transformer |

| α,θ                   | =        | phase angle                                                         |

| ΔM                    | =        | delta modulation                                                    |

| Δ-ΣΜ                  | =        | delta sigma modulation                                              |

| Δv                    | =        | central delta step                                                  |

| f <sub>0</sub>        | =        | characteristic frequency of integrator                              |

| i(t)                  | =        | input to the modulator                                              |

| o(t)                  | =        | output of the modulator                                             |

| ε                     | =        | error                                                               |

| fc                    | =        | frequency of the clock signal                                       |

| X(I),Y(I),Z           | Z(I)     |                                                                     |

|                       | =        | 3-phase inputs to $\Delta - \Sigma$ modulation simulator            |

| ф                     | =        | flux                                                                |

| V <sub>CE</sub>       | =        | collector-emitter voltage of a transistor                           |

| V <sub>CE (SAT)</sub> | Ħ        | saturation value of V <sub>CE</sub>                                 |

| ц                | = | base current of a transistor         |

|------------------|---|--------------------------------------|

| г                | = | collector current of a transistor    |

| 1 <sup>CO</sup>  | = | leakage current of a transistor      |

| V <sub>EB</sub>  | = | emitter-base voltage of a transistor |

| V (BR)EBO        | = | breakdown emitter-base voltage       |

| h <sub>FE</sub>  | = | forward current transfer ratio       |

| t                | = | turn-on time                         |

| t <sub>off</sub> | = | turn-off time ·                      |

| t <sub>s</sub>   | = | storage time                         |

| td               |   | delay time                           |

| τ                | = | time constant                        |

| T1               | = | transistor 1                         |

| dV/dt            | = | rate of rise of voltage              |

# TABLE OF CONTENTS

|             |                            |             |                                                                               | PAGE NO. |

|-------------|----------------------------|-------------|-------------------------------------------------------------------------------|----------|

|             |                            |             |                                                                               |          |

| ACKNOWLEDGE | MENTS                      |             |                                                                               | i        |

| SYNOPSIS    |                            |             |                                                                               | ii       |

| LIST OF PRI | NCIPAL S                   | YMBOLS      |                                                                               | iii      |

| · ·         |                            |             |                                                                               |          |

|             | TNTRODU                    | CTION       |                                                                               |          |

| CHAPTER 1:  | INTRODU                    |             |                                                                               | 1        |

|             | $1.1 \\ 1.2 \\ 1.3 \\ 1.4$ | Static      | ng Machine System<br>ng Machine System<br>Inverter System<br>of Investigation | 23       |

| CHAPTER 2:  | CHARACT<br>TECHNIQ         |             | S OF INDUCTION MOTORS AND SPEED CONTROL                                       |          |

|             | 2.1                        |             | ion Motor Characteristics                                                     |          |

|             |                            | 2.1.1       | Torque-Speed Characteristics<br>Induction Motor Drive Stability               |          |

|             |                            | 2.1.3       | Effect of Input Voltage and Rotor<br>Resistance on the Torque-Speed           | •        |

|             |                            | 2.1.4       | Characteristics<br>Extension of Negative Slope Region by                      | . 8      |

|             |                            |             | Variation of Supply Frequency                                                 |          |

|             | 2.2                        |             | cent Speed Control Techniques                                                 |          |

|             |                            | 2.2.1       | Phase Angle Control<br>Rectifier-Inverter Control                             | •        |

|             |                            | 2.2.3       |                                                                               | . 15     |

|             |                            |             |                                                                               | ·        |

| CHAPTER 3:  | DELTA M                    | ODULATI     | ON TECHNIQUES                                                                 |          |

|             | 3.1                        |             | Modulation                                                                    | . 28     |

|             |                            | 3.1.1       | Derivation of the Overload<br>Characteristic                                  | . 31     |

|             |                            | 3.1.2       |                                                                               | •        |

|             |                            | 3.1.3       | •                                                                             | . 32     |

|             |                            | 3.1.4       |                                                                               |          |

|             | 3.2                        | Delta 3.2.1 | Sigma Modulation<br>Derivation of the Overload                                | . 33     |

|             |                            | J. 4. L     | Characteristic                                                                | . 34     |

|             |                            | 3.2.2       | Derivation of the Threshold of Coding.                                        |          |

|             |                            | 3.2.3       | Characteristics of Delta Sigma<br>Modulation                                  | 36       |

|             |                            |             | MOUUTALION                                                                    | •        |

| 3.3 | Delta | Sigma Modulation with Double                             | _  |

|-----|-------|----------------------------------------------------------|----|

|     | Int   | egration                                                 | 30 |

|     |       | Overload Level                                           | 3  |

|     | 3.3.2 | Threshold of Coding                                      | 3  |

|     | 3.3.3 | Characteristics of Delta Sigma<br>Modulation with Double |    |

|     |       | Integration                                              | 38 |

#### CHAPTER 4:

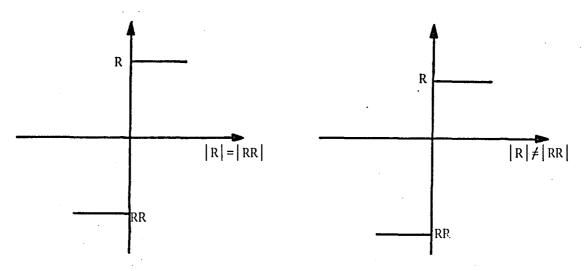

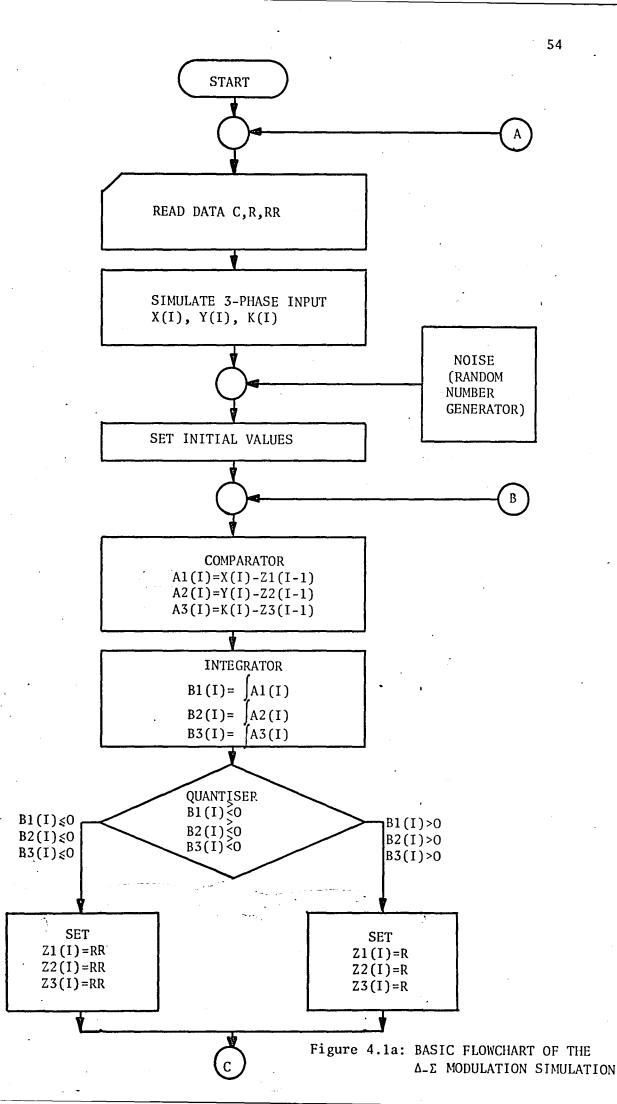

# DIGITAL COMPUTER SIMULATION OF DELTA SIGMA MODULATION

| 4.1 | Decie   | Flouchant                         | 45 |  |

|-----|---------|-----------------------------------|----|--|

| 4.1 |         | Flowchart                         |    |  |

|     | 4.1.1   | Input Waveform Generation         | 46 |  |

| •   | 4.1.2   | Delta Sigma Modulation            | 47 |  |

|     | 4.1.3   | Graph Plotting                    | 48 |  |

|     |         | Noise and Distortion              | 48 |  |

|     |         | Fourier Analysis                  | 49 |  |

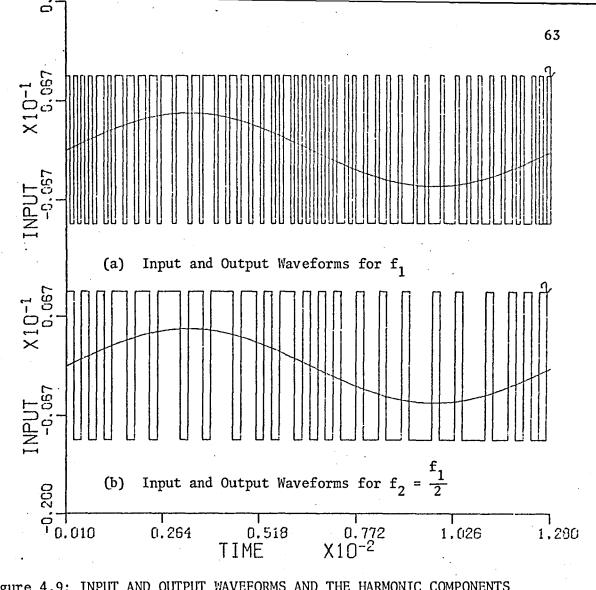

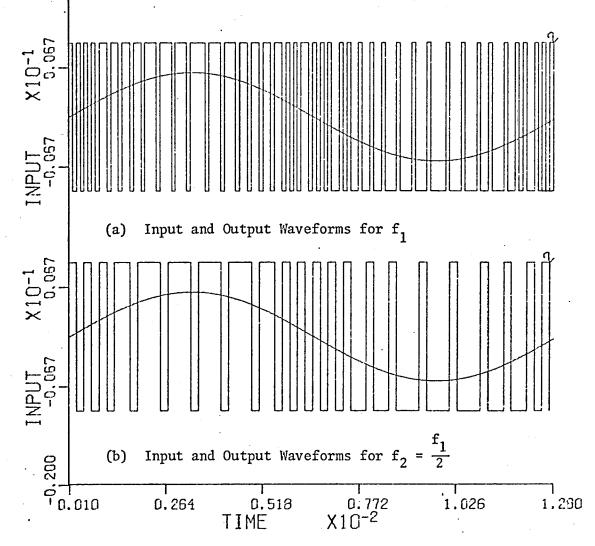

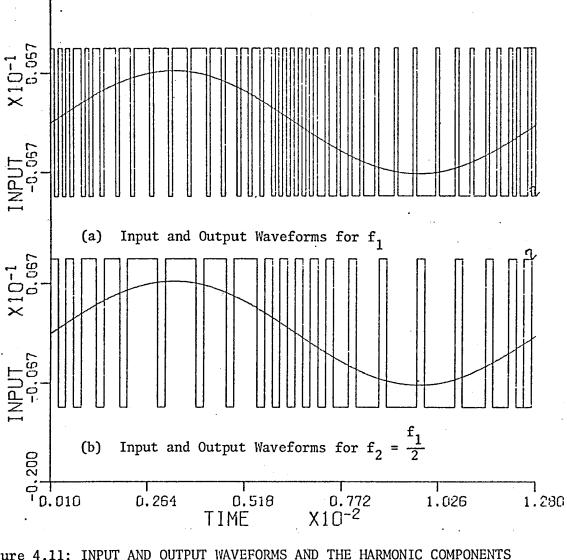

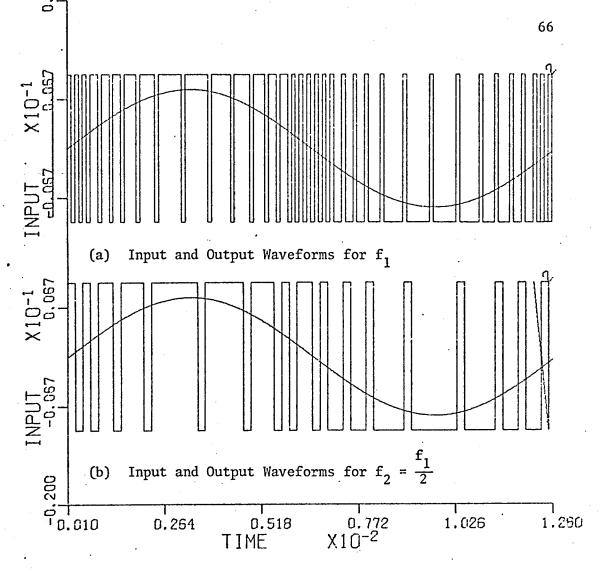

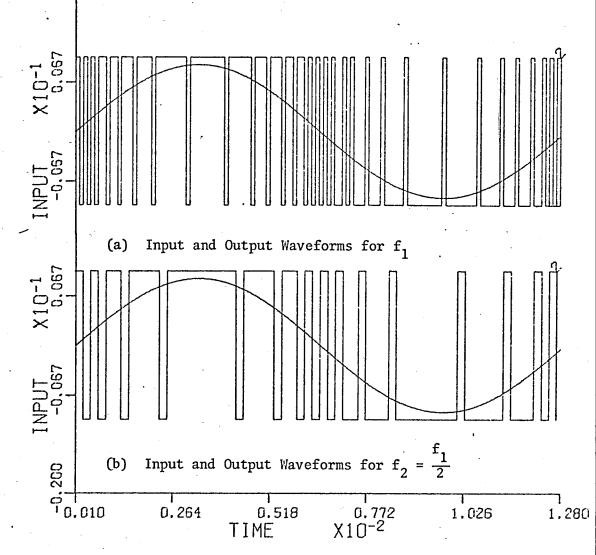

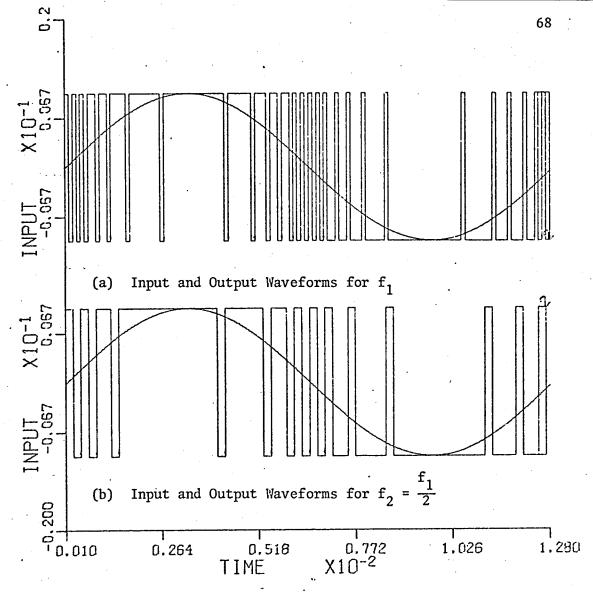

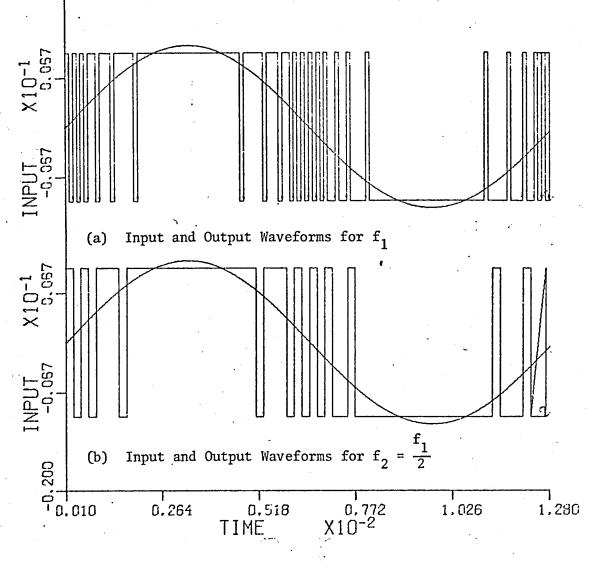

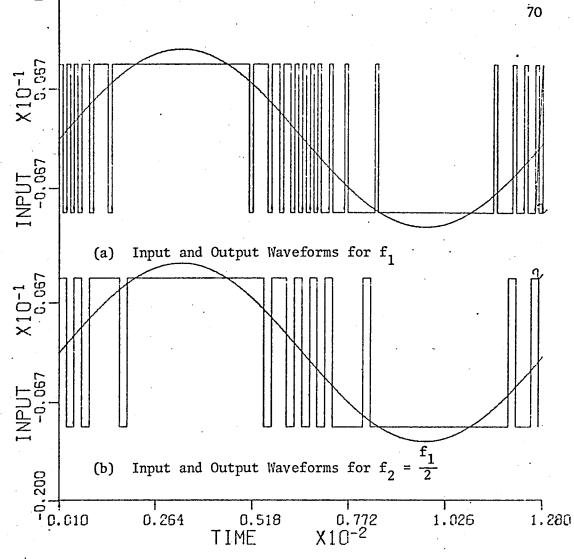

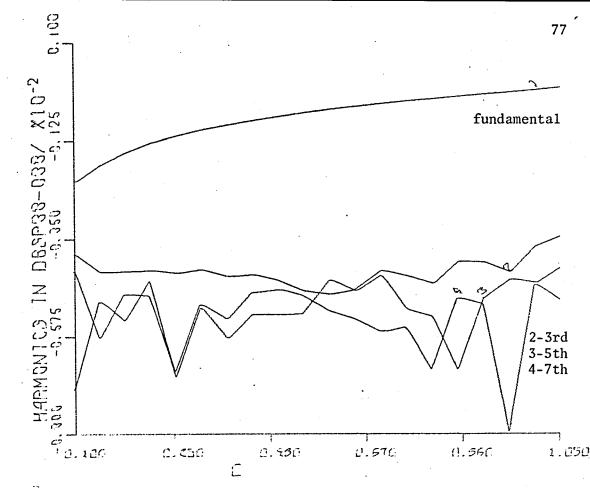

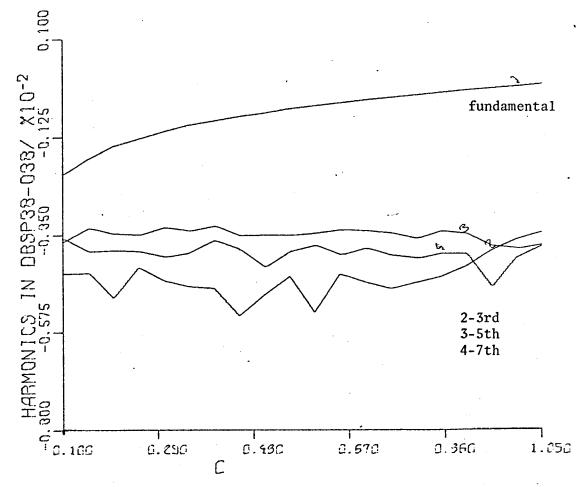

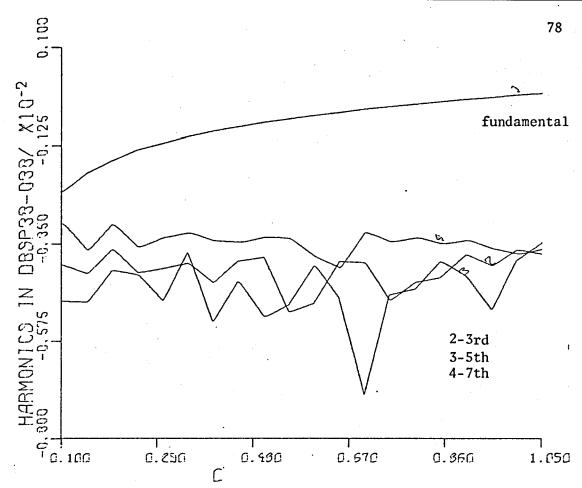

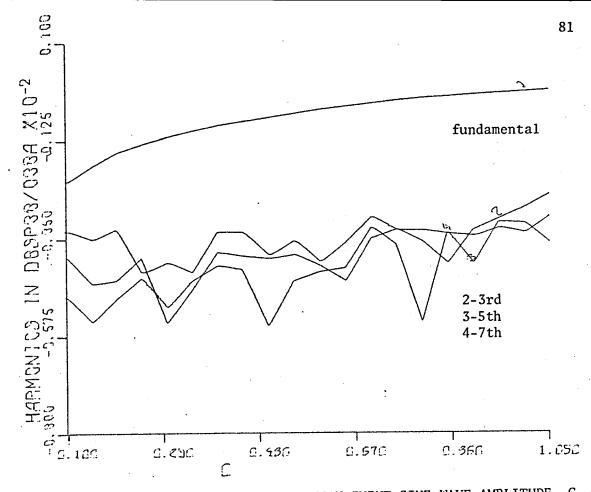

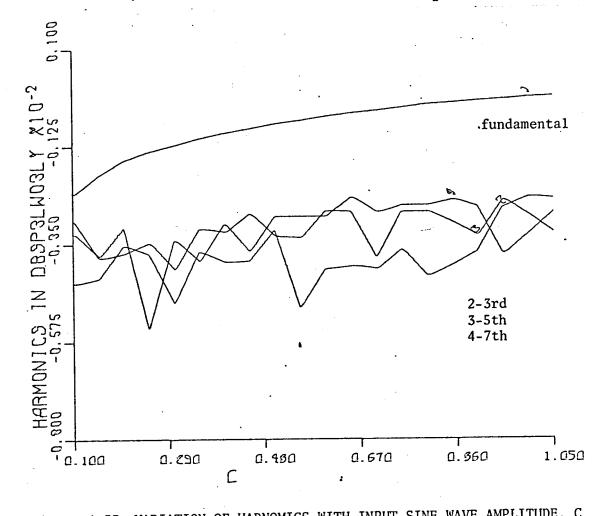

| 4.2 | Results |                                   |    |  |

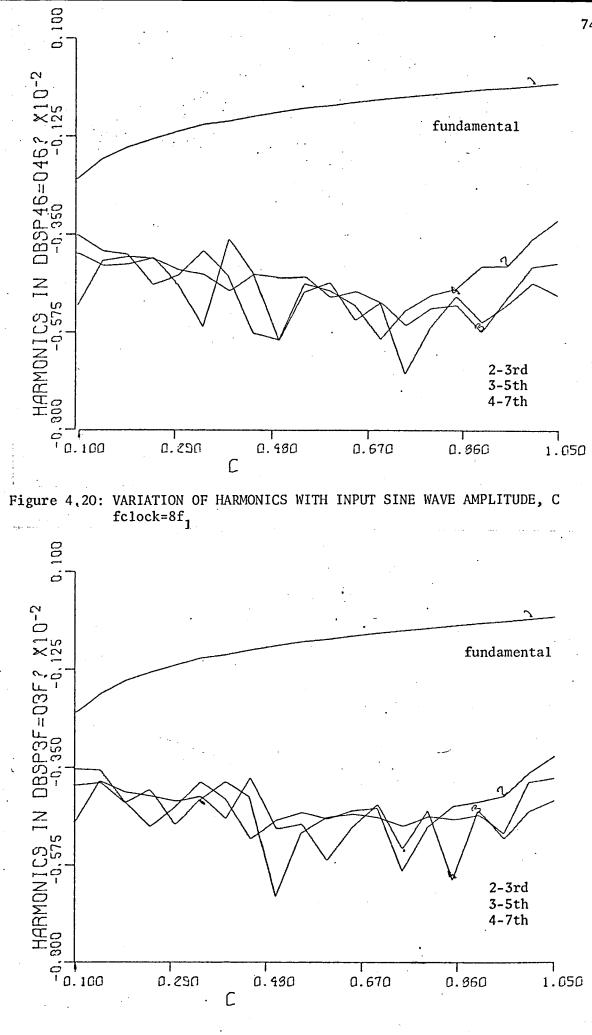

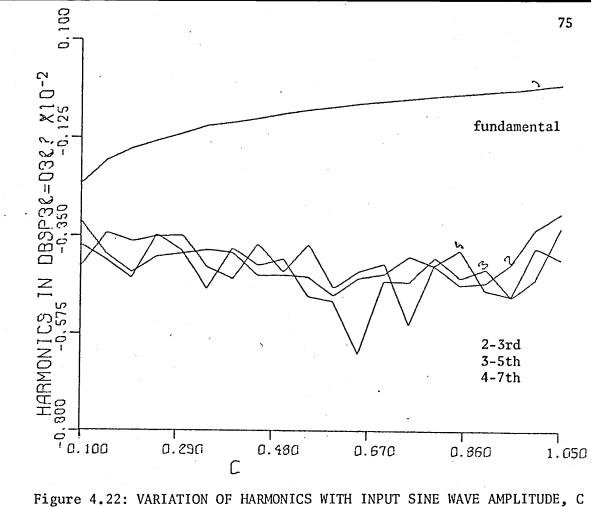

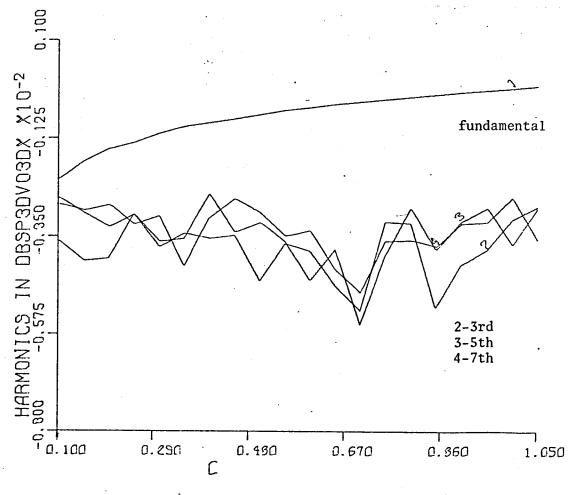

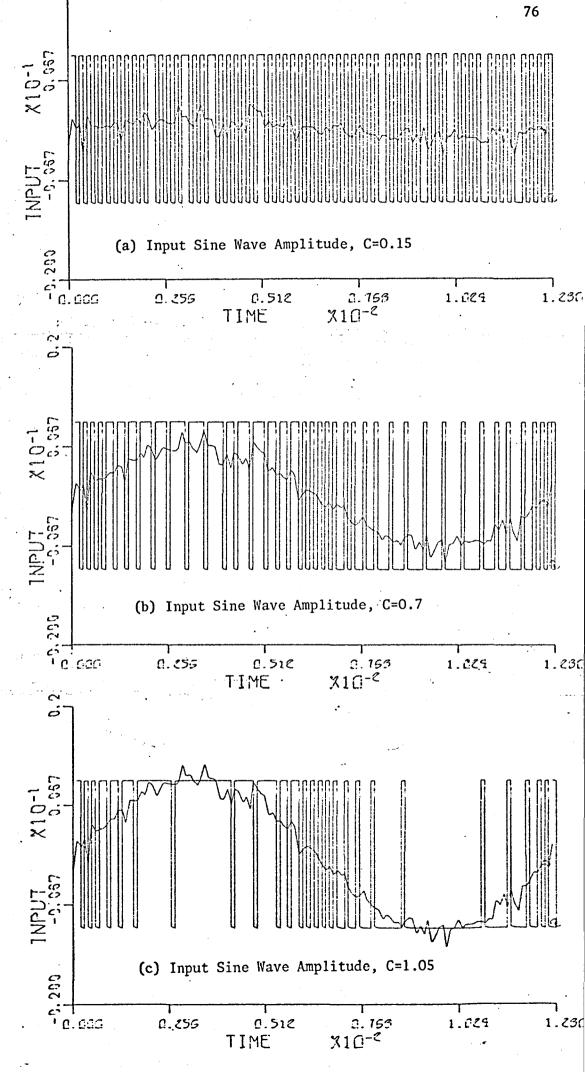

|     | 4.2.1   | Effect of the Clock Frequency and |    |  |

|     |         | the Input Sine Wave Amplitude C   |    |  |

|     |         | on the Harmonic Content           | 50 |  |

|     | 4.2.2   | Effect of Noise                   | 52 |  |

|     | 4.2.3   | Effect of Distortion              | 53 |  |

#### CHAPTER 5:

### DESIGN AND PERFORMANCE OF DELTA SIGMA MODULATORS

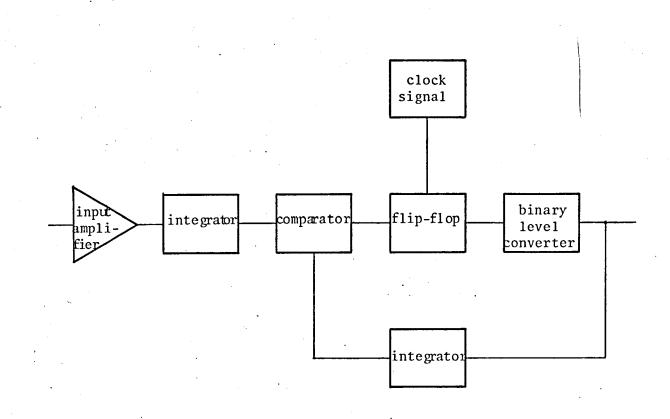

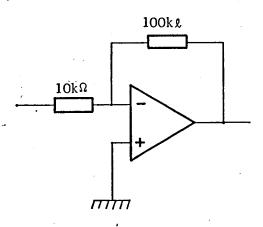

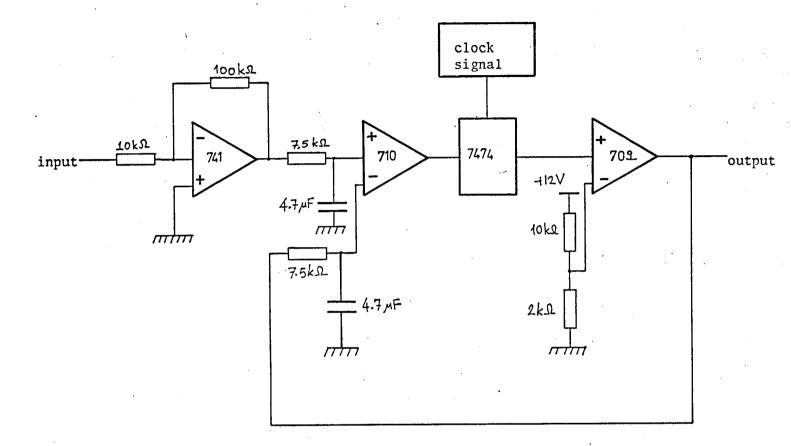

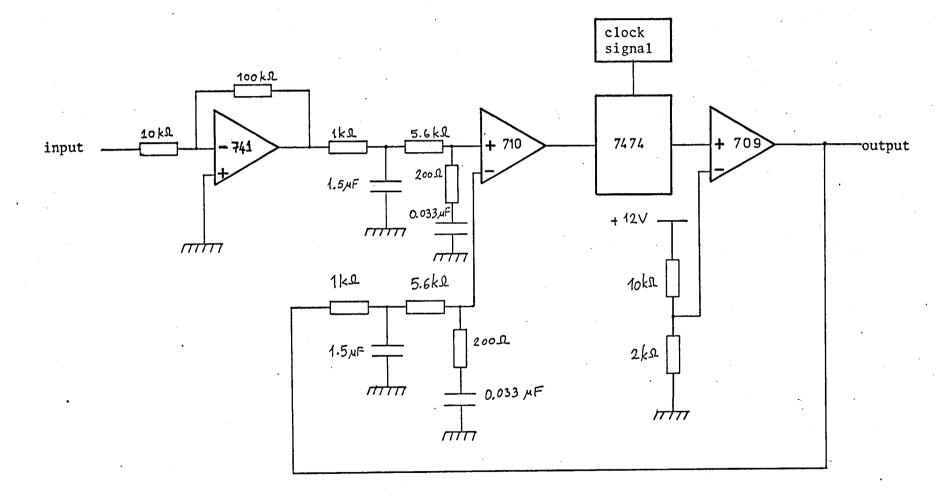

| Design of Delta Sigma Modulator with |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Integration                   | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

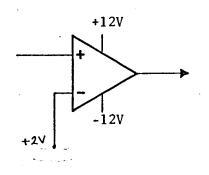

| 5.1.1 Input Amplifier                | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1.2 Comparator                     | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Design of Delta Sigma Modulator with |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Double Integration                   | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Theoretical Assessment of the Two    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Modulators                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

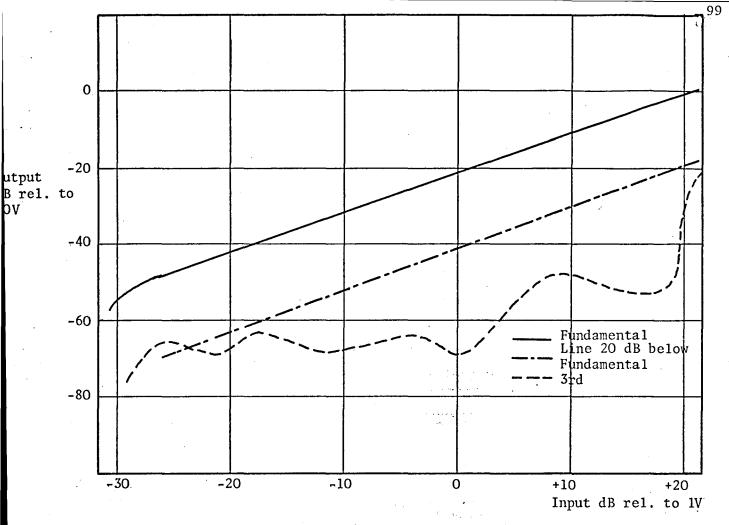

| Experimental Tests on the Two        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Modulators                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

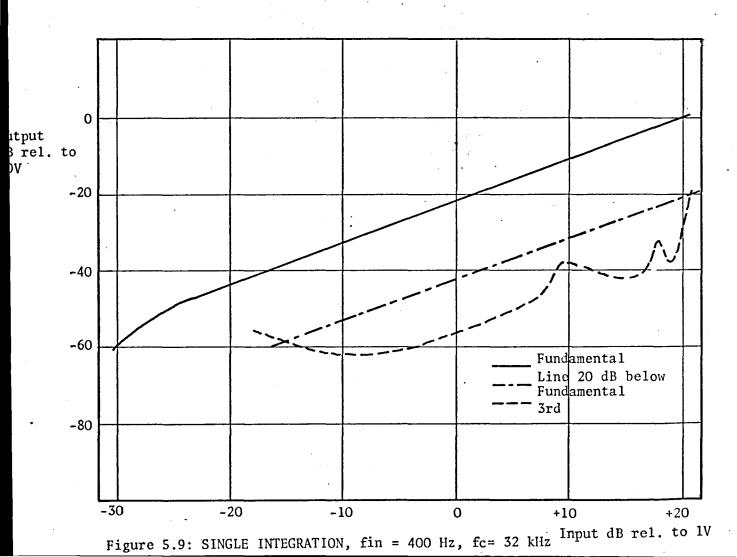

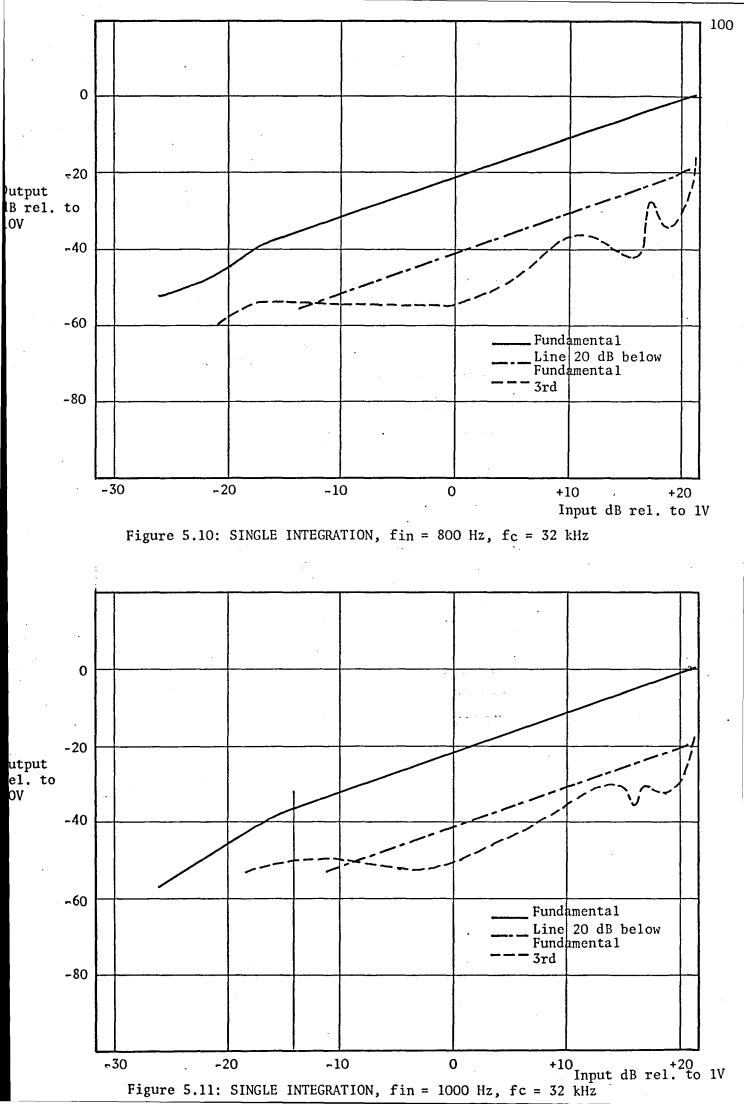

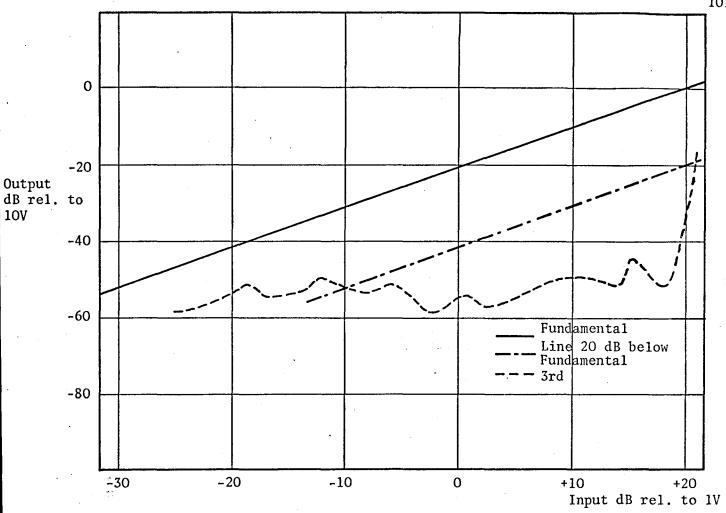

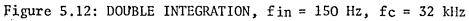

| 5.4.1 Harmonic Content               | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

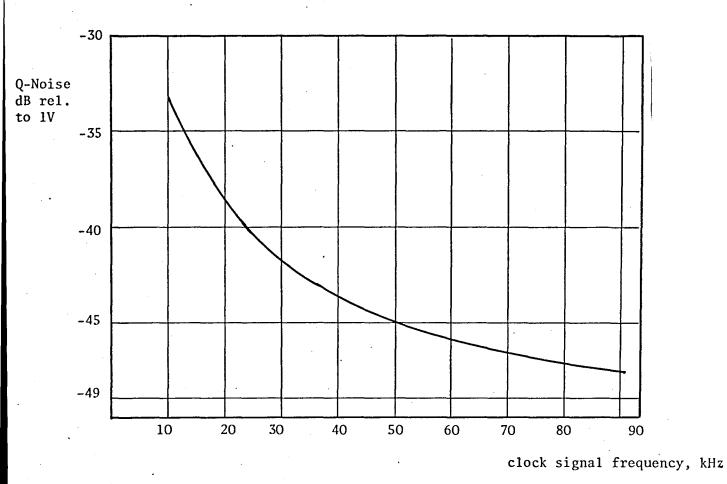

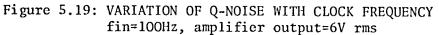

| 5.4.2 Quantisation Noise             | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.4.3 Discussion                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

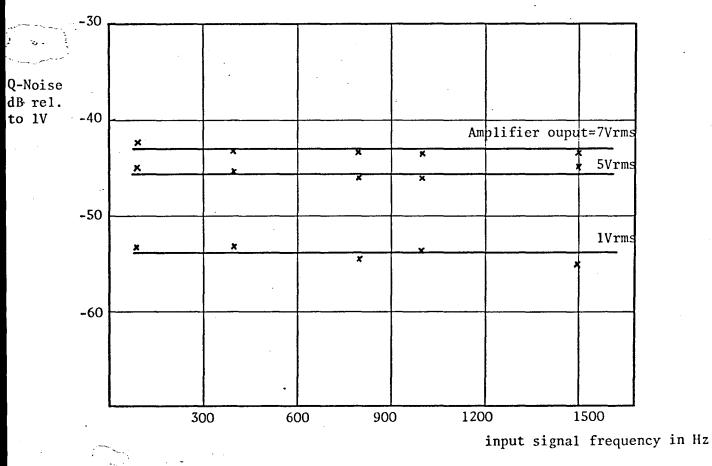

| Bistable Delta Sigma Modulator       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.2 Performance of the Modulator   | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.3 Synchronisation of the Clock   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal to the Input Signal           | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | Single Integration.<br>5.1.1 Input Amplifier.<br>5.1.2 Comparator.<br>5.1.3 Flip-Flop.<br>5.1.4 Binary Level Converter.<br>5.1.5 RC Integrator.<br>Design of Delta Sigma Modulator with<br>Double Integration.<br>Theoretical Assessment of the Two<br>Modulators.<br>Experimental Tests on the Two<br>Modulators.<br>5.4.1 Harmonic Content.<br>5.4.2 Quantisation Noise.<br>5.4.3 Discussion.<br>Bistable Delta Sigma Modulator.<br>5.5.1 Clock Pulse Generator.<br>5.5.2 Performance of the Modulator<br>5.5.3 Synchronisation of the Clock |

| CHAPTER 6: | APTER 6: |

|------------|----------|

|------------|----------|

### THE DEVELOPMENT OF THE SPEED CONTROL SYSTEM

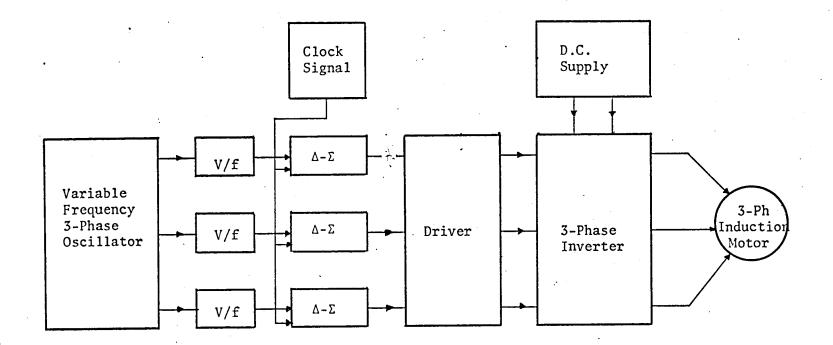

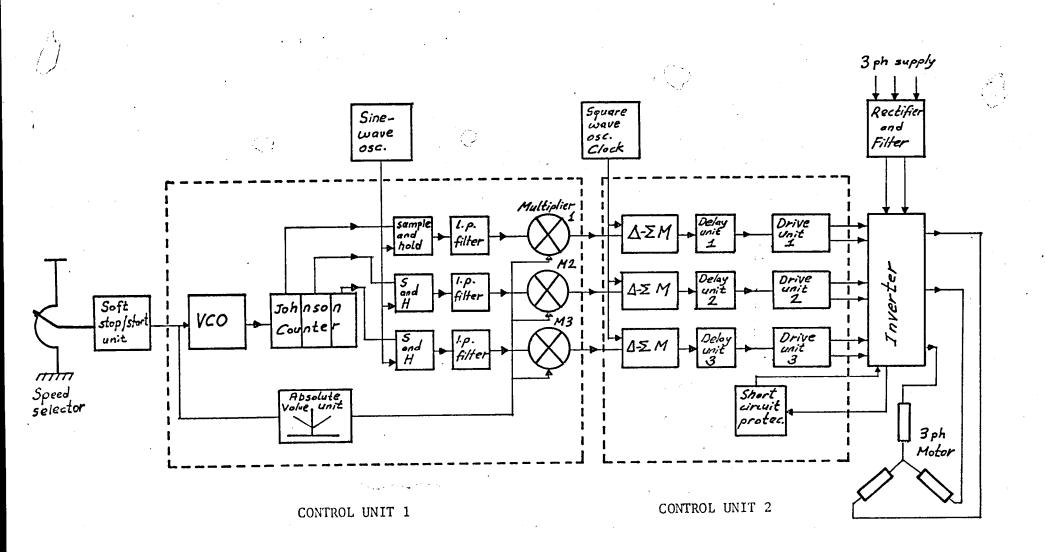

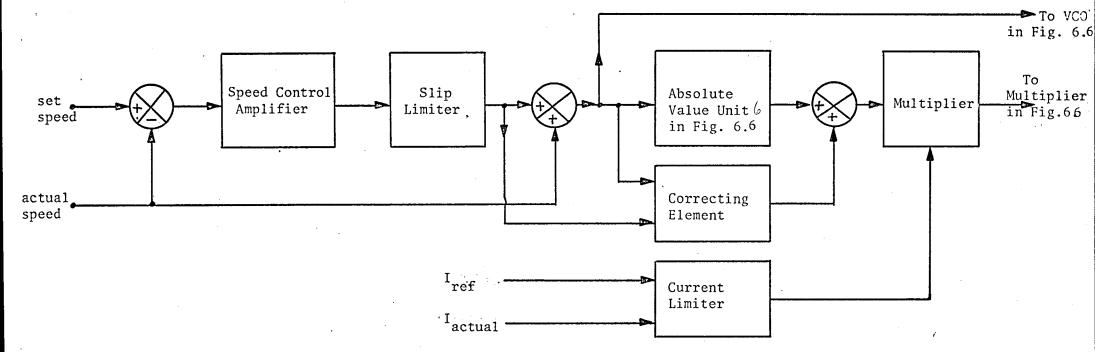

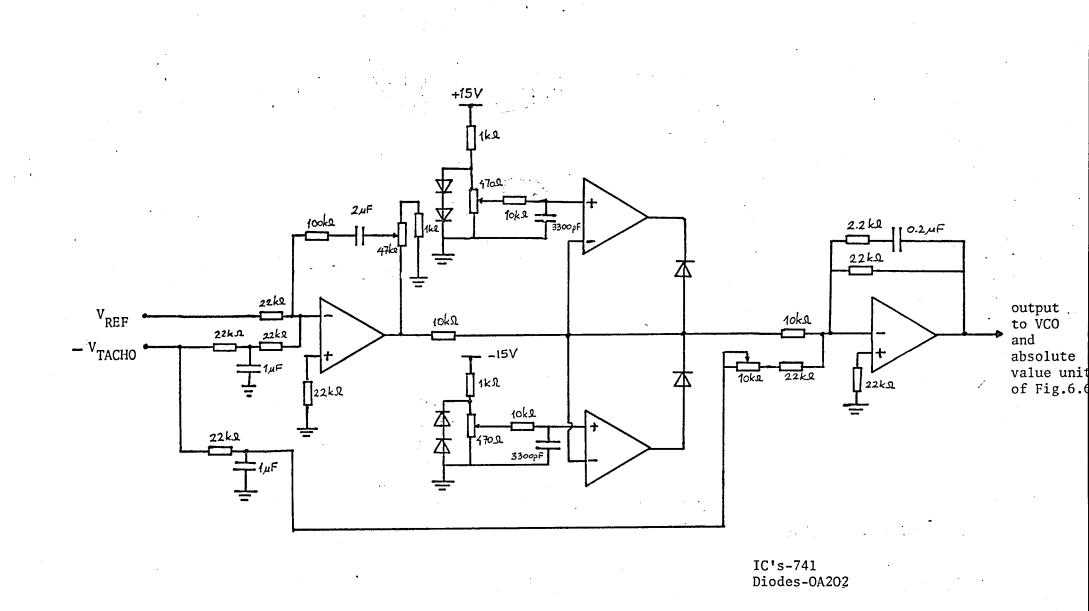

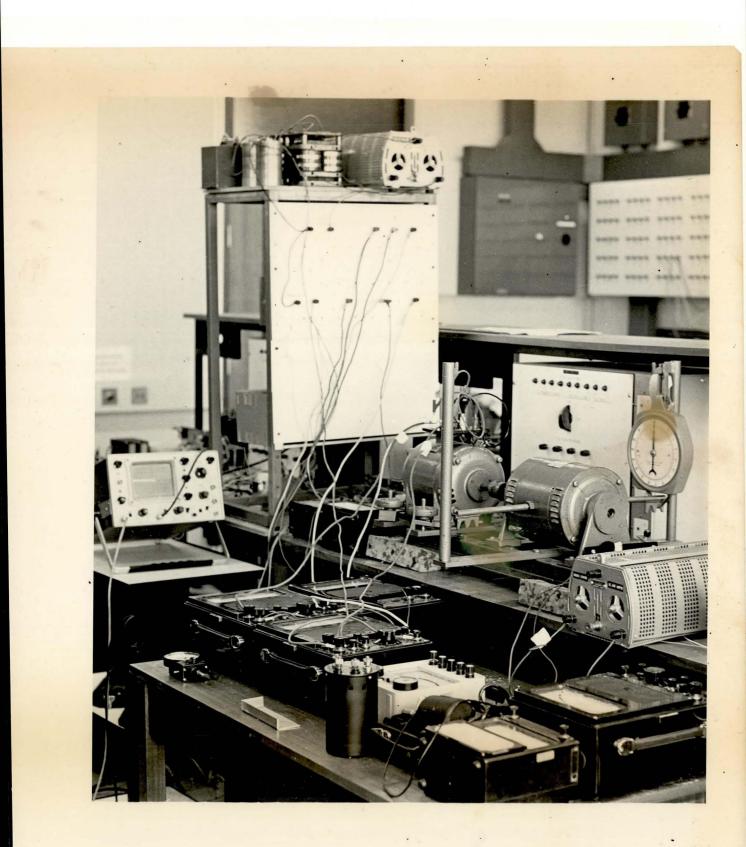

| 6.1 | Protot | ype System                      | 117 |

|-----|--------|---------------------------------|-----|

|     | 6.1.1  | 3-Phase Variable Frequency      |     |

|     |        | Oscillator                      | 117 |

|     | 6.1.2  | V/f Control Circuit             | 117 |

|     | 6.1.3  |                                 | 118 |

|     | 6.1.4  | The Driver and the Inverter     | 118 |

|     | 6.1.5  | Discussion                      | 119 |

| 6.2 | Improv | red Speed Control System        | 119 |

|     | 6.2.1  | System Block Diagram            | 119 |

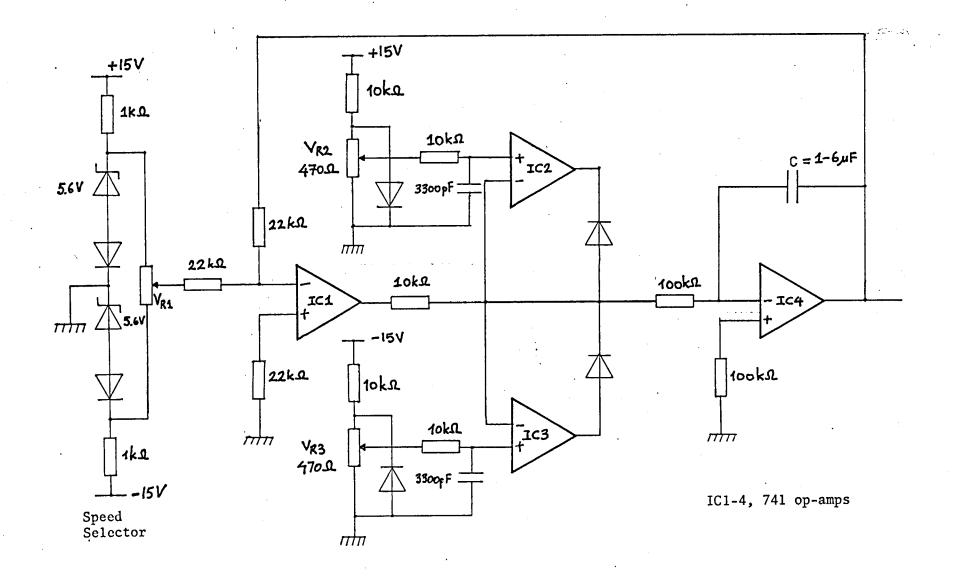

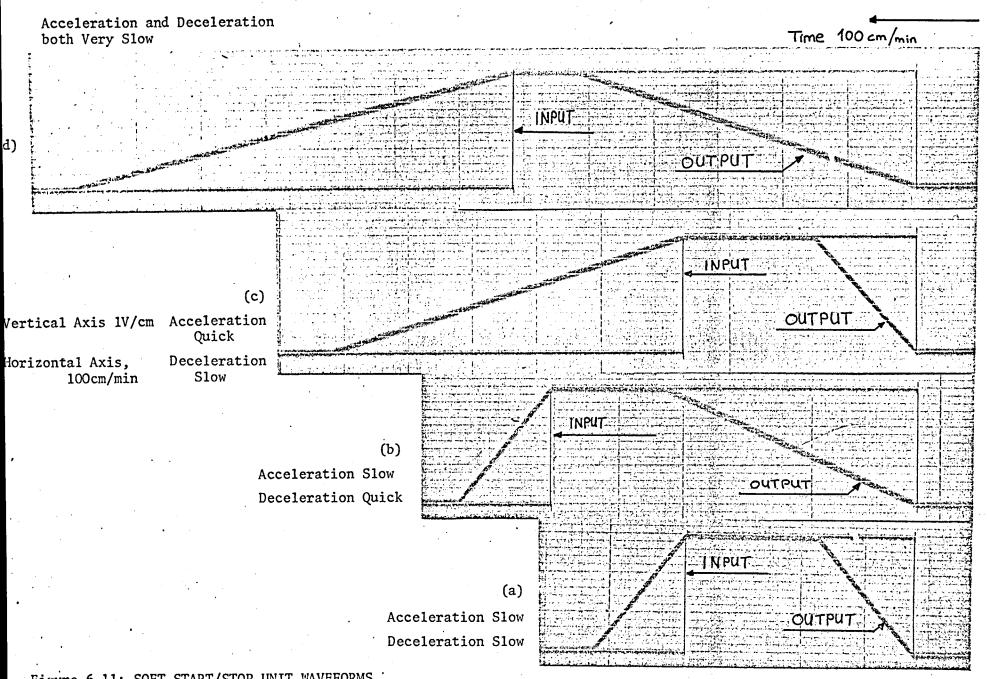

|     | 6.2.2  | Soft Start/Stop Unit            | 120 |

|     | 6.2.3  |                                 |     |

| ·   |        | Voltage Controlled 3-Phase      |     |

|     | :      | Oscillator                      | 122 |

|     |        | 6.2.3.1 Voltage Controlled      |     |

|     |        | Oscillator                      | 124 |

|     |        | 6.2.3.2 3-Stage Johnson Counter | 125 |

|     |        | 6.2.3.3 Sine Wave Oscillator    | 126 |

|     |        | 6.2.3.4 Sample and Hold Circuit | 127 |

|     |        | 6.2.3.5 Low-Pass Filter         | 127 |

|     |        | 6.2.3.6 Performance             | 128 |

|     | 6.2.4  | V/f Control Unit                | 129 |

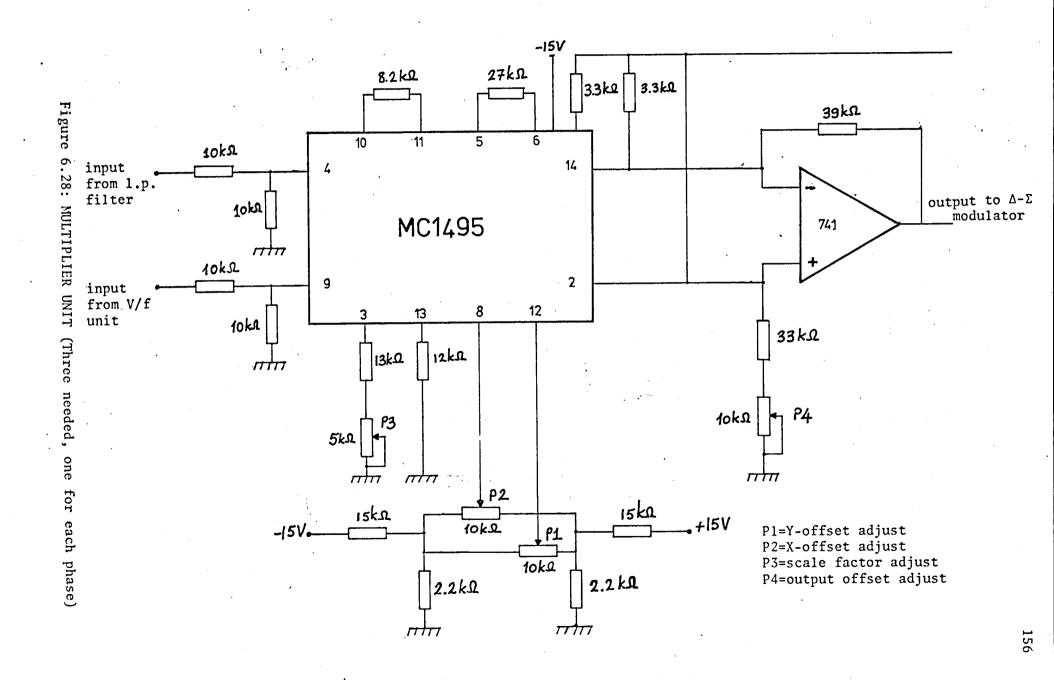

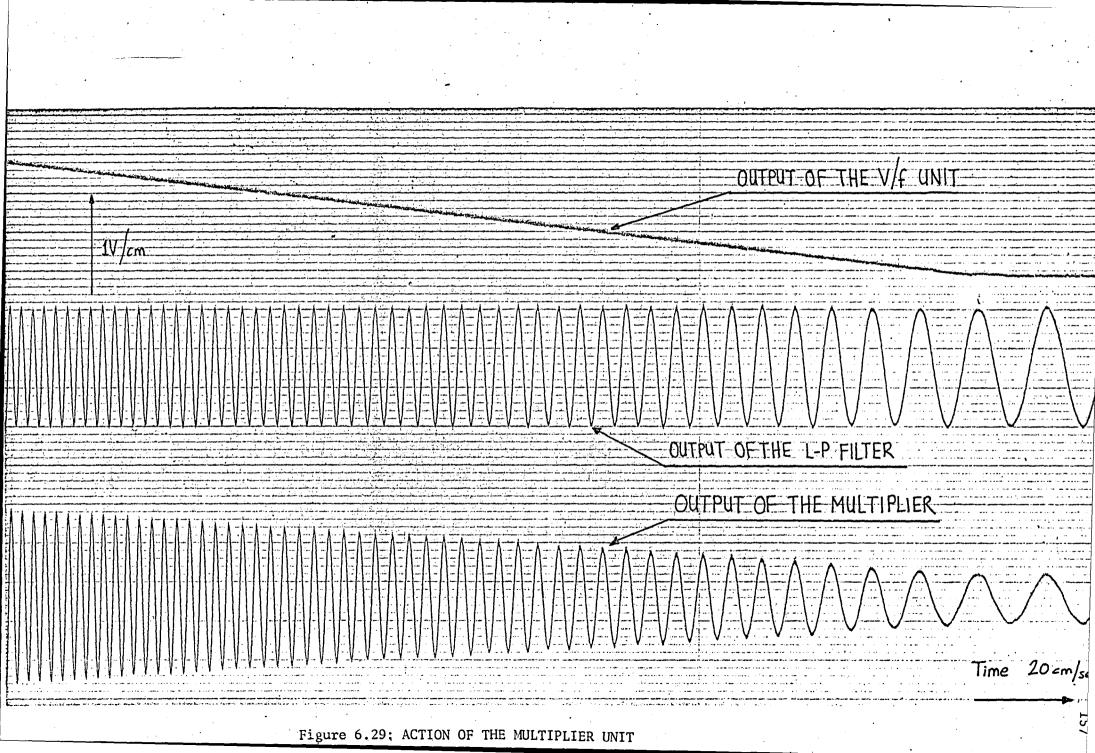

|     | 6.2.5  | Multiplier Unit                 | 129 |

|     | 6.2.6  | Modulator Unit                  | 130 |

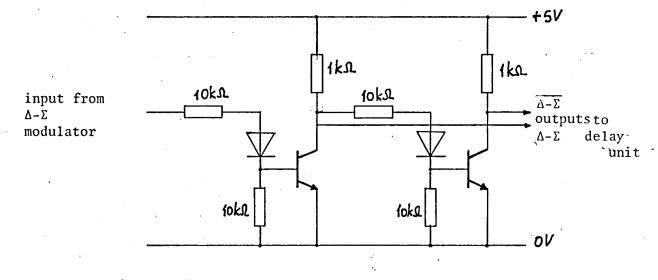

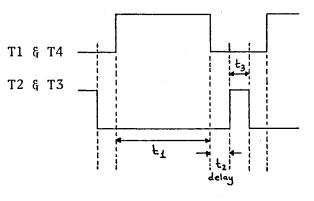

|     | 6.2.7  | Delay Unit                      | 131 |

|     | 6.2.8  | Power Supplies                  | 131 |

| 6.3 | Perfor | mance of the Control Unit       | 132 |

CHAPTER 7:

### DRIVER AND INVERTER DESIGN

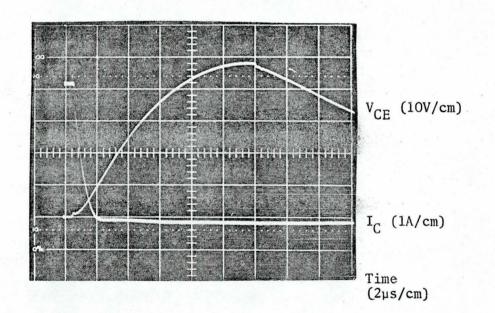

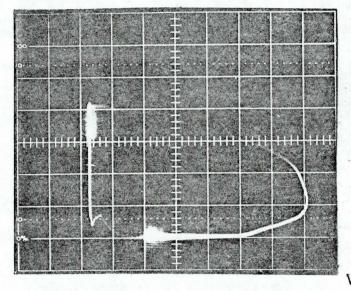

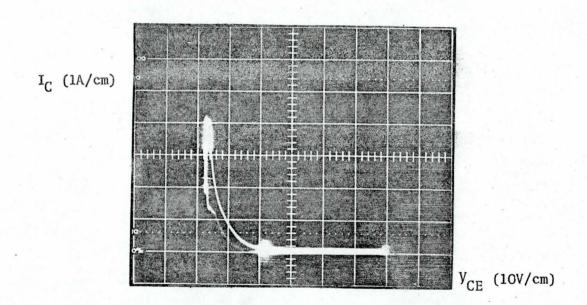

| 7.1 | Transi  | stor Switching Characteristics    | 166 |

|-----|---------|-----------------------------------|-----|

|     | 7.1.1   | Transistor in"on" and "off" Mode. | 166 |

| •   | 7.1.2   | Transistor During "Turn-on"       | 167 |

|     | 7.1.3   | Transistor During "Turn-off"      | 168 |

|     | 7.1.4   | Driver Requirements               | 168 |

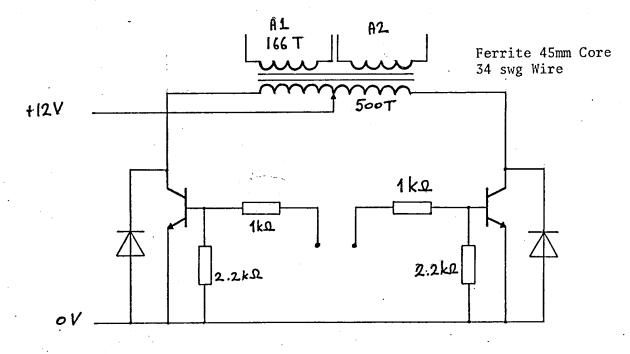

| 7.2 | Transfo | ormer Drive                       | 169 |

|     | 7.2.1   | Design of Transformer,            | 172 |

|     | 7.2.2   | Performance of the Driver         | 173 |

| 7.3 | Direct  | Drive                             | 174 |

|     | 7.3.1   | Design                            | 174 |

|     | 7.3.2   | Performance                       | 175 |

|     | 7.3.3   | Load Line Shaping to Limit dV/dt. | 177 |

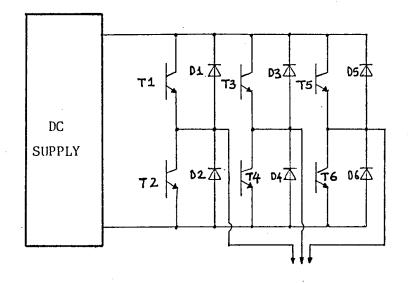

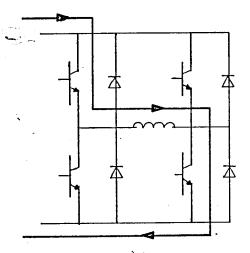

| 7.4 | Inverte | er Design                         | 178 |

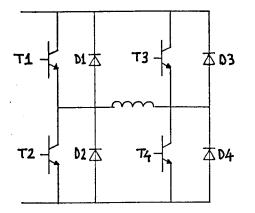

|     | 7.4.1   | Basic Inverter                    | 178 |

|     | 7.4.2   | Voltage Supply                    | 179 |

|     | 7.4.3   | Action of Fast Recovery Diodes    | 179 |

|     | 7.4.4   | Inverse Mode Operation of         |     |

|     |         | Transistors                       | 180 |

|     | 7.4.5   | Overcurrent Protection Circuit    | 181 |

|     | 7.4.6   | Phase Current Monitor Unit        | 182 |

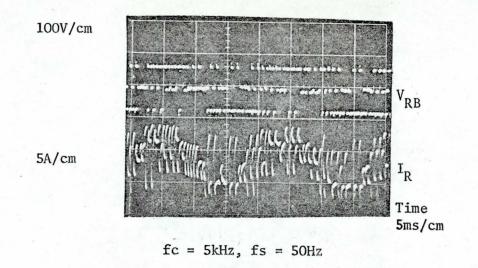

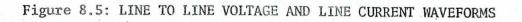

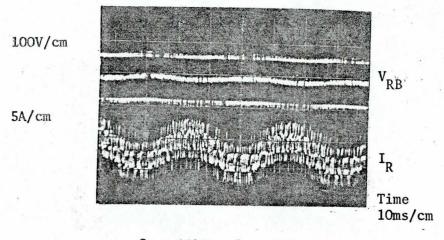

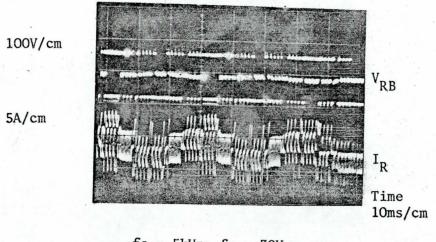

| CHAPTER 8:   | EXPERIMENTAL INVESTIGATION AND PERFORMANCE OF INDUCTION MOTOR DRIVEN BY A $\Delta$ - $\Sigma$ MODULATED INVERTER                                                        |                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|              | <ul> <li>8.1 Inverter Waveforms</li></ul>                                                                                                                               | 209<br>209<br>211<br>212<br>215 |

|              | <ul> <li>8.3.1 Sine Wave Supply</li> <li>8.3.2 Δ-Σ Modulated Input</li> <li>8.4 Efficiency of Induction Motor</li> <li>8.5 Dynamic Performance of the System</li> </ul> | 216<br>217<br>218<br>219        |

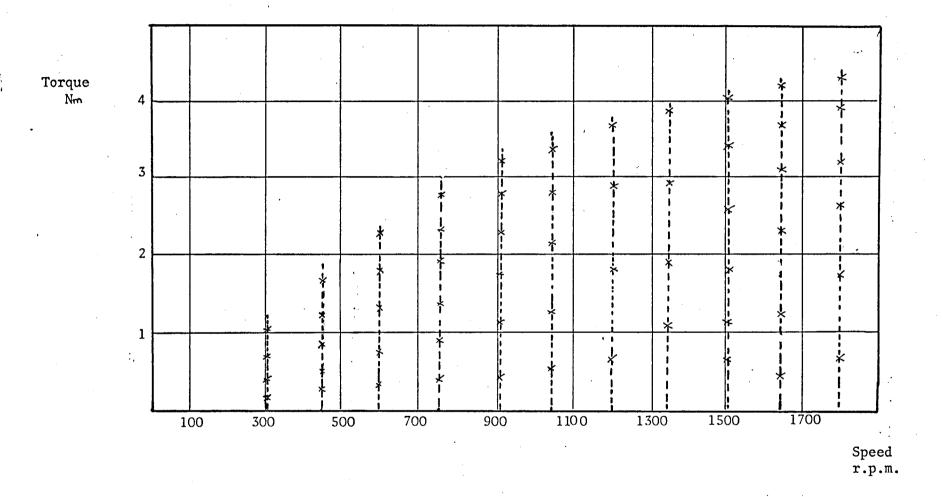

| CHAPTER 9:   | OPERATION IN CLOSED LOOP MODE                                                                                                                                           |                                 |

|              | <ul><li>9.1 Control Techniques</li><li>9.2 Design</li><li>9.3 Performance of the Induction Motor on</li></ul>                                                           | 239<br>241                      |

|              | Closed-loop<br>9.4 Advantages of Operation in Closed-loop<br>Mode                                                                                                       | 243<br>244                      |

| CHAPTER 10:  | CONCLUSIONS                                                                                                                                                             | 251                             |

| REFERENCES   |                                                                                                                                                                         | 258                             |

| APPENDIX I:  | CALCULATION OF QUANTISATION NOISE                                                                                                                                       | 261                             |

| APPENDIX II: | PROGRAM LISTING                                                                                                                                                         | 265                             |

| APPENDIX III | DESIGN EQUATIONS FOR 3-PHASE BRIDGE RECTIFIER                                                                                                                           | 277                             |

# CHAPTER 1

# INTRODUCTION

#### 1.1 GENERAL

There are many special-purpose industrial drives which require variable-speed operation. In general, variable-speed motor systems have used D.C. and/or A.C. commutator motors where a large speed range is required. In this respect, the Ward-Leonard system using a D.C. generatormotor combination is the traditional drive. The outstanding advantage of these machines is the ease with which their speed may be controlled, and yet provide a suitable torque at all speeds. Their major weakness is the commutator and brushgear assembly, giving rise to commutation problems and the need for regular servicing.

By contrast, the A.C. induction motor, which usually operates at an almost fixed speed, has a number of distinct advantages. In particular, in its Squirrel Cage form it is brushless, cheap, simple, reliable and requires little servicing. It can be operated in practically any environment, and run at a higher speed and over a wider temperature range than the commutator motor.

It can be seen that a variable-speed A.C. induction motor is the most desirable solution to many industrial problems. For this reason, the use of induction motors for variable-speed drive systems has attracted a lot of attention in the past.

Induction motors<sup>1</sup> are fundamentally single-speed machines, that speed being dependent on the frequency of the power supply. The speed of an induction motor is given by the following expression:

$$n = \frac{f}{p} (1-s)$$

(1.1)

where,

- n = Speed in rev/sec

f = Frequency of supply

p = Number of poles

- s = Slip

It is obvious from equation (1.1) that there are three possible methods of varying the speed;

• a) Varying the number of poles, p

The speed can be varied in steps by changing the number of poles, whilst maintaining a constant supply frequency. Pole-changing motors are specially wound and widely used for this purpose.

b) Varying the slip, s

In order to vary the slip at a constant torque, resistors can be connected in the rotor circuit of slip-ring induction motors. This means of control is, however, largely dependent on load, and cannot be applied to squirrel-cage motors.

c) Varying the supply frequency, f

Since the speed is approximately proportional to the frequency, the speed of a squirrel-cage induction motor can be varied by variation of the frequency.

#### **1.2** ROTATING MACHINE SYSTEM

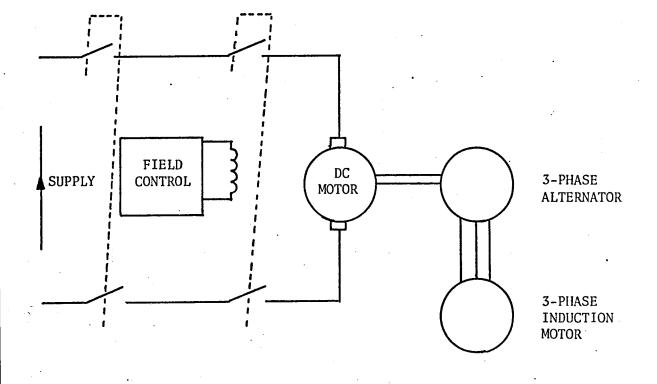

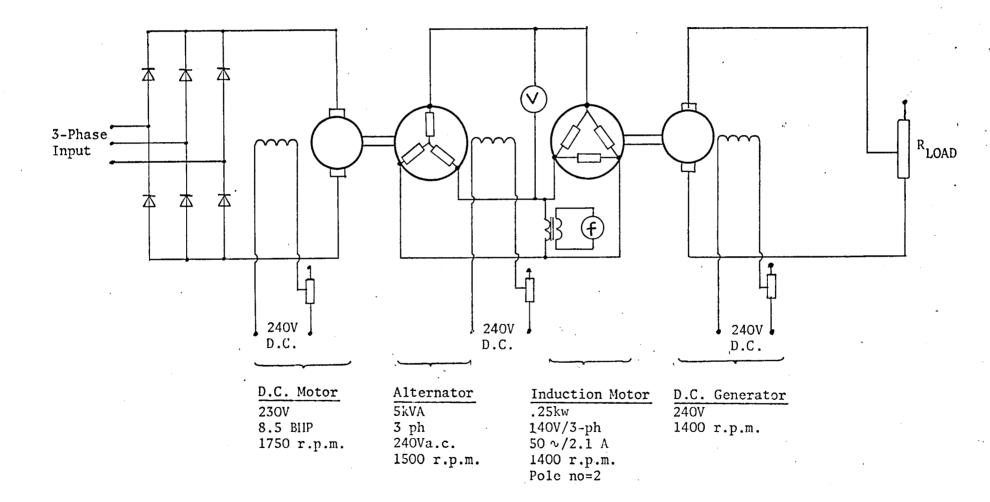

In the past the solution to the problem of a variable-frequency supply lay in the use of rotating machines, (Figure 1.1). A D.C. motor, the speed of which was controlled by varying the field excitation, was used to drive a 3-phase alternator, which produced the required supply voltage at a controlled frequency. This output was used to drive the induction motor.

The disadvantages of this system are the high cost and maintenance requirements, coupled with the fact that the system has a limited frequency range.

#### 1.3 STATIC INVERTER SYSTEM

Static inverters enable a supply of direct current or alternating current of one frequency to be converted to a supply of alternating current at some other frequency. The conversion of very large powers can be accomplished with thyristor inverters, which have now replaced much of the rotating electrical machinery that was previously used for frequency changing.

The static inverter system, which uses high-power electronic components to produce a 3-phase supply of variable frequency, first became realisable with the development of the thyratron, a thermionic device capable of conducting in one direction only, and then only after an "enabling" pulse has been applied to the gate terminal. However, the use of thyratron systems was limited by both the very high price of these devices (typically a 12 A thyratron could cost £50), and their short service life (typically one or two years).

The advent of the silicon controlled rectifier, or thyristor, enabled practical systems for static inversion to be developed. Thyristors have electrical characteristics similar to thyratrons, but cost only one tenth of the price. Theoretically they have an infinite service life, provided that they are operated within their ratings, and being solid-state devices they require no maintenance and they can be directly controlled electronically. These advantages have resulted in thyristor-based systems superceding motor-generator systems, and the installation of thyristorcontrolled induction motor drive systems is now growing at a rapidlyincreasing rate.

With the appearance on the market of medium-power, high-voltage, fastswitching transistors, the application of transistorized inverters for the speed control of A.C. machines has become a practical reality. Transistors offer some important advantages over thyristors. Since they can be switched off easily, by the removal of base drive and the application of a

voltage of reverse polarity to the base-emitter junction, there is no need for any commutation components, and the problem of trapped energy is solved. They can also be operated at very high frequencies.

#### **1.4** OBJECT OF INVESTIGATION

The object of the present investigation is to determine the applicability of delta-sigma modulation to the control of a small 3-phase induction motor. The work falls mainly into the following categories:

- (i) Investigation of the characteristics of delta-sigma modulation, from the point of view of speed control.

- (ii) Design and construction of a satisfactory wide-range speed control system which has the facilities of speed reversal, acceleration and deceleration control and the facility for operation in a closed-loop mode.

- (iii) Design and construction of a suitable driver and power transistor inverter for the amplification of delta-sigma modulated signals to supply an induction motor.

- (iv) Investigation of the performance of the induction motor when fed from a delta-sigma modulated inverter.

INDUCTION MOTOR SPEED CONTROL USING ROTATING MACHINES

# CHAPTER 2

# CHARACTERISTICS OF INDUCTION MOTORS AND

# SPEED CONTROL TECHNIQUES

#### 2.1 INDUCTION MOTOR CHARACTERISTICS

#### 2.1.1 Torque-Speed Characteristics

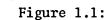

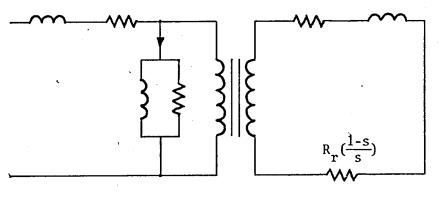

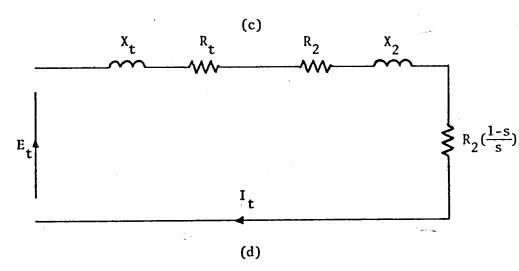

Before elaborating on the methods of static inversion which can be used to drive induction motors, it is worthwhile considering the behaviour of such motors on sinusoidal supplies, and for this purpose it is helpful to study the equivalent circuits of the motor shown in Figure 2.1.

In Figure 2.1.a we have the basic per-phase equivalent circuit<sup>4</sup> at a slip s. Considering the motor reduced to standstill with the mechanical power output represented by the power loss in a resistance equal to  $R_r \frac{1-s}{s}$ , leads to the equivalent circuit shown in Figure 2.1.b. By referring the motor impedances to the stator, and assuming the transformer to be ideal, we obtain the equivalent circuit shown in Figure 2.1.c. Finally, by applying Thevenin's theorem, the equivalent circuit shown in Figure 2.1.d is obtained, where:

$$E_{t} = \frac{jXE_{1}}{R_{1}+j(X_{1}+X_{0})} , \qquad (2.1)$$

$$R_{t}+jX_{t} = \frac{jX_{0}(R_{1}+jX_{1})}{R_{1}+j(X_{0}+X_{1})} , \qquad (2.2)$$

in which:

E<sub>1</sub> = input voltage per phase

R<sub>1</sub> = resistance of stator per phase

X<sub>1</sub> = leakage reactance of stator per phase

X<sub>0</sub> = magnetising reactance

Assuming the power required for the core loss is included in the mechanical output, the stator current/phase is:

$$I_{t} = \frac{E_{t}}{\sqrt{(R_{t} + \frac{R_{2}}{s})^{2} + (X_{t} + X_{2})^{2}}} \qquad (2.3)$$

The torque developed by the motor is calculated by equating the actual mechanical output at a speed  $\omega_s$  to the electrical power dissipated in the equivalent resistor  $R_2 \frac{(1-s)}{s}$  of Figure 2.1.c. i.e.  $T_*\omega_s(1-s) = I_t^2 R_2 \frac{(1-s)}{s}$ . Substituting for  $I_{+}$  from equation (2.3)

$$T = \frac{E_t^2 R_2 s}{\omega_s (s R_t^{+} R_2)^2 + s^2 (X_t^{+} X_2)^2} , \qquad (2.4)$$

The maximum or pull-out torque is found by differentiating equation (2.4) with respect to s and equating to zero, giving the slip for maximum torque as +R

$$s_{\rm m} = \frac{1 - N_2}{\sqrt{R_t^2 + (X_t + X_2)^2}}$$

, (2.5)

and, by substituting this in equation (2.4), the maximum torque as,

$$T_{max} = \pm \frac{E_t^2}{2\omega_s (R_t + \sqrt{R_t^2 + (X_t + X_2)^2})}, \qquad (2.6)$$

Equations (2.5) and (2.6) show that the rotor resistance does not effect the maximum torque produced by the motor, but only the speed or slip at which this occurs. If, for simplicity the stator parameters are neglected, the equations for the current and torque reduce to:

$$I = \frac{E_2}{\sqrt{X_2^2 + \frac{R_2^2}{s^2}}}, \qquad (2.7)$$

and

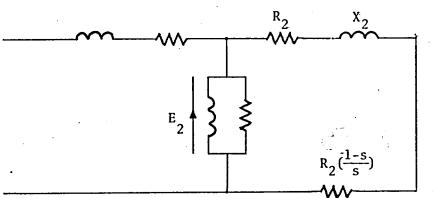

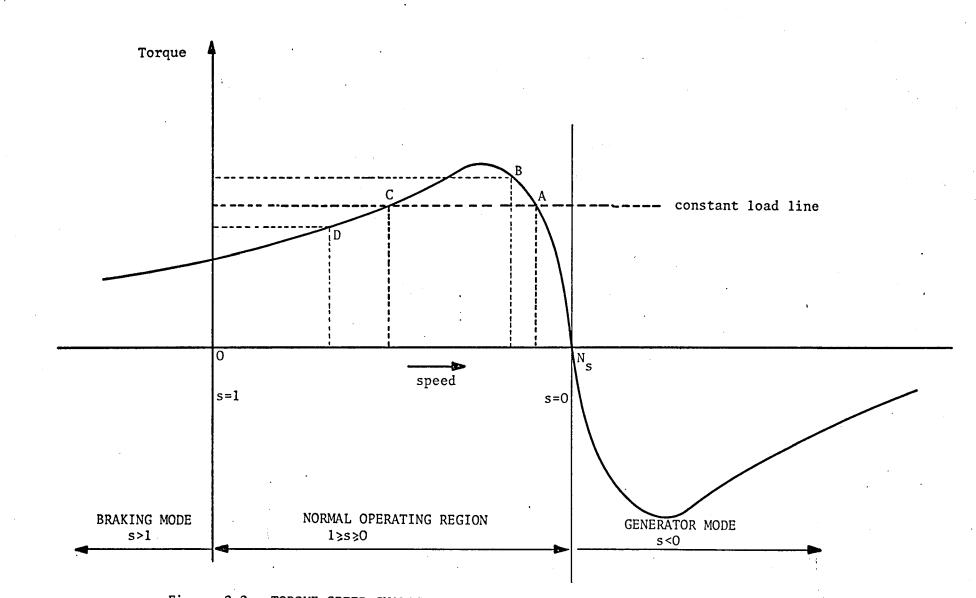

$$\Gamma = \frac{E_2^2 R_2 s}{\omega_s (R_2^2 + X_2^2 s^2)} , \qquad (2.8)$$

respectively. Equation (2.8) has two asymptotes; for s large T  $\alpha$   $\frac{1}{s}$  and for s small T  $\alpha$  s. The characteristics are shown in Figure 2.2. The operating region for motor action is between zero speed (s=1) and synchronous speed (s=0), and if the motor runs above synchronous speed (by being driven externally) it acts as an asynchronous generator feeding power to the supply. For a slip greater than 1, the machine is in a braking mode, a possibility exploited either by disconnecting the machine from the a.c. supply and injecting d.c. at the stator terminals (dynamic braking) or by interchanging any two of the three stator connections (plugging).

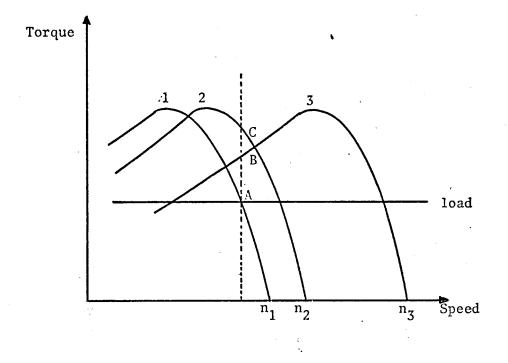

#### 2.1.2 Induction Motor Drive Stability

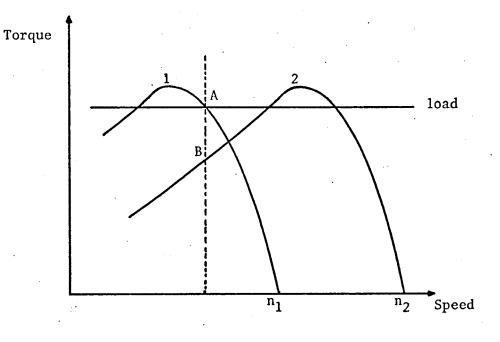

The matching of a motor with the load characteristics is of prime importance in any electrical drive, and a simple assessment of the ability of an induction motor to cope with a particular load situation may be considered with the assistance of Figure 2.2.

Assuming the motor is operating against a constant load torque, such that a balance is obtained when the motor and load characteristics intersect at A, it can be seen that should the speed decrease by a small increment (say to B), there is an excess of torque available to raise the speed back to that at A. Correspondingly, if the speed increases, insufficient torque is available to maintain the increase and the speed falls back to that at A. In both cases, the initial conditions are restored and the system is stable. However, operating at C does not fulfill this requirement, since a fall in speed to D is accompanied by a fall in the torque produced by the motor, resulting in a continued and rapid decelaration to standstill.

The above arguement shows qualitatively that the only stable operating region for an induction motor is on the negative slope region of its characteristics, so that for the motor to be driven over the widest possible speed range the region of negative slope must be extended to the whole of that range.

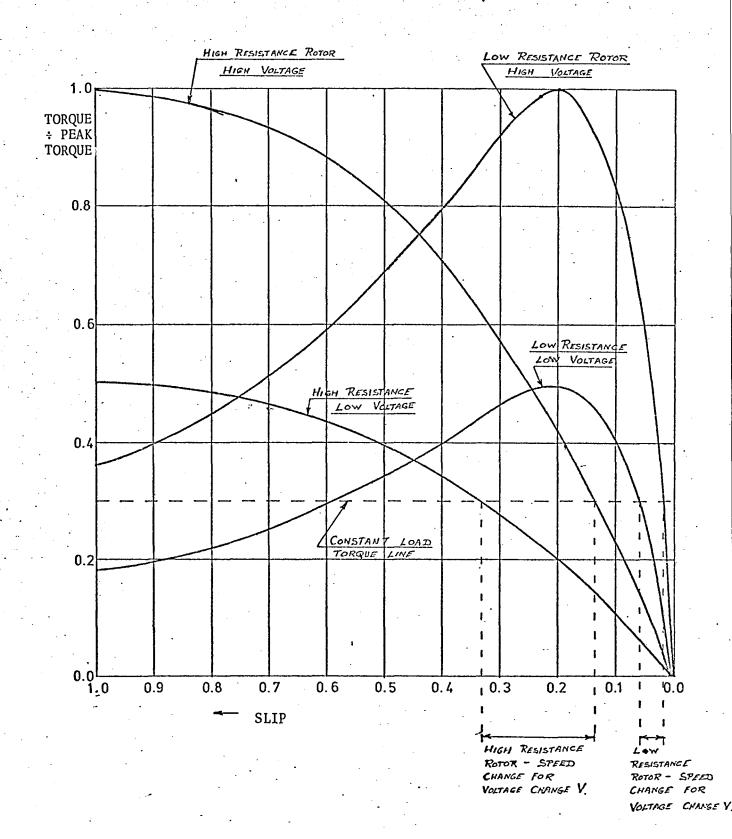

### 2.1.3 Effect of Input Voltage and the Rotor Resistance on the Torque-Speed Characteristics

Before discussing efficient methods of extending the negative-slope region of the torque-speed characteristic, it is valuable to consider the effect of input voltage and rotor resistance on this characteristic.

Increasing the rotor resistance increases the slip at which maximum torque is produced, and modifies the characteristic as shown in Figure 2.3. It can be seen that the negative slope region of the characteristics can be much extended, enabling the speed to be controlled over a wide range simply

by varying the voltage applied to the stator. However, although a given variation in the supply voltage produces a significantly greater speed change for a high resistance rotor, it involves excessive rotor-heating and requires the motor to be down-rated to prevent thermal damage. Such drives are therefore uneconomic, and the use of low resistance rotors for all drives exceeding about 1/2 hp is universal.

#### 2.1.4 Extension of Negative Slope Region by Variation of Supply Frequency

The negative slope region of a low rotor-resistance motor can be extended over the full speed range desired by changing the frequency of the supply. With the applied voltage assumed to be almost equal to the induced emf, then

$$V = k\Phi f$$

, (2.9)

where:

k = constant involving the form factor, the winding factor and the number of turns of the winding,

$\Phi$  = maximum flux per pole,

V = r.m.s. voltage applied.

Since an induction motor is designed to work at a given magnetic loading, the applied voltage must be varied in proportion to the frequency if the flux is to be kept constant. If V, but not V/f, is kept constant, and the frequency is decreased below the design frequency, the magnetic circuit saturates, whereas if the frequency is raised above the design frequency the iron circuit is not used to its fullest capabilities. Under the condition of V/f constant, the normalised form of the torque-speed characteristic is substantially unchanged by any variation of this ratio, being primarily dependent on the slip speed, until the frequency is sufficiently low for the magnetising reactance to become comparable with the rotor circuit impedance.

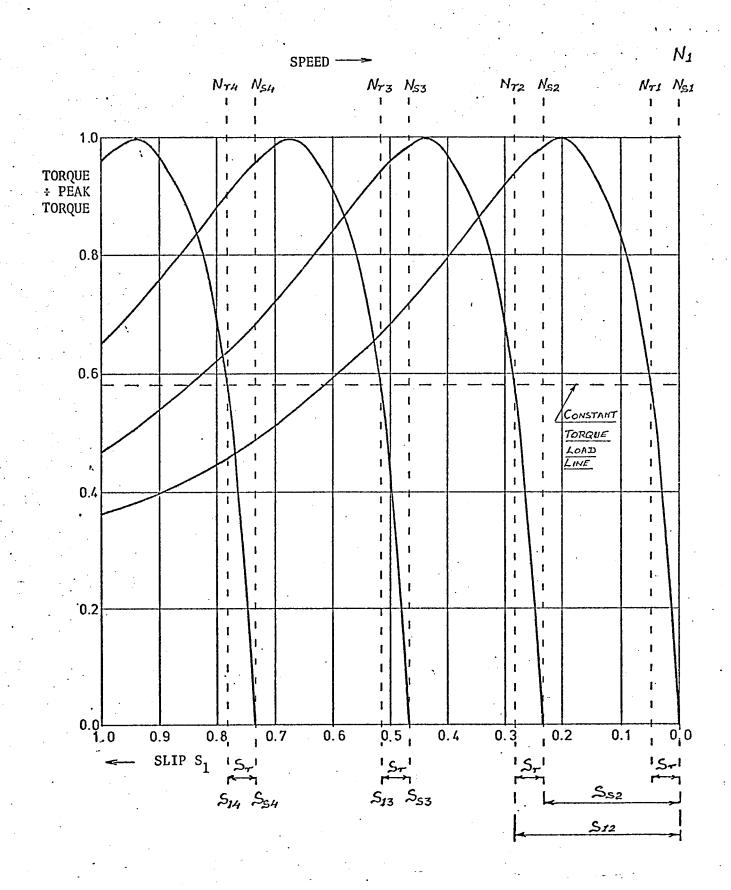

The characteristics of the induction motor as the supply frequency is changed can be derived from the equivalent circuit, with the supply

frequency ( $\omega_s$ ) treated as a variable, and the overall slip calculated to a base of the new maximum frequency ( $\omega_1$ ). Since the supply frequency is varied X<sub>2</sub> is no longer constant, and when it is replaced with the more explicit impedance term  $\omega_s L_s$ , equation (2.7) becomes,

$$I = \sqrt{\frac{R_2}{\frac{R_2}{s^2} + \omega_s^2 L_2^2}}$$

where s = slip =  $(\omega_s - \omega_r)/\omega_s$ .

Since the torque is given by,

$T = \frac{I^2 R_2}{\omega_s s}$

it follows that,

$$T = \frac{E_2^2}{\omega_s^2} \cdot \frac{(\omega_s - \omega_r)R_2}{R_2^2 + L_2^2(\omega_s - \omega_r)^2},$$

If

$s_1 = \text{slip to base frequency } \omega_1 = (\omega_1 - \omega_r)/\omega_1$   $s_s = \text{synchronous speed slip to base frequency } \omega_1 = (\omega_1 - \omega_s)/\omega_1$  $s_r = \text{rotor slip to base frequency } \omega_1 = (\omega_s - \omega_r)/\omega_1$

then '

$$s_r = s_1 - s_s$$

and from equation (2.11)

$$T = \frac{E_2^2}{\omega_s^2} \cdot \frac{\omega_1 R_2 s_r}{R_2^2 + \omega_1 L_2^2 s_r^2}$$

and letting  $X_a = \omega_1 L_2 = \omega_1 X_2 / \omega_s$

$$T = \frac{E_2^2}{\omega_s^2} \cdot \frac{\omega_1 R_2 s_r}{R_2^2 + X_a^2 s_r^2}$$

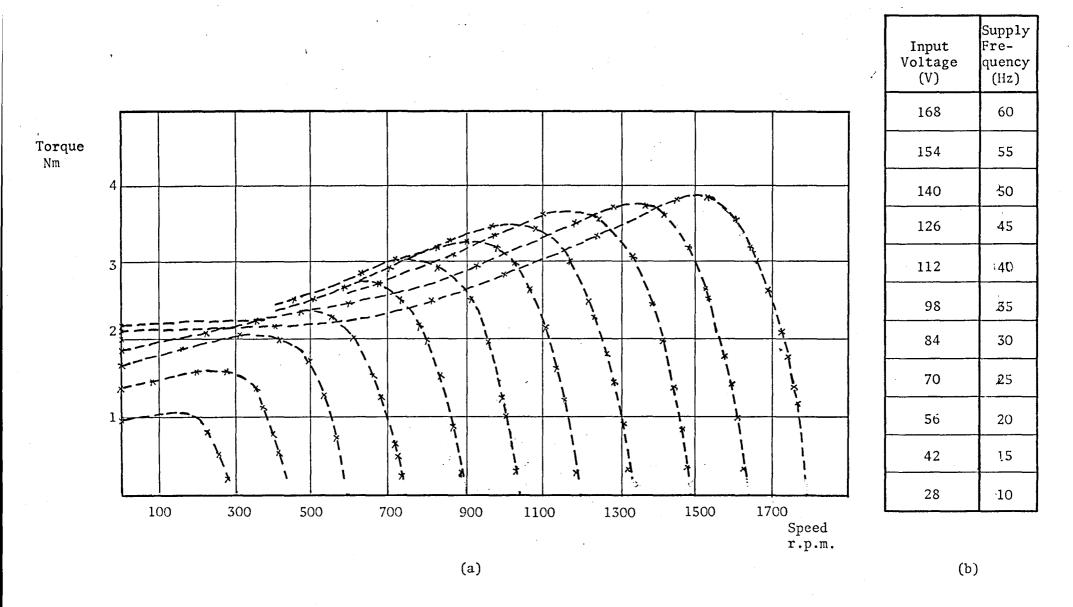

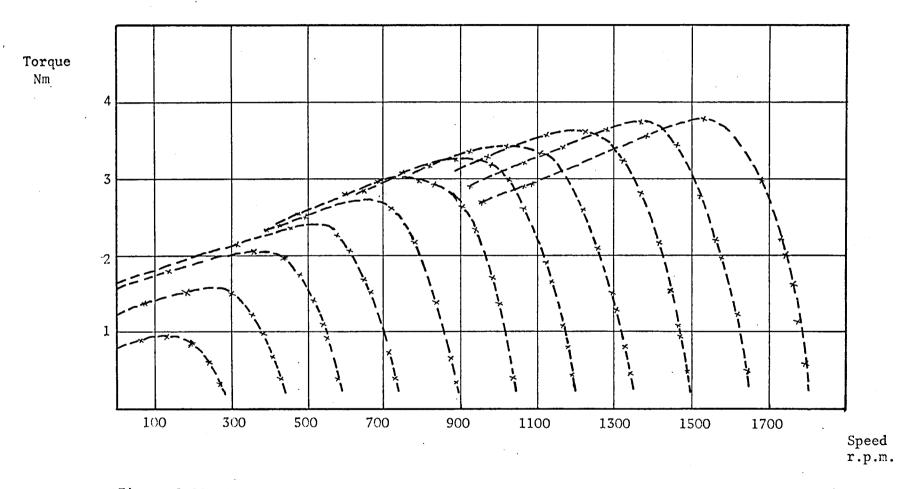

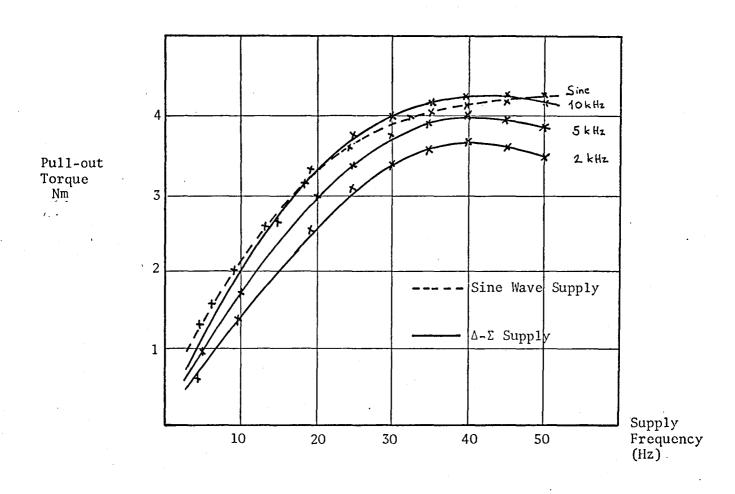

Equation (2.12) has the same form as equation (2.8) and it therefore gives a torque/slip characteristic of the same shape, provided that  $E_2/N_s$  is maintained constant, as shown by the family of curves in Figure 2.4 for various values of  $s_s$ .

(2.10)

(2.11)

(2.12)

#### 2.2 DIFFERENT SPEED CONTROL TECHNIQUES

The past decade has seen the development of many techniques suitable for the variable-speed control of a.c. motors in general and induction motors in particular. Different design requirements such as speed range, efficiency and maximum allowable losses, torque requirements, speed reversal, dynamic response, environmental and economic considerations, and accuracy of control are some of the factors which affect the choice between the different methods available.

Induction motors can have either a slip-ring, a squirrel-cage or a solid-iron rotor. Each has its particular area of application, in which different control techniques may be adapted. In drives where the speed normally varies only within a small range in the vicinity of the maximum value (for instance, in continuous rolling mills, blowers and marine propulsion), the preference is for slip-ring motors. For drives in dirty atmospheres, where corrosive vapours are present, or where there is a risk of explosion, squirrel-cage motors are mainly used. Some special loads may demand ultra-high speed drives, and when conventional laminated rotors with squirrel cages may not withstand the high centrifugal stresses involved a solid iron rotor structure is adopted. These and many other factors affect the choice of control techniques to be used.

Generally speaking, the frequency and the supply voltage must be controlled in harmony for a satisfactory speed control system. However, the exact relationship may depend on the purpose to which the motor is put. The torque produced depends on the magnitude of the rotating magnetic field and the rotor current, which in turn depends on the slip frequency and is reflected in the stator current. Hence, if the maximum rated torque of the motor is required at all speeds, the control system should be designed to maintain a constant flux density under all conditions. Over most of the speed range, this demands a voltage approximately proportional to frequency, but at very low speeds the voltage must be increased somewhat above the

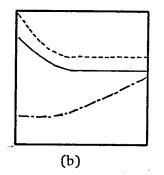

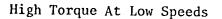

proportional value. In some applications, it is necessary for the motor to be capable of generating a starting torque in excess of the normal fullload torque, when it is advantageous to increase the flux density at low frequencies by an increase in the voltage-to-frequency ratio. These two conditions are illustrated respectively in Figure 2.5.a and Figure 2.5.b, while a further mode of control that might be employed in, for example, a traction control system<sup>5</sup>, is shown in Figure 2.5.c. This application requires a particularly high starting torque at low frequencies, which is facilitated by an increased voltage-to-frequency ratio. Above a certain frequency the ratio is kept constant, and remains so until near one-half maximum speed. However, beyond this speed the voltage is kept constant, and as the frequency and speed increase the stator flux and the available torque, fall.

Static frequency changers, incorporating either power transistors or thyristors as the switching elements, provide a particularly convenient means of fulfilling the above speed control requirements, and any others which are likely to arise. The voltage and frequency can be adjusted independently in two separate control blocks, or alternatively a single power controller can be employed. The supply can be either d.c. or a.c., which is a significant factor influencing the choice of control method.

#### 2.2.1 Phase Angle Control

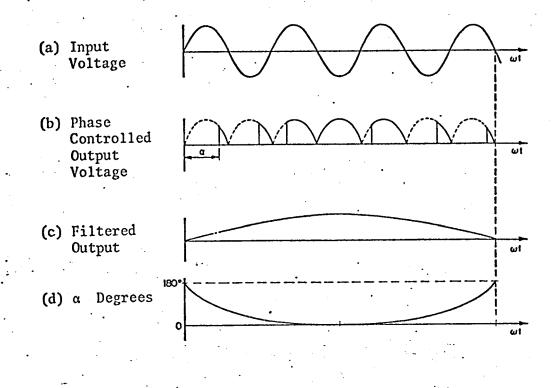

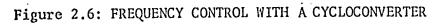

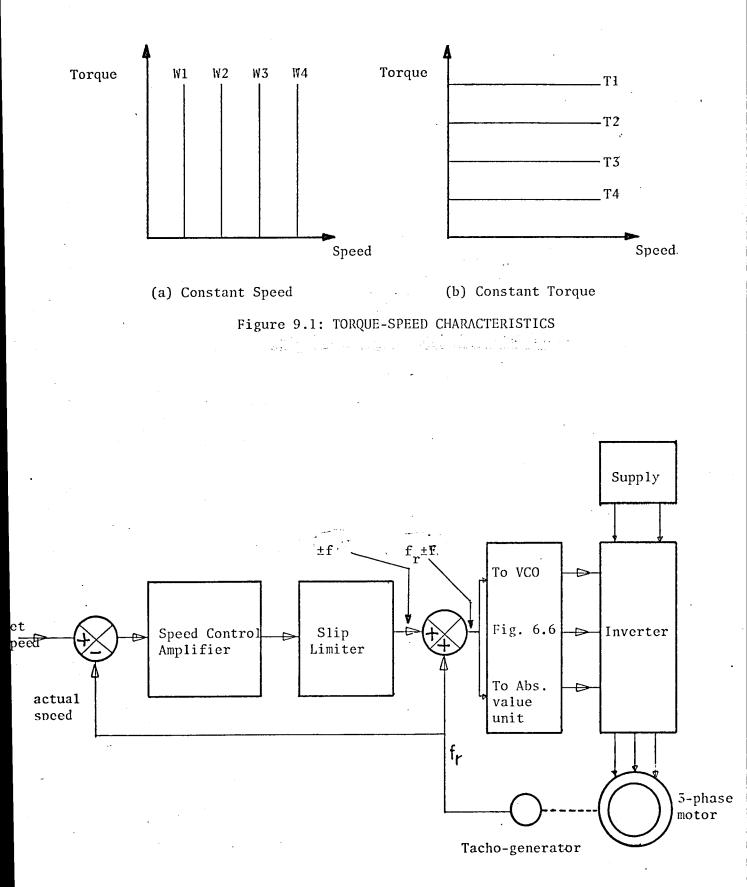

A high-frequency a.c. supply can easily be transformed to a lowfrequency supply by phase angle control, which permits certain parts of the input voltage to appear at the output, as in Figure 2.6. Such a power controller is called a cycloconverter<sup>6</sup>, with the required control exercised by suitable alteration of the angle  $\alpha$ , as in Figure 2.6.d. For a limited speed range, or for certain special torque requirements, either the frequency or the output voltage of the cycloconverter can be fixed, with the speed controlled by changing only the other parameter. The resulting torque-speed

characteristics are as shown in Figure 2.7.a and 2.7,b.

The two characteristics of Figure 2.7 can be combined for simultaneous control of voltage and frequency, with the quantities controlled through the angle  $\alpha$ . The frequency at which  $\alpha$  is varied determines the output frequency but the time variation of  $\alpha$  determines the total area under the voltage-time curve over an output cycle and hence the average and r.m.s. values.

Although this technique can be adapted to 3-phase systems, as shown in Figure 2.8, it has several disadvantages. Proportional control of voltage and frequency requires complex control circuitry and a minimum of eighteen switching components. The range of speed available is not very wide, with the upper frequency normally limited to about one third of the supply frequency by the increasing harmonic level of the output. Frequencies higher than the supply frequency can be obtained<sup>7</sup>, but forced commutation of the switching elements is required with is attendant difficulties. Since the range of speed variation is limited, it is perhaps not surprising that cycloconverter and phase angle control techniques have found little application in the speed control of induction motors.

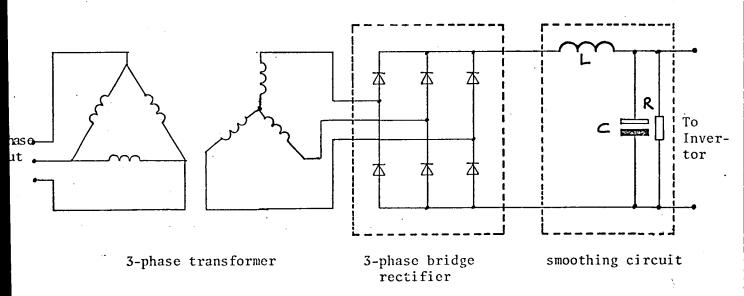

## 2.2.2 Rectifier-Inverter Control<sup>8-10</sup>

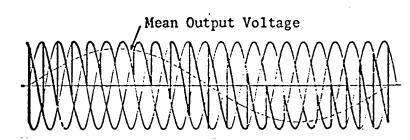

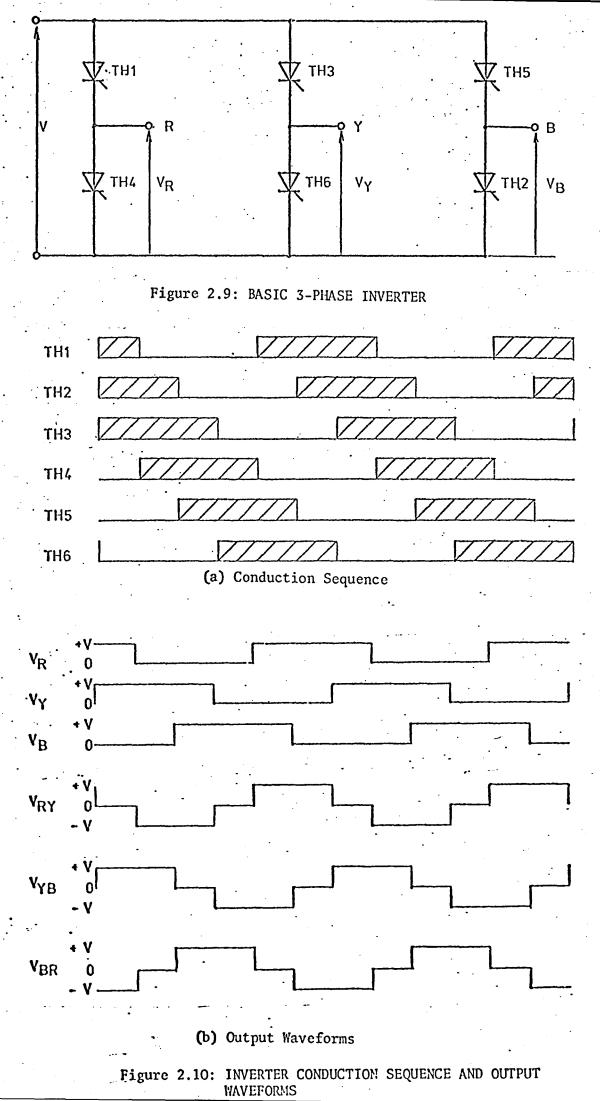

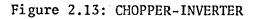

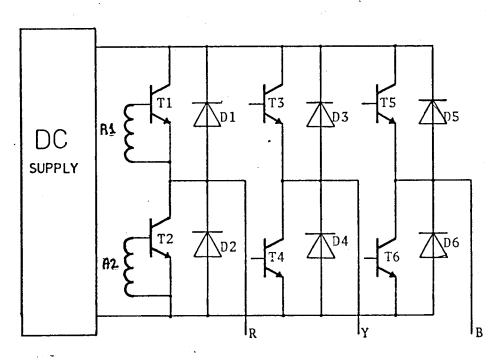

D.C. power is conveniently converted to a.c. power through an inverter. A 3-phase bridge arrangement is shown in Figure 2.9, in which the switching elements are assumed to be thyristors.

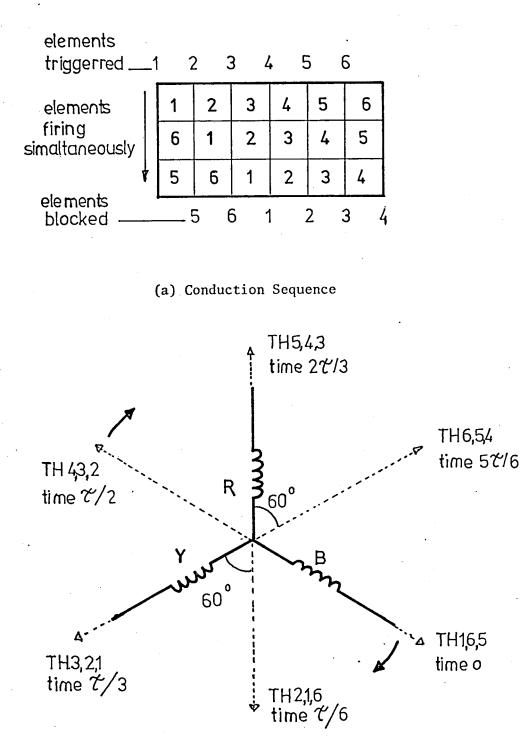

An ideal switch in series with a load fed from a d.c. supply would produce a rectangular voltage waveform across the load. For a 3-phase load, such as an induction motor, it is necessary to have a switching configuration to produce three separate voltages mutually displaced by 120<sup>o</sup> in time. If the switching elements are numbered 1 to 6 as in Figure 2.9, the conduction sequence for each thyristor is as shown in Figure 2.10.a. Although the on and off time of each thyristor is shown as a half cycle, in

practice switching pulses appear every 1/6th of a cycle. This is explained in Figure 2.11.a and 2.11.b.

The basic inverter circuit of Figure 2.9 is made to provide a variable frequency 3-phase supply simply by changing the rate at which the conduction sequence of the thyristors change.

In inverter systems which employ thyristors as switching elements, the problem of commutation is very important and requires special attention to ensure satisfactory operation.

When thyristors are switched on, they remain so until turned off by some external means. Most inverters employ forced commutation techniques<sup>11</sup> in which a charged capacitor provides a reverse bias to block the particular thyristor and holds this on until the thyristor turns off. For low and medium power work, the inverter thyristors may all be switched off simultaneously, and having changed the conduction sequence by adjustment of the firing circuitry they may be switched on again. For high power work, the thyristors are usually switched off separately, to ensure reliability of the system. The charge required on the capacitor may be supplied from the d.c. supply feeding the inverter or, alternatively, from a quite separate external supply. An inverter controlled in this way will only change the frequency of the output; control of the voltage must be accomplished by different means.

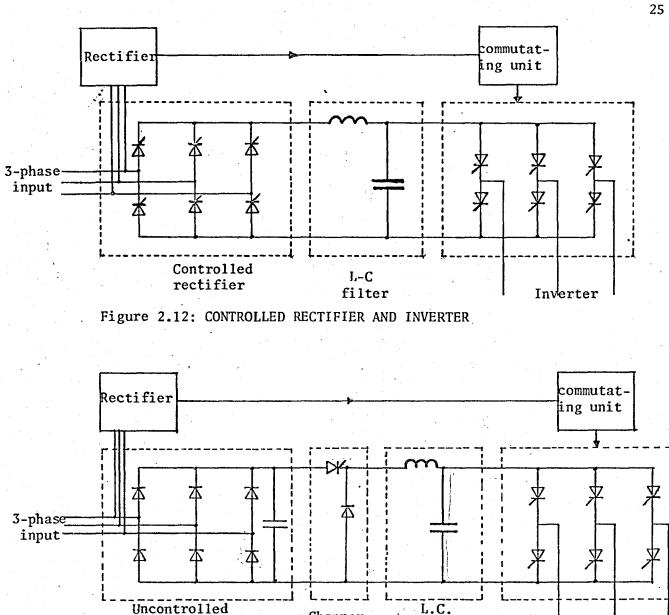

One method of voltage control requires, the additional phase-controlled rectifier shown in Figure 2.12, to vary the voltage fed to the inverter. The main disadvantage of this is that it is difficult to provide reliable inverter commutation over a wide range of input voltages. At low voltages either large commutating capacitors are required to store sufficient energy for commutation or, as is usually the case, an auxiliary voltage supply is necessary, as shown in Figure 2.12. When the voltage level is low the controlled rectifier is likely to be in discontinuous conduction and a .

smoothing LC filter is also required. This will result in a slow response system.

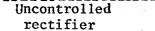

Figure 2.13 shows an alternative means of controlling the d.c. input to the inverter, where a 3-phase uncontrolled rectifier is followed by a chopper and a filter. This circuit has the advantage of a good power factor at the a.c. input, and a possibly faster response due to the smaller LC filter time constant on the output of a high-frequency chopper.

In both methods, the power delivered by the inverter is handled twice, once by the d.c. voltage control and once by the inverter, which means an increased number of components. A further disadvantage is the need for a separate commutation capacitor supply. The harmonic content of the output voltage contains a high proportion of both 5th and 7th components, which limits its use for low-speed control applications.

Instead of using two separate units, control can be accomplished by a single power unit controlled by pulse-width-modulation techniques<sup>12-13</sup>. A rectifier can supply a constant d.c. voltage to the inverter, with both the voltage and the frequency being controlled by the circuit of Figure 2.14. The harmonic content in the output is much reduced, and filtering is accomplished by the inherent time delays of the motor. The P.W.M. circuit has the advantages of good power factor to the a.c. line, fast response, no auxiliary rectifier supply and a low number of switching components. Regeneration to the d.c. supply is immediately possible, but regeneration to an a.c. bus requires another power controller.

## 2.2.3 Modulation Techniques<sup>14</sup>

The choice of the particular method of pulse width modulation rests on the requirements of the application. When high-frequency switching is necessary for an improved performance and for reduced losses in the motor, the switching losses in the inverter (due to the high operating frequency) must be kept to a minimum.

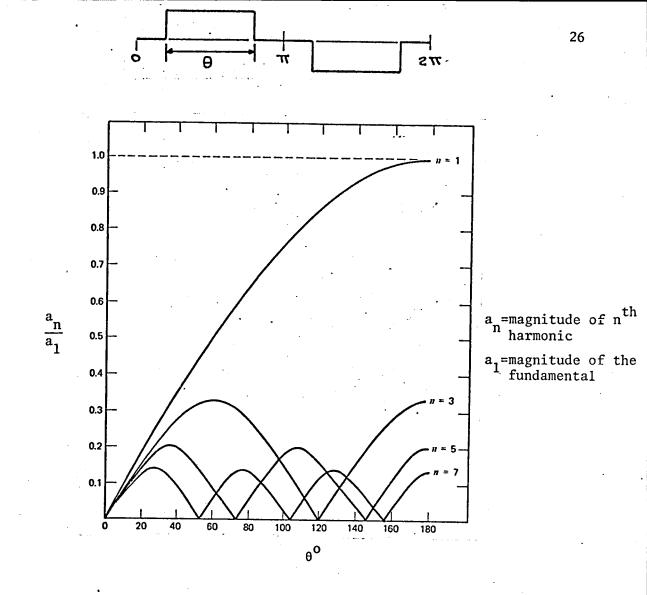

The basic method of voltage control is provided by the pulse width modulated square wave shown in Figure 2.15. The output waveform contains all odd harmonics of the fundamental, and these become large with respect to the fundamental at low output when the pulse width is very narrow. Under this condition the amplitude of the harmonic voltages approaches that of the fundamental, and the technique is only suitable for systems which do not require control down to very low speeds.

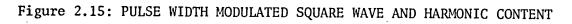

To reduce harmonics further, the number of pulses per cycle needs to be increased. Figure 2.16 shows the magnitudes of the harmonics of three pulse and ten pulse per half cycle systems. As the figure shows, the magnitudes of the harmonics are substantially reduced. As the number of pulses per half cycle is increased, the amplitudes of some higher harmonics become significantly greater, but such harmonics produce negligible current in a motor.

As more pulses are used the harmonic magnitudes are reduced further, although it also becomes more and more difficult to generate the required inverter sequencing. However, this technique can be used in conjunction with harmonic cancelling systems without increasing the number of inverters.

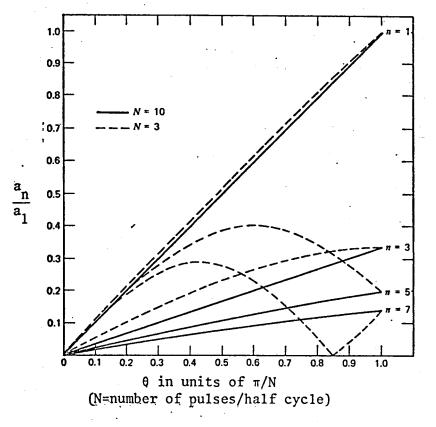

An improved modulation technique involves a sine wave envelope, and can be formed by the action of a comparator which mixes a sawtooth waveform with a reference sine wave, as shown in Figure 2.17.a. As can be seen from Figure 2.17.b, the harmonic level is reduced considerably and a much better approximation to a sine wave results.

However, additional problems may arise if the sawtooth waveform is not synchronized to the reference sine wave. In such cases, especially if the switching frequency of the inverter is low (which is the case if the switching element is a thyristor) the resulting waveform "jitters" and consequently contains even harmonics and a d.c. component. A high switching to output frequency ratio can eliminate this problem, but if this cannot be achieved (as is the case with thyristors) it is better to synchronize the two waveforms.

(b)

Figure 2.1: INDUCTION MOTOR EQUIVALENT CIRCUITS

Figure 2.2: TORQUE SPEED CHARACTERISTICS OF AN INDUCTION MOTOR

Figure 2.3: RELATIVE SPEED CHANGES FOR HIGH AND LOW RESISTANCE ROTORS SUBJECTED TO THE SAME VOLTAGE CHANGE

Figure 2.4: TORQUE-SLIP CURVES FOR VARIABLE FREQUENCY

# Figure 2.5: VARIATION OF MOTOR VOLTAGE AND FLUX WITH SPEED

Figure 2.8: 3-PHASE CYCLOCONVERTER

(b) Stepped mmf. axes

Figure 2.11: Mmf IN SPACE W.R.T. WINDINGS AND THE THYRISTOR SWITCHING SEQUENCE The six steps are displaced in time by  $\pi/3$  radians. The frequency is  $1/\tau$

Chopper

filter

Inverter

Figure 2.14: P.W.M. INVERTER

Figure 2.16: HARMONIC CONTENT OF THREE PULSE AND TEN PULSE PER HALF CYCLE SQUARE WAVE

(b) Harmonic Content

FIGURE 2.17: SINUSOIDAL PULSE MODULATION

# CHAPTER 3

# DELTA MODULATION TECHNIQUES

### 3.1 DELTA MODULATION

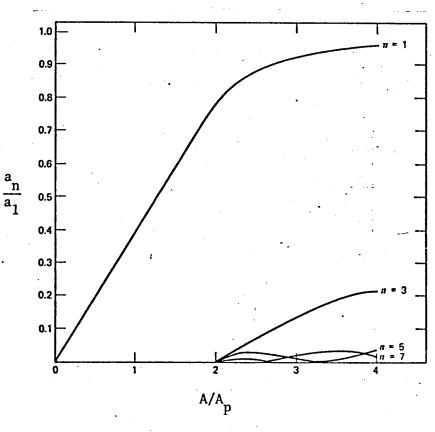

Delta-modulation techniques  $^{15-16}$  are well known in communication systems, where they are extensively used for the transmission of speech signals in binary form. The principles of operation and the behaviour of a delta-modulated system can easily be understood by consideration of Figure 3.1. Here, P.M. is a pulse modulator which passes pulses from the pulse generator P.G. to the network  $F_1$ , with one polarity if the voltage  $\varepsilon$ is positive and with the opposite polarity if  $\varepsilon$  is negative. The output signal  $e_1$  of this network is compared with the signal  $e_0$  to be transmitted, and the difference signal  $\varepsilon$  is applied to the modulator. If the network  $F_1$ is chosen such that the system is stable, each pulse attempts to reverse the polarity of the difference signal  $\varepsilon$ , with the result that the mean difference between the information signal  $e_0$  and the output signal  $e_1$  of the feedback network  $F_1$  is small.

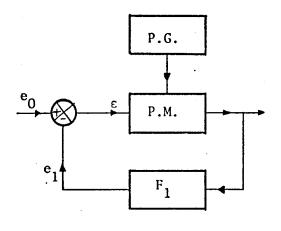

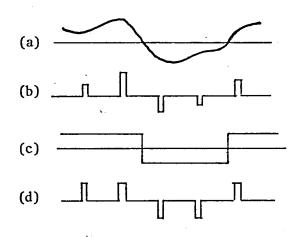

Details of the system may be developed from the simple feedback circuit shown in Figure 3.2, containing a clipping amplifier A and a periodically operated switch S. Figure 3.3 shows the characteristics of four possible feedback systems where

- a) A is linear and switch S permanently closed, so that V is normal, and continuous.

- b) Switch S is closed periodically, so that V is quantised in time.

- c) Amplifier A is used to clip the input, so that with S permanently closed V is quantised in amplitude.

- d) Voltage V is quantised both in time and in amplitude, by the clipping amplifier A and the periodically operated switch S.

Thus, if a suitable integrating network is incorporated in the feedback loop this becomes a delta modulation system. A delta modulator coder and decoder are shown in schematic form in Figure 3.4.a and 3.4.b respectively.

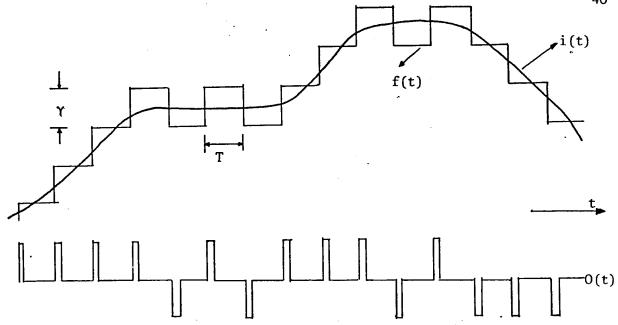

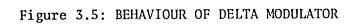

The coder is seen to be a non-linear sampled data control system, in which the comparator compares the analog input signal i(t) with the integrated

version of the digitally encoded signal obtained from the modulator f(t), to decide which of the two has the larger amplitude. Although the comparison process is continuous, the digital output signal e(t) shows only the difference at a particular instant, and the term "delta" arises from this difference. If, at any instant of time, i(t) > f(t), a "high" or "positive" output will result, but if i(t) < f(t) the output is "low" or "negative". The analog signal i(t) thus results in the coder producing at its output a stream of binary pulses, of duration  $\tau$  and amplitude +V or -V. Integration of these pulses gives f(t), and since the pulses are very narrow, f(t) consists of steps of magnitude  $\gamma = V\tau$ . For every positive pulse at the coder output f(t) increases by  $\gamma$ , and every negative pulse results in f(t) decreasing by  $\gamma$ . The value of the output O(t) is decided at regular clock instants, such that O(t) is given by,

$$O(t) = V \operatorname{sign} (i_r - f_r)$$

at the r<sup>th</sup> sampling instant.

Suppose i(t) increases suddenly, causing e(t) to be positive for a number of clock periods. During this time s(t) is +V, and at each sampling instant a positive pulse is passed to the integrator causing f(t) to increase by  $\gamma$ . Eventually, when f(t) > i(t), the error changes sign, and provided that e(t)<0 at the next sampling instant, a negative pulse is produced at the output of the modulator. This negative pulse reduces f(t) by  $\gamma$ , and for as long as e(t)<0 at each sampling instant, f(t) is decreased by  $\gamma$  until the error changes sign. The action of the modulator is thus to produce a waveform f(t) which tracks the input i(t), with a "step like" waveform which never differs from i(t) by more than  $\pm\gamma$ . This process is illustrated in Figure 3.5.

It can also be seen from Figure 3.5 that the rate of occurrence of the binary pulses at the output of the modulator is proportional to the instantaneous value of the slope of the input signal i(t). Thus, when the

slope of i(t) is positive, the output O(t) consists of more positive pulses than negative ones, and vice versa when the slope of i(t) is negative. When the magnitude of the slope of i(t) is small the pulses in the O(t) waveform frequently alternate, and when the slope of i(t) is zero, the O(t) waveform consists of pulses of alternate polarity. Figure 3.6 shows the waveforms at various points of the modulator, when a sine wave is present at the input.

In the previous analysis the integrator has been assumed ideal. In practice, the output pulses are of finite duration, and the response of an RC integrating network to these pulses is exponential rather than increasing in steps.

In Figure 3.4.b a delta modulation decoder is shown. As seen, the input is integrated and the function f(t) obtained. High frequency effects contained in the rising and falling parts of each f(t) step are removed by filtering f(t), by a filter whose frequency band is identical to the frequency band occupied by i(t).

As described, delta modulation contains information on the slope of the input signal, which means that d.c. signals cannot be encoded. Consideration of Figure 3.6 indicates that the output from a delta modulator must first be integrated, to recover the original signal, before it can be applied to a motor for speed-control purposes. However, following integration the delta-modulated signal becomes an analog signal, and since subsequent amplification requires a normal amplifier with biassed transistor elements, delta modulation is not suitable for the speed control of an induction motor.

However, this difficulty is easily overcome by integrating the input signal before it leaves the modulator, so as to generate output pulses carrying the information corresponding to the amplitude of the input signal. Delta-sigma ( $\Delta$ - $\Sigma$ ) modulation is a realization of this principle, but before going into the behaviour and operation of  $\Delta$ - $\Sigma$  modulators it will

be useful to derive some of the parameters which are necessary for a better understanding of its use.

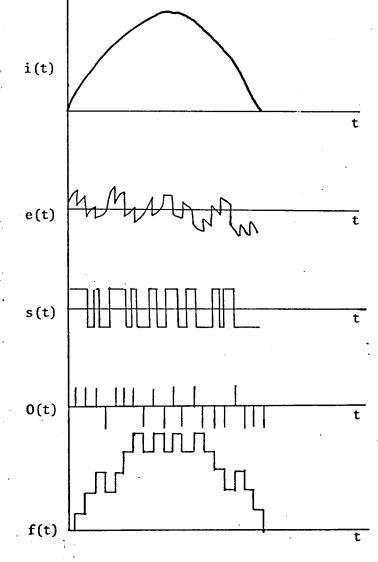

# 3.1.1 Derivation of the Overload Characteristic

An important aspect of delta modulation is the problem of overloading. Assuming an RC network is used for the integrator, the slope of the exponential response to a step input determines the maximum rate at which the integrator output can move. If either the amplitude or the frequency, or both, of the signal are raised sufficiently, its slope exceeds that of the exponential curve, when the modulator can no longer track the input signal and increased distortion will result. However, as long as the slope of the input signal is equal to or less than the slope of the exponential curve at the amplitude common to both, there will be an output from the coder which closely follows the input signal. By referring to Figure 3.7, and considering the two points A and B respectively on the exponential response leading to +V with time constant T and on the sine wave E sin $\omega$ t of the same amplitude, and assuming the digitised levels of O(t) to be  $\pm V$ , the slope of the exponential at amplitude v is

$=\frac{V-V}{T}$

and the slope of the sine wave at the same amplitude is

$= \omega (E^2 - v^2)^{\frac{1}{2}}$ .

The difference in slopes,

$$D = \frac{(V-v)}{T} - \omega (E^2 - v^2)^{\frac{1}{2}}$$

which is a function only of v. The minimum difference occurs when

$$V = \frac{E}{(1+\omega^2 T^2)^{\frac{1}{2}}}$$

and the value of D for this minimum condition is

$$D_{\min} = \frac{V - E(1 + \omega^2 T^2)^{\frac{1}{2}}}{T}$$

The overload condition is given by  $D_{min}=0$ , when

$$E = \frac{V}{(1+\omega^2 T^2)^{\frac{1}{2}}}$$

(3.1)

which identifies the relation between E and  $\omega$  and specifies the overload characteristic.

### 3.1.2 Derivation of the Threshold of Coding

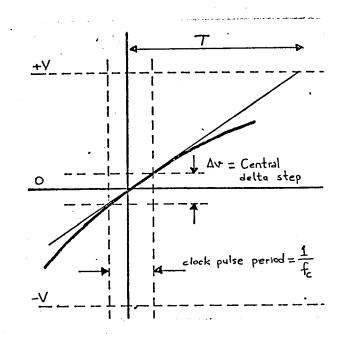

In Figure 3.8 the "central delta step" is the change in the integrator voltage during one clock pulse period. The minimum amplitude below which the input fails to excite the modulator occurs when the peak-to-peak amplitude of the signal is smaller than the central delta step. The threshold of coding is defined as

$$E_{\min} = \frac{\Delta v}{2}$$

where  $\Delta v$  is related to other parameters by

$$\Delta v = \frac{V}{T} \cdot \frac{1}{f_c}$$

and

where  $f_0$  is the characteristic frequency of the integrator.

$E_{\min} = \frac{V}{Tf_c^2} \qquad T = \frac{1}{2\pi f_c}$

By substitution:

$$E_{\min} = \frac{\pi V f_0}{f_c}$$

(3.2)

and with the input dynamic range of the system defined as the ratio of the overload level to the threshold of coding:

$$\frac{E_{\max}}{E_{\min}} = \frac{V/(1+\omega^2 T^2)^{\frac{1}{2}}}{\frac{\pi V f_0}{f_c}} = \frac{f_c}{\pi (f_0^2 + f^2)^{\frac{1}{2}}} .$$

(3.3)

3.1.3 Quantisation Noise<sup>17</sup>

Quantisation noise arises as the reconstructed signal f(t) attempts to follow the original signal by successive approximations. Although it is normally defined as the difference or error between the input signal i(t) and the reconstructed signal f(t), it may also be defined as the difference between i(t) and the final filtered output. The first of these will give a larger error signal and since there is no exact relation between i(t) and f(t) the difference signal will have a random variation.

When the input to the modulator is zero, the pattern of the digital output is 1010101. The integrator output is thus a triangular wave with peaks of  $\pm \frac{\Delta v}{2}$ , and the mean square difference between this and the input is  $\frac{(\Delta v)^2}{12}$ . This is the total error energy, and is contained in a line spectrum of the multiples of  $f_c$ . When a sine wave input is applied the error is greater.

### 3.1.4 Characteristics of Delta Modulation

The equations so far derived characterise the performance of a basic delta modulator. Reference to equations 3.1, 3.2 and 3.3 suggests that for the best performance the characteristic frequency  $f_0$  of the integrator should be as small as possible. But (from equation 3.1) this may cause the overload characteristic to fall within the bandwidth of the input signal. In order to have a flat dynamic range,  $f_0$  must be chosen to be either equal to or greater than the maximum input signal frequency.

The equations also suggest that the best modulator performance is obtained with a high clock frequency. Figure 3.9 shows the characteristics of a basic delta modulator, and it will be seen that for low frequencies amplitude overloading is dominant, and that as the frequency of the input sine wave increased the slope overload effect prevails.

#### 3.2 DELTA-SIGMA MODULATION

To avoid differentiation of the input signal, an integrator can be included at the input to the delta modulator, when the output becomes coded with information on the amplitude of the input signal. This modification results in delta sigma modulation ( $\Delta$ - $\Sigma$  M) which, although similar to pulse code modulation, differs in that P.C.M. involves the

generation of an n-digit code, whereas since  $\Delta - \Sigma$  M requires<sup>18</sup> only a single-digit code it is therefore much less complex.

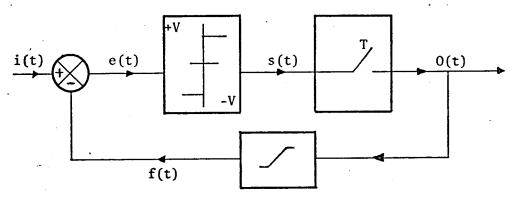

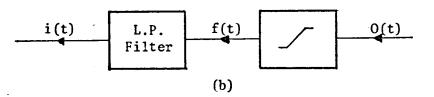

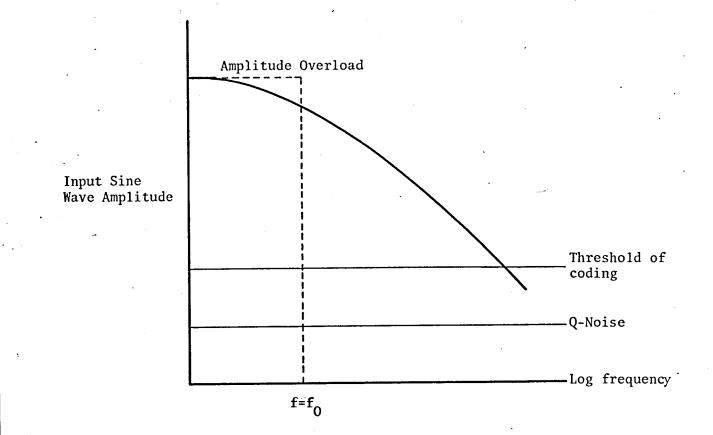

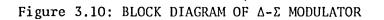

The block diagram of a  $\Delta$ - $\Sigma$  modulator is shown in Figure 3.10, and the modulator operates as follows:

The quantiser produces an output of +V when e(t)>0 and -V when e(t)<0, and the output s(t) appears at sample times with a sampling interval T. The comparator combines the integrated analog input signal with the integrated version of the digitally encoded signal, to decide which of the two has the larger amplitude. Since the encoder functions in such a way that the output follows the input, the analogue input is converted to a digital signal.

Noting that

$$e(t) = \int i(t)dt - \int 0(t)dt$$

$$= \int [i(t) - 0(t)]dt$$

we can replace the two separate integrators in the block diagram of Figure 3.10 by a single integrator in the forward path, leading to the simplified block diagram shown in Figure 3.11.

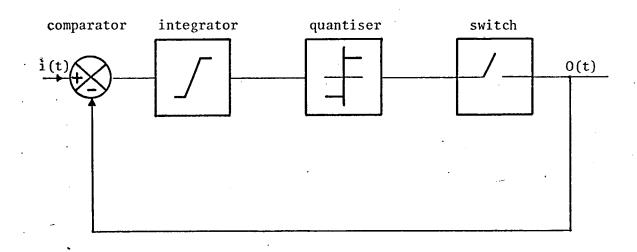

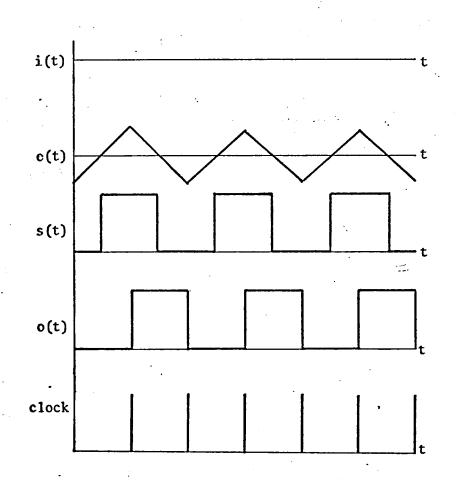

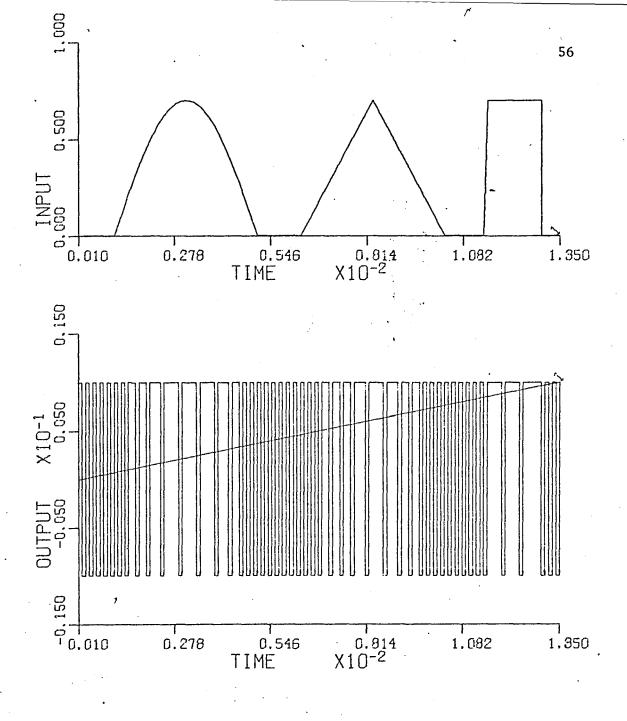

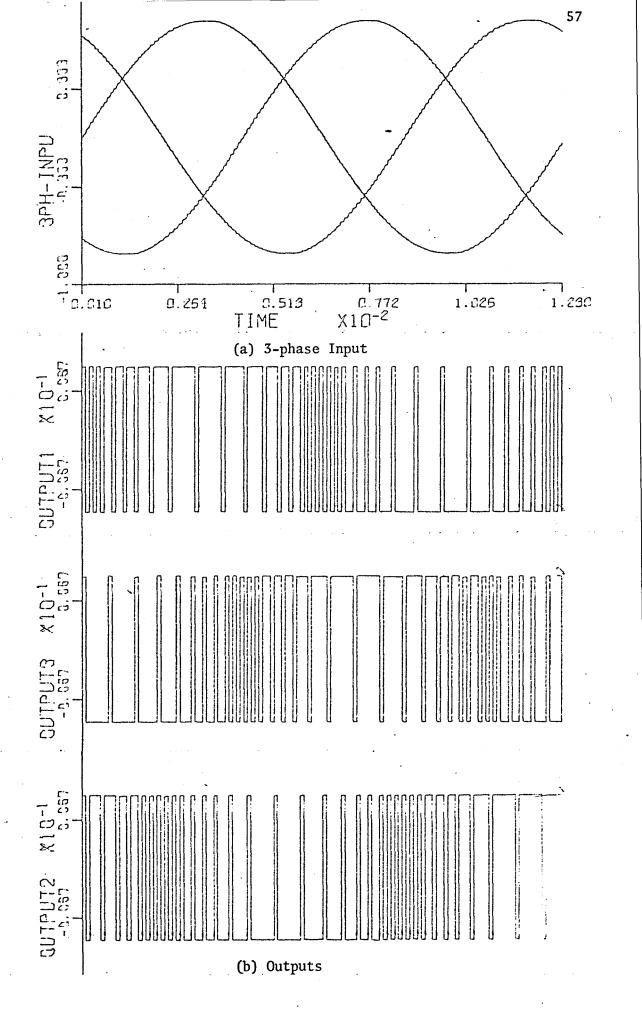

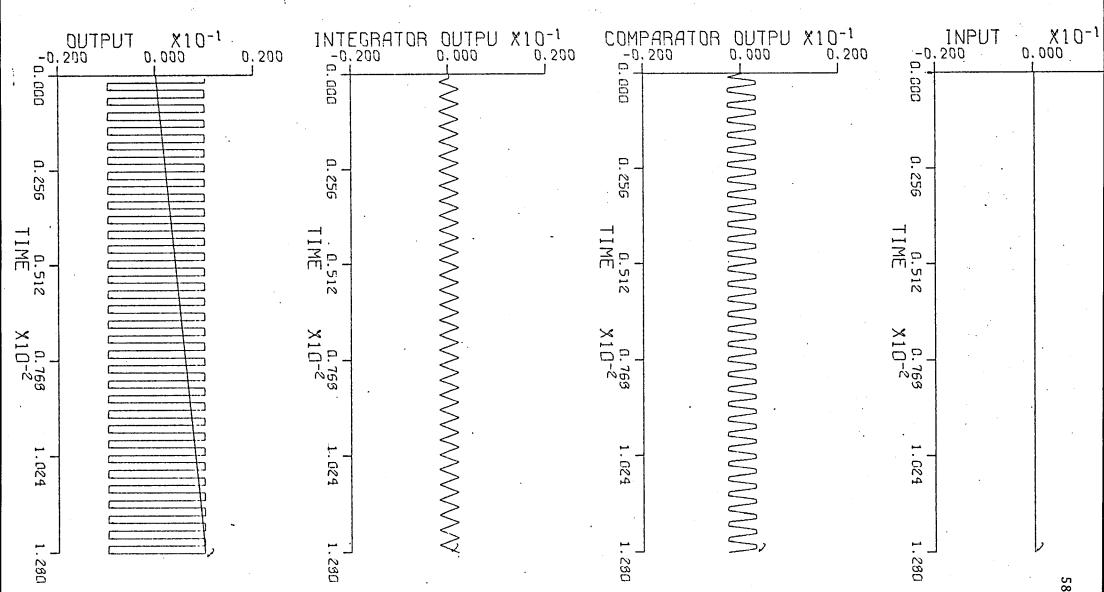

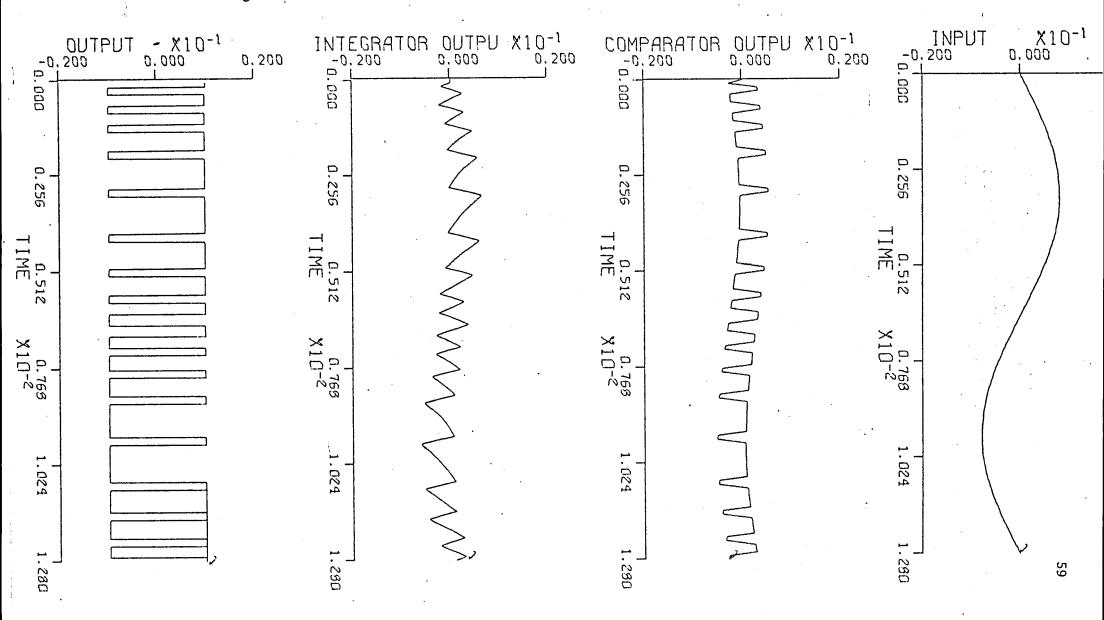

Figure 3.12 shows the output of a  $\Delta$ - $\Sigma$  modulator, for a staircase input. As seen, the output contains information on the level of the input amplitude. When no input signal is applied, the modulator is said to be idling, and Figure 3.13 shows the corresponding wave forms at different parts of the circuit. As can be seen from the figure, the output consists of pulses with a frequency of one-half the clock rate, where the clock rate is the frequency of the switch. The mean output of the modulator when idling is zero.

### 3.2.1 Derivation of the Overload Characteristic

By applying the same argument as in 3.1.1, the slope of the exponential at an amplitude v is  $\frac{V-v}{T}$ , and the slope of the output from the

RC integrator at the modulator input is

$$\frac{dV}{dt} = \frac{\omega E \cos \omega t}{(1+\omega^2 T^2)^{\frac{1}{2}}} = \frac{\omega}{(1+\omega^2 T^2)^{\frac{1}{2}}} \cdot \left[E^2 - v^2 (1+\omega^2 T^2)\right]^{\frac{1}{2}}$$

The difference D is

$$D = \frac{V-v}{T} - \frac{\omega}{(1+\omega^2 T^2)^{\frac{1}{2}}} \cdot \left[E^2 - v^2(1+\omega^2 T^2)\right]^{\frac{1}{2}}$$

which must be equal to or greater than zero to avoid overloading. By differentiating D with respect to v, and equating to zero, we obtain

$$v = \frac{E}{1+\omega^2 T^2}$$

and substituting this into the above equation and putting  $D_{min}=0$  the limit of the non-overload condition is obtained as

$$E = E_{max} = V \qquad (3.4)$$

This result illustrates the advantage of  $\Delta-\Sigma$  modulation, in providing an overload characteristic independent of the input signal frequency.

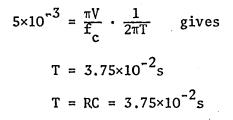

# 3.2.2 Derivation of the Threshold of Coding

With  $\Delta$ - $\Sigma$  modulation the threshold of coding is modified, although it still remains related to the central step size  $\Delta v$ , where

$$\Delta v = \frac{V}{T} \cdot \frac{1}{f_c} = \frac{2\pi V f_0}{f_c}$$

With an input signal  $i(t) = Esin\omega t$ , the peak output from the input RC integrator is  $E/(1+\omega^2 T^2)^{\frac{1}{2}}$ , so that using the definition of the threshold of coding

$$\frac{E}{(1+\omega^2 T^2)^{\frac{1}{2}}} = \frac{\Delta v}{2} = \frac{\pi V f_0}{f_c}$$

$E = E_{\min} = (1+\omega^2 T^2)^{\frac{1}{2}} \pi V f_0$

or

The input dynamic range of the modulator is given by

$$\frac{E_{\max}}{E_{\min}} = \frac{V}{(1+\omega^2 T^2)^{\frac{1}{2}} \pi V f_0} = \frac{f_c}{\pi f_0 (1+\omega^2 T^2)^{\frac{1}{2}}}$$

(3.5)

or

It will be seen that, unlike the overload characteristic, the threshold of coding is frequency dependent, and that it increases with the input signal frequency. However, comparison of equations (3.3) and (3.6) shows that the input dynamic range is the same as that of the basic delta modulator.

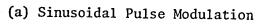

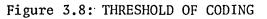

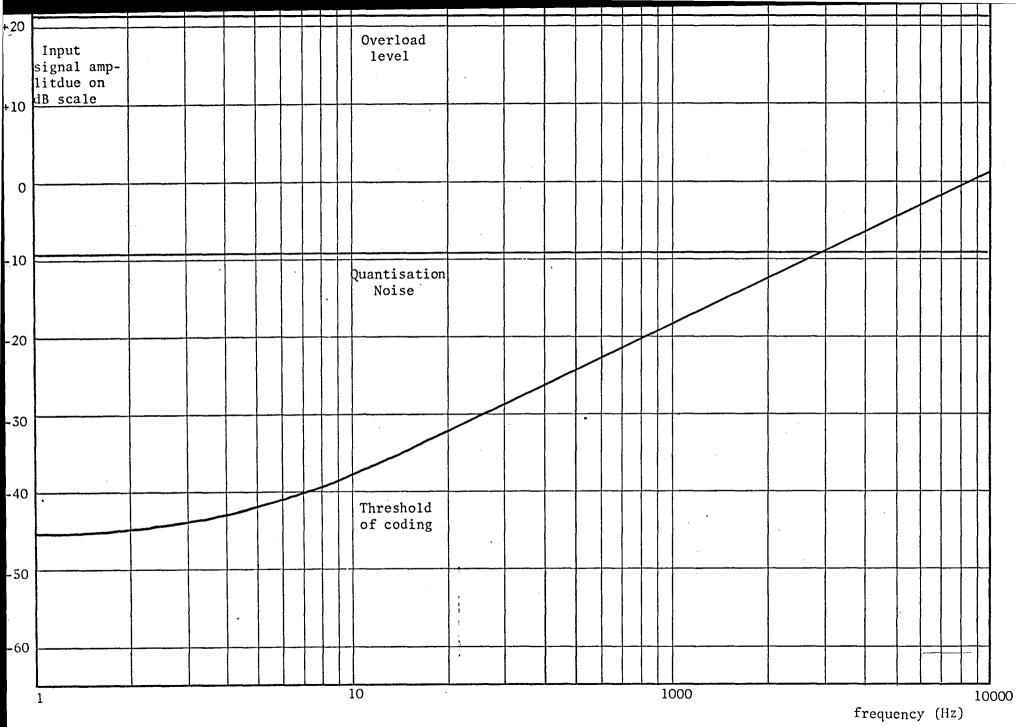

# 3.2.3 Characteristics of Delta Sigma Modulation

Although  $\Delta - \Sigma$  modulation has the flat overload characteristic specified by equation (3.4), and is limited only by the digital levels  $\pm V$ , the threshold of coding is not flat and varies with the input signal frequency. At frequencies above the cut-off frequency of the integrator  $f_0$ , the threshold of coding increases, and the value of the time constant T is therefore dependent on the input signal bandwidth.

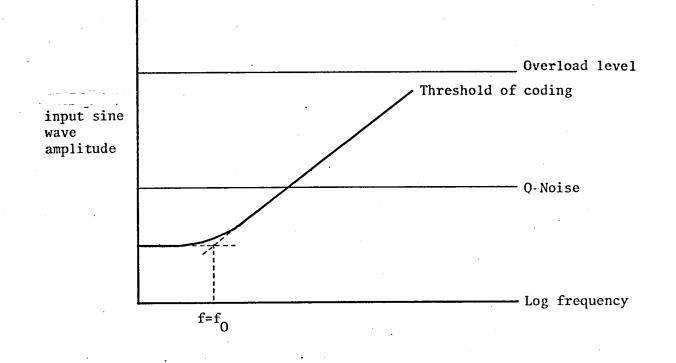

Reference to equation (3.5) indicates that reducing V reduces the threshold of coding and increases the dynamic range. However, for stable operation of the comparator, V cannot be reduced below a minimum voltage. Figure 3.14 shows the characteristics of  $\Delta$ - $\Sigma$  modulation, and it is clear that as the frequency increases the threshold of coding approaches the overload level.

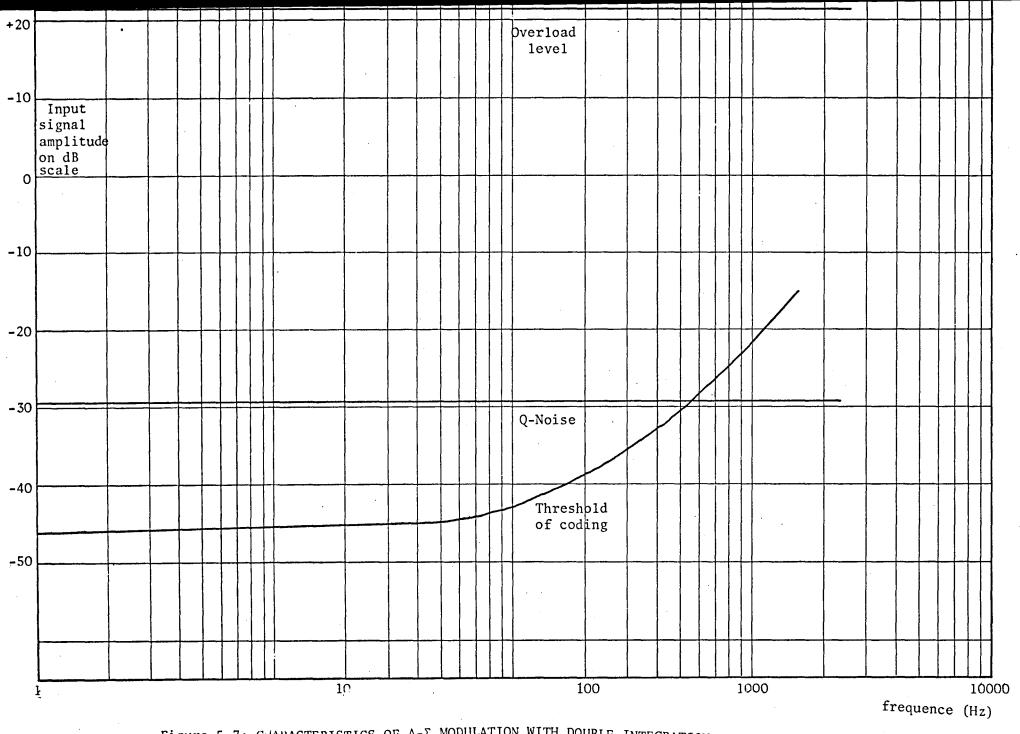

### 3.3 DELTA SIGMA MODULATION WITH DOUBLE INTEGRATION

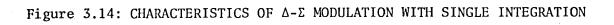

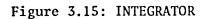

The performance of delta sigma modulators can be improved by using a second integrator immediately following the first, both to reduce the quantisation noise and to increase the dynamic range at high frequencies. The integrator required is shown in Figure 3.15, for which the transfer function is

$$H(f) = \frac{1+j f/f_3}{(1+j f/f_1)(1+j f/f_2)}$$

(3.7)

(3.6)

where,

$$\mathbf{f}_{1} = \frac{1}{2\pi R_{1}C_{1}(1+C_{2}/C_{1})}$$

(3.8)

$$f_{2} = \frac{1}{2\pi R_{2}C_{2}\left[1 - \frac{1}{4}\left(1 + \frac{R_{1}}{R_{2}}\right)^{2} \frac{R_{2}C_{2}}{R_{1}C_{1}}\right]}$$

(3.9)

$$f_3 = \frac{1}{2\pi r C_2}$$

(3.10)

The magnitude of H(f) is,

$$|H(f)| = \frac{f_1 f_2 \left(1 + \frac{f^2}{f_3^2}\right)^{\frac{1}{2}}}{\left[(f_1^2 + f^2)(f_2^2 + f^2)\right]^{\frac{1}{2}}}$$

which reduces to,

$$H(f) = \frac{f_1 f_2}{[(f^2 + f_1^2) (f^2 + f_2^2)]^{\frac{1}{2}}}$$

if f<sub>3</sub> is large.

# 3.3.1 Overload Level

The condition for the overload level is given by

$$E_{\max} = V |H(f)| \cdot |H^{-1}(f)| = V$$

(3.12)

where V is the level of the digital sequence and |H(f)| is given by equation (3.11).

# 3.3.2 Threshold of Coding

or E

$E|H(f)| = \Delta v/2$ , is the condition for the threshold of coding. Thus,

$$\frac{Ef_{1}f_{2}}{(f^{2}+f_{1}^{2})^{\frac{1}{2}}(f^{2}+f_{2}^{2})^{\frac{1}{2}}} = \frac{\Delta v}{2} = \frac{16Vf_{1}f_{2}}{\pi f_{c}^{2}}$$

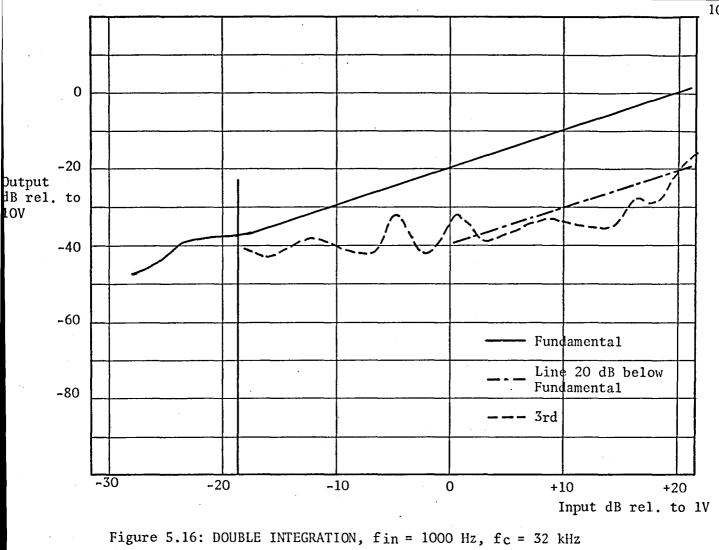

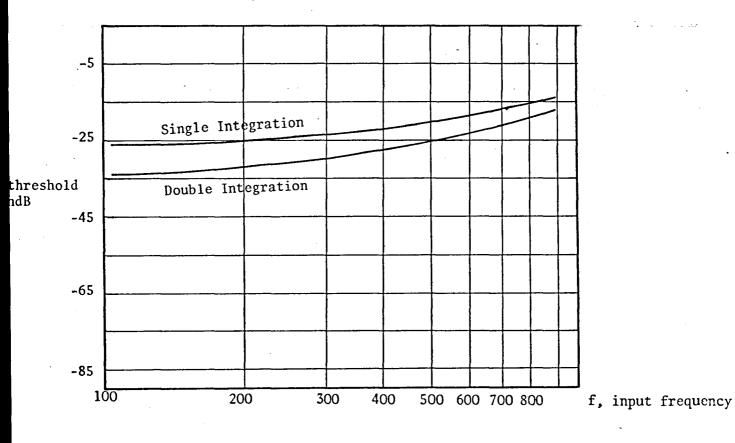

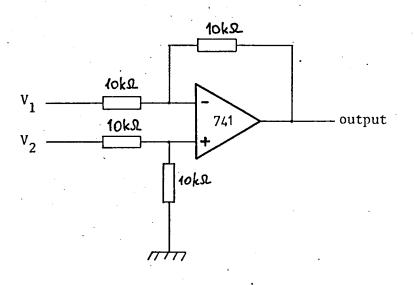

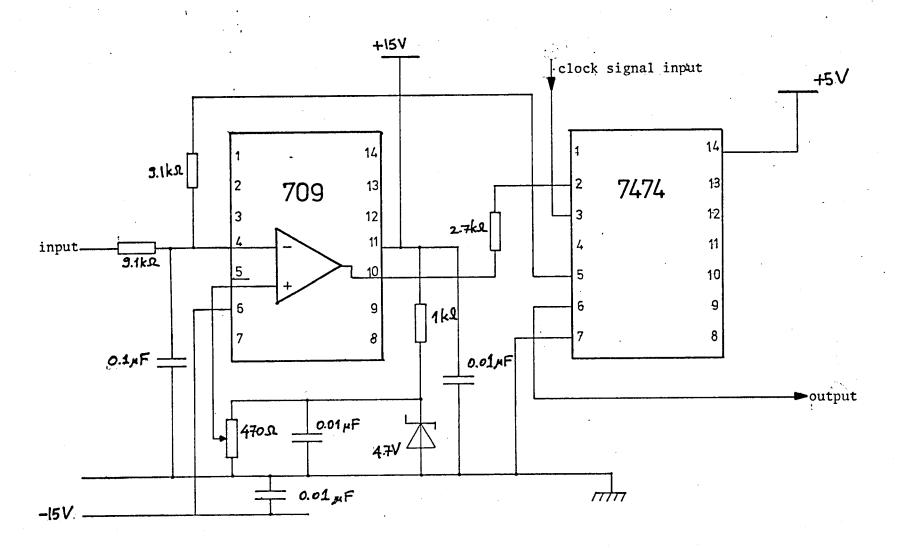

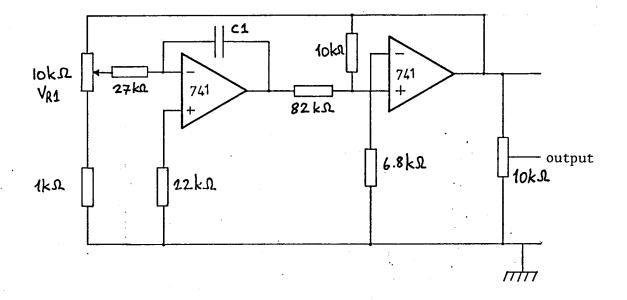

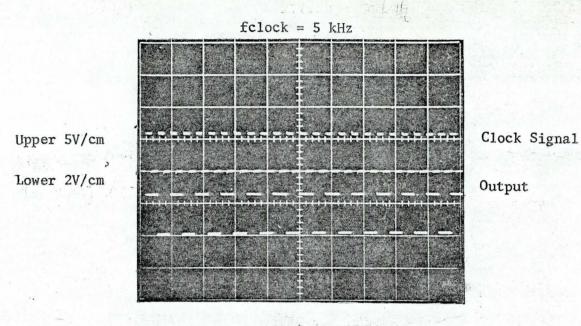

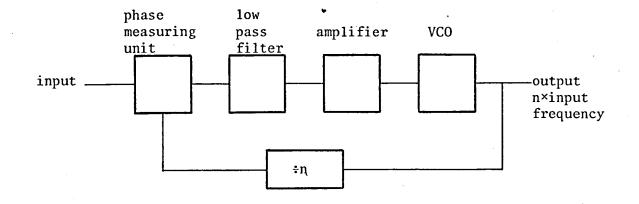

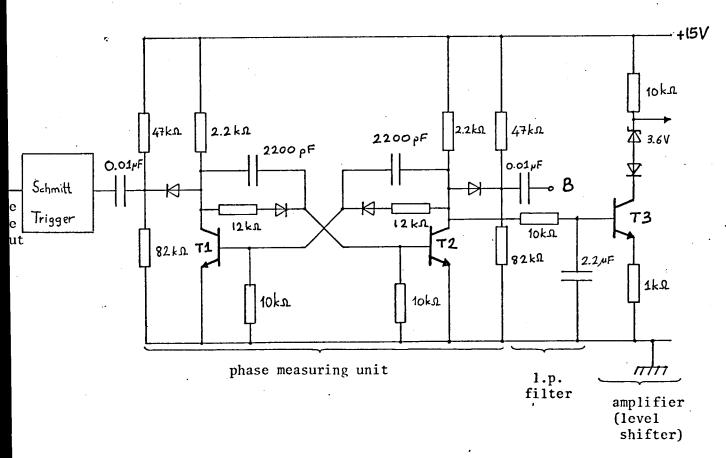

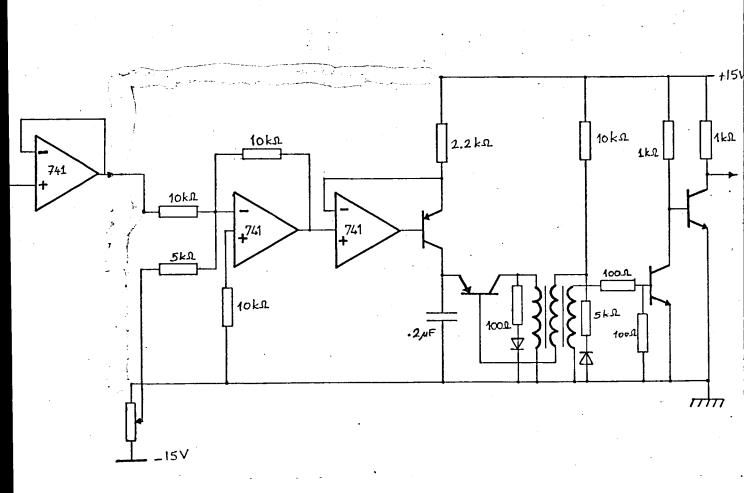

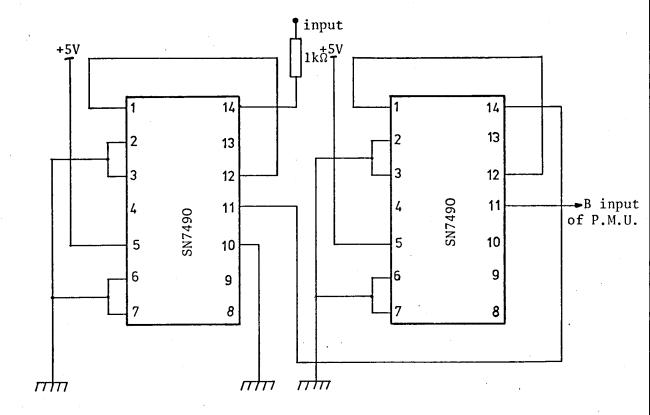

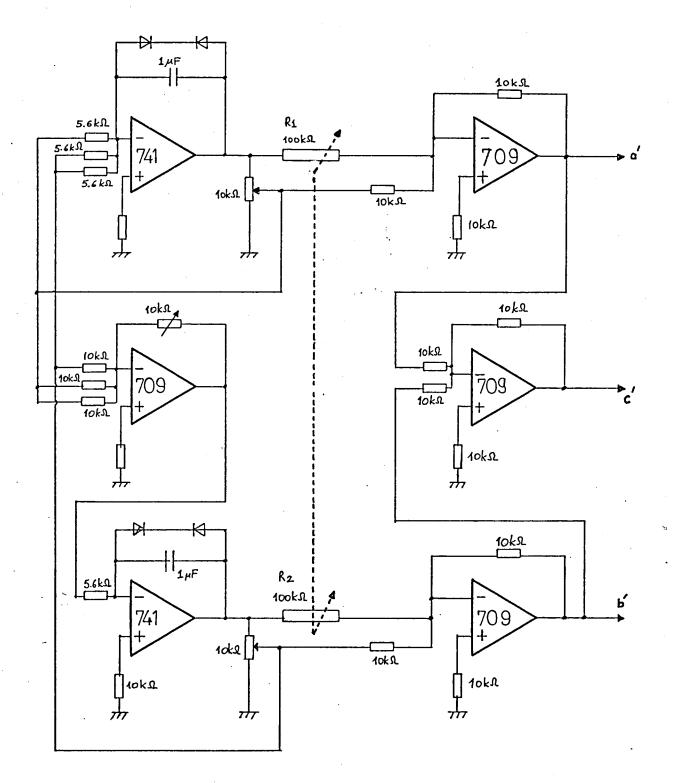

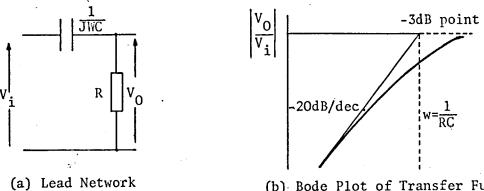

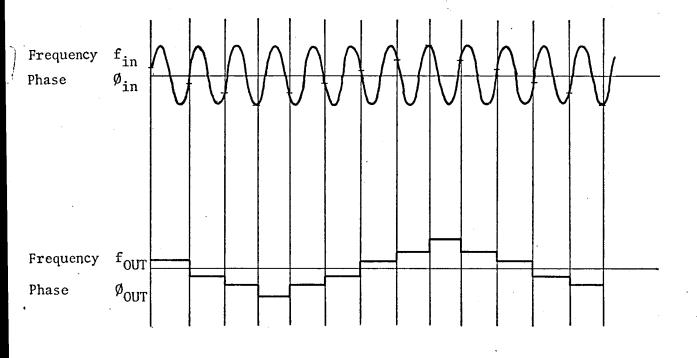

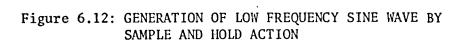

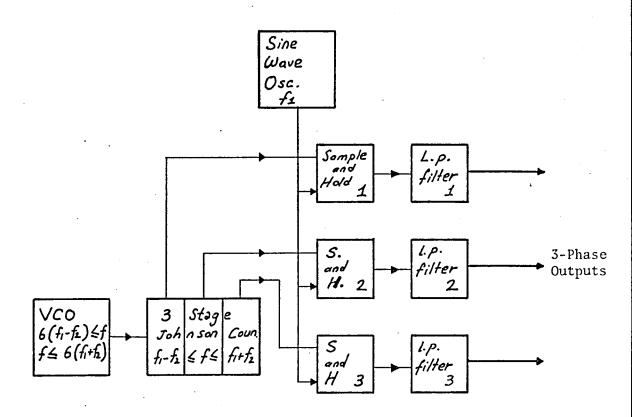

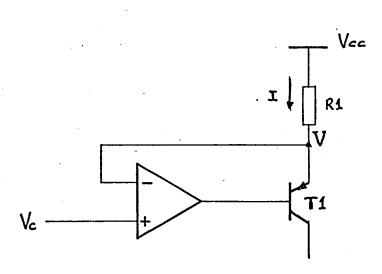

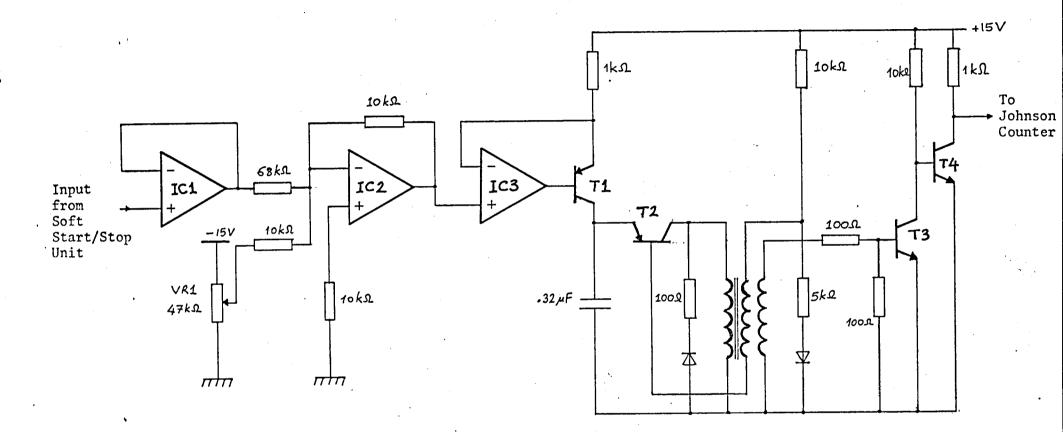

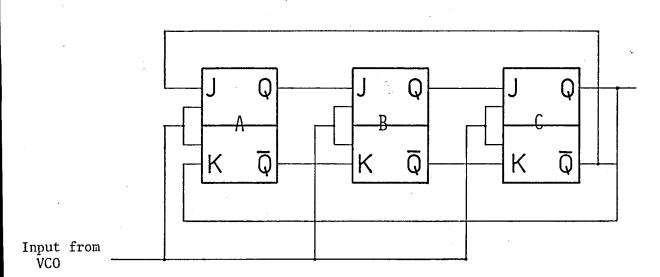

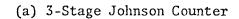

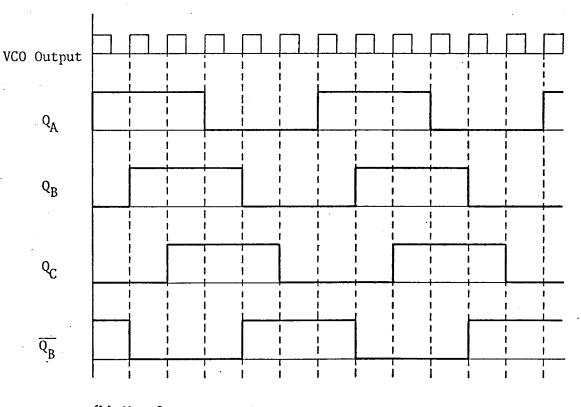

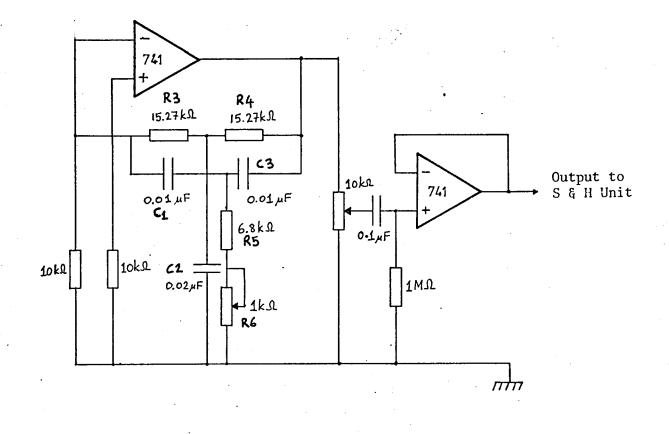

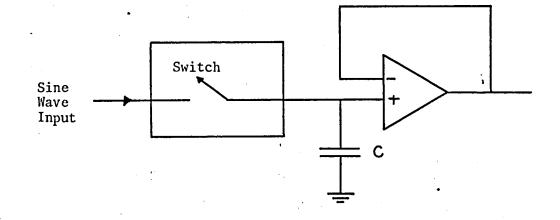

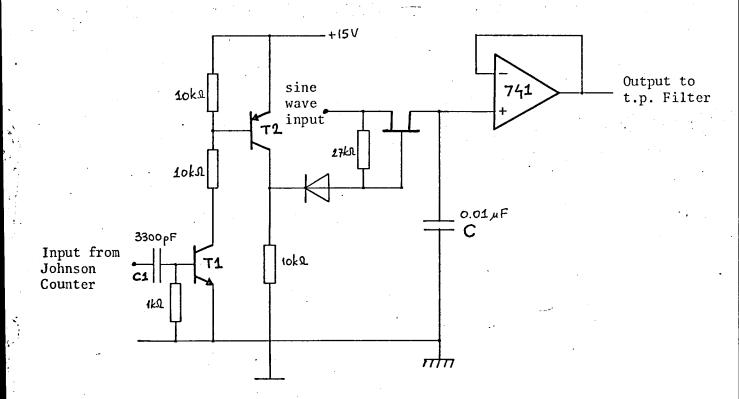

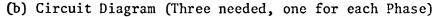

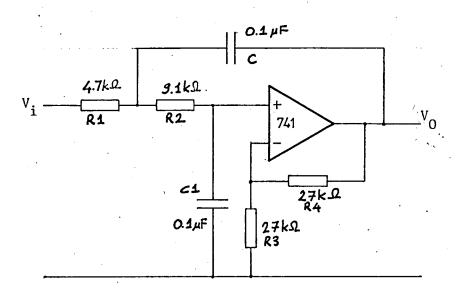

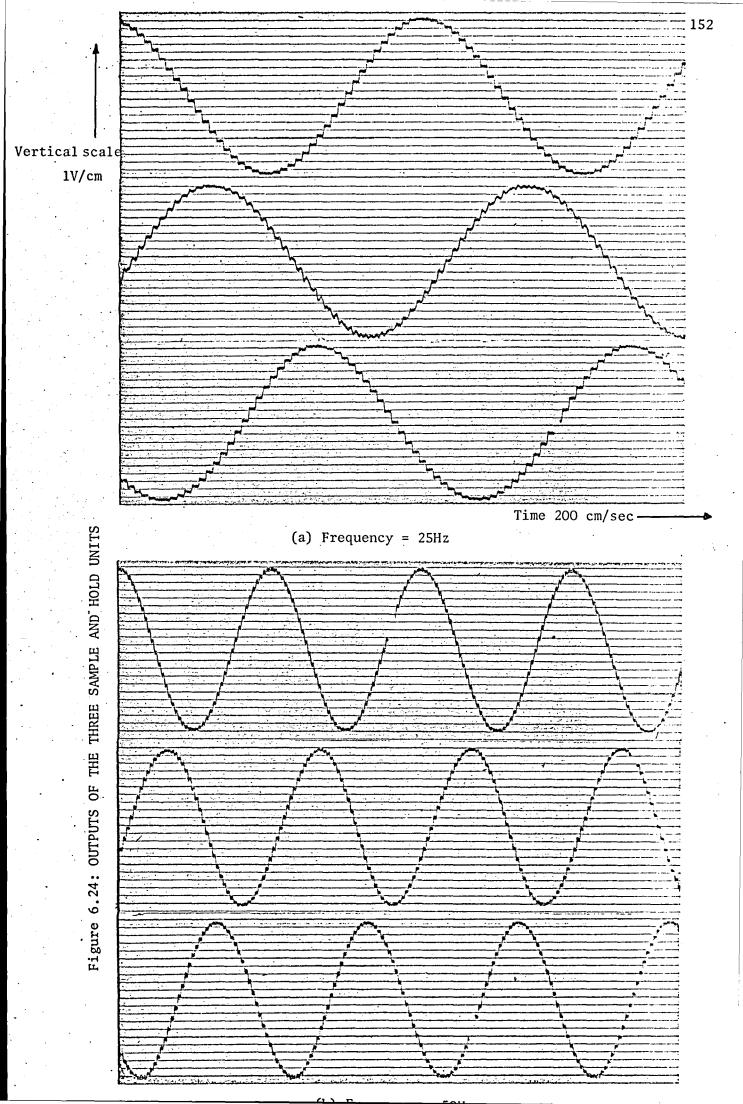

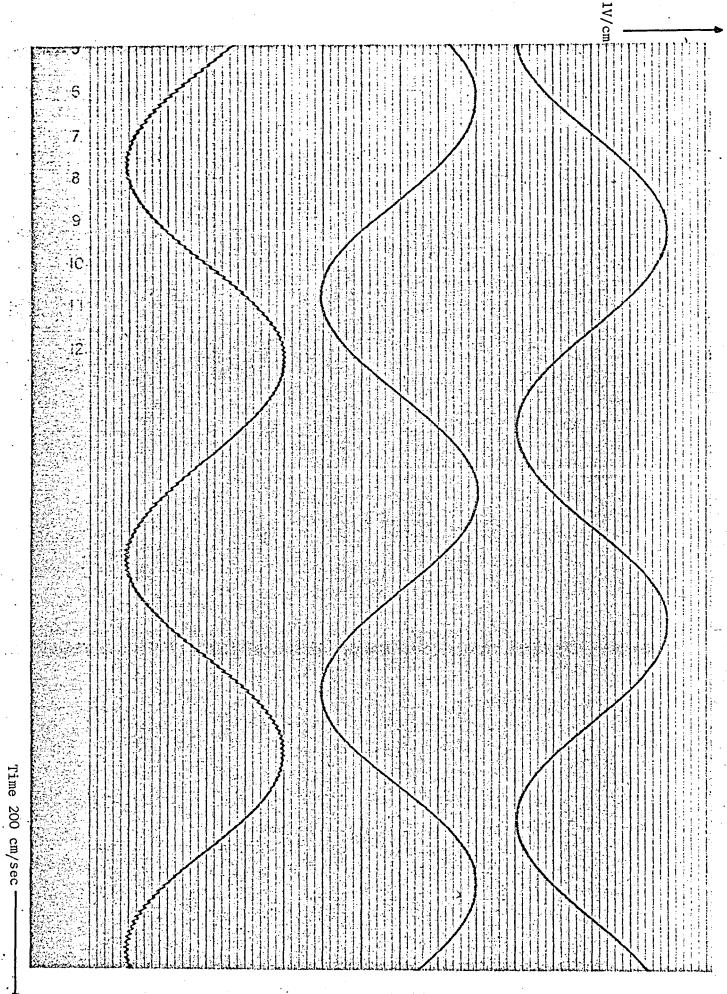

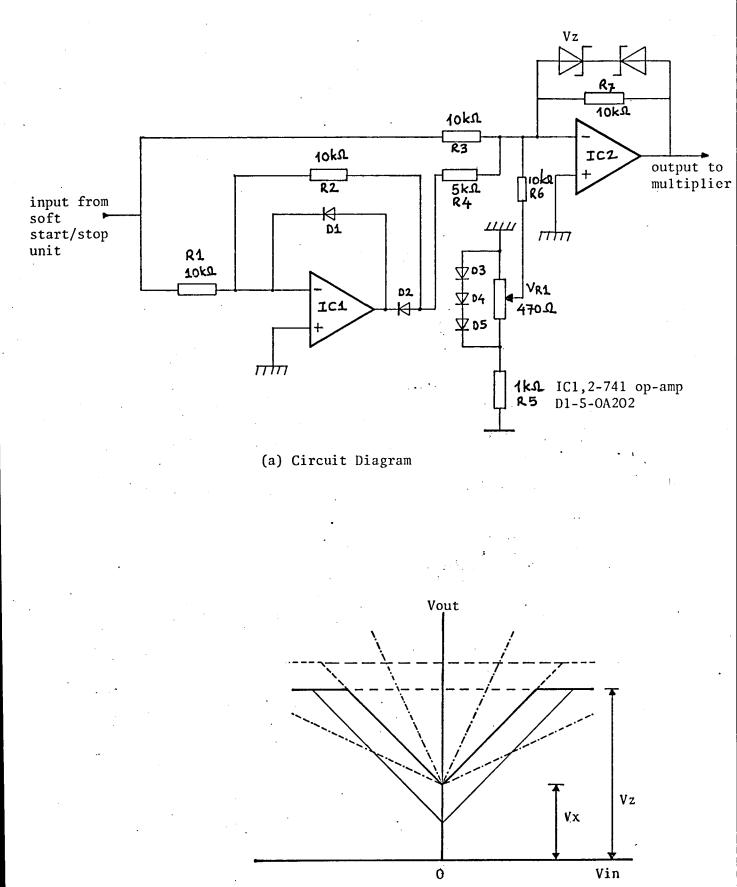

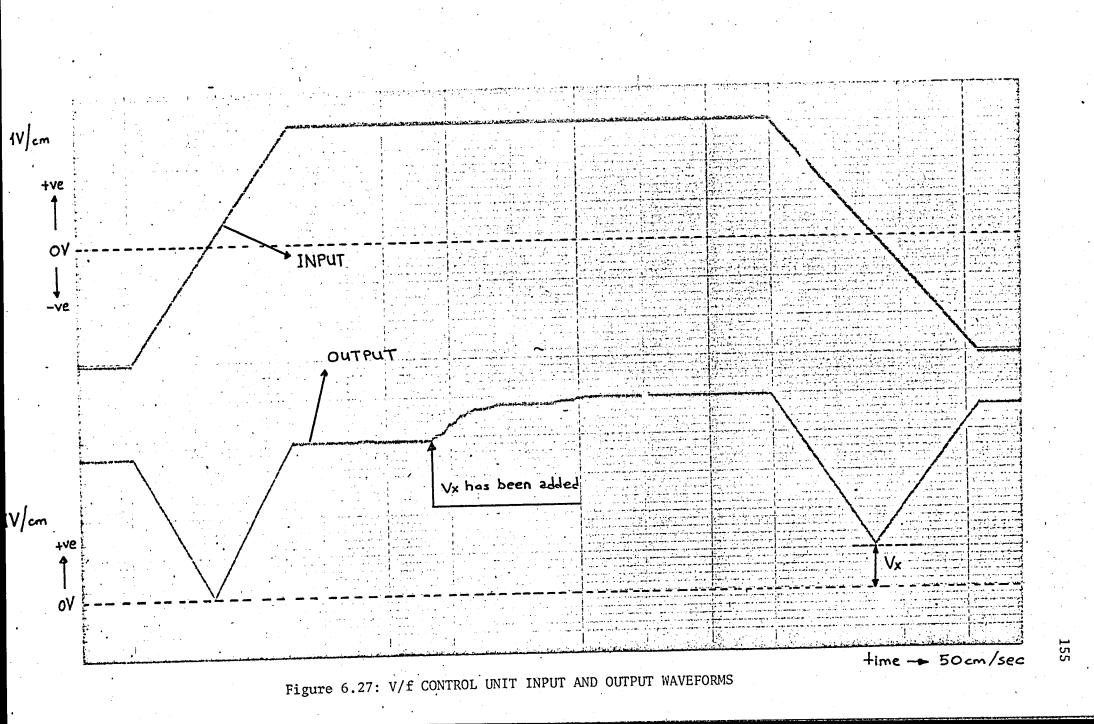

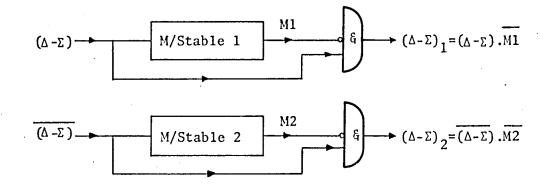

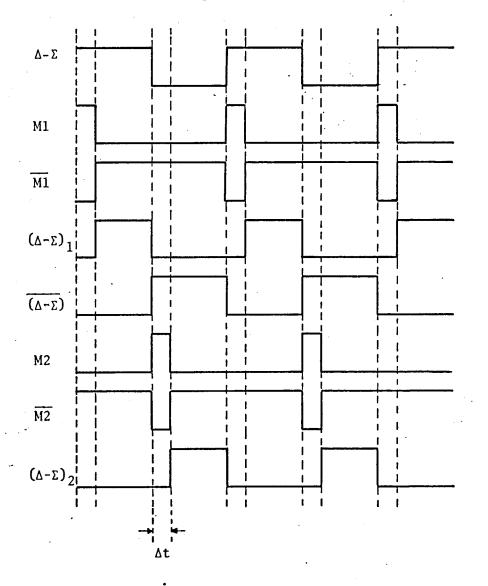

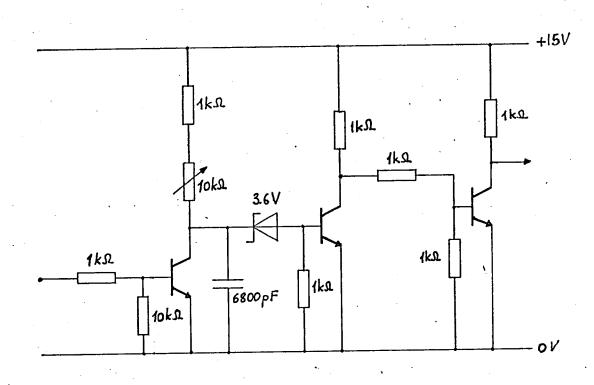

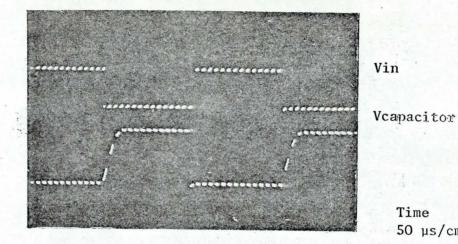

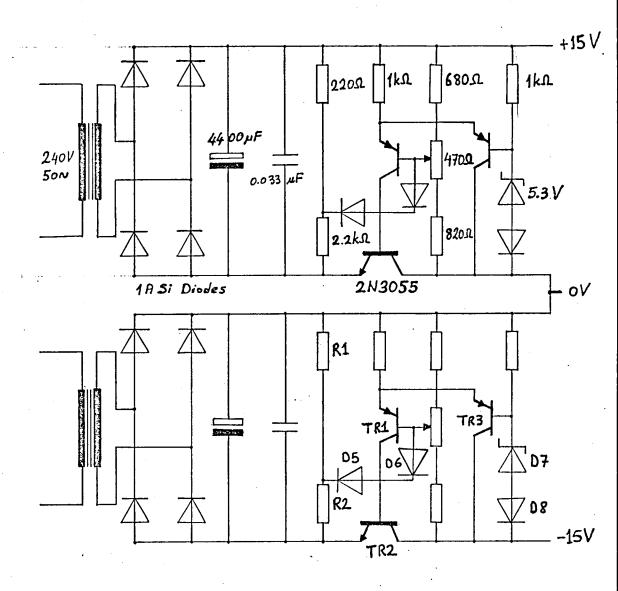

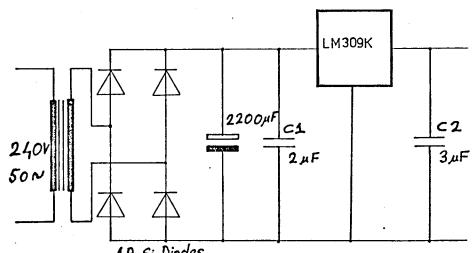

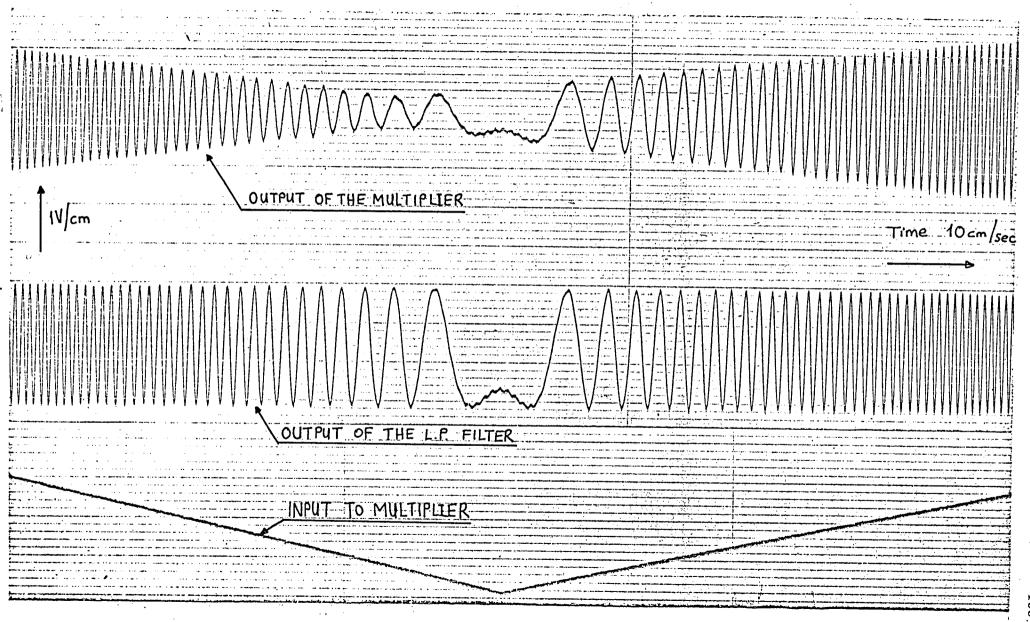

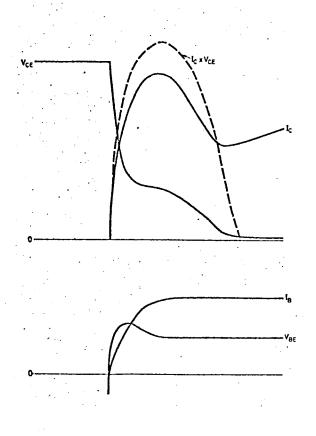

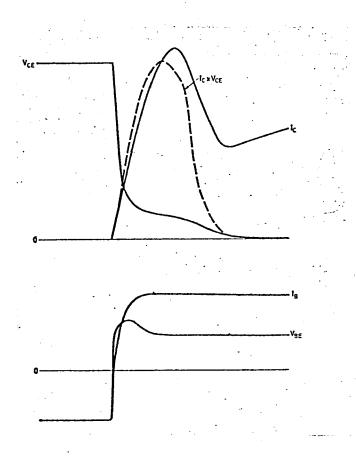

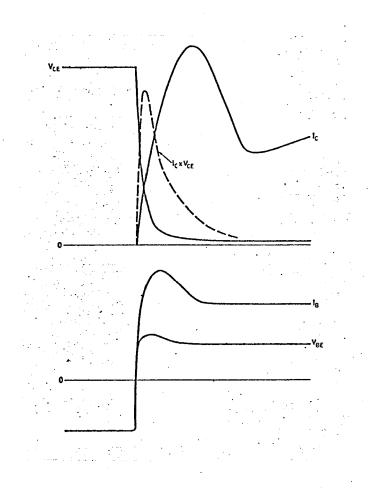

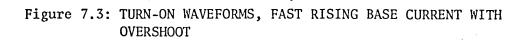

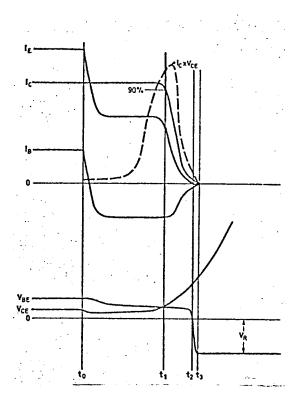

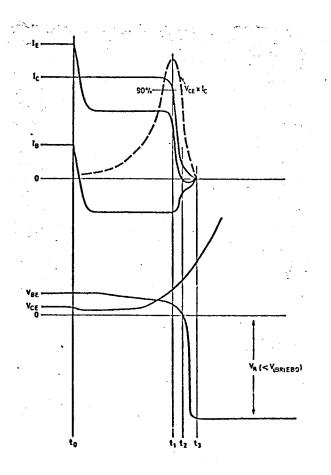

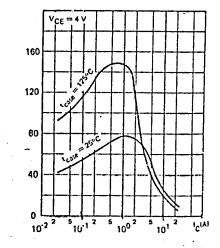

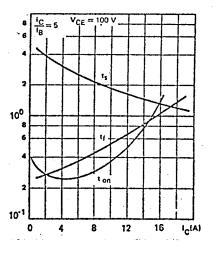

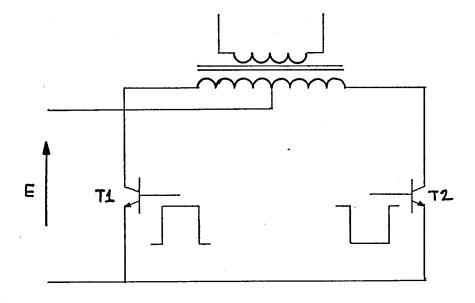

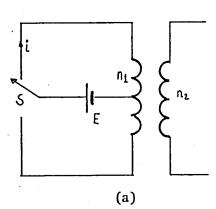

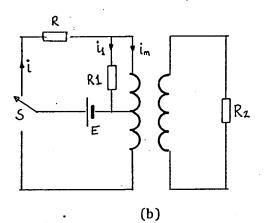

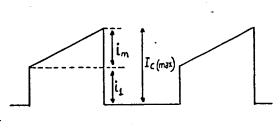

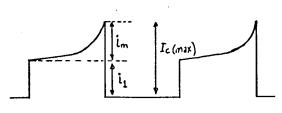

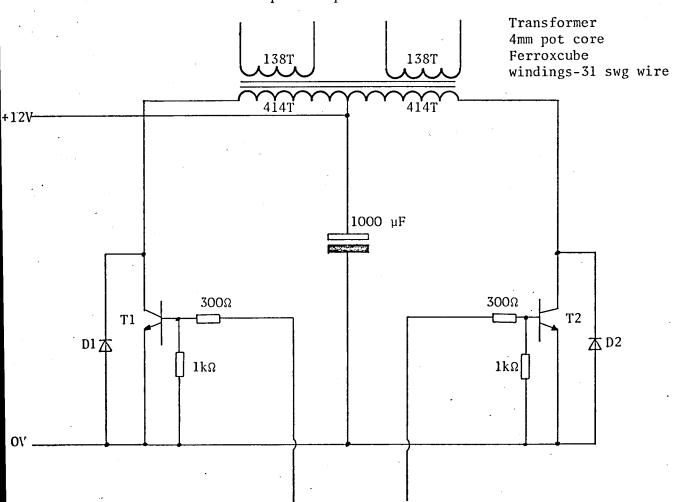

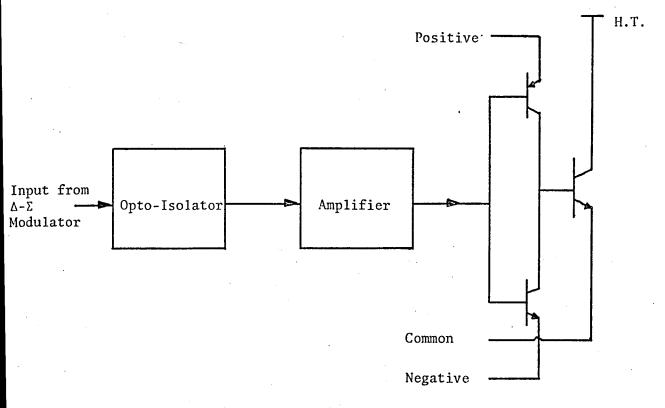

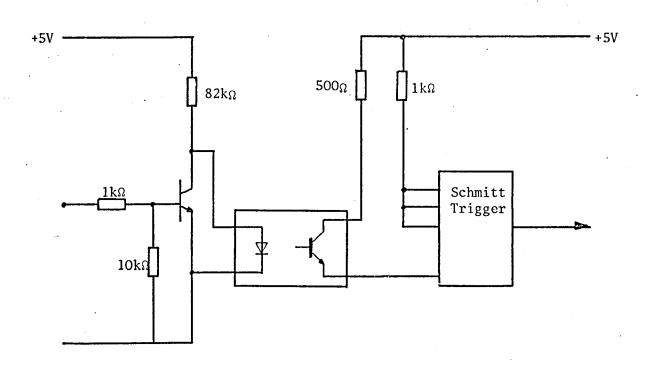

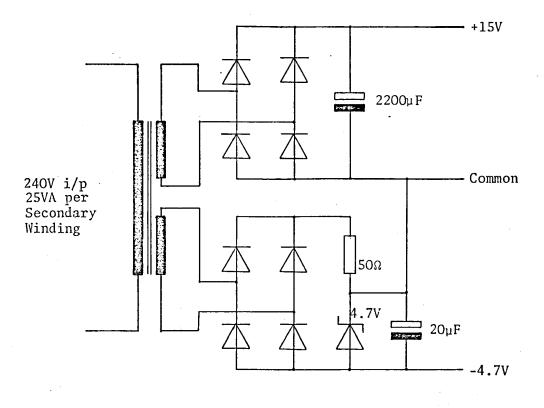

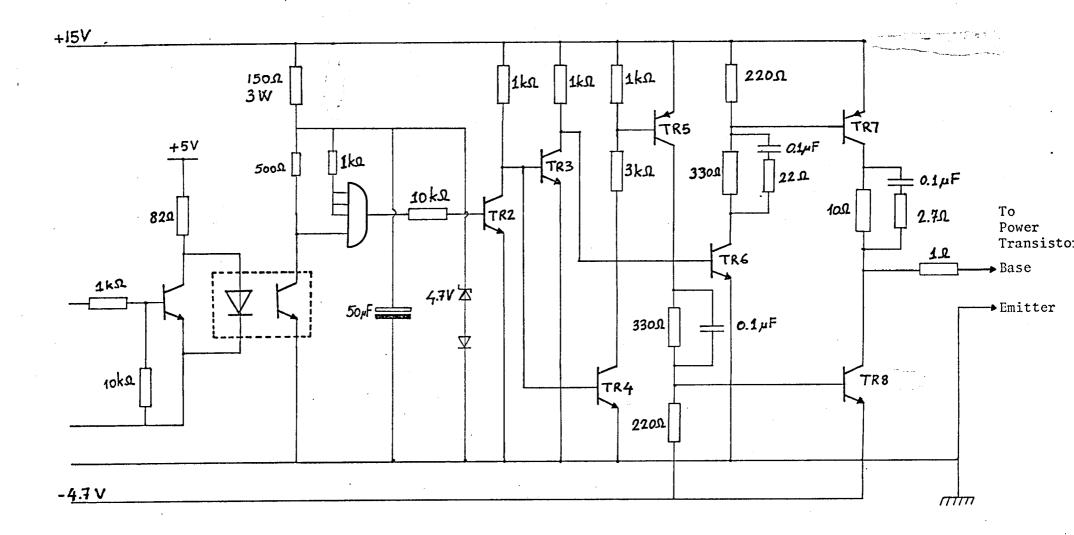

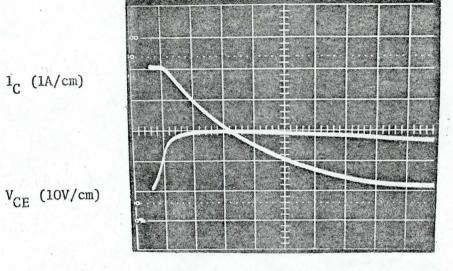

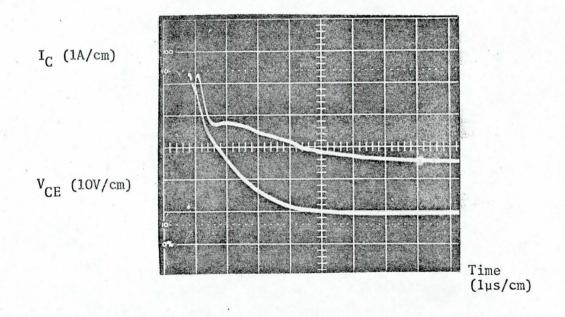

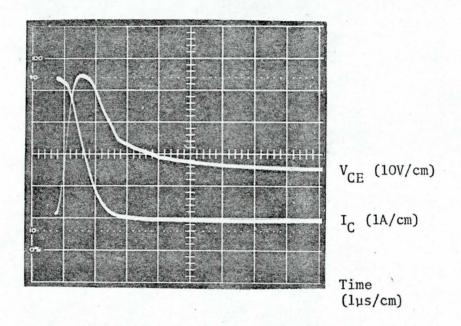

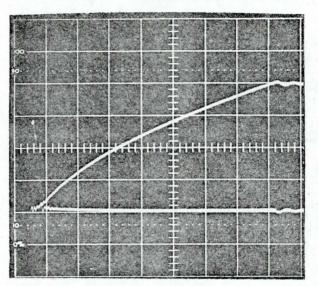

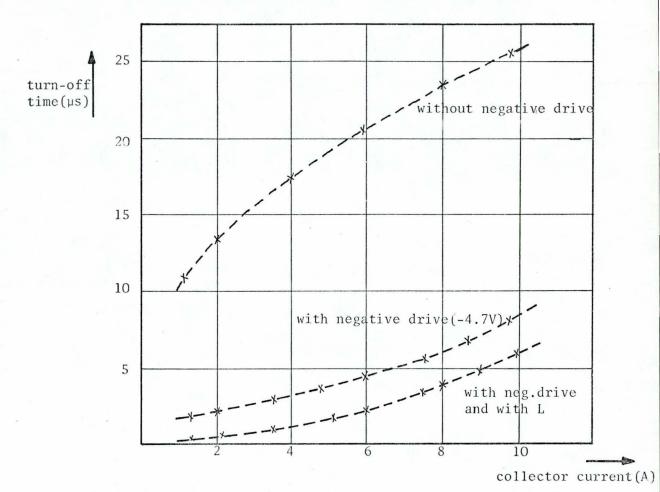

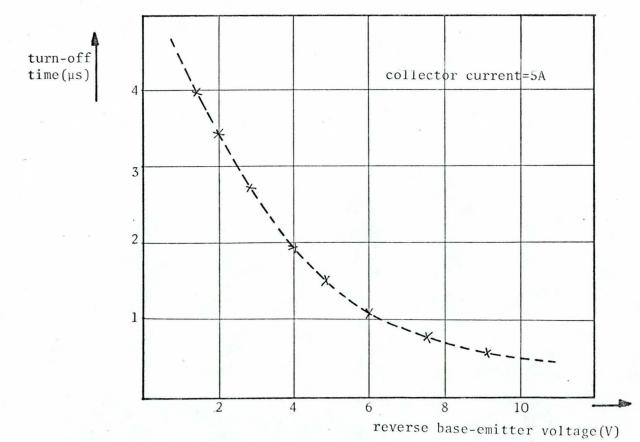

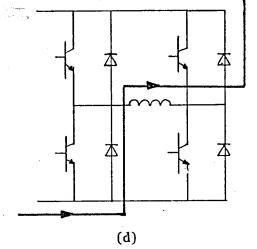

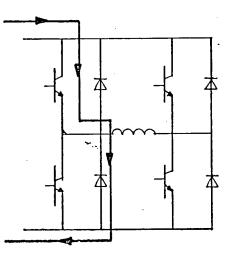

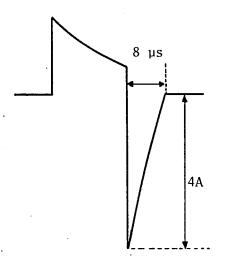

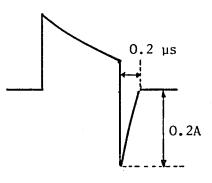

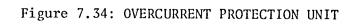

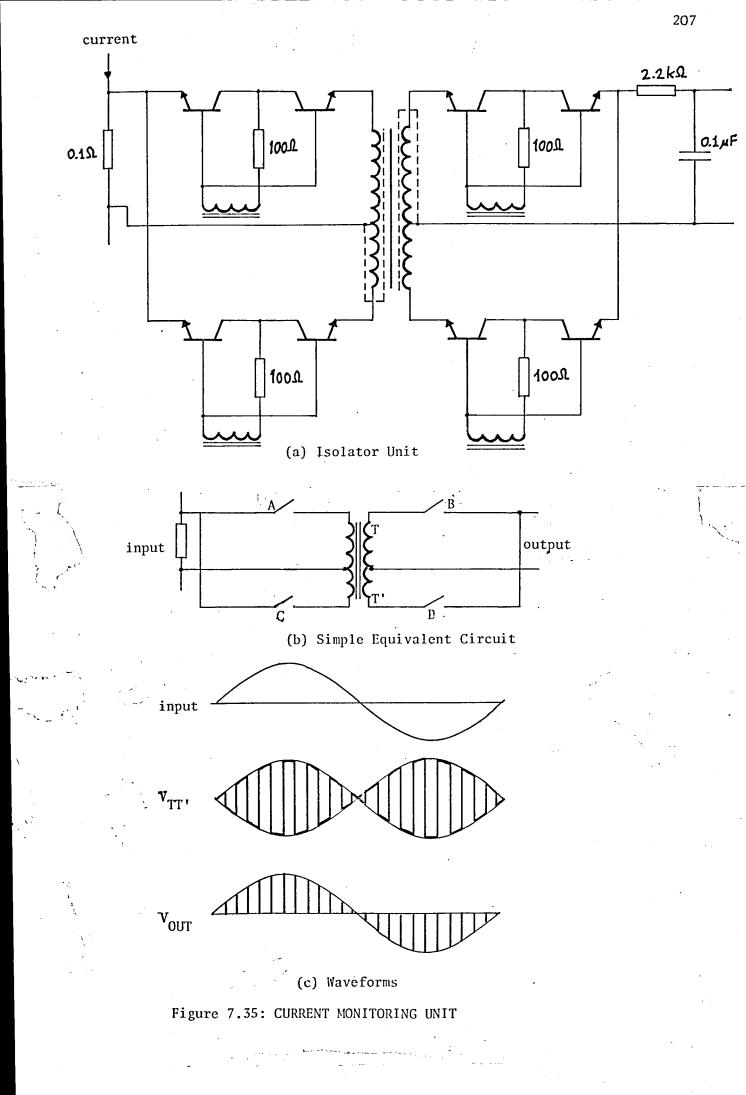

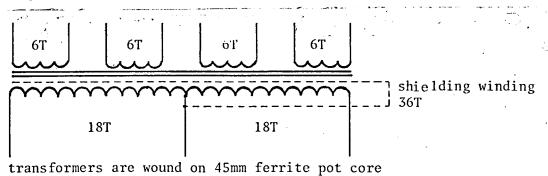

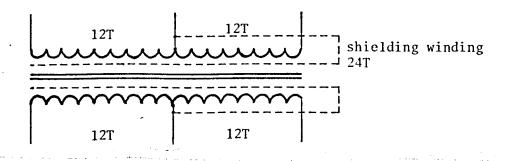

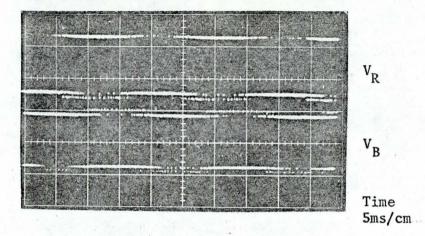

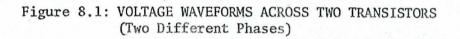

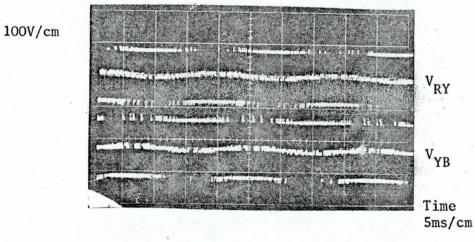

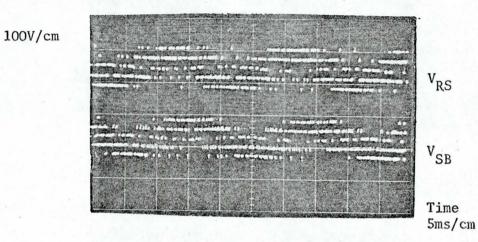

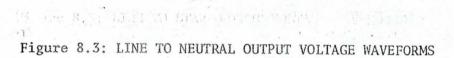

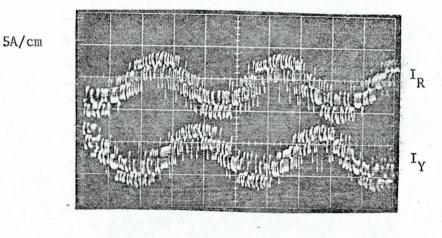

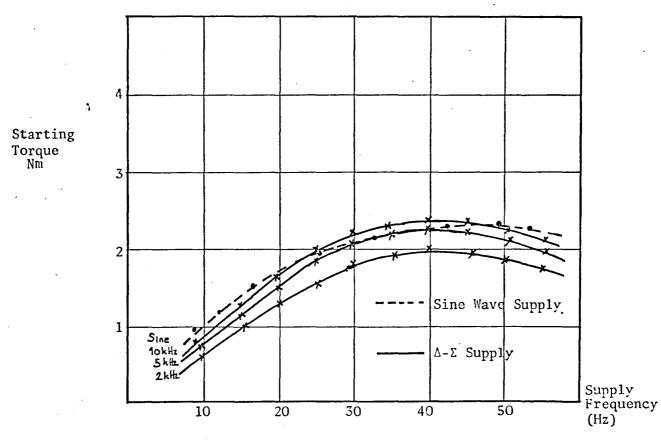

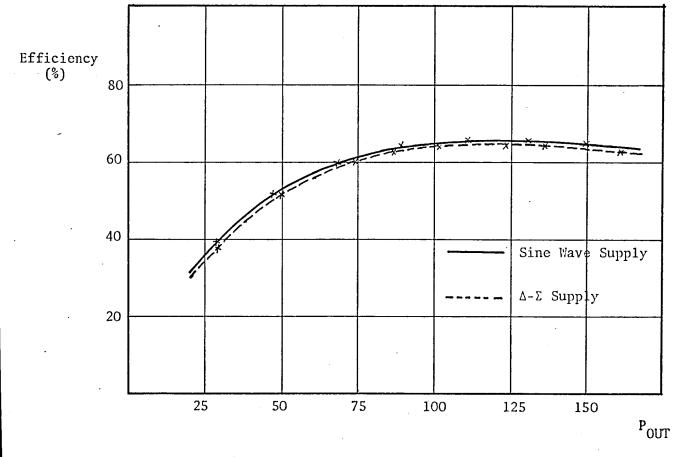

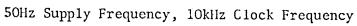

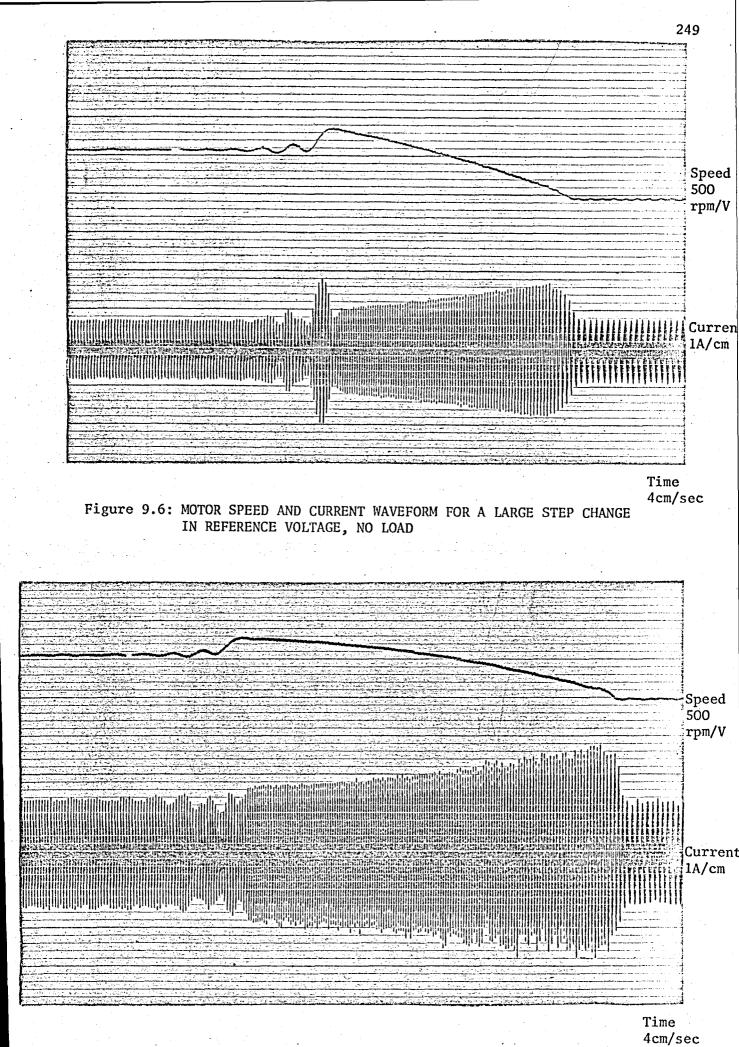

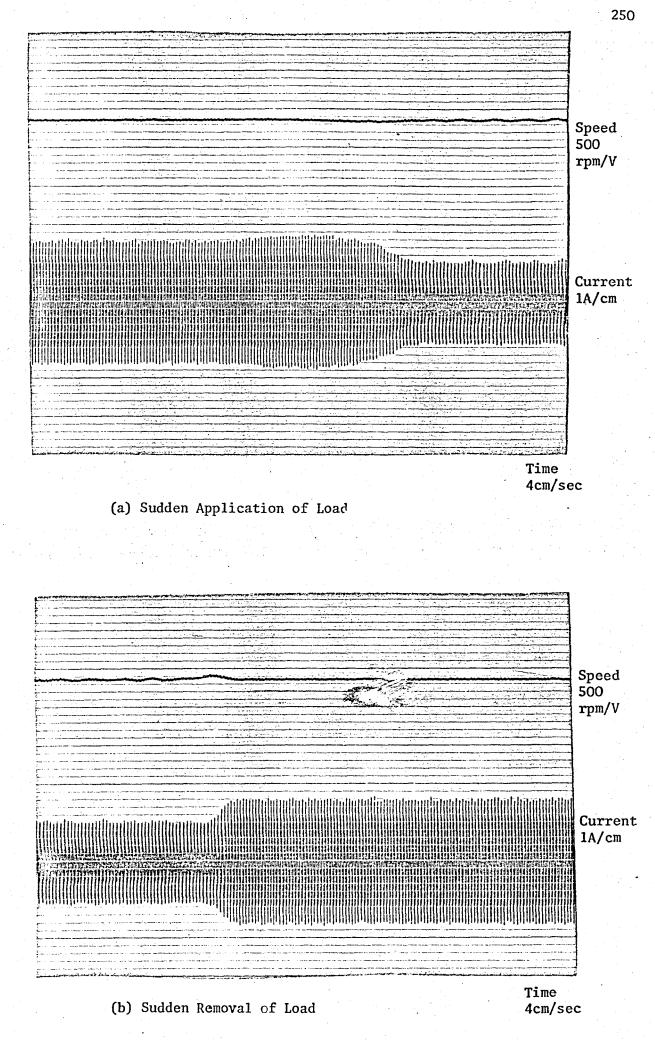

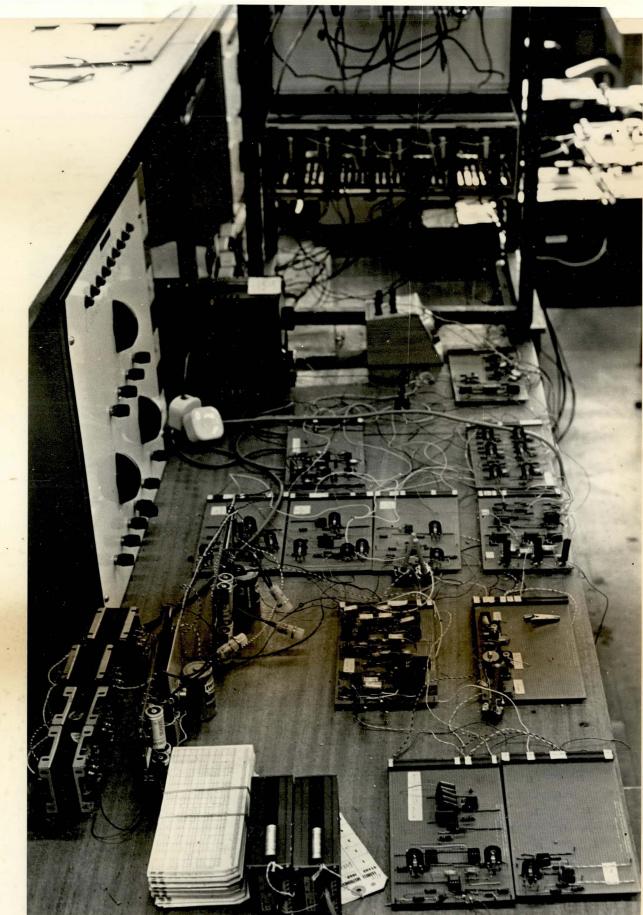

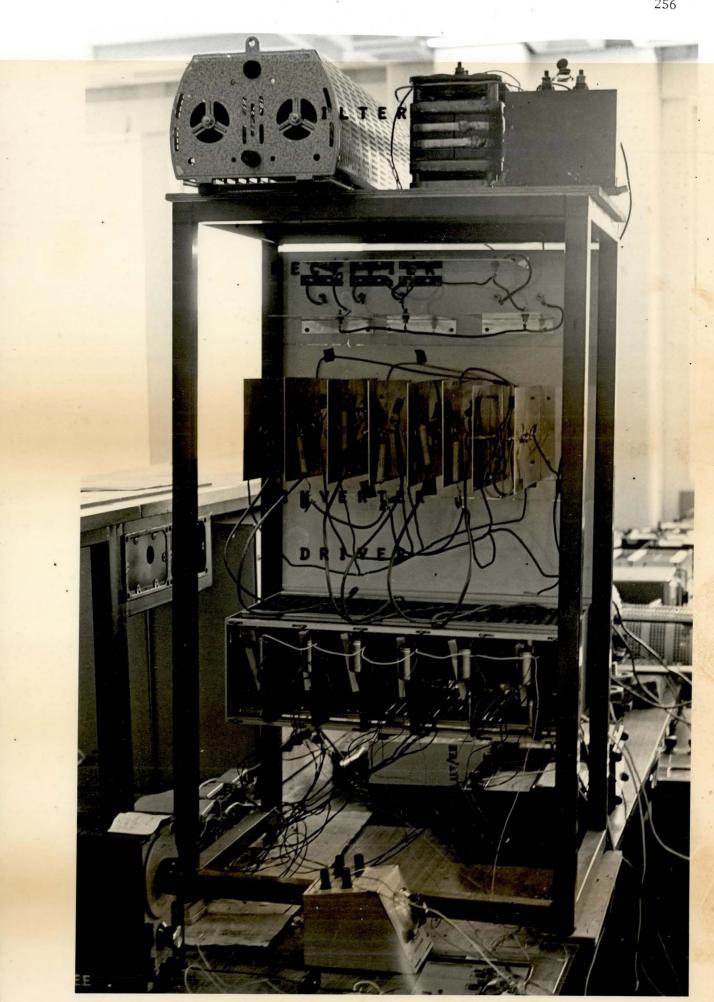

$$= E_{\min} = \frac{16V(f^{2}+f_{1}^{2})^{\frac{1}{2}}(f^{2}+f_{2}^{2})^{\frac{1}{2}}}{\pi f_{c}^{2}} \qquad (3.13)$$