## Specification and Verification of Network Algorithms Using Temporal Logic

by

Ra'ed Bani Abdelrahman

A Doctoral Thesis

Submitted in partial fulfilment of the requirements for the award of

> Doctor of Philosophy of Loughborough University

> > 12 December 2018

Copyright 2018 Ra'ed Bani Abdelrahman

## Abstract

In software engineering, formal methods are mathematical-based techniques that are used in the specification, development and verification of algorithms and programs in order to provide reliability and robustness of systems. One of the most difficult challenges for software engineering is to tackle the complexity of algorithms and software found in concurrent systems. Networked systems have come to prominence in many aspects of modern life, and therefore software engineering techniques for treating concurrency in such systems has acquired a particular importance. Algorithms in the software of concurrent systems are used to accomplish certain tasks which need to comply with the properties required of the system as a whole. These properties can be broadly subdivided into 'safety properties', where the requirement is 'nothing bad will happen', and 'liveness properties', where the requirement is that 'something good will happen'. As such, specifying network algorithms and their safety and liveness properties through formal methods is the aim of the research presented in this thesis. Since temporal logic has proved to be a successful technique in formal methods, which have various practical applications due to the availability of powerful model-checking tools such as the NuSMV model checker, we will investigate the specification and verification of network algorithms using temporal logic and model checking. In the first part of the thesis, we specify and verify safety properties for network algorithms. We will use temporal logic to prove the safety property of data consistency or serializability for a model of the execution of an unbounded number of concurrent transactions over time, which could represent software schedulers for an unknown number of transactions being present in a network. In the second part of the thesis, we will specify and verify the liveness properties of networked flooding algorithms.

Considering the above in more detail, the first part of this thesis specifies a model of the execution of an unbounded number of concurrent transactions over time in propositional Linear Temporal Logic (LTL) in order to prove serializability. This is made possible by assuming that data items are ordered and that the transactions accessing these data items respects this order, as then there is a bound on the number of transactions that need to be considered to prove serializability. In particular, we make use of recent work which places such bounds on the number of transactions needed when data items are accessed in order, but do not have to be accessed contiguously, i.e., there may be 'gaps' in the data items being accessed by individual transactions. Our aim is to specify the concurrent modification of data held on routers in a network as a transactional model. The correctness of the routing protocol and ensuring safety and reliability then corresponds to the serializability of the transactions. We specify an example of routing in a network and the corresponding serializability condition in LTL. This is then coded up in the NuSMV model checker and proofs are performed. The novelty of this part is that no previous research has used a method for detecting serializablity and cycles for unlimited number of transactions accessing the data on routers where the transactions way of accessing the data items on the routers have a gap. In addition to this, linear temporal logic has not been used in this scenario to prove correctness of the network system. This part is very helpful in network administrative protocols where it is critical to maintain correctness of the system. This safety property can be maintained using the presented work where detection of cycles in transactions accessing the data items can be detected by only checking a limited number of cycles rather than checking all possible cycles that can be caused by the network transactions.

The second part of the thesis offers two contributions. Firstly, we specify the basic synchronous network flooding algorithm, for any fixed size of network, in LTL. The specification can be customized to any single network topology or class of topologies. A specification for the termination problem is formulated and used to compare different topologies with regards to earlier termination. We give a worked example of one topology resulting in earlier termination than another, for which we perform a formal verification using the NuSMV model checker. The novelty of the second part comes in using linear temporal logic and the NuSMV model checker to specify and verify the liveness property of the flooding algorithm. The presented work shows a very difficult scenario where the network nodes are memoryless. This makes detecting the termination of network flooding very complicated especially with networks of complex topologies. In the literature, researchers focussed on using testing and simulations to detect flooding termination. In this work, we used a robust technique and a rigorous method to specify and verify the synchronous flooding algorithm and its termination. We also showed that we can use linear temporal logic and the model checker NuSMV to compare synchronous flooding termination between topologies.

Adding to the novelty of the second contribution, in addition to the synchronous form of the network flooding algorithm, we further provide a formal model of bounded asynchronous network flooding by extending the synchronous flooding model to allow a sent message, non-deterministically, to either be received instantaneously, or enter a transit phase prior to being received. A generalization of 'rounds' from synchronous flooding to the asynchronous case is used as a unit of time to provide a measure of time to termination, as the number of rounds taken, for a run of an asynchronous system. The model is encoded into temporal logic and a proof obligation is given for comparing the termination times of asynchronous and synchronous systems. Worked examples are formally verified using the NuSMV model checker. This work offers a constraint-based methodology for the verification of liveness properties of software algorithms distributed across the nodes in a network.

## Acknowledgements

This research was funded by Ajloun National University, Jordan. Many thanks goes to Ajloun National University for providing the funding for this research.

Foremost, I would like to express my deepest appreciation to my supervisors Dr. Amitabh Trehan, Dr. Rafat Alshorman and Dr. Walter Hussak for their guidance, support and kindness through my PhD study journey.

A very special gratitude goes to my parents for their support, encouragement, love and prayers.

My heartfelt thanks go to my wife, children, brothers and sisters and all family members who have been an essential and indispensable source for moral support, selfless support, understanding, with constant love.

Special thanks goes to my supportive friends and to everyone I met and supported me during my PhD journey.

## Contents

| A        | bstra | $\operatorname{ct}$                             | ii           |

|----------|-------|-------------------------------------------------|--------------|

| A        | cknov | wledgements                                     | $\mathbf{v}$ |

| 1        | Intr  | oduction                                        | 1            |

|          | 1.1   | Background                                      | 1            |

|          | 1.2   | Overview of the state-of-art                    | 4            |

|          | 1.3   | Statement of the research problem/knowledge gap | 4            |

|          | 1.4   | Critical evaluation                             | 5            |

|          | 1.5   | Aim                                             | 5            |

|          | 1.6   | Objectives                                      | 6            |

|          | 1.7   | Contributions                                   | 6            |

|          | 1.8   | Overview of thesis chapters                     | 7            |

| <b>2</b> | Res   | earch Background                                | 8            |

|          | 2.1   | Better Software Engineering                     | 11           |

|          | 2.2   | Formal Methods                                  | 12           |

|          | 2.3   | Basics of Database and Transactions             | 13           |

|          |       | 2.3.1 Importance of Concurrency Control         | 15           |

|          | 2.4   | Distributed Systems                             | 18           |

|          | 2.5   | Temporal Logic                                  | 24           |

|          |       | 2.5.1 Temporal Properties                       | 26           |

|          |       | 2.5.2 Temporal Operators                        | 27           |

|          |       | 2.5.3 Properties Expressed in Temporal Logic    | 27           |

|          | 2.6   | Model Checking                                  | 29           |

|          |       | 2.6.1 Stages of Model Checking                  | 31           |

|          |       | 2.6.2 Transactions and Temporal Logic           | 31           |

|          | 2.7   | Thesis Structure                                | 32           |

| 3        | Lite  | erature review and RM                           | 34           |

|          | 3.1   | Introduction                                    | 34           |

|          | 3.2                                                                         | Literature Review                                                                                                                                                                                                                                                                        | 35                                                                                                                                             |

|----------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.3                                                                         | Motivation                                                                                                                                                                                                                                                                               | 38                                                                                                                                             |

|          | 3.4                                                                         | Research Methodology                                                                                                                                                                                                                                                                     | 39                                                                                                                                             |

| 4        | Net                                                                         | work routing protocols                                                                                                                                                                                                                                                                   | 40                                                                                                                                             |

|          | 4.1                                                                         | Introduction                                                                                                                                                                                                                                                                             | 40                                                                                                                                             |

|          | 4.2                                                                         | Motivation                                                                                                                                                                                                                                                                               | 41                                                                                                                                             |

|          | 4.3                                                                         | Methodology                                                                                                                                                                                                                                                                              | 41                                                                                                                                             |

|          | 4.4                                                                         | Concurrent Transactions and Serializability                                                                                                                                                                                                                                              | 42                                                                                                                                             |

|          |                                                                             | 4.4.1 Concurrent Transactions and Histories                                                                                                                                                                                                                                              | 42                                                                                                                                             |

|          |                                                                             | 4.4.2 Transactions Accessing Data in the Same Order                                                                                                                                                                                                                                      | 43                                                                                                                                             |

|          | 4.5                                                                         | Description of the Protocol                                                                                                                                                                                                                                                              | 46                                                                                                                                             |

|          | 4.6                                                                         | Temporal Logic                                                                                                                                                                                                                                                                           | 47                                                                                                                                             |

|          |                                                                             | 4.6.1 Syntax of LTL                                                                                                                                                                                                                                                                      | 48                                                                                                                                             |

|          |                                                                             | 4.6.2 Semantics of LTL                                                                                                                                                                                                                                                                   | 48                                                                                                                                             |

|          | 4.7                                                                         | Specification of Routing Protocol in LTL                                                                                                                                                                                                                                                 | 49                                                                                                                                             |

|          | 4.8                                                                         | Verification of the Routing Protocol using the NuSMV model checker                                                                                                                                                                                                                       | 55                                                                                                                                             |

|          | 4.9                                                                         | Conclusion                                                                                                                                                                                                                                                                               | 56                                                                                                                                             |

| <b>5</b> | Syn                                                                         | chronous network flooding                                                                                                                                                                                                                                                                | 57                                                                                                                                             |

|          | 5.1                                                                         | Introduction                                                                                                                                                                                                                                                                             | 57                                                                                                                                             |

|          | 5.2                                                                         | The Synchronous Flooding Algorithm                                                                                                                                                                                                                                                       | 58                                                                                                                                             |

|          |                                                                             |                                                                                                                                                                                                                                                                                          |                                                                                                                                                |

|          | 5.3                                                                         | Linear Temporal Logic                                                                                                                                                                                                                                                                    | 60                                                                                                                                             |

|          | 5.3                                                                         | Linear Temporal Logic                                                                                                                                                                                                                                                                    |                                                                                                                                                |

|          | 5.3                                                                         |                                                                                                                                                                                                                                                                                          | 60                                                                                                                                             |

|          | 5.3<br>5.4                                                                  | 5.3.1 Syntax of LTL                                                                                                                                                                                                                                                                      | 60<br>60                                                                                                                                       |

|          |                                                                             | 5.3.1       Syntax of LTL       Syntax of LTL         5.3.2       Semantics of LTL       Syntax                                                                                                                                                                                          | 60<br>60<br>61                                                                                                                                 |

|          |                                                                             | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm                                                                                                                                                                                               | 60<br>60<br>61<br>62                                                                                                                           |

|          |                                                                             | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions                                                                                                                                                                         | 60<br>60<br>61<br>62<br>62                                                                                                                     |

|          |                                                                             | 5.3.1Syntax of LTL                                                                                                                                                                                                                                                                       | 60<br>60<br>61<br>62<br>62                                                                                                                     |

|          |                                                                             | <ul> <li>5.3.1 Syntax of LTL</li></ul>                                                                                                                                                                                                                                                   | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>62</li> <li>63</li> </ul>                                                             |

|          |                                                                             | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions                                                                                  | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>63</li> </ul>                                                 |

|          |                                                                             | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions5.4.5Topological Constraints                                                      | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> </ul>                                     |

|          | 5.4                                                                         | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions5.4.5Topological Constraints5.4.6Termination                                      | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> <li>66</li> </ul>                         |

|          | 5.4                                                                         | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions5.4.5Topological Constraints5.4.6TerminationApplications                          | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> <li>70</li> </ul>             |

| 6        | 5.4<br>5.5<br>5.6<br>5.7                                                    | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions5.4.5Topological Constraints5.4.6TerminationApplicationsWorked ExampleConclusions | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> </ul>             |

| 6        | 5.4<br>5.5<br>5.6<br>5.7                                                    | 5.3.1       Syntax of LTL                                                                                                                                                                                                                                                                | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> <li>66</li> <li>66</li> <li>70</li> <li>76</li> </ul> |

| 6        | <ul> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>Asy</li> </ul> | 5.3.1Syntax of LTL5.3.2Semantics of LTLSpecification of the Synchronous Flooding Algorithm5.4.1Edge Propositions5.4.2Send-message Propositions5.4.3Message-received Propositions5.4.4Initial Conditions5.4.5Topological Constraints5.4.6TerminationApplicationsWorked ExampleConclusions | <ul> <li>60</li> <li>60</li> <li>61</li> <li>62</li> <li>63</li> <li>63</li> <li>64</li> <li>66</li> <li>70</li> <li>76</li> <li>78</li> </ul> |

|                           |                                               | 6.3.1                                             | Propositions                                                                                                                                                                                           |                |          |     | • | 83                                                                                       |

|---------------------------|-----------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-----|---|------------------------------------------------------------------------------------------|

|                           |                                               | 6.3.2                                             | States                                                                                                                                                                                                 |                |          | •   |   | 83                                                                                       |

|                           |                                               | 6.3.3                                             | Run constraints                                                                                                                                                                                        |                |          |     | • | 84                                                                                       |

|                           |                                               | 6.3.4                                             | Termination                                                                                                                                                                                            |                |          |     | • | 85                                                                                       |

|                           |                                               | 6.3.5                                             | Rounds                                                                                                                                                                                                 |                |          |     | • | 85                                                                                       |

|                           | 6.4                                           | Compa                                             | ring Asynchronous and Synchronous Termination                                                                                                                                                          | n.             |          |     | • | 86                                                                                       |

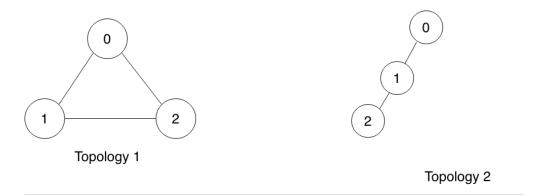

|                           |                                               | 6.4.1                                             | Worked Examples                                                                                                                                                                                        |                |          | •   | • | 87                                                                                       |

|                           | 6.5                                           | Conclu                                            | sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                          |                |          |     | • | 94                                                                                       |

| _                         | C                                             |                                                   |                                                                                                                                                                                                        |                |          |     |   |                                                                                          |

| 7                         | Con                                           | nclusior                                          |                                                                                                                                                                                                        |                |          |     |   | 97                                                                                       |

|                           | 7.1                                           | Future                                            | work                                                                                                                                                                                                   | •••            |          | •   | • | 98                                                                                       |

|                           |                                               |                                                   |                                                                                                                                                                                                        |                |          |     |   |                                                                                          |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                                          | dix                                               |                                                                                                                                                                                                        |                |          |     |   | 108                                                                                      |

| -                         |                                               |                                                   | cotocol encoding into LTL                                                                                                                                                                              |                |          |     |   | 108<br>108                                                                               |

| -                         | Rou                                           | iting p                                           | cotocol encoding into LTL<br>us Flooding Algorithm encoding into LTL                                                                                                                                   |                |          |     |   |                                                                                          |

| A                         | Rou                                           | iting p<br>chrono                                 | -                                                                                                                                                                                                      | de =           | 0.       |     |   | 108<br>114                                                                               |

| A                         | Rou<br>Syn                                    | n <b>ting p</b><br>chrono<br>Topol                | us Flooding Algorithm encoding into LTL                                                                                                                                                                |                |          |     |   | <b>108</b><br><b>114</b><br>114                                                          |

| A                         | Rou<br>Syn<br>B.1                             | <b>iting p</b><br><b>chrono</b><br>Topol<br>Topol | us Flooding Algorithm encoding into LTL<br>ogy1 terminates before Topology2 with initial no                                                                                                            | de =           | 0.       | •   | • | <b>108</b><br><b>114</b><br>114<br>116                                                   |

| A                         | <b>Rou</b><br><b>Syn</b><br>B.1<br>B.2<br>B.3 | nting pr<br>chrono<br>Topol<br>Topol<br>Topol     | us Flooding Algorithm encoding into LTL<br>ogy1 terminates before Topology2 with initial not<br>ogy2 terminates before Topology1 with initial not                                                      | de =           | 0.       | •   | • | <b>108</b><br><b>114</b><br>114<br>116                                                   |

| A                         | <b>Rou</b><br><b>Syn</b><br>B.1<br>B.2<br>B.3 | nting pr<br>chrono<br>Topol<br>Topol<br>Topol     | us Flooding Algorithm encoding into LTL<br>ogy1 terminates before Topology2 with initial not<br>ogy2 terminates before Topology1 with initial not<br>ogy1 terminates before Topology2 regardless of ir | de =<br>nitial | 0.<br>no | ode |   | <ul> <li>108</li> <li>114</li> <li>114</li> <li>116</li> <li>118</li> <li>121</li> </ul> |

## List of Figures

| 1.1 | Safety-Critical Systems Controller Diagram.                               | 2  |

|-----|---------------------------------------------------------------------------|----|

| 2.1 | A graphic representation of problems resulting from errors in spe-        |    |

|     | cifications                                                               | 12 |

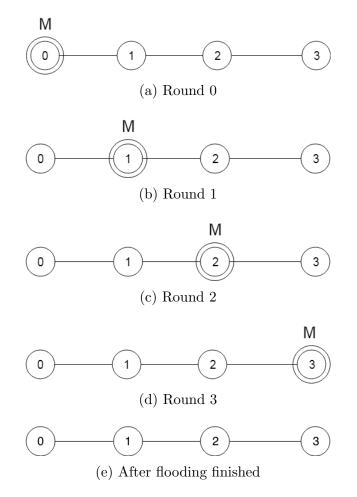

| 2.2 | Flooding - line connection                                                | 20 |

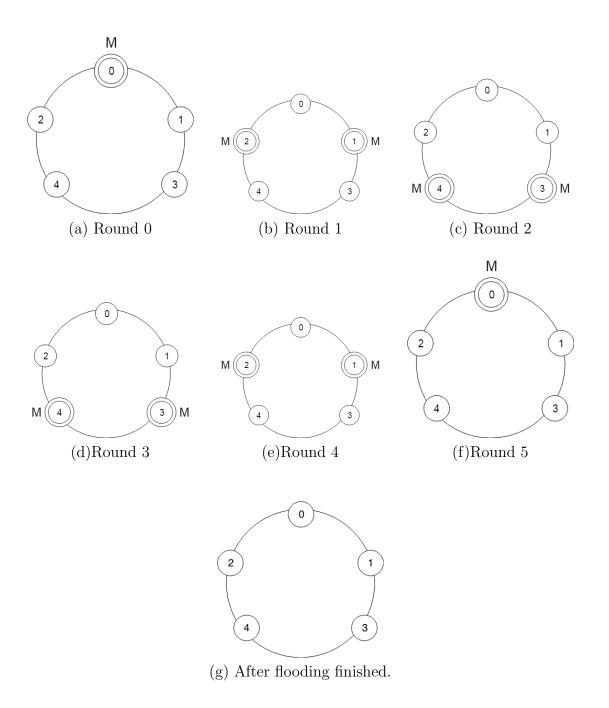

| 2.3 | Flooding - ring connection                                                | 22 |

| 2.4 | Flooding - triangle connection                                            | 23 |

| 2.5 | Flooding - 2 ring connection                                              | 24 |

| 2.6 | Thesis Chapters                                                           | 33 |

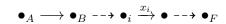

| 4.1 | Representation of the set of ordered routers                              | 47 |

| 4.2 | Representation of the set of ordered routers with gaps. $\ldots$ $\ldots$ | 47 |

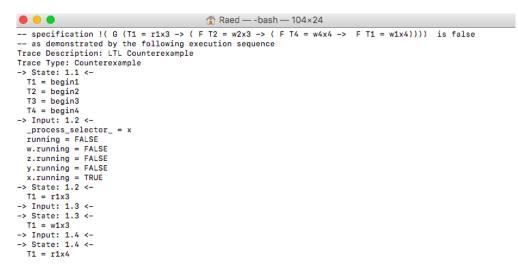

| 4.3 | Counterexample on cycle $T_1T_3T_2T_1$                                    | 53 |

| 4.4 | Counterexample on cycle $T_1T_2T_4T_1$                                    | 53 |

| 4.5 | Counterexample on cycle $T_2T_1T_4T_2$                                    | 54 |

| 4.6 | Counterexample on cycle $T_3T_2T_4T_3$                                    | 54 |

| 4.7 | Counterexample on cycle $T_3T_1T_4T_3$                                    | 55 |

| 4.8 | Counterexample on cycle $T_3T_1T_4T_3$                                    | 55 |

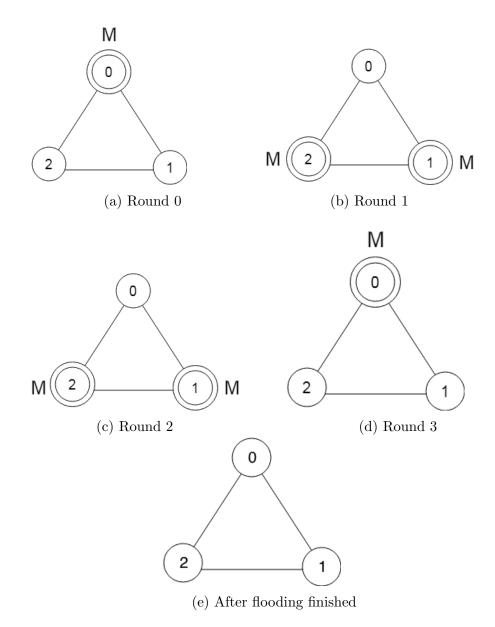

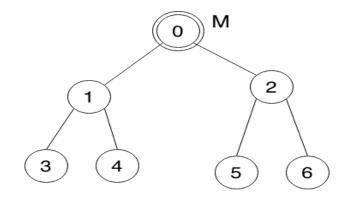

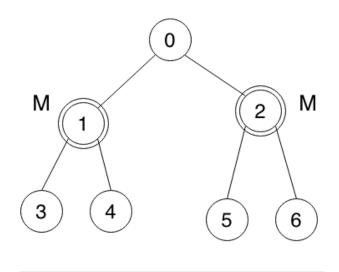

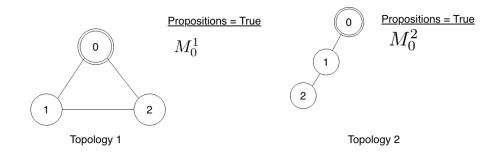

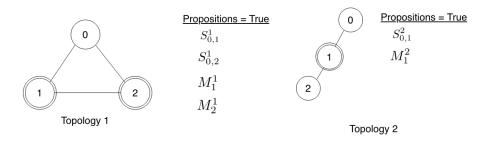

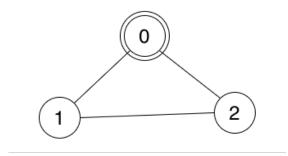

| 5.1 | Flooding example 1                                                        | 59 |

| 5.2 | Flooding example 2                                                        | 60 |

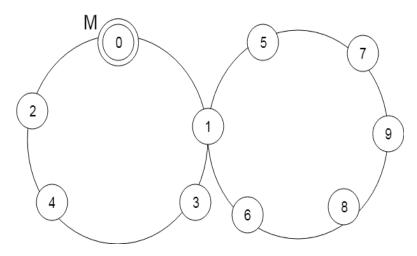

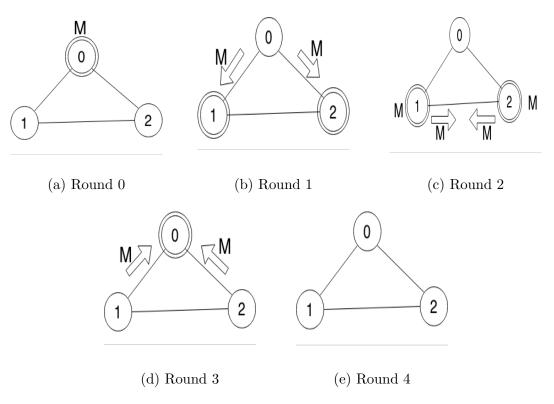

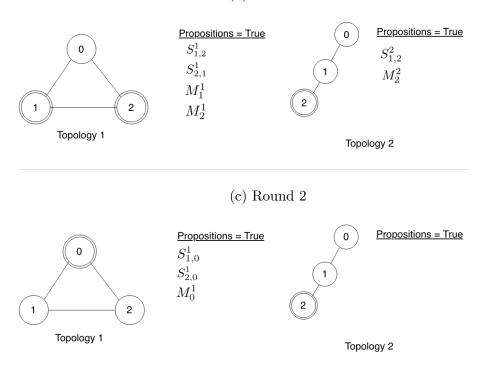

| 5.3 | Flooding on two topologies                                                | 66 |

| 5.4 | Flooding rounds in two topologies                                         | 68 |

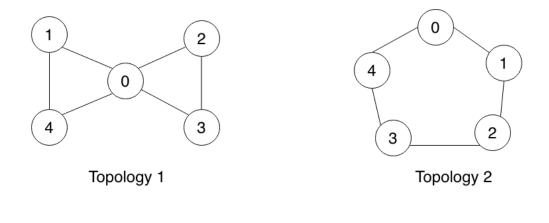

| 5.5 | Two topologies containing five nodes                                      | 70 |

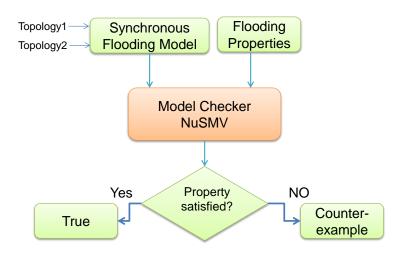

| 5.6 | Synchronous flooding model checking block diagram                         | 71 |

| 5.7 | Toplogy1 terminates before Topology2 with initial node 0. $\ldots$ .      | 74 |

| 5.8 | Toplogy2 terminates before Topology1 with initial node 0. $\ldots$ .      | 75 |

| 5.9 | Topology1 terminates before Topology2 always                              | 76 |

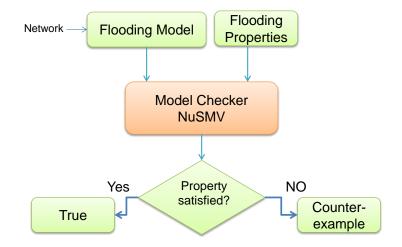

| 6.1 | Example 2.6                                                               | 81 |

| 6.2 | Synchronous and Asynchronous flooding model checking block dia-           |    |

|     | gram                                                                      | 88 |

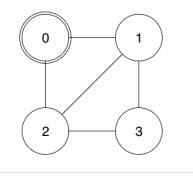

| 6.3 Figure of four nodes | 91 |

|--------------------------|----|

|--------------------------|----|

## List of Tables

| 2.1 | Two transactions executing simultaneously               | 16 |

|-----|---------------------------------------------------------|----|

| 2.2 | Bus tickets - two transactions executing simultaneously | 16 |

| 2.3 | Dirty read problem example                              | 17 |

| 2.4 | Temporal logic operators.                               | 27 |

## Chapter 1 Introduction

This chapter presents a brief background to the research conducted, and an overview of the state-of-art (which will be presented in details in the Literature Review Chapter), statement of the research problem, critical evaluation, aim, objectives, contributions and then an overview to the thesis chapters.

#### 1.1 Background

Software is used in different devices and systems to accomplish specific tasks according to the device and environment. Many of the devices that we see around us come with a software which controls it. The software that controls the working of an Information and Communication Device is our interest. examples of such devices include the automated teller machine (ATM) where the user inputs the card key and make a selection of the amount of money required and an output in cash is given to the user. An aeroplane is another example. Inputs can be as location, weather, ...,etc. which will be given to the programs that control the aeroplane in deciding its trajectory. Medical instruments such as a pacemaker which is used to monitor and regulate the heartbeat of a human heart takes inputs as signals of the heart and give outputs by the program as to control the heartbeat. Autonomous cars are also another example of such systems and devices. This type of program which controls these devices is called a controller of the device. The controller listens to inputs and takes decisions and gives outputs as shown in Figure 1.1.

Figure 1.1: Safety-Critical Systems Controller Diagram.

Due to the high costs of errors in safety-critical systems, better software engineering methods need to take place to avoid defects in controllers. While designing controllers for safety-critical systems, it is important to ensure that the controller is reliable and takes correct decisions which cover all possible scenarios. Usually, the controllers come with a set of requirements that they need to satisfy. To check if the controller satisfies its requirements, test cases can be used to find the outcomes, but when the number of components that interact with the controller increases, manual verification becomes increasingly difficult where some errors of the controller can go unnoticed. A verification technology called model checking can solve this problem. The approach to do the verification is by constructing a mathematical model of the device controller and writing its requirements in a formal notation. If the mathematical model of the controller satisfies the requirements written in this formal notation, then this means that the controller satisfies its requirements. This is done automatically which eliminates human errors of manual proofs. Temporal logic proved to be a successful technique in formal methods and can be used to specify the properties of critical systems.

This research focuses on using temporal logic on distributed systems as they are considered reactive systems and have properties to be met. Reliability and safety are two of the main concerns in critical computer-based systems. The jobs running on these systems are not tolerant to errors in output. Concurrency makes these systems very difficult to build and verify, especially in light of the emergence of mobile systems. The transactions within concurrent systems require the use of shared resources. The resources that are accessed and updated by such concurrent transactions should leave the system in a consistent state, as having more than one transaction attempting to access and update similar data items could leave the system in an inconsistent and unsafe state. If we look at networking systems, we notice that the software used to make sure a certain packet is delivered from its source to its destination, on routers in this instance, is built according to certain routing algorithms. Routing protocols serve to specify the path by which data packets are delivered to the specified destination. Routing protocols are usually tested according to different situations and scenarios, but in these situations which are not tested for there is the possibility that a system could malfunction or become insecure.

This research considers maintaining the safety property, which means that nothing bad will happen, in a distributed system where routers in a network have data items that are shared by unlimited number of transactions. This is considered a new contribution where unlimited number of transactions access data items in with a 'gap', which will be defined later in Chapter 4. This contribution provides easier cycle detection after calculating the gap. The contribution here provides correctness for the network routers. Other research mainly focuses on testing/simulations. The method presented here explores all possible system states in a bruteforce manner. As concurrency can cause different problems in a system, specifying the system and verifying it should be accomplished in a way which maintains the system safety. Accessing the data items on routers can lead to having the data being modified in an incorrect way which will violate the safety property of the system. The transactions also need to be managed in by certain rules which leads to a safe system state. A network protocol is presented in Chapter 4 to help maintaining the safety property in distributed systems. The research also focuses on the liveness property, something good will happen, in message passing distributed systems. The second and third contributions work with memory-less network flooding where nodes on the network don't have memory. The well-know synchronous and asynchronous flooding algorithm is specified and verified. The termination of the flooding algorithm is specified and verified using linear temporal logic (LTL) and the NuSMV model checker. In the second contribution, we specify the basic synchronous network flooding, for any fixed size of network, in LTL. The specification can be customized to any single network topology or class of topologies. A specification for the termination problem is formulated and used to compare different topologies with regards to earlier termination. A worked example is given of one topology resulting in earlier termination than another, for which we perform a formal verification using the NuSMV model checker. In the third contribution, we provide a formal model of bounded asynchronous network flooding by extending the synchronous flooding model to allow a sent message, non-deterministically, to either be received instantaneously, or enter a transit phase prior to being received. A generalization of 'rounds' from synchronous flooding to the asynchronous case is used as a unit of time to provide a measure of time to termination, as the number of rounds taken, for a run of an asynchronous system. The model is encoded into temporal logic to compare the termination times of asynchronous and synchronous systems. Worked examples are formally verified using the NuSMV model checker. This work offers a constraint-based methodology for the verification of liveness properties of software algorithms distributed across the nodes in a network.

#### **1.2** Overview of the state-of-art

State-of-the-art, formal methods, are used in system specifications, especially in critical systems where the cost of failure could notably go beyond the cost of system development. Formal methods are mathematical entities that can be used to model the system in question, and are used to model system properties in a thorough manner. Formal methods are mathematical-based techniques used for both the specification and verification of software systems. The use of formal methods in software engineering ensures a certain robustness and reliability to the final product. Temporal logic has been used in specifying and verifying different properties of reactive systems. The ability of using temporal logic and model checking to rigorously reason about the specifications properties in reactive systems is the advantage which led to use them in Human Computer Interaction (HCI) field in the computer technology, Air Traffic Control (ATC), autonomous vehicles, trains signalling systems and many other safety-critical systems.

In distributed systems, testing and simulation is the main technique used. As this covers only specific scenarios, faults can happen in the systems. In this research we use formal methods to prove correctness. Mathematical proofs can be done by an expert person in mathematics which for businesses is not always considered. On the other hand, manual proof is liable to human error. In this research we use linear temporal logic and the model checker NuSMV to carry automatic proof which eliminates errors. Temporal logic is used to specify the safety and liveness properties in network algorithms. The method used in this research explores all possible system states in a brute-force manner leading to building rigorous systems.

# 1.3 Statement of the research problem/knowledge gap

Temporal logics have been used in the specification and verification of safety and liveness properties of concurrent transactions in databases systems. This research investigates the application of linear temporal logic to distributed systems which include shared resources accessed by different transactions. It also investigates the application of linear temporal logic to other networks with message passing and no memory. It look to specify and verify the safety and correctness of concurrency with respect to collections of different transactions accessing data in different ways. It also looks to specify liveness property of memory-less flooding algorithm. The research is a combination of theoretical modelling and practical specification and verification using a temporal logic model checker NuSMV.

#### **1.4** Critical evaluation

Linear temporal logic proved to be a good technique in specifying different network algorithms properties. It showed that it can check for safety property as for the first contribution. The livenss property was specified in the second and third contribution using temporal logic. Termination of the synchronous and asynchronous flooding algorithm is specified in this research in linear temporal logic. This shows that linear temporal logic is a powerful method and can be used to specify network algorithms and its properties. In the case that a property was not met, the model checker gives a counterexample showing the states that cause the error. The states represent a trace which can be helpful in defining the error. Linear temporal logic is chosen in this research over other techniques as first-order temporal logic because there are practical and theoretical obstacles to formal verification in such logics. LTL is used also due to the nature of the problem of flooding where all messages that arrive 'at the same time' are aggregated into the same round, this has ruled out standard process calculi approaches such as CSP [1] and CCS [2], which only allow two processes at a time to synchronize sending and receiving of messages.

Even with the specifications presented in this research, and the use of one of the most powerful model checkers available, NuSMV, proofs will only be possible in practice for fairly small sizes of network. A strong mathematical background can help in solving and proving some problems where data is accessed in different ways other than what is presented in this work. Some problems faced during this research will need more time and effort to tackle in addition to higher mathematical skills.

#### 1.5 Aim

Applying linear temporal logic to specify and verify safety and livness properties in distributed systems.

#### 1.6 Objectives

The objectives of this research are as as follows:

- Investigate the usage of temporal logic and select appropriate one(s) for the research in addition to selecting a model checker and learning using it.

- Review the literature of the field.

- Find distributed systems problems that can be specified and verified using temporal logic.

- Investigate how data is accessed on routers and if can be modelled.

- Apply theoretical work to the model when matching.

- Use a model checker to verify the properties over the model.

- Provide conclusions and possible future work.

#### 1.7 Contributions

This work provides three contributions. The first contribution specifies a model of the execution of an unbounded number of concurrent transactions over time in propositional Linear Temporal Logic (LTL) in order to prove serializability. It uses recent work which places bounds on the number of transactions needed when data items are accessed in order, but do not have to be accessed contiguously, i.e., there may be 'gaps' in the data items being accessed by individual transactions. The aim of this contribution is to specify the concurrent modification of data held on routers in a network as a transactional model. The correctness of the routing protocol and ensuring safety and reliability then corresponds to the serializability of the transactions. Verification of the software of administrative routing protocols is expected to be one of the main applications of this work.

The second contribution works on memory-less flooding. We specify the basic synchronous network flooding algorithm, for any fixed size of network, in LTL. The specification can be customized to any single network topology or class of topologies. A specification for the termination problem is formulated and used to compare different topologies with regards to earlier termination. A worked example is given of one topology resulting in earlier termination than another, for which we perform a formal verification using the NuSMV model checker.

The third contribution provides a formal model of bounded asynchronous network flooding by extending the synchronous flooding model to allow a sent message, non-deterministically, to either be received instantaneously, or enter a transit phase prior to being received. A generalization of 'rounds' from synchronous flooding to the asynchronous case is used as a unit of time to provide a measure of time to termination, as the number of rounds taken, for a run of an asynchronous system. The model is encoded into temporal logic. It also compares the termination times of asynchronous and synchronous systems. Worked examples are formally verified using the NuSMV model checker. This work offers a constraint-based methodology for the verification of liveness properties of software algorithms distributed across the nodes in a network.

#### 1.8 Overview of thesis chapters

The second chapter will provide a research background. The third chapter provides literature review, motivation, and research methodology. The first, second, and third contributions are presented in Chapter 4, Chapter 5, and Chapter 6 respectively. Chapter 6.5 provides general contributions and future work. Appendices are provided at the end of the thesis.

## Chapter 2

### **Research Background**

Software complexity has increased rapidly in recent years due to the increased complexity of the systems using the software. To create software that can accomplish certain requirements requires that such software first needs to be specified in the early stages of development as per these requirements, and at a later stage needs to be verified against those requirements to ensure that they have been properly met. With the increase in demand to provide reliable software, especially in critical systems, software engineers must avoid introducing errors into their software and attempt to verify that the requirements specified by the client are met. The software in reactive systems, where the system consists of different parts that react together and with the environment, requires that certain properties must be satisfied, amongst which are safety and liveness. Network systems consist of software which is designed to achieve certain tasks over the network. Different network algorithms are used in these systems to achieve particular tasks, and ensuring that these have been specified and verified using a rigorous method avoids the introduction of errors into these systems. Formal methods, and specifically Temporal Logics, have been used by different systems to specify and verify software so as to achieve the required properties in these systems due to their power in these regards. In this thesis, temporal logic will be used to specify and verify network algorithms with respect to safety and liveness. The safety property will be examined in the first part of the thesis, namely in Chapter 4. The second part of this thesis will examine the liveness property, as discussed in Chapter 5 and Chapter 6. In Chapter 4, we will investigate the use of Linear Temporal Logic LTL to specify and verify the concurrent modification of data on the routers in a network as a transactional model in order to prove serializability. The correctness of the routing protocol, and ensuring safety and reliability, can then be said to correspond to the serializability of the associated transactions. In Chapter 5, we will specify a basic synchronous network flooding algorithm, for any fixed size of network, in Linear Temporal Logic. A specification of the termination problem

is formulated and is used to compare different topologies in terms of earlier termination. Chapter 6 provides a formal model of bounded asynchronous network flooding by extending the model of synchronous flooding to allow a sent message to either be received instantaneously, or enter a transit phase prior to being received, in a non-deterministic manner. The model is encoded into temporal logic and a proof obligation is given in terms of comparing the termination times for asynchronous and synchronous systems. This chapter will give an introduction to the different concepts and techniques that will be used in the thesis in addition to a number of examples of system failures.

Different business, and indeed the public sector, have certain, unique standards for the products they deliver which are ultimately to limit the potential for physical or economic damage. Smartphones users, for instance, would become upset at any faults or failures in their devices because of wrong or unexpected results. However, such system failures clearly do not cause physical harm to the users; rather, they have the potential to cause economic damage. This kind of failure can negatively impact the companies using these systems. For instance, in September 2016 Samsung recalled 2.5 million Note 7 phones due to a manufacturing issue with their batteries that resulted in overheating [3], in some instances resulting in severe burns being inflicted on a large number of customers. The BBC reported that this recall was believed to have cost Samsung \$5.3 bn, who ultimately recalled this smartphone to ensure the safety of its customers. Samsung offered either a replacement or a refund [3].

In stock market trading and e-business, users access data remotely via different forms of transactions in what can be described as a highly mobile environment. For instance, If the stocks trader receives inconsistent data, he/she may accordingly make a poor decision and will be negatively affected in a financial, though not physical, sense. For example, if a transaction has to read more than one data element that is being broadcast by the server to the clients, the client needs to receive consistent and correct data. One might consider a trader exchanging dollars in one country whilst another makes the same exchange in another country through the same exchange company; if the data is not fresh on both sides, they can receive different amounts of money. This example shows the seriousness of having a correctly specified and verified scheduling algorithm. In database management, the system responsible for managing data concurrency and consistency is called the scheduler [4]. Its responsibility is to schedule different concurrent transactions containing reads and writes of a set of data items. Choosing an appropriate and accurate schedule is thus essential to ongoing database integrity.

Critical computer systems are very strict and their failure is not acceptable; the negative impact that might result from a software or operational defect should be prevented at all costs. The famous chip manufacturer, Intel, lost about 475 million US dollars because of a design fault in its Pentium II processor, which was discovered in 1994 [5]. Patient information can be collected during the normal life of the patient without requiring that they be hospitalized using mobile technologies. Every year we see new health technologies intended to improve patient health and/or lifestyle. Healthcare is becoming increasingly reliant on technology to perform its various operations. When the issue is one of health, such operations become even more critical. At least six cancer patients died due to radiation overexposure caused by the software controlling a Therac-25 radiation therapy machine in 1985-1987 [6]. This bug was a direct result of concurrent programming errors. As a result of software malfunctions, passengers have died in aircraft, car, and train accidents. A fatal Airbus crash in May 2015, where an Airbus A400M crashed in Spain, was because of engine control software issues [7]. In August 2007, Skype experienced a critical disruption due to massive restarts of users [8] as a result of an error in the associated software. This problem was ultimately found to have occurred due to an unexpected number of users trying to concurrently access the systems. The software ultimately had to be updated on users' systems and then reconnected to the service, and because of restarts of those users, the system had a huge number of transactions representing connections to the service by their users [8].

With the increase of the number of the interactive systems, the potential for defects increases exponentially [5]. Specifying and verifying the correctness of the software in such environments should be undertaken to ensure proper fault avoidance. In September 2017, a check-in system failure created chaos at airports across the world [9]. The biggest airports worldwide, including London Heathrow, Charles de Gaulle in Paris, Changi in Singapore and Washington DC's Reagan Airport, amongst others, were affected because of this failure. The check-in software responsible was provided by a company called Amadeus, who specialize in travel technology, confirmed that this failure was a result of a network issue. Passengers affected by this problem had their flights either delayed or cancelled. Airport personnel were unable to provide the details required by these passengers until the system started working again; in such situations, airline companies are required to compensate travellers, which will clearly cost them large amounts of money [9]. The network software in these and other communication systems handle very large amounts of data transmission and large numbers of transactions, and so network algorithms which have not been formally specified and verified could cause unexpected issues at some unknown point in the future.

This research focusses on the specification and verification of network algorithms using temporal logic. The problems that occurred as listed above, and indeed that have occurred in many other systems, indicate the need to use robust methods of software engineering. This thesis focusses on the software part of communication, in particular on the networking algorithms used in networking systems. The following section will discuss the different areas of software engineering and the importance of the software requirements and the verification part of the software. Section 2.2 introduces the formal methods used to address these purposes and the importance of their use in software engineering. Section 2.3 introduces the definitions used in this thesis with regards to database transactions in addition to describing some of their more important properties. This section represents an important prelude to Chapter 4, which discusses data modification on network routers. Section 2.4 gives an introduction to distributed systems and distributed algorithms, which are discussed further in Chapter 5 and Chapter 6. In Section 2.5, temporal logic is introduced in addition to temporal properties and temporal operators; temporal logic is used in this thesis to specify and verify network problems. After this, Section 2.6 discusses model checking and its importance.

#### 2.1 Better Software Engineering

Software engineering starts from the early stages of the software specification, and typically ends with the maintenance of the software. This is of particular importance when considering financial constraints. Tools, theories and methods are used in software engineering to successfully create software with the required standards. The most elementary steps of software engineering consist of software specification, development, validation and evolution [10]. In a business sense, companies will attempt to produce reliable and trustworthy software for their clients while keeping minimizing the revenue required to achieve this goal.

Some of the most important steps in software engineering are the specification and verification of the software. Selecting higher standard specification and verification methods for reactive and concurrent systems implies highers level of dependability. Software specification represents that start of the software engineering process's activities. The specification starts when software engineers meet with their customers and gain a comprehensive description of the software to be developed and its constraints. Poor or incorrect specifications or misunderstandings will lead to a system that does not meet the customer's needs, which in the extreme can lead to financial loss for both the software production company and the user alike [11]. This demonstrates the serious need to form specifications that correctly describe the required system. Later in the system development process, the system will need to be checked to meet the requirements of the customer. This process is called verification. Verification is tested against the current specifications for the software; in critical systems, this is a crucial step in determining and demonstrating their correctness. Using formal methods and model checking to both specify and verify software is considered to provide reliable software that meets the associated requirements.

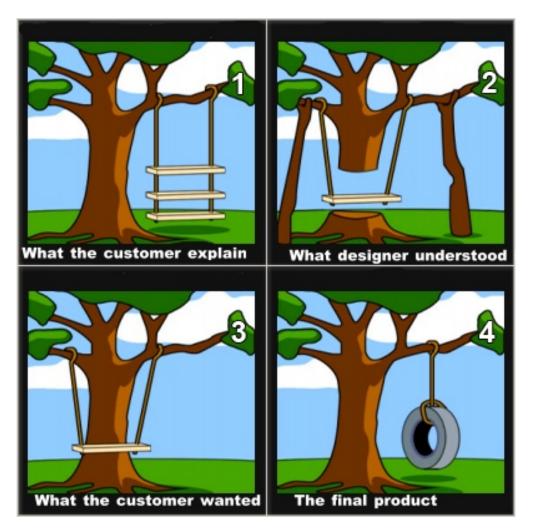

Figure 2.1 shows a famous cartoon drawing of creating a swing and reflecting the idea during software development. It shows how incorrect or misunderstood specifications can lead to unintended results.

Figure 2.1: A graphic representation of problems resulting from errors in specifications

#### 2.2 Formal Methods

State-of-the-art, formal methods, are used in system specifications, especially in critical systems where the cost of failure could notably go beyond the cost of system development. Formal methods are mathematical entities that can be used to model the system in question, and are used to model system properties in a thorough manner. Formal methods are mathematical-based techniques used for both the specification and verification of software systems. The use of formal methods in software engineering ensures a certain robustness and reliability to the final product.

The quality of the results that can be obtained by applying formal methods in verifying critical systems has led to their extensive use by software engineers. The National Aeronautics and Space Administration (NASA) reported that formal methods should be part of every software engineer's and computer scientist's education [5]. To provide an ultra-detailed verification of the system, the appropriate properties should be defined and specified in a precise manner.

In critical systems, the major approaches used to specify and verify the correctness of the concurrency control protocol are those of mathematical proofs. Mathematical proofs need a person with high levels of experience in mathematics, which makes their use difficult in the software development industry [12]. In addition to this need, mathematical proofs could themselves have errors due to human error. Using automated proofs as available model checkers to model systems formally according to their specifications and to prove their correctness saves time and avoids human error. In this manner, the desired properties can be verified using an exhaustive search of all possible states that the system can enter during execution. Model checkers can provide different and interesting features by observing the different states the system goes through. In NuSMV, in case a certain property is not met, a counterexample is given showing how the system *did not* comply with the property. This research will use formal methods, specifically temporal logic and model checkers, to specify and verify network algorithms and their properties.

#### 2.3 Basics of Database and Transactions

This section will provide an introduction to the basics of databases and database transactions; it will also introduce concurrency and the need to control concurrency. This section will be helpful as an introduction to Chapter 4 as the topics discussed here provide an excellent guide to concurrency problems when modifying data on network routers.

A database is defined as a collection of related data which is organized so that it can easily be accessed, managed, and updated [4]. This database can vary according to its type and to different organizations. A transaction is a sequence of database operations performed by the execution of a program. Database transactions entail, for instance, banking functions, reservations, and stock market functions, amongst many others. If a person is to book a flight, they will very likely access a booking page to check for the availability of flights from their departure to their destination airports. Different airlines may operate at different stages of their journey. The customer will thus be accessing a database that combines different airlines with the different airports on their journey, whilst the booking of the flight itself represents the transaction they make on the database. Once the customer books their ticket, their details will be used to reserve seats on the flight(s) on this journey. The first step, that of searching for the flight, represents a read operation from the database; the booking step represents the write operation. The plane will have certain places available for travellers. Once the traveller books a ticket, the availability of seats for other travellers will, obviously, be reduced. A booking system should run without faults and ensure that certain properties are met, for instance, that no two travellers can book the same seat; if all seats are reserved, the system should not allow any further bookings to be made on that flight. Other properties must hold in such systems where different transactions by different users could potentially attempt to access the database simultaneously. We can imagine how such issues have grown exponentially with today's mobile technologies. A person can nowadays book a ticket for a trip using his/her smart-phone in a very straightforward manner.

Concurrency is one of the topics that has been considered for decades and indeed has grown with new mobile technologies. The scheduler is the database system component that handles concurrency control. The scheduler is an essential component of transaction processing systems that deals with users running concurrent transactions. The scheduler produces schedules which represent the interleaved execution of these transactions. The schedule is also sometimes called a history. A transaction can perform the following database operations:

- Access operation (read operation): fetches the data value of a data item x. This is denoted by Read(x).

- Update operation (write operation): updates the value of a data item x. This is denoted by Write(x).

The database is a representation of part of the real world [12, 13, 14]. This means that its state is governed and controlled. An example is that a person's weight cannot be negative. Another example is that only a definite number of passengers can be seated in an aircraft according to its number of seats. Such restrictions are referred to as integrity constraints, which create a framework to ensure that data consistency is valid when any user performs an operation that will result in a change to the database. A database is said to be in its consistent state at a certain time if all data element values are valid according to the integrity constraints. If a transaction is to commit, it should maintain the database is in its consistent state. Four properties of transactions (known as ACID properties) should be valid when transactions are executing in the database to preserve its consistency. Furthermore, in an environment where multiple transactions are executing, the database management system (DBMS) must schedule the concurrent execution of the transactions steps. The schedule of these transactions operations must have the property of being serializable [4]. To understand more of the required properties, we should review these properties and what they mean. The first four properties are the ACID properties:

Atomicity: All operations of a transaction are required to be complete or else the transaction is aborted. The transaction is treated as a single unit.

*Consistency:* A transaction is aborted if any part of it violates an integrity constraint. It should keep the database in a consistent state to commit.

*Isolation:* In a concurrency environment, simultaneously running transaction behaviours do not affect each other. Access to shared resources must be serialized by the transactions.

*Durability:* Once a transaction is committed, the changes its makes cannot be undone. Effects should also not be lost, even in the instance of a system failure.

*Serializability:* Results of schedules in an environment where transactions are executed concurrently should maintain a consistent system.

After understanding the different properties, we should consider transaction concurrency, and why it is important to control it, further. This is considered in the following section.

#### 2.3.1 Importance of Concurrency Control

In an environment with multiple transactions accessing shared data and that are executed in parallel, concurrency control is needed to avoid any undesirable situation that can violate the consistency of the database. In other words, the DBMS needs to preserve some or all ACID properties in such environments [12, 15]. Without concurrency control, transactions running simultaneously over a shared database can create data integrity and consistency issues. The following example explains the first problem:

Suppose that we have two transactions (Transaction1, Transaction2) accessing a data item x in a database. The item x has an initial value of 5 (x = 5).

Transaction1: Read(x); x = x - 3; Write(x);

Transaction2: Read(x); x = x + 7; Write(x);

The concurrent execution of the two transactions is represented in Table 2.1. In Table 2.1, the final value of x is 12. If the transaction were executed in a se-

| Step | Transaction 1 | Transaction 2 |                                       |

|------|---------------|---------------|---------------------------------------|

| 1    | Read(x)       |               |                                       |

| 2    | x = x - 3     |               |                                       |

| 3    |               | Read(x)       |                                       |

| 4    |               | x = x + 7     |                                       |

| 5    | Write(x)      |               |                                       |

| 6    |               | Write(x)      | $\leftarrow$ older value is cancelled |

Table 2.1: Two transactions executing simultaneously.