### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2019

# GaN-Based High Efficiency Transmitter for Multiple-Receiver Wireless Power Transfer

Ling Jiang *University of Tennessee*, ljiang7@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Jiang, Ling, "GaN-Based High Efficiency Transmitter for Multiple-Receiver Wireless Power Transfer. " PhD diss., University of Tennessee, 2019.

https://trace.tennessee.edu/utk\_graddiss/5466

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Ling Jiang entitled "GaN-Based High Efficiency Transmitter for Multiple-Receiver Wireless Power Transfer." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Daniel Costinett, Major Professor

We have read this dissertation and recommend its acceptance:

Fred Wang, Leon M. Tolbert, Reid Kress

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# **GaN-Based High Efficiency Transmitter for Multiple-Receiver Wireless Power Transfer**

A Dissertation Presented for the Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Ling Jiang May 2019

#### **ACKNOWLEDGEMENT**

I would like to express my sincerest gratitude to my advisor, Dr. Daniel Costinett, for his support, guidance, and encouragement throughout my Ph.D. studies. Thank him for guiding me into this exciting research area, providing me precious suggestions and inspiring new ideas on my research. His passion for the research always motivates me.

I would like to extend my gratitude to Dr. Leon. M. Tolbert and Fred Wang for their instructions. They are generous to give me support, suggestions and encouragement. They broaden my knowledge of power electronics.

I would like to thank Dr. Aly Fathy for his precious suggestions and comments during the project meeting.

I would like to appreciate Dr. Reid Kress for serving on my dissertation committee and giving me good suggestions.

I am also profoundly grateful to the staff members of the University of Tennessee. They are Mr. Robert B. Martin, Ms. Wendy Smith, Ms. Dana Bryson, and Ms. Judy Evan for providing a wonderful and safe place for my research.

Special thanks also go to all the colleagues in the power electronics lab and in EECS department in UTK. Every discussion with them has broadened my knowledge. I really enjoy working with them and cherish being friends with them. Particularly, I want to thank the colleagues whom I worked in projects: Mr. Brad Trento, Ms. Lu Wang, Mr. Chongwen Zhao, Mr. Jie Li, Mr. Spencer Cochran, Mr. Farshid Tamjid, Mr. Farhan Quiyum, Mr. Peter Pham, and Ms. Alex Bolinsky. It is my great pleasure to work with them. I would like to thank Dr. Bo Liu for his kindness and his broad knowledge in this field. His suggestions help me solve many technical problems.

I would like to express my heartiest thanks and love to my parents for their unconditional love and support in my life. I want to give my deepest gratitude to Mr. Zhichao Liu for his considerate care all the time. His optimistic and cheerful attitude encouraged me to make progress in the research and to explore a wonderful life.

This dissertation made use of Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and the Department Of Energy under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program.

#### **ABSTRACT**

Wireless power transfer (WPT) has attracted great attention from industry and academia due to high charging flexibility. However, the efficiency of WPT is lower and the cost is higher than the wired power transfer approaches. Efforts including converter optimization, power delivery architecture improvement, and coils have been made to increase system efficiency.

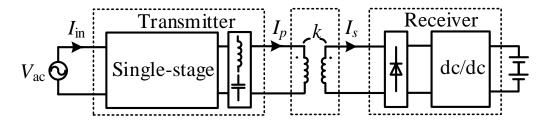

In this thesis, new power delivery architectures in the WPT of consumer electronics have been proposed to improve the overall system efficiency and increase the power density.

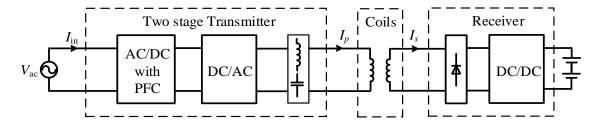

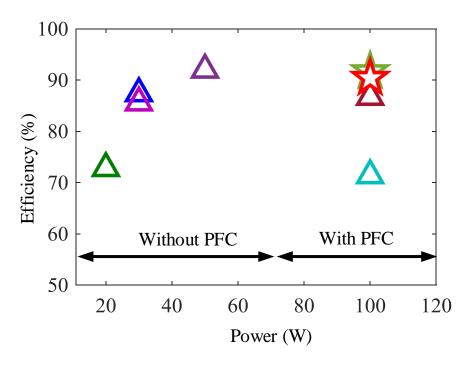

First, a two-stage transmitter architecture is designed for a 100 W WPT system. After comparing with other topologies, the front-end ac-dc power factor correction (PFC) rectifier employs a totem-pole rectifier. A full bridge 6.78 MHz resonant inverter is designed for the subsequent stage. An impedance matching network provides constant transmitter coil current. The experimental results verify the high efficiency, high PF, and low total harmonic distortion (THD).

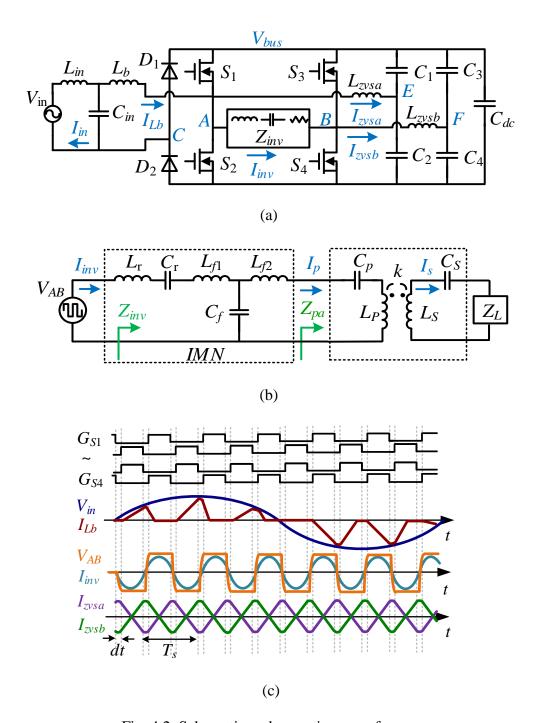

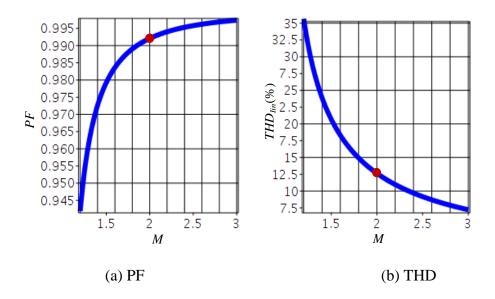

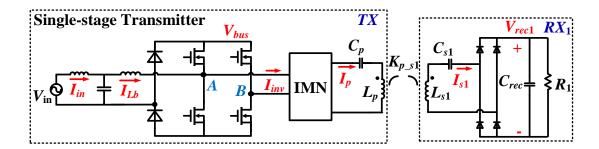

Then, a single-stage transmitter is derived based on the verified two-stage structure. By integration of the PFC rectifier and full bridge inverter, two GaN FETs are saved and high efficiency is maintained. The integrated DCM operated PFC rectifier provides high PF and low THD. By adopting a control scheme, the transmitter coil current and power are regulated. A simple auxiliary circuit is employed to improve the light load efficiency. The experimental results verify the achievement of high efficiency.

A closed-loop control scheme is implemented in the single-stage transmitter to supply multiple receivers simultaneously. With a controlled constant transmitter current, the system provides a smooth transition during dynamically load change. ZVS detection circuit is proposed to protect the transmitter from continuous hard switching operation. The control scheme is verified in the experiments.

The multiple-reciever WPT system with the single-stage transmitter is investigated. The system operating range is discussed. The method of tracking optimum system efficiency is studied. The system control scheme and control procedure, targeting at providing a wide system operating range, robust operation and capability of tracking the optimized system efficiency, are proposed. Experiment results demonstrate the WPT system operation.

# TABLE OF CONTENTS

| 1 | Introduc  | tion                                                             | 1  |

|---|-----------|------------------------------------------------------------------|----|

|   | 1.1 Win   | reless power transfer                                            | 1  |

|   | 1.1.1     | The background of wireless power transfer                        | 2  |

|   | 1.1.2     | Magnetic inductive coupling                                      | 4  |

|   | 1.1.3     | Magnetic resonant coupling                                       | 1  |

|   | 1.1.4     | The standards for WPT                                            | 2  |

|   | 1.2 Mo    | tivation and strategy                                            | 3  |

|   | 1.2.1     | The innovation of transmitter architecture                       |    |

|   | 1.2.2     | A single transmitter for multiple receivers charging application | 5  |

|   | 1.3 Dis   | sertation outline                                                | 7  |

| 2 | Literatur | e review                                                         | 8  |

|   | 2.1 WP    | T architecture                                                   |    |

|   | 2.1.1     | The state-of-art industrial WPT products                         | 8  |

|   | 2.1.2     | The state-of-art academic WPT architectures                      |    |

|   | 2.2 The   | converter topologies of the transmitter                          | 21 |

|   | 2.2.1     | Ac-dc rectifier                                                  | 21 |

|   | 2.2.2     | High frequency resonant inverter                                 | 27 |

|   | 2.2.3     | Single-stage ac-ac converter for induction heating and lighting  |    |

|   | 2.3 Cor   | npensation network                                               |    |

|   | 2.4 Sof   | t switching techniques of PWM converters                         | 37 |

|   | 2.4.1     | The principle of soft switching                                  | 38 |

|   | 2.4.2     | Auxiliary circuit to assist with ZVS                             |    |

|   | 2.5 The   | control strategy of the wireless power transfer system           |    |

|   | 2.5.1     | The control scheme for single receiver WPT system                |    |

|   | 2.5.2     | The control scheme for the multiple-receiver WPT system          | 43 |

|   | 2.6 ZV    | S detection                                                      | 44 |

|   | 2.7 Sun   | nmary                                                            | 45 |

| 3 | Two-stag  | ge transmitter design                                            | 51 |

|   | 3.1 Top   | ology selection                                                  | 51 |

|   | 3.1.1     | Bridgeless PFC rectifier                                         | 51 |

|   | 3.1.2     | The selection of high frequency inverter                         | 58 |

|   | 3.2 The   | design of Totem-pole rectifier                                   | 59 |

|   | 3.2.1     | The operation of Totem-pole rectifier with CRM                   | 60 |

|   | 3.2.2     | ZVS condition for CRM totem-pole rectifier                       | 65 |

|   | 3.2.3     | Control implementation and THD reduction                         | 68 |

|   | 3.2.4     | The current spike issue at the input voltage zero cross          | 72 |

|   | 3.3 Full  | bridge resonant inverter                                         |    |

|   | 3.3.1     | Inverter operation                                               | 74 |

|   | 3.3.2     | ZVS tank design                                                  | 76 |

|   | 3.3.3     | Device selection                                                 | 77 |

|   | 3.4 Imp   | edance matching network for constant current output behavior     | 79 |

|   | 3.4.1     | Basic compensation network                                       |    |

|   | 3.4.2     | Multiple receivers charging application                          | 88 |

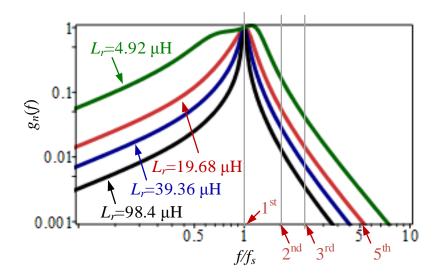

|   | 3.4.3    | IMN design for the constant output current behavior                   | 90  |

|---|----------|-----------------------------------------------------------------------|-----|

|   | 3.5 Ex   | perimental verification                                               |     |

|   | 3.6 Sui  | nmary                                                                 | 99  |

| 4 | Single-s | tage transmitter design                                               | 100 |

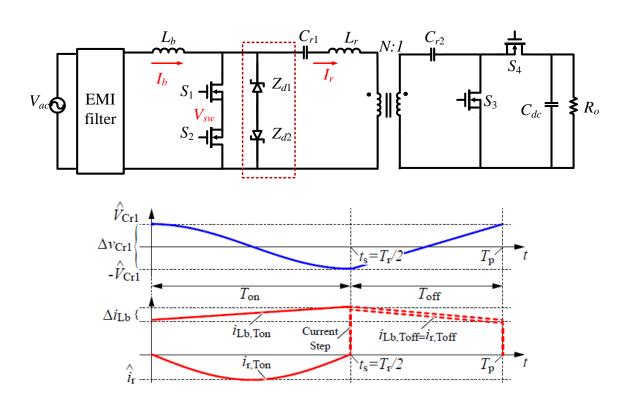

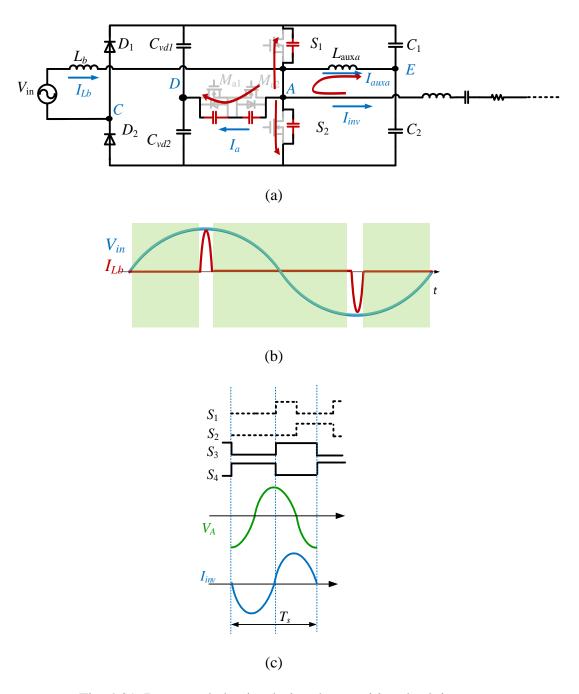

|   | 4.1 Sin  | gle-stage transmitter                                                 | 100 |

|   | 4.1.1    | Operation principle                                                   | 101 |

|   | 4.1.2    | Constant output current achievement                                   | 107 |

|   | 4.2 The  | e improved single-stage transmitter                                   | 110 |

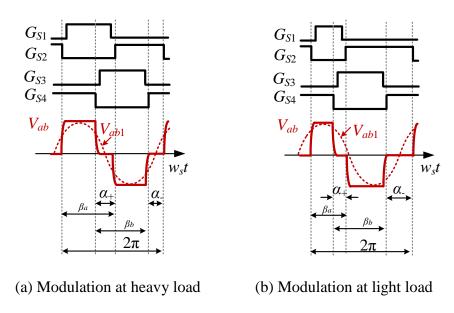

|   | 4.2.1    | Operation principle                                                   | 110 |

|   | 4.2.2    | Design considerations for $C_{vd}$ and $C_{dc}$                       | 111 |

|   | 4.2.3    | The selection of $M_{a1}$ and $M_{a2}$                                | 116 |

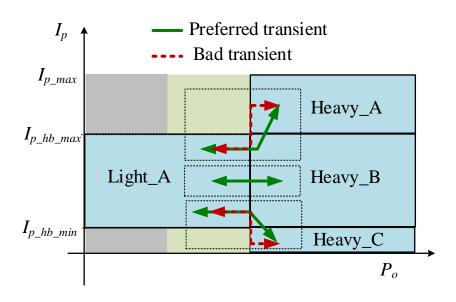

|   | 4.3 The  | e transitions between the two operation modes                         | 118 |

|   | 4.3.1    | The transition from heavy load mode to light load mode                | 119 |

|   | 4.3.2    | The transition from light load mode to heavy load mode                |     |

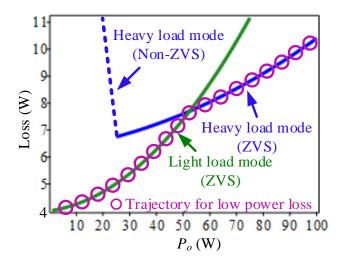

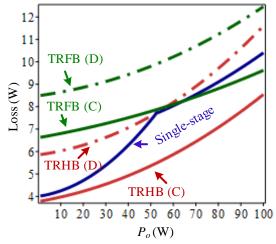

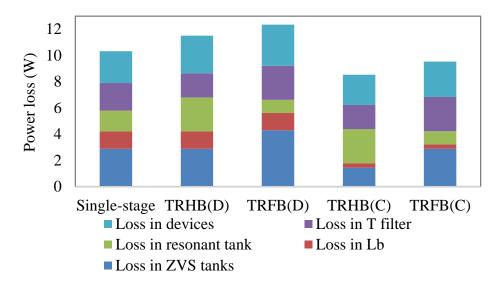

|   | 4.4 The  | e loss model and efficiency estimation                                | 127 |

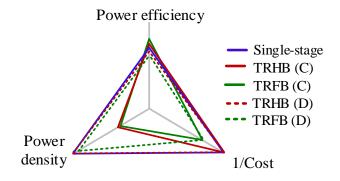

|   | 4.5 Top  | pologies comparison                                                   | 130 |

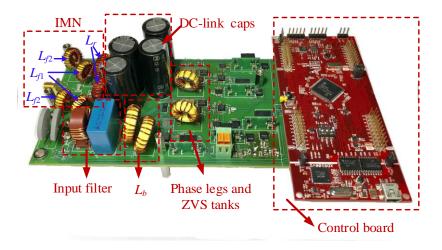

|   | 4.6 Ex   | perimental verification                                               | 136 |

|   | 4.7 Sui  | nmary                                                                 | 148 |

| 5 | Dynami   | c operation of single-stage transmitter                               | 150 |

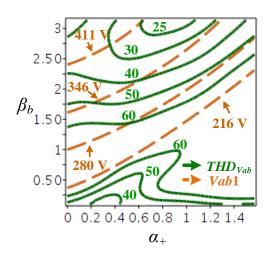

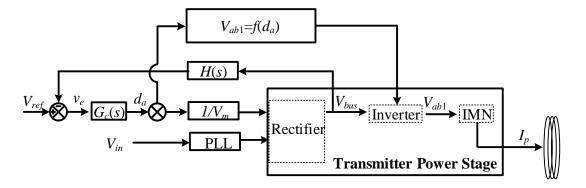

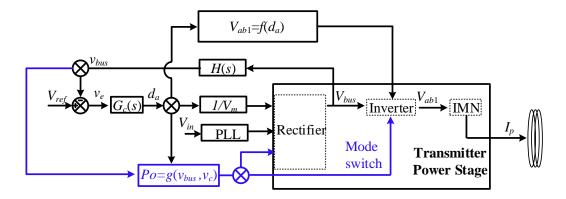

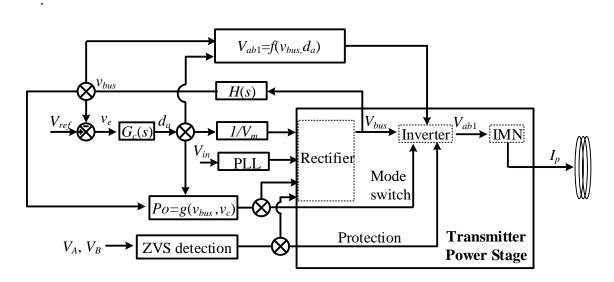

|   | 5.1 Co   | nstant output current regulation in the heavy load mode               | 150 |

|   | 5.1.1    | Constant $V_{bus}$ regulation                                         | 151 |

|   | 5.1.2    | Constant $V_{ab1}$ regulation                                         | 152 |

|   | 5.1.3    | The achievement of Constant $I_p$                                     | 154 |

|   | 5.2 Sin  | gle-stage transmitter dynamic operation over full power range         | 154 |

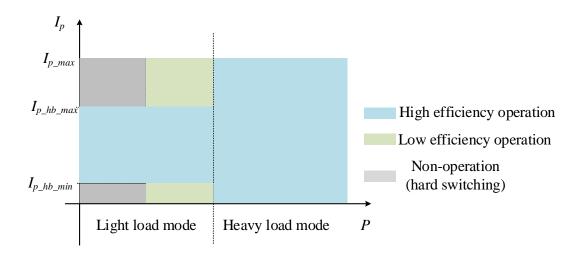

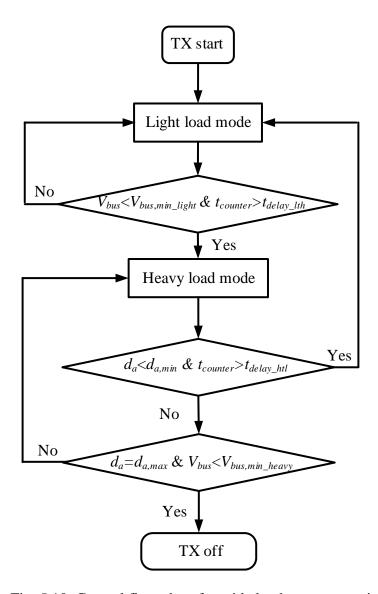

|   | 5.2.1    | Dynamic operation in light load mode                                  | 154 |

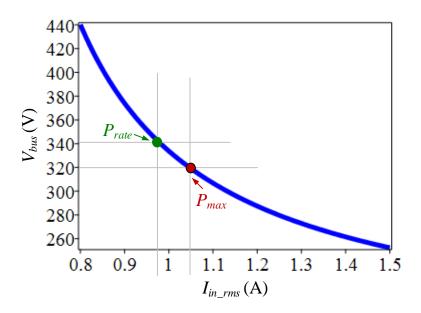

|   | 5.2.2    | Operation boundaries                                                  | 156 |

|   | 5.2.3    | Wide power range operation                                            | 160 |

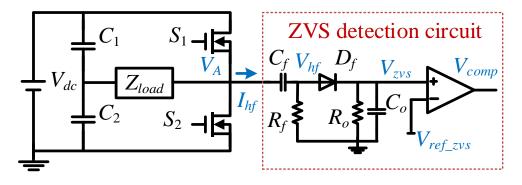

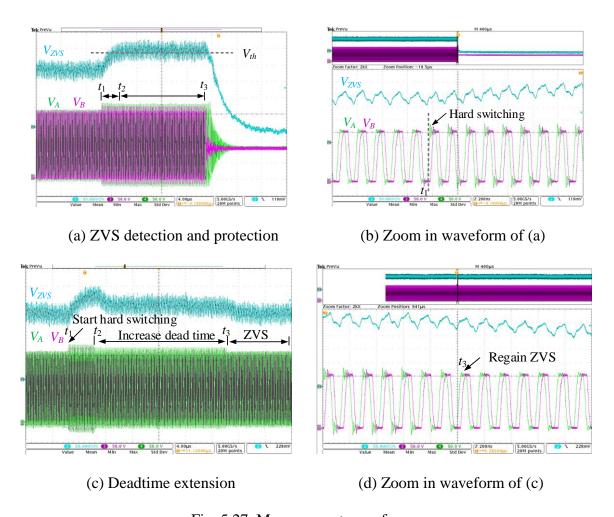

|   | 5.3 ZV   | S detection                                                           | 165 |

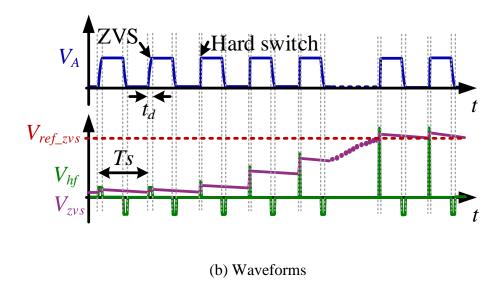

|   | 5.3.1    | Operation principle                                                   | 165 |

|   | 5.3.2    | Design considerations                                                 | 167 |

|   | 5.3.3    | Discussion of several applications                                    | 169 |

|   | 5.4 Exp  | perimental verification                                               | 171 |

|   | 5.4.1    | Single transmitter with multiple receivers in heavy load mode         | 171 |

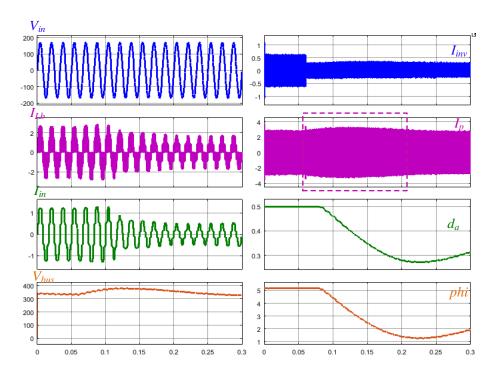

|   | 5.4.2    | Dynamic operation over a wide power range                             | 182 |

|   | 5.4.3    | ZVS detection                                                         | 185 |

|   | 5.5 Su   | nmary                                                                 | 188 |

| 6 | WPT Sy   | stem Operation with single-stage transmitter                          | 189 |

|   | 6.1 WI   | PT system configuration                                               | 189 |

|   | 6.1.1    | Transmitter configuration                                             | 190 |

|   | 6.1.2    | Receiver configuration                                                | 195 |

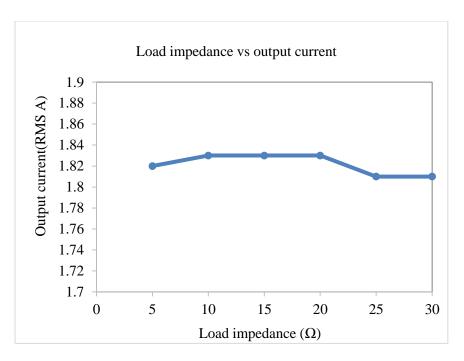

|   |          | stem operating range                                                  |     |

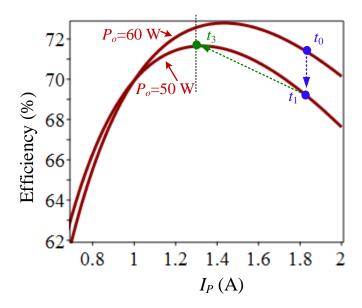

|   | 6.3 The  | e impact of variable $I_p$ on system efficiency                       | 200 |

|   | 6.3.1    | The impact of variable $I_p$ on the transmitter efficiency            | 202 |

|   | 6.3.2    | The impact of variable $I_p$ on the loss of coils and diode rectifier | 204 |

|   | 6.3.3    | System efficiency optimization with variable $I_p$                    |     |

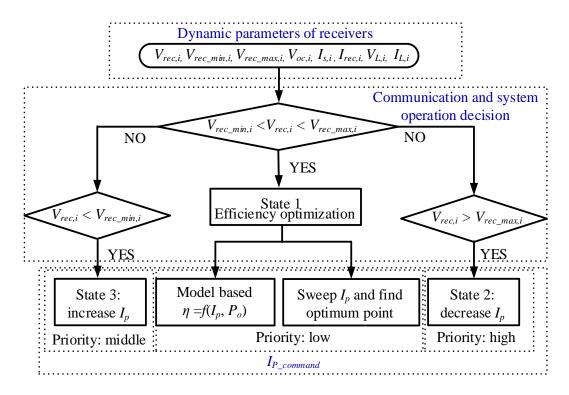

|   | 6.4 The  | e control scheme and procedure of the WPT system                      | 209 |

| 6.4.1      | System control scheme                                        | 209 |

|------------|--------------------------------------------------------------|-----|

| 6.4.2      | System control procedure                                     | 210 |

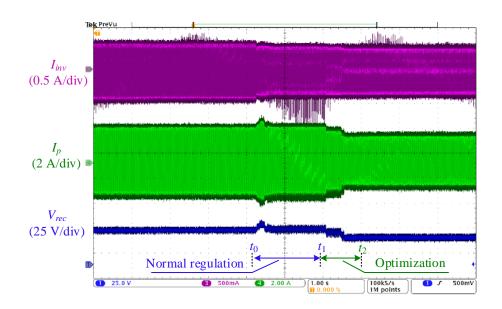

| 6.5 Ex     | perimental demonstration                                     | 213 |

| 6.5.1      | Transmitter responses to the system State 2                  | 214 |

| 6.5.2      | Transmitter responses to the system State 3                  | 216 |

| 6.5.3      | System efficiency optimization in system State 1             | 216 |

| 6.6 Su     | mmary                                                        | 220 |

| 7 Conclus  | sion and future work                                         | 221 |

| 7.1 Co     | onclusion                                                    | 221 |

| 7.1.1      | Summary of the work                                          | 221 |

| 7.1.2      | Contributions                                                | 223 |

| 7.2 Fu     | ture work                                                    | 225 |

| 7.2.1      | WPT system optimization                                      | 225 |

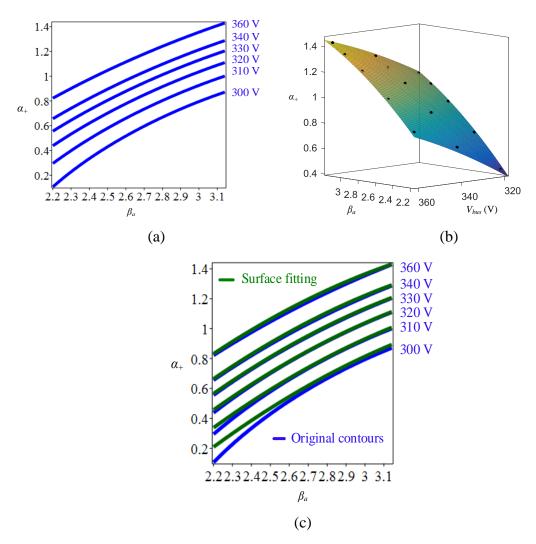

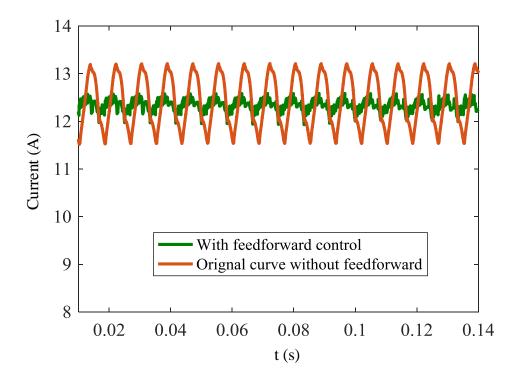

| 7.2.2      | Implementation of feedforward control                        | 225 |

| 7.2.3      | Improvement of load change transition by feedforward control | 229 |

| 7.2.4      | Feasibility of reducing DC link capacitor                    | 229 |

| 7.3 Pu     | blication list                                               | 234 |

| References |                                                              | 236 |

| Vita       |                                                              | 251 |

# LIST OF TABLES

| TABLE 1.1 COMPARISON OF WPT STANDARDS                                | 4     |

|----------------------------------------------------------------------|-------|

| TABLE 2.1 COMPARISON OF WPT ARCHITECTURE ON THE CONSUMER ELECTRONICS | 16    |

| TABLE 2.2 COMPARISON OF WPT FOR EV APPLICATION                       | 20    |

| TABLE 2.3 COMPARISON OF ADAPTER                                      | 24    |

| TABLE 2.4 COMPARISON OF HIGH FREQUENCY RESONANT INVERTER             | 31    |

| TABLE 2.5 NUMBER OF POWER SEMICONDUCTORS BREAK DOWN                  | 49    |

| TABLE 3.1 COMPARISON OF BRIDGELESS PFC RECTIFIER                     | 52    |

| TABLE 3.2 DESIGN SPECIFICATION OF CUK RECTIFIER                      | 54    |

| TABLE 3.3 DESIGN SPECIFICATION OF TOTEM-POLE RECTIFIER               | 56    |

| TABLE 3.4 THE COMPARISON BETWEEN THESE TWO TOPOLOGIES                | 56    |

| TABLE 3.5 COMPARISON OF CLASS E AND CLASS D AMPLIFIER                | 59    |

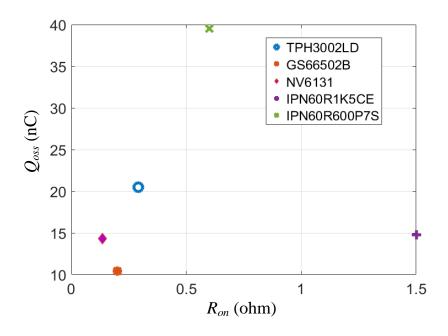

| Table 3.6 Devices Comparison at $V_{DS}$ =200 V                      |       |

| TABLE 3.7 PARAMETER OF PROTOTYPE                                     | 95    |

| TABLE 4.1 TOPOLOGY HARDWARE COMPARISON                               | . 134 |

| TABLE 4.2 DESIGN PARAMETERS                                          | . 137 |

| TABLE 4.3 MEASURED INPUT CURRENT PERFORMANCE                         | . 146 |

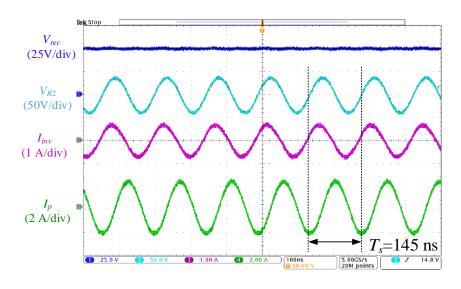

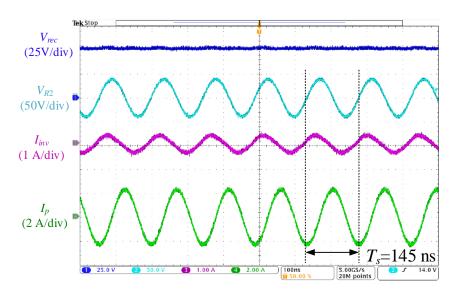

| TABLE 5.1 LOAD CONDITION AND TEST RESULTS FOR TWO-RECEIVER SYSTEM    | . 174 |

| TABLE 5.2 MEASUREMENT RESULTS OF CLOSED-LOOP CONTROL                 | . 176 |

| TABLE 5.3 LOAD SWITCHING TEST                                        | . 183 |

| TABLE 5.4 DESIGN PARAMETER OF ZVS DETECTION                          |       |

# LIST OF FIGURES

| Fig. 1.1. The application of WPT [1]                                                     | 2    |

|------------------------------------------------------------------------------------------|------|

| Fig. 1.2. Categories of WPT technologies.                                                | 3    |

| Fig. 1.3. Tightly coupled coils [5]                                                      |      |

| Fig. 1.4. (a) Approach 1: guide the positioning charging. (b) Approach 2: free positio   | ning |

| based on a mechanically moveable primary coil. (c) Approach 3: free positioning base     |      |

| the selective excitation of a coil array [8].                                            |      |

| Fig. 1.5. Loosely coupled coils [5].                                                     |      |

| Fig. 1.6. WPT standards landscape.                                                       |      |

| Fig. 1.7. WPT system with the multi-stage transmitter.                                   |      |

| Fig. 1.8. Multiple devices charging application [21].                                    |      |

| Fig. 1.9. The sketch of single transmitter charging multiple devices.                    |      |

| Fig. 2.1. System configuration for the commercial consumer electronics application [     |      |

| 8 9                                                                                      |      |

| Fig. 2.2. EPC9512 amplifier board and schematic configured as 33 W Class                 |      |

| amplifier [29].                                                                          |      |

| Fig. 2.3. EPC9513 rectifier board photo configured as 5 W [32]                           |      |

| Fig. 2.4. TI Transmitter board bq500211AEVM-210 with class D amplifier [13]              |      |

| Fig. 2.5. The configuration of class E with secondary side diode rectifier for V         |      |

| application [41].                                                                        |      |

| Fig. 2.6. The configuration of Class $E^2$ dc-dc converter for WPT application [45]      |      |

| Fig. 2.7. The wireless power transfer system with class D amplifier and diode br         |      |

| rectifier [47].                                                                          |      |

| Fig. 2.8. A wireless power transfer system with full bridge inverter and diode rectifier |      |

|                                                                                          |      |

| Fig. 2.9. A single-stage ac-ac transmitter is proposed for WPT system application [40]   |      |

| Fig. 2.10. WPT system in EV application with ac power supply [52].                       |      |

| Fig. 2.11. Schematic of EV wireless charging system [56]                                 |      |

| Fig. 2.12. Matrix transmitter proposed in [64]                                           |      |

| Fig. 2.13. Z source converter based two-stage transmitter [65]                           |      |

| Fig. 2.14. The combination of diode rectifier and flyback for ac-dc converter            |      |

| Fig. 2.15. PFC boost rectifier.                                                          |      |

| Fig. 2.16. Basic bridgeless boost rectifier.                                             |      |

| Fig. 2.17. Improved bridgeless boost rectifier (Totem-pole bridgeless rectifier)         |      |

| Fig. 2.18. Class E power amplifier.                                                      |      |

| Fig. 2.19. Class E operation under various load conditions [31]                          |      |

| Fig. 2.20. Class D transmitter(half-bridge configuration).                               |      |

| Fig. 2.21. Impedance matching network in the WPT system.                                 |      |

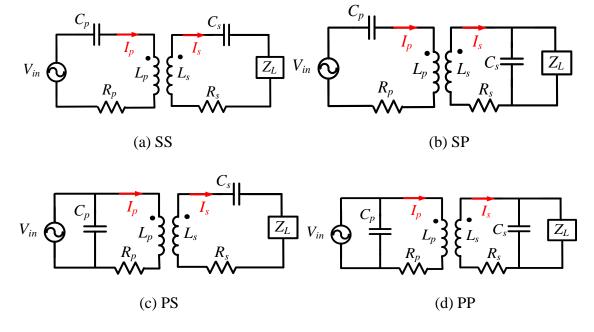

| Fig. 2.22. Basic compensation networks.                                                  |      |

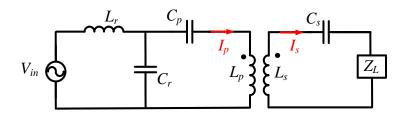

| Fig. 2.23. LCC/S network.                                                                |      |

| Fig. 2.24. LCL/S network.                                                                |      |

| Fig. 2.25. ZVS converter.                                                                |      |

| Fig. 2.26. The principle of an auxiliary circuit for soft switching.                     |      |

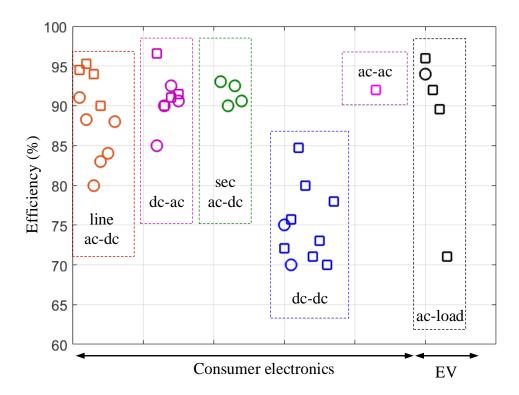

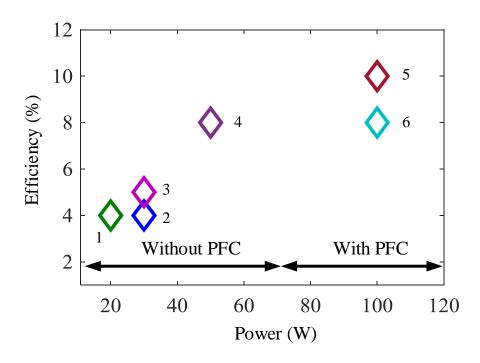

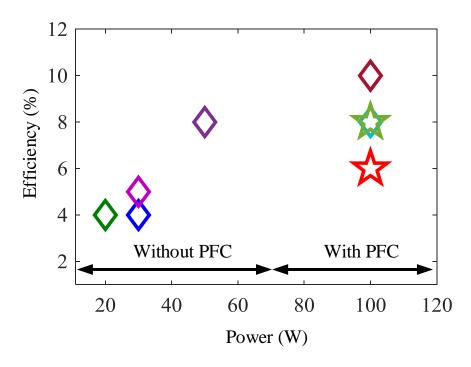

| Fig. 2.27. The reported efficiency from the literature review                            |      |

| Fig. 2.28. Traditional WPT system in the consumer electronics application              | . 49 |

|----------------------------------------------------------------------------------------|------|

| Fig. 2.29. The state-of-art transmitter in the consumer electronics application        | . 50 |

| Fig. 3.1. WPT system with the two-stage transmitter.                                   | . 52 |

| Fig. 3.2. Bridgeless Cuk PFC rectifier [72].                                           |      |

| Fig. 3.3. The main waveforms of bridgeless Cuk PFC rectifier in simulation             | . 56 |

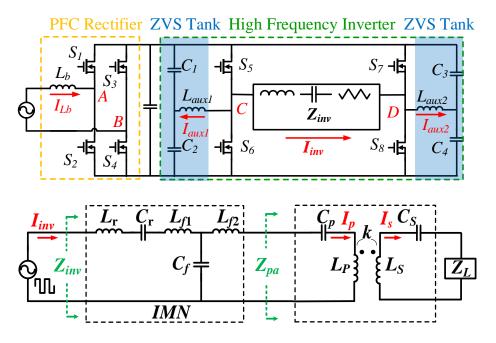

| Fig. 3.4. Two-stage converter for wireless power transfer transmitter                  |      |

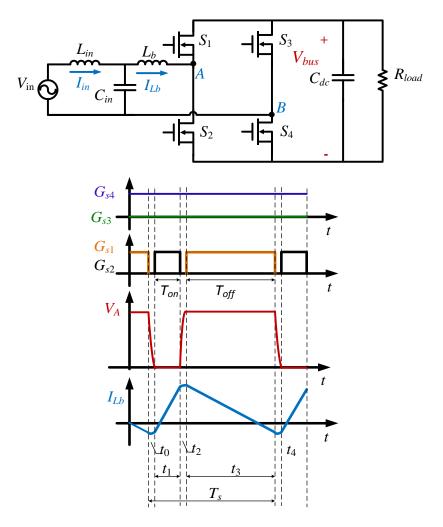

| Fig. 3.5. Totem-pole rectifier and the waveform.                                       | . 63 |

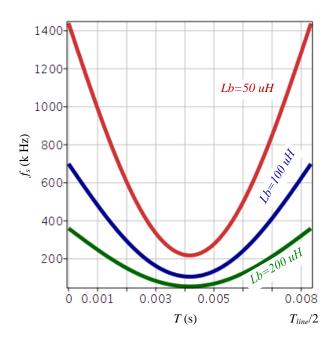

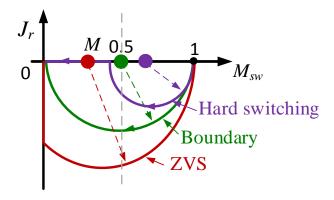

| Fig. 3.6. $f_s$ change along with line period in CRM.                                  | . 64 |

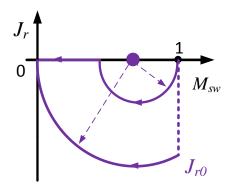

| Fig. 3.7. The trajectory of resonance for the CRM with different $M_n$ .               | . 66 |

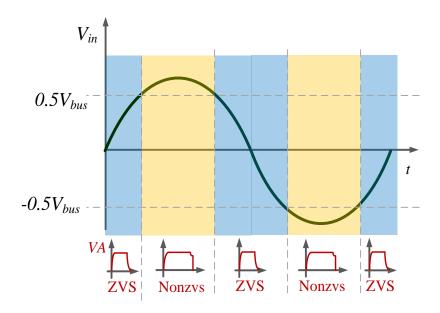

| Fig. 3.8. Natural ZVS region and non-ZVS region in a line cycle with CRM               |      |

| Fig. 3.9. Initial current $J_{r0}$ for ZVS when $V_{in}$ is larger than $0.5Vb_{us}$   | . 67 |

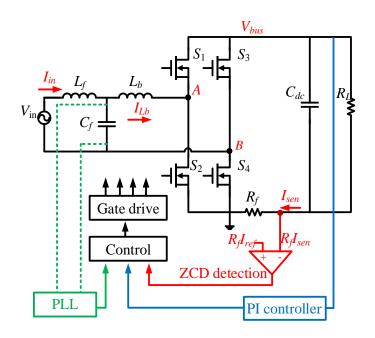

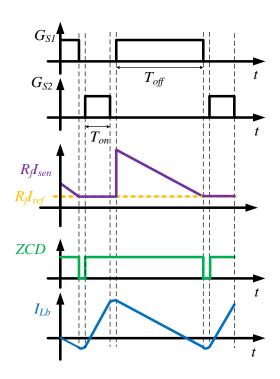

| Fig. 3.10. Totem-pole rectifier in CRM.                                                | . 70 |

| Fig. 3.11. Input current and inductor current with negative current extension for ZVS. | . 71 |

| Fig. 3.12 $\Delta T_{on}$ compensation for THD improvement.                            | . 71 |

| Fig. 3.13. Current spike issue near input voltage zero cross point.                    | . 73 |

| Fig. 3.14. Totem-pole rectifier in CRM.                                                |      |

| Fig. 3.15. Suppression of the current spike                                            |      |

| Fig. 3.16. Full bridge operation waveforms.                                            |      |

| Fig. 3.17. ZVS tank and waveforms.                                                     |      |

| Fig. 3.18. $C_{oss}$ curves vs $V_{ds}$ .                                              | 78   |

| Fig. 3.19. FOM of five candidates.                                                     |      |

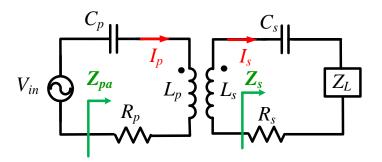

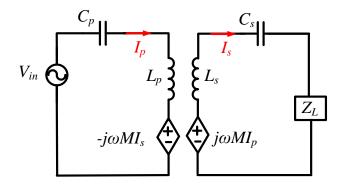

| Fig. 3.20. SS compensation network.                                                    |      |

| Fig. 3.21. M model of SS circuit.                                                      | . 81 |

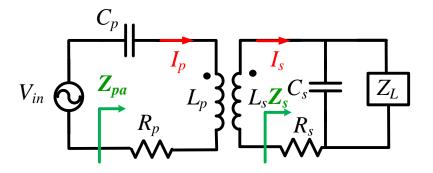

| Fig. 3.22. SP compensation network.                                                    |      |

| Fig. 3.23. M model of SP circuit.                                                      | . 84 |

| Fig. 3.24. The equivalent circuit of the secondary side.                               | . 84 |

| Fig. 3.25. PS compensation network.                                                    |      |

| Fig. 3.26. PP compensation network.                                                    | . 87 |

| Fig. 3.27. The equivalent circuit of a single transmitter with multiple receivers      |      |

| Fig. 3.28. The compensation network.                                                   |      |

| Fig. 3.29. Output network of the inverter.                                             |      |

| Fig. 3.30. Transfer gain with different $L_r$                                          |      |

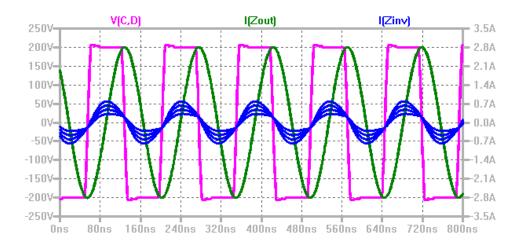

| Fig. 3.31. Simulation verification for the inherent current source behavior            | 93   |

| Fig. 3.32. A prototype of the two-stage transmitter.                                   | . 95 |

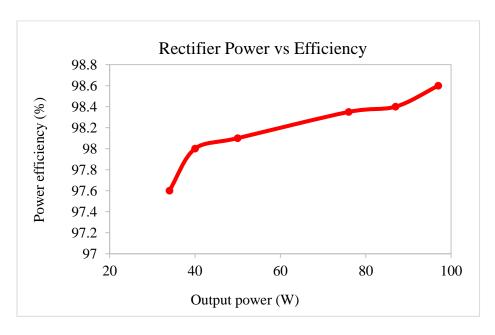

| Fig. 3.33. Experimental rectifier power efficiency                                     |      |

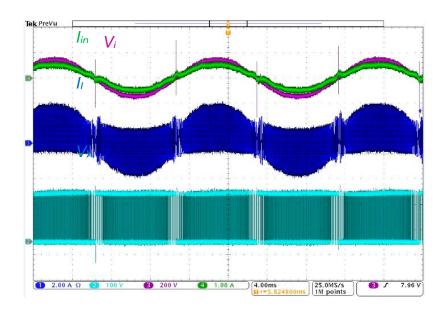

| Fig. 3.34. Experimental rectifier waveforms.                                           |      |

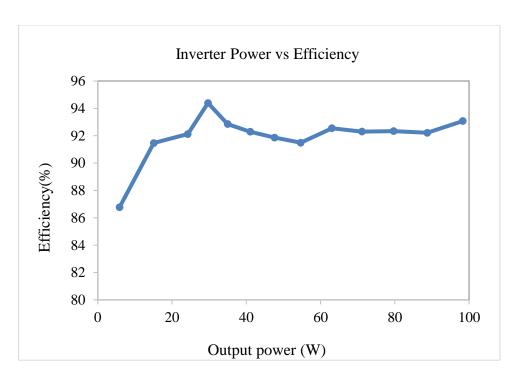

| Fig. 3.35. Experimental inverter power efficiency.                                     |      |

| Fig. 3.36. Experimental inverter waveforms for constant current behavior verification. |      |

| Fig. 3.37. Experimental results for constant current behavior verification             |      |

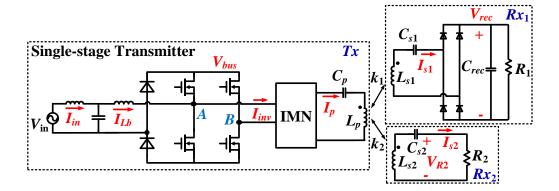

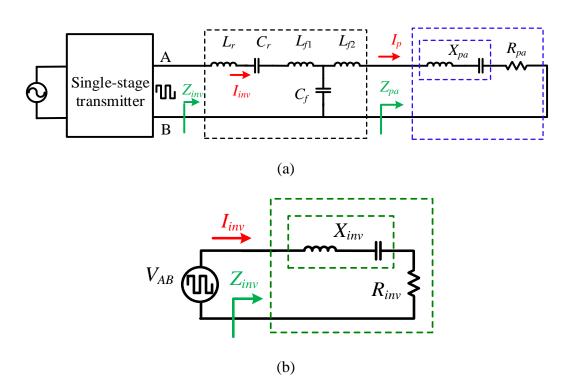

| Fig. 4.1. The single-stage transmitter in the wireless power transfer system           |      |

| Fig. 4.2. Schematic and operation waveforms.                                           |      |

| Fig. 4.3. PF and THD of input current as a function of M                               | 105  |

| Fig. 4.4. The modulation of the inverter.                                              |      |

| Fig. 4.5. THD contours.                                                                |      |

| Fig. 4.6. Control trajectory.                                                          |      |

| Fig. 4.7. ZVS tank current.                                                            |      |

| Fig. 4.8. Schematic and operation waveforms at light load mode                       |       |

|--------------------------------------------------------------------------------------|-------|

| Fig. 4.9. Two-operation modes of the single-stage transmitter.                       | . 113 |

| Fig. 4.10. Schematic and waveform of VDR.                                            | . 113 |

| Fig. 4.11. Ripple bus voltage vs $C_{dc}/C_{vd}$ .                                   | . 117 |

| Fig. 4.12. Average bus voltage vs $C_{dc}/C_{vd}$ .                                  |       |

| Fig. 4.13. The practical design of the auxiliary circuit.                            | . 117 |

| Fig. 4.14. Simplified circuit.                                                       |       |

| Fig. 4.15. Initial waveform of transition from heavy load mode to light load mode    | . 120 |

| Fig. 4.16. Main waveforms at heavy load mode.                                        | . 121 |

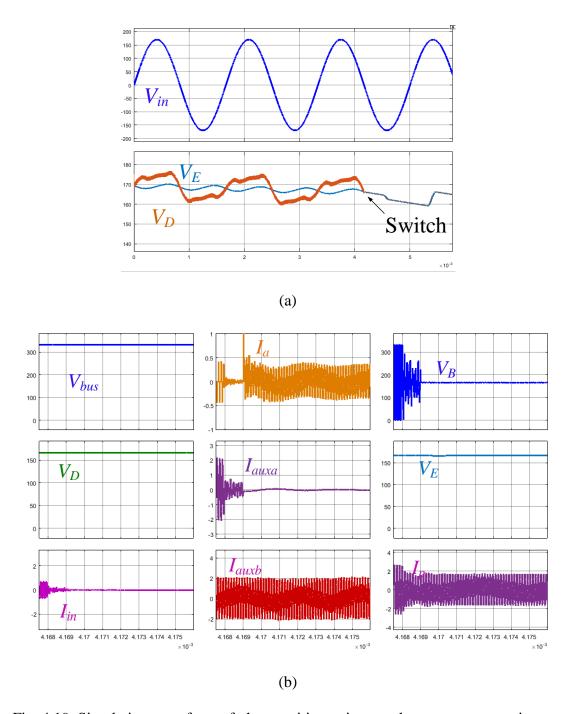

| Fig. 4.17. Simulation waveform of $V_E$ and $V_D$ at heavy load mode                 | . 122 |

| Fig. 4.18. Simulation waveform during the transition at positive line voltage        | . 123 |

| Fig. 4.19. Simulation waveform of the transition at input voltage zero cross point   | . 124 |

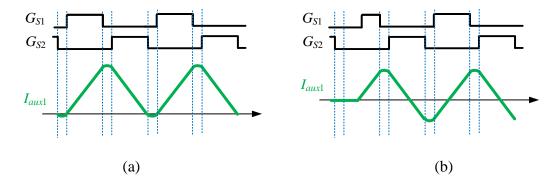

| Fig. 4.20. Two different turns on strategies.                                        | . 125 |

| Fig. 4.21. Resonant behavior during the transition dead time.                        | . 126 |

| Fig. 4.22. Current flow through $S_1$ and $S_2$                                      | . 129 |

| Fig. 4.23. Current flow through $S_3$ and $S_4$                                      | . 129 |

| Fig. 4.24. Calculated power loss curves.                                             | . 130 |

| Fig. 4.25. P <sub>loss</sub> comparison                                              |       |

| Fig. 4.26. Power loss breakdown at full power (100 W).                               | . 135 |

| Fig. 4.27. Comparison of three topologies                                            |       |

| Fig. 4.28. Laboratory prototype.                                                     | . 137 |

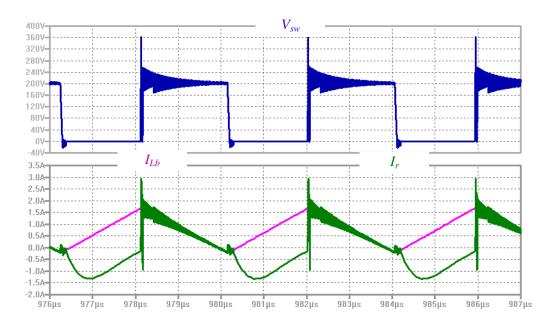

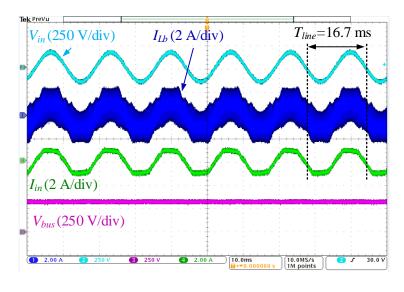

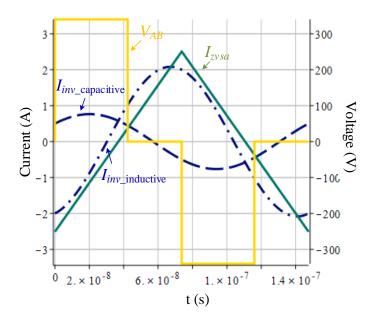

| Fig. 4.29. Waveforms at full power.                                                  | . 138 |

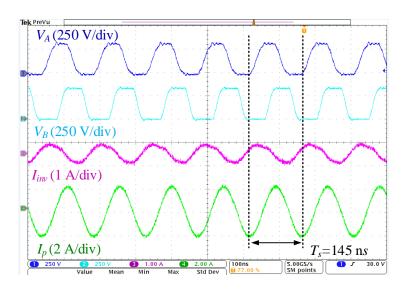

| Fig. 4.30. Waveforms at $P_o=72$ W                                                   |       |

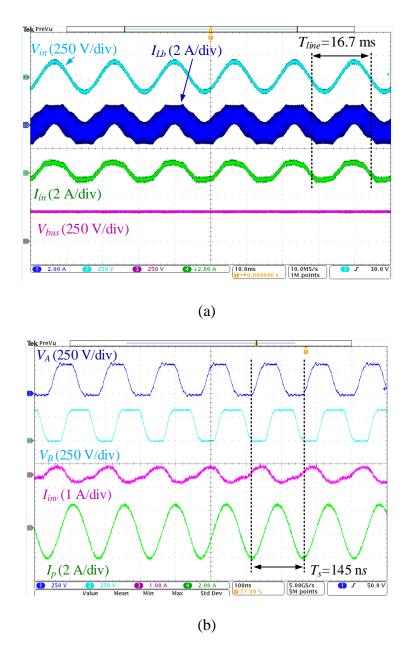

| Fig. 4.31. Waveforms at light load mode (50 W).                                      | . 141 |

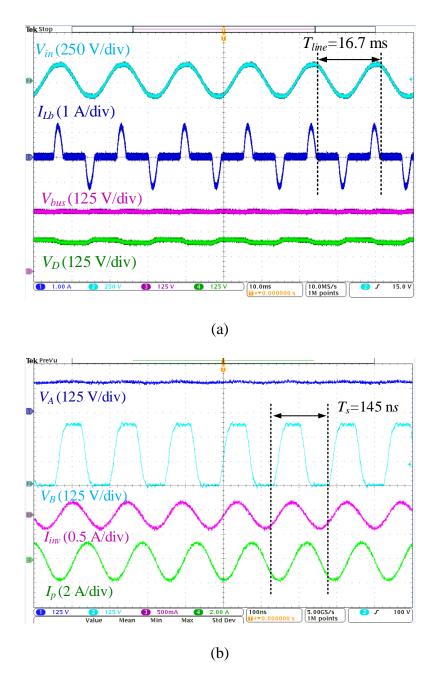

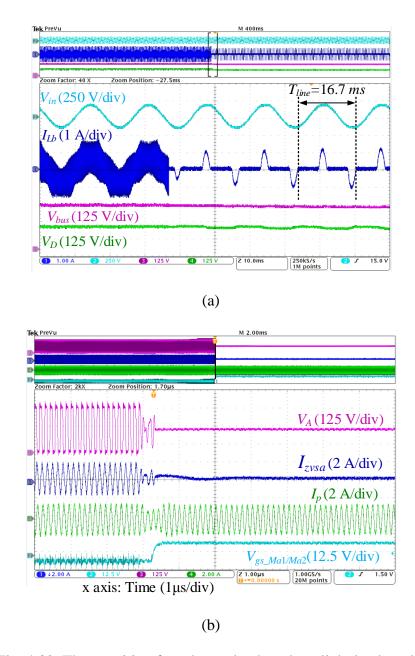

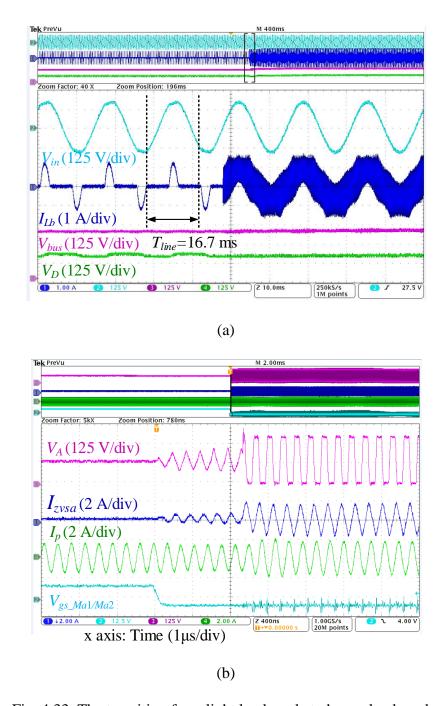

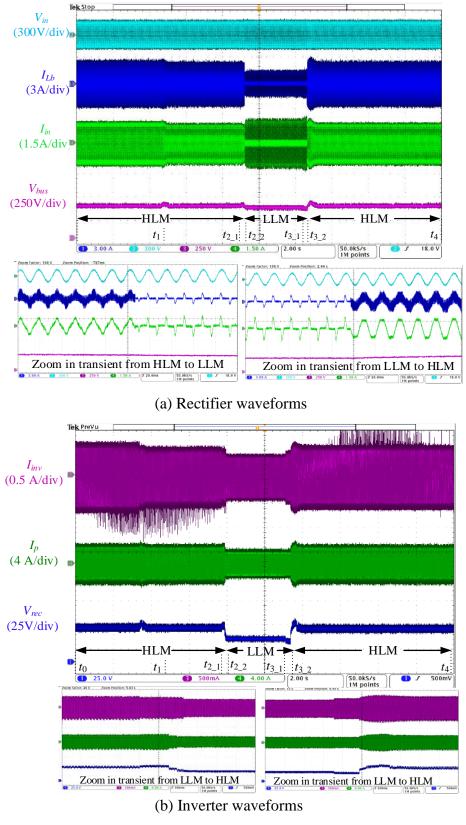

| Fig. 4.32. The transition from heavy load mode to light load mode                    | . 142 |

| Fig. 4.33. The transition from light load mode to heavy load mode                    |       |

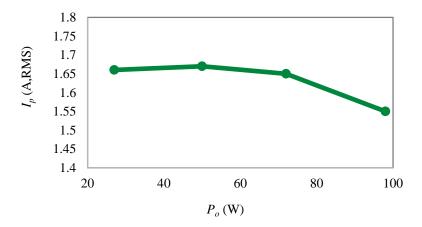

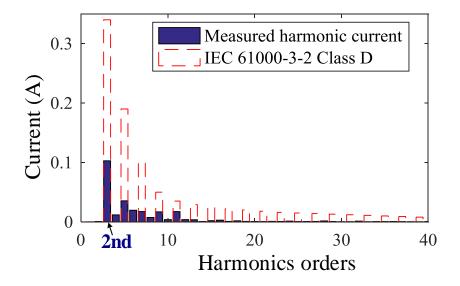

| Fig. 4.34. Experimental results for constant transmitter coil in the heavy load mode | . 145 |

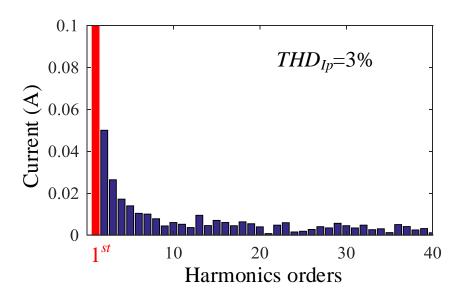

| Fig. 4.35. Harmonics analysis of <i>I</i> <sub>in.</sub>                             | . 146 |

| Fig. 4.36. Harmonics analysis of $I_p$                                               | . 146 |

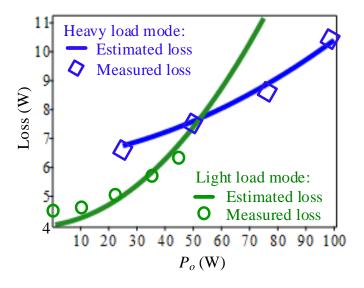

| Fig. 4.37. Measured loss.                                                            | . 147 |

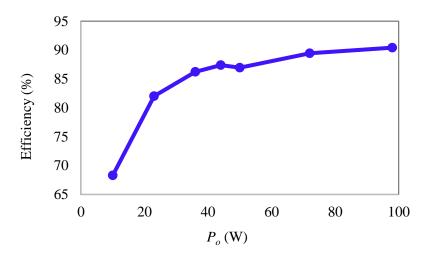

| Fig. 4.38. Measured power efficiency.                                                | . 148 |

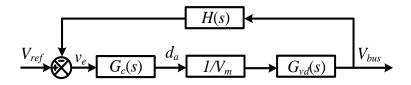

| Fig. 5.1. Closed-loop control diagram for constant transmitter coil current          | . 151 |

| Fig. 5.2. The closed-loop control diagram for $V_{bus}$ .                            | . 151 |

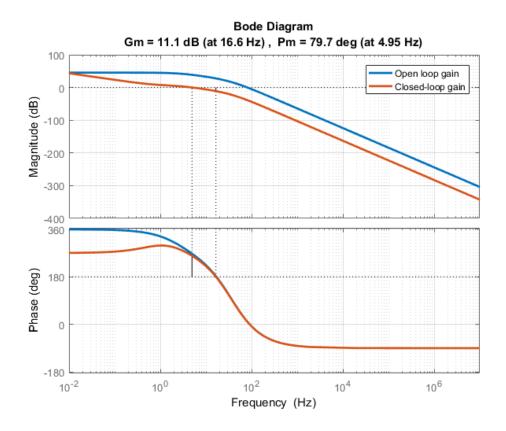

| Fig. 5.3. Bode plot of voltage control loop.                                         | . 153 |

| Fig. 5.4. Control trajectory for constant $V_{ab1}$ .                                |       |

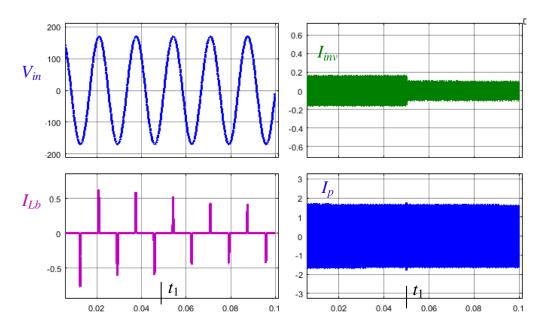

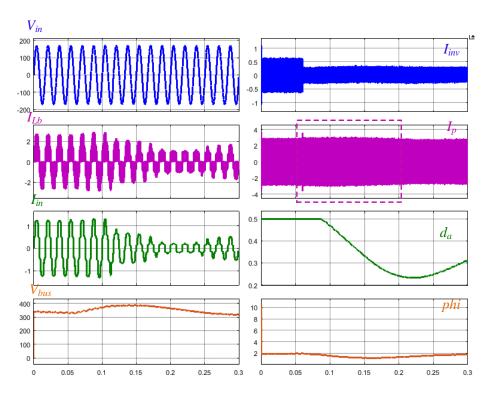

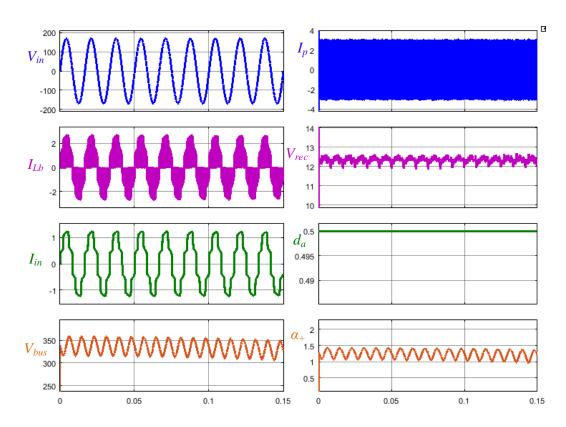

| Fig. 5.5. Constant current achievement in heavy load mode in the simulation          | . 155 |

| Fig. 5.6. Constant current achievement in light load mode in the simulation          | . 155 |

| Fig. 5.7. Operation boundary over full power range                                   | . 159 |

| Fig. 5.8. Control diagram with mode switching for a wide power range                 | . 161 |

| Fig. 5.9. The definition of $P_{max}$ .                                              |       |

| Fig. 5.10. Control flow chart for wide load range operation.                         |       |

| Fig. 5.11. ZVS detection method in half-bridge configuration                         | . 166 |

| Fig. 5.12. Simplified ZVS detection circuit.                                         | . 169 |

| Fig. 5.13. ZVS detection in a full bridge configuration.                             | . 170 |

| Fig. 5.14. ZVS detection for both upper and bottom devices.                          |       |

| Fig. 5.15. Schematic of two-receiver WPT system.                                     |       |

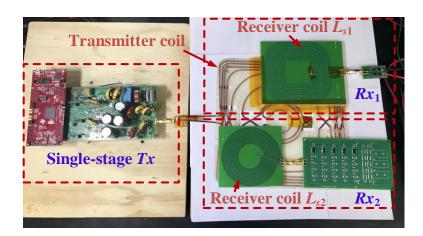

| Fig. 5.16. Hardware setup.                                                          | . 173 |

|-------------------------------------------------------------------------------------|-------|

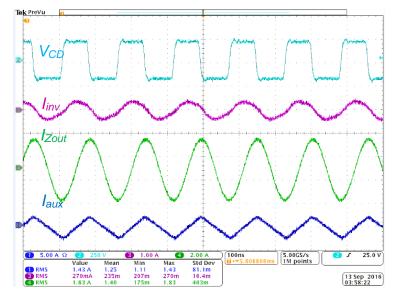

| Fig. 5.17. Measurement waveform with two receivers                                  | 174   |

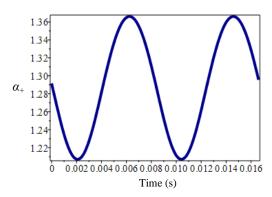

| Fig. 5.18. Experimental results of load-step change with open loop control          |       |

| Fig. 5.19. Experimental results of load-step change with the closed-loop controller | . 177 |

| Fig. 5.20. Schematic of WPT system with three receivers.                            |       |

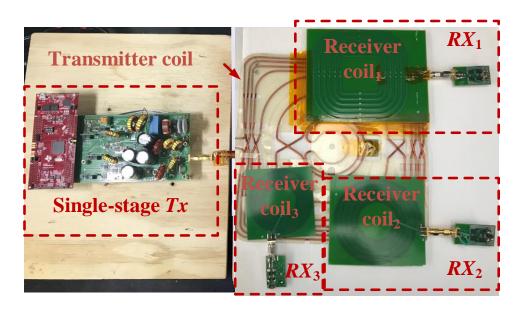

| Fig. 5.21. Hardware setup of WPT system with three receivers                        | 179   |

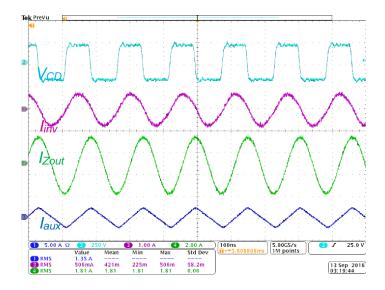

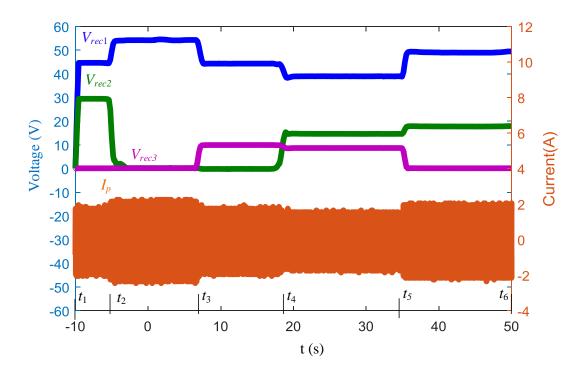

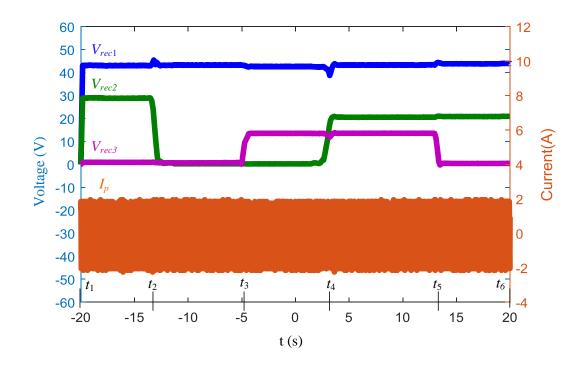

| Fig. 5.22. Measurement results with open loop control                               |       |

| Fig. 5.23. Measurement results with closed-loop control                             |       |

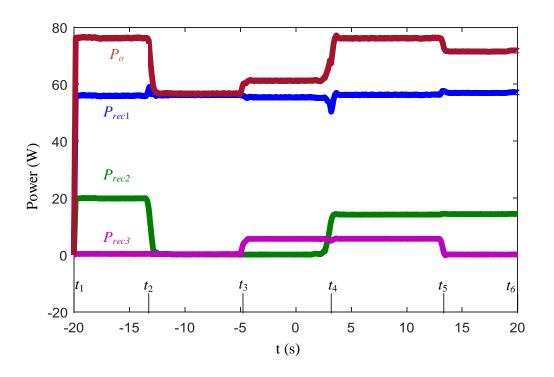

| Fig. 5.24. Power change on the three receivers with closed-loop control             |       |

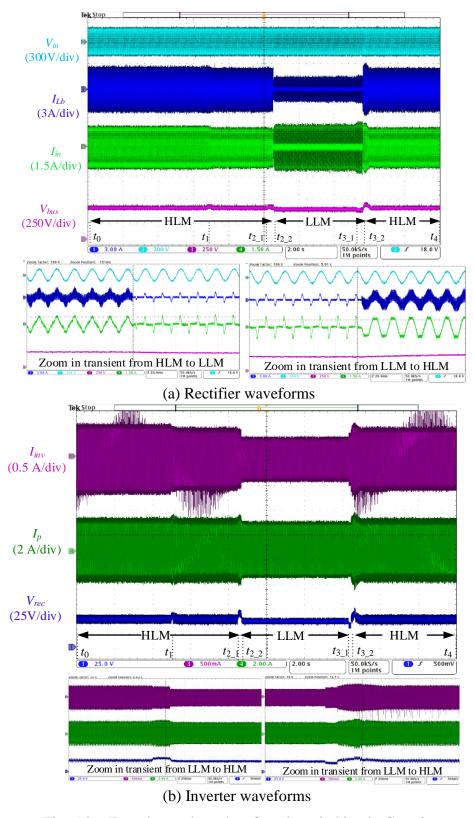

| Fig. 5.25. Experimental results of mode switching in Case 1                         | 184   |

| Fig. 5.26. Experimental results of mode switching in Case 2                         |       |

| Fig. 5.27. Measurement waveforms                                                    | 187   |

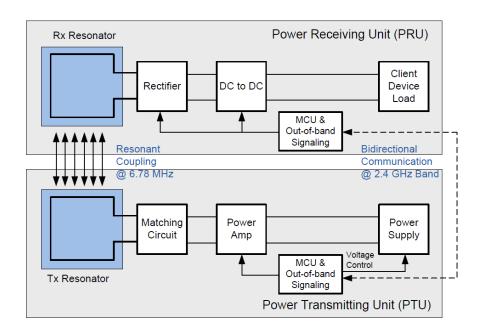

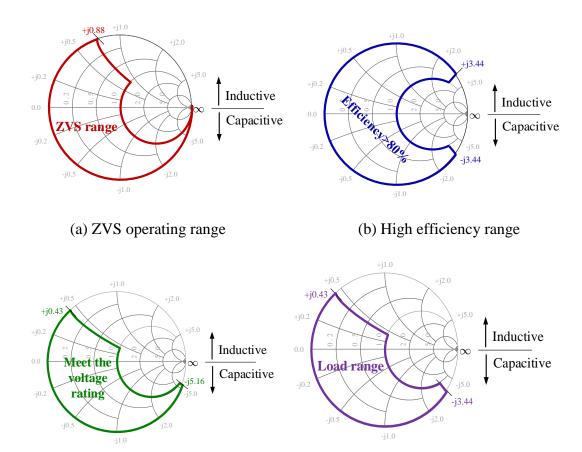

| Fig. 6.1. A4WP WPT system baseline system configuration [14]                        | . 190 |

| Fig. 6.2. Output network of the inverter.                                           |       |

| Fig. 6.3. The impact of reactive current on ZVS operation.                          | . 193 |

| Fig. 6.4. Reactive load range of the transmitter.                                   | . 194 |

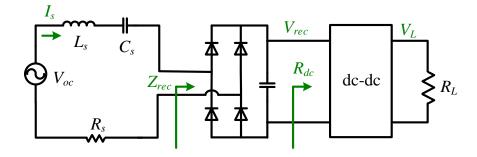

| Fig. 6.5. Simplified receiver configuration.                                        | . 195 |

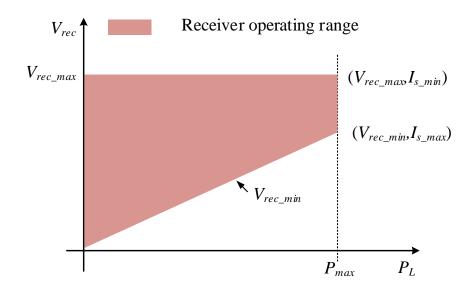

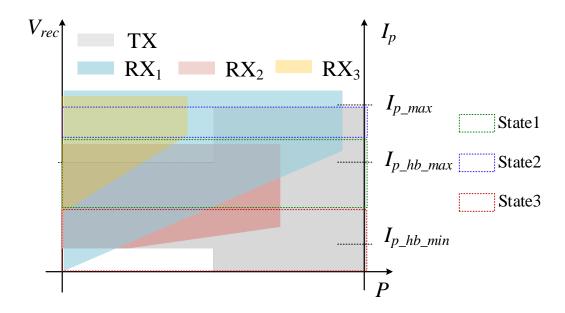

| Fig. 6.6. Receiver operating range.                                                 | . 198 |

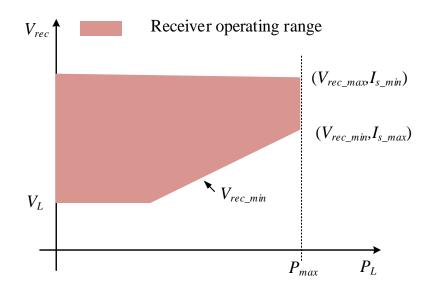

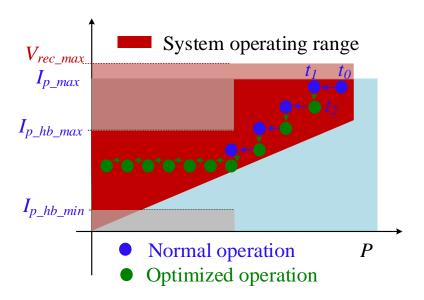

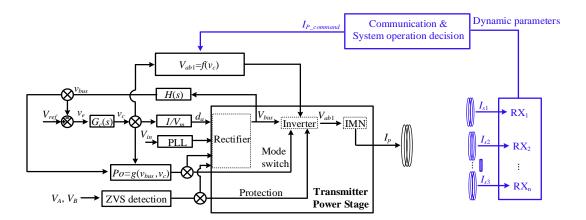

| Fig. 6.7. System operating range.                                                   | 201   |

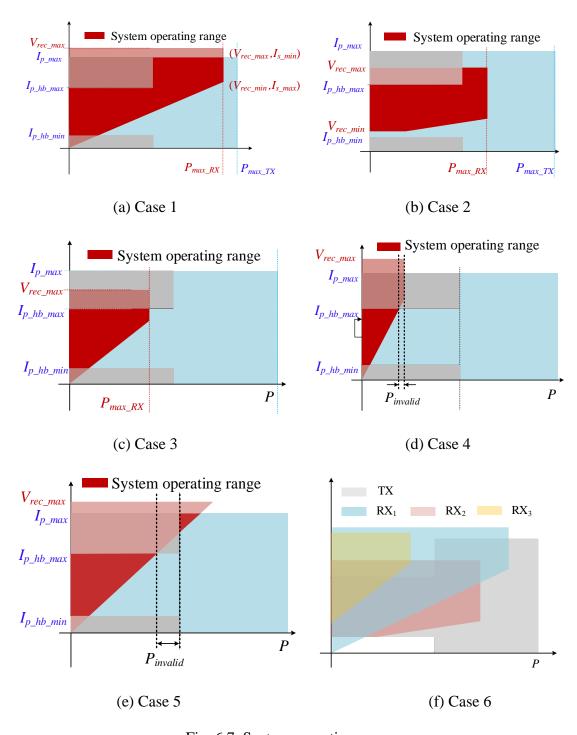

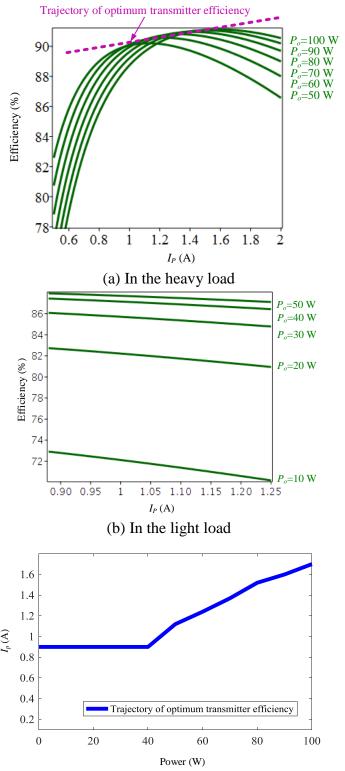

| Fig. 6.8. Transmitter efficiency vs. I <sub>p</sub>                                 | 203   |

| Fig. 6.9. The loss in the coils and diode rectifier $vs. I_p.$                      |       |

| Fig. 6.10. The trajectory of system efficiency optimization.                        | 208   |

| Fig. 6.11. The process of achieving system efficiency optimization                  | 209   |

| Fig. 6.12. Demonstration of three system operating states.                          | 212   |

| Fig. 6.13. Transmitter control diagram when considering system operation            |       |

| Fig. 6.14. System control flow chart.                                               |       |

| Fig. 6.15. Transmitter responses to State 2.                                        |       |

| Fig. 6.16. Experimental waveforms of transmitter responses to State 2               |       |

| Fig. 6.17. Transmitter responses to State 3.                                        |       |

| Fig. 6.18. Experimental waveforms of transmitter responses to State 3               |       |

| Fig. 6.19. System setup for the demonstration in State 1.                           |       |

| Fig. 6.20. Estimated system efficiency optimization in State 1                      |       |

| Fig. 6.21. Experimental demonstration of system efficiency optimization             | 219   |

| Fig. 7.1. The achievement of the single-stage transmitter.                          |       |

| Fig. 7.2. The improved closed-loop control diagram for the single-stage transmitter |       |

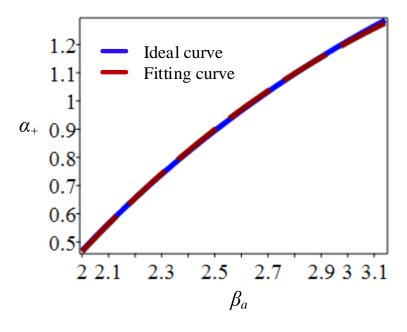

| Fig. 7.3. Improved mathematical mode via a surface fitting.                         |       |

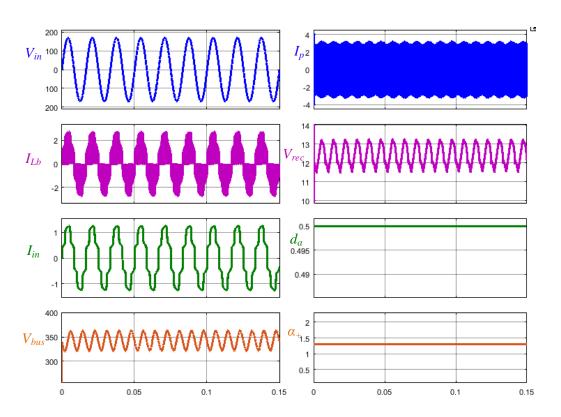

| Fig. 7.4. The performance with the original controller during the transition        |       |

| Fig. 7.5. The improved performance with feedforward control during the transition   |       |

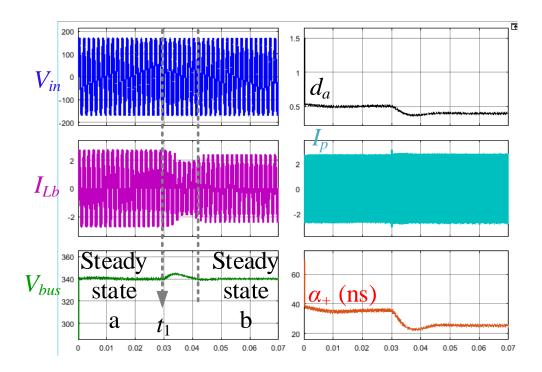

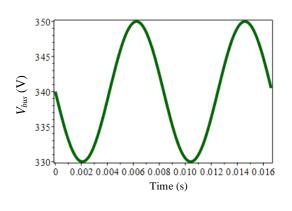

| Fig. 7.6. $\alpha_+$ changes along with bus voltage                                 |       |

| Fig. 7.7. Waveforms with reduced DC link capacitor without feedforward control      |       |

| Fig. 7.8. Waveforms with the reduced DC link capacitor with feedforward control     |       |

| Fig. 7.9. Waveforms with the reduced DC link capacitance with feedforward control.  | 233   |

## 1 INTRODUCTION

## 1.1 Wireless power transfer

In the recent decades, due to many merits, such as high flexibility, convenience, and safety, wireless power transfer (WPT) has attracted great attention in electric vehicles (EV) and consumer electronics, such as mobile devices, monitors, household appliances, and medical implants, as shown in Fig. 1.1. Recently, efforts have also been made towards dynamically charging vehicles in driving and smart tables which enable simultaneous charging of multiple devices on a single surface.

According to the power rating, WPT systems are categorized into three levels. (1) Low power, up to 15 W, typically used to charge medical or mobile devices. (2) Medium power range up to a few hundred watts for monitors, laptop and multiple consumer electronics. (3) High power mainly for industrial automation and EV charging application.

The wireless power market total revenue is expected to reach 8.5 billion by 2018. As reported in Pike Research, the number of wireless powered products will triple by 2020 to a \$ 15 billion USD market [1].

Fig. 1.1. The application of WPT [1].

## 1.1.1 The background of wireless power transfer

Wireless power transfer enables power transfer from source to load through an air gap, without interconnecting wires. This idea is first verified by Nikola Tesla in the 1910s through the Wardenclyffe Tower based on inductive and capacitive coupling. Even though he failed to popularize these findings at that time, this method is now widely used in nearfield wireless power systems. The earliest commercial product using inductive coupling is the inductive heating at the 1971 national association of homebuilder convention in Houston, Texas. The operation frequency of this system is 25 kHz. The magnetic flux induced by the high frequency output current of transmitter generates large eddy currents in a pot, heating it [2]. One of the first commercial product based on inductive wireless charging is the electric toothbrush in the early 1990s. Normally, the toothbrush is placed in a moist environment and needs to be regularly charged. A wired charger in the moist

environment causes electric shock for the users. The development of an inductive charger for electric toothbrush can fully enclose and insulate the plugs and wires. Therefore, it improves safety.

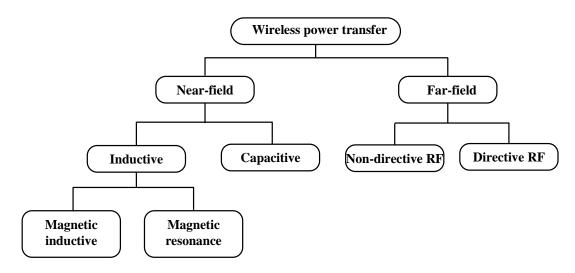

Wireless charging technologies can be classified into near-field (non-radiative), based coupled charging, and far-field (radiative RF) charging as shown in Fig. 1.2. The near-field technique consists of inductive coupling and capacitive coupling. Inductive coupling can be further divided into the magnetic inductive coupling and magnetic resonant coupling. In capacitive coupling, the achievable amount of coupling capacitance is dependent on the surface area of devices. Since consumer electronics typically have limited size, it is hard to implement this technique [3], [4]. But it is feasible in the EV charging application. The far-field technique includes direct RF power beamforming and non-direct RF radiation.

The former requires knowing the exact location of the receiver for power transfer [3].

The research in this thesis aims at consumer electronics application with inductive coupling techniques. And the following discussion refers to inductive power transfer.

Fig. 1.2. Categories of WPT technologies.

#### 1.1.2 Magnetic inductive coupling

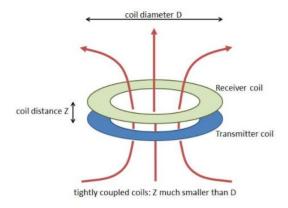

Inductive power transfer works by creating an alternating magnetic field in a transmitter coil and converting that flux into an electrical current in the receiver coil. Fig. 1.3 shows inductively coupled coils. The transmitter coil is driven by high frequency ac current. Depending on the coupling coefficient, a fraction of the magnetic flux generated by the transmitter coil penetrates the receiver coil and contributes to power transmission. The amount of flux coupled to the secondary coil is proportional to the cross-section area that presents to the magnetic field. The perfect coupling which has coupling coefficient k=1 is obtained when all the flux generated by the primary coil is coupled to the secondary coil. The maximum k can be obtained when the secondary coil has identical dimensions to the primary and the two coils are placed close to each other. Since the flux drop with distance, the secondary coil has to be placed as close as possible to the primary coil.

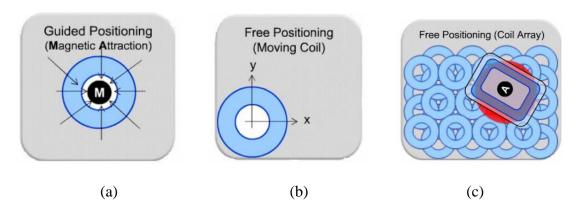

Because of this feature, the effective charging distance of inductive coupling is typically within 20 cm [3], [6]. Charging is also sensitive to misalignment in the X and Y directions. The transmitter and receiver should use the same coil and be perfectly aligned [7] to get the most efficient power transfer system. There are three methods that are typically used to ensure perfect alignment, as shown in Fig. 1.4. The first approach in Fig. 1.4(a) is using a magnet for positioning. The second approach in Fig. 1.4(b) is moving the position of transmitter coil to the location of the detected device. The third one in Fig. 1.4(c) is to use a large number of transmitter coils, and only power the coil aligned to the receiver.

Fig. 1.3. Tightly coupled coils [5].

Fig. 1.4. (a) Approach 1: guide the positioning charging. (b) Approach 2: free positioning based on a mechanically moveable primary coil. (c) Approach 3: free positioning based on the selective excitation of a coil array [8].

#### 1.1.3 Magnetic resonant coupling

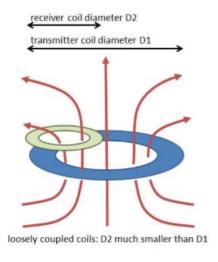

Magnetic resonant coupling was first introduced by the research group at Massachusetts Institute of Technology (MIT) in 2007 [9]. The basic idea of resonant coupling is that the two resonant coils are tuned at the same frequency. The magnetic resonant coupling typically operates at megahertz frequency, and the quality factors of coils are high, facilitating low power loss in coils. High *Q* coils can help mitigate the sharp decrease in the coupling coefficient when the distance increases [3]. As reported, extending the effective power transfer distance to meter range is possible [3]. Therefore, the resonant coupling also refers to loosely coupled technique. Fig. 1.5 shows the loosely coupled coils. There are several key capabilities of resonant coupling compared to magnetic inductive coupling due to high frequency and fully resonant features. With resonance, the charging position has higher spatial freedom in X, Y and Z directions. Devices are placed on the right, left, the top or bottom side of the charging station. Compared to the inductive coupling, the resonant coupling has a higher tolerance to the misalignment.

Fig. 1.5. Loosely coupled coils [5].

- The resonant coupling allows a single transmitter to charge multiple devices simultaneously. Each device, as it is put close to the charging station, can efficiently pick up the power it needs. Adding or removing one device will not impact the rest.

- Resonant coupling wireless power can be transmitted through some materials, such as wood, stone, glass, or concrete. This feature allows the transmitter to be placed under the table or embedded in the concrete wall[10].

#### 1.1.4 The standards for WPT

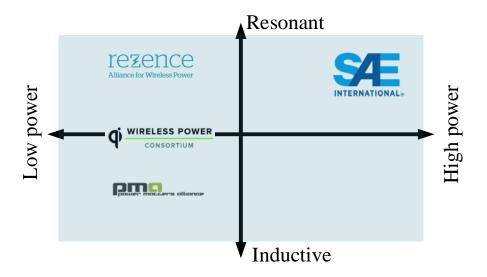

There are four standards (three for consumer electronics, one for EV application) developed in the past few years.

- (1) Wireless power consortium (WPC) was established in 2008 [11]. The standard set by WPC is named as "Qi." The most recent Qi specification V1.2.3 in 2017 calls for an ac frequency in the primary coil of between 87 and 205 kHz for the power range from 5 W to 30 W [7]. WPC has planned to develop classes up to 2.5 kW. The technology also includes foreign object detection (FOD) such that the charger does not expend energy heating up conductive objects that have been accidentally placed in the field [5].

- (2) Power matters alliance (PMA) is another industry consortium developing WPT standards [12], for an ac frequency between 277 kHz and 357 kHz, up to 20 W. PMA has proposed solutions up to 2.4 kW for kitchen appliances [13].

- (3) In 2012, the Alliance for wireless power (A4WP) developed another standard, "Rezence", for 6.78 MHz magnetic resonant coupling. A4WP is aiming at extending the charging distance and improving spatial freedom[14]. The power rating under this standard is up to 70W for the transmitter, and 50 W for a receiver according to the baseline

specification,V1.3, in 2014 [15]. In 2015, PMA and A4WP were merged into a new organization named AirFuel Alliance [16].

(4) SAE International is working on specifications for wireless charging of electric and plug-in hybrid vehicles [17]. Standard SAE J2954 for EVs announced that the low-frequency band centers at 85 kHz (range from 81.38-90 kHz) in 2013. It also defines three power levels for EVs, WPT 1 (maximum power rating is 3.7 kW), 2 (maximum power rating is 11 kW) and 3 (maximum power rating is 22 kW) [4].

Table 1.1 concludes these four standards. Generally, the inductive coupling has a lower operating frequency which makes the design for power circuits easier. Lower frequency can also help reduce the losses in the switches and inductors. The high frequency resonant coupling works at MHz frequency range, increasing the design complexity of converters. The high frequency operation also brings in the potential electromagnetic interference (EMI) challenges.

Fig. 1.6 shows the four WPT standards with respect to different coupling methods and power level.

# 1.2 Motivation and strategy

To further popularize the application of WPT system, significant efforts are made and will be made towards high efficiency and high power density, lowering the bill of material, improving the system robustness and enhancing the interface to provide user better experience. System integration on the converter level is an approach to increase the efficiency, reduce the system volume and component count. The implementation of simultaneously charging of multiple receivers can bring in higher spatial freedom for the users. This thesis mainly focuses on the transmitter design.

TABLE 1.1 COMPARISON OF WPT STANDARDS

| Standard                   | SAE               | WPC (Qi)                                 | AirFuel Alliance                                        |          |  |

|----------------------------|-------------------|------------------------------------------|---------------------------------------------------------|----------|--|

| Standard                   | SAE               | WPC (QI)                                 | PMA                                                     | A4WP     |  |

| Technology                 | LF-<br>resonance  | Inductive and LF-<br>resonance           | Inductive HF-resonar                                    |          |  |

| Supported by the companies | WiTricity,<br>BWM | Apple, LG,<br>Motorola, Sony,<br>Samsung | Dell, EPC, Starbucks,<br>WiTricity, Duracell, Power man |          |  |

| Members                    | /                 | 433 [18]                                 | 150 [19]                                                |          |  |

| Certified products         | /                 | 1304 [18]                                | 29 [19]                                                 | 60       |  |

| Power range                | Up to 22 kW       | 5 W-30 W                                 | 0-20 W Up to 70                                         |          |  |

| Operation frequency        | 85 kHz            | 87-205 kHz                               | 277-357 kHz                                             | 6.78±MHz |  |

Fig. 1.6. WPT standards landscape.

#### 1.2.1 The innovation of transmitter architecture

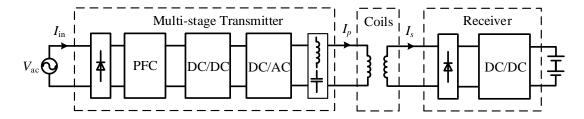

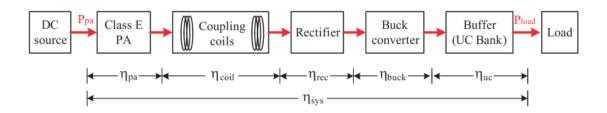

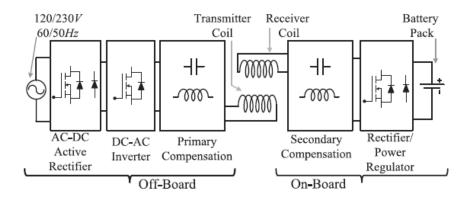

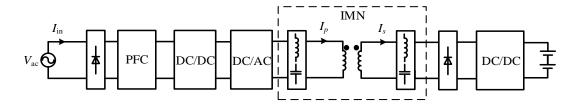

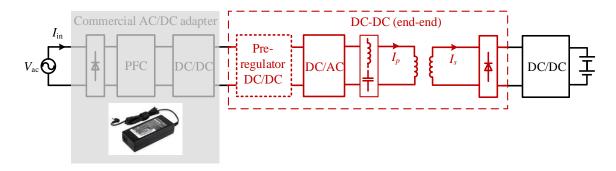

Multiple-stage transmitter architecture is a conventional structure, as shown in Fig. 1.7. Generally, it is comprised of a full bridge diode rectifier which converts utility frequency ac power to dc, a PFC, a dc-dc converter that processes dc voltage to the desired bus value, and a dc/ac inverter which converts the dc bus voltage to a high frequency ac current which drives the transmitter coil. This architecture has merits in the decoupling of individual converter functions. Each stage employs the best design for the specific ratings. However, it exhibits low end-to-end (dc-dc) efficiency and bulk size due to the number of cascaded conversion stages. Therefore, reducing the number of power conversion stages is one potential approach to improve system efficiency.

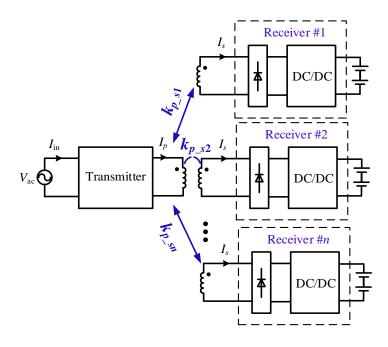

### 1.2.2 A single transmitter for multiple receivers charging application

Resonant coupling techniques allow multiple devices to be charged concurrently by a single transmitter. This achievement further improves the convenience and reduces the use of wires. In the future, the transmitter can be placed on the wall or ceiling of a room. Then all those electric devices in the room including light, mobile devices and TVs can be powered wirelessly, as shown in Fig. 1.8. In addition, when the clocks, radios, music players and remote controllers are powered up wirelessly, the batteries inside them can be removed. As reported, this can reduce 6 billion batteries disposed of each year, reduce a large source of toxic waste and groundwater contamination [20].

In this thesis, the transmitter is designed to provide the possibility for the multiple receivers concurrently charging application.

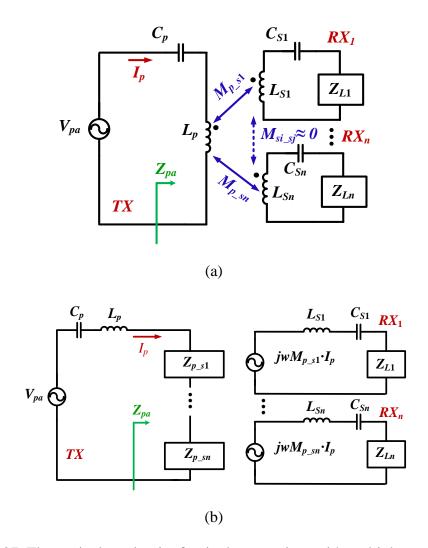

Fig. 1.9 shows the simplified schematic of the multiple charging cases, assuming no cross-coupling among the receivers.

Fig. 1.7. WPT system with the multi-stage transmitter.

Fig. 1.8. Multiple devices charging application [21].

Fig. 1.9. The sketch of single transmitter charging multiple devices.

#### 1.3 Dissertation outline

The outline of this dissertation is as follows:

Chapter 2 presents the literature review of the WPT architecture, the converter topologies, the compensation network, soft switching techniques and the control strategy in the WPT system.

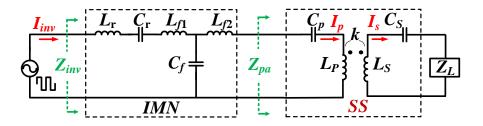

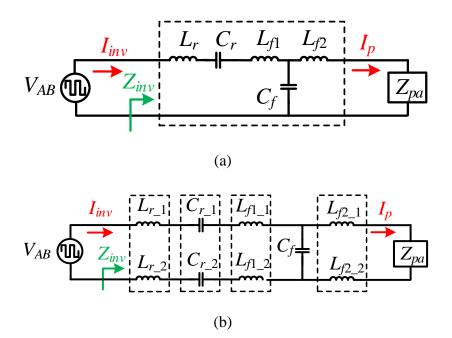

Chapter 3 designs a two-stage transmitter for high PF, low THD, high efficiency and low part count. The inverter together with compensation network maintains constant current behavior for multiple receiver application.

Chapter 4 develops a single-stage transmitter for high PF, low THD, high efficiency and low part count. The control scheme is proposed to regulate the input current and output power simultaneously. An auxiliary circuit is proposed to improve the light load efficiency. The loss model is derived. The comparison among different topologies has been made.

Chapter 5 implements a closed-loop control scheme to regulate constant transmitter current at the output of the single-stage transmitter during a dynamic load change. A full power range operation is achieved by combining heavy load mode and light load mode operation.

Chapter 6 discusses a WPT system operation with the implementation of the singlestage transmitter. The system level control scheme is introduced. The capability and approach of achieving wide system operating range and optimum system efficiency are addressed.

Chapter 7 concludes this work and presents future work.

#### 2 LITERATURE REVIEW

This chapter reviews the state-of-the-art of WPT system, in terms of architecture, impedance matching network and control strategies. This review helps to understand the opportunities and challenges for the research in the future.

### 2.1 WPT architecture

This section reviews the state-of-the-art WPT architecture, including the consumer electronics application, high power application, industrial products and academic work. The achievement of different topologies will be concluded. And the opportunities for improvement will be investigated.

#### 2.1.1 The state-of-art industrial WPT products

The consumer electronics WPT system includes low power (few watts) to medium power (few hundred of watts) ranges. The front-end ac-dc rectifier usually either uses a wall adapter which converts ac to dc in a rectifier or alternatively, a dc voltage source from a battery or other dc supply in the technical products [22], [23]. Therefore, most of the literature about WPT system design in this power range start from dc input. Fig. 2.1 shows an example.

Fig. 2.1. System configuration for the commercial consumer electronics application [24].

The market of the WPT system in consumer electronics is classified into 3 categories [25]:

- (1) Finished products. There are thousands of Qi and Airfuel certified products available in the market, including standalone charging pads for mobile phones, monitor, and laptops. Mophie provides a Qi-certified wireless charging pad for the iPhone [26]. There are also many WPT systems that are embedded in other systems. For example, a wireless charger embedded in a table clock or a monitor as shown in [27].

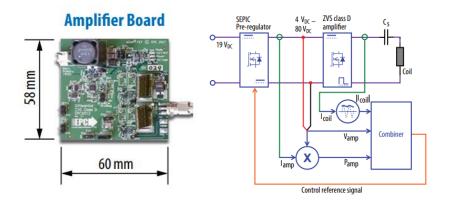

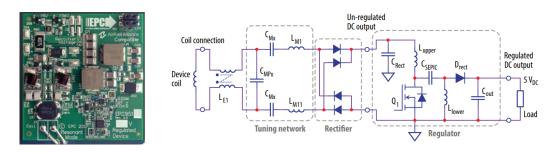

- (2) Modules [25]. A branch of business focuses on the parts and modules for building a WPT system. WiTricity has WiT-5000 reference design board, 6.78 MHz, 24 W input (12V, 2A). The dc-dc (including the inverter, coils and the secondary rectifier, also refer to end-end) efficiency is 60 %. Coil to coil efficiency achieves 90%. The distance between the transmitter coil and receiver coil (Z range) is 5mm-45mm [28]. The communication of transmitter and receiver uses Bluetooth. The topology is not reported. EPC developed many transmitter boards and receiver boards. The transmitters cover 10 W-60 W power rating, while receivers include 5 W and 10 W power rating. The topologies of the transmitter are either class D or class E amplifiers. EPC 9512 is a class D amplifier [29], as shown in Fig. 2.2. The input is required to connect to a 19 V dc source. The SEPIC converter boosts bus voltage to 80 V. The efficiency of the ZVS class D amplifier is 90.6 % [30]. The development board EPC 9083 is a 60 W class E wireless transmitter and requires 40 V dc bus input [31]. The 5 W receiver develop board EPC 9513 is comprised of a diode rectifier and a subsequent SEPIC dc-dc converter which controls the output voltage to 5 V [32], as shown in Fig. 2.3. The efficiency of these development boards is not reported. Wurth worked with Texas Instruments (TI) on a WPT system reference design, as shown in

Fig. 2.4. Wurth contributes to the coil design, while TI on the circuit design with their own semiconductors and controller. A class D amplifier is used to provide high frequency ac current at the primary side. The diode rectifier and a subsequent dc-dc converter at the secondary side are for dc voltage regulation [13].

(3) Chipset. IC manufactures work actively on integrated circuits for the WPT system control applications. NXP launched NXQ1TXH5 which is a chip-based 5 W Qi-certified wireless transmitter at 2016. It utilizes a full bridge inverter and reports 85% efficiency [33]. TI launched an integrated receiver bq51011 (93% efficiency) [34] and bq5105xB (90% efficiency) [35] based on Qi V1.2 in 2012. The late one integrates a battery charger into the chip. ST promoted the STWBC-EP that complies with Qi V1.2.3 for a 15 W transmitter and STWLC33 for a 15 W receiver [36]. This receiver achieves 97% peak efficiency [37].

Industry has also developed WPT for EV applications. WiTricity claimed the DRIVE 11 evaluation system achieves a grid-to-battery peak efficiency for a 3.6-11 kW system up to 94% [38]. Evatran began to sell their Plugless L2 WPT system to the public in 2014 [4]. Now they have 7.2 kW system for TESLA model S, BMW 13, NISSAN LEAF [39].

In a summary, the front-end ac-dc rectifier is not included in the WPT design for consumer electronics application. An extra adapter is used in the standalone charger. Or the dc source is provided is WPT charger is embedded in the other systems. And dc input of resonant inverter has typically low voltage.

Fig. 2.2. EPC9512 amplifier board and schematic configured as 33 W Class-D amplifier [29].

Fig. 2.3. EPC9513 rectifier board photo configured as 5 W [32].

Fig. 2.4. TI Transmitter board bq500211AEVM-210 with class D amplifier [13].

#### 2.1.2 The state-of-art academic WPT architectures

### 2.1.2.1 Consumer electronics WPT system

The system architecture of the WPT system in the academic work is similar to commercial products, as shown in Fig. 2.1. The front-end ac-dc rectifier either uses a wall adapter or a dc voltage source [4], [40], [24].

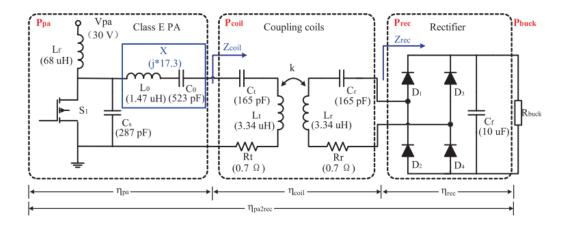

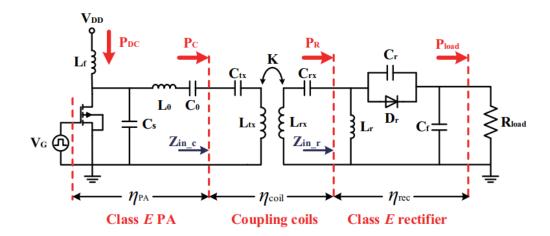

Fig. 2.5 shows a common architecture for the WPT system [41]. It is comprised of a Class E inverter, coupling coils and diode full bridge rectifier. The Class E inverter is known to be a promising topology for high frequency and low power applications thanks to the simple circuit and soft switching.

Many systems are derived based on this architecture. Class E inverters can be paralleled to increase the power delivery capability. [42] uses dual class E inverters in parallel at the primary side. [43] employs six inverters in parallel to achieve a power up to 301 W. The end-to-end efficiency achieves 84.7%. The Class E<sup>2</sup> dc-dc converter with 6.78 MHz operation frequency is proposed in [44], [45], as shown in Fig. 2.6. It is comprised of a primary class E transmitter and a secondary class E rectifier. The measured peak end-end efficiency is 80 % at 20 W output power [45]. The Class EF<sup>2</sup> converter is derived by adding an LC network across the switch. It achieves lower voltage stress on the switch and lowers THD of the amplifier output current compared to Class E amplifier. The peak efficiency is reported as 71% at 29 W output power [46].

Fig. 2.5. The configuration of class E with secondary side diode rectifier for WPT application [41].

Fig. 2.6. The configuration of Class  $E^2$  dc-dc converter for WPT application [45].

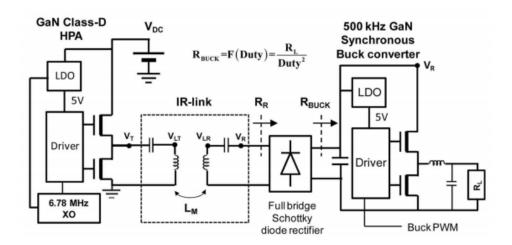

For low power applications, the Class E inverter is widely adopted due to the simple circuitry. However, since it has large voltage stress on the main device, for the medium power range application, the Class D inverter is more common [47], as shown in Fig. 2.7. More details about the class D inverter will be discussed in Section 2.2.2. In addition, a synchronous buck converter is implemented after the diode rectifier to pick up the demanded power.

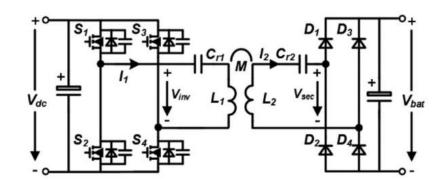

The full bridge resonant inverter has a higher capability of delivering power than a half-bridge inverter. Besides, two-phase legs enable the use of phase shift modulation to adjust the output voltage. Therefore, it is also widely used [48], [49], especially in the medium-to-high power applications. Shown in Fig. 2.8, the primary side is a full bridge resonant inverter with 80 V input voltage, and the secondary side implements a diode rectifier. The reported end-end efficiency is 78% [49].

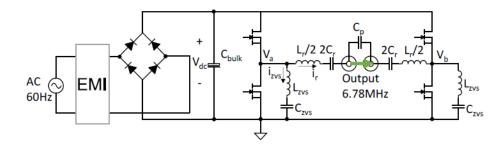

All the above-mentioned architectures are based on a dc input. To complete a whole system, an extra commercial adapter is required. Thus the system optimization is hard to achieve. A transmitter based on the line frequency ac input is proposed in [40], as shown in Fig. 2.9. The motivation of this approach is to design the front-end ac-dc rectifier and high frequency resonant inverter together, thus obtaining an optimized system design, reduced number of power conversion stage and improved system efficiency.

Table 2.1 concludes the comparison among the typical WPT architectures for consumer electronics. First, the front-end ac-dc rectifier usually is not included in the research scope. Second, significant efforts are made on the Class E inverters/rectifier at high frequency and lower power level. Third, attention starts to be given to the integrated system architectures.

Fig. 2.7. The wireless power transfer system with class D amplifier and diode bridge rectifier [47].

Fig. 2.8. A wireless power transfer system with full bridge inverter and diode rectifier [49].

Fig. 2.9. A single-stage ac-ac transmitter is proposed for WPT system application [40].

TABLE 2.1 COMPARISON OF WPT ARCHITECTURE ON THE CONSUMER ELECTRONICS

| Input | Architecture                                          | $f_o$    | Distance/k | $P_o$ | η                   | Ref. |

|-------|-------------------------------------------------------|----------|------------|-------|---------------------|------|

| dc    | Pri: Class E<br>Sec: load                             | 6 MHz    | 30 cm      | 105 W | 77%<br>dc-load      | [50] |

| dc    | Pri: Class E<br>Sec: diode rectifier                  | 6.78 MHz | 45 mm      | 10 W  | 72.1%<br>dc-dc      | [42] |

| dc    | Pri: Dual Class E<br>Sec: diode rectifier             | 134 kHz  | 10 mm      | 295 W | 75.7%<br>dc-dc      | [42] |

| dc    | Pri: 6 Class E<br>Sec: diode rectifier                | 6.78 MHz | 42 mm      | 301 W | 84.7%<br>dc-dc      | [43] |

| dc    | Pri: Class E<br>Sec: Class E                          | 6.78 MHz |            | 20 W  | 80%<br>dc-dc        | [45] |

| dc    | Pri: Class EF2<br>Sec: Class EF2                      | 6.78 MHz |            | 29 W  | 71 %<br>dc-dc       | [46] |

| dc    | Pri: Class D inverter<br>Sec: diode<br>rectifier+buck | 6.78 MHz | 50 mm      | 44 W  | 73 %<br>dc-dc       | [47] |

| dc    | Pri: Full bridge<br>inverter<br>Sec: rectifier        | 97.6 kHz | k: 0.44    | 5 W   | 71%<br>dc-dc        | [48] |

| dc    | Pri: Full bridge<br>inverter<br>Sec: diode rectifier  |          | k: 0.1     | 60 W  | 78%<br>dc-dc        | [49] |

| ac    | Pri: Full bridge<br>diode+inverter<br>Sec:            | 6.78 MHz |            | 50 W  | 92 % acprimary load | [40] |

#### 2.1.2.2 High power WPT system

In this section, previous research on the single-phase high power WPT system is reviewed. So far, the high power WPT systems are mainly for EV charging. The power rating typically greater to kW.

Fig. 2.10 shows a typical high power WPT system architecture [51], [52]. Different from consumer electronics, these high power systems typically are designed including the front-end ac-dc rectifier. The ac-dc rectifier converts line frequency ac to a regulated dc bus. It can regulate the output power by adjusting the bus voltage. Include this stage in the design scope, then the subsequent dc-dc converter that was introduced in the consumer electronic WPT systems can be eliminated. The secondary side can employ either the diode rectifier or the active rectifier.

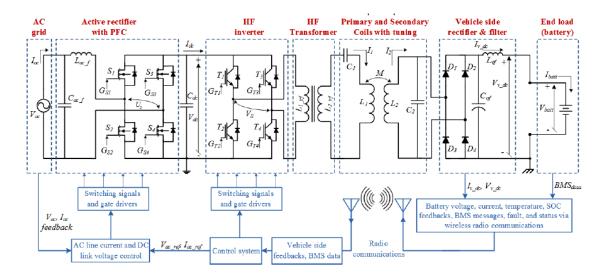

The front-end ac-dc PFC rectifier in the conventional EV wireless charging system is typically comprised of a diode rectifier and a PFC circuit [53], [54], [55]. Fig. 2.11 shows the state of the art EV wireless charging system which is comprised of a bridgeless totem-pole PFC rectifier, full bridge inverter, coils and secondary rectifier [56]. Employing this totem-pole rectifier into transmitter while keeping the subsequent high frequency inverter, the number of power conversion stages is reduced[57], [58], [59]. As reported in [58], the power efficiency at 7.7 kW achieves 96.5% and the PF is 0.99. The control IC for the totem-pole rectifier has been implemented by the IC companies, such as NXP [60]and TI [61].

Fig. 2.10. WPT system in EV application with ac power supply [52].

Fig. 2.11. Schematic of EV wireless charging system [56].

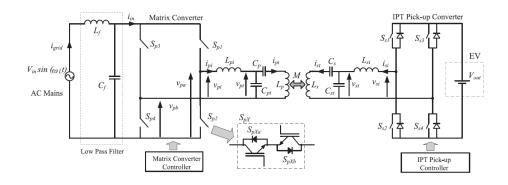

References [62], [63] and [64] introduce a full bridge, current fed, direct ac-ac converter in EV WPT applications, as shown in Fig. 2.12. It is a boost-derived topology. Duty cycle and phase shift are employed to control the input current and output voltage with low THD of the input current. The load power is regulated and soft switching is achieved for the inverter switches. However, since the bus voltage is not regulated, significant double line frequency ripple exists on the bus. This double line frequency ripple flows through the coils to the receivers bringing in other harmonics and increasing the radiation from the coils. The impact of low-frequency ripple on the battery is still unknown. Moreover, the actual semiconductor count is high.

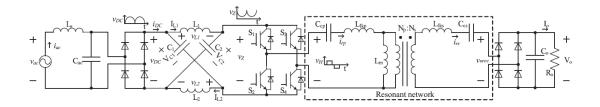

The high power WPT system in Fig. 2.13 is formed by a primary integrated Z-source converter and a diode rectifier at the second side. The Z-source converter regulates the input current and output power. However, it is limited to low frequency (for example 20 kHz) applications due to hard switching. Furthermore, a significant double line frequency ripple exists at the output of the transmitter.

Table 2.2 summarizes the comparison among the typical high power WPT architectures for EV charging. In all of those architectures, the design of the ac-dc PFC rectifier is included. The main difference among these architectures is the transmitter structure. Different approaches are investigated to reduce the number of semiconductor devices at the transmitter side.

Fig. 2.12. Matrix transmitter proposed in [64].

Fig. 2.13. Z source converter based two-stage transmitter [65].

TABLE 2.2 COMPARISON OF WPT FOR EV APPLICATION

| Architecture                                             | $f_o$  | distance | $P_o$  | η                 | Device counts | Ref. |

|----------------------------------------------------------|--------|----------|--------|-------------------|---------------|------|

| Pri: diode<br>rectifier+inverter<br>Sec: diode rectifier | 30 kHz | 120 mm   | 3 kW   | 96 %<br>ac-load   | 14            | [54] |

| Pri: Totem-pole rectifier+inverter Sec: diode rectifier  | 22 kHz | 162 mm   | 6.6 kW | 92%<br>ac-load    | 12            | [56] |

| Pri: Matrix<br>converter<br>Sec: diode rectifier         | 50 kHz |          | 1.2 kW |                   | 12            | [62] |

| Pri: Matrix<br>converter<br>Sec: active rectifier        | 20 kHz |          | 1 kW   | 89.6 %<br>ac-load | 12            | [64] |

| Pri: Zsource<br>converter<br>Sec: diode rectifier        | 20 kHz | 200 mm   | 1 kW   | 71%<br>ac-load    | 12            | [65] |

# 2.2 The converter topologies of the transmitter

The transmitter converts utility line frequency ac power to high frequency ac power for driving the transmitter coil. This section provides a literature review of the state of the art of individual power conversion stage. The challenges and opportunities of different topologies in terms of efficiency, voltage and current stress of semiconductor stress and the part count are investigated to guide future research.

## 2.2.1 Ac-dc rectifier

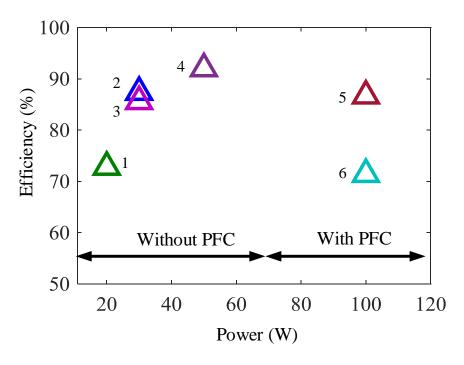

Since the design for the low power to medium power range WPT system typically employs a commercial adapter as a dc source for the following transmitter stage, the-state-of art ac-dc adapters in the industry and academic area are reviewed in this section.

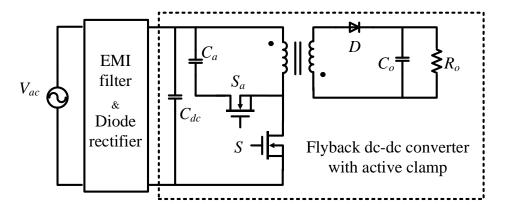

The diode full bridge rectifier is the simplest rectifier circuit. Depending on the application, a subsequent dc-dc converter might be used to adjust the bus voltage. The flyback is the most popular topology for this dc-dc power conversion due to a low parts count, low cost and simplicity [66], [67], [68] as shown in Fig. 2.14. The well-known flyback converter suffers from high voltage stress during the main switch turns off and high switching loss during the turn on. Therefore, a resistor-capacitor-diode (RCD) clamp [66] or active clamp [69] typically are adopted to solve those issues. In addition, the input current of flyback is discontinuous which requires larger input filter. As a result, the flyback is mainly used for low power level applications. As addressed in [66], the flyback converter is prevalent at lower power levels (below 45 W). [69] shows 94.5% peak efficiency in a 45 W system (90 V ac input voltage, 20 V output voltage) with 25 W/in<sup>3</sup> power density.

Fig. 2.14. The combination of diode rectifier and flyback for ac-dc converter.

The input current harmonic content of an off-line converter impacts other electronic equipment connected to the grid. The standard IEC-61000-3-2 [70] gives a limitation of the harmonic components for different equipment. Equipment is classified into four categories: (1) Class A includes the balanced 3-phase equipment. (2) Class B includes portable tools. (3) Class C is the lighting equipment. (4) Class D includes monitors, screens, TV, and computers which have input power between 75 W and 600 W.

For higher power application where PFC is required (when power is larger than 75 W), a boost PFC rectifier is often used [71], as shown in Fig. 2.15. The Boost PFC has continuous input current, so it is superior to other topologies such as buck and flyback for smaller input filter design. In addition, the resistive input impedance of boost converter ensures higher PFC and low THD of input current with small control effort. Moreover, buck type PFC rectifier has dead angles during the time intervals when the input voltage is lower than the output voltage. As a result, the boost PFC rectifier offers a cheap and straightforward solution, thus is widely used in industry [72].

Fig. 2.15. PFC boost rectifier.

The output voltage of the boost PFC must be higher than the peak of the input line voltage. For example, the universal line-voltage range is 90-265 Vrms. If this is the application, the output voltage of the boost PFC must be greater than 380-400V. If the application requires or prefers this voltage rating for the output, then this topology is a good candidate. But for the adapter application which requires low output voltage such as 48 V, 24 V, or 12 V, a high step down dc-dc converter is needed. The resonant LLC converter is typically implemented for the subsequent dc-dc converter due to high efficiency by featuring soft switching and compact size [72], [73], [74], [67], [75]. [72] achieves 95.3 % efficiency and 11.7 W/in<sup>3</sup> power density based on the paper design of a 100 W system. [76] addresses a design case with diode rectifier, boost PFC and LLC for a 150 W adapter that achieves 94.2% efficiency. The peak frequency of PFC and LLC are 1 MHz and 500 kHz respectively. The reported power density is 21.4 W/in<sup>3</sup>. In [77] the adapter consists of a diode full bridge rectifier and half-bridge LLC converter with 90 % efficiency. The commercially-available adapters typically have 6 W/in<sup>3</sup> power density. And the best-inclass commercial adapter achieves 12 W/in<sup>3</sup> for 150 W system [78]. A comparison is made based on the literature review, shown in Table 2.3.

TABLE 2.3 COMPARISON OF ADAPTER

| Topologies             | Power density          | $P_o$ $\eta$ |       | Topologies           | Ref. |

|------------------------|------------------------|--------------|-------|----------------------|------|

| Literature             | 25 W/in <sup>3</sup>   | 45 W         | 94.5% | flyback              | [69] |

| Literature             | 11.7 W/in <sup>3</sup> | 100 W        | 95.3% | PFC rectifier+LLC    | [72] |

| Literature             | 21.4 W/in <sup>3</sup> | 150 W        | 94.2% | PFC<br>rectifier+LLC | [76] |

| AN3233                 |                        | 150 W        | 91%   | PFC<br>rectifier+LLC | [79] |

| AN2749                 |                        | 40 W         | 80%   | flyback              | [80] |

| DEMO_5ASAG_60W1        |                        | 60 W         | 83%   | flyback              | [81] |

| DEMO-IDP2303A-<br>100W | 12 W/in <sup>3</sup>   | 100 W        | 88.3% | PFC rectifier+LLC    | [82] |

| ADP-65JH HBAN          | 15.5 W/in <sup>3</sup> | 90 W         | 84%   |                      | [83] |

| DPS-120AB-3            | 3.4 W/in <sup>3</sup>  | 120 W        | 88%   |                      | [84] |

The full bridge diode rectifier in the boost PFC rectifier causes high conduction loss. By integrating of the diode bridge and the boost PFC, the number of semiconductors in the line-current path is reduced. Thus conduction loss is decreased. Bridgeless PFC rectifier [85, 86] achieves lower parts count and higher efficiency by integrating the diode full bridge rectifier with subsequent PFC stage. There are several types of bridgeless PFC rectifiers, such as buck bridgeless rectifier[87], buck-boost bridgeless rectifier, bridgeless flyback rectifier [88], bridgeless SEPIC rectifier [89], [90] bridgeless Cuk PFC [91],[72] rectifier and bridgeless boost PFC [92],[93], [94], [92].

Buck type PFC rectifiers exhibit the above-mentioned disadvantages. The bridgeless buck PFC in [87] integrates a flyback into the circuit which helps improve the dead angle issue. But it increases the complexity of the circuit significantly. The measured PF is 0.95 and efficiency is below 90%. Bridgeless flyback rectifier in [88] suffers from high voltage stress on the main switch. The bridgeless SEPIC rectifier requires 7 passive components [89]. The bridgeless Cuk PFC is derived by integrating the boost PFC and LLC resonant converter. The advantages of this topology include isolation and step-up and down capability. The main issue of this topology is the high voltage stress on the main switches. In addition, a snubber circuit is required to avoid over voltage the main switch.

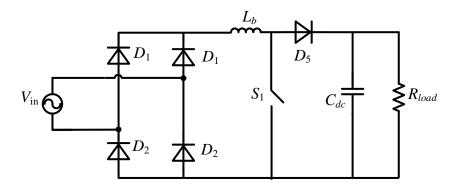

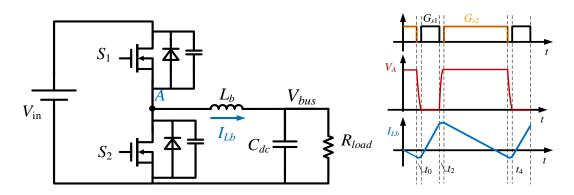

For non-isolated applications, the bridgeless boost PFC, shown in shown in Fig. 2.16 [86] has many merits including simple circuitry, high efficiency and achievable high PF and low THD with simple control. Compare with the conventional PFC rectifier in Fig. 2.15, two diodes are eliminated. As a result, there are always two semiconductors placed in the line-current path, resulting in reduced conduction losses. At the positive half-line cycle,  $D_1$ ,  $S_1$  and  $S_2$  form the current path. During the negative half-line cycle,  $D_2$ ,  $S_2$

and  $S_1$  start to operate. However, this bridgeless PFC rectifier has significantly higher common-mode noise than the conventional PFC boost rectifier [95], [96]. The operation at the positive half- line period when  $S_2$  has connected the output ground to the ac source is normal. But at the negative half-line period, the output ground is connected to the ac source with high frequency pulses. The amplitude of those pulses is equal to high bus voltage. Those high frequency voltage pulses charge and discharge the equivalent parasitic capacitance between the output ground and the ac line ground, resulting in the asymmetrical on the two half line period, eventually causing a high common-mode noise [92].

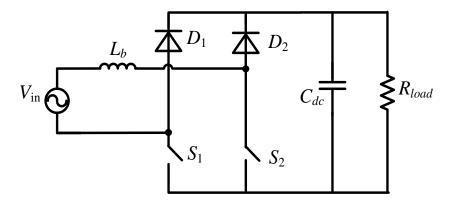

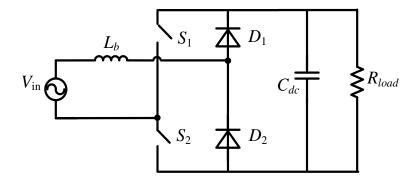

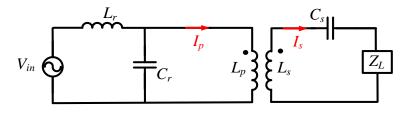

A modification of this original bridgeless rectifier is totem-pole rectifier as shown in Fig. 2.17. This totem-pole rectifier considerably reduces the common mode noise issue by exchanging the position of  $D_1$  and  $S_2$ . At the positive period, rectifier ground is connected to the ac source via  $D_1$ , at the negative period, ac source is connected to the constant positive bus terminal. Thus, the high frequency pulses on the ground as discussed above is eliminated. So, the common mode noise is reduced. Because of the low component counts, high efficiency and low common mode noise, this totem-pole rectifier has been widely investigated for the charger and data center power supply applications[93]. Recently Texas Instrument launched a reference design for 1.6 kW GaN based 1 MHz CRM interleaved totem-pole rectifier. This reference design achieves 98.7% efficiency at full load and 250 W/in<sup>3</sup> power density [61]. The adapter consists of a CCM front-end totem-pole rectifier and subsequent LLC resonant converter that achieves 94.5% efficiency in a 500 W prototype [97].

Fig. 2.16. Basic bridgeless boost rectifier.

## 2.2.2 High frequency resonant inverter

Class E and class D are two popular power amplifiers due to high efficiency and simple circuitry.

## A. Class E inverter

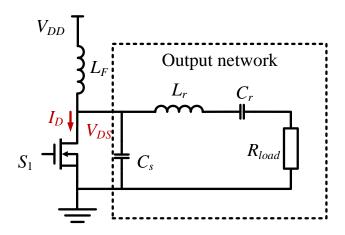

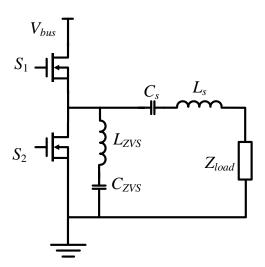

The schematic of Class E amplifier is shown in Fig. 2.18. It is comprised of a transistor and a load network. The transistor operates as an on/off switch and the load network shapes the voltage and current waveforms to achieve the lowest power loss via soft switching. The main advantage of class E amplifier is that it only consists of a single transistor and gate driver. Moreover, it absorbs parasitic capacitance of the transistor as a natural part of the operation.

However, it has many limitations.

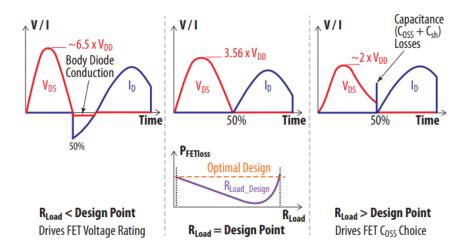

(1) The voltage stress on the switch is 3.56 times the bus voltage  $V_{DD}$  [98]. In practice, when the  $C_{oss}$  of transistor replaces  $C_s$ , the non-linear variation of  $C_{oss}$  with drain voltage can further increase the voltage stress across the semiconductor, reaching a value of almost 4.4 times the input voltage [99].

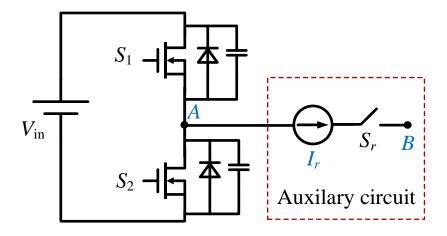

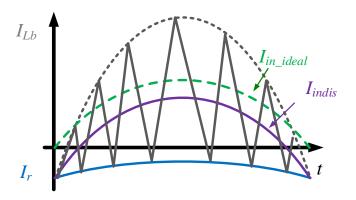

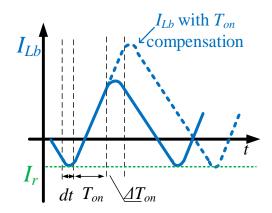

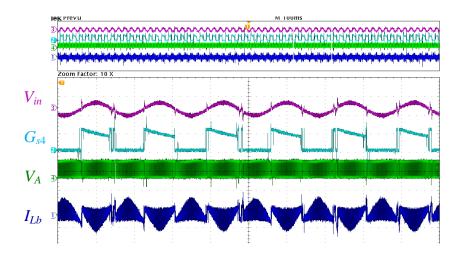

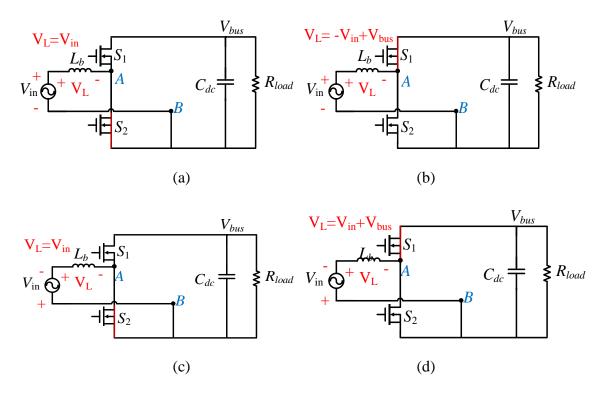

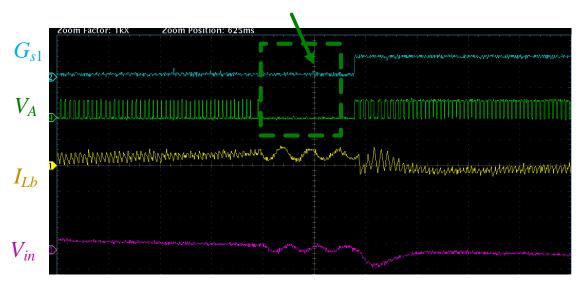

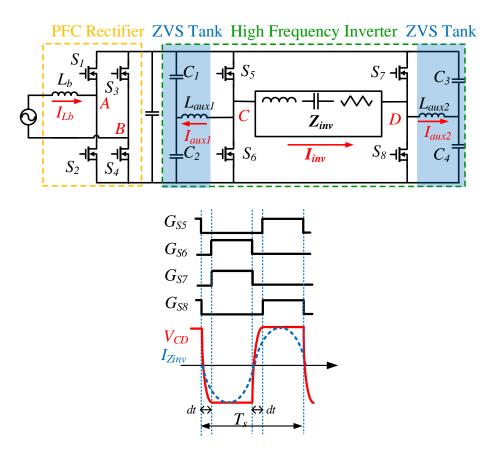

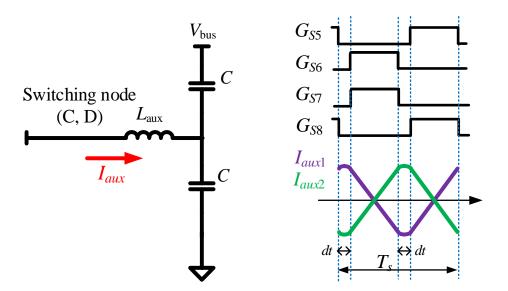

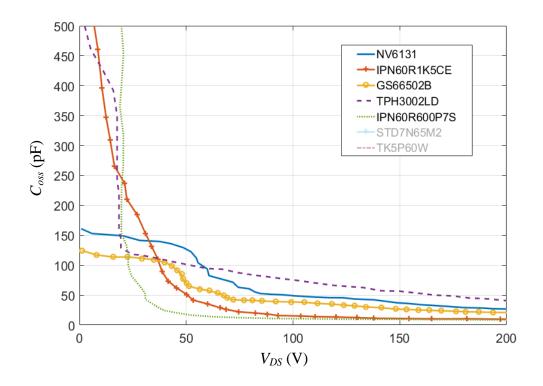

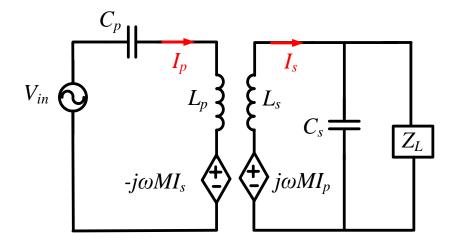

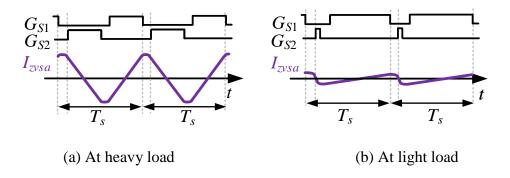

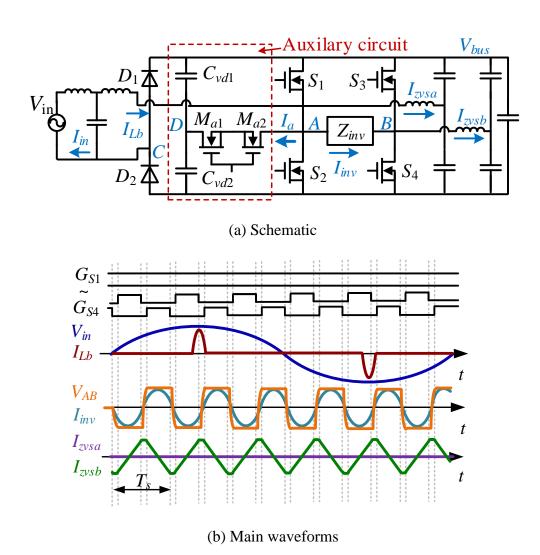

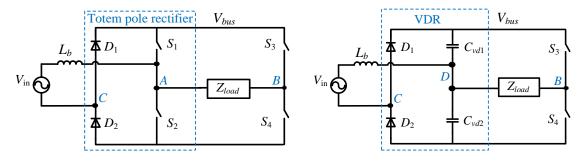

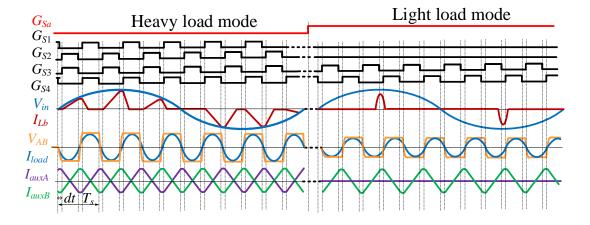

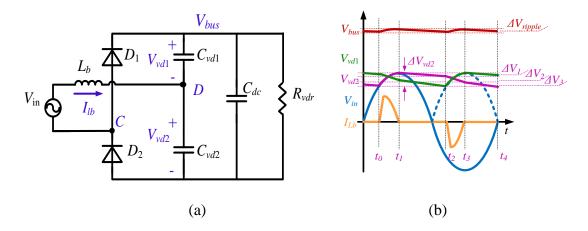

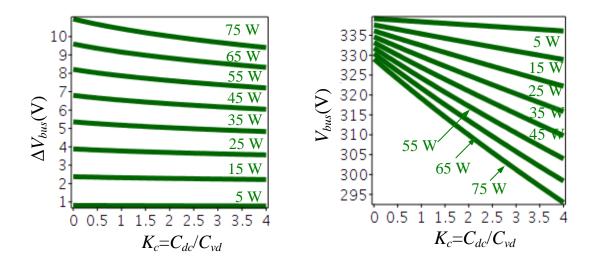

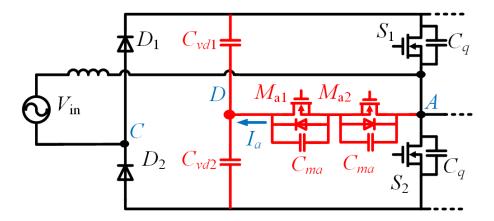

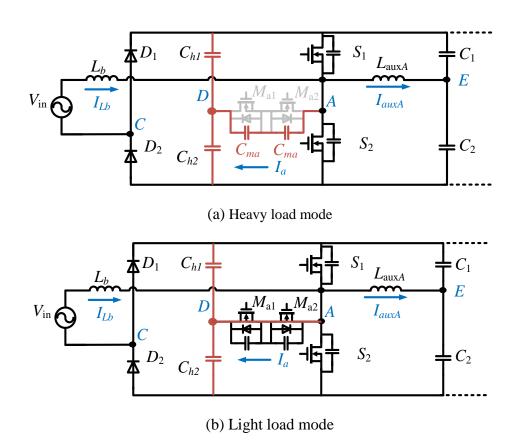

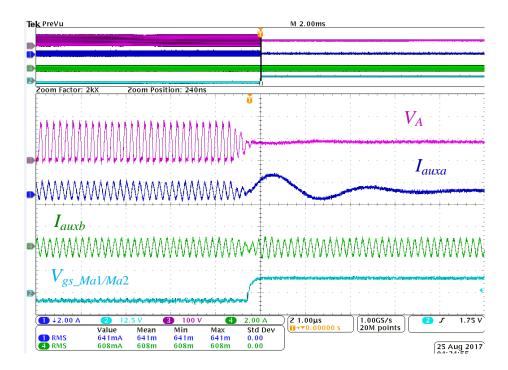

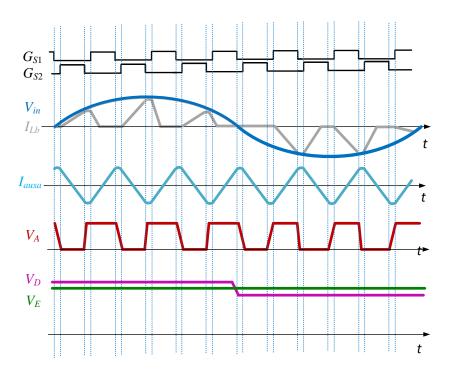

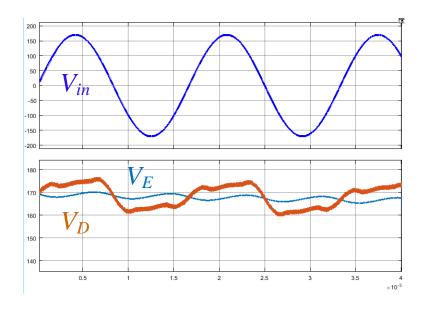

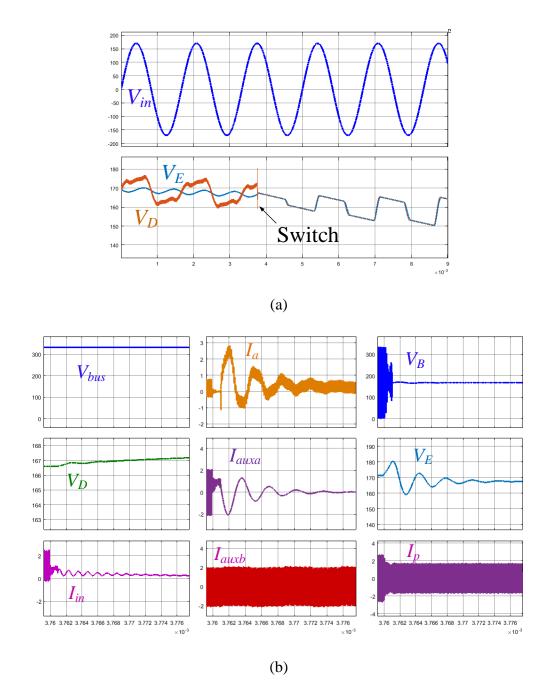

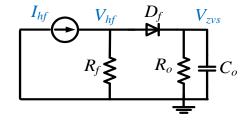

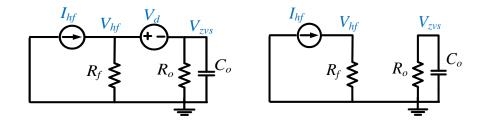

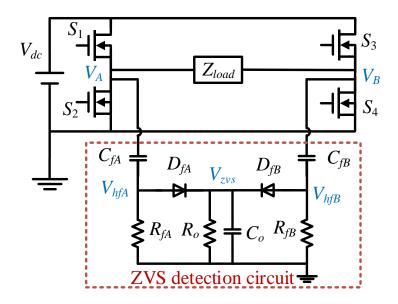

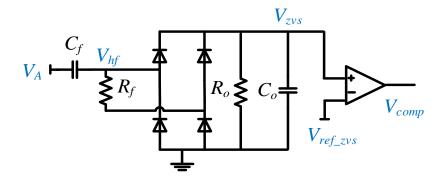

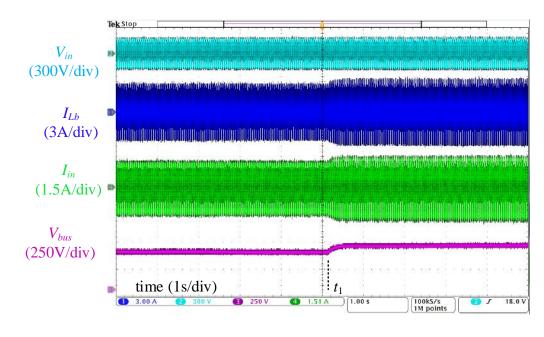

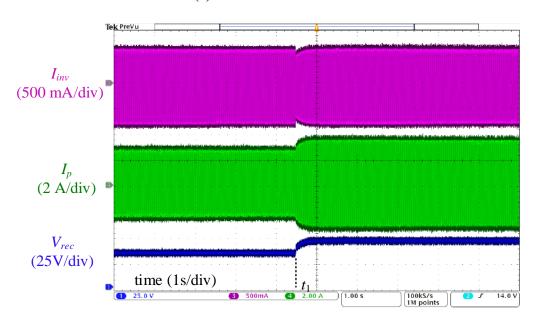

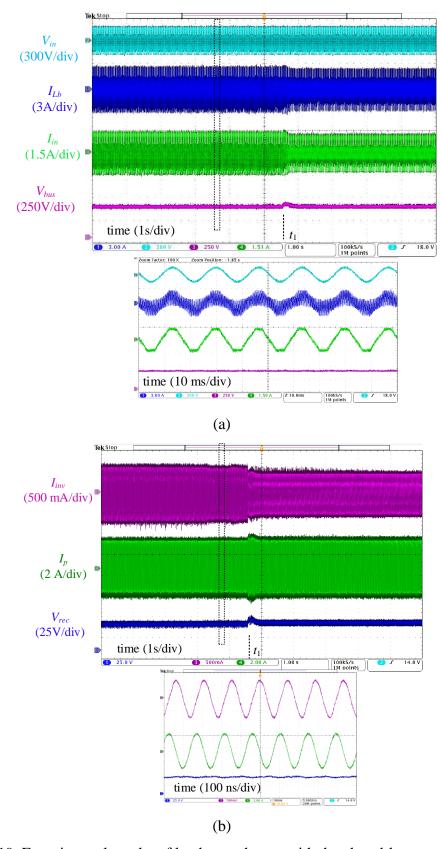

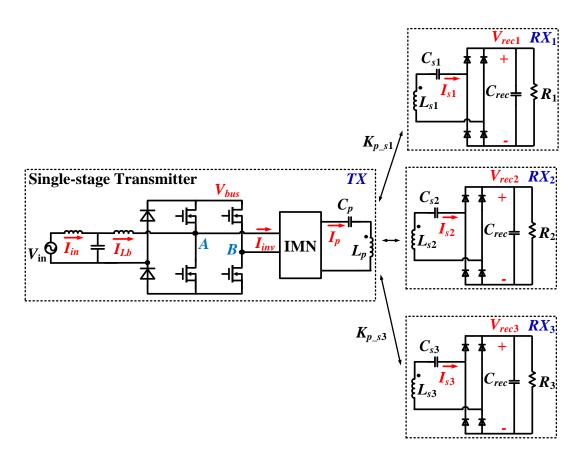

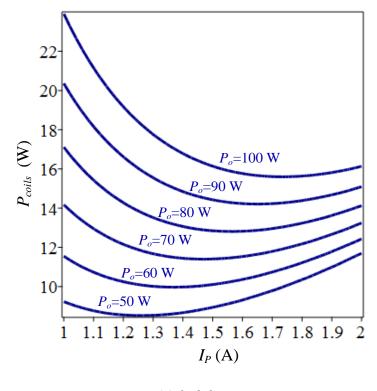

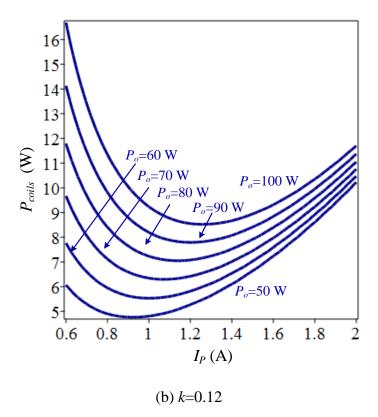

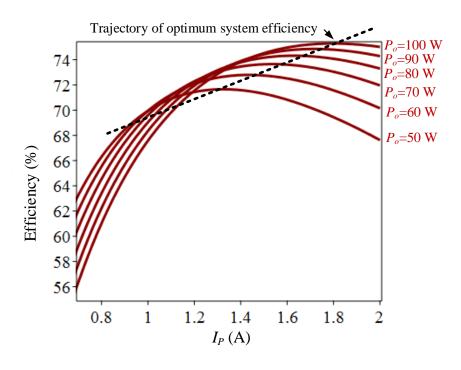

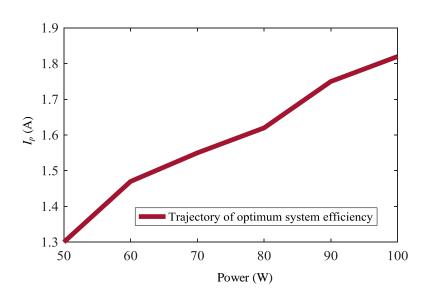

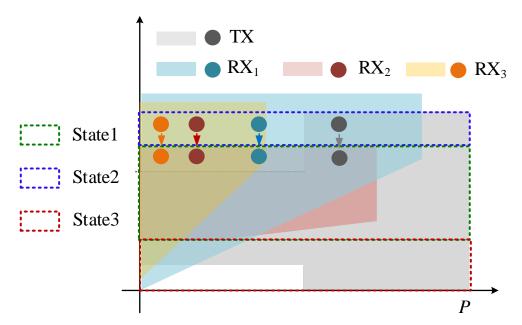

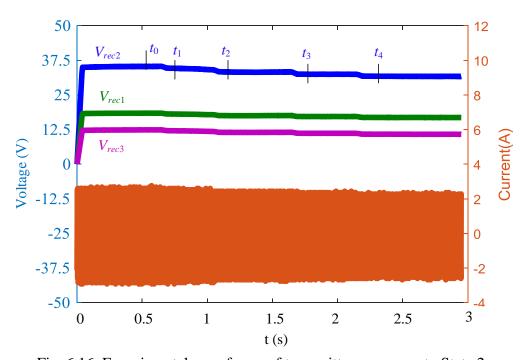

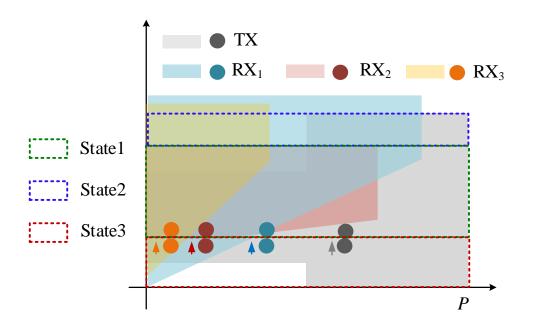

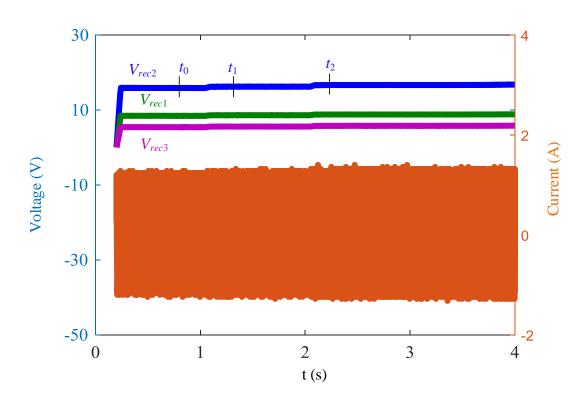

(2) The Class E amplifier is sensitive to load variation. To achieve high efficiency, ZVS is necessary for this class E amplifier. The output network is tuned inductively for a specific load for the soft switching operation. In loosely coupled WPT systems, there is load variation due to variation in the coupling between the transmitter and receiver, introducing changes in the load impedance seen by the amplifier, as shown in Fig. 2.19. When the load increases, the pre-tuned network changes from inductive to capacitive, therefore resulting in high switching loss. When the load decreases, it becomes more inductive and causes in high loss due to diode conduction.