## Doctorado en Ingeniería Electrónica

**Tesis Doctoral**

# **Contributions to Phase Two of AGATA**

## electronics

Autor:

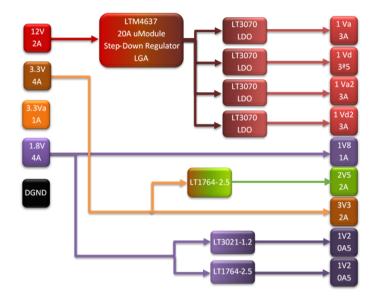

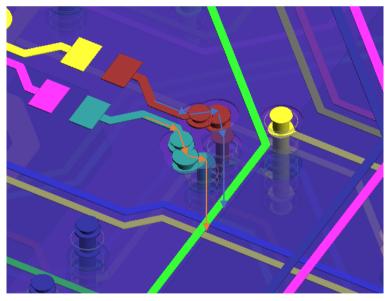

Javier Primitivo Collado Ruiz

Directores:

Vicente González Millán

Andrés Gadea Raga

Valencia, noviembre 2019

# Acknowledgements

I would like to start with a grateful thank to my supervisors Vicente Gonzalez and Andres Gadea, who first placed their trust in me to carry out this project, and supported in good and in the bad moments of its development. Only they have the best idea of the mountains we had to climb to carry out this thesis. I would like to thank also to the TEDRA team member Enrique Sanchis, who, together with Vicente accepted me to join them five years ago.

Furthermore, I would like to thank formally to the IFIC (Instituto de Fisica Corpuscular) CSIC and the University of Valencia for hosting me during my thesis period. The work of this thesis has been partially supported by the Ministerio de Ciencia, Innovación y Universidades Spain, under grants SEV-2014-0398, FPA2014-57196-C5 and FPA2017-84756-C4, by the European Commission FEDER funds and by the Generalitat Valenciana, Conselleria d'Educació, Investigació, Cultura i Esport under the grant PROMETEU/2019/005. Furthermore, I would like to thank to the Keysight Technologies Spain collaboration for the equipment for external board measurements on the Chapter 6.

I also like to thank to many members of the AGATA collaboration, in particular to the Phase 2 electronics development team, for the long discussions and joint hard work, without with this thesis would have never been feasible: Alberto Pullia, Amel Korichi, Erik Legay, Gustav Vinther-Jørgensen, Ian Lazarus, Laurent Charles, Nabil Karkour, Nicolas Dosme, Mos Kogimtzis and Xavier Lafay. Also I would like to thank to many others I meet from AGATA collaboration and worked together not mentioned before, especially with Diego Barrientos and Emmanuel Clement in Phase 1.

Me gustaría agradecer también a todos los con los que he compartido numerosas horas en el laboratorio TEDRA, ayudándonos los momentos más complicados: Xavi Egea, Jose María Blasco y Jose Manuel Deltoro. También añadir a aquellos con los que he compartido muchas horas en el IFIC y cuyas conversaciones han ayudado sin duda a avanzar en esta tesis: Fernando Carrió y David Calvo.

-|-

También agradecer al equipo de técnicos del IFIC y del departamento de Ing. Electrónica de la ETSE que me han ayudado en numerosas ocasiones. Sin olvidarse de aquellos a los que he codirigido trabajos fin de grado o han hecho sus prácticas con nosotros: Joel, con especial agradecimiento por la interfaz gráfica de test; Jorge y Agustin, por su inestimable ayuda en los test de la fuente de alimentación de la Fase 1, Miguel, Jose y Josep.

Ya a nivel más personal, me gustaría agradecer a mucha gente que me ha acompañado estos años y aportado en otros niveles. A los que conocí en Burjassot durante mi tiempo en la ETSE y el IFIC: Javi, Eva, Silvia, Gess, Ramón, Arnau, Carmen, Pablo, Delia, Manu, Jorge. A mi maestro, Toni Ruz y a toda la Escuela Nin Ruz Ryu: Raúl, Hector, Pablo, Alex, Raquel, Dani, Jose, Jorge.... Al grupo musical Oktopus, Guillem, Helder y Amparo, que me esperan pacientemente de mi descanso para terminar este texto. A los que me soportan todos los días: Víctor, Dimitri, Alex. Estefi, Iván, Jahna, Patri, Aarón, Carlotes, Roca, Andres, Alejandro y por supuesto todos los de LEDC que aún no he mencionado Juan, Dani, Mayte (y miniMay), Marco, Natalia, Paw, Natalia, Juanito, Lorena, Álvaro, Alvar, Iván, Víctor, Carlos, Marc. Sin olvidarse de los que están más lejos, pero siguen presentes y he visitado durante mis viajes en la tesis: Guillermo, Manu, Nieves, Pau, Mari Paz, Lucia, Jorge, Miguel Ángel. Con premio especial a quien más me ha sufrido últimamente con la tesis, Lorena. A mis compañeros de Recreación: Fernando, Vero, Elías y Ángela. A mis físicos dispersos por el mundo: Guillem, Alberto, Sara, María L., María G., Elena, Laura, Silva, Ana, Loli, Cristian, Carlos, Néstor.

Por último, a mi Familia, sobretodo mis padres, que nunca me han dejado ni dejarán de lado, a mi hermano Dani y a Hajni que me han apoyado en todo aun estando lejos y con especial atención a mi sobrina Luna, a quien dedico esta tesis.

-11-

## Abstract

In the field of Nuclear Physics, high-resolution gamma ray spectroscopy is an accurate method to perform nuclear structure studies, retrieving the energy and angular distributions from gamma photons emitted in the transition between nuclear states. In order to obtain the nucleus in an excited state, such that will emit gamma-rays, we are forced to collide matter, doing nuclear reactions (in the in-beam spectroscopy) or resort to the radioactive decay (decay spectroscopy). The High Purity Germanium (HPGe) semiconductor detectors have shown to provide good response as gamma-ray detector. As other semiconductor detectors, HPGe produce, with high sensitiveness, a current proportional to gamma ray energies while there are subject to high voltage inverse polarization, in cryogenic conditions.

The AGATA (Advanced GAmma Tracking Array) HPGe detector array is a state-ofthe-art detector array for the gamma ray spectroscopy technique in nuclear physics. In order to improve the sensitivity, AGATA HPGe detectors have the outer contact divided in 36 segments in order to determine photon position and energy deposited in each segment. With the interaction energy and position information is possible to reconstruct (Track) the gamma-ray interaction sequence using tracking algorithms. With such technique is possible to maximize the sensitivity of the detector array (energy resolution and P/T) without using part of the detection solid angle for the anti-Compton active shields. In addition to the segmented detectors, the positions sensitive HPGe arrays require sampling electronics with spectroscopic signal-to-noise ratios, which provides the traces to be processed by the Pulse Shape Analysis algorithms.

To provide maximum efficiency and sensitivity, the AGATA project aims to construct a  $4\pi$  solid angle detector array. This geometry optimizes as well the information obtained, something that is especially important in experiments using expensive radioactive ion beams. Another goal in the construction of AGATA is the mobility of the array. AGATA is installed in different laboratories to take advantage of the variety of beams and complementary instrumentation existing in different European centres.

-111-

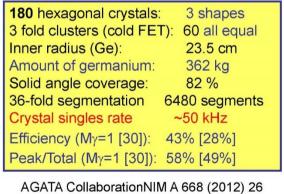

The AGATA project is currently in its Phase 1, using a second generation electronics, which aims at building a 1  $\pi$  solid angle coverage. This requires 45 detectors, that today are partly instrumented with the previous Phase 0 electronics, mostly design and produced in the period from 2005 to 2007. Presently, the main goal for the AGATA collaboration, regarding electronics, is the development of the Phase 2 version, with the objective of instrumenting 180 detectors, which is partly done by the work described in this thesis. The main improvements for this Phase 2 electronics are: the integration of all the electronics from digitizers to readout, including Pre-processing, in one standalone system and the use of Ethernet as the readout protocol. The Ethernet technology will enable a multipoint connection and the possibility to distribute the data anywhere within the AGATA processing farm.

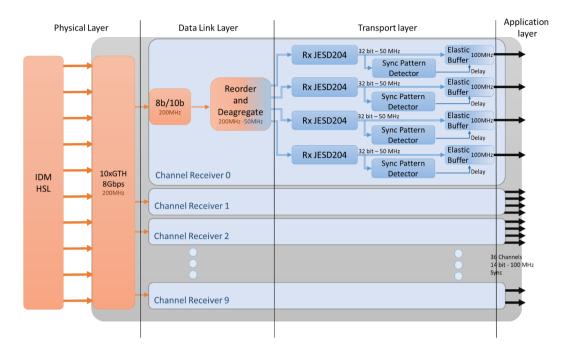

One of the main problems found in the integration of all the system is the optimization of the FPGA resources used in the Pre-processing. Despite of the increase in the high-speed transceiver data rates of the last FPGA developed in the industry, the number of transceivers on the devices is limited. Furthermore, the FPGA cost increases largely with the amount of transceivers, which is an issue for the AGATA detectors, with a need for a large number of transceivers but not at an especially high data rate. To reduce system complexity, cost and power, the number of high speed digital lines is optimized through data aggregation, increasing the speed data rate of each line but with a reduction of 4 to 1 in the total number of transceiver lines. The solution is carried out through the Input Data Mezzanine board, conceived and developed completely under this thesis work.

From a technological point of view, the main objective of the thesis is to prove the possibility of reading up to 40 optical or copper low rate inputs, using JESD204 or equivalent protocol, in the FPGA using only 10 transceivers through a time division multiplexing technique. The work is done with state-of-the-art in hardware-software FPGA design, high-speed digital design and digital communications, as well as with the knowhow of the AGATA current electronics. Although this device is designed for AGATA, we consider that this technology will be of interest for other instruments and applications.

-IV-

## Resumen

En el campo de la física nuclear, la espectroscopia de rayos gamma de alta resolución es un método preciso para estudiar la estructura del núcleo, extrayendo la energía y la distribución angular de los fotones gamma emitidos en las transiciones entre estados nucleares. Para obtener núcleos en un estado excitado y por tanto emitan rayos gamma, hemos de hacer chocar la materia, produciendo reacciones nucleares (espectroscopia de haz) o recurrir a desintegraciones radiactivas (espectroscopia de desintegración). Los detectores de semiconductor de germanio de alta pureza (HPGe) han demostrado tener una buena respuesta interaccionando con rayos gamma. Al igual que otros detectores de basados en semiconductores, cuando se los somete a alto voltaje, los detectores HPGe producen una alta corriente de medida proporcional a la energía de los rayos gamma incidentes.

El multi-detector HPGe AGATA (Advanced GAmma Tracking Array) es uno de los espectrómetros gamma de alta resolución más avanzados que existen dedicado al estudio de la física nuclear. Para maximizar la sensibilidad, los detectores HPGe de AGATA tienen los contactos exteriores divididos en 36 segmentos, de este modo se puede determinar la posición del fotón y la energía depositada en cada una de estas partes. Con la información sobre la posición y la energía de los fotones es posible reconstruir las interacciones de los rayos gamma a través de los algoritmos de tracking. Gracias a esta técnica, es posible maximizar la sensibilidad del detector (resolución energética y factor P/T) sin necesidad de utilizar parte del ángulo sólido de detección para otros detectores dedicados a la supresión del efecto Compton. Además de los detectores mismos, los detectores de HPGe sensibles al posicionamiento requieren una electrónica de muestreo con ratios señal a ruido de calidad espectroscópica, que capturen y digitalicen las trazas para ser procesadas por los algoritmos de análisis de forma de pulso (Pulse Shape Analysis).

Para conseguir la máxima sensibilidad y eficiencia, el proyecto AGATA busca construir el multi-detector cubriendo una superficie total con  $4\pi$  de ángulo sólido, optimizando la información obtenida, algo especialmente crítico en experimentos que usan

-V-

costosos haces de iones radiactivos. Otro objetivo en la construcción de AGATA es su movilidad. El multi-detector AGATA se instala en diferentes laboratorios para aprovechar la variedad de haces e instrumentación complementaria que existen en los diferentes centros europeos.

El proyecto AGATA se encuentra actualmente en su Fase 1, que busca cubrir hasta  $1\pi$  de ángulo sólido y se encuentra funcionando con la segunda generación de electrónica. Los 45 detectores instalados actualmente utilizan en parte la anterior generación o Fase 0 de electrónica, que fue diseñada y producida entre 2005 y 2007. El principal objetivo a nivel de electrónica en la colaboración AGATA es el desarrollo de la nueva generación para la Fase 2, que busca instrumentar 180 detectores y la cual se ha desarrollado parcialmente en esta tesis. Los principales objetivos de la electrónica para la Fase 2 son la integración de en un solo dispositivo, desde la digitalización hasta la salida de datos y el protocolo Ethernet como comunicación para dicha salida. La tecnología Ethernet permitirá una conexión multipunto y la posibilidad de leer los datos desde cualquier sitio de la granja de procesado de AGATA. También se han tenido en cuenta, en el diseño, facilitar el mantenimiento y evitar la obsolescencia de los componentes utilizados.

Uno de los grandes problemas que se encuentran en la integración del sistema electrónico de AGATA es la optimización de los recursos en la FPGA por parte del Preprocesado. Con el avance de la tecnología, a pesar del aumento de la tasa de datos por transceptores de alta velocidad en estos dispositivos (entre 16 y 32 Gbps), el número de transceptores en las FPGAs no se ha incrementado sustancialmente. Además, el coste de los dispositivos FPGA aumenta considerablemente con el número de transceptores. Esto es un problema crítico en AGATA, ya que requiere un gran número de canales digitalizados por dispositivo, pero no a una velocidad especialmente alta (sobre 2 Gbps). Para reducir la complejidad del sistema, el coste y la potencia total, el número de líneas de alta velocidad se ha optimizado mediante agregación de datos por multiplexado en tiempo, incrementando la velocidad de tasa de datos, pero con una reducción en el número total de éstas de 4 a 1. Esta solución se ha llevado a cabo a través de la tarjeta Input Data Mezzanine, concebida y desarrollada enteramente en esta tesis.

-VI-

El objetivo principal desde el punto de vista científico es demostrar la posibilidad de leer 40 canales bajo el protocolo JESD204 o uno equivalente, vía fibra óptica o por cable físico, únicamente con 10 transceptores de alta velocidad de una FPGA, gracias a la técnica de multiplexado por división en el tiempo. La base de la que se parte es la electrónica actual de AGATA y se apoya en tecnología del estado del arte sobre diseño hardware y software para FPGA, diseño digital de alta velocidad y comunicaciones digitales. A pesar de que este diseño se ha realizado principalmente para el proyecto AGATA, consideramos que esta tecnología será de interés para otros instrumentos y aplicaciones.

# Contents

| AbstractIII                                                           |

|-----------------------------------------------------------------------|

| ResumenV                                                              |

| Chapter 1: Technology in Nuclear Gamma-Ray Spectroscopy1              |

| 1.1 Nuclear Gamma Ray Spectroscopy1                                   |

| 1.1.1 Brief introduction to the Atomic Nucleus2                       |

| 1.1.2 Gamma radiation Interaction with matter5                        |

| 1.1.3 Detectors for gamma-ray detection in Nuclear Science6           |

| 1.1.4 High-Resolution Gamma-Ray spectroscopy and Germanium detectors9 |

| 1.1.5 In-Beam Spectroscopy11                                          |

| 1.1.6 Gamma Ray Detector Arrays and Tracking15                        |

| 1.1.7 The Gamma-ray Tracking Concept19                                |

| 1.1.8 AGATA The Advanced Gamma Tracking Array20                       |

| 1.2 Technology on the Edge23                                          |

| 1.2.1 High speed links23                                              |

| 1.2.2 Instrumentation technology27                                    |

| 1.2.3 Parallel processing and FPGA28                                  |

| Chapter 2: AGATA spectrometer electronics and Read Out                |

| 2.1 General description33                                             |

| 2.2 Detector preamplifier                                             |

| 2.3 Digitalization                                                    |

| 2.3.1 First generation (Phase 0) digitizer35                          |

| 2.3.2 Second generation (Phase 1) digitizer                           |

| 2.4 Pre-processing                                         | 42 |

|------------------------------------------------------------|----|

| 2.4.1 Triggering system                                    | 42 |

| 2.4.2 Energy processing                                    | 43 |

| 2.4.3 Comparison of the Phase 0 and Phase 1 Pre-processing | 46 |

| 2.5 Trigger and Synchronization system                     | 49 |

| 2.6 Data acquisition system                                | 52 |

| 2.7 Phase 2 electronics requirements                       | 53 |

| Chapter 3: AGATA Phase 1 Electronics Test System           | 55 |

| 3.1 Motivation and testbench                               | 57 |

| 3.2 Performed Tests                                        | 58 |

| 3.3 Software                                               | 60 |

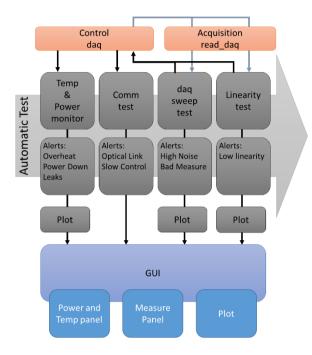

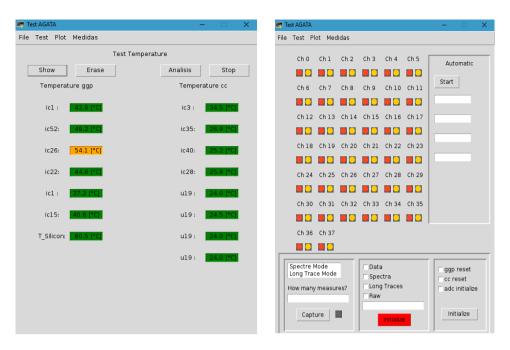

| 3.3.1 Stage I: Automation Code                             | 60 |

| 3.3.2 Stage II: Graphical User Interface                   | 62 |

| 3.3.3 Stage III: Standalone test upgrade                   | 64 |

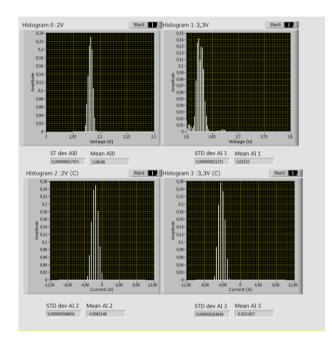

| 3.4 PSU analysis                                           | 65 |

| Chapter 4: AGATA Phase 2 electronics                       | 67 |

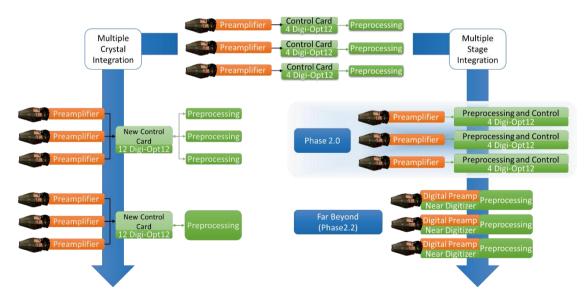

| 4.1 Goals for the Phase 2 Electronics of AGATA             | 69 |

| 4.2 Design of the AGATA Phase 2 Electronics                | 71 |

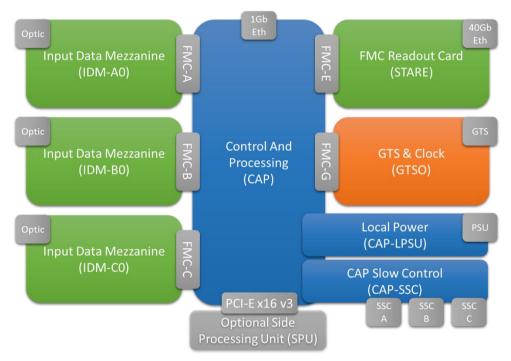

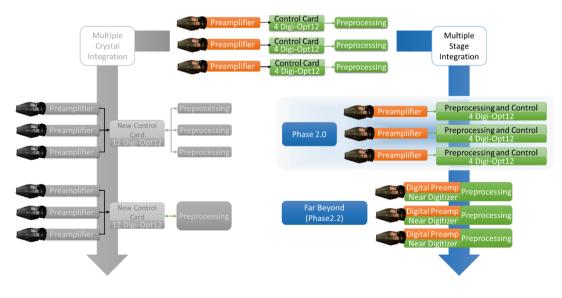

| 4.2.1 Preliminary PACE design                              | 71 |

| 4.2.2 The Phase 2 electronic collaboration.                | 72 |

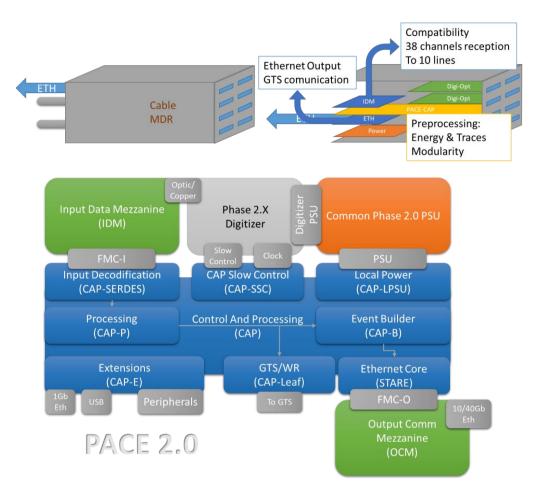

| 4.2.3 IDM prototype and PACE design                        | 73 |

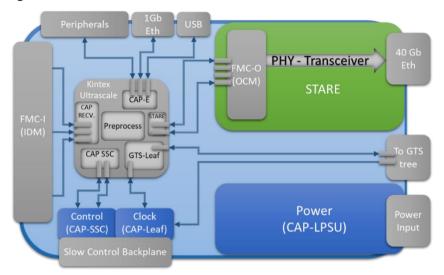

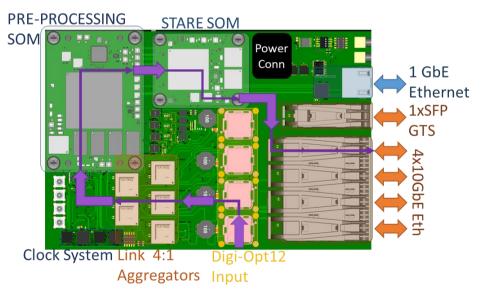

| 4.2.4 Description of the AGATA Phase 2 electronics         | 74 |

| 4.3 Production PACE design                                 | 79 |

| Chapter 5: Input Data Mezzanine Design                     | 81 |

| 5.1 Design requirements                            | 83  |

|----------------------------------------------------|-----|

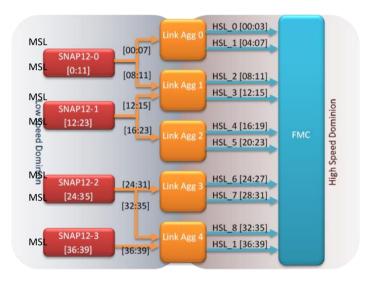

| 5.2 The IDM design                                 | 84  |

| 5.2.1 Input Area                                   | 85  |

| 5.2.2 Link Aggregator Area.                        | 86  |

| 5.2.3 FMC Output Area                              | 90  |

| 5.2.4 Control Area                                 | 91  |

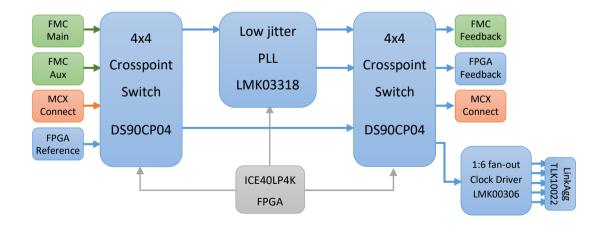

| 5.2.5 Clock Network                                | 98  |

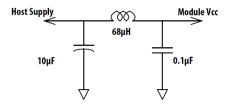

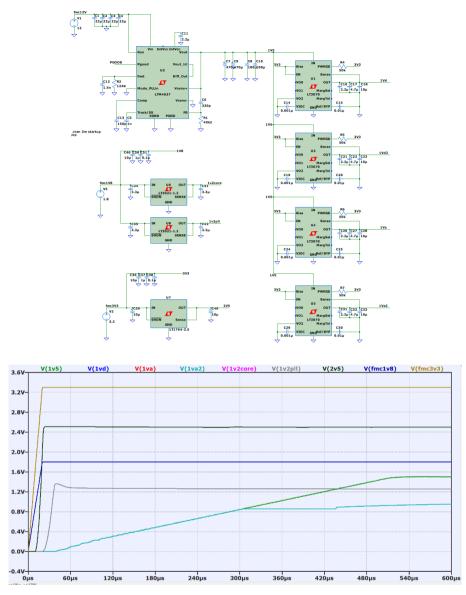

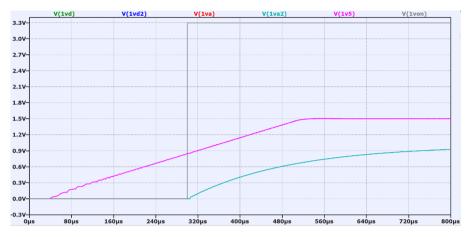

| 5.2.6 Power Supply                                 | 100 |

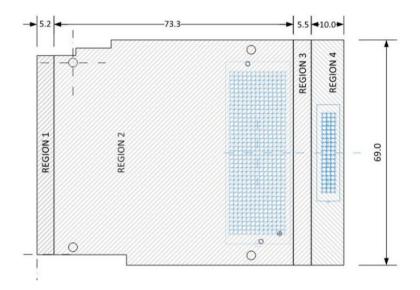

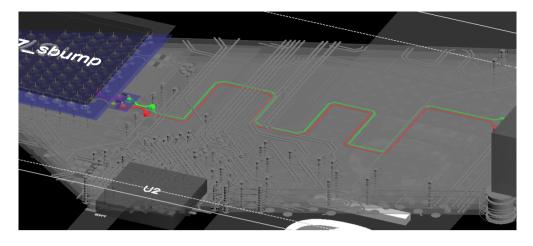

| 5.3 Timing and High Speed considerations           | 103 |

| 5.3.1 Design, Stack-up and materials.              | 103 |

| 5.3.2 Differential line design                     | 106 |

| 5.3.3 Synchronous clock networks                   | 108 |

| 5.4 Mechanical, Power and High Speed analysis.     | 108 |

| 5.4.1 Power analysis.                              | 108 |

| 5.4.2 Mechanical simulation                        | 110 |

| 5.4.3 High speed analysis                          | 111 |

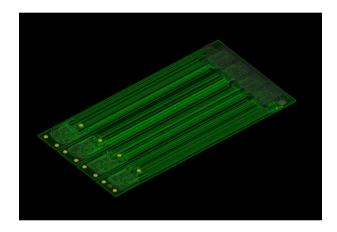

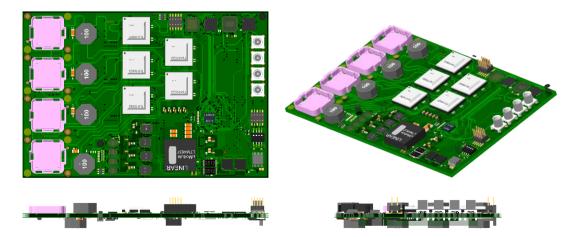

| 5.5 Layout and prototype production                | 113 |

| 5.5.1 Layout                                       | 113 |

| 5.5.2 Manufacture and prototype productions        | 114 |

| Chapter 6: Test and validation.                    | 117 |

| 6.1 Preliminary tests                              | 119 |

| 6.1.1 Test for IDM v1.2                            | 119 |

| 6.1.2 Test for IDM v1.3                            | 119 |

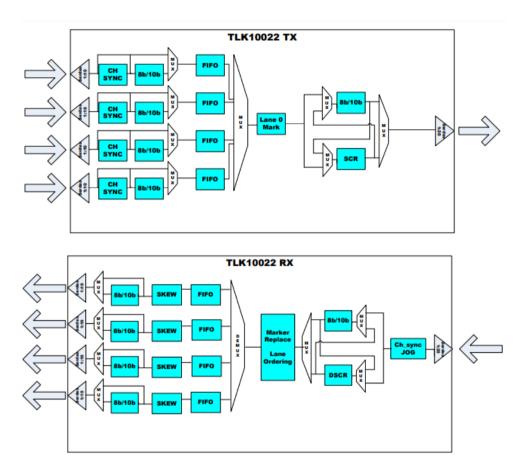

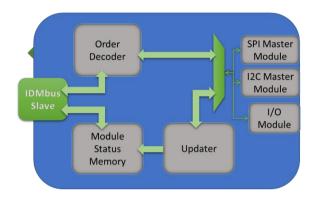

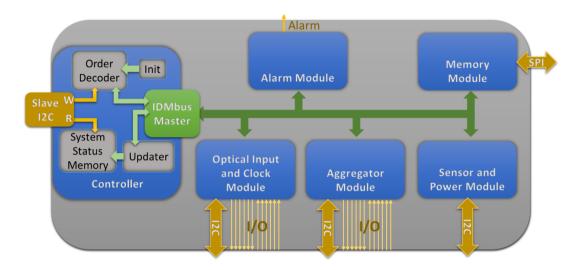

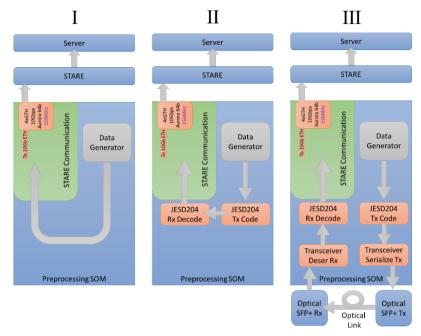

| 6.2 The data receiver firmware system for CAP-PACE | 120 |

| 6.2.1 The CAP Pre-processing firmware description120 |

|------------------------------------------------------|

| 6.2.2 The receiver module122                         |

| 6.2.3 Other Firmware modules127                      |

| 6.3 The IDM testbench128                             |

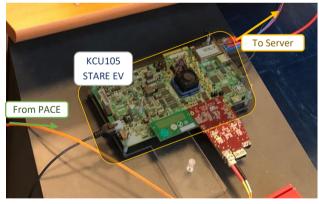

| 6.3.1 Testbench description128                       |

| 6.3.2 Verification of the data path131               |

| 6.4 The AGATA Phase 2.0 Electronics proof-of-concept |

| Chapter 7: Conclusions143                            |

| List of figuresXIII                                  |

| List of tablesXIX                                    |

| ReferencesXXI                                        |

| Appendix A XXIX                                      |

| Appendix BXXXI                                       |

| Appendix C XXXV                                      |

| Appendix DXLIII                                      |

Chapter 1: Technology in Nuclear Gamma-Ray Spectroscopy

### 1.1 Nuclear Gamma Ray Spectroscopy

The first experiment identifying high energy photons was carried out on November 1895, when Roentgen discovered the X-Rays with his experiments using cathode ray tubes [1]. Furthermore, the following year Becquerel demonstrated the existence of radiation with a photographic plate becoming darkened just with uranium salt and no sun exposure, being in this way the first radiation detector. Curie improved the detection with the piezoelectric effect of quartz and discovered radiation as general effect on matter in radioactive substances. [2]

Those discoveries lead to the idea of the nucleus in 1911 as the origin of the radiation, opening a new chapter of science thanks to the ideas about the structure of the nucleus from Rutherford and the experiments of Geiger and Marsden. Further experiments in 1940s and 1950s would reveal that nuclei are no longer the fundamental units of the universe as it was thought. [3]

The nuclear gamma-ray spectroscopy is the quantitative analysis of the photon spectra emitted by a nucleus. These gamma-ray photons, occurring during the transitions of the nucleons (protons and/or neutrons) between two quantal states in the nucleus, are on the very high energy side of electromagnetic spectrum. With gamma-ray spectroscopy techniques it is possible to measure basic nuclear properties of excited nuclear states such as excitation energy, angular momentum (spin) and parity using conservation laws and electromagnetic selection rules. In addition, the determination of decay probabilities of nuclear states (with lifetime measurements) gives direct information on the relationship between the initial and final states within the nucleus.

The many-body nature and the fact that it is formed by two types of fermions, characterizes the atomic nucleus as one of the most complex systems in nature. The advancement in the study of the nucleus and its complexity requires each time more accurate and complete information from the detectors that become our eyes into the tiny world of matter.

### 1.1.1 Brief introduction to the Atomic Nucleus.

Presently, the science vision of the matter is that it's compound of several fundamental particles, including the ones that were earlier thought to be and conformed the nucleus. Each element in nature, in whatever state, is compound by a central core called nucleus, with positive electric charge, and several electrons in quantized atomic shells with negative charge. These shells define many of its electrochemical or atomic properties.

The nucleus is responsible for the radiation saw by those early researchers and is composed itself by a certain number of particles, i.e. protons and neutrons. The number of particle in the nucleus is called mass number A, and, due to the fact that both particles have a similar mass, gives an approximate value of the total mass per nucleus. Protons have positive charge, and neutrons, with no electrical charge, are needed to stabilize the nuclei.

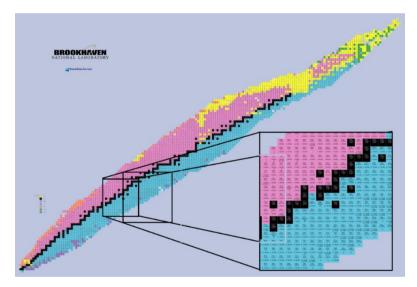

Fig. 1.1. Table of nuclides with the stable elements in black and for the other nuclides the colour indicates the type of decay (or radiation) happening in the unstable nuclei, i.e. red:  $\beta$ +, blue: $\beta$ -, orange: proton-decay, yellow:  $\alpha$ -decay, purple: neutron-emitters

The number of protons Z or atomic number, define the true name of the element because of its chemical importance. The number of neutrons N defines a series of isotopes, elements with identical chemical properties and name but with different amount of neutrons, with different nuclear properties, lifetimes and levels. This extends the periodic table set by chemical or atomic definitions to the table of nuclides, found on Fig. 1.1. There are around 3000 nuclei discovered, although only about 300 hundred are stable. They respond to particular characteristics like proton-neutron relation, magical numbers and presence of drip-lines, as well as other aspects as geometrical distribution (deformation) or the presence of collective rotational and vibrational states at the Fermi level [4].

Each non stable element will decay by emitting a Beta, Alfa, heavier particles or even, in extreme cases, neutrons or protons, transforming the nuclei into another element. The Alfa decay is an emission of the equivalent of a Helium nucleus (2 protons and 2 neutrons) from a heavier nucleus; the Beta decay is the emission of an electron ( $\beta$ -) plus and antineutrino or a positron ( $\beta$ +) and a neutrino. The positron (anti-matter partner of the electron) usually annihilates with another electron in the matter into two photons with the energy corresponding to the electron mass, i.e. 0.511 Mev [5].

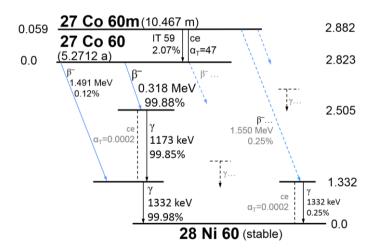

Fig. 1.2. Level-Scheme of Ni60 populated in the  $\beta$ -decay of Co60. [6]

In the decay of a nucleus, several excited nuclear levels can be populated on the daughter nucleus. This nuclear levels mostly de-excite to lower or fundamental energy levels emitting the energy difference as electromagnetic radiation, i.e. gamma-ray photons. Taking into account the nuclear shell structure, the transition energies are related to the nuclear shells (following the Pauli exclusion principle since protons and neutrons are Fermions) and give valuable information to understand the internal structure. The energy

of these photons gives direct information of the excited levels and their de-excitation, revealing themselves as specific energy peaks on the gamma ray spectra [3]. With energy levels and data from each nuclide, the decay (or de-excitation) level-scheme is elaborated as for example in the case of Co60 decay, shown in Fig. 1.2, representing the probability of decay for each level (the branching ratio) and type of radiation emitted in each decay.

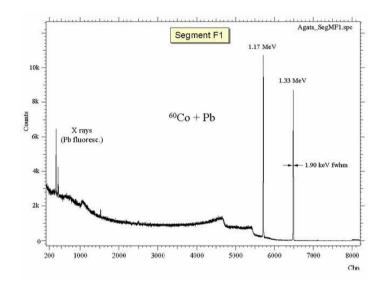

Fig. 1.3. AGATA calibration: Co60  $\beta$ -decay radioactive source measured Spectra, with the 1.17 MeV gamma emitted in the de-excitation of the state 4+ to 2+ and 1.33 MeV emitted in the de-excitation of the state 2+ to 0+ of Ni60. ©2004 IEEE.[7]

In order to extract this structural data and other possible information related to the excited level in the state of the nucleus, a proper detector is required. Furthermore, not only emission following radioactive decay of the nucleus, but also the emission of gamma-radiation by the products of a nuclear reaction or following excitation of a nuclear beam colliding to a proper target could give even more information about the nuclear structure. The development of detectors has been evolving in the last 50 years towards better energy resolution and analysis capabilities, as the ability to produce new reactions with the use of heavy-ion and radioactive-ion beam accelerator facilities, to fulfil a wide spectrum of nuclear states to study.

### 1.1.2 Gamma radiation Interaction with matter

To understand how to extract the maximum possible amount of information from the gamma rays emitted in an experiment, the knowledge of the interaction of gammarays with matter is of paramount importance. It is relevant not only to evaluate the detected radiation of interest, but also to recognize the unwanted sources of radiation that could degrade our measurements.

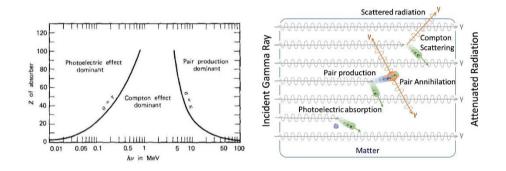

A photon of high energy which approaches matter, releases energy through three possible interactions. It could be fully absorbed by the atom and this will free an electron through Photoelectric Absorption, it can collide to an electron and share its energy in a Compton Scattering process, or, providing it has enough energy, create a positron electron pair in a Pair Production event. The probability of each one of these interactions to occur depends on the energy of the gamma-ray but also on the atomic number of the material the photon is interacting with. Let's describe briefly these three mechanisms.

Fig. 1.4. Left: Attenuation coefficients for gamma ray in relation with atomic number Z of absorber material. Right: Image representing the different interactions of gamma ray with matter.

*Photoelectric Absorption*: The photoelectric effect is dominant at low-energies of the gamma spectrum, and the energy is related to the incoming photon energy and the electron binding energy. The electron is ejected with the remaining kinetic energy from the unbind one. This secondary electron will release its energy by electromagnetic interaction with the medium.

*Compton Scattering*: This effect is dominant in the mid-energy range of the gamma spectrum (1-few MeV). The gamma ray transfers part of its energy to an electron as kinetic energy and a new photon with the difference of energies is generated.

*Pair Production*: the pair production effect is dominant at high energy levels of the gamma spectrum (>10MeV). The photons with energies above the mass of two electrons, and in presence of the nucleus electric field, can transform into a pair of electron and positron. The energy above the 1022 KeV, required for the pair production, is directly translated into their kinetic energy.

In Fig. 1.4 the interaction areas are depicted and from them we can understand their influence in our spectra. The low energy area has a decreasing Photoelectric Absorption, on the central part the Compton is the main mechanism and for the highest energies the pair production is dominant.

#### 1.1.3 Detectors for gamma-ray detection in Nuclear Science

The detectors in Nuclear Science profit from the properties of the interaction of the radiation with matter and sets-up specific conditions in an enclosed environment in order to generate a readable signal proportional to the energy of the incoming radiation. The detection is achieved in a vast amount of manners, depending of the kind of event or radiation, the sources and the energy range under study. Also different kind of detection systems can provide different information, from just decay rates to energies, position of the interaction or even characterization of the radiation received.

In the present section I will mainly concentrate in the detectors used for the detection of gamma radiation.

One of the early developed detectors was based on the effects of charged particles crossing a gas. The charged particles can be the entering radiation into the detector or can be produced within the detector material by, for example, an interacting gamma-ray.

This gas is ionized along the track of the particle and this ionization is collected thanks to a charged field. Depending on the charge collecting method, several types of detector have been developed. An Ionization Chamber collects charge through the electrodes generating the electromagnetic field in the gas. A second method is the proportional counter based on the fact that increasing the field in the gas generates a multiplication avalanche effect that increases the reaction effect compared to a single track. Another type of ionization chamber is the Geiger-Mueller Counter. In this case, higher electric fields are applied and a huge avalanche is triggered in the gas at each particle crossing. However, this method is only able to retrieve a value corresponding to the number of interactions but not to the energy of the particle due to the avalanche mechanism.

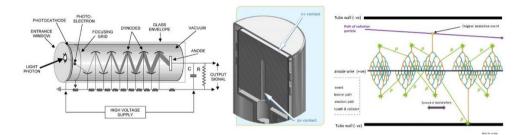

Fig. 1.5. Left: Scintillator and PMT diagram[8]. Center: Example diagram of a Camberra SEGe Coaxial Ge Detector. Right: Geiger Muller Counter diagram[9].

Another traditional technique to obtain information about the energy of a particle is the scintillation effect. The main function of scintillation materials is to transform the energy deposited by the radiation into detectable light. This light is collected and converted into electronic signals using photomultiplier tubes or photodiodes. The photomultiplier tubes generate electrons in a photocathode when photons hit it and the electrons colliding to the dynodes, placed sequentially increasing the positive potential, produce a multiplying cascade of electrons along the photomultiplier structure, generating a proportional current measured at the anode. In the case of the photodiode, the photons affect a semiconductor material taking advantage of the junction light absorption effect. As the output signal is proportional to the received radiation energy, scintillators are widely used in spectra analysis. The main disadvantage of scintillators materials for spectroscopy applications, as for example sodium iodide, is their poor energy resolution. The last technology that allows to detect gamma radiation is based on semiconductor diodes. When a semiconductor P-I-N doped structure (p+ doped-intrinsic-n+ doped) is reverse polarized, a fixed electromagnetic field is generated in the material. Any photon reaching the semiconductor will transfer its energy to electrons and positrons using one of the interactions described before. If the secondary electrons and positrons have enough energy, they will create electron-hole pairs in the intrinsic zone and the field forces them to move to the P and N electrodes. The bigger the energy the larger the amount of pairs created, being the charge proportional to the gamma ray energy. Due to the larger atomic number, Germanium is preferred to Silicon as semiconductor material.

Fig. 1.6. Nal(TI) scintillator spectra (A) and Ge(Li) Semiconductor spectra (B) comparison. Greater energy resolutions on the gamma ray peaks are observed on semiconductor device.[10]

The big disadvantage of Ge semiconductor detectors is related to the working temperature. At room temperature a noticeable amount of background noise is present due to thermal induced electrical currents. This problem is solved lowering the detectors temperature in cryostats, normally at liquid nitrogen temperatures (77K or -196 °C) [11].

Among the benefits of using Ge semiconductors, we have the size required for the same amount of retrieved energy because of their higher densities and their excellent energy resolution, due to the high amount of charge carriers (electron-hole pair) per incoming energy particle compared to gas or scintillators [12]. Approximately one ionization is produced per 3 to 5 eV of radiation in semiconductors (depending on the material) and about ~30eV for gases [10]. This leads to better energy resolutions and therefore higher sensitivity, still an order of magnitude better than scintillators. Among the semiconductor detectors, the excellent energy resolution of germanium (better than 0.2 % at 1.333 MeV) makes it the best gamma detector for high resolution gamma-ray spectroscopy studies.

# 1.1.4 High-Resolution Gamma-Ray spectroscopy and Germanium detectors

In the field of the Gamma-Ray spectroscopy the aim of the detector is to have an accurate map of the number of photons according to their energy. There are three main parameters that contribute to the detection sensitivity namely the detector efficiency, the peak-to-total ratio (equivalent to the signal-to-noise ratio) and the energy resolution.

The detector efficiency is related to the properties of the detectors used. Not all photons from an event interact in the active sensor material, and not all the photons interacting inside the active material are depositing their full energy. The first component of the efficiency is related to geometrical characteristics of the detector, in particular the solid angle  $\Omega$  from the gamma source subtended by the detector. The second component of the efficiency, the intrinsic one, is independent of the source to detector distance and it is related to the detector depth, the technology and active material [5]. The total efficiency  $\varepsilon$  can be measured as the number of events recorded divided by the number of radiation particles emitted by number of radiation particles incident on detector.

The second important parameter on spectroscopy is the Peak-to-Total (P/T) ratio, that is, the relation between the energy of the peaks in the active material and the total energy. This is a useful parameter to have an objective and independent measure and comparison of the efficiency regardless the laboratory and event conditions. It can be extracted through a measurement of the high-end peak of the differential pulse height spectrum, where all the information of high peak energies is stored [5].

The last element to take into account is energy resolution, i.e. the capability of detectors to define a single energy value peak. In the spectra, each monoenergetic pulse will be represented as a Gaussian peak added to the background and the rest of the spectrum. This pulse width at half height or FWHM will define the energy resolution of the detector and its standard deviation ( $\sigma$ ) is extracted from it. In the energy resolution is where semiconductor detectors, and Germanium in particular, have their best benefits.

In germanium detectors PIN structures, as in Silicon detectors, there is a limit on the volume of active material detector because of the impurities. These impurities create "electron traps" and capture electrons released from ionization. To limit this effect, the thickness of the semiconductor must be restrained to values below 1cm. There are two known solutions to overcome this limitation. The first one is to induce new forced impurities to generate enough electrons to be captured, compensating this way the effect of the intrinsic impurities. A second solution, only available after several years of technology improvements, is to refine the material to purify enough the semiconductor.

The first solution, developed in the early 60's, is carried out doping the Si or Ge with lithium by controlled diffusion [13], the resulting detectors being named as Si(Li) and Ge(Li) detectors. The main issue of the Lithium doped detectors is that, at room temperature, the diffusion of Li ions destroys the delicate compensation profile of the impurities, so the storage of the detectors has to be at low temperatures [14].

The second solution was first possible to manufacture in the early 70's and only for the Ge and this detector are called HPGe detectors (High Purity Germanium detectors) [15][16]. It's an expensive process and allows to grow up detectors of about 10-12 cm diameter [9]. Unlike the Ge(Li), the HPGe can be stored at room temperature, they have a faster and versatile production and less neutron-induced radiation damage [14].

The already mentioned ionization per eV takes the main part in this better resolution. Regarding the difference between Germanium and Silicon, Germanium is usually preferred due to the higher densities (Si: 2.33 g/cm<sup>3</sup>; Ge: 5.32 g/cm<sup>3</sup>), higher electron mobility (Si:  $2.1 \cdot 10^4$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, Ge:  $3.6 \cdot 10^4$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and hole mobility (Si:  $1.1 \cdot 10^4$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, Ge:  $4.2 \cdot 10^4$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), and lower energy per electron-hole due to the smaller band gap (Si: 3.76 eV, Ge: 2.96 eV) [17] resulting in a larger amount of charge per incident gamma ray. Additionally, the interaction cross sections for the relevant mechanisms, in our energy range of interest, depend on the atomic number (Z) of the detector material (photoelectric as Z<sup>4.5</sup>, Compton as Z, Pair Production as Z<sup>2</sup>) so the larger atomic number of Ge (Z=32) compared with Si (Z=14) is relevant for the intrinsic efficiency of the detectors.

### 1.1.5 In-Beam Spectroscopy

The In-Beam Spectroscopy is the technique to obtain the gamma emission energy spectra for a nucleus produced or excited in a reaction resulting from colliding nuclei. An ion beam colliding to a target is the main instrument to obtain excited states of the nucleus far from stability or with high spin states. The necessity to study nuclei further from stability has triggered the construction of Radioactive Ion Beam facilities, where the ion beam impinging into the target is composed of unstable nuclei.

A discussion of the characteristic of the reactions in necessary to understand the capabilities of the technique.

The atomic nucleus has tiny dimensions, in the order of several fm of radius. Therefore, most of the beam particles miss the target, which implies a small cross-section for the impact, in the other of 1 barn (10<sup>-28</sup> m<sup>-2</sup>). There are two main parameters that will define the possible outcome of the collision: the impact parameter b, as the distance between the two colliding nucleons centres in relation to the collision trajectory, and the kinetic energy of the incident beam of ionized atoms.

If the impact parameter b is too large in relation to the atomic radius, the two nucleus have a kinetic energy transfer mainly through the electromagnetic interaction, i.e. an elastic scattering with no nuclear excitation or nucleon exchange.

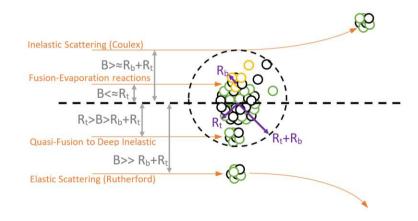

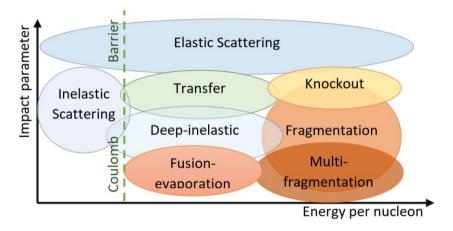

Fig. 1.7. A conceptual view of the possible results related to impact parameter B between beam and target nuclei.

With an impact parameter b approaching the sum of nuclear radius, reactions of interest for the in-beam spectroscopy start to happen. With low incident beam kinetic energy, and in case the parameter b is close enough to the sum of target and beam nuclear radius, there is an excitation without matter exchange in the collision, i.e. an inelastic scattering. The inelastic scattering can happen through the Coulomb interaction (Coulomb excitation), or, at smaller impact parameter it plays a role in the inelastic excitation. With slightly higher energies and smaller impact parameters b, transfer of nucleons is on-set, starting from the quasi-elastic, where few nucleons are transferred, until the Deep Inelastic regime is reached. In this transfer reactions the nucleons are moved between the two nuclei, resulting in new excited elements near both original A and N configurations of the projectile and target. [18]

Fig. 1.8. Representation of possible reactions in relation to energy beam and impact parameter.

At smaller impact parameters b, the nuclear fusion becomes possible, starting with the quasi fusion reactions to smaller impact parameters with Fusion-Evaporation reactions. In the case of fusion-evaporation reactions, both nucleons merge combining their masses, losing the memory of the original fused nuclei and some nucleons are usually evaporated in the process, since the compound nucleus is created at relatively high excitation energy. [19] The fusion-evaporation reaction is used to obtain excited high spins in neutron deficient nuclei of interest. To produce the fusion, the kinetic energy of the beam must overcome the Coulomb repulsion. As mentioned before, after the fusion, few nucleons are emitted by evaporation. Due to the availability of stable projectiles and targets for the nuclear reactions, in general, after evaporation, a neutron deficient metastable excited nucleus is created after 10<sup>-20</sup> seconds.

In general, the evaporation of neutrons and charged particle is followed by the emission of gamma-rays de-exciting the entry states of the reaction products through the complex excited level scheme. The de-excitation sequence reaches finally the so-called Yrast line, that represent the lower state energy level for each angular momentum, thus the de-excitation follows the Yrast line until the nucleus reaches the ground state. In limited occasions fusion evaporation or quasi-fusion can be used to study neutron-rich nuclei close to the stability line. In this case the detection of the evaporated or out-coming light charged particles is fundamental to select the reaction channel.

To study neutron rich nuclei, the multi-nucleon transfers and deep inelastic reactions can be used. Spectroscopy techniques using these reactions profit from the nucleon transference and the equilibration of the N:Z ratio happening on the reaction. Therefore, light to medium mass nuclei beam, against very heavy stable targets, gain neutrons after such reactions.

Reactions with sizeable higher kinetic energy beams than the ones studied before are dominated by fragmentation. With beam energies above 30 MeV/A (energy per nucleon) colliding to a target results in a loss of a number of protons and neutrons, with almost all momentum conservation on the beam nuclei. A whole family of possible nuclei are produced with different yields. There is a particular case of fragmentation when the b parameter is in the order of the nuclei radius called knockout, capable of stripping only one nucleon from the nucleus of interest.

Reactions with high energy beams combined with Fragment separator facilities are used in relativistic Radioactive ion beam facilities to obtain the secondary radioactive beam. In such facilities the in-flight Fragment Separator is used to select the desired nucleus and use it on a secondary reaction on a target placed at the separator focal plane position. The other use of projectile fragmentation is to directly study long lived excited states, with detectors at the end of the separator. These type of Radioactive Ion Beam facilities are called In-Flight facilities.[20]

Another reaction at relativistic energies, used in in-flight Radioactive Ion facilities, is the induced projectile fission. It is performed with heavy beams, for example <sup>238</sup>U, impinging, in general, on light target, causing the fission of the heavy nuclei. The resulting fragments beams are mass separated and selected, like in the fragmentation production method, to be used for secondary reactions. The secondary reactions in In-Flight facilities are exclusively in inverse kinematics and with large  $\beta$  (~ 50%), like relativistic coulomb excitation, knock-out reactions, fragmentation, etc.

The fragmentation is not the only production method used in the facilities for the production of radioactive ion beams, the Isotope Separation On-Line (ISOL) method is as well widely used. The ISOL method consists in generating the radioactive ions from whatever reaction, in general at lower energies, to have them reaccelerated after selection using magnetic separators or Laser Ionization techniques.

The drawback of the ISOL technique is that the time necessary for the ion selection, charge breading and acceleration, places a lower limit on the lifetimes of the radioactive nuclei to be used. The ISOL facilities provides beams to be used in direct and inverse kinematics reactions, with  $\beta \approx 10\%$ , as coulomb excitation, transfer reactions, deep inelastic, etc.

#### 1.1.6 Gamma Ray Detector Arrays and Tracking

The experimental investigation of the nuclear structure, using gamma-ray spectroscopy techniques, requires as a first step to obtain a nucleus in an excited state, such that in the de-excitation process electromagnetic radiation is emitted. This can be realized in two ways: first using nuclear reactions that obtain a reaction product in an excited state or excites the beam o target nuclei. The second option is to obtain an unstable nucleus in the ground or isomeric state that will later decay to excited states in the daughter nucleus.

The selection of the experimental set-up and the laboratory to perform the experiment is strongly dependent on the kind of measurement and the nucleus to be investigated.

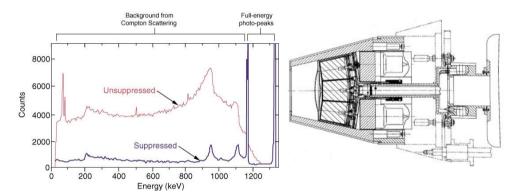

*Fig. 1.9. Left*: *image representing the effect of suppression on Germanium arrays.*[21]. *Right*: *Euroball cluster detector.*

State-of-the-art nuclear structure studies are dealing with nuclei very far from the stability line (many of them of relevance for the nucleosynthesis processes) or with very exotic states in nuclei closer to the stability, that might reveal new symmetries in the effective nuclear Hamiltonian. Gamma-ray spectroscopy in such cases requires advanced instrumentation as the Ge Detector Arrays, frequently coupled with complementary instrumentation in order to reveal the reactions channel, to track the trajectories of the moving nuclei or even to help performing measurements that can't be done only with the Ge detectors.

The second important aspect about these measurements is the laboratory, able to produce the nucleus in the state of interest. Presently the most interesting laboratories are the ones providing accelerated high-intensity beams of stable ions as well as Radioactive ion-beams (RIBs) produced with the ISOL or in-flight techniques. Europe provides, or will provide, some of these world-class laboratories as the in-flight facility FAIR (GSI, Darmstadt, Germany) [19] providing RIBs at relativistic energies, the ISOL Laboratories HIE-ISOLDE (CERN, Geneva, Switzerland) [20], SPIRAL2 (GANIL, Caen, France) [21], SPES (INFN-LNL, Legnaro, Italy) [22], that are providing or will provide RIBs beams at the Coulomb barrier energies or slightly above. There are other such facilities all over the world: FRIB (NSCL/MSU, Michigan, US) [23], ISAC-II (TRIUMF, Vancouver, Canada) [24] and RIBF (RIKEN/Nishina Center, Saitama, Japan) [25], etc.

In this section we will discuss the HPGe detector arrays, their history and finally the development of the advanced Tracking arrays of HPGe detectors.

Regarding the energy resolution for the gamma-ray measurements, we have already discussed that the best capabilities are on the HPGe detectors, due to near 0,2 % energy resolutions achieved at around 1 MeV gamma-ray energy. Therefore, the next parameters to optimize are the efficiency and the Peak-to-Total ratio (P/T). For this purpose, the germanium arrays were developed.

First, the large angular coverage by including in a set-up a large number of HPGe detectors, results in a larger efficiency. Moreover, the Compton scattering highly dominates the energy region of interest in Ge detectors and many of the scattered gamma ray scape from germanium active detector volume, with a low peak-to-Compton ratio. The first solution is to grow larger Ge crystal with HPGe to include the scattered photons, but this is limited by the semiconductor growing technologies, and the second one is to incorporate the Compton suppression shield to the bare Ge detector. With such a shield, initially build of NaI(TI) scintillator, the scattered gamma ray from Ge are detected on the surrounding a NaI(TI) scintillators. In the early small volume Ge detectors, improvements of a factor of 10 where achieved on the P/T values for Compton. [14]

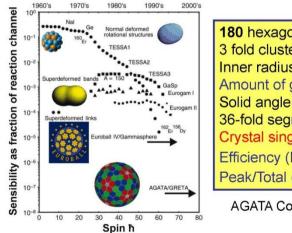

The first gamma array with suppression was built in 1980 and it was called TESSA. The detector achieved a P/T of 60% with 5 Ge(Li) detectors and NaI detectors tubes for suppression. The amount of detectors in the array was strongly limited because of the solid angle used by the Compton suppression shield. Later, the HERA spectrometer was built with major improvements including the use of HPGe as an advance for germanium detector and BGO (Bi<sub>4</sub>Ge<sub>3</sub>O<sub>12</sub>) scintillator as improvement for shielding. This detector was built with 21 HPGe + 44 BGO detectors deployed around the reaction target and reaching a 1.5% fullenergy absorption (peak) efficiency for 1 MeV gamma-rays. After this achievement, several arrays were built with the same techniques with around 12-40 Ge detectors and reaching about 3% of peak efficiency at 1 MeV gamma-ray energy.

After the explosion in the number of detectors, the scientific community, by the end of 1980s, proposed to build a full sphere detector with  $4\pi$  solid angle covering. This resulted in the construction of EUROBALL [22] detector in Europe and GAMMASPHERE detector [23] in USA, thanks to the work of big collaborations with multiple institutes involved. The GAMMASPHERE was developed in only one phase and was built with 110 hexagon detectors with BGO shielding covering 95% of  $4\pi$ . Nevertheless, the HPGe peak efficiency of the GAMMASPHERE was 10% and the P/T was about 50%.

The European project had a several step approach, GASP (Legnaro, Italy) and EUROGAM II (Dalesbury, UK + France) with 40 Ge covering 80% of  $4\pi$  resulting in 3% fullenergy efficiency and 54 Ge resulting in a peak efficiency of 3% or 5.8% in its two configurations. These detectors were the preliminaries to EUROBALL, introducing its encapsulated cluster detector, a 7 packed germanium detectors in the same cryostat merged in a hexagonal form to fit the sphere (see Fig. 1.9). The EUROBALL detector was built in steps upgrading EUROGAM II to EUROBALL III and later to EUROBAL IV. The final configuration had similar capabilities as GAMMASPHERE with 253 detectors and a peak efficiency between 7 and 10%, depending on the experimental conditions.

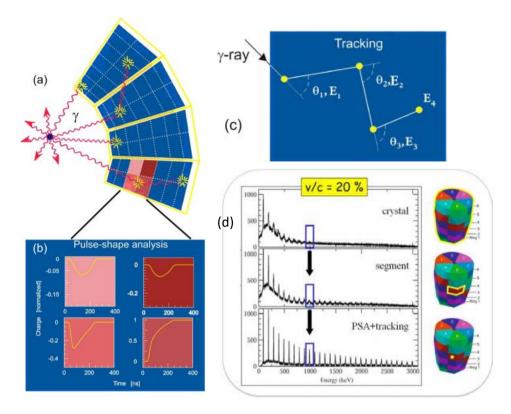

Fig. 1.10. a: Example of a gamma ray impact on several segmented sectors of HPGe. b: representation of the signals on each of the segments. c: gamma tray path for tracking techniques. [21] d: AGATA P/T signal demonstration for each part of the tracking algorithm.

Nevertheless, EUROBALL and GAMMASPHERE were not the end of the journey and a new idea came up and was developed at the turn of the millennium. The Compton suppression technique provided excellent peak-to-total (signal to background) ratios but reduced the solid angle covered by the Ge detectors, thus limiting the sensitivity of the arrays.

An European Commission financed initiative, the TMR network 'Development of gamma-ray tracking detectors' [24], taking place during the period 1996 to 2001 encouraged the development of the highly segmented position sensitive Germanium detector technology. This technique applies the so-called Pulse Shape Analysis (PSA) that uses the shape of the charged and induced (in neighbouring segments) signal, in highly segmented Ge contacts, to locate the position where the gamma deposited its energy [25].

The inception of the Ge position sensitive detectors technology has opened the possibility to build arrays of detectors based on the  $\gamma$ -ray tracking technique [26], providing an unprecedented level of sensitivity and efficiency.

Fig. 1.10 represents the path of the photons over a position sensitive Ge detector and the corresponding signals from the segments. Only two arrays with such technology are being built in the world, the European implementation of the tracking array is realized in the AGATA project. The second one, also under construction in the U.S.A., is the GRETA array [27].

## 1.1.7 The Gamma-ray Tracking Concept

The gamma-ray tracking process requires position sensitive semiconductor Germanium detectors. The technology of the position sensitivity, that requires segmented contacts in the detector and was developed in the mid 90's, is based on the early works on the E. Gatti, et al. [28] on the signal evaluation of multi-electrode detectors. This position sensitivity is achieved applying the Pulse Shape Analysis technique to the charge as well as to the induced signals in the segmented contacts of the Ge detector.

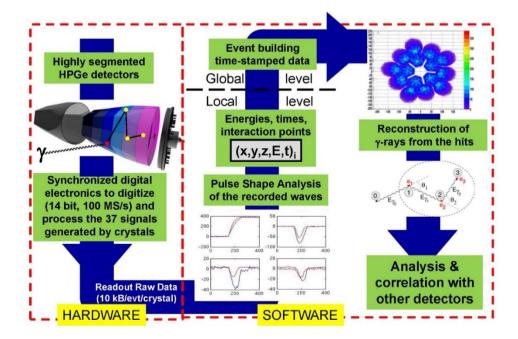

Fig. 1.11. Scheme showing the gamma-ray tracking concept differentiating between the hardware and software parts.

The position resolution depends strongly on the capability to understand the charge and image (induced) pulses for the detectors [29]. The complex Pulse Shape Analysis that is required can only be done using the sampled pulses of the detector, therefore the digital sampling electronics is playing a major role in the design and construction of such Tracking arrays. The digital hardware and software paths are depicted in Fig. 1.11.

As mentioned before, the digital sampling electronics is a fundamental part of the tracking arrays. Nevertheless, the signal processing starts with the low-noise spectroscopic charge amplifier. On Chapter 2 a more advanced overview of electronics for tracking arrays is explained in the context of AGATA spectrometer.

## 1.1.8 AGATA The Advanced Gamma Tracking Array

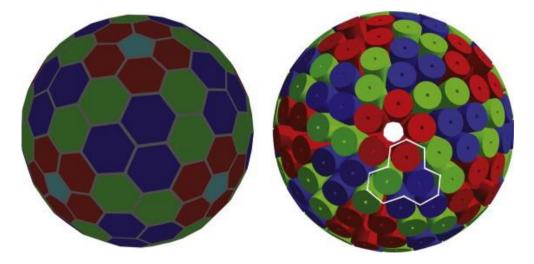

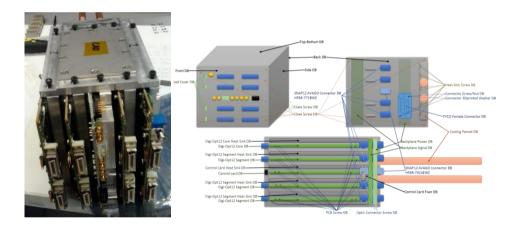

The Advanced Gamma Tracking Array is a spectrometer array developed by a huge European collaboration from 12 countries and more than 40 institutions and Universities [30]. The detector is an array of position sensitive HPGe crystals. Each piece is segmented in 6 layers in depth and 6 pieces per depth layer (for a total of 36 segments). To increase the overall geometrical efficiency, it is designed as 180 detectors over a whole sphere covering  $4\pi$  srrad of solid angle. Several studies were done in the initial phase in order to optimize the geometry using the technique of tiling the sphere Fig. 1.12 [31].

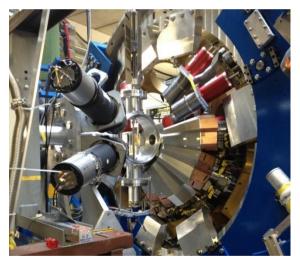

Fig. 1.12. The AGATA 180 detectors tiling of the Sphere and construction of the triple cluster. [32]

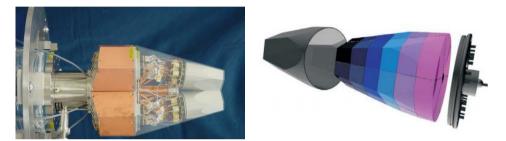

The final form is composed of a series of triple clusters and of asymmetric detectors in a particular geometry. This geometry maximizes the solid angle and lets only one hole for the accelerator beam pipe. Each triple cluster is built with a cryostat for cooling and preamplifiers placed between the cold and warm part [33], an example can be found in Fig. 1.13. The AGATA detector is designed to be built progressively in several phases. For the present one, Phase 1, the agreement in the collaboration was to build up to  $4/3\pi$  or, equivalently, 60 encapsulated detectors (20 triplets) until 2020. Phase 2, with the MoU under preparation, is aiming to complete the array.

Fig. 1.13. Left: The AGATA detector cryostat. **Right**: The AGATA detector segment distribution.[34]

AGATA is being built with the expectation, obtained with Monte-Carlo techniques and simulating the PSA and Tracking processing, to gain about 2 orders of magnitude in sensitivity with respect to the previous European array EUROBALL (see Fig. 1.14).

Fig. 1.14. AGATA sensitivity compared with previous arrays and AGATA design specifications.

The development is carried out taking into account the possibility to move the array to several laboratories around Europe to take advantage of the different beams and experimental possibilities in high-intensity stable beams and RIB facilities. For this reason, the newest technologies are used to integrate as much as possible and shrink the detector size on all of its areas: electronic, power supplies, processing, etc.

Since the collaboration started the construction of AGATA, the existing detectors have been used to perform experimental campaigns with smaller sub-arrays. On its last experimental campaign in 2019 at GANIL (Caen, France) AGATA used up to 45 detectors and until now it has been working together with many ancillary detectors such as NEDA, NWALL, DIAMANT, MuGAST and VAMOS [35] (see Fig. 1.15). Before going to GANIL, AGATA was placed in GSI (Darmstadt, Germany) [36] coupled to FRS in 2012-2014 and years before, the first place where it was assembled and tested was LNL (Legnaro, Italy) [37] in 2010.

Fig. 1.15. AGATA with 35 detectors coupled to NEDA, DIAMANT and NWall [30]

Until now, the AGATA spectrometer and its collaboration have produced more than 50 scientific publications in nuclear science and related areas and more than 80 publications in technical areas. Nevertheless, the detector is not already completed, and the next phase of development is creating expectations for the opening of possibilities with such instrument. The final approach to  $4\pi$  needs great efforts in the technical side due to the amount of channels to be processed and computing capability required for PSA, tracking and global synchronization. This is leading the collaboration to its Phase 2 of development relying in the new developments on the edge of technology.

# 1.2 Technology on the Edge

The electronic technology advances and the Nuclear Science take advantage of new elements to increase performance maximizing the scientific outcome. On the digital age, every information read from Nature has to be digitalized and codified and the main objective required by modern nuclear instrumentation is to acquire the maximum amount of information of an experiment with the current technology.

The detection of a full event demands high speed data and bandwidth throughputs before, or even after, the triggering system data reduction. The other relevant element for communication technology is the number of those high speed channels for detector arrays, even more demanding in the case of position sensitive highly-segmented detectors arrays.

In any detection system an information of paramount importance is related to the time in which the detection occurs, so a timing system is required to synchronize all the elements of the detector array.

Another area where technology improves the performance is on the processing capabilities and system control. Such a complex detector with a high number of electronics channels and several steps of parallel high speed processing, require an automation and control system able to cope with all the actions required to configure, start and stop the detection process and control each part from a user friendly point of view.

#### 1.2.1 High speed links.

On the field of high speed electronics, the technology has evolved into multi-Gbps links in the last decades [38]. The Ethernet 40G-100G [39] and Interlaken 400Gbps [40] became a standard in use in the computing and communications industries. Each of the single links of these high speed lines work at speeds between 10 and 40 Gbps. In order to

reach these data speed rates over long distances, optical lines and transceivers are used, moreover, the techniques of high speed PCB manufacture procedures and components for integrated circuits construction are fundamental.[41]

#### **Optical Lines**

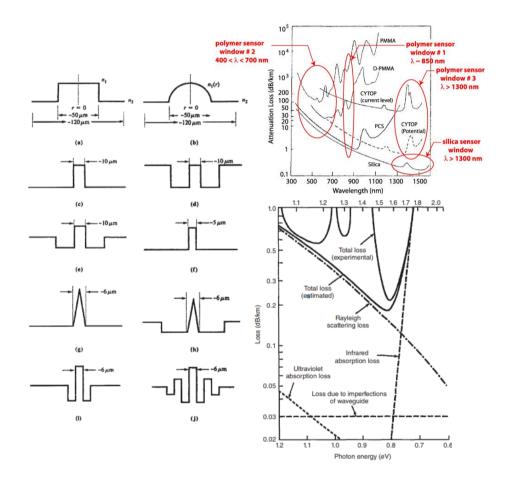

The optical lines are one of the main development area in the communication industry. There are several possibilities to transmit data through a controlled index wave guideline, as well as several methods to generate the optical light signal and retrieving it.[42]

Fig. 1.16. Left: Refractive index profiles of (a) step-index multimode fibers, (b) graded-index multimode fibers, (c) match-cladding single-mode fibers, (d, e) depressed-cladding single-mode fibers, (f–h) dispersion-shifted fibers, and (i, j) dispersion-flattened fibers.[42] Right Up: Optical line attenuations loss comparison on spectra between polymer and silica.[43] Right Down: Silica SiO2 loss in relation to Wavelength.

Inside an optical transmission line signal can propagate in several conditions, or modes, which relate to its dimensions and refractive index profile. These electromagnetic modes are used to propagate information in form of light of a given wavelength. In the one hand, we can select only one mode and we set up a Single Mode Fiber (OS), with core diameter less than ten times the selected wavelength. In the other hand, if we select several modes we are on a Multi Mode Fiber (OM), and we are working with bigger diameters for the active core of the fibre. This characteristics are achieved modifying the refractive index profiles as is represented in Fig. 1.16.

A second element in optical fibres is the material for the fibre itself, with impact on signal attenuation, wavelength dispersion and limitations on the length of the fibres (See Fig. 1.16 right). Common materials used are fused silica (SiO2)[42], fluoride glass [44], phosphate glasses [45], or specific polymers [43].

The third interesting element of fibres as communication technology is integrating a bunch of fibres in a single cable. This is directly related to technology material, modes and industry capabilities. The technology of Multi-core fibers (MCF) allows to merge several active cores of controlled refraction index to implement multiple transmission lines on the same section of cable [46][47]. Once the core is manufactured, the rest of the material for the cable is filled with Polydimethyl siloxane, Silicon oils or Acrylates.

About the sensor at reception transceiver side, we normally expect a PIN photodiode optimized for the used wavelength. The most commonly used are silicon, germanium, InGaAsP[48] or GaAlAsSb. Nevertheless, other elements can be found as receptors like Avalanche Photodiodes [49], photodiode arrays, Schottky barrier photodiodes [50] or Metal-Semiconductor detectors (MSM) [51]. On the transmission side, the usual elements are LEDs, edge-emitting lasers diodes (EELD) and vertical cavity surface-emitting laser (VCSELs).

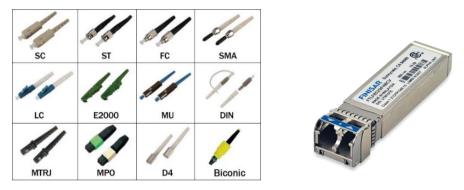

For the fiber interconnection, industries have set a series of standards. On the passive side of the optical line, the optical cables have a label to specify the mode and performance, as in OM1 to OM5 for multimode or OS1-2 for monomode. There is a wide variety of connectors for the physical connection of the optical line as depicted on Fig. 1.17.

On the active side of optical lines, the transceiver main standard widely used is Ethernet Small Form-factor Pluggable transceiver (SFP) and its evolutions SFP+ [52] or SFP28, a full-duplex line up to 10Gbit/s and 25Gbit/s, or the quad full-duplex version QSFP+ and QSFP28 up to 40Gbit/s and 100Gbit/s aggregated bandwidth respectively [53]. Manufacturers also develop their own connectors and standards as PPOD [54], MiniPod [55] and MicroPod from Broadcom Avago, SNAP12 modules, FireFly optical versions from Samtec [56] or the CXP [57] version of SFP, all of them with 12 optical lines.

Fig. 1.17. **Right**: types of optical mechanical connectors. **Left**: Example of an active transceiver part SFP+ connector from Finisar Corporation with a LC mechanical connector socket.

#### High speed PCB.

The high speed communication technology and optical lines require from the electronic elements an appropriate response of the copper connections from the printed circuit boards (PCB) side. Common speeds nowadays for this systems could reach over 10-30Gbps in most critical cases, and the electronic integration increase requires less space and more connections for the same PCB area.

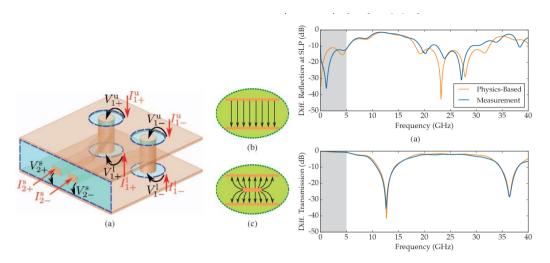

Many tools and techniques had been developed in the last years to cope with these requirements. There is a special need for high speed materials as Nelco [58], Rogers [59] or FR408 [60], usually designed for RF applications, with low loss tangent and low dielectric constant at 10GHz frequencies. These materials allow to ensure a controlled impedance for the differential lines in the designed PCB (see Fig. 1.18), in addition to proper design techniques as trace line matching, constant impedance matching, via optimization, return lines analysis, crosstalk corrections [61][62][63].

Fig. 1.18. Example of a differential strip line and the high speed transmission and reflexion analysis.[64]

On the integration side, industry has developed a new methodology to generate smaller PCBs interconnection called High Density Interconnect (HDI) [65]. With this technology it's possible to use laser vias down to  $50\mu$ m, vias in pads and via pitch below 0.4 mm [66].

## 1.2.2 Instrumentation technology.

Reading signal data from a detector is not trivial since the signal has usually a low amplitude or can be a current measurement. In the last case, it has to be converted to a voltage signal with an RC element. So the first step reading the signal is to deliver and adapt it to the proper condition, amplification and shape for the next step in the electronic chain.

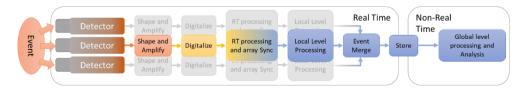

Fig. 1.19. Diagram of an Array detector instrumentation.

The world of storage, processing and communications nowadays is digital, so after a proper signal adaptation it has to be digitized.

The digitalized signal is sent to the real time processing and the triggering trees to verify whether the data is valid or not. This is a critical point due to fact that the full array and different complementary detectors have to contain the elements that make valid the event for our purpose or, at least, should be synchronized to identify the data that are of the same event. Once the data is valid, it's digitally sent to the storage systems for further processing and extraction of physical information. An example of an array detector instrumentation diagram can be found on Fig. 1.19.

#### 1.2.3 Parallel processing and FPGA.

The amount of channels to process in real time on nuclear spectrometry before sending the signals and spectra for processing requires a very high degree of parallelization. In the field of real time processing, one can perform the calculations required with a relative fast sequential processor in such a way that the time to process is less than the real time scale timing unit. Nevertheless, when the number of channels in parallel to process increases, we have to move to a faster processor or increase the number of processors. The speed limits of electronic devices processing cycles are due to the power and thermal requirements so the real solution is parallel computing [67].

The real time parallel computing can be done in any of the big devices for computing as multicore processors or DSPs, parallel devices or Graphic Processing Units (GPU), Field Programmable Gate Arrays (FPGA) or Application-Specific Integrated Circuit. For our application, the multicore processor is excluded due to the high amount of parallelism required on the real time side. Nevertheless, they play an important role in nonreal time processing stages in computing grids or data centres where the data from detectors is stored. GPU multiprocessor units are an option valid for the high amount of channels but not at the level of the electronics to perform the real time processing. However, these devices could be an aid to the processing centres with the stored data.

The specific integrated ASICs are valid for processing and even for other tasks if they are including more specific analogic or digitalizing parts. The main problems of ASICs are the design costs and time of production. While this solution fits on many experimental set-ups, the complexity and flexibility required for our Pre-processing makes another solution more appealing.

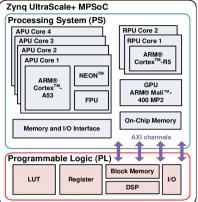

FPGA devices give a mixed solution between an ASIC and a fixed parallel processing system, with the benefits of customization compared to the general processors or GPU, but with an increase on the production time and design. FPGAs are devices formed by a matrix of basic electronic cells. These cells have a logical part, a register part and the capability to interconnect between them. Over the years more modules in addition to the basic cells were added, such as memory cells, digital signal processor (DSP) cells, high speed transceivers cells and, in the last years, full microcontrollers and microprocessors.

The last FPGAs have capabilities up to millions of cells as in the biggest Kintex and Virtex Ultrascale+ in Xilinx [68] or in Stratix X from Intel [69], transceivers capable of differential full-duplex lines of 32 Gbps, more than 100 Mb of distributed memory, thousands of DSP blocks and some of them incorporate ARM processors like Zynq in Xilinx and SX SoC in Intel. In the high performance devices, the aggregated bandwidth is large because of the High Speed transceivers (up to 32 Gbps) implemented, but the number of transceivers itself is low and decreases drastically in low-end devices (from 80 to 8).

In some scenarios, like ours, we would need a big number of not-so-high data rate transceivers but a reasonable big amount of resources to implement the data processing. This seems a no-win situation because devices with a lot of resources have a lot of high data rate transceivers that will be underused and, moreover, at a high price. On the opposite, devices with lower data rates, appropriate for our application, provide fewer logical resource so Pre-processing algorithms would use several of them. As it will be

shown, the use of auxiliary circuitry will provide the best of the two options: full use of data bandwidth and logical resources at a reasonable cost.

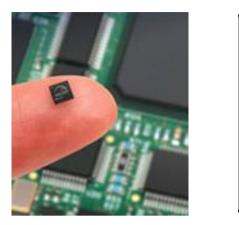

Fig. 1.20. Left: IGLOO FPGA size reference. Right: Zynq Ultrascale+ MPSO processor multicore ARM + GPU + Cortex ARM Microcontroller + Xilinx FPGA fabric

On the other edge of the FPGA state-of-the-art we can find the low power low consumption and usually low cost FPGAs for electronics with high integration. With no transceivers and lower capabilities (40k-100k cells at much), these devices reach power consumptions in the order of  $\mu$ W or even less in standby mode and sizes below 1cm<sup>2</sup> (see Fig. 1.20). Examples of this devices are the ICE family of Lattice Semiconductors [70] or the IGLOO from Microsemi [71].

# Chapter 2: AGATA spectrometer electronics and Read Out

# 2.1 General description

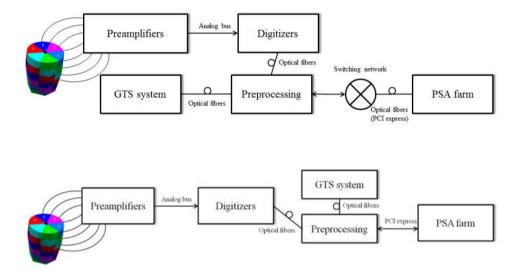

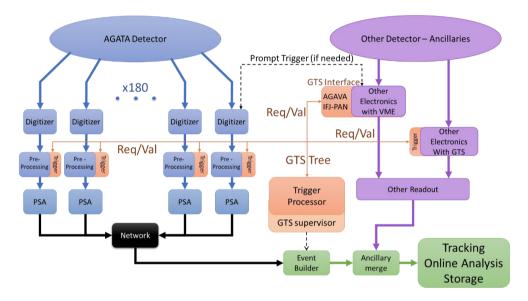

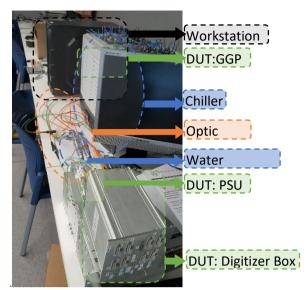

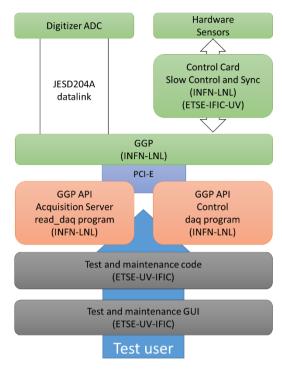

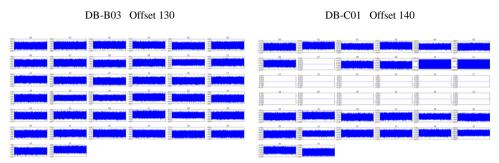

In Chapter 1, Fig. 1.19 showed the basic scheme of the electronics for a Germanium detector array. For the AGATA case, there have been two generations of electronics up to present with similar configurations described both in Fig. 2.1. The first one was developed for the demonstrator or Phase 0 of AGATA and was also used at the beginning of the next phase to instrument 10 more detectors. The second one was designed in the Phase 1 of AGATA and used along with the precedent electronics in the array for an equivalent number of detector channels. In the rest of the document the early generation of electronics will be called Phase 0 and the second, Phase 1.

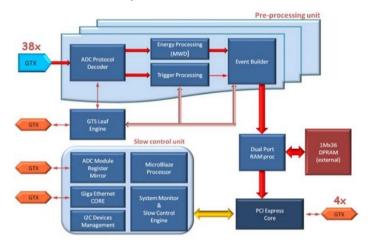

Fig. 2.1. **Up**: First generation of AGATA electronics and Read-Out. Down: Second generation of AGATA electronics, design in the Phase 1 of the array.

Both electronics are composed by the same functional elements: the detector electronics part or preamplifier, the digitizer, the Pre-processing, the Global Trigger System (GTS) leaf and are followed in the data stream by the data acquisition system. However, they differ in the way of implementing these functionalities for some parts.

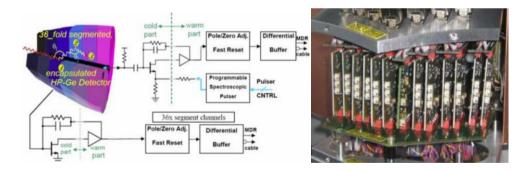

## 2.2 Detector preamplifier

The detector preamplifier is the only part that stays the same along the AGATA generations (Phase 0, Phase 1 and in the future Phase 2). The deep study carried out in due time and the simplicity of their elements makes it unnecessary to upgrade it [33]. This electronic is side by side to the detector and it's implemented in two parts: one on the cold part inside the cryostat area and one on the warm part outside the cryostat. The reason for this structure is that, as mentioned in Chapter 1, germanium only collects the charges created during the ionization process, thus, in order to maintain a low-noise environment, the first stage of the electronics should remain as close as possible to the detector. The detector is cooled to 90K for normal operation and preamplifier has to be operated at temperatures near 130 K  $\pm$ 20 K, where their noise contribution is minimal.

On the cold part we have a low-noise silicon Field-Effect Transistor (model BF862), a 0.8 pF feedback capacitance and  $1G\Omega$  feedback resistance as a first low-noise charge amplifier stage [72]. The warm part implements the low noise transimpedance amplifier to transform current to voltage, a pole-zero stage, the fast reset system and a differential output buffer to feed the MDR (Mini D Ribbon) cables with the analogue signal to reach digitizers (Fig. 2.2).

Fig. 2.2. Left: Preamplifier cold and warm part conceptual design on the AGATA cryostat. Right: Images of the AGATA preamplifiers.

In order to keep noise at minimum, both parts are carefully connected with several individual thin wires with low thermal conductivity and by a specific grounding. The preamplifier is perfectly characterized in order to ensure signal shaping and proper input for the digitizing step following the specifications.

The fast-reset circuitry avoids the effect of the saturation in the pre-amplifier stages in case of non-wanted high energy events, like cosmic rays, quickly discharging the capacitance in the pole-zero stage. This same circuit is also used for the measurement of Time over Threshold to correct overflowed signals. [73]

There are two types of preamplifier boards, the core and the segment. Each core card has two preamplifier signals for two different gains of the same core. The segment ones amplify three segment signals per board. The last key element added to the preamplifiers is the high precision pulser for the core boards. Introduction of calibration pulses into the detector bulk capacitance allows to perform tests and calibrations for the detectors.

## 2.3 Digitalization

The differential output from the detector preamplifier is connected through 6channel copper MDR mini ribbon cables [74] of 10 m length each to the digitalization stage, in the same room of the detector. The digitizers have been improved in the different generations.

## 2.3.1 First generation (Phase 0) digitizer

In the first version of digitizers, corresponding to the design during the Phase 0, the ADCs boards were based on the AD6645 (high speed, high performance, monolithic 14-bit analog-to-digital converter) chip from Analog Devices. This integrated circuit (IC) is capable of digitalizing differential signals at 100Msps with 14-bit resolution. Once the data is digitalized, it is serialized on a Xilinx Virtex-II FPGA and sent through optical fibers to the Pre-processing stage via SFP optical connectors. The FPGA also performs a constant fraction discriminator (CFD) for fast trigger output and the Time-over-Threshold calculations of the preamplifiers. The output signals from the FPGA consist of 16-bits per channel corresponding to the digitalized data plus 2 bits for the trigger information. While the AD6645 IC has 14-bit resolution, the effective number of bits (ENOB) reached by the digitizer is about 12-bit, in very good agreement with the noise specifications of the ADC IC.

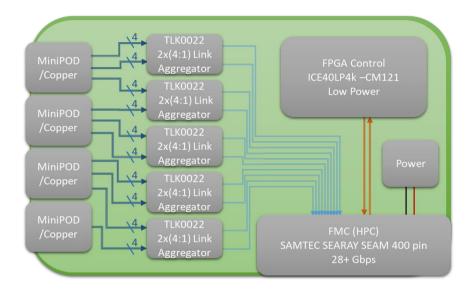

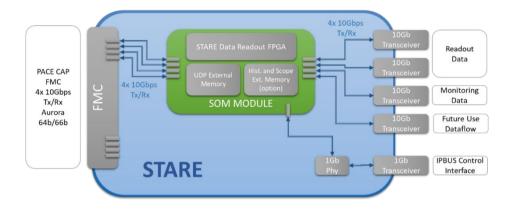

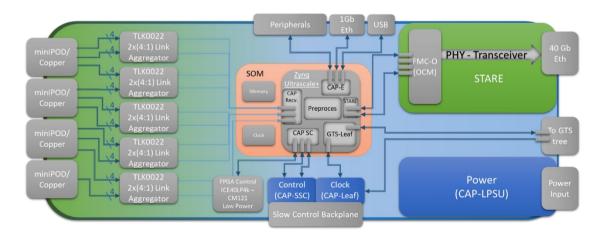

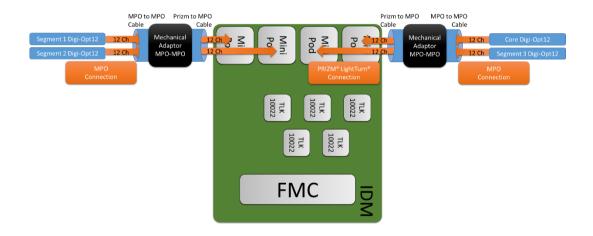

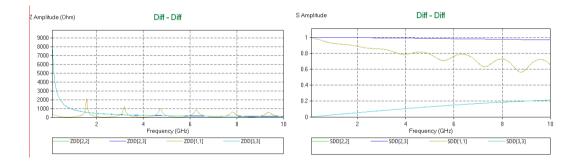

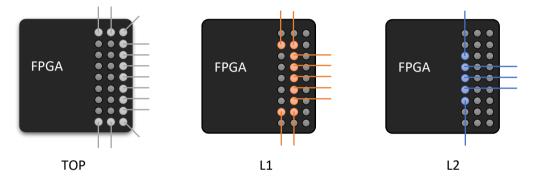

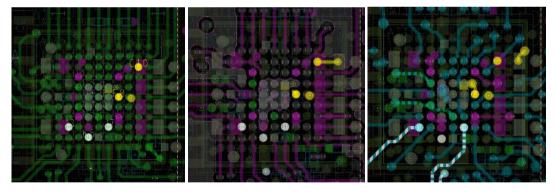

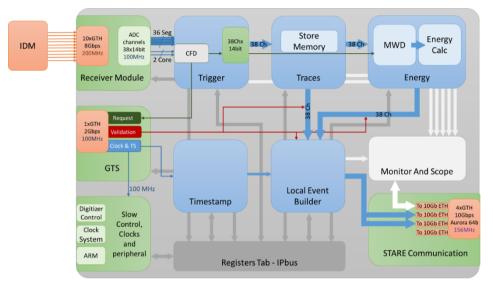

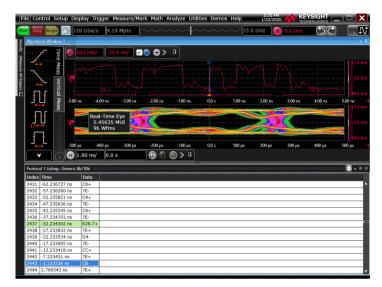

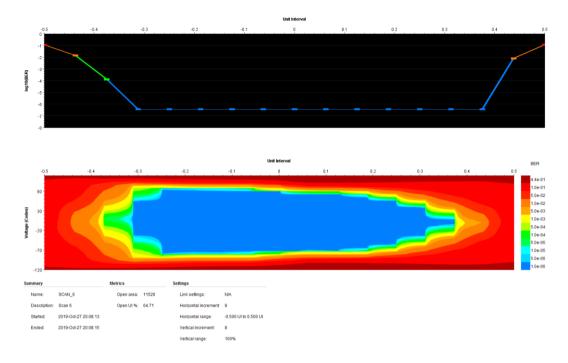

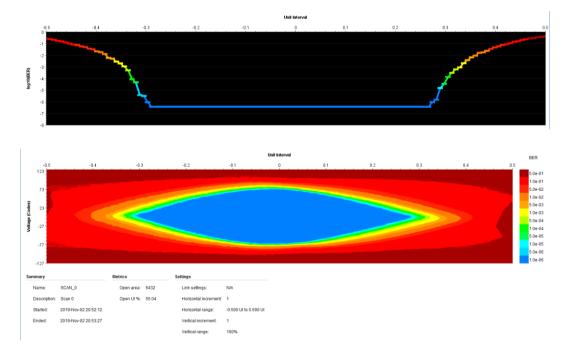

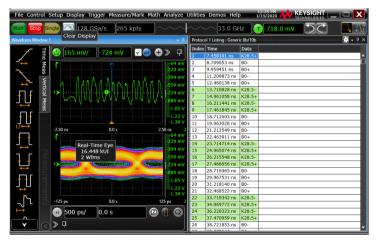

The digitizers are distributed in segment boards with 6 FADC, the Virtex-II to serialize the 6 channels and the optical output. Another specific board is available for the core with only 2 FADC instead and some extra features like a pulser and a fast trigger output. There is also another type of board on the digitizer system, a Control Card with a Xilinx Spartan II E and Ethernet connection for the slow control. All the mentioned boards have a mezzanine board to board connection for the motherboard.