# University of Mississippi

# eGrove

**Electronic Theses and Dissertations**

**Graduate School**

2019

# Scheduling Irregular Workloads on GPUs

David Arthur Troendle University of Mississippi

Follow this and additional works at: https://egrove.olemiss.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Troendle, David Arthur, "Scheduling Irregular Workloads on GPUs" (2019). Electronic Theses and Dissertations. 1705.

https://egrove.olemiss.edu/etd/1705

This Dissertation is brought to you for free and open access by the Graduate School at eGrove. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of eGrove. For more information, please contact egrove@olemiss.edu.

# Scheduling Irregular Workloads on GPUs

A Dissertation presented in partial fulfillment of requirements for the degree of Doctor of Philosophy in the Department of Computer and Information Science The University of Mississippi

by

David Troendle

December, 2018

#### ABSTRACT

Graphic Processing Units (GPUs) have emerged as proven, powerful accelerators for data and compute intensive applications. It creates a massive number of threads, each of which operates on a part of the problem. When all threads complete the problem is solved. Data irregular workloads which hold dynamic data dependencies and parallelism, however, pose unique programming/performance challenges because a thread cannot make progress until all dependencies are cleared. This requires a special scheduling mechanism shared by all threads and atomic access to the shared scheduler. The scheduler is usually implemented with a queue data structure. The use of atomic operations to synchronize access to a data structures, however, comes with overhead that severely limits scalability. As the number of threads increases, overhead disproportionally increases. This results in diminished thread effectiveness because more of a thread's computing potential is lost to overhead.

This doctoral research aims at understanding the nature of the overhead for data irregular GPU workloads, proposing a solution, and examining the consequences of the result. We propose a novel, retry-free GPU workload scheduler for irregular workloads. When used in a Breadth First Search (BFS) algorithm, the queue scales to within 10% of ideal scalability on a Fiji GPU with 14,336 active threads. The proposed scheduler is based on a simple, monolithic concurrent queue<sup>1</sup>. The dissertation presents research that shows the retry overhead associated with Compare and Swap (CAS) operations<sup>2</sup> is the principle reason why concurrent queues do not scale well as the number of clients increase in a massively multi-threaded environment.

The proposed concurrent queue is based solely on non-failing atomic operations such

<sup>&</sup>lt;sup>1</sup>The queue works like a traditional queue except that enqueue/dequeue operations return the queue index where data is stored (enqueue) or will appear (dequeue).

$<sup>^2</sup>$ Traditional state-of-the-art concurrent queues are based on CAS operations. CAS operations can fail. Failures force retries.

as atomic\_add, atomic\_inc and atomic\_min. Since these operations never fail, there is no retry overhead. The non-failing atomic operations also allow an arbitrary number of elements on each enqueue or dequeue operation for the same cost as operating on a single element. Limited dynamic parallelism can result in situations where there are more threads than available tasks. When this happens, atomic dequeues result in retries caused by queue empty failures. The dissertation presents a novel solution that transforms the atomic queue empty failure to a non-atomic data arrival problem. The result is a wait-free concurrent queue that has no retires – neither from the atomic operations used to manage queue access nor from the dequeue queue empty exception.

The consequences of this research suggest a refocus of research from atomic overhead reduction to thread saturation. The techniques used in this dissertation effectively reduce overhead, leaving idle threads as the most significant remaining scalability-limiting factor. To address this problem, the dissertation also proposes a speculate and correct single-source, shortest path (SSSP) algorithm that effectively saturates the GPU.

# **DEDICATION**

This research is dedicated to my wife, Jean, and my children Michael and Michelle.

I also dedicate this work to my teachers who, throughout my life, have believed in me and always took the time to show me the way. Foremost among my teachers is my advisor, Dr. Byunghyun Jang. Very few would have given an older student a chance to earn a PhD. Throughout my graduate studies, he has believed in me, saw me through all the failures that are part of research, encouraged me to keep trying and celebrated my successes. In no small part, my success is his success.

# **ACKNOWLEDGEMENTS**

The candidate acknowleges the help and support he received from past and current members of the HEteROgEneous Systems research (HEROES) lab. These include past members Dr. Kyoshin "Joel" Choo; Md. Mainul Hassan, MS; Esraa Gad; Xiaoqi "Chelsea" Hu, MS and Ajay Sharma, MS. Current members include Mengshen "Mason" Zhao and Hossein Pourmeidani, MS.

A special thanks goes to past member Tuan Ta, who pointed out the importance of concurrent data structures, which is the foundation of much of this research.

# Contents

| ABSTRACT   |                                  | ii |  |

|------------|----------------------------------|----|--|

| DEDICATION |                                  |    |  |

| ACKN       | ACKNOWLEDGEMENTS                 |    |  |

| INTR       | ODUCTION                         | 1  |  |

| 1.1        | Overview                         | 1  |  |

| 1.2        | Foundation                       | 2  |  |

| 1.3        | Porting to a GPU                 | 4  |  |

| 1.4        | Dealing with dynamic parallelism | 5  |  |

| 1.5        | Contributions                    | 6  |  |

| 1.6        | Organization of dissertation     | 7  |  |

| BACK       | GROUND                           | 8  |  |

| 2.1        | Thread synchronization on GPUs   | 8  |  |

| 2.2        | Irregular workloads on GPUs      | 9  |  |

| 2.3        | Concurrent data structures (CDS) | 10 |  |

| 2.4        | Persistent Thread Model          | 11 |  |

| 2.5        | Excess Persistent Threads        | 12 |  |

| 2.6        | Bread-First Search on GPUs       | 12 |  |

| 27         | Single Source Shortest Path      | 13 |  |

| PERS                       | ISTENT TASK SCHEDULING DESIGN CHALLENGES                               | 15 |  |

|----------------------------|------------------------------------------------------------------------|----|--|

| 3.1                        | Persistent task scheduling design challenges                           | 15 |  |

| 3.2                        | CAS failure                                                            | 17 |  |

| 3.3                        | Empty queue checking                                                   | 18 |  |

| 3.4                        | Lock-step execution                                                    | 19 |  |

| CONC                       | CURRENT QUEUE FOR PERSISTENT GPU THREADS                               | 21 |  |

| 4.1                        | Concurrent queue for persistent GPU threads                            | 21 |  |

| 4.2                        | Example Queue Operation                                                | 22 |  |

| 4.3                        | Wait-Free, Retry-Free, Arbitrary- $n$ Dequeue                          | 24 |  |

| 4.4                        | Data Arrival Details                                                   | 24 |  |

| 4.5                        | Wait-free, retry-free, arbitrary-n enqueue                             | 26 |  |

| KERNEL DESIGN              |                                                                        | 28 |  |

| 5.1                        | Kernel design                                                          | 28 |  |

| 5.2                        | Persistent thread considerations                                       | 28 |  |

| 5.3                        | Porting considerations                                                 | 29 |  |

| 5.4                        | The chunked persistent thread model                                    | 30 |  |

| 5.5                        | Queue operation considerations                                         | 31 |  |

| EXPE                       | RIMENTAL SETUP                                                         | 33 |  |

| 6.1                        | BFS driver application and its data dependency                         | 33 |  |

| 6.2                        | Input graph datasets                                                   | 34 |  |

| 6.3                        | Confidence interval                                                    | 36 |  |

| 6.4                        | Programming language and test hardware                                 | 38 |  |

| ANALYSIS OF PROPOSED QUEUE |                                                                        |    |  |

| 7.1                        | Optimal queuing method and chunk size                                  | 40 |  |

| 7.2                        | Effects of the arbitrary- $n$ and retry-free properties on performance | 55 |  |

| 7.3    | Scalability                                           | 56  |

|--------|-------------------------------------------------------|-----|

| 7.4    | BFS performance comparison                            | 58  |

| SSSP   | GPU SPECULATE AND CORRECT ALGORITHM                   | 61  |

| 8.1    | Motivation                                            | 61  |

| 8.2    | Bellman-Ford SSSP algorithm                           | 62  |

| 8.3    | Proposed GPU speculate and correct SSSP algorithm     | 63  |

| 8.4    | SSSP benchmark datasets                               | 70  |

| 8.5    | Speculate and correct SSSP kernel performance details | 71  |

| 8.6    | SSSP benchmark comparison                             | 72  |

| RELA   | TED WORK                                              | 75  |

| 9.1    | Concurrent data structures                            | 75  |

| 9.2    | GPU persistent thread scheduling                      | 78  |

| 9.3    | GPU graph algorithms                                  | 79  |

| SUMN   | MARY AND CONCLUSION                                   | 80  |

| BIBLI  | BIBLIOGRAPHY                                          |     |

| Appen  | adices                                                | 88  |

| Kerne  | l Support Variables                                   | 89  |

| Code : | Listing: The Direct Dequeue / Enqueue Kernel          | 91  |

| Code   | Listing: The Direct Dequeue / Proxy Enqueue Kernel    | 95  |

| Code   | Listing: The Proxy Dequeue / Direct Enqueue Kernel    | 100 |

| Code   | Listing: The Proxy Dequeue / Enqueue Kernel           | 105 |

| Code 1 | Listing: SSSP Kernel                                  | 110 |

VITA 118

# List of Figures

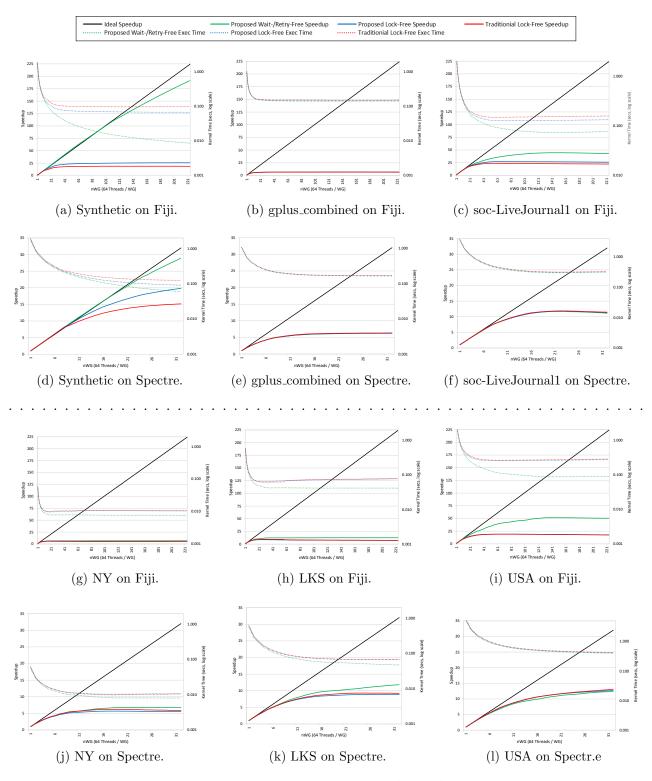

| 3.1  | CAS retry overhead for BFS on various datasets and hardware                 | 16 |

|------|-----------------------------------------------------------------------------|----|

| 3.2  | Queue empty retry overhead for BFS on various datasets and hardware         | 17 |

| 3.3  | Wavefront lock-step execution                                               | 19 |

| 4.1  | Proposed queue structure and operation                                      | 22 |

| 6.1  | BFS traversal strategy                                                      | 33 |

| 6.2  | Area under Z PDF for p=0.95 and p=0.99 $\dots$                              | 36 |

| 7.1  | Synthetic graph dependency clearance by depth level                         | 41 |

| 7.2  | BFS kernel execution time by device/queuing algorithm/chunk size (synthetic |    |

|      | data)                                                                       | 42 |

| 7.3  | gplus_combined analysis                                                     | 43 |

| 7.4  | soc-LiveJournal1 analysis                                                   | 45 |

| 7.5  | USA-road-d.NY analysis                                                      | 47 |

| 7.6  | USA-road-d.LKS analysis                                                     | 49 |

| 7.7  | USA-road-d.USA analysis                                                     | 51 |

| 7.8  | Execution time and speedup                                                  | 54 |

| 7.9  | Traditional speedup curves                                                  | 56 |

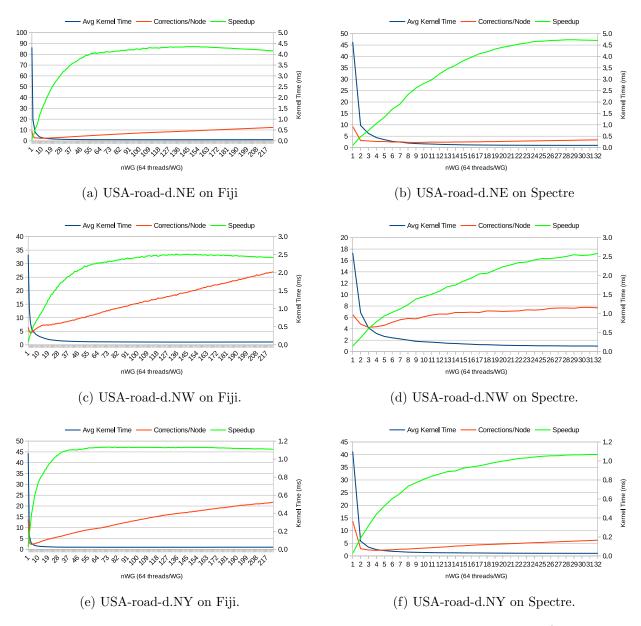

| 7.10 | Scalability                                                                 | 56 |

| 8.1  | Vertex/Edge terminology                                                     | 64 |

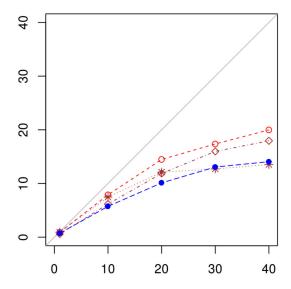

| 8.2  | Speculate and correct SSSP performance on selected datasets/GPUs            | 71 |

# List of Tables

| 6.1 | Selected SNAP social media graph datasets statistics               | 34 |

|-----|--------------------------------------------------------------------|----|

| 6.2 | The $9^{th}$ DIMACS implementation challenge dataset statistics    | 34 |

| 7.1 | Performance comparison with CHAI BFS (ms)                          | 58 |

| 7.2 | Performance comparison with Rodinia BFS (ms)                       | 59 |

| 8.1 | Selected ninth DIMACS implementation challenged dataset statistics | 69 |

| 8.2 | SSSP performance (average kernel time in ms) summary               | 73 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Overview

GPUs accelerate applications by mapping a massive number of threads to data and computation tasks to solve a problem. Early GPU designs required a streaming-style thread mapping with no or little dependencies among threads. For applications amenable to that requirement, GPUs offer an effective, power efficient solution with impressive scalability and acceleration. However, for data irregular applications holding dynamic dependencies and parallelism, results were disappointing. This dissertation aims at identifying the overhead sources causing the poor performance in data irregular workloads and proposing novel solutions. Two main sources of inefficiency we identified are:

- 1. Retries caused by failed atomic operations.

- 2. Retries caused by empty conditions in dequeue operations when no task is available for an idle thread,

This dissertation describes the research that identified the above overhead, and proposes the following novel solutions:

- 1. A wait-free, retry-free queue that uses only non-failing atomic operations,

- 2. Refactoring the atomic dequeue queue empty failure into a non-atomic data arrival problem.

In general, lack of available work remains an intractable acceleration limiting problem for data dependent applications. However, in some cases, it is possible to speculate rather than wait for dependencies to clear. If incorrect speculations can be detected and corrected, then GPU threads can be kept saturated with either speculation or correction tasks. The technique is effective if the number of incorrect speculations is small enough. This dissertation demonstrates the effectiveness of the speculate and correct approach on the SSSP problem.

#### 1.2 Foundation

GPUs have emerged as powerful application accelerators. Acceleration is achieved by applying a massive number of threads to a problem. The more effectively an algorithm exploits the parallelism, the better the acceleration. From the earliest Multi-Core Multi-Threaded (MCMT) implementations, exploiting thread parallelism has proven a challenging design problem. The two most common issues are workload balancing (keeping all threads busy) and thread interference caused by atomic operations.

In a GPU environment, the problem is further complicated by the GPU's architecture. On a MCMT processor, thread instruction paths are always independent of each other, while on a GPU they are not always independent<sup>1</sup>. Early GPU implementations allowed only workloads with full thread independence (i.e., no thread depends on the work done by any other thread). This allowed the hardware scheduler to schedule work in any order, usually with the primary objective of hiding global memory latency.

As GPUs matured, they eventually added the hardware support that enabled processing workloads with data dependencies. Work with outstanding dependencies cannot be scheduled for execution until all its dependencies are cleared. While data dependent workloads were allowed, GPUs provided no scheduling support. It was left to the programmer to detect when all dependencies have cleared and schedule that work for execution. Thus, an efficient scheduler is essential to the successful GPU acceleration of data dependent workloads

<sup>&</sup>lt;sup>1</sup>GPUs cluster threads into thread groups that execute in lock-step. This creates an artificial relationship between threads in a group that does not exist in a MCMT environment, and complicates GPU algorithm design.

and is an important research problem.

Unlike traditional processors, GPU threads are created, scheduled, and destroyed by hardware, and the programmer has no control over the order of thread execution. GPUs have two levels of hardware thread scheduling: one that assigns a software thread group (i.e., workgroup in OpenCL and thread block in CUDA terminology) to GPU cores (i.e., Compute Units (CUs) in OpenCL and Streaming Multiprocessors (SMs) in CUDA), and another that schedules hardware thread groups (i.e., wavefront in AMD and warp in NVIDIA terminology)<sup>2</sup> on the SIMD engines. The GPU hardware thread execution model imposes programming challenges for workloads that require a certain thread execution order. For example, in graph traversal algorithms, multiple threads traversing different parts of a graph may need to run in a specific order to satisfy dependencies among vertices. Such workloads cannot benefit from GPU acceleration without a special programming technique.

Data irregular workloads [5] are those whose execution flow and parallelism change dynamically at runtime depending on data. While there are other forms of irregularity (e.g., associated with control flow or memory access patterns – see Burtscher et al. [5]), efficiently dealing with data irregularity has been one of the most difficult design challenges in GPU programming. A programming technique known as persistent threads [31] has emerged as a compelling solution for accelerating such irregular workloads<sup>3</sup> [31, 54]. The persistent thread model creates enough threads to saturate the GPU provided there are available tasks. All threads stay alive until the end of a GPU kernel. Computing tasks can be formed dynamically throughout the kernel and scheduled to running threads under an algorithm-specific task dependency constraint. When a persistent thread needs a task to execute, it obtains a unique token identifying a task from the task scheduler. When a running task completes, it may make other tasks ready for execution by passing the unique tokens for the newly runnable tasks to the scheduler. A queue data structure (or variant) plays a critical role in designing the task scheduler. The queue is shared by all threads and requires

<sup>&</sup>lt;sup>2</sup>We use OpenCL terminology hereinafter to simplify the presentation.

<sup>&</sup>lt;sup>3</sup>We simply refer to data irregular workloads as irregular workloads.

atomic access to the shared queue access variables. A CAS operation is typically used to manage access, but a CAS succeeds for only one competing thread, forcing the unsuccessful competitors to retry until they succeed.

Designing a persistent thread task scheduler that performs well under a GPU's Single Instruction Multiple Data [40] (SIMD) thread model is a difficult task arising from two factors: 1) CAS failure retry overhead, and 2) atomic contention issues arising from the lock-step execution nature of a GPU's SIMD thread groups. CAS failure retries disproportionally increase as the number of competing threads increases, and thus limit efficiency. In a lock-step execution environment, no thread can make progress until all CAS operations in the lock-step execution thread group succeed. This dissertation proposes a wait-free array-based concurrent queue data structure to address the design issues of a persistent thread task scheduler. The proposed concurrent queue has the following novel properties:

- Retry-free: This property ensures the atomic operations managing access to the shared queue variables never retry. They successfully complete first time, every time. Further, dequeue failures due to an empty queue condition have been refactored and do not cause dequeue retries. Dequeue failures are handled outside the queue mechanism, and require no atomic operations.

- Arbitrary-n: Each queue operation can operate on an arbitrary number of entries for the cost of a single entry. Lock-step execution of atomic operations in a GPU wavefront can cause intense contention. The arbitrary-n property allows a single proxy thread to perform atomic operations on behalf of all threads in a lock-step execution thread group. This property allows a simple monolithic queue to serve as an efficient persistent thread task scheduler, and avoids the overhead of multi-level queues.

### 1.3 Porting to a GPU

Often porting a data dependent algorithm begins with a multi-threaded CPU version. Sometimes the algorithm is an established CPU algorithm that needs to be ported to a GPU. Sometimes it is a new algorithm that is easier to develop and debug in a multi-threaded CPU environment. Rendering an algorithm in a GPU environment has proven a difficult challenge that has been mastered by few. The proposed queue structure was designed to ease this task. This dissertation describes how a typical MCMT thread can be refactored into a persistent thread using the proposed queue. It identifies how each major section of a MCMT threaded algorithm can be refactored into a GPU kernel using the proposed queue.

# 1.4 Dealing with dynamic parallelism

An application is an algorithm applied to a dataset. When there are no dependencies in the dataset, tasks can be performed in any order. Data dependencies force tasks to be performed in a specific order. Only the subset of tasks with no dependencies can be scheduled to a thread. Typically, as a task runs it clears dependencies held by other tasks, allowing them to be scheduled. *Dynamic parallelism* is the number of tasks eligible for processing at any instant in time. Often, the number of threads exceeds dynamic parallelism. When this happens, the threads with no tasks assigned do not accelerate, which limits the overall ability of the GPU to accelerate the application.

It is possible for an algorithm to speculate if it can detect and correct when it has speculated incorrectly. Speculate and correct is a form of dynamic programming that speculates rather than waiting when it encounters a for a data dependency to clear, and corrects when it detects an incorrect speculation. If speculations are sufficiently correct, this can allow the algorithm to ignore data dependencies and saturate all threads by speculating. When an incorrect speculation is detected, tasks dependent on the incorrect speculation are rescheduled for correction.

This involves two queues: One queue handles speculation and the other queue handles corrections. The correction queue has a higher priority. In this manner, corrections are performed before speculation can propagate the effects of an earlier incorrect speculation. One important example of this approach is SSSP. SSSP finds the short weighted path

from a single source vertex to all descendants. The Bellman-Ford algorithm [2, 21] can be viewed as a speculate and correct algorithm. The algorithm makes at most |V| - 1 passes on the graph. Each pass detects and corrects path errors made in a previous pass. If a pass makes no corrections, no further passes are required. The algorithm is inefficient in a GPU environment, because there are sufficient threads to concurrently correct any errors and immediately queue their descendants for correction. The net result is that the SSSP problem can be done in a single pass, while keeping all threads busy. For the DIMACS [17] roadmap datasets, the speculate and correct algorithm improved performance by two orders of magnitude for small GPUs such as the AMD Spectre, and one order of magnitude for large GPUs such as the AMD Fiji. This dissertation details the SSSP GPU speculate and correct algorithm.

### 1.5 Contributions

The contributions of dissertation are summarized as follows.

- 1. A highly scalable concurrent queue data structure is proposed and implemented for massively multi-threaded GPU architectures.

- 2. BFS is implemented to demonstrate and analyze the performance characteristics of the proposed queue.

- 3. A refactoring process is presented to aid in the rapid migration of CPU thread-safe algorithms to an equivalent GPU algorithm.

- 4. BFS performance is compared with state-of-the-art competitors found in the literature.

- 5. A novel speculate and correct SSSP algorithm is presented that outperforms state-of-the-art algorithms found in the literature by two orders of magnitude for small GPUs such as the AMD Spectre and one order of magnitude for larger GPUs such as the AMD Fiji.

# 1.6 Organization of dissertation

The remaining chapters of this dissertation are organized as follows: Chapter 2 gives background information; Chapter 3 outlines persistent thread scheduling design challenges; Chapter 4 details the proposed queue; Chapter 5 discusses the kernel design; Chapter 6 details the experimental setup; Chapter 7 analyzes the proposed queue; chapter 8 presents a speculate and correct SSSP algorithm; Chapter 9 gives related work; and chapter 10 summarizes results and gives concluding remarks.

#### CHAPTER 2

#### BACKGROUND

### 2.1 Thread synchronization on GPUs

The GPU thread execution model clusters threads into groups called wavefronts. From the programmer's perspective, all threads in a wavefront appear to execute in lock-step<sup>1</sup>. To hide memory latency, GPUs use a zero-cost wavefront switching mechanism. If a wavefront stalls on a long latency operation (e.g., memory read or write), the GPU attempts to switch to another ready wavefront. The programmer does not have control over this hardware thread (wavefront) scheduling. This requires all threads within a wavefront to be independent in order to avoid deadlock situations, and imposes significant limitations on thread synchronization and communication.

# Algorithm 1 Critical section.

- 1: while !lock(flag) do

- 2: end while

- 3: ...

- 4: unlock(flag)

The lock-step execution nature of a wavefront has unexpected consequences when atomic operations are used to serialize access to shared resources. For example, the simple mutex-based critical section shown in Algorithm 1 causes a deadlock on a GPU. The problem is the mutex unlock on line 4 of Algorithm 1 may never execute. This is because all the threads in a wavefront simultaneously compete for the flag on line 1. The hardware picks a

<sup>&</sup>lt;sup>1</sup>A wavefront is formed from several hardware SIMD thread groups. The threads in a SIMD thread group are actually executed in parallel. The wavefront is a logical grouping that appears to execute in lockstep.

winner, and all other competing threads fail. The failing threads spin (lines 1-2) on the lock until they obtain it. This never happens because when the failing threads spin, the lock-step execution of a wavefront also forces the winning thread into a No Operation (NOP) spin. This prevents the successful thread from ever executing line 4, which clears the flag. Blocking techniques from a multi-threaded CPU environment must be adjusted to work in a GPU's lock-step thread environment.

# 2.2 Irregular workloads on GPUs

The challenges associated with processing irregular workloads on GPUs have been well studied. Che et al. [7] developed a suite of OpenCL applications to study irregular graph workloads. Tzeng et al. [54] studied task scheduling for irregular GPU workloads, from a single monolithic task queue to distributed queuing with task stealing and donation. They also proposed static and dynamic dependency-aware scheduling schemes for irregular workloads, and studied them with H.264 Intra Prediction video compression and the N-Queens constraint satisfaction problem [5].

In irregular workloads, a task may depend on the completion of some other task(s) before it can be processed. As a task is completed, it can clear dependencies for other dependent tasks so that they can be scheduled to execute. At any instant there is a dynamic subset of tasks with no active dependency that are ready to execute.

Processing an irregular workload requires a mechanism for scheduling the dynamic subset of independent tasks. A common approach is to use a software scheduler that is shared by all threads. This requires atomic serialization of the shared access variables, which in turn causes significant atomic contention in a massively parallel GPU environment. Further, the lock-step execution of a wavefront increases simultaneous atomic access and consequently exacerbates contention issues. A practical irregular workload scheduler must be aware of the GPU's unique thread execution model.

# 2.3 Concurrent data structures (CDS)

In multi-threaded shared memory systems, threads perform tasks concurrently and synchronize with one another through data structures in logically shared memory. Data structures play a crucial role in achieving good performance on such systems. Concurrent Data Structure (CDS) research evolved as an alternative to mutual exclusion serialization strategies such as critical sections. Traditionally, CDSs are implemented using two techniques: blocking and non-blocking, and their characteristics are classified as follows [46, 45]:

- Obstruction-free: A thread competing for data structure access makes progress only after the interference from other threads ceases.

- Lock-free: At least one thread competing for data structure access makes progress after finite time.

- Wait-free: All threads competing for data structure access make progress after finite time.

Non-blocking CDSs guarantee that if one or more active threads try to perform operations on a shared data structure, some operations will complete in finite time. Cederman et al. [6] showed that non-blocking CDSs perform better than blocking ones in most cases. Most state-of-the-art CDSs are lock-free and implemented using *CAS* operations to manage shared variable access.

In CAS-based implementations, when multiple threads attempt to update a shared variable at the same time, only one succeeds while all other competitors fail and must retry. The highly threaded nature of a GPU environment tends to increase competition. A CAS implementation ensures only one competitor at a time succeeds. So, at best CAS implementations are lock-free. A wait-free CDS is better suited to highly competitive GPU environments, because all competitors succeed in finite time. However, wait-free CDSs have proven difficult to achieve [15].

#### 2.4 Persistent Thread Model

A GPU's thread execution model clearly imposes significant disadvantages on irregular workloads. A common solution is to launch enough independent persistent threads [19, 31] to saturate the hardware and use a task scheduler to assign tasks to the persistent threads. The scheduler holds unique tokens that identify the independent tasks. When a persistent thread is ready for new work, it requests a task token from the scheduler. As a thread performs a task, it may produce new tasks with cleared dependencies. When this happens the thread stores the unique tokens of the newly discovered independent tasks in the scheduler.

# **Algorithm 2** Persistent thread model.

- 1: while WorkRemains() do

- 2: **if** GetWorkToken() **then**

- 3: DoWorkUnit()

- 4: ScheduleNewlyDiscoveredTokens()

- 5: end if

- 6: end while

Algorithm 2 shows the basic persistent thread model. Each pass through lines 1–6 is called a work cycle and all persistent threads remain active as long as any task remains. Line 2 requests a work token from the scheduler. If it gets work, line 3 works on the task associated with the task token, and line 4 schedules any work tokens whose dependencies were cleared by the work done on line 3. If the thread fails to get work at line 2 it simply loops until all work is done or it gets work.

Choosing a data structure to implement the task scheduler is an important design decision. In the massively threaded GPU environment, scalability is a primary design consideration. A CDS with a wait-free property is ideal because all competing threads make progress in finite time. A concurrent stack (Treiber et al. [51]), queue (Valois et al. [57], Harris [25]) or deque (Michael et al. [44], Valois [58], Sundell et al. [50]) are potential candidates for the persistent thread task scheduler. While a deque [50] is a more general form

of a queue, the scheduler requires only the features of a much simpler single ended queue. A stack's push and pop operations compete for a single shared access location, the top of stack pointer, which causes high contention. For these reasons, we chose and developed a wait-free concurrent queue for the task scheduler. It minimizes the overhead associated with the dequeue operation used to obtain task tokens (Algorithm 2, Line 2) and the enqueue operation used to schedule task tokens (Algorithm 2, Line 4).

#### 2.5 Excess Persistent Threads

Dynamic parallelism is a form of parallelism in which the number of independent tasks available for execution varies over time. In the persistent thread model, the number of persistent threads can exceed available dynamic parallelism. This dissertation refers to the persistent threads in excess of dynamic parallelism as excess persistent threads.

Even though the excess threads have no available work, they nonetheless futilely attempt to dequeue a task token each work cycle. Each futile attempt results in a queue empty exception, and increased atomic retry contention with no opportunity for benefit. The excess threads cannot be destroyed because they may be needed in the future. Since there is no software-level system (e.g., operating system) on GPUs, those threads cannot be put to sleep.

The proposed solution is to ensure an excess thread dequeues only once. This prevents excess persistent threads from retrying multiple times when there are no available tasks in the task queue. This mechanism is detailed in §4.1 (Concurrent queue for persistent GPU threads).

# 2.6 Bread-First Search on GPUs

BFS is an important, fundamental graph algorithm that finds numerous applications in many diverse fields. It has been extensively researched and optimized for CPU [28, 56, 59, 9] and recently GPU [28, 36, 37, 42] environments. Because it exhibits irregularity and

dynamic parallelism, it has been considered as a representative irregular GPU workload.

Harish et al. [24] pioneered the acceleration of BFS on GPUs, but achieved limited acceleration over CPU implementations. Deng et al. [14] introduced a Sparse-Matrix Vector Product-based formulation for BFS and achieved a 10× acceleration over CPU implementations. Luo et al. [39] presented a GPU BFS implementation using a hierarchical queue and a three-layer CUDA kernel that was intended for applications with near-regular graphs typically found in Electronic Design Automation (EDA) applications. It achieved up to 10× speedup over CPU implementations.

The Rodinia benchmark suite [7] includes a BFS implementation using course-grain atomic operations. The CHAI benchmark suite [29] includes a true heterogeneous BFS implementation. Liu et al. [37] achieved the best-performing BFS implementation known to the author. It implements a CUDA hybrid top-down/bottom-up algorithm. It's top-down performance is similar to other implementations on low-fanout deep graphs such as roadmap datasets, but the bottom-up algorithm achieves exceptional performance on high-fanout shallow graphs such as social media datasets.

Top-down BFS is a simple algorithm with an easily understood data dependency whose performance has been extensively studied on CPUs and GPUs. For these reasons, a top-down persistent thread BFS implementation was chosen to drive the queue and demonstrate its performance characteristics.

#### 2.7 Single-Source Shortest Path

SSSP (Cormen et al. [10, pp 643–683]) finds the shortest weighted path between graph vertices starting from a single source. The weight is an abstract metric suitable for the problem. For instance, if the shortest distance is desired, then an appropriate weight would be the distance between adjacent nodes. Alternatively, if the shortest time is desired, then the travel time between adjacent nodes would be an appropriate weight. The problem can become complicated if there are cycles in the graph with negative weights.

There are several algorithms for this problem. The most notable are due to Dijk-stra [16], and Bellman [2] and Ford et al. [21]. Dijkstra's algorithm does not allow cycles, while the Bellman-Ford algorithm does allow non-negative cycles. Typically, Bellman-Ford runs slower than Dijkstra.

The Bellman-Ford algorithm [2, 21] performs at most |V| passes to develop the paths and detect negative cycles. Each pass detects and corrects errors made in the previous path. Each pass speculates the best path and corrects errors made in prior passes. The algorithm is inefficient in a GPU environment, because there are sufficient threads to concurrently correct any path errors as they are detected. Queuing the descendants of a corrected path for immediate correction avoids multiple passes. The correction queue has higher priority than the speculation queue. The helps minimize propagation of incorrect speculations. The net result is that the SSSP problem can be done in a single pass, and the GPU threads are kept busy either speculating or correcting. Further, the speculation frontier expands exponentially. The exceptional scaling characteristics of the proposed queue are well-suited to the speculate and correct technique. However, the technique introduces correction overhead.

#### CHAPTER 3

#### PERSISTENT TASK SCHEDULING DESIGN CHALLENGES

3.1 Persistent task scheduling design challenges

The queue data structure plays a critical role in persistent thread task scheduling. A persistent thread requests a task token from the queue when it needs work and stores a new task token in the queue when it discovers a newly independent task. The massively threaded GPU environment generates unique design challenges because a large number of threads atomically compete for queue access. Traditional CAS-based concurrent queues exhibit three major challenges when used for persistent task scheduling on GPUs.

- 1. CAS failure: CAS operations can fail if there is more than one competing thread: one succeeds while all other competitors must retry until they succeed.

- 2. **Dequeue "queue empty" checking:** When there are excess persistent threads due to lack of data parallelism, the kernel must keep retrying dequeues until data is available.

- 3. Lock-step execution: Lock-step execution increases retries and delays progress until all competing threads in a wavefront succeed.

The following subsections describe each challenge in more depth.

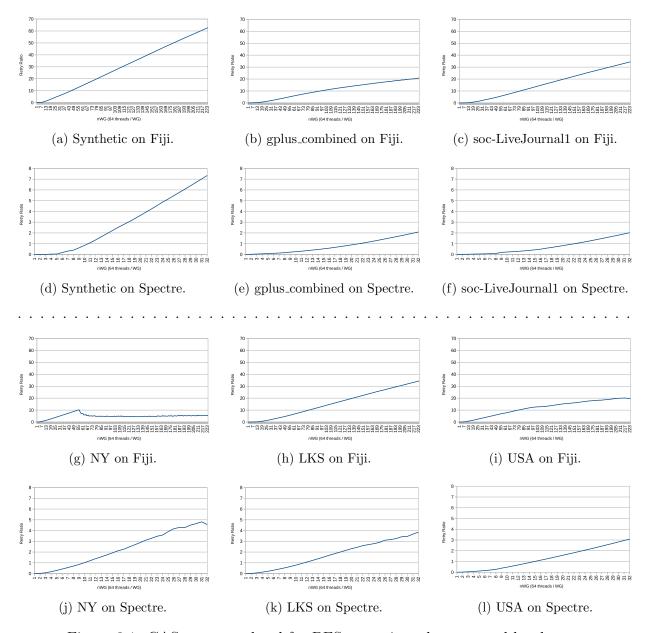

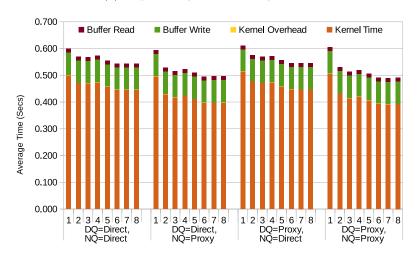

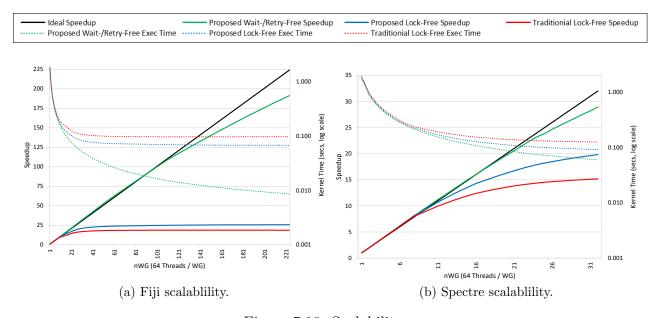

Figure 3.1. CAS retry overhead for BFS on various datasets and hardware.

Figure 3.2. Queue empty retry overhead for BFS on various datasets and hardware.

# 3.2 CAS failure

CAS operations can either succeed or fail. Each failure forces a retry until the operation eventually succeeds. In the best case all accesses succeed on their first attempt. In the worst case,  $\mathcal{O}(n^2)$  tries are required for n operations. As the number of threads increases, so does atomic competition and thus the number of retries. Experiments show

that the actual number of retires required for n competitors lies between n (best case) and  $\frac{n(n+1)}{2} = 1 + 2 + \cdots + n$  (worst case). In other words, one thread succeeds on its first attempt; another thread requires two attempts before it succeeds; etc. Figure 3.1 shows the CAS retry overhead for BFS (input data and experimental configuration are detailed in §6.2 (Input graph datasets)). Note that these experiments used a persistent thread model with a traditional lock-free CAS-based queue and a proxy thread. In general, contention increases as the number of threads increase (shown in terms of 64-thread workgroups on the x-axis). The y-axis shows the overhead ratio which is computed as:

CAS

$$retry\ ratio = \frac{\#CAS\ retries}{\#Successful\ CAS\ ops}$$

The retry ratio varies with dynamic parallelism and the number of persistent threads, which directly correlates to the number of CUs tested (e.g., the larger Fiji GPU has more CUs and thus requires more persistent threads to saturate the hardware than the smaller Spectre GPU). Generally the retry ratio increases as the number of threads increase. However, this is not always true. For example, in Figure 3.1g, retry overhead increases up to about 50 workgroups, then declines until about 70 workgroups and remains about level thereafter. The effects of CAS retries are also dataset dependent, with larger datasets tending to have higher overhead. When there are sufficient threads to saturate the CUs, CAS retries typically increase the number of queue operations by 4- to 60-fold. This strongly motivates a queue design that minimizes CAS failure retries. The proposed queue is retry-free for both enqueue and dequeue operations and always gives best case retry performance.

# 3.3 Empty queue checking

The second source of retries is caused by dequeue operations that experience a queue empty exception. This is an intrinsic characteristic of all traditional queues. For example, when a thread experiences a queue empty exception on a dequeue it must retry until data is enqueued. Figure 3.2 shows the dequeue queue empty retry overhead for BFS (input data configurations are detailed in §6.2 (*Input graph datasets*)). The overhead is expressed as:

Dequeue overhead =

$$\frac{\#Queue \ empty \ retries}{\#Successful \ dequeue \ ops}$$

The effects of the dequeue queue empty exception are highly dependent on a dataset's parallelism, and the number of persistent threads required to saturate the GPU. Retries present an intractable problem. When data parallelism is limited, the larger number of persistent threads required to saturate the GPU generate retries due to queue empty exceptions. On the other hand, when data parallelism is good, there are more threads competing for the queue and thus more CAS retries. The source of the retries does not matter. Either limits GPU acceleration.

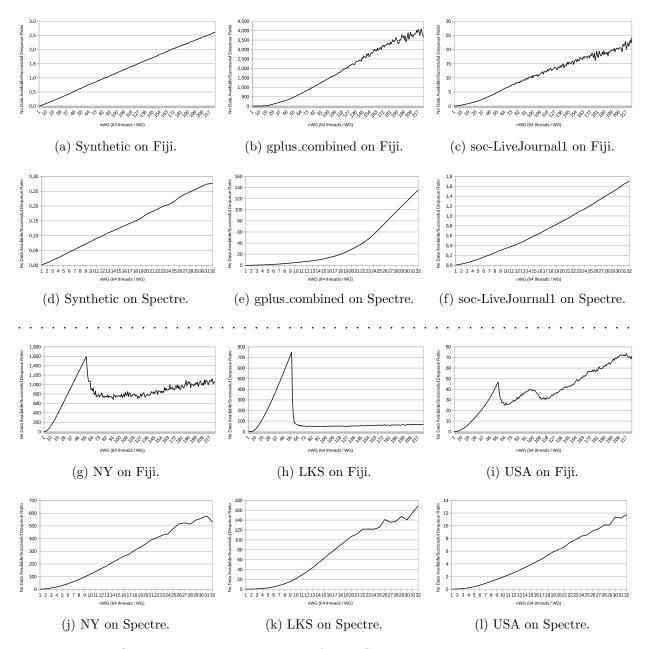

Figure 3.3. Wavefront lock-step execution.

#### 3.4 Lock-step execution

A GPU's lock-step execution model causes two design challenges. The first is "increased retries." If there are k hungry threads in a wavefront, all k threads will simultaneously attempt a dequeue forcing a worst case of  $\frac{k(k+1)}{2}$  retries. In a CPU environment this can be mitigated with a backoff technique [41], but in a GPU the programmer has no control over the GPU hardware schedulers. The second is "delayed progress." Figure 3.3 depicts a wavefront with a retry loop. The rectangular boxes represent its threads. The ellipse represents the retry loop (either due to CAS failure or a queue empty condition). The common Program Counter (PC) for all threads has progressed somewhere inside the retry loop. The shading represents competing threads that have not yet succeeded. The unshaded

threads are not competing either because they have succeeded or never needed to compete. The threads still competing force the non-competing threads into a NOP spin even though the non-competing threads are ready to proceed. The net effect is that no thread in the wavefront can progress until all competing threads succeed.

These problems are typically solved using a multi-level queue structure. The intraworkgroup level implements a queue for each workgroup and uses a proxy thread and local variables. Only the proxy thread accesses the queue, thus eliminating the need for atomic operations. The inter-workgroup level uses a shared global queue that brokers communication between workgroups. The brokering mechanism is typically either task stealing or task donation. In either case, a multi-level queue increases code length because it must detect when and where work needs to be stolen or donated.

The proposed queue design works differently. It is a monolithic queue. The intraworkgroup queue operations are handled by a proxy thread that access multiple queue entries in a single non-failing operation. Because all workgroups share the same queue, no interworkgroup brokering is required. The operations never fail, avoiding the adverse effects of kernel retry loops.

#### CHAPTER 4

# CONCURRENT QUEUE FOR PERSISTENT GPU THREADS

# 4.1 Concurrent queue for persistent GPU threads

A concurrent queue specialized for use as a GPU persistent thread scheduler should avoid the adverse effects of retries and lock-step execution. The proposed design avoids CAS retries by using a non-failing atomic fetch-add, and queue empty retries by using a data-not-arrived sentinel that is used to signal no data has been enqueued to a queue slot.

Each queue slot is initialized with either the data-not-arrived sentinel or initial task token(s) appropriate for the problem. For example, the BFS application initializes the first queue slot with the source vertex task token (i.e., vertex ID), and the remaining slots with the data-not-arrived sentinel. When a thread needing a task dequeues, it receives a unique queue slot index rather than an actual task token. This avoids detecting and handling a queue empty occurrence because a unique slot index is always available even though a task token may not yet have arrived.

Once in each work cycle, a thread checks its slot index for the arrival of a task token until a task token arrives. Since each thread has a unique slot index, no atomic operations are needed. When a task token arrives, the thread begins processing the task associated with the token. In the course of processing the task, newly independent task tokens can be enqueued. This overwrites the data-not-arrived sentinels, and the threads monitoring those slot indices detect task token arrival and begin their processing.

The use of an atomic fetch-add has another advantage. It can atomically advance the front (dequeue) and rear (enqueue) access variables by an arbitrary value. Thus, for the cost of a single atomic operation, an arbitrary number of slots can be reserved. This allows one thread in a wavefront (typically the first) to be designated as a proxy thread and to perform all enqueues and dequeues on behalf of all threads in the wavefront, including the proxy thread. This avoids the adverse effects of a wavefront's lock-step execution and the need for a multi-level queue design. The combination of a data-not-arrived sentinel and atomic fetch-add brings these features to the queue design:

- 1. Wait-free: An atomic fetch-add completes in bounded time. Thus, all threads make progress.

- 2. **Retry-free**: An atomic fetch-add never fails and, for dequeue operations, a slot index is always available even if a task token has not yet arrived at that slot. The only two causes of retries are removed, thus making both atomic and queue operations retry-free.

- 3. **Arbitrary-n**: An atomic fetch-add can reserve an arbitrary number of slots in each operation. This enables a proxy thread in each wavefront to provide queue services to all threads in the wavefront. The lock-step execution of the wavefront distributes queue slots to all affected threads in parallel.

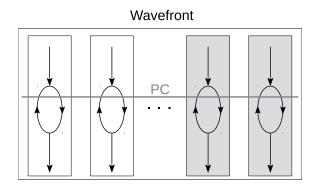

Figure 4.1. Proposed queue structure and operation.

### 4.2 Example Queue Operation

Figure 4.1 depicts the proposed queue structure. The data-not-arrived sentinels are shown as shaded entries. Rather than actually storing or retrieving task tokens, the enqueue and dequeue operations return the slot index where the task token will be stored (enqueue)

or is to be retrieved (dequeue). Suppose three threads are hungry (i.e., need work). The proxy thread performs:

```

StartSlotIndex = \mathtt{atomic\_fetch\_add}(Front, 3)

```

StartSlotIndex is set to 2, and Front atomically advances to 5. The first hungry thread is assigned slot index 2; the second hungry thread is assigned slot index 3; and the third hungry thread is assigned slot index 4. All slot assignments are done in parallel. The first two threads have data and start processing it immediately. The third client thread sees its data has not yet arrived and non-atomically checks again in each subsequent work cycle until data arrives. The following subsections detail each queue operation with a code snippet from the actual kernel.

Listing 4.1. Wait-free, retry-free, arbitrary-n dequeue.

```

// Get base index of the slots for hungry threads.

2

if (IsProxyThread) {

lnQueueSlotsNeeded = Ou;

3

lnThreadsEndingThisCycle = Ou;

4

}

5

6

if (ThreadNeedsWork) {

// Count all threads and assign each thread

9

// it's relative slot index

10

DequeueThreadSlotIndex=atomic_inc(&lnQueueSlotsNeeded);

11

}

12

13

// Get base index of the slots for hungry threads.

if (IsProxyThread && lnQueueSlotsNeeded)

15

lQueueSlotBaseIndex=atomic_add(&Parms->WorkQueueFront,

16

lnQueueSlotsNeeded);

}

17

18

19

if (ThreadNeedsWork) {

20

DequeueThreadSlotIndex += lQueueSlotBaseIndex;

21

ThreadNeedsWork = false;

22

QueueDataAvailable = false;

23 | \}

```

# 4.3 Wait-Free, Retry-Free, Arbitrary-n Dequeue

Listing 4.1 is the kernel code snippet of the wait-free, retry-free, arbitrary-n dequeue. It details how hungry threads are counted, queue slots are reserved, and how queue slots are distributed to the threads in parallel.

- Lines 2-5: lnQueueSlotsNeeded is zeroed by the proxy thread. It will contain a count of the number of hungry threads in the wavefront in a given work cycle.

- Lines 7–11: Each thread in the wavefront executes these lines in lock-step. If ThreadNeedsWork is true, the thread is hungry and will be assigned a slot. For each hungry thread, line 10 increments the number of hungry threads (lnQueueSlotsNeeded), and assigns the private variable DequeueThreadSlotIndex a slot index relative to the wavefront. Later, this will be converted to an actual queue slot index.

- Lines 14–17: The proxy thread reserves queue slots for all the hungry threads in the wavefront. To avoid unnecessary atomic contention, this is done only if there is at least one hungry thread. Line 16 performs the actual allocation. The base index of the reserved area is stored in lQueueSlotBaseIndex, and WorkQueueFront is atomically incremented by the number of slots allocated.

- Lines 19–23: Each hungry thread in the wavefront executes these lines in lock-step. Line 20 converts the thread's wavefront relative slot index to an actual queue index unique for this thread. Line 21 flags the thread as no longer hungry. Line 22 flags that the thread needs to check for data arrival.

#### 4.4 Data Arrival Details

Listing 4.2 is the kernel snippet that checks data arrival, which occurs when the thread's unique slot index no longer has the data-not-arrived sentinel. It details how a thread ensures its slot index is in bounds and how the thread checks for data arrival.

Listing 4.2. Data arrival.

```

1

if (!QueueDataAvailable)

2

// Check to see if data has arrived.

3

if ((DequeueThreadSlotIndex < QueueSize) &&

4

(QueueDataAvailable = (WorkQueue[DequeueThreadSlotIndex] !=

5

Missing))) {

6

7

// Work as arrived. Setup to process this node.

8

// No atomics are needed because this is the only

9

// thread accessing the slot or node.

10

11

// Get work token (index of node to process).

CurrentNodeIndex=WorkQueue[DequeueThreadSlotIndex];

12

13

14

// Get assigned node.

15

CurrentNode = Nodes[CurrentNodeIndex];

16

17

// Get starting edge for this node.

CurrentEdge = Edges + CurrentNode.StartingEdgeIndex;

18

19

20

// Get current node cost;

21

CurrentNodeCost = Costs[CurrentNodeIndex];

22

}

23

}

```

- Lines 1-23: This is executed only if data has not yet arrived, which is signaled by QueueDataAvailable.

- Lines 3-5: These lines perform the actual data arrival check. No atomic operations are required. They ensure the assigned slot index is within queue bounds and the data at the slot index is no longer the data-not-arrived sentinel. If data has arrived, it sets QueueDataAvailable to true.

- Lines 6-22: These lines are executed once just before node enumeration occurs. They form the enumeration prolog and setup for child enumeration.

Listing 4.3. Wait-free, retry-free, arbitrary-n enqueue.

```

1

// Initialize

if (IsProxyThread)

lnQueueSlotsNeeded = Ou;

3

4

٦.

5

6

// Count all newly discovered work in this cycle and assign slot index

7

// for each thread.

8 | if (nNewlyDiscoveredWork) {

EnqueueThreadSlotIndex =

9

10

atomic_add(&lnQueueSlotsNeeded, nNewlyDiscoveredWork);

11

}

12

13

// Reserve space in queue, and get base index.

if (IsProxyThread && lnQueueSlotsNeeded)

14

15

lQueueSlotBaseIndex = atomic_add(&Parms->WorkQueueRear, lnQueueSlotsNeeded);

}

16

17

18

if (nNewlyDiscoveredWork) {

19

// Convert slot index to base index within queue.

20

EnqueueThreadSlotIndex += lQueueSlotBaseIndex;

21

22

// Copy newly discovered work to the queue slot reserved for this

23

// work token.

24

for (uint32_t i = Ou; i < nNewlyDiscoveredWork; ++i) {</pre>

25

WorkQueue[EnqueueThreadSlotIndex++] = NewlyDiscoveredWork[i];

26

}

27

}

```

#### 4.5 Wait-free, retry-free, arbitrary-n enqueue

Listing 4.3 is the kernel snippet of the wait-free, retry-free, arbitrary-n enqueue. It details how the number of newly discovered task tokens are counted, how the slots are reserved, and how the task tokens are inserted into the queue in parallel.

- Lines 2-4: lnQueueSlotsNeeded is zeroed by the proxy thread. It will contain a count of the number of entries that need to be enqueued in this work cycle.

- Lines 8-11: Each thread in the wavefront executes these lines in lock-step. If a thread has enqueued new tasks, the number of new task tokens is counted. Each thread will

be assigned the number of slots needed. The base of that area relative to the wavefront is stored in EnqueueThreadSlotIndex. Later it will be converted to an actual queue index.

- Lines 14-16: The proxy thread reserves queue slots for all newly discovered task tokens in the wavefront. To avoid unnecessary atomic contention, this is done only if there is at least one newly discovered task token. Line 15 performs the actual allocation. The base index of the reserved area is stored in lQueueSlotBaseIndex, and WorkQueueRear is incremented by the number of slots allocated.

- Lines 18-27: Each thread with newly discovered tasks executes these lines in lock-step. Line 20 converts the wavefront relative start index to an actual queue index. Lines 24-26 copy each newly discovered task token index to its queue slot in lock-step. This overwrites the data-not-arrived sentinel. The thread monitoring this slot sees the arrival in its next work cycle when it executes lines 3-5 of Listing 4.2.

#### CHAPTER 5

#### KERNEL DESIGN

## 5.1 Kernel design

The chapter discusses the design issues of a data irregular kernel implementing an algorithm using the persistent thread model. This dissertation studies implementations using the persistent thread model and concurrent queue discussed and developed in the previous chapters. The kernel design must be sensitive to the architecture of the hosting GPU.

#### 5.2 Persistent thread considerations

Algorithm 2 on page 11 gives the persistent thread model. DoWorkUnit() performs the assigned task. However, there are no guarantees that wavefront threads are assigned tasks with homogeneous complexity. Thus, within a wavefront, longer running, more complex tasks delay faster running, less complex tasks because all threads within a wavefront run in lock-step. The effect is that the longest running DoWorkUnit() controls the execution time of the work cycles within wavefront. The slower running tasks NOP and do not accelerate the application.

In some cases tasks can be divided into subtasks of nearly uniform complexity. These subtasks are referred to as *chunks*. For instance, in BFS, a task processes a vertex by enumerating its children. Thus the complexity of a BFS task depends on the number of children, which can vary significantly. However, processing each child has roughly uniform complexity, and is a good candidate for a chunk. This dissertation studies the maximum number of chunks that should be processed in each work cycle.

# Algorithm 3 Chunked MCMT thread model.

- 1: Prolog()

- 2: for up to ChunkMax chunks do

- 3: DoChunk()

- 4: end for

- 5: Epilog()

## 5.3 Porting considerations

In many cases, a kernel begins life as a MCMT thread. Algorithm 3 gives a simplified view of the work performed by each thread. This corresponds to DoWorkUnit() on line 3 of Algorithm 2 on page 11. Prolog() sets up for chunk processing and may be trivially empty; DoChunk() processes the nearly uniformly complex chunks; and Epilog() handles any post-processing details.

## Algorithm 4 Chunked persistent thread model.

```

1: DataArrived \leftarrow false

2: NeedsToken \leftarrow true

3: while WorkRemains() do

if NeedsToken then

4:

QueueSlot \leftarrow GetWorkToken()

5:

NeedsToken \leftarrow false

6:

DataArrived \leftarrow false

7:

end if

8:

if !DataArrived then

9:

10:

Token \leftarrow Queue[QueueSlot]

if Token! = DataNotArrivedSentinel then

11:

DataArrived \leftarrow true

12:

Prolog()

13:

end if

14:

end if

15:

if DataArrived then

16:

for up to ChunkMax chunks do

17:

18:

DoChunk()

end for

19:

if last chunk then

20:

NeedsToken \leftarrow true

21:

Epilog()

22:

end if

23:

ScheduleNewlyDiscoveredTokens()

24:

25:

end if

26: end while

```

#### 5.4 The chunked persistent thread model

Algorithm 4 shows how chunking affects the persistent thread model. It shows how the components of Algorithm 3 are ported to the chunked persistent thread model. This dissertation studies optimal number of chunks to process in each work cycle. The following details the algorithm:

- 1. Lines 1-2: Initializes flags.

- 2. Lines 3-26: Defines a work cycle.

- 3. Lines 4-8: Dequeues a queue slot if work is needed. GetWorkToken() atomically dequeues work. This operation never fails, but the slot will have the data not arrived sentinel until data arrives (is enqueued).

- 4. **Lines 9-15:** This executes only if data has not yet arrived. It checks if its slot contains a valid token (i.e., does not contain the "data not arrived sentinel"). When arrival is detected, it sets the data arrival flag and executes the *Prolog* to setup for chunk processing. (See Algorithm 3 line 4.)

- 5. **Line 13:** An example of porting a BFS *Prolog()* function can be found in Appendix E lines 141-154.

- 6. **Lines 16-25:** This processes at most ChunkMax chunks, and helps keep the complexity of a work cycle roughly homogeneous. When the last chunk is processed, the task is complete and it flags a new token is needed. It executes an Epilog to do any cleanup necessary.

- 7. **Line 18:** An example of porting a BFS *DoChunk()* function can be found in Appendix E lines 162-201.

- 8. **Line 22:** An example of porting a BFS *Epilog()* function can be found in Appendix E lines 241-266.

- 9. Line 24: Enqueues any newly discovered independent tasks.

#### 5.5 Queue operation considerations

The arbitrary-n property of the proposed concurrent queue permits the use of a proxy thread to perform queue operations on behalf of all threads in the wavefront. When chunking is taken into consideration, not all threads in a wavefront will be hungry at the beginning of each work cycle. (Threads with unprocessed chunks will not become hungry until all chunks are processed.)

Thus, for each queue operation (dequeue or enqueue) there are two options – use a proxy thread or have each thread directly dequeue or enqueue. This dissertation studies the optimal queue operation configuration.

#### CHAPTER 6

#### EXPERIMENTAL SETUP

## 6.1 BFS driver application and its data dependency

Breadth First Search (BFS) was chosen to test the proposed concurrent queue for use as a persistent task scheduler. The classic top-down BFS algorithm (see Cormen et al. [10, pp 594–601] and Sedgewick [48, pp 395–398]) traverses a graph in a width-first manner starting from a source vertex. In a multi-threaded environment, all threads at any given level enumerate their children, and must complete their enumerations before next level processing can begin. This is the source of BFS data dependency and dynamic parallelism. The BFS data dependency can be stated as: enumeration of child vertices depends upon (i.e., must wait for) the completion of all vertex enumeration at the parent level. Enumerated children must be queued until all parent level processing completes. At that point the queued children can begin enumerating their children. This processing pattern continues until no more children are enumerated.

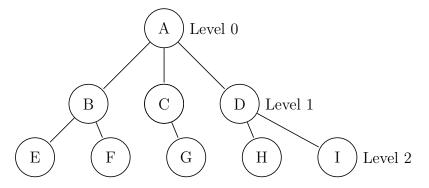

Figure 6.1. BFS traversal strategy.

For example, refer to Figure 6.1. Traversal starts at level 0 by enumerating node A's children (nodes B-D, which are at level 1). Nodes B-D cannot begin enumerating their

children until node A completes its enumeration. Level 1 processing of nodes B-D discovers nodes E-I. Enumeration of nodes E-I (at level 2) begins only after nodes B-D (at level 1) complete their enumeration. This process continues until enumeration at a level yields no new children.

The number of vertices available for processing at any given instant depends on the input dataset. Carefully chosen datasets allow for evaluation under a variety of data parallelism conditions. This ranges from a synthetic dataset that massively saturate threads to a small road map datasets that do not saturate the hardware.

| Dataset          | n Vertices  | n Edges    |     | Edges 1 | Per Vert | ex       |

|------------------|-------------|------------|-----|---------|----------|----------|

| Dataset          | ii vertices | n Euges    | Min | Max     | Avg      | Std      |

| gplus_combined   | 107,614     | 30,494,866 | 0   | 49,041  | 283.4    | 1,245.18 |

| soc-LiveJournal1 | 4,847,571   | 68,993,773 | 0   | 20,293  | 14.2     | 36.08    |

Table 6.1. Selected SNAP social media graph datasets statistics.

| Dataset Description |                        | n Vertices              | n Edges    | Edges Per Vertex |     |        |        |

|---------------------|------------------------|-------------------------|------------|------------------|-----|--------|--------|

| Dataset             | Description            | Description in vertices |            | Min              | Max | Avg    | Std    |

| USA-road-d.BAY      | San Francisco Bay Area | 321,270                 | 800,172    | 1                | 7   | 2.4907 | 0.9916 |

| USA-road-d.CAL      | California and Nevada  | 1,890,815               | 4,657,742  | 1                | 8   | 2.4634 | 0.9464 |

| USA-road-d.COL      | Colorado               | 435,666                 | 1,057,066  | 1                | 8   | 2.4263 | 0.9424 |

| USA-road-d.CTR      | Central USA            | 14,081,816              | 34,292,496 | 1                | 9   | 2.4352 | 0.9525 |

| USA-road-d.E        | Eastern USA            | 3,598,623               | 8,778,114  | 1                | 9   | 2.4393 | 0.9487 |

| USA-road-d.FLA      | Florida                | 1,070,376               | 2,712,798  | 1                | 8   | 2.5344 | 0.9627 |

| USA-road-d.LKS      | Great Lakes            | 2,758,119               | 6,885,658  | 1                | 8   | 2.4965 | 0.9531 |

| USA-road-d.NE       | Northeast USA          | 1,524,453               | 3,897,636  | 1                | 9   | 2.5567 | 0.9551 |

| USA-road-d.NW       | Northwest USA          | 1,207,945               | 2,840,208  | 1                | 9   | 2.3513 | 0.9463 |

| USA-road-d.NY       | New York City          | 264,346                 | 733,846    | 1                | 8   | 2.7761 | 0.9814 |

| USA-road-d.USA      | Full USA               | 23,947,347              | 58,333,344 | 1                | 9   | 2.4359 | 0.9467 |

| USA-road-d.W        | Western USA            | 6,262,104               | 15,248,146 | 1                | 9   | 2.4350 | 0.9324 |

Table 6.2. The  $9^{th}$  DIMACS implementation challenge dataset statistics

## 6.2 Input graph datasets

For BFS, the degree of irregularity changes depending on the input graph. We selected six diverse graph datasets in three categories as test input data. The three categories are:

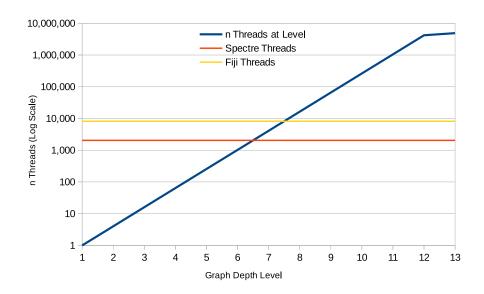

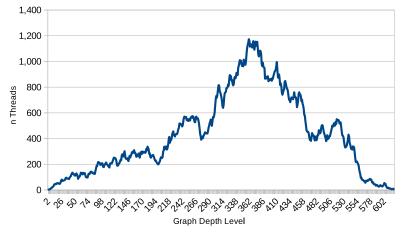

• Synthetic: To analyze the scalability of the proposed persistent scheduler without

the influence of other factors, we constructed a synthetic dataset designed to keep all persistent threads busy. This ensures kernel performance differences are due only to thread contention and not simply idle threads. Figure 7.1 on page 41 shows the number of vertices available for thread assignment at each level. The test synthetic dataset has 10,485,760 vertices, with a fanout of 4 edges per vertex. After the first 8 levels, both the Spectre and Fiji GPUs are fully saturated. This effectively removes lack of work as source of poor acceleration. It exposes how performance and scalability is affected by the various algorithms, hardware and thread counts.

- Social media: Social media graphs and their processing speed are becoming increasingly important as Social Networking Service (SNS) gets popular. We selected two representative social media datasets [30] as detailed in Table 6.1. Typically social media graphs have a large edge fanout<sup>1</sup>, but are not very deep. The two datasets cover small- and medium-sized social media graphs. Figure 7.3a on page 43 and Figure 7.4a on page 45 show this property graphically as well as its available dynamic parallelism.

- Roadmap: Roadmap graphs typically have a fanout of between 2 and 3 but are deep. Table 6.2 shows the roadmap datasets available in the 9<sup>th</sup> DIMACS implementation challenge [17]. The datasets selected for analysis are shaded in gray. They were selected so that they cover a broad spectrum of roadmap graphs. Because roadmap graphs are so deep, the number of vertices available at any given level is smaller than in social media graphs. Figure 7.5a on page 47, Figure 7.6a on page 49 and Figure 7.7a on page 51 show this characteristic graphically. Only the USA dataset saturates the lowend GPUs with a small number of CUs (e.g., AMD's Spectre GPU) to any significant degree. Thus, the lack of tasks (i.e., insufficient data parallelism) is a limiting factor in this category.

<sup>&</sup>lt;sup>1</sup>The large fanout of social media graphs present a design challenge. As edges are discovered, they must be stored in local or private memory before being queued. Private and local memory are scarce resources that limit the number of edges that can be processed. The proposed queue and the Rodinia benchmark avoid this issue, but it is an issue for the CHAI BFS benchmark.

#### 6.3 Confidence interval

From a statistical perspective, the average,  $\overline{X}$ , described above is actually an estimate of the true population mean,  $\mu$ . Some expression of confidence that  $\mu$  lies within a margin of error about  $\overline{X}$  is required. The margin of error about  $\overline{X}$  can be expressed as  $\overline{X} \pm E$ , where E is the confidence interval. The question becomes what confidence interval assures  $\mu$  lies within  $\overline{X} \pm E$  with probability p. This is a well-known problem with solution:

$$\overline{X} \pm \frac{Z_p \sigma}{\sqrt{n}}$$

,

Where  $Z_p$  is the Z-value corresponding to probability p,  $\sigma$  is the population standard deviation, and n is the sample size of  $\overline{X}$ . When  $\sigma$  is not known, the sample standard deviation, s, is used.

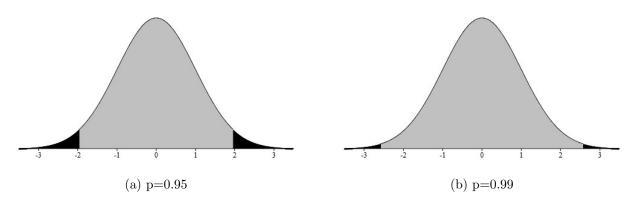

Figure 6.2. Area under Z PDF for p=0.95 and p=0.99

Two common  $Z_p$  are  $Z_{0.95} = 1.96$  and  $Z_{0.99} = 2.576$ . Figure 6.2 shows the excluded areas under the Probability Distribution Function (PDF) in black. The areas in gray are the normalized 0.95% and 0.99% intervals. The term  $\frac{\sigma}{\sqrt{n}}$  can be viewed as converting the normalized interval to the observed distribution's interval with sample size n and standard deviation s.

This dissertation uses  $Z_{0.95}$  and estimates  $\sigma$  with s.  $\overline{X}$  is computed using 100 samples.

Thus, the confidence interval for  $\overline{X}$  becomes:

$$E = \frac{1.96s}{\sqrt{100}} = \frac{1.96s}{10} = 0.196s$$

The concise expression of the confidence interval is: 95% of the time, the population mean  $\mu$  is within the interval:

$$\overline{X} \pm \frac{0.196s}{10} \tag{6.1}$$

It is clear from Equation 6.1 that reducing s and/or increasing n tightens the confidence interval. Increasing n increases run times, which can be expensive for large datasets. Using one iteration to warm-up the GPU can reduce s at very little cost. Thus, 1 iteration is dedicated to warm-up before doing the 100 samples.

For our computations, the confidence interval in Equation 6.1 is very small. Graphically they amount to little more than a thin line immediately above and below the computed means. Because they contribute so little to the graphical presentation, they are shown only for Figure 7.2 on page 42 and dropped thereafter.

While not shown graphically, the confidence intervals have an effect on the conduct of the experiments as detailed in the next section.

#### 6.3.1 Confidence interval considerations

The tighter the confidence interval about  $\overline{X}$ , the better the probability that  $\overline{X}$  is closer to the true mean  $\mu$ . Examining Equation 6.1 yields the three ways the confidence interval can be tightened:

1. Use a less stringent  $\mathbb{Z}_p$ : For example the interval about the mean in Figure is 6.2a is tighter about the mean than for Figure 6.2b. However, changing  $\mathbb{Z}_p$  is ultimately unproductive from the perspective of achieving a tighter confidence interval where  $\mu$  is in that interval with some fixed probability. (A reduced  $\mathbb{Z}_p$  simply trades off a narrower

confidence interval for an increase in the probability of an error.)

- 2. **Increasing** n: As n increases, so does its square root, making the confidence interval smaller. Because the square root diminishes the effect of an increasing n, it is not a good first choice. The additional samples increase benchmark runtime.

- 3. Reducing s: There are several ways to control s. One easy trick is to ensure the GPU is not working on any other problem (e.g., the Graphical User Interface (GUI)). Another technique is to avoid code constructions that intrinsically vary in execution time. For instance, if threads compete for an atomic variable using a CAS, only one thread at a time will succeed and force the others to retry. There is no accurate way to predict how long it will take to succeed.

The experiments performed in this dissertation quiesce the GUI, and only one CAS is performed, but it is used in a way that does not involving any retrying.

#### 6.4 Programming language and test hardware

We chose an OpenCL 2.0 programming environment because it is an established, non-proprietary cross platform industry standard. However, porting to CUDA should not lose any intellectual merit.

All experiments were performed on two hardware platforms: a powerful high-end discrete GPU (AMD's Fiji), and a low-end integrated GPU with shared CPU-GPU memory (AMD's Spectre) The Spectre GPU has 8 CUs and shares memory with the CPU. The Fiji GPU has 56 CUs and separate device memory.

We used a workgroup size of one wavefront (64 threads) to avoid barriers, and launched 4 workgroups on each CU. This resulted in 2,048 persistent threads (32 workgroups of 64 threads) on the Spectre, and either

1. 14,336 persistent threads (224 workgroups of 64 threads) on the Fiji for scaling experiments, or

2. 8,192 persistent threads (128 workgroups of 64 threads) for optimal queue method experiments.

.

#### CHAPTER 7

## ANALYSIS OF PROPOSED QUEUE

This chapter analyzes the proposed queue from three perspectives:

- 1. Optimal queuing method (direct or proxy) and chunk size,

- 2. Scalability, and

- 3. Effect of the arbitrary-n and retry-free properties on performance.

## 7.1 Optimal queuing method and chunk size

For this analysis, one experiment was performed for each of the six selected datasets. Each experiment varies the chunk size from 1 to 8 for each of the 4 possible queuing methods. To obtain a data point, for each configuration BFS was run 100 times and the results averaged. The smaller Spectre GPU was configured for 32 workgroups of 64 threads, for a total of 2,048 persistent threads. The larger Fiji GPU was configured for 128 workgroups of 64 threads, for a total of 8,192 threads.

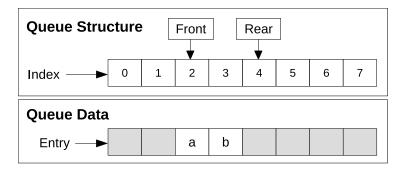

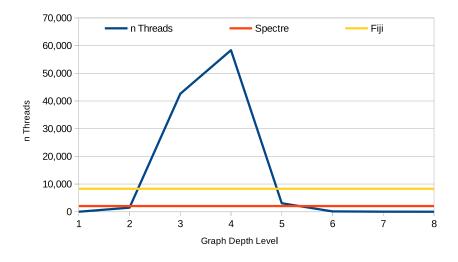

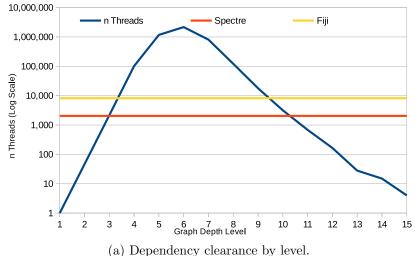

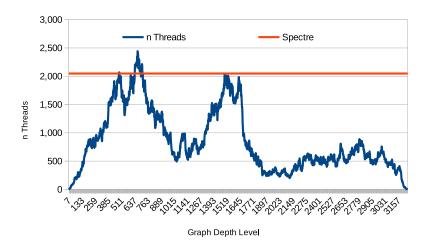

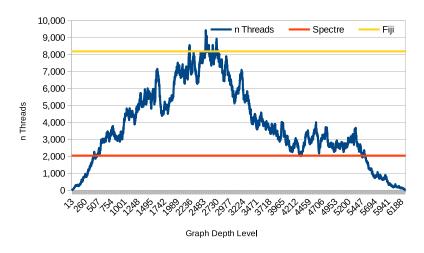

Figure 7.1. Synthetic graph dependency clearance by depth level.

## 7.1.1 Synthetic dataset optimal queuing method and chunk size

Figure 7.1 shows the number of available nodes at the start of each depth level. The number of nodes available is the direct result of the dependencies cleared at each level. The choice of 4 edges per node causes a rapid expansion in available nodes and heavily favors a chunk size of of 4, which is experimentally verified. The first 7 levels each finish in one work cycle. By level 8, there are more nodes available than there are persistent threads for both the Spectre and Fiji GPUs. After level 8, the number of nodes continues to exponentially increase resulting in massively more available work than persistent threads.

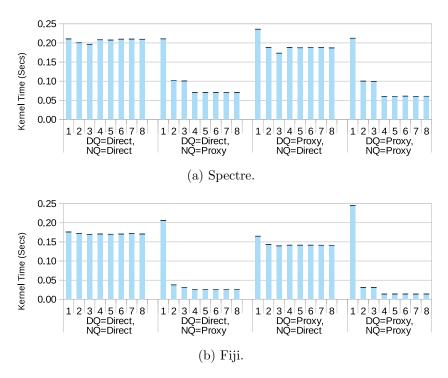

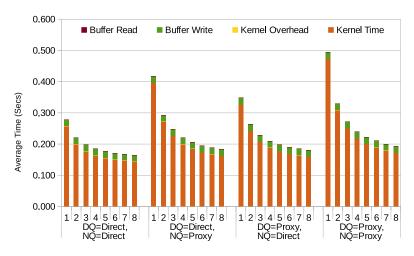

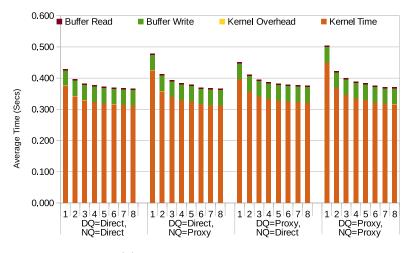

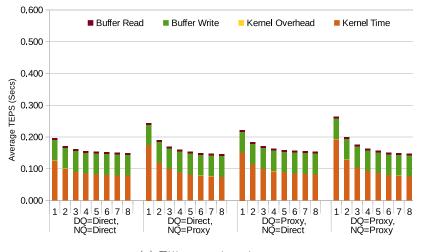

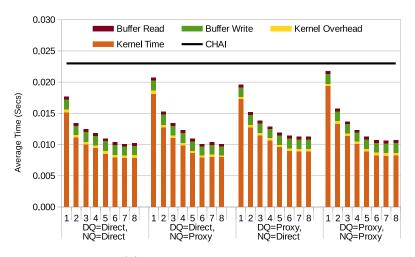

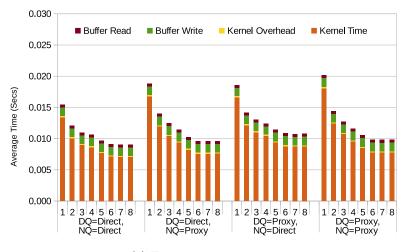

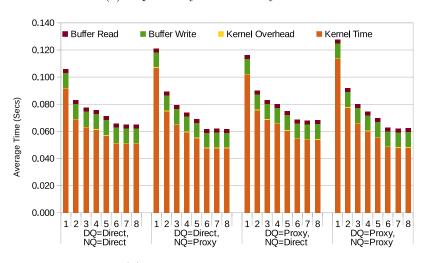

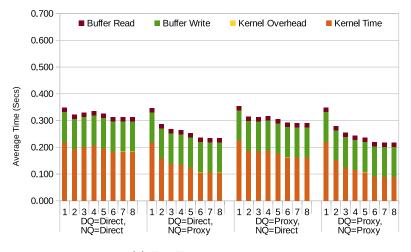

Figure 7.2 shows the performance of queuing algorithm by chunk size for the Spectre (Figure 7.2a) and the Fiji (Figure 7.2b) devices. For the test dataset, the proxy enqueue/dequeue queuing algorithm is the best for both devices. Our observation is as follows:

- The confidence intervals are shown at the top of each bar. The intervals were very tight and appear only as a dark mark at the top of each bar.

- Generally the Fiji outperformed the Spectre except for the proxy enqueue/dequeue queuing algorithm with a chunk size of 1.

Figure 7.2. BFS kernel execution time by device/queuing algorithm/chunk size (synthetic data).

- Once the chunk size reaches 4, execution time does not change. This is an artifact of choosing 4 edges per node for the test data and is not generally true for all workloads.

- For both devices, the proxy enqueue/dequeue queuing algorithm with a chunk size of 4 is best.

(a) Dependency clearance by level.

(b) Spectre execution times.

(c) Fiji execution times.

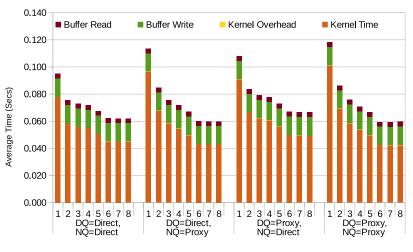

Figure 7.3. gplus\_combined analysis.

## 7.1.2 gplus\_combined dataset optimal queuing method and chunk size

This dataset consists of "circles" from Google+. The Google+ data was collected from users who had manually shared their circles using the "share circle" feature. Figure 7.3 gives the analysis for this dataset.

Figure 7.3a shows the number of threads cleared at each dependency level. It requires 8 levels to process. Figure 7.3b breaks down the execution times by queuing algorithm and chunk size for the Spectre GPU. Figure 7.3c breaks down the execution times by queuing algorithm and chunk size for the Fiji GPU.

Both the Spectre's 2,048 threads, and the Fiji's 8,192 threads are significantly saturated. Ordinarily this would favor proxy access. However, chunking reduces dequeue contention. Further, refer to Table 6.1 on page 34 and notice there are over 100 times more edges than nodes. Thus it is likely a node can be discovered via many edges. Only the first discovery results in an enqueue. The overall effect is reduced contention, marginally favoring direct enqueue/dequeue.