# EXPLORATION INTO THE PERFORMANCE OF ASYMMETRIC D-ARY HEAP-BASED ALGORITHMS FOR THE HSA ARCHITECTURE

A Thesis presented in partial fulfillment of requirements for the degree of Master's of Science in the Department of Computer and Information Science The University of Mississippi

> by Stephen Blake Adams

May 2014

Copyright Stephen Blake Adams 2014 ALL RIGHTS RESERVED

### ABSTRACT

Heterogeneous computing is a fairly recent trend in both hardware and software design; based around identifying the opportunities presented by utilizing all available hardware components in a computing system to perform a computationally intensive task in the most efficient way possible. One incredibly interesting field of the heterogeneous computing paradigm is general purpose computing on the graphic processing unit. General purpose computing on the graphic processing unit consists of utilizing the hardware capabilities of the graphic processing unit to perform computationally intensive tasks which exhibit many opportunities for parallel execution. While many vector or matrix-based data structures and algorithms showcase the performance benefits through this computing paradigm, many graph/tree-based data structures and algorithms are understood to be unsuitable for the nature of the GPGPU computing paradigm.

The *d*-heap, a tree-based data structure, has undergone many design changes to take advantage of different trends in computer technology. The introduction of the memory hierarchy and the popularity of varying levels of data caches presented the development of the implicit d-heap which ensured that child nodes would not span across cache blocks. Based upon the general structural design of the implicit *d*-heap, is the asymmetric *d*-heap, introduced by Brian Vinter and Weifeng Liu. The asymmetric *d*-heap seeks a heterogeneous solution to the common heap data structure that utilizes both the throughput oriented processing cores of the graphic processing unit and the latency oriented processing cores of the computing solutions and the possible performance benefit opportunities of a truly heterogeneous system in understanding the nature of the *ad*-heap data structure which is designed specifically for the tightly coupled THC(Truly Heterogeneous Computing) architectural concept promoted

by the HSA (Heterogeneous Systems Architecture) Foundation. Using the batch k-selection algorithm, the behavior behind the design of the ad-heap presents a great deal of interesting information which can be utilized in the design of future heterogeneous solutions for existing data structures and associated algorithms which would normally not benefit from current GPGPU technology. Using both a loosely coupled discrete-GPU based experimental platform and a more tightly-coupled accelerated processing unit-based platform; we explore many of the limitations concerning the asymmetric d-heap design by understanding the performance and behavior of the design on both platforms. We do so by presenting a more accurate and practical implementation of the ad-Heap design for both experimental platforms and addressing the performance metrics and limitations uncovered by the series of experiments. By understanding these limitations and analyzing the different aspects of the general design; we begin to understand many of the design decisions and other general details that have to be considered when distributing the computational workload between both devices on a HSA-based architecture.

### TABLE OF CONTENTS

| ABSTRACT     |                                                                          | ii |

|--------------|--------------------------------------------------------------------------|----|

| LIST OF FIGU | VRES                                                                     | vi |

| A BRIEF INTI | RODUCTION TO HETEROGENEOUS COMPUTING                                     | 1  |

| 1.1          | The Computing Paradigm of Heterogeneous Computing                        | 1  |

| 1.2          | Recent Development Trends in Heterogeneous Computing $\ldots$ .          | 2  |

| THE BASICS ( | OF GENERAL PURPOSE PROGRAMMING WITH THE GPU                              | 5  |

| 2.1          | Understanding the Hardware Characteristics of the CPU                    | 5  |

| 2.2          | Leveraging the Hardware Characteristics of the GPU for General Pur-      |    |

|              | pose Programming                                                         | 7  |

| 2.3          | Modern Parallel Programming Platforms for GPGPU Programming              | 9  |

| 2.4          | Adapting a Serial Executing Application for GPU Hardware                 | 12 |

| 2.5          | Understanding the OpenCL Memory Model                                    | 15 |

| 2.6          | Summarizing the Basics of GPGPU Programming with OpenCL $$ .             | 18 |

| ADAPTING T   | HE HEAP FOR HETEROGENEOUS COMPUTING                                      | 20 |

| 3.1          | Addressing the Nature and Design of the Heap Data Structure $\ .$ .      | 21 |

| 3.2          | Adapting the Heap Data Structure for Latest Trends in Technology .       | 25 |

| 3.3          | The $ad$ -Heap, Designed for Truly Heterogeneous Systems $\ldots \ldots$ | 26 |

| ADDRESSING   | THE LIMITATIONS OF GPU COMPUTING WITH HSA ARCHITEC-                      |    |

| TURE         |                                                                          | 31 |

| 4.1          | Limitations of Current GPU Hardware/Software Solutions                   | 31 |

| 4.2         | The Hardware and Software Design of the HSA Solution                         | 33  |

|-------------|------------------------------------------------------------------------------|-----|

| 4.3         | Truly Heterogeneous Computing Solution and its Importance in Ben-            |     |

|             | efiting Modern Algorithms                                                    | 35  |

| EXPLORING 7 | THE AD-HEAP-BASED BATCH K-SELECTION BEHAVIOR                                 | 36  |

| 5.1         | Characteristics of the Batch $k$ -Selection Algorithm $\ldots \ldots \ldots$ | 36  |

| 5.2         | Introducing the Physical Experimental Platforms                              | 40  |

| 5.3         | Basic CPU Implementation of Heap Operations                                  | 43  |

| 5.4         | CPU Update-Key Operation Results                                             | 47  |

| 5.5         | CPU Batch k-Selection Algorithm Results                                      | 49  |

| 5.6         | Exploring the $ad$ -Heap Execution Characteristics on the GPU                | 56  |

| 5.7         | Exploring the Batch $ad$ -Heap Execution Characteristics on the GPU          | 68  |

| UNDERSTANI  | DING AND COMPARING THE AD-HEAP-BASED BATCH K-SELECTI                         | [ON |

| BEHAVIOR    |                                                                              | 75  |

| 6.1         | Practicality of the <i>ad</i> -heap data structure                           | 77  |

| 6.2         | The <i>ad</i> -heap as a design initiative.                                  | 80  |

| BIBLIOGRAPH | ΗΥ                                                                           | 82  |

| VITA        |                                                                              | 85  |

## LIST OF FIGURES

| 2.1  | Simple Loosely Coupled GPGPU Platform Diagram                                                                                                                                     | 8  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Relationship Of Work-Items/Work-Groups                                                                                                                                            | 11 |

| 2.3  | OpenCL Memory Model                                                                                                                                                               | 17 |

| 3.1  | Basic Heap Data Structure Graphical Representation                                                                                                                                | 22 |

| 3.2  | Heap Data Structure Indexing Scheme                                                                                                                                               | 24 |

| 3.3  | The Implicit <i>d</i> -ary heap                                                                                                                                                   | 25 |

| 3.4  | ad-Heap Data Structure                                                                                                                                                            | 28 |

| 5.1  | Batch k-Selection Algorithm                                                                                                                                                       | 37 |

| 5.2  | Data Set Details and associated size                                                                                                                                              | 38 |

| 5.3  | Algorithm-Specific Statistics                                                                                                                                                     | 40 |

| 5.4  | Experimental Platform Information                                                                                                                                                 | 41 |

| 5.5  | 8-Heap CPU Update Key Performance                                                                                                                                                 | 47 |

| 5.6  | 16-Heap CPU Update Key Performance                                                                                                                                                | 47 |

| 5.7  | 32-Heap CPU Update Key Performance                                                                                                                                                | 48 |

| 5.8  | 64-Heap CPU Update Key Performance                                                                                                                                                | 48 |

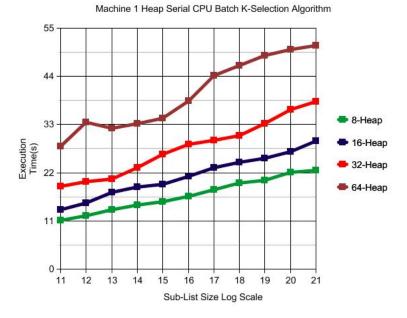

| 5.9  | Machine 1 $k$ -Selection Algorithm Results $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                         | 49 |

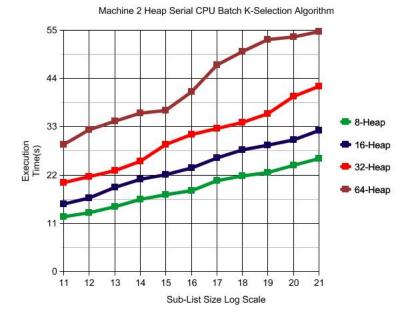

| 5.10 | Machine 2 $k$ -Selection Algorithm Results $\ldots \ldots \ldots$ | 50 |

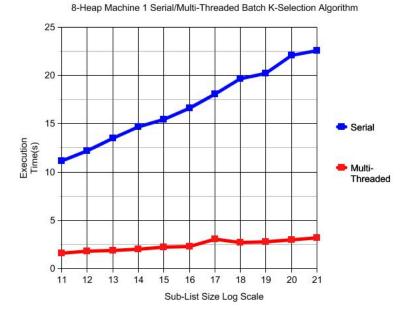

| 5.11 | Machine 1 $k$ -Selection 8-Heap Multi-Threaded/Serial Comparison                                                                                                                  | 51 |

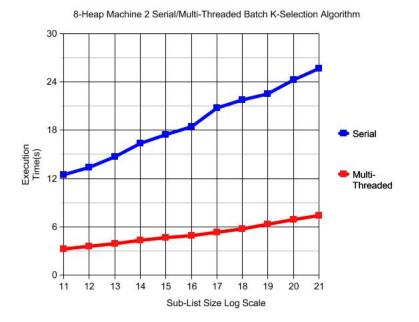

| 5.12 | Machine 2 $k$ -Selection 8-Heap Multi-Threaded/Serial Comparison                                                                                                                  | 51 |

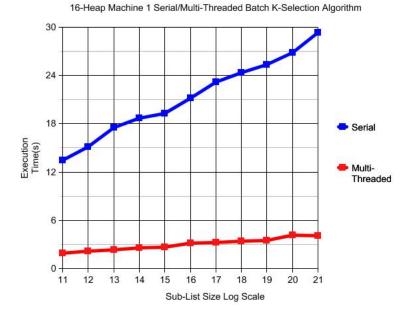

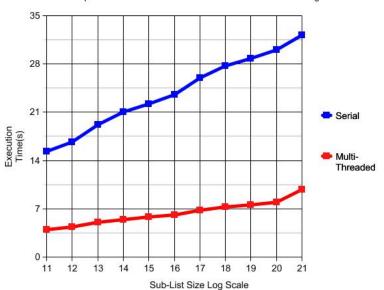

| 5.13 | Machine 1 $k\mbox{-Selection}$ 16-Heap Multi-Threaded/Serial Comparison                                                                                                                                                     | 52 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.14 | Machine 2 $k$ -Selection 16-Heap Multi-Threaded/Serial Comparison                                                                                                                                                           | 52 |

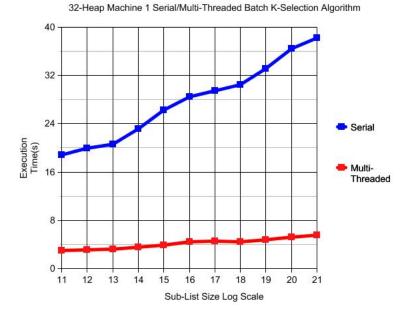

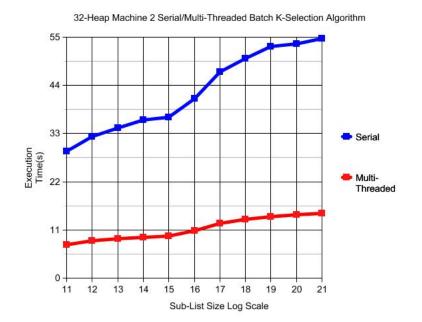

| 5.15 | Machine 1 $k-$ Selection 32-Heap Multi-Threaded/Serial Comparison                                                                                                                                                           | 53 |

| 5.16 | Machine 2 $k$ -Selection 32-Heap Multi-Threaded/Serial Comparison                                                                                                                                                           | 53 |

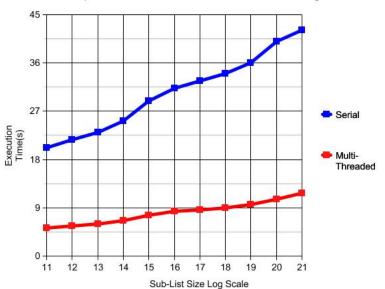

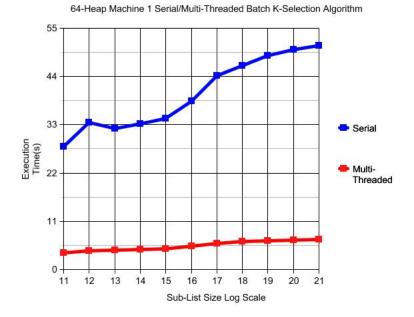

| 5.17 | Machine 1 $k$ -Selection 64-Heap Multi-Threaded/Serial Comparison                                                                                                                                                           | 54 |

| 5.18 | Machine 2 $k$ -Selection 64-Heap Multi-Threaded/Serial Comparison                                                                                                                                                           | 54 |

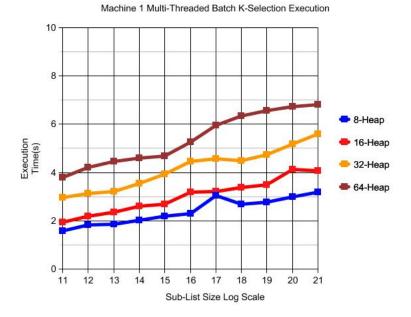

| 5.19 | Comparing the execution time of different values of $d$ using the multi-threaded implementation on Machine $1 \dots $ | 55 |

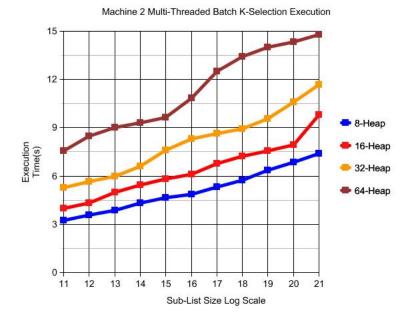

| 5.20 | Comparing the execution time of different values of $d$ using the multi-threaded implementation on Machine 2                                                                                                                | 56 |

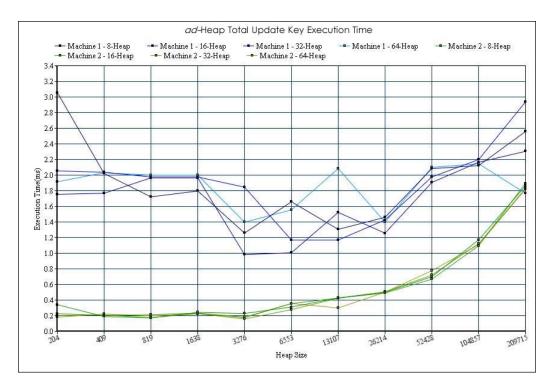

| 5.21 | Total Update Execution Time <i>ad</i> -heap                                                                                                                                                                                 | 59 |

| 5.22 | 8-Heap <i>ad</i> -Heap <i>Update-Key</i> Operation Performance                                                                                                                                                              | 60 |

| 5.23 | 16-Heap <i>ad</i> -Heap <i>Update-Key</i> Operation Performance                                                                                                                                                             | 60 |

| 5.24 | 32-Heap <i>ad</i> -Heap <i>Update-Key</i> Operation Performance                                                                                                                                                             | 60 |

| 5.25 | 64-Heap <i>ad</i> -Heap <i>Update-Key</i> Operation Performance                                                                                                                                                             | 61 |

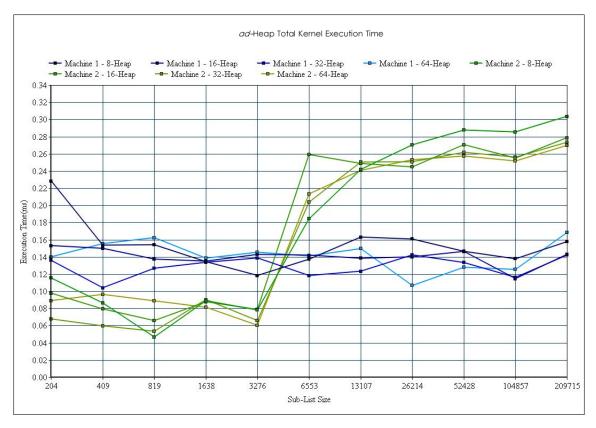

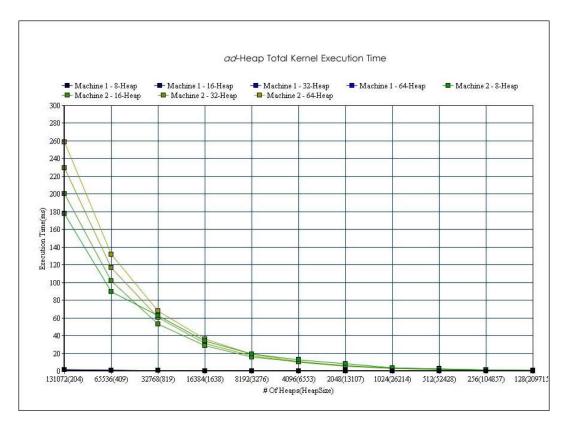

| 5.26 | Total Kernel Execution Time Comparison Between Both Platforms                                                                                                                                                               | 62 |

| 5.27 | 8-Heap <i>ad</i> -Heap Kernel Execution Times                                                                                                                                                                               | 63 |

| 5.28 | 16-Heap <i>ad</i> -Heap Kernel Execution Times                                                                                                                                                                              | 63 |

| 5.29 | 32-Heap <i>ad</i> -Heap Kernel Execution Times                                                                                                                                                                              | 63 |

| 5.30 | 64-Heap <i>ad</i> -Heap Kernel Execution Times                                                                                                                                                                              | 64 |

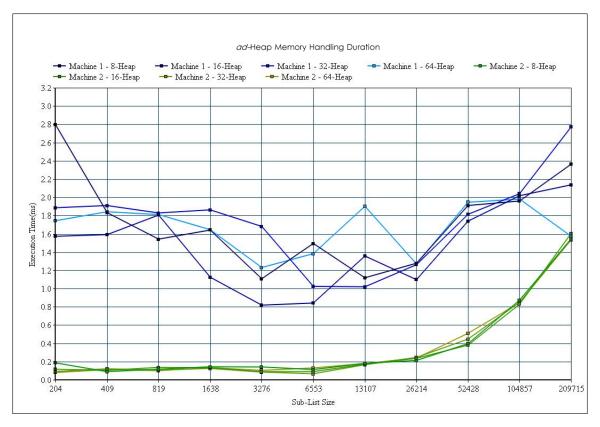

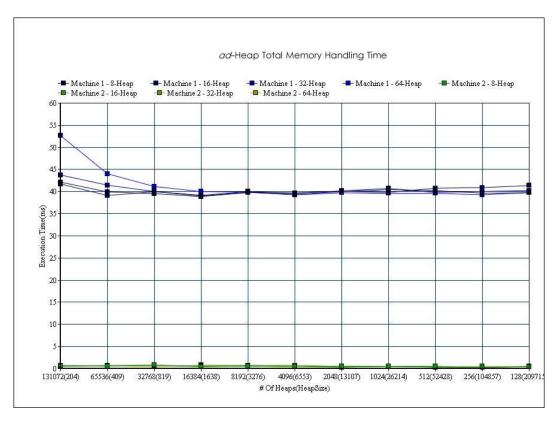

| 5.31 | Total Memory Handling Time Comparison Between Both Platforms                                                                                                                                                                | 65 |

| 5.32 | 8-Heap <i>ad</i> -Heap Memory Handling Times                                                                                                                                                                                | 65 |

| 5.33 | 16-Heap <i>ad</i> -Heap Memory Handling Times                                                                                                                                                                               | 66 |

| 5.34 | 32-Heap <i>ad</i> -Heap Memory Handling Times                                             | 66 |

|------|-------------------------------------------------------------------------------------------|----|

| 5.35 | 64-Heap <i>ad</i> -Heap Memory Handling Times                                             | 66 |

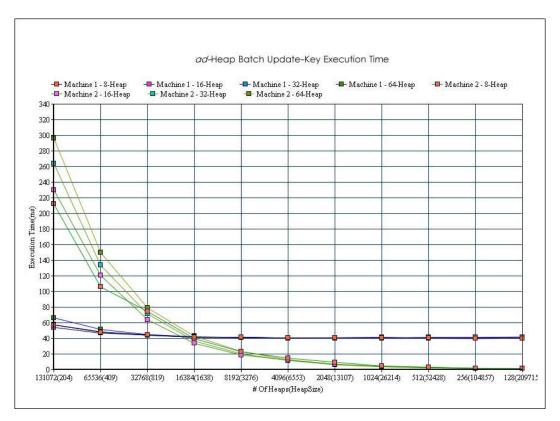

| 5.36 | Total <i>Update-Key</i> Operation Execution Time between both experimental plat-<br>forms | 70 |

| 5.37 | Total Kernel Execution Time between both experimental platforms                           | 71 |

| 5.38 | Total Memory Handling Time between both experimental platforms $\ldots$ .                 | 72 |

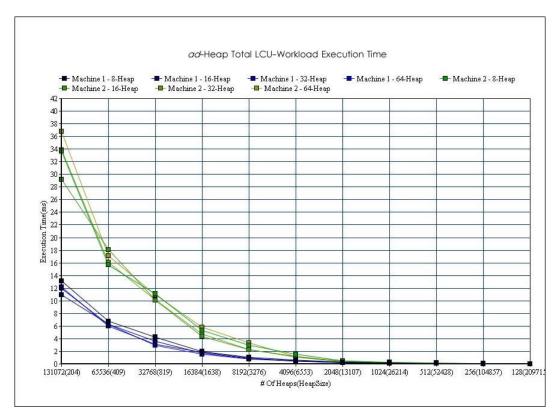

| 5.39 | Total LCU-Workload Time between both experimental platforms                               | 73 |

### CHAPTER 1

### A BRIEF INTRODUCTION TO HETEROGENEOUS COMPUTING

By taking the very basic meaning of Heterogeneous(heter-o-ge-ne-ous), defined in the Merriam-Webster dictionary as "made up of parts that are different", and Computing(com-put-ing) defined by the same source as "to determine especially by mathematical means" (Merriam-Webster Online (2009)); we can very easily understand the primary motivation behind the popular computing paradigm described by Heterogeneous Computing. The typical computing platform is a fascinating myriad of hardware components working closely together to produce a solution to a given problem. Even on such a minuscule level, each individual logical gate has a different purpose, a different methodology behind their execution mechanism. Given these differences, each logical gate within an integrated circuit execute to produce a common synergistic solution. Synergy is very simply described as the instance where the combined production of all parts working together is greater than the sum weight of those same parts. Though an important trait in successful business management environments, synergy is also extremely important on a fundamental level of computer architecture. Synergy is a term that perfectly characterizes the purpose of heterogeneous computing.

### 1.1 The Computing Paradigm of Heterogeneous Computing

The computing device is comprised of many electronic hardware components. A heterogeneous computing solution seeks to utilize all of these components in an efficient manner which best meets the goal of the application or the programmer of the application. The programmer must seek a solution to his application which best utilizes these components in a synergistic manner. Application performance goals may vary from platform to platform depending on both the user-base and the hardware requirements. Some solutions may demand the best execution performance for a specific algorithm or method while other solutions may utilize an optimal scheduling heuristic to ensure that the overall hardware platform is fully utilized and all tasks are receiving enough processing power to balance their computations at an optimal level. With the recent popularity in mobile computing electronics, a primary goal of many heterogeneous computing solutions have been to effectively perform at an optimal level while efficiently throttling the overall power consumption of the device. Given the limited power resources of modern mobile electronics, the ability to produce the application results while maintaining a suitable power consumption level has been crucial in both software and hardware design. Heterogeneous computing is both a software and hardware-based paradigm with much ongoing research in both areas.

### 1.2 Recent Development Trends in Heterogeneous Computing

Recent research and development has resulted in a interesting concept titled as Heterogeneous System Architecture (HSA), a topic which will ultimately be discussed in a later chapter. Many hardware manufacturers such as AMD, ARM, and Samsung have invested a large amount of development effort in heterogeneous hardware platforms which locate both the graphic accelerator compute units (i.e., GPUs) and the low latency central processing cores (i.e., CPUs) on the same silicon die. The two groups of processing cores share either the same system memory directly or the same last-level cache within the hardware design. By situating both hardware components on the same silicon die, the PCI-E bus which is used for communication between the devices is removed, thus removing a possible performance bottleneck (memory transfers)( Daga et al. (2011)). AMD's recent APU(Accelerated Processing Unit) is based around this design concept (Branover et al. (2012))( (AMD APU Fusion), 2010). The more tightly coupled heterogeneous platform allows for performance and power consumption benefits while only sacrificing the raw computational peak performance of a discrete graphic processing unit( D'Alberto (2012)). Intel's HD Graphics and Ivy Bridge architecture was Intel's architectural debut into this realm of heterogeneous computing( Damaraju et al. (2012)). AMD's "Kaveri" platform is the most recent development in accomplishing the design concept described as a truly heterogeneous computing system by AMD.

The hardware capabilities of mobile devices such as phones and tablets have accelerated in recent years. With this acceleration of technology, application demands have also seen a large amount of growth and focus. Computer vision and augmented reality-based applications were once mainly a application area limited to powerful stationary computers with large and powerful graphic processing units capable of handling the large load of performing the computational intensive feature detection and graphics rendering. With innovations in both hardware design and heterogeneous computing technology, these applications have been introduced to the realm of mobile electronics; allowing anything from 'smartphones' to 'smartTVs' to demonstrate exciting augmented reality and graphically-intensive applications. There has been a great deal of developmental research in implementing existing efficient computer vision applications using newly introduced heterogeneous computing API features in popular open source computer vision libraries such as OpenCV. OpenCV is an interesting example of a popular development library which now includes several heterogeneous computing aspects to better improve the performance of its computer vision features (Pulli et al. (2012)). Computer vision application development frameworks such PTAM(or Parallel Tracking and Mapping) can utilize many of the GPGPU libraries within the OpenCV computer vision library to accelerate the performance of their FAST corner feature detection computation (Klein and Murray (2007)).

Topics such as AMD's "Kaveri" technology and OpenCV's additional GPGPU computing libraries are excellent examples of both the exploration and interest presented by software and hardware companies in heterogeneous computing (Bradski). From investigating the performance differences between discrete and integrated graphic processing units in general purpose computations to exploring the potential performance benefits of incorporating OpenCV's OpenCL libraries in the parallel tracking and mapping augmented reality application; heterogeneous computing has presented a volatile and interesting research area with many aspects to explore and many areas that I have yet to fully understand. In this large area of potential research, general purpose programming for graphic processing units present one of the largest areas of innovation involving heterogeneous computing.

### CHAPTER 2

### THE BASICS OF GENERAL PURPOSE PROGRAMMING WITH THE GPU

To best understand the concepts discussed and theorized in the overall research surrounding this thesis requires only a very basic understanding of both computer architecture, graphic processing unit design, and general purpose computing with graphic processing units (a.k.a., GPGPU). General purpose computing, an incredibly broad area of programming, is generally described as computational tasks without a specific or more-so simply a general purpose. Whereas the typical programming tasks for a graphic processing unit can be described as graphics rendering or the typical programming tasks for a sound processing unit can described as processing and producing audio signals to and from the computer's applications; general purpose computing tasks are often handled by the central processing unit of the computer. As you can imagine, general purpose computation with the graphic processing unit involves designating a subset of these general purpose tasks to be handled by the graphic processing unit of the computer. Revisiting the principals described by heterogeneous computing, all tasks within this subset of general purpose computational tasks must share some characteristic or detail which allows them to be processed more efficiently on the graphic processing units. To better understand how to distinguish between these programming tasks requires a small understanding of the architectural designs of both the central processing unit and the graphic processing unit(s).

### 2.1 Understanding the Hardware Characteristics of the CPU

The central processing unit can be considered as the primary component of the modern computer. Self-described by its name, as a processing unit, the central processing unit governs all programming tasks and processes central to the overall computer. These tasks include everything from basic arithmetic or logical calculations to the general input and output operations that are typically encountered with your standard computer program. In a sense, the central processing unit can be understood as the governing unit of all other hardware components that the computing device is comprised of. The central processing unit has undergone an extensive amount of changes over the last century with the introduction of transistors, integrated circuits and eventually microprocessors and multi-core processors. The popular Moore's Law, named after Intel co-founder Gordon E. Moore, characterizes this growth in CPU technology by accurately predicting that the number of transistors on integrated circuits would double approximately every two years. As such, the central processing unit is a very unique and exciting component of computer hardware that could warrant an entire paper describing the evolution of its design in itself.

The central processing unit, given its role in the line-up of individual hardware components is to effectively, efficiently, and accurately execute the computer program(or computer programs). The central processing unit is built with extensive instruction pipelines consisting of complicated integrated circuits and designed around an efficient memory hierarchy which begins with the processing core's registers and continuing through a series of memory and instruction caches before reaching the system memory. All of these aspects of the central processing unit's design is simply to achieve one central goal; to effectively, efficiently, and accurately execute the computer program. In general, the central processing unit is optimized for sequential processing and low memory latency. Given the introduction of multi-core central processing units, more opportunity for parallelism exists amongst the physical cores of the central processing units, though this still does not amount to the level of parallelism available in modern graphic processing units. Hence, we begin to draw the metaphorical line between the programming tasks which are better suited for which hardware component( Hennessy and Patterson (2003)).

# 2.2 Leveraging the Hardware Characteristics of the GPU for General Purpose Programming

Differing from the central processing unit, the graphic processing unit is designed with an entirely different purpose. The primary motivation behind graphic processing units were, and still are, to efficiently render the graphical components desired by the computer application and related software. To achieve this, the graphic processing unit must have the ability to perform thousands of simultaneous calculations to produce the accurate image frame according to the demands of the software (e.g., graphics pipeline). This design requirement eventually lead to the large dedicated and discrete graphic processing units which are evident on the modern computer hardware market today. The computer architectural reflection of this requirement is a fairly large electronic circuit composed of thousands of processing engines or cores. This design trait allows for a large level of data parallelism and throughput while sacrificing the memory latency presented in modern central processing units. The graphic processing unit does offer its own memory hierarchy with its own associated memory spaces very similar to modern central processing unit design (Hennessy and Patterson (2003)).

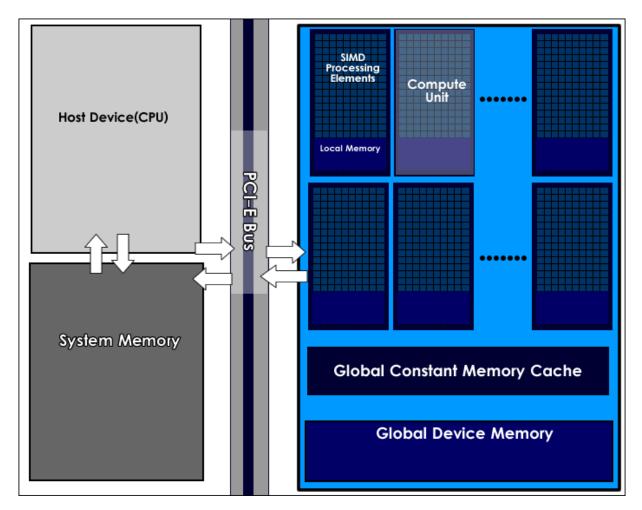

Figure 2.1 gives a very basic representation of a traditional loosely coupled heterogeneous computing platform consisting of a discrete GPU and multi-core CPU platform. The graphic processing unit device hardware consists of many compute units, each compute unit with its own large amount of SIMD processing engines. In the loosely coupled discrete GPU-based heterogeneous platform, communication and memory transfer between devices take place on the PCI-E bus. This connection scheme often presents a potential bottleneck in computationally intensive applications that may require frequent large data transfers between both devices.

General purpose computation on the graphic processing unit is to effectively leverage the resources of the device to increase the performance on many computationally intensive programs which offer many opportunities of high-level data parallelism. The graphic pro-

Figure 2.1. A simplified diagram of discrete GPU system and a very high level representation of the architectural components of the GPU.

cessing unit is comprised of thousands of processing cores described as shader engines in relationship to the device for graphic rendering tasks. Within the graphic processing unit, these shader engines could be separated into different groups corresponding to their specific task or purpose within the graphics pipeline in the production of the frame. These different groups consist of the commonly known pixel and vertex shaders and the newer geometry and tessellation shaders. The introduction of the "Unified Shader Model" which introduced a consistent set of instructions across all shader types essentially constructed the developmental bridge into utilizing the graphic processing unit for general purpose programming tasks. The consistent instruction set introduced in the unified shader model eventually lead to the development of general purpose compute programs known as kernels. To understand the intricacies and mechanics of kernel programs requires a general understanding of both the architectural philosophy of the graphic processing unit and the programming platform or API used to construct the kernel program. To understand the nature of kernel programs is to understand the nature of the graphic processing unit itself and more importantly the shader engines (or stream processors) which the graphic processing unit uses to achieve the high-level of throughput to produce better performance in computationally intensive parallel applications. It is also helpful to remember that the graphic processing unit is merely supplemental to the central processing unit, thus staying true to the very synergistic nature of heterogeneous computing.

### 2.3 Modern Parallel Programming Platforms for GPGPU Programming

In the area of general purpose computing with graphic processing units, there exists many programming platforms or APIs whose primary purpose is allowing the programmer to create applications which utilize the graphic processing technology for their own general purpose programs. Two of the most popular programming platforms typically discussed in this area of research is OpenCL and CUDA. CUDA, the product of a collaborated effort of NVIDIA and the University Of Toronto, is a C-based(and later extended to C++/FORTRAN) proprietary programming platform and GPGPU SDK for NVIDIA graphic processing units only(NVIDIA Corporation (2011)). OpenCL, developed by the Khronos Group(originally developed by Apple Inc.), is a cross-platform heterogeneous parallel programming platform and framework. OpenCL is C-based but also offers C++ extensions for programmers who prefer the C++ programming language variety. OpenCL is an interesting programming platform in comparison to CUDA, distinctly because OpenCL does not limit itself to only graphic processing units. OpenCL describes itself as both a crossplatform heterogeneous programming platform, allowing kernel programs to be executed on any OpenCL compatible parallel processing device which can also include multi-core microprocessors or digital signal processors.

Between these two programming platforms, you may find that synonymous objects and concepts are titled differently which can lead to a lot of general confusion. Information provided by both hardware and software manufacturers also suffer from this confusion; where hardware and software components may switch titles depending on the context of the sentence that they are presented in. Examples of this synonymous terminology include stream processors which are often described as shader engines, SIMD cores, or SIMD engines. The SIMD acronym means "Single Instruction Multiple Data" and characterizes the execution model of the kernel program. SIMD originates from a characterization known as Flynn's taxonomy which consists of SISD(Single Instruction Single Data), SIMD, MISD(Multiple Instruction Single Data), and MIMD(Multiple Instruction Multiple Data). In later revisions, the above definitions have been extended to programs rather than just instructions. For the nature of general purpose computing on graphic processing units, we only concern ourselves with the SIMD model.

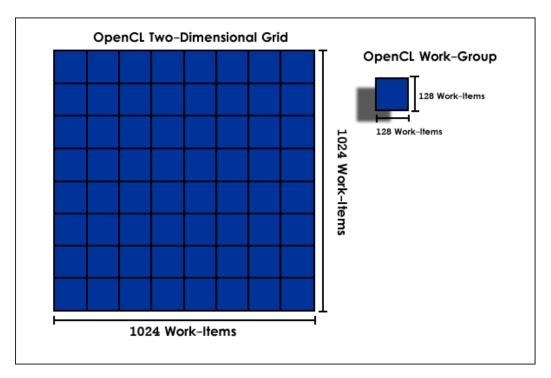

As we explore the programmability of the graphic processing unit and the programming platforms which unlock this capability, we encounter synonymous terms such as workitems(OpenCL) and threads(CUDA). Similar to the standard computer science definition of a thread, the work-item or thread can be viewed as the smallest unit of computation which essentially executes the sequence of instructions described in the kernel program. In addition to work-items and threads, we have work-groups or thread-blocks. As you can assume from their given labels, work-groups and thread-blocks can be one/two/or three dimensional structures comprised of work-items or threads, respectively. Continuing with the case of the OpenCL programming platform, you begin to see a hierarchy of computation. This hierarchy begins with a overall grid consisting of work-groups of work-items. These work-items are further grouped together to form corresponding wavefronts within the work-groups. The wavefront consists of 64 work-items which are executed simultaneously.

Figure 2.2. Understanding the thread configuration and how it applies to your problem space and algorithm allows you to understand how to best utilize the hardware.

Understanding these programming concepts allows the programmer to visualize the parallelism of his application and how different aspects of his application can translate to a kernel program. Understanding the underlying hardware concepts can help the programmer understand the execution model which his program relies upon. Revisiting the hardware components of the graphic processing unit described previously, these thousands of stream processing cores are distributed to a group of compute units(also often called execution units). Each compute unit has its own local (or scratchpad) memory while all compute units share a common constant/global device memory area. Relating to this architectural model, the previously mentioned work-groups are processed by the compute unit. All compute units execute their work-groups simultaneously. Though a compute unit can process several work-groups (depending on the hardware and memory limitations of the device), the compute unit does so in a sequential manner. Each work-item has its own private memory

while every work-item in a given work-group share a memory area titled as local memory(or scratchpad memory). Every work-item in the global space share the same central device memory area appropriately named global memory. As you can imagine, given the purpose and motivation behind the architectural design of the graphic processing unit, the memory bandwidth between these memory spaces differ greatly and provide a primary focal point in the implementation details of this research.

Above is a very basic description of the relationship between the software and hardware components which are described by the OpenCL programming platform for graphic processing units. As you can imagine, given the volatile and dynamic nature of the graphic processing technology and ongoing development and innovation in this area, there are many different real-world varieties of this technology ranging from the basic and heavily marketed discrete graphic processing units to the interesting system-on-chip heterogeneous variety which is currently rising in popularity amongst mobile devices. Given these varying representations of the same fundamental hardware device, the discussed programming platform aspects remain consistent between each of these representations.

### 2.4 Adapting a Serial Executing Application for GPU Hardware

From a software or program-level, the implementation or incorporation of OpenCL within the application consists of separating the application into two essential parts. The portion of the application that is primarily executed on the central processing unit is called the "host" code and serves as the primary program which sets up the OpenCL programming environment, manages and creates the OpenCL data structures, launches the OpenCL kernel(s), and operates on the return values of the kernel programs. The standard OpenCL setup process consists of identifying the OpenCL platform on the computer and recognizing the array of OpenCL compatible devices of this platform. This array of OpenCL compatible devices of this platform.

units or any general purpose parallel processing unit. Once the OpenCL compatible device(s) is chosen, the OpenCL context is created for the use of managing other OpenCL objects such as command queues, OpenCL memory buffers, and also OpenCL kernel objects amongst this OpenCL device or collection of OpenCL devices described by the OpenCL context. There is a large amount of setup code involved in implementing OpenCL into the application but much of it can simply be repeated from application to application in most cases. The large amount of general setup code does allow for a large amount of control over the OpenCL components of your application (Munshi et al. (2011)).

Aside from setting up the OpenCL environment within the application, the programmer must also seek to understand which areas of his application can benefit the most from the graphic processing unit technology. This approach can begin with profiling and characterizing which portions of the application are most computationally intensive. Once these portions are discovered and profiled, the programmer must determine the parallelism opportunities of these computationally intensive sequences. Essentially polarizing the computationally intensive highly parallel portions of the program and the standard sequential portions is the key to determine which areas of the application can benefit most from general purpose programming on the graphic processing unit. Often an easy way to visualize this strategy is to seek for portions of the program which perform a small amount of calculations over an extremely large data set. A common example of an algorithm which exhibit these characteristics is the basic vector addition example which performs the addition of two elements in two separate vectors while storing the result in another vector at the index which corresponds to the index of the two elements of the original vectors. Another common example is matrix multiplication which performs the multiplication between two matrices (fairly self-explanatory) (Matsumoto et al. (2012)). Both of these examples are often cited as the beginner's introduction to the realm of general purpose programming with the graphic processing unit; the essential "Hello World" of the heterogeneous computing world.

Adapting the application to utilize the OpenCL programming platform requires both

a great understanding of the algorithm's problem domain and also the characteristics of the OpenCL programming platform which will exploit the potential parallelism of the algorithm. The kernel program, which can be viewed as a function itself, is a unique program based in a somewhat limited version of the C99 C standard. Once the kernel program has been created, the programmer acquires the responsibility of designating the problem domain that kernel program shall execute within. This domain is characterized by two primary aspects, the global work-items specification and the local work-items specification. These two details can be expressed in three dimensions, depending on which representation maps best to the algorithm that it is effectively attempting to optimize. In a naive explanation, if the problem domain consists of a single one-dimensional data set then the most optimal specification would be one-dimensional; this includes problem domains that require a computation on a large vector or array of data. Similarly, such as the matrix multiplication example discussed earlier, if the problem domain consists of a two-dimensional data set, these specifications can be expressed as two dimensional; and so forth with a three-dimensional data set. Acknowledging these details allows the programmer to specify the amount of work-items and the subsequent grouping of work-items in a identifiable model that the kernel program will effectively execute on.

While this may seem overcomplicated to a beginner programmer in OpenCL, with ongoing experience in utilizing the OpenCL programming platform in their programs, the programmer begins to see the optimization possibilities and the resulting parallel execution model more clearly in their subsequent applications. Returning to the concept of work-items and work-groups, once the programmer has specified the dimensions and amount of workitems in the global problem space and the dimensions and amount of work-items in the local problem space(within each work-group), OpenCL processes this information and executes the kernel program within this specified problem space. The behavior of the work-items within this N-dimensional problem space must be understood by the programmer when translating portions of his algorithms(or his entire algorithm) to a suitable kernel program. Work-items within the global problem space share the same global memory space while work-items within the same local work-group share the local memory space. Synchronization methods such as work item barriers and memory fences are familiar instruments to most parallel programmers and they are also required within the kernel program to protect the integrity of the model and prevent any discrepancy between the OpenCL execution model and the kernel program itself. Within the 64 work-item wave front, there is also an opportunity for thread-divergence which can also affect the overall hardware utilization and present opportunities for less-thanoptimal performance.

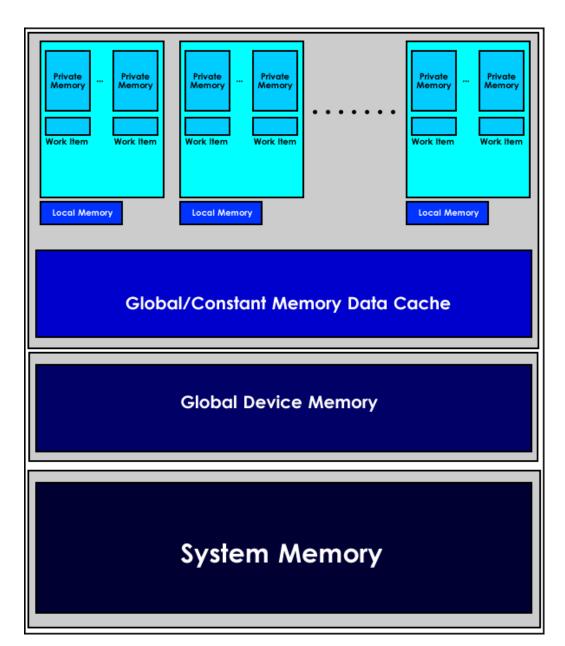

#### 2.5 Understanding the OpenCL Memory Model

Revisiting the OpenCL memory model, we acknowledge that there are four primary memory spaces that the kernel programmer must be aware of when optimizing his algorithm based upon OpenCL's specifications. The first and foremost is the system memory or host memory which is shared between the "host" device and the OpenCL device. In discrete graphic processing platforms, memory transfers between the host device's system memory and OpenCL device's global memory is performed over a PCI-Express bus. This transfer protocol presents a performance bottleneck where the OpenCL kernel's performance is limited by the slower transfer bandwidth of the PCI-Express bus. There has been a large amount of research and focus in hardware solutions to relieve this bottleneck. One common approach is evident in a modern hardware component described as an APU or accelerated processing unit. In an accelerated processing unit, the graphic processing unit and the central processing unit are much more closely coupled on a single silicon die. While this removes the memory transfer bottleneck and improves the power consumption of the device; there are some performance limitations inherent to the graphic processing unit design when coupled with the central processing unit on the same silicon die. These limitations can be described as a lower number of dedicated transistors to the graphic processing unit resulting in a lower number of stream processing SIMD cores and a lower number of general compute(or execution) units (Munshi et al. (2011)).

The next memory area of interest within the OpenCL memory model is titled as global memory. The name, rather self-explanatory, implies the definition of the memory space; global/constant memory is the memory space shared by all work-groups within all compute units on the OpenCL device. This memory area is not synchronized between workitems or work-groups, so careful detail and focus must be exercised in the memory handling of the kernel program when working within this memory space to prevent any discrepancy between the global work-items which read and write from this memory space. Within each work-group is a memory space titled as local(or scratchpad) memory which is synchronized between all work-items within the work-group. Each work-item within the work-group shares this memory space and acquires the same view of this memory space. Predictably, the memory latency between the local memory space and global/constant memory space differs greatly, therefore it is suggested to perform the majority of memory accesses in the local memory space area and limiting the amount of memory access to the global memory space to increase the overall performance and lower the overall memory latency.

Since all work-items within the work-group share this same local memory, there is also a large amount of careful detail that must be exercised in programming the kernel program to execute accurately and consistently within this local memory scope. Each work-item has its own private memory which is used by that work-item for storing and processing information specific to that work-item such as common variables within the kernel program. Data within this private memory can not be accessed or viewed by other work-items. Generally, designating the memory space that information must be stored in is done either within the kernel function's argument field by an associated prefix before each argument or within the kernel program itself by the same prefix. OpenCL kernels may include auxiliary functions but given the nature of the memory addressing scheme within the OpenCL memory model, these functions cannot take arguments such as pointers to memory spaces; therefore these functions can be easily understood or viewed as inline functions within the main kernel program. Understanding the OpenCL memory model allows the programmer to understand how to structure the memory accessing nature of his resulting kernel program.

Figure 2.3. The layout of the very basic graphical representation of the OpenCL memory model.

To summarize the entire OpenCL programming model in a very basic manner, we begin with the OpenCL components present within the "host" program which consists of the basic setup OpenCL objects such as the OpenCL platform(s) comprised of OpenCL devices. The OpenCL context consists of the management of the OpenCL objects such as OpenCL memory buffers, OpenCL execution command queues, and OpenCL programs which consist of OpenCL kernel objects, across the collection of OpenCL devices within the OpenCL platform of interest. You begin to note a hierarchy present within this realm of the OpenCL programming model. While this may seems like a very large and tedious amount of boiler-plate code; this hierarchy allows for an high level of control and design freedom to optimize the application for the performance benefits of high-level data and task parallelism. Understanding this aspect of the OpenCL programming model and adapting it your application involves understanding the relationship between your application and the OpenCL device(s).

### 2.6 Summarizing the Basics of GPGPU Programming with OpenCL

To further summarize the OpenCL programming model that we have discussed in earlier pages. We explore the OpenCL execution model which closely mirrors the hardware architecture details of the OpenCL device with concepts such work-items and work-groups with each work-item processing the sequence of code within the kernel object. The workitems are handled by the OpenCL device's SIMD processing cores while the compute units of the OpenCL device effectively handles each local work-group. Understanding the nature of the OpenCL device specific to the platform executing your application helps you determine which OpenCL device is best suited for your algorithm and which execution model is best suited for that OpenCL device. In addition to understanding the very basic nature of the OpenCL execution model, the OpenCL memory model describes the resource management detail that must be considered to promote the best performance out of the kernel program. Understanding the role and characteristic of each individual memory area allows the programmer to effectively utilize the entire hardware in an incredibly efficient manner exhibiting both high level parallel performance and efficient memory handling for low memory latency. Understanding the hardware and software-related characteristics of each hardware components allows the programmer to develop an optimal workload distribution scheduler to determine which workload is best for which device; this approach has resulted in many interesting research topics such as the dynamic scheduling of the breadth-first search algorithm over real-world graph instances (Hong et al. (2011)).

It may seem that only specifying details of the OpenCL programming platform for general purpose computing on the graphic processing unit may limit the understanding of the concept to only the details of the OpenCL programming platform; given the fact that there are many other programming platforms available. But the concepts discussed in the previous pages involving the different characteristics of OpenCL programming are easily translated to other existing GPGPU programming platforms as well. Given the design of modern graphic processing units, each programming platform follows a similar programming model design to exploit the performance benefits based upon the central architectural design. OpenCL is the most widely used and available implementation of this programming paradigm due to its open source and cross-platform nature which are the basic design goals by the Khronos Group. For this thesis, OpenCL has been the platform of choice.

Understanding the very nature of heterogeneous computing and general purpose programming on graphic processing units will provide insight behind the motivation of my research and the implementation details described in my experiments. Understanding the potential benefits of incorporating these concepts in modern algorithms to fully utilize modern technology designed around the concept of heterogeneous computing will allow you to see the nature and behavior. Described in this chapter is only the very basic details of general purpose computing with graphic processing units which are required for further understanding of this document and its associated research. Programming-specific details and API characteristics were not discussed and can provide material for yet another paper; but their details aren't effectively useful for understanding this document.

### CHAPTER 3

### ADAPTING THE HEAP FOR HETEROGENEOUS COMPUTING

Algorithm(Al·go·rithm), is a term originating from the transliteration of the surname of Arabian mathematician al-Khwarizmi, famous for his introduction of mathematical concepts such as algebra to Western civilization. An algorithm is best described as the sequence of steps to achieve a solution to a specific task or problem. In the realm of computer science, an algorithm can be understood as the mechanics of the computer program which execute to perform a certain task. Every computer science student is extremely familiar with the concept of an algorithm; perhaps from a formal definition perspective or simply the inherent nature of their approach to programming solutions. With further investigation of algorithms within the area of computer science, we begin to see their most primitive components, the data structures( Levitin (2002)).

Re-examining the phrase "Computer and Information Science", we note the inclusion of the term "Information". A large component of the study of Computer Science involves understanding the representation and handling of information, often referred to as data. The purpose of the computing device as a mechanical device is to effectively process, represent, and handle data for the purpose of accomplishing a solution at the discretion of both the programmer and the user. To accomplish this goal, information or data must be represented in a manner which allows the device to easily perform the calculations and computations demanded by the algorithm. These resulting structures are appropriately called "Data Structures" and they exist in many different varieties with different purposes. Combining the science behind these data structures and the mechanics of the algorithms that utilize them presents an ever-changing area of focus, research, and analysis to develop algorithmic solutions that use the computing device hardware more effectively. Many of these information representation structures have a counterpart within the area of mathematics. For example, many varieties of the graph structure are utilized in computer science, these varieties can also be characterized in their mechanics and efficiency by graph theory, a vast and interesting area of research and study within mathematics. Often these complicated and intricate structures are representative of a much larger set of information being processed by the computer program; this allows for a level of abstraction of the problem domain being handled and processed by the computer program. Internally, or within the programming language itself, exists a concrete representation that can be modified or structured to implement a much more complicated data structure. An example of this concrete data representation within the C programming language is the basic array.

### 3.1 Addressing the Nature and Design of the Heap Data Structure

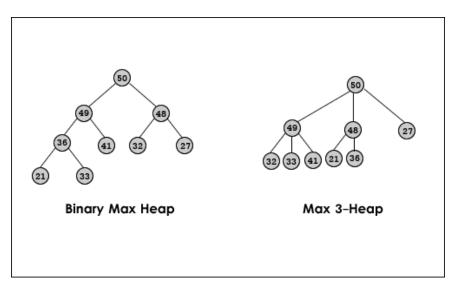

Referring back to graph-based data structures, a great example of this structure type is the tree-based data structure, the heap. Tree-based implies an acyclic graph hierarchical representation of the information which begins with a "root" node branching into subsequent nodes with each subsequent node branching into more nodes. The heap is an unusual treebased data structure in comparison to other common tree-based data structures such as Binary Search Trees, Red-Black Trees, and also B-Trees. Each heap implementation or representation share a common property that distinguishes them as a heap; this property is the ordering of the nodes which the Heap data structure consists of. The heap data structure comes in two primary varieties, the Max Heap and the Min Heap. As the names imply, the Max Heap is characterized by the root node having the maximum value or key of all nodes within the Heap data structure; the Min Heap is the opposite. The ordering property of the heap data structure reflects these varieties by ensuring that the keys of the children of a specific node is either greater-than or less-than the keys of that specific parent node. With this ordering specification exhibited throughout the entire heap data structure; the root value becomes whichever node that has the maximum or minimum key or value(Levitin (2002)).

The heap data structure is a complete tree structure exhibiting the smallest possible height for a Tree-based structure based upon the number of nodes within the heap. As nodes are inserted into the heap, the Tree-representation essentially grows from left to right on the fringe level of leaf nodes until a new level within Tree structure is required. The mechanics of the insert operations are different from typical tree insert operations to ensure that the integrity of the heap ordering property is retained. The heap structure provides an efficient way to extract the maximum or minimum values amongst a collection of values or keys in constant time. While the root node's value or key is the maximum or minimum order statistic of all keys or values within the tree, the Heap isn't completely sorted in any definite manner given the lack of relationship between all keys or values on any given level within the heap tree.

Figure 3.1. As with most data structures and information representations, it is much easier to understand with a visual reference.

In its most simplistic form, the Binary Heap, the heap consists of nodes where each node, aside from the nodes on the last full level, have two children nodes. The nodes within the last full level of the heap, following the description stated earlier in this chapter, can have as little as no children depending on the population of the last fringe level of the heap data structure. This is the most basic implementation of the heap data structure. A representation that would exhibit a smaller number of children yet retain the connectivity of the graph structure would result in a sorted degenerate tree. The heap structure can be further extended to include cases where the heap nodes are allowed a greater number of children. This is known as the d-heap or d-ary Heap where d denotes the maximum number of children each node is allowed. d-heaps are very common within many graph-based algorithms in computer science.

The basic operations of the heap data structure are similar to the basic operations surrounding most common data structures. There is the *Insert-Node* operation, *Update-Key* operation, and *Delete-Min/Max* operations and associated observer operations for extracting information from the heap structure such as the value of the heap's root node. The *Insert-Node* operation is fairly straightforward, simply inserting a new node and associated keyvalue into the heap structure. The *Update-Key* operation essentially changes the key value of a given node within the heap structure. The *Delete-Min/Max* operation removes the root node from the heap and oftentimes returns this value to the calling function for further use. The mechanics of these operations become a unique focal point, since any operation that modifies the structure of the heap structure or the values of the nodes within the heap structure might require additional work to ensure that the heap ordering property remains intact. This additional work can be described by two different methods known as bottom-up reconstruction or top-down reconstruction.

In the case of inserting a new node or updating the value of a node to a new value which is greater than(or less than in the case of a Min Heap) the original's parent node's value, the bottom-up reconstruction is utilized. In the bottom-up reconstruction, the new node or node of interest is propagated up the structure of the heap until the heap ordering property is satisfied. Similarly, the top-down reconstruction method is used when the new node or value is propagated down the structure of the heap until the heap ordering property is satisfied. When a new node is inserted into a heap structure, the node is placed as the last possible child node within the heap given the heap's structure constraints. This node is then propagated up through the heap through a series of comparison and swaps with node and its subsequent parent(s). When the root node of the heap is deleted, the last node in the heap replaces the root and comparison and swaps between the node of interest and its maximum child node are performed until the ordering property is satisfied. When a node's key is updated or changed to a new value, either approach can be taken; depending on the relationship between the node and its parent or associated children node. Understanding the mechanics of these operations allows for an understanding of how to optimize the these operations in heterogeneous solutions discussed in the previous chapters.

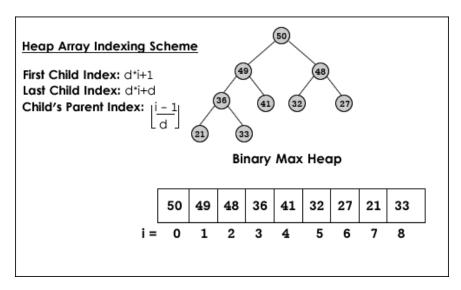

Figure 3.2. The array indexing scheme demonstrated on a binary heap structure.

The concrete representation of the Heap structure is often implemented as an array where each element within the array corresponds to a node within the heap structure. This representation presents an efficient indexing methodology of accessing heap node details such as the parent of a specific node or the corresponding children of a specific node. These constant-time indexing operations provide an efficient method of execution for performing the basic operations that are natural to the heap data structure.

### 3.2 Adapting the Heap Data Structure for Latest Trends in Technology

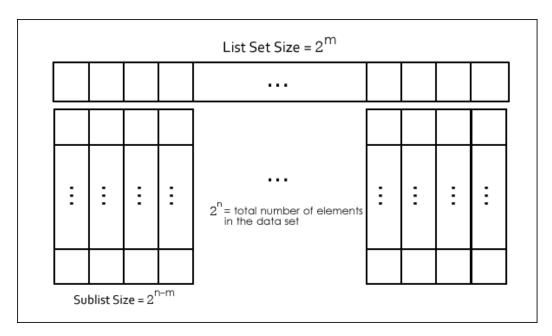

The heap is an incredible tool in implementing many efficient and common computer science algorithms such as finding the kth order statistic from a collection of values(an algorithm we'll be inspecting further), the essential Heap Sort, and many graph-based algorithms. Research is continuously driven by the possibility of further optimizing both algorithms and data structures to effectively take advantage of modern technology and modern programming platforms to improve their general performance. One interesting modification in the concrete representation of the Heap structure, for better performance on symmetric multicore processors, is the introduction of the implicit d-heap.

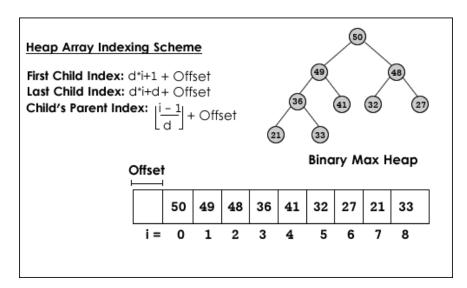

Figure 3.3. The Implicit *d*-ary heap.

The implicit *d*-heap was an intellectual response to the growing popularity of the memory hierarchy and the use of data caches on modern processors in the late 20th century. As the performance of the modern processor continued to improve with higher clock frequencies, the memory latency between the processing core and the physical system memory became a performance bottleneck]. The introduction of a memory hierarchy brought about an interest in adapting different algorithms and associated data structures to take advantage

of the benefits of the cache performance. Ladner and LaMarca proposed the implicit d-heap structural design to better align the components of the heap structure with the processing hardware's cache blocks (LaMarca and Ladner (1996)). In this newer design, siblings of a node would not span over cache blocks. They achieved this design goal by adding an offset of (d-1), where d is the maximum number of child nodes, to the head of the Heap's array representation. This additional offset required minor changes to the array addressing scheme as well.

Similar to the rise in popularity of the associated memory hierarchy, many researchers and developers are investigating the performance optimization opportunities presented by translating portions of their existing algorithms to high throughput-oriented devices such as the graphic processing unit. Revisiting the concepts covered in the previous chapters on heterogeneous computing with the graphic processing unit; many algorithms have exhibited a large performance increase in utilizing the high-throughput oriented hardware of the graphic processing unit. Unfortunately, many highly divergent graph-based algorithms and data structures have had a complicated time adjusting to this current trend and remains a heavily researched topic. For example, the heap structure which had undergone a structural change for better performance on modern symmetric multi-core processors, became the focal point of Weifeng Liu and Brian Vinter (Liu and Vinter (2014)).

### 3.3 The *ad*-Heap, Designed for Truly Heterogeneous Systems

Weifeng Liu and Brian Vinter investigated the associated operations of the traditional *d*-heap data structure looking for opportunities to exploit any potential parallelism. They discovered that the only opportunity for parallelism within these operations was the Top-Down Heap reconstruction sequence which required the maximum child of the specific node of interest to be found on each level. In this case, the opportunity for parallelism was to find the maximum child from a large group of children. The main issue of this discovery was that the level of data parallelism of this process is limited by the number of children or the value of d. Therefore in cases that the value of d is quite small, the opportunity to see any improvement from the graphic processing unit was also very small. In this case, the performance of the utilizing the graphic processing unit would be even worse than the typical mult-core implementation since the hardware of the graphic processing unit was not being fully utilized.

Modern hardware manufacturers, recognizing the potential for more powerful and power efficient platforms, began to research and develop solutions which would eliminate much of the overhead and bandwidth issues that typically bottle-necked the traditional loosely coupled heterogeneous platforms. This technology, a product of the HSA Foundation, is described as a truly heterogeneous platform that would allow the host device and the graphic processing unit to work more closely together within a unified memory space eliminating much of the memory cost and address mapping encountered in traditional loosely coupled heterogeneous platforms. On a hardware level, the central processing unit and graphic processing unit would be connected by either a shared data cache or the system memory; but located on the same silicon die thus reducing the slow memory bandwidth of the PCI-E bus. Given these essential design changes, the application load could distributed more easily by both the programmer and the operating system to which device would be able to provide the best performance. Additionally, this technology would combine the central processing unit and graphic processing unit in a closely manner to reduce the context differential typically encountered with traditional heterogeneous platforms and their associated kernel launching and execution protocol.

Though hardware platforms such as AMD's APU or accelerated processing unit and Intel's merged CPU and GPU have somewhat implemented much of these features on a hardware level by locating both hardware components on the same silicon die; the associated heterogeneous programming platforms have yet to completely implement the necessary synchronization and communication features to remove the context switching overhead. This is the essence of heterogeneous computing and Weifeng Liu and Brian Vinter theorized and implemented what they described as the ad-heap or the asymmetric d-heap based around this trend of modern technology. The asymmetric d-heap, as the name implies, is an implicit d-heap structured for performance on asymmetric multi-core processors. An asymmetric multi-core processor is synonymous to a heterogeneous computing platform; essentially combining two types of processing cores into one computational unit.

These compute units are separated into two categories, the throughput-oriented unit(such as the typical graphic processing compute unit) and the latency-oriented unit(such as the typical central processing unit's processing core). The design motivation behind the asymmetric *d*-heap was to effectively separate the execution mechanism of the *d*-heap to allow the portions that presented opportunity for parallelism to be executed on the throughputoriented cores and the portions that required sequential execution to be executed on the latency-oriented cores. This is very similar to adapting most algorithms to loosely coupled heterogeneous platforms; but given the nature of the *d*-heap structure and the relatively small amount of opportunity for parallelism, this provided an opportunity to explore the possible benefits of more closely coupled heterogeneous platforms.

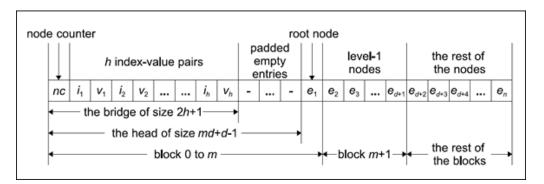

Figure 3.4. The ad-Heap array structure proposed by Weifeng Liu and Brian Vinter (Liu and Vinter (2014)).

To accomplish this, the original *d*-heap structure was only modified in a modest sense. The original empty head of the implicit *d*-heap became a storage container for information that would be later used by the latency-oriented cores. If an operation performed on the *ad*-Heap structure required the heap to be reconstructed from the top down; the graphic processing unit handled the downward propagation of the value. On each level of the heap, the children of the node of interest would be analyzed in parallel to determine the maximum child. Once the maximum child was found, it would be compared to the current node of interest. In a traditional execution of this operation, if the maximum child was greater than the node of interest then the two nodes would effectively be swapped and the node of interest would continue to propagate down the heap. In the case where this computation is performed on the graphic processing unit, a space of memory is allocated in the local memory of the device which is described as the implicit bridge. When a swap is needed between two nodes, the index of the node and the new value are stored as an index-value pair on this implicit bridge rather than the assignment being directly handled within the device code.

This index-value pair placement and implicit bridge construction is to avoid the associated bandwidth and thread divergency penalty incurred by allowing only one thread within the device's wavefront to perform the assignment to global memory. Once the value has been propagated down the heap to its proper location, the workload of the throughput-oriented cores are finished and the wavefront offloads the implicit bridge to global memory in the location of the implicit *d*-heap's empty head section where the latency-oriented cores can perform the proper assignments based on the information provided in the implicit bridge. The implicit bridge is composed of a node counter which keeps an associated count of the index-value pairs on the implicit bridge.

To perform this effectively, a complicated level of synchronization and communication must be implemented to ensure that both the throughput-oriented compute units and latency-oriented compute units are able to communicate their results and workload with as little overhead as possible. Unfortunately this programming model is only theoretically presented by the HSA Foundation and presented in a theoretical sense in the associated *ad*-Heap paper by Weifeng Liu and Brian Vinter. Despite this, and the current lack of truly heterogeneous HSA platforms available, Weifeng Liu and Brian Vinter simulated the modern technology with their proposed design by counting the number *find-maxchild* and *compare-and-swap* operations in the d-heap on the CPU and executing the same amount of work with their *ad*-heap implementation on the CPU and the GPU. In their performance statistics of this simulation, they also included the approximate cost of the synchronization between the throughput-oriented and latency-oriented processing cores. They found a significant improvement in this design over similar experimental platforms that executed the operations either strictly on the standalone CPU, loosely coupled CPU and GPU platform.

### CHAPTER 4

## ADDRESSING THE LIMITATIONS OF GPU COMPUTING WITH HSA ARCHITECTURE

Weifeng Liu and Brian Vinter addressed some of the common issues surrounding general programming on the graphic processing unit in their unique design of the *ad*-heap structure. The design philosophy promoted the use of the theoretical AMP(Asymmetric Multi-core Processors) technology to generate the performance benefits of general purpose programming on the graphic processing unit while negating the possible issues which would normally limit these performance benefits( Vuduc et al. (2010)). Normally these limitations can be categorized as either an under-utilization of the hardware or memory/computational thread-related execution which does not translate well to modern graphic processing unit technology( Owens et al. (2005)).

#### 4.1 Limitations of Current GPU Hardware/Software Solutions

Modern discrete graphic processing units typically perform active data transfers across the PCI-E bus to the system memory which is accessed by the central processing unit. In applications where there is frequent communication and data transfer between the central processing unit throughout the course of the application's execution; there is an associated penalty which corresponds to both the memory bandwidth and the memory paging/handling overhead which can limit the performance of the application. Similarly, there is an estimated associated overhead from the context-switch associated with each kernel launch in an application that may require a large number of kernel launches. Therefore, in an application whose execution is more closely coupled between the central processing unit and graphic processing unit, the associated overhead of the memory handling and kernel launches can dramatically decrease the overall performance thus rendering the graphic processing unit solution to be ineffective compared to a strict-central processing unit solution.

Algorithms which require a large amount of irregular memory access patterns are typically unable to reap the performance benefits of highly parallel hardware devices such as the graphic processing unit. The GPU hardware is designed and optimized for highly parallel tasks and computation. When individual computational threads issue memory requests in a manner which is not uniform to the group of parallel threads as a whole, the underlying memory subsystem of the graphic processing unit is unable to effectively process the requests in a low-latency efficient manner as the central processing unit typically would. Generally, programmers must adapt their existing algorithms to properly utilize the graphic processing unit's memory subsystem to fully benefit from the computational power of the hardware.

Thread divergence can often affect the performance of modern graphic processing units. If the application's amount of parallel work decreases over the course of the kernel execution, the amount of utilized SIMD threads will also decrease resulting in an underutilization and inefficient use of the graphic processing unit technology. Oftentimes, this is encountered when thread-id based conditional blocks within the kernel code result in the threads either diverging in their overall work pattern or a large amount of threads becoming idle within much of the kernel program's execution. The resulting low hardware utilization reflects the performance of the kernel program and the overall performance of the application.

When translating sections of the application for execution on the graphics rendering device, the programmer typically investigates the large loop-based computation. Loop-based computations which exhibit iteration-based data dependencies often do not translate well to the parallel nature of the graphic processing unit. In similar nature, algorithms which depend on the manipulation of shared data between each iteration of the loop can promote in-deterministic results from multiple threads attempting to modify or access the shared data in a parallel fashion. To resolve this issue on modern graphic processing units, the use of synchronization methods and/or atomic operations provide a solution but often hinders the parallel nature of the program's execution and reduces the overall performance.

#### 4.2 The Hardware and Software Design of the HSA Solution

As discussed previously, the *ad*-heap is a very interesting case where the current limitations of the hardware and software solutions of general purpose programming on the graphic processing unit would otherwise prevent any benefits from translating the data structure and its operations from a traditional multi-core central processing unit implementation. Despite these limitations, by adapting the structure design and general execution concept of its operations, the *ad*-heap should inherit an increased performance on systems which follow the True Heterogeneous Computing philosophy. Many hardware manufacturers such as ARM Holdings, AMD, and Qualcomm have combined their development and research efforts with academic research groups at institutions such as Northeastern, University of Illinois, and the University of Mississippi to form the non-profit consortium known as the HSA Foundation. The HSA(Heterogeneous System Architecture) foundation seeks to advance the topic of truly heterogeneous computational systems as innovative technology solutions to the modern heterogeneous computing paradigm( (HSA Foundation) (2013)).

The design of the HSA architecture addresses many of the limitations of current discrete graphic processing unit heterogeneous solutions. By tightly-coupling the central processing unit and graphic processing unit, the PCI-E memory transfer penalty is effectively eliminated. Most modern APU or accelerated processing units resolve this potential bottleneck by allowing the graphic processing unit and central processing unit to share the same system memory while residing on the same silicon die. The HSA solution seeks to allow the central processing unit and graphics accelerator unit to share the same last-level cache of the primary memory hierarchy of the system rather than the system memory which further reducing the bandwidth penalty( (AMD Developer Central) (2013)).

Further addressing the limitations of modern GPGPU heterogeneous platforms' mem-