# System-Level Optimization of Baseband Filters for Communication Applications

Juan F. Fernández-Bootello<sup>a</sup>, Manuel Delgado-Restituto, and Ángel Rodríguez-Vázquez

Instituto de Microelectrónica de Sevilla, Centro Nacional de Microelectrónica Avda. Reina Mercedes s/n, Campus Universidad de Sevilla, E-41012 Sevilla (Spain)

## **ABSTRACT**

In this paper, a design approach for the high-level synthesis of programmable continuous-time baseband filters able to achieve optimum trade-off among dynamic range, distortion behavior, mismatch tolerance and power/area consumptions is presented. The proposed approach relies on building programming circuit elements as arrays of switchable unit cells and defines the synthesis as a constrained optimization problem with both continuous and discrete variables, this last representing the number of enabled cells of the arrays at each configuration. The cost function under optimization is, then, defined as a weighted combination of performance indices which are estimated from macromodels of the circuit elements. The methodology has been implemented in MATLAB<sup>TM</sup> and C++, and covers all the classical approximation techniques for filters, most common circuit topologies (namely, ladder simulation and cascaded biquad realizations) and both transconductance-C ( $G_m$ -C) and active-RC implementation approaches. The proposed synthesis strategy is illustrated with a programmable equal-ripple ladder  $G_m$ -C filter for a multi-band power-line communication modem.

Keywords: Low-power electronics, programmable filters, analog continuous-time filters, CAD tools for VLSI.

#### 1. INTRODUCTION

Analog baseband filters are signal-conditioning circuits used at the analog interface of data converters in communication transceivers for channel selection and (in some cases, adaptive) power level adjustment. Pushed by the increasing demand on low-cost, high-performance microelectronic solutions, the current trend is to implement these filters in monolithic form, embedded in fully-integrated mixed-signal transceiver realizations. Such system on a chip (SoC) solutions for communication applications avoid the use of external passive components (e.g., high performance discrete filters are no longer employed) and aim to provide a smaller form factor for the electronic appliance, as well as an overall reduction on power consumption – primordial for battery-operated devices. In this scenario, the design of baseband filters may become a challenging task if, as occurs with most recent wide-band communication standards, the objective of minimal power consumption and/or chip area must be traded-off with tight requirements on dynamic range, selectivity, linearity, or operation speed.

An optional, yet increasingly frequent, design feature of integrated baseband filters which further rises the complexity of the synthesis task is *programmability*. Programmable filters must be able to satisfy different system-level specifications upon the definition of a limited set of electrical variables and, therefore, they may constitute an efficient mean for saving power and area consumptions in SoCs for communications. Application examples in which the programming capabilities of baseband filters can be exploited are, for instance, in transceivers targeting different standards<sup>1,2</sup> (e.g., in cellular phones with capability for 2G and 3G services), in variable throughput data rate systems<sup>3</sup>, or in multi-carrier architectures used for improving the communication reliability (e.g., in power line modems for home automation and Internet access<sup>4</sup>). Because different configurations of programmable filters surely convey different minimal requirements for their active building devices, programmability is usually combined with multi-mode power-adaptation strategies to reduce the average current consumption of the filter.

A major difficulty on the implementation of programmable filters is to cope with non-ideal effects, such as parasitic poles or variable loading conditions of the building blocks, which may substantially vary from one operation mode to another.

a.bootello@imse.cnm.es; phone +34 955056666; fax +34 955056686

3,

245

This, together with the presumably design complexity (even for ungrouped realizations) makes the synthesis of programmable filters a matter which requires the application of proper circuit principles, a careful architecture selection process and optimum transfer of system-level specifications to their building blocks. Bearing this in mind and taking into account that it is vital to shrink as much as possible the SoC design's time-to-market (specially in the communication arena), the availability of high-level CAD tools for speeding up architectural exploration and block sizing, without actually going to a transistor-level design, becomes strategically more and more relevant. This paper is, in fact, a contribution to this topic and proposes a design methodology, developed in MATLAB<sup>TM</sup> and C++, for the high-level synthesis of programmable baseband filters (non-programmable single-spec structures constitute a subset within the design scope of the methodology and, hence, they are also accepted for synthesis). At the time being, the implemented tool only covers continuous-time realizations, namely, transconductance- $C^{3,5,6}$  ( $G_m$ -C) and active- $R^{1,7}$  techniques, but in the future will be expanded to also cover anti-aliasing plus switched-capacitor (SC) filtering cascades.

The tool has been planned as a general design framework in that it provides software modules for solving, with certain limitations, all the synthesis steps from system-level specifications to the optimized requirements for the building blocks. This includes modules for the approximation, active network representation, and implementation problems. The approach differs from other software packages which only cover partial aspects of the synthesis route, quite often non-oriented to integrated realizations. In addition, the developed software package addresses most common circuit topologies, namely, ladder simulation and cascaded biquad realizations, outperforming other systems which only deal with biquad-based synthesis<sup>8,9</sup>. Finally, it should be noted that the optimization process realized at the implementation module may take into account, depending upon user choice, different metrics such as dynamic range, distortion behavior, mismatch tolerance, systematic deviations on time- and frequency responses, and power/area consumptions, thus providing a complete control on the filter performance under all possible configurations.

For the sake of conciseness, the paper will exclusively focus on  $G_m$ -C techniques and ladder structures.

## 2. DESIGN PROBLEM AND PROGRAM DESCRIPTION

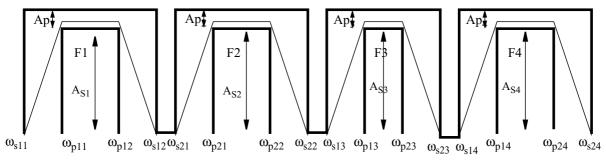

Assume a bank of filters such as the one consisting of four masks depicted by the way of example in Fig.1. Our primary target is to design a single filter structure capable to meet, through programming, all filtering mask specifications. Whenever needed, two or more filter structures will be designed to cover the whole set.

Solving this design problem means obtaining filter coefficients to cover the whole set of configurations. These coefficients must be realized through programmable components. The adopted strategy combines rough programming through component switching (discrete) and fine tuning through electrical parameter control (continuous). The latter is applied to capacitors, while the former is applied to transconductors. Important issues taken into account involve minimum degradation of noise, dynamic range, ..., minimum area and minimum power consumption.

Unitary transconductors are used ready from the beginning. Pros include simpler design and tuning. Counters include suboptimal scaling of the internal node voltages.

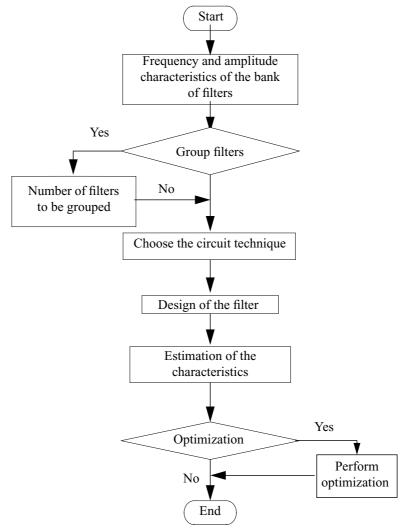

The program starts by defining the filter bank specs ( $A_p$ ,  $A_s$ , $\omega_p$ , $\omega_s$  in Fig.1). First of all, a decision is made whether to use only one structure for the whole set or several covering partially the set. Second, the filter architecture is selected; either LC or cascaded biquad. Third, filter coefficients are obtained taking into account amplitude and noise scaling. State variables are employed to properly handle issues associated to noise, scaling, sensitivity, ... A statistical optimization process

Figure 1: Example of a bank of filters.

Figure 2: Flow diagram of the program.

is used with the optimization objectives being placed on power, area, dynamic range... Fig.2 shows the flow diagram of the process.

# 3. REPRESENTATION AND EVALUATION TECHNIQUES

## 3.1. State-space representation

If the option of filter implementation by ladder simulation is chosen, the filter coefficients mentioned in the previous section take, conventionally, the form of a passive structure and the associated set of resistor, capacitor and inductor values. Altogether, the dynamics of the circuit can be described by the following general matrix equation, derived from Kirchhoff's,

$$\mathbf{J} = (\mathbf{G} + s\mathbf{C} + s^{-1}\Gamma)\mathbf{v} \tag{1}$$

where V is a vector which, in ther most general case, includes nodal voltages and branch currents, **J** is a vector which denotes the input current source, and **G**, **C** and  $\Gamma$  are matrices whose elements are algebraic combinations of the passive component values. If V only contains nodal voltages, **C** represents a capacitance matrix and  $\Gamma$  an inductance matrix. Otherwise, if V is formed exclusively by branch currents, **C** and  $\Gamma$  represent, respectively, inductances and capacitances.

Now the question is how to infer from the above general description, a realizable active ladder and a convenient representation which allows an easy evaluation of filter performances. This problem has been solved in <sup>15-17</sup>, where different matrix decomposition methods have been proposed for building active ladders. Among these methods, we have considered in our tool, the so-called *topological decomposition* approach (that gives rise to standard leapfrog structures), and the *right-inverse decomposition* approach (well-suited for band pass filters).

In the topological decomposition approach, the matrix  $\Gamma$  is factorized as

$$\Gamma = \mathbf{A}\mathbf{D}\mathbf{A}^{\mathrm{T}} \tag{2}$$

where **D** is a diagonal matrix, and therefore, Eq.1 can be written as

$$\mathbf{D}^{-1}(\mathbf{A}^{\mathrm{T}})^{-1}s\mathbf{z} = \mathbf{v}$$

$$s\mathbf{C}\mathbf{V} = \mathbf{J} - \mathbf{G}\mathbf{v} - \mathbf{A}\mathbf{z}$$

(3)

In right-inverse decomposition, Eq.1 takes the form

$$\Gamma^{-1} s \mathbf{Z} = \mathbf{v}$$

$$\mathbf{C} s \mathbf{v} = \mathbf{J} - \mathbf{G} \mathbf{v} - \mathbf{z}$$

(4)

If we denote by X the vector,

$$\mathbf{x} = \begin{bmatrix} \mathbf{v} \\ \mathbf{z} \end{bmatrix} \tag{5}$$

both Eq.3 and Eq.4, can be expressed by the following extended state-space representation,

$$s\mathbf{E}\mathbf{x} = \mathbf{A}\mathbf{x} + \mathbf{B}E_{i}$$

$$E_{o} = \mathbf{C}\mathbf{x} + DE_{i}$$

(6)

where A,B,C,E are matrices, D is a scalar,  $E_i$  is the input signal and  $E_o$  is the ourput signal. Hence the transfer function of the filter is:

$$H(s) = \frac{E_o(s)}{E_i(s)} = \mathbf{C}(\mathbf{E}s - \mathbf{A})^{-1}\mathbf{B} + \mathbf{D}$$

(7)

Namely, for the topological decomposition and the right-inverse decomposition approaches, the matrixes  $\mathbf{A}$  and  $\mathbf{E}$  are described by Eq.8 and Eq.9, respectively,

$$\mathbf{A} = \begin{bmatrix} 1 & 0 \\ -\mathbf{G} & 1 \end{bmatrix} \qquad \mathbf{E} = \begin{bmatrix} \mathbf{D}^{-1} (\mathbf{A}^{\mathbf{T}})^{-1} & 0 \\ 0 & \mathbf{C} \end{bmatrix}$$

(8)

$$\mathbf{A} = \begin{bmatrix} 1 & 0 \\ -\mathbf{G} & 1 \end{bmatrix} \qquad \mathbf{E} = \begin{bmatrix} \Gamma^{-1} & 0 \\ 0 & \mathbf{C} \end{bmatrix} \tag{9}$$

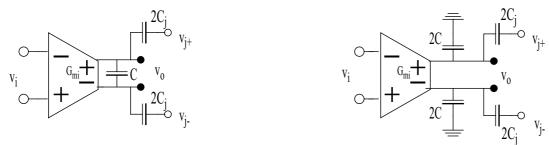

Note that Eq.7 can directly mapped into a  $G_m$ -C structure based on simple integrators (as those in Fig.3) in such a way, that matrix E represent capacitances, and matrix A and B transconductances. Interestingly, matrix E must be symmetric because non-diagonal elements represent node-to-node coupling capacitors.

## 3.2. Amplitude scaling

Using the model from the Eq.6, the internal functions fican be computed. These functions are the transfer functions from the input of the filter to the output of integrator i (xi) and are important for the calculation of the maximum signal level of the filter. We can group all the components fi in a vector (Eq.10) and calculate the magnitudes at the internal nodes with Eq.11.

Figure 3: First order section using conventional transconductors.

$$\mathbf{F} = \left[ f_1 \, f_2 \, \dots \, f_N \right]^{\dagger} \tag{10}$$

$$\mathbf{F} = (\mathbf{E}s - \mathbf{A})^{-1}\mathbf{B} \tag{11}$$

Once transfer function from the input to the internal nodes has been calculated, the filter can be scaled. Initial unscaled variables  $x_i$  from Eq.6 can be transformed on the mapped variables  $y_i$  which are scaled by doing  $\mathbf{y} = \mathbf{T}\mathbf{x}$  the state-space representation is then transformed as follows.

$$(\mathbf{TET}^{-1})s\mathbf{y} = [\mathbf{TAT}^{-1}]\mathbf{y} + [\mathbf{TB}]E_{i}$$

$$E_{o} = [\mathbf{CT}^{-1}]\mathbf{y} + \mathbf{D}E_{i}$$

$$\mathbf{E_{SCAL}}s\mathbf{y} = \mathbf{A_{SCAL}}\mathbf{y} + \mathbf{B_{SCAL}}E_{i}$$

$$E_{o} = \mathbf{C_{SCAL}}\mathbf{y} + \mathbf{D}E_{i}$$

(12)

There are two forms for amplitude scaling. The  $L_{\infty}$  norm, that consist on doing all the internal node amplitudes equal by scaling nodes impedances and the  $L_2$  norm, <sup>10</sup>that consist on doing

$$|f_i|_2^2 = \frac{1}{2\pi} \int_{-\infty}^{\infty} |f_i(j\omega)|^2 d\omega = k$$

(13)

If we choose to scale the filter by the  $L_{\infty}$  norm, matrix T in the Eq.12 must be chosen as

$$T_{ii} = \frac{1}{max(f_i(j\omega))} \quad T_{ij} = 0 \ i \neq j$$

(14)

on the other hand if the  $L_2$  norm is chosen to scale the filter matrix T must be chosen as

$$T_{ii} = \frac{1}{\sqrt{|f_i|_2^2}} \qquad T_{ij} = 0 \ i \neq j$$

(15)

If we scale the filter with he  $L_{\infty}$  or the  $L_2$  we achieve a completely scaled filter but the transconductors become in a non integer relation, hence for maintaining the integer relation between transconductors a completely scaled filter can not be achieved instead off a semiscaled filter will be designed.

# 3.3. Scaling the filter maintaining an integer relation between transconductors

To perform an scaled filter maintaining an integer relation between transconductors we use a matrix  $T_1$  that must have the following characteristic

Figure 4: Equivalent noise source of a transconductor.

$$T_{1ii} = \frac{M_i}{N_i} \qquad T_{1ij} = 0 \qquad i \neq j \tag{16}$$

The  $T_1$  coefficients must approximate as much as possible to the coefficients of T of Eq.12. This approximation is not unique. This allow to the designer to have a freedom degree for choosing the coefficients  $M_i$  and  $N_i$ . In this point we must distinguish two cases: Filters whose matrix E is diagonal (There are not bidirectional capacitors) and filters whose matrix E is not diagonal (there are bidirectional capacitors).

## 3.3.1. Matrix E diagonal.

Initially all the elements of the matrix  $\mathbf{A}$  are ones (except in many cases the coefficients that are provided by the transformation of the resistors at the source and load, but this resistors can be chosen in an integer relation) and in the case of LC ladder filters, this matrix have a maximum of three elements per row (band-pass ladders). Hence the matrix  $\mathbf{A}$  at the first represents an incidence matrix. When the transform matrix  $\mathbf{T}_1$  is applied the elements of the matrix  $\mathbf{A}$  are transformed as follow

$$A_{ij} \to \frac{M_i}{N_i} \times \frac{N_j}{M_i} \times A_{ij} \tag{17}$$

while the elements of the matrix  $\mathbf{E}$  are not altered. Hence, to achieve a integer relation between transconductors the elements of the transformed matrix  $(\mathbf{A_{SCAL}})$  must be multiplied by the least common multiple of the  $N_i \times M_j$  that have non zeros in the column j. This multiplication must be done in the matrix  $\mathbf{E}$  too because the unitary frequency of the integrators must be unaltered.

## 3.3.2. Matrix E not diagonal

When the matrix E is not diagonal, after scaling, the elements that are not in the diagonal are transformed as follow

$$E_{ij} \to \frac{M_i}{N_i} \times \frac{N_j}{M_j} \times E_{ij}$$

and  $E_{ji} \to \frac{M_j}{N_j} \times \frac{N_i}{M_i} \times E_{ji}$  (18)

As in Section.3.3.1 for obtaining an integer relation between the transconductors each row must be multiplied by a factor. If we denote this factor as  $\alpha$  for *ith* row and  $\beta$  for *jth* row the total transformation for the matrix **E** is

$$E_{ij} \rightarrow \frac{M_i}{N_i} \times \frac{N_j}{M_j} \times E_{ij} \times \alpha$$

and  $E_{ji} \rightarrow \frac{M_j}{N_j} \times \frac{N_i}{M_i} \times E_{ji} \times \beta$  (19)

Like this two elements represent bidirectional capacitors they must be equal. If they are not equal a new multiplication must be performed to satisfy this condition. This involves that ith row and jth row are interrelated. This interrelation does not exit when the E matrix is diagonal. In that case each row is only related by itself.

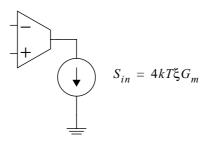

## 3.4. Noise scaling

The noise due to a transconductor can be modeled by a current source connected at the output of the transconductor as shown in Fig.4 where  $\xi$  is the noise factor of the transconductor which depends on the transconductor structure and typically has a value larger than 1.

The spectral density of the output noise due to the transconductors is 11,12

$$S_G(f) = \sum_{i} \sum_{l} 4kT\xi G_{m_l} |g_i|^2$$

(20)

where  $g_i$  is the transfer function from the input of transconductor l where i denotes de node of the filter and l the transconductor connected to node i. The output noise mean-squared value is

$$N_{Total} = \int_{0}^{\infty} S_G(f)df = \sum_{i} N_{oi}$$

(21)

where  $N_{oi}$  is the output noise produced by each node of the filter. This noise is proportional to the inverse of the sum of the transconductors as follow

$$N_{oi} \propto \frac{1}{\sum_{l} G_{mli}} \propto \frac{1}{I_i} \Rightarrow N_{oi} I_i = \alpha_i$$

(22)

where  $\sum_{l} G_{mli}$  and  $I_i$  are the transconductance and the bias current of the ith stage and  $\alpha_i$  is a constant set by the circuit topology. If we group  $g_i$  in a vector  $\mathbf{G}$

$$\mathbf{G} = \left[ g_1 \ g_2 \ ... g_N \right] \tag{23}$$

Using Eq.6, G can be computed as

$$\mathbf{G} = \mathbf{C}(s\mathbf{E} - \mathbf{A})^{-1} \tag{24}$$

A possible optimization for the noise is to minimize the noise with a constant total bias  $I_{Total}$ . This can be done with the following relation

$$\frac{N_{oi}}{I_i} = \frac{N_{Total}}{I_{Total}} \tag{25}$$

where

$$\frac{N_{oi}}{I_i} \propto \left| g_i \right|^2 \tag{26}$$

Thus for the lowest  $N_{Total}$  at a fixed  $I_{Total}$  all the  $G_{mi}$  should be scaled to the contribute the same noise to the filter output per unit bias current. Ideally, the optimum scale factor is<sup>3</sup>

$$\beta_i = \sqrt{\frac{N_{oi}/I_i}{N_{Total}/I_{Total}}} \tag{27}$$

This value is not usually an integer number, hence we must choose an integer value which will be close to the proportionate by Eq.27. The choice of this integer value is a new freedom degree for the designer.

In case of filters whose E matrix is not diagonal, As there are rows that are interrelated, noise scaling only will be performed in the not interrelated rows.

This values for noise scaling can be introduced in a vector denoted by noise\_scal.

## 3.5. Others characteristics to take into account

Many other characteristic must be taken into account like sensitivity to parameter variation or non-ideal effects of integrators blocks this characteristics are describes in <sup>13,14</sup>.

## 3.6. Performing optimization

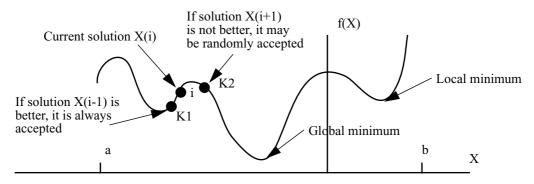

In section.3.3 and section.3.4 we have seen that the designer has a relative freedom degree for the choice of the coefficients M,N and  $noise\_scal$  for obtaining space state matrices that permit the use of unitary transconductors. Hence this coefficients can be introduced in an optimization algorithm. For doing this optimization, a simulated annealing algorithm ca be used.

## 3.6.1. Simulated annealing algorithm (SA)

SA is an effective and commonly optimization algorithm used to solve non linear optimization problems<sup>18</sup>. The principal idea of this algorithm is presented in Fig.5. For example, starting in state i the new state K1 is accepted, but the new state K2 is only accepted with a certain probability. The probability of accepting worse states is high at the beginning and decreases when a parameter denoted *Temperature* decreases. It can be shown that the algorithm will find, under certain condition, the global minimum and not get stuck in a local minimum. SA has been chosen because most of the optimization methods get stuck in a local minimum so they are very sensible to the starting point. This not happens in SA although is good to start with a starting point close to the minimum.

A general formulation for the optimization problem is

min

$$f(x)$$

subject to  $Ck_i(x)=0$ ;  $Cu_i(x)<0$   $i \in \varepsilon$  (28)

where  $\varepsilon$  is a finite sets of indices. The function f is denoted as the objective function or the cost function and the functions Ck and Cu are the constrains of the function f.

## 3.7. Our optimization problem

Our minimization problem consists on to minimize a cost function which must defined by the designer and can depend of: power consumption, area, linearity, DR..., and constrained principally by

$$noise\_scal \times (\mathbf{T_1ET_1^{-1}})s\mathbf{y} = noise\_scal \times [\mathbf{T_1AT_1^{-1}}]\mathbf{y} + noise\_scal \times [\mathbf{TB}]E_i$$

$$E_o = [\mathbf{CT_1^{-1}}]\mathbf{y} + \mathbf{D}E_i$$

$$\mathbf{E_{SCAL}}s\mathbf{y} = \mathbf{A_{SCAL}}\mathbf{y} + \mathbf{B_{SCAL}}E_i$$

$$E_o = \mathbf{C_{SCAL}}\mathbf{y} + \mathbf{D}E_i$$

(29)

where the transformation matrix  $T_1$  is defined in Eq.16 and *noise\_scal* is defined in Section.3.4. Other constrains can be defined too, for example the maximum node voltage. In this case the node voltages are the coefficients of the vector  $\mathbf{y}$  in Eq.29. Our vector  $\mathbf{x}$  is defined as

$$\mathbf{x} = \begin{bmatrix} M \ N \ noise\_\text{scal} \end{bmatrix} \tag{30}$$

The initial value of the vector xis chosen so that constrains will be satisfied, taking into account amplitude and noise scaling (section.3.2 and section.3.4).

Figure 5: Principle of simulated annealing.

Table 1Characteristics of the transconductor

| Vdd | 3.3 |

|-----|-----|

| بح  | 5   |

| Γ   | 0.7 |

## 4. DESIGN EXAMPLE USING OPTIMIZATION

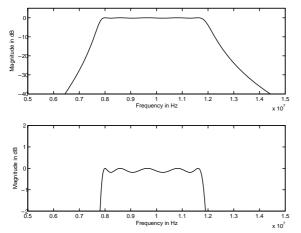

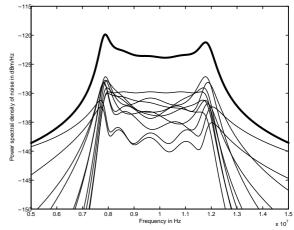

The proposed design is a 5 order band-pass Tchebycheb filter with a ripple of 0.188 dB a centre frequency of 9.63 MHz a band with of 3.8 MHz and noise specifications of -120 dBm in band and -135 dBm out or band. The only constrain for the proposed is that the internal nodes magnitude must be belong  $1.4 \times vin$ . The cost function has been defined as follow

$$f(x) = \frac{Power}{Power_0} + \frac{C_{Total}}{C_{Total0}} + \frac{max\_nodes}{100}$$

(31)

In this cost function Power and  $Power_0$  denote the power at  $\mathbf{x}$  and the power at  $\mathbf{x_0}$ .  $C_{Total}$  and  $C_{Total0}$  denote the total capacitance at  $\mathbf{x}$  and  $\mathbf{x_0}$  and maxnodes denote the maximum internal nodes magnitude of the filter. This cost function

intends to minimize the area, power and the internal nodes magnitude. Internal nodes magnitude has a weight of  $\frac{1}{100}$

because we want to minimize at first of all power and area. As it was said in the previous section these cost function and constrains must be defined by the designer and will depend on each particular design.

The proposed characteristic of the transconductor is shown in Table 1 where  $\Gamma$  is the current efficiency of the transconductor and is defined as

$$\Gamma = \frac{G_m}{I_O} \tag{32}$$

and  $I_{\mathcal{Q}}$  is the current consumption of the transconductor. The power consumption can be estimated hence as

$$Power = \sum_{i} \left(\frac{Vdd}{\Gamma}\right) G_{mi} \tag{33}$$

where *Vdd* is the supply voltage.

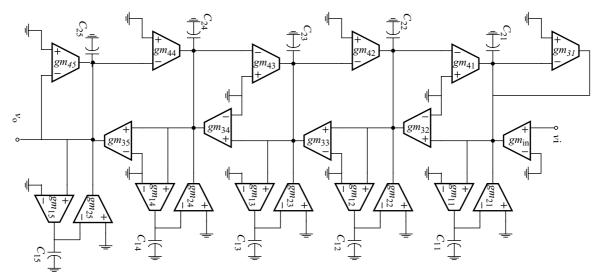

In Fig.6 it can be seen the conceptual schematic of the single ended version of the filter and in Table 2 we can see the number of unitary transconductor connected at each node after optimization is applied.

Table 2: Unitary transconductors and capacitors in the filter

| i | g <sub>mli</sub> | g <sub>m2i</sub> | g <sub>m3i</sub> | g <sub>m4i</sub> | $C_{1i}$ (pF) | $C_{2i}$ (pF) |

|---|------------------|------------------|------------------|------------------|---------------|---------------|

| 1 | 11               | 9                | 3                | 3                | 5.12          | 5.21          |

| 2 | 17               | 19               | 6                | 4                | 8.21          | 10.60         |

| 3 | 17               | 15               | 4                | 3                | 9.12          | 7.53          |

| 4 | 17               | 15               | 4                | 3                | 8.64          | 7.95          |

| 5 | 11               | 12               | 6                | 4                | 5.12          | 6.95          |

The value of the unitary transconductor is

Figure 6: Conceptual schematic of the filter

$$G_m = 31.43 \mu A/V \tag{34}$$

Principal characteristics of the filter before and after optimization are shown in Table 3.it can be observed that the improve in power and area is about 35%. This improve in power an area is performed at the cost of increasing the internal nodes magnitude (1.36 vs. 1.07 V). If internal nodes magnitude are needed to be smaller, the designer has two options, to add a constrain which limit the internal nodes magnitude more than in the example design or put into the cost function a bigger weight that penalizes higher internal nodes magnitude (Eq.31).

Table 3 Comparison of the filters before and after the optimization

|                        | Filter before optimization | Filter after optimization |

|------------------------|----------------------------|---------------------------|

| Power <sub>0</sub>     | 43 mW                      | 27.6mW                    |

| $C_{Total0}$           | 119 pF                     | 74.4 pF                   |

| max_nodes <sub>0</sub> | 1.07 V                     | 1.36V                     |

| Capacitance spread     | 2.2                        | 2.07                      |

# 5. CONCLUSIONS

A program for the design of continuous time programmable analog filters has been presented. The program uses a *Simulated Annealing* algorithm to optimize the filter characteristics. Using this program a five order Tchebycheb bandpass filter has been designed obtaining an improve at the system level about of 35% in power and area consumption compared with the initial design.

#### **ACKNOWLEDGMENT**

This work was supported in part by the spanish P.R.O.F.I.T. Project AFIN (FIT-070000-2001-843).

#### REFERENCES

- 1. T. Hollman, S. Lindfors, M. Länsirinne, J. Jussila, and K. A. I. Halonen, "A 2.7-V CMOS Dual-Mode Baseband Filter for PDC and WCDMA". *J. Solid-State Circuits*, **Vol.** 36, pp. 1148-1153, Jul. 2001.

- 2. H. A. Alzaher, H. O. Elwan, and M. Ismail, "A CMOS Highly Linear Channel-Select Filter for 3G Multistandard Integrated Wireless Receivers". *J. Solid-State Circuit*, Vol. 37, pp. 27-37, Jan. 2002.

- 3. F. Behbahani, W. Tan, A. Karimi-Sanjaani, A. Roithmeier, and A. A. Abidi, "A Broad- Band Tunable CMOS Channel-Select Filter for a Low-IF Wireless Receiver". *J. Solid-State Circuits*, **Vol**. 35, pp. 476-489, Apr. 2000.

- 4. P. Sutterlin and W. Downey. "A Power Line Communication Tutorial Challenges and Technologies". [http://www.echelon.com].

- 5. S. Pavan, and Y. P. Tsividis, "Widely Programmable High-Frequency Continuous-Time Filters in Digital CMOS Technology". *J. Solid-State Circuits*, Vol. 35, pp. 503-511, Apr. 2000.

- 6. V. Gopinathan, M. Tarsia, and D. Choi. "Design Considerations and Implementation of a Programmable High-Frequency Continuous-Time Filter and Variable-Gain Amplifier in Submicrometer CMOS", *J. Solid-State Circuits*, **Vol.** 34, pp. 1698-1707, Dec. 1999.

- 7. A. M. Durham, and W. Redman-White, "Integrated Continuous-Time Filter for 16-b DSP Interfaces", *J. Solid-State Circuits*, Vol. 28, pp. 835-839, Jul. 1993.

- 8. E. Lauwers, and G. Gielen, "ACTIF: A high-level Power Estimation Tool for Analog Continuous-Time Filters". *Proc. Int, Conf. on Computer-Aided Design*, pp. 193-196, 2000.

- 9. M. R. Kobe, E. Sánchez-Sinencio, and J. Ramírez-Angulo, "OTA-C Biquad-Based Filter Silicon Compiler", *Analog Integrated Circuits and Signal Processing*, **Vol.** 3, pp. 243-258, 1993.

- 10. G. Groenewold."The Design of High Dynamic Range Continuous-Time Integratable Bandpass Filters", *IEEE Trans. Circuits and Systems*, **Vol**.38, pp. 838-852, Aug. 1991.

- 11. G. E. Efthivoulidis, L. Tòth, and Y. P. Tsividis. "Noise in G<sub>m</sub>-C Filters", *IEEE Trans. Circuits and Systems-II*, **Vol.** 45, pp. 295-302, Mar. 1998.

- 12. L. Tóth, G. E. Efthivoulidis, V. Gopinathan, and Y. P. Tsividis. "General Result for Resistive Noise in Active RC and MOSFET-C Filters", *IEEE Trans. Circuits and Systems*, **Vol**.45, pp. 295-302, Mar. 1998.

- 13. S. Koziel, S. Szczepanski, and R. Schauman. "A general Approach to continuous-time  $G_m$ -C Filters based on matrix descriptions" Proc. ISCAS, **Vol.** IV, pp. 647-650, Scottdale (AR), May 2002.

- 14. W. J. A. de Heij, E. Seevinck, and K. Hoen. "Practical Formulation of the Relation between Filter Specifications and the Requirements for Integrator Circuits", *IEEE Trans. Circuits and Systems-II*, **Vol**. 36, pp. 1124-1128, Aug 1989.

- 15. N. P. J. Greer, R. K. Henderson, L. Ping, and J. I. Sewell. "Matrix methods for the design of transconductors ladder filters", *IEE Proc.-Circuits Devices Sys.*, Vol.141, pp. 89-100, Apr. 1994.

- 16. L. Yue, N. P. J. Greer, and J. I. Sewell "Efficient design of ladder-based transconductor-capacitor filters and equalizers", *IEE Proc.-Circuits Devices Syst.* Vol 142, pp. 263-272, Aug. 1995.

- 17. R. K. Henderson, L. Ping, and J. I. Sewell. "Canonical design of integrated ladder filters", *IEE Proc.-G*, Vol.138, pp. 222-228, Apr. 1994.

- 18. F. Medeiro, B. Pérez-Verdú, and A. Rodríguez-Vázquez. *Top-down design of high-performance sigma-Delta Modula-tors*, Kluwer Academic Publishers, Dordrecht (The Netherlands), 1999.

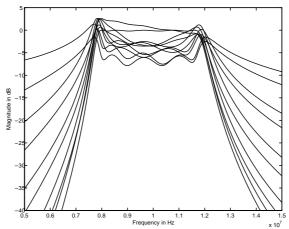

Figure 7: Magnitude of the designed filter

Figure 7: Spectral density of noise and noise produced by each node

Figure 8: Internal nodes magnitude