University of Pennsylvania ScholarlyCommons

Publicly Accessible Penn Dissertations

2019

## Efficient Precise Dynamic Data Race Detection For Cpu And Gpu

Yuanfeng Peng University of Pennsylvania, yuanfeng.jack.peng@gmail.com

Follow this and additional works at: https://repository.upenn.edu/edissertations

Part of the Computer Sciences Commons

#### **Recommended Citation**

Peng, Yuanfeng, "Efficient Precise Dynamic Data Race Detection For Cpu And Gpu" (2019). *Publicly Accessible Penn Dissertations*. 3641. https://repository.upenn.edu/edissertations/3641

This paper is posted at ScholarlyCommons. https://repository.upenn.edu/edissertations/3641 For more information, please contact repository@pobox.upenn.edu.

## Efficient Precise Dynamic Data Race Detection For Cpu And Gpu

#### Abstract

Data races are notorious bugs. They introduce non-determinism in programs behavior, complicate programs semantics, making it challenging to debug parallel programs. To make parallel programming easier, efficient data race detection has been a research topic in the last decades. However, existing data race detectors either sacrifice precision or incur high overhead, limiting their application to real-world applications and scenarios. This dissertation proposes approaches to improve the performance of dynamic data race detection without undermining precision, by identifying and removing metadata redundancy dynamically. This dissertation also explores ways to make it practical to detect data races dynamically for GPU programs, which has a disparate programming and execution model from CPU workloads. Further, this dissertation shows how the structured synchronization model in GPU programs can simplify the algorithm design of

data race detection for GPU, and how the unique patterns in GPU workloads enable an efficient implementation of the algorithm, yielding a high-performance dynamic data race detector for GPU programs.

**Degree Type** Dissertation

Degree Name Doctor of Philosophy (PhD)

Graduate Group Computer and Information Science

First Advisor Joseph Devietti

Keywords Concurrency, Data Races, Debugging, GPU, Parallel Programming, Software Tools

Subject Categories Computer Sciences

#### EFFICIENT PRECISE DYNAMIC DATA RACE DETECTION FOR CPU AND GPU

#### Yuanfeng Peng

#### A DISSERTATION

in

Computer and Information Science

#### Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

2019

Supervisor of Dissertation

Joseph Devietti Assistant Professor of Computer and Information Science

Graduate Group Chairperson

Rajeev Alur Zisman Family Professor of Computer and Information Science

Dissertation Committee

Steve Zdancewic, Professor of Computer and Information Science

Rajeev Alur, Zisman Family Professor of Computer and Information Science

Mayur Naik, Associate Professor of Computer and Information Science

Vinod Grover, Director of Engineering, NVIDIA

#### EFFICIENT PRECISE DYNAMIC DATA RACE DETECTION FOR CPU AND GPU

© COPYRIGHT

2019

Yuanfeng Peng

This work is licensed under a Creative Commons Attribution 4.0 License.

To view a copy of this license, visit:

https://creativecommons.org/licenses/by/4.0/

To my wife Jing, for her love, support, and trust along this journey.

I would never have made it here without you.

#### ACKNOWLEDGEMENTS

Many people say surviving a Ph.D. program isn't an easy job. This is true, although I wouldn't use the word *survive* today, when I'm about to graduate. For me, the past 5 years have been an exciting adventure, made possible by many people I owe a debt of gratitude to.

I'll start by thanking my advisor Joe Devietti. Joe, thanks for being such an awesome mentor, collaborator, and friend. I can still remember the interview we had 6 years ago, the theme of which was on data race detection, a topic that became the research focus of my whole Ph.D. study. Thanks for admitting me as your first student, which is the start of the awesome journey. Your patience and trust meant a lot to me, especially in the first few years, when I, as an international student, was struggling to adapt to the new environment and overcome cultural and language barriers. I appreciate your optimism and constant encouragements, which are especially invaluable when things were not looking up. Thanks for being such a great teacher, I can still recall the 501 classes 5 years ago. Thanks for all the jokes and humor in our meetings and discussions, which spiced up the workdays and made the long journey more pleasant. Special thanks are also due to you for your understanding and openness for letting me finish up the program remotely in the past 3 years, which makes my life much easier. Most importantly, I want to thank you for your enthusiasm for research and hacking, which is contagious and I'm glad and proud that I still love research after all these years.

I'm lucky to have collaborated with a number of amazing people. I'd like to thank Ben Wood, for his insights, hard work, and jokes in our collaborations, and for his unparalleled ability to come up with creative acronyms. William Mansky is a magician of formal proofs, and I'm grateful for him teaching me how to do that. I'm grateful for the PL insights and perspectives from Steve Zdancewic, and for his helpful feedback on writing. I'm amazed at the incredible coding abilities of Arial Eizenberg, and I appreciate learning so much from his code. I also want to thank Christian DeLozier, for all the ideas and resources he kindly shared. I appreciate the energy and insights in research from Brandon Lucia. I owe my special thanks to Prof. Yuebin Bai, who gave me significant help and support for starting my adventure in research back in

college.

I also got a tremendous amount of help from faculty members at Penn. I appreciate the constructive feedback from Andreas Haeberlen, and helpful advice from Steve Zdancewic, on my WPE II writing and presentation. I also want to thank Steve Zdancewic, Rajeev Alur, Mayur Naik, and Vinod Grover, for kindly agreeing to be my dissertation committee, and for their feedback on my thesis proposal.

In the summer of 2016, I had the opportunity to work with Vinod Grover at NVIDIA. I'm grateful for his insights and help in my intern project, and I'm happy that we had the opportunity to continue our collaboration after the internship. I also want to thank my colleagues at NVIDIA, especially to Yang Chen, Sean Lee, Mahesh Ravishankar, and Thibaut Lutz, for their help in hacking the NVCC compiler.

At Penn, my fellow students have made my life more rewarding. I would like to thank all past and current members of ACG, including Brooke Candelore, Christian DeLozier, Ariel Eizenberg, Omar Navarro Leija, Luo Liang, Laurel Emurian Mirarchi, Sameer Railkar, Kelly Shiptoski, Nimit Singhania, Akshitha Sriraman, Abhishek Udupa, for the great atmosphere of the group. I'm also grateful for making friends with many students in the department, including Yu Wang, Meng Xu, Xie Long, Sean Welleck, Sepehr Assadi, Yang Li, Teng Zhang, and Jizhou Yan: thank you all for making my time at Penn more memorable.

Finally, I would like to thank my family. I'm grateful for my parents, for their love to, support for and faith in me throughout my education. I want to thank my sister, for being a role model of mine when I was a kid and for taking care of my parents when I was abroad doing my Ph.D. Last but certainly not the least, a few words to my wife and soul mate, Jing. You have been a wonderful lover and partner in this journey, and I'm grateful for your patience and faith in me for all these years, especially during the difficult days, when we had to be physically apart and had no money. You made my life colorful, bringing smiles and laughs into our daily lives. Thanks for all the company and consolation, in all these days when we are not wealthy yet happy. I have a lifetime of words for you, but for now let me stop with one more thing: after all the difficulties you've encountered and sacrifices you've made, thank you for being such a warrior for your dream, and for being such a unique YOU that I love and am proud of, for just the way you are.

#### ABSTRACT

#### EFFICIENT PRECISE DYNAMIC DATA RACE DETECTION FOR CPU AND GPU

#### Yuanfeng Peng

#### Joseph Devietti

Data races are notorious bugs. They introduce non-determinism in programs behavior, complicate programs semantics, making it challenging to debug parallel programs. To make parallel programming easier, efficient data race detection has been a research topic in the last decades. However, existing data race detectors either sacrifice precision or incur high overhead, limiting their application to real-world applications and scenarios. This dissertation proposes approaches to improve the performance of dynamic data race detection without undermining precision, by identifying and removing metadata redundancy dynamically. This dissertation also explores ways to make it practical to detect data races dynamically for GPU programs, which has a disparate programming and execution model from CPU workloads. Further, this dissertation shows how the structured synchronization model in GPU programs can simplify the algorithm design of data race detection for GPU, and how the unique patterns in GPU workloads enable an efficient implementation of the algorithm, yielding a high-performance dynamic data race detector for GPU programs.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv |                |                                                                  |     |  |  |  |

|---------------------|----------------|------------------------------------------------------------------|-----|--|--|--|

| ABSTRACT            |                |                                                                  |     |  |  |  |

| LI                  | LIST OF TABLES |                                                                  |     |  |  |  |

| LI                  | sт о           | F FIGURES                                                        | xii |  |  |  |

| 1                   | Intro          | oduction                                                         | 1   |  |  |  |

| 2                   | Bac            | kground                                                          | 4   |  |  |  |

|                     | 2.1            | Data races                                                       | 4   |  |  |  |

|                     | 2.2            | Precise Dynamic Data Race Detection                              | 5   |  |  |  |

|                     | 2.3            | Vector Clock Algorithm For Dynamic Race Detection                | 6   |  |  |  |

| 3                   | Met            | adata Redundancy Reduction in Dynamic Race Detection             | 9   |  |  |  |

|                     | 3.1            | Metadata Redundancy                                              | 9   |  |  |  |

|                     | 3.2            | The SLIMFAST System                                              | 11  |  |  |  |

|                     | 3.3            | Implementation of SLIMFAST                                       | 18  |  |  |  |

|                     | 3.4            | Evaluation of SLIMFAST                                           | 21  |  |  |  |

|                     | 3.5            | Conclusion                                                       | 27  |  |  |  |

| 4                   | Perf           | formant Architecture for Race Safety with No Impact on Precision | 28  |  |  |  |

|                     | 4.1            | Metadata Redundancy at the Hardware Level                        | 28  |  |  |  |

|                     | 4.2            | The PARSNIP System                                               | 29  |  |  |  |

|                     | 4.3            | Optimizations in PARSNIP                                         | 41  |  |  |  |

|                     | 4.4            | Design Evaluation                                                | 44  |  |  |  |

|                     | 4.5            | Conclusion                                                       | 50  |  |  |  |

| 5  | Pra                 | ctical Dynamic Data Race Detection for GPU                      | 51  |  |  |

|----|---------------------|-----------------------------------------------------------------|-----|--|--|

|    | 5.1                 | GPU (CUDA) Programming Model                                    | 51  |  |  |

|    | 5.2                 | Challenges For Dynamic Data Race Detection on GPU               | 53  |  |  |

|    | 5.3                 | Redundancy in GPU Race Detection                                | 54  |  |  |

|    | 5.4                 | Barracuda Semantics                                             | 55  |  |  |

|    | 5.5                 | Implementation                                                  | 67  |  |  |

|    | 5.6                 | Evaluation                                                      | 77  |  |  |

|    | 5.7                 | Conclusion                                                      | 80  |  |  |

| 6  | Mor                 | e Efficient Data Race Detection for GPU                         | 82  |  |  |

| U  | 6.1                 |                                                                 |     |  |  |

|    |                     | The CURD System                                                 | 82  |  |  |

|    | 6.2                 | Implementation                                                  | 94  |  |  |

|    | 6.3                 | $Evaluation \ of \ Curd \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 97  |  |  |

|    | 6.4                 | Conclusion                                                      | 104 |  |  |

| 7  | Rela                | ated Work                                                       | 105 |  |  |

|    | 7.1                 | CPU Data Race Detection                                         | 105 |  |  |

|    | 7.2                 | GPU Data Race Detection                                         | 107 |  |  |

| 8  | Con                 | clusions                                                        | 109 |  |  |

|    | 8.1                 | Summary of Techniques                                           | 109 |  |  |

|    | 8.2                 | Limitations                                                     | 110 |  |  |

|    | 8.3                 | Looking forward                                                 | 111 |  |  |

| BI | <b>BIBLIOGRAPHY</b> |                                                                 |     |  |  |

### LIST OF TABLES

| 3.1 | SLIMFAST characterization data                           | 25  |

|-----|----------------------------------------------------------|-----|

| 4.1 | Components in access history checks                      | 31  |

| 4.2 | Illustrative example trace of PARSNIP                    | 39  |

| 4.3 | Events per 1K instructions in PARSNIP.                   | 49  |

| 5.1 | The benchmarks used with BARRACUDA.                      | 78  |

| 6.1 | Benchmark details with $\operatorname{Curd}\text{-}Lazy$ | 101 |

## LIST OF FIGURES

| 2.1        | Illustrative example of a program with data races.   | 5 |

|------------|------------------------------------------------------|---|

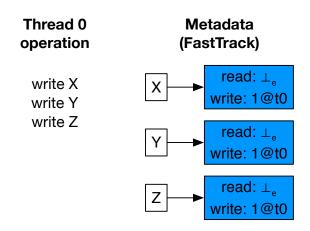

| 3.1        | Example trace showing metadata redundancy            | C |

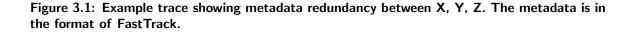

| 3.2        | Redundancy ratio of programs                         | 1 |

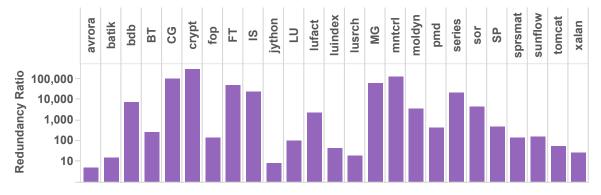

| 3.3        | FASTTRACK operational semantics                      | 2 |

| 3.4        | <i>EpochPair</i> and <i>EpochPlusVC</i> in FASTTRACK | 3 |

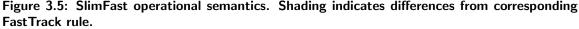

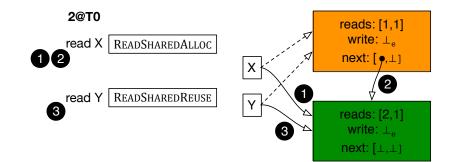

| 3.5        | SLIMFAST operational semantics                       | 4 |

| 3.6        | Invariant metadata for writes                        | 5 |

| 3.7        | The <i>EpochPlusVC</i> format in SLIMFAST            | 5 |

| 3.8        | Metadata sharing via Next map                        | 5 |

| 3.9        | EpochPlusVC redundancy                               | 7 |

| 3.10       | Invariant in <i>EpochPair</i>                        | 9 |

| 3.11       | SLIMFAST's metadata update algorithm                 | ) |

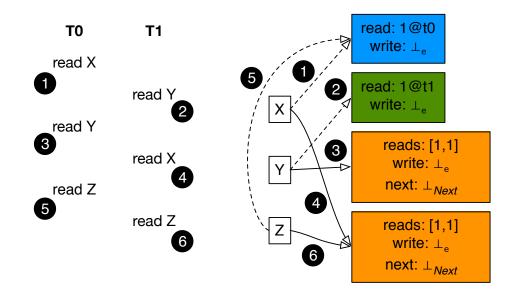

| 3.12       | Space reduction over FASTTRACK                       | 2 |

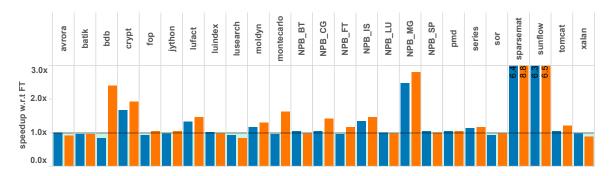

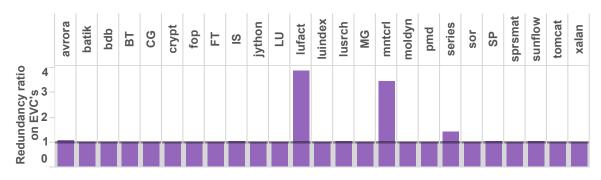

| 3.13       | Speedup of FASTTRACK-reference and SLIMFAST          | 3 |

| 3.14       | <i>EpochPlusVC</i> 's redundancy ratio in SLIMFAST   | 7 |

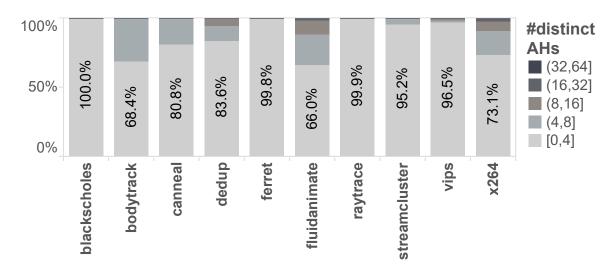

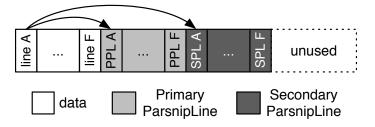

| 4.1        | Redundancy in cache lines                            | 0 |

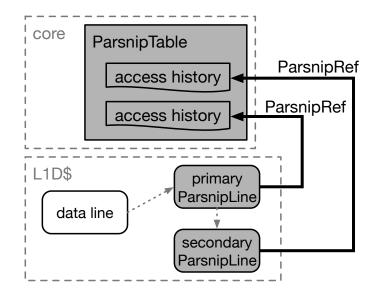

| 4.1        | PARSNIP's key states                                 |   |

| 4.2        | PARSNIP's physical address space layout              |   |

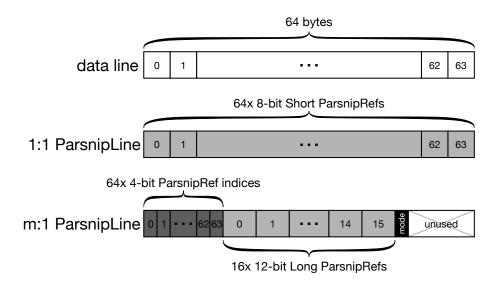

| 4.4        | ParsnipLine modes                                    |   |

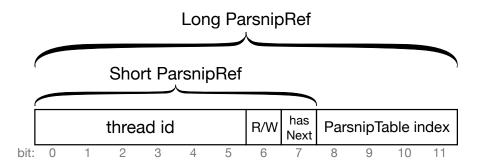

| 4.5        | ParsnipRef formats                                   |   |

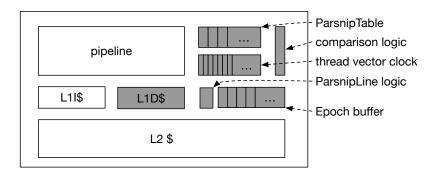

| 4.5<br>4.6 | PARSNIP additions to a conventional core             |   |

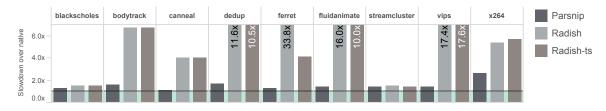

| 4.7        | Slowdown of PARSNIP                                  |   |

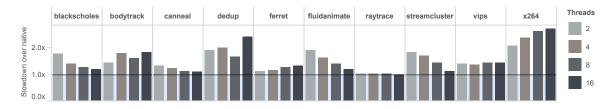

| 4.8        | Scalability of PARSNIP                               |   |

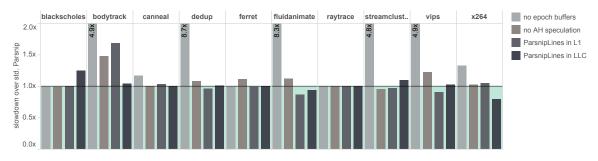

| 4.9        | Optimizations effectiveness in PARSNIP               |   |

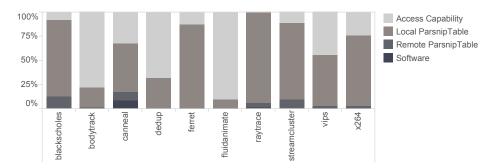

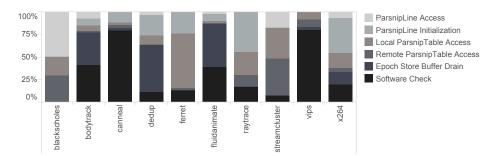

| -          | Latency breakdown in PARSNIP                         |   |

|            | Events breakdown in PARSNIP   48                     |   |

| 1.11       |                                                      | , |

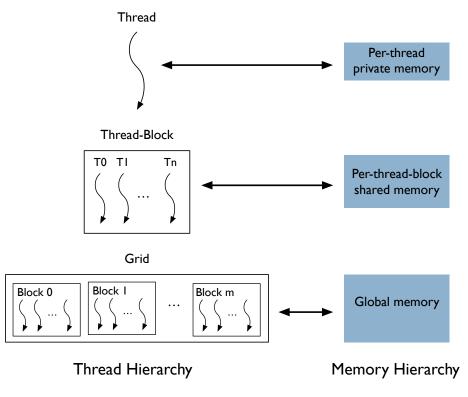

| 5.1        | The CUDA thread and memory hierarchy                 | 2 |

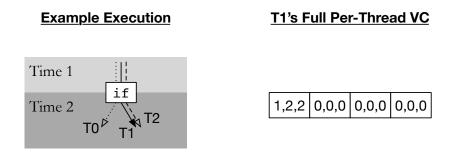

| 5.2        | Example of PTVC redundancy                           | 5 |

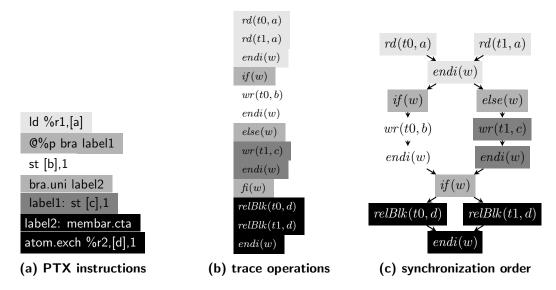

| 5.3        | Modeling PTX as a trace                              | 5 |

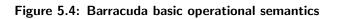

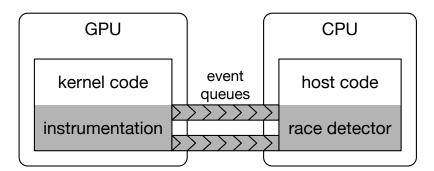

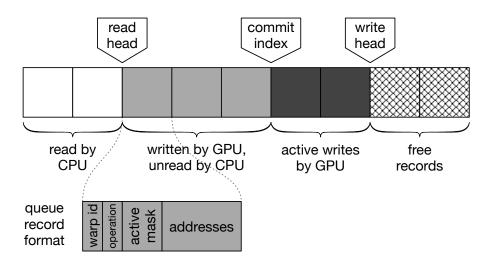

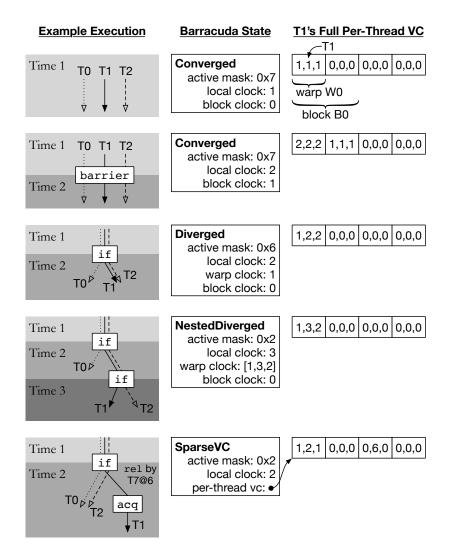

| 5.4        | BARRACUDA basic operational semantics                | 2 |

| 5.5        | Semantics for synchronization operations             | 5 |

| 5.6  | Memory fence litmus tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.7  | Overview of BARRACUDA system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67  |

| 5.8  | Events queue in BARRACUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70  |

| 5.9  | PTVC formats in BARRACUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72  |

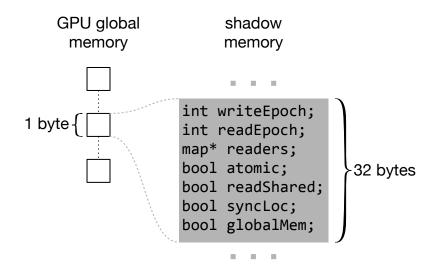

| 5.10 | $\operatorname{BarracudA}$ shadow memory format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75  |

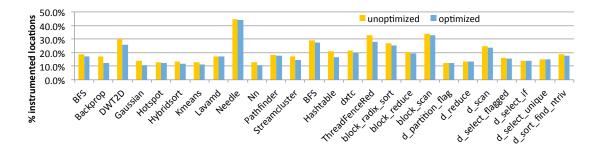

| 5.11 | Static PTX instructions instrumented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79  |

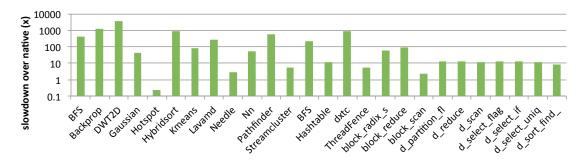

| 5.12 | Performance overhead of BARRACUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79  |

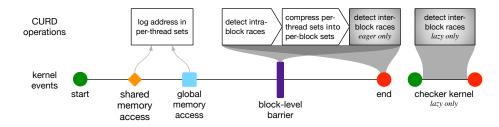

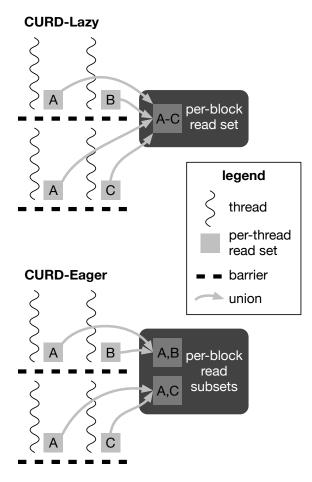

| 6.1  | High-level operation of CURD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84  |

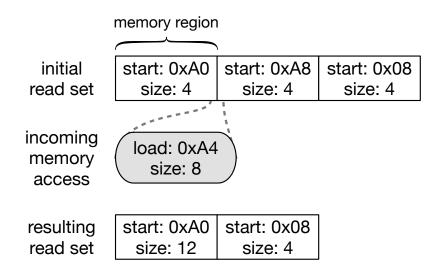

| 6.2  | $\mathrm{Curd}$ 's read and write sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84  |

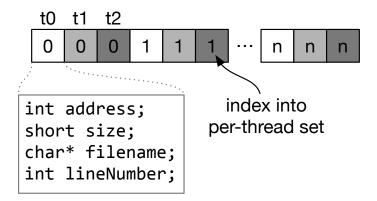

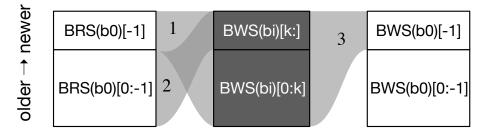

| 6.3  | Layout of read/write sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86  |

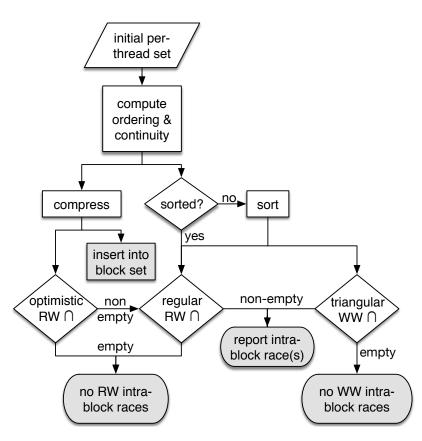

| 6.4  | Steps in intra-block race detection in $CURD$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 87  |

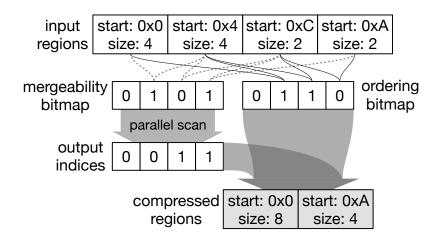

| 6.5  | Per-thread sets compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88  |

| 6.6  | Compression in lazy and eager schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

| 6.7  | $\operatorname{Curd}$ -Eager inter-block checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93  |

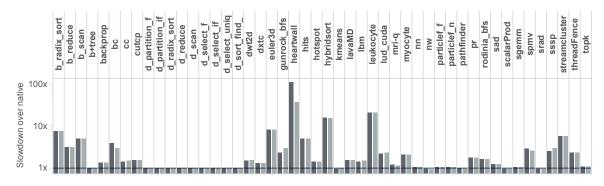

| 6.8  | Slowdown of $Curd$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98  |

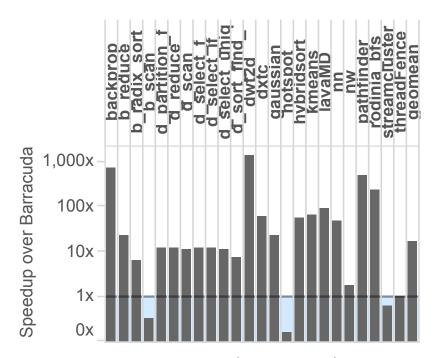

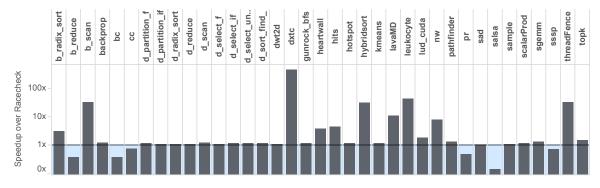

| 6.9  | Curd-Lazy's speedup over $\operatorname{Barracuda}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

| 6.10 | $\operatorname{Curd}-Lazy's$ speedup over CUDA-Racecheck $\hfill \ldots \hfill n hfill not \hfill \ldots \hfill \ldots \hfill \ldots \hfill not \hfill \ldots \hfill \hfill not \hfill \hfill \hfill \hfill \hfill \hfill \hfill not \hfill \hfill not \hfill $ | 99  |

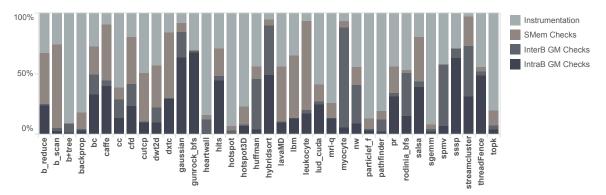

| 6.11 | Overhead breakdown of $CURD$ -Lazy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 102 |

#### CHAPTER 1

# Introduction

With the proliferation of multicore processors in everything from servers to wearables, parallel programming has become ever more critical to efficiently and effectively utilizing modern processors. However, how to write correct and efficient multithreaded programs remains a well-known challenge in parallel computing. In particular, the potential for programs to contain data races is an issue that programmers often have to address. Data races can introduce non-sequentially-consistent[69] and/or undefined behavior[13] into programs, making programs hard to understand and reason about. In fact, data races can cause disastrous consequences in the real world: they are the culprits in the Therac-25 disaster[62], the Northeastern electricity blackout of 2003[43], and the mismatched NASDAQ Facebook share prices of 2012[56, 10]. Unfortunately, even experienced programmers can write code that contains data races, especially as the complexity of a parallel program grows.

To prevent potential disastrous outcomes, programmers typically need to prevent the presence of data races in their code, a process that involves extensive testing and debugging efforts. A useful tool for debugging parallel programs is data race detectors; in fact, identifying general data races is a key part of several algorithms for checking or enforcing higher-level properties of multithreaded programs, such as atomicity[37, 42] or determinism[85, 24]. As a result, data race detection has been an attractive research topic for the past a few decades, and there exists extensive work on static, dynamic, or hybrid detection schemes[1, 79, 38, 31, 100, 25, 54, 117, 101, 113, 39, 91, 68].

Unfortunately, building data race detectors that are both efficient and precise is a challenging task[31, 38, 41]. Existing approaches remain limited by missing true data races, reporting false data races, or incurring prohibitively high run-time overheads. It remains an open question whether efficient, precise data race detection can be provided in production scenarios.

Another important aspect of data race detection research is to support parallel programs that run on hardware other than CPUs[119, 75, 118, 64]. In particular, with the increasing ubiquity of GPU hardware and applications, efficient data race detection schemes for GPU programs have become more and more necessary. However, data race detectors designed for the CPU execution model typically cannot scale to the large numbers of threads in a GPU program[81], thus cannot be applied. With more complex GPU applications emerging, the need for an efficient data race detector for GPU is increasingly pressing.

This work proposes approaches to improve the efficiency of dynamic data race detection without sacrificing precision for CPU, and algorithms to enable practical data race detection for GPU. A key insight in improving the efficiency of dynamic data race detectors is that redundancy abounds in the metadata maintained by the detectors, which promises potential performance gain if such redundancy can be reduced properly. Full precision can be guaranteed as long as the redundancy reduction is lossless, i.e., no useful information is lost in the reduction. With effective metadata redundancy reduction, both the temporal and spatial overheads of dynamic data race detection can be improved. The improvement is even more significant if the reduction is done in hardware, making practical a hardware-assisted race detection system that can be always-on.

Further, the general idea of identifying and reducing redundant metadata can be also useful in scaling classical data race detection algorithms designed for CPU applications to GPU programs, enabling the first fully precise dynamic data race detector for GPU. To build an even more efficient GPU data race detector, the next part of this work is to take into account the structured synchronization paradigm and common memory access patterns when designing an algorithm for GPU data race detection. This enables the construction of a new GPU data race detector that outperforms prior industry-level tools while providing stronger detection capability.

The subsequent chapters of this dissertation are organized as follows. Chapter 2 provides relevant background knowledge and related work about the data race detection problem. Chapter 3 explains the metadata redundancy in dynamic data race detection and introduces the SLIMFAST

system, a pure-software scheme to reduce such redundancy and improve performance. Chapter 4 next discusses metadata redundancy shown at the hardware level and describes the design of PARSNIP, a hardware-assisted data race detector that manages redundancy reduction in hardware. Chapter 5 switches focus to data race detection for GPU, by presenting BARRACUDA, a data race detector that scales classical CPU-oriented algorithm to GPU. Chapter 6 introduces a more efficient algorithm design for GPU race detection and describes CURD, an efficient implementation of the algorithm that provides higher performance and coverage than previous tools. Chapter 7 discusses related work to this dissertation. Chapter 8 concludes the dissertation.

This dissertation draws on multiple published works. The SLIMFAST [87] system, described in Chapter 3, was originally presented at IPDPS 2018. The PARSNIP [89] design, described in Chapter 4, was originally published at MICRO 2017. The BARRACUDA [29] system, introduced in Chapter 5, was originally presented at PLDI 2017. The CURD [88] detector was presented at PLDI 2018, and Chapter 6 explains the design of CURD and includes evaluation results of it. The remaining content is original work.

#### CHAPTER 2

# Background

Data races have been a topical research problem. This chapter provides a brief overview of the general data race detection problem.

#### 2.1. Data races

A multithreaded program can be modelled as a single trace of operations, with operations from each thread interleaved. Operations consist of memory reads and writes, lock acquires and releases, and thread fork and join. The *happens-before* relation  $\xrightarrow{hb}$  is a partial order over these trace events. Given events *a* and *b*, we say *a* happens before *b*, written  $a \xrightarrow{hb} b$ , if:

- a and b are from the same thread and a precedes b in program order; or

- a precedes b in synchronization order, e.g., a is a lock release relt(m) and b the subsequent acquire acqt(m); or

- (a, b) is in the transitive closure of program order and synchronization order.

If *a happens-before b* then we can equivalently say that *b happens-after a*. Two events not ordered by the *happens-before* relation are said to be concurrent. Two memory accesses to the same address form a *data race* if they are concurrent and at least one access is a write.

The impact of data races on a program's behaviour can be illustrated using a simple example in Figure 2.1. The program in this example has two threads, *Thread1* and *Thread2*, and a shared variable x. *Thread1* writes to x on line 1 and line 2, and *Thread2* reads the value of x on line 1. As the writes by *Thread1* and the read by *Thread2* are not ordered by any synchronization operation, there are two instances of data races, namely (line 1 by *Thread1*, line 1 by *Thread2*) and (line 2 by *Thread1*, line 1 by *Thread2*). Because the value of x read by *Thread2* can be either 1 or otherwise, the behavior of *Thread2* becomes unpredictable: either foo() or bar()

| Thread | 1     | Thread 2   |

|--------|-------|------------|

| x = 0  |       | if x == 1: |

| x = 1  |       | foo()      |

|        |       | else:      |

|        |       | bar()      |

|        | x = 0 |            |

Figure 2.1: Illustrative example of a program with data races.

can be called.