# EFFICIENT AND ROBUST SIMULATION, MODELING AND CHARACTERIZATION OF IC POWER DELIVERY CIRCUITS

A Dissertation

by

## YA WANG

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Peng Li             |

|---------------------|---------------------|

| Committee Members,  | Weiping Shi         |

|                     | Prasad Enjeti       |

|                     | Duncan M. Walker    |

| Head of Department, | Miroslav M. Begovic |

December 2017

Major Subject: Computer Engineering

Copyright 2017 Ya Wang

#### ABSTRACT

As the Moore's Law continues to drive IC technology, power delivery has become one of the most difficult design challenges. Two of the major components in power delivery are DC-DC converters and power distribution networks, both of which are time-consuming to simulate and characterize using traditional approaches. In this dissertation, we propose a complete set of solutions to efficiently analyze DC-DC converters and power distribution networks by finding a perfect balance between efficiency and accuracy.

To tackle the problem, we first present a novel envelope following method based on a numerically robust time-delayed phase condition to track the envelopes of circuit states under a varying switching frequency. By adopting three fast simulation techniques, our proposed method achieves higher speedup without comprising the accuracy of the results. The robustness and efficiency of the proposed method are demonstrated using several DC-DC converter and oscillator circuits modeled using the industrial standard BSIM4 transistor models. A significant runtime speedup of up to 30X with respect to the conventional transient analysis is achieved for several DC-DC converters with strong nonlinear switching characteristics.

We then take another approach, average modeling, to enhance the efficiency of analyzing DC-DC converters. We proposed a multi-harmonic model that not only predicts the DC response but also captures the harmonics of arbitrary degrees. The proposed full-order model retains the inductor current as a state variable and accurately captures the circuit dynamics even in the transient state. Furthermore, by continuously monitoring state variables, our model seamlessly transitions between continuous conduction mode and discontinuous conduction mode. The proposed model, when tested with a system decoupling technique, obtains up to 10X runtime speedups over transistor-level simulations with a maximum output voltage error that never exceeds 4%.

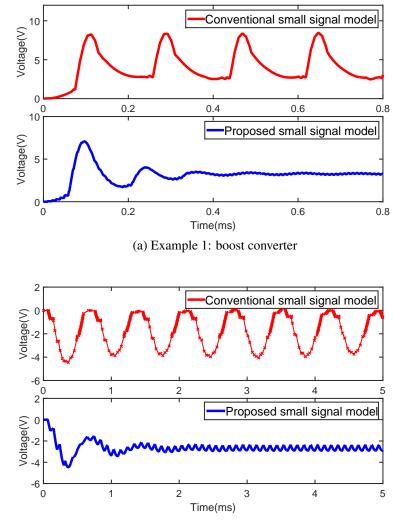

Based on the multi-harmonic averaged model, we further developed the small-signal model that provides a complete characterization of both DC averages and higher-order harmonic responses. The proposed model captures important high-frequency overshoots and undershoots of the converter response, which are otherwise unaccounted for by the existing techniques. In two converter examples, the proposed model corrects the mislead-ing results of the existing models by providing the truthful characterization of the overall converter AC response and offers important guidance for converter design and closed-loop control.

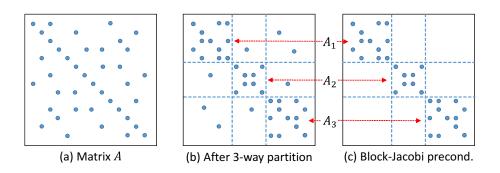

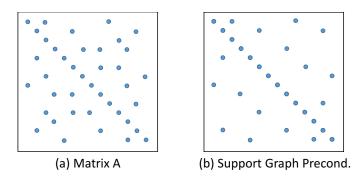

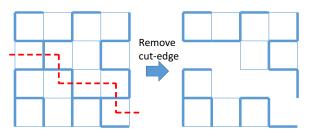

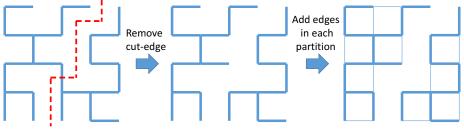

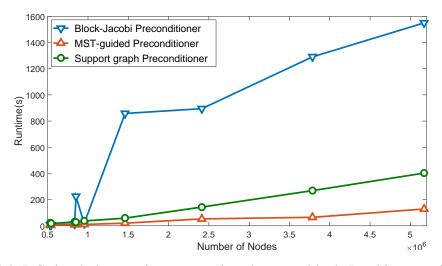

To address the problem of time-consuming simulation of power distribution networks, we present a partition-based iterative method by integrating block-Jacobi method with support graph method. The former enjoys the ease of parallelization, however, lacks a direct control of the numerical properties of the produced partitions. In contrast, the latter operates on the maximum spanning tree of the circuit graph, which is optimized for fast numerical convergence, but is bottlenecked by its difficulty of parallelization. In our proposed method, the circuit partitioning is guided by the maximum spanning tree of the underlying circuit graph, offering essential guidance for achieving fast convergence. The resulting block-Jacobi-like preconditioner maximizes the numerical benefit inherited from support graph theory while lending itself to straightforward parallelization as a partition-based method. The experimental results on IBM power grid suite and synthetic power grid benchmarks show that our proposed method speeds up the DC simulation by up to 11.5X over a state-of-the-art direct solver.

# DEDICATION

To my mother, my father and my wife.

#### ACKNOWLEDGMENTS

First I would like to express my greatest gratitude for my advisor, Prof. Peng Li, for continuously providing support and help for the past five years. With his profound experience in circuit simulation, he introduced me to the frontier of electronic design automation research and offered many valuable insights to my research work. His diligence and perseverance have set the standard for me and keep driving me to reach for higher goals. I am truly thankful for having Prof. Peng Li as my Ph.D. advisor. This dissertation would not have been possible without him.

I would like to thank Dr. Weiping Shi, Dr. Prasad Enjeti and Dr. Hank Walker for serving on my Ph.D. committee and providing insightful comments and suggestions. I have greatly benefited from their feedbacks on my preliminary exam.

I would also like to thank my colleagues and friends in Computer Engineering & System Group. Di Gao and Wenrui Zhang have been truly reliable teammates while we are working on the same research projects. Dr. Yong Zhang, Dr. Qian Wang, Dr. Honghuang Lin, Jimmy Jin and Xin Zhan have all offered tremendous help by providing inspiring technical discussions.

Finally, I would like to thank my parents, who have always put their deepest trust in me. They encouraged me to study abroad for a Ph.D. degree and it turns out to be the best decision I ever made. Their selfless support and unconditional love make it possible for me to see beyond the horizons. I would also like to thank my wife, Sharon, for her continuous support. The past four years together at Texas A&M University will become my most cherished memories. Thanks for always being there for me and giving me a purpose to fight for.

#### CONTRIBUTORS AND FUNDING SOURCES

## Contributors

This work was supported by a dissertation committee consisting of Professor Peng Li, Professor Weiping Shi and Professor Prasad Enjeti of the Department of Electrical and Computer Engineering and Professor Duncan Walker of the Department of Computer Science and Engineering.

All work conducted for the dissertation was completed by the student independently.

## **Funding Sources**

This work was made possible in part by Semiconductor Research Corporation (SRC) through Texas Analog Center of Excellence at the University of Texas at Dallas under Grant Number 1836.115.

Its contents are solely the responsibility of the authors and do not necessarily represent the official views of the Semiconductor Research Corporation.

# TABLE OF CONTENTS

| AE                                                          | BSTR. | ACT                                                                     | ii  |  |

|-------------------------------------------------------------|-------|-------------------------------------------------------------------------|-----|--|

| DE                                                          | EDICA | ATION                                                                   | iv  |  |

| AC                                                          | CKNO  | OWLEDGMENTS                                                             | v   |  |

| CC                                                          | ONTR  | IBUTORS AND FUNDING SOURCES                                             | vi  |  |

| TA                                                          | BLE   | OF CONTENTS                                                             | vii |  |

| LI                                                          | ST OF | F FIGURES                                                               | x   |  |

| LIS                                                         | ST OF | F TABLES x                                                              | iv  |  |

| 1.                                                          | INTI  | RODUCTION AND LITERATURE REVIEW                                         | 1   |  |

|                                                             | 1.1   | Efficient Simulation of DC-DC converters                                | 3   |  |

|                                                             | 1.2   | Multi-harmonic Modeling of DC-DC converter                              | 4   |  |

|                                                             | 1.3   | Small Signal Modeling of DC-DC Converters                               | 6   |  |

|                                                             | 1.4   | Efficient Analysis of Power Distribution Networks                       | 7   |  |

|                                                             | 1.5   | Organization of Dissertation                                            | 9   |  |

| 2. ROBUST AND EFFICIENT TRANSISTOR-LEVEL ENVELOPE-FOLLOWING |       |                                                                         |     |  |

|                                                             | ANA   | ALYSIS OF DC-DC CONVERTERS 1                                            | 10  |  |

|                                                             | 0.1   |                                                                         | 1 1 |  |

|                                                             | 2.1   | 0                                                                       | 11  |  |

|                                                             | 2.2   | Time-delayed Phasing Tracking for Circuits with Variable Switching Fre- | 13  |  |

|                                                             |       | 1                                                                       | 13  |  |

|                                                             |       | 8 - 1                                                                   | 15  |  |

|                                                             |       | $\mathcal{O}$                                                           | 18  |  |

|                                                             |       |                                                                         | 20  |  |

|                                                             | 2.3   |                                                                         | 20  |  |

|                                                             | 2.5   | 5 6 6                                                                   | 22  |  |

|                                                             |       | • •                                                                     | 23  |  |

|                                                             |       | 5                                                                       | 23  |  |

|                                                             | 2.4   |                                                                         | 26  |  |

|                                                             |       | 1                                                                       |     |  |

|    |     | 2.4.1 Dynamic prediction scheme                                       | 27 |

|----|-----|-----------------------------------------------------------------------|----|

|    |     | 2.4.2 Automatic node selection for convergence check                  | 29 |

|    |     | 2.4.3 Adaptive envelope step selection by LTE                         | 31 |

|    | 2.5 | Simulation Results                                                    | 32 |

|    |     | 2.5.1 A three-stage ring oscillator                                   | 33 |

|    |     | 2.5.2 A PWM controlled DC-DC converter                                | 35 |

|    |     | 2.5.3 A PFM DC-DC converter                                           | 38 |

|    |     | 2.5.4 A PSM DC-DC converter                                           | 41 |

|    | 2.6 | Summary                                                               | 43 |

| 3. | MU  | LTI-HARMONIC LARGE-SIGNAL NONLINEAR MODELING OF LOW-                  |    |

|    | POV | VER PWM DC-DC CONVERTERS                                              | 45 |

|    | 3.1 | Generalized Switch Model with Device Non-idealities                   | 45 |

|    |     | 3.1.1 Equivalent switch model based on switching functions            | 46 |

|    |     | 3.1.2 Non-ideal device modeling and the complete equivalent converter | 40 |

|    | 2.2 | model                                                                 | 49 |

|    | 3.2 | Efficient Multi-harmonic Modeling of the Switch Cell                  | 50 |

|    |     | 3.2.1 Multi-harmonic model of switch cell                             | 51 |

|    | 2.2 | 3.2.2 Multi-harmonic model of the DC-DC converter                     | 55 |

|    | 3.3 | System Decoupling                                                     | 55 |

|    | 3.4 | Experimental Results                                                  | 58 |

|    |     | 3.4.1 Boost converter open-loop simulation                            | 60 |

|    | 25  | 3.4.2 Buck converter open-loop simulation                             | 61 |

|    | 3.5 | Summary                                                               | 63 |

| 4. |     | LTI-HARMONIC SMALL-SIGNAL MODELING OF LOW POWER PWM                   |    |

|    | DC- | DC CONVERTERS                                                         | 64 |

|    | 4.1 | Multi-Harmonic Average Model                                          | 65 |

|    | 4.2 | Small-Signal State-Space Model                                        | 67 |

|    | 4.3 | Small-signal AC model                                                 | 71 |

|    |     | 4.3.1 Frequency-domain small-signal model                             | 71 |

|    |     | 4.3.2 Parametric dependencies of high-frequency behavior              | 72 |

|    | 4.4 | Experimental Results                                                  | 74 |

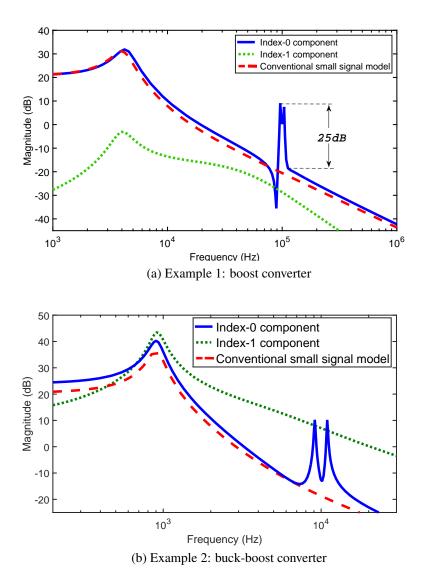

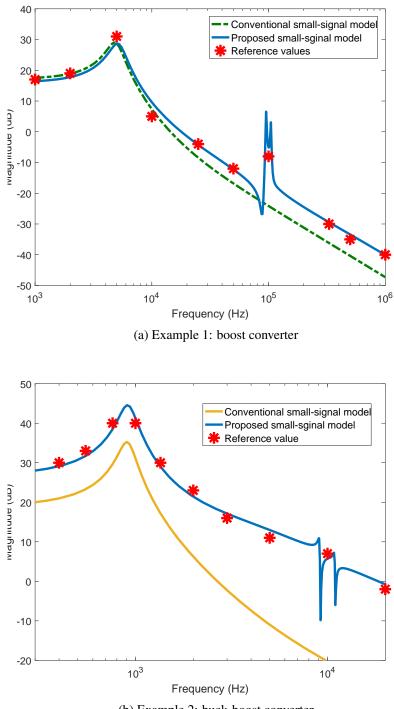

|    |     | 4.4.1 Analysis of the Frequency-Domain Responses                      | 78 |

|    |     | 4.4.2 Stability analysis and closed-loop design                       | 79 |

|    | 4.5 | Summary                                                               | 81 |

| 5. | CON | VERGENCE-BOOSTED GRAPH PARTITIONING USING MAXIMUM                     |    |

|    | SPA | NNING TREES FOR POWER DISTRIBUTION NETWORKS                           | 83 |

|    | 5.1 | Background                                                            | 84 |

|    |     | 5.1.1 Power gird analysis                                             | 84 |

|    |     |                                                                       |    |

|    |       | 5.1.2  | Precondi  | tioned Iterative Solvers                 | 85  |

|----|-------|--------|-----------|------------------------------------------|-----|

|    |       |        | 5.1.2.1   | Block-Jacobi preconditioner              | 86  |

|    |       |        | 5.1.2.2   | Support graph preconditioner             | 87  |

|    | 5.2   | MST-g  |           | conditioner                              |     |

|    |       | 5.2.1  | Minimur   | n-cut partition of maximum spanning tree | 89  |

|    |       | 5.2.2  |           | m flow                                   |     |

|    | 5.3   | Experi | mental Re | sults                                    | 91  |

|    |       |        |           | of results                               |     |

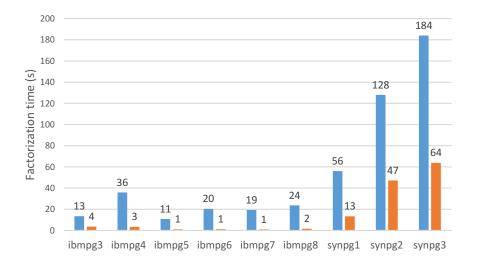

|    |       |        | -         | Efficient factorization                  |     |

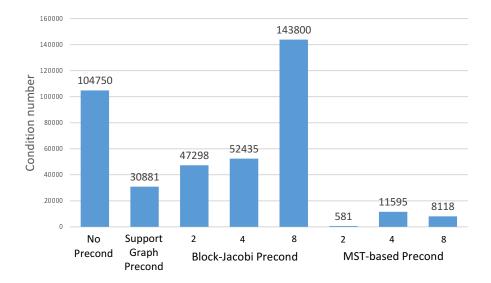

|    |       |        | 5.3.1.2   | Accelerated convergence                  | 93  |

|    |       | 5.3.2  | Compari   | son with direct solver                   | 96  |

|    | 5.4   |        |           |                                          |     |

| 6. | CON   | ICLUSI | ON        |                                          | 99  |

| RF | EFERI | ENCES  |           |                                          | 101 |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                                      |      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | A power delivery system consists of an external power source, a DC-DC converter and power distribution networks (PDN)                                                                                                                                                                                                                |      |

| 1.2    | Power Supply trends.                                                                                                                                                                                                                                                                                                                 | 3    |

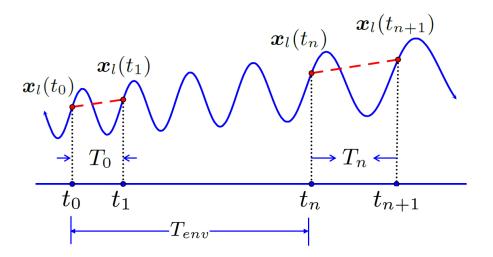

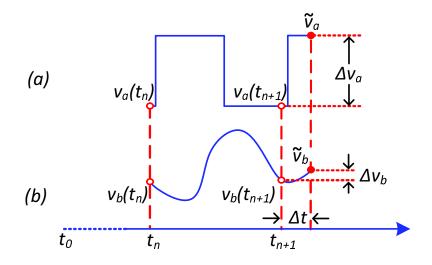

| 2.1    | Basic envelope following method. $t_0, t_1, t_n$ and $t_{n+1}$ are four time points at equal phase and satisfy both $t_1 = t_0 + T_0$ and $t_{n+1} = t_n + T_n$ .                                                                                                                                                                    | . 12 |

| 2.2    | Three typical voltage waveforms in a DC-DC converter: (a) external tri-<br>angular signal, (b) typical internal signal driving power switches, and (c)<br>typical output response with both frequency and amplitude modulation.<br>Specific level crossing times may be used to define equal phase conditions<br>(red dashed lines). | . 14 |

| 2.3    | Slope function and equal-phase points.                                                                                                                                                                                                                                                                                               | . 16 |

| 2.4    | Equal-phase points defined by equal slope function value are shown in the dashed lines.                                                                                                                                                                                                                                              | . 17 |

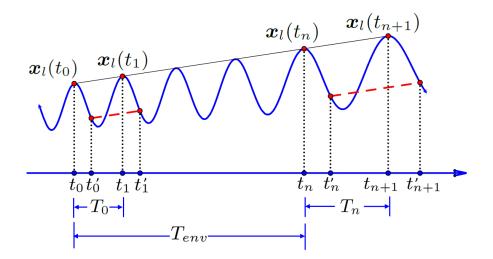

| 2.5    | Time delayed phase tracking method.                                                                                                                                                                                                                                                                                                  | . 20 |

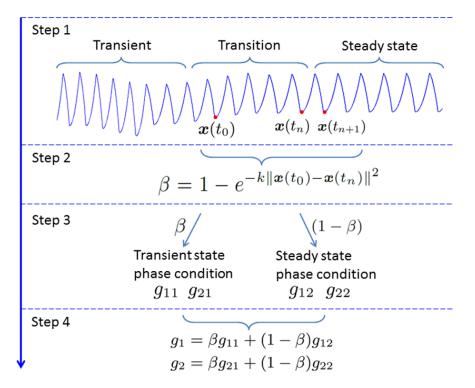

| 2.6    | The unifying phase condition. Steps 1 and 2 illustrate the dependency of the continuous mode tracking parameter $\beta$ on current circuit state. Steps 3 and 4 weight phase conditions according to $\beta$ to define the unifying phase conditions.                                                                                | . 25 |

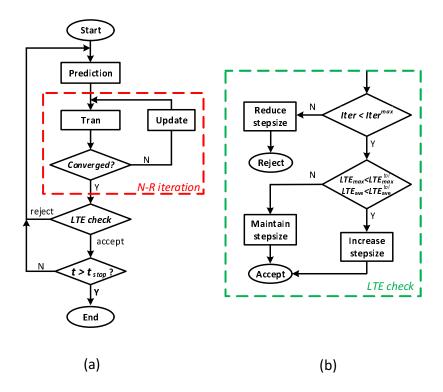

| 2.7    | The simulation flow of proposed envelop following algorithm (a) and the flow of adaptive envelope step selection (b)                                                                                                                                                                                                                 | . 27 |

| 2.8    | The transient analysis waveforms of one iteration of an envelope following step.                                                                                                                                                                                                                                                     | . 30 |

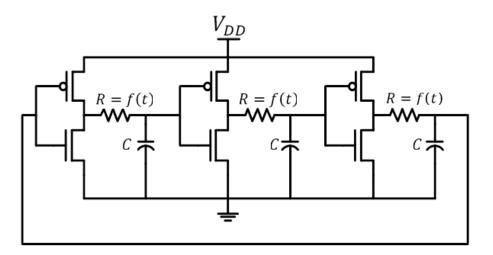

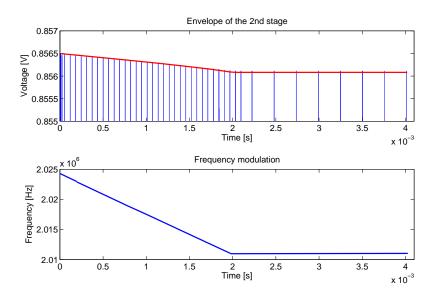

| 2.9    | A three-stage ring oscillator with the value of R controlled by a function of time $f(t)$ .                                                                                                                                                                                                                                          | . 33 |

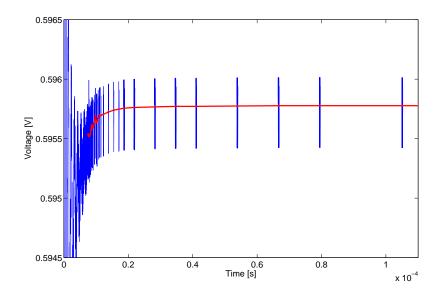

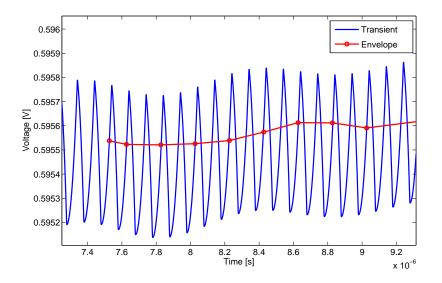

| 2.10 | The envelope of the second stage output voltage of the ring oscillator (top) and its frequency variation (bottom) simulated by the proposed EF method. In the top figure, the red line is the envelope while the blue lines are the transient responses obtained in each cycle of envelope following | 34 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

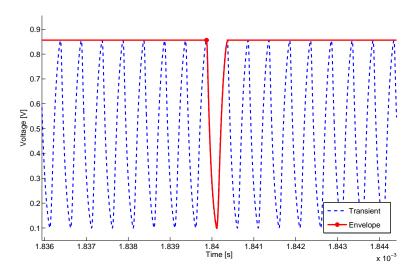

| 2.11 | Comparison between the proposed EF analysis (red solid line) and tran-<br>sient analysis (blue dashed line) of the ring oscillator.                                                                                                                                                                  | 34 |

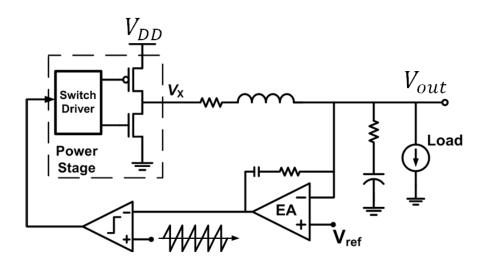

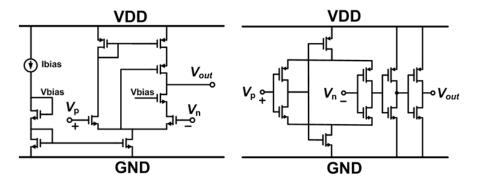

| 2.12 | A PWM controlled DC-DC converter.                                                                                                                                                                                                                                                                    | 35 |

| 2.13 | The error amplifier (left) and comparator (right) of the PWM controlled DC-DC converter.                                                                                                                                                                                                             | 36 |

| 2.14 | Simulation of the PWM DC-DC converter using the proposed EF method.<br>The red line is the envelope of the output voltage while the blue lines are<br>the transient responses obtained in each cycle of envelope following                                                                           | 37 |

| 2.15 | Detailed comparison of envelope following results (red) and transient sim-<br>ulation results (blue) of the PWM DC-DC converter.                                                                                                                                                                     | 37 |

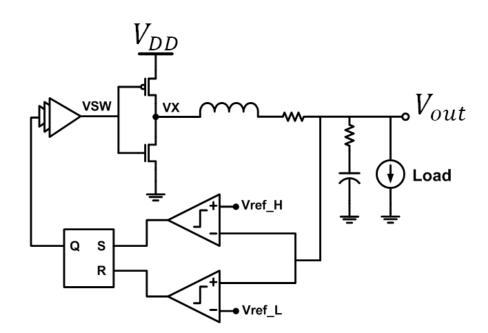

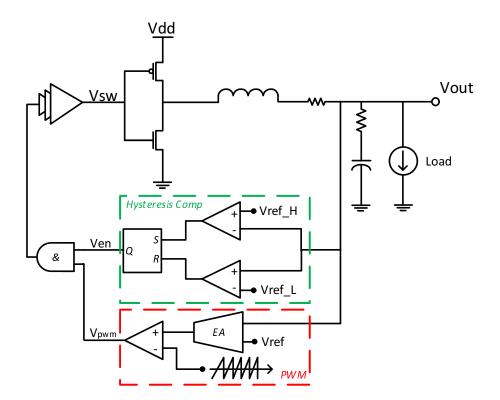

| 2.16 | A hysteretic/PFM DC-DC converter                                                                                                                                                                                                                                                                     | 38 |

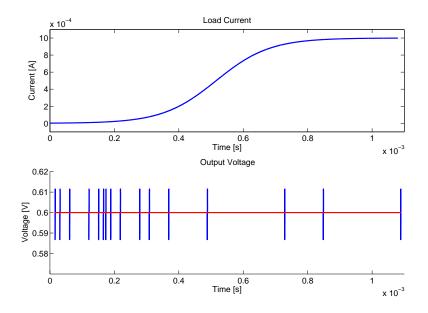

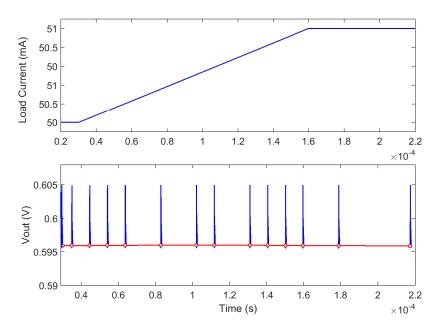

| 2.17 | Load current waveform (top) and the envelope of the hysteretic converter<br>output node response simulated by our EF method (bottom). In the bottom<br>figure the red line is the envelope while the blue lines are the transient<br>responses obtained in each cycle of envelope following          | 39 |

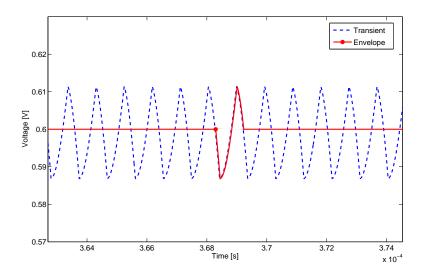

| 2.18 | Detailed comparison of the proposed EF method (red solid line) with the transient analysis (blue dashed line) for the PFM/hysteretic converter                                                                                                                                                       | 40 |

| 2.19 | A PSM DC-DC converter.                                                                                                                                                                                                                                                                               | 41 |

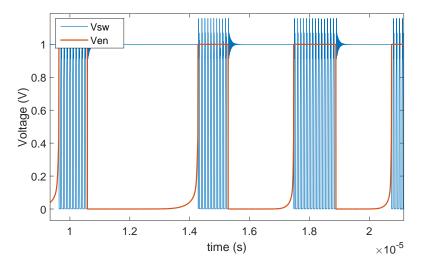

| 2.20 | The switching signal $V_{sw}$ and the enabling signal $V_{en}$                                                                                                                                                                                                                                       | 42 |

| 2.21 | Linearly increasing load current (top) and the output node voltage response<br>simulated by the proposed EF method (bottom). In the bottom figure the<br>red line is the envelope while the blue lines are the transient responses<br>obtained in each step of envelope following.                   | 43 |

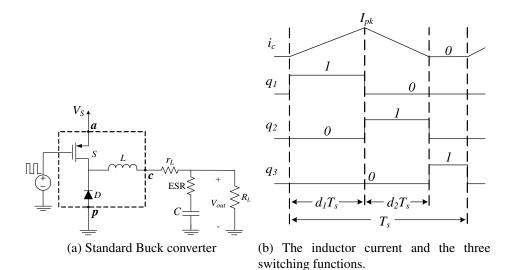

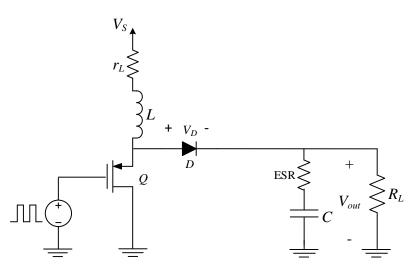

| 3.1  | Standard Buck PWM DC-DC converter                                                                                                                                                                                                                                                                    | 46 |

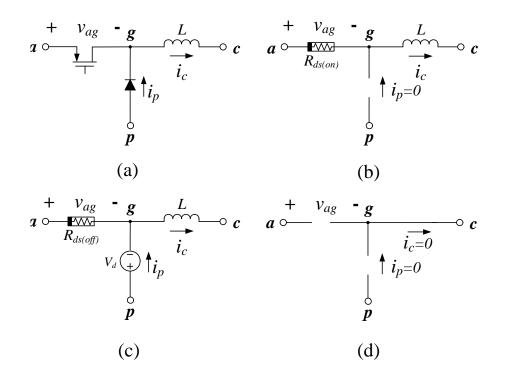

| 3.2  | The three-terminal switch cell(a) and its equivalent circuits in three opera-<br>tion intervals (b)(c)(d).                                                                                                                                                                                           | 47 |

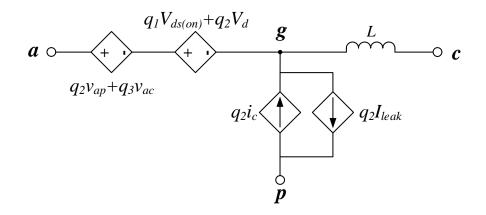

| 3.3  | The equivalent model of the switch cell with non-ideal device characteristics.                                                                                                                                                                                                                       | 48 |

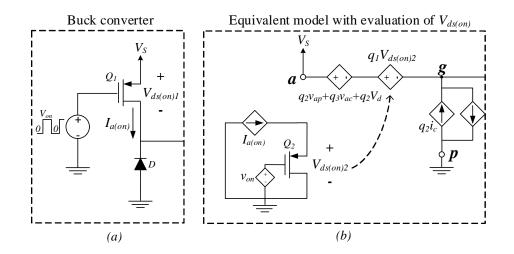

| 3.4  | A buck converter operating at the first interval(a) and its equivalent model with an additional circuit to evaluate the voltage drop $V_{ds(on)}$ using an accurate device model(b).                                                            | 49 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

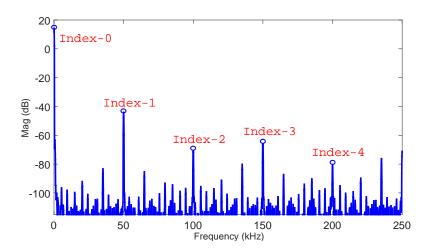

| 3.5  | The FFT spectrum of the output voltage of a boost converter operating in the steady state                                                                                                                                                       | 52 |

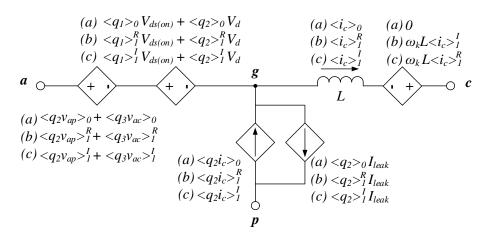

| 3.6  | The multi-harmonic model of the three-terminal the switch cell including<br>(a) index-0 average model, (b) the real part of index-1 average model and<br>(c) the imaginary part of index-1 average model                                        | 54 |

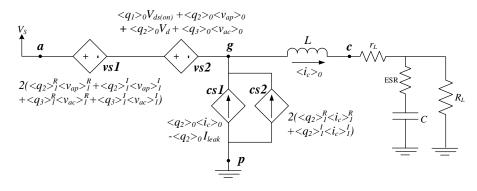

| 3.7  | The index-0 average model of the buck converter. Controlled sources $vs1$ and $cs2$ depend on the index-1 average model and will be completely removed in the decoupled index-0 average model.                                                  | 56 |

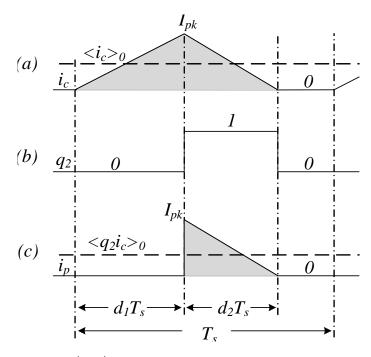

| 3.8  | Illustration of $\langle q_2 i_c \rangle_0$ calculation: (a) inductor current $i_c$ , (b) switch function $q_2$ , and (c) product term $q_2 i_c$ . The 0-index average can be calculated by dividing the shaded area by the length of interval. | 57 |

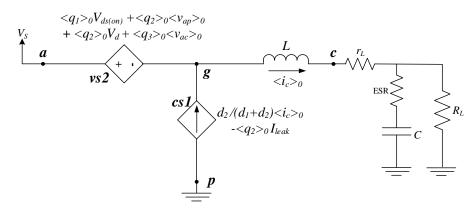

| 3.9  | The decoupled index-0 average model of the buck converter                                                                                                                                                                                       | 59 |

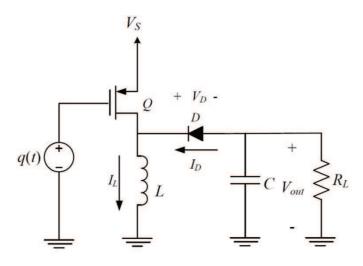

| 3.10 | A standard boost converter with $V_s = 2V$ , $L = 300\mu H$ , $C = 1\mu F$ and $R_L = 50\Omega$                                                                                                                                                 | 60 |

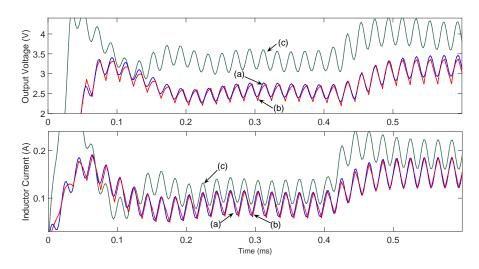

| 3.11 | Boost converter open-loop simulation with varying duty ratio using our proposed model(a), transistor-level circuit(b), and the in-place circuit averaging technique(c).                                                                         | 61 |

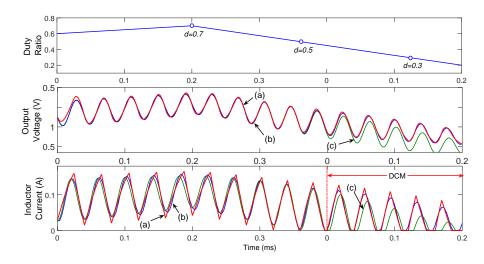

| 3.12 | Buck converter open loop simulation of the transistor-level circuit(a), our proposed model(b), and the modified multi-frequency average model(c)                                                                                                | 62 |

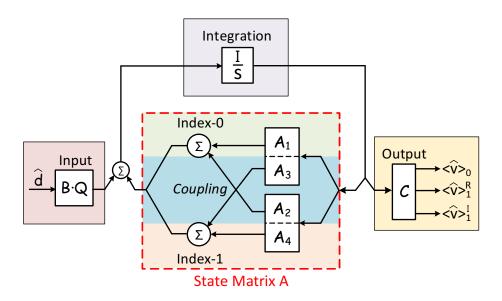

| 4.1  | The state space of the multi-harmonic small-signal model and the interac-<br>tions between its subsystems                                                                                                                                       | 68 |

| 4.2  | Illustration of the linear time-variant (LTV) system with the frequency-<br>shift effect                                                                                                                                                        | 72 |

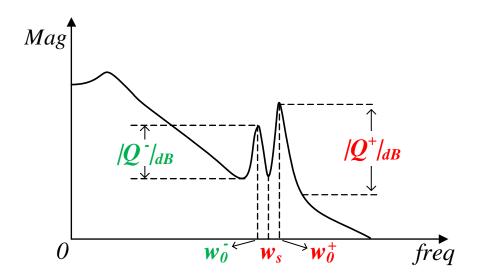

| 4.3  | The effect of $Q$ and $\omega_0$ on a boost converter frequency response                                                                                                                                                                        | 74 |

| 4.4  | The Buck-Boost Converter                                                                                                                                                                                                                        | 75 |

| 4.5  | The control-to-output transfer functions of the DC-DC converters modeled<br>by the proposed small-signal model(index-0 and index-1) and the conven-<br>tional small-signal model.                                                               | 76 |

| 4.6 | Comparison of our proposed model, traditional small signal model and reference values                                                                                                          | 77 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.7 | Comparison of the transient responses of the closed-loop systems designed<br>by the conventional small-signal model and the proposed small-signal model.                                       | 80 |

| 5.1 | An example of building a block-Jacobi preconditioner from a matrix A based on 3-way partitioning                                                                                               | 86 |

| 5.2 | An example of building a support graph preconditioner from a matrix A                                                                                                                          | 87 |

| 5.3 | Comparison between partition strategies of (a) the block-Jacobi precondi-<br>tioner and (b) the MST-guided preconditioner. The thick lines represent<br>the maximum spanning tree of the graph | 89 |

| 5.4 | DC simulation runtime comparison between block-Jacobi preconditioner,<br>support graph preconditioner and the proposed MST-guided preconditioner.<br>92                                        |    |

| 5.5 | Factorization time of support-graph preconditioner (left column) and par-<br>allel MST-guided preconditioner (right column).                                                                   | 93 |

| 5.6 | Condition numbers of a benchmark using different preconditioners. Num-<br>bers above block-Jacobi and MST-guided preconditioner indicate the num-<br>ber of partitions.                        | 95 |

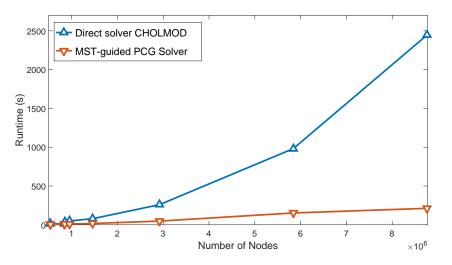

| 5.7 | The runtime comparison of direct solver CHOLMOD and the MST-guided preconditioned conjugated gradient (PCG) Solver                                                                             | 96 |

# LIST OF TABLES

| TABLE      | J                                                                                                                                                                                                                                                                                                                                                                                                    | Page     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | Simulation Results for DC-DC converters                                                                                                                                                                                                                                                                                                                                                              | 44       |

| 3.1        | Errors and speedups of the proposed model                                                                                                                                                                                                                                                                                                                                                            | 63       |

| 4.1<br>4.2 | Circuit parameters<br>Lead compensator designs based on the conventional small-signal model<br>and the proposed small-signal model                                                                                                                                                                                                                                                                   | 75<br>80 |

| 5.1        | Comparison of iteration numbers between the support graph precondi-<br>tioner (SG), block-Jacobi preconditioner (Block) and MST-guided pre-<br>conditioner (MST). $Rd_{Block}$ and $Rd_{SG}$ are the reduction rate of iteration<br>numbers of MST-guided method compared to the block-Jacobi and sup-<br>port graph method, respectively. '-' indicates converge failure within 5000<br>iterations. | 94       |

| 5.2        | Summary of DC simulation runtimes of direct solver and our proposed solver. #Node: the number of nodes. #Dev: the number of devices. Fact: Cholesky decomposition runtime. Solve: solving runtime. Total: total runtime. Iter: number of iterations to convergence. Part: number of partitions. Error: the average error of node voltages in V. All the runtimes are in seconds.                     | 98       |

#### 1. INTRODUCTION AND LITERATURE REVIEW

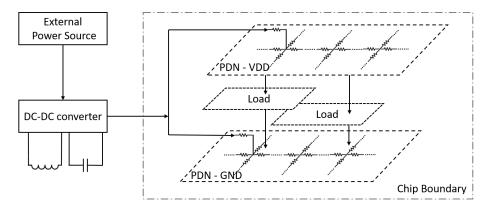

Power delivery has become one of the most important aspects of today's integrated circuit (IC) design. As shown in Fig. 1.1, there are two major components that process and deliver the power from an external power source to the individual functional circuit on the chip. The first component is the DC-DC converters, which step up/down the external power supply voltage to desired voltage levels for different functional circuits. The second component is the power distribution networks (PDN), which are large circuit networks that deliver power to each transistor. Both components are critical in delivering stable and robust voltages to functional circuits and may lead to catastrophic consequences when either component is designed incorrectly.

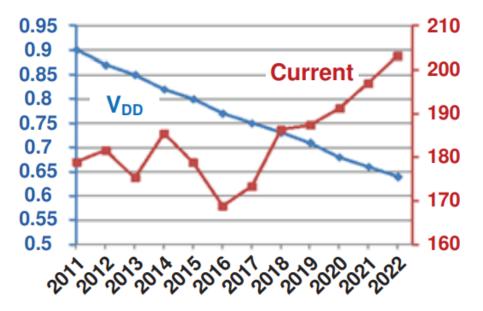

Nowadays, power delivery design circuit is becoming more and more challenging. As shown by International Technology Roadmap for Semiconductors (ITRS) in Fig. 1.2, two significant trends in power supply are observed. First of all, as the supply voltage keeps scaling down to reduce power consumption, the functionalities of the on-chip circuits are more vulnerable to supply voltage noise and IR drops on power distribution networks. Second, with more functional circuits being integrated into the chip, the load current continues to increase, which causes the DC-DC converter being more susceptive to output voltage drop in fast load transient and heavy load conditions. Overall, the situations demand better power delivery design methods that provide efficient and accurate analysis of DC-DC converters and power distribution networks.

While it is important to efficiently analyze, simulate and model DC-DC converters and power distribution networks, finding the proper methods is proved to be very challenging [2, 3]. Analyzing both circuits requires carefully designed algorithms to properly extract desired information from a large amount of data in an efficient manner. In this dissertation,

Figure 1.1: A power delivery system consists of an external power source, a DC-DC converter and power distribution networks (PDN).

we propose a set of solutions to efficiently analyze DC-DC converters and power distribution networks. At the core of the solutions, the philosophy of tackling the problem is the efficiency and accuracy trade-off. While it is time-consuming and usually not cost-efficient to process all simulation data and obtain exact solutions, it is desirable to neglect redundant information and only extract relevant results about the circuit behavior. For DC-DC converter, we propose to exploit envelope following and circuit averaging techniques to efficiently obtain circuit responses. The envelope following methods achieves efficiency by tracing the slowly varying envelope of the circuit and skipping many fast-changing switching cycles in between [4, 5]. The circuit averaging methods builds averaged behavior models of the periodic circuits and ignore the transient within one cycle. For power distribution networks, instead of using a direct solution like Cholesky factorization, we take a divide-and-conquer approach by partitioning the network and build an iterative solution using the result from each partition [6, 3].

Figure 1.2: Power Supply trends. Reprinted from [1].

### 1.1 Efficient Simulation of DC-DC converters

DC-DC converters, due to their modulation mechanism, demonstrates multi-rate characteristics and leads traditional transient analysis method to severe over-sampling problem [4]. While the analysis has to take extremely small steps to capture the switching activities, it also needs to cover a long period of time due to slow load variations. The amount of data accumulated during the simulation is large and thus the efficiency of the traditional analysis methods degrades.

The time-domain envelope following (EF) method is well suited for the simulation of such circuits with a multi-rate characteristic [2, 4, 5]. The efficiency of envelope following stems from the fact that it efficiently traces the slowly varying envelope of the circuit by skipping many fast-changing switching cycles in between. An EF method is introduced in [2] to simulate open-loop switching power converters with a fixed clock frequency and the general difficulty in simulating closed-loop switching converters is discussed. [5] extends

this method for closed-loop converters and the problem of quasi-algebraic variables is addressed. [7] introduce a method that exploits the parallelism in the envelope-following method and parallelize the Newton update solving part to boost the simulation performance. In [8] quadratic and exponential approximations of the envelope are used in EF simulation. However, only fixed-frequency PWM converters are targeted. To analyze variable-frequency converters, [9] approximates variations of the switching period by assuming that the envelope stepsize is an integer multiple of the last switching period of each EF step, which is not true in general. Another envelope following method for closed-loop converters is proposed in [10] for a specific type of converters with multiple switching intervals with a fixed clock (switching) period. The key limitation of [9] and [10] is that the entire converter is treated simplistically as a linear switched network with each switching interval modeled using a linear state transition function.

In this dissertation, we propose an enhanced envelope following method that efficiently simulates DC-DC converters operating with complex modulation controls, *e.g.*, pulse width modulation (PWM), pulse frequency modulation (PFM) or pulse skipping modulation (PSM). At the core of our new envelope following algorithm is a novel timedelayed phase condition that provides robust tracking of the circuit envelope in the transient phase, under a varying switching frequency. We further develop a mechanism that can smoothly track the transitions between the transient and steady-state phases, thereby providing a unifying solution to the EF simulation of both modes of operation. The proposed method is verified using several DC-DC converters and demonstrated improved efficiency compared with traditional transient analysis.

#### 1.2 Multi-harmonic Modeling of DC-DC converter

While envelope following method reduces the simulation time by only capturing the envelope of the responses and skipping multiple switching cycles, the average modeling techniques achieve efficiency by replacing the circuit with a model that only capture averaged behaviors between cycles the ignores the details in between. In particular, state-space averaging has been a very popular simulation technique of pulse-width modulated (PWM) DC-DC converters. In [11, 12, 13], both large-signal and small-signal state-space average models for DC-DC converters operating in continuous conduction mode (CCM) and Discontinuous Conduction Mode (DCM) are presented. However, without considering non-ideal device characteristics, [12] and [13] are inaccurate in simulating low-power DC-DC converters. Furthermore, the modeling approach of [12] and [13] is circuit-specific, thereby limiting the ability to automate the modeling and simulation process on arbitrary DC-DC converter topologies.

Alternatively, the PWM switch model [14, 15], which is a linearization of the threeterminal switch cell, can be readily applied to a wide range of DC-DC converters. By tracking the circuit operating mode based on averaged circuit states, [16] enhances the basic PWM switch model to support simulation of DC-DC converters operating in both CCM and DCM. However, a major limitation of the PWM switch model is that it neglects the dynamic behavior of DC-DC converters within one cycle and provides no information about the waveform ripples. As suggested in [17], the PWM switch model has an underlying assumption of the small ripple condition, which prevents it from being applied to converters with large ripples. It has been shown that neglecting the ripples of state variables can lead to large discrepancies in the simulation results of converters operating at low frequencies [18].

To address this problem, a lot of work has been done on the generalized averaging techniques [19]. In [18], a multi-frequency averaged model is introduced which conducts frequency selective averaging on the switched state-space models of DC-DC converters. However, this method is based on boost converters and cannot be easily applied to other converter configurations. In [20], a flexible method of in-place averaging that replaces

elements in DC-DC converters with the  $k^{th}$ -index average elements is presented, thereby allowing for the tracking of responses with harmonics up to  $k^{th}$  degree. However, the method in [20] assumes a continuous inductor current with ideal switches. As a result, such a model becomes neither suitable nor accurate enough for low-power DC-DC converter simulations.

To solve the problem, we propose a multi-harmonic averaged modeling method of DC-DC converters that combines the accuracy of enhanced state-space averaging, the flexibility of PWM switch models and the multi-frequency nature of the generalized models. The proposed model, which is based on the switch cell, can be readily applied to various types of DC-DC converters. It approximates the converter response using multiple harmonics up to an arbitrary degree. We demonstrate the efficiency and generality of the proposed method using different DC-DC converters.

## 1.3 Small Signal Modeling of DC-DC Converters

Both envelope following method and averaged modeling method provide paths for efficiently analyzing the large-signal behavior of DC-DC converters. As the complexity of the modern low-power integrated circuits grows exponentially, there is an increasing need for accurate control techniques in designing DC-DC converters [21]. Converter circuit behavior is typically highly nonlinear due to the strong switching activities and the presence of nonlinear devices. The small-signal model, which approximates the behavior of the DC-DC converter by linearizing the nonlinear devices and switches at a certain DC operating point, is widely used by designers to design the control blocks and closed-loop systems, as well as to analyze system stability.

Typically, a small-signal model is obtained by first deriving the averaged model of the DC-DC converter, then injecting perturbations to the averaged model through the control signal/supply voltage, followed by evaluating the sensitivity of the circuit states. For low-

power DC-DC converters, it is critically important to capture the high-frequency circuit responses in stability analysis and closed-loop design. For example, [22] demonstrates significant accuracy improvement in small-signal models by capturing high-order harmonics in DC-DC series resonant converters.

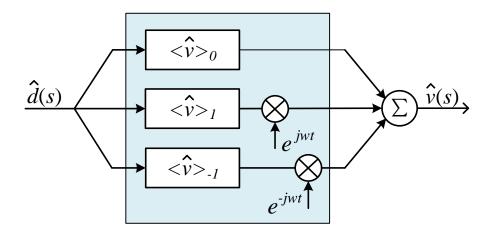

Based on the multi-harmonic large-signal model, we further derive a small-signal model that captures the higher-order effects of the DC-DC converter behavior. The proposed model considers both the DC averages and the higher-order harmonic components as well as the interactions between them, thereby providing a complete small-signal characterization of the converter circuits. The proposed model forms a linear time-variant (LTV) system that can be empirically analyzed for stability. Using several closed-loop design examples, we demonstrate that in practice our model shows significant accuracy improvements in high-frequency responses over existing methods in the literature, thereby providing useful design insights for critical applications such as optimization and design centering.

#### **1.4 Efficient Analysis of Power Distribution Networks**

Power distribution networks is another important component in power delivery design. As shown in Fig. 1.1, the power distribution networks distribute the power drawn from DC-DC converters to individual transistor on each functional circuit. With the complexity of chip design continuing to increase to multi-million or even multi-billion gates, the size of the power distribution networks also increase dramatically and analyzing such circuits are becoming more and more challenging.

The bottleneck of analyzing the power distribution networks lies in efficiently finding the solution to the following linear system problem Ax = b, where A is a large sparse matrix representing the conductance of the circuit, b is a vector of the external current sources and x is a vector of node voltages. There are largely two families of methods to solve the sparse matrix system - the direct method and the iterative method. The direct solution methods [23, 24], which decompose the matrix into upper and lower triangular matrices and then solve the system using forward/backward substitution, have been widely adopted for their robustness and accuracy in circuit simulation. However, these methods have limited application in power grid analysis due to extremely large circuit size and the superlinear time and memory complexity of matrix factorization. Iterative solvers including conjugate gradient (CG) and generalized minimal residual method (GMRES), which update the solution step by step and solve the linear system iteratively, are considered more suitable for power grid analysis due to the favorable memory requirement.

To facilitate fast convergence, preconditioned iterative solvers are introduced and various preconditioning techniques have been studied. The support graph preconditioner, which is presented in [25, 26] as a general preconditioner for symmetric positive-definite (SPD) matrices, is particularly interesting. This technique identifies an underlying subgraph from the matrix, called the support graph, and uses it as the preconditioner of the matrix. For a particular type of support graphs, the maximum spanning tree (MST), it is proved that the preconditioned system has a bound of  $O(n^2)$  on the condition number for any  $n \times n$  SPD matrix. [27] extends the support graph technique to power grid analysis by building a hierarchical maximum spanning tree from the circuit, showing a significant improvement in runtime and memory usage over direct solution methods.

The limitation of the support graph technique is that as a flat preconditioning method, it can only be applied to the full power grid. Recent development in parallel processing has made partition-based preconditioners more favorable. [3] presents a parallel additive Schwarz preconditioner based on the algebraic partition on the circuit conductance matrix. [6] introduces an overlapping partition-based power grid analysis method using spatial locality to provide approximate boundary conditions. Multigrid method [28] is another family of preconditioners, which maps the original problem to a reduced system

using certain geometric properties of the power distribution network (PDN). Both of these methods assume that the PDN is well-structured and the partition is already given. However, for large and complex IC designs with millions of nodes and beyond, the PDN is not always well-structured and finding a reasonable partition is not trivial. [29] presents a complete package including hypergraph partitioning and block Jacobi preconditioning techniques. But as a general-purpose circuit simulator, it lacks the efficiency for power grid analysis.

To address the problems mentioned above, we propose a hybrid method that combines the support graph preconditioner with the block Jacobi preconditioner. The proposed method efficiently finds a partition of the matrix based on the support graph extracted from the circuit. The result is an elegant yet powerful partition-based preconditioner that targets optimizing the numerical convergence property of the partitioned system. We verify the performance of our proposed method on several industrial power grid circuits. Compared with direct method and other partition-based iterative method, our proposed method demonstrates significant improvement in simulation efficiency.

#### **1.5** Organization of Dissertation

The remaining part of this dissertation is organized as follows. In Chapter 2 we elaborate an efficient and robust envelope following algorithm for simulating DC-DC converters. In Chapter 3 a multi-harmonic large-signal averaging modeling technique that takes DC-DC converters' device non-idealities into account is discussed and verified. Chapter 4 extends the multi-harmonic average model to derive small-signal models for DC-DC converters which demonstrate significant accuracy improvements in high-frequency responses over existing methods. In Chapter 5 we present the convergence-boosted graph partitioning method that enables fast and accurate simulation of large power distribution networks. Finally in Chapter 6 we draw conclusions.

# 2. ROBUST AND EFFICIENT TRANSISTOR-LEVEL ENVELOPE-FOLLOWING ANALYSIS OF DC-DC CONVERTERS \*

Highly efficient DC-DC converters are indispensable in today's low power microprocessors, embedded systems, and portable devices [30]. However, the simulation of these circuits is generally very challenging due to the existence of complex dynamics, widely spread time scales (*e.g.* fast switchings with slowly varying amplitudes) and feedback control. These difficulties render the use of the standard transient analysis very inefficient, for instance, by forcing the stepsize to be very small.

In this chapter, we develop a robust and efficient envelope following method to provide a unifying solution to the simulation of DC-DC converters with both transient and steadystate behaviors under a constant or varying switching frequency. Of our particular interest are real-life DC-DC power converters that are operated with complex modulation controls, *e.g.*, pulse width modulation (PWM), pulse frequency modulation (PFM) or pulse skipping modulation (PSM). Even with the standard transient analysis, these circuits are very challenging to simulate due to the co-existence of multi-rate nature, strong nonlinearities, hard switching activities, digital/memory and hysteretic effects and strong feedback control. These characteristics significantly stress the robustness and efficiency requirements of the applied envelope following method and prevent us from using techniques that have been shown to be successful for oscillators such as [4].

At the core of our new envelope following algorithm is a novel time-delayed phase condition that provides robust tracking of the circuit envelope in the transient phase, under a varying switching frequency. We further develop a mechanism that can smoothly track

<sup>\*©2016</sup> IEEE. Reprinted, with permission, from Ya Wang, Peng Li and Suming Lai, "Robust and Efficient Transistor-Level Envelope-Following Analysis of PWM/PFM/PSM DC-DC Converters", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Volume: 35, Issue: 11, Nov. 2016

the transitions between the transient and steady-state phases, thereby providing a unifying solution to the EF simulation of both modes of operation. The implementation of three fast simulation techniques improves the efficiency of the algorithm without compromising the accuracy of the results. The proposed method can be transparently applied to PWM, PFM and PSM converters under a constant or varying switching frequency. We demonstrate the excellent robustness, generality, and efficiency of the proposed technique using several DC-DC converters and oscillator circuits.

#### 2.1 Backgrounds

We review the basic backward-Euler based envelope following method for converters with a constant switching frequency (*e.g.* PWM converters). An electronic circuit can be described using a standard differential-algebraic equation (DAE)

$$\dot{\boldsymbol{q}}(\boldsymbol{x}) + \boldsymbol{f}(\boldsymbol{x}) = \boldsymbol{u}(t), \tag{2.1}$$

where  $x \in \mathbb{R}^N$  is a vector of state variables, q is a nonlinear charge function, f describes the resistive nonlinearities, and u(t) is the excitation to the circuit [31].

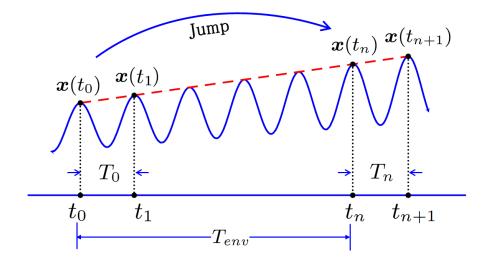

The output voltage of converters such as PWM converters demonstrates fast switching activities with a slowly varying amplitude as a result of load change, a characteristic that is well suited for EF analysis [32]. As shown in Fig. 2.1, denote the constant switching cycle of the circuit at  $t_0$  by  $T_0$  and switching cycle at  $t_n$  by  $T_n$ . The switching cycle is known as a constant, so we have  $T_0 = T_n$ . Denote the state variable at time t by  $\mathbf{x}(t)$ , accordingly the state at time  $t_0$  by  $\mathbf{x}(t_0)$  and that at  $t_n$  by  $\mathbf{x}(t_n)$ . Then define  $t_n$  as the time point that is n cycles after  $t_0$ , namely  $t_n = t_0 + nT_n$ , so that circuit at  $t_n$  has the same phase as at  $t_0$ . By the envelope following method, starting from a given  $\mathbf{x}(t_n)$ , we simulate the circuit for one cycle  $T_n$  to get another state vector of equal phase  $\mathbf{x}(t_{n+1}) = \mathbf{x}(t_n + T_n)$ . As shown in Fig. 2.1, if the amplitude of the circuit response changes slowly enough, a

Figure 2.1: Basic envelope following method.  $t_0, t_1, t_n$  and  $t_{n+1}$  are four time points at equal phase and satisfy both  $t_1 = t_0 + T_0$  and  $t_{n+1} = t_n + T_n$ .

line can be drawn to pass through these three equal-phase points, implying that

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{nT_n} = \frac{\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)}{T_n}.$$

(2.2)

Note that  $x_{n+1}$  can be evaluated as  $x_{n+1} = \phi(x_n, t_n, T_n)$ , where  $\phi$  is the state transition function of the circuit. Now (2) can be written as

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{nT_n} = \frac{\phi(\boldsymbol{x}(t_n), t_n, T_n) - \boldsymbol{x}(t_n)}{T_n}.$$

(2.3)

The only unknown in this equation is  $x_n$ , which can be solved by any nonlinear solution method such as Newton-Raphson Method.

Starting from a known initial state  $\boldsymbol{x}(t_0)$ , one may skip a large number of switching cycles which is  $T_{env} = nT_n$  as in Fig. 2.1, to directly solve for the state  $\boldsymbol{x}(t_n)$ . To move one step forward, the same procedure is re-started by treating the solved  $\boldsymbol{x}(t_n)$  as the

new initial state  $x(t_0)$  and  $x(t_{n+1})$  as  $x(t_1)$ , respectively. However, this basic EF method assumes that the switching cycle does not change, which prevents its application to circuits with dynamically changing switching frequencies like PFM DC-DC converters, which are the focuses of the next section.

# 2.2 Time-delayed Phasing Tracking for Circuits with Variable Switching Frequencies

For the types of circuits of interest here, the varying switching frequency is set by a specific modulation or tuning mechanism. As such, the switching period  $T_n$  is not known *a priori* and must be treated as an unknown variable. Another consequence of the varying frequency is that the skipped time interval between  $t_0$  and  $t_n$  may not be an integer number of cycles, *i.e.*, it is generally true that  $T_{env} \neq nT_n$ . To see the issues involved, we rewrite (2) slightly as

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{T_{env}} = \frac{\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)}{T_n},$$

(2.4)

where the three unknown variables are  $\boldsymbol{x}(t_n)$ ,  $T_n$ , and  $T_{env}$ . Since there are N + 2 unknowns and only N equations (N being the dimensionality of (2.4)), this system is underdetermined. In fact, (4) alone does not guarantee  $\boldsymbol{x}(t_0)$ ,  $\boldsymbol{x}(t_n)$  and  $\boldsymbol{x}(t_{n+1})$  being at the same phase. Varying switching frequencies introduce significant challenges to envelope following. We propose a novel and numerically robust technique for tracking the phase of circuits operating under a changing switching frequency.

#### 2.2.1 Challenges and possible solutions

Several existing EF methods address varying switching or oscillation frequencies. In the oscillator simulation technique of [33],  $T_n$  is predetermined during the integration process by using the notion of Poincaré map. With  $T_n$  computed,  $T_{env}$  is set to be an integer multiple of  $T_n$ . However, the underlying assumption that  $T_n$  remains unchanged

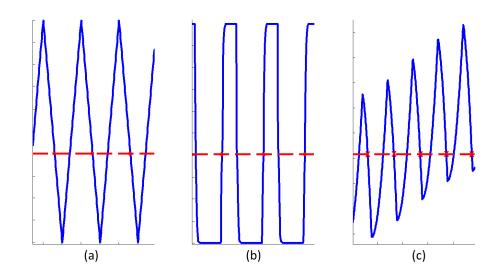

Figure 2.2: Three typical voltage waveforms in a DC-DC converter: (a) external triangular signal, (b) typical internal signal driving power switches, and (c) typical output response with both frequency and amplitude modulation. Specific level crossing times may be used to define equal phase conditions (red dashed lines).

within one envelope step is not true in general and can potentially prevent use of large envelope stepsizes for transient phases of the circuit. In addition, it not always possible to determine  $T_n$  by Poincaré map as suggested in [34]. This situation could be worse for DC-DC converters with digital behaviors and hard switching activities. [4] addresses this problem in oscillator simulation by adding two extra phase conditions at  $t_n$  and  $t_{n+1}$  by constraining the time derivatives of a nodal voltage at these two points. Though proved effective for oscillators, this technique may not be suitable for DC-DC converters due to the presence of digital characteristics and sharp signal transitions, which exacerbate the numerical noise inherent in the numerical evaluation of time derivatives.

Fig. 2.2 shows waveforms of three typical nodes in DC-DC converters. Fig. 2.2(a) shows the external triangular signal that is used in the PWM DC-DC converter of Fig. 2.12. Fig. 2.2(b) shows a typical internal voltage signal that drives the MOS switches in both PWM and PFM DC-DC converters. Fig. 2.2(c) depicts a typical output waveform with

a varying amplitude during the transient phase of a PWM/PFW DC-DC converter. Common properties of these representative signals are that: they all have discontinuous first derivatives; and there are long periods of time in which the first-order derivative of a signal is either very large or approximately constant. These characteristics present practical challenges for the aforementioned EF techniques developed for oscillators.

On the other hand, sharp signal changes in a converter indicate certain controlledswitching events that are taking place in the circuit. These switching activities reliably reflect the onset or ending of a specific mode of operation and can be in principle leveraged to robustly identify equal-phase points that shall be sampled by an EF method. Clearly, the main challenge here is to achieve such in a numerically robust manner. For example, we may purposely choose to monitor one or multiple internal signals with large sharp swings and use the moments at which such signals cross given critical threshold levels to determine the sampling time instants for EF, as shown in Fig. 2.2 by the dashed lines. For instance, the output of the SR-latch of the PFM converter used in the experimental section (Fig. 2.16) can be a good choice as its switching activities reveal the on or off states of the power switches. However, using fixed signal crossing levels is problematic for signals that experience amplitude modulation as in Fig. 2.2(c).

#### 2.2.2 Robust monitoring of phase change

Motivated by the above discussion, we introduce a new equal-phase condition that can capture both frequency and amplitude variations in a converter. To do that, we begin with a definition of slope function  $slp(\cdot, \cdot)$ . Slope function is defined by two points over a given period. As shown by points A and B in Fig. 2.3, the slope function of A and B is

$$slp(A, B) = \frac{x(B) - x(A)}{t(B) - t(A)},$$

(2.5)

$$x$$

$A$   $B$   $C$   $D$   $b$   $t$

Figure 2.3: Slope function and equal-phase points.

where x(A) and x(B) are the amplitudes of points A and B, t(A) and t(B) the time instants of A and B. The slope function is useful in defining equal-phase condition because the slope function of two equal-phase points can be used to find other equal-phase points in the vicinity. For example in Fig. 2.3, assume that A and B are already known as equalphase points, *i.e.* they mark the beginning and ending of one switching cycle. In this case, slp(A, B) is in fact the cycle-slope of the signal during the corresponding switching period. Then, points C and D are also equal-phase points if and only if slp(A, B) - slp(C, D) = 0 is satisfied. Note that this new phase condition is a more general case of the scheme that is based on crossing times of fixed signal threshold levels discussed at the end of Section 2.2.1.

When computing slope function to find points with equal phase, we monitor one or multiple internal circuit nodes (branches), or phase monitoring nodes (or branches). To robustly specify equal-phase points, we assume that phase monitoring nodes are provided by the designer and exposed to the simulation algorithm. In general, these nodes can be chosen rather easily by leveraging a very minimum amount of design knowledge. For instance, for PFM controlled DC-DC converters, a natural choice is the regulated output node that drive internal comparators to alter the switching behavior. Using the idea of

Figure 2.4: Equal-phase points defined by equal slope function value are shown in the dashed lines.

slope function, we now formally define the proposed equal-phase condition. As shown in Fig. 2.4, denote the voltage of a phase monitoring node by  $x_l$ . Four nodes involving the envelope can then be denoted by  $x_l(t_0)$ ,  $x_l(t_1)$ ,  $x_l(t_n)$  and  $x_l(t_{n+1})$ . Under the assumption that the variance of the envelope slope within one step is small, the equal-phase condition can be defined as

$$\frac{\boldsymbol{x}_{l}(t_{n+1}) - \boldsymbol{x}_{l}(t_{n})}{T_{n}} - \frac{\boldsymbol{x}_{l}(t_{1}) - \boldsymbol{x}_{l}(t_{0})}{T_{0}} = 0.$$

(2.6)

Note that results from previous envelope cycle  $x_l(t_0)$  and  $x_l(t_1)$  are already available and are at equal phase. When (6) is satisfied, the value of slope function of  $x_l(t_n)$  and  $x_l(t_{n+1})$ is equal to that of  $x_l(t_0)$  and  $x_l(t_1)$ , meaning that  $x_l(t_n)$  is at the equal phase as  $x_l(t_{n+1})$ .

Since the system needs two phase conditions, we simply apply (6) to another phase monitoring node, denoted by  $x_k$ . Now the new system of envelope following formulation

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{T_{env}} - \frac{\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)}{T_n} = 0$$

$$\frac{\boldsymbol{x}_l(t_{n+1}) - \boldsymbol{x}_l(t_n)}{T_n} - \frac{\boldsymbol{x}_l(t_1) - \boldsymbol{x}_l(t_0)}{T_0} = 0$$

$$\frac{\boldsymbol{x}_k(t_{n+1}) - \boldsymbol{x}_k(t_n)}{T_n} - \frac{\boldsymbol{x}_k(t_1) - \boldsymbol{x}_k(t_0)}{T_0} = 0.$$

(2.7)

Here to distinguish between two different cycle periods, we denote the period at  $t_0$  by  $T_0$ (already known at this time) and one at  $t_n$  by  $T_n$ .

While (7) appears to be robust, a close examination reveals that (7) has a fundamental problem. Note that the  $l^{th}$  row of the first equation and the second equation in (7) have the shared term  $(\boldsymbol{x}_l(t_{n+1}) - \boldsymbol{x}_l(t_n))/T_n$ . Similarly,  $(\boldsymbol{x}_k(t_{n+1}) - \boldsymbol{x}_k(t_n))/T_n$  is shared by the  $k^{th}$  row of the first equation and the third equation. Substituting the last two equal-phase equations into the  $l^{th}$  and  $k^{th}$  rows of the first equation leads to

$$\frac{\boldsymbol{x}_{l}(t_{n}) - \boldsymbol{x}_{l}(t_{0})}{T_{env}} - \frac{\boldsymbol{x}_{l}(t_{1}) - \boldsymbol{x}_{l}(t_{0})}{T_{0}} = 0$$

$$\frac{\boldsymbol{x}_{k}(t_{n}) - \boldsymbol{x}_{k}(t_{0})}{T_{env}} - \frac{\boldsymbol{x}_{k}(t_{1}) - \boldsymbol{x}_{k}(t_{0})}{T_{0}} = 0,$$

(2.8)

which correspond to forward Euler integration of the envelope of  $x_l$  and  $x_k$ , respectively. The explicit forward Euler method is not A-stable and has much degraded stability region. It is rarely used in practice. The formulation of (7) effectively applies the explicit forward Euler type integration to the two phase monitoring nodes, a problem that shall be remedied by an improved equal phase condition introduced next.

### 2.2.3 Time-delayed equal-phase condition

A deep investigation reveals that the above problem stems from the fact that the introduced two phase conditions do not provide fully independent new constraints of the circuit state. In (7), shared terms involving envelope states exist between the  $l^{th}$  row of the first equation and the second equation, and between the  $k^{th}$  row of the first equation and the third equation. Such sharing renders the phase conditions and the backward Euler based EF equation constrain a common set of state variables and may manifest itself in several different ways. If the phase conditions are constructed by forcing the two monitored nodal voltages (or branch currents in general) to cross a predetermined level at equal phase points, a special case of the more general phase conditions adopted in (7), it can be shown that the equal phase equations would be identical to the  $l^{th}$  and  $k^{th}$  rows of the first equation of (7), rendering the full system underdetermined. As discussed already, the more general formulation of (7) immediately reduces the integration of two monitoring nodes to forward Euler while the deeper cause of this phenomenon is due to the sharing.

The key observation behind our solution to the above problem is to note that an equalphase condition needs not to be defined at the beginning nor end of each cycle; it can be forced anywhere within a cycle. This observation leads to a new equal-phase condition, termed *time-delayed phase condition*, resulting in a new EF formulation

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{T_{env}} - \frac{\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)}{T} = 0$$

$$\frac{\boldsymbol{x}_l(t'_{n+1}) - \boldsymbol{x}_l(t'_n)}{T_n} - \frac{\boldsymbol{x}_l(t'_1) - \boldsymbol{x}_l(t'_0)}{T_0} = 0$$

$$\frac{\boldsymbol{x}_k(t'_{n+1}) - \boldsymbol{x}_k(t'_n)}{T_n} - \frac{\boldsymbol{x}_k(t'_1) - \boldsymbol{x}_k(t'_0)}{T_0} = 0,$$

(2.9)

where  $t'_0 = t_0 + \alpha T_0$ ,  $t'_1 = t_1 + \alpha T_0$ ,  $t'_n = t_n + \alpha T_n$  and  $t'_{n+1} = t_{n+1} + \alpha T_n$ .  $\alpha \in (0, 1)$  is a constant factor used to delay the sampling time of phase condition, as illustrated in Fig. 2.5. In (9), the first equation represents the same backward-Euler style equation involving the state variables at a set of four points  $t_0$ ,  $t_1$ ,  $t_n$  and  $t_{n+1}$ . In contrast, the last two equations specify the equal-phase condition at a different set of four points with each delayed by a fraction of the respective cycle time from the corresponding point in the first set. The two equal-phase condition in (9) constrain a different set of state variables from ones that are

Figure 2.5: Time delayed phase tracking method.

in the first equation. The new state variables that are forced to be at an equal phase are the future states of the corresponding variables in the first equation and are related to the latter variables through the nonlinear state transition characteristics of the converter excited by the external input.

#### 2.2.4 Robust numerical solution

Our proposed EF method is described in (9) and the unknown vector that needs to be solved is

$$\boldsymbol{X} = \left[\boldsymbol{x}^{\mathrm{T}}(t_n), T_n, T_{env}\right]^{\mathrm{T}}.$$

(2.10)

To solve the system in (9) by the Newton Raphson method, we need to evaluate the Jacobian matrix properly which involves computation of the sensitivities of each term in (9) with respect to any of the three unknown variables. The evaluation of sensitivities is done by computing the corresponding partial derivatives. Most of them are straightforward to evaluate except for those terms that involve the state transition function, explained as follows. Since in every Newton-Raphson iteration an inner-loop transient run from  $t_n$  to  $t'_{n+1}$  is performed in order to get  $x(t_{n+1})$  and  $x(t'_{n+1})$ , the desired sensitivities terms can be accumulated through every transient step [32]. For convenience of notation, denote  $x(t_n)$  by  $x_0$  (not to be confused with  $x(t_0)$  in Fig. 2.1) and the state at the  $k^{th}$  step of the inner-loop transient simulation by  $x_k$ , (1) can be written as

$$\frac{\boldsymbol{q}(\boldsymbol{x}_k) - \boldsymbol{q}(\boldsymbol{x}_{k-1})}{h_k} + \boldsymbol{f}(\boldsymbol{x}_k) = \boldsymbol{u}(t_k), \qquad (2.11)$$

at the  $k^{th}$  step of the transient simulation, with a stepsize of  $h_k$ . Differentiating (11) with respect to  $x_0$  gives

$$\frac{\partial \boldsymbol{x}_{k}}{\partial \boldsymbol{x}_{0}} = \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}} + \frac{\partial \boldsymbol{f}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}}\right]^{-1} \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k-1})}{\partial \boldsymbol{x}_{k-1}}\frac{\partial \boldsymbol{x}_{k-1}}{\partial \boldsymbol{x}_{0}}\right].$$

(2.12)

Note that  $\frac{1}{h_k} \frac{\partial q(x_k)}{\partial x_k} + \frac{\partial f(x_k)}{\partial x_k}$  is the Jacobian matrix of (1) and is available from the transient simulation. Starting from  $\frac{\partial x_0}{\partial x_0} = I$ , applying (12) repeatedly at every transient step and accumulating the results will give all the desired sensitivity terms with respect to  $x_0$  along the way including  $\frac{\partial x_{n+1}}{\partial x_0}$  in the end. Other sensitivity terms can be found in a similar way. Differentiating (11) with respect to  $T_n$  and  $T_{env}$  gives

$$\frac{\partial \boldsymbol{x}_{k}}{\partial T_{n}} = \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}} + \frac{\partial \boldsymbol{f}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}}\right]^{-1} \\ \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k-1})}{\partial \boldsymbol{x}_{k-1}}\frac{\partial \boldsymbol{x}_{k-1}}{\partial T_{n}} + \frac{\partial \boldsymbol{u}(t_{k})}{\partial T_{n}} + \frac{\boldsymbol{q}(\boldsymbol{x}_{k}) - \boldsymbol{q}(\boldsymbol{x}_{k-1})}{h_{k}T_{n}}\right], \quad (2.13)$$

and

$$\frac{\partial \boldsymbol{x}_{k}}{\partial T_{env}} = \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}} + \frac{\partial \boldsymbol{f}(\boldsymbol{x}_{k})}{\partial \boldsymbol{x}_{k}}\right]^{-1} \left[\frac{1}{h_{k}}\frac{\partial \boldsymbol{q}(\boldsymbol{x}_{k-1})}{\partial \boldsymbol{x}_{k-1}}\frac{\partial \boldsymbol{x}_{k-1}}{\partial T_{env}} + \frac{\partial \boldsymbol{u}(t_{k})}{\partial T_{env}}\right].$$

(2.14)

Starting from  $\frac{\partial x_0}{\partial T_n} = 0$  and  $\frac{\partial x_0}{\partial T_{env}} = 0$ , all sensitivity terms with respect to  $T_n$  and  $T_{env}$  can also be accumulated by applying (13)(14) repeatedly.

## 2.3 Unifying Phase Tracking

An EF method transparently applicable to a variety of converters with PWM, PFM modulation or a combination of thereof, is highly desirable. In fact, a PFM converter may effectively operate under a constant switching frequency in steady state. We consider steady-states of PFM converters to motive the need for a new unifying phase condition.

## 2.3.1 Problems with steady state EF analysis

To see why the formulation of (9) may not be applied to steady state, we examine the following partial derivatives of the two phase conditions. Denote the first phase condition in (9) by  $g_1$  and the second one by  $g_2$ . It can be shown that

$$\frac{\partial g_1}{\partial T_{env}} = \frac{1}{T_n} \left( \frac{\partial \boldsymbol{x}_l(t'_{n+1})}{\partial T_{env}} - \frac{\partial \boldsymbol{x}_l(t'_n)}{\partial T_{env}} \right)$$

(2.15)

$$\frac{\partial g_2}{\partial T_{env}} = \frac{1}{T_n} \left( \frac{\partial \boldsymbol{x}_k(t'_{n+1})}{\partial T_{env}} - \frac{\partial \boldsymbol{x}_k(t'_n)}{\partial T_{env}} \right).$$

(2.16)

When the circuit gets settled in steady state under constant input excitations,  $\frac{\partial u(t_k)}{\partial T_{env}} = 0$ . According to (14), the sensitivity terms of (15) and (16) are both zero, implying that both phase conditions do not constrain unknown  $T_{env}$  and (9) becomes under-determined as a result. The root cause of this pathological situation is that the circuit appears to be autonomous in steady sate with its current/future states only depend on its past states, but not on time.

#### 2.3.2 Phase condition for steady state

As a first step to addressing the above problem, we adopt a new steady state phase condition that involves  $T_{env}$  by noting that cycle T becomes a constant in steady state

$$T_n - T_0 = 0, (2.17)$$

where  $T_0$  is the cycle time at time  $t_0$ . Also in steady state,  $T_{env}$  is an integer multiple of T

$$T_{env} - nT_n = 0, (2.18)$$

where n is the number of cycles skipped in one envelope following step. Replacing two phase conditions in (9) by (17) and (18) yields

$$\frac{\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)}{T_{env}} - \frac{\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)}{T_n} = 0$$

$$T_n - T_0 = 0$$

$$T_{env} - nT_n = 0.$$

(2.19)

The system described in (19) is equivalent to the classic envelope following algorithm for circuits with fixed switching frequencies described in (2.2), which can be used to reliably solve any steady state solutions.

#### **2.3.3** Smooth circuit state tracking and unifying phase condition

Till this point, we have developed two separate EF problem formulations in (9) and (19), respectively for transient and steady states. However, a circuit may transition between the two modes of operation back and forth and such transitions may be smooth and are not known *a priori*. Clearly, a unifying formulation is desirable. Denote the first phase

condition in (9) by  $g_{11}$  and the phase condition described in (17) by  $g_{12}$ , namely

$$g_{11} = \frac{\boldsymbol{x}_l(t'_{n+1}) - \boldsymbol{x}_l(t'_n)}{T_n} - \frac{\boldsymbol{x}_l(t'_1) - \boldsymbol{x}_l(t'_0)}{T_0}$$

(2.20)

$$g_{12} = T_n - T_0. (2.21)$$

Similarly, denote the second phase condition in (9) by  $g_{21}$  and the phase condition described in (18) by  $g_{22}$ , namely

$$g_{21} = \frac{\boldsymbol{x}_k(t'_{n+1}) - \boldsymbol{x}_k(t'_n)}{T_n} - \frac{\boldsymbol{x}_k(t'_1) - \boldsymbol{x}_k(t'_0)}{T_0}$$

(2.22)

$$g_{22} = T_{env} - nT_n. (2.23)$$

The key idea in developing a unifying solution is to define a set of weighted new phase conditions,

$$g_1 = \beta g_{11} + (1 - \beta) g_{12}$$

$$g_2 = \beta g_{21} + (1 - \beta) g_{22}$$

(2.24)

where  $\beta \, \in \, [0,1]$  is a continuous internal parameter that continuously tracks the current circuit mode of operation, as illustrated in Fig. 2.6. Using this new phase conditions, the unifying formulation of the envelope following problem is

$$T_{env}[\boldsymbol{x}(t_{n+1}) - \boldsymbol{x}(t_n)] - T_n[\boldsymbol{x}(t_n) - \boldsymbol{x}(t_0)] = 0$$

$$\beta g_{11} + (1 - \beta)g_{12} = 0$$

$$\beta g_{21} + (1 - \beta)g_{22} = 0.$$

(2.25)

We now discuss the significance and the implementation of the internal parameter  $\beta$ . Since the transitions between transient and steady states may not be abrupt, the goal be-