# A MILLIMETER-WAVE COEXISTENT RFIC RECEIVER ARCHITECTURE IN 0.18- $\mu m$ SiGe BiCMOS FOR RADAR AND COMMUNICATION SYSTEMS

#### A Dissertation

by

#### CHADI DAHER GEHA

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Cam Nguyen

Committee Members, Jose Silva-Martinez

Laszlo Kish Mark Everett

Head of Department, Miroslav Begovic

December 2015

Major Subject: Electrical Engineering

Copyright 2015 Chadi Daher Geha

#### **ABSTRACT**

Innovative circuit architectures and techniques to enhance the performance of several key BiCMOS RFIC building blocks applied in radar and wireless communication systems operating at the millimeter-wave frequencies are addressed in this dissertation. The former encapsulates the development of an advanced, low-cost and miniature millimeter-wave coexistent current mode direct conversion receiver for short-range, high-resolution radar and high data rate communication systems.

A new class of broadband low power consumption active balun-LNA consisting of two common emitters amplifiers mutually coupled thru an AC stacked transformer for power saving and gain boosting. The active balun-LNA exhibits new high linearity technique using a constant gm cell transconductance independent of input-outputs variations based on equal emitters' area ratios. A novel multi-stages active balun-LNA with innovative technique to mitigate amplitude and phase imbalances is proposed. The new multi-stages balun-LNA technique consists of distributed feed-forward averaging recycles correction for amplitude and phase errors and is insensitive to unequal paths parasitic from input to outputs. The distributed averaging recycles correction technique resolves the amplitude and phase errors residuals in a multi-iterative process. The new multi-stages balun-LNA averaging correction technique is frequency independent and can perform amplitude and phase calibrations without relying on passive lumped elements for compensation. The multi-stage balun-LNA exhibits excellent performance from 10 to 50 GHz with amplitude and phase mismatches less than 0.7 dB and 2.86°,

respectively. Furthermore, the new multi-stages balun-LNA operates in current mode and shows high linearity with low power consumption. The unique balun-LNA design can operates well into mm-wave regions and is an integral block of the mm-wave radar and communication systems.

The integration of several RFIC blocks constitutes the broadband millimeter-wave coexistent current mode direct conversion receiver architecture operating from 22-44 GHz. The system and architectural level analysis provide a unique understanding into the receiver characteristics and design trade-offs. The RF front-end is based on the broadband multi-stages active balun-LNA coupled into a fully balanced passive mixer with an all-pass in-phase/quadrature phase generator. The trans-impedance amplifier converts the input signal current into a voltage gain at the outputs. Simultaneously, the high power input signal current is channelized into an anti-aliasing filter with 20 dB rejection for out of band interferers. In addition, the dissertation demonstrates a wide dynamic range system with small die area, cost effective and very low power consumption.

# **DEDICATION**

To my family, Hiyam and Daher Geha, and Rana Nouaime and her family, Rami and Reem Nouaime

For all their love, prayers, and unwavering support

#### **ACKNOWLEDGEMENTS**

This dissertation would have never been possible without the help of many people. First and foremost, I would like to express my deep gratitude to my advisor, Prof. Cam Nguyen, for his guidance, encouragement and constant support throughout my doctoral program at Texas A&M University. I would like to specially thank him for the opportunity to be part of his research group and giving me faith and confidence; hence a comfortableness in doing the research. Academically, I have learned from his courses and our weekly research meetings and technical discussions have consolidated my knowledge into valuable experiences for my professional career. In-life, friendly conversations with him will always be the important guide I need in my whole life. His scholarly technical knowledge has been of paramount inspirations to me for new ideas which significantly improve RFIC circuit and system performances, and for the definite shape of the research in this dissertation. I would like to thank him for kindly letting me have the freedom in researching and discovering new things beside the main topics.

I sincerely would like to thank my committee members, Prof. Jose Silva-Martinez, Prof. Laszlo B. Kish, and Prof. Mark Everett for their guidance, comments and supports, particularly during my preliminary examination. I am also very grateful to Prof. Kai Chang and Prof. Sanchez for all that I learned from their courses on broadband microwave systems and CMOS RFIC design. I would like to thank Prof. Sam Villareal for his support and guidance throughout my TA work for the capstone senior design

class. I also want to thank Ms. Tammy Carda and Ms. Melissa Sheldon for their kind help on all my departmental issues through my Ph.D. study.

I would like to thank my former lab-mates, Dr. Cuong Huynh, Dr. Sanghun Lee, and Dr. Jaeyoung Lee for their useful technical discussions and helps. My thanks also go to my current lab-mates, Yuan Luo, Sunhwan Jang, Youngman Um, Kyoungwoon Kim, Donghyun Lee, Juseok Bae, Meng-Jie Hsiao, Yan Liu, Qianjie Guo, and Fangyu Meng for their technical discussions and their jokes.

My special and deepest appreciations go out to my family members to whom I owe so much. I thank my parents, Hiyam and Daher Geha for their love and endless support, not only for several years of my doctoral program but also for my entire life. I would like to thank my beloved sister and her family, Rana and Joseph Nouaime for their constant encouragement and words of wisdom. Finally, I thank God Almighty for the gifts of heaven, my niece and nephew, Reem and Rami Nouaime. I love you.

# TABLE OF CONTENTS

|                                                               | Page |

|---------------------------------------------------------------|------|

| ABSTRACT                                                      | ii   |

| DEDICATION                                                    | iv   |

| ACKNOWLEDGEMENTS                                              | v    |

| TABLE OF CONTENTS                                             | vii  |

| LIST OF FIGURES                                               | X    |

| LIST OF TABLES                                                | xiv  |

| CHAPTER I INTRODUCTION                                        | 1    |

| <ul> <li>1.1 Background and Motivation</li></ul>              |      |

| 1.2.1 Radar System Overview                                   | 5    |

| 1.2.1.1 Transmitter                                           |      |

| 1.2.1.2 Antenna System                                        |      |

| 1.2.1.3 Receiver                                              |      |

| 1.2.2.1 Radar Interferers and Solutions                       |      |

| 1.2.2.2 Radar Equations                                       |      |

| 1.2.3 Radar Pulse Compression                                 |      |

| 1.2.3.1 Linear Frequency Modulation Pulse Compression         |      |

| 1.2.3.2 Phase-Coded Pulse Compression                         |      |

| 1.2.4 Signal Modulation                                       |      |

| 1.2.4.1 On-Off Key Modulation (OOK)                           |      |

| 1.2.4.2 Pulse Position Modulation (PPM)                       |      |

| 1.2.4.3 Pulse Amplitude Modulation (PAM)                      |      |

| 1.2.4.4 Bi-Phase Modulation (BPM)                             |      |

| 1.3 Transceivers Architecture for Short Range Radar and Radio |      |

| Communications Systems                                        | 19   |

| 1.4 Dissertation Organization                                 |      |

|                                                               |      |

| CHAPTER II SICS COEXISTENT RECEIVER ARCHITECTURE AND          |      |

| SYSTEM SPECIFICATIONS                                         | 23   |

| 2.1 MMW Receivers History                                        | 23 |

|------------------------------------------------------------------|----|

| 2.1.1 Heterodyne Receiver                                        |    |

| 2.1.2 Phased Array Receiver Principles and Architecture          | 24 |

| 2.1.3 Homodyne Receiver                                          | 28 |

| 2.2 SICS Coexistent Receiver Definition                          | 29 |

| 2.3 Coexistent RX for Radar and Radio Terminals                  | 30 |

| 2.4 Signal Conditioning Functions in Low Power Wideband Receiver | 31 |

| 2.5 Low Power Coexistent Receiver Architecture Fundamentals      |    |

| 2.5.1 Low Power ADC at Baseband                                  |    |

| 2.5.2 Merging Variable Gain Amplifier (VGA) into ADC             | 35 |

| 2.5.3 Anti-Aliasing and Anti-Blockers Filters                    |    |

| 2.5.3.1 SRR Filter Specification                                 |    |

| 2.5.3.1.1 SRR Anti-Aliasing Requirements                         |    |

| 2.5.3.1.2 SRR Anti-Blocker Specifications                        |    |

| 2.5.3.2 IEEE 802.16-SC Filter Specifications                     |    |

| 2.5.3.2.1 LMDS Anti-Aliasing Requirements                        |    |

| 2.5.3.2.2 LMDS Anti-Blocker Requirements                         |    |

| 2.6 SICS Feed-forward Anti-Aliasing Filter                       |    |

| 2.7 CRRA Non-idealities and System Specifications                |    |

| 2.7.1 Limits to AM Detection                                     |    |

| 2.7.2 Limits to Cross Modulation                                 |    |

| 2.7.3 Harmonic Distortion                                        |    |

| 2.7.4 Harmonic Downconversion                                    |    |

| 2.8 Receiver Specifications                                      |    |

| 2.8.1 SRR Receiver Specifications                                |    |

| 2.8.2 Mini-UAV SAR Radar Receiver                                |    |

| 2.9 SICS Coexistent Receiver System Architecture                 | 56 |

| CHAPTER III A WIDEBAND LOW POWER CONSUMPTION 22-35               |    |

| GHZ ACTIVE BALUN-LNA                                             | 58 |

| OHZ ACTIVE BALON-LINA                                            | 50 |

| 3.1 Introduction                                                 | 58 |

| 3.2 Proposed Architecture and Circuit Analysis                   |    |

| 3.2.1 Input Matching                                             |    |

| 3.2.2 Linearity                                                  |    |

| 3.2.3 Noise Analysis                                             |    |

| 3.2.4 Stability and Power Efficiency                             |    |

| 3.3 Transformers and Inductors Layouts                           |    |

| 3.4 Active Balun-LNA Perfomance                                  |    |

|                                                                  |    |

| CHAPTER IV A HIGHLY LINEAR MULTI-STAGES ACTIVE                   |    |

| BALUN-LNA WITH DISTRIBUTED FEED-FORWARD AVERAGING                |    |

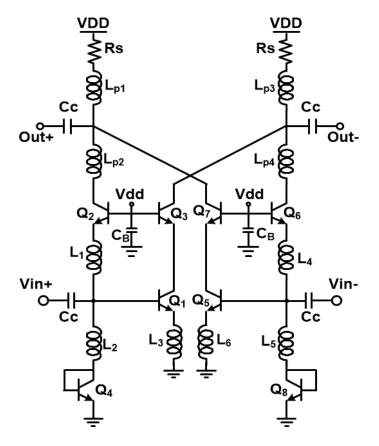

| RECYCLES CORRECTION TECHNIQUE                                    | 84 |

| 4.1 Introduction                                                     | 84  |

|----------------------------------------------------------------------|-----|

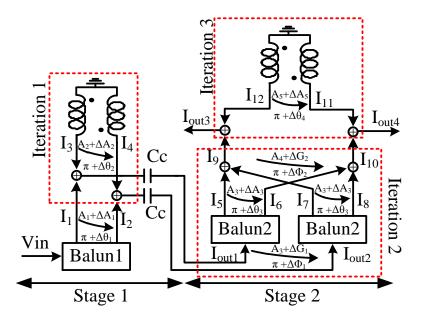

| 4.2 Distributed Feed-Forward Averaging Recycles Correction Technique |     |

| 4.2.1 Main Idea                                                      |     |

| 4.2.2 Active and Passive Devices Mismatches                          | 95  |

| 4.2.3 Linearity                                                      | 98  |

| 4.3 Circuit Implementation                                           | 98  |

| 4.4 Simulations and Measurements                                     | 100 |

| CHAPTER V A 22-44 GHZ MILLIMETER-WAVE COEXISTENT                     |     |

| RECEIVER ARCHITECTURE AND CIRCUITS DESIGN                            | 105 |

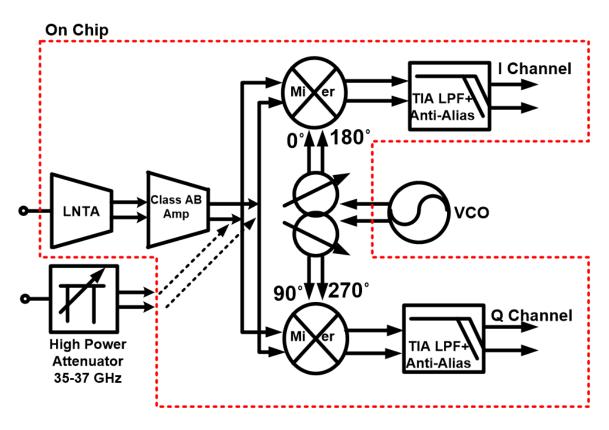

| 5.1 Proposed Receiver Architecture                                   | 105 |

| 5.2 Circuits Implementation                                          |     |

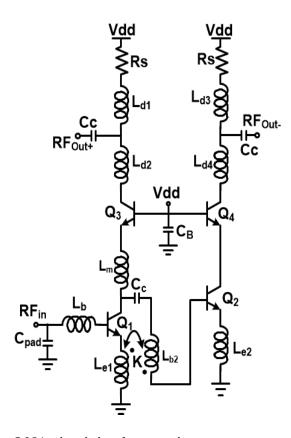

| 5.2.1 Balun-LNA                                                      |     |

| 5.2.2 Class AB Amplifier                                             |     |

| 5.2.3 Passive Mixer and Phase Shifter                                |     |

| 5.2.4 TIA and Anti-Aliasing Filter                                   | 118 |

| 5.3 Simulations and Measurements                                     |     |

| CHAPTER VI SUMMARY AND CONCLUSION                                    | 129 |

| 6.1 Dissertation Summary                                             | 129 |

| REFERENCES                                                           | 132 |

| APPENDIX A                                                           | 144 |

# LIST OF FIGURES

|                                                                                                                                                                  | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1.1 Radar consists of subsystems: a transmitter, an antenna system, and a receiver.                                                                         | 5    |

| Fig. 1.2 RF pulse signal.                                                                                                                                        | 6    |

| Fig. 1.3 Antenna systems can consist of one antenna using (a) circulator, (b) T/R switch, (c) two separate antennas, and (d) antenna array such as phased array. | 8    |

| Fig. 1.4 Conventional radar receiver architecture.                                                                                                               | 9    |

| Fig. 1.5 Conventional pulse radar system architecture [18]                                                                                                       | 10   |

| Fig. 1.6 CW LO leakage at 24.15 GHz [18].                                                                                                                        | 12   |

| Fig. 1.7 Linear frequency modulation pulse compression implementation methods (a) time domain, (b) frequency domain                                              | 16   |

| Fig. 1.8 Phase-coded pulse compression using 13 bits Baker code                                                                                                  | 17   |

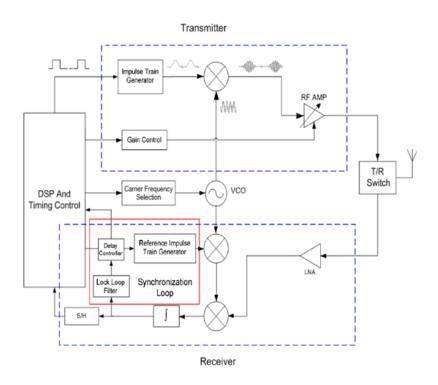

| Fig. 1.9 System architecture for both radar and communication systems [24]                                                                                       | 20   |

| Fig. 2.10 Heterodyne receiver architecture.                                                                                                                      | 24   |

| Fig. 2.11 General concept of phased array system architecture                                                                                                    | 25   |

| Fig. 2.12 Passive RF phased array architecture.                                                                                                                  | 27   |

| Fig. 2.13 Homodyne receiver architecture at mm-wave.                                                                                                             | 28   |

| Fig. 2.14 SRR wideband receiver architecture with front-end signal conditioning blocks.                                                                          | 32   |

| Fig. 2.15 Programmable variable gain amplifier specification for SRR application.                                                                                | 37   |

| Fig. 2.16 SRR anti-blocker filter level diagram.                                                                                                                 | 44   |

| Fig. 2.17 SICS coexistent receiver architecture.                                                                                                                 | 57   |

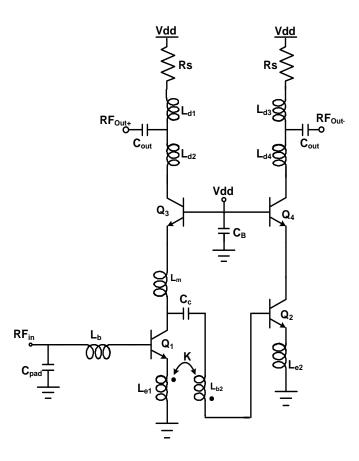

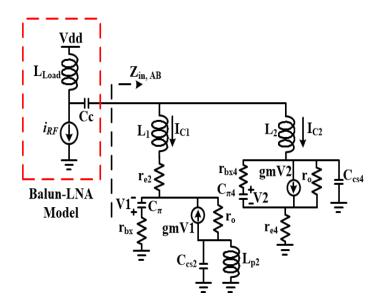

| Fig. 3.18 Proposed Balun-LNA architecture.                                                                                                                       | 60   |

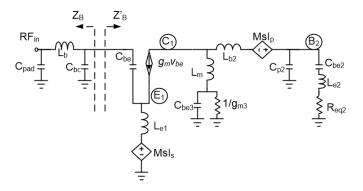

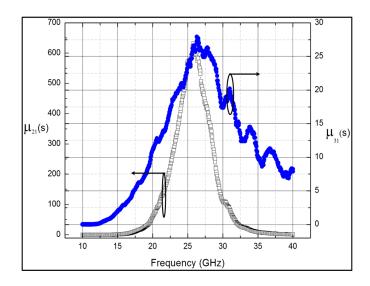

| Fig. 3.19 | Small signal model of the balun-LNA's input impedance. gm is the small signal transconductance of Q1. Req2 is defined as ωTLe2 of Q2. Ip and Is are the primary and secondary currents of the transformer. | 62 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

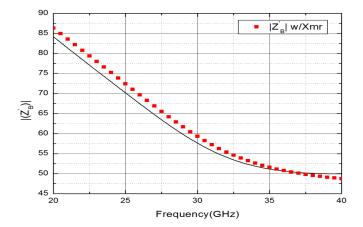

| Fig. 3.20 | Comparison of magnitudes of Z'B with and without transformer                                                                                                                                               | 65 |

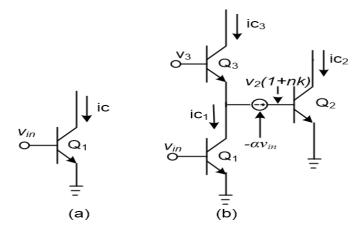

| Fig. 3.21 | Linearity model analysis: (a) Conventional CE stage and (b) Proposed Gm stage.                                                                                                                             | 65 |

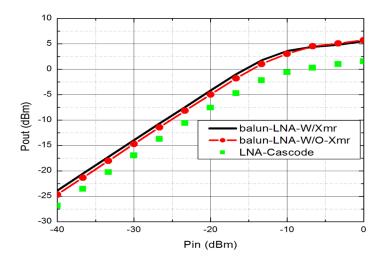

| Fig. 3.22 | Compression curves for (a) Cascode LNA, (b) balun-LNA with transformer, (c) balun-LNA without transformer.                                                                                                 | 69 |

| Fig. 3.23 | Noise sources model of the proposed balun-LNA.                                                                                                                                                             | 70 |

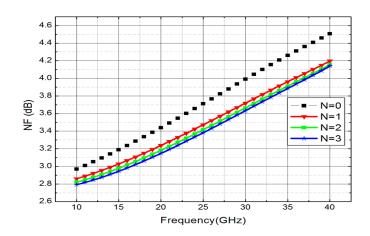

| Fig. 3.24 | NF for the differential output balun-LNA with ideal coupling coefficient; K; and transformer multiple turns n.                                                                                             | 73 |

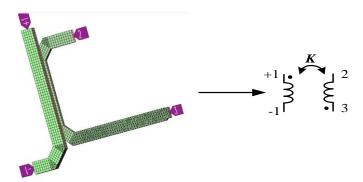

| Fig. 3.25 | Stacked transformer layout structure and its schematic. Port (1,-1): M6; Port (2, 3): M5                                                                                                                   | 75 |

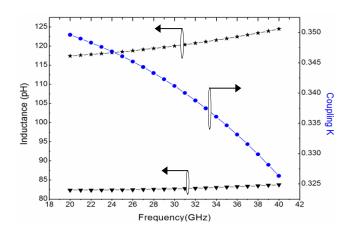

| Fig. 3.26 | Inductance values; Le1, Lb2, and coupling coefficient, K, for stacked transformer using IE3D.                                                                                                              | 77 |

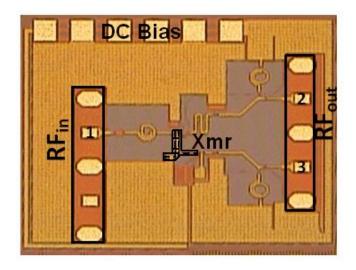

| Fig. 3.27 | Die photograph of the balun-LNA.                                                                                                                                                                           | 78 |

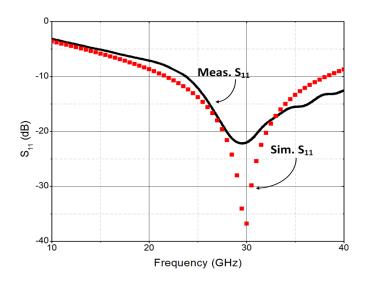

| Fig. 3.28 | Measured and simulated S11 of the proposed balun-LNA                                                                                                                                                       | 80 |

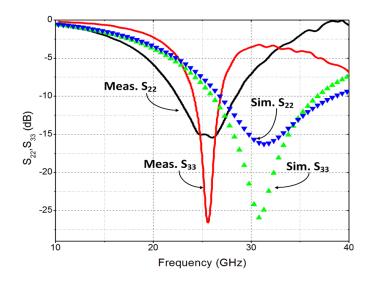

| Fig. 3.29 | Measured and simulated S22 and S33 of the proposed balun-<br>LNA.                                                                                                                                          | 80 |

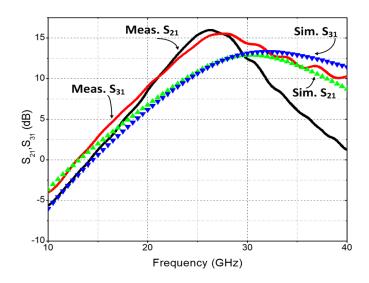

| Fig. 3.30 | Measured and simulated S21 and S31 for the balun-LNA.                                                                                                                                                      | 81 |

| Fig. 3.31 | Stability factor of the proposed balun-LNA.                                                                                                                                                                | 81 |

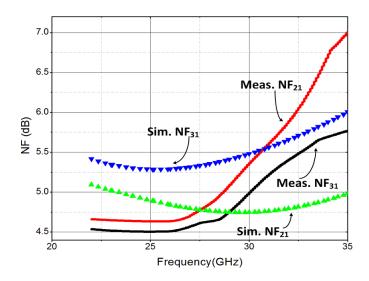

| Fig. 3.32 | Measured and simulated noise figures of the proposed balun-<br>LNA.                                                                                                                                        | 82 |

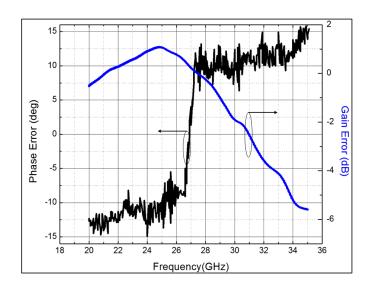

| Fig. 3.33 | Measured gain and phase mismatches.                                                                                                                                                                        | 82 |

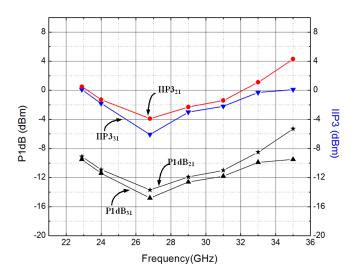

| Fig. 3.34 | Measured P1dB and IIP3 for the proposed balun-LNA                                                                                                                                                          | 83 |

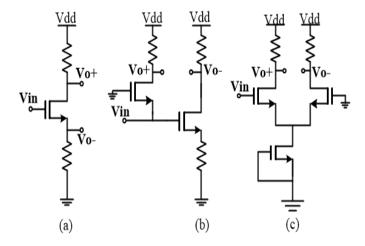

| Fig. 4.35 | Conventional balun-LNA structures.                                                                                                                                                                         | 86 |

| Fig. 4.36 | Proposed balun-LNA architecture with distributed averaging correction technique.                                                                                                                           | 87 |

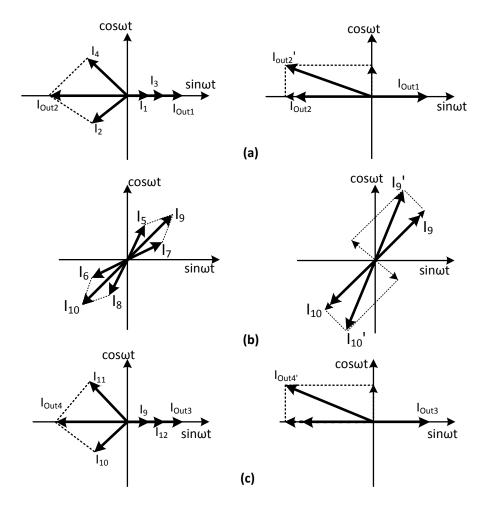

| Fig. 4.37 | Vector magnitude representation of the averaging recycles correction technique (a) output iteration 1 with and without orthogonal terms (b) output iteration 2 with and without orthogonal terms (c) output iteration 3 with and without                        | 02             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

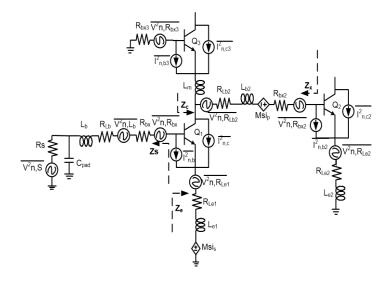

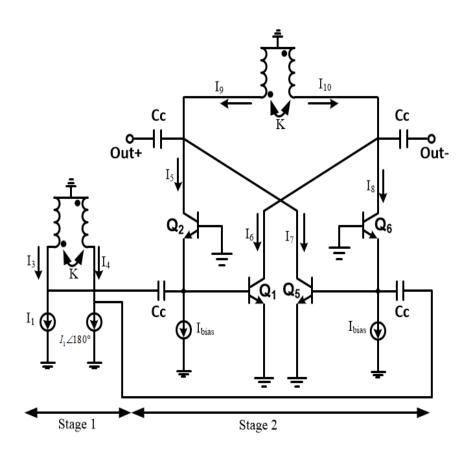

| Fig. 4.38 | Transistor model of the multi-stages balun-LNA.                                                                                                                                                                                                                 |                |

| 11g. 4.36 | Transistor model of the mutit-stages barun-LivA.                                                                                                                                                                                                                | 7 <del>4</del> |

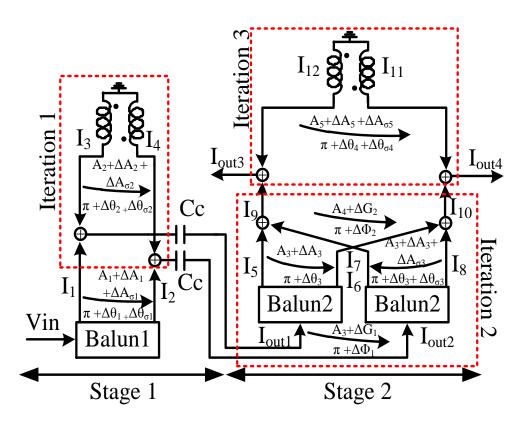

| Fig. 4.39 | Proposed model architecture of the multi-stages balun-LNA including active and passive mismatches parameters                                                                                                                                                    | 96             |

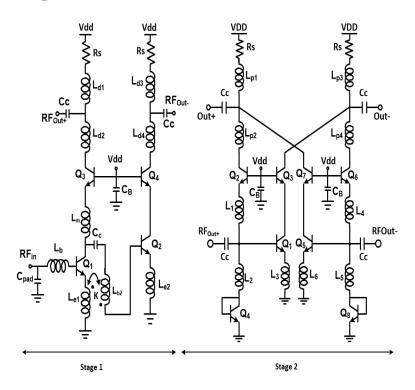

| Fig. 4.40 | Proposed multi-stages balun-LNA circuit implementation                                                                                                                                                                                                          | 98             |

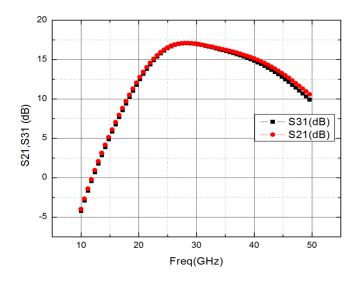

| Fig. 4.41 | S21, and S31 power gains of the proposed multi-stages balun-<br>LNA.                                                                                                                                                                                            | 101            |

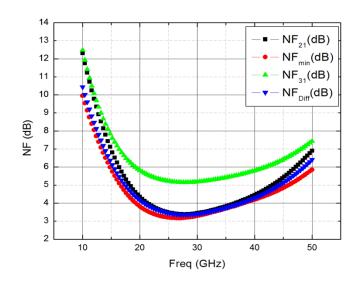

| Fig. 4.42 | Noise figure simulations of the proposed multi-stages balun-<br>LNA.                                                                                                                                                                                            | 102            |

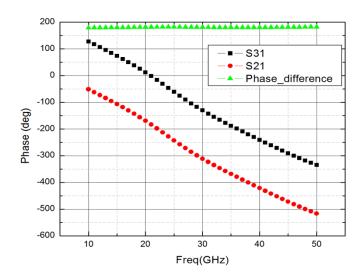

| Fig. 4.43 | Phase balance and phase difference of the proposed multi-stages balun-LNA.                                                                                                                                                                                      | 102            |

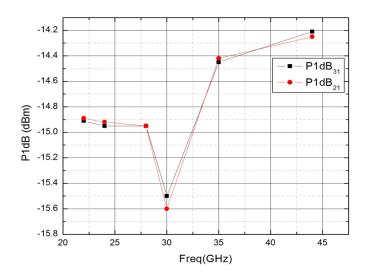

| Fig. 4.44 | Input referred 1 dB gain compression of the proposed multi-<br>stages balun-LNA.                                                                                                                                                                                | 103            |

| Fig. 4.45 | Micrograph die of the proposed multi-stages balun-LNA                                                                                                                                                                                                           | 103            |

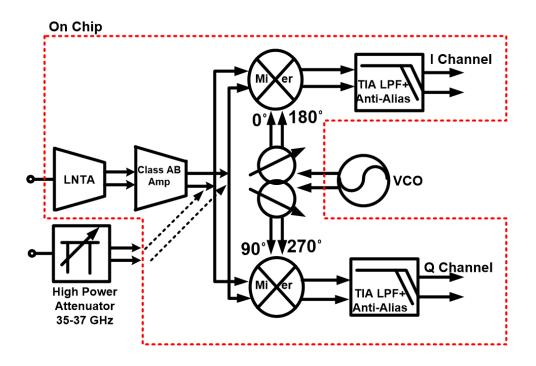

| Fig. 5.46 | Proposed millimeter-wave coexistent receiver architecture.                                                                                                                                                                                                      | 106            |

| Fig. 5.47 | Active balun-LNA circuit implementation.                                                                                                                                                                                                                        | 110            |

| Fig. 5.48 | Class AB Amplifier                                                                                                                                                                                                                                              | 113            |

| Fig. 5.49 | Small signal model for the class AB amplifier input impedance with rbx is the base parasitic resistance, ro is the output resistance, re emitter resistance, base-emitter capacitance $C\pi$ , transconductance gm, and collector-substrate capacitance $Ccs$ . | 114            |

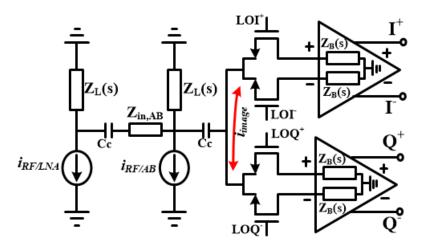

| Fig. 5.50 | Single sided I/Q receiver RF front end model with current driven passive mixer using 50% duty cycle. Class AB amplifier limits i_image drawbacks on the I/Q receiver.                                                                                           | 115            |

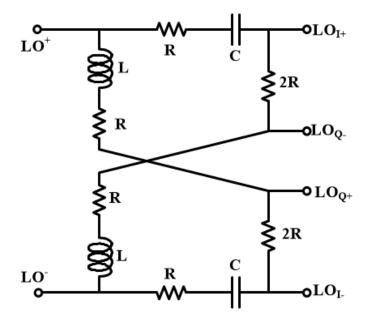

| Fig. 5.51 | Quadrature all pass signal phase generator                                                                                                                                                                                                                      | 118            |

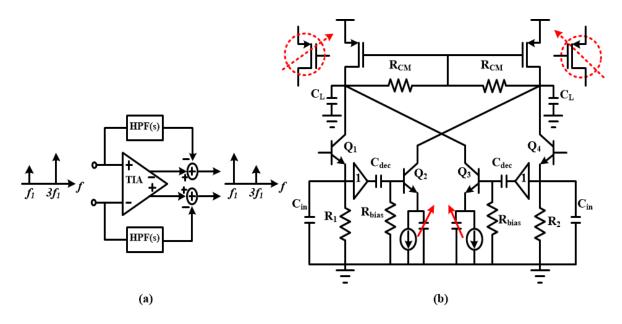

| Fig. 5.52 | (a) Proposed system level TIA with feed-forward HP filter (b) circuit level design with possible bandwidth control and feed-forward HP filter zeros' locations bits control. | .119 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

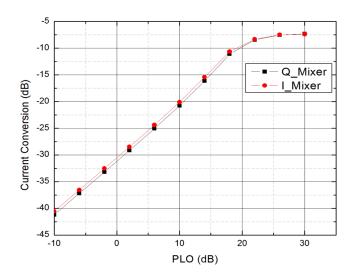

| Fig. 5.53 | Optimum LO power sweep for minimum current conversion loss.                                                                                                                  | .123 |

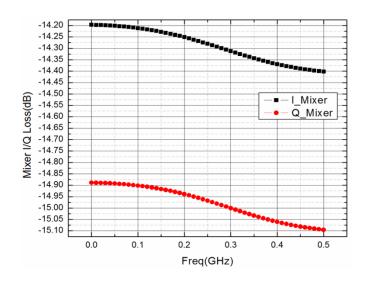

| Fig. 5.54 | Passive mixer current conversion loss for PLO = 15 dBm                                                                                                                       | .123 |

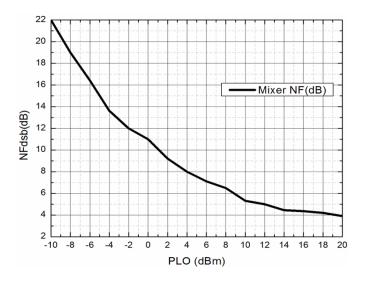

| Fig. 5.55 | Passive mixer doubled sided noise figure for PLO sweep                                                                                                                       | .124 |

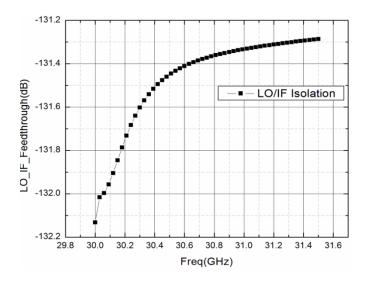

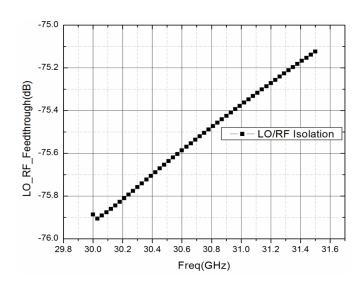

| Fig. 5.56 | LO to IF feedthrough.                                                                                                                                                        | .124 |

| Fig. 5.57 | LO to RF feedthrough.                                                                                                                                                        | .125 |

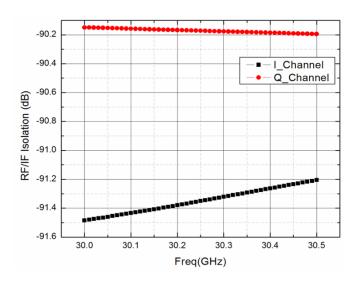

| Fig. 5.58 | RF to IF feedthrough.                                                                                                                                                        | .125 |

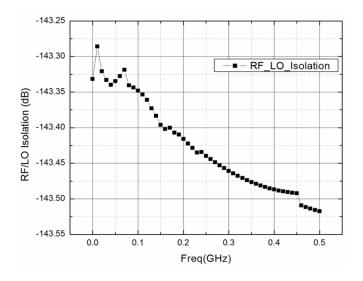

| Fig. 5.59 | RF to LO feedthrough                                                                                                                                                         | .126 |

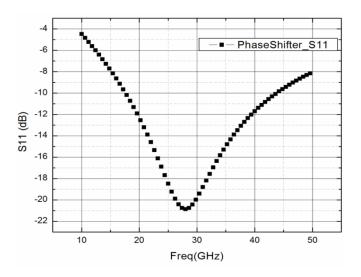

| Fig. 5.60 | Input return loss into the phase shifter.                                                                                                                                    | .126 |

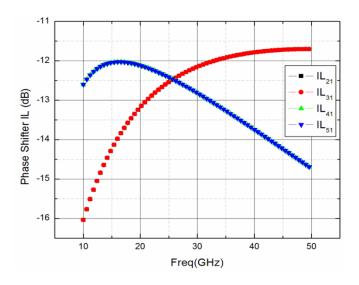

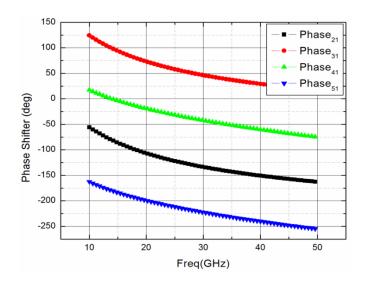

| Fig. 5.61 | Insertion loss of the quadrature phase shifter.                                                                                                                              | .127 |

| Fig. 5.62 | Phase balance of the quadrature phase shifter                                                                                                                                | .127 |

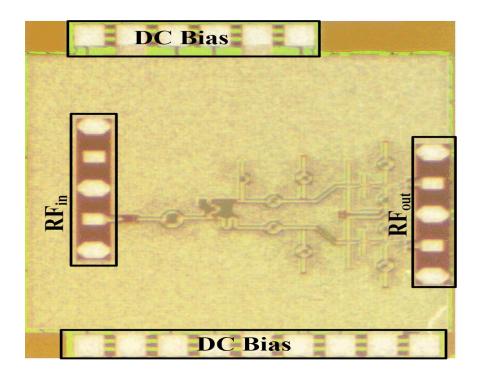

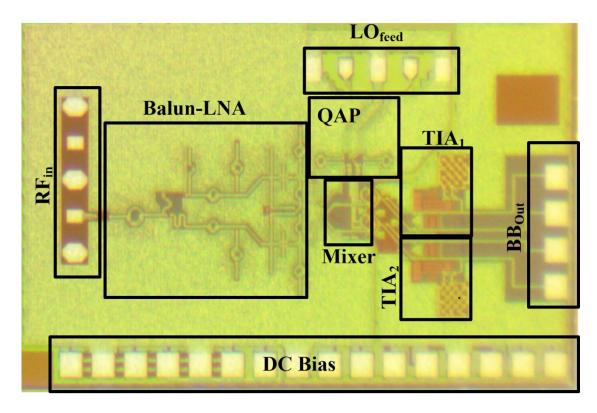

| Fig. 5.63 | Micrograph die of the receiver.                                                                                                                                              | .128 |

## LIST OF TABLES

|                                                                                | Page |

|--------------------------------------------------------------------------------|------|

| Table 2.1 Automotive radar receiver specifications                             | 52   |

| Table 2.2 RF Front-End Specifications for high gain high sensitivity mode      | 53   |

| Table 2.3 RF front-end specifications for high linearity mode settings         | 54   |

| Table 2.4 SAR RX specifications for UAV                                        | 55   |

| Table 3.5 Circuit components values of the implemented balun-LNA               | 62   |

| Table 3.6 Proposed Balun-LNA comparison to existing balun/LNA designs          | 83   |

| Table 4.7 Proposed multi-stages balun-LNA comparison to existing designs       | 104  |

| Table 5.8 Circuit components values for the implemented balun-LNA.             | 110  |

| Table 5.9 MM-wave coexistent receiver performance compared to existing designs | s128 |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Background and Motivation

With the ever growing consumers' demands for high data rate wireless communications and high resolution high accuracy sensing and detection, communication and radar networks have congested the low-end frequency spectrum infrastructure. To cope with users end strains, the Federal Communications Commission (FCC) has allocated some unlicensed bands at the microwave and millimeter wave frequency spectrum [1]-[2]. Transceivers targeting microwave and millimeter-wave (mm-wave) applications based on the wireless metropolitan area network standards (802.16) ranging from 10-66 GHz, ultra-wideband short range radar vehicular sensor from 22-29 GHz, and military radar for unmanned aerial vehicle (UAV) from 35-37 GHz [3], etc. are essential to achieve the users end demands. This frequency spectrum allocation still encounters adjacent as well as coexistence channels, similar to lower frequency spectrums, like radio astronomy at 23.6-24 GHz, industrial-scientific-medical (ISM) at 24.05-24.25 GHz, local multipoint-distribution system (LMDS) at 31 GHz, and cloud radar at 35 GHz [4]. In fact, the frequency spectrum presents a dilemma for some sensitive frequency bands where overlapping exists. For that reason, the FCC regulates the effective isotropic radiated power (EIRP) for the ultra-wideband (UWB) devices to limit the radiated emissions and noise on the spectrum. In literature, many transceivers are reported for microwave and mm-wave applications with limited agility using singleband approach [5]-[13], dual-band design [14]-[15], and lastly wideband RF front-end receivers [16]-[18].

Dedicated transceivers for mm-wave targeting specific applications have come to light in recent years. A 0.18-μm 24 GHz CMOS RF front end was reported in [5]. An automotive short-range and long-range radar sensor for *Ka*- and *W*- bands application with its FCC regulations was addressed in [6]-[7]. Various broadband architectural transceivers designs for the 60 GHz wireless communications are reported in [8]-[10]. Such receivers with single-balanced RF mixers tend to suffer from local oscillator (LO) leakage; thus causing receiver desensitization. Fully integrated using 4 and 8 elements phased array receivers in CMOS for 24 GHz ISM band are reported in [11]-[12]. Further, a fully integrated 77 GHz BiCMOS phased array receiver with dipole antenna on chip for long-range automotive radar sensor is reported in [13].

To increase versatility and functionality, dual-band transceivers/receivers are demonstrated in [14]-[15]. Adding more passive components to achieve dual-bands resonance introduces high signal loss and increases chip area; and hence, increases the power consumption. The dual-bands 24/31 GHz based sub-harmonic receiver architecture in [13] requires fine tuning for the quadrature phases generation schemes as well for amplitude mismatches to improve bands rejection. An automotive dual-bands direct conversion transceiver for collision avoidance is reported in [15]. The large frequency spread of the transceiver frequency planning causes two dedicated local oscillators running at 22 and 77 GHz to be integrated on a single chip. The drawback is more power consumption, larger chip area, and more complex layout floor planning not

to mention the phase noise issues. As we can see; single-band or dual-bands transceivers as reported have limited flexibility and hence creating urgent needs to address these problems.

A more desired approach targets wideband RF front-end transceivers to increase functionality and have the capabilities to support multiple standards simultaneously suffers from limited linearity and high noise figure [16]-[18], thus limiting the receiver dynamic range.

A millimeter-wave coexistent wideband direct conversion receiver for multistandard multi-band radar and communication systems translates simultaneously the

entire frequency spectrum and provides more capabilities and numerous advantages as

compared to the single and non-optimized dual-band counterparts. More functionality

can be clearly seen in the fact that more information is transmitted and received, and

more remote targets are sensed simultaneously on coexistent multiple channels system.

Working on wideband spectrum makes the systems more robust to the fluctuation of the

propagation environment such as severe multi-path fading, urban settings, and

mountainous terrains or frequency-dependence attenuation. Coexistent multi-standards

multi-band operations can be implemented using a single system leading to substantial

benefits including reduced die area, high density IC integration, low cost, and low power

consumption. However, the design of multi-mode multiband system is challenging and

requires new techniques to design the circuits' blocks efficiently with optimized

performances.

In order to meet the high demands for short-range radar and communication

systems in the future, we need to develop miniaturized, highly integrated SoC (System on Chip), low-cost, low-power mm-wave receivers capable of high-resolution, precise and fast location detection, and high data rate wireless communication. The proposed coexistent multi-mode multi-band system should effectively utilize the newly opened mm-wave spectrum, exploit the unique characteristics of UWB and work under various standards constraints simultaneously.

This dissertation proposes and develops a wideband current mode millimeter rwave coexistent receiver for multi-standards multi-bands working in K/Ka bands (18-27 GHz/26.5-40 GHz) and V band (40-75 GHz) for short-range high-resolution radar and high data rate wireless communication systems. The proposed receiver is designed using 0.18 µm SiGe BiCMOS technology. The coexistent receiver architecture works to support all standards within the range 22-44 GHz simultaneously resulting in low-cost, miniature, and low-power consumption systems. The developed mm-wave multistandard multi-band coexistent receiver can be used for numerous cost-effective and multi-functionality applications such as short-range high-data-rate wireless communications, sensing, imaging, tracking, and automotive radar.

#### 1.2 Millimeter-Wave Short Range Radar System

As early as 1886, German physicist Heinrich Hertz experimentally demonstrated that radio waves reflected from solid objects can be used for detection and ranging, thus the name Radar (Radio Detection and Ranging) [21]. Shortly after that, radar systems were developed independently and simultaneously in the naval academies of various

countries. Nowadays, radar systems are being used in various aspects of life for military and commercial purposes such as locating targets at sea, air, and ground.

#### 1.2.1 Radar System Overview

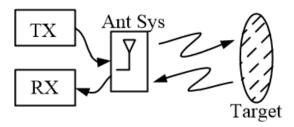

The main purpose of a radar system is to detect accurately the position, range and property for a specific target. To accomplish this task a radar system must consists of 3 sub-systems: a transmitter, an antenna, and a receiver. Fig. 1.1 illustrates the concept.

Fig. 1.1 Radar consists of subsystems: a transmitter, an antenna system, and a receiver.

#### 1.2.1.1 Transmitter

Radar systems operate over an extremely wide range of frequencies from low RF, to microwave and millimeter-wave regimes, up to 300 GHz [21] and beyond. Radar systems have various architectures for antennas, transmitters and receivers. For instance, the transmitter architecture of an ultra-wideband short range vehicle sensor is characterized mainly into 3 different categories, which are: 1) pseudorandom noise (PN) coded continuous wave (CW) transmitters; 2) frequency chirped transmitters systems; and 3) gated pulsed transmitters [21].

All of the previously described transmitters systems can deploy a traditional

process technique known as pulse compression to enhance the radar systems performances. Furthermore, some of the reported systems encompass hybrid structure of various techniques at a greater system design complexity [18]. The PN coded continuous wave (CW) transmitter system is essentially a frequency spread spectrum type system resilient to interferences, but it lacks the necessary dynamic range due to high leakage from transmitter to receiver. As for frequency-chirped transmitters, they are difficult to implement for UWB bandwidth in excess of 1 GHz due to the challenge of generating a wideband low phase-noise chirp in CMOS technologies [22].

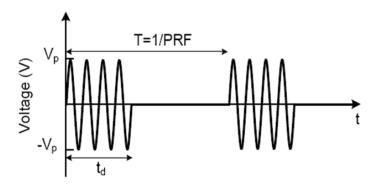

Fig. 1.2 RF pulse signal.

A pulsed transmitter radiates an RF train of pulses or (loosely speaking) impulses with a system-defined carrier frequency, pulse repetition frequency (PRF), and duty cycle. The PRF is the frequency at which the RF pulses or impulses are transmitted, and is inversely proportional to T, where T is the time between transmitted pulses, as shown in Fig. 1.2. The duty cycle of RF pulses is defined as the ratio of  $t_d/T$ , where  $t_d$  is the transmitted pulse width. In a gated pulse system, the transmitter and receiver operate in a

time duplex fashion (TDD) meaning one of them is on at a time, hence achieving a high dynamic range and making it easier to detect a returned signal at the expense of increased hardware and signal complexity. A pulsed radar signal can be incoherent or coherent. To be coherent, there must be a deterministic phase relationship for the carrier from pulse to pulse. This can be accomplished by switching a CW carrier on and off.

The waveform modulation can be introduced into all types of transmitters systems. Various types of modulation schemes can be used including phase, frequency and amplitude modulation, or a combination of modulation types. For pulsed systems, the modulation can be applied within each pulse over the time period t<sub>d</sub>. In the case of adding signal modulation functionality, the transceiver in radar systems can be used in communication systems.

### 1.2.1.2 Antenna System

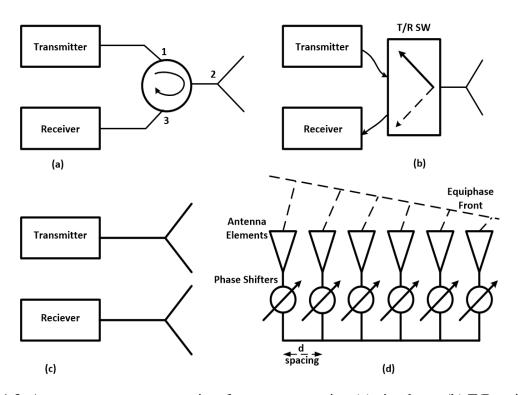

Radar antenna systems consist of various types of antennas as follow: 1) single antenna shared between transmitter and receiver; 2) a pair of independent antennas for transmission and reception; 3) an array of antennas.

Fig. 1.3 shows the block diagram of all types of radar antenna systems configurations. A single antenna type of configuration is more suitable for the gated pulse radar type due to the time division duplexing operation of the system. Such configuration setup is established using a circulator and or a T/R switch to select the path of operation. Note that in either operational mode, transmitting or receiving, it is important to maintain high isolation between ports to minimize the leakage spectrum. If

separate transmit and receive antennas are used, the high intrinsic isolation between the antennas minimizes the leakage from the transmitter to the receiver through the antenna system.

Fig. 1.3 Antenna systems can consist of one antenna using (a) circulator, (b) T/R switch, (c) two separate antennas, and (d) antenna array such as phased array.

Finally, a radar array antenna system with high gain and high directivity is desirable, especially at mm-wave frequencies. The transmitter and receiver can share an antenna array or use separate arrays. Antenna arrays are used extensively in radio astronomy at 23.6-24 GHz and at 44 GHz for synthetic aperture radar (SAR) applications [21].

#### **1.2.1.3 Receiver**

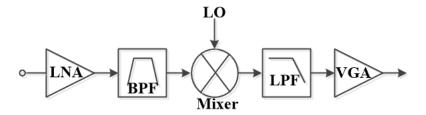

Fig. 1.4 Conventional radar receiver architecture.

The conventional radar receivers amplify, filter, and correlate the received signal to an intermediate frequency (IF) or baseband signal, from which the target can be correctly characterized. Fig. 1.4 shows the basic radar receiver architecture consisting of a low noise amplifier (LNA), a linear phase band pass filter (BPF), mixer, low pass filter and variable gain amplifier (VGA). As the first stage in the receiver, the LNA should exhibit high gain and a low noise figure to maintain a low noise figure for the whole receiver chain. The band pass filter sets the RF band select of the receiver and limits the receiver noise. The mixer correlates the received signal frequency to the IF band or DC by cross correlating the received signal with the local oscillation (LO) signal. In a coherent radar system, the receiver's LO is synchronized with the transmitter LO; coherent systems are common in modern radar systems. Upon down-conversion to the IF band, the signal is filtered and amplified. The IF low pass filter (LPF) sets the final noise bandwidth for the receiver and the VGA sets the receiver dynamic range based on the analog to digital converter (ADC) full scale range. The output of the receiver is then digitized, and digital signal processing is applied.

#### 1.2.2 Short Range Pulse Radar System

The architecture for the short range radars is constrained by the requirements of high range resolution as low as 5 cm, close range detection accuracy for static and moving target, and high dynamic range. Pulsed radar solution is perhaps the most suitable architecture given the time duplex mode of operation, thus high isolation is achieved between transmit and receive side at the expense of complex timing and pulse gated delay circuitry. Hence, a wide dynamic range is attained that helps improve range resolution. Other functionalities include good range accuracy, clutter reduction, and multipath resolution. Pulsed radar is also perhaps one of the simplest architectures to implement, thus potentially making it the most cost effective [18].

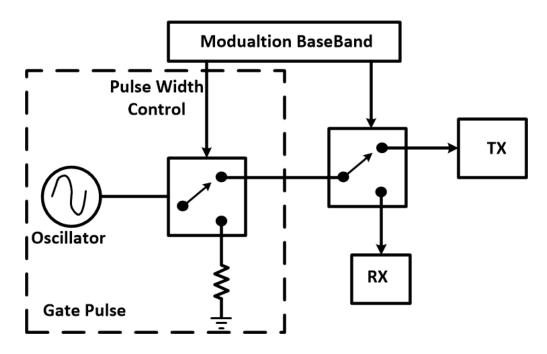

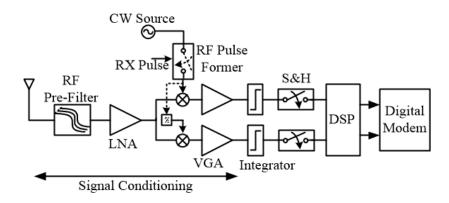

Fig. 1.5 Conventional pulse radar system architecture [18].

The pulsed radar architecture is shown in Fig. 1.5 [18]. A baseband impulse gates the sinusoid from an oscillator to generate a high frequency gated RF pulse signal transmitted by the TX. The resulting RF-pulse signal, as shown in Fig. XX, occupies a bandwidth of approximately 1/t<sub>d</sub>, where t<sub>d</sub> is the width of the baseband impulse; the precise bandwidth will depend on the shape of the impulse envelope [21]. The transmission of gated RF pulse triggers a baseband delay circuitry, which waits certain time for a second trigger event to take place. Before the second trigger is activated, the TX/RX select switch is toggled between the TX antenna and the LO ports of the receiver. At the second trigger, the second switch is changed from the TX to RX. The RX then samples its output at this instant and stores it for processing. Thus, the input from the RX antenna is multiplied with a replica of the transmitted pulse. If the two pulses do not overlap in time, the output will be zero, whereas if they are coincident, the output will be a maximum. The delay between the two triggers determines the range gate being scanned at the time. Thus, by changing this delay, objects at varying distances can be detected [18], [22].

#### 1.2.2.1 Radar Interferers and Solutions

The pulsed radar sensor suffers from various interferers that tend to degrade its effective cross sectional radar target detection accuracy as well increases false alarm rate. The most harmful interferers affecting the sensor receivers' detection process and dynamic range are listed as follow: 1) interferers emitted by the radar sensor and radiated as blockers on the frequency spectrum; 2) interferers emitted in-band due to

limited TX/RX isolation; 3) interferers in-band or jammers radiated from similar sensor systems [18].

For the regulatory commissions, the first interferes type are of worrisome due to spurious emissions generated from the radar sensors. Those emissions must be filtered in accordance the regulatory spectral emission limits. For instance, the transmit power and its vertical antenna gain directivity for a short range radar sensor is limited to 35 dB below the -41.3dB<sub>m</sub>/MHz for a maximum 30 degree elevation with the horizontal plane due to certain sensitive passive test equipment - e.g., astronomy radio equipment at 23.6-24 GHz and 24.05-24.25 GHz ISM band [4].

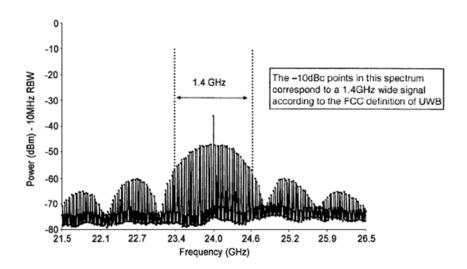

Fig. 1.6 CW LO leakage at 24.15 GHz [18].

In addition, the finite switch isolation in the pulsed radar sensor leaks spurious emissions into the radar receiver's due to CW transmit signal, thus affecting the radar sensor detection accuracy and receiver sensitivity and dynamic range. Fig. 1.6 illustrates

the CW leakage into the receiver's spectrum [18]. The last spurious emissions radiated in-band and/ or jammers are caused by CW transmit signals appearing in the pulsed radar receiver spectrum. This artifact is mainly due to UWB frequency modulated continuous wave (FM-CW) transmitter radar sensor operating at 26 GHz in the vicinity of the pulsed radar receiver. Those interferes can potentially saturates the radar receiver and desensitizes it, thus increasing the receiver down time. However, a careful design can alleviate this problem through a coherent radar approach where carrier frequency is being changed from pulse to pulse and also employ a randomization concept. A further benefit of this randomized pulsing is in meeting the spectral emission limits of the FCC by spreading the radiated energy more evenly across the operating bandwidth [18].

#### 1.2.2.2 Radar Equations

The received power at the input of the radar receiver is calculated using radar equation

$$P_r = \frac{P_t G_{tx} G_{rx} \lambda^2 \sigma}{\left(4\pi\right)^3 R_{\text{max}}^4} \tag{1.1}$$

where  $P_{rx}$  is the power at the input of the receiver,  $P_{tx}$  is the power at the output the transmitter,  $G_{tx}$  is the transmit antenna gain,  $G_{rx}$  is the receive antenna gain,  $\lambda$  is the wavelength of the carrier frequency,  $\sigma$  is the radar cross section (RCS) of the target, and R is the range to the target [21].

The maximum range of the radar system correlated the with the resolution accuracy is derived from (1.1)

$$R_{\text{max}} = \left(\frac{P_{t}G_{tx}G_{rx}\lambda^{2}\sigma}{(4\pi)^{3}P_{r,\text{min}}}\right)^{1/4}$$

(1.2)

where  $R_{max}$  is the maximum target range and  $P_{r,min}$  is the minimum detectable power at the input of the receiver. The expression demonstrates the relationship between the target range, transmitted power, and minimum detectable received power. Increasing the transmitted power and/or decreasing the minimum detectable received power increases the maximum range of the radar.

The minimum signal to noise ratio for a single pulse at the output of the receiver,  $SNR_{o,min} \ is \ calculated \ as$

$$SNR_{o,\min} = \frac{SNR_{in,\min}}{NF} \tag{1.3}$$

where  $SNR_{in,min}$  is the minimum signal to noise ratio for a single pulse at the input of the receiver and NF is the noise figure of the receiver. Manipulating equations (1.1) and (1.3),  $SNR_{o,min}$  is calculated as

$$SNR_{o,\min} = \frac{EIRP_{pk}G_{rx}\lambda^2\sigma}{\left(4\pi\right)^3R_{\max}^4KT_a(NF)(BW)}$$

(1.4)

where EIRP<sub>pk</sub> is defined as the peak effective isotropic radiated power, K is the Boltzmann constant (1.38e<sup>-23</sup>J/K),  $T_a$  is the antenna temperature, and BW is the receiver bandwidth.

#### 1.2.3 Radar Pulse Compression

Radar pulse compression is a general term used to describe a waveform shaping process produced by a modified propagating waveform through electrical network properties of a medium. The pulse compression technique consists of a CW source with dispersive delay line through a rectangular function on the transmit side whilst the echoed signal is filtered through a surface acoustic wave (SAW) pass band filter to generate a pulse compression before post processing. The purpose of the pulse compression concept is to combine the high energy of a long pulse width with the high resolution of a short pulse width. Thus, this pulse compression technique improves the signal to noise ratio for less power transmission. The pulse compression concept is a frequency modulated pulse method that consists of two classes; 1) frequency modulation or FM modulation; 2) phase modulation or PM modulation.

#### 1.2.3.1 Linear Frequency Modulation Pulse Compression

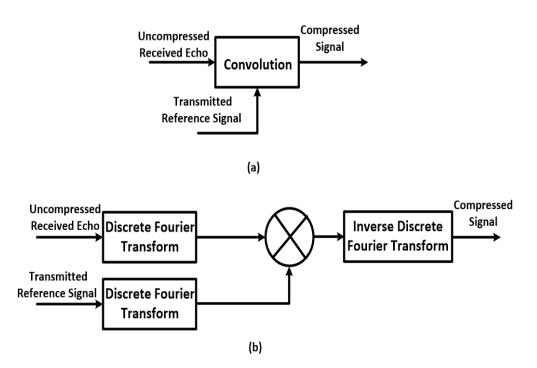

Linear frequency modulation (LMF) pulse compression radar or (Chirping) is the practical implementation of a matched-filter system. The transmit pulse signal can be described either by the frequency response  $H(\omega)$  or as an impulse response h(t) of the modulated filter. The received echo is fed into a matched filter whose frequency response is the complex conjugate  $H^*(\omega)$  of the modulating filter. The output of the matched filter is the compressed pulse which is just the inverse Fourier transform of the product of the signal spectrum. A filter is also matched if the signal is the complex

conjugate of the time inverse of the filter's impulse-response. This is often achieved by applying the time inverse of the received signal to the pulse-compression filter. The output of this matched filter is given by the convolution of the signal h(t) with the conjugate impulse response h\*(-t) of the matched filter. In essence, the matched filter results in a correlation of the received signal with a delayed version of the transmitted signal as shown in Fig 1.8 below. For this chirp pulse compression example, the output of the matched filter is a sinc function with problematic time side-lobes. An amplitude weighting function is used at the output of the match filter to suppress the time side-lobes to less than 30 dBs.

Fig. 1.7 Linear frequency modulation pulse compression implementation methods (a) time domain, (b) frequency domain.

#### 1.2.3.2 Phase-Coded Pulse Compression

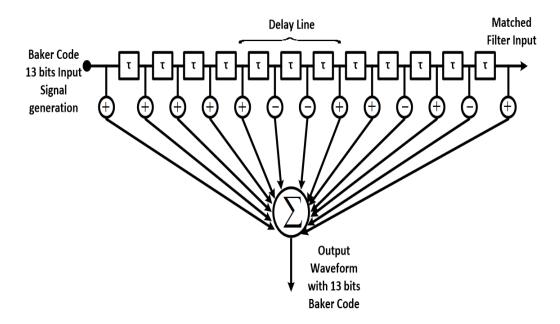

Phase-coded pulse compression based on the binary phase shift keying (BPSK) modulation technique sub-divides a long transmitted pulse into equally timed short pulses with a particular phase. The phase of each sub pulse is selected in accordance with the phase code modulation sequence (BPSK) which is either positive +1 or negative -1. The phase of the transmitted pulse alternates between 0 and  $\pi$  in accordance with the

Fig. 1.8 Phase-coded pulse compression using 13 bits Baker code.

transmitted pulse coded sequence of elements as illustrated in Fig. 1.8. Since the transmitted frequency is not a multiple of the reciprocal sub-pulse width, the coded signal is discontinuous at the phase-reversal point. In fact, the phase 0,  $\pi$  random selection is critical. To overcome the side-lobes limitations, optimum binary codes known as Baker codes have been developed to suppress this artifact.

#### 1.2.4 Signal Modulation

Signal modulation schemes can be implemented in pulsed radar systems to support the data communication. On-Off-Key modulation (OOK), Pulse Position Modulation (PPM), Pulse Amplitude Modulation (PAM) and Bi-phase modulation (BPM) are the most widely used for this objective; the transmitted information can be coded by changing its pulse position, shape or polarity [23].

#### 1.2.4.1 On-Off Key Modulation (OOK)

OOK denotes the simplest form of amplitude-shift keying (ASK) modulation that represents digital data as the presence or absence of a carrier wave. In its simplest form, the presence of a carrier for a specific duration represents a binary "1", while its absence for the same duration represents a binary "0". The main disadvantage of OOK modulation system is that it is more prone to noise, interference, and multipath fading. Thus, it will be more difficult for the receiver/demodulator to distinguish between fading/noise and data pulse transmission.

#### 1.2.4.2 Pulse Position Modulation (PPM)

PPM is a form of signal modulation in which M message bits are encoded by transmitting a single pulse in one of  $2^{M}$  possible required time-shifts. Such transmission is periodic every T seconds, and the bit rate is M/T bit per second. The advantage of PPM is that the pulse position will appear to be random on the time domain, which

translates into a smoothly spread spectrum on the frequency domain.

#### 1.2.4.3 Pulse Amplitude Modulation (PAM)

PAM is a form of signal modulation where the message information is encoded in the amplitude of a series of signal pulses. It is an analog pulse modulation scheme in which the amplitudes of a train of carrier pulses are varied according to the sample value of the message signal. PAM supports multi-level amplitude modulation which is suitable for high data rates. However, the pulses will be very close to each other and more susceptible to noise and interference while larger pulses will require more power for amplification.

#### 1.2.4.4 Bi-Phase Modulation (BPM)

BPM is RF transmitted pulse signal that alternates between 0 and  $\pi$  to represent the bit sequence of elements "1" or "0". BPM is less sensitive to noise compared to AM modulation schemes; and the requirement for accurate timing control is also not as stringent as PPM. Furthermore, BPM supports wide range of digital data transmission from WiFi to satellite television.

# 1.3 Transceivers Architecture for Short Range Radar and Radio Communications Systems

The system architecture reported in [24] holds dual mode functionalities for short range radar and communications systems. As for the communication system mode of operation, modulated RF train pulses are transmitted using any of the modulation

schemes from section 1.2.4. The receiver generates a series of RF pulses with exactly the same shape and intervals, called template signal, to correlate with received pulses in order to detect the transmitted information [23]. Time delay is expected between the two users end, and loop synchronization is in place to align the template train pulse and the received signal.

In radar system mode configuration, the transmitter sends RF gated pulses periodically with lower pulse repetition frequency (PRF). The receiver operates in similar fashion as mentioned in the communication mode mechanism. That is, the received signal is correlated to the very same transmitted signal acting as template signal on the receiver end with known time delay measured as multiple of the time gated pulse which is equal to the pulse width.

Fig. 1.9 System architecture for both radar and communication systems [24].

#### 1.4 Dissertation Organization

This dissertation presents several new circuit architectures and techniques to improve performance of some key CMOS and SiGe/BiCMOS RFIC circuits operating at RF, microwave and millimeter-wave frequencies, and the development of a new millimeter-wave coexistent current mode direct conversion receiver for multi-standards multi-bands operating at K/Ka and V bands and not limited to short range radar and communication systems.

Chapter II discusses system architecture level and design specifications for short range radar and wireless communication systems at millimeter-wave frequency. Chapter III presents a new low power consumption active balun-LNA for millimeter-wave application using SiGe BiCMOS technology. Analysis design procedure, parameter trade-off, simulation and measurement results, and layout issues are discussed. In Chapter IV, a novel 2 stages low power balun-LNA with phase and gain mismatches cancellation technique independent of frequency is presented. The cancellation technique is frequency independent and do not rely on passive components for neutralization and compensation. The active balun-LNA is well-balanced over a wide frequency range from DC up to millimeter-wave regimes and detailed analysis is provided. In Chapter V, a new coexistent millimeter-wave system and circuits level architecture using SiGe BiCMOS current mode direct conversion receiver is presented. An auxiliary path for high power jamming interferers for military unmanned aerial vehicular (UAV) radar system at 35-37 GHz is considered as well. The detailed design of some building blocks including fully balanced quadrature passive mixer and phase shifter, trans-impedance amplifier (TIA), and out of band interferers rejection filter known as anti-aliasing filter is presented. Finally, chapter VI summarizes the contribution of this dissertation.

#### **CHAPTER II**

# SICS COEXISTENT RECEIVER ARCHITECTURE AND SYSTEM SPECIFICATIONS

# 2.1 MMW Receivers History

Most microwave and mm-wave receivers' designs reported in literature are dedicated to serve single or dual bands applications. Some of these applications involve short range high resolution vehicular radar at 22-29 GHz to wireless high data rate metropolitan area network from 10.6-66 GHz. However, various types of receivers' architectures are reported to serve these applications based on homodyne approach, heterodyne designs, and phased array types as well. We will provide a small window into each receiver's design approach highlighting its proponents and drawbacks.

# 2.1.1 Heterodyne Receiver

MM-wave heterodyne type receiver architecture design consists of multi-mixing stages to bring about the spectrum to an intermediate frequency (IF) followed through with some filtering made ready after A/D converter for digital processing. However, polyphase filters are needed to suppress LO images after each mixing stage. The design of RF polyphase filter is not trivial and not to mention the need for gain compensation stage to maintain SNR level at the expense of power and die area. Until recently, a new concept of mm-wave heterodyne receiver's considered [8], [9] shown in Fig. 2.10 below. The architecture consists of RF mixing followed by direct mixing stage to alleviate the

image problem and resolve some complex issues related to high in-band phase noise associated with LO frequency planning and layout floor designs.

Fig. 2.10 Heterodyne receiver architecture.

# 2.1.2 Phased Array Receiver Principles and Architecture

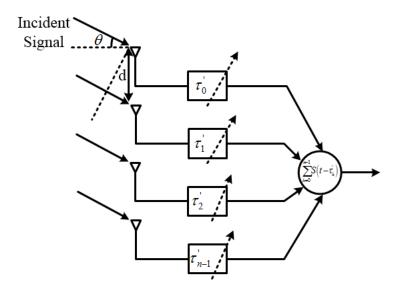

A phased array receiver consists of several signal paths, each connected to a separate antenna. The radiated signal arrives at spatially-separated antenna elements at different times. An ideal phased-array compensates the time delay difference between the elements and combines the signals coherently to enhance the reception from the desired direction(s) while rejecting emissions from other directions [25]. Fig. 2.11 shows a one dimensional n-elements linear array hit by a plane wave. The arrival incident signal to each antenna element is progressively time delayed by  $\tau$ . This time delay difference between two adjacent antenna elements is related to their separation distance (d) and their angle of incidence ( $\theta$ ) with respect to the normal. The governing relationship is given by

$$c\tau = d\sin\theta \tag{2.1}$$

where c is the speed of light. The incident signal at the kth antenna element can be expressed as

$$S_{k}(t) = A(t - k\tau)\cos(\omega_{c}t - k\omega_{c}\tau + \varphi(t - k\tau))$$

(2.2)

where the amplitude of the kth element is defined by  $A(t-k\tau)$ ; the carrier frequency is defined by  $\omega_c$ ; and the phase delay is defined by  $\varphi(t-k\tau)$ . The equal spacing of the

Fig. 2.11 General concept of phased array system architecture.

antenna elements is reflected in (2.2) as a progressive phase difference  $\omega_c \tau$  and a progressive time delay  $\tau$  in A(t) and  $\phi$ (t). Adjustable time delay elements ( $\tau$ 'n) can compensate the signal delay and phase difference simultaneously [25]. The combined signal summation  $S_s(t)$  can be expressed as

$$S_{s}(t) = \sum_{k=0}^{n-1} S(t - \tau_{k})$$

$$= \sum_{k=0}^{n-1} A(t - k\tau - \tau_{k}) \cdot \cos\left[\omega_{c}t - \omega_{c}\tau_{k} - k\omega_{c}\tau + \varphi(t - k\tau - \tau_{k})\right]$$

(2.3)

For  $\tau_{k}^{'} = -k\tau$  the total output signal power is given by:

$$S_s(t) = nA(t)\cos(\omega_c t + \varphi(t))$$

(2.4)

For a narrowband phased array design the time delay between antenna elements is translated into an adjustable phase delay elements in the RF path. Note that in a narrowband signal the relative slow change in amplitude A(t) and phase  $\phi$  (t) compared to the carrier frequency  $\omega_c$  necessitate only the need to compensate for the progressive phase difference  $\omega_c \tau$ . The time delay element can be replaced by a phase shifter which provides phase-shift  $\Phi_k$  to the kth receiver signal path. To add the power signal coherently,  $\Phi_k$  should be given by:

$$\Phi_k = k\omega_c \tau \tag{2.5}$$

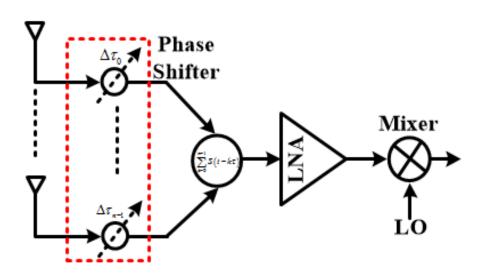

The phase compensation for a narrow band signal can be made at various locations in the receiver chain, i.e, RF path, LO, Baseband, or digital domain. For the broadband type of phased array architecture, the only suitable structure is limited to passive RF phase shifting architecture. In this approach, antennas elements are directly

followed by passive phase shifters or time delays elements fed into a combiner to coherently add signals into the LNA input. A single path receiver is suitable for this approach as shown in Fig. 2.12. The main drawbacks of this design are the lack of amplitude control as well as the limited receiver dynamic range and sensitivity due to passive phase shifter and combiner losses [25], [26]. As a single-path receiver, the phased array receiver can be realized using various known down conversion schemes such as

Fig. 2.12 Passive RF phased array architecture.

heterodyne, direct conversion, wide-band IF, and low-IF. The design trade-offs are dictated according to each signal-path receiver type. One important factor in a phased array system is its ability to attenuate the incident interference power from other directions. Thus, the spatial filtering is applied. Furthermore, a spatial processing technique can be considered by changing the nulls location and the side lobes levels by changing the weight signal power factor of each element in the phased array system.

Hence, the spatial filtering and processing techniques help improve the signal to noise and interferers' ratio for the phased array receiver chain.

# 2.1.3 Homodyne Receiver

Fig. 2.13 Homodyne receiver architecture at mm-wave.

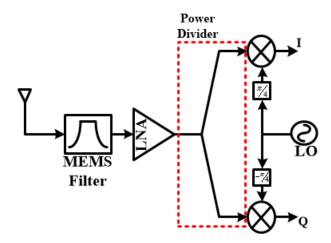

An alternative approach to the previously mentioned receiver architectures is the homodyne receiver structure also known as direct down conversion receiver. At mm-wave, all interconnects have to be simulated in a 3D EM simulator to see the effects of inductance loading and coupling parastics to substrate. In this spirit, the mm-wave homodyne receivers reported in [16], [18], [22], consist of a LNA followed by a power divider fed into in-phase/quadrature single balanced mixers. The cross correlated outputs, mixers outputs, is fed into a wideband variable gain amplifier (VGA). The baseband signal is integrated and dumped before being digitally processed. Fig. 2.13 shows the system receiver architecture. For instance, this approach was dedicated to the short range vehicular radar system from 22-29 GHz application. The main disadvantage

of this single balanced mixer design scheme is subject to LO power feed-through causes receiver desensitization that can lead to noise figure increase. Also, the integration and dump block on the baseband side is very vague and doesn't present a real solution.

# 2.2 SICS Coexistent Receiver Definition

In May 1995, J. Mitola proposed "The Software Radio Architecture", [27], that is transmit/receive *multiple channels simultaneously* completely eliminating the Analog Front-End (AFE). However, such a system probably is an over reach at mm-wave frequencies and is bounded by advancement in technology not foreseen in the near future. Razavi's proposed Cognitive Radio design approach [28]. The main idea stems from intelligently sensing the frequency spectrum and makes allocation of freed up channels for reuse. The system design entails many challenges from the AFE design and technology aspects and may not be applicable any time soon. A more practical approach that copes with industry needs based on multi stacked systems integrations on a single die also known as System on Chip (SOC) [29]-[30]. However, the rapid increase in systems integration becomes impractical not to mention the die size and its power consumption and I/O complexity. Our portrayal of coexistent receiver architecture is based on a configurable, agile platform supporting any predefined single channel bandwidth with any modulation scheme located anywhere on a defined broad spectrum.

#### 2.3 Coexistent RX for Radar and Radio Terminals

Our System presents the challenge of designing an mm-Wave coexistent radio and radar receiver architecture (CRRA) supporting multi-standards multi-bands applications. The current mode coexistent receiver architecture is based on configurable agile platform supporting any predefined single channel bandwidth with any modulation. If multiple bands requested simultaneously then parallel structure is needed with possible blaun-LNA block being shared. The system will be operating from 22-44 GHz sustaining short range vehicle radar receiver from 22-29 GHz, Industrial-Scientific-Medical (ISM) band from 24.05-24.25 GHz, military radar receiver for reconnaissance missions using unmanned aerial vehicular at 35-37 GHz, ultra-wideband (UWB) wireless application from 10-66 GHz known as Metropolitan Access Area Network (WiMAN) for 802.16a standard, and 44 GHz for satellite communication. This is just to list few applications, it should be able to support all channels receivers operating within the frequency band; given we have a wideband tunable local oscillator (LO) with a good phase noise and a wideband phase shifter with minimum insertion loss as well as low amplitude and phase mismatches. For a system to be considered CRRA, it has to meet certain criteria:

- No RF pre-filter right after antenna e.g. (SAW Filter or BAW Filter), providing the necessary flexibility.

- Having a reconfigurable ADC combined with a VGA.

- Having a reconfigurable current mode RF-Front End.

- Limit power consumption for possible wireless support.

• Having out of band harmonics and interferers' rejection.

In general, all RF-Front End circuits including RF pre-filter and base-band (BB) blocks are conditioning signals for the analog to digital conversion (ADC) to provide accurate digital representations for the demodulated signals. That being said, the receiver has to have a robust linearity to IN/OUT of band interferers, cross modulation, and amplitude modulation (AM) detection. Some aspects of these interferers are subject to the type of receiver architecture. For example, a second order intermodulation product (IP2) is very important for direct conversion approach although a differential structure is supported. Therefore, designing a receiver involves paramount tradeoffs between sensitivity and linearity.

# 2.4 Signal Conditioning Functions in Low Power Wideband Receiver

Mitola's main idea concept presents the ADC as the only interface between the analog domain and the digital world. With simple calculations, it is immediately concluded that Mitola's concept is impossible to be implemented at mm-wave frequencies considering the ADC sampling frequency and its power consumption requirements. In general, the ADC is a low pass filter shaping the signal in its simplest form. Note that the ADC dynamic range has to be larger than incoming signal dynamic range including interferers and blockers. It is important for the incoming signal to be down converted, filtered, and amplified prior to the ADC. Fig. 2.14 shows the signal conditioning blocks for the wideband receiver architecture where LO frequency planning

and layout floor plays a major role in the structure design. The assumption here is the LO is provided externally supporting wideband differential signal as stated in the section 2.3.

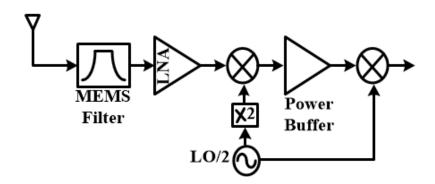

Fig. 2.14 SRR wideband receiver architecture with front-end signal conditioning blocks.

The architecture scheme shows a homodyne type approach also known as direct conversion with zero IF which is easier to achieve wideband operation with the least signal blocks path, hence reducing power and losses. The receiver first block consists of RF preselect filter using MEMS technologies. A low noise amplifier (LNA) is followed where the signal is amplified with minimum added noise. After the LNA block, the signal is down converted to baseband using in-phase/quadrature mixers making the receiver more robust to frequency image spectrum. Ideally, the in-phase/quadrature operation is image free, however in practice the image rejection ratio (IRR) is limited by the amplitude and phase mismatches between the I and Q paths [31], [32].

The simple frequency planning and low IRR requirements makes the direct conversion zero IF receiver an attractive choice at mm-wave. For narrow band receivers, the rejection of interferers and blockers are established through cascaded filtering functions from the RF pre-filter, LNA output LC tank, and baseband low pass filter. However, wideband receivers experience a little or no filtering up till the VGA block where a first order low pass in its natural form is expected. For that reason the FCC limits the transmit power on the spectrum in some cases so the background noise spectrum and interferers are low for some sensitive passive radar applications. Chapter I addresses the interferers and blockers mitigations mainly after the demodulation section in the receiver chain. However, the filter needs to be applied as early as possible in the receiver chain so the receiver down time is very small.

#### 2.5 Low Power Coexistent Receiver Architecture Fundamentals

Starting from the receiver back end where digital Modem is followed by the DSP block for demodulation and constellation recovery. The analog to digital interface is based on the availability of low power reconfigurable ADC with finite resolution and more reasonable sampling frequency to preserve the low power wideband receiver concept for radar and radio terminals. In some operational domains, the coexistent receiver is wired and in other operational mode has limited power access for wireless and surveillance applications. The ADC is preceded with the AFE circuits for filtering and amplification.

This means that the selected channel, and adjacent channels, is sampled with minimal filtering and amplification consistent with low power ADCs. To preserve the wideband operational mode, the AFE circuits should remain as simple as possible with the least parasitic losses. Most of the filtering operation is pushed further down the

receiver chain into the digital and demodulation section. The VGA is lumped into the ADC block, and a continuous feed-forward poly-phase high pass anti-aliasing filter is selected to deal with interferers and harmonics rejections. A current mode RF front-end is considered to maintain high in-band linearity and low noise figure followed by a transimpedance amplifier providing I-V conversion.

Similar to homodyne wideband RX, it is clear that from the upstream ADC it is most beneficial that the channel of interest is down-converted to zero-IF. This is because of the low-pass nature of all analog circuits and the most efficient in power consumption. Although in principles these circuits can be transformed into any filters or amplifications types, the power consumption, circuits' complexity, and losses make it undesirable approach.

#### 2.5.1 Low Power ADC at Baseband

The power budget for the ADC is limited to less than 32 mW designed in advanced CMOS technologies. According to FCC regulations; a minimum of 500 MHz bandwidth is needed for UWB systems including mm-wave based UWB systems and their transmitters and receivers. A simple literature review shows that a 10 bits pipeline ADC with up to 1 GS/s is possible [33]. For example, this ADC can be used for short range vehicular radar application. Based on 802.16-SC standard for single wireless carrier for WiMAN between 10-66 GHz, a local multipoint-distribution system (LMDS) at 31 GHz with 500 MHz bandwidth including 19-20 channels bandwidth up to 25/28 MHz with QPSK modulations are targeted with readily available 10 bits ADCs' using

pipeline architecture with 100 MS/s and consumes less than 5 mW. More advancement in CMOS technologies can reduce the power/conversion-step for the ADCs' and improve the bits resolutions thus increases the ADC signal bandwidth.

# 2.5.2 Merging Variable Gain Amplifier (VGA) into ADC

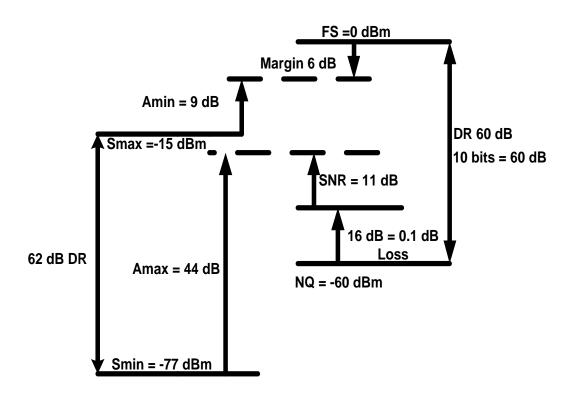

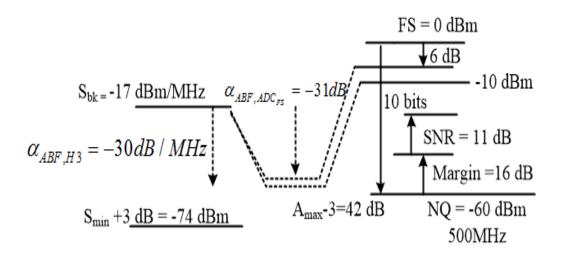

According to the FCC regulations, a UWB receiver requires a minimum of 500 MHz channel bandwidth. For a wideband receiver, it is more reasonable to shift the gain control of the high dynamic range signal from the programmable gain amplifier (PGA) or VGA or the combination of both to the RF front-end. Shifting the programmable gain functions completely to the DSP forces the ADC power consumption to become excessively high. In reality, it is a tradeoff between ADC power consumption, and the RF front-end. The incoming signal dynamic range needs to be lower than the ADC dynamic range so that all analog values are mapped, digitized, and normalized properly. Due to advancement in CMOS digital technologies, we assume greater role for the AGC. Let us study the effect of the AGC behavior on the short range vehicular radar (SRR) sensor.

According to SRR transmit standard [1]-[2]; the specifications for transmit emissions EIRP mean power density is regulated to -41.3 dBm/MHz with an additional 35 dB attenuation for passive radar applications, 23.6-24 GHz, with antenna sidelobes elevation above 30° with the horizontal plane. The peak transmit EIRP power density is limited to -17 dBm/MHz for 50 MHz bandwidth. From these specifications, we can determine the receive strength signal at the receiver antenna side to be between -77 dBm

to -15 dBm. This is a 62 dB dynamic range. We assume that the receiver architecture is based on pulsed radar design approach, thus the benefit of higher receiver dynamic range compared to its counterpart's structures. Further, the TX/RX mode of operation is based on time duplex, hence reducing the TX/RX leakage. Given the design requirements for the *prf*, *probability of target detection and probability of false alarm a minimum*  $(SNR_0)_{min}$  is required. The minimum SNR is 1.1 dB and 10 pulses are integrated to reach the required SNR target of 11 dB based on RX NF of 8 dB.

Starting with the ADC, we used a 10 bits pipeline ADC. Such ADC is readily available with Full Scale (FS) output of 0 dBm (1.2 V peak to peak) and a sampling frequency of 1 GS/s and supporting bandwidth up to the Nyquist rate. The ADC only consumes 32 mW from a 1.2V power supply using 65 nm CMOS process. Then, the ADC quantization noise is at -60 dBm; so all signal conditioning circuits are required to amplify input signals above the ADC noise floor plus the modulation scheme SNR. All RF front-end circuits, anti-aliasing and anti-blocking filter are required to amplify input signal by 28 dB. Also, we have to consider the SNR degradation mainly due thermal noise, quantization noise, and clock jitter. To limit our SNR degradation to 0.1 dB due to noise quantization, we need to add 16 dB as a safety margin. For large input, gain must be lowered from 44 to 9 dB leaving 6 dB margins below full scale output for envelope variations and AGC gain setting error. Fig. 2.15 shows the frequency planning for the programmable variable gain amplifier. It is really important to emphasize the sharing between the VGA and the DSP part instead of using higher resolution ADC, thus

increasing the power consumption. Note that an increase in signal bandwidth requirement may set higher gain requirements on the AFE and VGA.

Fig. 2.15 Programmable variable gain amplifier specification for SRR application.

Similarly, the 802.16-SC for the WiMAN standard with 25/28 MHz bandwidth operates from -85 dBm to -15 dBm. At high data rate transfer, the minimum receiver sensitivity floor is set at -75 dBm. A larger dynamic range is expected due to smaller bandwidth. To digitize 28 MHz bandwidth, a 10 bits pipeline ADC with 100 MS/s is expected within the power budget of 5mW [34] from a 1V power supply using 90 nm CMOS process. Allowing for the 15 dB SNR for proper signal detection at an acceptable bit error rates; the RF/analog front-end variable gain is expected to vary from

41 dB to 9 dB. A lower ADC dynamic range due to wider system bandwidth requirements forces the RF front-end to carry higher burden in terms of power consumption.

# 2.5.3 Anti-Aliasing and Anti-Blockers Filters