UNIVERSITY OF HERTFORDSHIRE

# Analysis and Coordination of Mixed-criticality Cyber-physical Systems

by

Simon Maurer

A thesis submitted to the University of Hertfordshire in partial fulfillment of the requirements of the degree of

Doctor of Philosophy

March 2018

#### UNIVERSITY OF HERTFORDSHIRE

### Abstract

Centre for Computer Science and Informatics Research (CCSIR) School of Computer Science

Doctor of Philosophy

by Simon Maurer

A Cyber-physical System (CPS) can be described as a network of interlinked, concurrent computational components that interact with the physical world. Such a system is usually of reactive nature and must satisfy strict timing requirements to guarantee a correct behaviour. The components can be of mixed-criticality which implies different progress models and communication models, depending whether the focus of a component lies on predictability or resource efficiency.

In this dissertation I present a novel approach that bridges the gap between stream processing models and Labelled Transition Systems (LTSs). The former offer powerful tools to describe concurrent systems of, usually simple, components while the latter allow to describe complex, reactive, components and their mutual interaction. In order to achieve the bridge between the two domains I introduce the novel LTS Synchronous Interface Automaton (SIA) that allows to model the interaction protocol of a process via its interface and to incrementally compose simple processes into more complex ones while preserving the system properties. Exploiting these properties I introduce an analysis to identify permanent blocking situations in a network of composed processes. SIAs are wrapped by the novel component-based coordination model Process Network with Synchronous Communication (PNSC) that allows to describe a network of concurrent processes is supported due to well defined interfaces.

The work presented in this dissertation follows a holistic approach which spans from the theory of the underlying model to an instantiation of the model as a novel coordination language, called *Streamix*. The language uses network operators to compose networks of concurrent processes in a structured and hierarchical way. The work is validated by a prototype implementation of a compiler and a Run-time System (RTS) that allows to compile a Streamix program and execute it on a platform with support for ISO C, POSIX threads, and a Linux operating system.

## Acknowledgements

First, my gratitude goes to the University of Hertfordshire for providing the funding and infrastructure for my PhD and for giving me the opportunity to start a career in academia.

I would like to thank my primary supervisor and research mentor Dr Raimund Kirner for the support of my PhD and related research. I am grateful for his commitment to provide me with guidance even late at night or on weekends. His broad knowledge and his patience were a huge help throughout the whole of the PhD.

Further, I would like to express my gratitude to Dr Olga Tveretina, my secondary supervisor, for her valuable inputs and her mental support. My thanks also go to Dr Prof Alex Shafarenko, leader of the research group Compiler Technology and Computer Architecture (CTCA), for his invaluable feedback.

I thank Giovina for her patience and her interest in abstract topics that are not hers. Her cheerful and supportive attitude were a big help throughout this project and I am ever grateful to her for leading me onto this path. Her hilarious personifications of certain aspects of my work, complete with pictures and all, is only one of many examples of her brilliant way of supporting me.

Although I do not know these people personally I want to give a shout out to Randall Munroe for his book "Thing Exaplainer - Complicated Stuff in Simple Words", showing that complicated things can be explained with only a 1000 words and Linda Liukas, for her book "Hello Ruby", advocating the fact that computer science is not as difficult as common belief suggests and that it can be taught to anyone.

Last but not least, I want to thank my family and friends from abroad for their continuous support and their willingness to pay us visit on a regular basis.

# Contents

| Preface             |       |  |   |   |   |       |   |   |   |   |   |   |  |  |   |   |   |   |  | i   |

|---------------------|-------|--|---|---|---|-------|---|---|---|---|---|---|--|--|---|---|---|---|--|-----|

| Abstract            |       |  |   |   |   |       |   |   |   |   |   |   |  |  |   |   |   |   |  | i   |

| Acknowledgements    |       |  |   |   |   |       |   |   |   |   |   |   |  |  |   |   |   |   |  | ii  |

| Contents            |       |  | • | • |   | <br>• | • | • | • | • | • | • |  |  | • | • |   | • |  | iii |

| List of Figures     |       |  | • | • |   | <br>• | • | • | • | • | • | • |  |  | • | • |   | • |  | vii |

| List of Definitions | <br>• |  |   |   |   |       |   | • |   | • | • |   |  |  |   |   | • | • |  | х   |

| Acronyms            | <br>• |  | • | • | • | <br>• | • | • | • | • | • | • |  |  |   | • | • | • |  | xi  |

| 1        | Intr | oducti | ion                                               | 1  |

|----------|------|--------|---------------------------------------------------|----|

|          | 1.1  | Thesis | and Research Questions                            | 5  |

|          | 1.2  | Contri | ibutions                                          | 7  |

|          |      | 1.2.1  | Publications                                      | 10 |

|          | 1.3  | Struct | ure of this Dissertation                          | 11 |

| <b>2</b> | Bac  | kgrour | nd                                                | 13 |

|          | 2.1  | A Side | e-note on Terminology                             | 13 |

|          | 2.2  | Comp   | onent-based Design                                | 15 |

|          | 2.3  | Perma  | nent Blocking and Deadlocks                       | 16 |

|          | 2.4  | Cyber  | -physical Systems                                 | 19 |

|          | 2.5  | Comm   | nunication in Cyber-physical Systems              | 20 |

|          |      | 2.5.1  | Communication Coupling in Time                    | 21 |

|          |      | 2.5.2  | Communication Coupling in Space                   | 22 |

|          |      | 2.5.3  | Communication Coupling in Synchronisation         | 22 |

|          | 2.6  | Coord  | ination Languages                                 | 23 |

| 3        | PN   | SC wit | h SIA - An Analysable Event-based Component Model | 25 |

|          | 3.1  | Proces | ss Networks with Synchronous Communication (PNSC) | 25 |

|          | 3.2  | Synch  | ronous Interface Automata (SIA)                   | 28 |

|          |      | 3.2.1  | Definition of SIAs                                | 28 |

|          |      | 3.2.2  | Composition of SIAs                               | 30 |

|          |      | 3.2.3  | Relation of a SIA to its Process                  | 31 |

|          |      | 3.2.4  | Interaction of SIAs                               | 33 |

|          | 3.3  | Model  | ling a Crossroad with SIAs                        | 37 |

|          |      | 3.3.1  | Streaming Network with Buffered Communication     | 41 |

|          | 3.4  | Chapt  | er Summary                                        | 43 |

| <b>4</b> | Miz  | ced-criticality PNSCs and Time-based Processes                              | <b>44</b> |

|----------|------|-----------------------------------------------------------------------------|-----------|

|          | 4.1  | Communication Decoupling of PNSCs                                           | 45        |

|          |      | 4.1.1 Decoupling PNSCs in Time                                              |           |

|          |      | 4.1.2 Decoupling PNSCs in Synchronisation                                   |           |

|          |      | 4.1.3 Decoupling PNSCs in Time and Synchronisation                          |           |

|          | 4.2  | Time-based Component Model of PNSCs                                         | 51        |

|          |      | 4.2.1 Time-triggered Processes in a PNSC                                    | 52        |

|          |      | 4.2.2 Rate-bounded Communication                                            | 55        |

|          |      | 4.2.2.1 Rate-control with the MIRT protocol                                 | 57        |

|          |      | 4.2.2.2 Rate-control with the buffered MIRT protocol                        |           |

|          |      | 4.2.2.3 Rate-control with the PBRT protocol                                 | 59        |

|          |      | 4.2.2.4 Rate-control with the buffered PBRT protocol                        | 59        |

|          | 4.3  | Message Semantics                                                           | 60        |

|          | 4.4  | Cross-criticality Interfaces                                                | 63        |

|          |      | 4.4.1 Mixed-criticality Network with CCIs                                   | 64        |

|          | 4.5  | Discussion                                                                  | 66        |

|          | 4.6  | Chapter Summary                                                             | 67        |

|          |      |                                                                             |           |

| <b>5</b> |      | manent Blocking Analysis of PNSCs with SIAs                                 | 69        |

|          | 5.1  | Permanent Blocking of SIAs                                                  |           |

|          |      | 5.1.1 Permanent Blocking Analysis                                           |           |

|          |      | 5.1.1.1 Permanent Blocking Analysis with Acyclic SIAs                       |           |

|          |      | 5.1.1.2 Permanent Blocking Analysis with Cyclic SIAs                        |           |

|          |      | 5.1.1.3 Permanent Blocking Analysis on an Assembly of Processes             |           |

|          |      | 5.1.2 Deadlock Analysis                                                     | 75        |

|          | •    | 5.1.2.1 Deadlock Analysis on an Assembly of Processes                       |           |

|          | 5.2  | Implementation of the Permanent Blocking Analysis                           |           |

|          |      | 5.2.1 Algorithm to Compute $Sys(s)$                                         |           |

|          | ۳۵   | 5.2.2 Algorithm to Compute $dl((N_1, \ldots, N_n), s) \ldots \ldots \ldots$ |           |

|          | 5.3  | Chapter Summary                                                             | 83        |

| 6        | Stre | eamix - An Instantiation of PNSCs as a Coordination Language                | 85        |

|          | 6.1  | Coordination Model                                                          | 86        |

|          |      | 6.1.1 Computational Components                                              | 87        |

|          |      | 6.1.2 Routing Network                                                       | 87        |

|          |      | 6.1.3 Extra-functional Requirements Layer                                   | 88        |

|          | 6.2  | Box Abstraction                                                             | 88        |

|          |      | 6.2.1 User-defined Boxes                                                    | 88        |

|          |      | 6.2.2 Implicit Boxes                                                        | 89        |

|          |      | 6.2.2.1 FIFO Buffers                                                        | 90        |

|          |      | 6.2.2.2 Routing Node                                                        | 91        |

|          |      | 6.2.2.3 Temporal Firewall                                                   | 93        |

|          |      | 6.2.2.4 Rate-control Guard                                                  | 93        |

|          |      | 6.2.3 Interaction Protocol of a User-defined Box                            | 93        |

|          |      | 6.2.4 Box Annotations and Grammar                                           | 95        |

|          | 6.3  | Nets: Instantiations of Boxes                                               | 96        |

|          |      | 6.3.1 Flow Direction Ambiguities                                            | 97        |

|   |                | 6.3.2   | Self-loop Connection                                   | 99  |

|---|----------------|---------|--------------------------------------------------------|-----|

|   |                | 6.3.3   | Side-port Connection                                   | 99  |

|   |                | 6.3.4   | Net Interface                                          | 101 |

|   |                | 6.3.5   | Net Declaration and Prototyping                        | 101 |

|   | 6.4            | Netwo   | ork Composition                                        |     |

|   |                | 6.4.1   | Net Assignments                                        |     |

|   |                | 6.4.2   | Serial Composition                                     |     |

|   |                | 6.4.3   | Parallel Composition                                   |     |

|   |                | 6.4.4   | Operator Precedence                                    |     |

|   |                | 6.4.5   | Time-controlled Nets                                   |     |

|   |                | 6.4.6   | Wrapper                                                |     |

|   | 6.5            |         | ibing a Cyber-physical System with Streamix            |     |

|   | 6.6            |         |                                                        |     |

|   | 6.7            |         | ser Summary                                            |     |

|   | 0.7            | Unapt   |                                                        | 119 |

| 7 | Too            | lchain  | for Streamix                                           | 120 |

|   | 7.1            | The S   | treamix RTS Library                                    | 123 |

|   |                | 7.1.1   | Implementation of Computational Components             | 124 |

|   |                | 7.1.2   | Implementation of Channels                             | 126 |

|   |                |         | 7.1.2.1 Implementation of Time-triggered Communication | 129 |

|   |                |         | 7.1.2.2 Implementation of Rate-bounded Communication   | 131 |

|   |                |         | 7.1.2.3 Implementation of Routing Nodes                | 132 |

|   | 7.2            | SMXC    | - The Streamix Compiler                                | 134 |

|   |                | 7.2.1   | The Streamix Context Checker                           | 135 |

|   |                | 7.2.2   | Generation of Dependency Graph                         |     |

|   |                | 7.2.3   | Generation of Interaction Protocol Descriptions        |     |

|   | 7.3            | smxrt   | tsp - The Streamix RTS Preprocessor                    |     |

|   | 7.4            |         | ia - The Permanent Blocking Analysis                   |     |

|   | 7.5            |         | ssion                                                  |     |

|   |                | 7.5.1   | Scheduler of the Streamix RTS                          |     |

|   |                | 7.5.2   | Order of SIA Composition                               |     |

|   |                | 7.5.3   | Static and Pure Nets                                   |     |

|   | 7.6            | Chapt   | cer Summary                                            |     |

|   |                |         |                                                        | -   |

| 8 | $\mathbf{Rel}$ | ated W  | Vork                                                   | 147 |

|   | 8.1            | Interfa | ace Theory                                             | 147 |

|   | 8.2            | Mixed   | l-criticality Models                                   | 148 |

|   | 8.3            | Coord   | lination Models and Languages                          | 149 |

|   |                | 8.3.1   | S-Net                                                  | 150 |

|   |                | 8.3.2   | BIP                                                    | 151 |

|   |                | 8.3.3   | Giotto                                                 | 151 |

|   |                | 8.3.4   | Ptolemy and Ptides                                     | 152 |

|   | 8.4            | Deadle  | ocks and Permanent Blocking                            | 153 |

| - | ~              |         |                                                        |     |

| 9 |                |         | n and Outlook                                          | 156 |

|   | 9.1            |         | nary of the Dissertation                               |     |

|   | 9.2            | Discus  | ssion of the Results                                   | 157 |

| 9.3     | Outlook | <br> | ••• | <br> | <br> |  | <br> |  | <br> | <br>. 15 | 9 |

|---------|---------|------|-----|------|------|--|------|--|------|----------|---|

|         |         |      |     |      |      |  |      |  |      |          |   |

| Bibliog | raphy   |      |     |      |      |  |      |  |      | 17       | D |

# List of Figures

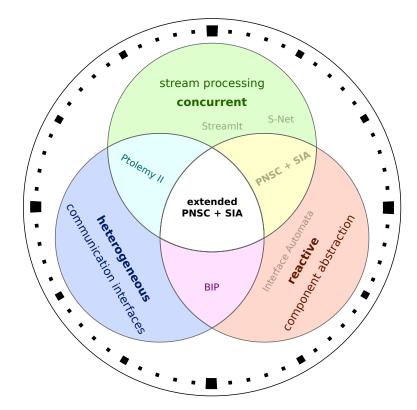

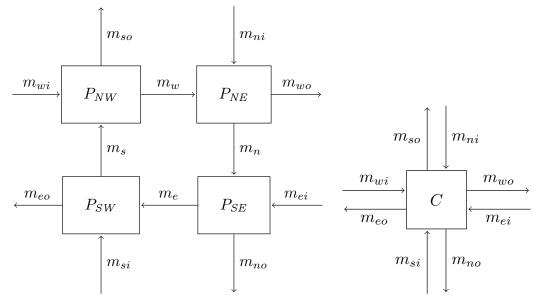

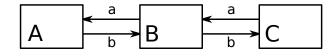

| 1.1          | A simple schematic representation of properties of CPSs and how the novel PNSC model bridges the gap between stream processing and LTS for complex componets.       | 9        |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $2.1 \\ 2.2$ | An example of gridlock on a crossing (no turning)                                                                                                                   | 17<br>18 |

|              |                                                                                                                                                                     | 10       |

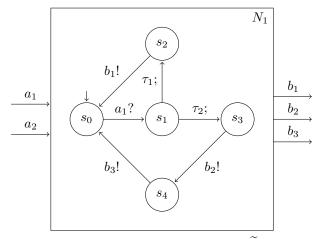

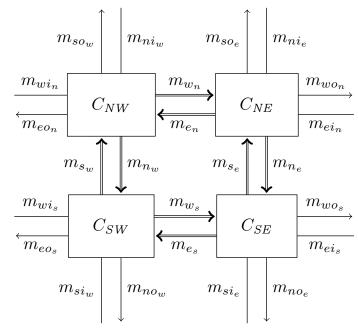

| $3.1 \\ 3.2$ | The PNSC network modelling the crossroad example depicted in Figure 2.1.<br>An example of a process $N_1$ where SIA $\tilde{N}_1$ describes the interaction pro-    | 27       |

| 3.3          | tocol of $N_1$                                                                                                                                                      | 32       |

| 3.4          | <i>a</i> is shared                                                                                                                                                  | 33       |

|              | actions $d$ and $e$                                                                                                                                                 | 34       |

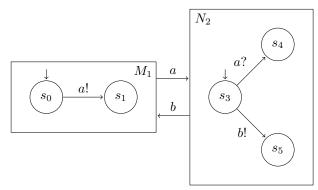

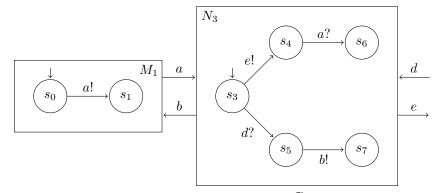

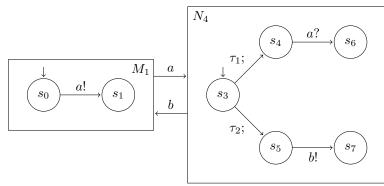

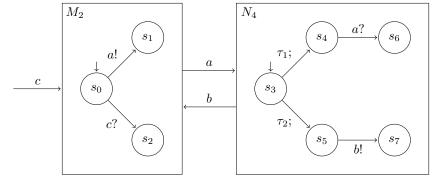

| 3.5          | An example of a PNSC where the SIA $\tilde{N}_4$ of process $N_4$ has the internal actions $\tau_1$ and $\tau_2$ .                                                  | 35       |

| 3.6          | An example of a PNSC with SIAs containing open actions, shared actions, ignored actions and internal actions.                                                       | 36       |

| 3.7          | The composed process $M_2N_4$ with its composed SIA $\widetilde{M_2N_4}$ as a result of the composition of the system depicted in Figure 3.6.                       | 36       |

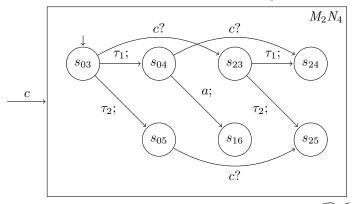

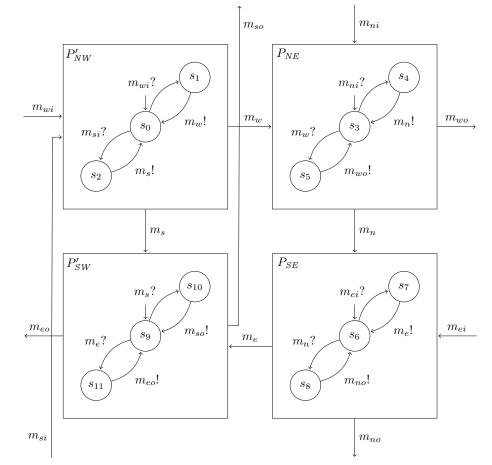

| 3.8          | A PNSC model of Figure 3.1 extended by the corresponding SIAs of each process. Due to the symmetry of the model, the system can potentially                         |          |

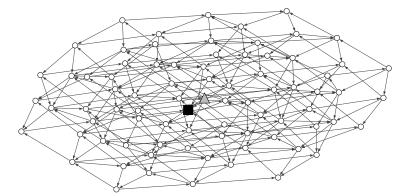

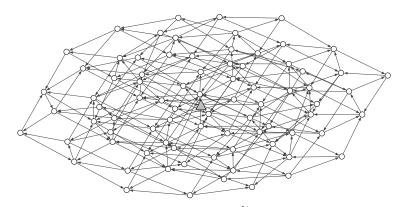

| 3.9          | reach a permanent blocking state — a deadlock, involving all four processes.<br>The graph representing the SIA $\tilde{P}_{res}$ . It consists of 80 states and 248 | 37       |

| 0.9          | transitions. The black square node represents a state where no further transitions are possible and the grey triangle node represents the initial                   |          |

|              | state                                                                                                                                                               | 38       |

| 3.10         | ) An example of an environment $\tilde{P}_{env}$ for the PNSC of Figure 3.8                                                                                         | 39       |

| 3.11         | 1 The resulting SIA $\widetilde{P}_{res} \otimes \widetilde{\widetilde{P}}_{env}$ when applying the environment $\widetilde{P}_{env}$ of                            |          |

|              | Figure 3.10 on the PNSC $P_{res}$ of Figure 3.8                                                                                                                     | 39       |

| 3.12         | 2 An adapted version of the crossroad model of Figure 3.8 that breaks the                                                                                           | 40       |

| 3.13         | symmetry and resolves the problem of permanent blocking                                                                                                             | 40       |

|              | transitions. The grey triangle node represents the initial state of the system                                                                                      | 41       |

|              |                                                                                                                                                                     |          |

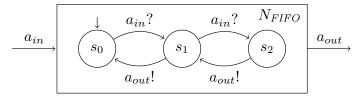

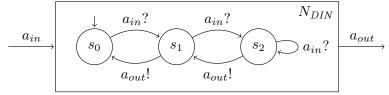

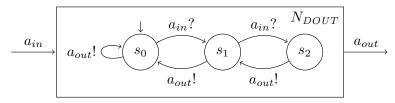

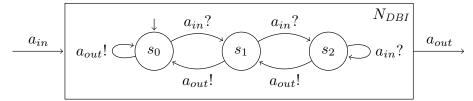

| 3.14         | An example of a process $N_{FIFO}$ and its corresponding SIA $\tilde{N}_{FIFO}$ , modelling a First-in, First-out (FIFO) buffer of length two with input $a_{in}$ and                                                                 | 4.1  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.15         | output $a_{out}$                                                                                                                                                                                                                      | . 41 |

| 3.16         | arrows) forming a streaming network                                                                                                                                                                                                   | . 42 |

|              | in Figure 3.15                                                                                                                                                                                                                        | . 43 |

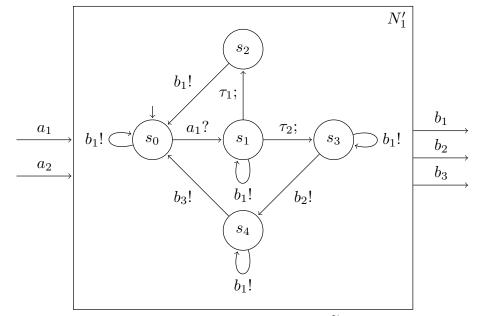

| 4.1          | An example of a process $N'_1$ where SIA $\tilde{N}'_1$ describes the interaction pro-<br>tocol of $N'_1$ with port $b_1$ decoupled in synchronisation.                                                                               | . 47 |

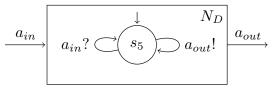

| 4.2          | An example of a decoupling process $N_D$ and its SIA $\tilde{N}_D$ with input $a_{in}$<br>and output $a_{out}$ .                                                                                                                      | . 48 |

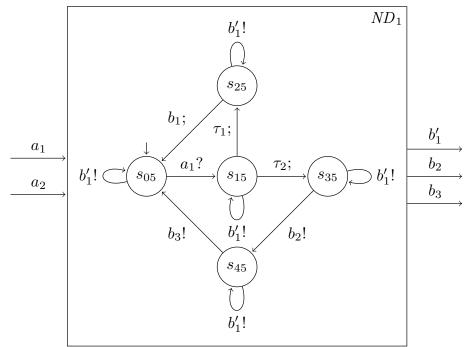

| 4.3          | The resulting abstract process $ND_1$ of the composition $N_1 \otimes N_D$ where<br>SIA $\widetilde{ND}_1 = \widetilde{N}_1 \otimes \widetilde{N}_D$ . SIA $\widetilde{ND}_1$ is syntactically equivalent to SIA $\widetilde{N}'_1$ , |      |

| 4.4          | depicted in Figure 4.1                                                                                                                                                                                                                | . 48 |

| 4.4          | input $a_{in}$ and an output $a_{out}$ .                                                                                                                                                                                              | . 50 |

| 4.5          | An example of a SIA, modelling a FIFO buffer of length 2 with input $a_{in}$ and a decoupled output $a_{out}$ .                                                                                                                       | . 51 |

| 4.6          | An example of a SIA, modelling a FIFO buffer of length 2 with a decoupled                                                                                                                                                             |      |

| 4.7          | input $a_{in}$ and a decoupled output $a_{out}$                                                                                                                                                                                       | . 51 |

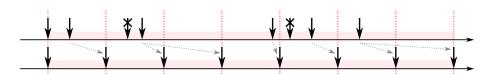

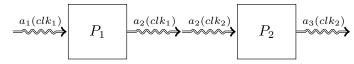

| 1.1          | line represents the arrival instances of message tokens and the lower time-<br>line represents the release instances of message tokens.                                                                                               | . 53 |

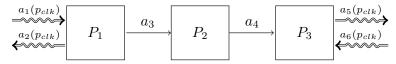

| 4.8          | A temporal firewall with a decoupled port pair $\langle a_{in}, a_{out} \rangle$ and a port $p_{clk}$ which is connected to a clock signal.                                                                                           | . 53 |

| 4.9          | An example of a time-triggered PNSC where the PNSC is decoupled<br>through temporal firewalls while processes inside the time-triggered PNSC                                                                                          | . 00 |

| 4 10         | trigger sporadically (e.g. process $P_2$ )                                                                                                                                                                                            | . 54 |

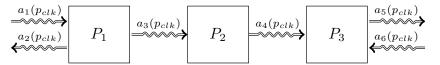

| 4.10         | An example of a time-triggered PNSC where each process in the PNSC is decoupled through temporal firewalls.                                                                                                                           | . 55 |

| 4.11         | An example of a time-triggered PNSC where each process in the PNSC is decoupled through a temporal firewall with a different clock rate each.                                                                                         | . 55 |

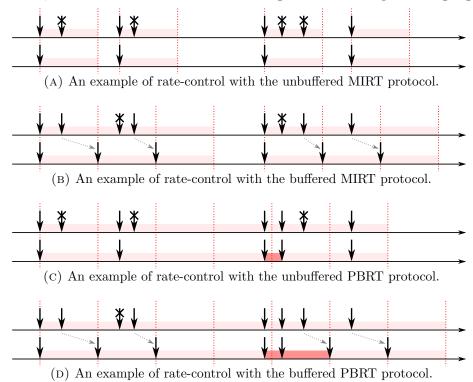

| 4.12         | Examples of rate-control protocols. In each figure the upper time-line represents the arrival instances of message tokens while the lower time-                                                                                       |      |

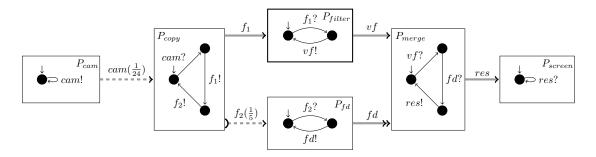

| 4.13         | line represents the release instances of message tokens                                                                                                                                                                               | . 60 |

|              | low critical process $P_{fd}$ towards the high criticality process $P_{filter}$                                                                                                                                                       | . 66 |

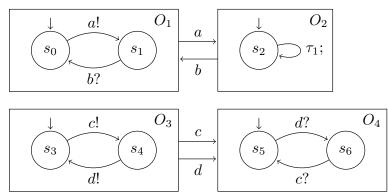

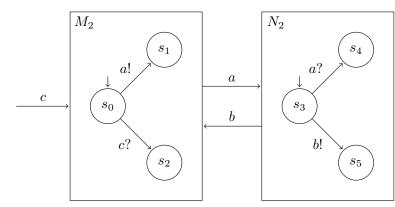

| $5.1 \\ 5.2$ | A PNSC formed of four processes, each described by a SIA with a cycle.<br>An example of a PNSC where the process $M_2$ is alive and process $N_2$ is                                                                                  | . 72 |

|              | lonely blocking in state $s_3 \in S_{\widetilde{N}_2}$                                                                                                                                                                                | . 76 |

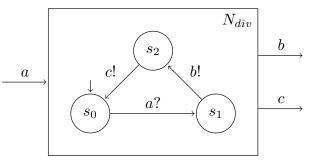

| 6.1          | An example of a diverging node with an input port $a$ and two output ports $b$ and $c$ .                                                                                                                                              | . 91 |

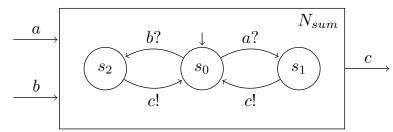

| 6.2          | An example of a summing node with input ports $a$ and $b$ and an output port $c$                                                                                                                                                      | . 92 |

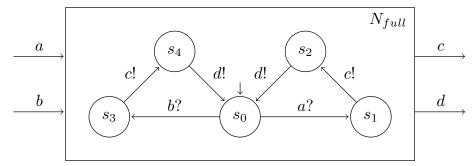

| 6.3   | An example of a routing node as combination of summing and diverging                                                                  | 0.0   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

|       | nodes with input ports $a$ and $b$ and output ports $c$ and $d$                                                                       | . 92  |

| 6.4   | An example of a simple network where three components are intercon-<br>nected with no obvious data flow direction.                    | . 97  |

| 6.5   | An example of an ambiguous flow direction. The net <i>B</i> can be connected<br>in four different ways                                | . 97  |

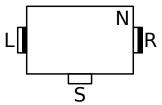

| 6.6   | Schematic representation of a <i>net</i> with the three optional port groupings left $(L)$ , right $(R)$ , and side $(S)$ .           | . 98  |

| 6.7   | The representation of the network of Figure 6.4 with the use of left and right collections.                                           | . 99  |

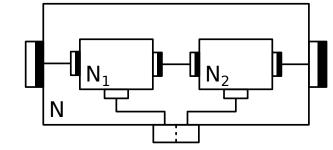

| 6.8   | Locality enforcing serial composition of two nets $N_1$ and $N_2$ , written as                                                        | . 55  |

| 0.0   | $N = N_1 \cdot N_2 \cdot \cdot$ | . 106 |

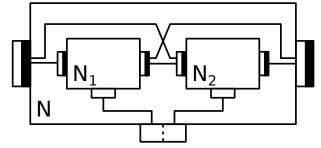

| 6.9   | A serial composition of two nets $N_1$ and $N_2$ , written as $N = N_1$ : $N_2$                                                       |       |

|       | where by<br>passing is allowed. $\ldots$                                                                                              | . 107 |

|       | Parallel composition of two nets $N_1$ and $N_2$ written as $N_1   N_2 \dots \dots$                                                   | . 109 |

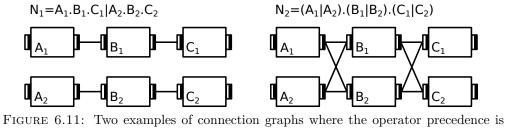

| 6.11  | Two examples of connection graphs where the operator precedence is il-                                                                |       |

|       | lustrated.                                                                                                                            | . 110 |

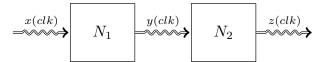

| 6.12  | A time-triggered instance of the box N1 and N2 where all channels are temporal firewalls with period $clk = 1s.$                      | 111   |

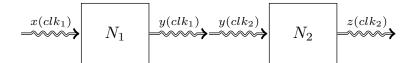

| 6 1 3 | A time-triggered instance of the box N1 and N2 where the channel $y$                                                                  | . 111 |

| 0.15  | is modelled by two temporal firewalls, with the periods $clk_1 = 1s$ and                                                              |       |

|       | $clk_2 = 2s$ , respectively                                                                                                           | . 112 |

| 6.14  | A schematic representation of the scoping mechanism where ports from                                                                  |       |

|       | any collection of the net ${\cal N}$ can be connected to ports from any collection                                                    |       |

|       | of the wrapper $W$                                                                                                                    | . 113 |

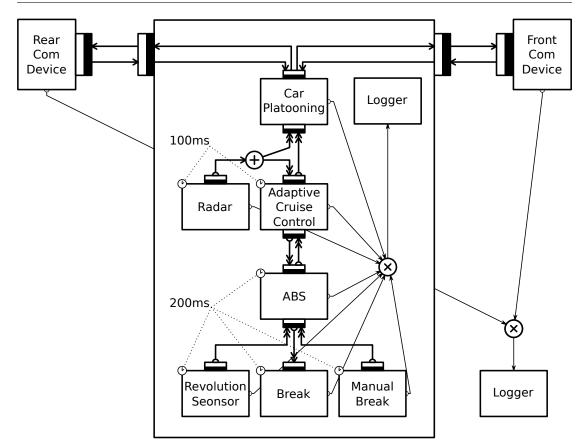

| 6.15  | Structured representation of the car platooning example                                                                               | . 116 |

| 6.16  | The Streamix program describing the car platooning application depicted                                                               | 1157  |

|       | in Figure 6.15                                                                                                                        | . 117 |

| 7.1   | A schematic overview of the toolchain for Streamix.                                                                                   | . 121 |

# List of Definitions

| 2.1 | Definition (Four Deadlock Conditions)                                    |

|-----|--------------------------------------------------------------------------|

| 3.1 | Definition (PNSC Process)                                                |

| 3.2 | Definition (Composed PNSC Process)                                       |

| 3.3 | Definition (SIA)                                                         |

| 3.4 | Definition (SIA composition operator $\otimes$ )                         |

| 4.1 | Property (Time-triggered Input)                                          |

| 4.2 | Property (Time-triggered Output)                                         |

| 4.1 | Definition (Semi-state Message)                                          |

| 4.2 | Definition (State Message)                                               |

| 4.3 | Definition (Event Message) 61                                            |

| 4.4 | Definition (Message Semantics of Communication Channel) 62               |

| 5.1 | Definition (Context of a process)                                        |

| 5.2 | Definition (Context of a SIA)                                            |

| 5.3 | Definition (Liveness of a SIA state)                                     |

| 5.4 | Definition (Liveness of a SIA)                                           |

| 5.5 | Definition (Liveness of a PNSC process)                                  |

| 5.6 | Definition (Liveness of a PNSC)                                          |

| 6.1 | Definition (Self-loop Connection)                                        |

| 6.2 | Definition (Side-port Connection)                                        |

| 6.3 | Definition (Net Interface)                                               |

| 6.4 | Definition (Connection of Serial Composition)                            |

| 6.5 | Definition (Net Interface of Locality Enforcing Serial Composition) 105  |

| 6.6 | Definition (Net Interface of Bypassing Serial Composition)               |

| 6.7 | Definition (Net Interface of Deterministic Parallel Composition) 108     |

| 6.8 | Definition (Net Interface of Non-deterministic Parallel Composition) 109 |

## Acronyms

- **AST** Abstract Syntax Tree. 135

- **BIP** Behaviour, Interaction, Priorities. 151, 154, 160

- CCI Cross-criticality Interface. 7, 8, 20, 45, 63, 68, 89, 119, 149, 157, 159

- CFS Completely Fair Scheduler. 145

- **CPS** Cyber-physical System. i, vii, 1–9, 11, 13, 15, 19, 20, 23, 24, 44, 46, 85, 87, 90, 97, 108, 115, 118, 119, 145, 149, 150, 154, 156, 158, 159

- **CSP** Communicating Sequential Processes. 4, 155

- DAG Directed Acyclic Graph. 71, 81

- **DFS** Depth-first Search. 81

- EDF Earliest Deadline First. 145

- **FIFO** First-in, First-out. viii, 41, 42, 46, 49–51, 53, 57, 63, 90, 91, 93, 112, 120, 122, 124, 126, 127, 142, 143, 150, 151, 155

- GML Graph Modelling Language. 139, 141

- **IA** Interface Automaton. 3, 16, 147, 148, 153, 157, 159

- **IIOA** Interface Input/Output Automaton. 148

- IOA Input/Output Automaton. 147, 148

- **IOT** Internet of Things. 13, 15

- **KPN** Kahn Process Network. 3, 21, 67, 150, 152

- **LET** Logical Execution Time. 24, 152

- LTS Labelled Transition System. i, vii, 3, 6, 8, 9, 38, 83

- MIMO Multiple Input, Multiple Output. 26, 88

- MIOA Modal Input/Output Automaton. 148, 153

- MIRT Minimal Inter-release Time. 56–60, 132

- MoC Model of Computation. 152

- MPI Message Passing interface. 4

- NoC Network on Chip. 67

- PBRT Period-bounded Release Time. 56, 59, 60

- PNSC Process Network with Synchronous Communication. i, vii, viii, 3, 5, 8–11, 13, 25–28, 33–37, 39, 41–47, 52–55, 60, 65–67, 70–77, 80, 83, 85, 88–90, 119, 120, 129, 131, 142, 143, 145, 148, 149, 151, 152, 154, 156–161

- **RTS** Run-time System. i, 10, 11, 67, 93, 95, 120, 121, 123–125, 127–129, 131, 132, 141–146, 157, 158, 161

- **SDF** Synchronous Data Flow. 21, 152

- SIA Synchronous Interface Automaton. i, vii, viii, 2, 3, 6–11, 25, 28–43, 47, 48, 50, 51, 53, 67, 69–80, 82–84, 88–92, 94, 95, 120, 121, 123, 134, 135, 140–145, 148, 151, 156–161

- SISO Single Input, Single Output. 150

- TTA Time-triggered Architecture. 21, 52, 69, 149

- WCET Worst-case Execution Time. 20, 52, 54, 67, 145, 160

- XML Extensible Markup Language. 139

## Chapter 1

# Introduction

Nowadays, with microcontrollers getting smaller and more efficient, computing is becoming more and more pervasive in our everyday life. This is achieved by embedding computer devices in physical objects such that the computing devices interact with the physical world. Such systems are called Cyber-physical Systems (CPSs). A CPS is a reactive system that senses its environment (the physical world), performs a computation on a computational entity (this can be anything from a simple embedded device to a large scale distributed system), and then actuates on the environment according to the computations. The actuation on the environment causes the environment to change which, in turn, is detected by the sensors and the computation is performed with the new dataset. Typically, this reactive loop is time-critical and is executed as long as the system is running. In contrast to a traditional embedded system, i.e. a time-critical system, dedicated to a single hardware platform, a CPS tends to be an assembly of networked subsystems where some subsystems interact with the physical world and some may be purely computational.

Examples of CPSs can be found in the domain of automotive vehicles (e.g. anti-lock braking system, adaptive cruise control, electronic stability control, platooning), avionic vehicles (e.g. flight control systems, black box, pressure control), or smart spaces (e.g. intelligent highway control, building control), to name only a few.

Because of the direct interaction of CPSs with the physical world, it is often crucial to respect timing requirements imposed by the physical world to guarantee a correct behaviour of the system. In case of critical applications such as nuclear power plants, avionic systems, or cars, huge efforts are made to verify the correct behaviour of the application. The main difference between critical systems and best-effort systems is that critical systems are designed for the worst case whereas best-effort systems are designed for the average case. Henzinger and Sifakis argue that over time, this difference led to a gap between the models employed in the two domains and that the gap is continuing to widen [1]. Due to the difference of the employed models, critical and non-critical applications tend to be physically separated and run on dedicated hardware platforms. This is a problem because with the evolution of hardware towards multi/many-core architectures, there is the interest to integrate components with different criticality requirements on the same platform. Such systems are typically called mixed-criticality systems [2]. What adds further to the challenge of integrating CPSs on a multi/many-core architecture is that CPSs are often heterogeneous in the sense that several applications from different domains with different characteristics must coexist or interact with each other [3]. Eker et al. address this challenge by assembling multiple models, each suitable for its specific application domain, in one framework [3]. Others argue that one meta model, allowing to describe and compose heterogeneous systems, is more beneficial because it provides a better ground for a meaningful analysis of the system [1, 4, 5].

Another challenge is the inherent concurrency of CPSs [6]. Streaming networks are well-recognised for coping with concurrent systems [7]. They consist of processing nodes (often called filters) connected via communication channels where a channel is connected to a single producer node and a single consumer node. This property of streaming networks, combined with the implicit synchronisation of producers and consumers due to a blocking channel access, allows to tame the complexity of concurrent systems which makes them also an interesting paradigm to apply to CPSs. However, current streaming models (e.g. [8–10]) tend to rely on the possibility that a system can be decomposed into transformational components such that the behaviour of a component can be described as a pure function. Such a decomposition makes it easier to understand component dependencies and allows to analyse the system, e.g. for schedulability [11] or deadlocks [12]. However, given that CPSs are often systems of reactive nature, such a decomposition is difficult [13].

An interesting approach where no decomposition in transformational components is required are interface theories [14] which allow to describe components with arbitrary behaviour by their interfaces and build complex components out of simple ones by composition. Several interface models have been proposed to describe communication compatibility between components [15–17] as well as additional properties such as modalities [18], resource usage [19, 20], or timing constraints [21, 22]. However, these models do not target streaming networks and lack the capability of describing the blocking semantics of message passing in streaming networks.

In this dissertation I introduce a novel automata-based interface description model, called Synchronous Interface Automaton (SIA), that allows to describe the interaction

protocol of processes with their environment. SIAs are suitable to describe the blocking semantics of Kahn Process Network (KPN)-based [23] streaming networks and thus serve as a powerful tool to bridge the gap between Labelled Transition System (LTS) and stream processing. An incremental composition operation allows to build complex processes out of simple ones. A novelty of the SIA model is that it allows to identify permanent blocking situations (e.g. deadlocks) in a composed network due to the blocking semantics of the model. The inspiration for the SIA model stems from Interface Automata (IAs) [15]. The blocking semantics of the here presented SIAs differs fundamentally from the blocking semantics of IAs. This enables SIAs to describe process networks where processes interact with synchronous communication, e.g. stream processing applications.

I further introduce a novel component-based model, called Process Network with Synchronous Communication (PNSC) that serves as a wrapper for SIAs and allows to model an assembly of reactive processes, i.e. processes capable of consuming and producing streams of infinite length. I extend the model to support the coexistence and interaction of processes with an event-triggered and a time-triggered execution scheme. In the former case, sporadically occurring events are causing a subsystem to perform its computation while in the latter case a fixed schedule imposes time instances when a subsystem is performing its computation. There are application domains where both models are required (e.g. automotive domain) but the two models are often used in limited ways to just co-exist but do not directly interact with each other (e.g. [24–26]). The problem is that interaction may cause interference from a subsystem of low criticality towards a subsystem of high criticality which must be avoided. A novelty of the extended PNSC model is that it allows not only the co-existence of the two triggering semantics in the same system but also allows interaction between time-triggered subsystems and event-triggered subsystems. The key point is to guarantee that the event-triggered subsystem, having a lower criticality level, is not interfering with the time-triggered subsystem of higher criticality. Further, the model allows to use the same mechanism to avoid interference from a lower critical event-triggered subsystem to a higher critical event-triggered subsystem. Two time-triggered subsystems do not interfere with each other out of construction [27], independent of their criticality level.

To provide control on communication bandwidth usage, the model allows to limit the communication rate of a process to an upper bound. This is achieved with a novel approach of controlling message passing between processes with different consequences depending on the message semantics.

A challenge related to the inherent concurrency of CPSs is the efficient execution of concurrent systems on multi-core hardware platforms. With the ever growing capabilities of integrated circuits due to the persistence of Moore's law, software engineers face the challenge to design, develop, and maintain complex software systems that exploit the available computation power. As a consequence of reaching the power wall through frequency scaling [28], parallel hardware architectures have been designed. Even in the domain of embarrassingly parallelisable applications where it is easy to split the computation load in a large number of independent computational chunks due to lack of data or code dependencies, parallelization remains not a simple task because of the tight coupling between hardware and software (e.g. efficient use of memory hierarchy) and the inherent difficulty of debugging parallel code. Nowadays, there are tools, libraries, and languages available that help to cope with some of the problems. In the domain of Big Data on large scale distributed systems examples are Hadoop<sup>1</sup>, HPCC<sup>2</sup>, and Hydra<sup>3</sup>. For shared memory multi-core architectures some examples are Cuda<sup>4</sup>, OpenMP<sup>5</sup>, and TBB<sup>6</sup>.

However, multi- and many-core processor architectures have emerged to a broad variety of application fields, including CPSs, where it is hard to identify potential blocks that can exhibit parallelism due to dependencies between tasks and, especially, due to the reactive nature of CPSs. In their survey on programming solutions for multicore architectures in the domain of CPSs, Castrillon et al. note that even though achievements were made in academia, in industry, CPS software development for parallel architectures remains mostly manual [5]. A reason for this is that industry often relies on legacy code that may include system libraries or multiple layers of mixed languages which is often ignored by academic solutions (e.g. introducing a new language requires industry to rewrite lots of legacy source code in the new language which they may be hesitant to do).

To cope with concurrency in applications, programming languages either incorporate models (e.g. Actor model [29] in Scala, Communicating Sequential Processes (CSP) [30] in Ada) or libraries are provided (Open Message Passing interface (MPI) [31]) to simplify design, development, and maintainability of the application. While such models certainly help to structure the code and enforce good practices in parallel programming, it is still up to the programmer to separate between coordinational and computational aspects of the program. While an expert in a certain application domain - a *domain expert* - is very adept in solving problems and working with models related to this domain, it is rarely his or her expertise to cope with the inherent problems of concurrency and parallelization.

<sup>&</sup>lt;sup>1</sup>http://hadoop.apache.org/

<sup>&</sup>lt;sup>2</sup>https://hpccsystems.com/

<sup>&</sup>lt;sup>3</sup>https://github.com/addthis/hydra

<sup>&</sup>lt;sup>4</sup>http://www.nvidia.com/object/cuda\_home\_new.html

<sup>&</sup>lt;sup>5</sup>http://www.openmp.org/

<sup>&</sup>lt;sup>6</sup>https://www.threadingbuildingblocks.org/

An interesting approach to solve this problem is to separate the different concerns of an application, as proposed by Gelernter and Carriero in [32]. The main idea is to separate the concerns of computation and coordination by using a coordination language in addition to a programming language. This allows the domain expert to choose a language that suits his needs to program computational blocks which are then linked together, potentially by another person, using a coordination language based on a model that is suitable to cope with concurrency. This clear separation of concerns is an intriguing concept, especially for interdisciplinary application fields where experts from different domains work together. As CPSs tend to describe applications in interdisciplinary fields, a clear separation of concerns is desirable.

In this dissertation I introduce a new coordination language, called Streamix, that is based on the PNSC model, also introduced in this thesis. While Streamix is an instantiation of the PNSC model, the language provides more than just concrete syntax for the model: Streamix allows to describe a network of processes in a structured and hierarchical manner due to its usage of network composition operators. This is inspired by the coordination language S-Net [10] which allows to describe networks of pure components. The novelty of Streamix is that while it is based on the stream processing paradigm it retains the capability of describing CPSs where components are hard to decompose due to the reactive nature of CPS. Streamix is an exogenous coordination language where the coordinated components are unaware of the coordination exert on them [33].

This dissertation describes a holistic approach, reaching from the underlying theory of the coordination model to an instantiation of the model in the form of a language and a prototype toolchain that allows to compile Streamix code into an executable C program, check the program for permanent blocking, and link it with C implementations of PNSC processes. The resulting application can be executed on a platform with support for ISO C, POSIX threads, and a Linux operating system.

### 1.1 Thesis and Research Questions

In this section I present the thesis this dissertation aims to maintain and several research questions that guided me through my research. As described in the beginning of this chapter, my work aims at using models from different fields, namely stream processing and interface theory, and adapt the models in such a way that they are applicable for CPSs. Consequently, I formulate my thesis as follows:

It is possible to bridge the gap between stream processing and Labelled Transition Systems (LTSs) for complex components.

In the following I will describe several research questions that focus on sub-aspects of the thesis and help to dissect each aspect independently. I first ask a general question about coordination models to then refine it with three more precise questions:

#### How to coordinate mixed-criticality CPSs?

To answer this question, as a first step, it is crucial to identify properties of CPSs and understand how they relate to coordination aspects. A mixed-criticality CPS is an assembly of networked subsystems with strong and weak coupling between them. Some of the subsystems are critical systems, i.e. of high criticality, some are best-effort systems, i.e. of low criticality. The coupling between the different subsystems is of various degrees. Critical subsystems tend to have a weak coupling with other subsystems to prevent mutual interference while best-effort systems tend to be strongly coupled. A coordination model for a mixed-criticality CPS must be able to model these various degrees of coupling between subsystems while providing guarantees of correctness of the overall behaviour of the system.

To refine the research question I ask two follow-up questions centring around the coupling of subsystems. A third follow-up question focuses on coordination languages and the implication of reactive components on a language.

### What are suitable interfaces for reactive components with strong coupling to ensure correct behaviour of a system of such components assembled in a network?

A main property of a component that supports reactive behaviour is that it must be able to cope with infinite streams, i.e. potentially run infinitely. Due to this property, a component must support to read an input as a reaction to writing an output. This is because of a potential coupling between the output and the input through the environment. This must be reflected in the interface describing the component. In this dissertation I introduce the automata-based model SIA that allows to describe the interaction of a component with its environment. SIAs are based on a strict blocking semantics, modelling synchronous communication, which allows to describe streaming applications and their inherent strong coupling between components. The SIA model allows the composition of simple components into more complex ones while preserving the blocking semantics. I further introduce an analytic method, based on the SIA model, to detect situations where components are blocking indefinitely, e.g. deadlock situations.

# What are suitable interfaces for CPSs to integrate subsystems with different criticality levels?

In contrast to a strong coupling, addressed in the previous question, a weak coupling allows to ensure the system correctness based on the component correctness. The focus of this question lies on the interaction of subsystems with different degrees of coupling. A main challenge of a mixed-criticality system is to allow multiple subsystems with different criticality levels to co-exist on the same platform or even to interact with each other. The challenge of such a configuration is to assure that the subsystems with lower criticality levels do not interfere with subsystems of higher criticality levels. In this dissertation I introduce Cross-criticality Interfaces (CCIs) that allow to selectively implement a weak coupling between two components and prevent such an interference.

### What are the implications of reactive components on an exogenous coordination language?

The interaction of subsystems in a CPS is often based on reactive data processing where the environment imposes a link between the inputs and outputs of the component. A reactive component is hard to decompose because reactive components tend to rely on persistent state and internal synchronisation points. Due to this, simple and intuitive language primitives are required to describe reactive communication patterns in a structured way, such as chained components with mutual bi-directional interaction, without loosing in terms of locality. I adopt the notion of network operators to describe a network of reactive components. Different types of operators allow to describe a network in a structured and hierarchical manner by keeping information local.

### **1.2** Contributions

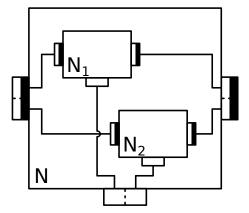

To illustrate the contribution of this dissertation, Figure 1.1 provides a simplistic overview of related work and the gap between research fields that this dissertation aims to bridge. In the figure, three circles represent three aspects that tend to be part of a CPS. Each circle is associated with a model that allows to describe particular properties of each aspect and tackle the challenge they pose for modelling CPSs.

• CPSs tend to be *concurrent* due to the fact that they interact with the physical world which is inherently concurrent [6]. In this work, concurrency aspects are

tackled with a stream processing model which provides inherent synchronisation between interacting components.

- CPSs tend to be *heterogeneous* with respect to multiple aspects such as mixedcriticality [2], different timing semantics [34], or different underlying theoretical models [3]. In this dissertation I focus on mixed-criticality aspects and different timing semantics and use well defined communication interfaces, called CCIs, to control the interaction between components.

- CPSs tend to be *reactive* systems with complex interacting components which are hard to decompose [13]. In order to support complex components in a stream processing model I introduce the novel SIA model, an analysable component abstraction.

Further, the figure shows a few examples of related work, prominent representatives of their domain, that are placed in the circles or the intersection of two circles to illustrate which aspects of CPSs are covered by their respective model. The symbolic dial, surrounding the three circles, represents the time-criticality aspect of CPSs. Of the represented models only the names that are not greyed-out support some sort of control over timing behaviour. The figure illustrates a clear gap between reactive systems with support for complex components and stream processing models. This gap is filled by the work presented in this dissertation, namely the PNSC model and the extension of the model.

The work described in this dissertation provides the following novelties and contributions:

- introduction of a novel exogenous, component-based coordination model, called PNSC, that allows to describe networks of processes, communicating through sporadic message passing. The novelty of the model is an LTS, called SIA, first introduced in this dissertation, that allows to capture the blocking semantics of interacting processes. The model allows to describe processes with persistent state and internal synchronisation points. These are properties that fit well with the requirements of CPSs which tend to be networks of reactive components. A composition operator allows to compose processes while preserving the properties of blocking communication.

- extension of the novel PNSC model. The extensions have no influence on the behavioural aspect of a process which preserves the exogenous coordination property of the PNSC model. The extensions provide support for

FIGURE 1.1: A simple schematic representation of properties of CPSs and how the novel PNSC model bridges the gap between stream processing and LTS for complex componets.

- mixed-criticality systems through selective communication decoupling to prevent unwanted interference between processes. The extension integrates seamlessly with SIAs which are used to describe the communication decoupling mechanism.

- multiple process execution schemes in a process network. This is achieved by using the communication decoupling mechanism in conjunction with clock signals to enforce a time-triggered process execution on a subset of processes. The model allows to enforce time-triggered communication on individual processes or on a network of processes.

- rate-controlled event-triggered communication. This is also achieved through selective communication decoupling. Two types of protocols are proposed, each applicable in a buffered and non-buffered situation, to enforce a limit on the communication rate.

- proposition of the novel message type *semi-state* which complements the well known message semantics of state messages and event messages in the context of stream processing.

- development of a novel static analysis, based on the interface theory with SIA, that allows to detect permanent blocking situations in the network. The analysis distinguishes between deadlock and lonely blocking situations.

- introduction of the novel exogenous coordination language Streamix. Streamix is an instantiation of the PNSC model. It allows to describe a network of complex reactive processes in a structured and hierarchical manner.

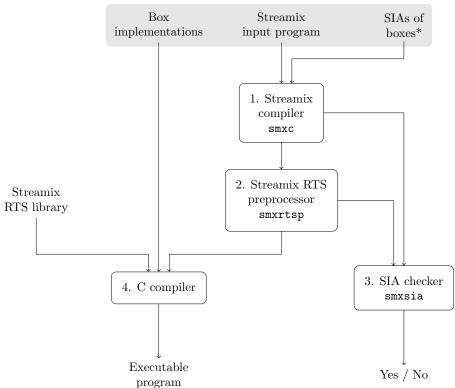

- development of a toolchain including a Run-time System (RTS), compiler, and permanent blocking checker that allows to produce executable applications by describing a system network by a Streamix program and linking it to individual C implementations and SIA descriptions of PNSC processes. The resulting application can be executed on a platform with support for ISO C, POSIX threads, and a Linux operating system.

#### 1.2.1 Publications

The following conference and workshop publications resulted from my research and have been published:

- Simon Maurer and Raimund Kirner. Coordination with Structured Composition for Cyber-physical Systems. In *Parallel Computing: On the Road to Exascale*, volume 27 of *Advances in Parallel Computing*, pages 615 624, Edinburgh, UK, September 2015. IOS Press. ISBN 978-1-61499-620-0. doi: 10.3233/978-1-61499-621-7-615

- Simon Maurer and Raimund Kirner. Cross-criticality Interfaces for Cyber-physical Systems. In Proc. 1st IEEE Int'l Conference on Event-Based Control, Communication, and Signal Processing, pages 1–8, Krakow, Poland, June 2015. IEEE. doi: 10.1109/EBCCSP.2015.7300670

- Raimund Kirner and Simon Maurer. On the Specification of Real-time Properties of Streaming Networks. In 18. Kolloquium Programmiersprachen und Grundlagen der Programmierung, Kärnten, Austria, October 2015

The following journal publication is ready for submission:

Simon Maurer, Raimund Kirner, and Olga Tveretina. Static Deadlock Analysis of Process Networks with Synchronous Interface Automata. *Ready for Submission*, 2017

#### **1.3** Structure of this Dissertation

The remainder of this dissertation is structured as follows:

- Chapter 2 provides background information on concepts I use throughout the dissertation and discusses terminology. The related topics are component-based design and more specifically interface theory, CPSs and their challenges, different communication models in CPSs, and coordination languages.

- Chapter 3 introduces the PNSC model that allows to describe networks of processes. The interaction of a process with its environment follows a clearly defined blocking semantics. In this chapter I further introduce the automata-based SIA model that allows to describe the interaction protocol of a process as its interface with its environment and I define a composition operator that allows to compose PNSC processes in arbitrary order.

- **Chapter 4** describes an extension to the PNSC model that allows to punctually loosen the communication coupling between interacting processes. This can be used to model mixed-criticality systems, based on a sporadic communication scheme to prevent undesired interference. The chapter further describes that, in conjunction with clock signals, the decoupling elements allow to construct temporal firewalls which can be used to change the sporadic communication model of a subset of processes to a time-triggered communication model. In this chapter I further introduce rate-control mechanisms to bound communication rates of processes to a maximum limit.

- Chapter 5 introduces a permanent blocking analysis that allows to identify permanent blocking situations in a PNSC. Further, the chapter introduces the distinction between deadlock situations and lonely blocking situations.

- **Chapter 6** describes the coordination language Streamix which represents an instance of the extended PNSC model. Streamix is an exogenous coordination language that allows to compose reactive components in a structured and hierarchical manner to form a network of processes.

- Chapter 7 describes a prototype of a toolchain for the coordination language Streamix. It includes the compiler for the Streamix language, the RTS preprocessor, the RTS, and the SIA model checker. Together, the tools allow to build an application that can be executed on a platform with support for ISO C, POSIX threads, and a Linux operating system.

- Chapter 8 compares the different aspects of my work with the state of the art. This includes interface theory, mixed-criticality models, coordination languages and models, and methods to detect or prevent permanent blocking situations.

- Chapter 9 finally concludes the dissertation and discusses the results and contributions of the thesis. It also includes directions for future research on this topic.

## Chapter 2

## Background

In this chapter I will discuss terminology and give some background on topics relevant for this dissertation.

The chapter is structured as follows: Section 2.1 discusses the term *real-time* and its ambiguous meaning in different research areas and relates embedded systems to Cyberphysical Systems (CPSs) and Internet of Things (IOT). Section 2.2 describes the basic idea of component-based design, the approach used as a corner stone for the Process Network with Synchronous Communication (PNSC) model proposed in this dissertation. I then describe properties of CPSs and discuss their relevance with respect to the design approach of CPSs in Section 2.4. Section 2.5 focuses on communication aspects such as the triggering semantics, i.e. time-triggered or event-triggered communication and communication coupling. Section 2.6 provides a short history on coordination languages and discusses classification aspects of coordination languages.

### 2.1 A Side-note on Terminology

Traditionally, a hard real-time system describes a system where the consequence of missing a deadline may result in a catastrophic event. Hence, the correctness criteria of a piece of software not only rely on the correctness of the result but also on the time of availability of the result. If the software provides a correct result but misses the deadline by doing so, the correctness criteria are not met. One tends to distinguish between hard real-time systems and soft real-time systems where the latter also imposes a deadline but the consequences of missing a soft deadline are less severe. By missing a soft deadline, the quality of the result only decreases but does not become useless.

There are two general points I want to make concerning the concepts of real-time systems. Firstly, I find that the distinction between best effort systems and soft real-time systems is only marginal and that a soft real-time system has much more in common with a best-effort application than with a hard real-time system. Ultimately, every system has a soft deadline because if a computation is never producing a result, the computation is hardly useful. Hence, technically, every system is a real-time system. However, there is a difference in terms of the usefulness of a result depending on when it is available. In the case of a best effort application, the expectation is that eventually a result will be available (before a non-specified deadline  $< \infty$ ) and the sooner it is available the better. With soft real-time systems, the expectation is put into numbers, meaning that the application is expected to deliver a result within a specified deadline and there is no immediate benefit if the result is available earlier. In contrast to a hard real-time system where the focus lies on giving *quarantees* to meet deadlines, in soft real-time systems no guarantees are given that a deadline is met. Rather, methods are used to decrease the possibility for deadlines to be missed. For example, in the case of a video stream application, buffers are used to store frames that resulted before the deadline in order to compensate during times when the deadline is missed.

The second point concerns the use of the term *real-time* which has an ambiguous meaning depending on the research community. Most commonly, in research, the term real-time describes the fact that an application has to respect a deadline, i.e. a result must be made available before a specified time limit has passed. However, I found that a lot of people, not necessarily researchers, associate the term real-time with simultaneously performing a computation as a direct reaction on events happening in the world, e.g. a football live stream, the logging of events while they are happening, the capturing and visualising of human motions while the human is performing the motions, etc. All these problems are probably designed and programmed, using in one way or another the notion of a deadline but the term real-time does not reflect that. Rather it reflects liveness of an application which creates, in my opinion, unnecessary confusion when explaining such problems to non-experts. Following the argument I made above that soft real-time and best-effort applications are more closely related than hard real-time problems are related to soft real-time problems, I advocate to use the term *time-critical* when talking about hard real-time problems. It immediately carries the message that time plays a critical part in such an application and avoids the confusion with live systems. Hence, throughout this dissertation I will use the term *time-critical* system when talking about a hard real-time system.

Time-critical systems are tightly coupled to the hardware they are running on. This is because the execution time of an application is dependent on the hardware architecture and to give guarantees that an application will meet the specified deadlines, it is important to fully understand the associated hardware architecture. Due to this, in the past, target hardware platforms for time-critical systems were often specialised boards fulfilling the exact requirements to provide the resource demands of the software application executed on the platform. As components on such boards were directly soldered on, such hardware boards were called *embedded systems* and the term became synonymous for hard real-time systems (or time-critical systems as I call them), including software and hardware components. With the evolution of hardware architectures, computational units were and still are becoming increasingly efficient and performant. Combined with the increasing demand for smarter, time-critical applications it often became necessary to build networked systems where not one single platform was used. Also, a lot of devices of today are embedded on a single board without necessarily hosting a time-critical system. Literally, the term *embedded system* only describes the technique of how a hardware board is assembled which is no longer an indication that the executed application is actually a time-critical system. Despite the potential confusion, the term *embedded* system is still used to describe a single platform, time-critical system. However, more complex systems, including multiple networked time-critical platforms, i.e. embedded systems, are referred to as Cyber-physical Systems (CPSs). The focus of the term CPS is put on the interaction between the physical and the cyber world through sensors and actuators.

Another term that relates to similar concepts is *Internet of Things (IOT)*. An IOT is an instance of the more general term CPS. It describes largely distributed applications where each "thing" represents a node in a network of interacting nodes.

Note that neither embedded systems, nor CPSs, nor the IOT must necessarily describe time-critical applications but as they interact with the physical world they generally do have timing constraints.

### 2.2 Component-based Design

Component-based design aims at separating concerns by dividing large systems into loosely coupled independent, concurrent components [39, 40]. This concept is a corner stone of a multitude of models, for example, in the area of stream processing [7] or coordination languages [41]. Typically, these models describe a composition of computational components that form a network. Linking structures, such as channels or shared memory locations, establishes connections between components. Such networks are usually explicitly constructed with the help of either a language (e.g. StreamIt [8] or S-Net [10] where networks are constructed by applying binary wiring operators on components) or a library (e.g. Open MPI [31] which provides an API to spawn channels linking components together). The question of compatibility between components is either inherently solved by construction of the language (S-Net only allows functional components and uses component signatures to check for compatibility) or is delegated to the programmer (Open MPI).

In component-based design, implementation details of components are often ignored and a component is represented by an abstraction. The key is to choose an abstraction that allows to describe the component accurately enough to expose certain properties while keeping the abstraction as simple as possible [39]. By composing simple components to build complexer ones, the properties exposed by the abstraction are used to check for compatibility of the components. Ideally, such a model supports heterogeneous systems and unifies the compatibility problem within one model [40]. In order for the programmer to be able to cope with concurrent systems, models have been proposed to check interoperability of components either by using an automata-based interface description of components such as Interface Automata (IAs) [15], causality interfaces [12], or transfer functions [20], to name only a few.

A specific aspect of compatibility of components is the liveness property of a system composed of components. A system is not guaranteed to be alive if a subset of the complete system or a subset of involved components can permanently block. A widely known case of permanent blocking is a deadlock situation [42].

In this dissertation I am interested in an automata-based approach to describe interfaces of components and use it to check for freedom of permanent blocking in the system. My approach is inspired by IAs but uses a different blocking semantics to make it suitable in the context of stream processing.

#### 2.3 Permanent Blocking and Deadlocks

In this dissertation I use the term *liveness* to describe whether a system is void of any blocking subsystems. I use the term *permanent blocking* as the opposite of *liveness*, i.e. to describe a system that has at least one blocking subsystem:

$$permanent\_blocking = \neg(liveness) \tag{2.1}$$

Permanent blocking must not necessarily be a deadlock. Coffman et al. identified four conditions that must hold simultaneously for a deadlock to occur [42]. These conditions are listed in Definition 2.1.

**Definition 2.1** (Four Deadlock Conditions). A system is in a deadlock situation if the following four conditions hold simultaneously:

- 1. Mutual exclusion: a task has exclusive control over a resource.

- 2. No pre-emption: a resource can only be released voluntarily by the task holding it.

- 3. Hold and wait: a task is holding at least one resource and is requesting at least another.

- 4. Circular wait: a task T<sub>1</sub> is holding a resource x and requests a resource y while a task T<sub>2</sub> is holding resource y and requests resource x. A circular wait is not necessarily limited to only two participants and can span over multiple parties.

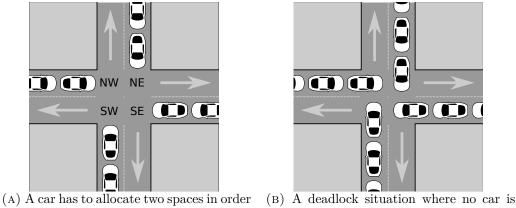

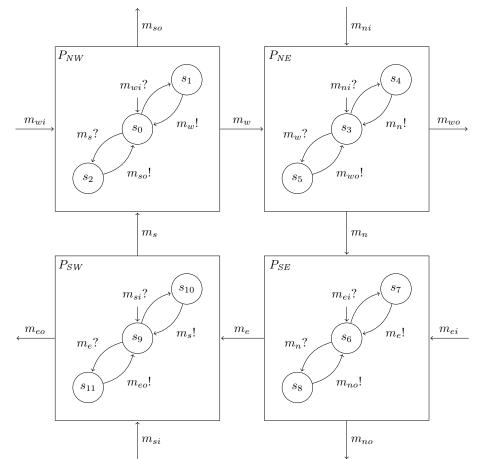

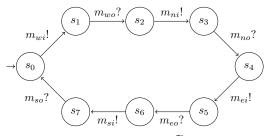

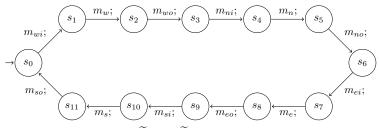

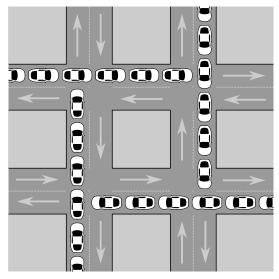

A practical example of a deadlock, or more specifically a gridlock, is illustrated in Figure 2.1. It depicts an intersection of two roads where cars are assumed to only drive straight ahead without turning. For a car, e.g. arriving from the West, to be able to cross the intersection, two spaces, e.g. NW and NE, have to be allocated. If traffic control allows to allocate spaces separately for cars arriving from each direction, the situation in Figure 2.1b can occur, where all spaces are occupied by an individual car such that no progression is possible for any car.

to advance. able to advance.

FIGURE 2.1: An example of gridlock on a crossing (no turning)

It is possible that in a system of multiple interacting processes only one process is permanently blocked while the rest of the system is processing without permanently blocking. If a process is blocking alone and no circular wait, as defined in Definition 2.1.4, is involved I call this process a *lonely blocker*. Hence, I distinguish between *deadlock* where multiple components block each other due to a circular wait and *lonely blocking* where one component is blocked by other components but is itself not causing other processes to block. Therefore I conclude that

$permanent\_blocking \neq deadlock$

and consequently with Equation 2.1 I conclude

$$deadlock \neq \neg(liveness)$$

However, deadlock implies permanent blocking, hence

$$deadlock \rightarrow permanent\_blocking$$

but permanent blocking does not necessarily imply deadlock:

```

\neg(permanent\_blocking \rightarrow deadlock)

```

Note that a permanent blocking process is either a lonely blocker or involved in a deadlock but not both.

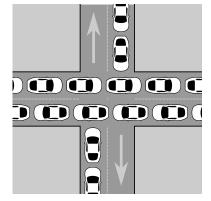

Using again the example of a road intersection I illustrate a permanently blocking system that is not in a deadlock situation but rather a lonely blocking situation in Figure 2.2. While cars from the East are able to progress to the West and vice versa, cars in the

FIGURE 2.2: A lonely blocking situation where progress is only possible from the East to the West and vice versa.

North and in the South are blocked and cannot progress. Assuming an infinite stream of cars and no priority rules, the cars from the North and the South will be blocked infinitely. Note that this blocking is not due to a circular wait condition, as defined in Definition 2.1.4, because the cars moving from East to West and vice versa are not blocked. Consequently, given that the system is in a permanent blocking situation without any deadlocks, the system is lonely blocking.

#### 2.4 Cyber-physical Systems

CPSs are systems that interact with the physical world through sensors and actuators. Because the actuation is usually a reaction to the sensing of the environment, CPSs are generally *reactive* and must often satisfy timing requirements.

Harel and Pnueli introduced the terms *transformational* and *reactive* to distinguish systems that are "relatively easy to develop from those that are not" [13]. In contrast to a transformational system that takes inputs, performs computation, and produces outputs, CPSs are often reactive systems where inputs are coupled to outputs via the environment. The output *out* of a transformational system, described by the function f, is dependent on the state *state* of the system and the input *in* to the system: