Article

# Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes

Giuseppe Schiavone <sup>1,\*</sup>, Jeremy Murray <sup>1,2</sup>, Richard Perry <sup>2</sup>, Andrew R. Mount <sup>2</sup>, Marc P. Y. Desmulliez <sup>3</sup> and Anthony J. Walton <sup>1</sup>

- <sup>1</sup> SMC, School of Engineering, University of Edinburgh, Edinburgh EH9 3FF, UK; jeremy.murray@pyreos.com (J.M.); anthony.walton@ed.ac.uk (A.J.W.)

- <sup>2</sup> School of Chemistry, University of Edinburgh, Edinburgh EH9 3FF, UK; richard.perry@ed.ac.uk (R.P.); a.mount@ed.ac.uk (A.R.M.)

- <sup>3</sup> School of Engineering & Physical Sciences, Heriot-Watt University, Edinburgh EH14 4AS, UK; m.desmulliez@hw.ac.uk

- \* Correspondence: giu.schiavone@gmail.com; Tel.: +44-131-650-5620

# Academic Editor: Fei Tang

Received: 9 February 2017; Accepted: 17 March 2017; Published: 22 March 2017

**Abstract:** This article presents a set of low-temperature deposition and etching processes for the integration of electrochemically deposited Ni-Fe alloys in complex magnetic microelectromechanical systems, as Ni-Fe is known to suffer from detrimental stress development when subjected to excessive thermal loads. A selective etch process is reported which enables the copper seed layer used for electrodeposition to be removed while preserving the integrity of Ni-Fe. In addition, a low temperature deposition and surface micromachining process is presented in which silicon dioxide and silicon nitride are used, respectively, as sacrificial material and structural dielectric. The sacrificial layer can be patterned and removed by wet buffered oxide etch or vapour HF etching. The reported methods limit the thermal budget and minimise the stress development in Ni-Fe. This combination of techniques represents an advance towards the reliable integration of Ni-Fe components in complex surface micromachined magnetic MEMS.

**Keywords:** Ni-Fe integration; Permalloy; MEMS; surface micromachining; selective etching; Ni-Fe electroplating; magnetic microactuators

# 1. Introduction

Electrochemically deposited alloys of nickel and iron (ECD Ni-Fe) are attractive materials for the fabrication of integrated magnetic microelectromechanical systems (MEMS) [1–4]. Although highly desirable for their large magnetic permeability and low coercivity [5–8], ECD Ni-Fe alloys are known to suffer from chemical deterioration when exposed to subsequent processing steps [9] and require therefore careful planning during the process integration stage.

Electroplating requires the preliminary deposition of a conductive seed layer that serves as a nucleation surface for the growth of the desired material through patterned moulds. Copper is one of the most commonly used seed layer materials, as it offers a balance between high conductivity, thus reducing non-uniformities caused by radial voltage drops on the wafer during electrodeposition, and ease of processing [10,11]. After electrodeposition, the mould is stripped and the exposed seed layer must be removed to electrically isolate the individual electroplated structures. To this end, wet etch processes are preferred to dry etching as the latter require expensive tools and possibly further masking. Conventional copper wet etchants are solutions based on  $(NH_4)_2S_2O_8$ ,  $HNO_3$ ,  $HCI/CuCl_2$  or  $HCI/FeCl_3$ . None of these chemicals is, however, selective enough to enable the copper to be removed while leaving Ni-Fe intact [12,13]. A method to selectively wet etch copper in the presence of structural

ECD Ni-Fe elements using conventional etchants is therefore desirable to facilitate the integration of soft magnetic elements in complex process flows while still employing standard techniques.

Moreover, when manufacturing MEMS devices with mechanically movable components such as microswitches and microactuators, surface micromachining is a key process that enables suspended and freestanding structures to be patterned and released [14]. To integrate moveable soft magnetic components based on ECD Ni-Fe in MEMS devices, it is necessary to develop robust sacrificial etch processes that preserve the integrity of the magnetic and other surrounding materials [15–19]. The release of freestanding structures in MEMS is usually the last step in the manufacturing process flow before packaging, as suspended elements make the devices significantly more sensitive to failure when subject to further processing [20]. For this reason, surface micromachining processes are often performed on complete devices that already incorporate all functional elements. It is therefore crucial to ensure sufficient etch selectivity between the sacrificial material of choice and the combination of other structural materials employed as functional device elements. Additionally, complex architectures require the patterning of sacrificial layers prior to surface micromachining, in order to allow for further processing step. Both the patterning and complete removal of sacrificial layers must therefore be fully compatible with Ni-Fe and the other structural materials.

Another key aspect that must be considered when integrating ECD Ni-Fe elements in MEMS process flows is the control of stress and stress gradients, as significant stress development is known to occur in Ni-Fe films during processing, especially when subject to high thermal loads [21–23]. Our group has previously reported on the increased levels of stress in ECD Ni-Fe when excessive heat is applied during processing [24–26], and identified the thermal budget as a critical obstacle to the integration of the alloys in MEMS devices. Constraints on the processing temperatures and times are therefore introduced, as excessive thermal loads can generate deteriorating levels of residual stress and stress gradient that may impair the functionality and integrity of the microfabricated devices [24,27].

The work reported herein addresses these fundamental challenges associated with the integration of ECD Ni-Fe in complex MEMS process flows. The article reports both a wet etching process to selectively remove the electroplating copper seed layer used as nucleation base for Ni-Fe, and a series of deposition and etching techniques that enable the patterning and release of freestanding Ni-Fe structures surrounded by silicon nitride structural dielectric, using silicon oxide as a sacrificial material that can be first patterned and then completely removed. All the processes developed in this study are run at temperatures below 200 °C, a limit defined based on previous work [25] to prevent excessive development of stress and stress gradients.

The ensemble of the methods presented herein provides a toolkit that aims at facilitating the integration of ECD Ni-Fe in complex MEMS architectures by using selective and low temperature deposition and etch processes.

The paper is organised as follows. Section 2 of the article presents an improved wet etch solution based on ammonium persulfate ( $(NH_4)_2S_2O_8$ ) that enables the selective removal of copper seed layers in the presence of electrodeposited Ni-Fe structures. Rotating pointer arm test structures are used to visually monitor the effects and completion of the etch process. The design and fabrication of the test structures are presented first, followed by the experimental details for the etching tests.

Section 3 of the article presents a short discussion on the choice of structural and sacrificial dielectric materials for surface micromachining. The development of low temperature deposition processes for structural silicon nitride and sacrificial silicon oxide films is then presented, followed by the details of a wet etch process based on Buffered Oxide Etch (BOE). This enables the patterning of relatively thick sacrificial silicon oxide ( $\sim 2 \mu m$ ) while preserving the integrity of structural silicon nitride dielectric elements.

Section 4 of the article completes the toolkit by presenting a complete surface micromachining process for the manufacturing of freestanding ECD Ni-Fe structures in the presence of silicon nitride as structural dielectric. The proposed method uses the low temperature silicon dioxide sacrificial material and silicon nitride structural material described in Section 3. The sacrificial layer is patterned by wet

etching first, and subsequently completely removed by means of a vapour hydrofluoric (HF) acid etch to avoid stiction. All the processes are limited to a maximum temperature of 200 °C, in order to minimise stress generation in Ni-Fe structures.

Finally, Section 5 closes the article by summing up the findings and providing some perspectives on the application of the results achieved.

## 2. Selective Copper Seed Etch

Test structures were produced on 3" silicon wafers to study the effects of different copper etching chemistries and tune the etching process for minimal Ni-Fe attack.

### 2.1. Test Structures

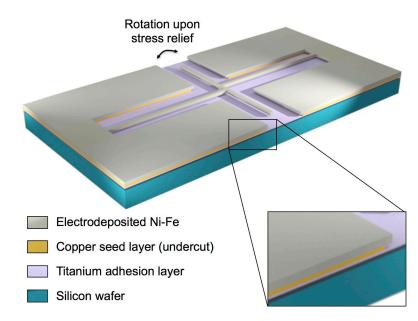

A conceptual drawing of the test structures used for this investigation is shown in Figure 1. Rotating structures of this kind are typically used as strain sensors [24,26,27], but they can also indicate the completion of the etch release process.

Figure 1. 3D diagram of the pointer arm microstructure used to characterise the copper seed layer etch.

The structure is fabricated by growing Ni-Fe through a patterned mould and comprises three elements: two parallel expansion arms and a transversal pointer arm. The two expansion arms (8  $\mu$ m wide, 850  $\mu$ m long and ~2  $\mu$ m thick) are attached at one end to a large anchor pad, with the other end connected to the transversal pointer arm with an offset joint.

## 2.2. Fabrication

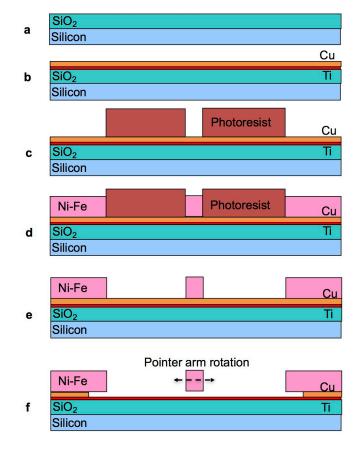

The fabrication of the test devices follows the diagram illustrated in Figure 2.

The starting substrate is a silicon wafer coated with a protective layer of 0.7 µm thick silicon dioxide (Figure 2a). The titanium and copper seed layer stack is then sputter deposited on the wafer in an OPT Plasmalab 400 magnetron sputtering system (Figure 2b). The copper serves as a seed layer for electroplating at a thickness of 300 nm to ensure good conductivity over the entire wafer area. The 30 nm thick titanium serves as adhesion layer between the copper and the underlying silicon dioxide insulator. Photolithography is then used to pattern the electroplating mould (Figure 2c). To this end, the wafer is first exposed to adhesion promoter hexamethyldisilazane (HMDS) at room temperature for 30 s, then Microchem MEGAPOSIT<sup>TM</sup> SPR<sup>TM</sup> 220-4.5 photoresist is dispensed and spun at 4000 rpm for 60 s, so as to obtain a thickness of about 4 µm. An edge bead removal (EBR) step

is performed to ensure that the seed layer is exposed at edge of the wafer, as it will serve as contact for the electrodeposition process. The photoresist is then soft baked at 90 °C for 60 s. The wafer is placed in the mask aligner, operated in proximity mode, and exposed to a dose of about 350 mJ/cm<sup>2</sup>. The photoresist is post-exposure baked at 115 °C for 90 s, and then developed in MEGAPOSIT<sup>TM</sup> MF26A developer until all the exposed photoresist is dissolved. A ~2 µm thick Ni-Fe layer is then electrodeposited using a DC power source to provide a current density of 20 mA/cm<sup>2</sup> (Figure 2d). The electroplating bath is composed of the chemicals reported in Table 1.

**Figure 2.** Fabrication process flow for the rotating pointer arm test structures: starting silicon substrate with protective silicon dioxide coating (**a**); sputter deposition of the titanium-copper seed layer stack (**b**); lithography to define the electroplated areas (**c**); electrodeposition of Ni-Fe through the photoresist mould (**d**); photoresist stripping and exposure of the copper seed layer (**e**); etching of the exposed copper seed layer and undercut etch underneath the pointer arm structures (**f**).

| Table 1. Chemica | l composition of | the Ni-Fe electro | plating bath. |

|------------------|------------------|-------------------|---------------|

|------------------|------------------|-------------------|---------------|

| Component                            | Concentration (gL <sup>-1</sup> ) |

|--------------------------------------|-----------------------------------|

| NiCl <sub>2</sub> ·6H <sub>2</sub> O | 110                               |

| FeCl <sub>2</sub> ·4H <sub>2</sub> O | 8                                 |

| H <sub>3</sub> BO <sub>3</sub>       | 25                                |

| Saccharin                            | 1                                 |

| Na dodecyl sulphate                  | 0.1                               |

| HCl                                  | 5                                 |

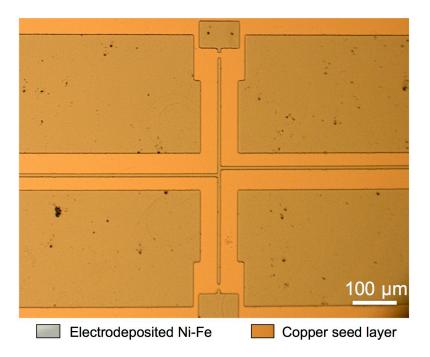

The thickness  $(2 \pm 0.2 \ \mu\text{m})$  and alloy composition (Fe contents of around  $20\% \pm 5\%$ ) of the films were verified by means of X-ray fluorescence measurements. Once the electrodeposition is completed, the photoresist is stripped to expose the copper seed layer for wet etching (Figure 2e). Figure 3 shows a photograph of a test structure at this point in the process.

Figure 3. Micrograph of Ni-Fe electrodeposited test structure anchored to the copper seed layer.

At this stage, the copper seed layer is etched (Figure 2f). The exposed copper surface is etched first, followed by the undercut underneath the Ni-Fe structures. Once the undercut etch is sufficient to completely remove the copper underneath the narrow beams (4  $\mu$ m sideways etch), these are no longer bound to the substrate and free to contract or expand to relieve the residual stress. The observation of a movement of the pointer arm is therefore an indication of the completion of the copper etch underneath the beams. The larger electrodeposited areas of the anchor pads at this stage remain fully anchored to the substrate, as the undercut only extends to half the width (4  $\mu$ m) of the narrow Ni-Fe beams, plus any over-etch.

## 2.3. Development of the Selective Etching Process

Permalloy (80:20) and nickel-iron alloys in other ratios are reportedly attacked by ferric chloride etchants [28–30], cupric chloride etchants [12,31] (although they might not attack pure nickel [32], their oxidising action attacks the iron component [31]), HNO<sub>3</sub>, HCl, H<sub>2</sub>SO<sub>4</sub>, H<sub>3</sub>PO<sub>4</sub> and HF [33]. In this work, the copper layer used as electrodeposition seed is etched with ammonium persulfate. To check the compatibility of this chemistry with ECD Ni-Fe, a first test was conducted by immersing test structures anchored to the underlying copper seed layer in a solution of ammonium persulfate diluted to a concentration of 20 gL<sup>-1</sup> in deionised (DI) water. The etching reaction of copper in ammonium persulfate is

$$Cu_{(s)} + S_2 O_8^{2-} \longrightarrow Cu^{2+} + 2SO_4^{2-}$$

(1)

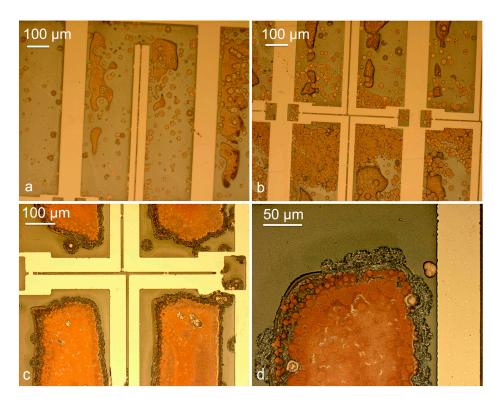

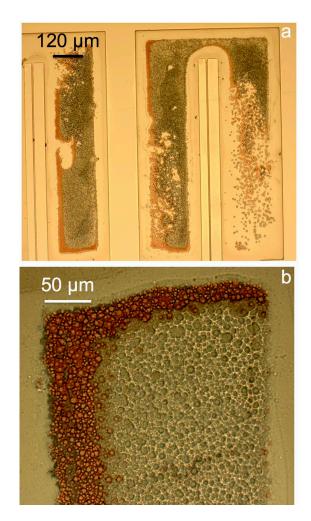

Three test wafers were left in the solution for 3, 5, and 10 min to monitor the progressive effects of the etchant on the ECD Ni-Fe. Figure 4 illustrates the results.

The micrographs of Figure 4 reveal two different undesired phenomena, namely the chemical attack of Ni-Fe, more evident in Figure 4c, and the redeposition of the etched copper on the anchored surfaces, even at the first stages of the etch (Figure 4a). Figure 4d shows in detail the redeposited copper layer on the ECD Ni-Fe. After 10 min in the etching solution the beams appear to be still anchored, suggesting that copper residue is still present underneath the narrow structures, while the edges of the ECD Ni-Fe structure exhibit signs of corrosion.

**Figure 4.** Micrographs of the test structures subject to copper etch with ammonium persulfate, at different etch times: 3 min (**a**); 5 min (**b**); and 10 min (**c**,**d**).

This highlights a problematic lack of selectivity. Wu et al. have shown that a pH in the alkaline range can help mitigate this phenomenon [9]. In light of this, ammonium persulfate was diluted this time to a concentration of 20 gL<sup>-1</sup> in 1 M sodium hydroxide (NaOH, 40 gL<sup>-1</sup>), in order to characterise the etching reaction at a higher pH (~12). A progressive pH decrease is expected during the etch in this solution as the OH<sup>-</sup> groups from the sodium hydroxide react to form water:

$$Cu^{2+} + 4NH_4^+ + 4OH^- \longrightarrow Cu(NH_3)_4^{2+} + 4H_2O.$$

(2)

This is more evident when small volumes of the etching solution are prepared.

A test wafer with the same test structures was immersed in the high pH etching solution for 10 min, and the results are shown in Figure 5.

The images show satisfactory selectivity, with the Ni-Fe structures exhibiting no visible signs of corrosion (at this scale and compared to Figure 4c) after 10 min in the etching solution. However, the copper seed is still present underneath the electrodeposited structures after this relatively long etch time, as indicated by the narrow beams in Figure 5a being straight and anchored. To increase the etch rate, the concentration of ammonium persulfate in the sodium hydroxide solution was increased to 50 gL<sup>-1</sup>.

As for the redeposition of etched metal observed prevalently on the bigger areas of the ECD structures, this effect has been reported in the literature and solved by adding a variety of complexing agents to the etching solution, such as 1,4,8,11 tetraazundecane [34] or dimethyl sulfoxide [35]. In this work, a different complexing agent is chosen, citric acid ( $C_6H_8O_7$ ), as it has the advantages of being inexpensive and commonly available. The addition of citric acid causes the formation of copper citrate complex and ammonia gas, according to the reaction

$$\operatorname{Cu}(\operatorname{NH}_{3})_{4}^{2+} + \{\operatorname{Cit}\}^{3-} \longrightarrow \operatorname{Cu}\{\operatorname{Cit}\}^{-} + 4\operatorname{NH}_{3(\operatorname{aq})},\tag{3}$$

where  ${Cit}^{3-}$  is the deprotonated species  $(C_6H_5O_7)^{3-}$  resulting from dissociation of citric acid in a high pH solution.

**Figure 5.** Micrographs of samples used for copper etch tests with ammonium persulfate in 1 M NaOH: overview of an anchor pad (**a**) and detail of the surface (**b**).

To verify the effectiveness as complexing agent,  $50 \text{ gL}^{-1}$  of citric acid were dissolved in the etchant to prevent the reduction of copper on Ni-Fe. The new etching solution was tested on another wafer and the results are presented in Figure 6. The undesired effects of Ni-Fe corrosion and redeposition of etched metal are eliminated and the copper seed layer is completely removed after 3–5 min in the etchant, as indicated by the rotation of the pointer arms and the clean wafer surface, which appears free of residue.

A series of etching solutions was then tested with ammonium persulfate concentrations ranging from 10 gL<sup>-1</sup> to 50 gL<sup>-1</sup>. The observed effect on the copper seed etching process is that higher concentrations of ammonium persulfate offer higher etch rate, without affecting the other exposed materials. If the solution is prepared in small volumes, a slight increase in the etch time for 300 nm sputtered copper is observed when large numbers of wafers are processed. No increase in the etch time was observed when etching up to a total of four patterned 3" silicon wafers in 200 mL of etching solution. Table 2 summarises the composition of the final developed etching solution.

Table 2. Chemical composition of the improved copper etching solution.

| Component                                                     | Quantity            |

|---------------------------------------------------------------|---------------------|

| (NH <sub>4</sub> ) <sub>2</sub> S <sub>2</sub> O <sub>8</sub> | 50 gL <sup>-1</sup> |

| C <sub>6</sub> H <sub>8</sub> O <sub>7</sub>                  | 50 gL <sup>-1</sup> |

| NaOH                                                          | 1 M                 |

This proposed solution enables the release of the presented pointer arm test structures by etching 300 nm thick copper with an undercut of 4  $\mu$ m in 3–5 min on average. This etch is a two-stage process which starts by removing the visible copper and consequently exposing the top part of the copper underneath the Ni-Fe. The etch process continues sideways underneath the Ni-Fe structures once the whole thickness of the copper is etched in the uncovered areas. This etch process causes no visible attack on Ni-Fe and titanium even after exposure for 10 min to the solution. This result opens wider possibilities of using ammonium sulphate based copper etchants in the presence of nickel and iron alloys, where other chemistries do not provide sufficient selectivity.

**Figure 6.** Photographs of ECD Ni-Fe structures successfully released from the copper seed layer after 4 min in ammonium persulfate diluted in 1 M NaOH and complexing agent: (**a**) overview of a test structure, and details of the offset joint in the centre (**b**); and pointer arm tip (**c**). Micrographs (**b**) and (**c**) are taken from a different structure. Note the titanium adhesion layer is visible below the ECD Ni-Fe after the copper is removed.

## 3. Selective Sacrificial Layer Etching

A critical requirement for surface micromachining is the choice of a suitable sacrificial layer. Desirable properties sought in the sacrificial material include robustness to support ECD Ni-Fe structures through other fabrication steps prior to the release, ease of etching for both patterning and final removal, and etch selectivity with respect to other structural materials.

## 3.1. Sacrificial Material

Common materials used as sacrificial layers in surface micromachined MEMS are amorphous silicon [36,37], polysilicon [37–39], polymers such as polyimide [20,40,41] and Parylene [42], and

PECVD silicon dioxide [43]. In the case of complex devices with suspended ECD Ni-Fe structures, the authors have shown that surface micromachining processes employing polysilicon or polymers as sacrificial layer may cause a progressive development of stress gradient in the electrodeposits, due to oxidation of the Ni-Fe film and the thermal budget applied during the required fabrication steps [25]. Silicon dioxide, on the other hand, can be deposited using a large variety of processes, producing films that exhibit different chemical and mechanical properties. Although SiO<sub>2</sub> can be selectively etched in HF-based chemistries with respect to silicon and some common metals, the etch rates of silicon nitride in such etchants can exhibit significant variation depending on the deposited by Low Pressure Chemical Vapour Deposition (LPCVD) shows good selectivity against HF-based SiO<sub>2</sub> etch [44], but it requires very high deposition temperatures (above 700 °C).

This and similar high-temperature processes are excluded in this work to ensure compatibility with MEMS architectures where Ni-Fe elements are already present on the wafer at earlier fabrication stages (e.g., embedded magnetic cores).

To this end, a process is proposed herein that enables the wet etch patterning of sacrificial  $SiO_2$ whilst using low-temperature Plasma Enhanced Chemical Vapour Deposition (PECVD) silicon nitride layers as a structural dielectric for complex devices. To enhance the wet-etch selectivity between sacrificial silicon dioxide and structural silicon nitride, a low temperature film is used as sacrificial layer. This has been achieved with a Surface Technology Systems (STS) Multiplex PECVD tool by lowering the temperatures of both the wafer holder and the gas inlet unit in the plasma chamber to 120 °C and by dropping the process frequency from the standard RF value of 13.56 MHz to 380 kHz. Tuning the properties of PECVD deposited dielectric layers by modifying the process conditions is a technique that has been widely adopted for a range of applications. The influence of dual high and low frequency PECVD parameters and substrate temperature has been used for instance to control the residual stress and mechanical properties in silicon nitride [45,46] films. On the other hand, low-temperature PECVD silicon oxides have been investigated for Through Silicon Via applications, benefitting from satisfactory step coverage and electrical properties while easing the process integration by avoiding excessive thermal loads [47,48]. In this work, a combination of low frequency and low temperature is used for the PECVD deposition of sacrificial silicon oxide. The low temperature enables the deposition of low density oxide that can benefit from a higher etch rate [49], while the low frequency introduces an ion bombardment mechanism that enhances chemical reactions and causes low energy ion implantation [50], improving the stability of the film when subjected to further processing [51].

To test the newly designed sacrificial material, blanket layers of  $\sim 2 \mu m$  thick silicon dioxide were produced using the PECVD process parameters listed in Table 3. The thickness of 2  $\mu m$  was chosen to emulate typical vertical gap dimensions for MEMS actuators [52].

In addition, blanket silicon nitride structural layers were also PECVD deposited to enable etch rate comparisons. The process parameters used for the deposition of 200 nm  $Si_3N_4$  are detailed in Table 4. Note that the temperature for this process is also maintained below the limit of 200 °C observed for this study.

| Table 3. Process parameters for th | ne PECVD deposition | of 2 $\mu$ m of sacrificial SiO <sub>2</sub> . |

|------------------------------------|---------------------|------------------------------------------------|

|                                    |                     |                                                |

| Process Parameter          | Value     |

|----------------------------|-----------|

| SiH <sub>4</sub> flow rate | 6 sccm    |

| N <sub>2</sub> O flow rate | 1420 sccm |

| RF frequency               | 380 kHz   |

| RF power                   | 60 W      |

| Wafer holder temperature   | 120 °C    |

| Gas inlet unit temperature | 120 °C    |

| Chamber pressure           | 550 mTorr |

| Deposition time            | 53 min    |

| <b>Process Parameter</b>   | Value     |  |

|----------------------------|-----------|--|

| N <sub>2</sub> flow rate   | 1900 sccm |  |

| $SiH_4$ flow rate          | 120 sccm  |  |

| NH <sub>3</sub> flow rate  | 8 sccm    |  |

| RF frequency               | 13.56 MHz |  |

| RF power                   | 60 W      |  |

| Wafer holder temperature   | 200 °C    |  |

| Gas inlet unit temperature | 200 °C    |  |

| Chamber pressure           | 550 mTorr |  |

| Deposition time            | 7.5 min   |  |

**Table 4.** Process parameters for the PECVD deposition of 200 nm of structural Si<sub>3</sub>N<sub>4</sub>.

# 3.2. Selective Wet Etching of Sacrificial SiO<sub>2</sub>

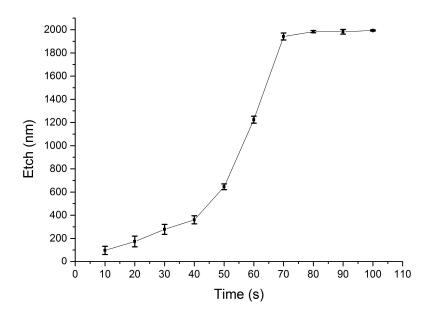

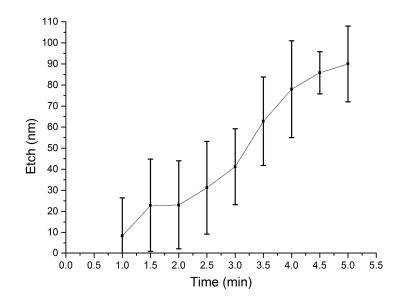

The etch rate of the low-temperature  $SiO_2$  films in BOE 10:1 (10:1 ammonium fluoride (NH<sub>4</sub>F) and hydrofluoric acid (HF)) at room temperature was tested first. To this end, a solution of 100 mL BOE 10:1 diluted in 200 mL DI water was prepared. Test wafers coated with the blanket sacrificial  $SiO_2$  layer were immersed and left in the etchant for different times, with the etch duration increased in steps of 10 s. The residual film thickness was measured with a Nanospec 3000 reflectometer on each sample, and the results are shown in Figure 7.

**Figure 7.** Etched thickness of sacrificial PECVD  $SiO_2$  in a solution of 1 part BOE 10:1 diluted in two parts DI water. Each measurement point is the average of five thickness measurements across the wafer surface.

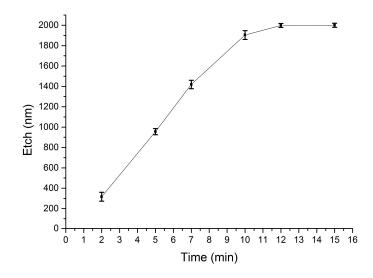

These measurements confirm a fast etch rate that removes the entire thickness of the sacrificial  $SiO_2$  in less than 80 s. To monitor the controllability of the etching process, a further diluted solution was prepared by mixing 1 part of 10:1 BOE in 10 parts of DI water. The experiment was repeated on test wafers identical to the ones used for the previous etch measurements, and the resulting removal curve is shown in Figure 8.

The etch rate of sacrificial  $SiO_2$  in the 1:10 diluted solution is much more controllable and enables the removal of the entire thickness of 2  $\mu$ m in about 12 min. The dilution level of BOE can therefore be increased to obtain a controllable etch, or reduced to accelerate the process.

To assess selectivity with respect to structural dielectrics, the etch rate of structural PECVD  $Si_3N_4$  was measured in the more concentrated BOE solution. The experiment is performed analogously to

the etching tests described above, and Figure 9 shows the resulting curve. The silicon nitride exhibits a fairly slow rate of removal, with the thickness of the structural dielectric being reduced by a maximum of 50 nm after the material is exposed to the etchant for 2 min. Figure 7 shows that during this time the same etching solution can remove  $2 \mu m$  of sacrificial silicon dioxide.

**Figure 8.** Etched thickness of sacrificial PECVD  $SiO_2$  in a solution of one part BOE 10:1 diluted in 10 parts DI water. Each measurement point is the average of five thickness measurements across the wafer surface.

**Figure 9.** Etched thickness of the structural silicon nitride in a solution of one part BOE 10:1 diluted in two parts DI water. Each measurement point is the average of five thickness measurements across the wafer surface. Note the magnitude of the dispersion bars, as the thickness range is much lower.

When the experiment on structural silicon nitride was repeated in the 1:10 diluted BOE solution, no appreciable change in thickness was measured for 10 min. These results demonstrate the feasibility of patterning sacrificial structures by wet etching low temperature, low frequency PECVD  $SiO_2$  whilst preserving the integrity of exposed PECVD  $Si_3N_4$ . The silicon nitride can therefore be employed as a protective or structural dielectric in complex devices. Approximate values for the etch rates are calculated and detailed in Table 5.

| Etchant                     | Material                             | Approximate Etch Rate |

|-----------------------------|--------------------------------------|-----------------------|

| 1:2 [BOE 10:1] in DI water  | PECVD SiO <sub>2</sub>               | 1500 nm/min           |

| 1:2 [BOE 10:1] in DI water  | PECVD Si <sub>3</sub> N <sub>4</sub> | 20 nm/min             |

| 1:10 [BOE 10:1] in DI water | PECVD SiO <sub>2</sub>               | 160 nm/min            |

| 1:10 [BOE 10:1] in DI water | PECVD Si <sub>3</sub> N <sub>4</sub> | not detected          |

**Table 5.** Wet-Etch Rates for the PECVD SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>.

The deposited sacrificial silicon dioxide films exhibit faster etch rates in BOE compared to films produced at standard conditions [34] (for effective comparison, note the further dilution of BOE in this study), and both at RF and low frequency [51].

The calculated selectivity between PECVD  $SiO_2$  and PECVD  $Si_3N_4$  in the more concentrated wet BOE chemistry is therefore around 75. Although far from the very high values of around 850 reported for phosphosilicate glass (PSG) against Si-rich LPCVD silicon nitride [34], the methods proposed in this work trade off selectivity in favour of compatibility with Ni-Fe elements, by using low-temperature deposition processes. This is a crucial aspect for the reliable integration of Ni-Fe in complex MEMS devices such as magnetic actuators, where buried magnetic cores and vias are required prior to the surface micromachining steps to release the actuator elements.

#### 4. Surface Micromachining with Vapour HF Etch

In this final section, a vapour phase HF etch is added to the set of viable processes that can be used with the combination of materials studied. Surface micromachining is demonstrated employing the wet etch processes described in the previous sections, plus a vapour phase HF release etch. To this end, microcantilever test structures were fabricated on 3" silicon wafers using ECD Ni-Fe (Table 1) and PECVD silicon nitride (Table 4) as structural materials, and PECVD silicon dioxide (Table 3) as sacrificial layer. This configuration was chosen as it mimics the manufacturing complexities and limitations encountered when producing magnetic MEMS devices such as microactuators.

#### 4.1. Test Structures

Test microcantilevers (200–300  $\mu$ m long and 10–100  $\mu$ m wide) were manufactured using low-stress electrodeposited Ni-Fe [24,27,53]. A two-step electrodeposition technique was used to first deposit the cantilever anchor, followed by the cantilever beam. This two-stage process avoids the introduction of additional mechanical stress and stress gradients in ECD Ni-Fe [25], enabling a clearer evaluation of the etch release. The sacrificial PECVD silicon dioxide reported in Section 3.1 was used to produce mesa structures that serve as a resting surface for the cantilever beams.

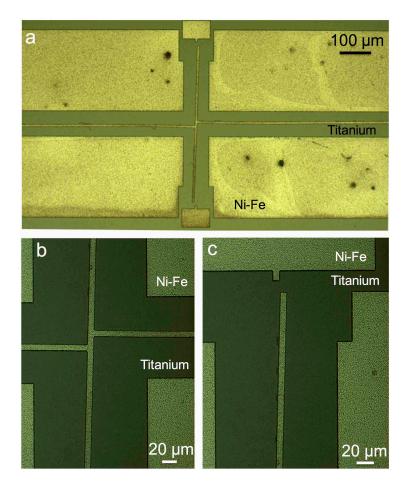

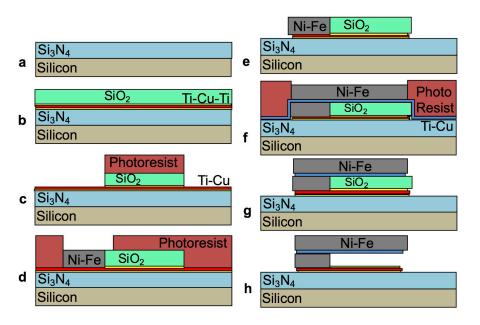

With reference to Figure 10, the process flow comprises of the following steps: (a) PECVD deposition of 200 nm structural  $Si_3N_4$  on a silicon substrate as per Table 4; (b) Sputter deposition of 30 nm Ti, 300 nm Cu, 30 nm Ti seed layer stack for electrodeposition. The topmost Ti layer is added to the seed layer stack both to protect the underlying copper from oxidation prior to the electrodeposition step, and to promote the adhesion of the subsequent sacrificial silicon oxide layer, PECVD deposited to a thickness of 2  $\mu$ m as per Table 3; (c) Photolithography and wet etch of the sacrificial layer in diluted BOE (Table 5) to define the mesa structures that support the cantilever beams, followed by a brief titanium wet etch in 1% HF to expose the conductive copper seed layer; (d) Photolithography to define the cantilever anchors and electrodeposition of Ni-Fe (Table 1) to a thickness that matches the sacrificial mesa; (e) Photoresist strip and wet etch of the Ti-Cu seed layer as per Section 2.3; (f) Sputter deposition of 30 nm Ti and 300 nm Cu seed layer, photolithography to define the cantilever beams and electrodeposition of 2  $\mu$ m Ni-Fe as per Table 1; (g) Photoresist strip and wet etch of the Ti-Cu seed layer and release of the Ti-Cu seed layer as per Section 2.3; (h) Complete removal of the remaining sacrificial layer and release of the freestanding structures.

**Figure 10.** Cross-sections of the process flow for the manufacture of the cantilever test structures: starting silicon substrate with structural silicon nitride layer (**a**); sputter deposition of a titanium-copper-titanium seed layer stack and PECVD deposition of the sacrificial silicon oxide (**b**); lithography and wet-etch patterning of the sacrificial silicon dioxide and the topmost titanium protective layer (**c**); lithography and electrodeposition of the Ni-Fe anchors through the photoresist and silicon dioxide mould (**d**); photoresist strip and wet etch of the copper and titanium seed layer (**e**); sputter deposition of a titanium-copper seed layer stack, lithography to define the cantilever beams, and electrodeposition of Ni-Fe cantilever beam through the photoresist mould (**f**); photoresist strip and wet-etch of the exposed titanium-copper seed layer (**g**); complete removal of the sacrificial silicon dioxide and release of freestanding cantilevers (**h**).

Note that this specific architecture requires a final seed layer strip after the removal of the sacrificial mesa and critical point drying to avoid stiction. This eliminates the anti-stiction benefit of the vapour HF process, as the wafers can be wet-etched in a series of adequate etchants and finally critical-point dried. The vapour HF process is nevertheless demonstrated herein as it can be employed for different architectures and applications.

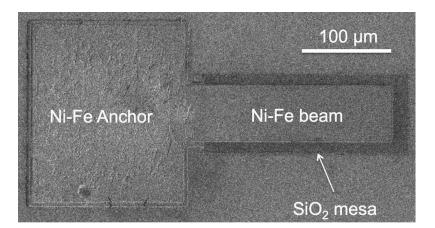

Figure 11 shows a cantilever test structure with the beam resting on the silicon dioxide sacrificial mesa, corresponding to Figure 10g.

**Figure 11.** SEM image of a 200  $\mu$ m long by 50  $\mu$ m wide cantilever with the beam resting on the sacrificial silicon dioxide mesa.

## 4.2. Release of the Cantilevers

The final step to produce freestanding cantilevers is the complete removal of the sacrificial layer by etching the remaining sacrificial oxide material with vapour HF (Figure 10h). The process was performed in a MEMSSTAR SVR-HF vapour phase dry release system. HF vapour is introduced in the process chamber at a flow rate of 150 sccm, and the pressure is ramped from 2 to 10 Torr in 1 to 2 min, and then kept constant for 300 s. The etch progress can be visualised by monitoring the generation of the by-products of the reaction

$$SiO_2 + 6HF \longrightarrow 2H^+ + SiF_6^{2-} + 2H_2O$$

<sup>(4)</sup>

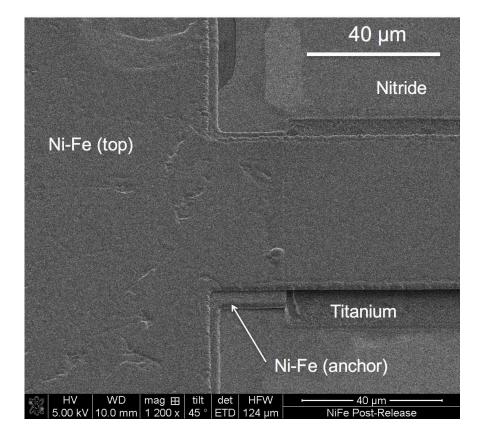

using a built-in laser interferometer, indicating the reaction rate. The low temperature PECVD silicon dioxide facilitates a rapid process that releases the cantilevers in less than 300 s, without attacking the Ni-Fe structures or the structural silicon nitride. The complete release is verified by applying an external magnetic field and observing the magnetic cantilevers free to deflect and align their easy magnetisation axis (length) with the external magnetic field lines (see video in Supplementary Materials). Figure 12 shows a SEM image of the anchored end of a cantilever after the removal of the sacrificial SiO<sub>2</sub> mesa.

**Figure 12.** Ni-Fe cantilever beam after the removal of the sacrificial silicon dioxide mesa by vapour HF etch. The etched gap is clearly visible. The dark shadow under the cantilever beam is the titanium adhesion layer exposed after the removal of the sacrificial silicon oxide mesa.

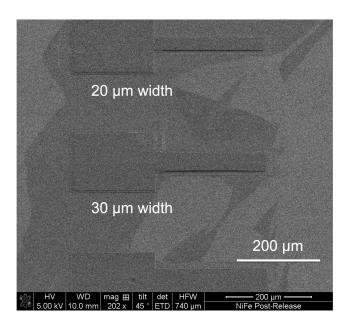

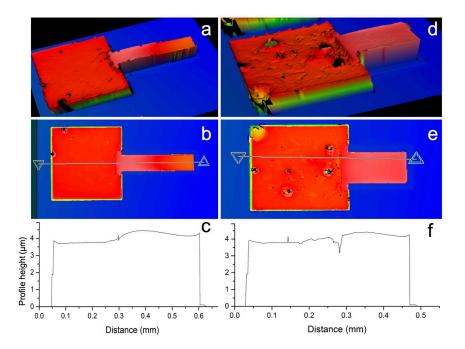

The etch release is a room temperature process, which also ensures that no undesirable thermal loads are applied to the Ni-Fe, thereby ensuring that the residual stress is not increased. This can be visually verified by observing freestanding structures that are flat and free from curling effects, which indicates low stress gradient through the thickness of the film. Figure 13 shows 200  $\mu$ m long cantilevers released with the described surface micromachining process.

Figure 13. Released 200 µm long Ni-Fe cantilevers with widths of 20 and 30 µm.

The SEM images show the complete removal of the sacrificial silicon dioxide, producing freestanding Ni-Fe cantilevers that, as a result of the improved processes detailed in this work, are not chemically attacked, nor do they suffer from excessive stress. Profiles were measured optically by white light interferometry to provide a measure of the curling of the beams and verify that they do not suffer from excessive stress induced by the processing. This is shown in Figure 14.

**Figure 14.** White light interferometry of two released cantilever beams: 300  $\mu$ m long × 70  $\mu$ m wide (**a**–**c**); and 200  $\mu$ m long × 100  $\mu$ m wide (**d**–**f**). 3D topology reconstructions (**a**,**d**); top views with the height measurement line (**b**,**e**); and measured profile height (**c**,**f**). Note the change in roughness between the pads (two electrodeposited layers stacked) and the beams (electrodeposited on a smooth sacrificial oxide mesa). Note that the surface roughness observed in (**d**) is due to the uneven growth of Ni-Fe, possibly associated to roughness of the underlying layer, current crowding effects due to topology defects, impurities, etc.

The vapour HF process is successfully proven as viable for use with ECD Ni-Fe, as no damage was observed on the ECD Ni-Fe and the PECVD silicon nitride. The full undercut width was also rapidly etched underneath the freestanding structures. No stiction effect was observed, no visible residue was left on the substrate, and no thermal load was applied.

## 5. Conclusions

A set of deposition and etching processes has been developed as a toolkit for the integration of surface micromachined ECD Ni-Fe in complex MEMS devices. The first process is a wet etch that uses a conventional ammonium persulfate chemistry, diluted in a sodium hydroxide solvent to enable the electrodeposition seed layer to be stripped with no detrimental effects on ECD Ni-Fe. Two PECVD processes are subsequently presented that enable the low-temperature deposition of structural silicon nitride and sacrificial silicon dioxide for use with ECD Ni-Fe. Finally, wet etch and vapour etch processes for the PECVD silicon dioxide are reported that enable the patterning of sacrificial structures and the complete removal of the sacrificial material, while preserving the structural PECVD silicon nitride.

All the reported processes avoid excessive thermal loads that are known to generate residual stress and stress gradients with consequent detrimental effects on Ni-Fe freestanding structures [25]. This is achieved by limiting the processing temperatures to below 200 °C, based on previously reported research [24].

The improved copper seed etch chemistry, the low-temperature PECVD sacrificial silicon dioxide and the corresponding wet etch patterning and vapour etch removal methods have been integrated into a process that emulates the manufacturing of complex magnetic MEMS devices. It is worth noting that the developed processes can be used in any combination and for a range of different applications. An all-wet surface micromachining process can be used, for instance, for the two-step cantilever architecture shown, since critical point drying is needed after the final seed etch step. Conversely, if a standard Ni-Fe beam or membrane is fabricated with no via-anchor structure (no seed layer underneath the sacrificial material), the vapour HF process can be used to avoid stiction without the need for critical point drying.

The reported results represent therefore a useful reference for the manufacturing of complex MEMS devices with integrated ECD Ni-Fe elements.

#### Supplementary Materials: The following are available online at www.mdpi.com/1996-1944/10/3/323/s1.

Acknowledgments: The authors would like to acknowledge Daniel Drysdale and Tony O'Hara of Memsstar for their help with HF vapour etching. This work was supported by the Edinburgh Research Partnership in Engineering and Mathematics, EPSRC/IeMRC through DTA funding DTA/15/2007, IeMRC/EPSRC (FS/01/02/10) through the Smart Microsystems grant. Data associated with the paper are available from the University of Edinburgh data repository at the address: http://dx.doi.org/10.7488/ds/1985.

**Author Contributions:** Giuseppe Schiavone conceived, designed, and performed the experiments. Jeremy Murray contributed to the fabrication of the pointer arm test samples. Richard Perry and Andrew Mount provided the chemical models that explain the observed results. Giuseppe Schiavone wrote the paper. Anthony Walton, Marc Desmulliez and Andrew Mount provided guidance and academic support, together with securing funding for the work.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- Daniel, L.; Sullivan, C.R.; Sanders, S.R. Design of microfabricated inductors. In Proceedings of the PESC Record, 27th Annual IEEE Power Electronics Specialists Conference, Baveno, Italy, 23–27 June 1996; Volume 2, pp. 1447–1455.

- Sullivan, C.R.; Sanders, S.R. Design of microfabricated transformers and inductors for high-frequency power conversion. *IEEE Trans. Power Electron.* 1996, 11, 228–238. [CrossRef]

- Myung, N.V.; Park, D.-Y.; Yoo, B.-Y.; Sumodjo, P.T.A. Development of electroplated magnetic materials for MEMS. J. Magn. Magn. Mater. 2003, 265, 189–198. [CrossRef]

- 4. Mathúna, C.Ó.; Wang, N.; Kulkarni, S.; Roy, S. Review of Integrated Magnetics for Power Supply on Chip (PwrSoC). *IEEE Trans. Power Electron.* **2012**, *27*, 4799–4816. [CrossRef]

- Luo, J.K.; Pritschow, M.; Flewitt, A.J.; Spearing, S.M.; Fleck, N.A.; Milne, W.I. Effects of Process Conditions on Properties of Electroplated Ni Thin Films for Microsystem Applications. *J. Electrochem. Soc.* 2006, 153, D155–D161. [CrossRef]

- 6. Arai, K.I.; Honda, T. Micromagnetic actuators. Robotica 1996, 14, 477–481. [CrossRef]

- Niarchos, D. Magnetic MEMS: Key issues and some applications. Sens. Actuators A Phys. 2003, 106, 255–262. [CrossRef]

- Flynn, D.; Toon, A.; Allen, L.; Dhariwal, R.; Desmulliez, M.P.Y. Characterization of Core Materials for Microscale Magnetic Components Operating in the Megahertz Frequency Range. *IEEE Trans. Magn.* 2007, 43, 3171–3180. [CrossRef]

- 9. Wu, Y.B.; Ding, G.F.; Wang, H.; Zhang, C.C. Efficient solution to selective wet etching of ultra-thick copper sacrificial layer with high selective etching ratio. In Proceedings of the 2011 16th International Solid-State Sensors, Actuators and Microsystems Conference, Beijing, China, 5–9 June 2011; pp. 1388–1391.

- 10. Quemper, J.-M.; Nicolas, S.; Gilles, J.P.; Grandchamp, J.P.; Bosseboeuf, A.; Bourouina, T.; Dufour-Gergam, E. Permalloy electroplating through photoresist molds. *Sens. Actuators A Phys.* **1999**, *74*, 1–4. [CrossRef]

- Cohen, U.; Hsie, W.C. Selective Chemical Removal of Coil Seed-Layer in Thin Film Head Magnetic Transducer. U.S. Patent 5,059,278 A, 22 October 1991.

- 12. Asai, O.; Hanazono, M. Electrolytic Etching Method. U.S. Patent 3,905,883 A, 16 September 1975.

- 13. Saulnier, T.A. Ferric chloride Etching Solutions. U.S. Patent 2,684,892 A, 27 July 1954.

- 14. French, P.J. Development of surface micromachining techniques compatible with on-chip electronics. *J. Micromech. Microeng.* **1996**, *6*, 197. [CrossRef]

- 15. Taylor, W.P.; Brand, O.; Allen, M.G. Fully integrated magnetically actuated micromachined relays. *J. Microelectromech. Syst.* **1998**, *7*, 181–191. [CrossRef]

- 16. Ruan, M.; Shen, J.; Wheeler, C.B. Latching micromagnetic relays. J. Microelectromech. Syst. 2001, 10, 511–517. [CrossRef]

- 17. Cho, I.-J.; Yoon, E. Design and fabrication of a single membrane push-pull SPDT RF MEMS switch operated by electromagnetic actuation and electrostatic hold. *J. Micromech. Microeng.* **2010**, *20*, 035028. [CrossRef]

- Glickman, M.; Tseng, P.; Harrison, J.; Niblock, T.; Goldberg, I.B.; Judy, J.W. High-Performance Lateral-Actuating Magnetic MEMS Switch. J. Microelectromech. Syst. 2011, 20, 842–851. [CrossRef]

- 19. Gray, G.D., Jr.; Prophet, E.M.; Zhu, L.; Kohl, P.A. Magnetically bistable actuator: Part 2. Fabrication and performance. *Sens. Actuators A Phys.* **2005**, *119*, 502–511. [CrossRef]

- 20. Bagolini, A.; Pakula, L.; Scholtes, T.L.M.; Pham, H.T.M.; French, P.J.; Sarro, P.M. Polyimide sacrificial layer and novel materials for post-processing surface micromachining. *J. Micromech. Microeng.* **2002**, *12*, 385. [CrossRef]

- 21. Girard, R. The Electrodeposition of Thin Magnetic Permalloy Films. *J. Appl. Phys.* **1967**, *38*, 1423–1430. [CrossRef]

- 22. Hadian, S.E.; Gabe, D.R. Residual stresses in electrodeposits of nickel and nickel–iron alloys. *Surf. Coat. Technol.* **1999**, *122*, 118–135. [CrossRef]

- 23. Yang, M.M.; Aboaf, J.A. rf-diode sputtered Permalloy film. J. Appl. Phys. 1989, 66, 3734–3740. [CrossRef]

- Murray, J.; Schiavone, G.; Smith, S.; Terry, J.; Mount, A.R.; Walton, A.J. Characterisation of electroplated NiFe films using test structures and wafer mapped measurements. In Proceedings of the 2011 IEEE ICMTS International Conference on Microelectronic Test Structures, Amsterdam, The Netherlands, 4–7 April 2011; pp. 63–68.

- 25. Schiavone, G.; Bunting, A.S.; Desmulliez, M.P.Y.; Walton, A.J. Fabrication of Electrodeposited Ni #x2013;Fe Cantilevers for Magnetic MEMS Switch Applications. *J. Microelectromech. Syst.* **2015**, *24*, 870–879.

- 26. Schiavone, G.; Murray, J.; Smith, S.; Desmulliez, M.P.Y.; Mount, A.R.; Walton, A.J. A wafer mapping technique for residual stress in surface micromachined films. *J. Micromech. Microeng.* **2016**, *26*, 095013. [CrossRef]

- 27. Schiavone, G.; Desmulliez, M.P.Y.; Smith, S.; Murray, J.; Murray, J.; Sirotkin, E.; Terry, J.G.; Mount, A.R.; Walton, A.J. Quantitative wafer mapping of residual stress in electroplated NiFe films using independent strain and Young's modulus measurements. In Proceedings of the 2012 IEEE International Conference on Microelectronic Test Structures, San Diego, CA, USA, 19–22 March 2012; pp. 105–110.

- Madou, M.J. Manufacturing Techniques for Microfabrication and Nanotechnology; CRC Press: Boca Raton, FL, USA, 2011. Available online: https://www.crcpress.com/Manufacturing-Techniques-for-Microfabricationand-Nanotechnology/Madou/p/book/9781420055191 (accessed on 9 February 2017).

- 29. Allen, D.M. Photochemical Machining: From "manufacturing's best kept secret" to a \$6 billion per annum, rapid manufacturing process. *CIRP Ann. Manuf. Technol.* **2004**, *53*, 559–572. [CrossRef]

- 30. Osborne, J.R. Variable Sloped Etching of Thin Film Heads. U.S. Patent 4,351,698 A, 28 September 1982.

- Stichel, W. Materials selection for corrosion control. Hrsg. von S.L. Chawla und R.K. Gupta, 508 S., zahlreiche Tabellen und Grafiken. ASM International Materials Park, OH 44073, USA, £ 104,00. ISBN 0-87170-479-9. Mater. Corros. 1995, 46, 249. [CrossRef]

- 32. Williams, K.R.; Gupta, K.; Wasilik, M. Etch rates for micromachining processing-Part II. J. Microelectromech. Syst. 2003, 12, 761–778. [CrossRef]

- 33. Byun, Y.H.; Kim, H.I.; Song, Y.S.; Yoon, J.K.; Chung, C.W. Chemical Etching of NiFe and IrMn Thin Films. *J. Ind. Eng. Chem.* **2002**, *8*, 257–261.

- 34. Wu, X.H.; Li, W.; Lam, S.-T.; Chang, H.C.; Ju, K.; Chang, J.-W. Etching Process to Selectively Remove Copper Plating Seed Layer. U.S. Patent 6,767,477 B2, 27 July 2004.

- 35. Lin, C.W.-C.; Yee, I.Y.K. Copper Etching Solution and Method. U.S. Patent 4,952,275, 28 August 1990.

- 36. Fritschi, R.; Frédérico, S.; Hibert, C.; Flückiger, P.; Renaud, P.; Tsamados, D.; Boussey, J.; Chovet, A.; Ng, R.K.M.; Udrea, F.; et al. High tuning range AlSi RF MEMS capacitors fabricated with sacrificial amorphous silicon surface micromachining. *Microelectron. Eng.* **2004**, *73*–74, 447–451. [CrossRef]

- 37. Frederico, S.; Hibert, C.; Fritschi, R.; Fluckiger, P.; Renaud, P.; Ionescu, A.M. Silicon sacrificial layer dry etching (SSLDE) for free-standing RF MEMS architectures. In Proceedings of the IEEE the Sixteenth Annual International Conference on Micro Electro Mechanical Systems, 2003 MEMS-03, Kyoto, Japan, 19–23 January 2003; pp. 570–573.

- Sugiyama, S.; Tabata, O.; Shimaoka, K.; Asahi, R. Micromachined sensors using polysilicon sacrificial layer etching technology. In Proceedings of the 1994 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1994; pp. 127–130.

- 39. Metzger, L.; Fischer, F.; Mokwa, W. Polysilicon sacrificial layer etching using CIF3 for thin film encapsulation of silicon acceleration sensors with high aspect ratio. *Sens. Actuators A Phys.* **2007**, *133*, 259–265. [CrossRef]

- 40. Ma, S.; Li, Y.; Sun, X.; Yu, X.; Jin, Y. Study of polyimide as sacrificial layer with O2 plasma releasing for its application in MEMS capacitive FPA fabrication. In Proceedings of the 2009 International Conference on Electronic Packaging Technology High Density Packaging, Beijing, China, 10–13 August 2009; pp. 526–529.

- 41. Pham, H.T.M.; Bagolini, A.; de Boer, C.R.; Laros, J.M.W.; Pakula, L.; French, P.J.; Sarro, P.M. Polyimide sacrificial layer for an all-dry post-process surface micromachining module. In Proceedings of the 2003 12th International Conference on TRANSDUCERS, Solid-State Sensors, Actuators and Microsystems, Boston, MA, USA, 8–12 June 2003; Volume 1, pp. 813–816.

- Huang, W.-L.; Ren, Z.; Lin, Y.-W.; Chen, H.-Y.; Lahann, J.; Nguyen, C.T.C. Fully monolithic CMOS nickel micromechanical resonator oscillator. In Proceedings of the 2008 IEEE 21st International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 10–13.

- 43. Bühler, J.; Steiner, F.-P.; Baltes, H. Silicon dioxide sacrificial layer etching in surface micromachining. *J. Micromech. Microeng.* **1997**, *7*, R1. [CrossRef]

- 44. Witvrouw, A.; Du Bois, B.; De Moor, P.; Verbist, A.; Van Hoof, C.A.; Bender, H.; Baert, C. Comparison between wet HF etching and vapor HF etching for sacrificial oxide removal. *Proc. SPIE* **2000**, *4174*, 130–141.

- 45. Cianci, E.; Schina, A.; Minotti, A.; Quaresima, S.; Foglietti, V. Dual frequency PECVD silicon nitride for fabrication of CMUTs' membranes. *Sens. Actuators A Phys.* **2006**, 127, 80–87. [CrossRef]

- Huang, H.; Winchester, K.J.; Suvorova, A.; Lawn, B.R.; Liu, Y.; Hu, X.Z.; Dell, J.M.; Faraone, L. Effect of deposition conditions on mechanical properties of low-temperature PECVD silicon nitride films. *Mater. Sci. Eng. A* 2006, 435–436, 453–459. [CrossRef]

- Puech, M.; Thevenoud, J.M.; Gruffat, J.M.; Launay, N.; Arnal, N.; Godinat, P. Fabrication of 3D packaging TSV using DRIE. In Proceedings of the 2008 Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, Nice, France, 9–11 April 2008; pp. 109–114.

- Archard, D.; Giles, K.; Price, A.; Burgess, S.; Buchanan, K. Low temperature PECVD of dielectric films for TSV applications. In Proceedings of the 2010 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 764–768.

- Deshmukh, S.C.; Aydil, E.S. Investigation of low temperature SiO2 plasma enhanced chemical vapor deposition. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 1996, 14, 738–743. [CrossRef]

- 50. Van de Ven, E.P.; Connick, I.W.; Harrus, A.S. Advantages of dual frequency PECVD for deposition of ILD and passivation films. In Proceedings of the Seventh International IEEE Conference on VLSI Multilevel Interconnection, Santa Clara, CA, USA, 12–13 June 1990; pp. 194–201.

- 51. Guan, D.; Bruccoleri, A.R.; Heilmann, R.K.; Schattenburg, M.L. Stress control of plasma enhanced chemical vapor deposited silicon oxide film from tetraethoxysilane. *J. Micromech. Microeng.* **2014**, *24*, 027001. [CrossRef]

- 52. Schiavone, G.; Desmulliez, M.P.Y.; Walton, A.J. Integrated Magnetic MEMS Relays: Status of the Technology. *Micromachines* **2014**, *5*, 622–653. [CrossRef]

- 53. Schiavone, G.; Smith, S.; Murray, J.; Terry, J.G.; Desmulliez, M.P.Y.; Walton, A.J. Micromechanical test structures for the characterisation of electroplated NiFe cantilevers and their viability for use in MEMS switching devices. In Proceedings of the 2013 IEEE International Conference on Microelectronic Test Structures (ICMTS), Osaka, Japan, 25–28 March 2013; pp. 13–18.

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).