## <sup>ublishi</sup> slocation Loops as a Mechanism for

- Thermoelectric Power Factor Enhancement in 2

- Silicon Nano-Layers 3

- Nick S. Bennett<sup>a\*</sup>, Daragh Byrne<sup>b</sup>, Aidan Cowley<sup>c</sup>, Neophytos Neophytou<sup>d</sup> 4

- <sup>a</sup> Nano-Materials Lab., Institute of Mechanical, Process & Energy Engineering, School of 5

- Engineering & Physical Sciences, Heriot-Watt University, Edinburgh EH14 4AS, United 6

- Kingdom 7

- <sup>b</sup> School of Physical Science, Dublin City University, Glasnevin, Dublin 9, Ireland 8

- <sup>c</sup> European Astronaut Centre (EAC), European Space Agency (ESA), Linder Höhe, D-51147 9

Cologne, Germany 10

- <sup>d</sup> School of Engineering, University of Warwick, Coventry CV4 7AL, United Kingdom 11

- <sup>\*</sup> Corresponding author, E: n.bennett@hw.ac.uk, T: +44 131 451 4379, F: +44 131 451 3129 12

- 13

A more than 70% enhancement in the thermoelectric power factor of single-crystal 14 silicon is demonstrated in silicon nano-films, a consequence of the introduction of 15 networks of dislocation loops and extended crystallographic defects. Despite these 16 defects causing reductions in electrical conductivity, carrier concentration and carrier 17 mobility, large corresponding increases in the Seebeck coefficient and reductions in 18 thermal conductivity lead to a significant net enhancement in thermoelectric 19 performance. Crystal damage is deliberately introduced in a sub-surface nano-layer 20

Publishing within a silicon substrate, demonstrating the possibility to tune the thermoelectric

properties at the nano-scale within such wafers in a repeatable, large-scale and cost effective way.

The recent global drive to be more efficient in the way we use energy, particularly to reduce the 24 amount of energy that goes to waste, has led to renewed interest in thermoelectrics (TE) for 25 waste heat harvesting. In particular demand are materials that use elements that are less costly, 26 less toxic and more Earth-abundant than the popular TE material bismuth telluride (Bi<sub>2</sub>Te<sub>3</sub>). 27 Despite requiring the scarce element tellurium, Bi<sub>2</sub>Te<sub>3</sub> has significantly better thermoelectric 28 performance than more abundant elemental semiconductors, such as silicon (Si). Three material 29 properties determine this performance – thermal conductivity ( $\kappa$ ), Seebeck coefficient (S) and 30 electrical conductivity ( $\sigma$ ). These interlinked properties are commonly combined to describe 31 performance in terms of the thermoelectric figure-of-merit (Z), where  $Z = S^2 \sigma / \kappa$ . Bi<sub>2</sub>Te<sub>3</sub> has 32 approximately 100-fold better Z than bulk Si [1], but is approximately 30-times more expensive 33 [2]. Therefore developing methods that provide significant gains in the Z of Si offers a potential 34 route to more cost-effective and environmentally friendly thermoelectric devices. 35

Since highly-doped Si (doping  $\sim 10^{19}$  cm<sup>-3</sup>) possesses S and  $\sigma$  competitive with other TE 36 37 materials, much recent focus has been on reducing its thermal conductivity, which is too high for most practical applications. It been demonstrated possible via nano-structuring, to vastly reduce 38  $\kappa$  with little or no degradation of other parameters in structures such as Si nanowires, nanofilms 39 or films containing porosity, periodic voids or vacancies [3-13]. This allows for higher Z and 40 makes nano-structured Si an attractive TE material. Such findings, with variations, have been 41 corroborated by numerous groups worldwide, through both theoretical and experimental studies 42 [3-13]. 43

**Publishing** to this drastic reduction in  $\kappa$ , which is quickly reaching the amorphous limit, further improvements might come from Si's thermoelectric power factor ( $PF = S^2 \sigma$ ), for which to date 45 limited progress has been made. However, a small set of recent studies have demonstrated that a 46 significant improvement in Si's *PF* is sometimes possible for polycrystalline Si [14-16] where 47 built-in potential barriers are created by nano-scale grain boundaries or voids [17], combined 48 with high levels of doping. These potential barriers increase energy filtering and as a 49 consequence, the Si Seebeck coefficient. Our previous work demonstrated that a Seebeck 50 coefficient improvement is also realizable in single-crystal Si nanowires by the introduction of 51 dislocation loops, which also create potential barriers and produce a similar effect [18]. This was 52 so far only demonstrated in n-type material and for relatively lowly-doped Si, where the PF is far 53 too low for practical applications. 54 In this current article we report that a significant enhancement in the power factor is also possible 55 for p-type bulk material, and more importantly, with high doping concentrations. Improvements 56

57 in the *PF* by ~70 % compared to control samples (bulk Si) are realized, giving  $PF = 6.6 \text{ mW m}^{-1}$ 58 K<sup>-2</sup> at 300 K – significantly higher than that of traditional Bi<sub>2</sub>Te<sub>3</sub> materials used in current

59 commercial devices.

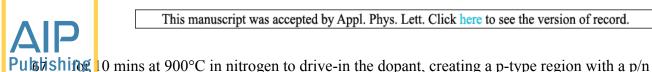

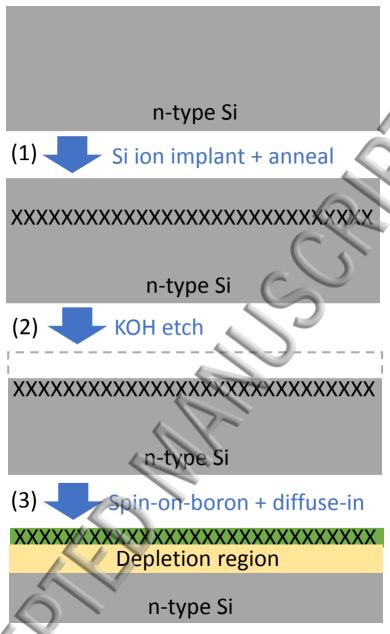

Four different sample types were fashioned from prime <100> single-crystal Si wafers (n-type, 5-10  $\Omega$  cm). Ion-implantation of <sup>28</sup>Si ions was carried out on a Varian VIISta ion implanter at beam energy 2 MeV. Two wafers received a fluence of  $2x10^{15}$  ions cm<sup>-2</sup> and two others received  $6x10^{15}$  ions cm<sup>-2</sup>. Wafers received thermal annealing in nitrogen in a furnace at 900°C for a time of either 20 or 60 mins, before being diced into squares. Along with a non-implanted control wafer, samples were then thinned by etching in 25% KOH solution at 60°C, to precisely remove the top 1.5 µm of the wafer. Spin-on dopant (boron) was deposited on each sample before heating

- 68 junction immediately beneath it, isolating the p-type defect-rich nano-layer from the n-type substrate. A dip in HF was applied to remove surface boron-silicate glass. The B doping profile 69

- was confirmed as being the same in all samples by differential Hall profiling [19], with a 70

- relatively flat doping peak. This confirmed the junction depth as being ~800 nm, to coincide with 71

- the bottom of the defective layer and that the thickness of pristine Si remaining at the top of the 72

- film was only ~30-45 nm. Fig. 1 provides a schematic illustration of the steps used for sample 73

75

76 Figure 1. Schematic diagram showing the sample fabrication steps. The Si wafers underwent Si ion-implantation and annealing to create a sub-surface nano-layer rich in defects (represented by Xs). Following removal of the wafer 77 78 surface by KOH etching, the nano-layer was doped p-type, creating a p/n junction and isolating it from the n-type substrate. 79

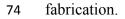

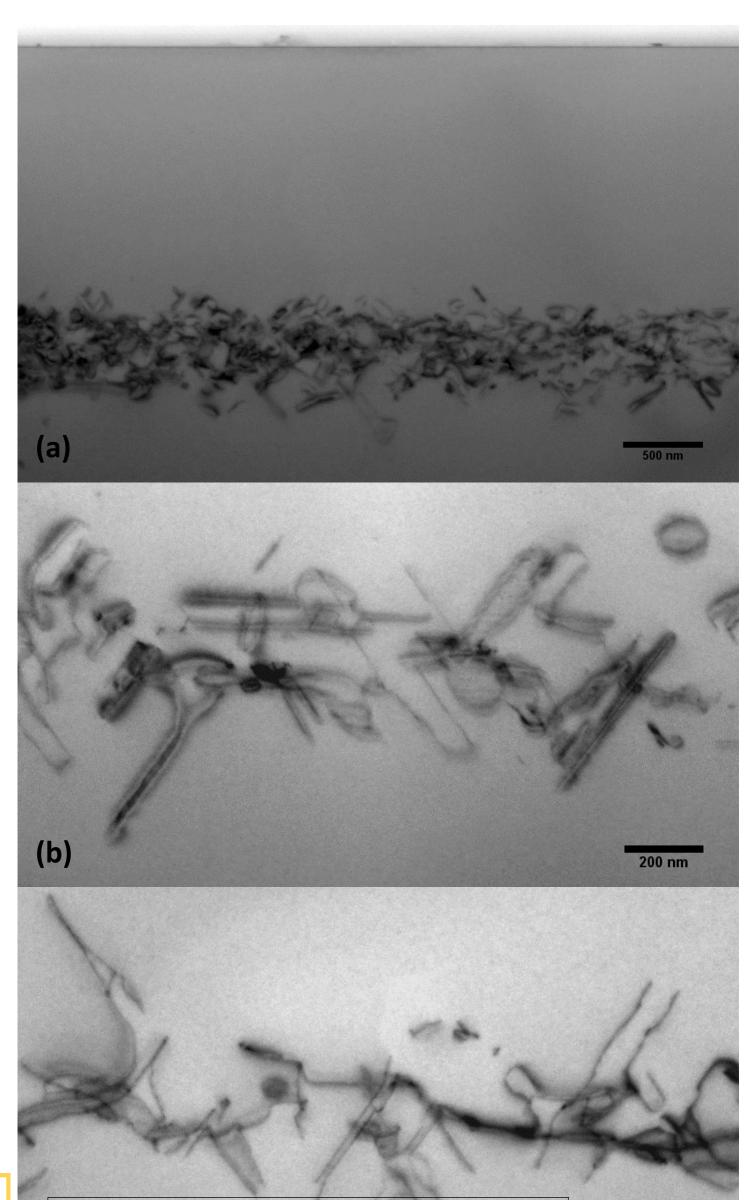

80 Each sample underwent characterization. The presence and nature of defects in the nano-layers were characterized by cross-sectional transmission electron microscopy (XTEM). Micrographs of 81 each of the samples created are presented in Fig. 2. Fig. 2(a) shows the location of the buried 82

## This manuscript was accepted by Appl. Phys. Lett. Click here to see the version of record.

Publishinger relative to the original wafer surface. The remaining micrographs show shows defects

Pa.

91

created with each of the four implant/annealing conditions. All micrographs show clear evidence 84 of dislocation loops and implantation extended defects, with the higher implant dose creating a 85 higher density of defects. Samples were sent to a commercial vendor for through-plane thermal 86 conductivity measurements. These were extracted by a thermo-reflectance method. Electrical 87 conductivity, Hall-effect and differential Hall measurements were made in air in van der Pauw 88 geometry, using a Biorad HL5900 tool. Temperature-dependent electrical conductivity and 89 Seebeck measurements were made in-plane on a Linseis LSR-3 instrument in He ambient at 10<sup>4</sup> 90

This manuscript was accepted by Appl. Phys. Lett. Click here to see the version of record.

92

Figure 2. Micrographs showing sub-surface defect-rich regions created in the Si wafers. (a) Shows the layer

location relative to the wafer surface (scale bar is 500 nm). (b) Shows defects created with 2 x 10<sup>15</sup> cm<sup>-2</sup> implant,

900°C, 20 mins annealing. (c) Shows defects created with 2 x 10<sup>15</sup> cm<sup>-2</sup> implant, 900°C, 60 mins annealing. (d)

Shows defects created with 6 x 10<sup>15</sup> cm<sup>-2</sup> implant, 900°C, 20 mins annealing. (e) Shows defects created with 6 x 10<sup>15</sup>

cm<sup>-2</sup> implant, 900°C, 60 mins annealing. (Scale bars in (b)-(e) are 200nm).

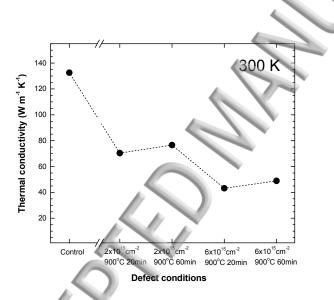

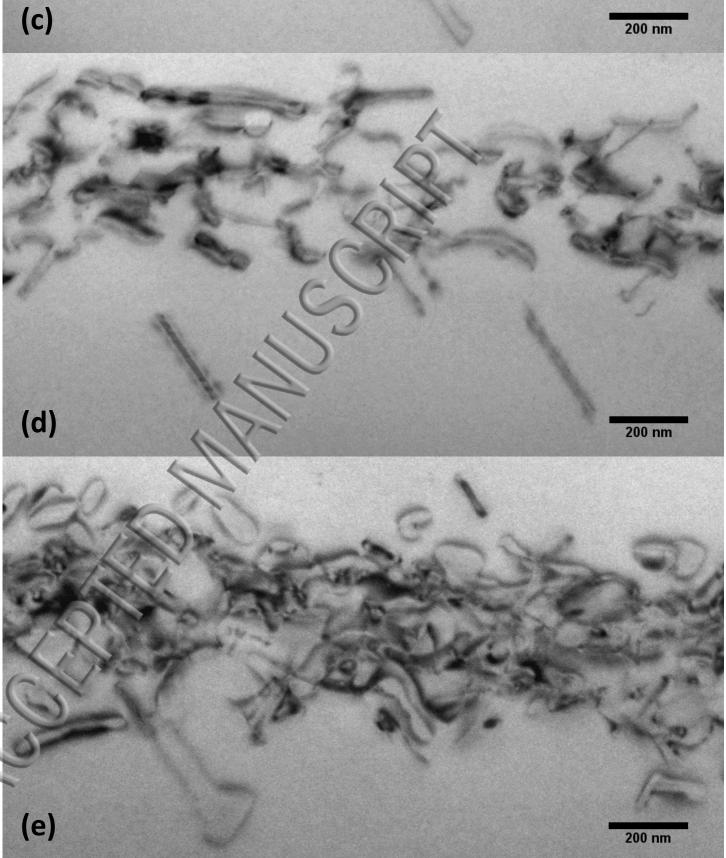

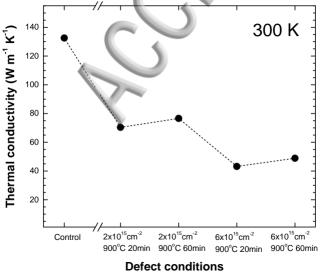

upishing 3 shows the variation with implant/annealing conditions for through-plane thermal conductivity at 300 K.  $\kappa$  was 132.6 W m<sup>-1</sup> K<sup>-1</sup> for the defect-free control sample and was found 99 to decrease significantly as a result of implantation-induced damage.  $\kappa$  fell to a value of 70.4 W 100 m<sup>-1</sup> K<sup>-1</sup> for the lower implantation fluence with 20 min annealing, but recovered slightly to 76.6 101 W m<sup>-1</sup> K<sup>-1</sup> following annealing for 60 min. This was an expected result since it is both intuitive 102 and well-established that the introduction of defects within a 'perfect' crystal lattice reduces its 103 thermal transport, and that with longer annealing, more damage will be removed and recovery of 104 thermal transport will occur. For the larger fluence,  $\kappa$  was reduced more, to 43.2 W m<sup>-1</sup> K<sup>-1</sup> for 105 20 min annealing and to 48.9 W  $m^{-1}$  K<sup>-1</sup> with 60 min annealing. 106

107

Figure 3. Thermal conductivity (through-plane) as a function of implant/annealing conditions for a control sample

relative to samples with 2 MeV Si implant with (i) 2 x 10<sup>15</sup> cm<sup>-2</sup> fluence, 900°C, 20 mins annealing, (ii) 2 x 10<sup>15</sup> cm<sup>-2</sup>

fluence, 900°C, 60 mins annealing, (iii) 6 x 10<sup>15</sup> cm<sup>-2</sup> fluence, 900°C, 20 mins annealing, and (iv) 6 x 10<sup>15</sup> cm<sup>-2</sup>

fluence, 900°C, 60 mins annealing. Measurements were made at 300 K.

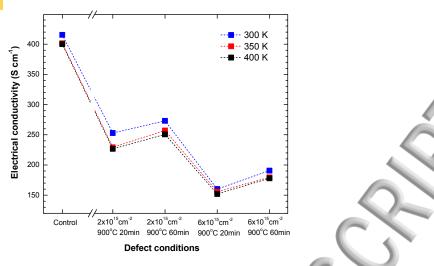

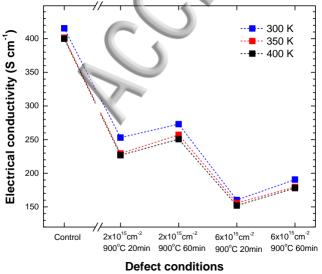

Fig. 4 shows the change in *σ* in each sample as a function of the conditions used to create

defects. Results are displayed for measurements made at 300, 350 and 400 K, although

Publishidigerences as a result of temperature were modest in these samples, with only a small conductivity decrease seen in each sample as the measurement temperature is raised. More 115 obvious was the change in conductivity as the implant/annealing conditions were changed. 116 Clearly the control sample had the highest  $\sigma$  of 415 S cm<sup>-1</sup>. For the lower of the implant fluences, 117 conductivity was reduced relative to the control, and for the higher fluence, conductivity was 118 reduced to less than half. For each fluence, it was the sample that received the shortest anneal 119 that had the lowest conductivity. These trends are intuitive and it is unsurprising that trends in 120 electrical conductivity match those in thermal conductivity (Fig. 3). These trends are similar in 121 magnitude, i.e. as thermal conductivity is reduced for a given condition, so is electrical 122 conductivity by a similar extent, suggesting little net gain in electrical/thermal transport behavior 123 results from the introduction of dislocations, each quantity being reduced by a factor of  $\sim 3$ . It is 124 worth mentioning that XTEM images – particularly Fig. 2(d) and 2(e) – are perhaps deceiving, 125 as one might expect the electrical/thermal conductivity to be lower for the sample in Fig. 2(e) 126 127 where defects are more apparent. This is opposite to what is measured. In reality, samples having received shorter anneals contain the most defects and lower electrical/thermal conductivity, yet 128 these defects are in the form of smaller Si-interstitial clusters, not visible in the XTEM at its 129 current resolution. 130

131

Figure 4. Electrical conductivity (in-plane) as a function of ion-implantation condition and annealing time, for three

measurement temperatures (300 K - 400 K).

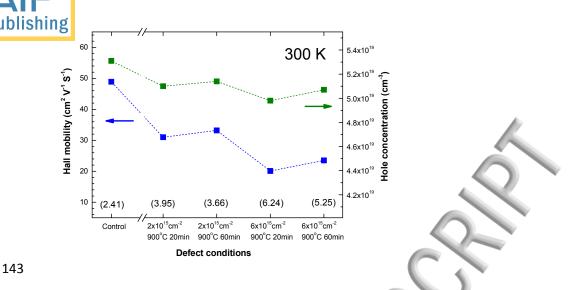

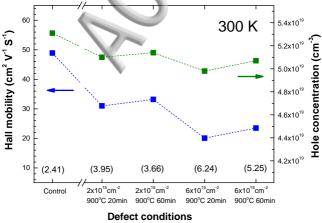

Fig. 5 gives further detail of the room-temperature  $\sigma$  by way of Hall measurement data. Carrier 134 concentration and Hall mobility at 300 K are presented. They show that defect-mediated 135 decreases in  $\sigma$  are a result of a fall in both Hall mobility and carrier concentration, though the 136 former drop is more significant. Crystallographic defects are well known to degrade carrier 137 mobility in Si and this clearly occurs in current samples. B dopant activation is highest in the 138 control sample following drive-in, whereas defects reduce the carrier concentration by up to 139 10%. Since B is well-known to cluster with self-interstitials it is likely that their presence during 140 the drive-in phase means a proportion of the dopants are trapped in inactive clusters rather than 141 finding substitutional sites. B activation improves slightly after longer-duration annealing. 142

Figure 5. Hall mobility (left axis) and hole concentration (right) as a function of defect conditions. Measurements

were made at 300 K. Values in parentheses are corresponding resistivity values in mΩ cm.

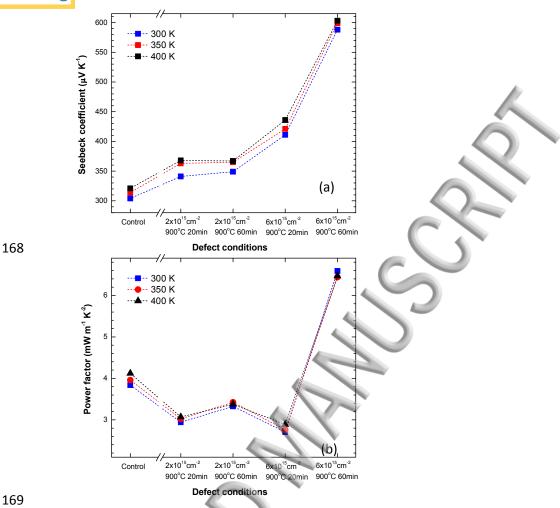

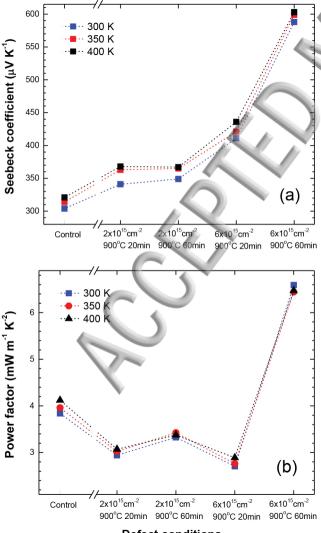

In-plane Seebeck coefficient measurements were carried out for each of the samples. Results are 146 displayed for measurements made at 300, 350 and 400 K, although as for  $\sigma$ , temperature-147 dependent differences are modest, with only a small S increase seen in each sample as the 148 measurement temperature is raised. In this case S was lowest in the control sample (Fig. 6(a)), 149 though this was expected since that sample had the highest electrical conductivity and the two 150 parameters are interrelated, with one usually increasing at the expense of the other. Combining 151 the two in the form of the power factor gives an indication of the net thermoelectric performance, 152 with  $PF = 3.8 \text{ mW m}^{-1} \text{ K}^{-2}$  at 300 K for the control sample (Fig. 6(b)). This *PF* value is in line 153 with the highest value pristine Si can provide under optimal doping conditions. All other 154 samples, with lower electrical conductivity, have a higher Seebeck coefficient. The two samples 155 receiving the lower implant dose  $(2x10^{15} \text{ cm}^{-2})$  have modestly higher S that, when combined with 156  $\sigma$ , result in a significantly lower thermoelectric *PF* than the control sample. For the higher 157 implant fluence  $(6x10^{15} \text{ cm}^{-2})$  with 20 min annealing the *PF* is worse still, since the relatively 158

**Publishing** I rise in S is more than negated by the much larger drop in  $\sigma$ . An interesting result occurs however, when the higher fluence sample is annealed for longer, resulting in the formation of a 160 dense network of mostly dislocation-loops with diameters roughly between 100 nm and 200 nm 161 (Fig. 2(e)). In this case the increase in S is much greater than for all other samples and bucks the 162 trend, since given its higher electrical conductivity than the previously mentioned sample, one 163 would expect its Seebeck coefficient to decrease. In fact, as the reader can see, not only is the 164 opposite true, but the increase in S is significant. This has a striking effect on the power factor, 165 which is now on average 70% higher than that of the control sample, with  $PF = 6.6 \text{ mW m}^{-1} \text{ K}^{-2}$ 166 at 300 K. 167

Figure 6. (a) Seebeck coefficient (in-plane) and (b) power factor as a function of defect conditions for three

measurement temperatures (300 K - 400 K).

The simultaneous increase in  $\sigma$  and S is rare, but significant, and results in improved power factors. It is similar to that observed in reference [14] for heavily B-doped nano-crystalline Si, again under high-temperature annealing. While the underlying reasons behind this are still under investigation, it is possible that a number of contributing factors coexist and act synergistically in order to achieve a simultaneous S and  $\sigma$  improvement. For the former, it is probable that potential barriers for holes are created at the dislocation sites, which improve energy filtering and consequently S. Indeed, when present within the crystal lattice, dislocation loops are known to

Putpishievert a significant pressure by pushing-apart nearby Si atoms – this pressure increasing the bandgap local to the dislocation site [20]. For the first annealing condition, this local band-gap 180 increase could be responsible for the reduction in conductivity and mobility. As well as allowing 181 loops to form, longer annealing would heal the majority of the Si volume, and thus a slight 182 increase in the electrical conductivity is observed, compensating for any further reduction from 183 the increasing potential barriers. The increased pressure may also improve carrier mobility, a 184 well-known consequence of applying stress in Si [21]. In addition, any local thermal 185 conductivity differences between pristine Si regions and the dislocations might improve S as 186 well. This is because the overall Seebeck coefficient is determined by the weighted average of S 187 in the two regions, with the weighting factor being the temperature drop in each region, 188 determined by their thermal conductivities [14, 22]. Thus, as the crystal lattice is healed, 189 especially in the last annealing step, and local thermal conductivity increases, the local Seebeck 190 coefficient in the dislocation regions (which is expected to be high compared to bulk Si) 191 becomes more important and could warrant the large increase in the overall S observed in Fig. 192 6(a). Our earlier calculations on the effect of filtering by barriers in p-type Si, indicate that 193 filtering alone could provide ~30-40% PF improvements [22, 23], whereas the rest of the 194 measured improvements could originate from the various other factors identified, such as local 195 variations in thermal conductivity and carrier mobility. 196

We have reported a significant enhancement in the power factor of single-crystal Si is possible for highly-doped p-type material, specifically an improvement of ~70 % compared to control samples (bulk Si), giving PF = 6.6 mW m<sup>-1</sup> K<sup>-2</sup> at 300 K. This is higher than that of traditional Bi<sub>2</sub>Te<sub>3</sub> materials used in commercial thermoelectric devices [24] and is a consequence of the introduction of a dense network of dislocation loops with diameter

Publishibg veen 100 nm and 200 nm. Despite these defects causing reductions in electrical 203 conductivity, carrier concentration and carrier mobility, large corresponding increases in 204 Seebeck coefficient and reductions in thermal conductivity lead to a significant net 205 enhancement in thermoelectric performance. This finding provides a route to significant 206 gains in the thermoelectric power factor of Si, a material that potentially offers a path to 207 more cost-effective and environmentally-friendly thermoelectric devices.

## 208 Acknowledgements

- NSB, DB and AC thank Science Foundation Ireland for partial support of this work through

- 210 grant 12/TIDA/E2378 and the Royal Society for supporting research exchange through grant

- 211 IE131212. NN acknowledges funding from the European Research Council (ERC) under the

- European Union's Horizon 2020 research and innovation programme (grant agreement No

- 213 678763). Dr Jan-Willem Bos of Heriot-Watt University is gratefully acknowledged for access to

- 214 Seebeck measurement facilities.

## 215 **References**

- [1] L. Weber and E. Gmelin, Transport properties of silicon. Appl. Phys. A 53 (1991) 136–140.

- 217 [2] S. Leblanc, S. K. Yee, M. L. Scullin, C. Dames, and K. E. Goodson, Material and

- manufacturing cost considerations for thermoelectrics, Renewable and Sustainable Energy

Reviews 32 (2014) 313.

- [3] A. I. Hochbaum, R. Chen, R. D. Delgado, W. Liang, E. C. Garnett, M. Najarian, A.

Majumdar, and P. D. Yang, Enhanced thermoelectric performance of rough silicon nanowires,

Nature 451 (2008) 163–167.

22Bishi [4] A. I. Boukai, Y. Bunimovich, K. J. Tahir, J. Yu, W. A. Goddard, and J. R. Heath, Silicon

- nanowires as efficient thermoelectric materials, Nature 451 (2008) 168–171.

- [5] G. Pennelli, and M. Macucci, Optimization of the thermoelectric properties of nanostructured

- 226 silicon, J. Appl. Phys. 114 (2013) 214507.

- [6] E. B. Ramayya, L. N. Maurer, A. H. Davoody, and I. Knezevic, Thermoelectric properties of

- ultrathin silicon nanowires, Phys. Rev. B 86 (2012) 115328.

- [7] I. Bejenari and P. Kratzer, Atomistic calculation of the thermoelectric properties of Si

- 230 nanowires, Phys. Rev. B 90 (2014) 045429.

- 231 [8] W. Liu, K. Etessam-Yazdani, R. Hussin, and M. Asheghi, Modeling and Data for Thermal

- 232 Conductivity of Ultrathin Single-Crystal SQI Layers at High Temperature. IEEE Transactions on

- electron devices 53 (8) (2006) 1868.

- [9] J. Tang, H. Wang, D. H. Lee, M. Fardy, Z. Huo, T. P. Russell, and P. Yang, Holey silicon as

- an efficient thermoelectric material, Nano Lett. 10 (2010) 4279-4283.

- 236 [10] J.-K. Yu, S. Mitrovic, D. Tham, J. Varghese, and J. R. Heath, Reduction of thermal

- conductivity in phononic nanomesh structures, Nature Nanotechnology 5 (2010) 718–721.

- 238 [11] P. E. Hopkins, C. M. Reinke, M. F. Su, R. H. Olsson III, E. A. Shaner, Z. C. Leseman, J. R.

- 239 Serrano, L. M. Phinney, and I. El-Kady, Reduction in the Thermal Conductivity of Single

- 240 Crystalline Silicon by Phononic Crystal Patterning, Nano Lett. 11 (2011) 107-112.

- [12] B. Xu and K. Fobelets, Spin-on-doping for output power improvement of silicon nanowire

array based thermoelectric power generators, J. Appl. Phys. 115 (2014) 214306.

delishing N. S. Bennett, N. W. Wight, S. R. Popuri, and J.-W. G. Bos, Efficient thermoelectric

- 244 performance in silicon nano-films by vacancy-engineering, Nano Energy 16 (2015) 350-356.

- [14] N. Neophytou, X. Zianni, H. Kosina, S. Frabboni, B. Lorenzi, and D. Narducci,

- 246 Simultaneous increase in electrical conductivity and Seebeck coefficient in highly Boron-doped

- 247 nanocrystalline Si, Nanotechnology 24 (2013) 205402.

- 248 [15] N. Neophytou, X. Zianni, H. Kosina, S. Frabboni, B. Lorenzi, and D. Narducci, Power

- 249 factor enhancement by inhomogeneous distribution of dopants in two-phase nanocrystalline

- systems, Journal of Electronic Materials 43 (6) (2014) 1896-1904.

- 251 [16] D. Narducci, B. Lorenzi, X. Zianni, N. Neophytou, S. Frabboni, G. C. Gazzadi, A.

- 252 Roncaglia, and F. Suriano, Enhancement of the power factor in two-phase silicon-boron

- nanocrystalline alloys, Physica status solidi a 211 (6) (2014) 1255-1258.

- 254 [17] B. Lorenzi, D. Narducci, R. Tonini, S. Frabboni, G.C. Gazzadi, G. Ottaviani, N.

- 255 Neophytou, X. Zianni, Paradoxical enhancement of the power factor in polycrystalline silicon

- due to the formation of nanovoids, Journal of Electronic Materials 43 (10) (2014) 3812-3816.

- 257 [18] N. S. Bennett, D. Byrne and A. Cowley, Enhanced Seebeck coefficient in silicon nanowires

- containing dislocations, Appl. Phys. Lett. 107 (2015) 013903.

- 259 [19] N. S. Bennett and N. E. B. Cowern, Doping characterization for germanium-based

- 260 microelectronics and photovoltaics using the differential Hall technique, Appl. Phys. Lett. 100

261 (2012) 172106.

- [20] K. P. Homewood and M. A. Lourenço, Light from Si via dislocation loops, Materials Today

8 (1) (2005) 34-39.

delishi [28] M. L. Lee, E. A. Fitzgerald, M. T. Bulsara, M. T. Currie and A. Lochtefeld, Strained Si,

- SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors, J.

- 266 Appl. Phys. 97 (2005) 011101.

- 267 [22] R. Kim and M. S. Lundstrom, Computational study of energy filtering effects in one-

- dimensional composite nano-structures, J. Appl. Phys. 111 (2012) 024508.

- [23] N. Neophytou and H. Kosina, Optimizing Thermoelectric Energy Filtering by Means of a

- 270 Potential Barrier, J. Appl. Phys., 114 (2013) 044315.

- [24] "Thermoelectric Energy Harvesting 2016-2026: Devices, Applications, Opportunities",

- 272 IDTechEx Report by H. Zervos, updated June 2016, www.idtechex.com

Defect conditions