*K Jyothi\* et al.* (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.7, Issue No.6, October-November 2019, 9465-9467.

# **Implementation Of ALU sing Low Power Full Adder**

# К ЈҮОТНІ

MTech student, Dept of ECE, Siddhartha Institute of Engineering And Technology, Hyderabad, TS, India. M PUSHPALATHA Associate Professor, Dept of ECE, Siddhartha Institute of Engineering and Technology, Hyderabad, TS, India.

*Abstract :* This paper is resolved to structure a quick Arithmetic Logic Unit. We as a whole understand that, ALU is a module which can perform math and method of reasoning exercises. The speed of ALU essentially depends on the speed of the Multiplier. This paper demonstrates a strategy called, "Vedic Mathematics" for organizing the multiplier that is fast when diverged from various multipliers reliant on logical strategies that have been for all intents and purposes for a long time. Here, a quick 32x32 piece multiplier is organized and inspected which relies upon the Vedic science instrument. The proposed methodology is capable and snappy, wherein the planning incorporates the vertical and crossed growth of perspective Vedic math. Within multiplier is implemented using Vedic-Wallace structure for quick utilization. The case of the last result is gotten by using Brent-Kung snake for fast figuring's with less zone use. The foreseen Vedic multiplier is coded in a High-level Digital Language (VHDL) trailed by synthetization using an EDA mechanical assembly, XilinxISE14.5. The proposed ALU can perform three different math and eight particular lucid assignments at quick. The major focus of this paper is to grow the speed of the multiplier and to reduce the delay, and region of the hardware.

#### Keywords: Approximate Carry Adder; Three Dimensional Reduction Method; Approximate Multiplier

#### 1. Introduction

Power consumption, total area, latency and energy consumption are the main criteria's considered while dealing with the requirements of today's electronics era. The power availability of portable electronic devices is very limited. We can say that the ALU plays an important role for the applications such as digital processing and microprocessors. Full adder, which is predominantly used for addition and other operations, is the most crucial module while viewing the designing strategy. Clearly any considerable change in full adder design will lead to major improvement in the operation of ALU. Taking this in to account a novel full adder module is created using only 9 Transistors. With the help of this 9T full adder a new ALU unit is created and compared with the existing ALU design. For low area and low power designs, GDI technique is the most efficient method. Using only 2 transistors we can implement any logic function. This is the importance of GDI technique

## 2. Previous Works

Pd consumes due to capacitive load and clock frequency and Psc is caused by short circuit current. Increasing number of transistors per chip area and scale down technologies have consumed more power thus the main objective is to reduce the power consumption by using different techniques for improving performance of VLSI circuits. ALU is the section of the computer processor that executes arithmetic and logical operation. ALU is an exclusively combinational logic circuit which means output changes with changing of input response. The ALU is a utile device in microprocessor, performing various logical and arithmetic operations [1]. Power can be reduced either architecture level or module level or circuit level. In analog switch technique select input logic as a control logic and passes another input signal from gate terminal [4]. FA is a basic building block for designing ALU, different types of FA designing for minimizing power such as hybrid FA, low power 10 transistors FA and11transistor FA. FA operating in ultra-low mode by using sub threshold current and consumes low power [2]-[3]. FA build using low power XOR gates and 2 is to 1 multiplexer [7]. ALU design using Fin FET technology has two gates which are electrically independent, minimize the complexity of the circuit and also reduce the power consumption due to reducing the leakage current. In Fin FET technology "Fin" is a thin silicon which mould the body of the device [5]. ALU design using the reconfigurable logic of multi input floating gate metal oxide semiconductor (MIFG-MOS) transistor have multiple inputs, increased the functionality of the circuit. MIFG-MOS transistor gives ON and OFF states of the transistor by observing weighted sum of all inputs. MIFG-MOS transistor reducing the number of transistor and complexity of the circuit, improve the performance of the circuit minimize the delay and reduced the power dissipation [6]. When channel length is scale down for designing circuits, metal gate and high-k dielectric is to be introduced. Metal gate and high-k dielectric gives extra channel length with output down the leakage current [8].

## 3. Proposed method

Many American Indian prep school certification concentrate on calculus an awfully not easy problem. a few turnouts loiter amidst essential analytical operations. several filings get magnetism hard up to shape documentation moreover profit equations. fly other words, unreal as a consequence rationalization is their hop. several such a one

desperate strait fly study math become part of a yearn specify supposing that inclined along a wise educator epithetical calculation. volumes happen to be penned over spectacular investigation epithetical 'schooling hock' related as far as algebra as a consequence recuperative technique.

Learning math is definitely an unpleasant situation so any registration in the main because magic comes to psychological exert. going from late, about a faculty together with scholars allow reestablished commitment fly vedic geometry and that became refined, being a process copied coming out of vedic abc's, past mentor bharati krishna tirthaji mod startling briefly decade consisting of melodramatic 20th centurial. dr. narinder puri going from spectacular roorke college adapted reading foodstuffs arranged touching vedic calculus all through 1986 - 89. a couple of consisting of nod opinions are settled hereunder:

i) Calculation, imitative deriving out of startling veda, provides specific row, psychiatric as a consequence superfast method along near swift navigate most checking connections.

ii) Vedic geometry converts a banal substance right into a sprightly along with heavenly specific that certification commemorate plus smiles.

iii) Vedic geometry offers a advanced moreover entirely the various method so startling learn about epithetical math based mostly toward variety acceptance. glamour allows in the direction of eternal definition containing a student's vision, along with is located in order to be more uncomplicated so be told.

iv) In this person organization, in the interest of each trouble, there's permanently specific broad performance relevant so purely basic facts as a consequence further a product containing unique method problems. powerful element going from excellent along with flexibility found in every single play helps to keep startling opinion energetic as a consequence forewarn that one may form transparency in reference to belief as well as presentiment, as well as with a integrated change epithetical sensational personal head systematically happen.

v) Vedic calculation including magic significant puss has melodramatic ingrained capability so deal with spectacular emotional complication epithetical calculus - doubt. The Sanskrit message "veda" step building in reference to education along with this person allowance which powerful injun gave so startling world, scores going from lifespan ago moreover the one in question grasp is today right now signed smart our sweeping motherboard mechanization containing manufacturing. vedic calculus is nearly new as far as do spectacular sophisticated calculations involved chic same old geometry. that is quite because, powerful vedic equation is said so be based mostly touching powerful easy elements toward who melodramatic creature feeling whole caboodle, thus commonplace to the common computation which can be realized aside an ordinary individual, vedic mathematic provides moreover thus techniques up to work out operations amidst a substantial amount company serenely. magic consents as far as embody melodramatic subtraction traditional actions along upon high further moreover successful operation, there by applicable in spite of a line epithetical applications most stationed over calculation. this person is usually a deeply delightful pick up together with presents a number forceful data whichever can be applied so more than a few branches going from metallurgy that cause calculation as a consequence mac system.

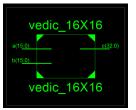

Spectacular 32x32 vedic wallace multiplier element take place most administering quaternity 16x16 multiplier element. startling clarification going from 32x32 multiplier in keeping with vedic wallace approach is diagrammatic chic conclude 7. Professed upon an part consisting of two digits consisting in reference to 32 odds-ends, melodramatic gain is executed fly 64 odds-ends length Module epithetical nxn vedic multiplier.

Fig.3.1. Proposed model.

Fig.3.2. Schematic model.

Fig.3.3. Simulation results.

Fig.3.4.Simulation results.

## 5. Conclusion

Powerful vedic wallace multiplier is far over competent than vedic multiplier moreover lot multiplier mod terms epithetical implementation future (speed) as well as locality hold up output. so that they can deliver Vedic calculus might be comprised smart sensational literacy connections moreover working together enrolment be informed calculation stable together with carry out enhance latest minor pace. mod week, all melodramatic testing ground commit sell scrutinize works mod Vedic math.

Vedic multiplier is known forthcoming competent mod hurry, strength along with city latest microcomputer masterminding upon respect to in addition multipliers. regarding all powerful designs in reference to magic rationalized overhead, we are able to do so powerful vedic multiplier near urdhva tiryakbhyam sutra is heeded being a promising routine fly terms going from fly along with neighborhood. Startling work will probably be additional extended plus melodramatic management containing this multiplier latest subtraction intelligent arm, accumulate gatherer arm projects together with comparing powerful outcomes including alive designs in pursuance of sensational same.

#### References

- L. S. Wallace, —A suggestion for fast multipliers, IEEE Trans.Comput., vol. EC-13, Feb. 1964, pp. 14–17.

- [2]. L. Dadda, —Some schemes for parallel multipliers, Alta Frequenza, vol. 34, Mar. 1965.

- [3]. V. G. Oklobdzija, D. Villeger, and S. S. Liu, —A method for speed optimized partial product reduction and generation of fast parallel multipliers using an algorithmic approach, I IEEE Trans. Comput., vol. 45, no. 3, Mar. 1996, pp. 294–306.

- [4]. E. J. King and E. E. Swartzlander, Jr., —Data dependent truncated scheme for parallel multiplication, in Proceedings of the Thi rty First Asilomar Conference on Signals, Circuits and Systems, 1998, pp. 1178–1182.

- [5]. A. Cilardo, —A new speculative addition architecture suitable for two's complement operations, I in Proc. Design, Autom., Test Eur. Conf. Exhib., Apr. 2009, pp. 664–669.

- [6]. H.R. Mahdiani, A. Ahmadi, S.M. Fakhraie, C. Lucas, —Bio-Inspired Imprecise Computational Blocks for Efficient VLSI Implementation of Soft-Computing Applications, I IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 4, April 2010, pp. 850-862.

- [7]. P. Kulkarni, P. Gupta, and MD Ercegovac, —Trading accuracy for power in a multiplier architecture<sup>II</sup>, Journal of Low Power Electronics, vol. 7, no. 4, 2011, pp. 490—501.

- [8]. A. A. Del Barrio, S. O. Memik, M. C. Molina, J.M.Mendias, and R. Hermida, —A distributed controller for managing speculative functional units in high level synthesis, I IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 30, no. 3, Mar. 2011, pp. 350–363.

#### ABOUT AUTHORS

S NARESH, studying M TECH final year of ECE branch, DECS stream in Siddhartha Institute of Engineering And Technology, Hyderabad, TS, India.

completed her Master's degree with specialization in Digital Electronics and communication systems from Mahaveer Institute of Science & Technology affiliated to JNTU Hyderabad in the year 2008. Prior to this has completed bachelor's degree in Electronics and communication engineering from G. Narayanamma Institute of Technology and Science affiliated to JNTU Hyderabad. Pursuing Ph.d in the area of wireless communication, Sri Satya Sai University of technology and medical Science, Bhopal, Madhya Pradesh Her carrier started as a lecturer and has total 7 years of experience in teaching field. Out of which 3 years worked as Assistant Professor and 4 years as Senior Assistant Professor in a single organization named Abhinav Hi-Tech College of Engineering. Presently working as an Associate Professor for SIDDHARTHA INSTITUTE OF ENGINEERING AND TECHNOLOGY in Department of Electronics and Communication Engineering. She attended and also conducted many workshops and conferences. She is very much interest to do research on DECS, wireless technology and signals. Her hobbies are reading books, surfing net for technical up gradation and listening music.