# FPGA-Based Implementation of Finite Set-MPC for a VSI System Using XSG-Based Modeling

| 著者                | Singh Vijay Kumar, Tripathi Ravi Nath,<br>Hanamoto Tsuyoshi |

|-------------------|-------------------------------------------------------------|

| journal or        | Energies                                                    |

| publication title |                                                             |

| volume            | 13                                                          |

| number            | 1                                                           |

| page range        | 260-1-260-18                                                |

| year              | 2020-01-04                                                  |

| URL               | http://hdl.handle.net/10228/00007591                        |

doi: info:doi/10.3390/en13010260

# Article FPGA-Based Implementation of Finite Set-MPC for a VSI System Using XSG-Based Modeling

# Vijay Kumar Singh<sup>1,\*</sup>, Ravi Nath Tripathi<sup>2</sup> and Tsuyoshi Hanamoto<sup>1</sup>

- <sup>1</sup> Graduate School of Life Science and Systems Engineering, Kyushu Institute of Technology, Fukuoka 808-0196, Japan; hanamoto@life.kyutech.ac.jp

- <sup>2</sup> Next Generation Power Electronics Research Center, Kyushu Institute of Technology, Fukuoka 808-0196, Japan; ravi1989tripathi@gmail.com

- \* Correspondence: singh.vijay-kumar378@mail.kyutech.jp or vijay.ec1985@gmail.com; Tel.: +81-906-736-9768

Received: 12 November 2019; Accepted: 2 January 2020; Published: 4 January 2020

Abstract: Finite set-model predictive control (FS-MPC) is used for power converters and drives having unique advantages as compared to the conventional control strategies. However, the computational burden of the FS-MPC is a primary concern for real-time implementation. Field programmable gate array (FPGA) is an alternative and exciting solution for real-time implementation because of the parallel processing capability, as well as, discrete nature of the hardware platform. Nevertheless, FPGA is capable of handling the computational requirements for the FS-MPC implementation, however, the system development involves multiple steps that lead to the time-consuming debugging process. Moreover, specific hardware coding skill makes it more complex corresponding to an increase in system complexity that leads to a tedious task for system development. This paper presents an FPGA-based experimental implementation of FS-MPC using the system modeling approach. Furthermore, a comparative analysis of FS-MPC in stationary  $\alpha\beta$  and rotating dq frame is considered for simulation as well as experimental result. The FS-MPC for a three-phase voltage source inverter (VSI) system is developed in a realistic digital simulator integrated with MATLAB-Simulink. The simulated controller model is further used for experimental system implementation and validation using Xilinx FPGA: Zedboard Zynq Evaluation and Development Kit. The digital simulator termed as Xilinx system generator (XSG) provided by Xilinx is used for modeling-based FPGA design.

**Keywords:** field-programmable gate array; finite set-model predictive control; model-based design; voltage source inverter; Xilinx system generator

# 1. Introduction

Model predictive control (MPC) possess appealing characteristics such as flexibility of simultaneous handling of multiple constraints and easy inclusion of nonlinearities [1–4]. This leads to considerable attention to exploit the characteristics of MPC for a wide variety of applications. However, it suffers from the problem of high computation requirement that results in real-time implementation problems. Despite the fact of high computational requirement, the real-time implementation of predictive control for power converters is of considerable interest to improve the dynamic performance as well as to optimize the entire system performance by including additional constraints. MPC has been applied for two-level voltage source inverter (VSI) [5,6], three-level neutral-point clamped converter (NPC) [2,7], active front end rectifier [8,9], cascaded H-Bridge inverter [10–12], asymmetric flying capacitor converter [13], three-phase direct Matrix converters [14,15], predictive control for UPS applications [16,17], predictive torque control (PTC), and field oriented control (FOC) of an induction machine [2,18], to name a few.

The fundamental approach behind the MPC is to have an appropriate plant or system model for the prediction of the future behavior of control parameters. Finite set-model predictive control (FS-MPC), also known as finite control set-MPC, is a classification of MPC which utilizes a discrete-time model of power converter having a limited number of switching states for solving the optimization problem and the control action can be directly applied to the converter without the need of external modulator [2,9]. This method reduces the computational loads up to some extent as compared to generalized MPC method by considering the discrete nature of the power converter model. The optimization function (cost function) for FS-MPC is designed considering the primary control objectives such as current, voltage, or power and any additional constraints. In general, the cost function is formulated based on the stationary  $\alpha\beta$  co-ordinates [19,20]. Considering current control with FS-MPC, the sinusoidal future current references need to be predicted accurately using an extrapolation method, however, the extrapolated reference causes unwanted oscillations that influence the transient response [7,9,19]. Considering the above issue, the cost function can be designed using a rotating dq frame that does not require extrapolation method because of continuous current references [19]. However, the comparative analysis based on design constraints and performance indices is required to be addressed for two frames. Furthermore, the computational burden corresponding to each co-ordinate system is crucial for practical system implementation.

Because of the computational requirements, practical implementations of predictive controls for power converters mainly depend on the micro-processing solutions such as digital signal processor (DSP) [3,4,18]. The computation required for the algorithm should strictly complete within a given sampling interval. However, delay in the computation of optimum switching state is observed that deteriorates the quality of waveforms [5,21]. To cope with this issue, delay compensation techniques are necessary to compute optimum switching state within the specified sampling interval [22,23]. Nevertheless, delay compensation techniques encounter additional issues of increased computational burden and an increased average switching frequency [22].

Field programmable gate array (FPGA) is a solution of choice because of parallel processing capability and distributed on-chip logic resources [24–31]. The FPGA-based system implementation makes the system compact, cost-effective for controller prototyping, and flexible for functional interfacing of devices according to our own choices. FPGAs consist of configurable logic blocks that can be utilized to realize various designs. One of the key features of FPGAs is its flexibility in hardware programmability and addressing a broader application area [30]. However, the system implementation using FPGA requires specific programming skill that is hardware description language (HDL) coding. Designing HDL code for a particular application is a tedious and time-consuming process toward controller development and considered more cumbersome with an increase in the level of controller complexity [25,26,32].

The controller development approach is crucial considering the FPGA-based real-time system implementation with an aspect of the straightforward utilization of the product in industrial applications. The digital simulator as a realistic virtual FPGA platform is advantageous considering the controller development process that facilitates an automatic code generation through the developed system to ease the FPGA-based system implementation. Moreover, model-based design (MBD) platform of the digital simulator provides system visualization and easy debugging that is appealing for rapid controller prototyping.

Xilinx system generator (XSG) as a digital simulator adopting MBD platform was used for the step-by-step design and modeling of the FS-MPC algorithm in  $\alpha\beta$ -frame in [31] for the load current control of three-phase VSI system. The performance of the FS-MPC was analyzed through the simulations in the integrated platform of XSG and MATLAB-Simulink considering steady state response and intermediate responses with the change in the sampling time. In [33], a hardware-in-the-loop (HIL) simulation methodology was adopted for the verification of the XSG-based FS-MPC in  $\alpha\beta$ -frame for a three-phase VSI system with motor load condition. The performance was tested for the step-by-step verification through simulations considering the controller in MATLAB-Simulink, XSG, and HIL co-simulation. A comparative analysis was presented through the controller performance with the effect of sampling time and reference tracking under dynamic conditions.

This paper presents the FPGA-based real-time implementation of FS-MPC for experimental validation of controller modeled in the digital simulator (XSG). The FS-MPC is developed for a three-phase VSI system with RL load using an optimization function consisting of current control objectives considering both stationary  $\alpha\beta$  and rotating dq reference frames for comparative analysis. The functionality of MBD platform is demonstrated through some intermediate responses for the controller development in both frames. In addition, the change in reference current is considered for transient behavior and dynamic response analysis. The computational requirements for both frames based on an FPGA resource sharing are used for comparative analysis. The FPGA board used for the experimental system is the Zedboard Zynq Evaluation and Development Kit.

Other sections of this paper are organized as follows: Section 2 describes the algorithm of FS-MPC in both  $\alpha\beta$  and dq frames considering the discrete-time mathematical model of the three-phase VSI system. In Section 3, the model-based design and development of controller in the digital simulator is explained. Section 4 covers the simulation results with detailed discussion. The experimental setup and the validation of the system performance are presented in Section 5. Finally, appropriate conclusions are drawn in Section 6.

# 2. Finite Set-MPC

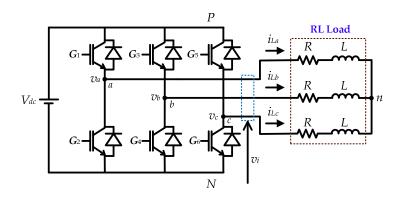

The power circuit of three-phase VSI with *RL* load is shown in Figure 1 where *R* is the load resistance and *L* is the load inductance. The FS-MPC based on current control objective uses a discrete-time model of the load current dynamic equation for the formulation of the control algorithm and deals only with a limited number of possible switching states of the power converter. The switching states of the converter are determined by the switching signals  $S_a$ ,  $S_b$ , and  $S_c$  as shown in Table 1. Considering all the possible switching combinations of the switching signals, eight switching states  $S(S_0-S_7)$  and hence, eight voltage vectors  $v_i$  ( $v_0-v_7$ ) are obtained as shown in Table 2.

Figure 1. Power circuit of three-phase VSI with RL load.

**Table 1.** Gating signals of the inverter power switches.

| Leg 'a', $S_a$               | Leg 'b', S <sub>b</sub>     | Leg ' <i>c</i> ', <i>S</i> <sub>c</sub> |

|------------------------------|-----------------------------|-----------------------------------------|

| <i>G</i> <sub>1</sub> ON, 1  | G <sub>3</sub> ON, 1        | G <sub>5</sub> ON, 1                    |

| G <sub>2</sub> OFF, 0        | G4 OFF, 0                   | G <sub>6</sub> OFF, 0                   |

| <i>G</i> <sub>1</sub> OFF, 0 | G <sub>3</sub> OFF, 0       | G5 OFF, 0                               |

| G <sub>2</sub> ON, 1         | <i>G</i> <sub>4</sub> ON, 1 | $G_6$ ON, 1                             |

| Switching States |       | tates   | Voltage Vectors                        | Index Number |  |

|------------------|-------|---------|----------------------------------------|--------------|--|

| $S = [S_a$       | $S_b$ | $S_c$ ] | $v_i = [v_{i\alpha} \; v_{i\beta}]$    |              |  |

| $S_0 = [0]$      | 0     | 0]      | $v_0 = [0, 0]$                         | 0            |  |

| $S_1 = [1$       | 0     | 0]      | $v_1 = [2V_{dc}/3, 0]$                 | 4            |  |

| $S_2 = [1$       | 1     | 0]      | $v_2 = [V_{dc}/3, \sqrt{3}V_{dc}/3]$   | 6            |  |

| $S_3 = [0]$      | 1     | 0]      | $v_3 = [-V_{dc}/3, \sqrt{3} V_{dc}/3]$ | 2            |  |

| $S_4 = [0]$      | 1     | 1]      | $v_4 = [-2V_{dc}/3, 0]$                | 3            |  |

| $S_5 = [0]$      | 0     | 1]      | $v_5 = [-V_{dc}/3, -\sqrt{3}V_{dc}/3]$ | 1            |  |

| $S_6 = [1$       | 0     | 1]      | $v_6 = [V_{dc}/3, -\sqrt{3}V_{dc}/3]$  | 5            |  |

| $S_7 = [1$       | 1     | 1]      | $v_7 = [0, 0]$                         | 7            |  |

Table 2. Voltage vectors and switching states with index number.

The load current dynamics behavior can be described by the vector differential equation as below:

$$\boldsymbol{v}_i = R\boldsymbol{i}_L + L\frac{d\boldsymbol{i}_L}{dt} \tag{1}$$

where inverter output voltage  $v_i$  is defined as a vector form in terms of the phase-to-neutral voltages of three phases *a*, *b*, *c* and expressed as follows:

$$v_i = \frac{2}{3} \left( v_{aN} + e^{j(2\pi/3)} v_{bN} + e^{j(4\pi/3)} v_{cN} \right)$$

(2)

Similarly, three-phase load currents  $i_L$  can be expressed in terms of line currents  $i_{La}$ ,  $i_{Lb}$ ,  $i_{Lc}$  of three phases as given below:

$$i_L = \frac{2}{3} \left( i_{La} + e^{j(2\pi/3)} i_{Lb} + e^{j(4\pi/3)} i_{Lc} \right)$$

(3)

#### 2.1. Discrete-Time Predictive Model

The discrete-time model of the load current dynamics (1) for a sampling time  $T_S$  represents the predictive model. It will be used to predict the future value of load currents considering all voltage vectors. The discrete-time model can be obtained by an approximation of load current derivative  $di_L/dt$  using the forward Euler discretization method given as:

$$\frac{d\mathbf{i}_L}{dt} \approx \frac{\mathbf{i}_L(k+1) - \mathbf{i}_L(k)}{T_S} \tag{4}$$

After substituting (4) into (1), an expression of predicted future load current at sampling interval k+1, is obtained for each of the seven different voltage vectors  $v_i(k)$  in  $\alpha\beta$  frame as:

$$i_{L\alpha}^{p}(k+1) = k_{1}i_{L\alpha}(k) + k_{2}v_{i\alpha}(k)$$

$$i_{L\beta}^{p}(k+1) = k_{1}i_{L\beta}(k) + k_{2}v_{i\beta}(k)$$

(5)

where  $k_1 = \left(1 - \frac{RT_s}{L}\right)$ ,  $k_2 = \frac{T_s}{L}$ .  $i^p_{L\alpha,\beta}(k+1)$ , and  $i_{L\alpha,\beta}(k)$  denotes the predicted future load currents at time k + 1 and the measured load currents at instant k, respectively, in  $\alpha\beta$ -frame. The coordinate transforms from *abc* to  $\alpha\beta$  are computed using mathematical relation defined by Clarke transformation as:

$$\begin{bmatrix} x_{\alpha} \\ x_{\beta} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} x_a \\ x_b \\ x_c \end{bmatrix}$$

(6)

where *x* can be any quantity voltage or current.

The predicted load currents in rotating *dq*-frame considering feed-forward terms for the decoupling of the *d* and *q* components of the current using forward Euler discretization is given below:

$$i_{Lq}^{p}(k+1) = k_{1}i_{Lq}(k) + k_{2}\left\{v_{id}(k) + k_{3}i_{Lq}(k)\right\}$$

$$i_{Lq}^{p}(k+1) = k_{1}i_{Lq}(k) + k_{2}\left\{v_{iq}(k) - k_{3}i_{Ld}(k)\right\}$$

(7)

where  $k_1 = (1 - \frac{RT_s}{L})$ ,  $k_2 = \frac{T_s}{L}$ ,  $k_3 = \omega^* L$ ,  $\omega^*$  is the angular frequency of the current reference. The voltages  $v_{id}$ ,  $v_{iq}$  and currents  $i_{Ld}$ ,  $i_{Lq}$  can be computed using Park transformation relation to get dq from  $\alpha\beta$  components given as:

$$\begin{bmatrix} x_d \\ x_q \end{bmatrix} = \begin{bmatrix} \cos \theta^* & \sin \theta^* \\ -\sin \theta^* & \cos \theta^* \end{bmatrix} \begin{bmatrix} x_\alpha \\ x_\beta \end{bmatrix}$$

(8)

where  $\theta^*$  is the reference phase angle for the coordinate conversion.

#### 2.2. Selection Criteria

To select the optimum switching state according to optimum voltage vector in each sampling and to minimize the error between the predicted and reference variables, a selection criteria is required to be defined considering desired control objectives. A cost function is formulated by incorporating error between each predicted and reference control variables as well as any constraints.

A simple cost function considering current control objective is usually defined in terms of the orthogonal  $\alpha\beta$  coordinates as follows:

$$g_{\alpha\beta} = \left| i_{L\alpha}^*(k+1) - i_{L\alpha}^p(k+1) \right| + \left| i_{L\beta}^*(k+1) - i_{L\beta}^p(k+1) \right|$$

(9)

where  $i_{L\alpha}^*$  and  $i_{L\beta}^*$  are the real and imaginary components of the reference current. The future reference current value required by (9) has to be predicted using Lagrange extrapolation formula [5]. However, for sufficient small  $T_S$ , a simple approximation  $i_L^*(k + 1) \approx i_L^*(k)$  can be used and no extrapolation is required. The same approximation is considered in this paper.

The cost function to control *d* and *q* components of the load current is formulated as:

$$g_{dq} = \left| i_{Ld}^*(k+1) - i_{Ld}^p(k+1) \right| + \left| i_{Lq}^*(k+1) - i_{Lq}^p(k+1) \right|$$

(10)

where  $i_{Ld}^*$  and  $i_{Lq}^*$  are the reference currents for *d* and *q* components, respectively.

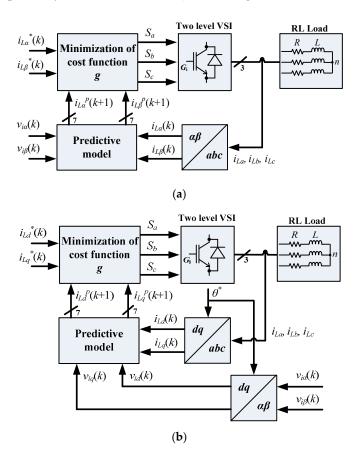

In order to demonstrate the implementation methodology of the FS-MPC in two different coordinates, the schematic diagram of the load current control using FS-MPC with stationary  $\alpha\beta$  and rotating *dq* reference frames are depicted in Figure 2a,b, respectively.

#### 3. Model-Based Design of FS-MPC

Model-based design of the FS-MPC is divided into three steps: computation of cost function, selection of optimum switching state, and generation of switching signals. The steps for modeling of the controller are described in the following subsections.

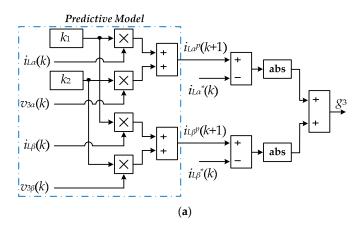

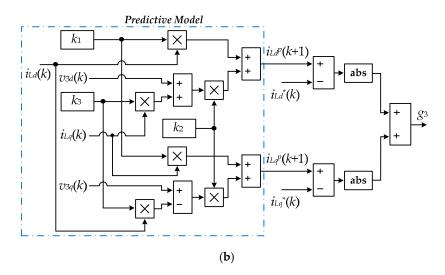

#### 3.1. Computation of Cost Functions

The cost function is computed using the predictive model that is modeled using discrete-time mathematical equations described in Section 2. The computation of cost function corresponding to a voltage vector (for ex.  $v_3$ ) is shown by the block diagram in Figure 3a,b for FS-MPC in  $\alpha\beta$  and dq frames, respectively. The modeling for the computation of predicted load currents and the cost function is represented for the FS-MPC in  $\alpha\beta$ -frame (Figure 3a) using (5) and (9) respectively. Similarly, the

model-based design for the load current prediction and the cost function computation is performed using (7) and (10) respectively for the FS-MPC in dq-frame (Figure 3b).

**Figure 2.** Schematic diagram of load current control using finite set-model predictive control (FS-MPC) in (**a**)  $\alpha\beta$ -frame and, (**b**) *dq*-frame.

Figure 3. Cont.

**Figure 3.** Block diagram representing modeling of a cost function for the FS-MPC in (**a**)  $\alpha\beta$ -frame and, (**b**) *dq*-frame using a voltage vector  $v_3$ .

Although only a single voltage vector ( $v_3$ ) is considered for the demonstration of the modeling steps during the computation of cost function, the cost functions need to be computed for each inverter voltage vectors ( $v_0-v_7$ ) defined for corresponding switching states ( $S_a$ ,  $S_b$ ,  $S_c$ ) as given in Table 2 to select minimum cost function in each sampling interval.

# 3.2. Selection of Optimum Switching State

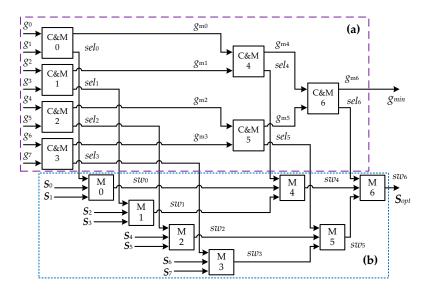

The block diagram for the selection of an optimum switching state  $S_{opt}$  corresponding to the minimum cost function  $g_{min}$  for each sampling interval is shown in Figure 4. A simple pipelining method is used to find the minimum among the computed cost functions. A logic to select a minimum between the two consecutive cost functions is developed using a comparator (C) and a 2:1 multiplexer (M). The output of the comparators (binary digit "0" or "1") are used as select lines ( $sel_0-sel_6$ ) for the multiplexers in the combined C&M (C&M0 ~ C&M6) to select the minimum cost function ( $g_{m0}-g_{m6}$ ) out of the two as shown in Figure 4a. Similar to the selection of  $g_{min}$ , an optimum switching state  $S_{opt}$  is selected using the corresponding select lines ( $sel_0-sel_6$ ) fed to the multiplexers (M0 ~ M6) by taking consecutive two switching states as shown in Figure 4b.

**Figure 4.** Block diagram to represent logic for the (**a**) selection of minimum of cost function, and (**b**) selection of optimum switching state.

#### 3.3. Generation of Switching Signal and Index Number

The switching signals corresponding to selected  $S_{opt}$  is also generated through modeling. The 3-bit binary combination of  $S_{opt}$  is sliced to generate switching signals for respective upper switches ( $G_1$ ,  $G_3$ ,  $G_5$ ), and complementary switching conditions are applied to lower switches ( $G_2$ ,  $G_4$ ,  $G_6$ ).

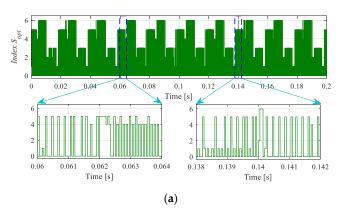

An index number is considered for an in-depth analysis purpose corresponding to eight possible voltage vectors ( $v_0-v_7$ ) as mentioned in Table 2. The index numbers are defined considering the decimal equivalent of the binary values of  $S_a$ ,  $S_b$ ,  $S_c$ . For example, the index number is defined as "4" corresponding to  $v_1$  having { $S_a$ ,  $S_b$ ,  $S_c$ } as {1, 0, 0}. The  $S_{opt}$  corresponding to the  $g_{min}$  is used to select an index number that replicates the definite switching state selection in each sampling time.

The digital logic for the selection of  $g_{min}$ , selection of the  $S_{opt}$ , and the implementation of  $S_{opt}$  to inverter through the model-based XSG (digital simulator) diagram was demonstrated in [31] based on the block diagram shown in Figure 4.

#### 4. Simulation Results

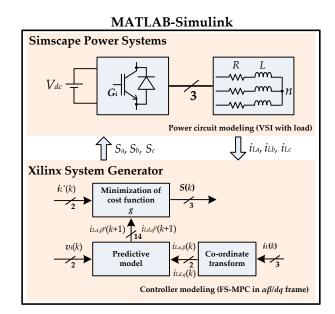

To demonstrate the development approach of the controller in  $\alpha\beta$  as well as dq frames, a simulation methodology is represented in Figure 5. The power circuit of three-phase VSI is developed in MATLAB-Simulink using simscape power systems toolbox, whereas the controller is developed in the digital environment of XSG using XSG toolbox. A fixed-point number representation approach was adopted for the development of FS-MPC in both frames. The parameters considered for the simulation are as follows; supply DC voltage ( $V_{dc}$ ): 145 V, load resistor (R): 10  $\Omega$ , load inductor (L): 10 mH, sampling time ( $T_S$ ): 50 µs.

Figure 5. Block diagram representation for modeling and simulation.

#### 4.1. System Performance

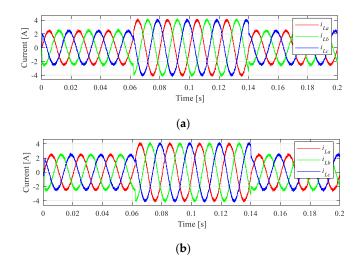

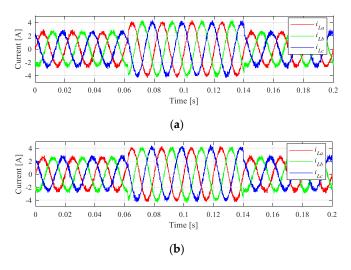

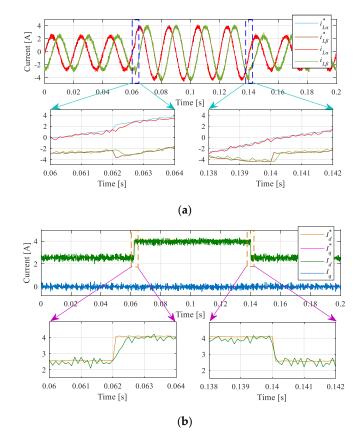

The three-phase load currents ( $i_{La}$ ,  $i_{Lb}$ ,  $i_{Lc}$ ) in Figure 6a,b are presented to validate the system performance with the FS-MPC implemented in  $\alpha\beta$  and dq frames, respectively. In order to investigate the dynamic performance of the FS-MPC for the three-phase VSI system, two step changes in reference current are considered for current tracking during the transients. The tracking performance of the load current is demonstrated for change in reference current from 2.5 A to 4 A at instant 0.062 s and from 4 A to 2.5 A at instant 0.14 s for the FS-MPC in  $\alpha\beta$ -frame (Figure 7a) and dq-frame (Figure 7b), respectively.

**Figure 6.** Simulation result: three-phase load current for the FS-MPC in (a)  $\alpha\beta$ -frame and (b) *dq*-frame.

**Figure 7.** Simulation result: tracking performance of load current for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) *dq*-frame.

In the case of *dq*-frame, the step changes are applied in the *d*-axis component of the reference current, keeping *q*-axis reference current zero. The harmonic content in the load current is also analyzed considering both the frames. A higher percentage THD is observed for current reference of 2.5 A (5.28% in  $\alpha\beta$ -frame and 5.61% in *dq*-frame) as compared to reference current of 4 A having percentage THD 3.54% in  $\alpha\beta$ -frame and 3.74% in *dq*-frame. The THD for lower current reference is not the same in  $\alpha\beta$  and *dq* frames, however, the THD is almost the same for higher reference current condition. The slight difference in THD may be due to the different mathematical computation for  $\alpha\beta$  and *dq* frames.

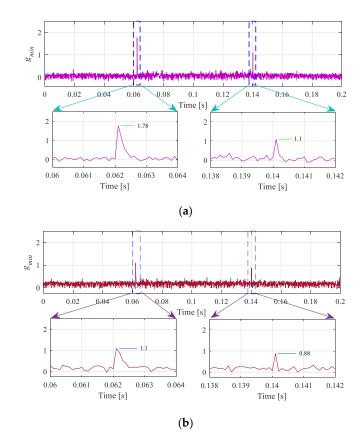

#### 4.2. Intermediate Response

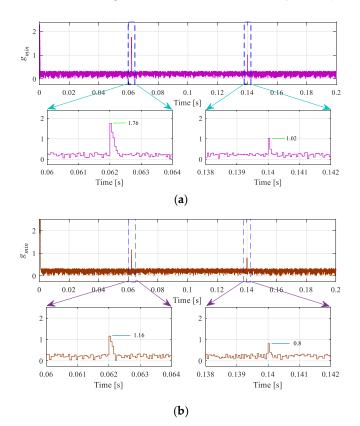

The intermediate responses are vital not only for the design and development of the controller, but also for in-depth analysis. In this paper, the performance of FS-MPC is analyzed considering the intermediate responses: minimum cost function  $g_{min}$  and index number at each sampling interval. The selected  $g_{min}$  represents the minimum current error and index number represents the switching state  $S_{opt}$  at each sampling interval. The value of  $g_{min}$  are shown in Figure 8a,b for the FS-MPC in  $\alpha\beta$  and dq frames, respectively. Further, the index number of the selected  $S_{opt}$  corresponding to the  $g_{min}$  at each sampling interval are shown in Figure 9a,b for the FS-MPC in  $\alpha\beta$  and dq frames, respectively.

**Figure 8.** Simulation results: the values of minimum cost function  $g_{min}$  for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) dq-frame.

Figure 9. Cont.

**Figure 9.** Simulation result: the index number of selected optimum switching state  $S_{opt}$  in each sampling interval for the FS-MPC in (a)  $\alpha\beta$ -frame and (b) dq-frame.

The index number is almost following the same profile for each cycle of current. However, the selected  $S_{opt}$  in each sampling intervals is not identical in  $\alpha\beta$  and dq frames that signify the different selection of optimum voltage vectors, consequently having the non-identical minimum current error.

The intermediate responses are intentionally demonstrated as enlarged view during the instant of transients caused by the step change in reference current. The minimum current error in Figure 8 is possessing a sharp spike at the instant of change in reference current. The value of the current spike in *dq*-frame is lower as compared to the  $\alpha\beta$ -frame. The intermediate responses for selection of minimum cost function and the index number corresponding to optimum switching state is analyzed for modeling and implementation of FS-MPC.

#### 5. Experimental Results

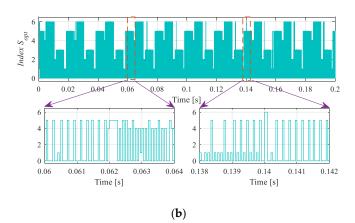

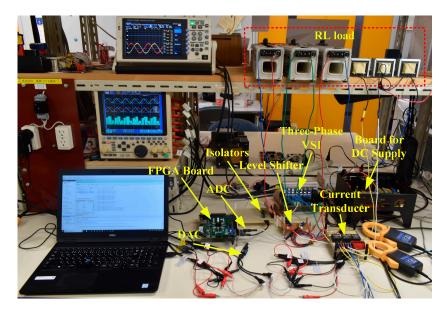

The experimental setup for real-time implementation of the FS-MPC is represented using block diagram as shown in Figure 10. The laboratory prototype of the experimental setup is depicted in Figure 11 and the experimental system components used for the development of laboratory prototype are listed in Table 3. The FPGA code was generated automatically through the modeled controller and programmed using dedicated software (Xilinx Vivado Design Suite) for real-time operation of VSI system with FS-MPC.

Figure 10. Block diagram of experimental setup.

Figure 11. Laboratory prototype of the experimental setup.

| Table 5. Description of components specifications for the experimental system. |                             |                       |  |  |  |

|--------------------------------------------------------------------------------|-----------------------------|-----------------------|--|--|--|

| S. No.                                                                         | Components                  | Specifications        |  |  |  |

| 1                                                                              | Three-phase VSI             | STEVAL-IHM023V3, 1 kW |  |  |  |

| 2                                                                              | DC supply                   | THDSHVMTRPFCKIT       |  |  |  |

| 3                                                                              | Current transducer          | LA 25-NP              |  |  |  |

| 4                                                                              | Op-amp IC for level shifter | LM385N                |  |  |  |

| 5                                                                              | Isolator IC                 | ADuM3440              |  |  |  |

Digilent Pmod AD1

**Digilent Pmod DA4**

Zedboard Zynq Evaluation and Development Kit

Table 3. Description of components specifications for the experimental system.

The performance of the FS-MPC in  $\alpha\beta$  and dq frames was experimentally evaluated and the experimental data are obtained through HIOKI 8855 Memory Hicorder. Further, the data are plotted with the help of MATLAB plotting tool for demonstration and analysis of experimental results.

# 5.1. System Performance

6

7

8

ADC

DAC

FPGA board

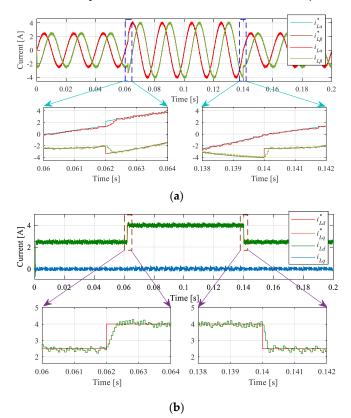

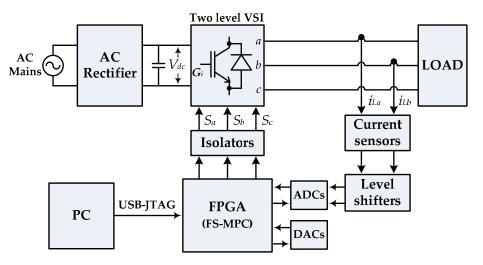

The FS-MPC in both frames is experimentally validated for system performance analysis considering the same system parameters as in the case of simulation. The three-phase load currents  $(i_{La}, i_{Lb}, i_{Lc})$  are shown in Figure 12a,b for the FS-MPC in  $\alpha\beta$  and dq frames, respectively. Further, the dynamic response is demonstrated in Figure 13a,b for the FS-MPC in  $\alpha\beta$  and dq frame, respectively, with the same step change in reference current as adopted in the simulation (2.5 and 4 A at instants 0.062 s and 0.14 s respectively). In order to investigate the dynamic response of the FS-MPC, the time span is intentionally expanded to demonstrate the current tracking during the transient caused by step changes in reference current.

**Figure 12.** Experimental result: three-phase load current for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) *dq*-frame.

**Figure 13.** Experimental result: tracking performance of load current for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) *dq*-frame.

The harmonic content in the load current during the experiment was measured through HIOKI power analyzer and current clamp sensor. The percentage THD in load current is 7.91% in  $\alpha\beta$ -frame, 8.15% in dq-frame for current reference of 2.5 A and 4.9% in  $\alpha\beta$ -frame, 4.8% in dq-frame for current reference of 4 A. Considering the simulation results, the current THD is significantly high during the experiment for lower current reference as compared to higher current reference. However, the difference between the percentage THD through the implementation with the FS-MPC in  $\alpha\beta$  and dq frame is smaller during the experiment as compared to the simulation.

#### 5.2. Intermediate Response

The value of  $g_{min}$  and the index number at each sampling interval are demonstrated in Figures 14 and 15 for the FS-MPC in  $\alpha\beta$  and dq frames, respectively. The index number profile for  $S_{opt}$  is similar to that analyzed during the simulations for each sampling interval. The non-identical nature of selected  $S_{opt}$  with respect to sampling interval validates the different selection of optimum voltage vectors, consequently the different minimum current error between the FS-MPC in  $\alpha\beta$  and dq frames.

**Figure 14.** Experimental results: the values of minimum cost function  $g_{min}$  for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) *dq*-frame.

Similar to the simulation results,  $g_{min}$  shows a sharp spike at the instant of step change and the value of the current spikes in the case of  $\alpha\beta$  frame is higher than dq frame. In addition, the value of current spikes during simulation and experiment is almost the same for both the frames.

In order to summarize the results obtained during simulation (Sim.) as well as experiments (Exp.) with both frames, a comparative analysis is presented in Table 4. The average switching frequency ( $f_{SW}$ ) is also depicted in the same table with the percentage THD in load current corresponding to the load changes. There is a noticeable difference between the average  $f_{SW}$  during the simulation and the experiment. A higher value of the average  $f_{SW}$  during the simulation may be due to the ideal power switches and absence of realistic inductive load properties. The average  $f_{SW}$  in  $\alpha\beta$  and dq frame for experiment is almost similar. However, the slight difference in THD as well as average switching frequency is maybe due to the different mathematical computation in  $\alpha\beta$  and dq frames. In addition, usually there are difference in performance between both frames and a decoupling term is included in dq-frame to compensate the computational difference of the  $\alpha\beta$  and dq frame.

**Figure 15.** Experimental results: the index number of selected optimum switching state  $S_{opt}$  in each sampling interval for the FS-MPC in (**a**)  $\alpha\beta$ -frame and (**b**) dq-frame.

#### 5.3. FPGA Resource Utilization

Digital logic resources of an FPGA are used during the implementation of the controller in real-time. The configurable logic blocks (CLBs) are the main constituents of the FPGA resources. A CLB element contains a pair of slices where a slice is composed of look-up tables (LUTs) and flip-flops (FFs) [34,35]. An FPGA chip consists of large arrays of LUTs. LUTs are used for making digital logics for desired system designs, whereas flip-flops are binary shift registers used to synchronize logic and save logical states between clock cycles within an FPGA circuit. The number of LUTs and flip-flops in a single slice varies based on the family of the FPGA chip. In 7 series FPGAs, a slice contains four LUTs and eight flip-flops [35]. In addition, DSP slices are a major component of the FPGA resources that are mainly used to implement signal processing functions. A DSP slice is composed of signed multiplier, adder/accumulator, arithmetic logic unit (ALU), and many more [36].

In order to analyze the complexity level between the FS-MPC developed in  $\alpha\beta$  and dq frames, the resource utilization of FPGA are summarized in Table 5. The number of slice LUTs and DSP cells show higher resource utilization for the case of FS-MPC in dq-frame. DSP cells utilization is nearly three times higher for dq-frame than  $\alpha\beta$ -frame. A higher FPGA resource utilization in the case of the FS-MPC in dq-frame is due to the additional coordinate transformation ( $\alpha\beta$  to dq) for voltage vectors including measured current, reference phase angle  $\theta^*$  generation using CORDIC SINCOS, and an extra effort for computation of feed-forward term used for decoupling.

| Performance Indices                                                | FS-MPC in <i>αβ</i> -Frame |                  | FS-MPC in <i>dq</i> -Frame |                  | Comments                                                                                                                             |  |

|--------------------------------------------------------------------|----------------------------|------------------|----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| i chomanee malees                                                  | Sim.                       | Exp.             | Sim.                       | Exp.             | Comments                                                                                                                             |  |

| Current error (spike) at<br>instant 0.062 s                        | 1.76                       | 1.78             | 1.16                       | 1.1              | <ol> <li>lower for <i>dq</i>-frame</li> <li>quite similar in experiment as<br/>compared to simulation for both<br/>frames</li> </ol> |  |

| Current error (spike) at<br>instant 0.14 s                         | 1.02                       | 1.1              | 0.8                        | 0.88             | <ol> <li>quite similar for both frames</li> <li>slightly lower for <i>dq</i>-frame</li> </ol>                                        |  |

| THD and average $f_{SW}$<br>for $i_{\rm L} = 2.5$ A                | 5.28%<br>3053 Hz           | 7.91%<br>2310 Hz | 5.61%<br>3306 Hz           | 8.15%<br>2350 Hz | <ol> <li>higher for <i>dq</i>-frame</li> <li>significantly high in experiment for<br/>both frames</li> </ol>                         |  |

| THD and average $f_{SW}$<br>for $i_{\rm L} = 4$ A                  | 3.54%<br>3733 Hz           | 4.9%<br>2550 Hz  | 3.74%<br>3920 Hz           | 4.8%<br>2580 Hz  | <ol> <li>quite similar for both frames</li> <li>slightly high in experiment</li> </ol>                                               |  |

| Transient response:<br>Settling time for step<br>change at 0.062 s | 200 µs                     | 400 µs           | 250 μs                     | 500 µs           | <ol> <li>significantly high in experiment for<br/>both frames</li> <li>slightly higher for <i>dq</i>-frame</li> </ol>                |  |

| Transient response:<br>Settling time for step<br>change at 0.14 s  | 150 μs                     | 280 μs           | 130 µs                     | 200 µs           | <ol> <li>high in experiment for both frames</li> <li>slightly lower for <i>dq</i>-frame</li> </ol>                                   |  |

Table 4. Comparative analysis chart for the FS-MPC in two frames.

Table 5. Field-programmable gate array (FPGA) resource utilization for the FS-MPC implementation.

| Logic Utilization Indices | Available   | Us       | ed       | Utilization Percentage |          |

|---------------------------|-------------|----------|----------|------------------------|----------|

| 8                         | 111 unu dic | αβ-Frame | dq-Frame | αβ-Frame               | dq-Frame |

| Number of slice LUTs      | 53,200      | 4364     | 8534     | 8.2%                   | 16.04%   |

| Number of FFs             | 106,400     | 1078     | 1327     | 1.01%                  | 1.25%    |

| Number of DSP cells       | 220         | 25       | 66       | 11.36%                 | 30%      |

# 6. Conclusions

This paper presents an FPGA-based real-time implementation of the FS-MPC in  $\alpha\beta$  as well as dq coordinates for the load current control of a three-phase VSI system. The FS-MPC algorithm is developed in a digital simulator of Xilinx which is an integrated platform with MATLAB-Simulink. A modeling approach was adopted for controller development to have an insight into the FS-MPC performance. To demonstrate the functionality of the modeling approach, the intermediate responses such as minimum cost function and index number are presented considering step-by-step analysis. The system performance is validated through simulation results and experimental results considering the dynamic behavior during transients for the FS-MPC in both frames as summarized in Table 4.

The current error spike during transient is almost the same for the simulation and experiment results that authenticates the realistic controller modeling in a digital simulator. However, the percentage THD of load current is higher in experiments as compared to the simulations that are because of the simplified model of the VSI and the load used for the simulation study. In addition, in  $\alpha\beta$ -frame slightly better percentage THD is achieved as compared to dq-frame in the simulation as well as the experiment. The system implementation through the FS-MPC in dq-frame can be used for in-depth system analysis, however, for the real-time implementation  $\alpha\beta$ -frame should be preferred as it has 2–3 times lower complexity considering the overall FPGA resource utilization.

**Author Contributions:** The manuscript preparation including system design, simulation, and experiments was performed by V.K.S. The idea of controller modeling was suggested by R.N.T. The work was completed under the supervision of T.H., R.N.T. and T.H. also contributed to the manuscript correction. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Kouro, S.; Cortes, P.; Vargas, R.; Ammann, U.; Rodriguez, J. Model Predictive Control—A Simple and Powerful Method to Control Power Converters. *IEEE Trans. Ind. Electron.* **2009**, *56*, 1826–1838. [CrossRef]

- 2. Rodríguez, J.; Cortes, P. *Predictive Control of Power Converters and Electrical Drives*, 1st ed.; Wiley-IEEE Press: New York, NY, USA, 2012; ISBN 978-1-119-96398-1.

- 3. Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M.; Young, H.A. Model Predictive Control: MPC's Role in the Evolution of Power Electronics. *IEEE Ind. Electron. Mag.* **2014**, *8*, 16–31. [CrossRef]

- 4. Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Rodriguez, J.; Young, H.A.; Marquez, A.; Zanchetta, P. Model predictive control: A review of its applications in power electronics. *IEEE Ind. Electron. Mag.* **2015**, *9*, 8–21. [CrossRef]

- 5. Rodríguez, J.; Pontt, J.; Silva, C.; Correa, P.; Lezana, P.; Cortés, P.; Ammann, U. Predictive current control of a voltage source inverter. *IEEE Trans. Ind. Electron.* **2007**, *54*, 495–503. [CrossRef]

- Nikhil, P.; Sonam, K.; Monika, M.; Wagh, S. Finite control set model predictive control for two level inverter with fixed switching frequency. In Proceedings of the 2018 SICE International Symposium on Control Systems (SICE ISCS), Tokyo, Japan, 9–11 March 2018; pp. 74–81. [CrossRef]

- Donoso, F.; Mora, A.; Cárdenas, R.; Angulo, A.; Sáez, D.; Rivera, M. Finite-Set Model-Predictive Control Strategies for a 3L-NPC Inverter Operating With Fixed Switching Frequency. *IEEE Trans. Ind. Electron.* 2018, 65, 3954–3965. [CrossRef]

- 8. Cortes, P.; Rodriguez, J.; Antoniewicz, P.; Kazmierkowski, M. Direct power control of an AFE using predictive control. *IEEE Trans. Power Electron.* **2008**, *23*, 2516–2523. [CrossRef]

- Rodríguez, J.; Kazmierkowski, M.P.; Espinoza, J.R.; Zanchetta, P.; Abu-Rub, H.; Young, H.A.; Rojas, C.A. State of the art of finite control set model predictive control in power electronics. *IEEE Trans. Ind. Inform.* 2013, 9, 1003–1016. [CrossRef]

- Tarisciotti, L.; Zanchetta, P.; Watson, A.; Bifaretti, S.; Clare, J.C. Modulated model predictive control for a seven-level cascaded H-bridge back-to-back converter. *IEEE Trans. Ind. Electron.* 2014, *61*, 5375–5383. [CrossRef]

- 11. Perez, M.A.; Cortes, P.; Rodriguez, J. Predictive control algorithm technique for multilevel asymmetric cascaded H-bridge inverters. *IEEE Trans. Ind. Electron.* **2008**, *55*, 4354–4361. [CrossRef]

- 12. Cortes, P.; Wilson, A.; Kouro, S.; Rodriguez, J.; Abu-Rub, H. Model predictive control of multilevel cascaded H-bridge inverters. *IEEE Trans. Ind. Electron.* **2010**, *57*, 2691–2699. [CrossRef]

- 13. Lezana, P.; Aguilera, R.P.; Quevedo, D.E. Model predictive control of an asymmetric flying capacitor converter. *IEEE Trans. Ind. Electron.* **2009**, *56*, 1839–1846. [CrossRef]

- 14. Rivera, M.; Rojas, C.A.; Rodriguez, J.; Wheeler, P.; Wu, B.; Espinoza, J.R. Predictive current control with input filter resonance mitigation for a direct matrix converter. *IEEE Trans. Power Electron.* **2011**, *26*, 2794–2803. [CrossRef]

- Wang, L.; Dan, H.; Zhao, Y.; Zhu, Q.; Peng, T.; Sun, Y.; Wheeler, P. A finite control set model predictive control method for matrix converter with zero common-mode voltage. *IEEE J. Emerg. Sel. Top. Power Electron.* 2018, 6, 327–338. [CrossRef]

- 16. Cortes, P.; Ortiz, G.; Yuz, J.; Rodríguez, J.; Vazquez, S.; Franquelo, L. Model predictive control of an inverter with output LC filter for UPS applications. *IEEE Trans. Ind. Electron.* **2009**, *56*, 1875–1883. [CrossRef]

- Khan, H.S.; Aamir, M.; Ali, M.; Waqar, A.; Ali, S.U.; Imtiaz, J. Finite Control Set Model Predictive Control for Parallel Connected Online UPS System under Unbalanced and Nonlinear Loads. *Energies* 2019, 12, 581. [CrossRef]

- 18. Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model Predictive Control for Power Converters and Drives: Advances and Trends. *IEEE Trans. Ind. Electron.* **2017**, *64*, 935–947. [CrossRef]

- Young, H.A.; Perez, M.A.; Rodriguez, J.; Abu-Rub, H. Assessing finite-control-set model predictive control: A comparison with a linear current controller in two-level voltage source inverters. *IEEE Ind. Electron. Mag.* 2014, *8*, 44–52. [CrossRef]

- 20. Xia, C.; Liu, T.; Shi, T.; Song, Z. A Simplified Finite-Control-Set Model-Predictive Control for Power Converters. *IEEE Trans. Ind. Inform.* **2014**, *10*, 991–1002. [CrossRef]

- 21. Cortes, P.; Kazmierkowski, M.P.; Kennel, R.M.; Quevedo, D.E.; Rodriguez, J. Predictive control in power electronics and drives. *IEEE Trans. Ind. Electron.* **2008**, *55*, 4312–4324. [CrossRef]

- 22. Cortes, P.; Rodriguez, J.; Silva, C.; Flores, A. Delay compensation in model predictive current control of a three-phase inverter. *IEEE Trans. Ind. Electron.* **2012**, *59*, 1323–1325. [CrossRef]

- 23. Yang, Y.; Wen, H.; Li, D. A fast and fixed switching frequency model predictive control with delay compensation for three-phase inverters. *IEEE Access.* **2017**, *5*, 17904–17913. [CrossRef]

- 24. Vyncke, T.J.; Thielemans, S.; Melkebeek, J.A. Finite-set model based predictive control for flying-capacitor converters: Cost function design and efficient FPGA implementation. *IEEE Trans. Ind. Inform.* **2013**, *9*, 1113–1121. [CrossRef]

- 25. Sanchez, P.M.; Machado, O.; Peña, E.J.B.; Rodríguez, F.J.; Meca, F.J. FPGA-Based Implementation of a Predictive Current Controller for Power Converters. *IEEE Trans. Ind. Inform.* **2013**, *9*, 1312–1321. [CrossRef]

- 26. Ma, Z.; Saeidi, S.; Kennel, R. FPGA implementation of model predictive control with constant switching frequency for PMSM drives. *IEEE Trans. Ind. Inform.* **2014**, *10*, 2055–2063. [CrossRef]

- Zhang, Z.; Wang, F.; Sun, T.; Rodríguez, J.; Kennel, R. FPGA-Based Experimental Investigation of a Quasi-Centralized Model Predictive Control for Back-to-Back Converters. *IEEE Trans. Power Electron.* 2016, 31, 662–674. [CrossRef]

- 28. Naouar, M.W.; Naassani, A.A.; Monmasson, E.; Slama-Belkhodja, I. FPGA-based predictive current controller for synchronous machine speed drive. *IEEE Trans. Power Electron.* **2008**, *23*, 2115–2126. [CrossRef]

- 29. Gulbudak, O.; Santi, E. FPGA-based model predictive controller for direct matrix converter. *IEEE Trans. Ind. Electron.* **2016**, *63*, 4560–4570. [CrossRef]

- 30. Saeidi, S. FPGA-Based Nonlinear Model Predictive Control of Electric Drives. Ph.D. Thesis, Technische Universitat Munchen, Munchen, Germany, May 2015.

- Singh, V.K.; Tripathi, R.N.; Hanamoto, T. Xilinx System Generator Based Modeling of Finite State MPC. In Proceedings of the 9th International Power Electronics Conference (IPEC 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018. [CrossRef]

- 32. Selvamuthukumaran, R.; Gupta, R. Rapid prototyping of power electronics converters for photovoltaic system application using Xilinx System Generator. *IET Power Electron.* **2014**, *7*, 2269–2278. [CrossRef]

- 33. Singh, V.K.; Tripathi, R.N.; Hanamoto, T. HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System. *Energies* **2018**, *11*, 909. [CrossRef]

- Monmasson, E.; Idkhajine, L.; Naouar, M.W. FPGA-based controllers. *IEEE Ind. Electron. Mag.* 2011, 5, 14–26. [CrossRef]

- 35. Xilinx. 7 Series FPGAs Configurable Logic Block: User Guide; Xilinx Inc.: San Jose, CA, USA, 27 September 2016.

- 36. Xilinx. 7 Series DSP48E1 Slice: User Guide; Xilinx Inc.: San Jose, CA, USA, 27 March 2018.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).