Vth-shiftable SRAM cell TEGs for direct measurement for the immunity of the threshold voltage variability

| 著者                                       | Yamaguchi Shogo, Imi Hitoshi, Tokumaru<br>Shogo, Kondo Takahiro, Yamamoto Hiromasa,<br>Nakamura Kazuyuki |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|

| journal or                               | 2017 International Conference of                                                                         |

| publication title                        | Microelectronic Test Structures (ICMTS)                                                                  |

| year                                     | 2017-06-22                                                                                               |

| その他のタイトル                                 | Vth-Shiftable SRAM Cell TEGs for Direct                                                                  |

|                                          | Measurement for the immunity of the Threshold                                                            |

|                                          | Voltage Variability                                                                                      |

| URL                                      | http://hdl.handle.net/10228/00007548                                                                     |

| doi: info:doi/10.1100/ICMTS 2017.7054265 |                                                                                                          |

doi: info:doi/10.1109/ICMTS.2017.7954265

# Vth-shiftable SRAM Cell TEGs for Direct Measurement for the Immunity of the Threshold Voltage Variability

Shogo Yamaguchi Hitoshi Imi Shogo Tokumaru Takahiro Kondo Hiromasa Yamamoto Kazuyuki Nakamura Center for Microelectronic Systems, Kyushu Institute of Technology

# Summary

In order to demonstrate the immunity of the 12-transistor ratio-less SRAM operation for the variability of the threshold voltage  $(V_{th})$  of MOSFETs by the measurement, we developed the  $V_{th}$ -shiftable SRAM cell TEGs (VTSTs). The measured results are discussed by the fail condition maps (FCMs) and the maximum limit of  $V_{th}$ -shift for stable SRAM operation.

# **Corresponding Author**

Shogo Yamaguchi Affiliation: Center for Microelectronic Systems, Kyushu Institute of Technology Address: 680-4 Kawazu, Iizuka, Fukuoka 820-8502, Japan Phone: +81-948-29-7584 Fax: +81-948-29-7586 E-mail: shogo\_yamaguchi@cms.kyutech.ac.jp Preference for oral or poster: POSTER (Either will do)

## Vth-shiftable SRAM Cell TEGs for Direct Measurement for the Immunity of the Threshold Voltage Variability

Shogo Yamaguchi Hit

hi Hitoshi Imi Shogo Tokumaru Takahiro Kondo Hiromasa Yamamoto Kazuyuki Nakamura

Center for Microelectronic Systems, Kyushu Institute of Technology

680-4 Kawazu, Iizuka, Fukuoka 820-8502, Japan

Phone: +81-948-29-7584 Fax: +81-948-29-7586 Email: shogo\_yamaguchi@cms.kyutech.ac.jp

## 1. Introduction

For SRAM using state-of-the-art processes of deep sub-micron generation, it is becoming difficult to secure operating margins due to the lowering of power supply voltage and the increase in the device characteristic variation [1][2]. To overcome this problem, we proposed the 12-transistor ratio-less SRAM (RL-SRAM) design [3][4]. In order to demonstrate the immunity of the ratio-less SRAM operation for the device characteristic variability by the measurement, we developed MOSAIC SRAM cell TEGs with intentionally-added device variability within the gate width [5]. However, the immunity for the device variability in the threshold voltage (V<sub>th</sub>) of MOSFETs has not been evaluated by the measurement. Therefore, we newly developed the V<sub>th</sub>-shiftable SRAM cell TEGs (VTSTs).

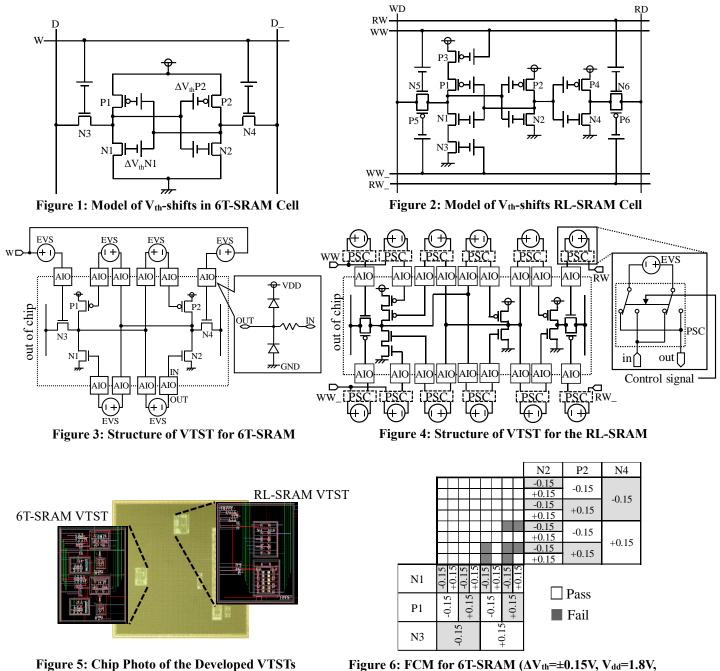

## 2. Design of Vth-shiftable SRAM Cell TEGs

Figures 1 and 2 show simple models for Vth-shifts in the MOSFETs in a 6-transistor SRAM (6T-SRAM) cell and the 12-transistor ratio-less SRAM (RL-SRAM) cell, respectively. Each MOSFET may have the inherent Vth-shift caused by the device characteristic variability. Figure 3 shows the developed VTST for 6T-SRAM. In this structure, the all gate terminals of MOSFETs are extracted to the chip boundary and tapped to analog I/O (AIO) buffers. Six external voltage sources (EVSs) are employed to apply the Vth-shift to each MOSFET. The arbitral V<sub>th</sub>-shift value ( $\Delta V_{th}$ ) and its polarity can be manipulated by the EVS. Figure 4 shows the VTST for the RL-SRAM with the polarity switching circuits (PSCs) that are employed to achieve the computerized polarity switching of the EVSs. Figure 5 shows the photo of developed VTSTs for 6T-SRAM and RL-SRAM using the 0.18µm CMOS process.

## 3. Measured Results and Discussions

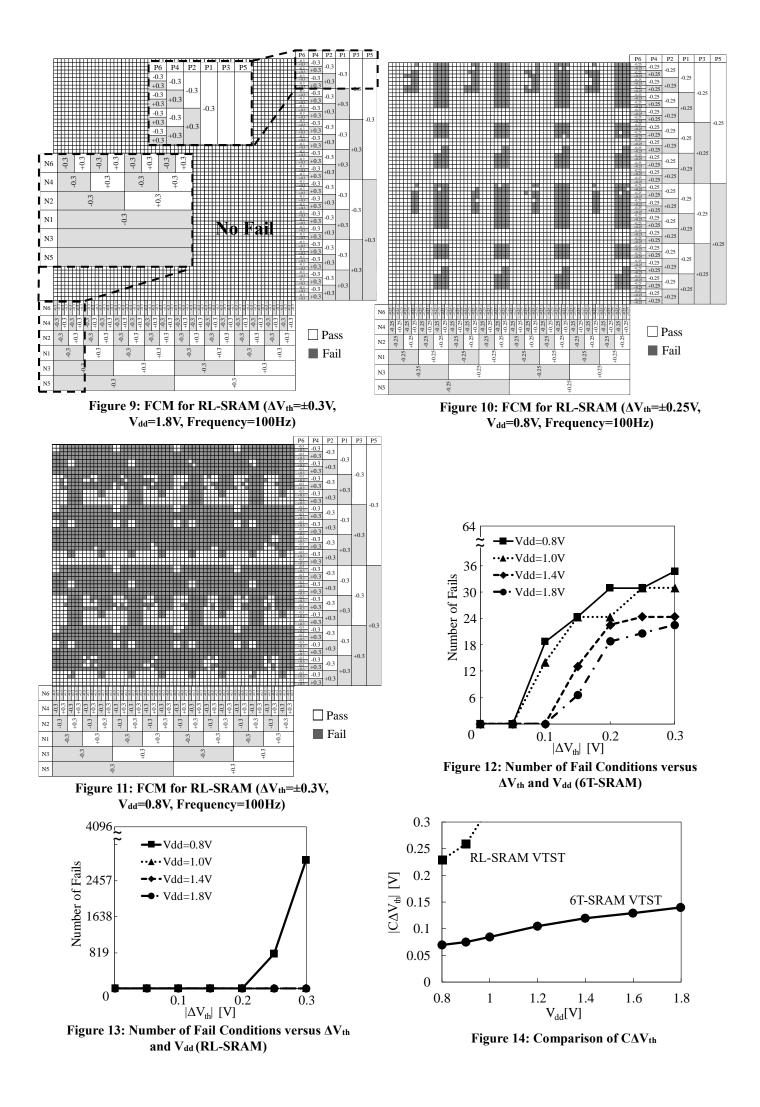

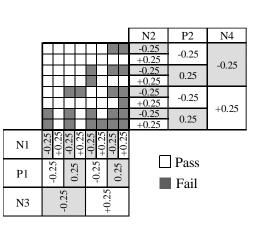

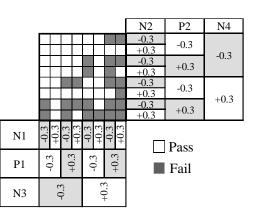

In the evaluation of measured results of the VTST, we defined the fail condition map (FCM) which summarizes all the combinations of the polarity setting for a Vth-shift. Since the V<sub>th</sub>-shift for each MOSFET can be set to  $(+\Delta V_{th} \text{ or } -\Delta V_{th})$ , the total number of combinations for the measurement are 64  $(= 2^6)$  for the 6T-SRAM cell and 4096  $(=2^{12})$  for the 12-transistor RL-SRAM cell, respectively. Figure 6 shows the FCM for the  $V_{th}$ -shift values of ±0.15V for the 6T-SRAM. The one cell in FCM indicates one combination of the polarities  $(+\Delta V_{th} \text{ or } -\Delta V_{th})$  of six transistors of which an SRAM cell is composed. For example, in the left and the upper corner cell in FCM in Fig.6, the Vth-shifts for all six MOSFETs are set to -0.15V. In the FCM, white colored cells and dark gray colored cells mean the combination of the V<sub>th</sub>-shifts is operable (Pass) as SRAM cell or not operable (Fail) as SRAM cell, respectively. In the Fig. 6, we can recognize the 7 combinations of the polarities of Vth-shift of  $\pm 0.15$ V are not operable. Figures 7 and 8 show the measured FCMs for the V<sub>th</sub>-shift values of  $\pm 0.25V$  and  $\pm 0.3V$ , respectively. From the results of FCMs in Figs. 6-8, the

$V_{th}$ -shifts of N3 and N4 tend to decide the operation. This is because the higher  $V_{th}$ -shifts of N3 and N4 prevent the write operation in the 6T-SRAM.

Figure 9 shows the FCM for the RL-SRAM for  $V_{dd}$ =1.8V,  $\Delta V_{th} = \pm 0.3 V$ . In spite of the same setting of the Fig.8 for 6T-SRAM, it has no fail. Figures 10 and 11 show the FCMs for  $V_{dd}$ =0.8V. Since the number of combinations of 4096 for an FCM for the RL-SRAM is too huge to finish the measurement by manual operations, the automated measurement environment using PSCs as shown in Fig.4 was developed. Figures 12 and 13 summarize the total counts of the fail conditions of FCMs versus the  $V_{th}$ -shifts ( $|\Delta V_{th}|$ ) for the 6T-SRAM and the RL-SRAM, respectively. Figure 12 means the maximum limit of Vth-shift for the 6T-SRAM is less than 0.15V even in the typical supply voltage ( $V_{dd}=1.8V$ ). Here we defined the Critical  $\Delta V_{th}$  (C $\Delta V_{th}$ ) as the maximum limit of  $|\Delta V_{th}|$  for stable SRAM operation. Figure 14 summarizes the detail of the relationship between the  $C\Delta V_{th}$ and the supply voltage for the 6T-SRAM and RL-SRAM, respectively. The fail in the RL-SRAM can be observed just in the less than half of the typical supply voltage.

## 4. Conclusion

We developed VTSTs for 6T-SRAM and RL-SRAM and evaluated them to investigate the influences of SRAM operation by Vth fluctuation using measured FCMs and  $C\Delta V_{th}s$ . As a result, we successfully confirmed the superior immunity of  $V_{th}$  fluctuation of the RL-SRAM than the 6T-SRAM.

#### Acknowledgements

This work was supported by VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Cadence Design Systems, Inc., Mentor Graphics, Inc., the Rohm Corporation and the Toppan Printing Corporation. This research was also supported by funds from the Japanese Ministry of Education, Culture, Sports, Science and Technology, MEXT.

#### References

[1] E. Seevinck et al., "Static-noise margin analysis of MOS SRAMcells", IEEE J. Solid-State Circuits, vol. SC-22, no. 5, October 1987.

[2] L. Chang et al., "Stable SRAM cell design for the 32nm node and beyond", Symp. VLSI Tech. Dig., pp. 292-293, Jun. 2005.

[3] T. Saito, H. Okamura, H. Yamamoto and K. Nakamura, "Ratioless 10Transistor Cell and Static Column Retention Loop Structure for Fully Digital SRAM Design", IEEE International Memory Workshop (IMW), pp.167-170, May 2012.

[4] T. Kondo, H. Yamamoto, H. Imi, H. Okamura and K. Nakamura, "A Measurement of Ratio-less 12-transistor SRAM cell Operation at Ultra-low Supply-voltage", International Conference on Solid State Devices and Materials (SSDM), pp.82-83, Sep. 2014.

[5] H. Okamura, T. Saito, H. Goto, M. Yamamoto and K. Nakamura, "Mosaic SRAM Cell TEGs with Intentionally-addred Device Variability for Confirming the Ratio-less SRAM Operation", IEEE International Conference on Microelectronic Test Structures (ICMTS), Mar. 2013.

Figure 7: FCM for 6T-SRAM (ΔV<sub>th</sub>=±0.25V, V<sub>dd</sub>=1.8V, Frequency=100Hz)

Figure 6: FCM for 6T-SRAM ( $\Delta V_{th}$ =±0.15V,  $V_{dd}$ =1.8V, Frequency=100Hz)

Figure 8: FCM for 6T-SRAM ( $\Delta V_{th}=\pm 0.3V$ ,  $V_{dd}=1.8V$ , Frequency=100Hz)