### Software and Hardware Supports for Multi-OS Environment

マルチOS環境を支援するソフトウェア およびハードウェア機能の提案

February 2012

Waseda University Graduate School of Fundamental Science and Engineering Major in Computer Science and Engineering Research on Distributed Systems

Yuki KINEBUCHI

© Copyright by Yuki Kinebuchi 2012 All rights reserved

## Acknowledgements

This is a great opportunity to express my respect to my thesis advisor, Prof. Tatsuo Nakajima. My research and this dissertation would not exist without his support and patience. I would also like to thank all the members at Distributed Computing Laboratory in Waseda University for encouraging me.

## Abstract

Personal mobile devices are rapidly enhancing their functionalities. Not limited to phone and text messages, they offer web browsing via the Internet, free to install applications on the users' requests, play musics and videos, etc. Now they are capable of running multiple OS instances with support of virtualization. Like the use in desktop/enterprise systems, virtualization for embedded mobile devices allows consolidating multiple OS instances and enhancing the security of hosted OS environment. In addition, there are applications specific to embedded systems such as hosting real-time OS (RTOS) and application OS (GPOS) concurrently without spoiling the real-time responsiveness of the RTOS.

There is no doubt that virtualization brings many benefits to the embedded mobile devices, however virtualization is not a panacea. Additional layer of virtualization incurs additional complexity to the software stack of devices. Some extra engineering efforts of developing such device might make the system prone to bugs and security risks. In this dissertation we take the position that some applications of embedded virtualization can be supported with more light-weight methods. The methods leverages architecture specific features that are common or expected to be common among embedded mobile devices. We first focus on real-time and application OS consolidation, for which we propose a thin abstraction layer that achieves better interrupt responsiveness than virtualization. Next we focus on hosting a kernel integrity monitor for rootkit detection. The monitor is hosted within an isolated memory region that is protected by means of processor architecture.

## Contents

| 1        | Intr | oducti  | ion                                    | 1  |

|----------|------|---------|----------------------------------------|----|

|          | 1.1  | Motiva  | ation                                  | 1  |

|          | 1.2  | Contri  | ibutions                               | 2  |

|          | 1.3  | Organ   | ization of the Dissertation            | 2  |

| <b>2</b> | Dise | cussior | ns on Embedded System Virtualization   | 5  |

|          | 2.1  | The U   | Jse of Embedded System Virtualization  | 5  |

|          | 2.2  | Perfor  | mance and Real-time Responsiveness     | 6  |

|          | 2.3  | Engin   | eering Cost                            | 7  |

|          | 2.4  | Securi  | ty                                     | 8  |

| 3        | Mic  | rokern  | nel-based Multi-OS Architecture        | 11 |

|          | 3.1  | Backg   | round                                  | 11 |

|          | 3.2  | Implei  | mentation                              | 13 |

|          |      | 3.2.1   | L4-embedded $\ldots$                   | 14 |

|          |      | 3.2.2   | Wombat                                 | 15 |

|          |      | 3.2.3   | L4/TOPPERS                             | 16 |

|          | 3.3  | Task (  | Grain Scheduling                       | 17 |

|          |      | 3.3.1   | Full- and Para-virtualization          | 17 |

|          |      | 3.3.2   | Scheduling Algorithm                   | 18 |

|          |      | 3.3.3   | Global Priority                        | 18 |

|          |      | 3.3.4   | Global Scheduler                       | 19 |

|          |      | 3.3.5   | Task Grained Scheduling in L4-embedded | 19 |

|          |      | 3.3.6   | Task Grained Scheduling in Wombat      | 20 |

|          |      | 3.3.7   | Task Grained Scheduling in L4/TOPPERS  | 20 |

|          | 3.4  | Evalua  | ation                                  | 21 |

|          |      | 3.4.1   | Context Switch Overhead                | 22 |

|          |      | 3.4.2   | Interrupt Delay Overhead               | 22 |

|          |      | 3.4.3   | Task Grain Scheduling                  | 24 |

|          |      | 3.4.4   | Interrupt Delay Jitters                | 26 |

|          | 3.5  | Relate  | ed Work                                | 27 |

|   |      | 3.5.1 Improving OS Real-time Performance                               | 27         |

|---|------|------------------------------------------------------------------------|------------|

|   |      | 3.5.2 Hybrid Architecture                                              | 28         |

|   |      | 3.5.3 Hypervisor-based Systems                                         | 28         |

|   | 3.6  | Summary                                                                | 29         |

| 4 | Soft | tware-based Processor Core Multiplexing 3                              | 81         |

| - | 4.1  |                                                                        | 31         |

|   | 4.2  |                                                                        | 33         |

|   | 1.2  |                                                                        | 33         |

|   |      |                                                                        | 35         |

|   | 4.3  |                                                                        | 37         |

|   |      |                                                                        | 37         |

|   |      |                                                                        | 38         |

|   | 4.4  |                                                                        | 39         |

|   |      | 4.4.1 Basic Overhead                                                   | 39         |

|   |      | 4.4.2 Engineering Cost                                                 | 40         |

|   |      | 4.4.3 The Effect of Linux Load to TOPPERS Real-time Responsiveness . 4 | 41         |

|   |      | 4.4.4 The Effect of TOPPERS Periodic Task Load to Linux Throughput . 4 | 17         |

|   | 4.5  | Related Work                                                           | 17         |

|   | 4.6  | Summary                                                                | 50         |

| 5 | Cor  | re-local Memory Assisted Protection 5                                  | 51         |

| 0 | 5.1  |                                                                        | 51         |

|   | 5.2  | The LLM Architecture                                                   |            |

|   | 5.3  |                                                                        | 54         |

|   | 0.0  | 0.0                                                                    | 31         |

|   | 5.4  |                                                                        | 52         |

|   | 5.5  | Evaluations                                                            |            |

|   |      |                                                                        | 64         |

|   |      | -                                                                      | 66         |

|   |      | 5.5.3 Engineering Cost                                                 | 67         |

|   | 5.6  |                                                                        | 68         |

|   | 5.7  |                                                                        | <u>6</u> 9 |

| 6 | Cor  | nclusion 7                                                             | 1          |

# List of Figures

| 1.1  | Organization of the Dissertation                                             | 3  |

|------|------------------------------------------------------------------------------|----|

| 3.1  | Task grain scheduling                                                        | 13 |

| 3.2  | Wombat                                                                       | 15 |

| 3.3  | L4/TOPPERS                                                                   | 16 |

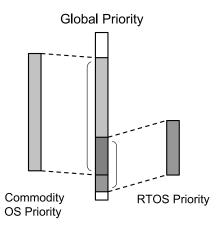

| 3.4  | Mapping the local priorities to the global priority                          | 18 |

| 3.5  | Global scheduler                                                             | 19 |

| 3.6  | Serial interrupt delays                                                      | 22 |

| 3.7  | Direct and indirect interrupt delays                                         | 23 |

| 3.8  | Dummy tasks without and with task grain scheduling                           | 25 |

| 3.9  | Testing task grain scheduling                                                | 26 |

| 3.10 | The intervals of TOPPERS's 2ms periodic task                                 | 27 |

| 4.1  | SPUMONE based system on a single-core processor                              | 33 |

| 4.2  | SPUMONE based system on a multi-core processor                               | 33 |

| 4.3  | Interrupt Delivery Mechanism                                                 | 38 |

| 4.4  | The interrupt priority levels assignment                                     | 38 |

| 4.5  | Virtual core migration                                                       | 39 |

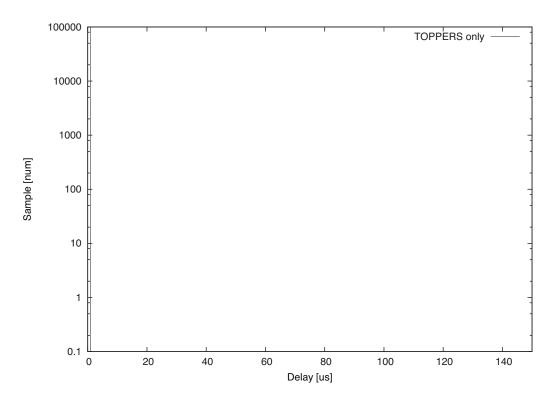

| 4.6  | The dispatch delay of $1ms$ periodic task on native TOPPERS)                 | 42 |

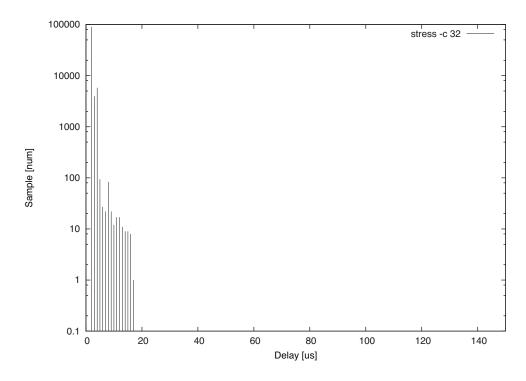

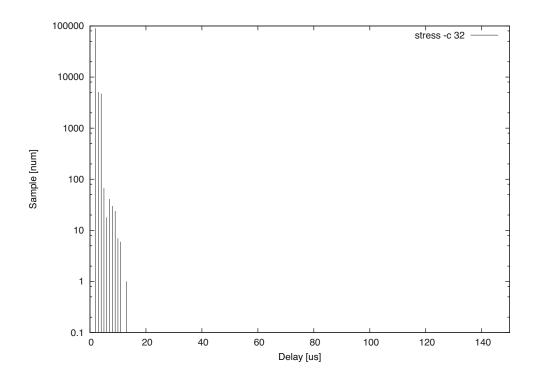

| 4.7  | Dispatch delay (CPU stress on Linux without IPL modification)                | 43 |

| 4.8  | Dispatch delay (CPU stress on Linux with IPL modification)                   | 43 |

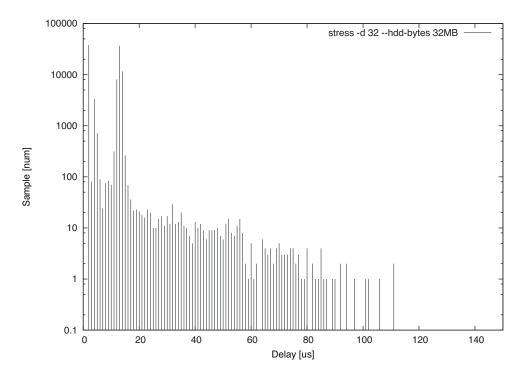

| 4.9  | Dispatch delay (CF read/write stress on Linux without IPL modification)      | 44 |

| 4.10 | Dispatch delay (CF read/write $\tt stress$ on Linux with IPL modification)   | 44 |

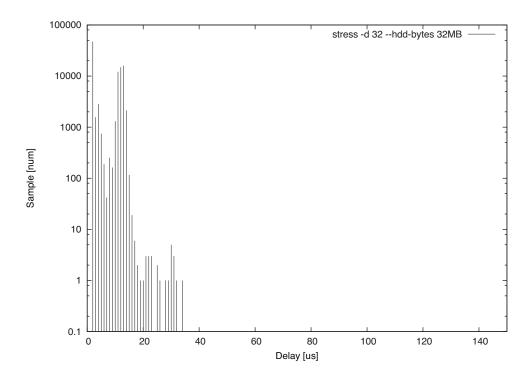

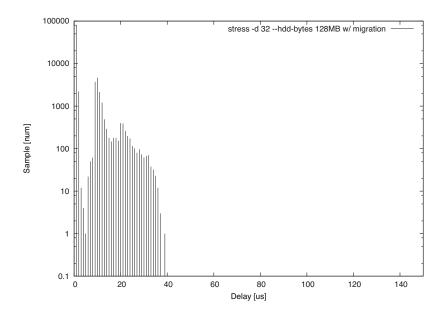

| 4.11 | Dispatch delay (NFS r/w $\tt stress$ on Linux without virt. core migration)  | 45 |

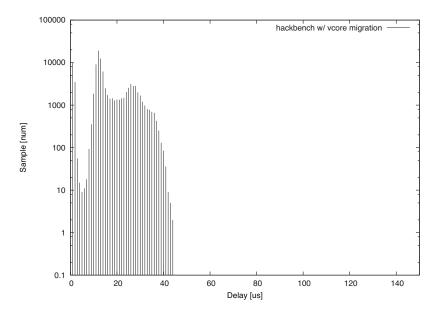

| 4.12 | Dispatch delay (NFS r/w $\tt stress$ on Linux with virt. core migration) $~$ | 45 |

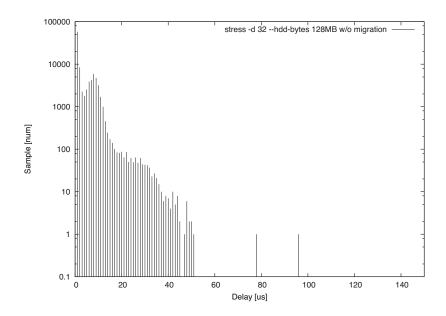

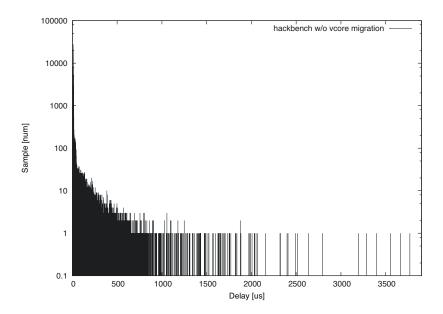

| 4.13 | Dispatch delay on SMP (frequent IPC on Linux without virt. core migration)   | 46 |

| 4.14 | Dispatch delay on SMP (frequent IPC on Linux with virt. core migration) .    | 46 |

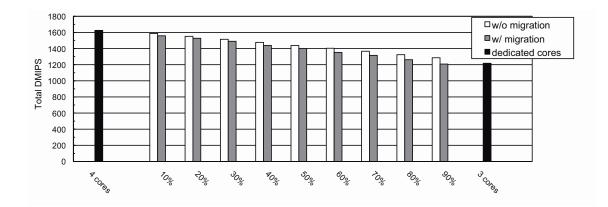

| 4.15 | The effect of load on TOPPERS to Linux's DMIPS score (y-axis in DMIPS,       |    |

|      | larger is better)                                                            | 48 |

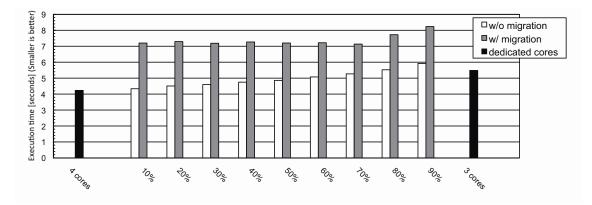

| 4.16 | The effect of load on TOPPERS to Linux's hackbench (y-axis in seconds,       |    |

|      | smaller is better)                                                           | 48 |

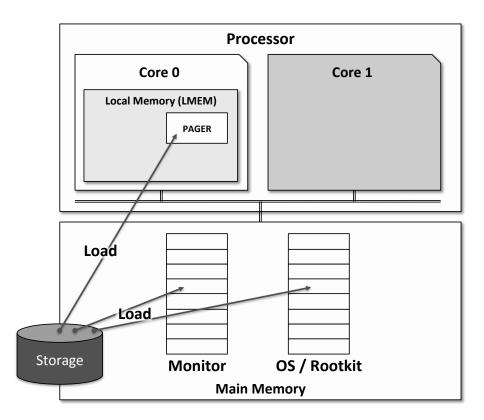

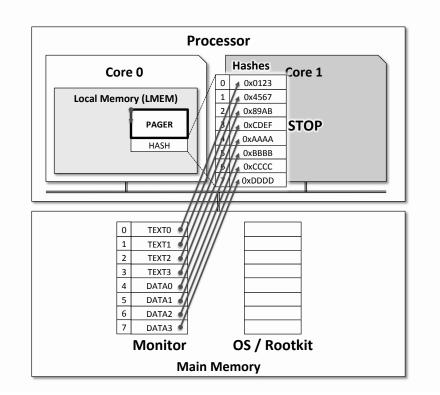

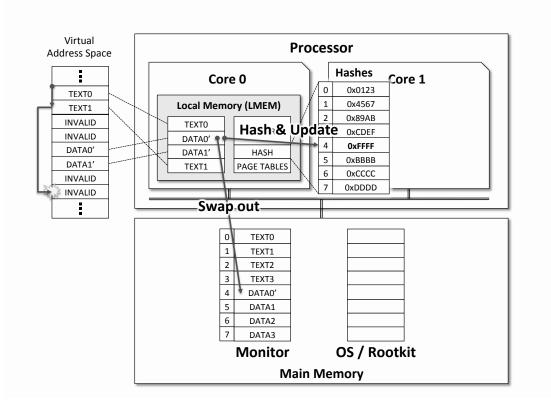

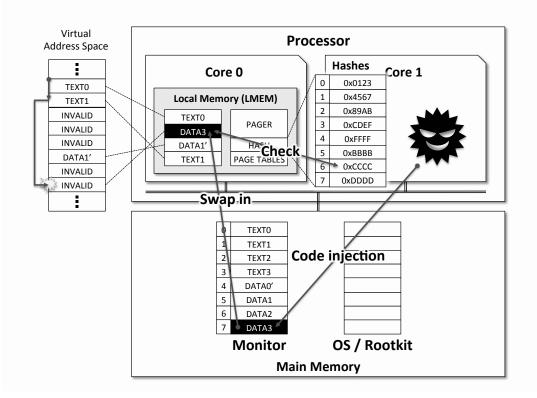

| 5.1  | Loading the pager, the monitor and the target OS                            | 55 |

|------|-----------------------------------------------------------------------------|----|

| 5.2  | The pager calculates the hash value of each page. The target OS is not      |    |

|      | activated at this point                                                     | 56 |

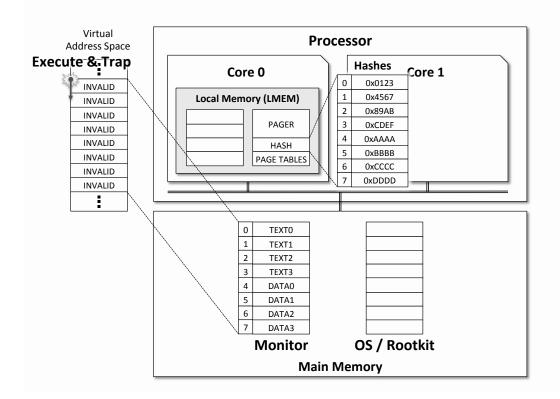

| 5.3  | Execute the entry of the monitor and trap into the pager                    | 57 |

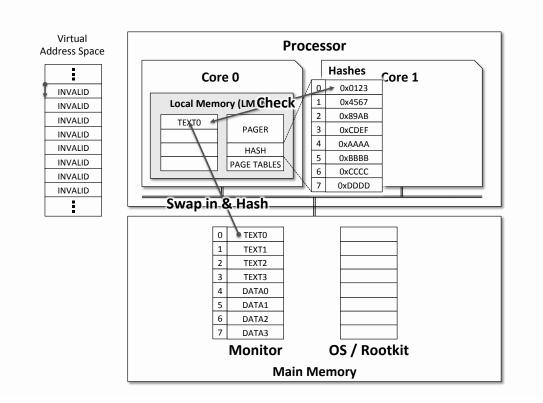

| 5.4  | The pager swaps in a page while calculating its hash value, and checks if   |    |

|      | the page is altered                                                         | 58 |

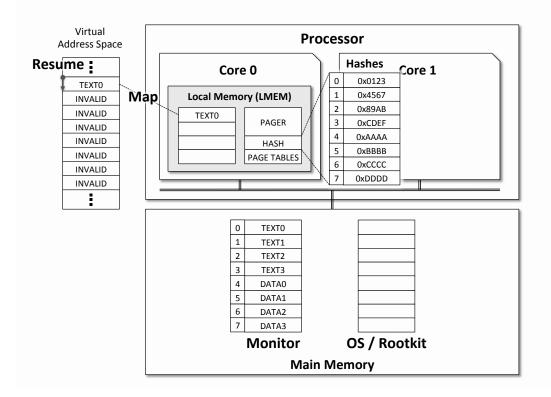

| 5.5  | The pagers maps the checked page into the address space                     | 59 |

| 5.6  | The pager tries to evict a page contained in the local memory to the main   |    |

|      | memory                                                                      | 60 |

| 5.7  | The pager detects a data page that is tampered by a malicious application   |    |

|      | running on the target OS                                                    | 61 |

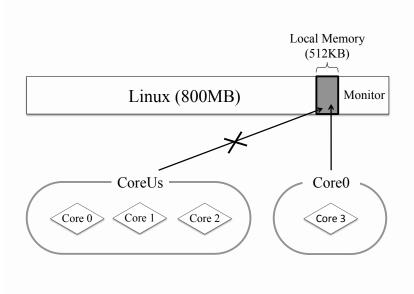

| 5.8  | The memory layout of the pseudo LLM architecture                            | 64 |

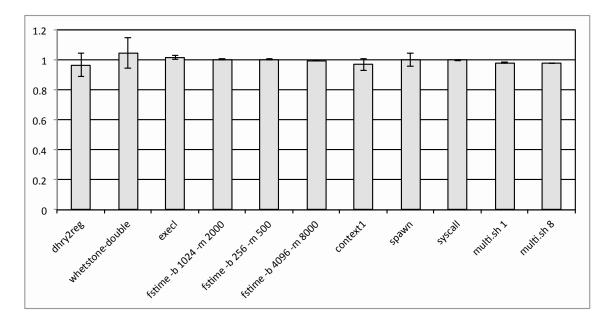

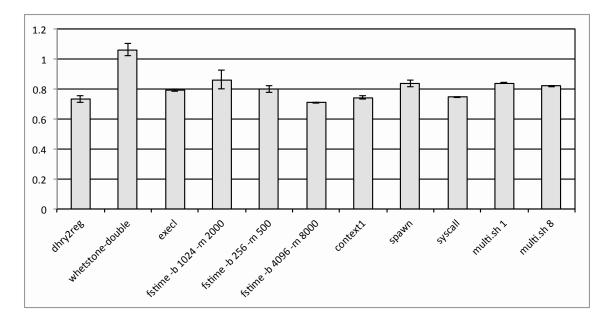

| 5.9  | The result of Unixbench on Linux with 3 cores running beside the monitor    |    |

|      | and the secure pager. Normalized to the score of native Linux with 3 cores. | 66 |

| 5.10 | The result of Unixbench on Linux with 3 cores running beside the monitor    |    |

|      | and the secure pager. Normalized to the score of native Linux with 4 cores. | 67 |

## List of Tables

| 3.1 | Evaluation settings                                             | 21 |

|-----|-----------------------------------------------------------------|----|

| 3.2 | Average interrupt delay: in <i>microseconds</i> (cycles)        | 23 |

| 3.3 | Worst interrupt delay: in <i>microseconds</i> (cycles)          | 23 |

| 3.4 | Average indirect timer interrupt delay: in $microseconds$       | 24 |

| 3.5 | Dummy tasks                                                     | 25 |

| 4.1 | A list of the modifications to the Linux kernel                 | 37 |

| 4.2 | The delay of handling the timer interrupts in TOPPERS.          |    |

| 4.3 | Linux kernel build time                                         | 40 |

| 4.4 | The total number of modified LoC in *.c, *.S, *.h, Makefiles    | 41 |

| 5.1 | Lines of code modified in web (row4) to greate the monitor OS   | 67 |

| 0.1 | Lines of code modified in $xv6$ (rev4) to create the monitor OS | 07 |

| 5.2 | Lines of code modified in Linux to run on the LLM architecture  | 68 |

## Chapter 1

## Introduction

Personal mobile devices are rapidly enhancing their functionalities. Not limited to phone and text messages, they offer web browsing via the Internet, free to install applications on the users' requests, play musics and videos, etc. At this point writing this thesis the latest device is equipped with multiple processor cores run with over 1.4GHz frequency and a gigabyte of memory [6]. This outstrips the performance of desktop computers those were available in 1990s.

As their hardware advances, now they are capable of running multiple OS instances with support of virtualization [9, 17, 32]. Like the use in desktop/enterprise systems, virtualization for embedded mobile devices allows consolidating multiple OS instances and enhancing the security of hosted OS environment. In addition, there are applications specific to embedded systems such as hosting real-time OS (RTOS) and application OS (GPOS) concurrently without spoiling the real-time responsiveness of the RTOS. These benefits of virtualization motivated the ARM architecture to add a hardware virtualization support to their upcoming instruction set architecture (ISA) [62].

#### 1.1 Motivation

There is no doubt that virtualization brings many benefits to the embedded mobile devices, however virtualization is not a panacea. Additional layer of virtualization incurs additional complexity to the software stack of devices. The hypervisor should be designed carefully to achieve reasonable performance. The straightforward port of an existing hypervisor from the desktop/enterprise field to embedded field does not perform well [34]. Extra engineering efforts of developing such device might make the system prone to bugs and security risks. In Chapter 2, we discuss the advantages and disadvantage of using hypervisors for embedded systems to accomodate multiple OS kernels in detail.

In this dissertation we take the position that some applications of embedded virtualization can be supported with more light-weight methods. The hybrid architecture [24, 66, 44, 59] and the logical partitioning of OS kernels [54] suggest the feasibility of running multiple-OS system without support of hypervisors. Traditional pure-hypervisor based virtualization requires explicit splitting of the privilege level of a hypervisor and guest OSes. Instead we discuss methodologies for accommodating multiple-OS instances without help of a hypervisor layer. Limiting our goal to support real-time scheduling in multi-OS architecture and guaranteeing safe execution of security monitor, we leverage virtualization technologies and some architectural support to achieve our goal.

#### **1.2** Contributions

There are two contributions in this dissertation:

- We first focus on real-time and application OS consolidation, running a real-time OS (RTOS) and an application OS (or GPOS: general-purpose OS) concurrently on a single mobile device. For which we propose a thin abstraction layer SPUMONE that achieves better interrupt responsiveness than virtualization. SPUMONE tries to minimize the modifications to the guest kernels alongside the implementation size of the virtualization layer itself. We also leveraged the architectural feature of the experimental platform to mitigate the affect of the GPOS's activities to the real-time responsiveness of the RTOS.

- Next we focus on hosting a kernel integrity monitor for rootkit detection. The monitor is hosted within an isolated memory region that is protected by means of processor architecture. We propose the limited local-memory (LLM) architecture that guarantees safe execution under a privileged processor core without support of a hypervisor layer.

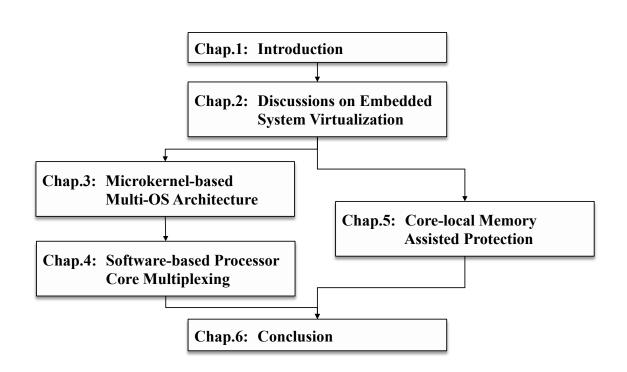

#### 1.3 Organization of the Dissertation

Figure 1.1 illustrates the structure of this dissertation. In the next chapter we discuss the tradeoffs of using virtualization in embedded systems. In Chapter 3, we first show our experience on running RTOS and GPOS on a embedded system VM that shows the overhead put into the interrupt handling. Chapter 4 follows the previous chapter, which introduces our light-weight virtualization technology that tries to eliminate the delay that we found in the experiment. The proposed methods minimize the interrupt delay caused by the interference of the application OS. In Chapter 5 we propose a method to run a security monitor without support of a hypervisor which requires a slight modification the architecture. Finally Chapter 6 concludes the dissertation.

Figure 1.1: Organization of the Dissertation

### Chapter 2

# Discussions on Embedded System Virtualization

In this chapter, we introduce the advantages and disadvantages of using a hypervisor in embedded systems, in order to backup the motivation of our proposal on running multiple OS without help of a hypervisor.

#### 2.1 The Use of Embedded System Virtualization

Mobile devices are capable of running multiple OS instances hosted by a hypervisor. The applications of hypervisors in the embedded systems are different from those in the desktop/enterprise world. The following describes the two major applications.

- Real-time scheduling. A hypervisor is leveraged for consolidating an application OS and a real-time control OS. A modern system-on-chip (SoC) for mobile devices equips application and baseband processors [7]. A baseband processor is in charge of handling mobile telecommunication signals, which usually runs a real-time OS that can handle interrupts within a hundred microsecond or even faster. Consolidating control and applications OSes to run concurrently on a single processor, the silicon vendor has an opportunity to simplify the design of the SoC. For this application, the hypervisor should be designed carefully to deliver interrupts with a reasonably small delay and to preserve the execution time of the tasks running on the RTOS. Type I hypervisor [51] is used to support this application. OKL4 [4] and virtualLogix VLX [9] are designed as type I hypervisor.

- Security enhancement. Virtualization may enhance the mobile device security [31]. OS can contain malicious attacks within the isolated virtual machine, not to propagate it to the remainder of the system, even when if the attacker promotes itself to the privileged mode. Since mobile devices are connected to the internet, as

the desktop/enterprise computers, we need to protect them from security attacks. Especially rootkits that stays in the system for long period of time can collect private informations.

Note that for the use in embedded systems, hypervisors need to support only a limited and fixed number of guests. For the enterprise use, it is worth running a number of application OS instances, however it is not always useful for personal users in embedded systems. A personal never use a second and a third Android unless paranoid about one's privacy, or using it in business. Some vendors use their hypervisors to integrate personal and business use cell-phones into a single device [17, 8]. Enterprises lend business phones to their employees, because personal phones may risk their security and confidentiality. Virtualization allows to install a virtual instance of a business phone into the personal phone, with which the second physical device would be unnecessary. An example of hosting two instances of Android OS is shown in [17]. Even in this case, they host guests up to two instances. Giving freedom of forking a number of virtual machines requires multiplexing the underlying peripherals and supporting virtual peripherals, which is difficult engineering because the hardware of the mobile devices varies from product to product. They use customized SoC that equips numbers of non-standardized controllers.

We take the position that an embedded system hypervisor does not require the rich functionalities we can find in the desktop/enterprise systems. Focusing our applications to the real-time support and security enhancement it is not necessary to host a complete symmetric OSes on an embedded device. Our proposal in Chapter 4 and Chapter 5 limits the use of OSes. RTOS accesses devices those are not used by the application OS, therefore it is unnecessary to virtualize peripherals. For the security purpose, the security monitor should run independently from the target OS in order to protect it from compromised by rootkits and to detect data inconsistencies. Eliminating some surplus features may contribute to simplify the design and the implementation of achieving the requirements, thus we claim these constraints and assumptions are reasonable for our background and challenges.

#### 2.2 Performance and Real-time Responsiveness

As discussed in [14] one of the primary requirements of hardware virtualization is low overhead. This is common among embedded and desktop/enterprise environment. Since embedded systems provide less computation power than desktop/enterprise systems, the overhead of virtualization is more critical. One of the main sources of the overhead of virtualizing hardware is the trapping between a hypervisor and guest kernels for instruction emulations. Another cause of the virtualization overhead is spatial isolation among guest kernels. Switching the execution of virtual machines entails extra cache flushes and TLB misses. In addition to low overhead, embedded systems also require real-time responsiveness. A hypervisor like Xen [16] schedules its virtual machines with a time-sharing based manner which harm the responsiveness of the guest OS. In addition, co-existing OSes may interfere the behavior of each other which may incur deadline misses. It is crucial to minimize the overhead of a hypervisor but also to minimize the affect of scheduling from the application OS to the real-time OS. In Chapter 3 we measured the real-time delay of a RTOS running on top of a hypervisor concurrently with a GPOS.

Hartig et al. [30] constructed a microkernel based system consisting of a real-time server and Linux running on top of L4 microkernel and investigated how to contain Linux's activity not to affect the real-time server. They modified Linux not to block the interrupts of processor and leveraged cache coloring to force exclusive usage of cache memory. In Chapter 4 we propose our method of reducing the real-time delay of a virtualized RTOS.

#### 2.3 Engineering Cost

Because of the absence of the hardware virtualization support by embedded processors, a commodity embedded system hypervisor adopts para-virtualization technique. The ARMv7 architecture has a number of instructions that do not trap in the user-mode but their behaviors rely on the privileged state of the processor. These instructions are called *sensitive* instructions [52]. In the terminology introduced by the early research on the virtualization by Popek and Goldberg [51], ARMv7 is not a virtualizable architecture. These sensitive instructions can be virtualized by dynamic translation [57, 19], replace with the help of compilers [41] and rewriting them by hand which is known as para-virtualization [65, 16]. Para-virtualization requires the modification of guest OS kernels, which entails engineering cost of replacing sensitive instructions with emulating instructions and trap into the hypervisor.

A number of enterprise servers and desktop computers may share the same paravirtualized OS. This can be also benefit in embedded systems which use the same GPOS, but the RTOS varies from manufacturers to manufacturers and products to products. Considering various combinations of RTOSes and GPOSes, even though the engineering cost of constructing a single hybrid system is claimed to be small enough, the engineering cost for supporting various combinations of RTOSes and GPOSes would still introduce a great engineering effort.

Constructing Multi-OS environment needs to balance the engineering cost and the overhead. An ideal hypervisor may not require modifications to guest OSes [31]. The drawbacks of engineering cost in the para-virtulization is not found in full-virtualization. Full virtualization exposes an interface identically to underlying hardware. However it introduces large overhead to guest OSes. In addition, it requires vast modifications to the ISA of processor cores, which might be available only for some high-end SoC products

that consumes more processor power and dominates larger area on the chip.

Hybrid kernels reduce these overheads by putting OS kernels in the same privileged mode. They run a GPOS kernel as a task on a RTOS kernel. The underlying RTOS can handle interrupts in real-time while running the GPOS as a non-real-time task of it. The drawback of the hybrid approach is the modification required to the guest kernel running on top of the RTOS. Since the RTOS exposes the binary interface different from the one of the underlying processor, the architectural part should be replaced by the API of the RTOS.

This motivated us to develop a light-weight abstraction layer that leverage architectural features that requires simple extensions to the processor and some features expected to be ubiquitous among future embedded processors. We also try to minimize the modification to hosted OS kernels, which allows adopting various combinations of RTOSes and GPOSes with reasonable engineering effort. We introduce the design of our virtualization layer SPUMONE in Chapter 4 which minimizes the required modifications to the guest OS kernels.

#### 2.4 Security

Strong isolation among OSes is an attractive feature for constructing a secure and reliable embedded system[31]. One of the approaches is to offer the spatial isolation in embedded systems is to use the microkernel. However, supporting spatial isolation with reasonable overhead requires a large amount of modification to the OS kernels. Also, for making IPC predictable, microkernels need to integrate IPC and synchronization, and it makes the microkernel complex and IPC slow as described in [47].

Despite the wide adoption as a research platform of security researches, a hypervisor itself is also the target of security attacks. As their functionality extends, hypervisor have increased their code size; now they are prone to vulnerabilities. We can find vulnerability reports on Xen and VMware at National Vulnerability Database [3]. Some vulnerabilities report the possibility of malware subverting the hypervisor layer, which means capable of gaining the complete control over the system.

In order to enhance the security of a virtualized system, it is crucial to minimize its attack surface by reducing the size and complexity of the hypervisor layer. The microkernel design can simplify the design of the hypervisor layer [32, 56]. Microkernels expose a well-defined programming interface, that are high-level abstraction of physical resources. Processors are virtualized as threads and tasks, memory management is virtualized as map/unmap function, interrupts are virtualized as IPCs, etc. These high-level API requires para-virtualization of guest kernels which is larger engineering effort than replacing sensitive instructions. Furthermore, a simple design enables verification of the microkernel. seL4 adopted formal verification to a microkernel [38]. It accomplished developing a bug free hypervisor, however it is applicable under strict limitations. For instance, in seL4's implementation, interrupts are replaced with polling on a signal, which introduce unpredictable delay into the interrupt delivery. This limitation disallows hosting real-time tasks on the microkernel.

In Chapter 5 we work on a method to protect a security module that runs beside the target without the support of a hypervisor.

### Chapter 3

# Microkernel-based Multi-OS Architecture

The emergence of functional embedded systems such as cell-phones and digital appliances brought up a new issue, building a system that supports both real-time and rich services. One of the solutions is leveraging a hypervisor to integrate a real-time operating system (RTOS) and an application operating system (or GPOS: general-purpose operating system) into a single device. In this chapter we report our experience on developing a preliminary setup of such solution with a real-world machine. We reveal sources of the overheads in the pure-hypervisor based multi-OS environment in order to discuss the design of multi-OS environment suitable for embedded system, which we introduce in the next chapter. We constructed a prototype system with an existing hypervisor, an RTOS, and a GPOS, measured some basic overheads. The experiments show that the GPOS's activities entail non-negligible overhead to the delay of interrupts sent to the RTOS.

#### **3.1** Background

In recent years, as seen in cell-phones and digital appliances, the scale and the complexity of softwares for embedded systems are increasing rapidly. These devices integrate large and complex softwares supporting functions such as network, multimedia and GUI. Despite the expansion of the software scale, software development time cycle is shortened, which entails bugs and insufficient reliability to their products. Developers are trying to leverage platforms and middleware to increase software reusability and also to extend an embedded OSes to support memory protection mechanism to increase their reliabilities. However, still the cost of their software engineering and testing is high.

To overcome these problems, GPOSes, originally targeting desktop/enterprise systems, are ported to embedded systems and already widely used. A typical example is Linux[61]. By using GPOSes in embedded systems, a wide variety of applications, network protocols, libraries and middlewares developed in desktop/enterprise systems can be reused. Also they provide a memory protection mechanism which can isolate applications to increase the system reliability.

While there are various advantages leveraging GPOSes in embedded systems, some technical challenges remain. A small memory footprint, short bootup time, and especially a real-time scheduling is one of the most challenging issue. There are still many efforts being made to shorten their response time. For instance, Molnar developed the real-time preemption patch [45] for Linux, which reduces the response time of the Linux kernel by making it preemptible. According to the analysis of Abeni et al.[13], the maximum kernel latency would be 28 milliseconds (ms) in traditional Linux, and 17 ms in Linux with the preemption patch. Even though applying the patch to the kernel, Linux still cannot achieve a few microseconds latency which is generally supported by embedded RTOSes used in traditional embedded systems.

Cell-phones balance real-time responsiveness and rich functionality by using some additional processors. A RTOS and a GPOS run simultaneously on their own dedicated set of a processor and memory. Modern cell-phones integrate these processors and memory into a single system-on-chip (SoC) [7]. However, an additional processor increases the price of the product by dominating some area on the chip. Even if the price of a single processor is a few dollars, cell-phones are sold in order of hundred thousands, so the resulting total production cost cannot be negligible.

In recent years, leveraging hypervisor in embedded systems has been focused to overcome these problems. A hypervisor enables integrating RTOS with low latency and GPOSes with rich services by running both of them simultaneously in a single device. Some early researches on consolidating a RTOS and a GPOS on a single embedded device are done by the ERTOS<sup>1</sup> group at NICTA<sup>2</sup>, developed Iguana[1], an L4 microkernelbased embedded real-time platform, and Wombat[40], para-virtualized Linux which runs in Iguana. Oikawa et al. also ported a RTOS to the L4 microkernel and to their own hypervisor. They evaluated the overhead of interrupt handling[49, 48]. The result shows that the overhead can be kept small enough. By giving a higher fixed priority to a virtualized RTOS, the real-time tasks reside in the RTOS can preserve their short response time. The hypervisor model let multiple OSes to share a single processor, which results in reducing the number of processors implemented on a device.

In this chapter, we introduce our experience on developing a multi-OS system that hosts a RTOS and a GPOS on an embedded system hypervisor. We used the above research contributions, the L4 microkernel, Wombat, Iguana. As a RTOS, we ported the work of para-virtualizing TOPPERS by Oikawa et al. that runs on the older version of the L4 microkernel to the latest version at the time. We evaluated the overhead of

<sup>&</sup>lt;sup>1</sup>Embedded and Real-Time Operating Systems (http://www.ertos.nicta.com.au/)

<sup>&</sup>lt;sup>2</sup>National ICT Australia (http://nicta.com.au/)

virtualization especially the interrupt latency on real-world hardware.

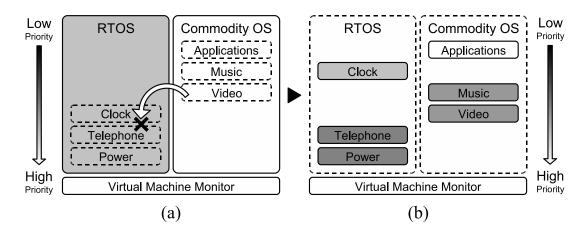

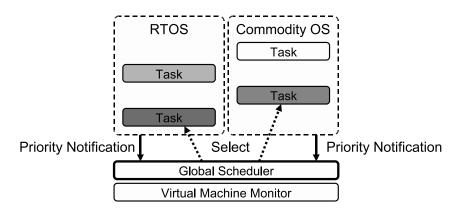

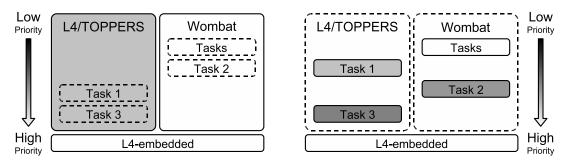

We also work on the problem that dispatching the RTOS prior to the GPOS in hypervisor-based systems limits real-time task deployment between guest operating systems. The task scheduling by a hypervisor is done in a unit of an OS, so it does not care about the priorities of the tasks running in guest OSes; therefore, all the high priority tasks should reside in the RTOS, and the remaining low priority tasks in the GPOS. There do exist applications for an RTOS which do not require high priority, and applications for a GPOS which requires high priority (Figure 3.1 (a)) such as an video player. Therefore we propose a task grain scheduling which enables a scheduling in a unit of a task by a hypervisor; even tasks are deployed in different guest OSes they can be prioritized (Figure 3.1 (b)). The proposed scheduling scheme shall increase the flexibility of the realtime task deployment in a hypervisor based multi-OS system, which leads to increasing the reusability of low priority applications for RTOSes and high priority applications for GPOSes.

Figure 3.1: Task grain scheduling

The next section introduces some related work. Section 3.2 introduces the implementation of our prototype system. Section 3.4.3 introduces the design of the task grain scheduling. Section 3.4 introduces the results of the evaluation. Finally Section 3.6 summarizes this chapter.

#### 3.2 Implementation

We built a prototype system with L4-embedded[2] as a hypervisor, Wombat as a guest GPOS, and TOPPERS/JSP 1.3 as a guest RTOS. In this section, we briefly introduce the hypervisor and the guest OSes, and describe how we implemented the task grain scheduling in our prototype system.

#### 3.2.1 L4-embedded

L4-embedded (L4 in following sentences) is a microkernel which shares some common features with a hypervisor. It has a capability to run para-virtualized OSes. Wombat is one of them, a para-virtualized Linux runs on L4. L4 supports IA-32, ARM, MIPS, and PPC architectures. This time, we implemented our prototype system in the IA-32 architecture version of L4.

The main functions provided by L4 are thread management, memory management, inter process communication (IPC), and interrupt handling. Their detail follows.

- Thread management. A thread is a unit of scheduling done by L4. The scheduling algorithm is fixed priority preemptive scheduling. Each one of the threads has its own context. The usages of threads in virtualized guest OSes are described in Section 3.2.2 and Section 3.2.3.

- Memory management. L4 provides some flexible memory management functions to user space applications, creating a memory space, mapping and unmapping page frames between memory spaces, etc. Multiple threads can reside in a single memory space. Wombat leverages these functions to manage address spaces since the functions provides features equivalent to an MMU.

- **IPC.** Data passing and synchronization between threads are done by IPC. The IPC function provided by L4 can be preformed either with or without passing data. In addition, IPC can be performed without blocking (asynchronous IPC). Also software interrupts and processor exceptions are translated to IPC message by L4, and sent to corresponding threads. Systems calls and page faults triggered by Wombat processes are handled by using this mechanism.

- Interrupt. Hardware interrupts are passed to threads as IPC messages from pseudo IRQ threads. To which thread a specific interrupt is notified, is set by L4 API. Generally, a thread which handles an interrupt is blocking to receive an IPC message from an interrupt source. When the thread has the highest priority than all other active threads (threads in ready state), it is dispatched immediately receiving the interrupt message. The interrupt from the same source is masked until the thread sends back a reply message to the corresponding IRQ thread.

- Device Servers. When a hardware is shared by multiple applications running on L4, the access to the hardware is arbitrated by using a device server. If a thread wants to access a hardware, it sends and receives IPC messages to corresponding device server. Since an interrupt message cannot be sent to multiple threads at the same time, a shared interrupt message is first sent to the device server, and then

Figure 3.2: Wombat

sent to the threads. For instance, a timer interrupt is generally used by numbers of OSes. In our prototype system it is used by both Wombat and L4/TOPPERS, so the interrupt is first sent to timer server, then to one of them.

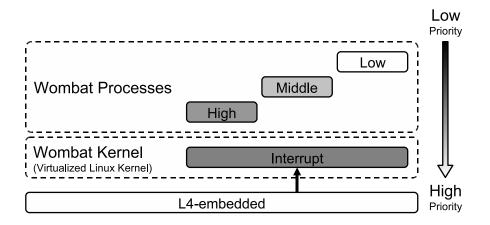

#### 3.2.2 Wombat

Wombat is a para-virtualized Linux which runs as a server on L4. Wombat we used in the prototype is based on Linux 2.6.10. It can run unmodified Linux applications.

#### Wombat Threads

Wombat consists of multiple L4 threads. In this section, we describe the role of each thread.

• Interrupt thread. The interrupt thread handles the interrupt messages sent to Wombat. It has the highest priority among the L4 threads running Wombat. Therefore when the message is sent, the interrupt thread is dispatched immediately even if other threads are running. The default L4 priority of the interrupt thread is set to 100.

After the L4 thread starts its execution, it calls interrupt\_loop() and get into an infinite loop. First it blocks to wait for an interrupt message. When it receives a message, calls a corresponding interrupt handler and blocks again to wait for another message. Before it blocks, it calls need\_resched() to check if rescheduling is necessary or not. If a task switch is going to be performed, it sends a message to the system call thread. Timer interrupt messages are sent from the timer server to the interrupt thread every 10 ms.

• System call thread. The system call thread handles system calls invoked by

Linux processes. Generally, system calls are implemented with software interrupt instruction. When a software interrupt is performed in a process, L4 traps and translate it to an IPC to the parent thread, which is a system call thread. When it finishes processing a system call, it sends a message back to the process and blocks again to wait for the next IPC. It is assigned L4 priority 99.

All system calls are handled by a single system call thread. To switch the context inside the Wombat kernel, the thread invokes arch\_switch(), which switches stacks and registers without trapping into L4. A corresponding process thread will be kept in block state until it is dispatched again.

When the quantum of a process is expired, a rescheduling message is sent to system call thread from interrupt thread. System call thread changes the state of corresponding process thread to **stop** state and switches to another kernel context by invoking **arch\_switch()**.

• **Process thread.** Process thread is a thread generated one for each Linux processes. Each Linux process has its own address space. All of them run in L4 priority 98. When it performs a system call, it block in **block** state till the reply IPC is sent. When the quantum is expired, the state of itself is changed by the system call thread to **stop** state. In this way, only one thread runs at a time.

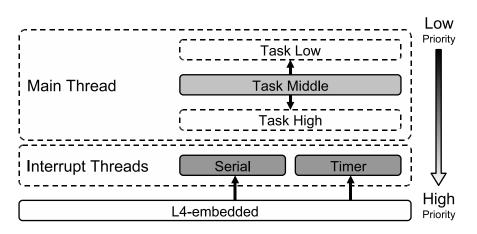

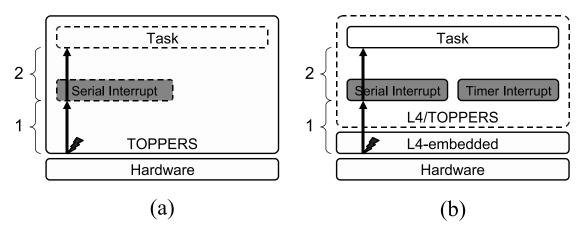

#### 3.2.3 L4/TOPPERS

L4/TOPPERS is a para-virtualized TOPPERS based on the porting done by Oikawa et al. In this section, we introduce the implementation of L4/TOPPERS and some extensions we made to support task grain scheduling.

Figure 3.3: L4/TOPPERS

L4/TOPPERS consists of the main thread and some interrupt threads (Figure 3.3). All the threads run in a single address space. The main thread executes all the tasks. Here we describe how we para-virtualized interrupt handling and interrupt locking mechanism in our system.

• Interrupt virtualization. Hardware interrupts are sent to interrupt threads, which they are created for interrupt source one each. All of them have a same priority. Timer interrupts are sent from the timer server.

When an interrupt thread starts executing, it associates itself to a specific interrupt source calling L4 API, gets in an infinite loop, and blocks to wait for an interrupt message. When an interrupt message is sent to the associated thread, it disabled interrupts and invokes an original L4/TOPPERS interrupt handler. When a new thread is activated, the interrupt thread changes the pc register and the sp register. of the main thread and let it switch to a new task.

- Interrupt lock. Original TOPPERS executes specific processor instructions to enable and disable interrupts. Since these instructions are privileged instruction, they cannot be executed by user-level applications. Therefore in L4/TOPPERS the interrupt disabling function should be implemented as locking and unlocking a common variable shared by threads.

- Idle state. When there is no active thread, the main thread invokes 14\_idle() which blocks to wait for an IPC message. Since there is no active threads in L4/TOPPERS in this state, other a thread in another OS can be executed. The main thread is resumed by sending IPC from interrupt threads.

#### 3.3 Task Grain Scheduling

In this section, we introduce the basic design of the task grain scheduling in hypervisor. Task grain scheduling enables assigning a higher priority to a task in the GPOS running concurrently beside the RTOS on top of an embedded system hypervisor.

#### 3.3.1 Full- and Para-virtualization

There are several different types of virtualization. One classification is full-virtualization and para-virtualization. A hypervisor supporting full-virtualization provides an interface identical to existing hardwares, so guest OSes could be run in it without any modification. The hypervisor with the task grain scheduling needs to acquire the information of guest OSes. To acquire the information in full-virtualization model, the hypervisor should know the binary layout of guest OSes and somehow trap some events such as task switches and priority changes. Since this introduce a great overhead to the hypervisor, full-virtualization is not suitable for implementing the task grain scheduling.

Figure 3.4: Mapping the local priorities to the global priority

In contrast, para-virtualization allows modifying guest OS source codes, so some hooks could be inserted into guest OSes to acquire information. The term para-virtualization was introduced in [65], and the basic idea already existed in early 1970s mentioned by Goldberg[26, 27]. In this chapter we consider only a hypervisor leveraging a paravirtualization technique.

#### 3.3.2 Scheduling Algorithm

The task grained scheduling targets a hypervisor and OSes supporting fixed priority preemptive scheduling, since it is generally supported by major RTOSes and also GPOSes to provide real-time tasks.

#### 3.3.3 Global Priority

Each OS has different scale of scheduling priority. Generally they are represented as integer numbers, but the value range (maximum and minimum) and the order (ascending, descending) differ. Therefore the priority of tasks running in different OS cannot be simply compared using their priority numbers. In our scheme we provide a global priority. By mapping the priority of each OS to the global priority as shown in Figure 3.4, tasks could be prioritized in a single common scale.

The priority of tasks running in different guest OS completely depends to a system configuration, so it is worthless to automate the priority mapping. The mapping should be done manually by developers during the design stage of the system. The mapping of priority numbers can be any kind of method, a simple addition or subtraction, giving a detailed mapping table, etc.

Figure 3.5: Global scheduler

#### 3.3.4 Global Scheduler

The global scheduler, which resides in a hypervisor selects OS running a task that has the highest global priority. A guest OS tells the priority of a currently running task on it to the global scheduler when tasks switches (Figure 3.5). With the fixed priority preemptive scheduling, the task switch occurs in following timings.

- The state of a task changes from running to block

- The state of a task changes from block to running

- A task is created

- A task is deleted

- The priority of a task is changed

In other words, this mechanism is a double layered scheduling. The guest scheduling is performed as it originally does, and the global scheduler performs the scheduling when the priority change is notified by guest OSes.

#### 3.3.5 Task Grained Scheduling in L4-embedded

In our prototype, the L4 priority is used as the global priority. The L4 priority is represented as 0 to 255 ascending (the larger is the prior) integer numbers. This range is bigger enough than the Linux and the TOPPERS priority range. Also, the L4 scheduler is used as the global scheduler. When a task is switched in a guest OS and the priority of currently running task changes, it modifies the priority of the thread by calling L4\_Set\_Priority() and the L4 scheduler is invoked by calling L4\_Yield().

#### 3.3.6 Task Grained Scheduling in Wombat

Linux supports two different types of scheduling algorithms, dynamic priority scheduling and fixed priority scheduling. This time, we map Linux fixed priority to the global priority. Note that the dynamic priority scheduling is done referring to the process **nice** value which is widely used in POSIX systems, but fixed priority has nothing to do with **nice**. In default Wombat, the priority of threads running Linux processes are always 98 in the L4 priority, regardless of the fixed priority set to the process. The fixed priority of Linux is represented as 0 to 99 ascending (the larger is the prior) integer. We calculate the global priority using following formulas.  $G_{W_P}(p)$  represents the global priority of a Wombat process p.  $P_W(p)$ represents the Linux fixed priority of a Wombat process p. It is written as **p**->**rt\_priority** in the Linux source code, in which **p** is a **task\_struct** structure pointer for a corresponding process.  $C_W$  represents the minimum global priority that can be set by Wombat.

$$G_{W_P}(p) = P_W(p) + C_W$$

$G_{W_S}(p)$  represents the global priority of a system call thread associated with the kernel context of a process p. The global priority of the system call thread changes dynamically with which process is running in Wombat.

$$G_{W_S}(p) = P_W(p) + C_W + 1 = G_{W_P}(p) + 1$$

$G_{W_I}$  represents the priority of the interrupt thread. It should have higher priority than the other Wombat threads. max(x) represents the maximum value that x could be.

$$G_{W_I} > max(G_{W_S}(p)) = max(P_W(p)) + C_W + 1 > G_{W_P}(p)$$

#### 3.3.7 Task Grained Scheduling in L4/TOPPERS

L4/TOPPERS notifies a priority to the global scheduler in following functions.

- dispatch\_r() is a function invoked when a task is dispatched. A task switch involves priority change, so priority is notified to the global scheduler.

- 14\_dispatch\_r() is a function invoked when a task is resuming from preemption. It involves priority change as well as dispatch\_r(), so the priority of resuming thread is notified to the global scheduler.

- check\_resched() is a function invoked by an interrupt handler to check if there is a pending task switch. If a new task is going to be activated, the priority of the new task is notified to the global scheduler.

Table 3.1: Evaluation settings

|                           | Wombat          | L4/TOPPERS      |

|---------------------------|-----------------|-----------------|

| Min/max priority          | $C_W = 93$      | $C_T = 110$     |

| Interrupt thread priority | $G_{W_I} = 100$ | $G_{T_I} = 120$ |

The priority of L4/TOPPERS is represented as 1 to 16 descending (the smaller is the prior) integer. T(t) represents the TOPPERS priority of a task t.  $G_T(t)$  represents the global priority of a task t. It is written as t->priority in the TOPPERS source code, in which t is a task\_control\_block structure pointer for a corresponding task.  $C_T$ represents the maximum global priority that can be set by L4/TOPPERS.

$$G_T(t) = C_T - T(t)$$

$G_{T_I}$  represents the priority of interrupt threads. It should be greater than the other TOPPERS threads.

$$G_{T_I} \ge C_T$$

$$C_T > max(G_T(t)) = C_T - 1$$

#### 3.4 Evaluation

We made evaluation with the prototype system in Section 3.2. The machine we used is DELL Precision 390; Intel Core2 Duo E6600 2.4GHz CPU, 2GB Memory and ATA133 512GB HDD. Core2 Duo is a dual core processor, but we used only one of the cores. To acquire the time we leveraged the **rdtsc** instruction which gives a time stamp which has an resolution of CPU ticks. We divide it with the frequency of the CPU and show them in *microseconds* ( $\mu$ s) or *milliseconds* (*ms*).

In the evaluation,  $C_W$  (the minimum global priority of the Wombat tasks),  $G_{W_I}$  (the global priority of the Wombat interrupt thread),  $C_T$  (the maximum global priority of the L4/TOPPERS tasks) and  $G_{T_I}$  (the global priority of the L4/TOPPERS interrupt threads) are set as shown in Table 3.1.  $C_W$  is 93 so it may expire  $G_{W_I}$ , but since the prototype system use only the Linux fixed priority from 0 to 5, it does not corrupt the scheduling.

Section 3.4.1 discusses about the context switch overheads. We evaluate direct and indirect interrupt delay as the basic overheads in Section 3.4.2. In Section 3.4.3, we run a dummy task set to try prioritizing tasks running in two different guest OSes. Section 3.4.4 evaluates the effect of frequent disk access performed in Wombat to a cyclic task running

in L4/TOPPERS.

#### 3.4.1 Context Switch Overhead

In case of L4/TOPPERS without the task grain scheduling, the basic context switch overhead is equivalent to original native TOPPERS. However since interrupts are interposed by L4, the task switch triggered by an interrupt would take longer time than native TOP-PERS. The overhead of the interrupt handling is shown in Section 3.4.2. Also, the context switch overhead of Wombat is described in [40] in detail.

When the task grain scheduling is enabled, system calls are invoked at every task switch to notify the priority of running task to the L4 scheduler. Therefore the time of an L4 system call is added to task switch overheads, for both L4/TOPPERS and Wombat.

#### 3.4.2 Interrupt Delay Overhead

The interrupt handling delay is increased when an OS is virtualized, because the interrupt is interposed by the underlying hypervisor. In this section, we measured and compared the delay of invoking interrupt handler for original TOPPERS (Figure 3.6 (a)) and L4/TOPPERS (Figure 3.6 (b)). We set measuring points at followings.

Figure 3.6: Serial interrupt delays

- TOPPERS

- The entry point of serial interrupt

- The beginning of serial handler

- The beginning of a task waiting for serial input

- L4/TOPPERS

- The entry point of serial interrupt in L4

- The beginning of the serial handler

- The beginning of a task waiting for serial input

The average of the delays are shown in Table 3.3. The overhead is  $3.46\mu s$ . The processing time between the entry point and the handler increases because of the virtualization. The increased overhead between the handler and the application is because the interrupt enabling and disabling instructions are replaced by alternative functions.

Table 3.2: Average interrupt delay: in microseconds (cycles)

| 1. Entry point - Handler 0.05 | 5(124) 2.45(5867)      |

|-------------------------------|------------------------|

| 2. Handler - Task 11.54       | 4(27623) 12.60 (30178) |

| Total 11.59                   | 0(27747) 15.05 (36045) |

Table 3.3: Worst interrupt delay: in *microseconds* (cycles)

|                          | TOPPERS/JSP   | L4/TOPPERS       |

|--------------------------|---------------|------------------|

| 1. Entry point - Handler | 0.07(171)     | 11.39(27270)     |

| 2. Handler - Task        | 19.28 (46170) | $13.95\ (33390)$ |

| Total                    | 19.35(27747)  | 25.34(60660)     |

We measured the overhead of interrupt handling with a device server (Figure 3.7 (b)), compare it with the direct interrupt handling (Figure 3.7 (a)).

Figure 3.7: Direct and indirect interrupt delays

The delay of passing an interrupt message to an user-level thread is almost same for indirect and direct (Table 3.4). The IPC passing from timer server to TOPPERS takes 9.18 $\mu s$ . Therefore the overhead of passing an interrupt message through a device server is  $8.98 \mu s$ .

|                                     | Direct | Indirect |

|-------------------------------------|--------|----------|

| Entry point - Thread                | 2.33   | 2.25     |

| Timer server - Handler (Indirect)   | -      | 9.18     |

| Interrupt thread - Handler (Direct) | 0.12   | -        |

| Total                               | 2.45   | 11.43    |

Table 3.4: Average indirect timer interrupt delay: in microseconds

The measurements show that the delay of handling interrupts directly is increased  $3.45\mu s$  (8298 cycles) because of the para-virtualization, and the overhead of handling interrupt through device server is  $8.98\mu s$ . Comparing these values with the original TOP-PERS, the delays are increased 30% and 90%. Whether this overhead is acceptable in constructing a system, depends on the requirement of a task set in the system. Note that the overhead is rather small comparing to the jitters in the Linux kernel. If this overhead is not negligible, one way to decrease it is to use a processor which has a higher frequency. Another way is to redesign the system not to share an interrupt source, or make the OS itself a device server.

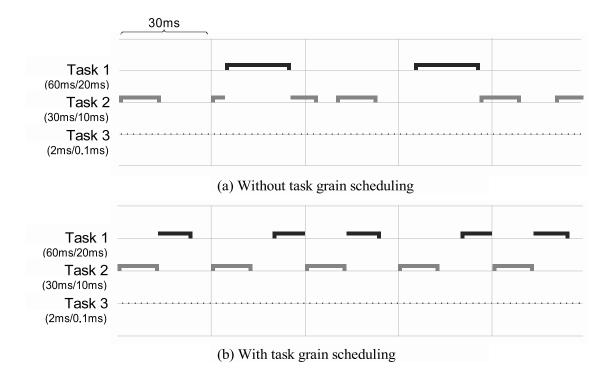

#### 3.4.3 Task Grain Scheduling

We observed the behavior of the task grain scheduling applying it to tasks shown in Table 3.5. This evaluation is done in DELL Precision 390, the machine described in detail at the top of this Section 5. Without the task grain scheduling, scheduling by the hypervisor is done in an unit of OSes (Figure 3.8 (a)), and with it done in an unit of tasks (Figure 3.8 (b)).

Task 1 and 3 are TOPPERS tasks which is activated in cycles shown in the table. Every time it is activated, it executes an empty loop for the execution time shown in the table.

**Task 2** is a real-time process running in Wombat. It executes an empty loop for 12ms.

We measured the time that tasks are activated and stopped without and with the task grained scheduling. The result is in Figure 3.9. To meet the deadline of Task 1, high priority is set to L4/TOPPERS. Therefore Task 1 gets a higher priority than Task 2, so the Task 2 is preempted when Task 1 is active. Thereby Task 2 misses its deadline as shown in Figure 3.9 (a).

(a) Without task grain scheduling

(b) With task grain scheduling

Figure 3.8: Dummy tasks without and with task grain scheduling

|          | OS         | Cycle | Execution time | L4 priority | Global priority |

|----------|------------|-------|----------------|-------------|-----------------|

|          |            |       |                | (w/o TGS)   | (w/TGS)         |

| Task 1   | L4/TOPPERS | 60ms  | 20ms           | 110 (High)  | 95 (Low)        |

| Task $2$ | Wombat     | 30ms  | 12ms           | 98 (Low)    | 96 (Middle)     |

| Task 3   | L4/TOPPERS | 2ms   | $100 \mu s$    | 110 (High)  | 105 (High)      |

Table 3.5: Dummy tasks

Figure 3.9 (b) shows the measurement with task grain scheduling. Task 2 is assigned a higher global priority than Task 1, so Task 2 is not preempted by Task 1. In this way, all the tasks meet their deadlines.

If we give following assumptions to the task set in Table 3.5, rate monotonic scheduling[39] can be applied.

- The tasks do not have any shared resources

- Deadlines are equal to cycles

- No overhead in task switch

The sum of CPU usage is,

$$0.1/2 + 10/30 + 20/60 = 0.71666...$$

Using the formula of rate-monotonic scheduling,

$$U = 3(\sqrt[3]{2} - 1) = 0.77976...$$

0.71666... < 0.77976

So these tasks can be guaranteed not to miss their deadlines.

Figure 3.9: Testing task grain scheduling

Since rate-monotonic scheduling has strict constraints, they are difficult to use in practical systems. However we believe the task grain scheduling increased the flexibility of priority setting in hypervisor-based system. If they try to overcome these problem without leveraging the task grained scheduling, task should be ported to another OS or task should be split to multiple tasks which both take big engineering costs.

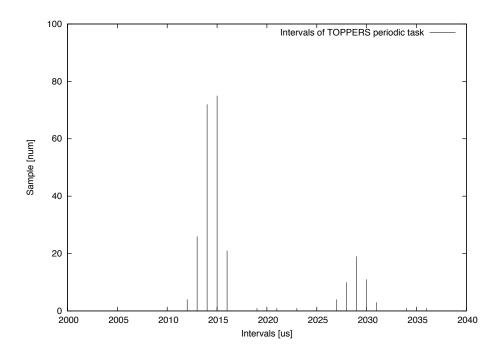

#### 3.4.4 Interrupt Delay Jitters

We measured the jitters introduced to the interrupt delay of para-virtualized TOPPERS. In the experiment, we run L4/TOPPERS and Wombat concurrently to see the effect of activities within Wombat. In this setup, all the tasks on L4/TOPPERS have higher priority than those on Wombat, which does not use the task grain scheduling. Critical sections in L4 could delay the dispatch of interrupt threads. When the API invocation in Wombat and the interrupt associated to L4 occurs in a same time, the dispatch of the L4/TOPPERS thread can be delayed.

We measured the intervals of L4/TOPPERS's periodic task which runs every 2ms, with running Wombat heavily loaded with a program accessing a HDD. We compare the cycle of the task with running them with the The y-axis shows the interval time from the previous dispatch time to the dispatch time of a cyclic task. The x-axis shows the iteration, how many times the cyclic task is dispatched. The worst case experienced  $19\mu s$

(44198 cycles) additional delay over the average interval of  $2017\mu s$  (4829941 cycles).

Figure 3.10: The intervals of TOPPERS's 2ms periodic task.

# 3.5 Related Work

In this section, we classify related work into three different groups, and compare with our approach.

#### 3.5.1 Improving OS Real-time Performance

There are some efforts made to modify an existing GPOS to support real-time scheduling. As we mentioned in Section 3.1, Molnar developed the Linux real-time preemption patch [45] which enables Linux to preemption processes in the kernel area. Ishiwata et al. extended the Linux kernel to support hard real-time tasks by replacing spin locks with mutex locks that support the priority inheritance [35, 36]. Some commodity products are also supporting extension to satisfy short response time required by embedded systems, such as MontaVista Linux [46].

In this approach, the task scheduling could be done in a unit of tasks (or process, in POSIX systems). However supporting both real-time and high throughput are contradicting concept. Supporting both of them at a time entails a complex system design, implementation and great engineering cost. Furthermore comparing to the hypervisorbased systems, applications for different OSes should be ported, or black box applications for other OSes can not be used.

#### 3.5.2 Hybrid Architecture

RTLinux [24], RTAI [44] are real-time extended Linux implementation, which are interpolating a microkernel between the Linux kernel and the underlying hardware to achieve the short interrupt response time and guaranteed real-time scheduling. RTLinux is replacing a part of Linux's hardware abstraction layer by their own real-time microkernel. In contrast, RTAI is implemented as Linux modules and giving minimal modification to the Linux kernel, though their basic ideas are the same. In this model, Linux processes never affect the behavior of the microkernel and its tasks, since the interrupt disabling instructions are removed from the Linux kernel and it only can disable the interrupt virtually. All the interrupts are first send to the microkernel and then to the Linux kernel. In this case, the priority of the Linux processes are always the lowest.

Linux on ITRON is Linux running as a task of the ITRON real-time OS[59]. The architecture of Linux on ITRON is similar to the technique taken by RTLinux and RTAI. The major difference is that Linux on ITRON is using an existing RTOS based on  $\mu$ ITRON specification as its interpolation layer. This gives an additional advantage of reusing existing applications compatible with  $\mu$ ITRON specification. Some discussions about the coarse grain scheduling of real-time tasks were discussed in the paper, but they have not implemented fine grained scheduling in their system.

Comparing to the hypervisor-based approach, hybrid architecture lacks flexibility to select an RTOS. RTLinux and RTAI provides its own API to real-time processes, which are not compatible with existing APIs. Linux on ITRON provides the  $\mu$ ITRON API to real-time processes, but no choice to use other RTOS APIs.

#### 3.5.3 Hypervisor-based Systems

A hypervisor is a system level software which enables multiple OSes to share hardwares, such as a processor, memory, and sometimes other peripheral devices. Each guest OSes runs in an isolated address space, so the fault of an OS does not affect other OSes. This characteristic is anticipated to make embedded systems more robust.

When the hypervisor itself supports real-time scheduling, it could be potentially used as a platform for running real-time applications. This is mentioned by David Golub et al. in the paper introducing an Unix server on the Mach microkernel[28]. Also, some efforts were made to make Mach real-time[47].

Xen[16] is a hypervisor developed for servers and desktops. It supports both para-

virtualization and full-virtualization. With para-virtualization, it can run modified Linux (XenoLinux) as its guest OS. Applications can run on XenoLinux without any modifications. Both full virtualization and para-virtualization is supported. A group in Samsung has experimentally ported Xen to the embedded ARM architecture, whose purpose was to enhance the security of devices [34]. The experiment does not discuss on interrupt lantencies. The scheduling of Xen aims to sustain system throughput, but not real-time responsiveness. The main scheduling algorithm is BVT[23] which sets a weight to each OS as a parameter. The processor usage of each OS get close to the ratio of weight after running for awhile. In this chapter we target embedded systems which require real-time scheduling. Achieving guaranteed real-time scheduling and high system throughput are contradicting concept.

L4Linux is a Linux kernel implemented on top of the L4Ka microkernel as a server[29]. Some additional work has been done for integrating real-time applications and L4Linux on top of L4Ka[30]. The purpose of this research was not scheduling granularity but good performance isolation. They 'tamed' Linux not to affect real-time tasks running beside it on top of L4Ka.

Oikawa et al. ported the TOPPERS/JSP kernel <sup>3</sup> [60] (TOPPERS for short) to the TL4 microkernel (TL4 for short) which is a modified L4Ka::Hazelnut kernel[58]. In other words, they built a TOPPERS interface on top of L4. TL4 has a capability to run multiple instances of TOPPERS. Each of them runs in an isolated memory space provided by TL4. Therefore, the entire TOPPERS kernel and its applications can be directly reused. They measured the delay of interrupt handling and task dispatch. The results show that the overhead is small and delay is close to the original TOPPERS. This research shows that the overhead of virtualization can be reasonable value.

Iguana is a real-time embedded platform constructed on the L4-embedded microkernel. In parallel, para-virtualized Linux, called Wombat, is developed on top of Iguana. Iguana was developed to facilitate the programming in the L4-embedded based system since L4-embedded supports only primitive mechanisms. Our work is using Iguana and Wombat as its platform. We ported the work of Oikawa et al. to the Iguana platform, and let TOPPERS run on L4-embedded beside Wombat.

Today, products such as VLX [8] and VMware Mobile [17] are available. The L4embedded project is now branched to the OKL4 project [4].

# 3.6 Summary

In this chapter we introduced our experience on developing a multi-OS architecture for embedded system that hosts a RTOS and a GPOS. We evaluated the real-time responsiveness of our implementation on the real-world machine. The result shows that the

$<sup>^{3}\</sup>mathrm{TOPPERS/JSP}$  is an embedded RTOS compatible with  $\mu\mathrm{ITRON}$  specification

hypervisor introduced large interrupt delay overhead into the interrupt response time of the RTOS. In addition the interrupt source shared between the OSes entailed jitters into the cycles of the periodic task. This is the limitation of the architecture which requires sharing an interrupt source between guest kernels.

We also developed the task grain scheduling on our implementation, which give flexibility of assigning a priority higher than tasks on the RTOS to tasks on the GPOS. Adopting the method we succeeded to let the experimental task set to fulfill the requirement of applying the rate-monotonic scheduling to meet the deadline.

# Chapter 4

# Software-based Processor Core Multiplexing

Despite the strong requirement of supporting deterministic real-time scheduling on virtualization based multi-OS embedded systems, which enables co-location of a RTOS and a GPOS on a single device, there are few investigations in real-world hardware. In this chapter we introduce our virtualization layer SPUMONE, which runs on single-core and multicore SH-4A processors which introduces low overhead and requires small engineering effort to modify guest OS kernels. SPUMONE now can execute the TOPPERS RTOS and Linux as a GPOS concurrently on a single embedded test platform. In addition we propose two methodologies to mitigate the interference of Linux to the real-time responsiveness of the RTOS. One leverages the interrupt priority level mechanism supported by the SH-4A processor. The other is the proactive migration of virtual core among physical cores to prevent the Linux kernel activity from blocking the interrupts assigned to the RTOS. The evaluation shows our methodologies can decrease the interrupt delay of the RTOS entailed by Linux. In addition, sharing a core between the RTOS and Linux will increase total processor utilization when executing some specific applications.

# 4.1 Background

Modern embedded systems like cell-phones and digital home appliances are rapidly expanding their functionality, getting competitive with desktop systems. However there are some embedded system specific requirements for real-time control processing, which is difficult to be supported by a GPOS.

Therefore, constructing an embedded device with a real-time and a GPOS has attracted attention as an approach to let embedded device balance real-time responsiveness and rich functionalities. There are various approaches to achieve this. One of the approaches is to use a multi-core SoC typically equipped with two processors, one for a RTOS and the other for a GPOS. Another approach is the hybrid system[66, 44, 59] which executes a general purpose OS as a task of a real-time OS.

In this chapter we focus on virtualization technologies, originally widely used in enterprise servers and desktop computers. Now, embedded systems are attracting attention as a new research field of virtualization technologies [31]. Embedded systems require different characteristics and gives some new challenges those have not been discussed on the previous application fields of virtualization technologies. According to the discussion in [14], the requirements to embedded system hardware virtualization are;

- minimal or no modification to OS kernels and their applications

- let OSes to reuse their native device drivers

- support real-time responsiveness in order to maintain the real-time property of RTOS

Hypervisors for enterprise servers and desktop systems, like VMware and Xen, do not fulfill these requirements. Especially the third requirement is difficult to be supported by functional hypervisors. Because virtual memory virtualization and I/O virtualization require complex manipulation of data structures inside hypervisors, they require to synchronize the data structures, and make the hypervisor complex. Therefore, we need to develop a virtualization layer specialized for embedded systems which is not based on the methodology of traditional pure-hypervisors that run in the most privileged level and isolate virtual machines.

We developed a virtualization layer on top of a real-world embedded device and evaluated its real-time responsiveness. There are three contributions introduced in this chapter.

- The first one is an OS consolidation methodology which fits the requirements of embedded systems. The evaluation shows that basic overhead and engineering required to the guest OSes are significantly small compared with related work.

- The second contribution of this chapter is an investigation on the real-time properties of virtualization technology on real-world devices.

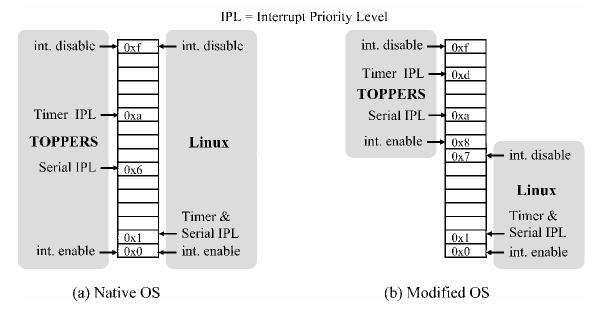

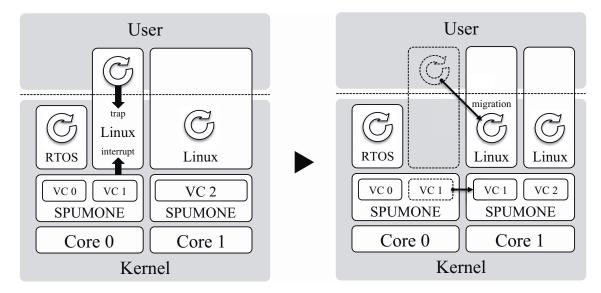

- The third contribution is our proposal of two methodologies for decreasing the overhead introduced to the RTOS. One is a methodology that leverages interrupt priority level (IPL) mechanism to enable RTOS to preempt GPOS's critical section. The other is to migrate virtual cores among physical cores, when they enter a critical section, in order to prevent GPOS kernel activities to block the execution of RTOS.

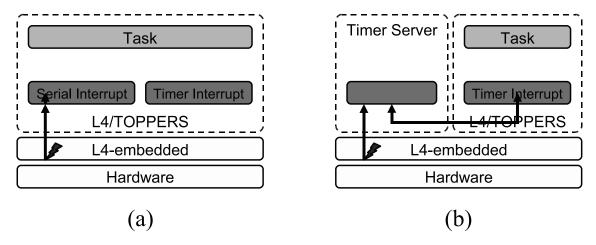

We developed a thin virtualization layer called SPUMONE which enables the coexecution of multiple OSes on single-core processor and multi-core processor equipped

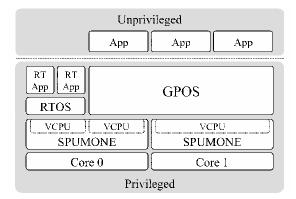

Figure 4.1: SPUMONE based system on a single-core processor

Figure 4.2: SPUMONE based system on a multi-core processor

with SH-4A architecture cores. SPUMONE can co-execute the TOPPERS RTOS<sup>1</sup> and Linux. The evaluation shows that our approach achieves sufficient real-time responsiveness for both methodologies. However, virtual core migration introduces a large overhead depending on the property of application executed on top of SMP Linux, which decreases the performance of GPOS applications.

# 4.2 Design and Implementation

This section introduces our methodology for accommodating multiple OSes on top of a single embedded device. The methodology is based on a thin virtualization layer called SPUMONE and some modifications to OS kernels.

#### 4.2.1 SPUMONE

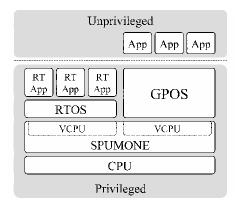

SPUMONE (Software Processing Unit, Multiplexing ONE into two or more) is a thin software layer for multiplexing a single physical processor into multiple virtual ones. In other words, SPUMONE provides a virtual multicore processor interface on top of a physical single-core processor. Unlike typical hypervisors or virtual machine monitors, SPUMONE itself and OS kernels are executed in privileged mode as shown in Fig.4.1, in order to simplify the system design and to eliminate the overhead of cross domain calls between user and kernel mode for system-calls and hypercalls. If an OS does not leverage privilege levels, its applications will be executed in kernel mode altogether.

Executing the virtualization layer and the kernels in the kernel mode contributes to minimize the overhead introduced to and the amount of modifications required to the OS kernels. Furthermore it makes the implementation of SPUMONE itself simple. Executing

<sup>&</sup>lt;sup>1</sup>TOPPERS is a RTOS which meets  $\mu$ ITRON RTOS specification widely used in Japanese industry http://www.ertl.jp/ITRON/

OS kernels in user mode is known to complicate the implementation of the abstraction layer, because various privileged instructions need to be emulated.

In SPUMONE based system, the majority of the kernel and application instructions, including the privileged instructions, are executed directly by the real processor, and only a minimal set of instructions are emulated by SPUMONE. These emulated instructions are invoked from the OS kernels using a simple function call. Since the interface has no binary compatibility with the original processor interface, we simply modify the source code of OS kernels, a method known as the para-virtualization Thus we assume we have access to the source code of the OS kernels. The modifications required to the OS kernels are described in details in Sec.4.2.2.

SPUMONE for multicore processors is designed in a distributed model: a dedicated instance of SPUMONE is assigned to each physical core as shown in Fig.4.2. This design is chosen in order to eliminate the unpredictable overhead of synchronization among multiple processor cores. In addition, the basic lock mechanism can be shared between single-core and multicore version, which may the simplify the design of SPUMONE. It also enables the system to scale on multicore and many-core processors as discussed in [18].

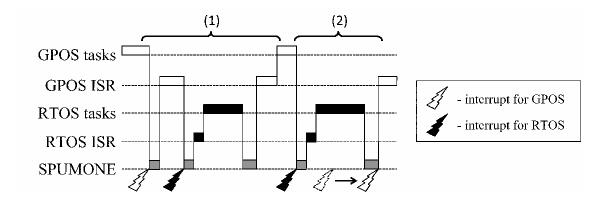

• Interrupt/Trap Delivery Interrupt virtualization is a key feature of SPUMONE. Interrupts are investigated by SPUMONE before they are delivered to each OS. SPUMONE receives an interrupt, then looks up the interrupt destination table to make a decision to which OS it should be sent. The destination virtual processor is statically defined for each interrupt when the kernels are built. Traps are also sent to SPUMONE first, then are directly forwarded to the currently executing OS.

To let SPUMONE receive interrupts before the OSes, we modified the interrupt entry point of the OS kernels to SPUMONE's vector table. The entry point of each OS is notified to SPUMONE via a virtual instruction for registering their vector table. An interrupt is first handled by SPUMONE's interrupt handler in which the destination virtual processor is decided and the corresponding scheduler is invoked. When the interrupt triggers an OS switch, all the registers of the current OS are saved into the register stack, then the register stack for the other OS is loaded. Finally the execution branches into the entry point of the destination OS. The processor registers are setup just as the real interrupt occurred, so the code of the OS entry points does not need to be modified.

The interrupt delivery process on multicore platform works basically as same as the one on single-core platform. Each SPUMONE instance delivers interrupts to their destinations. On multicore system, virtual cores may migrate among cores. In order to deliver interrupts to a virtual core running on a different core, the assignments of interrupts and physical cores are switched along with virtual core migrations.

• Virtual Processor Scheduling A processor is multiplexed by scheduling the exe-

cution of OSes. The execution states of the OSes are managed by a data structure that we call a virtual processor or a virtual core. When switching the execution of the virtual processors, all the hardware registers are stored into the corresponding virtual processor's register table, and then loaded from the table of the next executing virtual processor. The mechanism is similar to the process paradigm of a classical OS, however the virtual processor saves the entire processor state, including the privileged control registers.