Study on Multi-objective Optimization of Circuit Design by Evolutionary Computation Technologies

Bao, Zhiguo

April 2011

# Waseda University Doctoral Dissertation

# Study on Multi-objective Optimization of Circuit Design by Evolutionary Computation Technologies

## Bao, Zhiguo

Graduate School of Information, Production and Systems Waseda University

April 2011

#### Abstract

### Study on Multi-objective Optimization of Circuit Design by Evolutionary Computation Technologies

#### BAO, Zhiguo

Evolvable Hardware (EHW) has been researched for hardware design since early 1990s. It is classified into two categories: evolutionary circuit design and adaptive systems. Evolutionary circuit design uses evolutionary algorithms (EAs) to design a system that meets a predefined specification, and adaptive systems reconfigure an existing design to counteract faults or to adapt to a variable operational environment. EHW can be used as an alternative to conventional hardware design methodology. This research field has been actively studied by many researchers since Field Programmable Gate Array (FPGA) appeared as a hardware device. EHW techniques combined with FPGAs seems to be successful and promising in various applications, because it could automatically generate digital circuits by using EAs. EHW has been used to design digital circuits, such as a multiplier, a neural network, a robot controller, a traffic signal classifier, a digital image filter and so on. However, there still remain critical issues such as scalability, maintainability and generalization to apply EHW for practical design problems. One of them is a circuit optimization with mixed design constraints.

Therefore, in this research, the circuit design for mixed constraints is discussed, and a new design methodology using several evolutionary computation technologies is proposed. As a result, it is shown that our proposed design methodology can efficiently produce good circuits to meet the mixed design constraints.

The organization of the thesis is as follows:

In chapter 1, the evolutionary computation technologies are introduced, such as

Genetic algorithm (GA) or Particle Swarm Optimization (PSO). Evolutionary computation involves combinatorial optimization problems. GA is a search heuristic that mimics the process of natural evolution. This heuristic is routinely used to generate good solutions to optimization and search problems. PSO is a computational method that optimizes a problem by iteratively improving a candidate solution, and it is a method for performing numerical optimization without explicit knowledge of the gradient of the problem. EHW has an interesting application of evolutionary computation technologies. We focus on mixed constrained circuit design problems where evolutionary computation technologies are used to efficiently optimize circuit design and also to deal with the fault tolerance circuit design.

In chapter 2, GA is applied to gate level circuit design optimization. We propose optimal circuit design by using GA with parameterized uniform crossover (GApuc) and with fitness function composed of circuit complexity, power and signal delay. Parameterized uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space. It has higher exploratory power than one- and two-point crossover and we have more chances to find better solutions.

Its effectiveness is verified by experiments. From the results, we can see that the best elite fitness, the average value of fitness of the correct circuits and the number of the correct circuits of GApuc are better than that of GA with one- or two-point crossover. The best circuits generated by GApuc are 10.18% and 6.08% better in evaluating value compared with those by GA with one- and two-point crossover, respectively.

Chapter 3 proposes GA with different structure selection (GAdss) and its application to autonomous design optimization for combinatorial circuits.

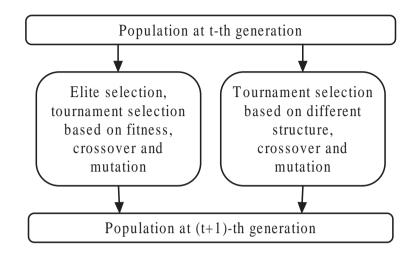

In traditional GA, the tournament selection for crossover and mutation is based

on fitness of individuals. It can make convergence easily, but maybe lose some useful genes. In selection, besides on fitness, we consider the different structure from individuals comparing to the elite one. First, some individuals are selected using more different structures, then crossover and mutation are performed for them to generate new individuals. By this way, GA can increase diversification to searching spaces, so that it can find better solution. By evolution, GAdss can find optimized circuits with less complexity, less power and less signal delay than traditional GA. From the results, we can see that the best elite fitness, the average value of fitness of correct circuits and the number of correct circuits of GAdss is 8.1% better in evaluating value than that by traditional GA.

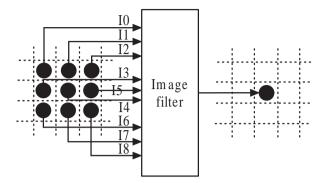

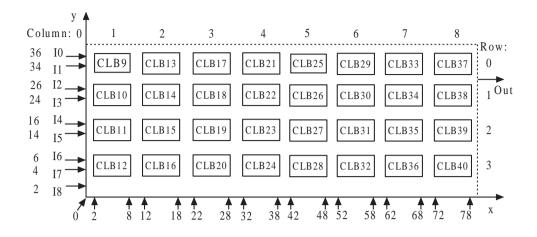

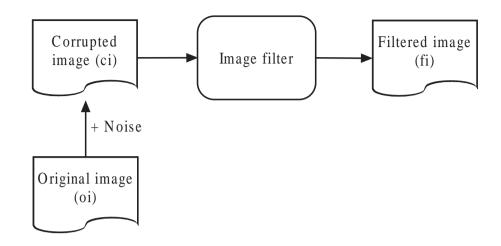

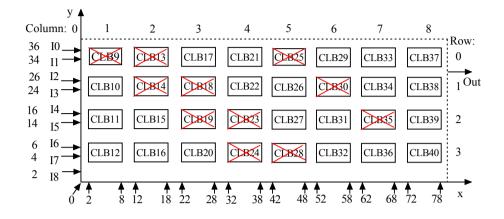

Chapter 4 describes mixed constrained image filter design for noise reduction using a GApuc (Genetic Algorithm with parameterized uniform crossover) on a reconfigurable processing array. The complexity, power and signal delay in Configurable Logic Blocks (CLBs) and wires are considered. An image filter for noise reduction is experimentally synthesized to verify the validity of the proposed method. By evolution, quality of the optimized image filter on reducing salt-and-pepper noise is better than that of other papers. Consequently it is shown that the proposed design method is effective in mixed constrained image filter design for salt-and-pepper noise reduction.

Chapter 5 proposes the use of PSO to design a mixed constrained image filter. In order to further reduce the processing time, PSO is used instead of GA. An image filter is experimentally synthesized using PSO to verify the effectiveness of our proposed method. By using evolution process, the quality of an optimized image filter by PSO is almost same as that of GA, but the running time by PSO is 10% shorter than that of GA.

Chapter 6 describes mixed constrained image filter design with fault tolerance for

noise reduction using GA on a reconfigurable processing array. Some CLBs (Configurable Logic Blocks) in a reconfigurable processing array are set fault at random. The proposed method with GA autonomously synthesizes a filter fitted to the reconfigurable device with some faults, evaluating the complexity, power and signal delay. An image filter for noise reduction is experimentally synthesized to verify our method. By evolution, the quality of an optimized image filter on a reconfigurable processing array with faults is almost same as that on a reconfigurable processing array with no fault. Consequently our proposed design method is also effective for fault-tolerant optimization.

Finally, chapter 7 concludes that the proposed method by GApuc can produce better circuits compared with other researches, and that PSO can get the almost same circuit in shorter processing time. Furthermore, the quality of an optimized image filter on a reconfigurable processing array with some faults is almost same as that on a reconfigurable processing array with no faults.

We will also apply evolutionary computation technologies to autonomous design circuits for more complex functional requirements, and enhance more practical information about circuit to fitness function. The future subject is to develop an adaptive system which can reconfigure an existing design by evolutionary computation technologies in order to meet a variable operational environment.

**Keywords**: Genetic Algorithm, Particle Swarm Optimization, Circuit optimization, Multi-objective optimization of circuit design, Image filter design for noise reduction, fault tolerance circuit design

# TABLE OF CONTENTS

|           |         |            |                                                                                                                                                      | Page |

|-----------|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| List of H | rigures |            |                                                                                                                                                      | iv   |

| List of 7 | Tables  |            |                                                                                                                                                      | vi   |

| Chapter   | 1: ]    | Introducti | on                                                                                                                                                   | 1    |

| 1.1       | Evolut  | cionary Co | omputation                                                                                                                                           | 1    |

|           | 1.1.1   | Evolution  | nary Algorithm                                                                                                                                       | 2    |

|           | 1.1.2   | Swarm I    | ntelligence                                                                                                                                          | 3    |

| 1.2       | Evolva  | ble Hardv  | ware                                                                                                                                                 | 3    |

| 1.3       | Mixed   | Constrain  | ned Circuit Design                                                                                                                                   | 5    |

| 1.4       | Thesis  | Organiza   | $tion \ldots \ldots$                               | 6    |

| Chapter   |         |            | l Circuit Design Optimization using Genetic Algorithm                                                                                                |      |

|           |         | with Para  | meterized Uniform Crossover                                                                                                                          | 9    |

| 2.1       | Introd  | uction     |                                                                                                                                                      | 9    |

| 2.2       | Gate I  | Level Circ | uit Design Optimization using GApuc                                                                                                                  | 11   |

|           | 2.2.1   | Objectiv   | e                                                                                                                                                    | 11   |

|           | 2.2.2   | Genetic I  | Encoding                                                                                                                                             | 12   |

|           | 2.2.3   | Fitness I  | Function $\ldots$                                                   | 14   |

|           | 2.2.4   | Tournam    | $ent Selection \ldots \ldots$ | 16   |

|           | 2.2.5   | Crossove   | r                                                                                                                                                    | 17   |

|           |         | 2.2.5.1    | One-point Crossover                                                                                                                                  | 17   |

|           |         | 2.2.5.2    | Two-point Crossover                                                                                                                                  | 18   |

|           |         | 2.2.5.3    | Parameterized Uniform Crossover                                                                                                                      | 18   |

|           |         | 2.2.5.4    | The range of probability in Parameterized Uniform<br>Crossover                                                                                       | 19   |

|           | 2.2.6   | Mutation   | 1                                                                                                                                                    | 19   |

|           |         |            |                                                                                                                                                      |      |

|         | 2.2.7  | Replacement                                                                                          | 20 |

|---------|--------|------------------------------------------------------------------------------------------------------|----|

|         | 2.2.8  | Evolutionary Process                                                                                 | 20 |

| 2.3     | Exper  | iments and Discussion                                                                                | 21 |

|         | 2.3.1  | Evaluation of GAs                                                                                    | 22 |

|         | 2.3.2  | Experimental Results                                                                                 | 23 |

|         | 2.3.3  | Discussion                                                                                           | 24 |

| 2.4     | Conclu | usion                                                                                                | 29 |

| Chapter |        | Gate Level Circuit Design Optimization using Genetic Algorithm<br>with Different Structure Selection | 33 |

| 3.1     | Introd | uction                                                                                               | 33 |

| 3.2     | Genet  | ic Algorithm with Different Structure Selection                                                      | 34 |

|         | 3.2.1  | Tournament selection                                                                                 | 35 |

|         | 3.2.2  | Crossover                                                                                            | 35 |

|         | 3.2.3  | Mutation                                                                                             | 36 |

| 3.3     | Gate I | Level Circuit Design Optimization using GAdss                                                        | 36 |

|         | 3.3.1  | Objective                                                                                            | 36 |

|         | 3.3.2  | Genetic Encoding                                                                                     | 37 |

| 3.4     | Exper  | iments and Results                                                                                   | 38 |

| 3.5     | Conclu | usion                                                                                                | 40 |

| Chapter |        | Mixed Constrained Image Filter Design for Noise Reduction us-<br>ing Genetic Algorithm               | 43 |

| 4.1     | Introd | uction                                                                                               | 43 |

| 4.2     | Image  | Filter Design for Noise Reduction using GA                                                           | 45 |

|         | 4.2.1  | Image Filter                                                                                         | 45 |

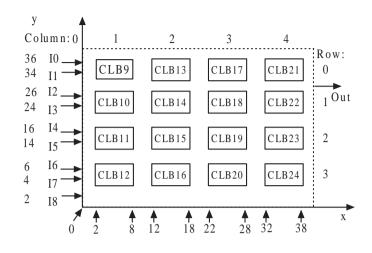

|         | 4.2.2  | Reconfigurable Processing Array for Image Filter                                                     | 45 |

|         | 4.2.3  | Genetic Encoding                                                                                     | 47 |

|         | 4.2.4  | Fitness Function                                                                                     | 48 |

| 4.3     | Exper  | imental Results                                                                                      | 51 |

|         | 4.3.1  | Experiments on salt-and-pepper noise                                                                 | 52 |

|         | 4.3.2  | Experiments on gaussian noise                                                                        | 57 |

| 4.4     | Conclu | usions                                                                                               | 58 |

| Chapter  | 5: Mixed Constrained Image Filter Design using Particle Swarm<br>Optimization |

|----------|-------------------------------------------------------------------------------|

| 5.1      | Introduction                                                                  |

| 5.2      | Particle Swarm Optimization                                                   |

| 5.3      | Image Filter Design using PSO                                                 |

|          | 5.3.1 Image Filter                                                            |

|          | 5.3.2 Reconfigurable Processing Array for Image Filter                        |

|          | 5.3.3 Genetic Encoding                                                        |

|          | 5.3.4 Fitness Function                                                        |

| 5.4      | Experimental Results                                                          |

| 5.5      | Conclusions                                                                   |

| Chapter  | 6: Fault-tolerant Image Filter Design using GA                                |

| 6.1      | Introduction                                                                  |

| 6.2      | Fault-tolerant Image Filter Design using GA                                   |

|          | 6.2.1 Image Filter                                                            |

|          | 6.2.2 Reconfigurable Processing Array for Image Filter                        |

|          | 6.2.3 Genetic Encoding                                                        |

|          | 6.2.4 Fitness Function                                                        |

| 6.3      | Experimental Results                                                          |

| 6.4      | Conclusions                                                                   |

| Chapter  | 7: Conclusions and Future work                                                |

| 7.1      | Conclusions                                                                   |

| 7.2      | Future work                                                                   |

| Acknow   | ledgements                                                                    |

| Bibliogr | aphy                                                                          |

| Publicat | ions                                                                          |

| Index    |                                                                               |

### LIST OF FIGURES

#### Figure Number Page EHW combines evolutionary techniques and a reconfigurable hardware. 4 1.1 1.25An example of mixed constrained circuit design optimization. 1.3An example of evolutionary circuit design. 6 2.1An initial 5\*5 array with the input/output function for a 2-bit full adder. 12 2.2172.3An example of Parameterized Uniform Crossover with a probability (Ppuc and (1 - Ppuc)).192.4An example of mutation. 202.5The process of our method. 212.622The evolutionary process of GA. 2.7Elite fitness of GA with different crossover vs the number of generations. 252.827The graphical representation of chromosome with fitness 670. . . . . 2.927The graphical representation of chromosome with fitness 692.... 2.10 The graphical representation of chromosome with fitness 716.... 282.11 The graphical representation of chromosome with fitness 722.... 282.12 The graphical representation of chromosome with fitness 728.... 292.13 The optimized circuit with fitness 670 after removing unnecessary gates. 30 2.14 The optimized circuit with fitness 692 after removing unnecessary gates. 30 2.15 The optimized circuit with fitness 716 after removing unnecessary gates. 30 2.16 The optimized circuit with fitness 722 after removing unnecessary gates. 32 2.17 The optimized circuit with fitness 728 after removing unnecessary gates. 32 3.1Reproduction of GA, left: traditional GA, right: GAdss. 34 . . . . . . . 3.2An initial $4^*4$ array with the input/output function for a 2-bit half adder. 36 3.3 The graphical representation of chromosome (501). 403.4The optimized circuit after removing unnecessary gates (501). 403.5The optimized circuit after removing unnecessary gates (471). . . . 41

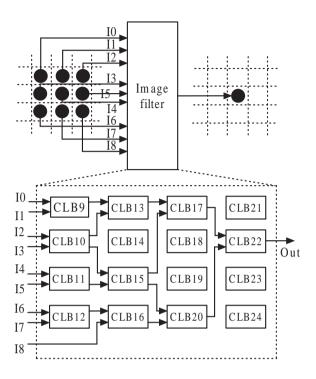

| 4.1 | An example image filter                                                       | 45 |

|-----|-------------------------------------------------------------------------------|----|

| 4.2 | A reconfigurable processing array                                             | 46 |

| 4.3 | The input and output of a image filter for noise reduction. $\ldots$ $\ldots$ | 48 |

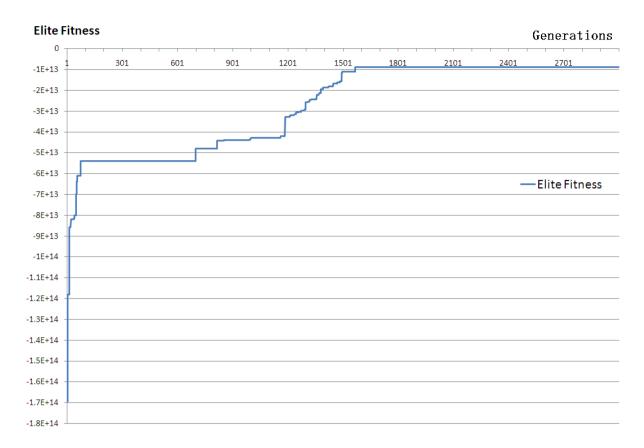

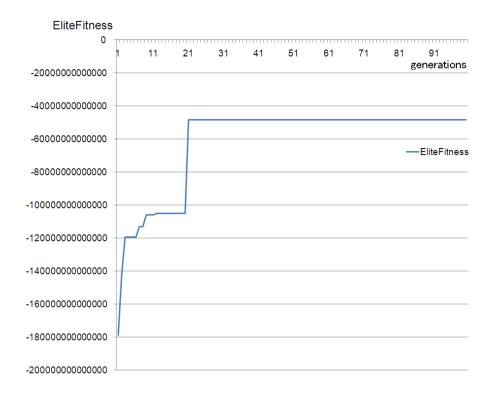

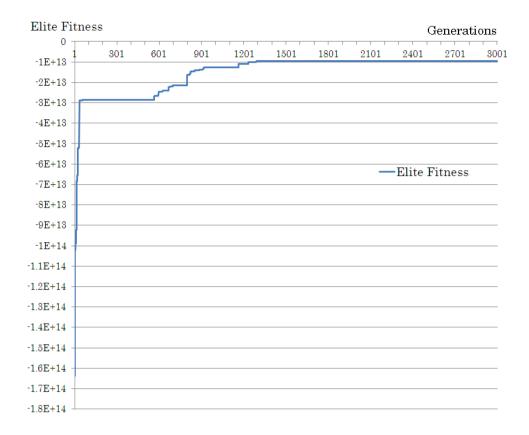

| 4.4 | Elite fitness of GA (Y-axis) vs. the number of generations (X-axis).          | 53 |

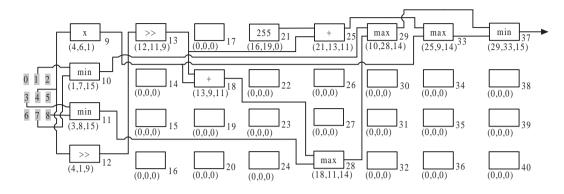

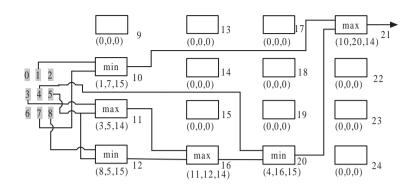

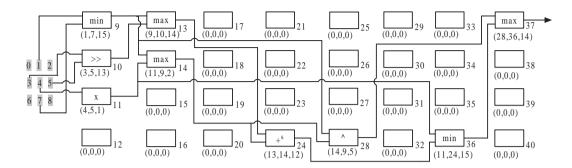

| 4.5 | The optimized image filter of the best one                                    | 57 |

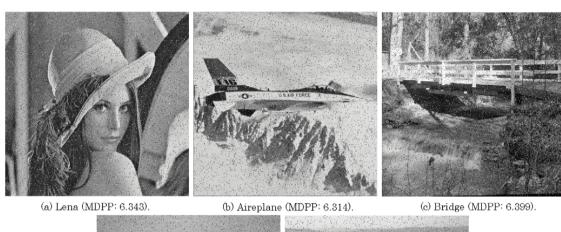

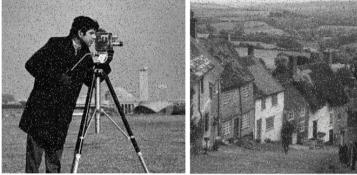

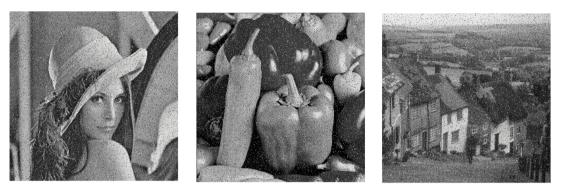

| 4.6 | The input images with noise                                                   | 60 |

| 4.7 | The output images by the evolved filter of Fig. 4.5                           | 60 |

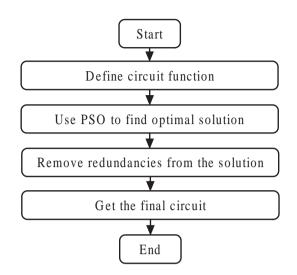

| 5.1 | The overview of our method                                                    | 62 |

| 5.2 | The evolutionary process of PSO                                               | 63 |

| 5.3 | An example image filter                                                       | 65 |

| 5.4 | A reconfigurable processing array                                             | 66 |

| 5.5 | Elite fitness of PSO (Y-axis) vs the number of generations (X-axis).          | 70 |

| 5.6 | The optimized image filter by PSO $(0.9)$                                     | 72 |

| 5.7 | The input images with noise                                                   | 73 |

| 5.8 | The output images by the evolved filter of Fig. 5.6                           | 73 |

| 6.1 | The overview of our method                                                    | 77 |

| 6.2 | A reconfigurable processing array with faults                                 | 78 |

| 6.3 | Elite fitness of GA (Y-axis) vs. the number of generations (X-axis).          | 83 |

| 6.4 | The optimized image filter of $Fault(2)$                                      | 85 |

| 6.5 | The input images with noise                                                   | 86 |

| 6.6 | The output images by the evolved filter of Fig. 6.4                           | 86 |

### LIST OF TABLES

| Table N | umber                                                                                                      | Page |

|---------|------------------------------------------------------------------------------------------------------------|------|

| 1.1     | Contents of following chapters                                                                             | 7    |

| 2.1     | The related researches                                                                                     | 10   |

| 2.2     | Information of gates.                                                                                      | 13   |

| 2.3     | A truth table of an adder with 5 inputs and 3 outputs                                                      | 15   |

| 2.4     | Conditions for evolution                                                                                   | 23   |

| 2.5     | Results of GA with different crossover                                                                     | 24   |

| 2.6     | The account of five elite fitness. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 31   |

| 3.1     | Conditions for evolution.                                                                                  | 38   |

| 3.2     | Results of different GA.                                                                                   | 39   |

| 4.1     | Features of related works.                                                                                 | 44   |

| 4.2     | Functions implements in a CLB                                                                              | 47   |

| 4.3     | An example of weight value setting                                                                         | 50   |

| 4.4     | Conditions for evolution                                                                                   | 52   |

| 4.5     | Results of GA with different crossover on salt-and-pepper noise                                            | 54   |

| 4.6     | Experiment environments                                                                                    | 55   |

| 4.7     | Test results (MDPP) between different papers                                                               | 56   |

| 4.8     | The best evolved image filter between different papers. $\hdots$                                           | 56   |

| 4.9     | Results of GA with different crossover on gaussian noise                                                   | 57   |

| 4.10    | Comparison of the noise reduction between different noise                                                  | 58   |

| 5.1     | Conditions for evolution                                                                                   | 69   |

| 5.2     | Fitness values of PSO with different $w$ , and GA                                                          | 71   |

| 6.1     | Features of related works.                                                                                 | 76   |

| 6.2     | Conditions for evolution                                                                                   | 82   |

| 6.3     | Results on a reconfigurable processing array with different faults. $\ . \ .$                              | 84   |

Chapter 1

### INTRODUCTION

#### 1.1 Evolutionary Computation

In computer science, evolutionary computation [1–3] is a subfield of artificial intelligence (more particularly computational intelligence) that involves combinatorial optimization problems.

The use of Darwinian principles for automated problem solving originated in the fifties. It was not until the sixties that three distinct interpretations of this idea started to be developed in three different places. Evolutionary programming (EP) was introduced by Lawrence J. Fogel in the USA, while John Henry Holland called his method a genetic algorithm (GA). In Germany, Ingo Rechenberg and Hans-Paul Schwefel introduced evolution strategies (ES). These areas developed separately for about 15 years. From the early nineties, they are unified as different representatives of one technology, called evolutionary computing. Also in the early nineties, a fourth stream following the general ideas had emerged - genetic programming (GP). These terminologies denote the field of evolutionary computing and consider evolutionary programming, evolution strategies, genetic algorithms, and genetic programming as sub-areas.

Evolutionary computation uses iterative progress, such as growth or development in a population. This population is then selected in a guided random search using parallel processing to achieve the desired end. Such processes are often inspired by biological mechanisms of evolution.

#### 1.1.1 Evolutionary Algorithm

In artificial intelligence, an evolutionary algorithm (EA) [4–6] is a subset of evolutionary computation, a generic population-based meta heuristic optimization algorithm. An EA uses some mechanisms inspired by biological evolution: reproduction, mutation, recombination, and selection. Candidate solutions to the optimization problem play the role of individuals in a population, and the fitness function determines the environment within which the solutions "live". Evolution of the population then takes place after the repeated application of the above operators.

EAs often perform well approximating solutions to all types of problems because they ideally do not make any assumption about the underlying fitness landscape; this generality is shown by successes in fields as diverse as engineering, art, biology, economics, marketing, genetics, operations research, robotics, social sciences, physics, politics and so on.

Genetic algorithm (GA) [7,8] is the most popular type of EA. The GA is a search heuristic that mimics the process of natural evolution. This heuristic is routinely used to generate useful solutions to optimization and search problems. GAs belong to the larger class of EA, which generate solutions to optimization problems using techniques inspired by natural evolution, such as inheritance, mutation, selection, and crossover.

In GA, a population of strings (called chromosomes or the genotype of the genome), which encode candidate solutions (called individuals, creatures, or phenotypes) to an optimization problem, evolves toward better solutions. Traditionally, solutions are represented in binary as strings of 0s and 1s, but other encodings are also possible. The evolution usually starts from a population of randomly generated individuals and happens in generations. In each generation, the fitness of every individual in the population is evaluated, multiple individuals are stochastically selected from the current population (based on their fitness), and modified (recombined and possibly randomly mutated) to form a new population. The new population is then used in the next iteration of the algorithm. Commonly, the algorithm terminates when either a maximum number of generations has been produced, or a satisfactory fitness level has been reached for the population. If the algorithm has terminated due to a maximum number of generations, a satisfactory solution may or may not have been reached.

#### 1.1.2 Swarm Intelligence

Swarm intelligence (SI) describes the collective behaviour of decentralized, self-organized systems, natural or artificial. The concept is employed in work on artificial intelligence. The expression was introduced by Gerardo Beni and Jing Wang in 1989, in the context of cellular robotic systems [9]. SI systems are typically made up of a population of simple agents interacting locally with one another and with their environment. The agents follow very simple rules, and although there is no centralized control structure dictating how individual agents should behave, local, and to a certain degree random, interactions between such agents lead to the emergence of "intelligent" global behavior, unknown to the individual agents.

Particle swarm optimization (PSO) [10–12] is a method for performing numerical optimization without explicit knowledge of the gradient of the problem to be optimized.

PSO optimizes a problem by maintaining a population of candidate solutions called particles and moving these particles around in the search-space according to simple formulae. The movements of the particles are guided by the best found positions in the search-space, which are continually updated as better positions are found by the particles.

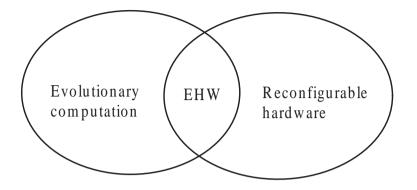

#### 1.2 Evolvable Hardware

Evolvable hardware (EHW) [13–19] is a new field about the use of EAs to create specialized electronics without manual engineering, as shown in Figure 1.1. It brings to-

Figure 1.1: EHW combines evolutionary techniques and a reconfigurable hardware.

gether reconfigurable hardware, artificial intelligence, fault tolerance and autonomous systems. EHW refers to hardware that can change its architecture and behavior dynamically and autonomously by interacting with its environment.

In its most fundamental form, an EA manipulates a population of individuals where each individual describes how to construct a candidate circuit. Each circuit is assigned a fitness, which indicates how well a candidate circuit satisfies the design specification. The EA uses stochastic operators to evolve new circuit configurations from existing ones. Done properly, over time the EA will evolve a circuit configuration that exhibits desirable behavior.

Each candidate circuit can be either simulated or physically implemented in a reconfigurable device. Typical reconfigurable devices are field-programmable gate arrays (FPGA, for digital designs) or field-programmable analog arrays (FPAA, for analog designs). At the lower level of abstraction, they are field-programmable transistor arrays (FPTA) that can implement either digital or analog designs.

The concept was pioneered by Adrian Thompson at the University of Sussex, England, who evolved a tone discriminator using fewer than 40 programmable logic gates and no clock signal in a FPGA in 1996. This is a remarkably small design for such a device and relied on exploiting peculiarities of the hardware that engineers normally avoid. For example, one group of gates has no logical connection to the rest

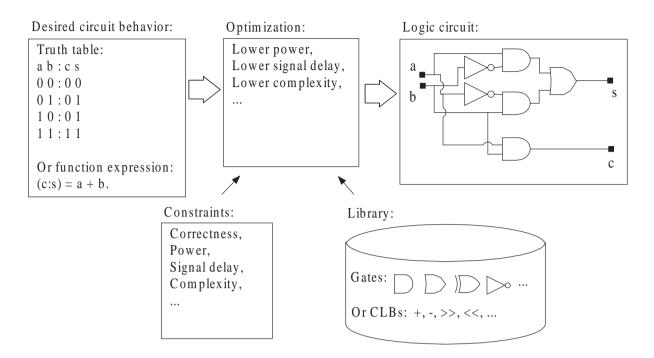

Figure 1.2: An example of mixed constrained circuit design optimization.

of the circuit, yet is crucial to its function.

EHW problems fall into two categories: original design and adaptive systems. Original design uses EAs to design a system that meets a predefined specification. Adaptive systems reconfigure an existing design to counteract faults or a changed operational environment.

#### 1.3 Mixed Constrained Circuit Design

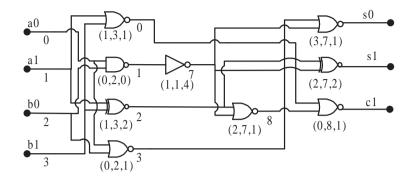

Circuit design flow in our proposed system is shown in Fig. 1.2, where an abstract form of desired circuit behavior (truth table or function expression) is finally turned into a design implementation in terms of logic gates or CLBs (Configurable Logic Blocks of FPGA). Circuit optimization is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints. Generally the circuit is constrained to correctness, less complexity, less power, and less signal delay. Integer string to appoint a circuit:

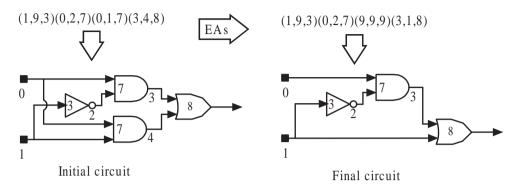

Figure 1.3: An example of evolutionary circuit design.

Thus, we need to consider the attribute of gates or CLBs, such as complexity, power, and signal delay. In mixed constrained circuit design optimization, it needs more processing time, when the number of gates or CLBs is larger.

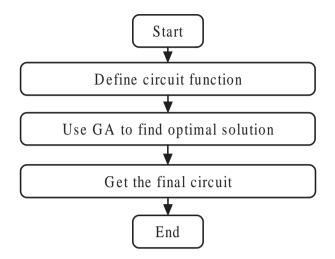

Evolutionary circuit design uses EAs to design a circuit that meets a predefined specification. First, an integer string is used to appoint a circuit. Then, the integer string is changed by EAs to get better circuit. In the end, a desired circuit can be created, as shown in Figure 1.3.

#### 1.4 Thesis Organization

The contents of following chapters are shown in Table 1.1.

In chapter 2, we propose a new method for circuit design optimization by GA, where mixed constraints on circuit complexity, power, and signal delay are considered. First, we introduce the evaluating value about correctness, complexity, power, and signal delay to the fitness function. Then GA can autonomously synthesize a circuit whose function is equivalent to a conventional design, but which is simpler and has better performance.

One-point crossover, two-point crossover, and parameterized uniform crossover

| Item      | Method | Level    | Circuit      | Optimization | Fault-tolerant |

|-----------|--------|----------|--------------|--------------|----------------|

| Chapter 2 | GA     | Gate     | Adder        | Yes          | No             |

| Chapter 3 | GAdss  | Gate     | Adder        | Yes          | No             |

| Chapter 4 | GA     | Function | Image filter | Yes          | No             |

| Chapter 5 | PSO    | Function | Image filter | Yes          | No             |

| Chapter 6 | GA     | Function | Image filter | Yes          | Yes            |

Table 1.1: Contents of following chapters.

[20] are typical crossover methods used in GA. Parameterized uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space, then it has more exploratory power than one and two-point crossover. Thus it enhances more diversification to searching spaces, then it has more chances of finding better solution. Therefore we use GA with parameterized uniform crossover, named GApuc.

In chapter 3, we propose a new approach for circuit design optimization by GA with Different Structure Selection (GAdss), where mixed constraints on circuit complexity, power and signal delay are considered. We introduce the evaluating value about correctness, complexity, power and signal delay for the fitness function in order to meed the mixed constraints. In the first step, the fitness function is used to find the solutions with 100% correctness of the target circuit, and with maximal evaluating values about complexity, power and signal delay. Then, GAdss can autonomously synthesize a circuit that is equivalent to a conventional design in functionality, but is simpler and has better performance. As a result, GAdss can find a better circuit, compared to traditional GA. To verify an effectiveness of our approach, a simple 2-bit half adder circuit is experimentally synthesized.

Chapter 4 describes mixed constrained image filter design for noise reduction using

a GA where parameterized uniform crossover is adopted on a reconfigurable processing array. The circuit complexity, power and signal delay in both logic blocks and wires are optimized. In this design, first, the evaluating values about correctness, complexity, power and signal delay are introduced to the fitness function. Then GA autonomously synthesizes an image filter which is simple and has better performance. To verify the validity of the proposed method, an image filter for noise reduction is experimentally synthesized.

Chapter 5 applies PSO to mixed constrained image filter design for noise reduction. The circuit complexity, power and signal delay which are caused by both logic gates and wires, are optimized. In this design, first, the evaluating value about correctness, complexity, power and signal delay are introduced to the fitness function. Then PSO autonomously synthesizes an image filter which is simpler and has better performance than the conventional design. To verify the validity of our method, an image filter for reducing noise is experimentally synthesized.

Chapter 6 describes mixed constrained image filter design with fault tolerant using GA on a reconfigurable processing array. There may be some faulty Configurable Logic Blocks (CLBs) in a reconfigurable processing array at random. The proposed method with GA autonomously synthesizes a filter fitted to the reconfigurable device with some faults, evaluating the complexity, power and signal delay in both CLBs and wires. An image filter for noise reduction is experimentally synthesized to verify the validity of our method. By evolution, the quality of the optimized image filter on a reconfigurable device with faults is almost same as that with no fault.

Finally, this paper concludes with a summary of the results in chapter 7.

#### Chapter 2

### GATE LEVEL CIRCUIT DESIGN OPTIMIZATION USING GENETIC ALGORITHM WITH PARAMETERIZED UNIFORM CROSSOVER

We propose optimal circuit design by using GA with parameterized uniform crossover (GApuc) and with fitness function composed of circuit complexity, power, and signal delay. Parameterized uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space, then it has more exploratory power than one and two-point crossover, so we have more chances of finding better solutions. Its effectiveness is verified by experiments. From the results, we can see that the best elite fitness, the average value of fitness of the correct circuits and the number of the correct circuits of GApuc are better than that of GA with one-point crossover or two-point crossover. The best case of optimal circuits generated by GApuc is 10.18% and 6.08% better in evaluating value than that by GA with one-point crossover and two-point crossover, respectively.

#### 2.1 Introduction

EAs is a generic population-based heuristic optimization algorithm. It uses some mechanisms inspired by biological evolution, such as selection, crossover, mutation, and replacement.

One of the interesting application of EAs, called EHW [13–19] has been researched for hardware design since early 1990s'. It is classified into two categories: evolutionary circuit design (or named "original design") and adaptive systems. Evolutionary circuit design uses EAs to design a system that meets a predefined specification, and

| Year | Author               | Level      | Circuit                     | Method | Fitness         | Experiment                 |

|------|----------------------|------------|-----------------------------|--------|-----------------|----------------------------|

| 1992 | J. R. Koza et al.    | Gate       | Boolean 11-multiplexer      | GP     | Correctness     | Software                   |

| 1994 | T. Higuchi et al.    | Gate       | Arbitration logical circuit | GA     | Correctness     | PLDs                       |

| 2000 | D. Keymeulen et al.  | Transistor | Fault-tolerant circuit      | GA     | Correctness     | FPTA                       |

|      |                      |            | (XNOR, multiplier)          |        |                 |                            |

| 2002 | J. F. Miller et al.  | Gate       | 4*4-Bit Multiplier          | GP     | Correctness     | Software                   |

| 2003 | K. A. Vinger et al.  | Function   | FIR-filter                  | GA     | Correctness     | Xilinx Virtex XCV1000 FPGA |

| 2004 | J. Torresen et al.   | Function   | Sign Number Recognition     | GA     | Correctness     | Software                   |

| 2004 | Y. Zhang et al.      | Function   | Image filter                | GP     | Correctness     | Xilinx Virtex XCV1000 FPGA |

| 2007 | E. Benkhelifa et al. | Gate       | 3-bit adder                 | GA     | Correctness and | Software                   |

|      |                      |            |                             |        | Number of gate  |                            |

| 2007 | L. Sekanina et al.   | Function   | Image filter                | GA     | Correctness     | Xilinx Virtex II Pro FPGA  |

Table 2.1: The related researches.

FIR-filter: Finite input response filter.

adaptive systems reconfigure an existing design to counteract faults or to adapt to a variable operational environment. EHW can be used as an alternative to conventional hardware design methodology. This field has been actively investigated by a number of researchers such as Higuchi [21], Julian Miller [22] and Adrian Thompson [23] since FPGA appeared first as a hardware device. The application of the EHW technique seems to be successful and promising, because it could automatically generate digital circuits by using EAs. EHW has been used to design digital filter [24], neural network chip [25], robot controller [26], multiplier [27], traffic signs classifier [28], digital image filter [29], polymorphic digital circuits [30] and so on. The related researches are listed in Table 2.1. However, there still remain critical issues such as scalability, maintainability and generalization [31–33] to apply EHW for practical design problems. One of them is a circuit optimization problem, where mixed design constraints are subjected.

In this chapter, we propose a new method for circuit design optimization by GA [7,8] which is one of typical EAs, where mixed constraints on circuit complexity, power, and signal delay are considered. First, we introduce the evaluating value about

correctness, complexity, power, and signal delay to the fitness function. Then GA can autonomously synthesize a circuit whose function is equivalent to a conventional design, but which is simpler and has better performance.

One-point, two-point crossover, and parameterized uniform crossover [20] are typical crossover methods used in GA. Parameterized uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space, then it has more exploratory power than one and two-point crossover. Thus it enhances more diversification to searching spaces, then we have more chances of finding better solution. Therefore we use GA with parameterized uniform crossover, named GApuc.

To verify the effectiveness of our method, a simple 2-bit full adder circuit is experimentally synthesized.

Section 2.2 describes the use of GApuc as a new method for the automatic design of an optimized circuit. Section 2.3 shows experiments on a 2-bit full adder circuit design as an example. Finally, this chapter concludes with a summary of the results in Sect. 2.4.

#### 2.2 Gate Level Circuit Design Optimization using GApuc

#### 2.2.1 Objective

The overall objective is to discover novel solutions by the application of GApuc in the circuit design optimization process. The target circuit has to provide identical functional behavior equivalent to the specification, but requires less complexity, less power, and less signal delay.

In this section, we will demonstrate the principle of GApuc in the circuit design process using a 2-bit full adder as a sample logic circuit.

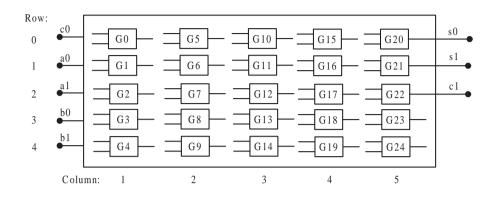

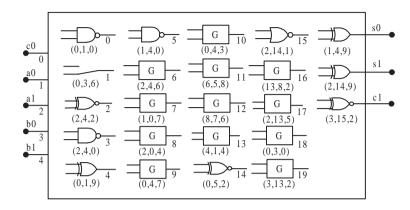

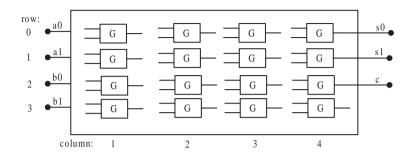

Figure 2.1: An initial 5\*5 array with the input/output function for a 2-bit full adder.

#### 2.2.2 Genetic Encoding

To process a genetic encoding easily, the logic circuit under consideration is assumed to be organized on a two dimensional array of gates, which was proposed in [19], shown in Fig. 2.1. Each gate accepts two inputs and produces one output according to its logical function. The gates in the first column of the array are set with predefined inputs. For the purpose of this experiment, the combinatorial circuit takes five primary inputs. Therefore there are 32 input patterns of the circuit. Gates in the following columns receive outputs from gates in the preceding columns.

The chromosome is a string of integers where each three continuous genes constitute a gate. Each triplet of the gate encodes the two inputs and the type of a gate, respectively, such as:

#### (Input\_1, Input\_2, Gate\_type).

In this experiment using a 2-bit full adder, the last two gates are not used, so the chromosome length is calculated by the following equation:

$$3 * ((number of columns) * (number of rows) - 2).$$

| GT | LF         | GC | EC | Power | EP | SD | ESD |

|----|------------|----|----|-------|----|----|-----|

| 0  | NAND       | 4  | 6  | 3     | 7  | 4  | 6   |

| 1  | NOR        | 4  | 6  | 3     | 7  | 4  | 6   |

| 2  | XNOR       | 8  | 2  | 4     | 6  | 6  | 4   |

| 3  | NOT(in1)   | 2  | 8  | 2     | 8  | 3  | 7   |

| 4  | NOT(in2)   | 2  | 8  | 2     | 8  | 3  | 7   |

| 5  | WIRE(in1)  | 0  | 10 | 6     | 4  | 8  | 2   |

| 6  | WIRE(in2)  | 0  | 10 | 6     | 4  | 8  | 2   |

| 7  | AND        | 6  | 4  | 5     | 5  | 7  | 3   |

| 8  | OR         | 6  | 4  | 5     | 5  | 7  | 3   |

| 9  | XOR        | 8  | 2  | 4     | 6  | 6  | 4   |

| -  | (not used) | 0  | 20 | 0     | 20 | 0  | 20  |

Table 2.2: Information of gates.

GT: gate type.

LF: logical function.

GC: gate complexity.

EC: evaluation of complexity.

EP: evaluation of power.

SD: signal delay.

ESD: evaluation of signal delay.

(2.1)

In the experiment, the array is a fixed size of 5\*5 gates (shown in Fig. 2.1), thus the length of the chromosome is 69 which is caused by (3 \* (5 \* 5 - 2)). The inputs of each gate in the first column of the array can take the value of any integer in the range of  $[0, (max\_number\_inputs - 1)]$ . On the other hand, gates on the other columns can take any integer value in the range of  $[0, ((now\_columns - 1) * (numberofrows) - 1)]$ . As for the third gene in the triplet, gate type is defined as shown in Table 2.2, which was proposed in [34, 35]. In order to judge the difference of the complexity, power, and signal delay between different gates, we assign values about complexity, power, and signal delay to each gate. In the evolution, the larger the fitness is, the better the circuit is. So we use evaluating values about complexity, power, and signal delay in fitness function. In Table 2.2, "GC" is the complexity about CMOS circuit of one gate, defined by the number of CMOS, "EC" equals to (10 - GC). "power" is the value about power of one gate, defined by the power of CMOS circuit, "EP" equals to (10 - power). "SD" is the value about signal delay of one gate, defined by the signal delay of CMOS circuit, and "ESD" equals to (10 - SD).

A typical chromosome then can be a sequence of triplets such as:

$$([0, X], [0, X], [0, 9])...([0, X], [0, X], [0, 9]).$$

Here, X means a range of a position of the corresponding signal. For primary input, X = 4. For input from output of a gate Gm shown in Fig. 2.1, X = m.

#### 2.2.3 Fitness Function

The fitness function in this experiment aims at accepting solutions with 100% correctness of the target circuit, and with maximal evaluating values about complexity, power, and signal delay. We use two functions  $F_1$  and  $F_2$ . The former is a ratio of correct outputs to all test data, and the latter is an evaluating function of circuit complexity, power, and signal delay. The following equations show how the fitness of individuals is calculated [34,35]:

$$F_1 = \frac{num\_rightout * 100}{num\_trainingdata}.$$

(2.2)

num\_rightout: the number of correct outputs generated from circuit individual.

|       | i     | nputs | 6     | output | s     |       |       |

|-------|-------|-------|-------|--------|-------|-------|-------|

| $a_1$ | $a_0$ | $b_1$ | $b_0$ | $c_0$  | $c_1$ | $s_1$ | $s_0$ |

| 0     | 0     | 0     | 0     | 0      | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 1      | 0     | 0     | 1     |

| 0     | 0     | 0     | 1     | 0      | 0     | 0     | 1     |

| 0     | 0     | 0     | 1     | 1      | 0     | 1     | 0     |

| 0     | 0     | 1     | 0     | 0      | 0     | 1     | 0     |

| 0     | 0     | 1     | 0     | 1      | 0     | 1     | 1     |

| 0     | 0     | 1     | 1     | 0      | 0     | 1     | 1     |

| 0     | 0     | 1     | 1     | 1      | 1     | 0     | 0     |

| 0     | 1     | 0     | 0     | 0      | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1      | 0     | 1     | 0     |

| 0     | 1     | 0     | 1     | 0      | 0     | 1     | 0     |

| 0     | 1     | 0     | 1     | 1      | 0     | 1     | 1     |

| 0     | 1     | 1     | 0     | 0      | 0     | 1     | 1     |

| 0     | 1     | 1     | 0     | 1      | 1     | 0     | 0     |

| 0     | 1     | 1     | 1     | 0      | 1     | 0     | 0     |

| 0     | 1     | 1     | 1     | 1      | 1     | 0     | 1     |

| 1     | 0     | 0     | 0     | 0      | 0     | 1     | 0     |

| 1     | 0     | 0     | 0     | 1      | 0     | 1     | 1     |

| 1     | 0     | 0     | 1     | 0      | 0     | 1     | 1     |

| 1     | 0     | 0     | 1     | 1      | 1     | 0     | 0     |

| 1     | 0     | 1     | 0     | 0      | 1     | 0     | 0     |

| 1     | 0     | 1     | 0     | 1      | 1     | 0     | 1     |

| 1     | 0     | 1     | 1     | 0      | 1     | 0     | 1     |

| 1     | 0     | 1     | 1     | 1      | 1     | 1     | 0     |

| 1     | 1     | 0     | 0     | 0      | 0     | 1     | 1     |

| 1     | 1     | 0     | 0     | 1      | 1     | 0     | 0     |

| 1     | 1     | 0     | 1     | 0      | 1     | 0     | 0     |

| 1     | 1     | 0     | 1     | 1      | 1     | 0     | 1     |

| 1     | 1     | 1     | 0     | 0      | 1     | 0     | 1     |

| 1     | 1     | 1     | 0     | 1      | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     | 0      | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     | 1      | 1     | 1     | 1     |

Table 2.3: A truth table of an adder with 5 inputs and 3 outputs.

*num\_trainingdata*: the number of all training data obtained from the truth table (Table 2.3) of a 2-bit full adder where inputs are  $a_1, a_0, b_1, b_0$  and  $c_0$ .

$$F_2 = \left(\sum_{i \in N} ecv_i\right) * \alpha_c + \left(\sum_{i \in N} epv_i\right) * \alpha_p + \left(\sum_{j \in Cols} \left(\min_{k \in Rows} edv_{jk}\right)\right) * \alpha_d.$$

(2.3)

$ecv_i$ : evaluation of complexity value of the gate i.

$epv_i$ : evaluation of power value of the gate i.

$edv_{j,k}$ : evaluation of signal delay value of the gate on column j and row k in an array.

$\alpha_c$ : the weight of complexity (set to 1 here).

$\alpha_p$ : the weight of power (set to 1 here).

$\alpha_d$ : the weight of signal delay (set to 1 here).

N: the number of gates in the array.

Cols: the number of columns in the array.

*Rows*: the number of rows in the array.

$$Fitness = \begin{cases} F_1, & when(F_1 < 100), \\ F_1 + F_2, & when(F_1 = 100). \end{cases}$$

(2.4)

The first part  $F_1$  of the fitness function compares the output response of the evolved circuit with the desired ones from a truth table (such as Table 2.3). If all matching, then the fitness value for the correctness is 100. The second fitness  $F_2$  searches for the most optimum solution in terms of complexity, power, and signal delay. This is done by designating gates with different evaluating values about complexity, power, and signal delay (shown in Table 2.2).

#### 2.2.4 Tournament Selection

Tournament selection runs a "tournament" among several individuals (such as two individuals in this research) chosen at randomly from the population and selects the winner which with better fitness value.

Figure 2.2: An example of crossover.

#### 2.2.5 Crossover

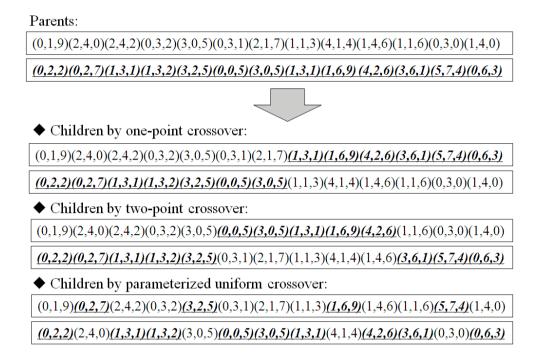

The crossover is operated between two parents, and two new individuals are generated. One-point crossover, two-point crossover, and parameterized uniform crossover are typical crossover methods, an example of these three types of crossover are shown in Fig. 2.2.

#### 2.2.5.1 One-point Crossover

A single crossover point on both parental chromosomes is selected randomly. All data beyond that point in either chromosome are swapped between the two parental chromosomes. The resulting chromosomes are the children.

#### 2.2.5.2 Two-point Crossover

Two-point crossover needs two points to be selected randomly on the parental chromosomes. Everything between the two points is swapped between the parental chromosomes, then generate two children chromosomes.

#### 2.2.5.3 Parameterized Uniform Crossover

The parameterized uniform crossover exchanges some gates with a probability of Ppuc (range: (0,0.5], see section 2.2.5.4). The procedure of the parameterized uniform crossover is given as follows.

- 1. Select two individuals as parents using tournament selection.

- 2. Some gates in the parents are selected as the crossover gates with a probability of *Ppuc*. We generate a random number Rn (range: [0,1]) at each gate, which will be selected if  $Rn \leq Ppuc$ .

- 3. Two parents exchange the crossover gates with each other.

- 4. The two new individuals become the individuals of the next generation.

In general, uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space. To see that this is true, consider the extreme case in which one parent is a string of all 0s and the other all 1s. Clearly uniform crossover can produce offspring anywhere in the space, while one and two-point crossovers are restricted to rather small subsets. Therefore, uniform crossover has the additional property that it has more exploratory power than that of one or two-point crossover.

The disruption potential is easily controlled via a single parameter Ppuc. This suggests the need for only one crossover form (parameterized uniform crossover), which is adapted to different situations by adjusting Ppuc.

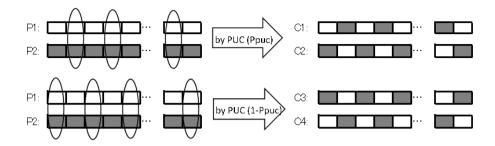

Figure 2.3: An example of Parameterized Uniform Crossover with a probability (*Ppuc* and (1 - Ppuc)).

# 2.2.5.4 The range of probability in Parameterized Uniform Crossover

For parameterized uniform crossover, the range of the probability (Ppuc) is from 0 to 0.5. Effect of *Ppuc* equals to that of (1 - Ppuc), for example, the effect of (*Ppuc* = 0.6 or 0.7) equals to that of (*Ppuc* = 0.4 or 0.3).

As shown in Fig. 2.3, P1 and P2 are two parental individuals, C1 and C2 are produced by parameterized uniform crossover (PUC) with a probability (*Ppuc*), C3 and C4 are produced by parameterized uniform crossover with a probability (1 – *Ppuc*).

$$\begin{split} C1 &= P1*(1-Ppuc) + P2*(Ppuc),\\ C2 &= P2*(1-Ppuc) + P1*(Ppuc),\\ C3 &= P1*(1-(1-Ppuc)) + P2*(1-Ppuc) = P1*(Ppuc) + P2*(1-Ppuc) = \\ P2*(1-Ppuc) + P1*(Ppuc),\\ C4 &= P2*(1-(1-Ppuc)) + P1*(1-Ppuc) = P2*(Ppuc) + P1*(1-Ppuc) = \\ P1*(1-Ppuc) + P2*(Ppuc),\\ \text{So, } C1 &= C4, C2 = C3. \end{split}$$

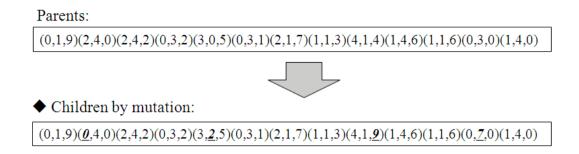

#### 2.2.6 Mutation

Mutation is executed on one parent so as to generate a new individual, as shown in Figure 2.4. The procedure of mutation is given as follows.

Figure 2.4: An example of mutation.

- 1. Select one individual as a parent using tournament selection.

- 2. Some genes are selected with a probability of Pm. We generate a random number Rn (range: [0,1]) at each gene, which will be selected if  $Rn \leq Pm$ . The selected genes are changed randomly and the new individual is generated.

- 3. The new individual becomes the individual of the next generation.

#### 2.2.7 Replacement

In the evolution of GA, for next generation, some elite individuals (Elite Size) are preserved, some new individuals (Crossover Size) are produced by crossover method, some new individuals (Mutation Size) are produced by mutation method. The population size is the sum of elite size, crossover size, and mutation size.

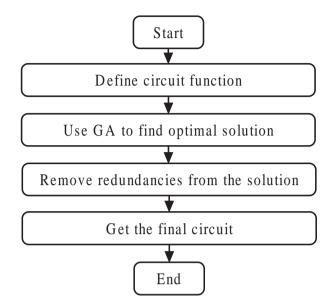

#### 2.2.8 Evolutionary Process

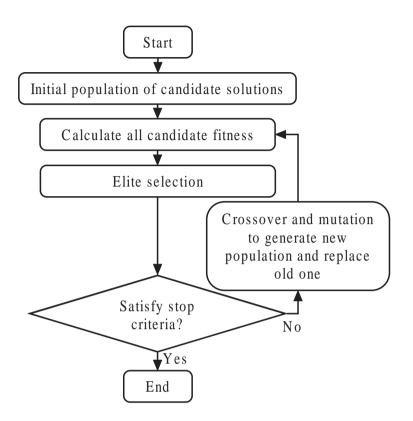

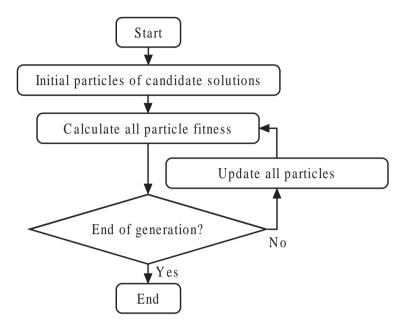

GA is a widely used search technique to find optimum or quasi optimum solutions for optimization or search problems. The overview of our GA method is shown in Fig. 2.5.

Figure 2.6 shows a graphical representation of the GA mechanisms. GA involves a search from a population of individuals. In the initialization of a GA population, each

Figure 2.5: The process of our method.

individual is randomly generated. In the evaluation, GA evaluates each candidate according to a fitness function, which indicates how well a candidate satisfies the design specification. In each generation, the elite individuals are preserved and the rest of the individuals are replaced by the new ones generated by crossover and mutation.

GA continues to evolve until it satisfies stop criteria (such as the maximum number of generations). With each generation involving in a competitive selection that rejects and discards poor solutions, based on the survival of the fittest paradigm, the elite fitness of the population is expected to increase in each generation. Therefore, a desired solution can be extracted from the population in the end. This process makes GA well suit combinatorial and continuous problems.

# 2.3 Experiments and Discussion

This experiment aims to verify circuit design optimization by GApuc. Table 2.4 shows the parameters of the evolution of GApuc. There is no fixed method to define the number of generations, population size, crossover probability and mutation proba-

Figure 2.6: The evolutionary process of GA.

bility. Therefor some preliminary experiments were performed in advance to decide parameters suitable for our experiment.

The proposed method has been implemented in Eclipse SDK 3.1.1 with jre 1.6.0; and tested on a PC with Inter(R) Core(TM)2 CPU at 2.67 GHz and 2.0 GB RAM.

# 2.3.1 Evaluation of GAs

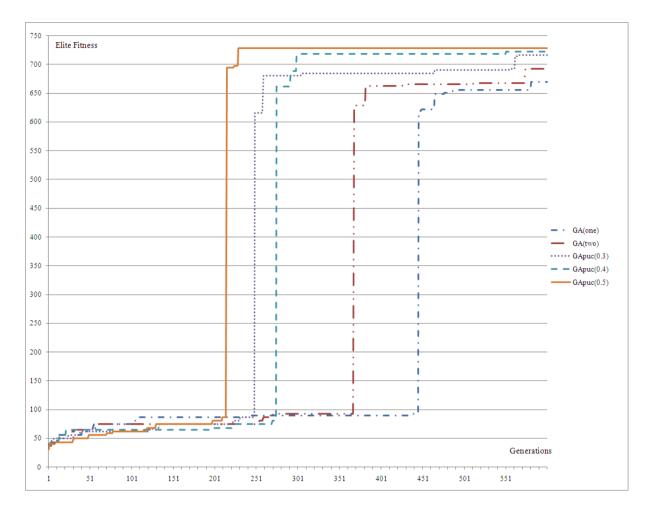

Figure 2.7 shows the elite fitness of GA vs the number of generations during the circuit evolution, where GA with one-point crossover, with two-point crossover, and with parameterized uniform crossover were experimented. From the results, we can see that the elite fitness jumps when  $F_1$  reaches 100, and it is increasing during the evolution period. When *Fitness* is less than 100, GA evolves to get correct circuit;

Table 2.4: Conditions for evolution.

| Number of Generation : 600                      |

|-------------------------------------------------|

| Population Size : 6010                          |

| Elite Size : 10                                 |

| Crossover Size : 3000                           |

| Mutation Size : 3000                            |

| Crossover Probability $(Pc)$ : 1                |

| Probability in $PUC$ ( $Ppuc$ ) : 0.3, 0.4, 0.5 |

| Mutation Probability $(Pm)$ : 0.015             |

PUC: Parameterized Uniform Crossover.

after *Fitness* reaches 100, GA evolves to get more optimized circuit.

#### 2.3.2 Experimental Results

Table 2.5 shows the results of GA with different crossover. For each GA, we select the successful results over 50 independent trials. In Table 2.5, "Best" means the best elite fitness value; "Quality1" the percent of better in evaluating value of best individual compared to that of GA with one-point crossover; "Quality2" the percent of better in evaluating value of best individual compared to that of GA with two-point crossover; "Average" the average fitness value of the top three individuals; "Var" the sample variance of elite fitness of correct individuals; "Quantity" the number of correct individuals over 50 independent trials; "Time" the average running time of one trial from 50 trials.

From the results, we can see that GApuc produces better solutions than GA with one-point crossover or two-point crossover, from the points of the best elite fitness, the average value of top three fitness and the number of correct circuits. Compared to

| Item     | GA(one) | GA(two) | GApuc(0.3) | GApuc(0.4) | GApuc(0.5) |

|----------|---------|---------|------------|------------|------------|

| Best     | 670     | 692     | 716        | 722        | 728        |

| Quality1 | -       | 3.86%   | 8.07%      | 9.12%      | 10.18%     |

| Quality2 | -       | -       | 4.05%      | 5.06%      | 6.08%      |

| Average  | 633.25  | 651.75  | 691.5      | 669.75     | 706.25     |

| Var      | 5678.80 | 1529.58 | 2210.53    | 2194.00    | 2096.13    |

| Quantity | 5       | 4       | 9          | 7          | 8          |

| Time(m)  | 5.16    | 5.22    | 5.2        | 5.24       | 5.26       |

Table 2.5: Results of GA with different crossover.

GA(one): GA with one-point crossover.

GA(two): GA with two-point crossover.

GApuc(0.3): GApuc with (Ppuc: 0.3).

GApuc(0.4): GApuc with (Ppuc: 0.4).

GApuc(0.5): GApuc with (Ppuc: 0.5).

one-point crossover and two-point crossover, the parameterized uniform crossover is much more likely to distribute its disruptive trials in an unbiased manner over larger portions of the space, thus it can find better solution.

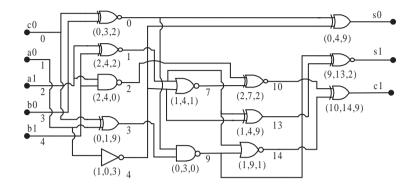

#### 2.3.3 Discussion

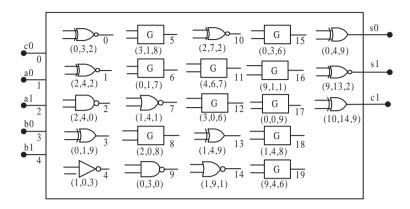

In the experiments, the optimized circuits were obtained. Some chromosomes are given as follows:

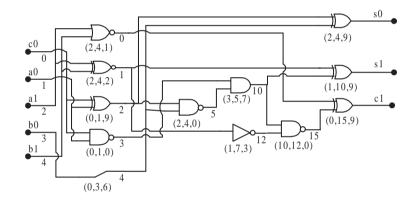

The chromosome with fitness 670, obtained by GA with one-point crossover:

(0,3,2)(2,4,2)(2,4,0)(0,1,9)(1,0,3)(3,1,8)(0,1,7)(1,4,1)(2,0,8)(0,3,0)(2,7,2)(4,6,7)(3,0,6)(1,4,9)(1,9,1)

Figure 2.7: Elite fitness of GA with different crossover vs the number of generations.

$$(0,3,6)(9,1,1)(0,0,9)(1,4,8)(9,4,6)$$

$(0,4,9)(9,13,2)(10,14,9).$

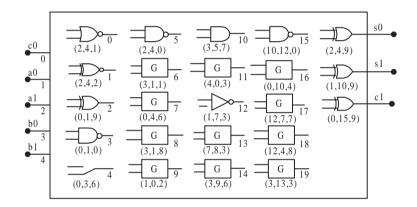

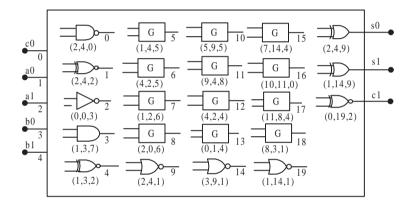

The chromosome with fitness 692, obtained by GA with two-point crossover:

$$\begin{aligned} &(2,4,1)(2,4,2)(0,1,9)(0,1,0)(0,3,6)\\ &(2,4,0)(3,1,1)(0,4,6)(3,1,8)(1,0,2)\\ &(3,5,7)(4,0,3)(1,7,3)(7,8,3)(3,9,6)\end{aligned}$$

$$(10, 12, 0)(0, 10, 4)(12, 7, 7)(12, 4, 8)(3, 13, 3)$$

$(2, 4, 9)(1, 10, 9)(0, 15, 9).$

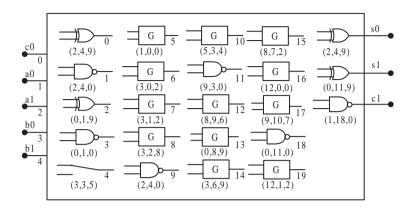

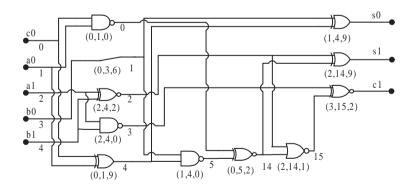

The chromosome with fitness 716, obtained by GApuc with (Ppuc: 0.3):

$$\begin{array}{l} (0,1,0)(0,3,6)(2,4,2)(2,4,0)(0,1,9)\\ (1,4,0)(2,4,6)(1,0,7)(2,0,4)(0,4,7)\\ (0,4,3)(6,5,8)(8,7,6)(4,1,4)(0,5,2)\\ (2,14,1)(13,8,2)(2,13,5)(0,3,0)(3,13,2)\\ (1,4,9)(2,14,9)(3,15,2). \end{array}$$

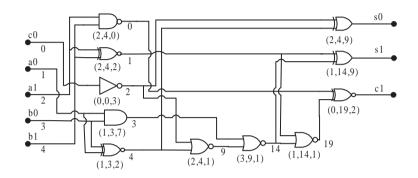

The chromosome with fitness 722, obtained by GApuc with (Ppuc: 0.4):

$$\begin{split} &(2,4,0)(2,4,2)(0,0,3)(1,3,7)(1,3,2)\\ &(1,4,5)(4,2,5)(1,2,6)(2,0,6)(2,4,1)\\ &(5,9,5)(9,4,8)(4,2,4)(0,1,4)(3,9,1)\\ &(7,14,4)(10,11,0)(11,8,4)(8,3,1)(1,14,1)\\ &(2,4,9)(1,14,9)(0,19,2). \end{split}$$

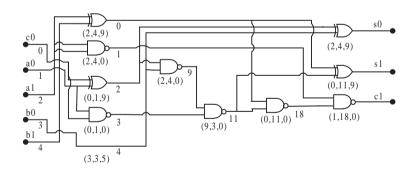

The chromosome with fitness 728, obtained by GApuc with (Ppuc: 0.5):

$\begin{array}{l}(2,4,9)(2,4,0)(0,1,9)(0,1,0)(3,3,5)\\(1,0,0)(3,0,2)(3,1,2)(3,2,8)(2,4,0)\\(5,3,4)(9,3,0)(8,9,6)(0,8,9)(3,6,9)\\(8,7,2)(12,0,0)(9,10,7)(0,11,0)(12,1,2)\\(2,4,9)(0,11,9)(1,18,0).\end{array}$

Figure 2.8: The graphical representation of chromosome with fitness 670.

Figure 2.9: The graphical representation of chromosome with fitness 692.

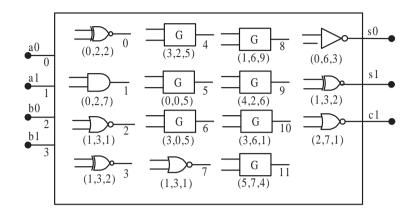

The graphical representation of these chromosomes are shown in Figures 2.8, 2.9, 2.10, 2.11 and 2.12, respectively. In these figures, the gates used in the final circuit are shown by logic gates symbols.

In the Table 2.6, we show the evaluating values about complexity, power, and signal delay of each gate in five experimented circuits. Then, calculate the sum of the evaluating values about complexity and power, and also calculate the min of the evaluating values about signal delay of each column. From this table, we can see how to calculate the fitness function of  $F_2$  and *Fitness*.

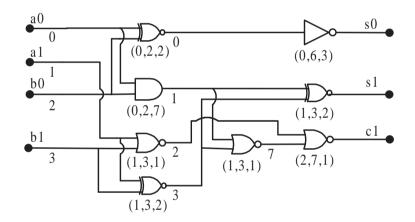

Figures 2.13, 2.14, 2.15, 2.16 and 2.17 show the optimized circuits with fitness

Figure 2.10: The graphical representation of chromosome with fitness 716.

Figure 2.11: The graphical representation of chromosome with fitness 722.

670, 692, 716, 722 and 728, respectively, after removing unnecessary gates.

The circuits in Figures 2.15, 2.16 and 2.17 are superior to the circuits in Figures 2.13 and 2.14 in quality, because the former has larger fitness and is composed of less gates, this leads a circuit with less complexity, less power, and less signal delay.

The circuit in Fig. 2.16 has one more gates than the circuit in Fig. 2.15. But the gates in Fig. 2.16 has less complexity, such as 'NOT' in  $col_1$  and 'NOR' in  $col_3$ . From Table 2.6, we can see the value of  $F_2$  of the circuit in Fig. 2.16 is lager than that of the circuit in Fig. 2.15. So the circuit in Fig. 2.16 has less complexity, less power, and less signal delay than the circuit in Fig. 2.15.

Figure 2.12: The graphical representation of chromosome with fitness 728.

#### 2.4 Conclusion

This chapter applied GA to circuit design optimization. First, we introduce the evaluating value about correctness, complexity, power, and signal delay to the fitness function. Then GA can autonomously synthesize a circuit that is equivalent to a conventional design in function, but is simpler and has better performance. By evolution, GApuc can find optimized circuits with less complexity, less power, and less signal delay than GA with one-point crossover or two-point crossover.

However, the number of correct individuals is low, and the running time is long, which points out the future research direction. Also, there are other crossover methods, such as arithmetic crossover [36] and heuristic crossover [37]. We will compare parameterized uniform crossover with other crossover methods in the problem of circuit design optimization, to search a better crossover method.

We will also apply GA to autonomous design circuits for more complex functional requirements, and enhance more practical information about circuit to fitness function. In the future, we will develop the adaptive systems which reconfigure an existing design by GA to adapt to a variable operational environment.

Figure 2.13: The optimized circuit with fitness 670 after removing unnecessary gates.

Figure 2.14: The optimized circuit with fitness 692 after removing unnecessary gates.

Figure 2.15: The optimized circuit with fitness 716 after removing unnecessary gates.

| item                                    |    | $col_1$ |     |    | $col_2$ |     |    | $col_3$ |     |     | $col_4$ |     | col <sub>5</sub> |    |     | $F_2/F$ |

|-----------------------------------------|----|---------|-----|----|---------|-----|----|---------|-----|-----|---------|-----|------------------|----|-----|---------|

| values                                  | EC | EP      | ESD | EC | EP      | ESD | EC | EP      | ESD | EC  | EP      | ESD | EC               | EP | ESD | -       |

| row0                                    | 2  | 6       | 4   | 20 | 20      | 20  | 2  | 6       | 4   | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row1                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row2                                    | 6  | 7       | 6   | 6  | 7       | 6   | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row3                                    | 2  | 6       | 4   | 20 | 20      | 20  | 2  | 6       | 4   | 20  | 20      | 20  | -                | -  | -   | -       |

| row4                                    | 8  | 8       | 7   | 6  | 7       | 6   | 6  | 7       | 6   | 20  | 20      | 20  | -                | -  | -   | -       |

| $\operatorname{sum}/\operatorname{min}$ | 20 | 33      | 4   | 72 | 74      | 6   | 50 | 59      | 4   | 100 | 100     | 20  | 6                | 18 | 4   | 570/670 |

| row0                                    | 6  | 7       | 6   | 6  | 7       | 6   | 4  | 5       | 3   | 6   | 7       | 6   | 2                | 6  | 4   | -       |

| row1                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row2                                    | 2  | 6       | 4   | 20 | 20      | 20  | 8  | 8       | 7   | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row3                                    | 6  | 7       | 6   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | -                | -  | -   | -       |

| row4                                    | 10 | 4       | 2   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | -                | -  | -   | -       |

| $\operatorname{sum}/\operatorname{min}$ | 26 | 30      | 2   | 86 | 87      | 6   | 72 | 73      | 3   | 86  | 87      | 6   | 6                | 18 | 4   | 592/692 |

| row0                                    | 6  | 7       | 6   | 6  | 7       | 6   | 20 | 20      | 20  | 6   | 7       | 6   | 2                | 6  | 4   | -       |

| row1                                    | 10 | 4       | 2   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row2                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row3                                    | 6  | 7       | 6   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | -                | -  | -   | -       |

| row4                                    | 2  | 6       | 4   | 20 | 20      | 20  | 2  | 6       | 4   | 20  | 20      | 20  | -                | -  | -   | -       |

| $\operatorname{sum}/\operatorname{min}$ | 26 | 30      | 2   | 86 | 87      | 6   | 82 | 86      | 4   | 86  | 87      | 6   | 6                | 18 | 4   | 616/716 |

| row0                                    | 6  | 7       | 6   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row1                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row2                                    | 8  | 8       | 7   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row3                                    | 4  | 5       | 3   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | -                | -  | -   | -       |

| row4                                    | 2  | 6       | 4   | 6  | 7       | 6   | 6  | 7       | 6   | 6   | 7       | 6   | -                | -  | -   | -       |

| $\operatorname{sum}/\operatorname{min}$ | 22 | 32      | 3   | 86 | 87      | 6   | 86 | 87      | 6   | 86  | 87      | 6   | 6                | 18 | 4   | 622/722 |

| row0                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row1                                    | 6  | 7       | 6   | 20 | 20      | 20  | 6  | 7       | 6   | 20  | 20      | 20  | 2                | 6  | 4   | -       |

| row2                                    | 2  | 6       | 4   | 20 | 20      | 20  | 20 | 20      | 20  | 20  | 20      | 20  | 6                | 7  | 6   | -       |

| row3                                    | 6  | 7       | 6   | 20 | 20      | 20  | 20 | 20      | 20  | 6   | 7       | 6   | -                | -  | -   | -       |

| row4                                    | 10 | 4       | 2   | 6  | 7       | 6   | 20 | 20      | 20  | 20  | 20      | 20  | -                | -  | -   | -       |

| $\operatorname{sum}/\operatorname{min}$ | 26 | 30      | 2   | 86 | 87      | 6   | 86 | 87      | 6   | 86  | 87      | 6   | 10               | 19 | 4   | 628/728 |

Table 2.6: The account of five elite fitness.

F: Fitness.

$EC\!\!:$  evaluation of complexity.

EP: evaluation of power.

ESD: evaluation of signal delay.

Figure 2.16: The optimized circuit with fitness 722 after removing unnecessary gates.

Figure 2.17: The optimized circuit with fitness 728 after removing unnecessary gates.

# Chapter 3

# GATE LEVEL CIRCUIT DESIGN OPTIMIZATION USING GENETIC ALGORITHM WITH DIFFERENT STRUCTURE SELECTION

In traditional GA, the tournament selection for crossover and mutation is based on fitness of individuals. It can make convergence easily, but maybe lose some useful genes. In selection, besides fitness, we consider the different structure from individuals comparing to the elite one. First, some individuals are selected using more different structures, then crossover and mutation are performed for these ones to generate new individuals. By this way, GA can increase diversification to searching spaces, so that it can find better solution. One of the promising application of GA is EHW, which is a new research field to synthesize an optimal circuit. We propose optimal circuit design by using GA with different structure selection (GAdss) and with fitness function composed of circuit complexity, power and signal delay. Its effectiveness is verified by simulations. From the results, we can see that the best elite fitness, the average value of fitness of correct circuits and the number of correct circuits of GAdss are better than traditional GA. The best case of optimal circuits generated by GAdss is 8.1% better in evaluating value than that by traditional GA.

#### 3.1 Introduction

In this chapter, we propose a new approach for circuit design optimization by GA with Different Structure Selection (GAdss), where mixed constraints on circuit complexity, power and signal delay are considered. We introduce the evaluating value about correctness, complexity, power and signal delay for the fitness function in order to

Figure 3.1: Reproduction of GA, left: traditional GA, right: GAdss.

meed the mixed constrains. In the first step, the fitness function is used to find the solutions with 100% correctness of the target circuit, and with maximal evaluating values about complexity, power and signal delay. Then, GAdss can autonomously synthesize a circuit that is equivalent to a conventional design in functionality, but is simpler and has better performance. As a result, GAdss can find a better circuit, compared to traditional GA. To verify an effectiveness of our approach, a simple 2-bit half adder circuit is experimentally synthesized.

In the next section, a brief overview of GAdss is described. Section 3.3 describes the use of GAdss as a new approach for the automatic design of an optimized circuit. Section 3.4 shows experiments on a 2-bit half adder circuit design as an example. Finally, the chapter concludes with a summary of the results in section 3.5.

#### 3.2 Genetic Algorithm with Different Structure Selection

In traditional GA, elite selection and tournament selection are based on the fitness of individuals. This is good for GA to find the local best solution, but it may be premature convergence. To make up for the weakness, we consider the different structure of individuals compared to the elite one. The value of different structure is defined by the sum of difference of genes between two individuals. We select some individuals with different structure to do crossover and mutation, to generate some new individuals to the next populations. This method can extend diversification to search spaces, so can find a better solution.

Figure 3.1 shows a graphical representation of the reproduction of GAdss. In each generation, the elite individuals are preserved. In selecting some individuals, half of them are processed by tournament selection based on fitness, and another half are processed by tournament selection based on different structure. Then crossover and mutation are performed to create new ones for next generation.

#### 3.2.1 Tournament selection