Study on Wideband Voltage Controlled Oscillator and High Efficiency Power Amplifier ICs for Wireless Communications

## LIU,Qing

${\bf Graduate~School~of~Information,~Production~and~Systems}$   ${\bf Waseda~University}$

February 2012

# Contents

|   | $\operatorname{Titl}$ | e Page                                                         | i    |

|---|-----------------------|----------------------------------------------------------------|------|

|   | Tab                   | le of Contents                                                 | ii   |

|   | Abs                   | tract                                                          | iv   |

|   | Ack                   | nowledgments                                                   | vi   |

|   | Ded                   | ication                                                        | viii |

| 1 | Intr                  | roduction                                                      | 1    |

|   | 1.1                   | Background                                                     | 1    |

|   | 1.2                   | Motivation and Research Objective                              | 5    |

|   | 1.3                   | Contribution of the Thesis and Its Structure                   | 8    |

| 2 | Nov                   | vel Wideband LC VCO IC                                         | 12   |

|   | 2.1                   | Overview                                                       | 12   |

|   | 2.2                   | Wideband LC VCO Design                                         | 13   |

|   |                       | 2.2.1 Transformer-based Switched Variable Inductors Design     | 14   |

|   |                       | 2.2.2 Switched AMOS Varactors Design                           | 24   |

|   |                       | 2.2.3 Cross-coupled PMOS Design                                | 30   |

|   |                       | 2.2.4 VCO Circuit Design                                       | 32   |

|   | 2.3                   |                                                                | 41   |

|   | 2.4                   | Summary                                                        | 44   |

| 3 | Hig                   | h Linearity and High Efficiency PA IC                          | 45   |

|   | 3.1                   | Overview                                                       | 45   |

|   | 3.2                   | Multicascode PA Design                                         | 47   |

|   |                       | 3.2.1 Transconductance Nonlinearity in Conventional Cascode PA | 47   |

|   |                       | 3.2.2 Principle Analysis of the Proposed Technique             | 51   |

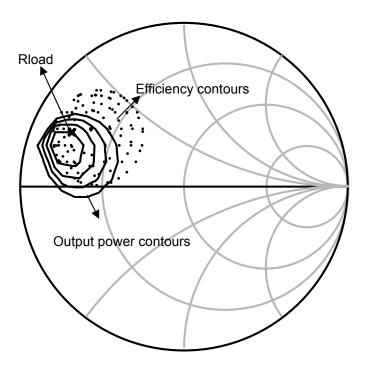

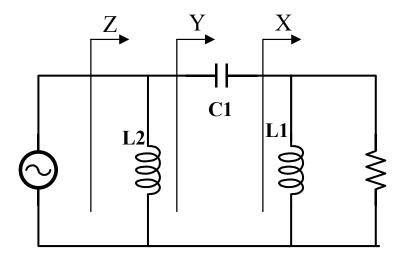

|   |                       | 3.2.3 Matching Network Design                                  | 55   |

|   |                       | 3.2.4 Stability Design                                         | 60   |

|   | 3.3                   | Overall Simulation Results                                     | 61   |

|   | 3.4                   | PA Layout                                                      | 70   |

|   | 3.5                   | Experiment Results                                             | 73   |

|   | 3.6                   | Summary                                                        | 77   |

Contents

| 4                                          | CM                                    | IOS Class-G Supply Modulation for Polar PAs with High Average   | )   |  |  |  |

|--------------------------------------------|---------------------------------------|-----------------------------------------------------------------|-----|--|--|--|

| Efficiency and Low Ripple Noise            |                                       |                                                                 |     |  |  |  |

| 4.1 Overview                               |                                       |                                                                 | 79  |  |  |  |

| 4.2 The Proposed Class-G Supply Modulation |                                       |                                                                 | 81  |  |  |  |

|                                            |                                       | 4.2.1 The Originality of the Proposed Class-G Supply Modulation | 81  |  |  |  |

|                                            |                                       | 4.2.2 The Principle Analysis                                    | 83  |  |  |  |

|                                            |                                       | 4.2.3 The Efficiency Analysis                                   | 85  |  |  |  |

| 4.3 Circuit Implementation                 |                                       | 87                                                              |     |  |  |  |

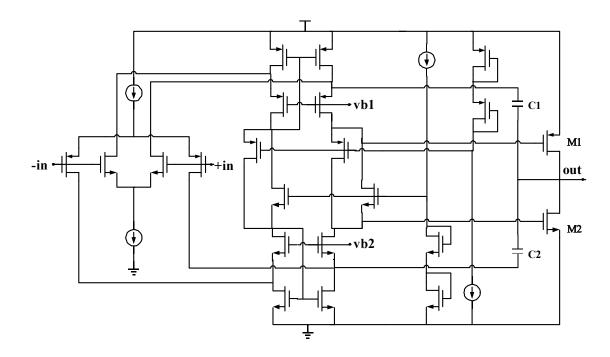

|                                            |                                       | 4.3.1 Two-Stage Class-AB Amplifier                              | 87  |  |  |  |

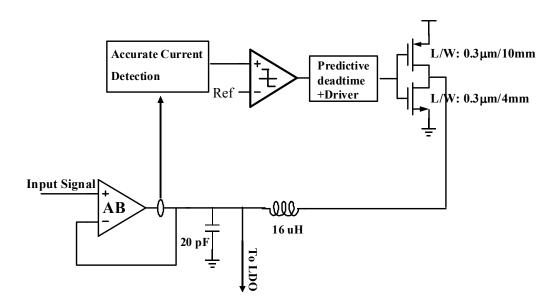

|                                            |                                       | 4.3.2 RWDM Switch-Mode Regulator                                | 88  |  |  |  |

|                                            |                                       | 4.3.3 Accurate Current Detection Circuit                        | 90  |  |  |  |

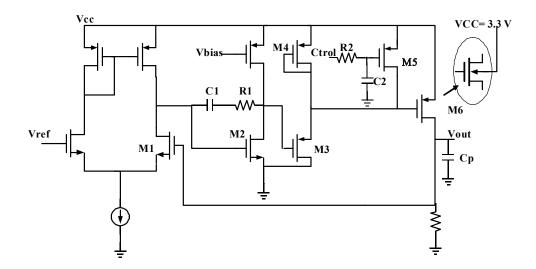

|                                            |                                       | 4.3.4 LDO Circuit Implementation                                | 93  |  |  |  |

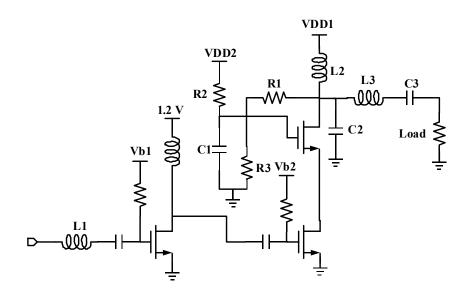

|                                            |                                       | 4.3.5 Class-E PA Design                                         | 95  |  |  |  |

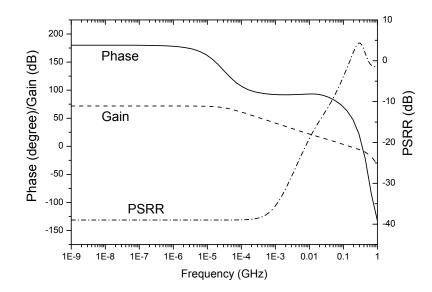

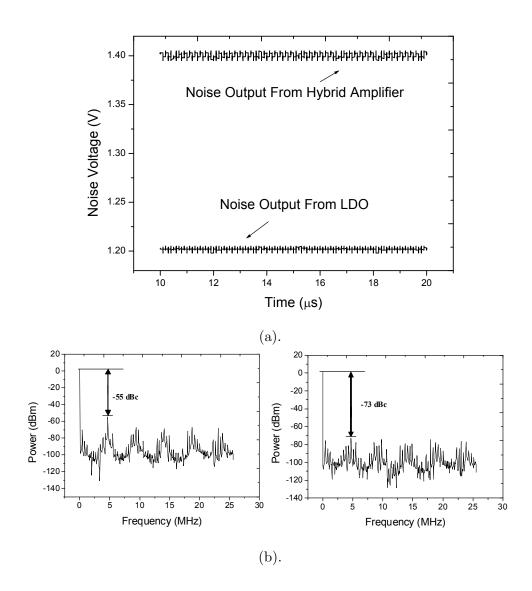

|                                            | 4.4 Simulation Results and Discussion |                                                                 | 96  |  |  |  |

|                                            | 4.5                                   | Summary                                                         | 103 |  |  |  |

| 5                                          | Conclusions and Future Work           |                                                                 |     |  |  |  |

|                                            | 5.1                                   | Conclusions                                                     | 105 |  |  |  |

|                                            | 5.2                                   | Future Work                                                     | 106 |  |  |  |

| Bi                                         | bliog                                 | graphy                                                          | 108 |  |  |  |

| T.i                                        | List of Publications                  |                                                                 |     |  |  |  |

### Abstract

As the growth in the wireless communication systems, the need of the high speed, high transmission data rate becomes critical issue to satisfy the wireless communication application for daily life. And the necessary of high integration of the baseband circuit and radio frequency analog transceiver in one chip makes the CMOS the most important process for Integrated Circuit (IC) design. However, it is a challenge work to design a high quality high speed Radio Frequency Integrated Circuit (RFIC) by CMOS process because of its low quality factor on-chip inductor, large parasitic capacitance and large substrate noise. Recent years, many researches were carried out and many techniques were reported to deal with these defects in design high performance RFIC in CMOS process. Among all of the components constituting the RFIC, Power Amplifier (PA) and Voltage Controlled Oscillator (VCO) are the most critical parts and it is quite significant to promote their performance.

VCO is the heart of the frequency synthesizer, the performance of the VCO has large effect on phase lock loop (PLL) and the quality of transceiver. For system with high dynamic range requirements, the VCO must achieve a corresponding spectral purity. Thus, the VCO should have a low harmonic frequency, especially, a low phase noise, which has important effect on Signal to Noise Ratio (SNR). VCO in a high speed communication system is far more challenge because of the requirement of wideband oscillation frequency. In this thesis, an ultra-wideband VCO is designed. A novel tunable switching inductor is proposed to enlarge the oscillation frequency, and switching AMOS varactor bank is used to decrease the VCO gain and improve the phase noise. The chip was fabricated in 0.13  $\mu$ m CMOS process and the experimental results demonstrate a wideband of 92.6% from 1.20 GHz to 3.27 GHz with a phase noise of -120 dBc/Hz at 1 MHz offset from the 3.1 GHz carrier is obtained.

PA is the key component in the transceiver and it consumes above 60% dc power

Abstract v

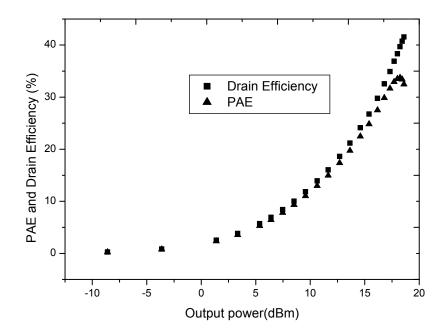

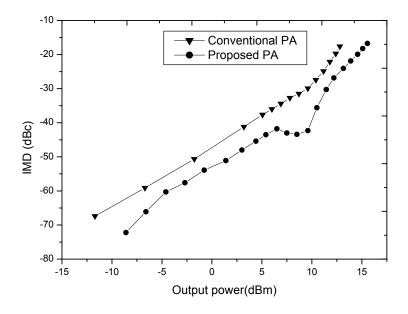

of the whole communication systems. Thus, the efficiency of the CMOS PA also affects the efficiency of the transceiver. However, in the modern wireless communication systems, the linear modulation is usually adopted for the high data rate and high speed communication systems, such as complex vector modulations. In this kind of modulations, the signal has a very high Peak to Average Ratio (PAR) and usually the PA should be backed off from output 1 dB Compression Point (P1dB) to get the desired specifications, which cause the efficiency of PA is much lower than the maximum efficiency near the output P1dB. Therefore, the linearization technique is developed for PA and it can decrease the back-off dBs from P1dB with the desired specifications, thus, increase the efficiency of the PA. In this thesis, a novel multi-cascode linearized CMOS PA is presented with post-linearization technique for 5.8 GHz Dedicated Short Range Communication (DSRC) applications. It was fabricated in 0.13  $\mu$ m CMOS process to verify the effectiveness of the proposed technique. Experimental results show a Third-order Intermodulation Distortion(IMD) improvement of 5.5 dB over large output power range and the maximum improvement of 10 dB with a high Power Added Efficiency (PAE) of 32% at the output 1 dB gain compression point (P1dB).

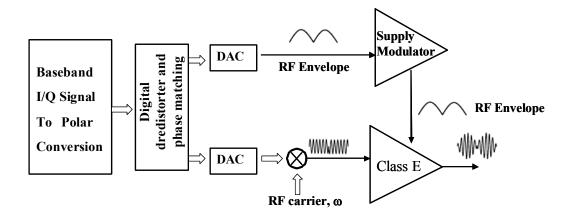

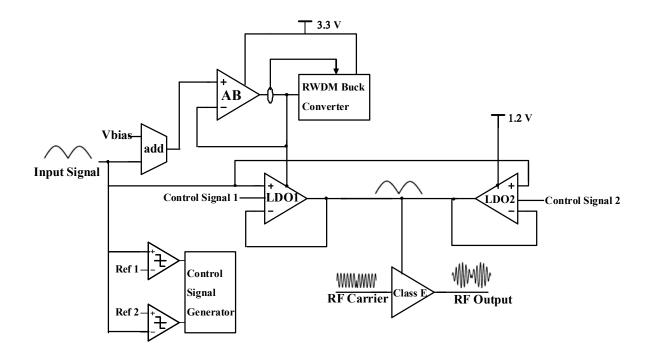

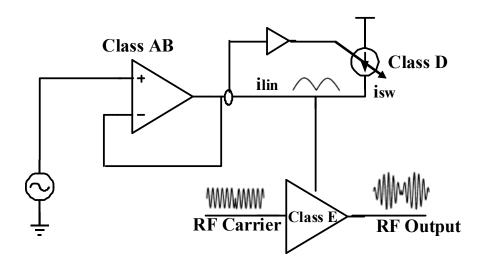

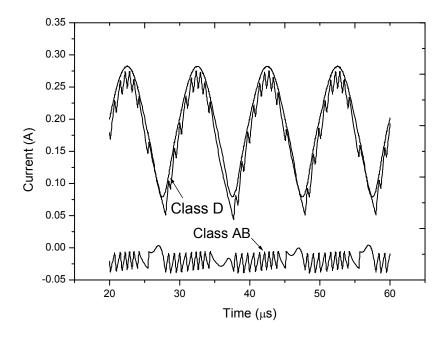

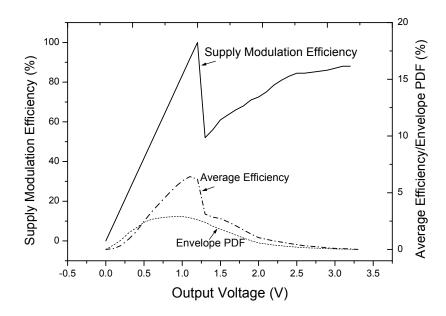

A CMOS Class-G supply modulation for polar PA with high average efficiency and low ripple noise is also proposed. In the proposed Class-G supply modulation, the parallel supply modulations which are controlled by switch signals are utilized for low power and high power supplies to increase the average efficiency. A low dropout (LDO) is utilized to suppress the delta-modulated noise and provide a low ripple noise power supply. The proposed supply modulation was designed with 0.13  $\mu$ m CMOS process. The simulation results show that the proposed supply modulation achieves a maximum efficiency of 85.1%. It achieves an average efficiency of 29.3% and a 7.1% improvement compared with the conventional supply modulations with Class-E power amplifier. The proposed supply modulation also shows an excellent spurious free dynamic range (SFDR) of -73 dBc for output envelope signal.

### Acknowledgments

It is a pleasure to thank the many people who made this dissertation possible.

First and foremost, I wish to express my sincere gratitude to my Ph.D. supervisor, Professor Toshihiko Yoshimasu. With his enthusiasm, inspiration, and great efforts to explain concepts clearly and simply, he helped to make the difficult problems fun for me. Throughout my doctoral research period, he provided encouragement, sound advice, good teaching, good company, and many good ideas. I will never forget his dedication in reviewing my papers from afternoon until very early in the morning. Nor will I forget his warmhearted and supportive smiles and words, which encouraged me to persist when I met difficulties in my research. I would have been lost without him.

I wish to express my sincere appreciation to Professor Goto. He gave me the chance to take a part time job in Waseda University Global COE Program International Research and Education Center for Ambient SoC sponsored by MEXT, Japan. where I get the financial support. I received that enable me study and live for years in Japan. Without these supports, it would have been impossible for me to conduct my research without interruption.

I am very grateful to the following professors who carefully read my doctor thesis and give me advice. They are Professor Inoue and Professor Yoshihara in IPS, Waseda University and Associate Professor Kanaya in Kyushu University.

I am also grateful to the following people for they give me the tapeout chance and their helpfull advices. They include Professor Nobuyuki Itoh in Okayama Prefectual University, Okayama, JAPAN, Mr. Koji Horie and Doctor Satoshi Kurachi in Semiconductor Company, Toshiba Corporation, Kawasaki-shi, JAPAN.

I am indebted to many student colleagues of Yoshimasu Lab, who have provided many stimulating and entertaining experiences in the high-pressure research environment in which we learned. I am especially grateful to Doctor Jiangtao Sun, Mr. YongJu Shu, Yusuke Takigawa, Yu Zhao, Xuewen Zhu and Gong Cheng, for their friendship and assistance over the years.

I also wish to thank my friends and colleagues in the GCOE Research Assistant

Acknowledgments vii

Group of Waseda University including Doctor Mingly Jiang, Doctor Zhiguo Bao and Mr. Xun He, who provided many interesting discussions and helped me view a single problem with various perspectives. Special thanks also go to Mrs. Kozy Ohata, a secretary of the GCOE office, who kindly and patiently helped me enormously with my documental stuffs on GCOE research.

I also wish to thank Professor Zhengxiang Luo, Professor Jingfu Bao and Professor Kai Yang. They always encourage me in these years. Without their encouragement, I think it is not easy for me to conquer so many troubles in the research.

Last, and most importantly, I wish to thank my entire family for providing a loving environment for me. I am forever indebted to my parents, Zhi-Ping Liu and Wen-Xiu He. They bore me, raised me, supported me, taught me, and loved me. And I also thank my uncle Wenduo He, aunt Yaohui Ming and aunt Wenli He. They help me a lot in my life.

Dedicated to my father Zhi-Ping Liu, my mother Wen-Xiu He.

# Chapter 1

# Introduction

#### 1.1 Background

With the fast development of the wireless communications, wireless communications has been used in every field of daily life. Explosive growth in the wireless market makes wireless communications the center of the industrial development in the  $21^{th}$  century.

In February 1980, a family of IEEE (Institute of Electrical and Electronic Engineers) 802 standards dealing with local area networks and metropolitan area networks was established [1]. These standards is maintained by the IEEE 802 LAN/MAN Standards Committee (LMSC) and an individual Working Group provides the focus for each area [2].

In the 1980s, cellular phones were first introduced. And the early systems became known as first generation (1G) mobile phones, such as Advanced Mobile Phone Service (AMPS), Nordic Mobile Telephone (NMT), and Radio Telefono Mobile Integrato (RTMI). In the 1990s, second generation (2G) mobile phone systems such as Global System for Mobile Communication (GSM) and IS-95 (CDMA) began to widely be used. And in Japan, the Personal Digital Cellular telecommunication system (PDC) is standardized as the digital mobile communication system. NTT DoCoMo has commercially operated the PDC system to provide voice, data, and facsimile communication service sine March 1993 [3]- [4]. Before the widely spread of the third generation (3G) mobile phone systems, 2.5G systems such

as General Packet Radio Service (GPRS), Code Division Multiple Access (CDMA) and Enhanced Data rates for GSM Evolution (EDGE) were developed as a transition from the second generation to third generation. In 2.5G, it provide a high speed of data and it can provide some benefits of third generation systems and also it is compatible with the second generation network.

The availability of low-cost digital circuits paved the way to adopting advanced digital modulation schemes. Due to the increased level of usage, service providers started to add more base stations which led to higher density and smaller size of cellular sites. From 2G systems, International Telecommunication Union (ITU) specifies the International Mobile Telecommunications-2000 (IMT-2000) as a generation of standards for mobile phones and mobile telecommunications services. Application services include wide-area wireless voice telephone, mobile Internet access, video calls and mobile TV, all in a mobile environment. Compared to the older 2G and 2.5G standards, a 3G system must provide peak data rates of at least 200 kbit/s according to the IMT-2000 specification. Recent 3G releases, often denoted 3.5G and 3.75G, also provide mobile broadband access of several Mbit/s to laptop computers and smartphones [2], [5], [6] and [7]. Universal Mobile Telecommunications System (UMTS) and Code Division Multiple Access 2000 (CDMA2000) are the representation of the 3G mobile telecommunications technologies. UMTS, which also being developed into a 4G technology, is specified by 3GPP and is part of the global ITU IMT-2000 standard. The most common form of UMTS uses Wideband Code Division Multiple Access (WCDMA) as the underlying air interface but the system also covers Time Division CDMA (TD-CDMA) and Time Division-Synchronous Code Division Multiple Access (TD-SCDMA) with a peak data rate of 2 Mbps [8].

In less than twenty years, mobile phones have gone from rare and expensive consumption to now every people has their own mobile phones as every family has their own land-line telephones. By the end of 2005, the global mobile phone market grew to 2 billion subscribers. Yet this market is still growing.

Concurrent with the developments of mobile phones, the other wireless commu-

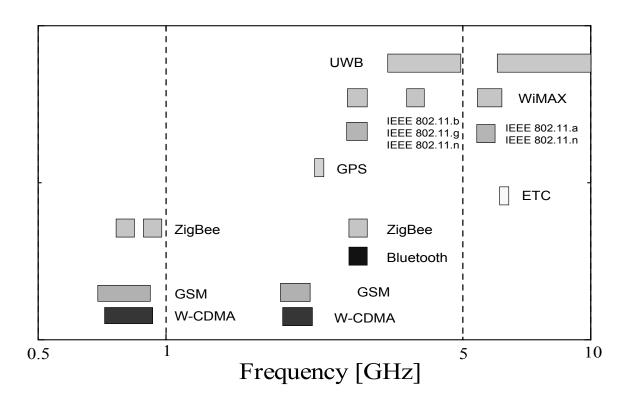

Figure 1.1: The main wireless communication systems.

nications such as ZigBee, Bluetooth, Global Positioning System (GPS), Worldwide Interoperability for Wireless Access (WiMAX), Ultra Wide Band (UWB) and Wireless Local

Area Network (WLAN) are also growing explosively. The main wireless communications

is shown in Figure 1.1. ZigBee is focused on control and automation, While Bluetooth

is focused on connectivity between laptops, PDAs, and the like, as well as more general

cable replacement [9]. The frequency range of UWB is from 3.1 GHz to 10.6 GHz and it

supports short distance communication with a data rate above 100 Mbps. And the UWB

is widely used in wireless Universal Serial Bus (USB) [10]. The most well-known systems

are probably applications related to Wireless Local Area Network (WLAN). The WLAN

worldwide service revenues are projected to reach 9.5 Billion dollar by 2007 (source: Alexander Resources). WLAN links two or more devices using some wireless distribution method

(typically spread-spectrum or OFDM radio), and usually providing a connection through an access point to the wider internet. This gives users the mobility to move around within a local coverage area and still be connected to the network [2], [11]. Wireless LAN is promoted by Wi-Fi Alliance which is a trade association technology and certifies products if they conform to certain standards of interoperability [12]. The original 802.11 standard allowed a maximum channel bit rate of only 2 megabits per second, while the current 802.11b standardcommonly known as Wi-Fi supports an 11 Mbps maximum rate. However, the widespread deployment of 802.11a and 802.11g standards, which allow a bit rate of up to 54 Mbps, pave the way for new types of mobile applications, including mobile commerce transactions and location-based services [13]. And the latest IEEE802.11n system offers enhanced 114 Mbps data rates, greater spectral efficiency, and better quality and robustness compared with the existing IEEE802.11a/b/g systems and it will create a demand for seamless connectivity between a growing array of multimedia and entertainment platforms [14].

The development trends of the mobile telecommunications systems and the other wireless communication systems all show the fast growth in high speed and high data rate communication ability. This need makes the system design more difficult and challenge.

With the developments in the wireless communication industry, there are several tremendous advantages in semiconductor technologies. Among them, GaAs HBT, GeSi HBT and Si CMOS is quite prevalent and the most significant progress made is CMOS technologies. The remarkable characteristic of CMOS transistors is that their speed increase, while the consume less power per function in digital circuits, and low cost duo to the decreased size and its Si materials. The digital circuit is nearly not impossible to be integrated by GaAs HBT or GeSi HBT with the merit of CMOS process. In addition, the integration of the RFIC in CMOS process make it the most widely used semiconductor technologies which can fulfill the integration of the whole system on one chip [15] to [17].

### 1.2 Motivation and Research Objective

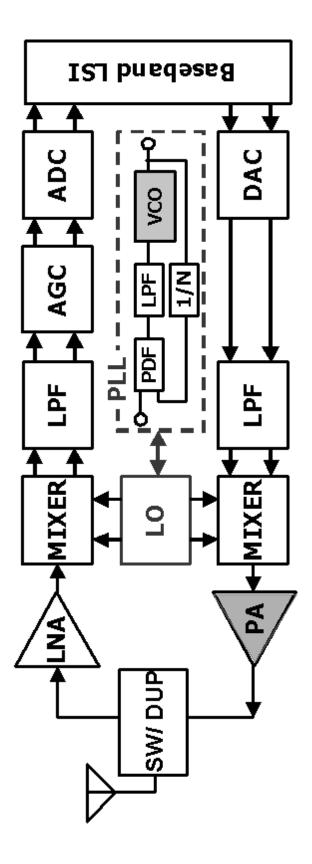

A typical wireless transceiver architecture is shown in Figure 1.2. The position of the VCO is as shown in this figure. The VCO is a key part with the most challenging aspects in PLL and it is controlled by the signal from the filter to provide an appropriate frequency reference to operate.

Commonly, in the cellular phone and WLAN, the bandwidth is quite narrow and design a VCO with low phase noise is not so difficult. With the development of the wireless communications, current trends clearly indicate a growing customer demand for multi-band multi-standard transceivers [18] and faster data rates [19] to [21]. The high data rate is achieved by using a wideband channel bandwidth. Applications such as the 3.1 to 10.6 GHz frequency range UWB system, the wideband VCO is necessary to cover a wideband range from 3.1 to 10.6 GHz [22] to [23]. Furthermore, the future cognizant radios which can sense unused or less crowded portions of the spectrum and reconfigure itself to operate there. These systems have a wideband in order to raise the utilization of the spectrum, therefore, requiring a wideband frequency synthesizer as well. Hence, wideband VCOs are becoming important in those applications.

Design wideband VCO is quite challenge in CMOS process because of the large parasitic capacitance. These parasitic capacitance exists in crossing couple NMOS or PMOS transistors and switches in a capacitor bank, which is commonly used for a wide turning ratio of capacitance. Between these two kinds of parasitic capacitors, the parasitic capacitor of switches in capacitor bank seriously detriments the turning ratio of the capacitance, thus, limited the turning range of the oscillation range. To enlarge the turning range, the new technique should be proposed to overcome the drawbacks in a conventional VCO.

The PA is the last active building block in the transmitter chain as shown in Figure 1.2. The most important function of a PA is to amplify the signal to a level high enough that it can travel through the air to the receiver and the signal can be correctly demodulated in the receiver. Nowadays, there is a trend of integrating all the components in

Figure 1.2: A typical wireless transceiver architecture.

a wireless communication system on a single chip [24] and [25] in CMOS process. However, there is still one component PA that is hard to integrated with other system in CMOS process because the drawback of the CMOS process. Today, almost all PAs in market are manufactured with III-V compound semiconductors. This is necessary because high output power and high power efficiency are required PA specifications in various applications. The III-V compound semiconductors offers a much better efficiency and linearity, and it also offers a higher output power compared with CMOS semiconductors because of the merit of the III-V compound process. This is very difficult to satisfy those requirements with CMOS technologies. In CMOS technologies, the poor quality value of the inductors cause large loss in the output matching network, which decrease the efficiency of PA. Further more, the lossy substrate of CMOS process also cause power loss in route and between the connection of MOS transistors, which also impairs the efficiency of PA. And up to now, almost all of the PA reported in CMOS has a low efficiency about 25% at P1dB when the operating frequency is above 5 GHz. The large variation of the parasitic capacitance in CMOS process also detriments the linearity of PA and the low breakdown drain to source voltage limited the output power capacity below 1 W. Because of all these drawbacks, the usage of the CMOS PA is largely limited in commercial product. However, due to the high manufacturing cost of the III-V technologies, and the impossible of integration of the whole system to realize system-on-chip (SoC) by III-V technologies, there is a growing interests of research on CMOS PA.

The first CMOS RF PA that could deliver hundreds mW power was reported in 1997, implemented in a single-ended configuration with a 0.8  $\mu$ m CMOS technology [26]. And the first CMOS RF differential amplifier that could deliver over 1W at GHz range was reported in 1998, implemented with a 0.35  $\mu$ m CMOS technology [27]. After that, there have been quite a few publications on CMOS RF PAs [28] to [32]. They all rely on off-chip components to implement low-loss impedance transformation network. After several years research of the CMOS PA, the fully integration of CMOS PA was reported in [33] and [34].

In the modern wireless communication systems, in order to get a high speed and

high data rate, the linear modulation with high PAR is used. The CMOS PA has to work in a back off state to get the desired specification. With a back-off state, the PA works with a poor efficiency. Commonly, the PA dominates the power consumption of the entire transceiver. Therefore, improving the PA power efficiency also improves the efficiency of the whole wireless communication systems. And this is especially important in portable devices such as cell phones, PDAs demanding low power systems for a longer battery life.

In light of the above trends, the main goals of this thesis are to design high performance wideband VCO and high linearity and high efficiency PA to satisfy the growth in the high speed and high data rate modern wireless communication. With new design techniques, the VCO and PA show an improved performance in CMOS process compared with the conventional prototypes.

#### 1.3 Contribution of the Thesis and Its Structure

The main objective of this research is to promote the performance the key component VCO and PA in the wireless communications. The research work can be divided into two significant parts, the first part focus on the design of a wideband VCO with a tunable switching inductors. This technique is further described in Chapter 2. To demonstrate the design techniques, an experimental prototype wideband VCO was designed. The prototype wideband VCO can cover a wide frequency band, in which many popular wireless communications are located. The second part focus on the design of a high linearity and high efficiency PA. A post-linearization is proposed dedicated for cascode architecture which usually used in CMOS PA to boost the output power capacity. To demonstrate the design techniques, an experimental prototype was designed for 5.8 GHz Dedicated Short Range Communication (DSRC) applications. This technique is further described in Chapter 3. A Class-G supply modulation PA is also design for high efficiency, the simulation is carried out to verify the effectiveness of the proposed Class-G supply modulation PA. This technique is further described in Chapter 4.

The primary contributions of this research are:

- ♦ A new technique was proposed with tunable switching inductors, the VCO with this technique can get a much more wideband turning range. The proposed tunable switching inductors are implemented based on transformers. By changing the equivalent inductance in the secondary, the effective inductance of the transformer is changed. The equivalent circuit of the transformer based tunable inductor is derived from the transformer equivalent T-model and the principle analysis is also given in this research. And many practical implementation issues are discussed.

- ♦ To verify the proposed technique, firstly, this wideband VCO was designed and optimized in ADS. Then, the wideband VCO was fabricated by 0.13  $\mu$ m CMOS process and the prototype was measured fully on-chip. The proposed wideband VCO exhibits a frequency tuning range as high as 92.6% from 1.20 GHz to 3.27 GHz at an operation voltage of 1.5 V. The measured phase noise of -120 dBc/Hz and -123 dBc/Hz at 1 MHz offset from the 3.1 GHz and 1.2 GHz, respectively, carrier is obtained.

- ♦ A multi-cascode post-linearization technique for CMOS cascode PA is proposed in this work and this architecture can minimize the transconductance distortion in the cascode stage, thus, linearize the cascode PA. The transconductance distortion is also analyzed in this work in order to search this effective technique and this analysis shows the transconductance distortion canceling can be achieved with only an additional commongate transistor as a linearizer. It also can be concluded that this linearizer does not sacrifice efficiency because of its closed to Class-C operation condition.

- $\blacklozenge$  To verify the proposed technique, firstly, this high linearity and high efficiency PA was designed and optimized in ADS. Then, the prototype PA was fabricated by 0.13  $\mu$ m CMOS process and measured fully on-chip. With a low supply voltage of 2.0 V, the

prototype PA produces an output power of 1 dB compression point (P1dB) of 17.3 dBm and Power Added Efficiency (PAE) of 32 % at the P1dB. The improvement in IM3 of 6 dB over large output power range and the maximum improvement of 12 dB are achieved. The measured Output Third Order Intercept Point (OIP3) is as high as 27.3 dBm.

- ♦ In order to increase the efficiency of the PA, a new architecture of Class-G supply modulation PA is proposed. In this architecture, hybrid amplifier is used for high power supply and LDO is used for the low power supply. This architecture has a high efficiency at high output current and low output current. It also has good SFDR at low output current comparing with the conventional supply modulation.

- ♦ In order to suppress the noise from the switching PA, a twice noise filtering technique is proposed to suppress the noise of switching PA. The first noise filter is implemented by the low output impedance of the Class-AB amplifier as in conventional supply modulation. The second noise filter consists of the LDO with a novel bias technique for a fixed dropout voltage to make the LDO with high PSRR. With this twice noise filtering technique, the noise is largely suppressed.

- ♦In order to track the current accurately for the switching PA, an accurate current detector is proposed. The proposed current detector overcomes the inaccuracy introduced by the channel length modulation in conventional current detector. It can accurately copy the current from Class-AB amplifier output stage with rail-to-rail output range within 0.4% error.

- ♦ To verify the proposed technique, the proposed Class-G supply modulation PA and conventional supply modulation PA are simulated. the simulation results confirms that it achieves an average efficiency of 29.3% and a 7.1% improvement compared with the conventional supply modulations with Class-E PA. The proposed supply modulation also shows

an excellent spurious free dynamic range (SFDR) of -73 dBc for output envelope signal.

This dissertation is organized into four relatively independent parts, including

Chapter 2: A Wideband LC VCO IC

Chapter 3: A High Linearity and High Efficiency PA IC

Chapter 4: A CMOS Class-G Supply Modulation for Polar PAs with High Average Efficiency and Low Ripple Noise

Chapter 5: Conclusions and Future Work

Chapter 2 focus on the wideband VCO design. A wideband VCO design with variable inductors are introduced in this paper. The prototype of the wideband VCO is also fabricated and measured. The measured result and the result analysis are also given in this chapter.

Chapter 3 focus on the high linearity and high efficiency PA design. To overcome the drawbacks of CMOS PA, a new post-linearization technique is introduced in this chapter. The prototype of the PA is also fabricated and measured. The measured result and the result analysis is also given in this chapter.

Chapter 4 focus on the high efficiency Class-G Supply Modulation PA design. To increase the average efficiency, a new Class-G Supply Modulation PA is introduced in this chapter. The prototype of the PA is simulated to demonstrate the improvement in average efficiency.

Chapter 5 provides the conclusion and future work of this thesis.

# Chapter 2

# Novel Wideband LC VCO IC

#### 2.1 Overview

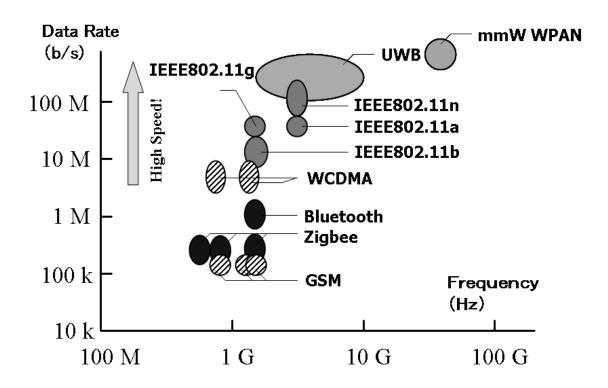

VCO is the key part in PLL, and the performance of VCO in terms of phase noise, tuning range and turning range also determines the performance of PLL, and hence, determines many of the basic performance characteristics of a transceiver. There is a trend towards wideband higher data transfer rates in wireless communication system as shown in Figure 2.1. And this trend demands very wide tuning range and low phase noise performance of VCO [35]-[39]. This trend also generates an interest of wideband VCO design. Whereas relaxation oscillators easily achieve very wide tuning range (i.e. 100% or more), their poor phase noise performance limited them in most of todays wireless communication applications. Because the LC VCO has a high qualify factor of LC tank, the performance of the LC VCO is much better compared with the relaxation oscillators. Because of this merit, the LC VCO has been used for many narrowband wireless transceivers. Compared with the relaxation oscillators, the LC VCO promises a broad application in wideband VCO design and there is a growing interest in extending tuning range of LC VCO. Recently, several wideband CMOS LC VCOs have been demonstrated using a variety of techniques [36]-[39]. Though, the accumulation-type MOS varactors support a very wide tuning range and their Q is sufficiently high that good phase noise performance can be maintained [37], the overall

Figure 2.1: The trend of the wireless communication systems.

phase noise performance is also highly dependent on the tuning sensitivity of the VCO, since noise from preceding stages of the frequency synthesizer is inevitably injected onto the VCO control input. Thus, on the other hand, decrease the tuning sensitivity of the VCO is critical to improve the phase noise performance. And there are also some reports about decreasing the tuning sensitivity and increasing the bandwidth of the VCO [40] - [42].

## 2.2 Wideband LC VCO Design

This wideband VCO is designed by 0.13  $\mu m$  CMOS process, the target of the wideband VCO is shown in Table 2.1.

Frequency Bandwidth

| Voltage             | 1.5 V                                    |

|---------------------|------------------------------------------|

| Turning Range       | ≥ 90 %                                   |

| Phase Noise @ 1 MHz | ≤-115 dBc@ 3.1 GHz and -120 dBc@ 1.2 GHz |

| Zeq O               | $C_{v}$                                  |

Table 2.1: Wideband VCO Target

$1.2~\mathrm{GHz} - 3.2~\mathrm{GHz}$

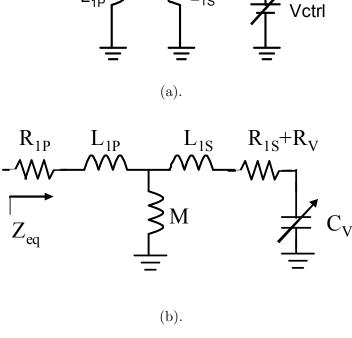

Figure 2.2: (a) Schematic of the transformer-based variable inductor. (b) The equivalent circuit of the variable inductor.

#### 2.2.1 Transformer-based Switched Variable Inductors Design

The proposed transformer-based switched variable inductors and its equivalent circuit is shown in Figure 2.2. In the Figure 2.2 (a)  $L_{1P}$  and  $L_{1S}$  are the primary and

secondary inductances, respectively. M is the mutual inductance, and  $i_1$  and  $i_2$  are the current through primary and secondary windings, respectively.  $C_V$  is the AMOS varactor for changing the capacitance and consequently changes the effective inductance  $L_{eq}$ , which is the inductance looking into the primary inductor of the transformer.  $C_V$  is controlled by the control voltage  $V_{ctrl}$ . The equivalent circuit is shown in Figure 2.2 (b).  $R_{1P}$  and  $R_{1S}$  are the primary and secondary parasitic resistance, respectively, and  $R_V$  is the parasitic resistance of the varactor. The equivalent impedance  $Z_{eq}$  from the circuit is derived to be:

$$Z_{eq} = R_{1P} + j\omega L_{1P} + j\omega L_{1P} \| (R_{1S} + R_V + j\omega L_{1S} - j(\omega C_V)^{-1})$$

(2.1)

where  $\omega$  is the angular frequency. After arranging the Equation 2.1, the equivalent impedance  $Z_{eq}$  is expressed as:

$$Z_{eq} = R_{1P} + j\omega L_{1P} + \frac{\omega^2 M^2}{R_{1S} + R_V + j\omega L_{1S} - j(\omega C_V)^{-1}}$$

(2.2)

The equivalent  $L_{eq}$  is derived from Equation 2.2 to be:

$$L_{eq} = L_{1P} - \frac{\omega M^2 [\omega L_{1S} - (\omega C_V)^{-1}]}{(R_{1S} + R_V)^2 + [\omega L_{1S} - (\omega C_V)^{-1}]^2}$$

(2.3)

if  $R_V\,+\,R_{1S}$  is small enough and Equation 2.2 can be approximated as:

$$L_{eq} \approx L_{1P} + \frac{\omega M^2}{(\omega C_V)^{-1} - \omega L_{1S}} \tag{2.4}$$

then equation Equation 2.4 can be rearranged to be:

$$L_{eq} \approx L_{1P} + \frac{\omega^2 M^2 C_V}{1 - \omega^2 L_{1S} C_V} \tag{2.5}$$

the angular frequency  $\omega$  is decided by oscillation frequency of the VCO and it can be expressed by:

$$\omega = \sqrt{\frac{1}{L_{eq}C_{tal}}} \tag{2.6}$$

where  $C_{tal}$  is the total capacitance of the LC-tank and MOS transistors. Replace  $\omega$  in Equation 2.5 with Equation 2.6, the Equation 2.6 can be rewritten by:

$$L_{eq} \approx L_{1P} + \frac{\omega^2 M^2 C_V}{1 - L_{1S} C_V / L_{ea} C_{tal}}$$

(2.7)

In Equation 2.7, the second part can be either positive or negative. This is a double-tuned transformer with only one driving port [43]. The resonator exhibits a two resonance-points characteristic with different signal levels. For the sake of simplicity, assume that the transformer is fully balanced, which means  $L_{1S} = L_{1P} = L$ ,  $R_{1S} = R_{1P} = R$  and  $C_{tal} = C_V = C$ . The two resonance frequencies as a function of the tank parameters is described as:

$$\varpi_{1,2} = \frac{1}{\sqrt{LC(1\pm k)}}$$

(2.8)

The quality factor at each resonance point is given by:

$$Q_{1,2} \cong \frac{1}{R} \sqrt{\frac{L}{C} (1 \pm k)} \tag{2.9}$$

The amplitude at the two resonance-points is described as:

$$V_{1,2} = \frac{i_1(1 \pm k)L}{2RC} \tag{2.10}$$

In order to avoid the unintentional occurrence of this upper resonate mode in the VCO, in the design,  $C_{tal}$  is much larger than  $C_V$  and  $L_{eq}C_{tal}$  is much larger than  $L_{1S}C_V$ . Thus, Equation 2.6 can be approximated as:

$$L_{eq} \approx L_{1P} + \omega^2 M^2 C_V \tag{2.11}$$

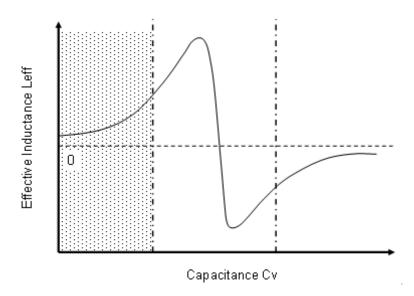

However, it shows the property of inductance only when the capacitance  $C_V$  is small. When the capacitance  $C_V$  becomes large, oscillation of the secondary transformer starts up. The image part becomes infinite and if the capacitance  $C_V$  continue to become large, the transformer shows a property of capacitance. And near the oscillation point, the Q-value also deteriorates. Thus, commonly, the small  $C_V$  is used as shown in the shadow in Figure 2.3.

Equation 2.11 reveals the principle of the proposed transformer-based variable inductor. The effective inductance is nearly linear with  $C_V$  and it can be changed by tuning  $C_V$  of the varactor. Thus, a continuous inductance can be obtained by turning the

Figure 2.3: The operational region of the transformer.

capacitance of the varactor  $C_V$ . In addition, the range of the tuning voltage is the same with the control voltage of the AMOS varactor bank. Therefore, the same control voltage can be used for the varactor in the AMOS varactor bank and in the variable inductors. And in the PLL system, they can share the same control voltage from the output of the PLL filter.

The equivalent resistance  $R_{eq}$  can also be obtained from Equation 2.2 as:

$$R_{eq} = R_{1P} + \frac{\omega^2 M^2 (R_{1S} + R_V)}{(R_{1S} + R_V)^2 + [\omega L_{1S} - (\omega C_V)^{-1}]^2}$$

(2.12)

If  $R_V + R_{1S}$  is negligible, this expression can be approximated as:

$$R_{eq} = R_{1P} + \frac{\omega^2 M^2 (R_{1S} + R_V)}{[\omega L_{1S} - (\omega C_V)^{-1}]^2}$$

(2.13)

In the same way as Equation 2.7 to Equation 2.11, the Equation 2.13 can be approximated as:

$$R_{eq} = R_{1P} + \omega^4 M^2 C_V^2 (R_{1S} + R_V)$$

(2.14)

From Equations 2.3 and 2.14, the quality factor of the equivalent inductor can be obtained as:

Figure 2.4: Schematic of the proposed transformer-based switched variable inductor set.

$$Q = \frac{\omega L_{eq}}{R_{eq}}$$

$$= \omega \left\{ L_{1P} - \frac{\omega M^2 [\omega L_{1S} - (\omega C_V)^{-1}]}{(R_{1S} + R_V)^2 + [\omega L_{1S} - (\omega C_V)^{-1}]^2} \right\}$$

$$\div \left\{ R_{1P} + \frac{\omega^2 M^2 (R_{1S} + R_V)}{(R_{1S} + R_V)^2 + [\omega L_{1S} - (\omega C_V)^{-1}]^2} \right\}$$

$$\approx \frac{\omega L_{1P} + \omega^3 M^2 C_V}{R_{1P} + \omega^4 M^2 C_V^2 (R_{1S} + R_V)}$$

(2.15)

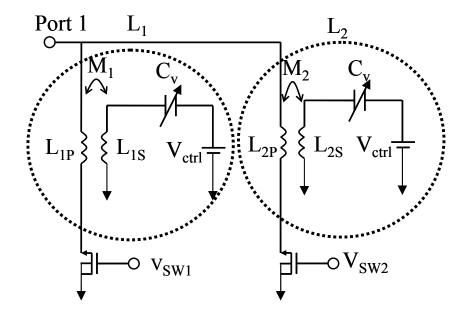

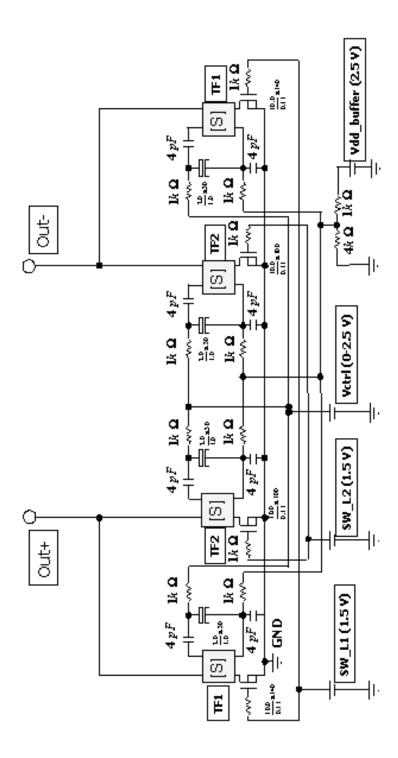

In this work, two transformer-based variable inductors ( $L_1$  and  $L_2$ ) are connected in parallel with two NMOS for switching the inductors. The schematic of the proposed transformer-based switched variable inductor set is shown in Figure 2.4. The two variable inductors have different effective inductance ( $L_{eq}$ ). Thus, coarse tuning of inductance can be realized by switching the two variable inductors and the fine turning of the inductance is by turning the varactor. To avoid the oscillation region as shown in Figure 2.3, the small size of the varactor is chosen for turning the inductance.

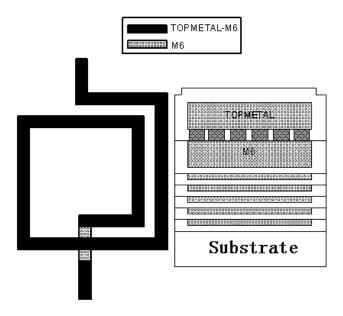

Figure 2.5: The metal layers in the CMOS process.

To decrease both the parasitic on-resistance and off-capacitance of the switching circuit, the NMOS switching connecting series with the inductors have the minimal gate length of 0.11  $\mu$ m and a total gate width of 600  $\mu$ m, which provide a good compromise between parasitic on-resistance and off-capacitance.

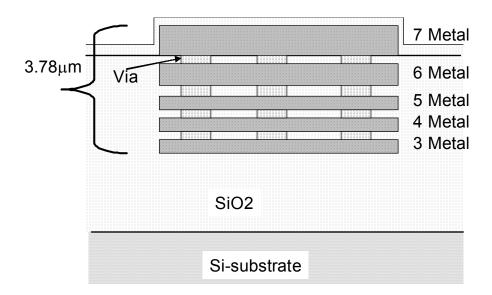

There are 7 metal layers in this 0.13  $\mu$ m CMOS process, and the top metal are quite think. The loss is very large if only use the top metal. Thus considering the loss in the metal and parasitic capacitance between the substrate, the top five metals are used for the transformer as shown in Figure 2.5. Composed by the top five layers, the metal thickness for the transformer is 3.78  $\mu$ m.

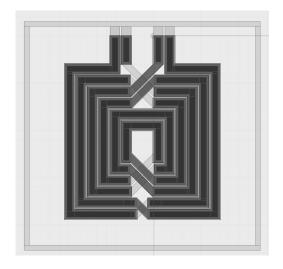

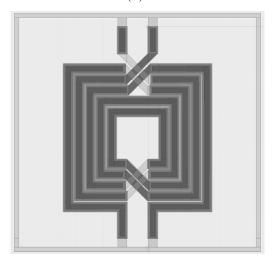

The transformers are designed with 3D Electronic Magnetic software Ansoft HFSS. The models of the two transformers are shown in Figure 2.6 (a) and Figure 2.6 (b). To enhance the effective coupling factor k, multiple circles coupling are used to decreasing the area of the transformers. The primary inductor of  $L_1$  is a double-turn 10- $\mu$ m-wide coil with a radius of 140  $\mu$ m. The secondary inductor of  $L_1$  is a triple-turn 10- $\mu$ m-wide coil with a radius of 164  $\mu$ m. The primary inductor of  $L_2$  is a double-turn 10- $\mu$ m-wide coil with a

(a).

(b).

Figure 2.6: (a) The layout of the transformer D116N2W10. (b) The layout of the transformer D140N2W10.

radius of 116  $\mu$ m. The secondary inductor of  $L_2$  is a quadruple-turn 10- $\mu$ m-wide coil with a radius of 164  $\mu$ m. The width of 10  $\mu$ m chosen for the metal layers also provide a good compromise between the metal loss and parasitic capacitance between the substrate. The S-parameter is also obtained in HFSS. The effective coupling factor is got by Z-parameter. The inductance value, quality factor and Z-parameter are calculated from the S-parameter.

Then calculate the inductance of the primary stage of transformer, the secondary stage of transformer is open. And the primary stage of transformer is open, when calculate the inductance of the secondary stage of transformer. Then, the inductance is obtained by the following expression:

$$L_p = \frac{Im(Z_{11})}{Re(Z_{11})} \tag{2.16}$$

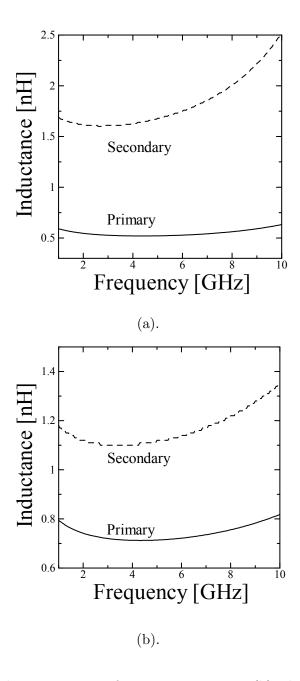

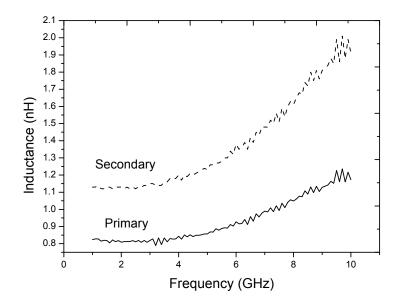

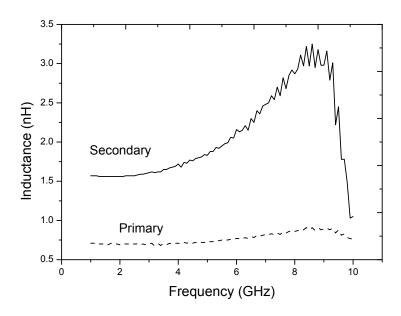

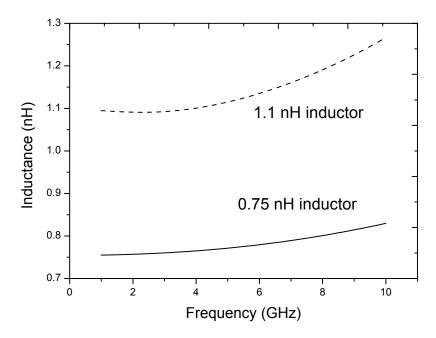

The inductance is variable with the frequency as shown in Figure 2.7. The inductance of the primary stage of transformer D116N2W10 is from 0.45 nH to 0.6 nH and the inductance of the secondary stage of it is from 1.6 nH to 2.5 nH. The inductance of the primary stage of transformer D140N2W10 is from 0.57 nH to 0.68 nH and the inductance of the secondary stage of it is from 1.15 nH to 1.3 nH.

The Q-factors from the primary stage inductor of transformer is very important like that of the inductors in the LC-tank in a conventional VCO. When test the Q-factors from the primary stage inductor, the secondary of the transformer is open. The Q-factors values is calculated as that in a inductor:

$$Q_p = \frac{Im(Z_{11})}{\varpi} \tag{2.17}$$

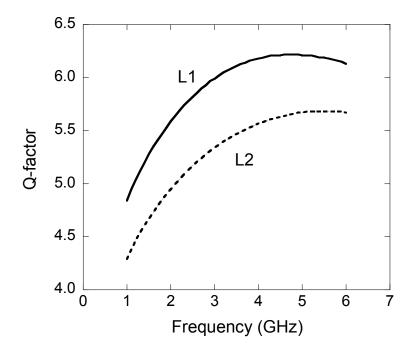

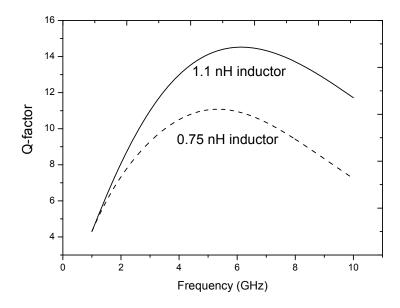

The simulation Q-factors from the primary stage inductor  $L_1$  of D116N2W10 and  $L_2$  of D140N2W10 are shown in Figure 2.8. Q-factors of  $L_1$  and  $L_2$  are expected to be from 4.2 to 6.2 over the same frequency range. These relatively low Q-factors comparing with general spiral inductors result from mutual coupling between the primary and secondary inductors.

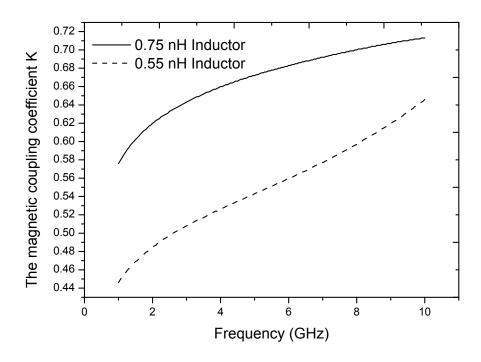

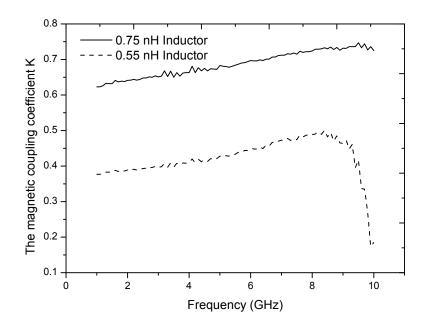

The simulated effective coupling factor k results are shown in Figure 2.9. The  $L_1$  has a large area compared with the  $L_2$  and thus the inductance  $L_1$  is larger than inductance  $L_2$ . The coupling length of  $L_1$  is also longer than the length of  $L_2$ , thus the effective coupling factor k in  $L_1$  is large than  $L_2$  as shown in Figure 2.9. The effective coupling factor k of  $L_1$  is from 0.57 to 0.68, and that of  $L_2$  is from 0.45 to 0.56.

The combination of the transformer based inductors are shown in Figure 2.4. There are three kinds of inductance can be connected in the LC tank when switch on or off the

Figure 2.7: (a) The inductance in transformer D116N2W10. (b) The inductance in transformer D140N2W10.

NMOS. The biggest inductance connected in the LC tank is obtained when the  $L_1$  is on and  $L_2$  is off. And the lowest inductance connected in the LC tank is obtained when the  $L_1$  is on and  $L_2$  is on.

Figure 2.8: The Q-factor of the inductor L1 and L2.

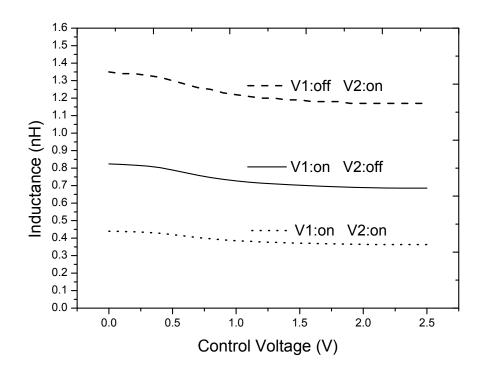

The detail circuit of the transformer based inductors are shown in Figure 2.10. There are two sets of transformer based inductors which are denoted as [S], and there two NMOS switching and two AMOS varactors for one set. The simulation of the inductance with the control voltage from 0 V to 2.5 V is shown in Figure 2.11. It is clear that the inductance is changed with the turning voltage. Each L1 and L2 are simultaneously turned on or off, and there are three kinds of inductance is obtained. The inductance of L1 varies from 0.82 nH to 0.94 nH and that of L2 varies from 0.71 nH to 0.94 nH by the control voltage (Vctrl). The inductance variation is not so high so as to gradually change the oscillation frequency and to avoid the degradation of the phase noise. Thus, by switching the three different kinds of inductance, the coarse turning of the VCO is carried out. The fine turning of the VCO is carried out by turning the varactor in the transformer based inductance and varactors in the capacitor bank.

Figure 2.9: The coupling factor k of inductor L1 and L2.

#### 2.2.2 Switched AMOS Varactors Design

MOS Varactors are based on MOS transistor structures (metal-oxide-semiconductor) and widely used in RF applications [44]. With PN-junction varactors, MOS varactors have a large capacitance per area, tuning range and the ratio of the  $C_{max}/C_{min}$ . The two most important types of MOS varactors are the NMOS and PMOS varactors. The NMOS varactor is the most commonly used varactor in CMOS technology. By varying the voltage between the two terminals (G and D/S), the capacitance of the device changes in accordance with the operating voltage by which it is biased. This device makes use of the gate oxide as dielectric so that the device capacitance is dependent on the capacitance of the charge zone  $(C_{Si})$  and the capacitance of the oxide  $(C_{ox})$ . The total capacitance C of the device is given by [45]:

Figure 2.10: The detail circuit of the transformer based inductors.

Figure 2.11: The three kinds of inductance of the transformer based inductors.

$$C = C_0 W L \tag{2.18}$$

where  $C_0$  is the capacitance per unit of area, which is equal to [46]:

$$C_0 = \left(\frac{1}{C_{ox}} + \frac{1}{C_{Si}}\right)^{-1} \tag{2.19}$$

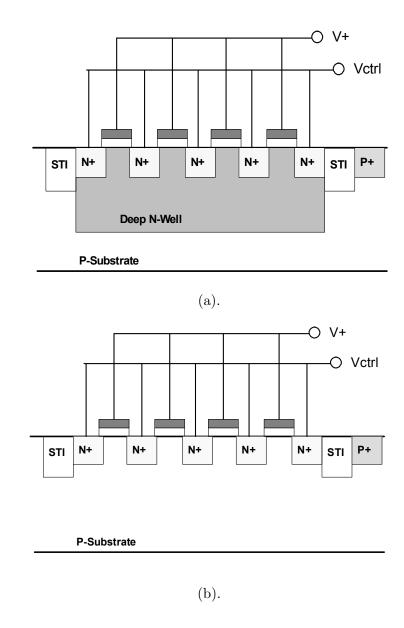

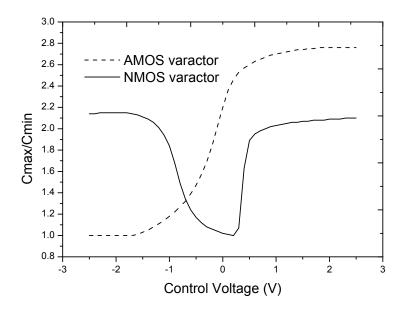

The effective capacitance from MOS Varactors almost three times higher than that of a PN-junction varactor per area [47]. The  $C_{max}/C_{min}$  ratio improves in comparison with that obtained with PN-junction varactors. NMOS varactors have a special operations modes, the accumulation mode which also called AMOS varactor. The difference between the AMOS varactor and the common NMOS varactors lies in the existence of an N well in the channel between the drain and the source in accumulation varactors, the difference of a cross section of an NMOS varactor and AMOS varactor is as shown in Figure 2.12.

Figure 2.12: (a)A cross section of an AMOS varactor. (b) A cross section of an NMOS varactor.

When a positive voltage (Vgs) is applied to the gate of an AMOS varactor, the total capacitance is mainly given by the oxide capacitance  $C_{ox}$ . When this voltage is decreased to negative values, the free electrons are repelled out the channel, generating an empty zone to which a capacitance  $C_{Si}$  is associated. In other words, when positive bias voltages are applied to the gate, the AMOS varactor C is the only capacitance of the varactor is  $C_{ox}$ .

Figure 2.13: The Cmax/Cmin of AMOS varactor and NMOS varactor.

However, when this bias is reduced, it becomes the series of of  $C_{ox}$  and  $C_{Si}$  [47]:

$$C = \frac{C_{ox}C_{Si}}{C_{ox} + C_{Si}} \tag{2.20}$$

Thus, the total capacitance decreased. Commonly, the  $C_{Si}$  is smaller than  $C_{ox}$ , and the variation of the capacitance is large. To compared with the NMOS varactor, the simulation capacitance of both NMOS varactor and AMOS varactor are shown in Figure 2.13. The  $C_{max}/C_{min}$  ratio of NMOS varactor is from 1 to 2.1, while the  $C_{max}/C_{min}$  ratio of AMOS varactor is from 1 to 2.75.

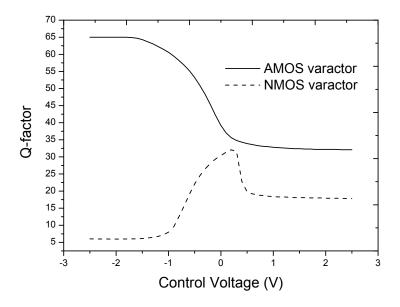

The Q-factors simulation results of the NMOS varactor and AMOS varactor are shown in Figure 2.14. To obtain a improvement in the performance of the two type of varactor, there must be a compromise between capacitance and the quality factor. When Q reaches its maximum point, the capacitance is at its minimum level and vice versa. Compared with the NMOS varactor, AMOS varactor has a high Q-factors. The Q-factors of the NMOS varactor is between 10 and 30, while the Q-factors of the NMOS varactor is between 30 and 70. It is very clear that AMOS varactor has a better performance than

Figure 2.14: The Quality factor of AMOS varactor and NMOS varactor.

#### NMOS varactor.

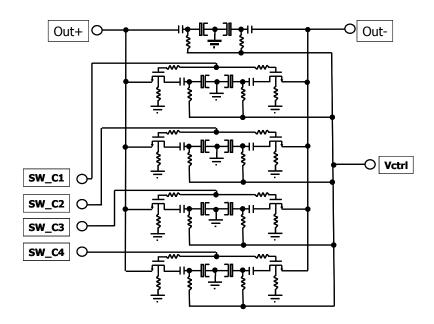

To get a broader turning range, the switched AMOS varactor is used in this design. The schematic of the AMOS varactor bank is shown in Figure 2.15. There are five varactor branches. The gate length and finger width of the unit switching NMOS is 0.11  $\mu$ m and 1000  $\mu$ m, respectively. The AMOS varactor of the first branch has a 30 unite cells, and the AMOS varactor of the other branches has a unite cell of 50. There are five varactor branches: the first branch is always turned on and other branches are selectively turned on using NMOS switches ( $SW_{-}C1$  to  $SW_{-}C4$ ). The control voltage ( $V_{ctrl}$ ) is the same as that for controlling transformer-based variable inductors. Hence, the variable inductors and varactors are simultaneously controlled by  $V_{ctrl}$ .

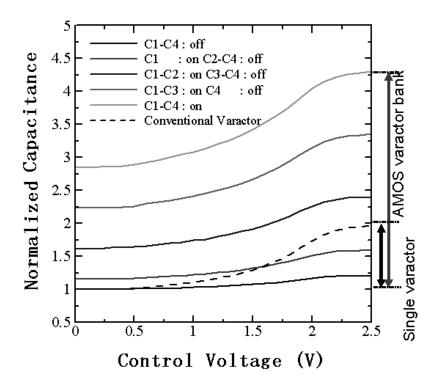

The simulation of the Figure 2.15 is shown in Figure 2.16. To compared with a conventional varactor, a single varactor is also simulated. In a single varactor, the turning range is about 1 to 1.6, however, the varactor bank has a turning range of 1 to 4.2. The varactor bank has a 2.5 times wider turning range than a single varactor.

Figure 2.15: Switched AMOS varactor bank.

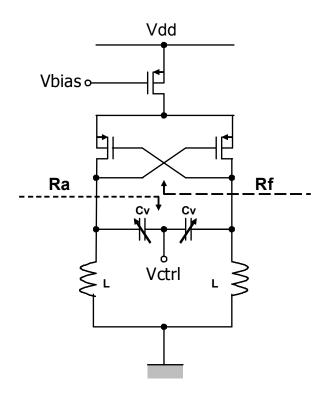

#### 2.2.3 Cross-coupled PMOS Design

The merit of the PMOS transistor compared with the NMOS transistor is the low Flicker noise. A characteristic of the PMOS transistor is shown in the Table 2.2, where fmax is the frequency where the power gain becomes 1 and ft is the frequency where the current gain becomes 1. The fmax is 36.5 GHz and ft is 40.4 GHz. The fmax and ft are large enough for the 1 GHz to 3 GHz VCO design.

The basic PMOS crossing coupling transistor VCO is shown in Figure 2.17. The length of the PMOS transistor is 0.13  $\mu m$  and the width of the PMOS transistor is 10  $\mu m$  \*60 figures.

To guarantee oscillation start-up at all operating temperatures and under worst case process variations, the PMOS transistor should provide enough negative resistance. If Rf is the resistance looking into the differential cross-couple pair of active devices, Ra is the equivalent differential resistance of the frequency selective network (comprised of LC

Figure 2.16: Capacitance turning range comparison.

tank), and gm is the small-signal transconductance of two PMOS transistors. In order to maintain the oscillation:

$$\frac{1}{Rf} + \frac{1}{Ra} < 0 (2.21)$$

and

$$Rf = \frac{2}{gm} \tag{2.22}$$

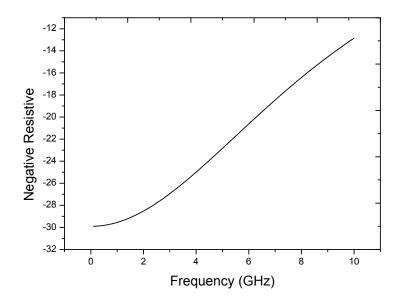

To get enough negative resistance, the bias current is 40 mA for the PMOS crossing coupling transistor and the power supply is 1.5 V. The simulation of the negative resistance is shown in Figure 2.18.

From 0 Hz to 10 GHz, the negative resistance is from -30 to -13  $\Omega$  and the negative resistance is enough for the VCO to start up oscillation in the required bandwidth.

| $W(\mu m)/L(\mu m)$ | 276/ 0.13 |

|---------------------|-----------|

| fmax [GHz]          | 36.5      |

| ft [GHz]            | 40.4      |

| Ids[uA/um]          | 75.7      |

Table 2.2: Wideband VCO Target

Figure 2.17: Basic PMOS crossing coupling transistor VCO.

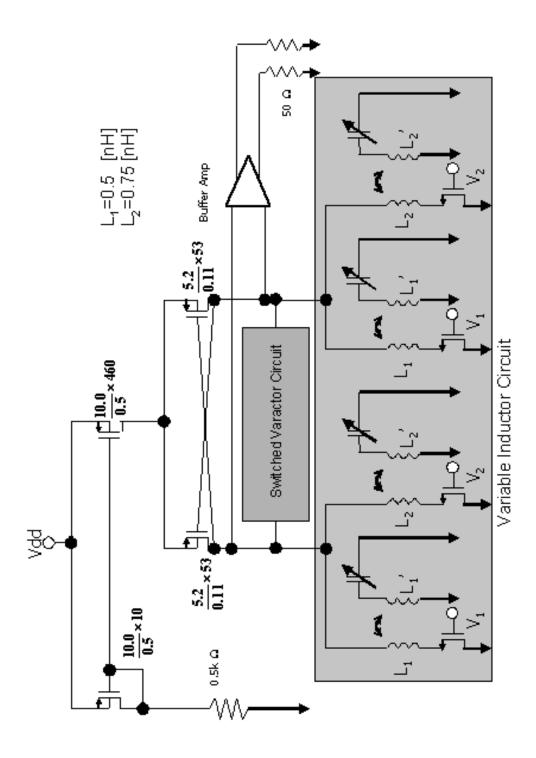

### 2.2.4 VCO Circuit Design

The equivalent circuit of the Proposed VCO is shown in Figure 2.19. In the proposed wideband VCO, the varactor bank is used for the capacitance turning and the transformer based switched variable inductors are used for the inductance turning. The turning voltage of both the varactor bank and the transformer based switched variable

Figure 2.18: The simulation of the negative resistance provides by PMOS crossing coupling transistor .

inductors are the same voltage from the PLL loop after the filter.

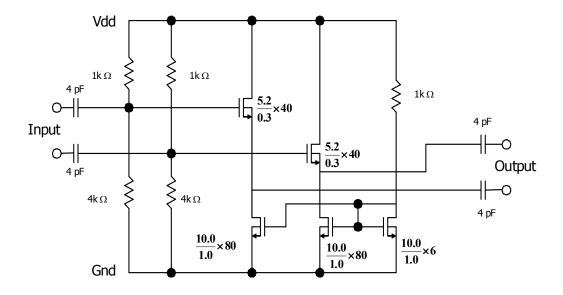

The buffer amplifier is shown in Figure 2.20. The buffer amplifier works as a source follower. The buffer amplifier separates the 50  $\Omega$  load from the LC tank. If the 50  $\Omega$  load is directly connected with the LC tank, the Q-value becomes too low and it affects the phase noise of the VCO. The transistors for the amplifier have a gate length size of 0.3  $\mu$ m and a gate width of 5.2  $\mu$ m by 40 figures. The power supply is 2.5 V and the bias current is 16 mA for each amplifier.

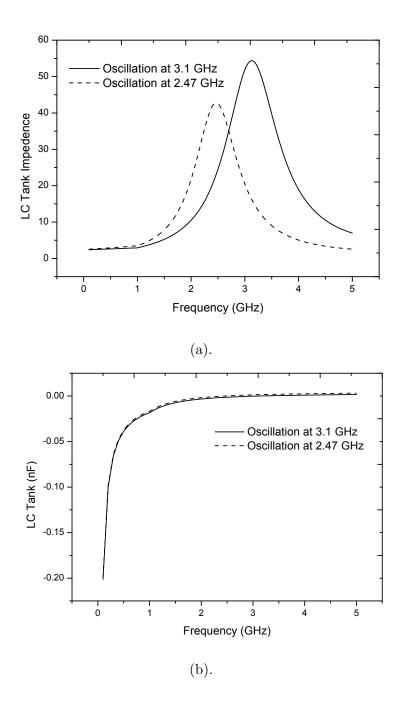

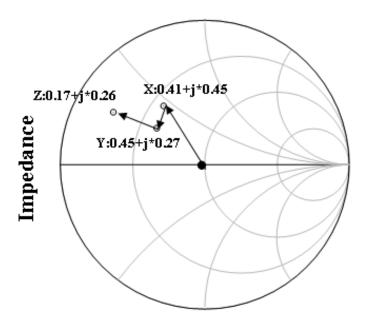

The simulation of the LC tank is carried out at 2.47 GHz and 3.1 GHz, respectively. The impendence and the reactance of the LC tank are showing in Figure 2.21. The impendence is 43  $\Omega$  at the oscillation of 2.47 GHz and 55  $\Omega$  at the oscillation of 3.1 GHz. Compared with the negative resistance as showing in Figure 2.18, the impendence is about -28.4  $\Omega$  at the oscillation of 2.47 GHz and -26.7  $\Omega$  at the oscillation of 3.1 GHz. These conditions satisfy the oscillation start-up criterion as in Equation 2.21. And there is still some margin to deal with the variation of the temperature, process and other factors. The

Figure 2.19: The equivalent circuit of the Proposed VCO.

Figure 2.20: Schematic of the buffer amplifier.

reactance of the LC tank is 0 at the oscillation frequency as showing in Figure 2.21.

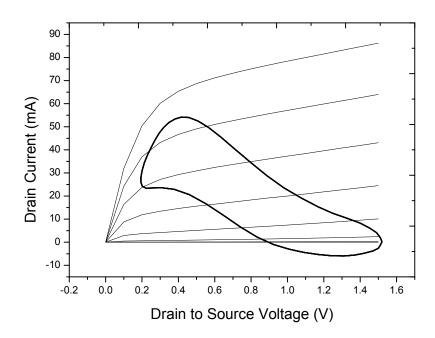

The load line of the PMOS crossing coupling transistors are drawn as showing in Figure 2.22. The loadline is drawn at a control voltage of 1.5 V and the oscillation frequency of 3.1 GHz. As shown in the figure, part of the loadline enters into the negative axis of current. The maximum current is near 53 mA and the minimal current is near -8 mA. It implies the PMOS crossing coupling transistors work in the Class-AB state and there is no waste of the quiescent bias current.

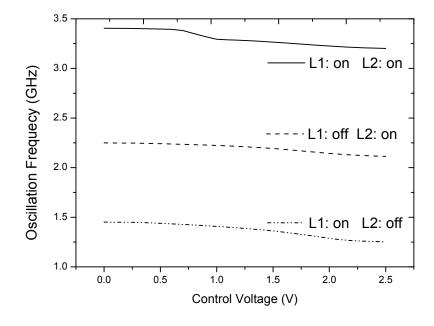

To show the coarse turning of the transformer based inductor, the simulation is carried out in Figure 2.23. The solid line shows the calculated oscillation frequencies when both L1 and L2 are turned on and the first AMOS branch is only turned on. This condition is for obtaining highest oscillation frequency. The broken line shows the frequencies when L1 is turned off and L2 are turned on and the first AMOS branch is only turned on. The dotted line shows frequencies when L1 is turned on and L2 is turned off with all AMOS varactor branches are turned on. This condition gives the lowest oscillation frequency. By selectively turning the AMOS varactor branches on, it is expected that the VCO generates

Figure 2.21: (a) The impedance of the LC tank at the oscillation frequency. (b) The reactance of the LC tank at the oscillation frequency.

continuous oscillation frequencies.

In Figure 2.24 illustrates the detail simulated oscillation frequencies of the VCO

Figure 2.22: The loadline of the PMOS crossing coupling transistors

Figure 2.23: The coarse turning of the transformer based inductor.

Figure 2.24: Simulated oscillation frequency tuning range.

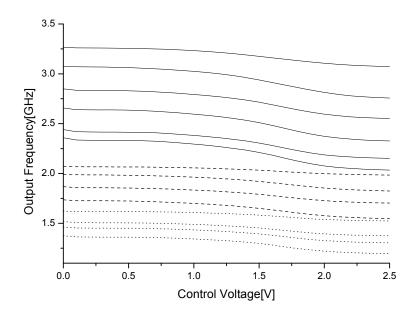

IC. The oscillation frequency is expected to be from 1.25 GHz to 3.45 GHz. For the four AMOS varactor banks C1-C4, they can be expressed by a four bit binary code, where "1" indicates the bank is on and "0" indicates the bank is off. The solid lines show the simulated oscillation frequencies when both  $L_1$  and  $L_2$  are turned on while the AMOS varactors are selectively turned on as "1000", "0100", "0010", "1100", "1110", "1111". The broken lines show the oscillation frequencies when only  $L_2$  is turned on while the AMOS varactors are selectively turned on as "1000", "1100", "1110", "1111". The dotted lines show oscillation frequencies when only  $L_1$  is turned on while the AMOS varactors are selectively turned on as "1000", "1110", "1111". By selectively turning on the variable inductors and AMOS varactor branches, the VCO is expected to generate continuous oscillation frequencies from 1.25 GHz to 3.45 GHz.

Figure 2.25: Photograph of the fabricated VCO IC.

Figure 2.26: The measured inductance of the transformer D116N2W10.

Figure 2.27: The measured inductance of the transformer D140N2W10.

Figure 2.28: The measured coupling coefficient.

Figure 2.29: Measured oscillation frequency tuning range.

# 2.3 Experiment Results

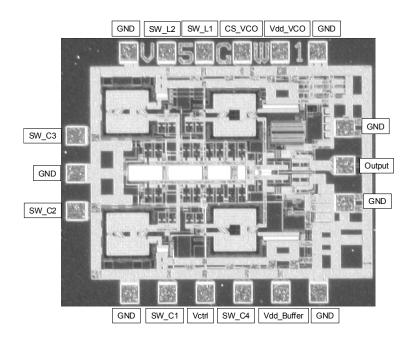

The proposed VCO IC is implemented in the 0.11  $\mu m$  CMOS process. Figure 2.25 shows a photograph of the fabricated VCO IC. The VCO IC size is 0.65 mm by 0.9 mm.

The VCO IC measurement is carried out with on-wafer probes. The measured inductance value is show in Figure 2.26 and 2.27. The inductance of the primary stage of transformer D116N2W10 is from 0.72 nH to 0.9 nH and the inductance of the secondary stage of it is from 1.6 nH to 2.5 nH. The inductance of the primary stage of transformer D140N2W10 is from 0.82 nH to 0.68 nH and the inductance of the secondary stage of it is from 1.15 nH to 1.3 nH. The measured effective coupling factor k results are shown in 2.28.

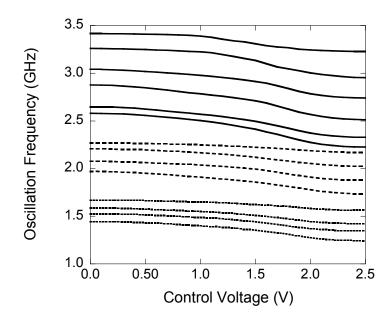

The dependence of the measured frequency tuning range on the control voltage is illustrated in Figure 2.29. Continuous oscillation frequency from 1.20 GHz to 3.27 GHz is obtained. Thus, a frequency tuning range as high as 92.6~% has been realized with a center frequency of 2.23 GHz. The measured oscillation frequencies agree well with the expected

Figure 2.30: Measured output power of the proposed VCO IC.

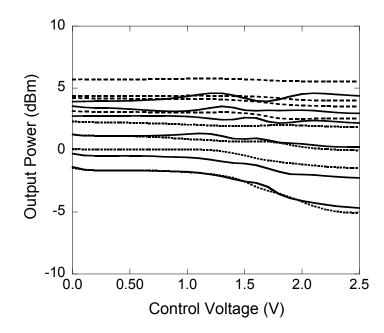

ones. The measured output power is from -5.1 dBm to +5.7 dBm over the frequency range from 1.20 GHz to 3.27 GHz, as shown in Figure 2.30. For each switched inductor, the output powers reduce as the output frequency decreases because the Q-factors decrease as the number of switch-on variator banks increases.

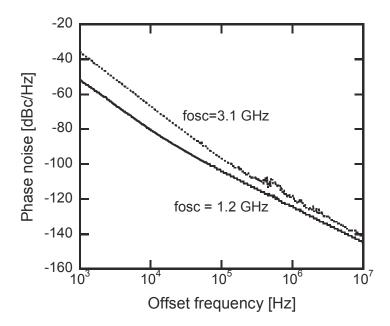

In Figure 2.29 and Figure 2.30, the solid lines show measured results when both  $L_1$  and  $L_2$  are turned on and AMOS varactors are selectively turned on. The broken lines show those when only  $L_2$  is turned on, and dotted lines shows those when  $L_1$  is turned on. As shown in Figure 2.29, course tuning is realized by switching inductors and AMOS varactors, and fine tuning is achieved by changing bias voltage (control voltage) to the AMOS varactors and variable inductors ( $C_V$  in Figure 2.4). It is estimated that a VCO with no  $C_V$  in Fig.2 has a tuning range of around 85%. Thus, a contribution of changing inductance to the tuning range is around 8%. The phase noise measurements are performed on Agilent signal source analyzer E5052B. Figure 2.31 illustrates measured phase noise curves of the VCO at oscillation frequencies of 1.2 GHz (solid line) at a control

Figure 2.31: Measured phase noise performance of the proposed VCO IC at 1.2 GHz (solid line) and 3.1 GHz (dotted line).

voltage of 2.5V and 3.1 GHz (dotted line) at a control voltage of 1.5V, respectively. The measured phase noises at 1 MHz offset from the carriers are -120 dBc/Hz at 3.1 GHz and -123 dBc/Hz at 1.2 GHz, respectively. The measured phase noises at offset frequencies from 1 KHz to 100 KHz at 3.1 GHz carrier (dotted line) is around 10 dBc/Hz higher than those at 1.2 GHz carrier (solid line). This phenomenon is mainly caused by low quality factor of the switched variable inductors, because this oscillation condition is obtained by turning on two transformer-based inductors ( $L_1$  and  $L_2$  in Fig.2) simultaneously. At the oscillation condition of 1.2 GHz, only  $L_1$  is turned on, and the quality factor of  $L_1$  is higher than that of the parallel connection of  $L_1$  and  $L_2$ .

Table 2.3 summarizes the performance of the proposed VCO IC and recently reported wideband VCOs using CMOS technologies. The VCO IC proposed in this paper exhibits an ultra-wideband tuning range with excellent phase noise.

Table 2.3: Summary of the proposed VCO IC and comparison with recently reported wideband VCOs

| Reference        | This work            | [50]                 | [51]                 | [52]                 | [53]                 |

|------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Technology       | $0.13~\mu\mathrm{m}$ | $0.13~\mu\mathrm{m}$ | $0.13~\mu\mathrm{m}$ | $0.13~\mu\mathrm{m}$ | $0.18~\mu\mathrm{m}$ |

| CMOS             |                      |                      |                      |                      |                      |

| Supply voltage   | 1.5 V                | 1.2 V                | 1.0 V                | 1.0 V                | 1.8 V                |

| Center frequency | 2.2 GHz              | 4.15 GHz             | 5.2 GHz              | 4.3 GHz              | 1.39 GHz             |

| Tuning range     | 92.6 %               | 50.6 %               | 69%                  | 58.7 %               | 66.6 %               |

| Phase noise      | -120 dBc             | -118 dBc             | -118 dBc             | -120 dBc             | -127 dBc             |

| @1 MHz           | @ 3.1 GHz            | @ 4 GHz              | @ 4.6 GHz            | @ 3 GHz              | @ 1.7 GHz            |

# 2.4 Summary

In this chapter, the limitation of the wideband VCO design is analyzed, firstly, Because of the limitation of the capacitor bank, the switched transformer-based switched variable inductors are proposed. The proposed novel ultra-wideband VCO IC has been demonstrated using 0.11  $\mu$ m CMOS technology. By simultaneously controlling transformer-based switched variable inductors and switched AMOS varactors, a continuous frequency oscillation from 1.20 GHz to 3.27 GHz was realized. The frequency tuning range is as high as 92.6 % with a center frequency of 2.23 GHz. The measured phase noises at 1 MHz offset from the carriers are -120 dBc/Hz at 3.1 GHz and -123 dBc/Hz at 1.2 GHz, respectively.

# Chapter 3

# High Linearity and High Efficiency PA IC

#### 3.1 Overview

In some wireless standards, such as GSM, where the modulated signal has constant envelope, a nonlinear PA can be used. A nonlinear PA generally has higher efficiency than a linear PA. However, with their higher efficiency, the data that these transceivers can transmit within a given bandwidth are quite low. In order to increase the data rate and get the high speed without increasing the bandwidth, a more spectrally efficient linear modulation scheme must be used as in Table 3.1. The use of the linear modulation makes the signal envelop has a much higher Peak to Average Ratio (PAR) and the PA has to back off several dBs from P1dB to satisfy the demanding specifications of Adjacent-channel Power Ratio (ACPR) and Error Vector Magnitude (EVM). However, in this case, the PA works in an ultra low efficiency state, and a large of the power consumption is wasted. To deal with this problems, the linearization technique is used for PA. The linearization technique can improve the linearity of the PA and operating with a less back-off from P1dB. Thus, the PA can work near the P1dB with a higher efficiency and more effective. Designing an effective linearization technique is quite important for PA in linear modulation system.

| System    | Bandwidth(MHz) | Modulation | PAR(dB) | Antenna Power(dBm) |

|-----------|----------------|------------|---------|--------------------|

| EDGE      | 0.20           | 8PSK       | 3.2     | 27                 |

| UMTS      | 3.84           | HPSK       | 3.5-7   | 24                 |

| cdma2000  | 1.23           | HPSK       | 4-9     | 24                 |

| 802.11b   | 11             | QPSK       | 3       | 20                 |

| 802.11a/g | 18             | OFDM       | 6-17    | 20                 |

| DSRC      | 2              | QPSK       | 4       | 12                 |

Table 3.1: Summary of wireless communication system with PAR

The research of the linearization technique is very attractive in these years. Many CMOS linear PAs were reported to realize high linearity in [54]-[62]. The linearization technique by suppressing the harmonic generated from the nonlinear source of transconductance  $g_m$  and gate-source capacitance  $c_{gs}$  is reported in [54]. The  $c_{gs}$  compensation is reported in [55],[56] and  $g_{m3}$  (the 3rd-order derivative of the dc transfer characteristic) canceling by multigated transistor (MGTR) is reported in [57] for linearization of the CMOS PA. Besides the above transistor level linearization, there are many system level linearizations, such as envelope elimination and restoration (EER) [58], digital predistortion [59], Doherty [59] and envelope tracking [62].

Dedicated Short Range Communication (DSRC) is being seriously considered as a promising wireless technology for enhancing transportation safety and highway efficiency. It also promises a proposed solution for the automatic debiting of vehicles in an electronic toll collection (ETC) system with a carrier frequency of 5.8 GHz, which makes a revolution in traffic charging without disturbing the traffic flow. The modulation of the DSRC-based ETC system is Amplitude Shift Keying (ASK) or Quadrature Phase Shift Keying (QPSK) with a peak-to-average power ratio (PAR) of 2 dB to 4 dB. Therefore, high linearity PA design is necessary for DSRC application. However, many linearization techniques sacrifice the power efficiency to obtain some improvement in linearity. The PAEs of the linearized

PAs operating during 5 GHz to 6 GHz are always below 25% at P1dB. Thus, a linearization technique with high linearity improvement and high efficiency is considered quite critical for modern linearity PA design.

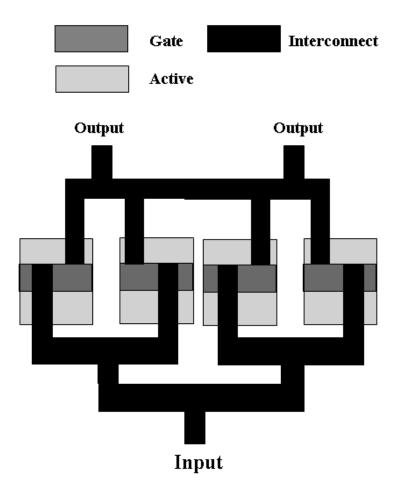

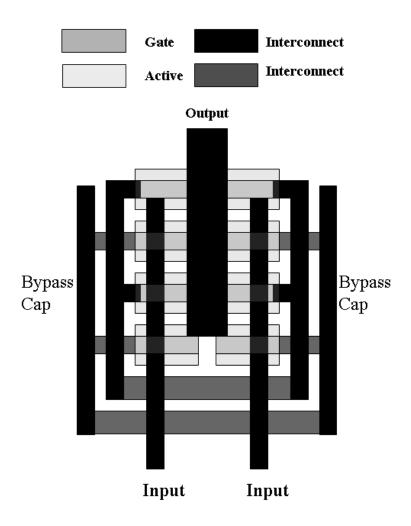

In this paper, a novel multi-cascode CMOS PA with post-linearization technique is proposed for the 5.8 GHz DSRC application. The post-linearization technique is dedicated for CMOS cascode PA, which is usually used to boost output power to overcome the poor device reliability and ruggedness problems [63]. Post-linearization is used to linearize LNA in [64]-[65]. However, it is only limited in LNA application and no application in PA is invested. In this paper, the principle analysis of the proposed novel multi-cascode PA with post-linearization is described with Volterra Series. To verify the effectiveness of proposed post-linearization technique, the novel CMOS PA is designed and fabricated. The measurement results demonstrate the proposed idea.

## 3.2 Multicascode PA Design

#### 3.2.1 Transconductance Nonlinearity in Conventional Cascode PA

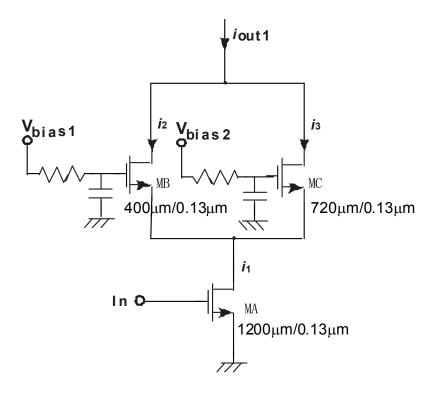

Figure 3.1 shows a conventional cascode PA and its simplified small signal AC equivalent circuit. The distortion of the cascode PA is the total distortion from the common source stage and common gate stage. The analysis is simplified and the result is also simplified in order to demonstrate the principle of the post-linearization technique.

In the cascode PA, the drain current can be expressed in terms of the gate-source voltage around the bias point by the power series expansion in limited third degree as [66]:

$$i_{outa} = g_{a1}v_{ga} + g_{a2}v_{ga}^2 + g_{a3}v_{ga}^3 (3.1)$$

$$i_{out} = g_{b1}v_{gb} + g_{b2}v_{gb}^2 + g_{b3}v_{gb}^3 (3.2)$$

where  $g_{ai}$  and  $g_{bi}$  are the ith-order derivative of the dc transfer characteristic of common source and common gate stage, respectively.

Figure 3.1: A conventional cascode PA and its simplified small signal AC equivalent circuit.

Let the excitation is:

$$v_s = \frac{1}{2} \sum_{q=-Q}^{Q} \exp(j\omega_q t) \tag{3.3}$$

where Q implies the excitation frequency and it is not equal to zero.

The  $v_{gb}$  can be expressed in a limited third order as:

$$v_{ab} = v_{ab1} + v_{ab2} + v_{ab3} (3.4)$$

where  $v_{gb1}$ ,  $v_{gb2}$  and  $v_{gb3}$  are the first, second and third orders of the response to the common source current.  $i_{out}$  can also be expressed in limited third order as:

$$i_{out} = i_{out1} + i_{out2} + i_{out3}$$

(3.5)

where  $i_{out1}$ ,  $i_{out2}$  and  $i_{out3}$  are the first, second and third orders of the corresponding response to  $v_{qb}$ .

Using Kirchhoff's Voltage Law for the input loop analysis,  $v_{ga}$  can be obtained as:

$$v_{ga} = \frac{1}{2} \sum_{q=-Q}^{Q} \frac{1}{j\omega_q c_{ga} z_{in} + 1} exp(j\omega_q t)$$

(3.6)

Let

$$v_{ga} = \frac{1}{2} \sum_{q=-Q}^{Q} H_0(\omega_q) exp(j\omega_q t)$$

(3.7)

where

$$H_0(\omega) = \frac{1}{j\omega_q c_{ga} z_{in} + 1} \tag{3.8}$$

The current excitations from the common source stage are discussed according to the orders. For the first order current  $g_{a1}v_{ga}$  from the common source stage: by using Kirchhoff's Current Law for the source node of cascode stage,  $v_{qb1}$  can be written as:

$$v_{gb1} = \frac{1}{2} \sum_{q=-Q}^{Q} H_1(\omega_q) exp(j\omega_q t)$$

(3.9)

where

$$H_1(\omega) = \frac{g_a}{j\omega c_{gb} + g_{b1}} \cdot \frac{1}{j\omega c_{ga} z_{in} + 1}$$

(3.10)

Thus, the first order current  $i_{out1,1st}$  from excitation of  $g_{a1}v_{ga}$  can be obtained as:

$$i_{out1,1st} = \frac{g_a}{2} \sum_{q=-Q}^{Q} H_1(\omega_q) exp(j\omega_q t)$$

(3.11)

By using nonlinear current analysis,  $i_{out2,1st}$  and  $i_{out3,1st}$  can be expressed as:

$$i_{out2,1st}$$

$$= \frac{g_a}{4} \sum_{q_1 = -Q}^{Q} \sum_{q_2 = -Q}^{Q} \left( \left\{ \frac{j(\omega_{q_1} + \omega_{q_2}) c_{g_b} g_{b_2}}{j(\omega_{q_1} + \omega_{q_2}) c_{g_b} + g_{b_1}} H_1(\omega_{q_1}) \right.$$

$$H_1(\omega_{q_2}) exp[j(\omega_{q_1} + \omega_{q_1})t] \right\}$$

(3.12)

and

$$i_{out3,1st} = \frac{1}{8} \sum_{q1=-Q}^{Q} \sum_{q2=-Q}^{Q} \sum_{q3=-Q}^{Q} \left\{ \left( \frac{-2g_{b2}^{2}}{j(\omega_{q1} + \omega_{q2} + \omega_{q3})c_{gb} + g_{b1}} + g_{b3} \right) \right.$$

$$H_{1}(\omega_{q1})H_{1}(\omega_{q2})H_{1}(\omega_{q3})exp\left[ j \sum_{j=1}^{3} \omega_{qj}t \right] \right\}$$

(3.13)

Usually,  $g_{b1}$  is much larger than  $c_{gb}$  to get a desired voltage gain. Therefore,  $c_{gb}$  is negligible compared with  $g_{b1}$ .

Thus, for two excitation frequencies, where Q=2, the terms of  $\omega = 2\omega_1 - \omega_2$  can be obtained as:

$$i_{out3,1st}(2\omega_1 - \omega_2) = \frac{3}{8}(g_{b3} - \frac{2g_{b2}^2}{g_{b1}})H_1(\omega_1)H_1(\omega_1)$$

$$\cdot H_1(-\omega_2)exp[j(2\omega_1 - \omega_2)t]$$

(3.14)

For the second order current  $g_{a2}v_{ga}^2$  from the common source stage,  $v_{gb1}$  can be obtained by using Kirchhoff's Current Law for the source node of cascode stage, and it can be written as:

$$v_{gb1}$$

$$= \frac{1}{4} \sum_{q_1 = -Q}^{Q} \sum_{q_2 = -Q}^{Q} \left( \left\{ \frac{g_{a2}}{j(\omega_{q_1} + \omega_{q_2})c_{gb} + g_{b1}} H_0(\omega_{q_1}) \right\} \right)$$

$$H_0(\omega_{q_2}) exp[j(\omega_{q_1} + \omega_{q_1})t] \}$$

(3.15)

and the corresponding current is

$${}^{l_{out1,2st}} = \frac{g_{b1}}{4} \sum_{q_1 = -Q}^{Q} \sum_{q_2 = -Q}^{Q} \left( \left\{ \frac{g_{a2}}{j(\omega_{q_1} + \omega_{q_2})c_{g_b} + g_{b_1}} H_0(\omega_{q_1}) \right. \right.$$

$$\left. H_0(\omega_{q_2}) exp[j(\omega_{q_1} + \omega_{q_1})t] \right\}$$

(3.16)

This part only generates even order current and the higher orders for the excitation of the second order current  $g_{a2}v_{ga}^2$  generate fourth and sixth orders signal. Thus, they have no effect on the third order distortion.

For the third order current  $g_{a3}v_{ga}^3$  from the common source stage,  $v_{gb1}$  can be obtained as:

$$v_{gb1}$$

$$= \frac{1}{8} \sum_{q1=-Q}^{Q} \sum_{q2=-Q}^{Q} \sum_{q3=-Q}^{Q} \left\{ \left( \frac{g_{a3}}{j(\omega_{q1} + \omega_{q2} + \omega_{q3})c_{gb} + g_{b1}} \right) \right.$$

$$H_0(\omega_{q1}) H_0(\omega_{q2}) H_0(\omega_{q3}) exp[j \sum_{j=1}^{3} \omega_{qj} t] \right\}$$

(3.17)

Thus, the corresponding current is

$$i_{out3,3th}$$

$$= \frac{1}{8} \sum_{q_1 = -Q}^{Q} \sum_{q_2 = -Q}^{Q} \sum_{q_3 = -Q}^{Q} \left\{ \left( \frac{g_{a_3} g_{b_1}}{j(\omega_{q_1} + \omega_{q_2} + \omega_{q_3}) c_{g_b} + g_{b_1}} \right) \right.$$

$$H_0(\omega_{q_1}) H_0(\omega_{q_2}) H_0(\omega_{q_3}) exp[j \sum_{j=1}^{3} \omega_{q_j} t] \right\}$$

(3.18)

The other high orders generated from third order current  $g_{a3}v_{ga}^3$  are above six orders and they are neglected.

For two excitation frequencies, where Q=2, the terms of  $\omega=2\omega_1-\omega_2$  can be obtained as:

$$i_{out3,3th}(2\omega_1 - \omega_2) = \frac{3}{8} \frac{g_{a3}g_{b1}}{(2\omega_1 - \omega_2)c_{gb} + g_{b1}}$$

$$H_0(\omega_1)H_0(\omega_1)H_0(-\omega_2) \cdot exp[j(2\omega_1 - \omega_2)t]$$

(3.19)

Thus, the nonlinearity in the total cascode PA is the total third order distortion from Equation.3.14 and Equation.3.19.

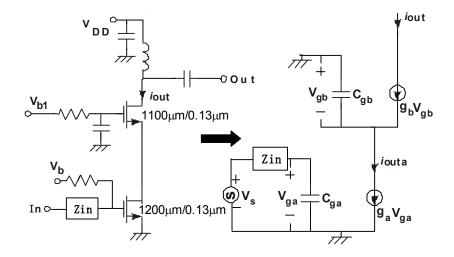

#### 3.2.2 Principle Analysis of the Proposed Technique

The nonlinearity in the total cascode PA is the total third order distortion from Equation.3.14 and Equation.3.19. The Equation.3.14 expresses the nonlinearity from common gate stage and Equation.3.19 expresses the nonlinearity from common source stage. In the cascode PA,  $g_{a1}$  is very large to get a large gain in the common source stage, and  $g_{b1}$  is small because the gate of the common gate stage isn't shorted to ground by a large bypass capacitor. Thus,  $H_1(\omega)$  is much larger than  $H_0(\omega)$ , and the nonlinearity generated in the common gate stage is much larger than that in common source gate. In this paper, the proposed technique is focused on the distortion canceling, which is mainly generated in common gate stage as shown in Equation.3.14.

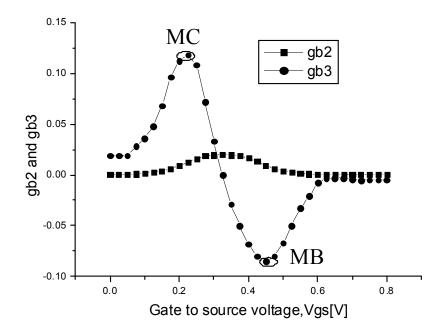

There are two parts contributing the nonlinear current from Equation. 3.14, and

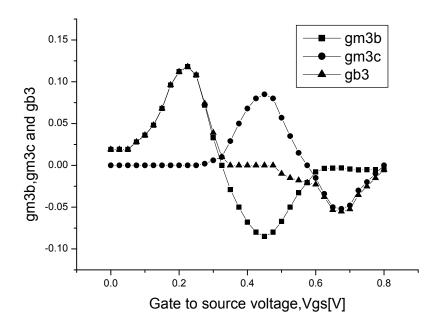

Figure 3.2:  $g_{b2}$  and  $g_{b3}$  in a NMOS transistor.

the first part of nonlinear current is:

$$i_{out3}(2\omega_1 - \omega_2) = \frac{3}{8}g_{b3}H_1(\omega_1)H_1(\omega_1)H_1(-\omega_2)$$

$$\cdot exp[j(2\omega_1 - \omega_2)t]$$

(3.20)

This part is directly contributed by the nonlinearity of  $g_{m3}$ . The second part of nonlinear current is:

$$i_{out3}(2\omega_1 - \omega_2) = -\frac{3}{4} \frac{g_{b2}^2}{g_{b1}} H_1(\omega_1) H_1(\omega_1) H_1(-\omega_2)$$

$$\cdot exp[j(2\omega_1 - \omega_2)t]$$

(3.21)

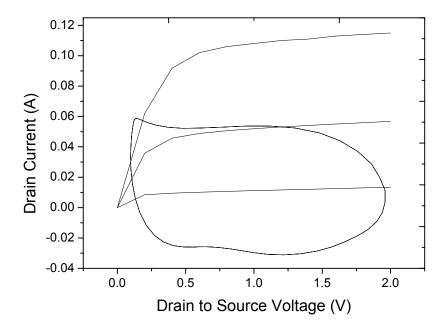

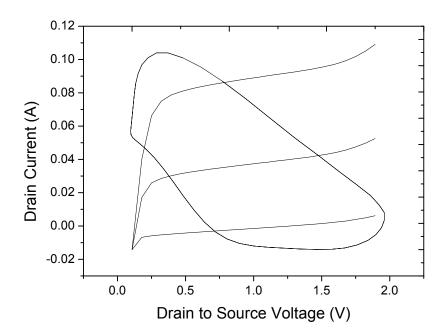

This part is generated by mixing the current of the fundamental frequency and the second harmonic frequency. The second part is normally small compared with the first part because of the small  $g_{b2}$  compared with  $g_{b3}$  as shown in Figure.3.2. The transconductance of common gate transistor is obtained by fixing the gate voltage and sweeping the voltage

Figure 3.3: Proposed multi-cascode transistor with post-linearization technique.

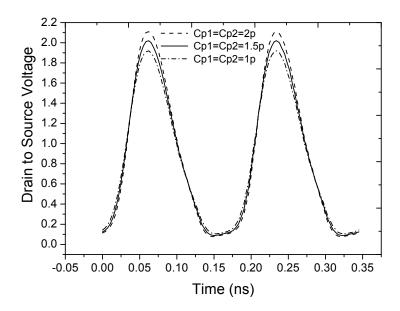

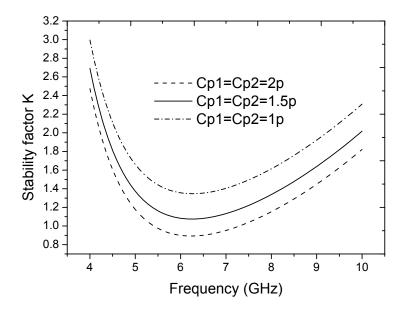

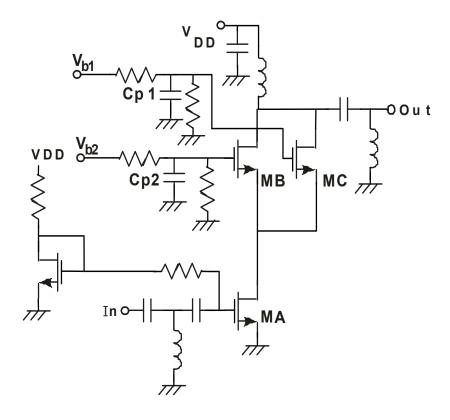

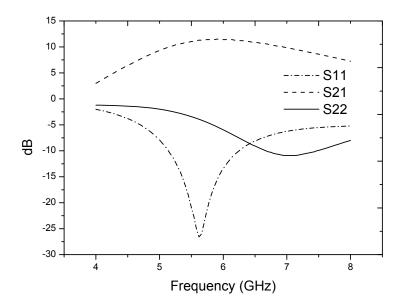

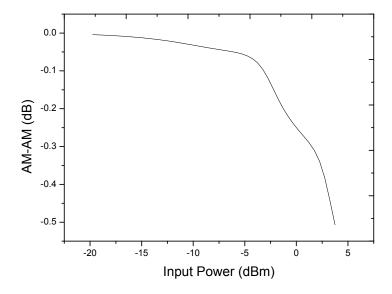

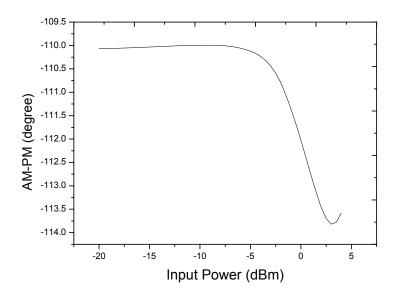

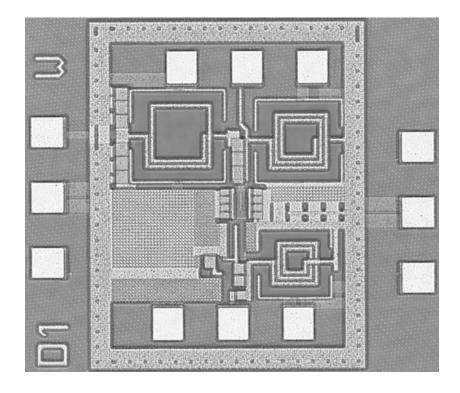

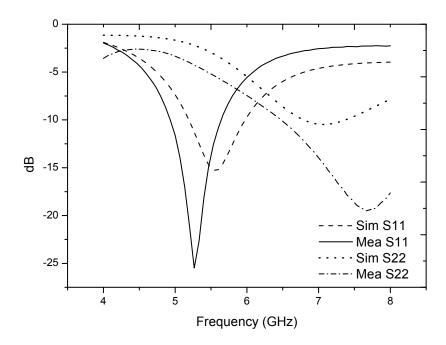

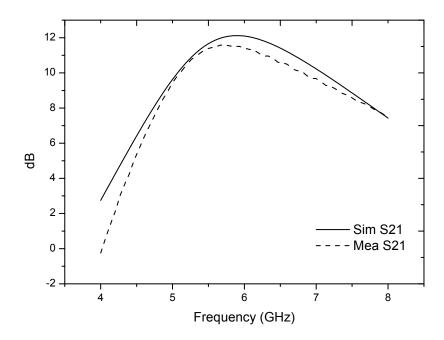

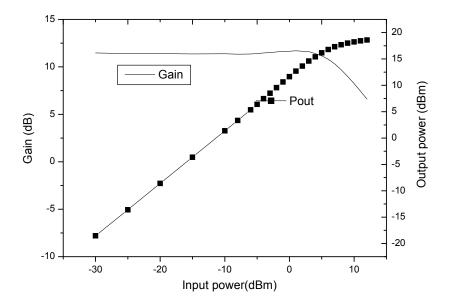

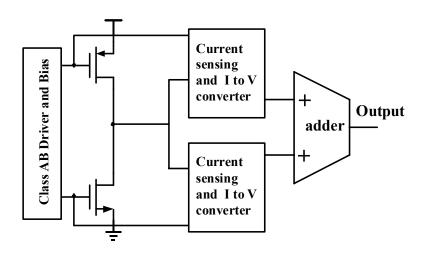

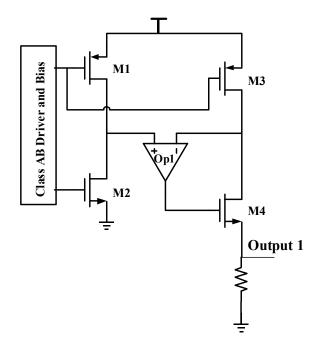

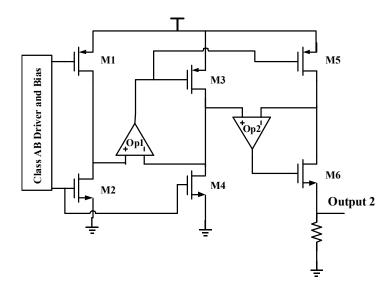

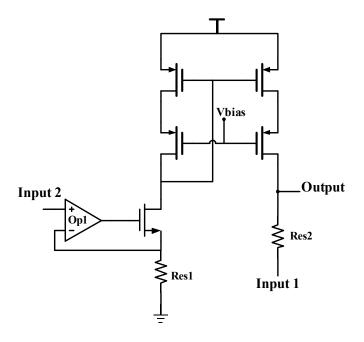

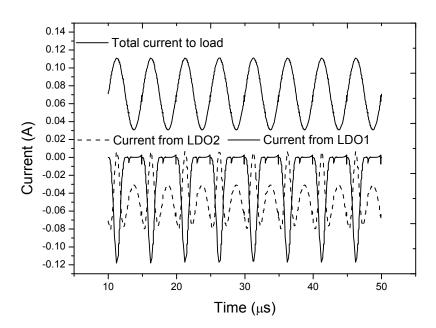

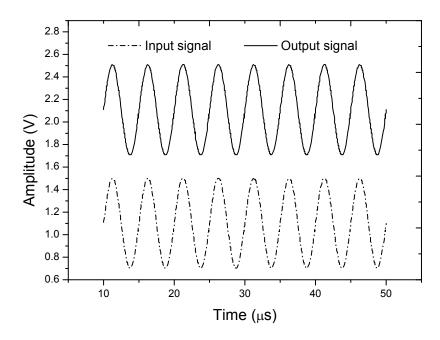

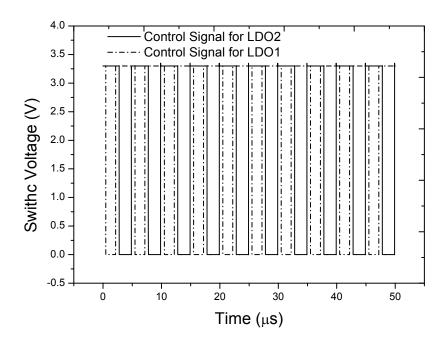

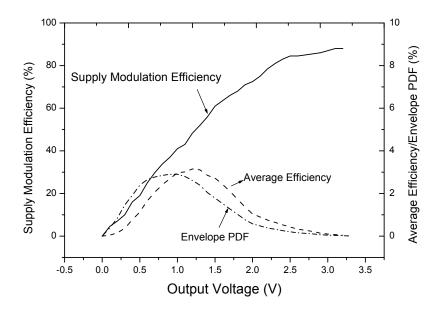

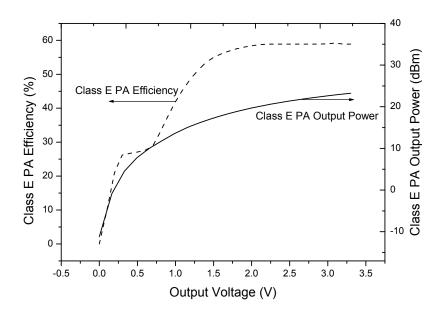

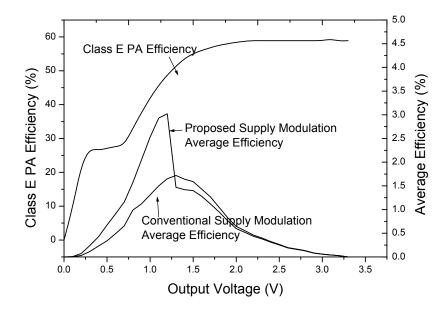

in the source. The  $g_{b2}$  is the differential of transconductance and  $g_{b3}$  is the differential of  $g_{b2}$ . It is assumed that the  $\omega = 2\omega_1 - \omega_2$  nonlinear current is only contributed by the first part. If the  $\omega = 2\omega_1 - \omega_2$  nonlinear current becomes zero, the IMD generated by the cascode stage is also zero and eliminated. Therefore, in this paper, a novel multi-cascode post-linearization technique is proposed to cancel the nonlinearity current at  $\omega = 2\omega_1 - \omega_2$ . The simplicity of the proposed circuit is shown in Figure.3.3.