# Low Complexity Hardware Oriented H.264/AVC Motion Estimation Algorithm and Related Low Power and Low Cost Architecture Design

#### HUANG, Yiqing

Graduate School of Information, Production and Systems

Waseda University

February 2010

#### Abstract

The ever increasing bit-rate on network applications such as broadcasting digital television makes storage capacity larger than ever before. Especially, the advent of Super Hi-Vision (SHV) which has feature of high resolution further intensifies the tough situation. Since limitation exists in network bandwidth and disk storage, the video compression technique is becoming more important than before. As the latest video coding standard, H.264/AVC can provide superior performance to previous standards. However, it also consists of huge complexity. When ASIC (Application Specific Integration Circuits) based real-time hardware system is considered, the intensive complexity in H.264/AVC will cause problems in hardware cost and power consumption. Therefore, to solve the problem, this dissertation focuses on two key issues which are low complexity hardware oriented algorithm and its related architecture.

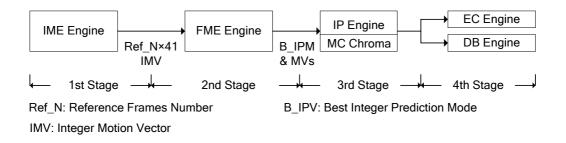

In H.264/AVC based system, motion estimation (ME) which is the major part of inter prediction is the most significant component. It consists of integer ME (IME) and fractional ME (FME) and occupies almost 90% computation, which makes it a must to divide IME and FME into two separate stages in real-time hardwired encoder. Besides motion estimation part, hardware engine of intra prediction is another time consuming part because of its abundant prediction modes. Moreover, the rate distortion based mode decision part which makes a final judgment of inter and intra modes also consumes lot of computation in the final stage of whole encoding system. Many software based fast algorithms have already been proposed to release complexity of H.264/AVC based system. However, most of these algorithms can not be efficiently realized in hardware because of constraints in hardware design. In hardware, factors such as predictable data flow, regular access of memory and full hardware utilization are important to the whole system's performance. Without considering these factors, hardware cost, throughput and power consumption will increase greatly. So, hardware oriented low complexity algorithm and related low cost and low power hardware architecture are important issues to H.264/AVC based real-time encoder design.

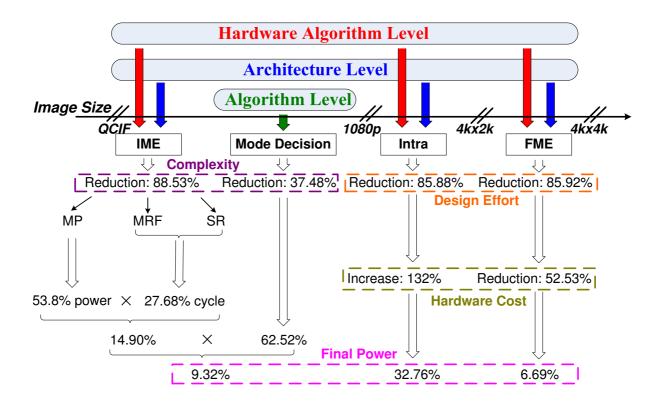

Based on analysis of existing works and current problem, this dissertation mainly

targets on low cost and low power H.264/AVC real-time hardwired encoder. In detail, it focuses on IME, FME, intra and mode decision, which are four computation intensive parts in H.264/AVC based system. Firstly, low complexity algorithm which follows hardware data flow is proposed. Secondly, based on proposed algorithm, flexible and highly parallel architectures are given out. Moreover, architecture and circuit optimizations are proposed to further reduce the hardware cost and power consumption.

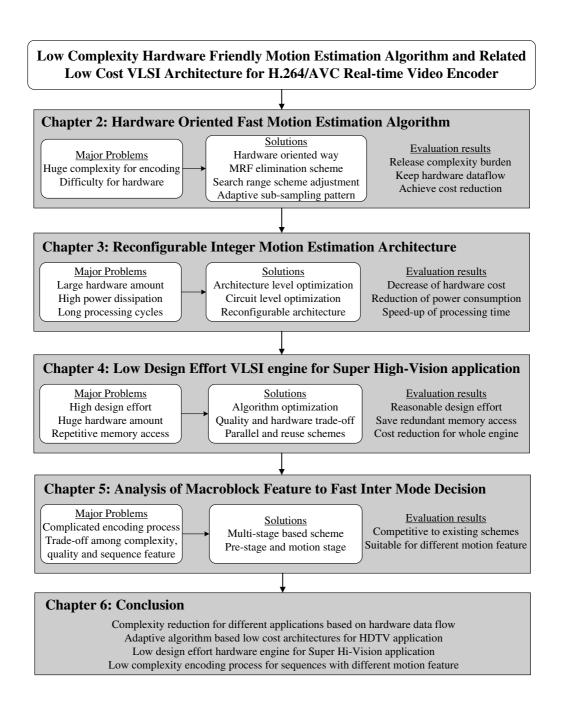

The whole dissertation consists of 6 chapters as follows.

In the first chapter, introduction in video compression field is given out. The development and feature of video coding standards and emphasis of this dissertation are described in detail.

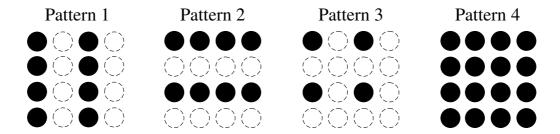

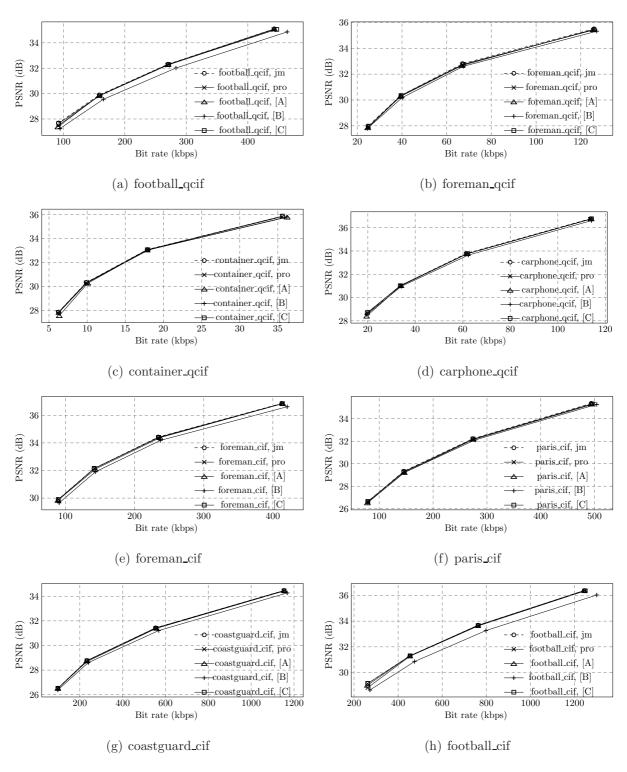

In the second chapter, hardware oriented low complexity motion estimation algorithms are given out. The complexity reduction is achieved in MRF, search range and matching pattern of H.264/AVC based system. Firstly, for MRF technique, gradient and block matching information are used for fast MRF algorithms. The proposed algorithms release the MRF complexity according to macroblock (MB) features in spatial and temporal domains. Secondly, based on the statistical analysis, it is shown that motion feature is conformity across several frames and search range can be adaptive adjusted according to the motion feature of MB. So, two proposals of search range adjustment is given out in this dissertation. For MB with extreme small motion, search range is restricted into 1/8 of original value. For MB with other cases, the search range is adjusted recursively according to the motion feature of MB on previous frame. Thirdly, since pixel difference can reflect spatial feature of current MB, it is used to classify matching pattern of ME process. An pixel difference based adaptive sub-sampling scheme is proposed, which uses three hardware oriented patterns for MB with different spatial features. By combining all the proposed schemes, the overall algorithm can achieve up to 95.72% complexity reduction with average 0.072dB PSNR loss and 0.902% bit-rate increase based on hardware data flow.

In the third chapter, two flexible IME architectures for adaptive sub-sampling algorithm, namely adaptive propagate partial SAD (APPSAD) and reconfigurable SAD Tree (RSADT), are proposed. By using configurable SAD, the proposed RSADT architec-

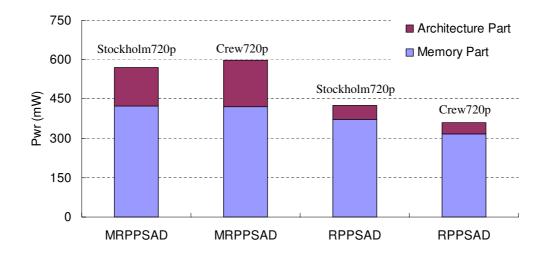

ture achieves data organizations in both architectural and memory level, which speeds up processing time and saving power consumption. For APPSAD, the original processing element (PE) is expanded into four different types. According to different matching patterns, only the related type of PE is enabled and power consumption of other types of PE can be saved. Moreover, circuit optimization is applied on both APPSAD and RSADT are optimized. The propagation chain, original PE and adder trees are simplified, with no redundant registers and adders. So, hardware cost and power consumption are further reduced. With TSMC 0.18um CMOS library, it is shown that the proposed architectures can achieve 61.71% saving of processing cycles and up to 39.8% power reduction of existing works.

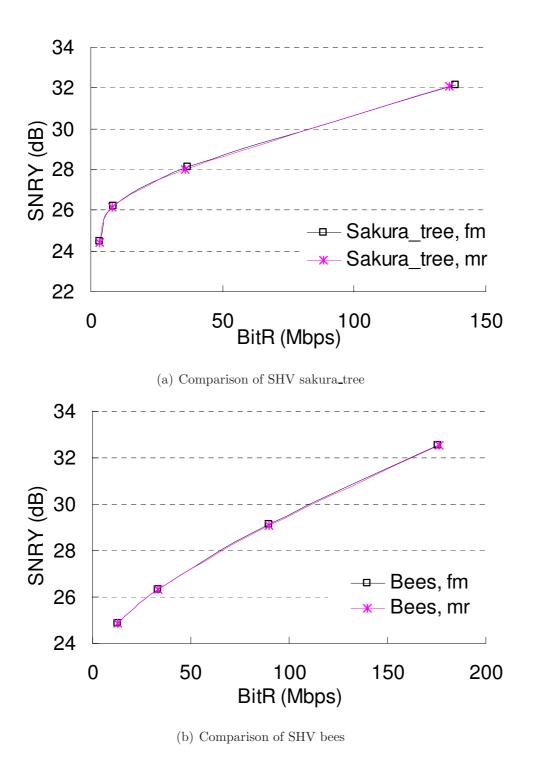

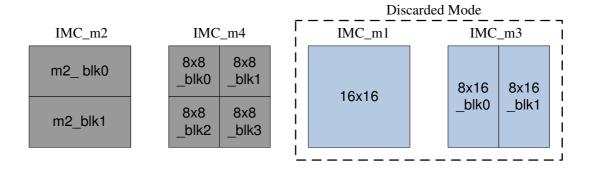

In the fourth chapter, two low design effort SHV engines for FME and intra prediction are proposed. Firstly, for FME engine, two optimizations in the algorithm level, namely inter mode pre-filtering and one-pass algorithm are proposed. For inter mode pre-filtering, it analyze the motion cost of sub-blocks in IME stage and only focuses on two modes which have smaller cost than others. As for one-pass algorithm, it firstly decides the sliding window based on integer motion cost of neighboring positions. Then, only half and quarter pixel within the sliding window are processed simultaneously, which saves hardware cost and processing time. In the hardware level, with quarter sub-sampling technique in FME stage, a 16-Pel interpolation structure is proposed, which speeds up 4 times of original 4-Pel design while keep almost the same hardware amount. With MB and frame level parallel processing flow, compared with representative design which requires 2.16GHz for 4k×4k@60fps, the proposed FME engine can accomplish real-time processing with only 145MHz. For intra engine, the predictor generation is the most time consuming part. From the analysis of data dependency issue of intra prediction, it is observed that the maximum parallel processing scale is two sub-block instead of original one sub-block way. In this dissertation, one lossless two sub-block parallel data flow are proposed, which saves 37.5% processing time of original one sub-block way. Also, in the original intra predictor generation engine, lots of repetitive computation exists among different modes. In the proposed fully utilized intra predictor generation architecture, no repetitive generation of predictors exists and it is applicable for all intra prediction

modes. With proposed architecture, the whole predictor generation process can be finished within only 22.5% cycles of original design. By combining parallel data flow and fully utilized architecture, the proposed intra predictor generation engine is capable of handling  $4k\times2k@60$ fps specification.

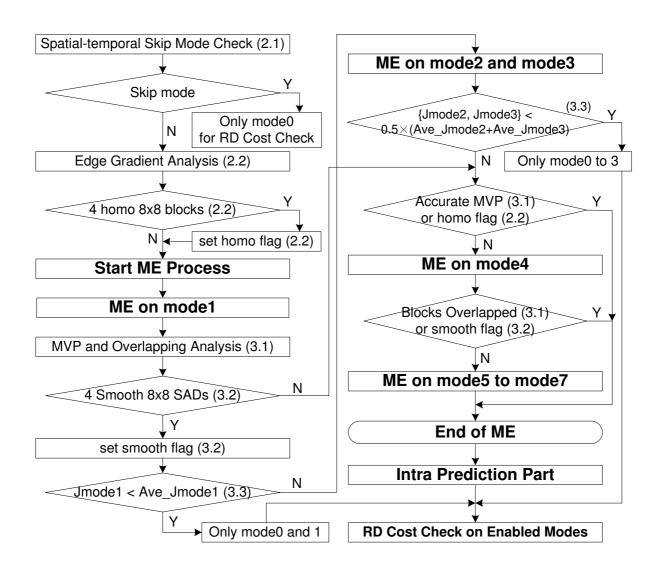

In the fifth chapter, high complexity problem in H.264/AVC mode decision is discussed. By utilizing spatial and temporal information, complexity reduction is achieved in two stages. Firstly, gradients of current MB and motion vector of encoded MB on both current and previous frames are utilized for pre-stage skip mode check. Secondly, during the motion stage, it is observed that information of motion vector predictor (MVP), block overlapping status and rate distortion cost can indicate the accuracy of matching process. In detail, the MVP represents the accuracy of predicted start point. The block overlapping status of different inter modes indicates the motion trend of object. As for rate distortion cost, it is an objective measurement of matching result. Thus, such information is used for early decision of whole encoding process in the proposed mode decision algorithm. Compared with existing works, the proposed algorithm can achieve up to 53.4% speed-up ratio with trivial quality loss.

In the sixth chapter, the whole dissertation is concluded and future trend in video compression fields is also briefly discussed. In this dissertation, it focuses on IME, FME, intra and mode decision which are four most important parts in H.264/AVC real-time encoding system. Hardware oriented low complexity algorithm and low cost, low power hardware architectures are proposed. By combining hardware oriented algorithms with proposed architectures, compared with recent 4-stage real-time encoder design, about 90.68% power in IME part can be reduced. As for SHV targeted FME and intra engines, about 93.31% and 67.24% estimated power reduction in hardware design.

#### Contents

| 1        | Intr | Introduction |                                                                |    |  |  |

|----------|------|--------------|----------------------------------------------------------------|----|--|--|

|          | 1.1  | Backg        | ground and purpose of this dissertation                        | ]  |  |  |

|          | 1.2  | Scope        | of this dissertation                                           | 4  |  |  |

| <b>2</b> | Har  | dware        | oriented fast H.264/AVC motion estimation algorithm            | 7  |  |  |

|          | 2.1  | Introd       | luction                                                        | 7  |  |  |

|          | 2.2  | Hardw        | vare oriented multiple reference frame elimination             | 1( |  |  |

|          |      | 2.2.1        | Aliasing problem and impact of edge detection                  | 11 |  |  |

|          |      | 2.2.2        | Gradient based multiple reference frame elimination            | 14 |  |  |

|          |      | 2.2.3        | Quantization parameter based threshold adjustment              | 16 |  |  |

|          |      | 2.2.4        | Similarity-analysis based multiple reference frame elimination | 21 |  |  |

|          | 2.3  | Hardw        | vare oriented search range adjustment                          | 27 |  |  |

|          |      | 2.3.1        | Motion feature based search range adjustment                   | 27 |  |  |

|          |      | 2.3.2        | Recursive 6-ring search range adjustment                       | 29 |  |  |

|          | 2.4  | Pixel        | difference based adaptive sub-sampling                         | 31 |  |  |

|          | 2.5  | Exper        | iments, comparison and analysis                                | 34 |  |  |

|          | 2.6  | Concl        | usion remarks                                                  | 48 |  |  |

| 3        | Flex | xible iı     | nteger motion estimation architecture                          | 50 |  |  |

|          | 3.1  | Introd       | luction                                                        | 50 |  |  |

|          | 3.2  | Recon        | figurable SAD tree architecture                                | 53 |  |  |

|          |      | 3.2.1        | System architecture                                            | 53 |  |  |

|          |      | 3.2.2        | Architecture level data organization and circuit modification  | 55 |  |  |

#### CONTENTS

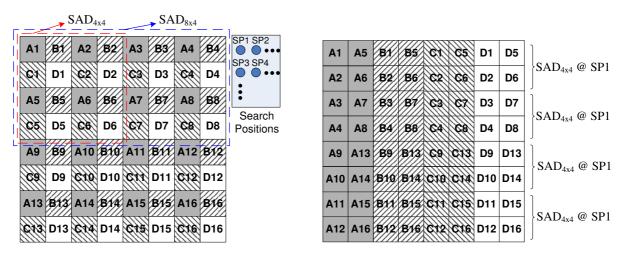

|   |     | 3.2.3               | Memory level pixel organization                                                 | . 58  |

|---|-----|---------------------|---------------------------------------------------------------------------------|-------|

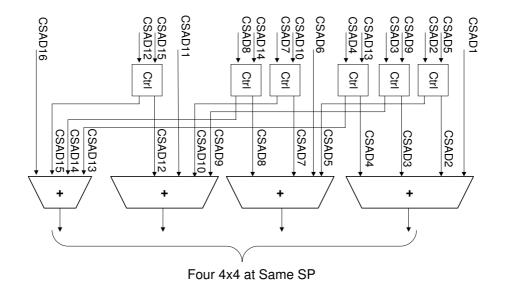

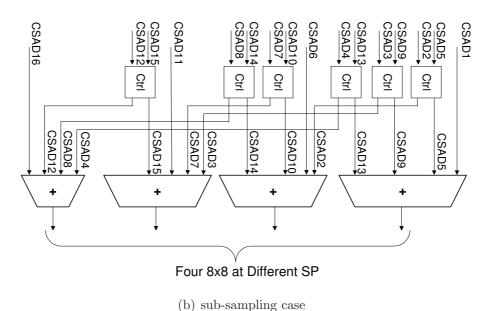

|   |     | 3.2.4               | Cross reuse structure for CSAD generation                                       | . 60  |

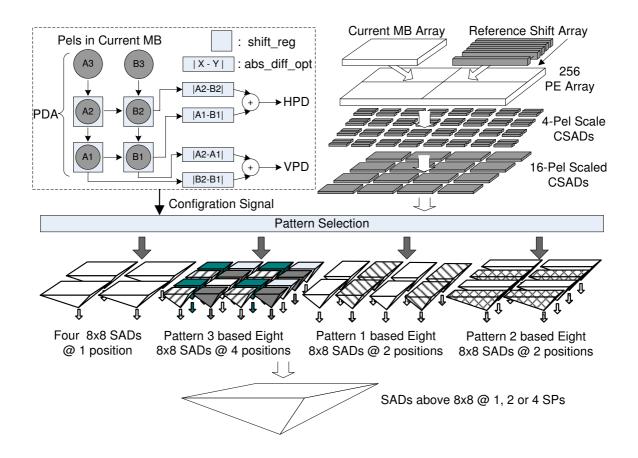

|   | 3.3 | Adapt               | ive propagate partial SAD architecture                                          | . 62  |

|   |     | 3.3.1               | System architecture                                                             | . 62  |

|   |     | 3.3.2               | Memory organization                                                             | . 65  |

|   |     | 3.3.3               | Compressor tree in standard cell library                                        | . 69  |

|   |     | 3.3.4               | Circuit optimization for single processing element                              | . 70  |

|   |     | 3.3.5               | Compressor tree based eight stage circuit optimization                          | . 72  |

|   | 3.4 | Exper               | iments, comparison and analysis                                                 | . 75  |

|   | 3.5 | Concl               | usion remarks                                                                   | . 83  |

| 4 | Low | $	extstyle design}$ | n effort VLSI engine for super high-vision application                          | 84    |

|   | 4.1 | Introd              | uction                                                                          | . 84  |

|   | 4.2 | Low c               | omplexity fractional motion estimation algorithm                                | . 89  |

|   |     | 4.2.1               | Mode reduction based mode pre-filtering scheme                                  | . 89  |

|   |     | 4.2.2               | Motion cost oriented directional one-pass scheme                                | . 91  |

|   |     | 4.2.3               | Overall hybrid schemes                                                          | . 93  |

|   | 4.3 | Archit              | secture level parallel improved schemes                                         | . 94  |

|   |     | 4.3.1               | Parallel improved 16-Pel processing                                             | . 94  |

|   |     | 4.3.2               | MB-parallel schedule                                                            | . 97  |

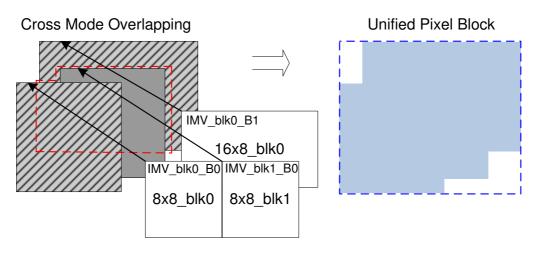

|   |     | 4.3.3               | Unified pixel block loading                                                     | . 97  |

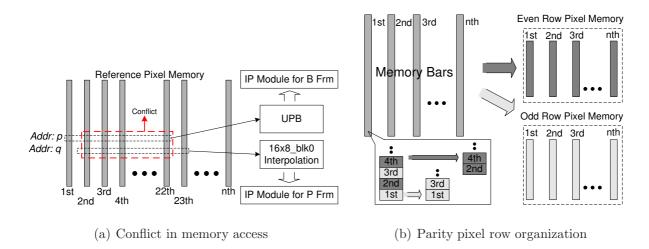

|   |     | 4.3.4               | Parity pixel organization for parallel processing                               | . 99  |

|   | 4.4 | Low d               | esign effort architecture for $\mathrm{H.264/AVC}$ intra predictor generation . | . 100 |

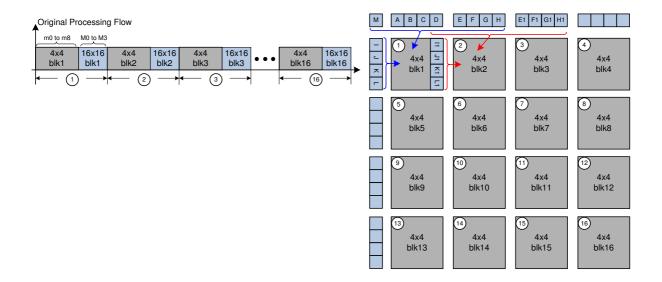

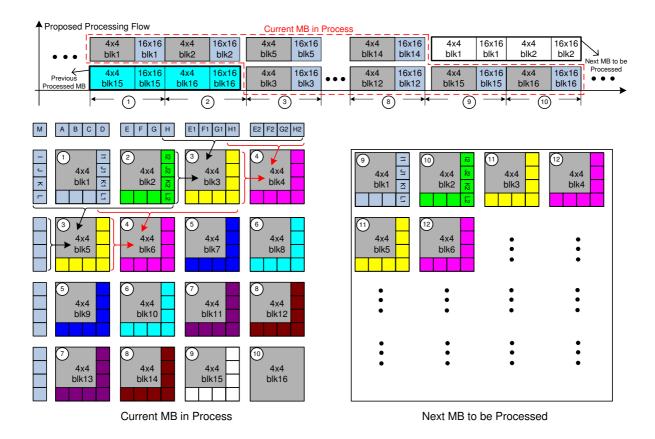

|   |     | 4.4.1               | Parallel processing flow for intra predictor generation                         | . 100 |

|   |     | 4.4.2               | Fully utilized parallel intra predictor generation architecture                 | . 102 |

|   | 4.5 | Exper               | imental result of low design effort engines                                     | . 110 |

|   | 4.6 | Concl               | usion remarks                                                                   | . 116 |

| 5 | Ana | alysis o            | of macroblock feature to fast inter mode decision                               | 117   |

|   | 5.1 | Introd              | uction                                                                          | . 117 |

|   | 5.2 | Pre-st              | age inter mode decision schemes                                                 | . 119 |

#### CONTENTS

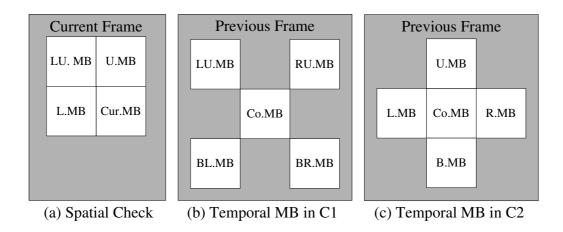

|    |        | 5.2.1  | MV oriented spatial-temporal inter mode check    | . 119 |

|----|--------|--------|--------------------------------------------------|-------|

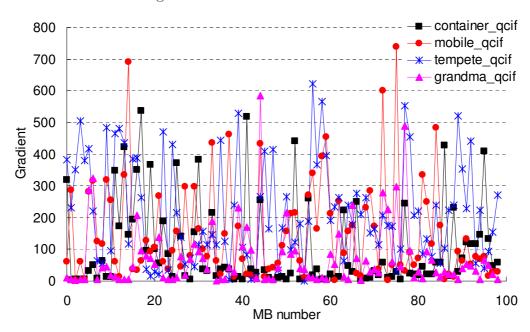

|    |        | 5.2.2  | Edge gradient based inter mode filtering         | . 121 |

|    | 5.3    | Motio  | n feature based fast inter mode decision schemes | . 125 |

|    |        | 5.3.1  | MVP accuracy and block overlapping analysis      | . 125 |

|    |        | 5.3.2  | Smoothness of sum of absolute difference (SAD)   | . 126 |

|    |        | 5.3.3  | Rate distortion cost analysis on big inter modes | . 127 |

|    | 5.4    | Overa  | ll algorithm and experiments                     | . 128 |

|    | 5.5    | Conclu | usion remarks                                    | . 133 |

| 6  | Con    | clusio | ns and future work                               | 134   |

| Ad | knov   | wledge | ement                                            | 138   |

| Re | efere  | nces   |                                                  | 140   |

| Ρı | ıblica | ations |                                                  | 146   |

#### List of Figures

| 1.1  | Overview of video coding standards                                  | 2  |

|------|---------------------------------------------------------------------|----|

| 1.2  | Block diagram of H.264/AVC video coding system                      | 3  |

| 1.3  | Overview of this dissertation                                       | 5  |

| 2.1  | Complexity in H.264 motion estimation                               | 8  |

| 2.2  | 4-stage pipeline based video coding system                          | 10 |

| 2.3  | Aliasing in Hybrid Video Coding                                     | 12 |

| 2.4  | RD Curves of QCIF 'football' and 'mobile'                           | 12 |

| 2.5  | 2-D Fourier Spectrum Amplitude of 'football_qcif' and 'mobile_qcif' | 13 |

| 2.6  | Convolution mask of Sobel operator                                  | 14 |

| 2.7  | MB partition in VBSME algorithm                                     | 16 |

| 2.8  | Edge gradient analysis flow chart                                   | 17 |

| 2.9  | Tolerance graph of 'foreman_qcif'                                   | 20 |

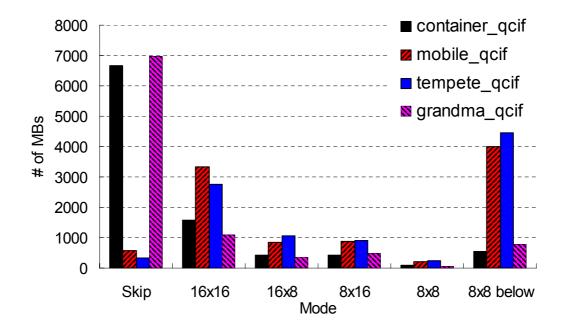

| 2.10 | Coding block sizes of QCIF sequences                                | 22 |

| 2.11 | Spiral search order                                                 | 23 |

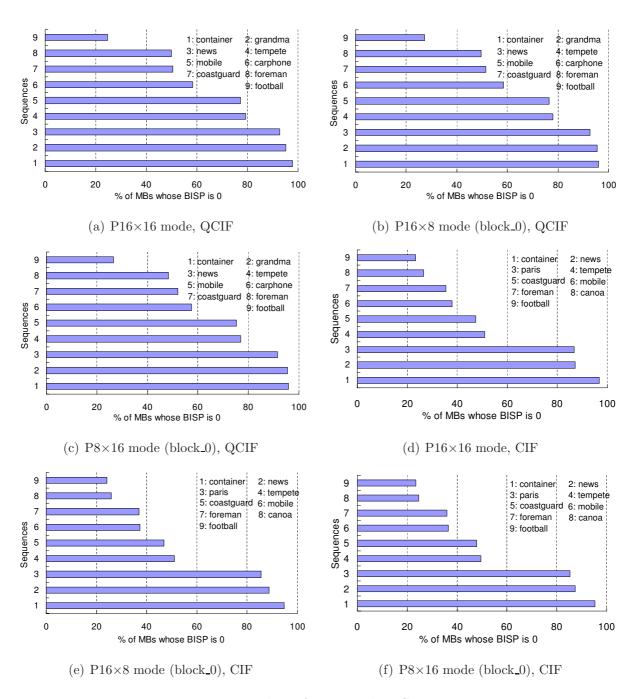

| 2.12 | Number of MBs with BISP in MVP                                      | 24 |

| 2.13 | Distribution of final best mode                                     | 26 |

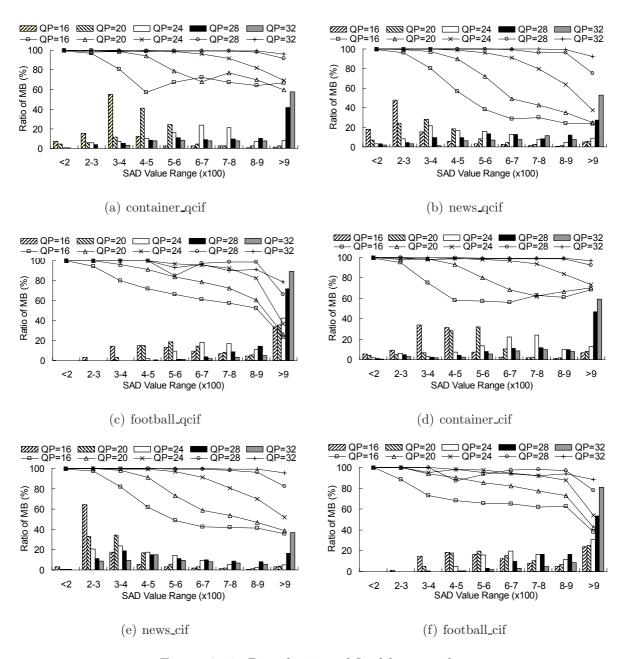

| 2.14 | Impact of search range to video quality                             | 28 |

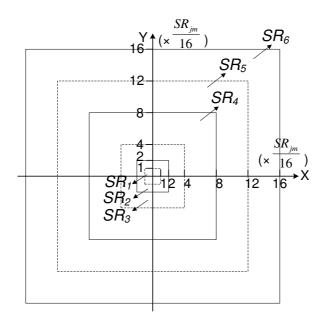

| 2.15 | 6-Ring search range adjustment                                      | 31 |

| 2.16 | Impact of direct sub-sampling                                       | 33 |

| 2.17 | Three sub-sampling patterns                                         | 34 |

| 2.18 | Flow chart of adaptive sub-sampling                                 | 35 |

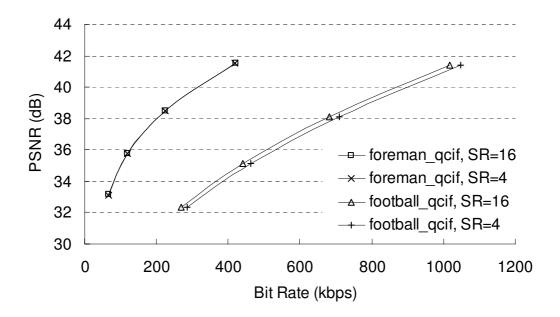

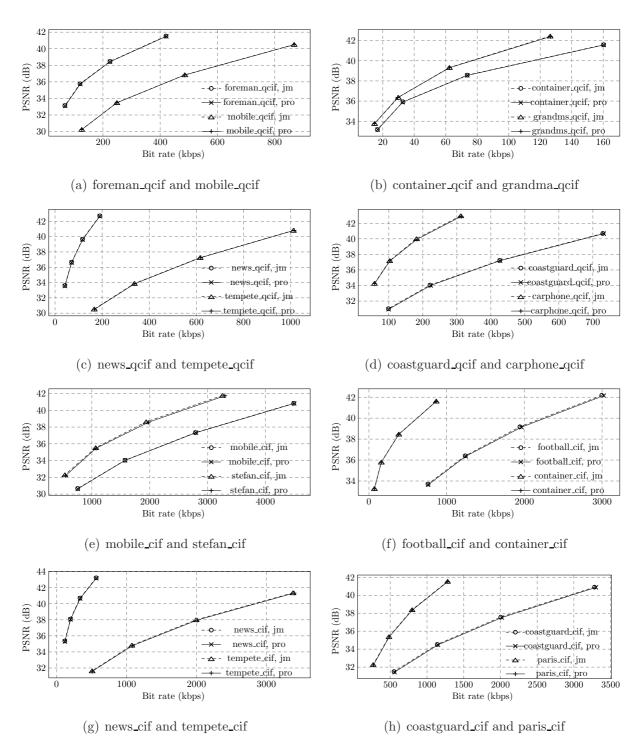

| 2.19 | Comparison of QCIF and CIF RD Curves                                | 40 |

#### LIST OF FIGURES

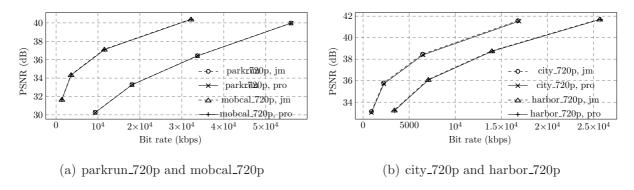

| 2.20 | Comparison of 720p RD Curves                               | 41 |

|------|------------------------------------------------------------|----|

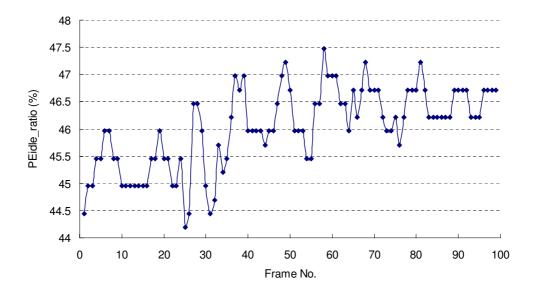

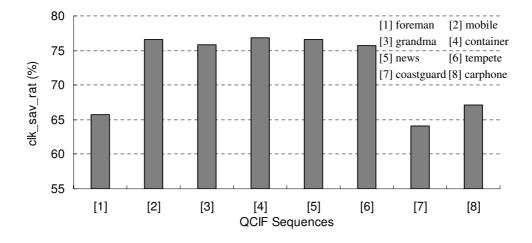

| 2.21 | PE idle ratio                                              | 46 |

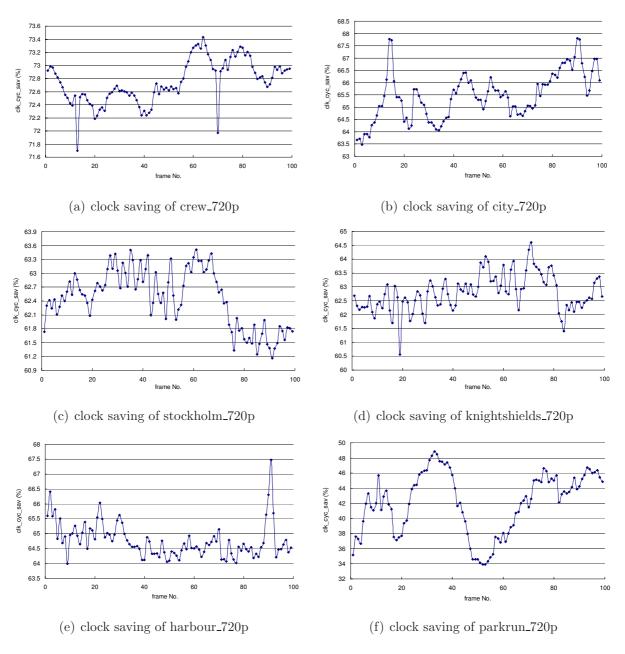

| 2.22 | Clock cycle saving ratio                                   | 46 |

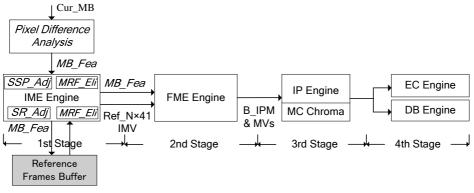

| 2.23 | 4-Stage encoding system with proposed algorithm            | 47 |

| 3.1  | Sub-sampling patterns and full pixel pattern               | 51 |

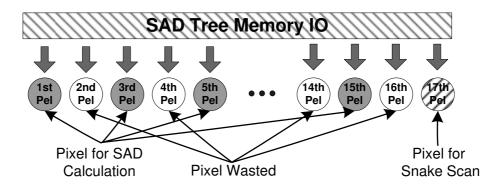

| 3.2  | Data reuse problem in SAD Tree structure                   | 52 |

| 3.3  | Original SAD Tree structure                                | 53 |

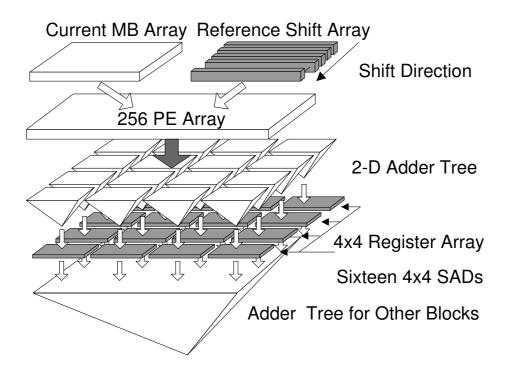

| 3.4  | Proposed reconfigurable SAD tree architecture              | 54 |

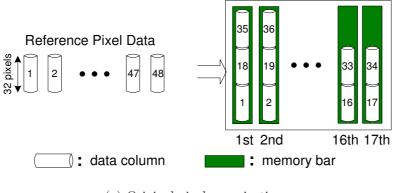

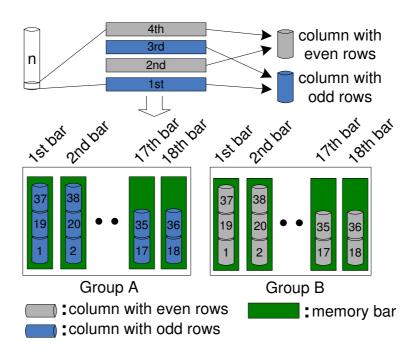

| 3.5  | Pixel data organization                                    | 57 |

| 3.6  | 4-Pel scaled CSAD                                          | 58 |

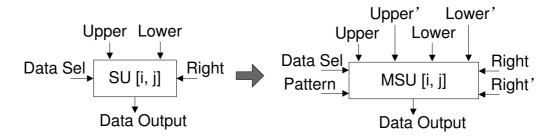

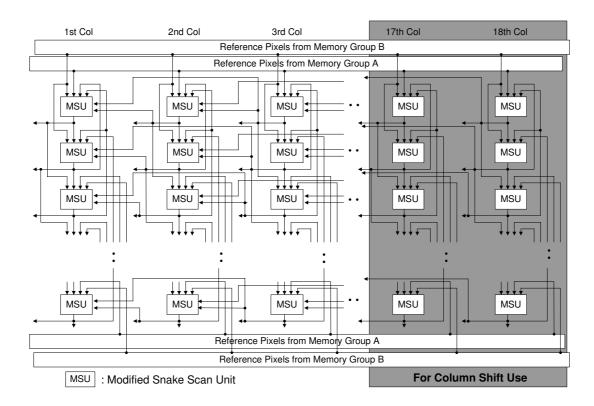

| 3.7  | Modification in SU                                         | 58 |

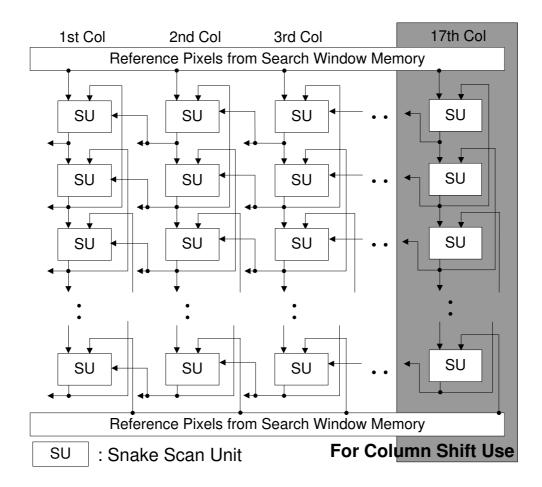

| 3.8  | Original reference shift array                             | 59 |

| 3.9  | Modified reference shift array                             | 60 |

| 3.10 | Memory level pixel organization                            | 61 |

| 3.11 | Cross reuse structure for CSAD generation                  | 62 |

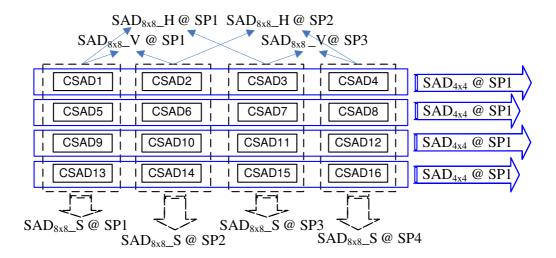

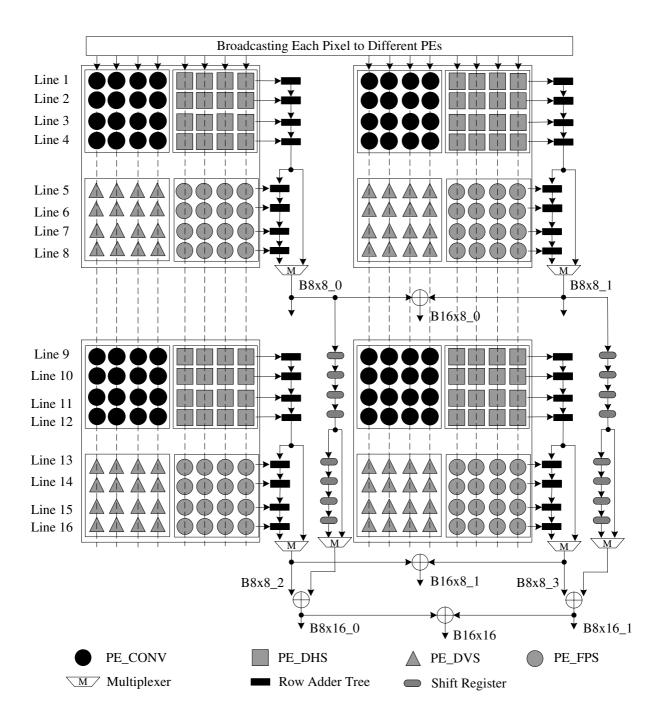

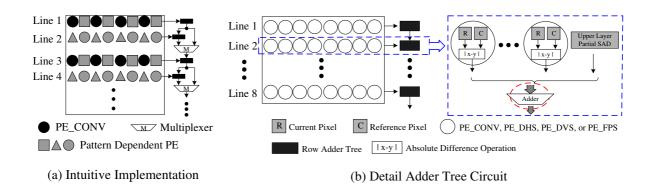

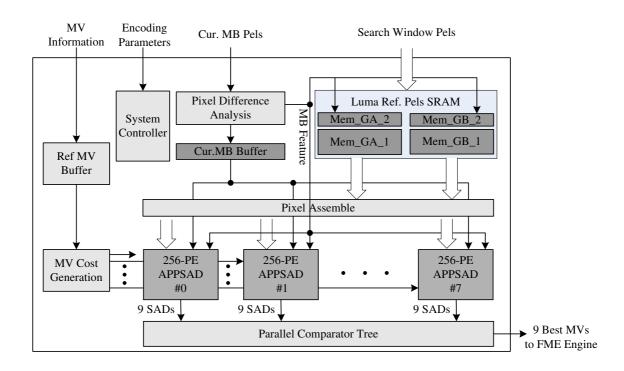

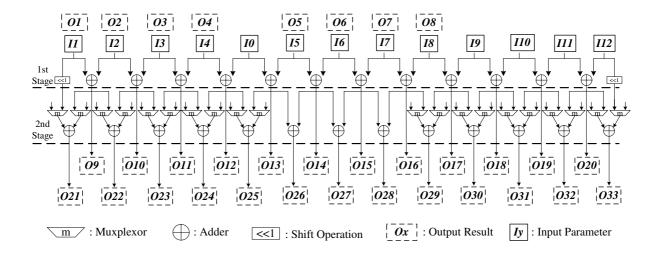

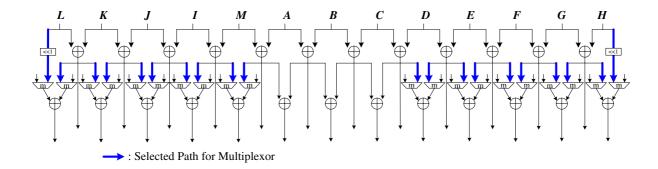

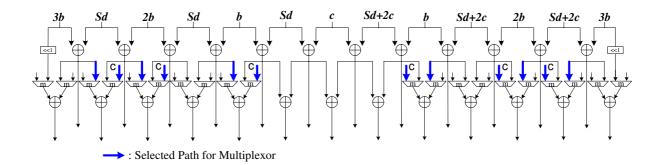

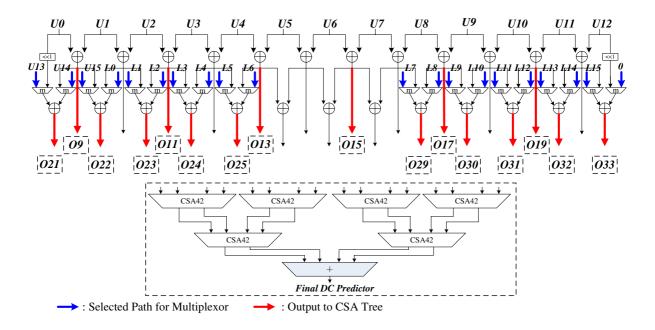

| 3.12 | Adaptive propagate partial SAD architecture                | 64 |

| 3.13 | 8x8 PE array in PPSAD architecture                         | 65 |

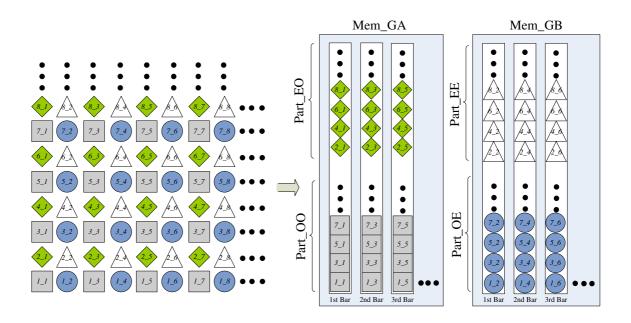

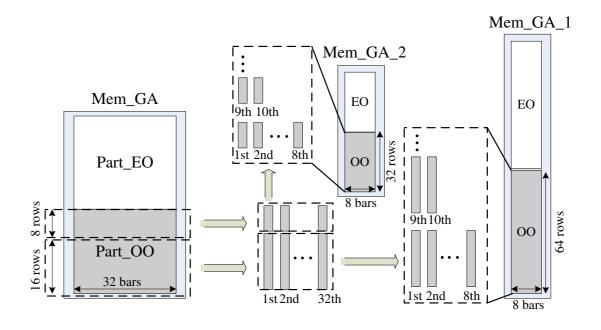

| 3.14 | Pixel classification and memory organization               | 66 |

| 3.15 | Memory separation and overlapping                          | 66 |

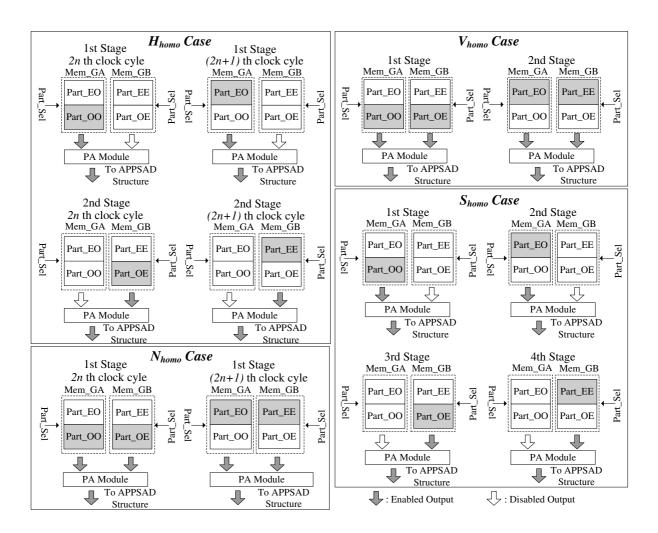

| 3.16 | Data flow of APPSAD architecture                           | 68 |

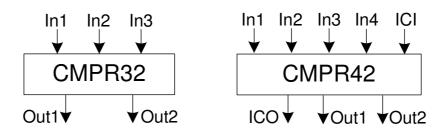

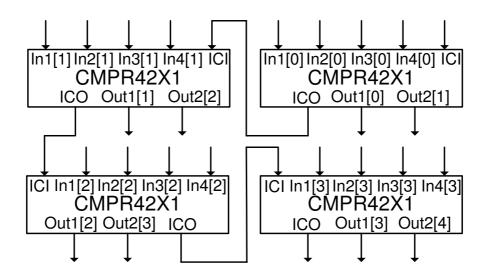

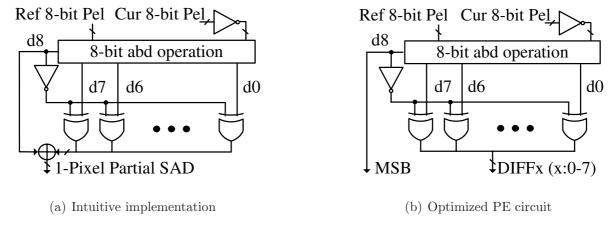

| 3.17 | Compressors in standard cell library                       | 70 |

| 3.18 | CMPR42X1 with Multiple-bits Wide Input                     | 71 |

| 3.19 | Optimization of processing element                         | 71 |

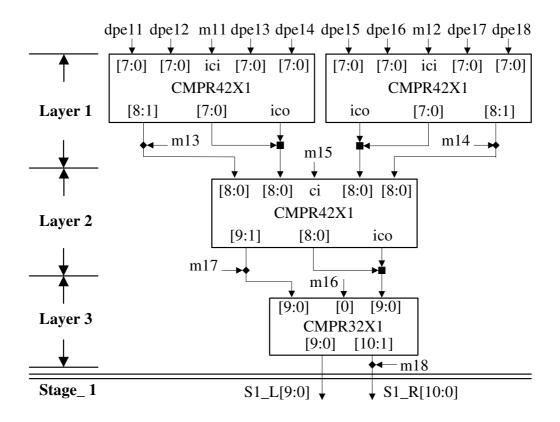

| 3.20 | Compressor tree structure for Stage_1                      | 72 |

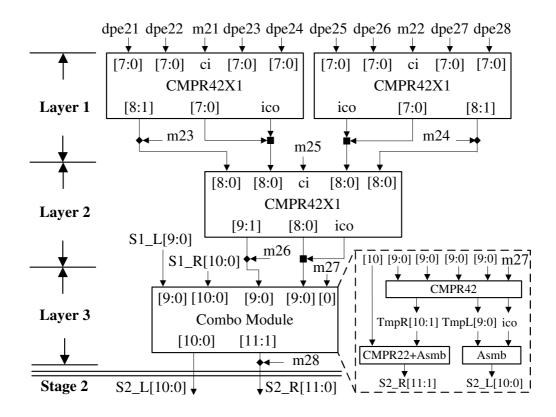

| 3.21 | Compressor tree structure for Stage_2                      | 73 |

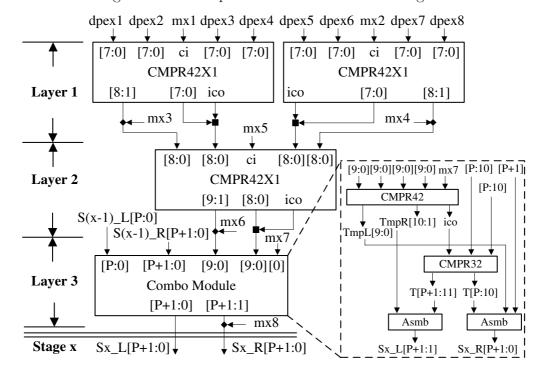

| 3.22 | Compressor tree structure for Stage_3, Stage_5 and Stage_7 | 73 |

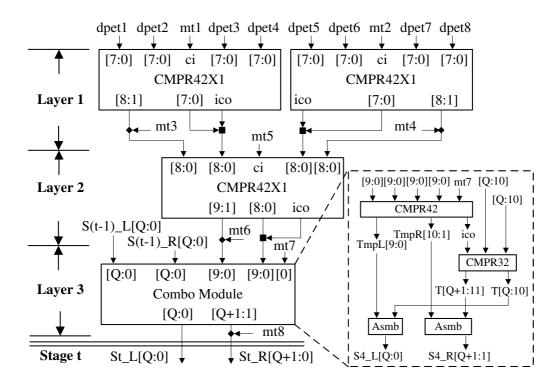

| 3.23 | Compressor tree structure for Stage_4, Stage_6 and Stage_8 | 74 |

| 3.24 | Clock saving of HDTV sequences                             | 77 |

| 3.25 | IME block diagram with APPSAD architecture                 | 80 |

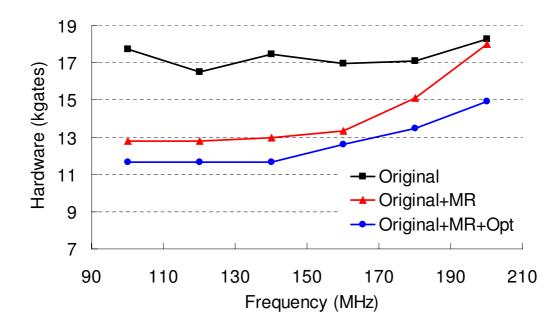

| 3.26 | Hardware cost saving of 8x8 PE array                       | 81 |

#### LIST OF FIGURES

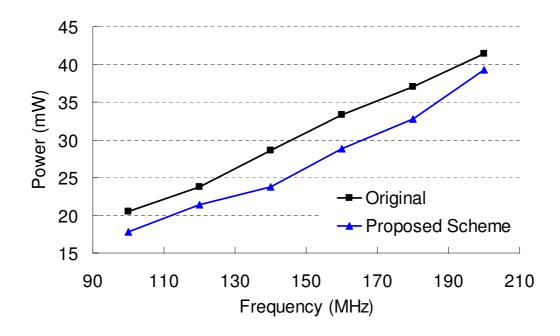

| 3.27 | Power dissipation of 8x8 PE array                                       |

|------|-------------------------------------------------------------------------|

| 3.28 | Power consumption comparison                                            |

| 4.1  | Spectrum comparison of HDTV1080p with SHV                               |

| 4.2  | Impact of mode reduction on SHV                                         |

| 4.3  | Mode reduction based mode pre-filtering scheme                          |

| 4.4  | Motion Cost Oriented One-pass Scheme                                    |

| 4.5  | Pseudo codes of FME algorithm                                           |

| 4.6  | RD curve comparison                                                     |

| 4.7  | 16-Pel interpolation process                                            |

| 4.8  | MB parallel processing schedule                                         |

| 4.9  | Unified pixel block loading scheme                                      |

| 4.10 | Solution to memory access conflict                                      |

| 4.11 | Original processing flow                                                |

| 4.12 | Proposed processing flow                                                |

| 4.13 | Proposed predictor generation engine                                    |

| 4.14 | Proposed architecture for I4MB modes                                    |

| 4.15 | Proposed architecture for I16MB plane mode                              |

| 4.16 | Proposed architecture configured for I16MB and I4MB DC Mode $\dots$ 109 |

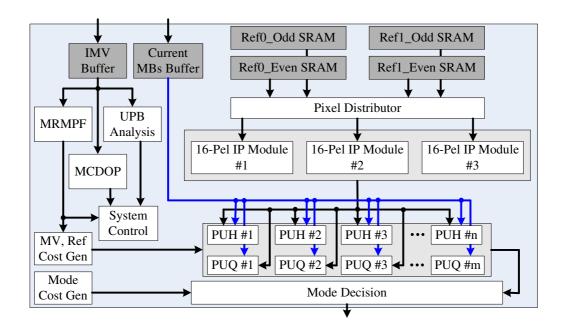

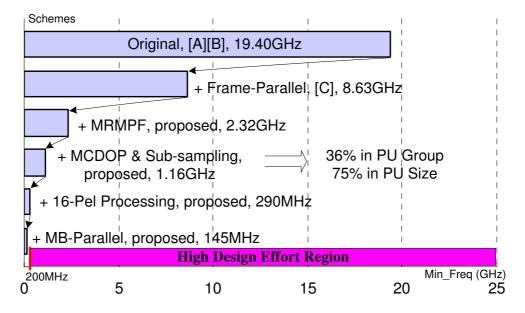

| 4.17 | 4kx4k Super Hi-Vision FME architecture                                  |

| 4.18 | Scheme for SHV FME engine                                               |

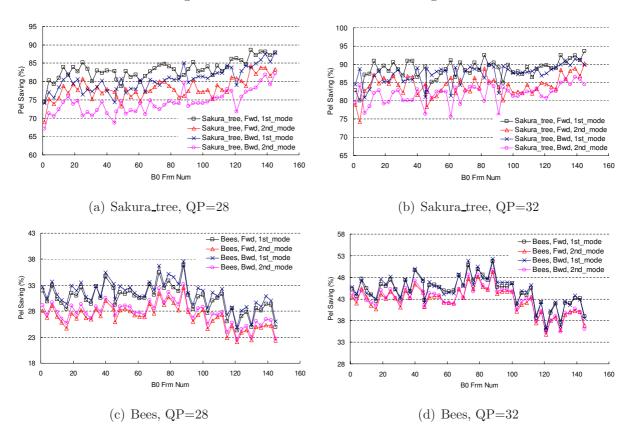

| 4.19 | Pixel saving ratio of UPB scheme                                        |

| 5.1  | Inter Block Modes in H.264/AVC                                          |

| 5.2  | Spatial-temporal Skip Mode Check                                        |

| 5.3  | Pseudo Codes of Pre-Stage Inter Mode Decision                           |

| 5.4  | Inter Mode Distributions                                                |

| 5.5  | Gradient Distributions of 20th Frame                                    |

| 5.6  | BIP Distribution of $16 \times 16$ Mode in 100 Frames                   |

| 5.7  | Overall Flow Chart of Proposed Algorithm                                |

| 5.8  | Comparison of RD Curves                                                 |

#### LIST OF FIGURES

#### List of Tables

| 2.1  | Impact of $THR_G$ on sequences                          | 19  |

|------|---------------------------------------------------------|-----|

| 2.2  | Simulation conditions for BISP on previous frame        | 25  |

| 2.3  | Simulation conditions for BISP on five reference frames | 29  |

| 2.4  | BISP Distribution on 1st to 5th Reference Frame         | 30  |

| 2.5  | Homo MB Ratio (%) for 1/4 Subsampling                   | 36  |

| 2.6  | Ratio (%) of MB with MRF Elimination                    | 37  |

| 2.7  | Ratio (%) of MB with Small Range Constraint             | 38  |

| 2.8  | Quality Comparison with Full Search                     | 42  |

| 2.9  | ME Time Reduction Ratio with Full Search<br>(%)         | 43  |

| 2.10 | Quality Comparison with UMHexagon Search                | 44  |

| 2.11 | Speed-up of UMHexagon Search                            | 45  |

| 3.1  | Quality analysis of adaptive sub-sampling               | 52  |

| 3.2  | Comparison with Extended SAD Tree                       | 78  |

| 3.3  | Comparison of RSADT with Previous Designs               | 79  |

| 3.4  | Comparison of APPSAD with Previous Designs              | 80  |

| 4.1  | Predictors of I4MB modes in 4×4 sub-block               | 104 |

| 4.2  | Output predictors of I4MB modes in 4×4 sub-block        | 107 |

| 4.3  | Output predictors of I16MB plane mode                   | 108 |

| 4.4  | Hardware statistics (1.62V,125°C)                       | 113 |

| 4.5  | Experimental result and comparison                      | 115 |

| 4.6  | Comparison of processing cycles for one 4×4 sub-block   | 115 |

#### LIST OF TABLES

| 5.1 | Complexity Analysis based on $-\Delta MET$ (%)                                      | 131 |

|-----|-------------------------------------------------------------------------------------|-----|

| 5.2 | Quality Analysis based on C1 and C2 (C1: $\Delta PSNR$ (dB); C2: $\Delta Bits$ (%)) | 131 |

#### Acronyms

AMPD: advanced mode pre-decision

APPSAD: adaptive propagate partial SAD

B.MB: bottom macroblock

BDBR: bjontegaard bit-rate

BDPSNR: bjontegaard peak source to noise ratio

BIP: best integer point

BISP: best integer search position

BitR: bit-rate

BL.MB: bottom-left macroblock

BMMB: big mode macroblock

BR.MB: bottom-right macroblock

CMO: cross mode overlapping

CMPR32: 3-2 compressor

CMPR42: 4-2 compressor

Co.MB: co-located macroblock

CRS: cross reuse structure

CSAD: configurable Sum of absolute difference

Cur.MB: current macroblock

DB: de-blocking

dynamic\_SR: dynamic search range scheme

EC: entropy coding

fm: full mode

FME: fractional motion estimation

HD: high definition

Homo: homogeneous

HW\_utiliz: hardware utilization

I4MB: intra  $4\times4$  prediction modes

I16MB: intra  $16 \times 16$  prediction modes

IBO: inner block overlapping

ICI: immediate carry-in

ICO: immediate carry-out

IMC: integer motion cost

IME: integer motion estimation

IMV: integer motion vector

IP: intra prediction

L.MB: left macroblock

LU.MB: left-up macroblock

MAFD: mean of absolute frame difference

MB: macroblock

MCDOP: motion cost oriented one-pass

ME: motion estimation

MET: motion estimation time

Min\_Freq: minimum required frequency

mr: mode reduction

MP: matching pattern

MRF: multiple reference frame

MRMPF: mode reduction based mode pre-filtering

MSU: modified snake scan unit

MV: motion vector

MVP: motion vector predictor

NMB: normal macroblock

Non Homo: nonhomogeneous

PA: pixel assemble

PD: pixel difference

PDA: pixel difference analysis

PE: processing element

PE\_CONV: conventional processing element

PPSAD: propagate partial sad

pro\_SR: proposed search range scheme

PSNR: peak source to noise ratio

PU: processing unit

PUH: processing unit for half pixel refinement

PUQ: processing unit for quarter pixel refinement

QP: quantization parameter

R.MB: right macroblock

**RD**: rate distortion

RSA: reference shift array

RSADT: reconfigurable SAD Tree

RU.MB: right-up macroblock

SA: similarity analysis

SAD: sum of absolute difference

$SAD8x8\_BL:$  bottom-left 8x8 SAD

SAD8x8\_BR: bottom-right 8x8 SAD

SAD8x8\_LU: left-up 8x8 SAD

SAD8x8\_RU: right-up 8x8 SAD

SHV: super hi-vision

SR: search range

SU: snake scan unit

U.MB: upper macroblock

UBP: unified pixel block

VBS: variable block size

#### Chapter 1

#### Introduction

#### 1.1 Background and purpose of this dissertation

Sixteen years ago, the advent of MPEG-2 standard enriches our life with worldwide digital television system. From that time, MPEG-2 has become a key technique which is widely used in transmission of High Definition (HD) TV signals over satellite, cable, and the storage of high-quality SD video signals onto DVDs. However, the increasing demand for more service over network, or desire for vivid and impressive daily life makes bit rates on network roar dramatically. Nowadays, high bit rate connections are almost everywhere around us. The ever increasing tough situation on network transmission continuously pushes video compression technique forward.

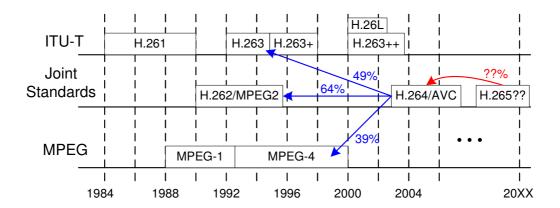

Currently, the latest video coding standard is H.264/AVC which firstly comes to existence in 2003 [1]. Compared with previous standards, the performance improvement of H.264/AVC is quite significant [2]. Figure. 1.1 demonstrates the development of video coding standards. Compared with MPEG-4 [3], H.263 [4], and MPEG-2 [5], the H.264/AVC standard can achieve 39%, 49% and 64% bit-rate reduction, respectively. In the near future, H.265 may come into existence and the performance improvement of new standard is always a heated topics. Figure. 1.2 gives out the whole block diagram of H.264/AVC based hybrid encoding system. The bold italic font marked on the diagram represent the new techniques introduced by H.264/AVC standard. For example, in H.264/AVC, it adopts techniques such as variable block size (VBS), multiple reference frame (MRF),

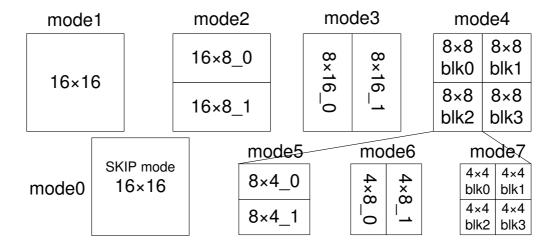

Figure 1.1: Overview of video coding standards

intra prediction (IP), context adaptive entropy coding (EC), in-loop de-blocking (DB) and so on. These techniques mainly fall into three categories. Firstly, H.264/AVC introduces techniques which target at higher prediction accuracy. The ME and IP parts fully exploit the temporal and spatial redundancy. Besides skip modes, there are seven inter modes with different block sizes in inter prediction. Considering the MRF technique, the efficiency of condensing temporal information is very high. As for IP modes, there exists nine intra 4×4 modes and four intra 16×16 modes. All these inter and intra modes are involved in a rate distortion based encoding process, which ensures the best outcome result over available resources. Secondly, H.264/AVC introduces techniques which focus on image enhancement. To remove the visible artifacts of block based hybrid compression scheme, it uses an adaptive in-loop de-blocking filter, where the strength of filtering is controlled by the values of several syntax elements. Also, the interpolation of half and quarter pixel for fractional motion estimation is an efficient way to compensate the inevitable aliasing problem, which also leads to better image quality. Thirdly, H.264/AVC introduces new mathematics model which greatly improves the compression capability. The powerful entropy coding method, namely CABAC, provides a good solution to the ever increasing bit rates.

Although, there are many appealing points in H.264/AVC standard, the shortcoming of this standard is also quite obvious. Compared with previous standards, the complexity problem of H.264/AVC become a 'hot potato' and many researchers focus on this topic for several years. The computation complexity of each part is also marked on Fig. 1.2.

#### 1.1 Background and purpose of this dissertation

Figure 1.2: Block diagram of H.264/AVC video coding system

Besides IP, mode decision and interpolation, the ME part is the most significant one, which occupies almost 90% computation. In order to reduce computation complexity while keep video quality, many software algorithms are proposed to speedup ME process. However, when hardware is considered, the efficiency of software level algorithm is greatly decreased. The high throughput of ME part makes pipeline stage a must, which deteriorates the efficiency of many fast algorithms. Also, important issues in hardware field are quite different from software region which has abundant power resource and computation capability as long as the computer is strong enough. In hardware fields such as ASIC design, issues like hardware cost, parallel processing, power dissipation, data reuse, memory size and hardware utilization are of great importance. Therefore, there exist a gap between software algorithm and hardware design. The purpose of this dissertation is to fill in this gap and propose hardware friendly fast algorithm together with some low hardware cost and low power architectures. The related research topics in this thesis are marked with broken lines in Fig. 1.2.

#### 1.2 Scope of this dissertation

This dissertation focuses on hardware friendly low complexity fast motion estimation algorithm and related low cost architecture. To attain this goal, this work focuses on three areas of research:

- 1. hardware friendly algorithm

- 2. low cost hardware architecture

- 3. fast mode decision scheme

To cover these three areas, the dissertation consists of six chapters as shown in Fig. 1.3.

Chapter 2 describes the origin of video quality loss in sampling based digital signal system. Based on theoretical and statistical analysis, several hardware friendly complexity reduction schemes are proposed. The proposed algorithm is based on hardware data flow and it releases the complexity in MRF technique, redundant search points and full pixel matching pattern. Experimental results show that, the proposed hardware friendly algorithm can achieve up to 95.26% complexity reduction and is orthogonal to existing software oriented fast algorithms. Moreover, all the proposed schemes can be easily implemented in pipeline stage based real-time encoding system.

In chapter 3, two HDTV targeted flexible hardware architectures are given out. The proposed structures adopts adaptive sub-sampling algorithm which can not be efficiently realized on existing SAD Tree and propagate partial SAD (PPSAD) architectures. In the proposed architectures, architectural level and memory level data organization is adopted, which enables full data reuse, hardware utilization and lower power consumption feature for adaptive sub-sampling algorithm. Compared with original design, the proposed reconfigurable SAD Tree and adaptive PPSAD architectures can achieve 38.8% and 39.8% reduction of power dissipation.

In chapter 4, the dissertation focuses on the high throughput issue of Super Hi-Vision (SHV) application. With the advent of SHV concept, the hardware implementation of SHV based real-time encoding system has become a hot topic. From the analysis of

Figure 1.3: Overview of this dissertation

existing works, the simple extension of these works to SHV will cause high design effort, large hardware resource and redundant memory access. In the propose architecture, algorithm level optimization and hardware level parallel processing are both adopted to satisfy the throughput issue. With only 145MHz work speed, one SHV 4k×4k@60fps targeted fractional motion estimation engine is given out. As for intra prediction, the

#### 1.2 Scope of this dissertation

predictor generation part is the most significant component towards high throughput application. In this dissertation, one highly parallel intra predictor generation structure is given out. Based on parallel processing flow and dedicated fully reuse structure, about 77.5% processing time is saved compared to original design.

For H.264/AVC based real-time system, mode decision is another important part considering the complexity of whole encoding system. The trade-off among video quality, complexity reduction and image feature is always a tough research topic. In chapter 5, one novel inter mode decision algorithm is introduced. The propose scheme achieves complexity reduction in a multi-stage way, which makes it suitable for image with different motion features. Compared with existing works, the proposal is superior to other schemes among various types of sequences.

Chapter 6 summarizes the whole research activities and gives out a brief view of future research direction which will further push my current research towards higher level and wider application fields

#### Chapter 2

## Hardware oriented fast H.264/AVC motion estimation algorithm

#### 2.1 Introduction

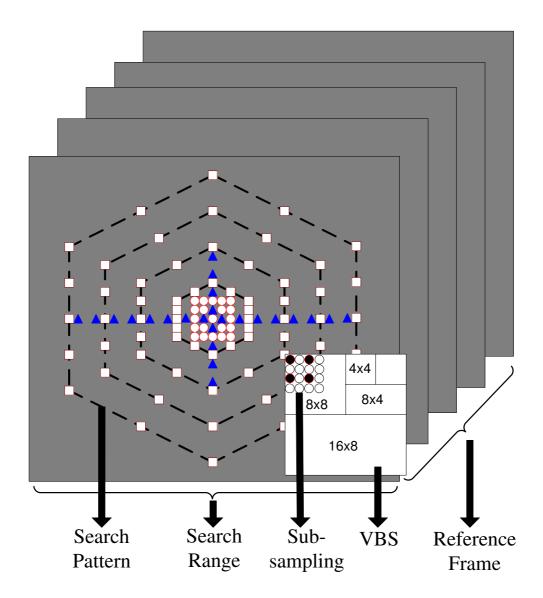

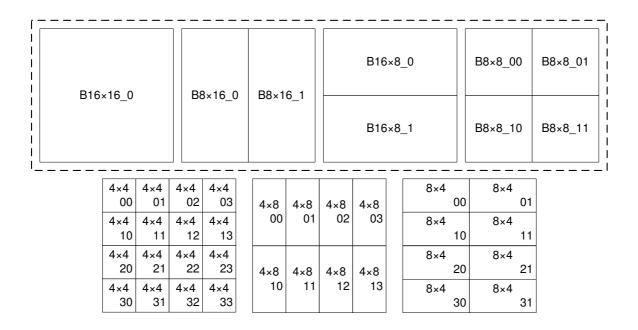

As mentioned in previous chapter, the H.264/AVC standard is superior to previous ones in terms of image quality and compression capability. However, it is also computation intensive due to many dedicated techniques. Literature [6] gives out complexity distribution of each part. The motion estimation (ME) part which occupies almost 90% computation turns out to be the most significant part. As shown in Fig. 2.1, the overwhelming complexity in ME mainly comes from five aspects. They are search pattern, search range, sampling pattern, VBS, and reference frame number. During ME of current MB, the VBS technique will divide one  $16\times16$  block into  $16\times8$ ,  $8\times16$ , and  $8\times8$  modes. When  $8\times8$  mode is selected, it can be further divided into  $8\times4$ ,  $4\times8$  and  $4\times4$  modes. Motion estimation is executed on each mode. For sampling pattern, as shown in Fig. 2.1, when quarter sub-sampling is used, only 1/4 of original pixels are used for block matching process. So, 75% calculation in block matching process can be saved. However, the direct sub-sampling will cause quality degradation. The relationship of reference frame number to complexity is linear. When 5 reference frames are used, the complexity will increase 5 times compared with 1 reference frame under the same conditions. The setting of search range determines the number of candidate search points, which also affects complexity a

Figure 2.1: Complexity in H.264 motion estimation

lot. In terms of search pattern, many existing patterns such as diamond search [7] [8], four-step search [9], three-step search [10], predictive zonal search [11] [12] and hexagon pattern [13] have already been proposed to reduce search points. Fig. 2.1 is an example of hexagon search pattern.

In order to reduce computation complexity while keep video quality, many works have been done [6, 13, 14, 15, 16]. Literature [14] proposes a fast motion estimation algorithm which is based on analysis of motion vectors (MVs) in previous frames. In literature [15], it uses the MVs of previous frames and up-layer blocks to reduce computation complexity

#### 2.1 Introduction

of search points and reference frames. In case of [16], the proposed algorithm first builds up three error surface by using initial 3 block modes (16×16, 8×8, 4×4). The decision of whether to test other modes or finer sub-block partition is based on the error surface analysis. The work of literature [6] uses four heuristic criterions to early terminate the ME process. These algorithms can achieve 30% to 90% reduction in ME time. As for search pattern based fast motion estimation, the UMHexagon search [13] can achieve ME time reduction up to 90%.

In hardware field, as mentioned by many works [17, 18, 19], it is a must to divide motion estimation engine into two stages due to the huge throughput in every clock cycle. As shown in Fig. 2.2, the integer motion estimation (IME) engine is arranged in the first stage while fractional motion estimation (FME) is in the second stage. Therefore, early termination on FME stage like [6] does not work because the IME which occupies 52% computation has already finished its work before handling best MVs to FME stage. As for motion vector based fast algorithms [14][15], they are not favorable for hardware because the storage of all MVs in previous frames is a great burden on system's hardware cost. For instance, with  $24 \times 24$  search window size, 10 bits are required for storage of one MB's MV in [14]. When 5 reference frames are adopted, even in the CIF format, the extra SRAM will be 19.8k bits. With the increase of image size (HDTV for example), the related extra memory will cause a serious burden on the system. For [16], since the rate distortion cost is only available in the last stage based on the hardwired video coding system, it is impossible to apply this algorithm in real-time encoding process. In terms of search pattern based fast algorithm [13], the irregular access of memory and unpredictable data flow make this algorithm difficult for hardware implementation. So, the existing software oriented algorithms are either impractical or inefficient for hardware design. For hardwired video encoding system, the widely adopted search scheme is full search algorithm which has best video quality, regular memory access and fixed processing control [20].

In this chapter, several hardware friendly fast motion estimation schemes are given out, which achieves complexity reduction while maintains full search data flow unchanged. Firstly, for MRF technique, two low complexity schemes are introduced. Based on mathematics analysis, the aliasing problem in image processing field is discussed. Image with

Figure 2.2: 4-stage pipeline based video coding system

high frequency feature is regarded as aliasing sensitive one and MRF technique is applied on such image. In this dissertation, I use Sobel edge detector to classify MB with different frequency feature. Also, simulation shows that for image which consists of abundant stationary parts, MRF can be eliminated. In this dissertation, similarity analysis is executed on central nine positions during block matching on first frame. The MRF technique on stationary MB is disabled to achieve further reduction of complexity. Secondly, in terms of search range, two adaptive search range adjustment schemes are given out. For small motion MB, search range is restricted in a local centering field and redundant search points are removed consequently. For ordinary motion MB, one recursive 6-ring search range adjustment scheme is introduced to achieve complexity reduction for such MB. Furthermore, in the aspect of matching pattern, one adaptive sub-sampling scheme is given out to release complexity and compensate quality loss of direct sub-sampling technique. The detail of each scheme is shown in the remaining parts of this chapter.

### 2.2 Hardware oriented multiple reference frame elimination

In this section, the aliasing problem in conventional video encoding system is analyzed. After that, two complexity reduction schemes for MRF technique are given out.

#### 2.2.1 Aliasing problem and impact of edge detection

In [21], it has already proved that aliasing is the main reason that deteriorates video quality. The adoptions of MRF and sub-pel interpolation in H.264 are actually to compensate for the aliasing problem. Here, I will analyze the aliasing problem in spatial and frequency domains and then give out influence of edge gradient on frequency spectrum.

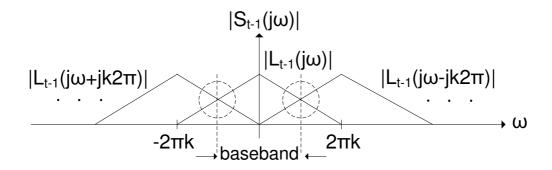

In order to ease the analysis, only one dimension signal is analyzed and the spatial sampling interval is assumed to be I=1. Let l(x) be spatial continuous signal. The  $l_t(x)$  and  $l_{t-1}(x)$  are signals at time instance t and t-1. Their spatial Fourier transforms are shown in Eq. 2.1. The  $d_x$  is the distance between  $l_t(x)$  and  $l_{t-1}(x)$ . It is shown that  $L_{t-1}(j\omega_x)$  and  $L_t(j\omega_x)$  are the same except their phase difference.

Let  $s_t(x_n)$  and  $s_{t-1}(x_n)$  be sampling results of space continuous signals  $l_t(x)$  and  $l_{t-1}(x)$  and their Fourier transform is shown in Eq. 2.2. Equation, 2.2 shows that aliasing problem can be avoided if Eq. 2.3 which represents the band limit low pass filter in the image sensor system is satisfied.

$$l_t(x) \Leftrightarrow L_t(j\omega_x) = L_{t-1}(j\omega_x) \cdot e^{-jd_x\omega_x} \tag{2.1}$$

$$S_t(j\omega_x) = S_{t-1}(j\omega_x) \cdot e^{-jd_x(\omega_x - k2\pi)} = \sum_{k=-\infty}^{+\infty} L_{t-1}(j\omega_x - jk2\pi) \cdot e^{-jd_x(\omega_x - k2\pi)}$$

(2.2)

$$L_{t-1}(j\omega_x) = 0, \qquad |\omega_x| \ge \pi \tag{2.3}$$

However, due to the nonexistence of idea low pass filter, the aliasing problem occurs inevitably in video coding system, as shown in Fig. 2.3. Another important result which is derived from Eq. 2.2 and Eq. 2.3 is that the image rich of high frequency signals is vulnerable to be affected by aliasing problem.

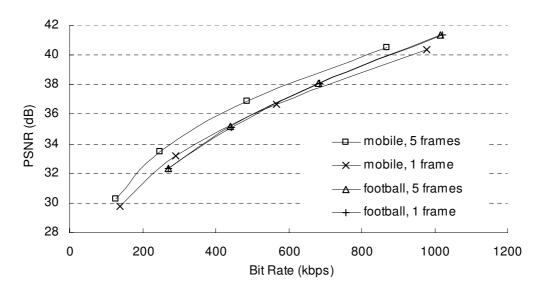

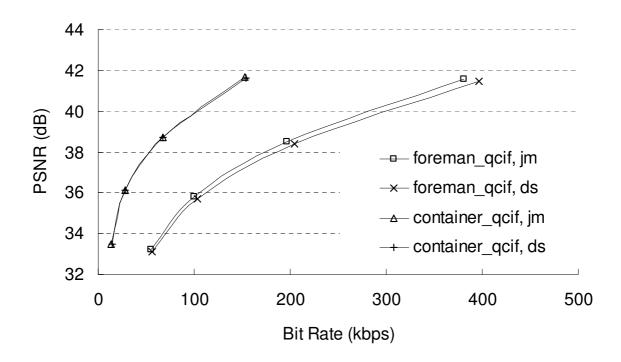

Figure 2.4 is the rate distortion (RD) curves of two qcif sequences. It is shown that 'mobile\_qcif' is more sensitive to MRF than 'football\_qcif'. The quality degradation of 'mobile\_qcif' with 1 and 5 reference frames is up to 1.5 dB, which is unacceptable for video coding system. In fact, from the features of sequences, it is shown that many textures are contained in 'mobile\_qcif' and sharp edges in the spatial domain will generate rich

Figure 2.3: Aliasing in Hybrid Video Coding

Figure 2.4: RD Curves of QCIF 'football' and 'mobile'

high frequency signals after Fourier transform. The abundant high frequency ingredient in 'mobile\_qcif' is the main reason of the occurrence of aliasing.

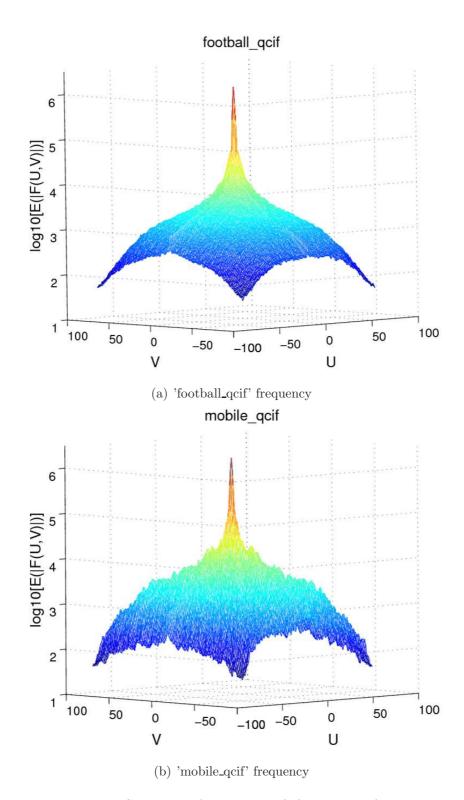

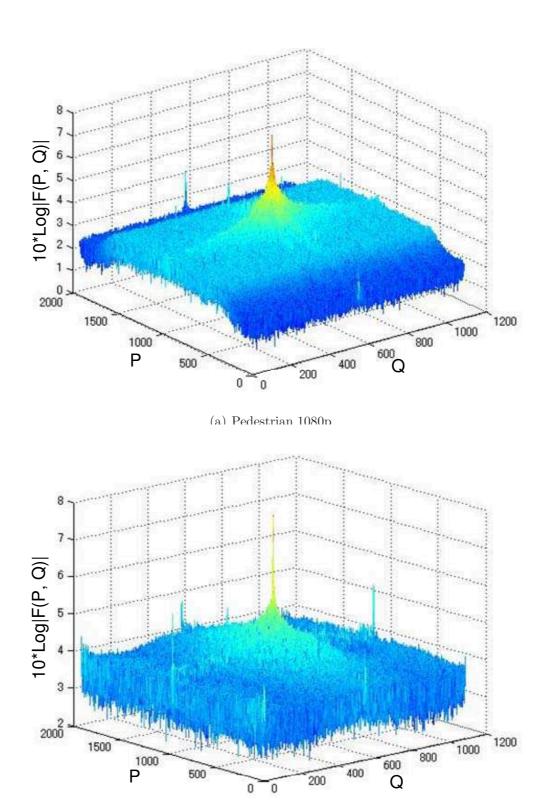

Figure. 2.5 is the 2-D Fourier spectrum amplitude of two sequences. Hamming window is used to compensate the spectrum leakage. The spectrum analysis obviously shows that high frequency signal in 'mobile\_qcif' is much more abundant than 'football\_qcif'. Thus, from the above theoretical analysis, it is proved that aliasing is the main reason of video quality degradation and Fourier spectrum can reflect the importance of MRF for video sequence.

The intuitive way of adjusting reference frame number is through analysis of Fourier spectrum. However, such kind of decision criterion is impractical because the compu-

Figure 2.5: 2-D Fourier Spectrum Amplitude of 'football\_qcif' and 'mobile\_qcif'

tation complexity will increase dramatically. In fact, the signal's frequency spectrum is coordinate with its gradient amplitude. Edge information in MB will reflect the spread of

| -1 | 0  | +1 |   | +1 | +2 | +1 |

|----|----|----|---|----|----|----|

| -2 | 0  | +2 |   | 0  | 0  | 0  |

| -1 | 0  | +1 |   | -1 | -2 | -1 |

|    | Gx | 1  | ı | L  | Gy | 1  |

Figure 2.6: Convolution mask of Sobel operator

frequency spectrum in that MB and gradient analysis is feasible to be used as a decision criterion. In the edge detection based reference frame elimination scheme, I use result of gradient amplitude of each MB to restrict number of reference frames.

#### 2.2.2 Gradient based multiple reference frame elimination

In edge detection field, there exist many operators. Among all of them, Sobel operator is widely used to get 2-D spatial gradient by emphasizing the edges which represent high spatial frequency. So, I use Sobel operator in the proposed fast algorithm. In fact, the Sobel operator is already applied in many mode decision algorithms [22][23][24] and its merit is proved by these algorithms. The convolution mask of Sobel edge detector is described in Fig. 2.6. In luminance picture, if P(m, n) denotes the pixel value at (m, n) position, as shown in Eq. 2.4 and Eq. 2.5, its gradients in x-direction and y-direction are  $G_x(m, n)$  and  $G_y(m, n)$ . G(m, n), which is the gradient of P(m, n) is calculated by addition of  $G_x(m, n)$  and  $G_y(m, n)$ , as shown in Eq. 2.6.

$$G_x(m,n) = |P(m-1,n-1) + 2P(m-1,n) + P(m-1,n+1) - P(m+1,n-1)$$

$$-2P(m+1,n) - P(m+1,n+1)|$$

(2.4)

$$G_y(m,n) = |P(m-1,n-1) + 2P(m,n-1) + P(m+1,n-1) - P(m-1,n+1)$$

$$-2P(m,n+1) - P(m+1,n+1)|$$

(2.5)

$$G(m,n) = G_x(m,n) + G_y(m,n)$$

(2.6)

$$\begin{cases}

G(m,n) < THR_G, & Homo \\

otherwise, & Non Homo

\end{cases}$$

(2.7)

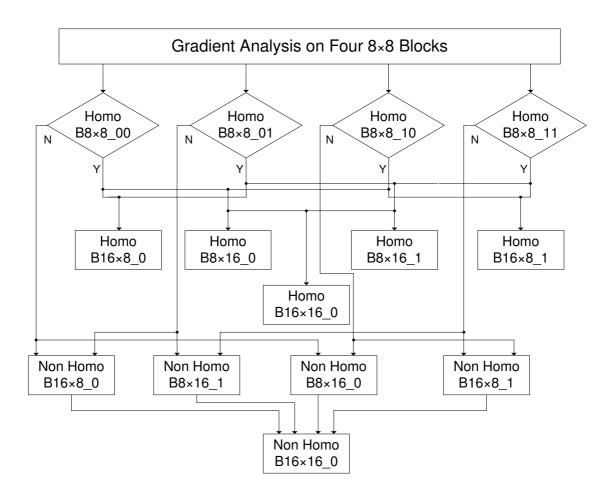

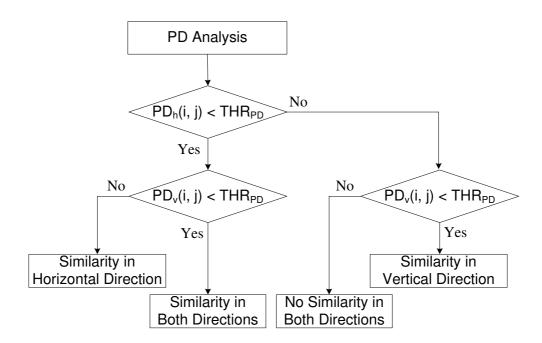

Figure 2.7 is the MB partition in H.264 VBSME algorithm. The edge detection criterion is applied base on the partition enclosed in dashed lines. The minimum block size in gradient analysis is  $8 \times 8$ . The block is regarded as homogeneous block if the analysis result is within certain threshold. Figure 2.8 is the flow chart of proposed edge gradient analysis procedure. Firstly, gradient analysis is executed on each  $8 \times 8$  block in the MB. One  $8 \times 8$  block is judged as homogeneous (Homo) block if it satisfies Eq. 2.7. Based on the result of four  $8 \times 8$  block, one  $16 \times 8$  block is judged as homo block if its sub  $8 \times 8$  blocks are all homo blocks. For example,  $B16 \times 8\_0$  is homo block if  $B8 \times 8\_00$  and  $B8 \times 8\_01$  are all homo blocks. The  $16 \times 16$  block is regarded as homo block only if all of its four sub  $8 \times 8$  blocks are homo blocks. Otherwise, it is treated as nonhomogeneous (Non Homo)  $16 \times 16$  block. Here, the setting of  $THR_G$  is a critical factor that affects both computation complexity and video quality. If the  $THR_G$  is set too high, the video quality will degrade greatly although complexity reduction can be achieved to some extent. On the other hand, too low  $THR_G$  can not release the intensive computation of MRF algorithm. In the following part, I will analyze the setting of  $THR_G$  in detail through experimental result. The edge gradient analysis is executed at the same time of loading pixels of current MB. It is finished before IME starts and will decides the reference frame number for the following block matching process.

Figure 2.7: MB partition in VBSME algorithm

#### 2.2.3 Quantization parameter based threshold adjustment

From the theoretical point of view, the threshold setting is always a trade-off between quality and complexity. The prediction error e in block matching process can be assumed as a jointly Gaussian source with zero mean and variance  $\sigma^2$ . According to [25], the distortion of quantization D is approximated as  $QP^2/3$ , where QP is the quantization parameter. So, the rate distortion function [26] can be represented as Eq. 5.12, where R(D) is the related transmission bit-rate for distortion D. The  $\sigma^2$  represents maximum distortion based on Gaussian model. When distortion D equals to zero, it indicates that original signal is reconstructed without any loss in image detail. All the information of image (including textures and noise) is exacted the same as original source image. Maximum transmission bit-rate is required for keeping the related information. In fact, such case is one ultimate state which will never happen in real video encoding system, like H.264/AVC. The reason is that the transform and quantization will cause some loss in image detail, which makes distortion between original source image and reconstructed one occur inevitably. On the other hand, when D is larger than  $\sigma^2$ , the related transmission bit-rate for D will become zero. This conclusion is in accordance with QP setting in H.264 encoding system. With the increase of QP, the smoothness of reconstructed frames

Figure 2.8: Edge gradient analysis flow chart

is increased, which results in decline of image's details. The related residue value is also decreased. It means that quality degradation for edge abundant image is quite obvious under big QP. In the extreme case, all the details are removed by one very large QP and the residue information is vanished, which indicates that no transmission bit-rate is required. Thus, from theoretical analysis of [25] and [26], the threshold can be simply regarded as linear relationship with QP value.

$$R(D) = \begin{cases} \frac{1}{2} log \frac{\sigma^2}{D}, & 0 \le D \le \sigma^2 \\ 0, & D > \sigma^2 \end{cases}$$

(2.8)

From the statistical point of view, exhaustive experiments are executed to get optimum threshold value. I apply edge gradient based reference frame elimination scheme on typical sequences. Since the setting of QP value will affect video quality which is represented by PSNR and bit-rate (BitR) variation, I define the  $\Delta PSNR$  and  $\Delta BitR$  as two tolerance 17

constraints under different QPs, as shown in Eq. 2.9. The  $PSNR_{pro}$  and  $BitR_{pro}$  represent the result based on proposed algorithm while  $PSNR_{jm}$  and  $BitR_{jm}$  are the result based on original JM full search algorithm. Equation, 2.9 can clearly show the PSNR and BitR difference of each point on RD curves.

$$\begin{cases}

\Delta PSNR = |PSNR_{pro} - PSNR_{jm}| \\

\Delta BitR = |10logBitR_{pro} - 10logBitR_{jm}|

\end{cases}$$

(2.9)

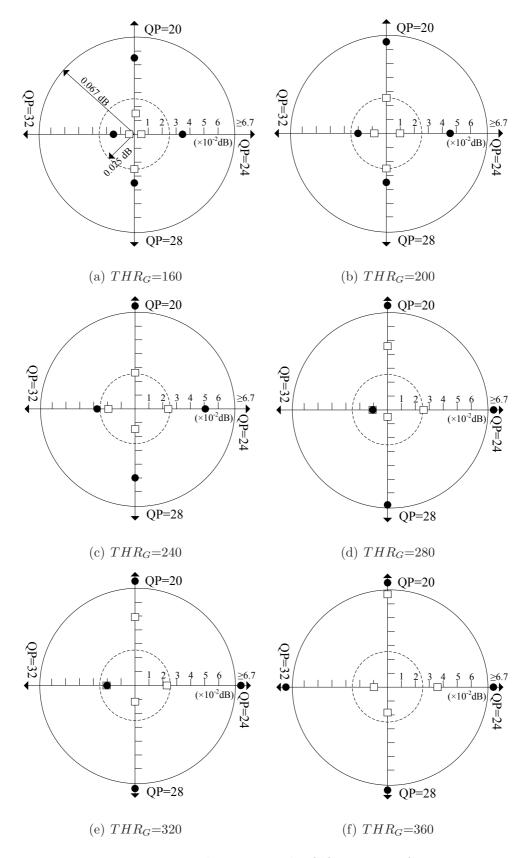

Several  $THR_G$  value is applied on typical MRF sensitive sequences to test the impact of  $THR_G$ . The sequences used are 'foreman\_qcif' and 'mobile\_qcif' which are both MRF sensitive sequences. Five reference frames are enabled and 200 frames are encoded under baseline profile. Table 2.1 is the experimental result with  $THR_G$  ranging from 160 to 360. On the whole, it is shown that for the same QP, the video quality degrades with the increase of  $THR_G$ . Specifically, for 'foreman\_qcif', if 0.067 dB is set as maximum tolerance constraint of PSNR loss and 0.025dB as maximum tolerance constraint of bit-rate gain, then it is shown that large  $THR_G$  is only suitable for big QP value. The data with asterisk represent the violation data against constraint. Figure 2.9 is the tolerance graph of 'foreman\_qcif' based on Table 2.1. It depicts the relationship of  $THR_G$ ,  $\Delta PSNR$ and  $\Delta BitR$ . Each black circle on the axle represents the  $\Delta PSNR$  under certain QP. Each white square represents the corresponding  $\Delta BitR$ . The solid circle line is the PSNR tolerance constraint while the broken circle line is the BitR constraint. Based on Table. 2.1 and Fig. 2.9, it is shown that when  $THR_G$  is set linearly with QP, maximum ME time can be achieved while video quality loss is under constraint. Different sequences have different tolerance degree. However, the linear relationship between  $THR_G$  and QP is the same for MRF sensitive sequences. For example, as shown in Table 2.1, if I set 0.03dB for PSNR constraint and 0.015dB for BitR constraint of 'mobile\_qcif', then it is also possible to get the linear relationship between QP and its  $THR_G$ . In fact, the increase of QP means that the reference frame will be more smooth so that the ratio of homo block is increased, which makes it reasonable to change  $THR_G$  according to QP. Therefore, I set the  $THR_G$ of edge gradient based reference frame number adjustment scheme as 10QP to achieve much ME time reduction while keep good video quality.

Table 2.1: Impact of  $THR_G$  on sequences

| S1, S   | 32 | $\Delta PSNR$ | $\times 10^{-2} (dB)$ $\Delta BitR(dB) \times 10^{-2} (dB)$ |      |       | $MET_R$ (%) |       |

|---------|----|---------------|-------------------------------------------------------------|------|-------|-------------|-------|

| $THR_G$ | QP | S1            | S2                                                          | S1   | S2    | S1          | S2    |

|         | 20 | 5.5           | 1.9                                                         | 1.5  | 0.6   | 56.10       | 56.55 |

| 160     | 24 | 3.5           | 0.8                                                         | 0.5  | 0.2   | 52.25       | 54.87 |

|         | 28 | 3.5           | 1.2                                                         | 2.5  | 0.6   | 48.17       | 53.17 |

|         | 32 | 1.5           | 1.6                                                         | 0.3  | 0.4   | 44.41       | 50.54 |

|         | 20 | 6.3           | 1.8                                                         | 2.5  | 1.4   | 57.32       | 57.50 |

| 200     | 24 | 4.6           | 2.4                                                         | 1.1  | 0.7   | 54.36       | 55.61 |

|         | 28 | 3.5           | 1.7                                                         | 2.5  | 0.4   | 50.45       | 53.18 |

|         | 32 | 2.0           | 0.8                                                         | 0.9  | 1.9   | 45.83       | 51.23 |

|         | 20 | *7.0          | *3.2                                                        | *2.6 | *1.6  | 60.18       | 58.25 |

| 240     | 24 | 5.2           | 2.7                                                         | 0.2  | 0.7   | 56.89       | 56.73 |

|         | 28 | 5.0           | 1.9                                                         | 1.4  | 0.5   | 53.15       | 55.07 |

|         | 32 | 2.8           | 0.6                                                         | 2.0  | 0.3   | 49.44       | 52.34 |

|         | 20 | *7.4          | *3.8                                                        | *4.7 | *3.1  | 62.62       | 59.11 |

| 280     | 24 | *6.8          | *3.8                                                        | *2.6 | 1.2   | 59.97       | 57.10 |

|         | 28 | 6.7           | 2.4                                                         | 0.5  | 0.4   | 56.03       | 55.63 |

|         | 32 | 1.1           | 0.1                                                         | 2.0  | 0.1   | 52.74       | 53.54 |

|         | 20 | *8.4          | *4.5                                                        | *4.8 | *6.7  | 64.39       | 60.45 |

| 320     | 24 | *7.4          | *5.5                                                        | 2.4  | *4.8  | 62.03       | 58.85 |

|         | 28 | *6.8          | *3.8                                                        | 0.6  | *3.5  | 58.43       | 57.20 |

|         | 32 | 2.0           | 1.6                                                         | 2.2  | 1.4   | 54.81       | 55.43 |

|         | 20 | *8.7          | *6.1                                                        | *6.3 | 0.117 | 65.62       | 62.49 |

| 360     | 24 | *7.8          | *7.7                                                        | *3.8 | 0.109 | 63.54       | 60.74 |

|         | 28 | *9.0          | *6.9                                                        | 1.7  | *6.6  | 59.96       | 59.19 |

|         | 32 | *7.5          | *6.6                                                        | 1.1  | 1.2   | 56.19       | 57.15 |

S1: foreman\_qcif, S2: mobile\_qcif

Figure 2.9: Tolerance graph of 'foreman\_qcif'

# 2.2.4 Similarity-analysis based multiple reference frame elimination

In H.264/AVC based real-time encoding systems, the widely adopted ME algorithm is a full search algorithm that provides regular access to memory, predictable control, and the optimal video quality [20]. In full search algorithm, the sum of the absolute difference (SAD) is selected as a criterion to determine the best position on the reference frame plane. It is obvious that considerable computational resources are wasted because only the MV that has minimum cost is stored while other MVs are discarded at the end of the search process. This wasteful situation becomes more significant if the MRF algorithm is introduced. In fact, since many static parts exist in each sequence, the computation of all search positions is not always necessary. In this section, statistical analysis of typical sequences will be given out and one similarity analysis (SA) based multiple reference frame elimination scheme is proposed.

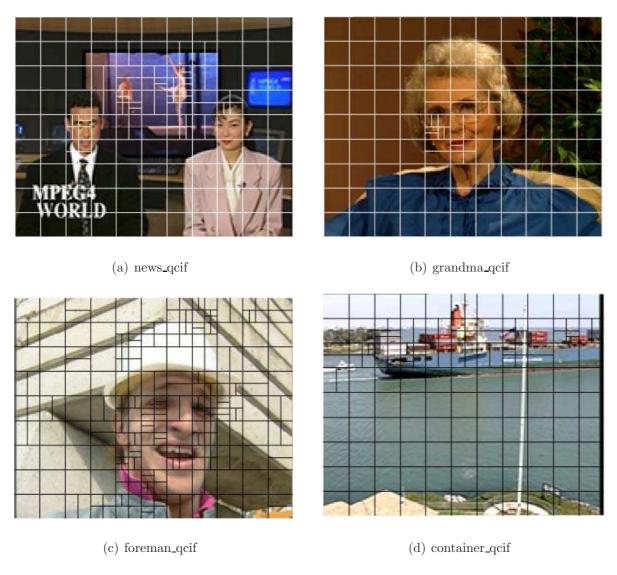

To simplify the statistical analysis, I select 'foreman\_qcif', 'news\_qcif', 'grandma\_qcif', and 'container\_qcif' as four typical sequences and extract the final coding mode for a certain frame. Figure. 2.10 shows the tracing result. The different sizes of black and white boxes overlaid on the images represent different block modes that are chosen after rate distortion (RD) optimization. It is shown that, if a large region has a similar trend of motion, it is more likely to be coded with a large block size. In detail, for sequences such as 'container\_qcif' and 'grandma\_qcif', there are many temporal stationary background parts which are mostly coded by a large blocks. Rapid moving parts such as the dancer in 'news\_qcif' and the facial expression in 'grandma\_qcif' are coded in small blocks. Although the lady's suit in 'news\_qcif' contains a large amount of edge information, it is also coded by large blocks because it is treated as stationary background. In the case of 'foreman\_qcif', even though many background MBs exist in the sequence, many MBs are still coded with small blocks because of the facial expression and the dithering of the vidicon.

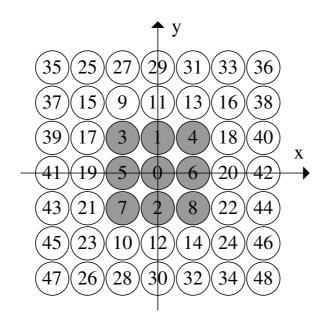

In JM software, the hardware-friendly full search algorithm is executed on different search positions. It adopts the spiral searching method, which searches from the center

Figure 2.10: Coding block sizes of QCIF sequences

to the outside positions. Figure 2.11 shows an example of spiral-order graph for the first 49 positions. The number in the circle represents the searching order. Position 0 is the motion vector predictor (MVP) point, which is calculated on the basis of neighboring blocks. The block matching process of ME starts from this position. The position that has the minimum cost (MV cost + SAD) is regarded as the best integer search position (BISP) and its corresponding MV is stored. From the previous analysis, it is known that for sequences with a large stationary part, the probability of selecting a big coding mode is very high. Therefore, if an MB with a stationary feature can be detected at an early stage, the ME computation can be reduced because splitting of the MB into small modes

Figure 2.11: Spiral search order

and the MRF technique are both unnecessary for such an MB.

Figure. 2.12 shows the ratio of MBs whose BISP fall into the MVP position (call such MBs as MVP\_MBs). Here, I only show histograms for the P16×16 mode and for the first block (block\_0) of the P16×8 and P8×16 modes. Since there is considerable similarity among the MRFs, only distribution of MVP\_MBs in the previous reference frame is given out. The simulation conditions are listed in Table. 2.2. First, note that the distribution in Fig. 2.12(a) is very similar to those in Fig. 2.12(b) and Fig. 2.12(c). This similarity also occurs among Fig. 2.12(d), Fig. 2.12(e), and Fig. 2.12(f), which means that the features of the sequence are similarly among the P16×16, P16×8, and P8×16 modes. To reduce the computation complexity, I only focus on the P16×16 mode of the first reference frame in my algorithm. Second, for sequences such as 'container\_qcif/cif', 'grandma\_qcif', and 'news\_qcif/cif', many MBs have their best position in the MVP point, which means that the initial MVP is of high accuracy. On the other hand, for sequences such as 'football\_qcif/cif' and 'canoa\_cif', the percentage of MVP\_MBs is low. Thus, the accuracy of the MVP can reflect the characteristics of MBs in different sequences.

Moreover, even though the current MB selects position 0 as the BISP on the previous reference frame, the final best mode may vary among the SKIP mode, and the  $P16\times16$ ,

Figure 2.12: Number of MBs with BISP in MVP

P16×8, P8×16, and P8×8 modes due to more accurate matching under other modes. Here, the inter search modes below 8×8 are also included in P8×8 mode when determining the final best mode in the H.264/AVC standard. Therefore, for MVP\_MB, the final best macroblock mode is traced for different quantization parameters (QPs). The experimental result is shown in Fig. 2.13. Here, I list the results of 3 QCIF and 3 CIF sequences as

Table 2.2: Simulation conditions for BISP on previous frame

| Sequences    | QCIF & CIF                            | QP             | 20  |  |  |

|--------------|---------------------------------------|----------------|-----|--|--|

| Search Range | $\pm$ 16 & $\pm$ 24                   | Frames Encoded | 200 |  |  |

| etc          | no B Slice, CAVLC, 5 Reference Frames |                |     |  |  |

|              | RDO is ON, GOP is IPPP                |                |     |  |  |

The x axis represents the SAD value range in the MVP position while the y axis is the percentage of MB quantities. Specifically, the histogram reflects the percentage of MVP\_MB quantities under different QP and SAD values. For sequences with many stationary parts such as 'container\_qcif/cif' and 'news\_qcif/cif', many MBs select the MVP as the best search position when QP is small. With increasing SAD value at position 0, the ratio of MVP\_MBs decreases; on the other hand, for big QP, this ratio increases rapidly with the SAD value. In the case of sequences with a large amount of motion such as 'football\_qcif/cif', the initial MVP is inaccurate and most MVP\_MBs have a large SAD value. The curves overlaid on the histogram represent the ratio of MBs whose final coding mode is big mode (SKIP mode, P16×16, P16×8, or P8×16), which means that the MBs are coded in the big mode with less MB splitting. From Fig. 2.13, it is shown that the ratio of MVP<sub>-</sub>MBs whose final mode is the big mode decrease rapidly in the case of small QP such as 16 and 20. In case of a big QP, this ratio decreases slowly. In fact, for a big QP, after the quantization and reconstruction of reference frames, the reference pixels become more homogeneous with a considerable loss of high-frequency components, which leads to big coding modes after RD.

$$SA \ on \ ref_1 \ (SP0 \ to \ SP8, P16 \times 16 \ Mode)$$

$$\begin{cases} BISP = 0 \ \& \ SAD_{8\times 8} \leq THR_{SAD}, BMMB \\ otherwise, NMB \end{cases} \tag{2.10}$$

On the basis of the above analysis, the ME and mode decision process can be sped-up for sequences with many stationary parts. I use a threshold  $(THR_{SAD})$  to indicate the degree of similarity of IME in the first reference frame  $(ref_1)$  and use it to guide the result of mode decision. To reduce the extra computation that is introduced into the ME process, I only focus on the P16×16 mode in my algorithm. The SA-based big-mode MB  $^{25}$

Figure 2.13: Distribution of final best mode

(BMMB) detection scheme is shown in Eq. 2.10. It means that during the IME process, the SA is performed on the 9 central positions of  $ref_1$  (the gray circles in Fig. 2.11). The MB is defined as a BMMB if its BISP at these 9 positions is 0 and all four of its 8×8 sized SAD  $(SAD_{8\times8})$  values are within  $THR_{SAD}$ ; otherwise it is treated as a normal MB (NMB). For a BMMB, the IME process is early terminated after IME of P16×16, P16×8, and P8×16 modes for the 9 central positions of the previous frame; and only big modes are

enabled during mode decision stage. On the basis of experimental results, the threshold is defined according to the QP value. In detail, when QP is less than 24,  $THR_{SAD}$  is set as  $6\times$ QP, otherwise it is set as  $7\times$ QP.

#### 2.3 Hardware oriented search range adjustment

In the H.264/AVC motion estimation, search range is another important factor which influence the computation complexity greatly. For example, when search range (SR) is decided, the number of search points can be calculated based on Eq. 2.11, where  $SP_{num}$  is the number of search point and SR is the dedicated search range. So, when SR equals 24, the  $SP_{num}$  will become 2401 which is a quite large number for hardware engine. Therefore, hardware oriented search range adjustment scheme is needed.

$$SP_{num} = (2SR + 1) \times (2SR + 1)$$

(2.11)

#### 2.3.1 Motion feature based search range adjustment

In H.264/AVC based encoding system, different sequences have different features; a large SR is not necessary for all sequences. Figure 2.14 shows two RD curves under different SR. It is shown that changing the SR does not cause significant video quality loss in 'foreman\_qcif'. On the other hand, the quality degradation in the case of 'football\_qcif' is very obvious, which means that a big SR is necessary for 'football\_qcif'.

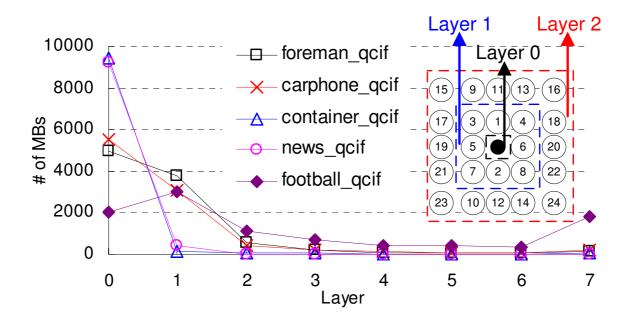

For MB with different motion (small or large motion), complexity reduction can be achieved based on the motion feature analysis. Since different type of sequences may have different best integer search point (BISP) distributions, I trace BISP result on each reference frames under  $16 \times 16$  mode, as shown in Table. 2.4. The simulation conditions are shown in Table. 2.3.

Firstly, it is shown that BISP distribution of the same sequence among different reference frames demonstrates the same motion feature. For example, in 'container\_qcif', the BISP distribution in first reference frame shows that many BISPs are located within centering 25 positions, the situation of which is almost the same with BISP distributions

Figure 2.14: Impact of search range to video quality

in other four reference frames. So the BISP distribution in first reference frame can represent the motion feature of this MB and I only focus on the first reference frame in my search range adjustment scheme.

Secondly, Table. 2.4 show that the BISP distribution of 'football\_qcif' is different from other 4 sequences. The BISPs located between 169th and 1088th position are much more than other 4 sequences, which shows its large motion trend. It also implies that the initial motion vector predictor (MVP) is far from accurate for 'football\_qcif'.

Thirdly, for sequences except 'football\_qcif', large proportion of BISPs are located within the inner 25 position, which shows the small motion trend. Comparing 'fore-man\_qcif' and 'carphone\_qcif' with 'container\_qcif' and 'news\_qcif', the proportion of BISPs that are located in position 0 is much smaller in 'foreman\_qcif' and 'carphone\_qcif'. It means that there are many static background MBs in 'container\_qcif' and 'news\_qcif' and MVP is of high accuracy for motion estimation in these sequences.

Therefore, from the statistic analysis of typical sequences, it is shown that the BISP location can reflect the motion feature of the MB. For MB with big motion, large search range is necessary to keep the overall best search point within available search range. On the other hand, for MB which shows static or small motion feature, many redundant

Table 2.3: Simulation conditions for BISP on five reference frames

| QP           | 24                                    | Sequences | qcif |  |  |

|--------------|---------------------------------------|-----------|------|--|--|

| Search Range | $\pm 16$ Frames Encoded               |           | 100  |  |  |

| etc          | no B Slice, CAVLC, 5 Reference Frames |           |      |  |  |

|              | RDO is ON, GOP is IPPP                |           |      |  |  |

search points exist in reference frames, which occupy much computation during motion estimation.

There exist many MV oriented search range adjustment algorithms [15][14]. However, implementing these algorithms will cause huge storage for MVs of former frames, which deteriorates the efficiency of system. Instead of analyzing MV, I use the motion feature which is extracted from IME process to guide search range adjustment process. Since small blocks contain less texture and are prone to be trapped into local optimum position, I just do motion feature analysis on  $16 \times 16$  mode. Based on the above analysis, the proposed motion feature analysis based search range adjustment scheme concludes 2 key steps:

- 1. In the first reference frame, VBSME in full search range is executed. The initial search range  $(SR_{JM})$  for QCIF, CIF and HDTV720p sequences are  $\pm 16$ ,  $\pm 24$  and  $\pm 64$  in both width and height.

- 2. After IME with first reference frame on  $16 \times 16$  mode, check BISP. If BISP is smaller than  $\pm 1/8$   $SR_{JM}$ , which means that MVP's accuracy is high, the search range is adjusted to  $\pm 1/8$  original search range in both width and height for rest ME process. With the decrease of search range on rest reference frames, much computation is saved.

#### 2.3.2 Recursive 6-ring search range adjustment

On the basis of statistical analysis of previous sub-section, the search range can be further adjusted for MBs of different motion feature on the first reference plane. In my algorithm, I divide the SR into 6 rings, as shown in Fig. 2.15. The scale of search range in the x direction and y direction is  $SR_{jm}/16$ , where  $SR_{jm}$  is the general SR in JM software (16 for QCIF and 24 for CIF). Since small inter modes tend to fall into local minimum, I only apply SR adjustment scheme based on BISP in the  $16\times16$  mode. The proposed scheme

#### 2.3 Hardware oriented search range adjustment

Table 2.4: BISP Distribution on 1st to 5th Reference Frame

| IME on 1st Reference Frame |       |       |       |       |       |  |

|----------------------------|-------|-------|-------|-------|-------|--|

| BISP                       | Seq 1 | Seq 2 | Seq 3 | Seq 4 | Seq 5 |  |

| 0                          | 4961  | 5556  | 9434  | 9263  | 2040  |  |

| 1~8                        | 3749  | 3095  | 159   | 433   | 2996  |  |

| 9~24                       | 564   | 436   | 38    | 34    | 1090  |  |

| $25{\sim}48$               | 204   | 235   | 64    | 17    | 706   |  |

| 49~80                      | 100   | 107   | 7     | 10    | 454   |  |

| 81~120                     | 53    | 74    | 7     | 6     | 388   |  |

| $121{\sim}168$             | 43    | 71    | 5     | 4     | 321   |  |

| 169~1088                   | 127   | 227   | 87    | 34    | 1806  |  |

|              | IME on | 2nd Refe | rence Fra | ıme   |       |

|--------------|--------|----------|-----------|-------|-------|

| BISP         | Seq 1  | Seq 2    | Seq 3     | Seq 4 | Seq 5 |

| 0            | 2827   | 4008     | 9183      | 8511  | 654   |

| 1~8          | 4624   | 3453     | 261       | 950   | 632   |

| 9~24         | 1375   | 1051     | 50        | 106   | 691   |

| $25{\sim}48$ | 439    | 499      | 85        | 35    | 857   |

| 49~80        | 175    | 191      | 13        | 16    | 748   |

| 81~120       | 79     | 135      | 9         | 14    | 646   |

| 121~168      | 43     | 82       | 8         | 11    | 798   |

| 169~1088     | 140    | 283      | 93        | 59    | 4674  |

|                 | IME on | ara Keie | rence Fra | ıme   |       |

|-----------------|--------|----------|-----------|-------|-------|

| BISP            | Seq 1  | Seq 2    | Seq 3     | Seq 4 | Seq 5 |

| 0               | 1972   | 3510     | 8826      | 7916  | 471   |

| 1~8             | 3612   | 3151     | 473       | 1191  | 369   |

| $9 \sim 24$     | 1997   | 1247     | 63        | 269   | 390   |

| $25{\sim}48$    | 985    | 697      | 102       | 65    | 471   |

| $49 \sim 80$    | 436    | 342      | 12        | 27    | 510   |

| 81~120          | 236    | 192      | 18        | 25    | 551   |

| $121 \sim 168$  | 115    | 116      | 10        | 19    | 599   |

| $169 \sim 1088$ | 250    | 348      | 99        | 91    | 6242  |

|                 | IME on | 4th Refe | rence Fra | ıme   |       |

|          |       |       | TCHCC 116 |       |       |

|----------|-------|-------|-----------|-------|-------|

| BISP     | Seq 1 | Seq 2 | Seq 3     | Seq 4 | Seq 5 |

| 0        | 1345  | 3141  | 8102      | 7563  | 391   |

| 1~8      | 2994  | 2942  | 1036      | 1118  | 281   |

| 9~24     | 1865  | 1321  | 88        | 459   | 297   |

| 25~48    | 1341  | 666   | 127       | 140   | 381   |

| 49~80    | 799   | 446   | 17        | 51    | 375   |

| 81~120   | 405   | 303   | 19        | 34    | 419   |

| 121~168  | 277   | 213   | 13        | 16    | 485   |

| 169~1088 | 478   | 472   | 102       | 123   | 6875  |

|                | IME on | 5th Refe | erence Fra | ıme   |       |

|----------------|--------|----------|------------|-------|-------|

| BISP           | Seq 1  | Seq 2    | Seq 3      | Seq 4 | Seq 5 |

| 0              | 1073   | 2917     | 6936       | 7389  | 335   |

| 1~8            | 2547   | 2604     | 2014       | 977   | 238   |

| 9~24           | 1734   | 1412     | 127        | 469   | 232   |

| $25{\sim}48$   | 1233   | 753      | 147        | 281   | 312   |

| 49~80          | 976    | 373      | 21         | 73    | 356   |

| 81~120         | 600    | 358      | 26         | 49    | 354   |

| $121 \sim 168$ | 397    | 275      | 18         | 14    | 427   |

| 169~1088       | 845    | 713      | 116        | 153   | 7151  |

Seq 1: foreman, Seq 2: carphone, Seq 3: container

Seq 4: news, Seq 5: football

Figure 2.15: 6-Ring search range adjustment

is given in Eq. 2.12. After IME on the  $m_{th}$  reference frame  $(ref_m)$ , the BISP of this frame (BISP(m)) in the  $16\times16$  mode is analyzed. If it is between the values of  $SP_{num}$  for  $SR_i$  and  $SR_{i+1}$ , then the SR in the  $(m+1)_{th}$  reference frame (SR(m+1)) is changed to  $SR_{i+2}$ . If the BISP(m) value surpasses the  $SP_{num}$  of  $SR_5$  in Fig. 2.15, then original JM SR is used for next ME process. The proposed search range scheme adaptively shrinks the SR for small-motion MBs. For normal or big motion MB, large SR value is still available to keep the best MV.

$$After IME on ref_m, m \in [1, 4]$$

$$\begin{cases}

(2SR_i + 1)^2 \le BISP(m) < (2SR_{i+1} + 1)^2, \\

SR(m+1) = SR_{i+2}, i \in [0, 4] \\

BISP(m) > (2SR_5 + 1)^2, \\

SR(m+1) = SR_{jm}

\end{cases}$$

(2.12)

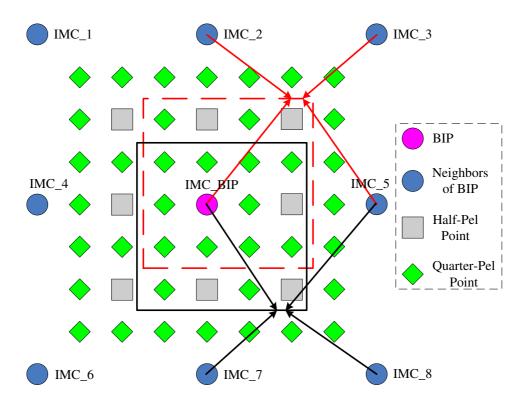

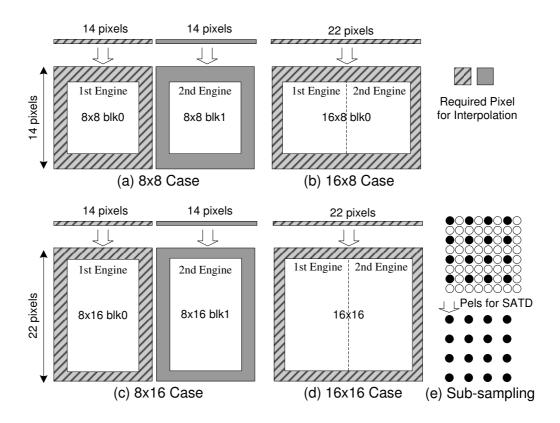

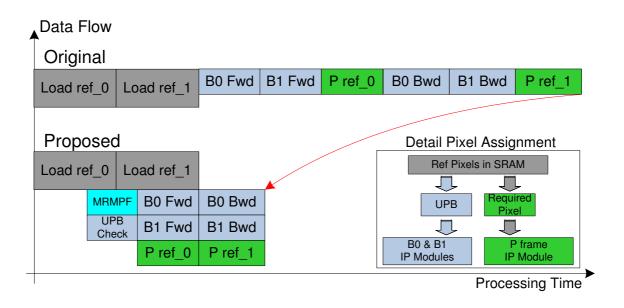

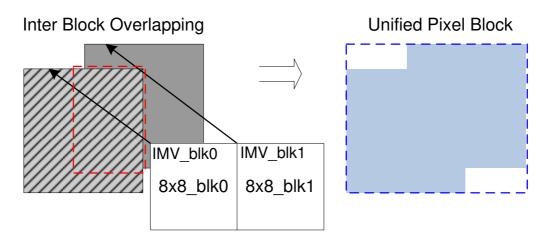

### 2.4 Pixel difference based adaptive sub-sampling