# DESIGNING POWER AWARE WIRELESS SENSOR NETWORKS LEVERAGING SOFTWARE

# MODELING TECHNIQUES

#### JOHN KHALIL JACOUB

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

at

University of Ontario

Institute of Technology

March 2014

#### **Abstract**

Wireless Sensor Networks (WSNs) are typically used to monitor specific phenomena and gather the data to a gateway node, where the data is further processed. WSNs nodes have limited power resources, which require developing power efficient systems. Additionally, reaching the nodes after a deployment to correct any design flaws is very challenging due the distributed nature of the nodes. The current development of WSNs occurs at the coding layer, which prevent the design from going through a typical software design process. Designing and analyzing the software modules of a WSN system at a higher abstraction layer than at the coding level will enable the designer of a WSN to fix any design errors and improve the system for power consumption at an early design stage, before the actual deployment of the network.

This thesis presents multiple Unified Modeling Language (UML) design patterns that enable the designer to capture the structure and the behavior of the design of a WSN at higher abstraction layers. The UML models are developed based on these design patterns that are capable of early validation of the functional requirements and the power consumption of the system hardware resources by leveraging animation and instrumentation of the UML diagrams.

To support the analysis of power consumption of the communication components of a WSN node, the Avrora network simulator was integrated with the UML design environment such that designer is able to analyze the power consumption analysis of the communication process at the UML layer. The UML and the Avrora simulation integration is achieved through developing a code generator that produces the necessary configuration for Avrora simulator and through parsing the simulator results. The methodology presented in this thesis is evaluated by demonstrating the power analysis of a typical collector system.

*Keywords*: Wireless Sensor Networks, Power Consumption and Analysis, Design Patterns, UML System Modeling, UML model execution

# **Author's Statement**

I, John Khalil Jacoub, hereby certify that I have prepared this Ph.D. thesis independently, and that only those sources, aids, and advisors that are duly noted herein have been used and/or consulted.

Signed this 25<sup>th</sup> day of April, 2014:

John Khalil Jacoub

#### **Acknowledgments**

I would like to thank my supervisor Dr. Ramiro Liscano for giving me the opportunity to pursue my Ph.D. degree under his supervision. I would like to express my sincere gratitude and appreciation for Dr. Liscano for his valuable advice, time, and encouragement he provided during these past five years. I would to extend my appreciation to my co-supervisor Dr. Jeremy Bradbury for his guidance and helpful recommendations throughout the thesis work. Thank you to the University of Ontario Institute of Technology (UOIT) and the Faculty of Engineering for offering me the facilities to complete my research.

A very special thank you to my lovely wife, Mrs. Laura Jacoub, for her love, support, patience, and faith in me. She has played an important role in revising and enhancing the thesis structure. Her support and encouragement were always motivating me to complete the thesis. Thank you for standing by me as I worked long hours to complete this degree.

I also wish to thank my parents, Dr. Khalil Jacoub and the late Mrs. Magda Jacoub, for their support, love, and for guiding me to be the man I am today. My parents have always been a source of encouragement and supported me to pursue higher education. I would like to extend my gratitude to my brother Dr. George Jacoub and my sister-in law Mrs. Michaela Jacoub for guiding me to apply for Ph.D. opportunities in Canada and for helping me to establish my life here.

Finally, but most importantly, I thank and praise my Lord Jesus Christ for His support spiritually and unwavering help every day in all conditions. Thank you, God, for blessing me and giving me the strength and perseverance to complete my Ph.D. degree. For "I can do all things through Christ who strengthens me" Philippians 4:13.

# Content

| Abstractii                                 |

|--------------------------------------------|

| Author's Statement                         |

| Acknowledgmentsv                           |

| Contentvi                                  |

| List of Tablesxiii                         |

| List of Abbreviations and Symbolsxiv       |

| 1. Introduction                            |

| 1.1 Motivation                             |

| 1.2 Thesis Statement and Scope of Research |

| 1.2.1 Problem Statement                    |

| 1.2.2 Thesis Statement                     |

| 1.3 Thesis Methodology and Contribution    |

| 1.3.1 Thesis Methodology                   |

| 1.3.2 Thesis Contribution                  |

| 1.4 Tools leveraged in the thesis          |

| 1.4.1 IBM Rational Rhapsody                |

| 1.4.2 Avrora Simulator                     |

| 1.5 Thesis Structure                       |

| 2. Background                              |

|    | 2.1  | WSN Structure                                                           | 16 |

|----|------|-------------------------------------------------------------------------|----|

|    | 2.2  | WSN Power Consumption                                                   | 18 |

|    | 2.3  | WSN Modeling                                                            | 19 |

| 3. | Mod  | deling Techniques for Wireless Sensor Networks                          | 21 |

|    | 3.1  | Introduction                                                            | 21 |

|    | 3.2  | Modeling Techniques Overview                                            | 22 |

|    | 3.2. | 1 High-Level SDL Models (HL-SDL)                                        | 22 |

|    | 3.2. | 2 Insense                                                               | 23 |

|    | 3.2  | 3 MathWorks Modeling Approach                                           | 23 |

|    | 3.2. | 4 Model Driven Engineering Approach (MDEA)                              | 24 |

|    | 3.2  | 5 Promela and the SPIN Model Checker for WSNs (PM)                      | 25 |

|    | 3.2. | 6 SensorML                                                              | 25 |

|    | 3.2. | 7 SystemC-AMS                                                           | 26 |

|    | 3.2. | 8 UM-RTCOM Model                                                        | 26 |

|    | 3.2. | 9 eXtended Reactive Modules (XRM)                                       | 27 |

|    | 3.3  | Overview from the Node's Software Architecture Perspective              | 27 |

|    | 3.4  | Overview from the System's Architecture Perspective                     | 29 |

|    | 3.5  | Model and Simulation Integration                                        | 30 |

|    | 3.6  | Concluding Remarks for the Review                                       | 31 |

| 4. | UM   | L Modeling and Power Consumption Analysis for Wireless Sensor Networks. | 35 |

|   | 4.1   | Introduction                                                      | 35 |

|---|-------|-------------------------------------------------------------------|----|

|   | 4.2   | WSN Systems Design Architecture                                   | 36 |

|   | 4.3   | Design Patterns for Wireless Sensor Networks                      | 39 |

|   | 4.3.1 | Sensor Node Service Component Design Pattern                      | 39 |

|   | 4.3.2 | 2 Sensor Node Event Handler Design Pattern                        | 42 |

|   | 4.3.3 | Association of the Application Software and OS Support Components | 46 |

|   | 4.4   | State-Chart Stereotypes                                           | 49 |

|   | 4.5   | Analysis in the UML Model Layer                                   | 50 |

|   | 4.5.1 | Instrumentation of State-Charts for Power and Timing Annotation   | 51 |

|   | 4.5.2 | 2 Model Execution                                                 | 53 |

|   | 4.6   | Summary and Limitations                                           | 57 |

| 5 | Gen   | erating TinyOS code for UML High Level Models                     | 60 |

|   | 5.1   | Introduction                                                      | 60 |

|   | 5.2   | TinyOS Code Structure                                             | 61 |

|   | 5.2.1 | Component Wiring                                                  | 62 |

|   | 5.2.2 | 2 Event Handlers                                                  | 63 |

|   | 5.3   | Code Generator Structure                                          | 65 |

|   | 5.3.1 | XML Parser                                                        | 65 |

|   | 5.3.2 | 2 Database Structure                                              | 66 |

|   | 5.3.3 | 3 Code Builder                                                    | 68 |

|   | 5.4   | Instrumentation of the Generated Code                                       | 70 |

|---|-------|-----------------------------------------------------------------------------|----|

|   | 5.4.  | 1 Code validation instrumentation                                           | 70 |

|   | 5.4.2 | 2 Instrumentation to Facilitate the Integration of the Simulator to the UML |    |

|   | mod   | lel                                                                         | 71 |

|   | 5.5   | Code Generation and Instrumentation Example                                 | 73 |

|   | 5.6   | Validating the generated Code                                               | 77 |

|   | 5.7   | Summary                                                                     | 81 |

| 5 | Integ | gration of the Simulator and the UML Models                                 | 83 |

|   | 6.1   | Introduction                                                                | 83 |

|   | 6.2   | The Parsing Tool                                                            | 84 |

|   | 6.3   | Integrating Simulation results with UML Model Example                       | 87 |

|   | 6.4   | Summary                                                                     | 89 |

| 7 | Eval  | luation                                                                     | 90 |

|   | 7.1   | Introduction                                                                | 90 |

|   | 7.2   | Power Consumption Improvement                                               | 91 |

|   | 7.3   | SensIV System Design                                                        | 93 |

|   | 7.3.  | 1 SensIV System Requirements and Specifications                             | 93 |

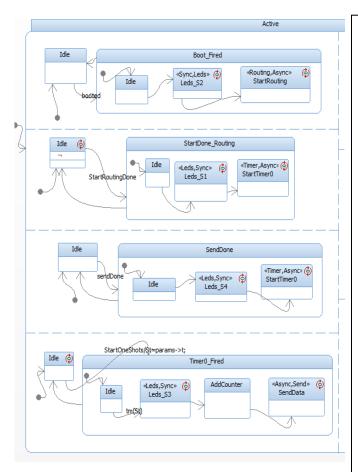

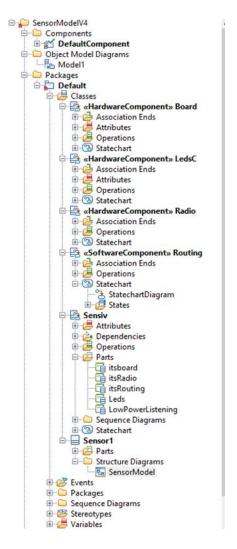

|   | 7.3.2 | 2 UML Models for SensIV System                                              | 94 |

|   | 7.3.3 | 3 SensIV Analysis at the Modeling Layer                                     | 00 |

|   | 7.3.4 | 4 Power Consumption Analysis of the WSN Network                             | 02 |

|    | 7.3.5 | Network Analysis Accuracy               | 122  |

|----|-------|-----------------------------------------|------|

| 7  | .4    | Framework Automation                    | 122  |

| 7  | .5    | Framework Generality                    | 124  |

|    | 7.5.1 | UML Model and Code Generator Generality | 125  |

|    | 7.5.2 | 2 The Generality of the Leveraged Tools | 126  |

| 7  | .6    | Threats to Validity                     | 127  |

|    | 7.6.1 | Monitored Data Type                     | 127  |

|    | 7.6.2 | 2 Data Collection Protocols             | 128  |

|    | 7.6.3 | Fault Tolerance Capability              | 128  |

|    | 7.6.4 | Hardware Constraints                    | 129  |

|    | 7.6.5 | Network Topology                        | 129  |

|    | 7.6.6 | Software Design                         | 130  |

| 7  | .7    | Summary                                 | 131  |

| 8  | Sum   | mary and Conclusion                     | 133  |

| 8  | .1    | Summary                                 | 133  |

| 8  | .2    | Thesis Contribution                     | 133  |

| 8  | .3    | Future Work                             | 135  |

| 9  | Refe  | prence                                  | I    |

| 10 | App   | endicesV                                | VIII |

# **List of Figures**

| Figure 1-1: Thesis Methodology Diagram                                            | 13 |

|-----------------------------------------------------------------------------------|----|

| Figure 4-1: Modeling, Verification, and Analysis at the Model Layer               | 36 |

| Figure 4-2: State-chart of Sensor Hardware Module                                 | 42 |

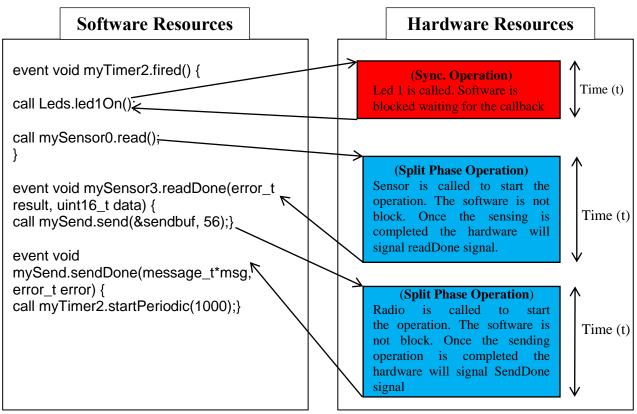

| Figure 4-3: Split Phase Communication                                             | 44 |

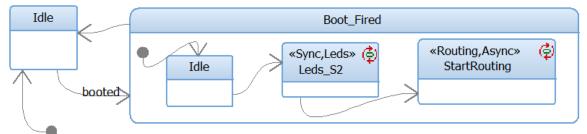

| Figure 4-4: Portion State-Chart for SensIV System                                 | 46 |

| Figure 4-5: RFID System Components                                                | 48 |

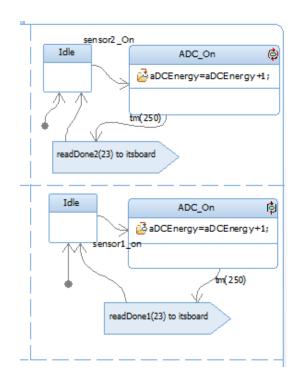

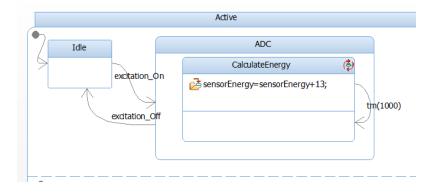

| Figure 4-6: ADC State-Chart Model                                                 | 52 |

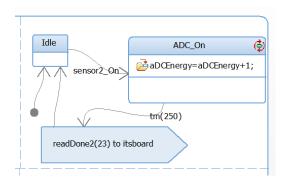

| Figure 4-7: Sensing State-Chart Model                                             | 52 |

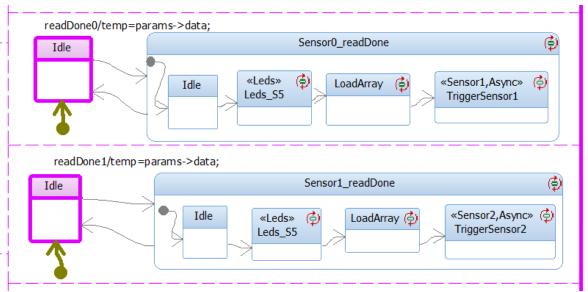

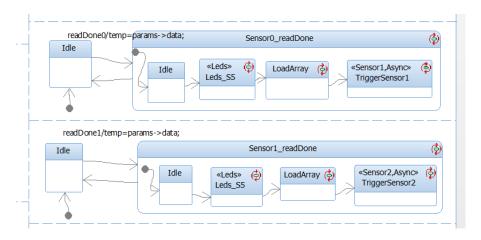

| Figure 4-8: Trigger Sensors State-Charts                                          | 53 |

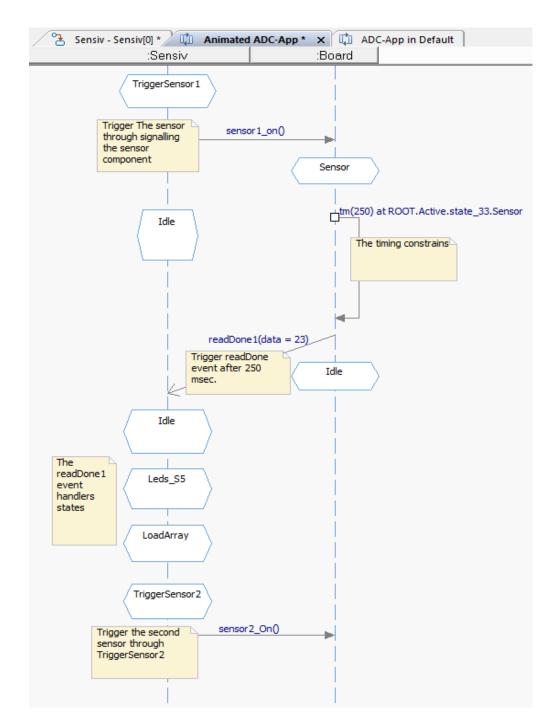

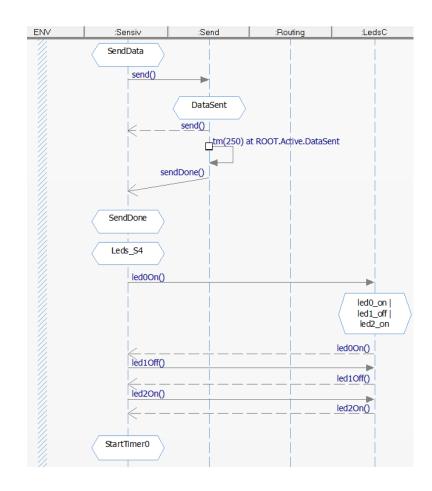

| Figure 4-9: Executed Sequence Diagram- Interaction between Application and Sensor |    |

| Component                                                                         | 54 |

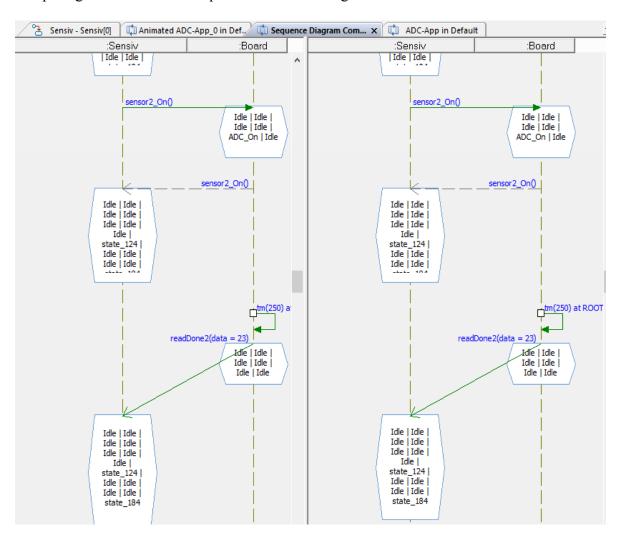

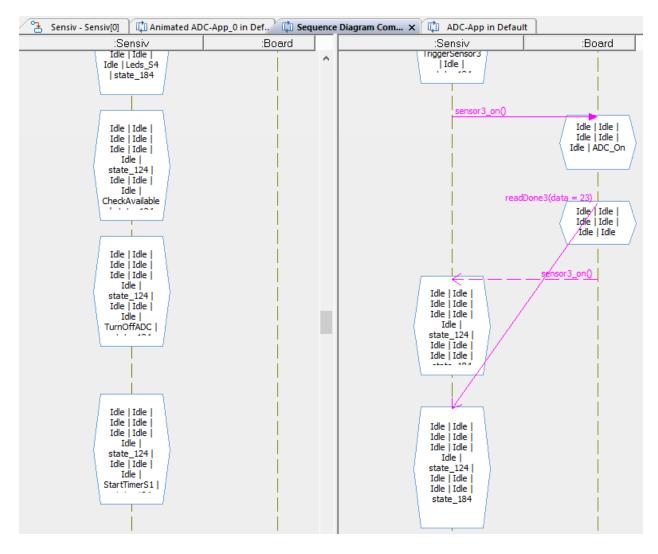

| Figure 4-10: Sequence Diagram Comparison Results-1                                | 56 |

| Figure 4-11: Sequence Diagrams Comparison Result-2                                | 57 |

| Figure 5-1: Code Generation and Verification                                      | 61 |

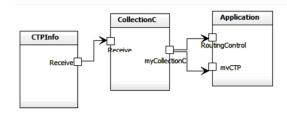

| Figure 5-2: TinyOS components                                                     | 63 |

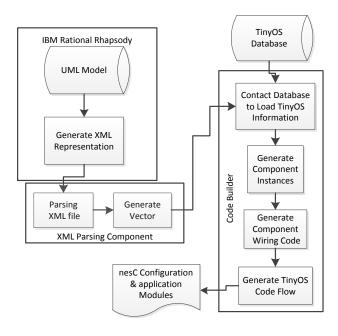

| Figure 5-3: Code Generator Structure                                              | 64 |

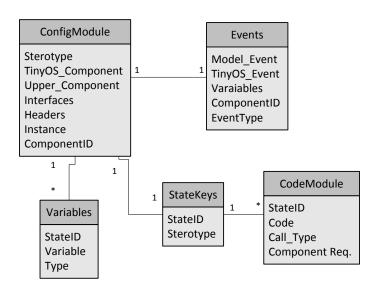

| Figure 5-4: Database Structure                                                    | 66 |

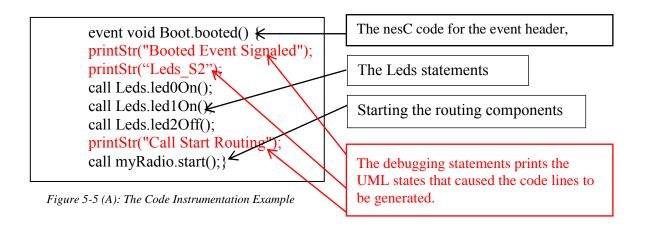

| Figure 5-5 (A): The Code Instrumentation Example                                  | 70 |

| Figure 5-6 (B): The Model States                                                  | 71 |

| Figure 5-7: Example of Debugging Statement for Simulator Integration              | 73 |

| Figure 5-8: The Trace File Output                                                 | 73 |

| Figure 5-9: Code Generation Example                                               | 76 |

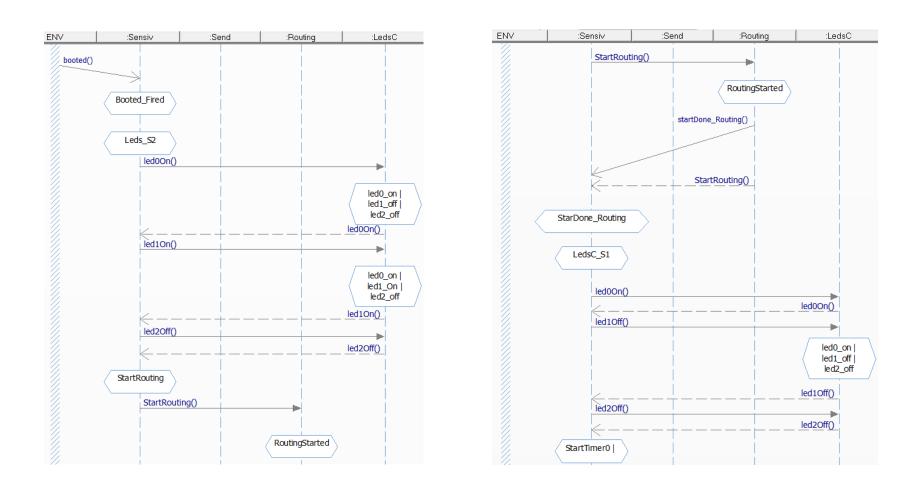

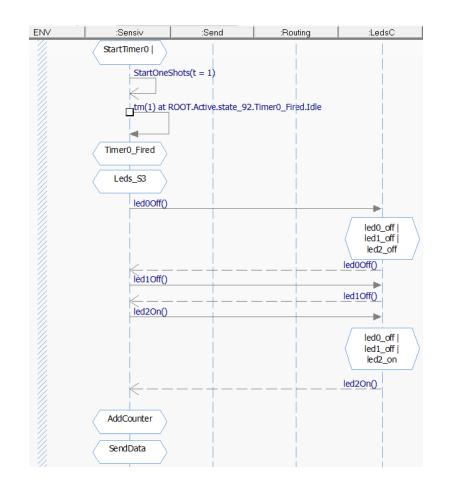

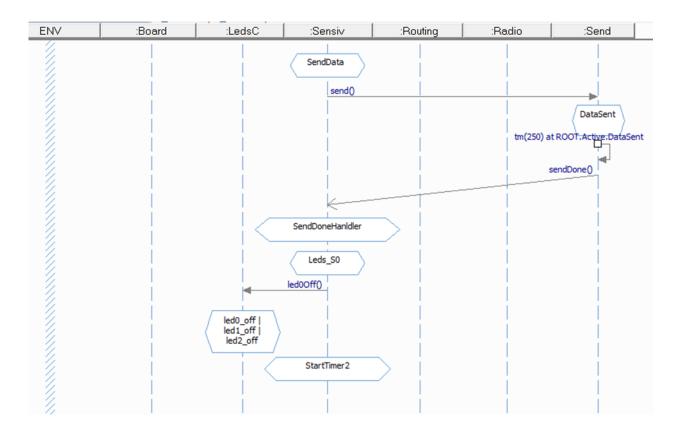

| Figure 5-10: Executed Sequence Diagram for Counter Sender Node (Part-A)   | 79  |

|---------------------------------------------------------------------------|-----|

| Figure 5-11: Executed Sequence Diagram for Counter Sender Node (Part-B)   | 80  |

| Figure 5-12: The screen shot Node1 log file                               | 81  |

| Figure 6-2: Parsing Log files and Trace file                              | 86  |

| Figure 6-3: Power Consumption Analysis of Counter Application             | 88  |

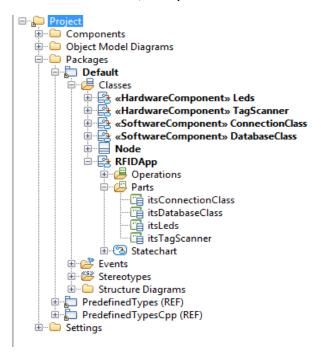

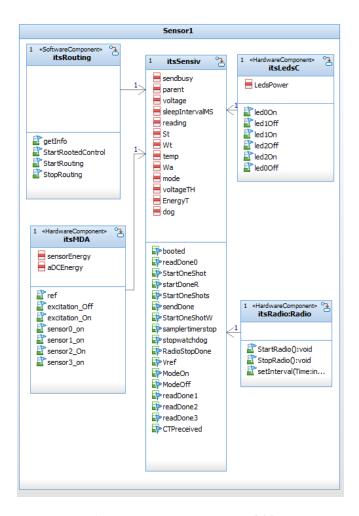

| Figure 7-1: Service Components UML Model for SensIV                       | 95  |

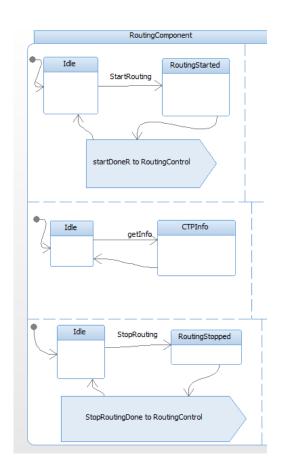

| Figure 7-2: Routing OS Component State-Chart                              | 96  |

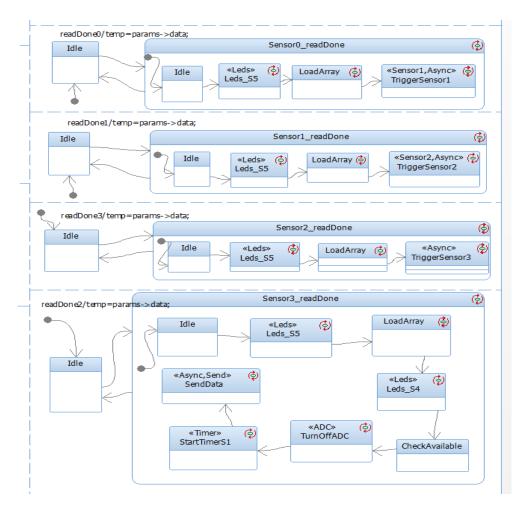

| Figure 7-3: Portion of SensIV State-Chart                                 | 98  |

| Figure 7-4: SensIV Panel Diagram                                          | 99  |

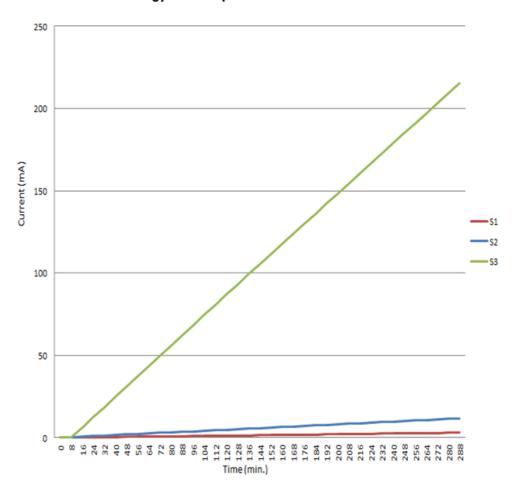

| Figure 7-5: Power Analysis for Three Scenarios of Controlling the ADC     | 103 |

| Figure 7-6: SensIV Topology Structure                                     | 105 |

| Figure 7-7: Physical Location of SensIV Nodes.                            | 105 |

| Figure 7-8: The Simulator Configuration                                   | 106 |

| Figure 7-9: The Call Trace Produced by Avrora                             | 108 |

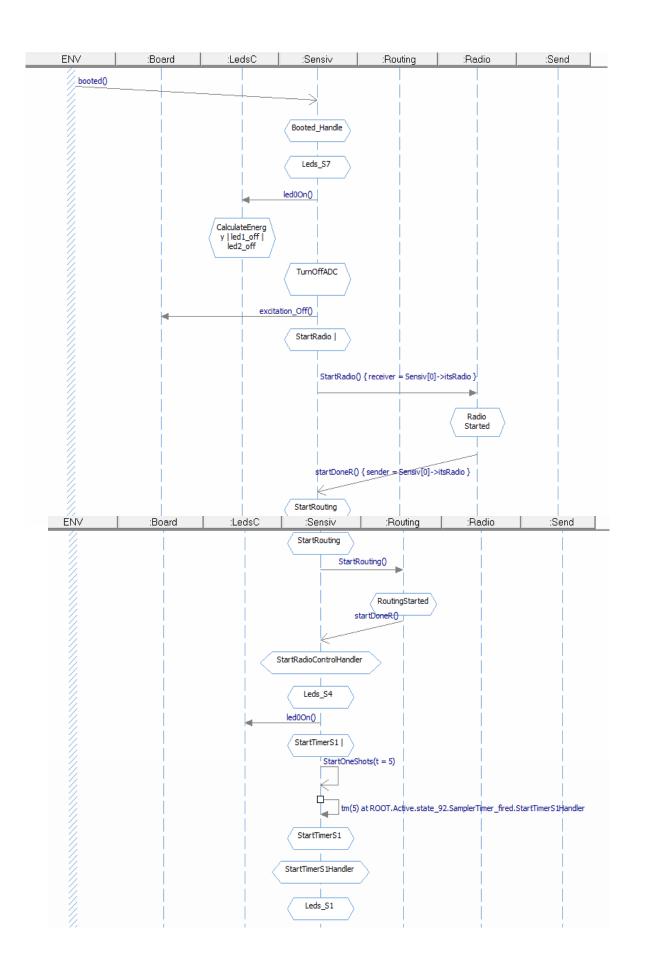

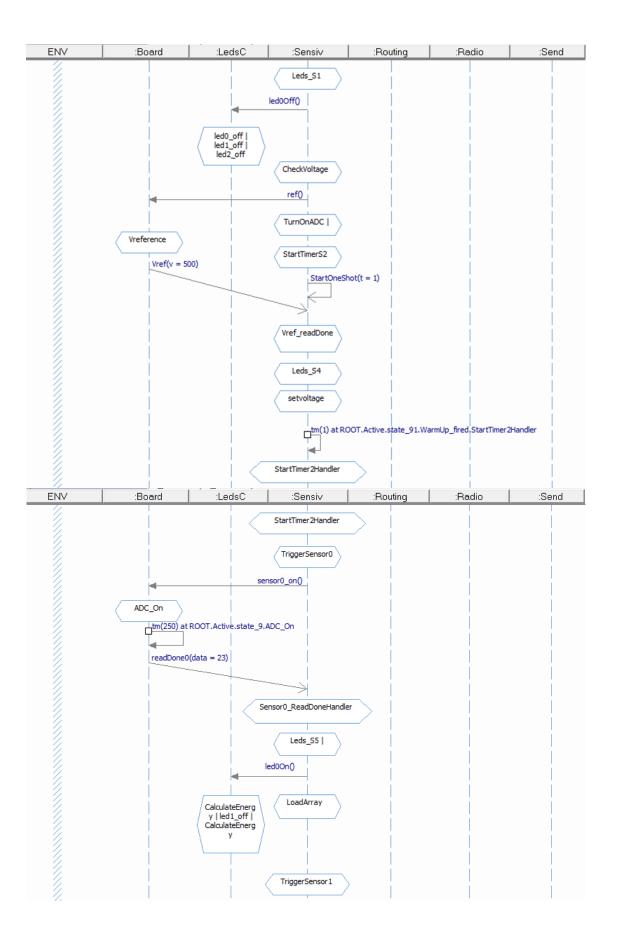

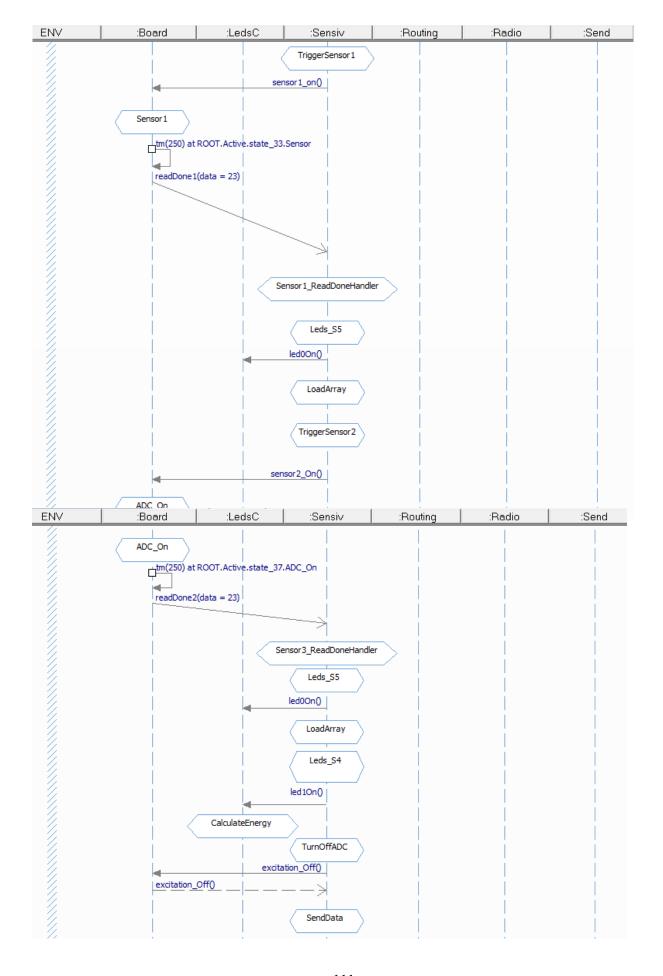

| Figure 7-10: SensIV Executed Sequence Diagram                             | 112 |

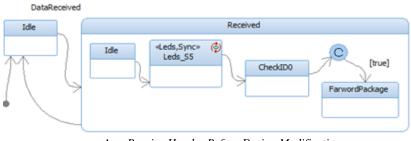

| Figure 7-11: Design Modification for Event Structure                      | 115 |

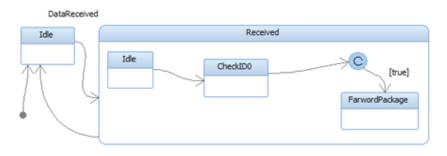

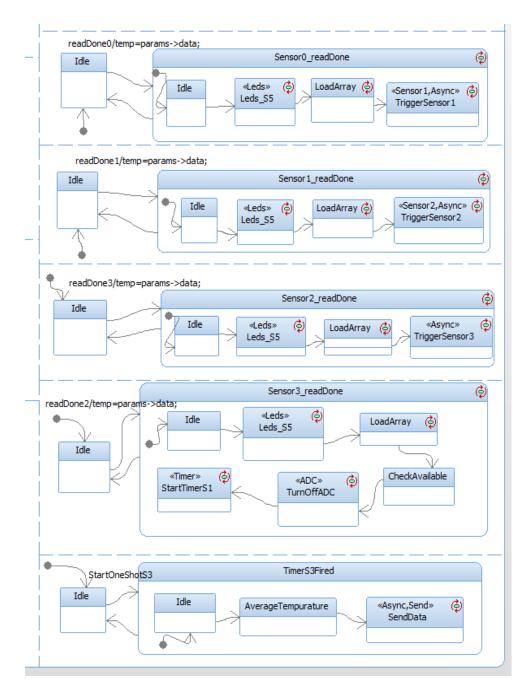

| Figure 7-12:Aggregation SensIV State-Chart Design                         | 118 |

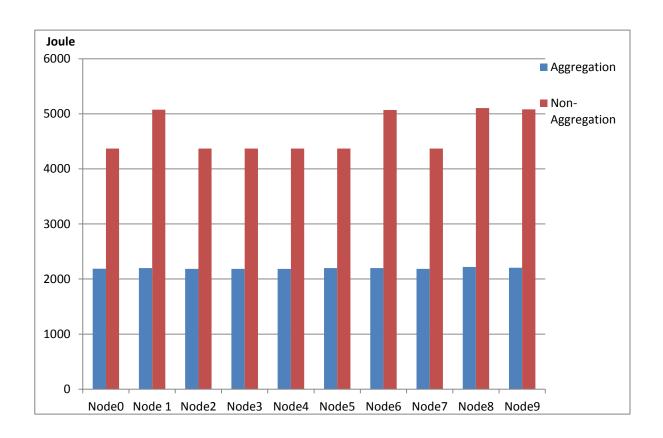

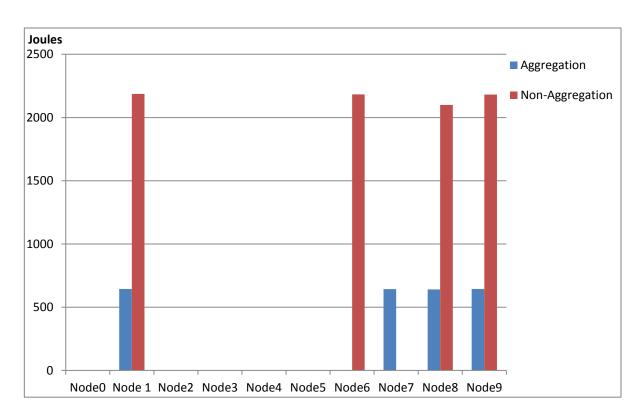

| Figure 7-13: Power Consumption of Network Sending Process                 | 119 |

| Figure 7-14: Power Consumption for the Network Receive Processing Process | 120 |

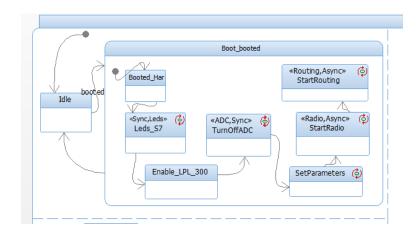

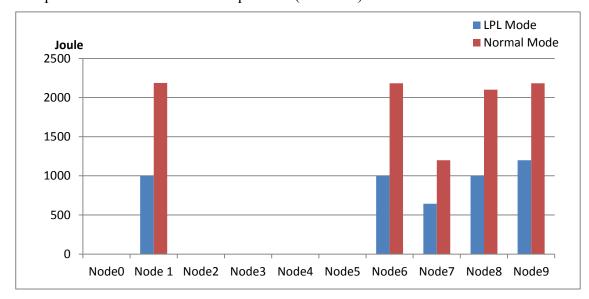

| Figure 7-15: Enabling LPL in Booted Event                                 | 121 |

| Figure 7-16: Power Consumption of Receiving Energy for LPL Vs Normal Mode | 121 |

# **List of Tables**

| Table 3-1: Overview of the Modeling Techniques                           | 33  |

|--------------------------------------------------------------------------|-----|

| Table 3-2: Modeling of Node and System Arcitecture                       | 33  |

| Table 4-1: Model Stereotypes                                             | 50  |

| Table 5-1: Explanation of the Database Tables                            | 68  |

| Table 7-1: Power Consumption Constrains                                  | 101 |

| Table 7-2: Power Consumption Analysis for SensIV Determintsic Components | 103 |

| Table 7-3: SensIV Nodes Total Power Consumption                          | 113 |

| Table 7-4: Power Consumption Report for Node 1, 6, 8, and 9              | 113 |

| Table 7-5: Power Consumption for Nodes 1, 6, 8, and 9 after Modification | 115 |

| Table 7-6: Aggregation Power Consumption for Nodes1, 6, 8, and 9         | 119 |

| Table 7-7: Designer and Automated Intervention Comparison                | 124 |

### List of Abbreviations and Symbols

WSN Wireless Sensor Networks

ADC Analog-to-Digital Converter

IP Internet Protocol

UML Unified Modeling Language

XML Extensible Markup Language

LQI Link Quality Indicator

RSSI Received Signal Strength Indication

SDL Specification and Description Language

TLC Target Language Complier

PIM Platform Independent Model

MDEA Model Driven Engineering Approach

WSAN Wireless Sensor Actor Networks

VM Virtual Machine

XRM eXtended Reactive Modules

RM Reactive Modules

WECT Worst Execution Case Time

WCS Worst Case Space

SNR Signal-Noise Ratio

BER Bit Error Rate

OS Operating System

CPU Central Processing Unit

OS Operating System

CTP Collective Tree Protocol

RPL Low Noisy Networks

VDHL Very High Speed Integrated Circuits

ISO International Organization for Standardization

USB Universal Serial Bus

FIFO First In, First out

#### 1. Introduction

#### 1.1 Motivation

Wireless Sensor Networks (WSNs) consists of tiny electronic devices that communicate wirelessly and are typically deployed in a field in large numbers to monitor specific phenomena, such as temperature, humidity, and soil moisture). WSNs have multiple applications in many areas, such as agriculture, military, localization, health, and environmental. For example, sensor networks can be deployed in a vineyard to monitor the temperature of the vineyard in order to mitigate for crop damage [1] [2] [3] [4]. Also, WSNs can be used to detect foreign chemical agents in the air or in the soil [5]. They have been used to monitor volcanic activity by deploying multiple sensors on the top of a volcano to consistently measure the temperature and the vapour of the volcano [6]. Basically, WSNs are pervasive in this day and age.

WSNs nodes are distributed across the operation field in huge number in order to monitor the phenomenon with a good resolution. For that reason, WSN nodes are difficult to reach once the nodes are deployed on the operating field. This challenge illustrates the necessity of testing and verifying the software system prior to deployment. In addition, the current design and analysis of software systems for WSNs occurs primarily at the coding layer, which prevents the design from going by the typical software development cycle and correct for errors early in the design stages. Implementation of the design at the coding layer, leads to a decrease in code portability and to platform-specific implementations [7].

The process of developing WSN software code is very challenging since the software design is prone for errors and the debugging process is very time consuming. Moreover, the limitation of user interface I/O hardware of each node (only 3 LEDs as output devices), leads difficulty to test the software while the software is operating and as a consequence, debugging

and correcting the system software code is very challenging. If the code errors are not detected during the implementation and verification stages of development then they may appear once the system is deployed and is operational, which is difficult and challenging to correct due to the operational conditions of WSN systems.

WSNs often consist of self-powered nodes that have limited power resources, which impose design constraints focused on the improvement of power consumption. For example, there is a requirement to improve the power consumption due to the limitation of the power resources otherwise the node the die and will not operate if the node ran out of power. The power consumption of each node is strongly influenced by the software design, the timing constrains of the software modules, the routing protocols used, and the network topology. Design decisions that do not take these issues into account can result in a battery drain on the sensor node, which eventually will lead to disabling the sensor network.

Software modeling enables the designer to capture the design of the software system at higher abstraction layers than at the coding layer, therefore, the designer is able to test and verify the design before the actual deployment. Also, representing the software design at higher abstraction layers gives the chance for early detection of any errors and, as such, early correction of the errors. Additionally, by using various tools of model execution techniques and code instrumentation, the designer can predict the power consumption of the software system. Moreover, by leveraging model driven approaches, the designer can generate and deploy the software code and consequently save the time consumed to implement and debug the code. Also, software modeling enables the designer to design the software system independent of the platform.

#### 1.2 Thesis Statement and Scope of Research

#### 1.2.1 Problem Statement

In general, the development of WSN applications occurs almost entirely at the coding layer, which results in an inability to take advantage of the software development life cycle, and reduces the chances of early detection of errors, verification for design requirements, and design improvements for power consumption before the deployment of the code as stated by Losia et. Al. [7] and Sharma et. Al. [8]. The resulting implementation is often time consuming to develop and debug, platform specific, prone to errors, and is developed during the last stage of the design. There is a lack of software modeling and analysis techniques for system operational requirements and power consumption for WSNs at an abstraction layer other than the coding layer.

#### 1.2.2 Thesis Statement

WSN modeling allows for early detection and verification of the system design performance than the current analysis at the coding layer. Using modeling executions techniques and instrumentation methods, this thesis provides an approach to analyze the system requirements and power consumption characterizes for the sensor nodes components in a WSN. Moreover, this thesis integrates the WSN simulation tools with the UML software models to analyze the power consumed during the communication processes, and feedbacks the simulator results to the design modeling layer.

#### 1.3 Thesis Methodology and Contribution

#### 1.3.1 Thesis Methodology

This thesis focuses on providing WSN developers the opportunity to develop a model for the software in a sensor node that is part of a WSN and the ability to analyze the model for

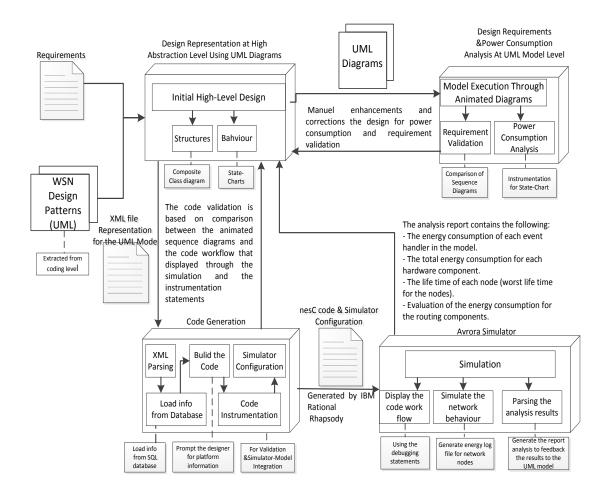

against any power design requirements. Furthermore, the WSN sensor node software design can be improved based on the feedback results obtained from the analysis of the models and sensor network simulations. This thesis does not focus on developing a design, which guarantees the Quality of Service (QoS) and power management as much as the availability of enhancing the design model based on the analysis results. The steps taken in this thesis methodology were as follows and correspond to Figure 1-1.

#### 1. Reviewing WSN software modeling approaches.

As a first step several software modeling approaches for WSN systems were reviewed in order to determine the best modeling language for capturing and analyzing the design of a WSN. Also, the review helped in becoming familiar with the modeling and analysis strategies used at the software modeling layer. This review is presented and discussed in detail in Chapter 3 along with a comparison of those approaches to the approach presented in this thesis.

#### 2. Representing the sensor node software design at the modeling layer.

This thesis developed 4 UML design patterns that guide a software designer to capture the design of the software of a sensor node at the modeling layer. The patterns capture the design components and the design behavior using the UML class diagram and state-charts diagrams. IBM Rational Rhapsody tool was leveraged to create the diagrams.

# 3. Verifying the design requirements and analyzing the power consumption at the modeling layer.

This thesis has leveraged the UML model execution technique to validate the design against the requirements and analyze the power consumption for the hardware components, such as LEDs, sensors, and ADC. The validation procedure and the analysis were done by executing the UML model and instrumenting the state-chart diagrams with both the power consumption

annotations and the timing annotations. Based on the validation procedure, the designer is able to correct and improve the design, which is considered as the first feedback analysis to the design. The model patterns and the verification are discussed in chapter 4.

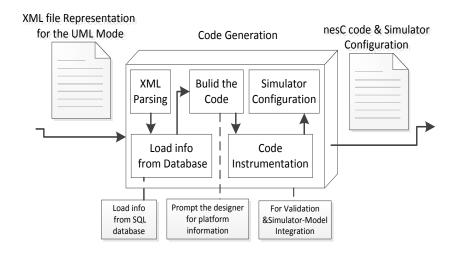

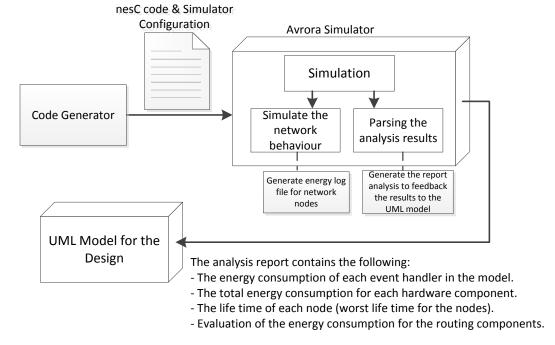

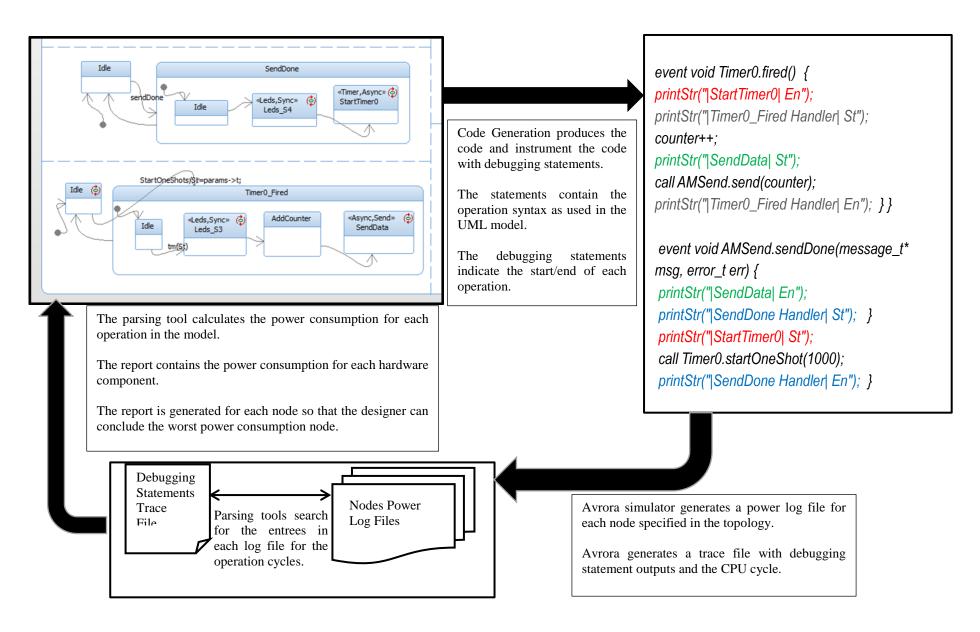

#### 4. Generating the code and configuration files for the network simulator

A simulator is used to estimate the power consumed by the communication components, which is not deterministic and hence very challenging to model in the UML modeling layer as were the hardware components. A code generator was developed in order to generate the code and the configuration files required for the WSN network simulator. The code generator parses the XML representation for the UML diagrams that represent the software design of the sensor node. This XML representation is generated by the UML modeling toolkit. Some of the sensor network information does not exist in the design model, such as the battery capacity and network topology, so the code generator has to prompt the designer for such details. The code generator instruments the generated code in order to facilitate integrating the results of the simulator back to the model.

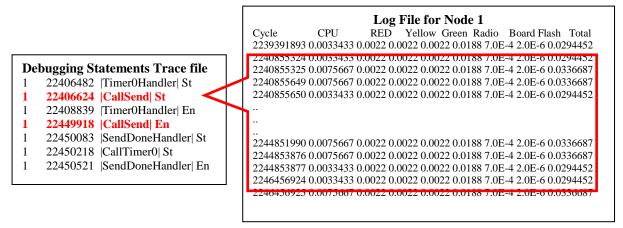

#### 5. Validating the generated code

The generated code from the UML model was validated using instrumentation statements that were added by the code generator. The code is executed on the network simulator and it displays the calls between the design's components defined in the UML model. The output from the instrumentation statements are compared to the UML executed model in order to ensure that the generated code workflow expresses exactly the behavior captured in the design. The code generator and validation procedure are discussed in detail in chapter 5.

#### 6. Power consumption analysis for the communication process

The simulator simulates the activity of each node in the network and generates a power consumption log file for each node. This thesis developed a parsing tool that uses the simulator's power consumption log file report together with the instrumentation output to display the power consumption at each portion of the UML model. This parsing tool enables the designer to relate the communication process analysis to the model layer and to integrate the simulation results with UML model.

#### **1.3.2** Thesis Contribution

This thesis developed a framework and methodology for model level analysis for WSNs. The framework allows the designer to represent the design at the modeling layer and enables the designer to early detect the design errors, validate the design against the system requirements, and improve the power consumption of the design. The thesis leverages the simulation tools to analyze the networking power consumption and integrates the simulation results with the design representation at the modeling layer (i.e. UML models). The developed framework contains the following developed tools:

- Representation of the WSN design at the modeling layer using UML diagrams: UML patterns are developed to capture the WSN design components and the WSN design behavior. Representation of the WSN design at the UML layer enables the designer to early verify the system requirements at the modeling layer and analyzing the power consumption of the sensor node leveraging the UML model execution feature. The developed framework contains the following developed tools:

- Generating code and the configuration files for a network simulator from the UML model: A code generator is developed in java to parse the XML representation of the

UML model and generate the equivalent code for the network simulator. The code generator also created the configuration file required for the simulator. The code generator also instrument the generated code with debugging statement to ease the integration between the simulation results and the UML models

• Parsing the simulation results tool: A tool has written in java code to parse the simulation results and feedback the results to the model, which enable the design to integrate the simulation results with the model. The integration of power analysis of the simulator is essential to feedback the simulator power analysis of the communication process back to the model.

#### 1.4 Tools leveraged in the thesis

The tools that were used can be categorized into 2 groups:

- The tools that were developed as part of this thesis contribution. The tools developed are the code generator and the parsing tool used to parse the results from the sensor network simulator. Those tools are explained in Chapters 4 and 5, respectively.

- The tools that existed and were leveraged to develop the UML models and analysis of the power consumption related to those software components that displayed deterministic power consumption characteristics. The tools used were the IBM rational Rhapsody for UML models and Avrora WSN simulator. Tools leveraged and developed in this thesis

#### 1.4.1 IBM Rational Rhapsody

IBM Rational Rhapsody [9] is an UML software design environment developed by IBM to ease a software designer on the use of UML tools and model driven approaches in software design. IBM Rational Rhapsody contains many features; however, this section contains the overview of the features that were used in this thesis:

Component Diagrams: Rational Rhapsody offers component diagrams that capture the system components, sub components, interfaces, operations, and attributes. Rhapsody contains a new feature called a composite class, which is a part of the component diagram. The composite class is considered as a container for the sub components and captures the structure of one main component. The composite class offers the feature "class part" which enables one class to create instance of another class. Therefore, one class can signal a method or an event of another class. The class part feature is essential to enable the animation of the sequence and state-chart diagrams, which captures the behavior of the design.

State-Charts: The state-chart defines the behavior of a component or a sub component. The behavior is captured through a group states, transitions, events, and triggered operations. Rational rhapsody offers the state-chart execution feature which executes the model and highlights the current executed state. The events can be triggered through a state within the same state-chart or from another state-machine of a separate component through using the class part feature. This feature enables the designer to specify the interaction between the system sub components and the main components. Additionally, the state-chart execution feature enables to the designer to inject events (manually generate the events) and observe the system behavior in case this particular event has occurred.

In addition, Rational Rhapsody enables the designer to add code to the state-chart to do a specific function so that the code is executed once the state is active. This feature is very helpful to instrument the state-chart which can be used for analysis purposes as explained in chapter 4. Moreover, the state-charts can be annotated to represent the time constrains of the system by timing the transition of the state-chart. The timing constrains facilitate the validation procedure of the requirements as well as the system analysis.

**Sequence Diagrams**: The sequence diagram presents the interaction between the system components in the form of messages. The diagram contains the component life line, the messages exchanged between the components, and the time different between the messages. The messages on the diagram can represent an event, a triggered operation, or internal method.

The sequence diagram offers two modes:

- *The design mode:* this mode creates methods, operations, and events once the designer draw them in the diagram and they are considered as part of the design.

- *The analysis mode*: this mode enables the designer to verify the behavior of the design and validate whether or not the design meets the functional and the non-functional requirements.

- The designer can draw the messages, time constrains, events, actors on a sequence diagram and save it as the non-executed sequence diagram. The messages, and events drawn have no effect on the design.

- The designer runs the animation mode of the design and the sequence diagram will capture the actual trace of the system in an executed sequence diagram.

- Rational Rhapsody offers a tool for comparing the sequence diagrams. The comparison verifies if the executed sequence diagram (from the actual system trace) is identical or different from the non-executed sequence diagram. The comparison shows the differences between the two sequences diagrams and test the timing of the signals between the system components, the sequence of the signals, the missing states, etc. The comparison is very helpful tool to validate the system design against the system requirements.

*Code Generation*: The code generation tool has support to generate the code for four languages; Java, C, C#, and C++. Additionally, IBM rational rhapsody contains a plugin to generate the XML representation for the model. The XML contains representation for developed diagrams. The XML representation helps in the code generation process in case the programming language of the target platform is not supported by Rhapsody.

#### **1.4.2** Avrora Simulator

Avrora simulator is cycle accurate instruction-level simulator (emulator) and is presented in [10]. The simulator is built in java language, so the simulation for the WSN design components takes place by the object oriented principle. Avrora simulator requires; the code representation for the software design, the network topology, and the simulation flags that configure the simulation.

Avrora represents each node of the network with an object and each object runs by an individual thread. By the threads the nodes interact with each other in the terms of sending/receiving messages based on the nesC code of the node. All the nodes are synchronized by the use of one global clock. The node activity is simulated by using a java event queue. In reality the low power consumption profile of OS puts the nodes into sleep where less power is consumed. The node wakes up whenever an event is signaled from a hardware component, clock, or a message received. Consequently, the simulator fills the event queue with the events that are about to be signaled in an order of which the software calls them. Then, the simulator consumes each event in the queue in a first-in-first out (FIFO) ordering.

The simulator has a class to simulate the behavior of the *CC2420* Radio Frequency transceiver chip, which is utilized in many sensor nodes based on the 802.15.4 communications protocol. The *CC2420* simulator class controls the sending and receiving process

of each node through using the *wait()* function so that the program guarantees the synchronization between the sender and receiver nodes. The collision avoidance is considered in the radio program as well. The CC2420 simulator class—calculates the summation of all RSSI of all the signals received by the node. If the RSSI is too high, this implies that there are too many nodes sending information to the receiver node and thus the radio program will force the sender node to wait or re-send the message later. Also, the RSSI value can be used to determine the range and location discovery of sensor nodes. Moreover, the program that simulates the radio communication process of the nodes simulates the 802.15.4 Link Quality Indicator (LQI). LQI consider the signal-to noise ratio and the measurements of the RSSI value in order to find the best parent node for each node in topology. The RSSI between the two nodes is determined through a topology configuration file, which is configured by the designer of the sensor network. The topology configuration file contains the X Y Z coordinates for the layout of the sensor nodes and the density of obstacles (if not present is zero) for each radio link. Based on the physical distance between the nodes, the simulator estimates the RSSI between the nodes.

Avrora offers instrumentation tools for debugging and analysis purposes. In order to use those tools the designer needs to configure the simulator to reflect the interest to use those tools. There is variety of tools offered by the simulator; however we will highlight the tools that are used in this thesis only.

**Debugging Statements in Avrora:** The debugging statements in Avrora are capable of printing any statements while executing a specific location of the code as well as the time/cycle of the statement execution. The debugging statements do not require any changes in the simulator structure.

Calls Monitor in Avrora: The monitor call is a debugging tool that is supported by Avrora in order to monitor the calls between the node components and the interrupt handlers. In this thesis approach, monitoring the call was leveraged to validate the generated code by comparing the monitored calls with the equivalent calls at the modeling layer.

Power Consumption Monitoring in Avrora Tool [11]: Avrora has a power model for the components of the nodes; the model was developed based on real time measurements and code executions of the sensor node components. The model covers the power consumption for the LEDs, CPU, Board, and Radio. The power consumption tool has the capability to generate a power consumption log file for each node in the network. The power consumption tool updates the log file whenever the power profile changes. The update contains the cycle number when the update occurred and the amount of power consumed for each component. Also, the power consumption tool can predict the life time of each single sensor node. At the end of the simulation, the tool prints out for each node; the node life time and the power consumed for each hardware resource in the sensor node.

Figure 1-1: Thesis Methodology Diagram

#### 1.5 Thesis Structure

The structure of this thesis is as follows.

• Chapter 2 contains the background material and contribution of this thesis. This chapter discusses the problem statement of this thesis and the methodology that is followed to solve this problem. The methodology explains the tools that are used and the tools that are implemented to solve the problem as well as the requirements at each design stage so that the reader gets a good overview about this thesis objective and this thesis contribution.

- *Chapter 3* discusses the prior art in software modeling for wireless sensor networks and compares this prior art to the approach taken in this thesis.

- Chapter 4 explains the UML design patterns that were developed as a part of this thesis contribution, as well as, the proposed methodology in using these design patterns to validate the operational system requirements. Chapter 4 also presents an approach to calculate the power consumption of any deterministic components in a sensor node by the instrumentation of the software model entities. In order to analyze the power consumed due to the communications caused by the sensor network, it was necessary to integrate the UML models with a sensor network simulator.

- Chapter 5 explains the code generator tool developed that parses the UML model and generates the equivalent code for the network simulator. This chapter also presents the validation procedure used against the generated code by instrumenting the generated code using debugging statement. The debugging statements ease comparing the software behavior at the coding level to the software behavior at the model level. Moreover, this chapter contains examples of generation and validation procedure of the code in order to demonstrate that the algorithms work properly.

- *Chapter 6* describes the integration between the UML models and the analysis coming back from the network simulator so that alterations to the software design can be performed as opposed to code alterations.

- *Chapter* 7 presents a complete study cases that demonstrate how to design the sensor system at the modeling layer, analyze the power consumption for the deterministic components, generate the code for the simulator, and finally simulate the design and

integrate the simulation results back to the UML models. Chapter 8 contains the conclusions and future work.

• *Chapter 8* contain the thesis contribution, the limitation of the developed methodology, and the future work.

#### 2. Background

#### 2.1 WSN Structure

Wireless Sensor Networks (WSNs) consists of tiny electronic devices that communicate wirelessly and are typically deployed in a field in large numbers to monitor specific phenomena, such as temperature, humidity, and soil moisture). The nodes communicate wirelessly in order to forward the packets to one gateway where the information is further processed.

Typically, each sensor node contains a wireless unit to communicate with the other nodes, a processor unit, one or more sensors attached to the node and Analog to Digital Converter (ADC) unit. The sensors sense the phenomenon and generate the analog signal that represents the sensed data then transfers the analog digital to the ADC that converts the sensed information to a digital form. The sensor node loads the digital information into data frames and sends the data by the wireless unit to the parent node. The nodes communicate with each other wirelessly to transfer the sensed data to one gathering node, which is known as a collector node. The collector node could be attached to a gateway to facilitate the transfer of data between the WSN and other devices on more conventional networks like those based on the Internet Protocol (IP).

Most of wireless nodes that are used in a WSN have a range of 500 meters. Therefore, the nodes rely on the multi-hop communication routing protocol to deliver the information from the source node to the destination node, especially if the WSN monitors the phenomena in a large field. The task of the routing protocol is to build the data path by establishing the routing tree structure. This structure defines the data path for each node by defining its parent node. The most common WSN routing protocols (i.e. CTP [26] and RPL [28]) use the expected transmission count (i.e. ETX) to estimate the link quality between each node and its neighbor

node. The ETX is a ratio between the successfully delivered frames and the total number of attempts to send those frames. Therefore, the lower the ETX is the better link quality the nodes have. Each node selects the parent node based on the lower ETX. Using this policy will avoid the infinite loops of forwarding the data packets. The root node (in most cases the gateway) broadcasts a frame which indicates that its ETX is zero so that all frames are collected in the gateway. The tree structure is maintained by broadcasting beacon frames to check the availability of the parent nodes. In case one of the nodes fails, the routing protocol builds a different path to overcome the broken link.

The tree structure dynamically changes based on the availability of the nodes and the packet delivery rate, which is determined by the ETX. Also, the packet delivery rate is affected by the environmental conditions of the transmission process. All of these conditions lead to the dynamic changes of the tree structure and the taken path by each data packet. Therefore, the communication process has a non-deterministic nature.

The data packet wakes up the node from the low power listening mode and signals the radio to start receiving the packet. Once the receiving process is completed, the radio component signals an event to indicate the completion of the process. The behaviour of the nodes when the packet is received can be different from one design to another based on the implementation of the event handler. The designs can be classified into the following categories:

Partially non-deterministic design: The non-deterministic portion of the design

is the receiving and forwarding of the received frames from the child nodes due to

the dynamic changes of the typology. Therefore, the implementation of the receive

event handler contains a simple code to forward the data packet until the packet

reaches the gateway. The rest of the node activities, such as sensing, controlling the ADC unit, and controlling the LEDs is fully deterministic since they are activated based on a specific timer and signalled for a specific rate of time.

Deterministic design: Some of the designs are fully deterministic where the communication process occurs based on a pre-defined pointto-point communication node.

#### 2.2 WSN Power Consumption

The power resources of WSN nodes are very limited, since each node is powered by rechargeable batteries. Therefore, the design of any application that executes on a sensor node must to be essentially power efficient to avoid the node failure. Therefore, the power consumption requirement is crucial since the life time of the node relies on the life time of the battery. Therefore, power consumption improvement is essential to maintain the life time of the node, especially during the dark hours since the batteries are not being charged. The power consumed by the node can be classified as follows:

- Sensor Node Power Consumption: This power consumed by the sensor node hardware components, such as (LEDs, ADC, Sensors, etc.). The amount of power consumed is proportional to the rate of signaling those components. The software design controls the rate of signaling those components and the duration of operating each component.

- Sensor Network Power Consumption: This power consumption by the sending and receiving process that occurred during the communication between the nodes. This portion is not consistent among all nodes and among all operational conditions due to the unstable topology nature, as explained in the previous section, and due to the

unpredictable data control packets. The communication process consumes around 60% of the total power consumption of each node.

There are multiple factors that influence the power consumption of each node, such as the following:

- The routing protocol that is used to control the communication process.

- The data collection methodology since the data collection methodology controls the number of packets sent and received.

- The software structure that controls the signaling of the hardware components.

#### 2.3 WSN Modeling

The design of WSN systems usually occurs at the implementation level and does not involve design at higher levels of abstraction. This leads to a decrease in code portability and to platform-specific implementations [2]. A WSN system produced using this approach is prone to both design and implementation errors and is very challenging to debug (user interfaces to sensor nodes are very limited so even simple text output is challenging). If errors are not detected during the implementation and verification stages of development, then they may appear once the system is deployed and is operational.

Modeling of a WSN enables the designer to capture the design at higher abstraction layers before the actual implementation of the application. This facilitates fixing and correcting design errors using diverse methods of design analysis. Early model analysis for the design enables the user to evaluate the design before the actual deployment. Moreover, modeling enables the designer to display the flow of the design so that the designer is capable of capturing and enhancing the design before the actual code implementation. Also, integration of the power

consumption analysis and the system model facilitates the evaluation of the design energy consumption.

The characteristics of modeling techniques can be categorized as follows:

- Language Syntax: the modeling language syntax can vary between graphical (i.e. UML) or textual syntax such XML language.

- *Language Scope:* the language scope can vary based on capturing either the procedural activity of the node or capturing structure of the node.

- *Language Tools:* the tools associated with each language can vary based on the aim of the modeling. For instance, some of the modeling language support model execution, other support code generation.

The system details that are captured with each modeling language are strongly dependent on the aim of the modeling, while the rest of the system details are abstracted out. An extensive survey was conducted for the existing modeling language for WSN and was explained in Chapter 3.

#### 3. Modeling Techniques for Wireless Sensor Networks

#### 3.1 Introduction

The objective of WSN software modeling is to represent the WSN design at a higher abstraction layer than at the coding layer. The result of this is to facilitate analysis of the WSN prior to any significant coding. The design details that are captured at the modeling layer are strongly dependent on the objective of modeling while the rest of the details are abstracted out, such as code generation, or analysis network performance. This chapter presents the results of a survey of nine modeling techniques for WSNs. The modeling techniques are different from each other in the terms of notation, the objective for the sensor model, the representation of the sensor node architecture, and the representation of the system architecture. Some of the modeling techniques capture the sensor node architecture, such as the sensor node software, and the interaction between the node's software components. Other modeling techniques capture the WSN system architecture, such as the interaction between the nodes and the topology structure. In this chapter, each modeling technique is explained briefly by showing the objective of the modeling, the modeling technique notation, the representation for sensor node software architecture, and the representation for the WSN architecture. Also, the software modeling approach that was developed in this thesis, was presented in order to compare this thesis approach to the art in software modeling techniques for WSNs.

The rest of the chapter is organized as follows; Section 3.2 gives an overview of the reviewed modeling techniques, Section 3.3 discusses the modeling of the node architecture, Section 3.3 presents the modeling of system architecture, and Section 3.5 has the conclusion.

## **3.2** Modeling Techniques Overview

This section provides an overview of each of the modeling technique included in the chapter. Some of the modeling techniques use an appropriate notation to support the aim of the modeling, such as UML, while others use their own notation, such as the Insense technique [12]. The techniques use different basic elements (e.g. channels, processes, modules, components) to express a WSN as a model. A channel is used to represent the communication between two elements of a WSN. For example, channels can represent the characteristics of sensor-node communication, node-node communication, and node-gateway communication. Processes, modules, and components are used to represent the sensors and nodes of a WSN. Also, the modeling techniques vary with the tools used by the modeling technique to achieve the modeling purpose. For example, some techniques use code generation tool to produce the operating system code, other modeling technique use model execution tools to analyze the software model. The modeling techniques surveyed also vary in terms of the scope of modeling. For example, some techniques are intended to model a single sensor node; some are intended to model the complete WSN.

#### 3.2.1 High-Level SDL Models (HL-SDL)

HL-SDL is a modeling language that uses the Specification and Description Language (SDL), which is normally used to model and simulate communication protocols as defined in [13]. Dietterle, et al. [14] adapted SDL to analyze the worst case execution time (WECT) of the node design and to generate the required nesC code for TinyOS once the analysis is completed. The HL-SDL uses SDL processes (i.e. extended finite state machines to model TinyOS components. The node is modeled as a collection of channels and processes. The HL-SDL approach focuses on modeling the node behaviors and did not capture the system

architecture. Dietterle, et al. has mentioned that the generated code requires a manual improvement in order to operate properly. An example of manual improvement of WSN generated source code is modifying the communication between the components from asynchronous in the model to synchronous in the target platform. In addition to manual improvement of the generated source code, simulation can be used at the model level to refine the model (with respect to performance) prior to code generation.

#### 3.2.2 Insense

Dearle et Al. [12] developed the Insense modeling language, which is java based language to create a component-based model for a WSN. Insense is built and run on the Contiki operating system, which is a popular operating system used for WSN [15]. Insense models the node behavior and analyzes the component behavior for worst case execution times (WCETs) and worst case space (WCS) within a given WSN node. The components in Insense model the behavior of the software and the hardware component. An example of a hardware-software binding is the interaction between the sensor (e.g. humidity, temperature or moisture) and the software component that handles the readings. The sensor type is modeled as a component that uses a communication channel to transfer data to the software components [9].

The model components are concurrent and they communicate synchronously via directional channels that are used to abstract away from low-level synchronization and communication issues. To the best of our knowledge, the approach does not have support to model the WSN system architecture.

#### 3.2.3 MathWorks Modeling Approach

Mozumudar et al. [16] have developed a framework in MatLab environment that aims to design, simulate, and generate the code for WSNs. The node behavior is modeled as a

parameterized state flow block. Nodes in the MathWorks approach also contain timing and random number generators that are used for simulation. MathWorks leveraged the tools such as state-charts execution, chart displays, scopes, and plots, to perform the algorithmic analysis. According to the analysis results the model can be refined. The final stage is to generate the WSN code using the Target Language Complier (TLC) which can generate C code for MANTIS [17] and nesC code for TinyOS. The Mathworks analysis approach has also been used successfully to generate the code for Power Efficient and Reliable In-Network Aggregation (EERINA) [18]

In MathWorks, the framework is able to model the static topology by modeling the nodes with state chart and the communication medium which is implemented in C, models the connectivity between the network nodes.

## 3.2.4 Model Driven Engineering Approach (MDEA)

Losilla, et al. [7] used UML and a Model Driven Engineering (MDE) approach that includes three modeling layers:

- WSN Domain Specific Modeling: a meta-model that created by a domain expert.

- Component-based Platform Independent Models (PIMs): A UML-like language primarily composed of activity diagrams and state-machine diagrams.

- NesC Platform Specific Model (PSM): used with the UML PIMs to generate the NesC source code.

Transformation rules were defined that control moving from one modeling layer to another. Moreover, manual refinement can occur after every transformation to improve the generated model. The MDEA approach is supported by the Eclipse IDE as well as a number of Eclipse plug-ins (e.g. MOFScript) that are responsible for automating the transformation process.

The MDEA approach is used to generate the nesC code for the MITRA WSN application, which was designed for the application domain of precision agriculture. For the system architecture, MDEA does not have representation for the topology structure. However, the MDEA approach develops a UML model for the gateway node and a model for the network nodes, assuming that all the nodes have the same behaviour.

## 3.2.5 Promela and the SPIN Model Checker for WSNs (PM)

V. Oleshchuk proposed using Promela and Spin model checking technique to check the WSN network connectivity. The technique uses Promela language as an input language for the design model. The approach included the physical location of all the dynamic nodes and supports adding and removing nodes as well as changing their physical location. The Spin model checker is used to perform a network connectivity check. Specifically, the physical location data of the nodes is analyzed in conjunction with the data about the coverage range of the sensors [19]. The only technique that did not model node behavior was the paper using the Promela Model Checker. The authors of this work decided to simply focus on the modeling of network connectivity as opposed to including any significant modeling of the node behaviors.

#### 3.2.6 SensorML

SensorML approach is an XML based language that supports modeling each sensor by specifying the sensor's meta-data (e.g. sensor ID, sensor type) as presented in the SensorML specification document manual [20]. The model includes representations of the physical elements (e.g. sensors and actuators) and the non-physical element (e.g. mathematical operation within the sensor). All of the elements are modeled as processes that are linked together explicitly by inputs and outputs. Linked sequences of processes form process chains that correspond to the behavior inside a single node [4]. SensorML has support to model network

elements, such as base station, sensors, and the network topology. SensorML does not provide any sort of model execution techniques that enables the designer to improve or test the design before the actual deployment.

## 3.2.7 SystemC-AMS

M. Vasilevski et. Al in [21] have developed SystemC-AMS that analyzes the communication channel between two nodes for Bit Error Rate (BER) and Signal –to Noise Ratio (SNR). The approach combines C++ with block diagrams to model the WSN and simulate the system. For each node SystemC-AMS models the Analog to Digital Converter (ADC), the microprocessor, and the communication channel between the node and the next hop node. On the system architecture level, the approach models the communication process between two nodes. However, the modeling technique does not have support for the network topology since the approach assumes that data is transmitted by single hop communication.

#### 3.2.8 UM-RTCOM Model

M. Diaz et. Al. [22] developed the UM-RTCOM modeling technique, which is a real-time component based modeling framework written in CORBA and developed to analyze the design for Wireless Sensor Actor Network systems (WSANs). WSANs have the same functionality as WSN; however, WSAN also reacts in response to the sensed data. The approach analyzes the design for WCET, deadlock freedom, and verification of live time of the design nodes. The modeling technique assumes the network is composed of sensors that have identical functionality, and actors of the same rules. The modeling approach captures the system architecture through modeling the network elements (sensors, actors, and the gateway) as three virtual machines (VMs), where each VM models a single element. The system behavior is modeled by the interaction between the three VMs. Sensors communicate

with actors and actor's communicate with the coordinator over channels. Communication via a channel is modeled as a tuple. A tuple is a sequence of fields with the form: (t1, t2, ..., tn) where each field ti can be: a TC identifier (or) a value of any established data type of the host language where the model is integrated. The communication channel protocol modeled in UM-RTCOM has been tested in an actual sensor network deployment by Barbaran et al. [23]. The deployment shows the improvement of the middleware overhead compared to another deployment where the motes send the sensed data periodically to the actors.

#### 3.2.9 eXtended Reactive Modules (XRM)

Demaille, et al. [24] have extended Reactive Modules (RMs) language to develop XRM language. The authors have used WSN design as a case study to demonstrate the capability of the developed modeling language. The approach leverages the model execution technique to calculate the package delivery probability and the power consumption of the nodes. The technique uses a module that captures the behavior of each single node in the network. Each module captures the node behavior, the communication capability, memory, and power consumption. XRM models the power consumption by deducting the power consumed value from a local variable for every time an activity is provoked in the module. The model has multiple modules to model the network nodes. Each module contains X-Y variable to indicate the physical coordinates of each node. Also, the modeling technique supports executing the modules which models the behavior of both the node and the system behavior.

# 3.3 Overview from the Node's Software Architecture Perspective

This section discusses how the software modeling techniques capture the software architecture of the elements in a sensor node, such as nodes, sensors, actuators,

software components, and hardware components. In particular, we consider the modeling of the node structure and the node behavior.

Most of the reviewed modeling techniques used a form of component-based modeling to represent the software in a sensor node. The WSN behavior is modeled by specifying the component's internal behavior, component to component interactions, and the communication channel's characteristics. The approaches reviewed can be divided into two distinct types. Those that focuses on the augmentation of the models to capture particular features such as concurrency, event-driven behavior, and real-time behavior and those that leverage standard models like state space and procedural coding that were later used for code generation or performance analysis.

Most of the reviewed modeling techniques reviewed used to create a platform independent model for the node software architecture. However, there is a necessity to include some of the hardware details for the following reasons: most of the modeling techniques surveyed can be used to create a platform independent model for the node architecture. However, there is a necessity to include some of the hardware details for the following reasons:

- The software behavior is tightly coupled to the hardware elements of the node.

Therefore the binding of software and hardware components should be represented in the model. For example, some of the sensor boards require signaling the sensors sequentially and not concurrently. Therefore the hardware properties impose a specific behavior on the software.

- The hardware information may be needed to be represented in order to be able to generate source code from the model. Generated source code is interacting with

the node hardware (timers, ports, sensor types) and therefore the model has to be aware of the hardware components in order to generate the correct code.

• The design analysis tools require some information about the hardware specification to develop the proper analysis results. For example, the WECT that is calculated by some modeling techniques is highly dependent on the hardware response time. Also, calculating the total power consumption is strongly related to the hardware used in the designing process.

## 3.4 Overview from the System's Architecture Perspective

The surveyed modeling techniques capture the WSN system architecture by representing network behavior, the topology structure, and the network behavior. Modeling network architecture is crucial because many important performance values are based on the network:

- Analyzing the network power consumption requires the representation of the network behavior since the communication process (sending and receiving) consumes most amount of power.

- Analyzing the packet lose requires the representation for transferring the data packet across the network.

- Analyzing the schedule-ability factors, such as WECT and WCS requires captures the time responses of the network elements.

- Analyzing the network connectivity requires capturing the network topology structure.

- Analyzing the communication channel between the channels requires the representation of the communication environment.

The topology of WSN systems can be dynamic or static. The static topology represents the nodes in a fixed location while the dynamic topology represents the nodes while they are in a

moving state. Additionally, based on the modeling target, the technique models the number of hops in the network design. We can categorize the topology representation by the modeling techniques into two categorize;

- *Group Representation*: For some the Modeling technique, representing the physical location is not essential to their approach, however, there is a necessity to represent various elements, such as the gateway, nodes, and actuator. Therefore, each element is represented with a separate model components. For instance, UM-RTCOM has a virtual machine to capture all the nodes behavior and another virtual machine to capture the actuators. MDEA uses a UML model to captures the design of the gateway and another one to represent all nodes.

- *Single Representation*: Other modeling techniques the physical location of the node is very essential to their approach so the model contains a representation for each single element in the network. Each node is defined by the X-Y coordinates.

# 3.5 Model and Simulation Integration

The modeling techniques for WSNs are capable of representing the design at higher abstraction layers and are capable of developing the system analysis at the modeling layer. Some of the parameters that the modeling techniques can analyze the design for are SNR, power consumption, WECT, WCT, and packet lose rate as explained in Section 3.4.

Some of the modeling techniques [25] [26] [27] have integrated the simulation tools such as OMNeT, Matlab, and Pmodel with the system model in order to develop further analysis for the system, such as testing the design performance, system scalability, and system optimization. The integration between the model and the simulator requires a coupling tool to intermediate the model domain and the simulator domain and requires a group of defined rules

that controls the transformation process between the model and simulation requirements. The coupling tool ensures that the underlying coding language, which is required by the simulator, matches the model semantics.

The integration between the model and the simulation tools enable the designer to assess the designer for various QoS parameter, such as the reliability, integrity, safety, and power consumption. Based on the survey that was published in [28] for 33 modeling techniques, the integration between the models and the simulation tool requires the generation of the simulator configuration. The generation process for the configuration faces a lot of challenges, such as the flaws in the generated items, as well as, the quality of the generated items. Moreover, based on the classification for surveyed techniques, some work should be invested in the feedback simulation results to the model, especially for the analysis of the non-functional requirements.

The feedback of the simulation analysis to the model enables the designer to evaluate the QoS parameters of the design at early stages of the design cycle. In addition, the feedback allows the designer to conduct the analysis which is very challenging in the model level. The feedback should be mapped to the model using the model terms so that the designer can relate the analysis results to the model. Additionally, based on the survey results, the best way to present the feedback is to visualize the system trace that is analyzed by the simulation and compared the feedback to the system trace that is displayed in the sequence diagram.

# **3.6** Concluding Remarks for the Review

Modeling technique enables the designer to represent the design at higher abstraction layers, which ease testing and correcting the design before the actual deployment. The elements can vary to be process, modules, components, diagrams, or channels. Modeling helps to resolve

some of the WSN software implementation challenges by the following (see Table 3-1):

- Calculating the system performance parameters, such SNR, BER, WECT, WCS, or power consumption.

- Generating the deployment code so that amount of effort used to write and debug the code is saved

- Checking the design correctness.

| Approach         | Notation                        | Modeling    | Modeling                                  | Modeling                                                             |

|------------------|---------------------------------|-------------|-------------------------------------------|----------------------------------------------------------------------|

|                  |                                 | Scope       | Elements                                  | Purpose                                                              |

| HL-SDL [14]      | SDL                             | Node        | Process-channels                          | nesC code<br>generation +<br>model execution<br>to analyze<br>(WECT) |

| Insense [12]     | Insense<br>Language             | Node        | components, channels                      | Analysis for WECT and WCS                                            |

| Mathworks [16]   | State Diagram and C             | Node-System | State-charts, communication medium        | NesC and C code<br>generation tool +<br>functional<br>analysis       |

| MDEA [29]        | UML                             | Node-System | Components<br>(wireless link as<br>class) | nesC Code<br>generation                                              |

| <b>PM</b> [19]   | Pormela                         | Network     | Processes, channel                        | Model checking<br>to verify the<br>connectivity of<br>the nodes      |

| SensorML [30]    | XML- Source<br>Code             | Node        | Components-<br>processes model            |                                                                      |

| SystemC-AMS [21] | Block Diagram –<br>C++          | Node        | Block diagram, source code                | Model Execution. Design analysis for SNR and BER                     |

| UM-RTCOM<br>[22] | CORBA                           | Node-System | Components, channels                      | Analyze WCET,<br>enhancing the<br>communication<br>properties        |

| <b>XRM</b> [24]  | eXtended<br>Reactive<br>Modules | Node-System | Modules                                   | Analyzing the Packet delivery probability and                        |

|  |  | power       |

|--|--|-------------|

|  |  | consumption |

Table 3-1: Overview of the Modeling Techniques

The scopes of the modeling technique can various to capture the node architecture, the network architecture, or both architectures. Modeling techniques uses different modeling elements to capture either the node behavior or the network behavior. The modeling techniques are targeted to analyze specific software challenges like concurrency, real-time, and event modeling. Modeling at the system level is also another feature that some modelers support.

As seen in Table 3-2 several modeling techniques like UM-RTCOM, XRM, PM, MDEA, and MathWorks can all model the sensor network but there is a focus for each on what behavior they model. They all model node activity and take into account node to node communication but not all can explicitly model the network topology as is the case with MDEA.

| Approach         | Node Behavior       | Network Behavior    | Network Topology    |

|------------------|---------------------|---------------------|---------------------|

| HL-SDL [14]      | Concurrency, event- | -                   | -                   |

|                  | driven              |                     |                     |

| Insense [12]     | Concurrency, real-  | -                   | -                   |

|                  | time                |                     |                     |

| Mathworks [16]   | Procedural, state   | Node/base station   | Single hope. Static |

|                  | space               | interaction         | topology            |

| MDEA [29]        | Procedural,         | Node/base station   | -                   |

|                  | state space         | interaction         |                     |

| <b>PM</b> [19]   | -                   | Node connectivity   | Multi hop, dynamic  |

|                  |                     |                     | topology            |

| SensorML [30]    | Event driven        | -                   | -                   |

| SystemC-AMS [21] | Procedural          | -                   | Single hop, static  |

|                  |                     |                     | topology            |

| UM-RTCOM [22]    | Concurrency, real-  | Nodes/actor/base    | Single hop,         |

|                  | time, event-driven  | station interaction | static topology     |

| XRM [24]         | Procedural,         | Power management-   | Single hop,         |

|                  | state space         | wake up states      | static topology     |

Table 3-2: Modeling of Node and System Arcitecture

This thesis approach has the following similarities to the modeling approach:

- Representation the topology as X-Y coordinates of the nodes using the strategy that is introduced by XRM.

- Calculating the power consumption using the strategy that is introduced by XRM and HL-SDL.

- Leveraging the state-chart to capture the node behavior, this is a similar to MDEA approach.

- The model of the node is platform independent. The platform specifications are added by the code generation, which is a similar approach to MDEA and Mathworks.

- Using the model execution techniques to analyze the system performance parameters.

However, none of the modeling techniques have presented a design patterns that are able to capture WSN design semantics. Additionally, our approach is capable of validating the functional represents of the design early during the design stages.

Additionally, this thesis introduced a methodology to validate the generated code by leveraging the sequence diagram execution feature and simulation results. Also the generated code by our approach does not require any sort of manual improvement, which is the case of MDEA and HL-SDL approach.

None of the modeling techniques have introduced a mythology to improve the design based on the analysis results. However, we have implemented a parsing tool to analyze the simulation results and integrate the results with the UML model so that the designer is capable to improve the design at the modeling layer.

# 4. UML Modeling and Power Consumption Analysis for Wireless Sensor Networks

## 4.1 Introduction