https://theses.gla.ac.uk/

Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# THEORY AND METHODOLOGY OF INTEGRATED LADDER FILTER DESIGN

A Thesis submitted to the

Faculty of Engineering

of the University of Glasgow

for the degree of

Doctor of Philosophy

by

LI PING

January 1990

(C) Li Ping, 1990

ProQuest Number: 11007332

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 11007332

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

TO MY PARENTS

#### SUMMARY

This thesis presents a systematic study of integrated ladder filter design. A theoretical model of ladder structures is first established in terms of a family of symmetric matrix polynomial systems (SMPS's). It is shown that SMPS's are a natural mathematical abstraction of ladder circuits. The properties of stability, canonical (or minimal) realisation, low-sensitivity and low-noise, are proved for SMPS's under certain very simple conditions.

A design methodology is then presented for active-RC, SC and digital ladders. The basic principle is that a SMPS can be decomposed by means of matrix factorisation into several linear systems, which can then be easily realised by active or digital circuits. It is shown that many existing methods, such as leapfrog or coupled biquads, result from some special decompositions. It is further shown that LU and UL factorisations drawn from numerical methods can be used to develop several novel structures (so-called LUD and ULD structures) which demonstrate significant improvments over existing ones regarding sensitivity, component area and dynamic range. This is confirmed by examples and statistical investigations.

Besides the matrix methods applicable to standard lowpass and bandpass cases, further research is undertaken for bandstop, highpass and allpass filter designs. It is demonstrated that frequency transformations can be used to reduce the hardware cost in many classical filtering cases. A novel building block, the so called TWINTOR, is introduced in bandstop design to reduce the switching rate. Active-RC and SC allpass ladders are constructed and proved to have significant advantages over the existing biquad circuits.

Matrix methods also provide an efficient vechicle for the development of a filter design software package called PANDDA. Its many outstanding features are described.

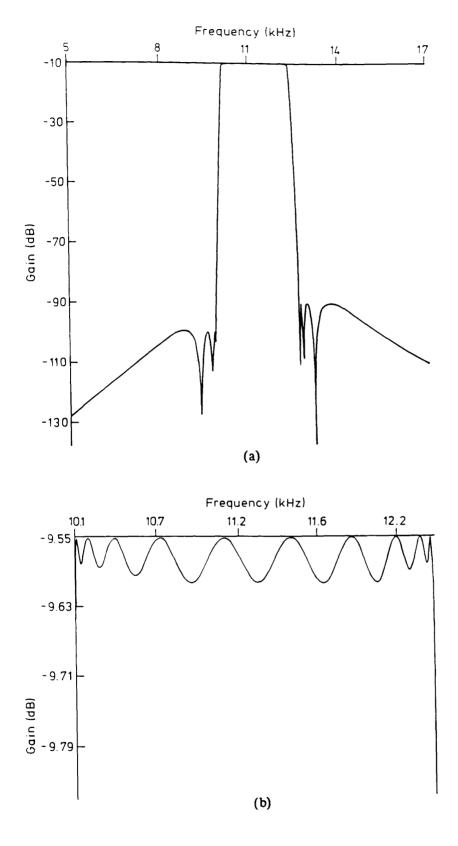

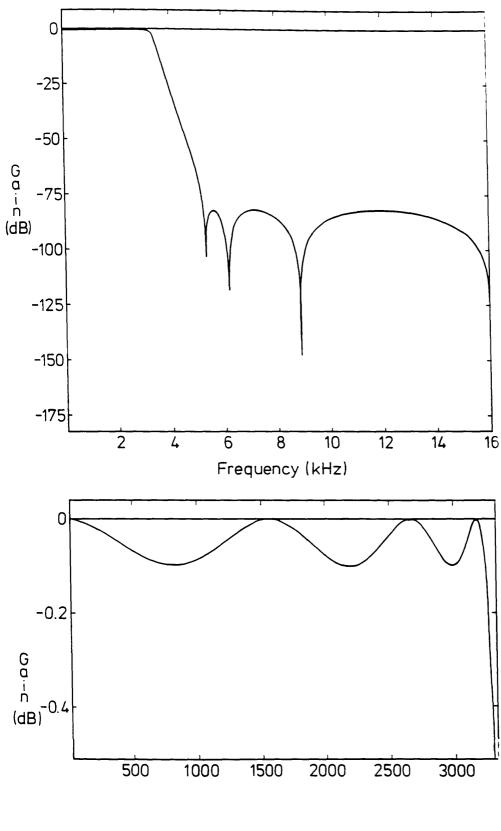

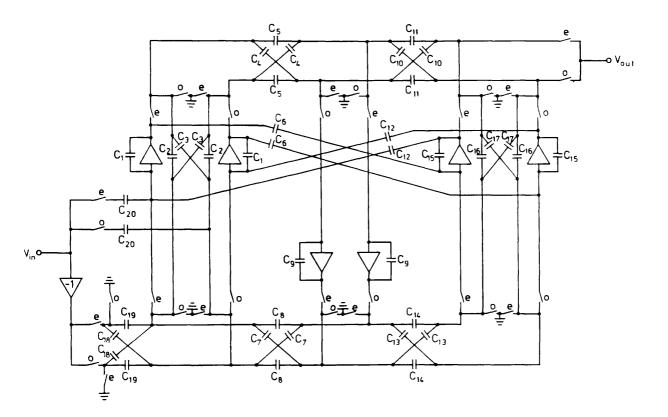

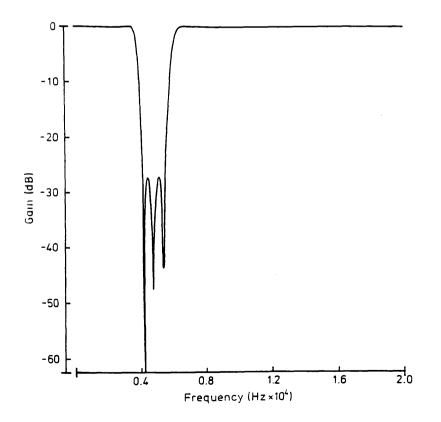

Finally measured results from two fabricated LUD SC filters are presented. They confirm the high quality of the novel circuit structures developed by this research.

i

#### **ACKNOWLEGEMENTS**

I wish to express my sincere thanks to my supervisor Professor J.I. Sewell for the opportunity to undertake this research and for his encouragement, help and guidance during the past three years. Thanks are also due to Professor J. Lamb for his encouragement in my studies and for allowing me to use the many facilities of the Department of Electronics and Electrical Engineering.

I would like to specially thank my friend Robert Henderson. His contribution in CAD software development has greatly facilitated this research. I gratefully appreciate his invaluable help throughout this work and, in particular, during the preparation of this thesis. I would also thank Lionel Wolovitz for many useful discussions.

I am grateful to Robert Taylor and James Reid for their collaboration in designing and testing the SC chips which have demonstrated the value of this work and to Wolfson Microelectronics Ltd., Edinburgh for the fabrication and evaluation of the designs.

I take great pleasure in acknowledging my colleagues Douglas Leith, Michael Manness, Majeed Ali Ahmed Foad, Martin Holland, Gail Hughes and Rebecca Cheung who have helped to create an enlightened atmosphere for research.

My thanks to Ann Mackinnon and Dugald Campbell for their assistance in using computer facilities and to Jessica Reid, Janice Whitelaw and Vi Winnie for their help in preparing the papers produced during this research.

I wish to acknowledge financial support from Glasgow University and also partly from the Royal Society and British Telecom.

Finally I would like to express my special thanks to my wife, Ruth, for her love and patience over all these years.

ii

# TABLE OF CONTENTS

| S UMM | ARY                                                    | i   |

|-------|--------------------------------------------------------|-----|

| ACKN  | OWLEDCMENTS                                            | i i |

| TABL  | E OF CONTENTS                                          | iii |

|       |                                                        |     |

| CHAF  | TER 1: INTRODUCTION                                    | 1   |

| 1.1   | BACKGROUND                                             | 2   |

| 1.2   | NETWORK ANALYSIS AND MATRIX PRINCIPLES                 | 2   |

|       | 1.2.1) Formulation of system descriptions              | 4   |

|       | 1.2.2) Ladder system matrices: sparse and symmetric    | 6   |

|       | 1.2.3) LU and UL matrix decomposition                  | 6   |

| 1.3   | FILTER DESIGN METHODS                                  | 10  |

|       | 1.3.1) Passive ladder and lattice network synthesis    | 10  |

|       | 1.3.2) First and second order circuit building blocks  | 11  |

|       | 1.3.3) Ladder simulations for active-RC and SC network |     |

|       | design                                                 | 16  |

|       | 1.3.4) Wave digital filters                            | 22  |

| 1.4   | COMPUTER AIDED FILTER DESIGN                           | 22  |

| 1.5   | GENERAL AIM AND OUTLINE OF THE THESIS                  | 22  |

|       | 1.5.1) Motivation                                      | 22  |

|       | 1.5.2) Purpose of the research                         | 23  |

|       | 1.5.3) Organisation of the thesis                      | 24  |

| 1.6   | STATEMENT OF ORIGINALITY                               | 26  |

|       |                                                        |     |

| CHAI  | TER 2: SYMMETRIC MATRIX POLYNOMIAL SYSTEMS             | 27  |

| 2.1   | I NTRODUCT I ON                                        | 28  |

| 2.2   | STABILITY CRITERIA                                     | 31  |

|       | 2.2.1) Critical stability                              | 31  |

|       | 2.2.2) Absolute stability                              | 32  |

| 2.3   | CANONICAL SYSTEMS                                      | 33  |

|     | 2.3.1)  | System order                                   | 33 |

|-----|---------|------------------------------------------------|----|

|     | 2.3.2)  | Condition for canonical ladder systems         | 34 |

| 2.4 | BOUNDEI | DNESS                                          | 38 |

|     | 2.4.1)  | The concept                                    | 38 |

|     | 2.4.2)  | Boundedness in the continuous domain           | 39 |

|     | 2.4.3)  | Boundedness for a terminated reactance network | 41 |

| 2.5 | SENSIT  | IVITY FORMULAE                                 | 43 |

| 2.6 | DISCRE  | TE SYMMETRIC MATRIX POLYNOMIAL SYSTEMS         | 46 |

| 2.7 | PSEUDO  | PASSIVITY AND LIMIT CYCLE SUPPRESSION          | 47 |

|     | 2.7.1)  | The concept                                    | 47 |

|     | 2.7.2)  | Psudopassivity for symmetric matrix polynomial |    |

|     |         | systems                                        | 48 |

|     | 2.7.3)  | Wave variables                                 | 49 |

|     | 2.7.4)  | Continuous time domain pseudopassive systems   | 52 |

| 2.8 | SUMMAR  | Y                                              | 53 |

|     |         |                                                |    |

| CHAPTER | 3: | MATRIX | METHODS | FOR | ACTIVE-RC | LADDER | DESIGN | 54 | 4 |

|---------|----|--------|---------|-----|-----------|--------|--------|----|---|

|         | •  |        |         |     |           |        |        | -  |   |

| 3.1 | INTRODUCTION                                             | 55 |

|-----|----------------------------------------------------------|----|

| 3.2 | MATRIX DESCRIPTION FOR ACTIVE-RC CIRCUITS                | 56 |

| 3.3 | MATRIX METHODS FOR ACTIVE-RC CIRCUIT DESIGN              | 61 |

|     | 3.3.1) Alternating sign for nodal voltages               | 61 |

|     | 3.3.2) System linearisation by matrix decompositions     | 62 |

|     | 3.3.3) Various ways to perform the matrix decompositions | 63 |

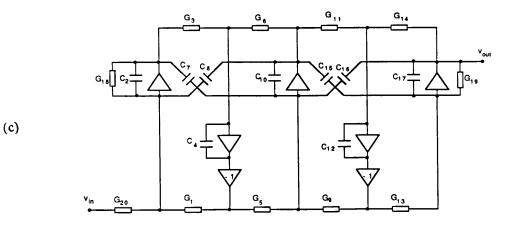

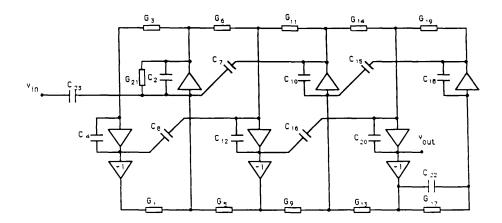

|     | 3.3.4) Examples of various circuit structures            | 64 |

|     | 3.3.5) A comparison of left- and right- LUD methods      | 70 |

| 3.4 | UL-LU and LU-UL METHODS                                  | 71 |

|     | 3.4.1) System linearisation by UL-LU methods             | 71 |

|     | 3.4.2) Procedure to solve (3.10)                         | 72 |

|     | 3.4.3) Formulae for LU-UL design                         | 73 |

| 3.5 | CANONICAL LADDER FILTER DESIGN                           | 77 |

|     | 3.5.1) Restrictions of the standard methods              | 77 |

|     | 3.5.2) Modified canonical prototype                      | 79 |

|     | 3.5.3) Canonical ladder simulation by active circuits    | 79 |

| 3.6 | SPECIAL DESIGN TECHNIQUES                                | 82 |

|     | 3.6.1) Hybrid matrix approaches                          | 82 |

|     | 3.6.2) Inverse matrix approaches                         | 84 |

|     |                                                          |    |

CHAPTER 4: MATRIX METHODS FOR SC AND DIGITAL LADDER DESIGN 87

| 4.1 | INTRODUCTION                                     | 88  |

|-----|--------------------------------------------------|-----|

| 4.2 | LDI TRANSFORMED DISCRETE LADDERS                 | 89  |

|     | 4.2.1) LDI transformed systems                   | 89  |

|     | 4.2.2) SC LDI ladders                            | 91  |

| 4.3 | BILINEAR-LDI DISCRETE LADDERS                    | 94  |

|     | 4.3.1) Bilinear-LDI systems                      | 94  |

|     | 4.3.2) SC bilinear-LDI ladders                   | 95  |

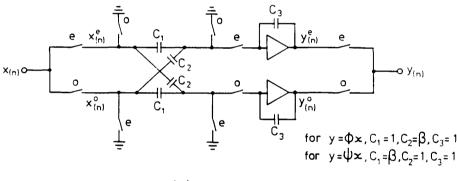

|     | 4.3.3) UL-LU and LU-UL discrete ladders          | 102 |

|     | 4.3.4) Canonical discrete ladders                | 105 |

| 4.4 | MODIFICATION OF BILINEAR DISCRETE LADDERS        | 107 |

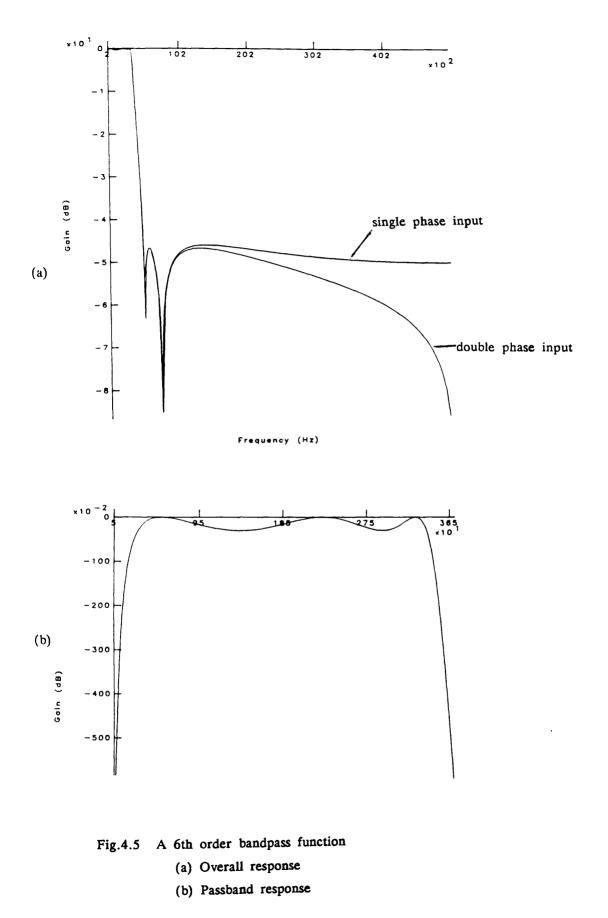

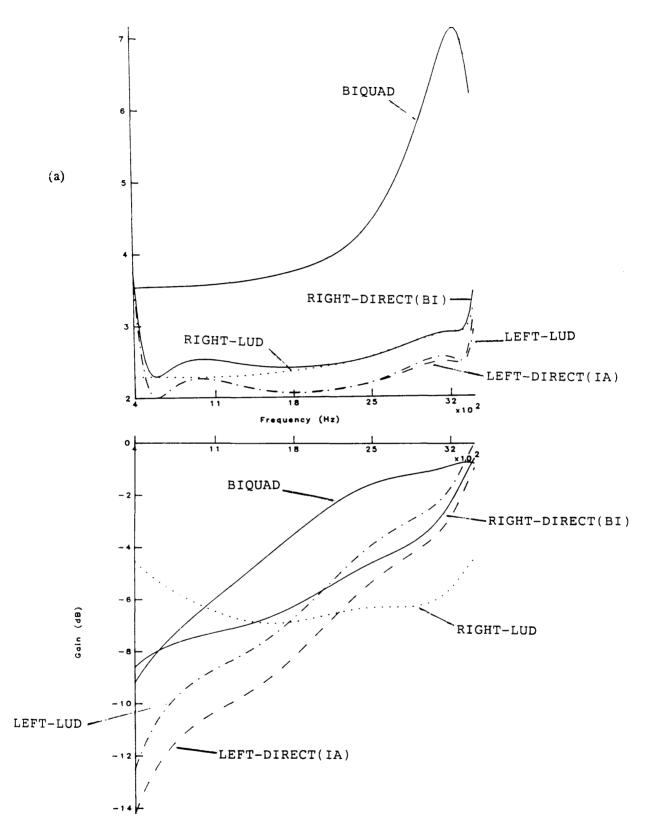

| 4.5 | HIGH ORDER DISCRETE LADDER DESIGN                | 108 |

| 4.6 | DIGITAL BILINEAR-LDI LADDERS                     | 113 |

|     | 4.6.1) Digital LU-LU ladders                     | 113 |

|     | 4.6.2) Scaling technique to increase parallelism | 116 |

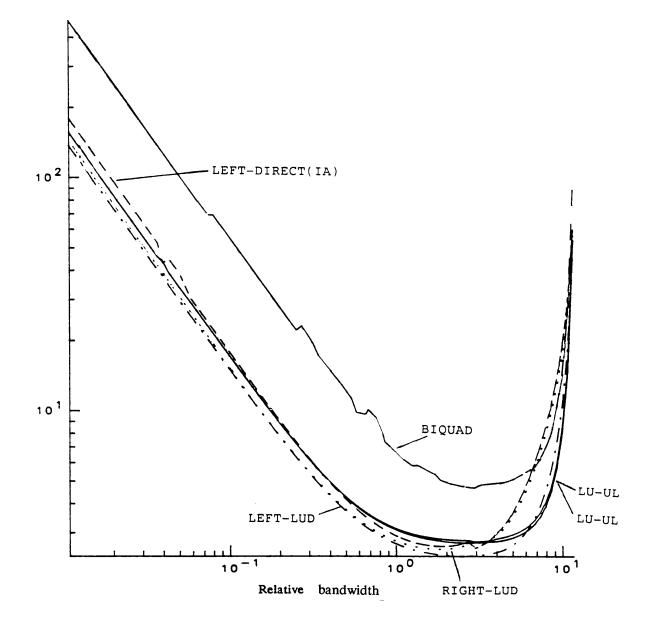

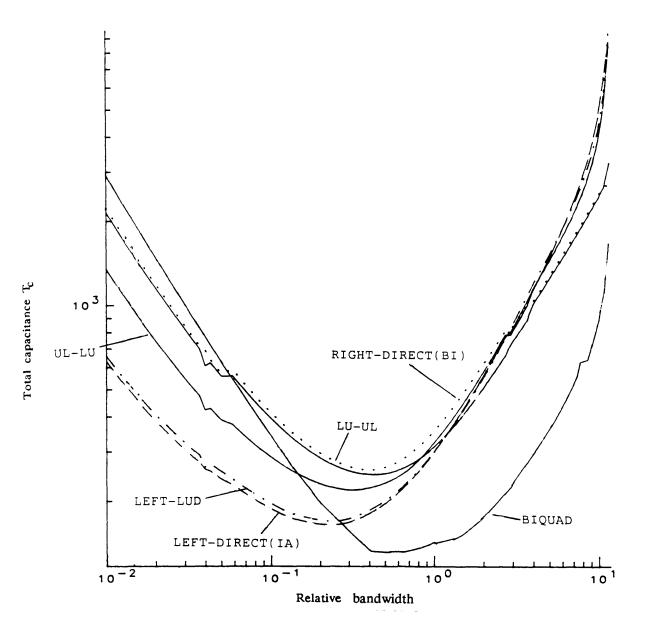

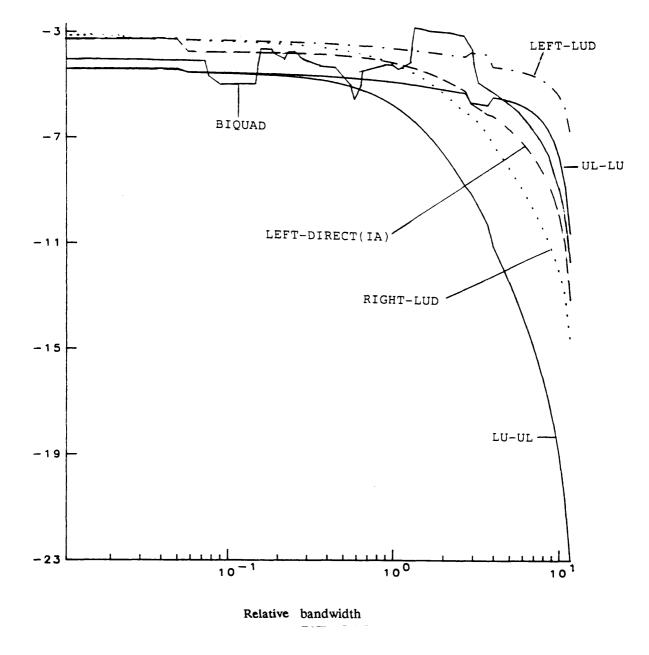

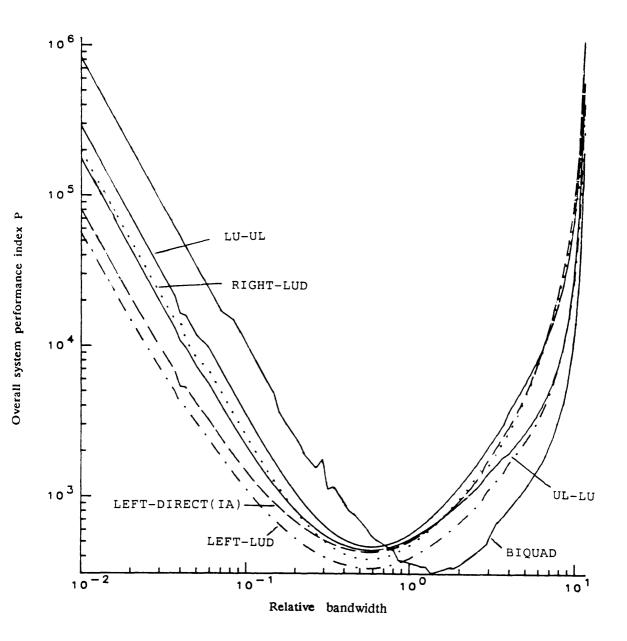

| 4.7 | STATISTICAL STUDIES                              | 121 |

| 4.8 | SUMMARY                                          | 123 |

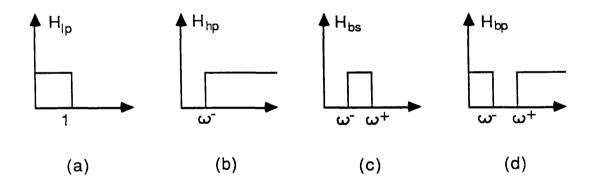

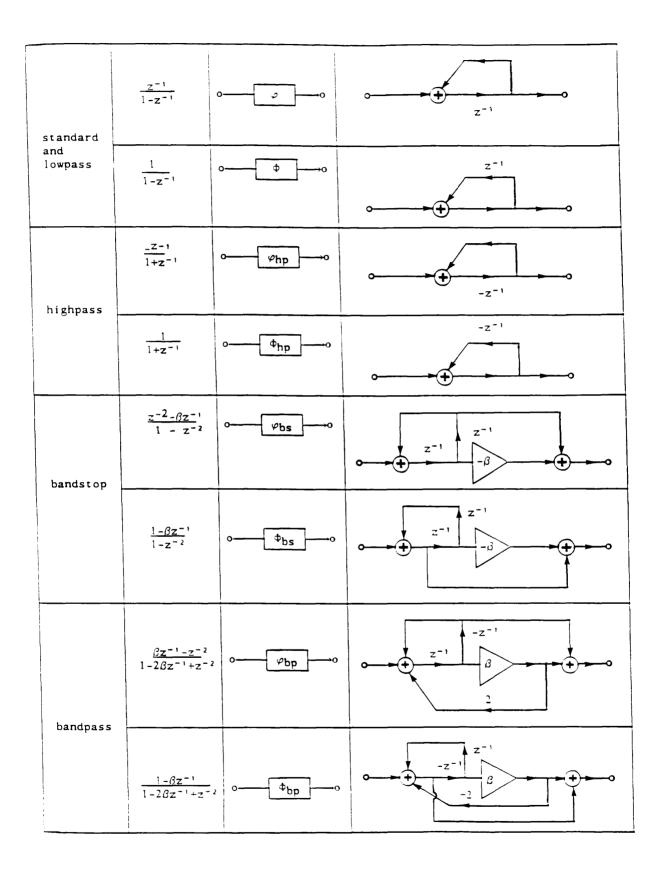

#### CHAPTER 5: FREQUENCY TRANSFORMATION METHODS FOR DISCRETE LADDER DESIGN 137 5.1 INTRODUCTION 138 5.2 FREQUENCY TRANSFORMATION METHODS FOR DIGITAL LADDER DESIGN 139 5.2.1) Lowpass to highpass transformation 140 5.2.2) Lowpass to bandstop transformation 142 5.2.3) Lowpass to bandpass transformation 143 5.2.4) Discussions 148 5.3 FREQUENCY TRANSFORMATION METHODS FOR SC LADDER DESIGN 148 5.3.1) Lowpass to highpass transformation 148 5.3.2) Lowpass to bandstop transformation 149 5.3.3) Lowpass to bandpass transformation 153 5.4 SUMMARY 153

v

| CHAPTER 6: ACTIVE AND DIGITAL ALLPASS LADDER DESIGN        | 154 |

|------------------------------------------------------------|-----|

| 6.1 INTRODUCTION                                           | 155 |

| 6.2 CONTINUOUS DOMAIN ALLPASS LADDERS                      | 156 |

| 6.2.1) Active RLC allpass ladder design                    | 156 |

| 6.2.2) Active RC ladder design                             | 158 |

| 6.3 DISCRETE DOMAIN ALLPASS LADDERS                        | 159 |

| 6.3.1) Left-LUD method for SC and digital ladder design    | 162 |

| 6.3.2) Right-LUD method for SC and digital ladder design   | 163 |

| 6.4 SENSITIVITY ESTIMATIONS                                | 166 |

| 6.5 EXAMPLES AND COMPARISONS                               | 168 |

| 6.6 SUMMARY                                                | 174 |

|                                                            |     |

| CHAPTER 7: SOFTWARE PACKAGE AND FABRICATED CIRCUITS        | 175 |

| 7.1 INTRODUCTION                                           | 176 |

| 7.2 PANDDA; A PROGRAM FOR ADVANCED NETWORK DESIGN: DIGITAL |     |

| AND ANALOGUE                                               | 176 |

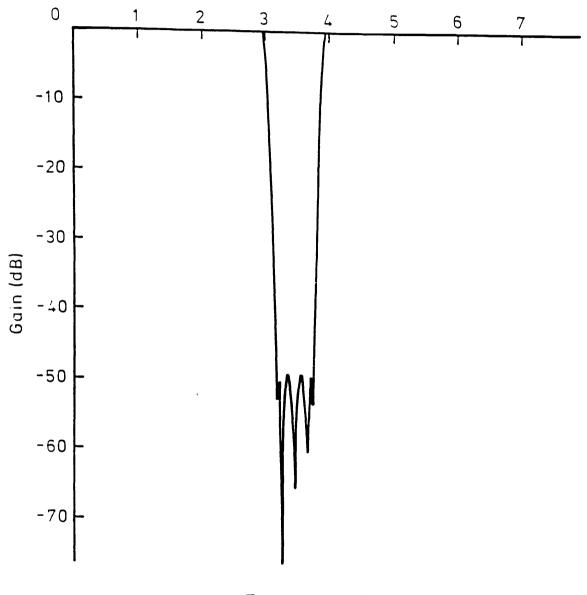

| 7.3 TEST RESULTS OF FABRICATED SC LADDER CIRCUITS          | 179 |

| 7.4 SUMMARY                                                | 180 |

|                                                            |     |

| CUARTER OF CONCLUCTIONS AND SUCCESSIONS FOR ROCCURE        |     |

| CHAPTER 8: CONCLUSIONS AND SUGGESTIONS FOR POSSIBLE        | 191 |

| FURTHER WORK                                               | 191 |

| 8.1 DISCUSSION OF THE RESULTS                              | 192 |

| 8.2 SUGGESTIONS FOR POSSIBLE FURTHER WORK                  | 194 |

REFERENCES 198

## CHAPTER 1

# INTRODUCTION

# 1.1 BACKGROUND

# 1.2 NETWORK ANALYSIS AND MATRIX PRINCIPLES

- 1.2.1) Formulation of system descriptions

- 1.2.2) Ladder system matrices: sparse and symmetric

- 1.2.3) LU and UL matrix decomposition

# **1.3 FILTER DESIGN METHODS**

- 1.3.1) Passive ladder and lattice network synthesis

- 1.3.2) First and second order circuit building blocks

- 1.3.3) Ladder simulations for active-RC and SC network design

- 1.3.4) Wave digital filters

# 1.4 COMPUTER AIDED FILTER DESIGN

- 1.5 GENERAL AIM AND OUTLINE OF THE THESIS

- 1.5.1) Motivation

- 1.5.2) Purpose of the research

- 1.5.3) Organisation of the thesis

# **1.6 STATEMENT OF ORIGINALITY**

## 1.1 BACKGROUND

Filter circuits are of great importance in communication systems, signal processing and control devices. They direct, channel, separate and transform electrical signals.

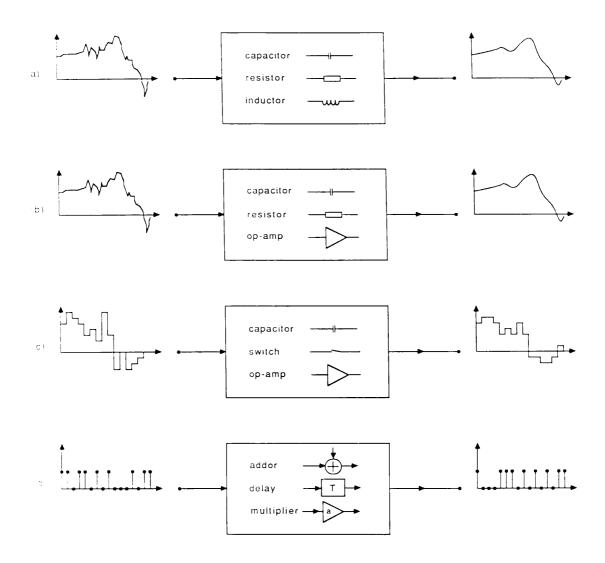

The majority of voice band filters were realised as RLC passive circuits, Fig.1.1a, [1-11] until the 1960s when it was recognised that size and eventual cost reduction could be achieved by replacing the large, costly inductors with active- RC networks, Fig.1.1b, [12-21]. The progress of integrated circuit (IC) technology, such as the monolithic operational amplifier and the thick and thin-film circuits, later enabled one to realize high-quality, miniature, hybrid active- RC circuits with very low cost. With the emergence of VLSI (Very Large Scale Integration) technology in the 1970's, it became possible to realise high order analogue filters on microminiature silicon chips [13,22-25].

In VLSI, it is easier to fabricate capacitors and switches than resistors with the required accuracy. This gave rise to a new analogue sampled-data system, the switched capacitor (SC) circuits, Fig.1.1c, [25-72]. Recent interest has grown in Gallium-Arsenide (GaAs) implementations of SC circuits for high frequency applications [31,41].

In the last two decades, digital filters (Fig.1.1d) have been increasingly employed in communications, signal processing and control functions [73-94]. This is due to the accuracy, flexibility, programmability and modularity of digital systems, in addition to the high level of integration achievable in VLSI.

# 1.2 NETWORK ANALYSIS AND MATRIX PRINCIPLES

Circuit theory is now divided into two major branches; analysis and design, each with its own distinct methodology. In circuit analysis, methods have been developed to handle systematically large, sparsely connected networks, a task which has been expedited by modern matrix and graph theory [95,96]. This rationalisation has not been reflected in the field of circuit design. Design methods, more or less, still focus on local building blocks rather than take an overall view of target systems.

- (a) Passive RLC filter

- (b) Active- RC filter

- (c) Switched-capacitor filter

- (d) Digital filter

The strategy of the research presented in this thesis is to incorporate network analysis techniques in circuit design. For this reason a brief review of circuit analysis is necessary.

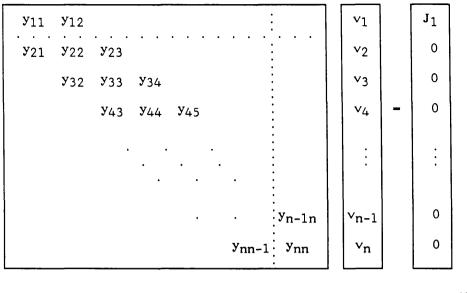

## 1.2.1) Formulation of passive network descriptions

Nodal approaches are most popular in formulating network equations. Suppose a network has n ungrounded nodes and m passive admittance elements. Let  $J_i$  be the current flowing into the i<sup>th</sup> node from n external independent current sources. The network behaviour is described by an admittance matrix equation of the form [95,96]:

$$\begin{bmatrix} y_{11} & y_{12} & \dots & y_{nn} \\ y_{21} & y_{22} & \dots & y_{2n} \\ \dots & \dots & \dots & \dots \\ y_{n1} & y_{n2} & \dots & y_{nn} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ \vdots \\ v_n \end{bmatrix} = \begin{bmatrix} J_1 \\ J_2 \\ \vdots \\ J_n \end{bmatrix}$$

(1.1)

or

$$\mathbf{Y} \mathbf{V} = \mathbf{J} \tag{1.2}$$

## Topological matrix decomposition:

Y can be decomposed on a topological basis as [96]

$$\mathbf{Y} = \mathbf{A} \mathbf{Y}_{\mathbf{b}} \mathbf{A}^{\mathsf{T}} \tag{1.3}$$

where  $\mathbf{Y}_b$  = diag {  $y_1$ ,  $y_2$ , ...  $y_m$  } is a m×m diagonal matrix and  $\mathbf{A}$  is a n×m incidence matrix defined by

$a_{ij} = \begin{cases} -1 & \text{if branch j is incident to and directed towards node i} \\ 0 & \text{if branch j is not incident to node i} \\ 1 & \text{if branch j is incident to and directed outwards from node i} \\ & (1.4) \end{cases}$

# Polynomial expression of the admittance matrix:

For an RLC network, the contributions of capacitor  $C_k$ , inductor  $L_k$  and conductors  $G_k$  to the admittance matrix are, respectively,  $sC_k$ ,  $s^{-1}L_k^{-1}$  and  $G_k$ . Consequently Y is a matrix polynomial in s with

$$Y = s C + s^{-1} \Gamma + G$$

(1.5)

Notice here  $\Gamma$  consists of the inverse inductance values. C,  $\Gamma$  and G can also be topologically decomposed by considering only the capacitance, inductance or resistance subnetworks respectively.

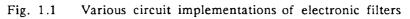

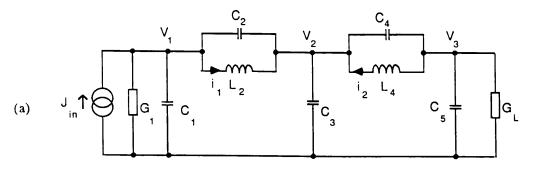

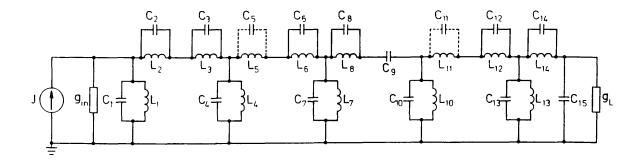

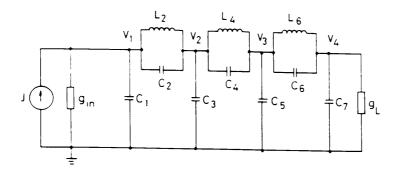

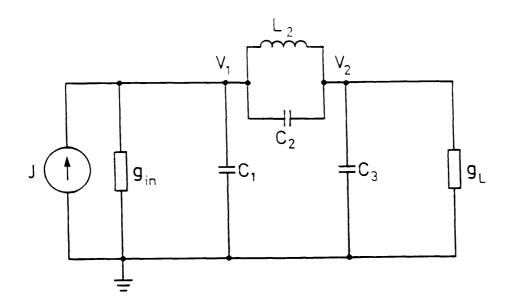

Fig. 1.2 A 6th order passive doubly-terminated ladder filter

*Example 1.1:* For a 6th order ladder, Fig.1.2, the nodal formulation leads to the following matrix equations,

$$\begin{cases} c_{1}+c_{2} & c_{2}\\ -c_{2} & c_{2}+c_{3}+c_{4} & -c_{4}\\ & -c_{4} & c_{4}+c_{5} \end{cases} + s^{-1} \begin{bmatrix} L_{2}^{-1} & -L_{2}^{-1} & -L_{4}^{-1} \\ -L_{2}^{-1} & L_{2}^{-1}+L_{4}^{-1} & -L_{4}^{-1} \\ & -L_{4}^{-1} & L_{4}^{-1}+L_{5}^{-1} \end{bmatrix} + \\ + \begin{bmatrix} G_{in} & & \\ & & G_{L} \end{bmatrix} \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} \\ v_{3} \end{bmatrix} = \begin{bmatrix} J_{in} \\ 0 \\ 0 \end{bmatrix}$$

(1.6a)

and the topological decompositions of C and  $\Gamma$  are

$$C = \begin{bmatrix} 1 & 1 & & \\ & -1 & 1 & 1 & \\ & & & -1 & 1 \end{bmatrix} \begin{bmatrix} C_1 & & & \\ & C_2 & & \\ & & C_3 & \\ & & & C_4 & \\ & & & & C_5 \end{bmatrix} \begin{bmatrix} 1 & & & \\ & 1 & -1 & \\ & & 1 & -1 \\ & & & 1 \end{bmatrix}$$

(1.6b)

$$\Gamma = \begin{bmatrix} 1 & & \\ -1 & 1 & \\ & -1 & 1 \end{bmatrix} \begin{bmatrix} L_2^{-1} & & \\ & L_4^{-1} & \\ & & L_5^{-1} \end{bmatrix} \begin{bmatrix} 1 & -1 & & \\ & 1 & -1 & \\ & & 1 & 1 \end{bmatrix}$$

(1.6c)

# 1.2.2) Ladder system matrices: sparse and symmetric

If a ladder circuit is labelled so that every node i is joined only to either nodes i-1 or i+1 or both, Fig.1.2, then matrices C,  $\Gamma$ , G and so Y are all tridiagonal, as can be seen from (1.6a). Therefore ladders are typical sparse systems [97].

From (1.3) it is seen that C,  $\Gamma$ , G and Y are all symmetric matrices. Furthermore it is easy to verify that C,  $\Gamma$  and G are non-negative definite [98] provided that only positive RLC elements are considered. Notice that the reverse is not always true. For example, let matrices C and  $\Gamma$  be

$$\mathbf{C} = \begin{bmatrix} 2 & 1 \\ 1 & 2 \end{bmatrix} \qquad \mathbf{\Gamma} = \begin{bmatrix} 2 & -1 \\ -1 & 2 \end{bmatrix} \qquad (1.7)$$

They are both positive definite but  $Y = sC + s^{-1}\Gamma$  can not be realised by an RLC circuit with positive elements.

# 1.2.3) LU and UL matrix decompositions

The solution of the algebraic equations,

$$Y V = J \tag{1.8}$$

can be performed by the *triangular* or LU decomposition technique [95,99]. The main advantage of LU decomposition over Gaussian elimination is that it enables efficient solution of system with different excitation vectors J. By LU decomposition a matrix Y is factorised as follows

$$\mathbf{Y} = \mathbf{L} \ \mathbf{U} \tag{1.9}$$

where L stands for the *lower triangular* and U for the *upper triangular* matrix. The system (1.8) is now written as

$$\mathbf{L} \ \mathbf{U} \ \mathbf{V} = \mathbf{J} \tag{1.10}$$

Define an auxiliary vector W as

$$\mathbf{U} \, \mathbf{V} = \mathbf{W} \tag{1.11}$$

Substitute W into (1.10)

$$\mathbf{L} \ \mathbf{W} = \mathbf{J} \tag{1.12}$$

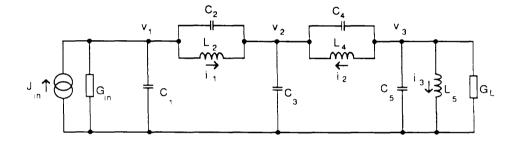

Due to the special form of L and U, the vectors W and the solution V can be calculated very efficiently. Consider the most simple case when Y is tridiagonal so that L and U will have the form,

$$\mathbf{L} = \begin{bmatrix} \mathbf{1}_{11} & & & \\ \mathbf{1}_{21} & \mathbf{1}_{22} & & \mathbf{0} & \\ & \mathbf{1}_{32} & \mathbf{1}_{33} & & \\ & & & \ddots & \ddots & \\ & & & & & \mathbf{1}_{n(n-1)} & \mathbf{1}_{nn} \end{bmatrix}$$

(1.13a)

and (notice the unity valued entries on the main diagonal of U)

$$\mathbf{U} = \begin{bmatrix} 1 & \mathbf{u}_{12} & & & \\ & 1 & \mathbf{u}_{23} & & 0 \\ & & 1 & \mathbf{u}_{34} & & \\ & & & \ddots & \ddots & \\ & & 0 & & & \ddots & \dot{\mathbf{u}}(\mathbf{n}-1)\mathbf{n} \\ & & & & & 1 \end{bmatrix}$$

(1.13b)

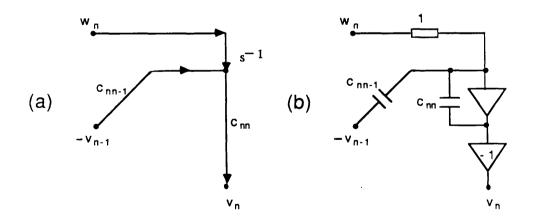

The solution of (1.12) can then be written as

$$w_{1} = J_{1}/l_{11}$$

$$w_{i} = J_{i}/l_{ii} - [l_{i(i-1)}/l_{ii}]w_{i-1} \qquad i=2,3,...n \qquad (1.14a)$$

This is called the *forward substitution* process, Fig.1.3a. To solve for the unknown vector V in (1.11), start with the last equation and work upward,

$$v_n = w_n$$

$v_i = w_i - u_{i(i+1)}w_{i+1}$   $i=n-1, n-2, ...1$  (1.14b)

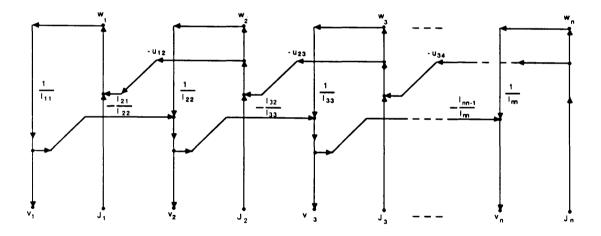

Fig. 1.3 Signal-flow-graph for solving a linear system by LU decomposition method

- (a) Forward substitution

- (b) Backward substitution

- (c) Overall process

This process is called *backward substitution*, Fig.1.3b. The whole forward and backward procedures can be visualised in a signal-flow-graph (SFG) form, Fig.1.3c. Notice a special relationship for (1.14) and Fig.1.3; *if* Y *is symmetric then* [99]

$$l_{i(i-1)}/l_{ii} = u_{i(i+1)}$$

(1.15)

A similar procedure can be developed if  $\mathbf{Y}$  is factorised by UL decomposition,

$$Y = U L$$

(1.16)

A SFG is given in Fig.1.4 for solving (1.8) via (1.16). Again if Y is symmetric then (1.15) holds.

Fig. 1.4 Signal-flow-graph for solving linear system by UL decomposition method

#### **1.3 FILTER DESIGN METHODS**

Generally speaking there are two approaches to filter structure design; direct methods and simulation methods. The former starts directly from a transfer function, either as a single polynomial or ratio of polynomials, and the networks are derived by some algebraic expansions of the transfer function. The latter transforms some prototype circuit into different implementations while preserving the transfer function. This is done in order to inherit certain beneficial properties from the prototype. Examples of direct design methods are:

1) direct realisation without any expansion, e.g., follow-the-leader type circuits [12,73]

2) expansion into the product or sum of second order sections, e.g., cascade, parallel biquads and allpass LC lattice [1,12,73]

3) expansion into partial fraction form, e.g., ladder and Gray-Markel's digital lattice [2,3,82]

A simulation is based on some sort of one-to-one correspondance between the prototype and the simulated circuit [3,12,73]. This correspondance could be between the port characteristics of the components in the two circuits, called component simulation, or between the signal-flow-graphs (SFGs) representing the two circuits, called functional simulation.

Component simulation methods, such as those using gyrators [17,60] and GICs [18] to simulate inductors, generally require floating opamps or floating capacitors which are prone to errors during manufacture. Functional simulation methods have been more successfully developed and have found wide industrial application, especially for SC circuits [19-21, 51-59]. They form the main topic investigated in this thesis.

## 1.3.1) Passive ladder and lattice network synthesis

For amplitude filtering the *doubly terminated ladders*, Fig.2, are the most widely used passive structures with well established theory [1-11]. Ladder circuits are well known for their distinguished property of being very insensitive to component deviations.

For delay equalisation, passive all-pass circuits are mostly realised as lattice derived bridged-T networks [1]. They are basically cascade second order filters,

with a unique fixed port resistance for both ports of each section. Since they are impedance matched they can be cascaded without introducing any distortion. Each second order section usually has 5 reactance elements, as shown in Fig. 1.5.

(a) (b)

# Fig. 1.5 A second order allpass lattice section and its equivalent bridged-T form

# 1.3.2) First and second order circuit building blocks

Most active and digital networks can be regarded as the repeated connection of a few regular structured subnetworks, so-called building blocks [3,12,16,73].

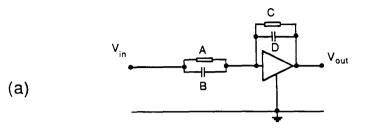

A list of first order active-RC, SC and digital building blocks is given in Fig.1.6. It can be verified that the transfer functions of the circuits in Fig.1.6 are, respectively,

(a)

$$H(s) = -(A+sB)/(C+sD)$$

(1.17a)

(b)

$$H(z) = [-A(1-z^{-1})+Bz^{-1}-C]/(D+E-Dz^{-1})$$

(1.17b)

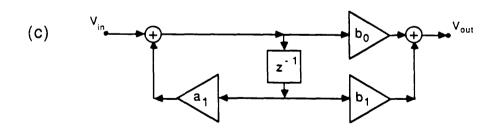

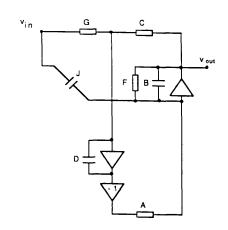

(c)

$$H(z) = (b_0 + b_1 z^{-1})/(1 + a_1 z^{-1})$$

(1.17c)

Fig. 1.6 First order building blocks

- (a) Active- RC circuit

- (b) Switched- capacitor circuit

- (c) Digital circuit

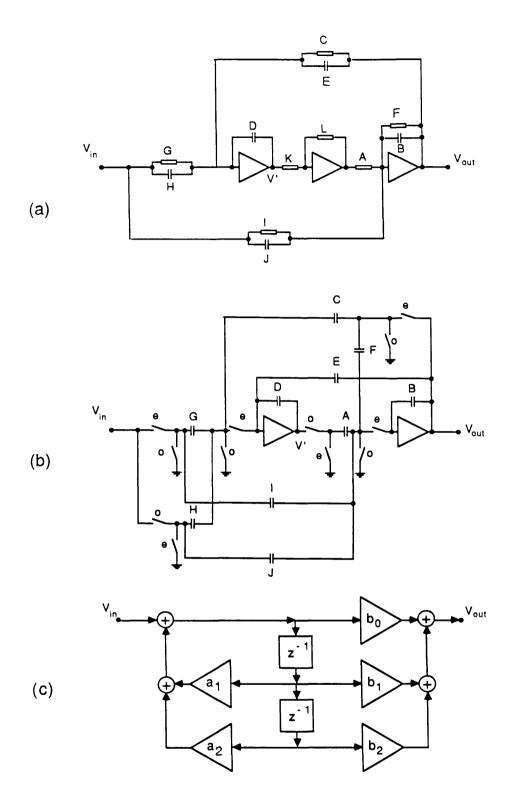

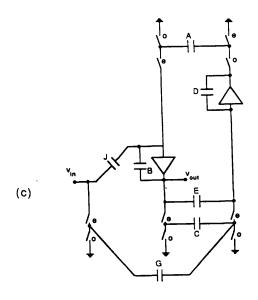

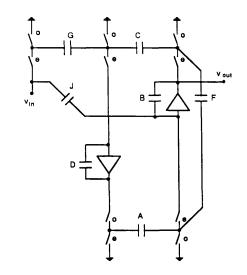

- Fig. 1.7 Second order building blocks

- (a) Active- RC circuit

- (b) Switched-capacitor circuit

- (c) Digital circuit

Second order building blocks, more often referred to as biquad sections, are particular useful as they can be assembled to form cascade or parallel biquad structures, based on the fact that any real rational function H(p) (p may be either s or z for the continuous domain or the discrete domain respectively) can be factorised as,

$$H(p) = \pi \qquad (1.18a)$$

$$a_{0i} + a_{1i}p^{-1} + a_{2i}p^{-2}$$

or alternatively can be partial fractioned as

$$H(p) = \sum \frac{d_{0i} + d_{1i}p^{-1} + d_{2i}p^{-2}}{c_{0i} + c_{1i}p^{-1} + c_{2i}p^{-2}}$$

(1.18b)

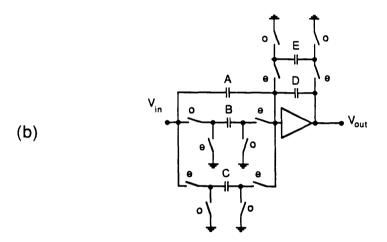

The design of cascade and parallel biquads can be easily carried out using the active-RC, SC and digital biquads shown in Fig.1.7, with the transfer functions,

(a)

$$H(s) = - \frac{DLJ + (HKA + DLI)s^{-1} + CKAs^{-2}}{DLB + (DLE + FKA)s^{-1} + (CKA)s^{-2}}$$

(1.19a)

(b)

$$H(z) = - \frac{DI + (AC - DI - DJ)z^{-1} + (DJ - AH)z^{-2}}{D(F + B) + (AC + AE - DF - 2DB)z^{-1} + (DB - AE)z^{-2}}$$

(1.19b)

(c)

$$H(z) = \frac{b_{0i} + b_1 z^{-1} + b_2 z^{-2}}{1 + a_1 z^{-1} + a_2 z^{-2}}$$

(1.19c)

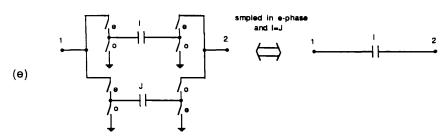

It is also convenient to separate the active-RC and SC realisations using only E-capacitor damping (F=0) or only F-capacitor damping (E=0). These two cases are referred to as the E-type and F-type circuits, respectively [12]. In particular, set H=I=0 in Fig.1.7a, to realise a pair of zeroes on the imaginary axis for active-RC circuits, or set I=J and H=0, to realise a pair of zeroes on the unit circle for SC circuits. In these cases the transfer functions can be simplified to,

(a)

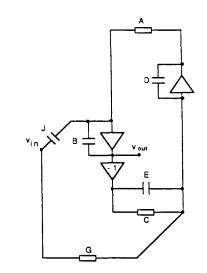

(b)

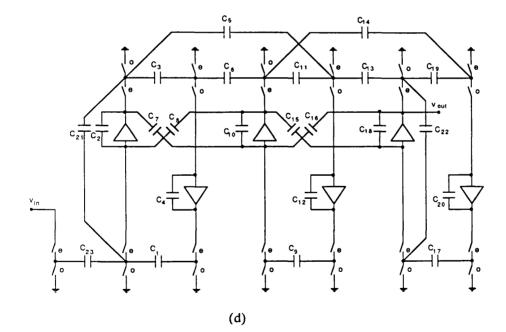

(d)

Fig. 1.8 E- type and F- type second order building blocks

- (a) E-type active-RC circuit

- (b) F- type active- RC circuit

- (c) E- type switched- capacitor circuit

- (d) F- type switched- capacitor circuit

- (e) Switched capacitor circuit equivalence

(a)

$$H(s) = - \frac{DJ+GAs^{-2}}{DB+DEs^{-1}+CAs^{-2}}$$

with L=K=1 (1.20a)

Ω

(b)

$$H(s) = - \frac{DJ+GAs^{-2}}{DB+FAs^{-1}+CAs^{-2}}$$

with L=K=1 (1.20b)

(c)

$$H(z) = - \frac{DJ + (AC - 2DJ)z^{-1} + DJz^{-2}}{DB + (AC + AE - 2DB)z^{-1} + (DB - AE)z^{-2}}$$

(1.20c)

(d)

$$H(z) = - \frac{DJ + (AC - 2DJ)z^{-1} + DJz^{-2}}{D(F+B) + (AC - DF - 2DB)z^{-1} + DBz^{-2}}$$

(1.20d)

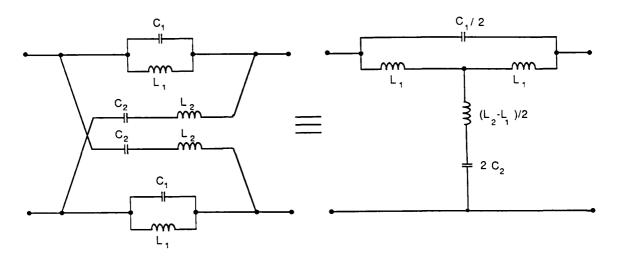

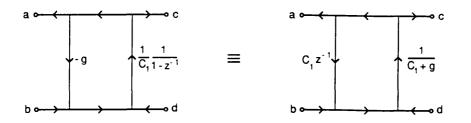

In Fig.1.8 circuit realisations are given for these special cases. Notice that when I= J, the parallel combination of two switched capacitors is equivalent to a single unswitched capacitor, Fig.1.18e and this property has been used in Fig.1.8c,d. It should also be noticed that the biquads in Fig.1.8 are special examples of the ladder structures developed in this thesis when order=2.

Cascade biquads structures are very regular and their design procedure can be easily automated. However they are also notorious for their poor sensitivity and noise behaviour.

The first and second order SC sections listed in Fig.1.6 and 1.7 are all insensitive to grounded stray capacitance [12,32]. This stray-insensitive property is vital for high precision circuit performance in the presence of significant bottom and top plate stray capacitance effects in current MOS technology. For practical considerations, only these stray-insensitive SC building blocks will be used in this thesis.

# 1.3.3) Ladder simulations for active-RC and SC network design

In 1966 Orchard presented his well-known observation that a properly designed terminated LC ladder would demonstrate very low sensitivity in the passband, with respect to the drift of component values [15]. Since then, various approaches have been proposed to simulate LC ladders by active and digital circuits [17-21,51-67,76-81] to benefit from this important property.

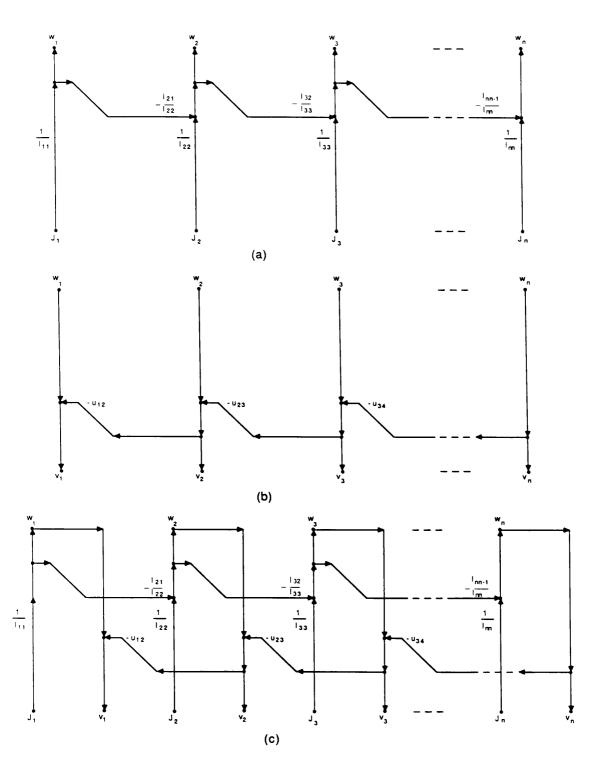

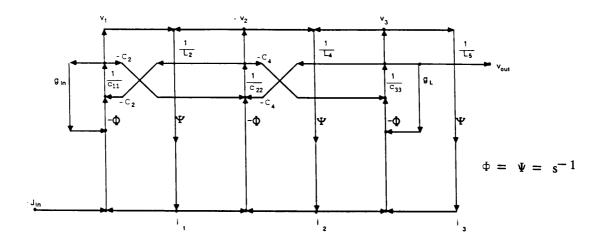

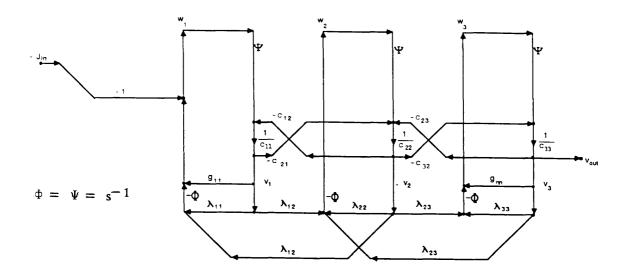

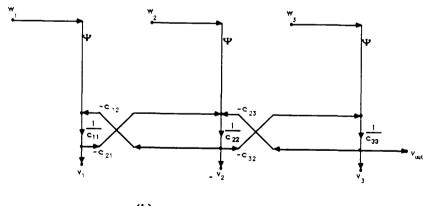

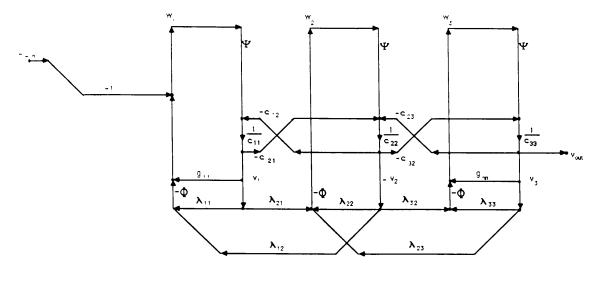

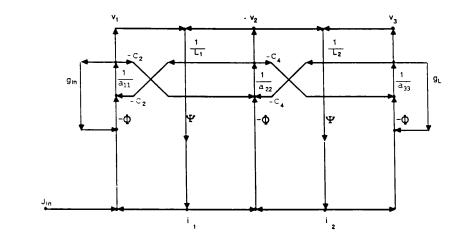

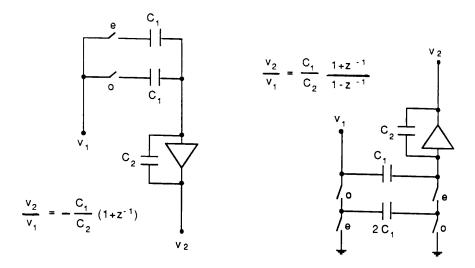

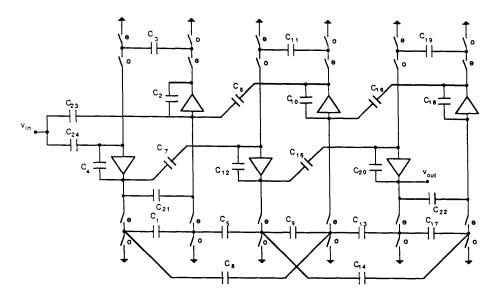

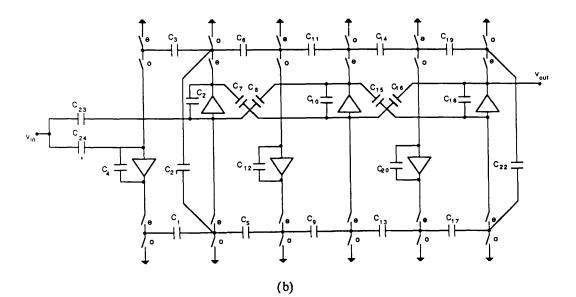

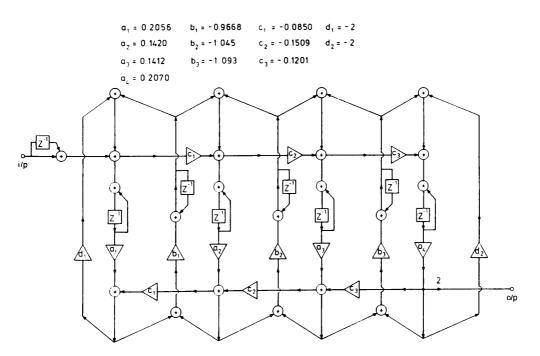

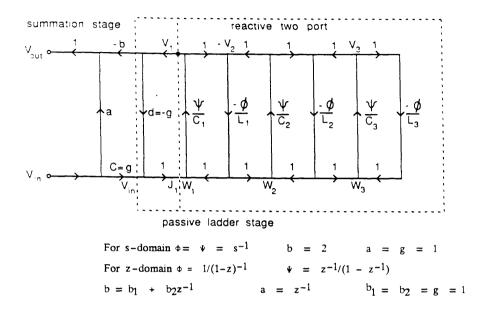

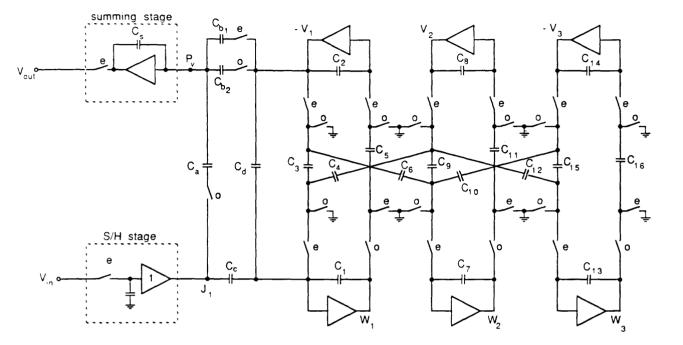

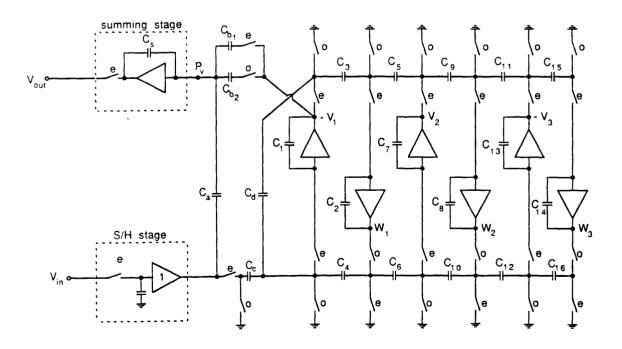

In an operational simulation approach, a set of equations is established which is sufficient to describe the LC ladder prototype. Each equation is then simulated by a simple active or digital network. In a leapfrog design these equations simply represent the voltage-current relationship of individual elements in the prototype [19,20,51], so they are linear with respect to frequency  $s = j\omega$ . Only first order sections are required to form the network. In a coupled biquad design the equations are set up for the voltage-voltage relationship between nodes and are generally quadratic with respect to s [21,53]. Biquad sections are required in simulation and hence the name.

# Example 1.2:

Take a 6th order active-RC ladder design as a example. Use the circuit shown in Fig.1.2 as prototype. In a leapfrog design the following network equations are obtained,

$c_{11}v_{1} = (-1/s)(i_{1}-Jin+g_{in}v_{1}) - C_{2}v_{2} \qquad c_{11} = C_{1} + C_{2}$   $L_{1}i_{1} = (1/s)(v_{1}-v_{2})$   $-c_{22}v_{2} = (-1/s)(i_{1}+i_{2}) - C_{2}v_{1} - C_{4}v_{3} \qquad c_{22} = C_{2} + C_{3} + C_{4}$   $L_{4}i_{2} = (1/s)(-v_{2}+v_{3})$   $c_{33}v_{3} = (-1/s)(i_{2}+g_{L}v_{3}) - C_{4}v_{2} \qquad c_{33} = C_{4} + C_{5}$   $L_{5}i_{3} = (1/s)v_{3} \qquad (1.21)$

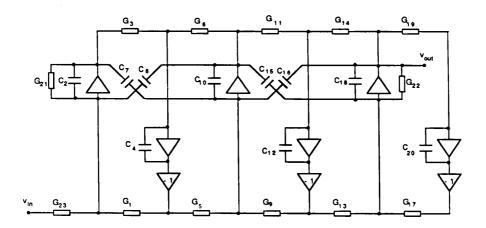

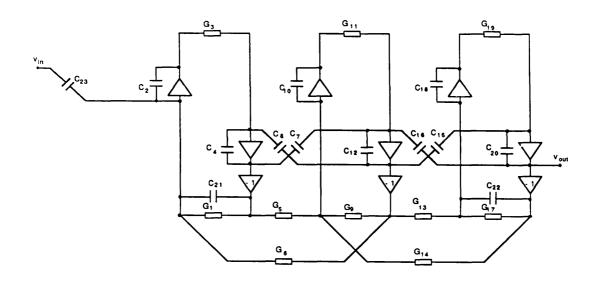

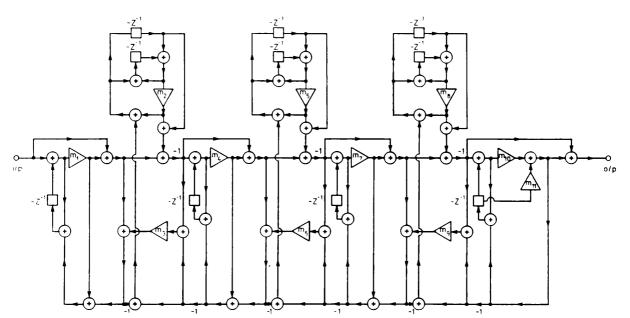

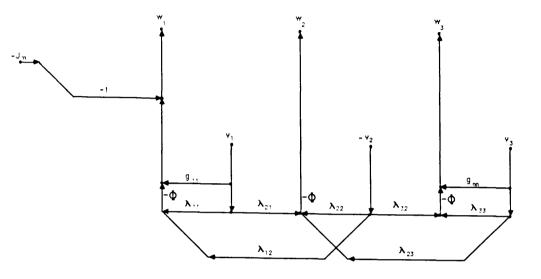

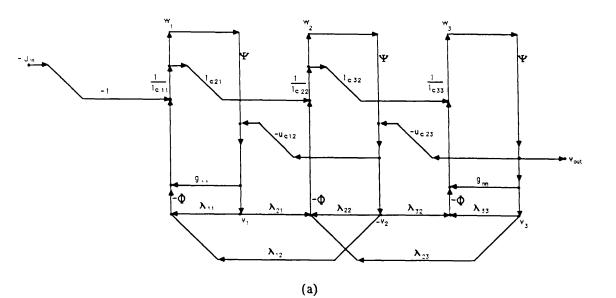

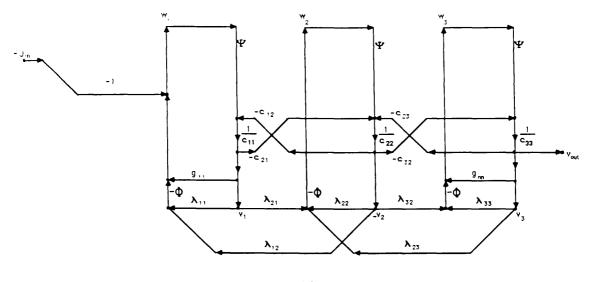

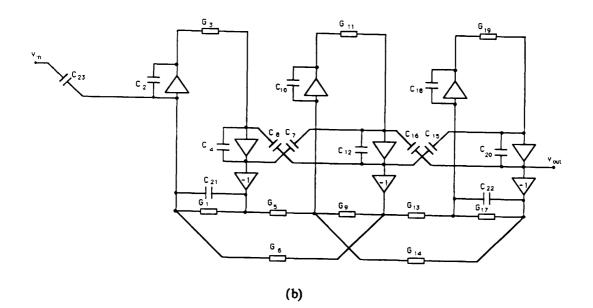

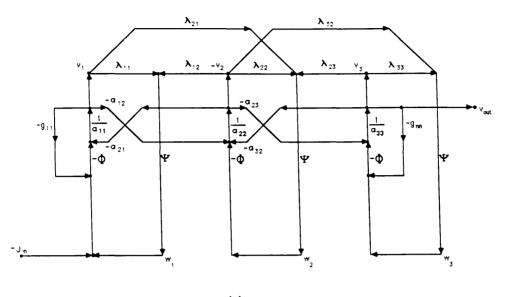

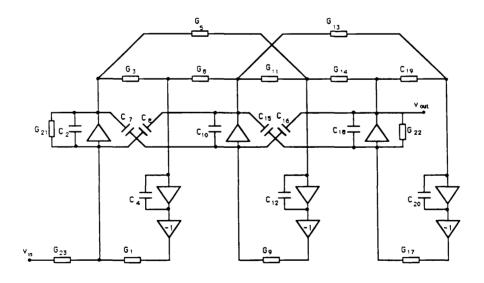

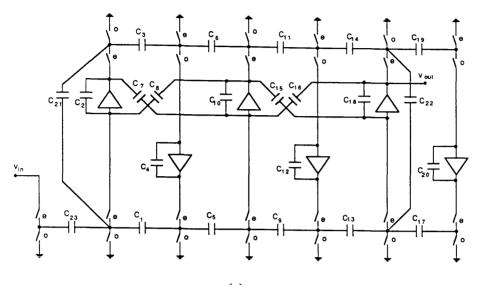

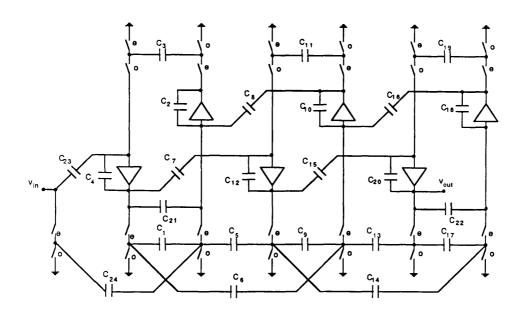

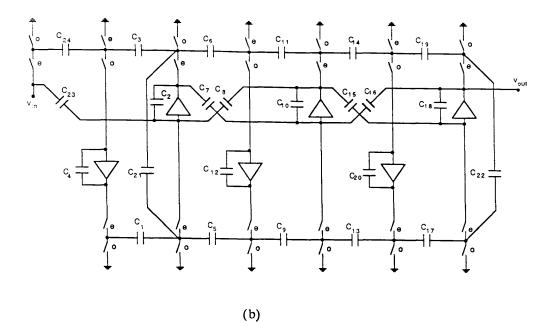

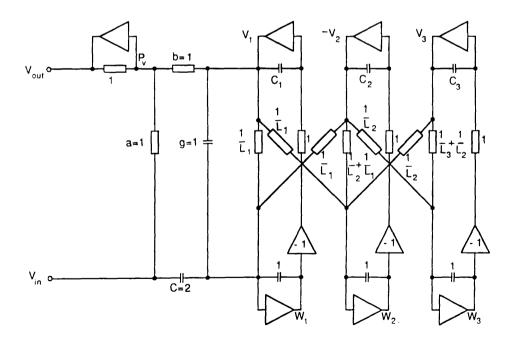

These equations are represented by the SFG shown in Fig.1.9a. To convert the SFG into active-RC circuit, one can use Fig.1.6 and replace the branches in the SFG by the corresponding active-RC branches. The resulting circuit is shown in Fig.1.9b.

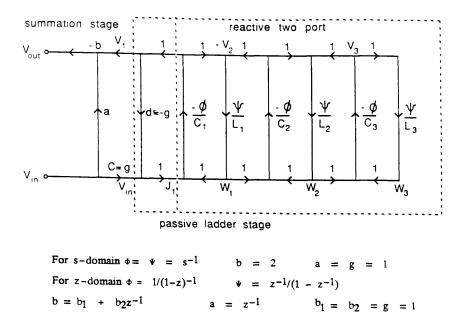

In a coupled biquad method the prototype, Fig.1.2, is described by a set of second order equtions,

$$v_{1} = \frac{-(s^{2}c_{12}+\lambda_{12})v_{2} - (-sJ_{in})}{s^{2}c_{11} + sg_{11} + \lambda_{11}} c_{11}=C_{1}+C_{2} g_{11}=g_{in}$$

$$-(s^{2}c_{21}+\lambda_{21})v_{1}-(s^{2}c_{23}+\lambda_{23})v_{3} c_{21}=C_{2} \lambda_{21}=1/L_{2} c_{23}=C_{4} \lambda_{23}=1/L_{4}$$

$$-v_{2} = \frac{-(s^{2}c_{21}+\lambda_{21})v_{1}-(s^{2}c_{23}+\lambda_{23})v_{3}}{s^{2}c_{22} + \lambda_{22}} c_{22}=C_{2}+C_{3}+C_{4} \lambda_{22}=1/L_{2}+1/L_{4}$$

$v_{3} = \frac{-(s^{2}c_{32}+\lambda_{32})v_{2}}{s^{2}c_{33} + sg_{nn} + \lambda_{33}} c_{32}=C_{4} \lambda_{32}=1/L_{4}$   $c_{33}=(C_{4}+C_{5}) g_{nn}=g_{L} \lambda_{33}=1/L_{4}+1/L_{5}$ (1.22)

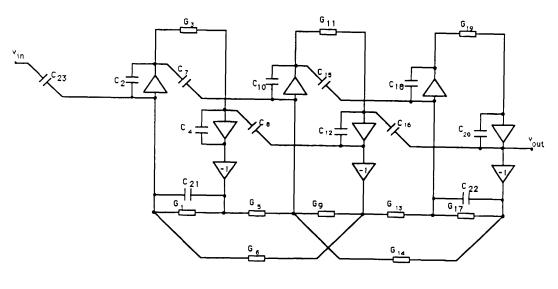

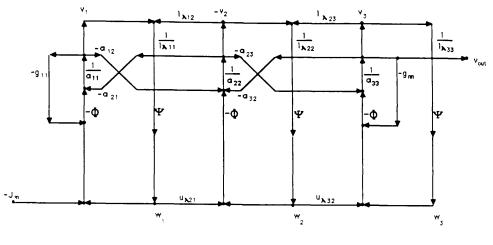

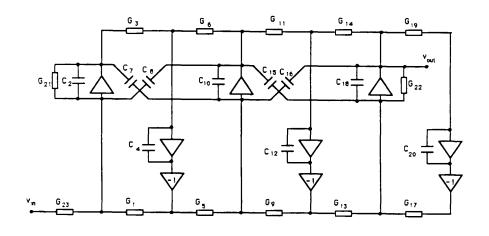

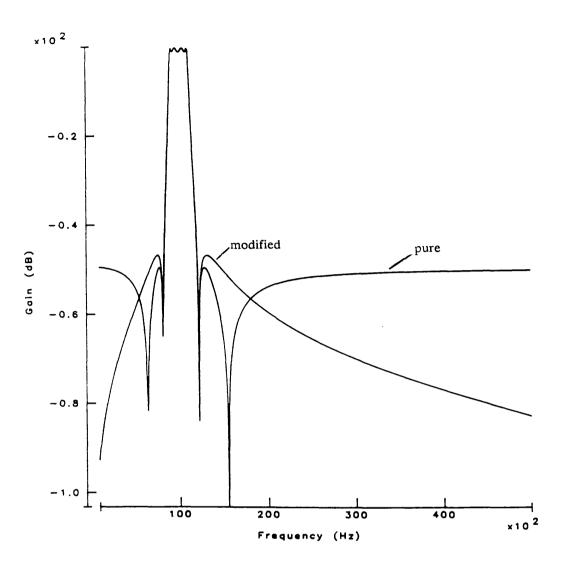

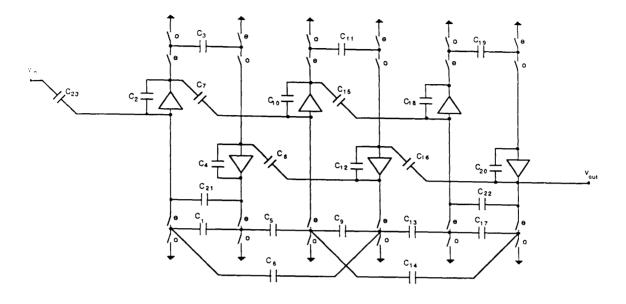

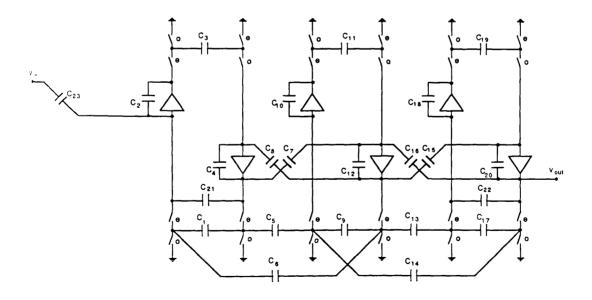

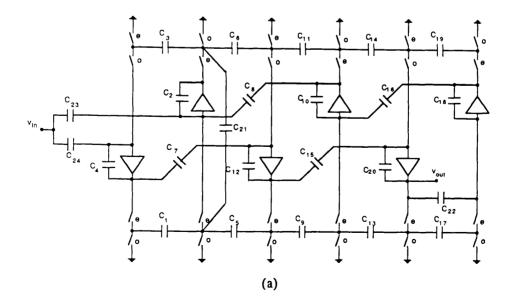

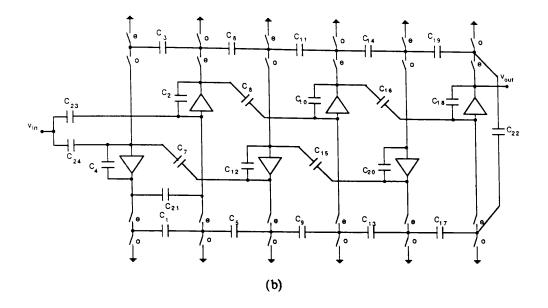

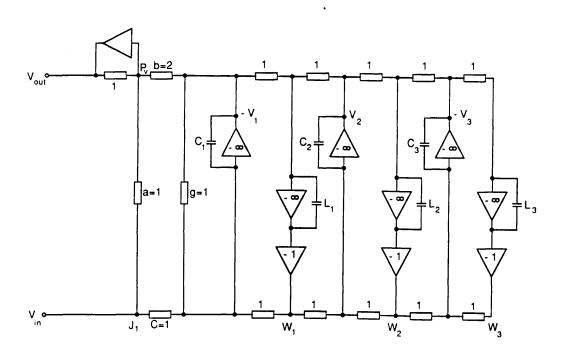

These equations are again represented by the SFG shown in Fig.1.10a (note  $a_{ij}=a_{ji}$  and  $\lambda_{ij}=\lambda_{ji}$ ) and can be replaced by connection of second order active- RC E- type biquads in Fig.1.7, resulting in the circuit in Fig. 1.10b.

In the leapfrog method there is a clear link between individual elements in the prototype and the building blocks in the simulated circuit. If the prototypes have an excessive number of components, such as in the bandpass case, an excessive number of integrators will be required. There are various ways to eliminate the redundant opamps [3] but they become tedious even for moderate design orders. In SC design very high capacitance spreads are often observed for bandpass leapfrog design. So normally leapfrog is only considered for the lowpass design case.

Coupled biquad filters always require an even number of opamps (not including inverters), which doubles the number of nodes. It is only efficient for even order filters whose node number is just half of the order e.g. a bandpass filter frequency-transformed from an odd order lowpass one.

SC simulations of passive ladders follow the same principle although some manipulation is required in adopting LDI type integrators [51,53].

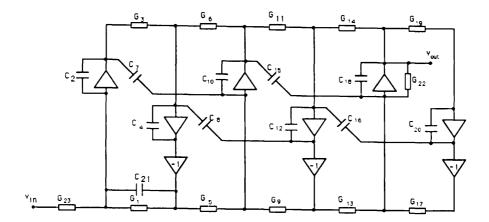

In general leapfrog and coupled biquad active-RC and SC circuits will possess capacitor coupled opamp loops, as shown by the loop  $c_2 - c_7 - c_{10} - c_8$  in Fig.1.9b and  $c_4 - c_7 - c_{12} - c_8$  in Fig.1.10b. These loops are detrimental to the performance of active-RC and SC circuits, since high frequency noise can oscillate around such loops, when non-ideal factors, such as on-switch resistances and finite GB product of the opamps, are included [35]. Examining the SFGs and the circuits carefully, it can be seen that such loops will exist if there are loops in the SFG with constant transmission (without frequency dependent factor s or z). In the z-domain, such loops are called delay-free-loops, and they cannot be realised by digital circuits. This explains why leapfrog and coupled-biquad methods are difficult to apply to digital filter

(a)

(b)

Fig. 1.9 Leapfrog type ladder simulation

- (a) Signal-flow-graph

- (b) Active- RC circuit realisation

(a)

# (b)

Fig. 1.10 Coupled-Biquads type ladder simulation

- (a) Signal-flow-graph

- (b) Active- RC circuit realisation

$C_1 = 3.450 \text{ F}$  $C_2 = 0.1717 \text{ F}$  $L_2 = 4.137 \text{ H}$  $C_7 = 3.082 \text{ F}$  $C_3 = 5.601 \text{ F}$  $C_4 = 0.8016 \text{ F}$  $L_4 = 3.828 \text{ H}$  $g_{in} = 1S$  $C_5 = 5.328 \text{ F}$  $C_5 = 0.5772 \text{ F}$  $L_6 = 3.659 \text{ H}$  $g_L = 1S$

| m <sub>1</sub> = -0.7748 | m <sub>5</sub> = - 0.7532         | m <sub>9</sub> = 0.1203   |

|--------------------------|-----------------------------------|---------------------------|

| $m_2 = -0.4140$          | m <sub>6</sub> = 0.1511           | m <sub>10</sub> = -0.6899 |

| m <sub>3</sub> = 0.08522 | m <sub>7</sub> = ~ 0. <b>8550</b> | m <sub>11</sub> = -0.5851 |

| m <sub>4</sub> = -0.9366 | m <sub>8</sub> = - 0.6774         |                           |

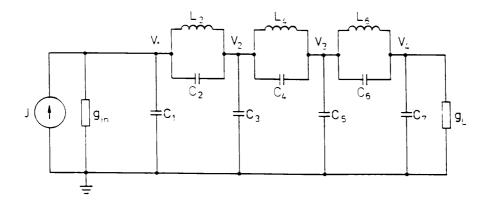

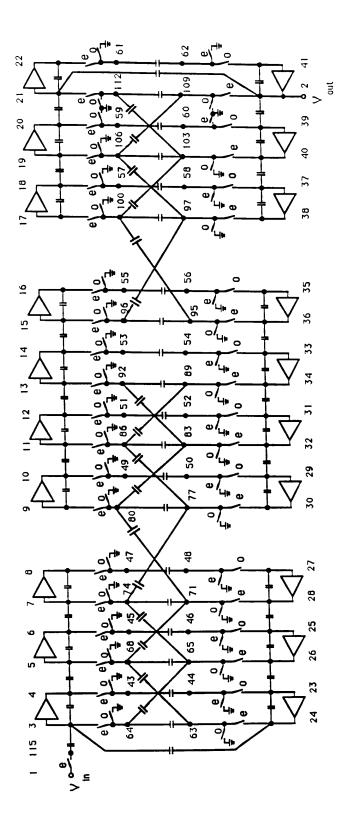

Fig. 1.11 Wave digital filter

- (a) A 7th order ladder prototype

- (b) A wave digital circuit simulation

design. Wave digital filters have been proposed to solve the unrealisability problem in ladder simulations [77].

## 1.3.4) Wave digital filter

The effects of coefficient quantisation in digital filters are analogous to the sensitivity problem of analogue filters. The *wave digital filter* method was originally proposed by Fettweis as the low sensitivity alternative to direct approaches, later it attracted much attention due to its good noise properties [77].

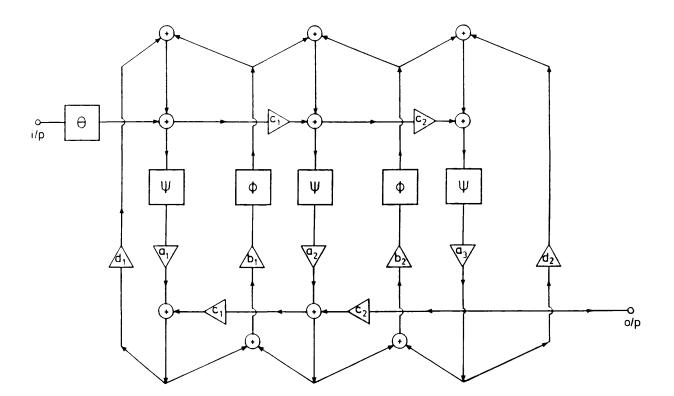

A wave digital filter is also a ladder simulation. However, it simulates the relationships between so-called *wave variables*, instead of voltages and currents. A passive ladder is regarded as a combination of a number of 2- port circuit elements and 3- port series and parallel wire interconnection called adaptors [73,77]. An example of the simulation of the 7th order circuit in Fig.11a is shown in Fig.1.11b.

# **1.4 COMPUTER AIDED FILTER DESIGN**

The large number of circuit options exaggerates the problem of design time and effort. Although design tables are available for some standard filters [2], they cannot cover all possible requirements. The performance of different structures under non-ideal conditions largely depends on the desired specifications, and is therefore a complex function of a large number of parameters such as Q factor, response class, order, filter structure and so on. Consequently, an exact prediction of the performance amongst different realisations is difficult, if not impossible. A full comparision of different approaches is preferable before deciding on a particular one. It seems that this can only be approached with the help of modern CAD (computer aided design) techniques. A great amount of effort has been expended [102-113] but, essentially, all the design software published so far remains at the development stage. The reason may lie in the mathematical and programming difficulties involved, as well as the fact that the fabrication technology has changed so rapidly since the 1970s.

# 1.5 GENERAL AIM AND OUTLINE OF THE THESIS

## 1.5.1) Motivation

Despite their obvious advantages regarding size, weight, cost and flexibility, active and digital circuits still suffer from some drawbacks, such as

1) Active components, such as transistors and opamps, have a finite gain-bandwidth (GB) product which imposes a limitation on their useful range of operation [33-35].

2) Active filters are likely to be affected by inaccuracies during manufacture or component drift due to environmental changes. For the digital case, an equivalent effect is caused by truncation of multiplier coefficients in finite wordlength storage [3,12,73].

3) In active filters a significant noise level issues from the active devices. Digital filters introduce noise due to signal quantisations [3,12,73].

The influence of the above problems depends, to a large extent, on the network topology adopted. A carefully designed structure will greatly improve the performance of the resulting filters.

## 1.5.2) Purpose of the research

It has long been known that highly stable, low sensitivity and low noise properties may be obtained by employing multi-feedback circuits. However, as the degree of circuit coupling increases, the current design methods, rooted in their view of local circuit connections, become intractable.

Effort has been devoted to regularise the design process by viewing a filter in terms of system theory. Marshall first introduced UL matrix decomposition into wave digital ladder simulations based on state space variables [81]. Snelgrove, Roberts and Sedra have also investigated state—space models in active ladder design [114][118]. They indicated that a proper choice of intermediate state variables can improve system performance. However, it is difficult to use the standard state space model to provide a clear insight into the relationship between the structure and performance of the filter system.

The research presented in this thesis will deal with the above-mentioned difficulty. Departing from the state space concept, a system description adopting high order matrix polynomials is studied as a fundamental mathematical framework. Ladder based structures are the most natural representation of such

systems. Very simple, attainable criteria have thus been formalised for deriving stable filter structures with low sensitivity and low noise.

Some very regular procedures are established to linearise the system description into a set of matrix equations which are realisable by basic circuit building blocks. By arranging the filter system in a form amenable to some well studied methods of linear algebra, present clumsy equation—by—equation procedures for ladder simulation can be replaced by single matrix processing steps. A unification of the existing methods is revealed, together with a family of novel structures. Various techniques will also be proposed for individual applications where standard methods meet difficulties, such as for bandstop, highpass or allpass functions or result in inefficient realisations, such as for all—pole filters.

#### 1.5.3) Organisation of the thesis

A review of the circuit analysis and design is included in the present chapter, together with some comments on the limitations of state-of-the-art filter design.

In Chapter 2 a theoretical investigation is presented for a family of matrix polynomial systems. Definitions and criteria are formulated for canonical ladder prototypes. It is shown that important properties like boundedness and pseudopassivity, which are essential to achieve low sensitivity and low noise systems, are closely related to the matrix symmetry. Sensitivity formulae are derived for both symmetric or asymmetric deviations of matrix entries.

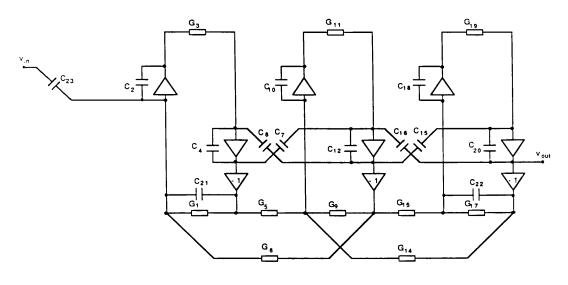

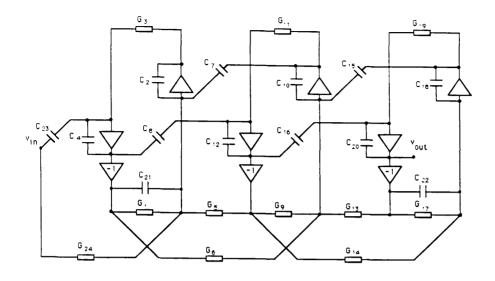

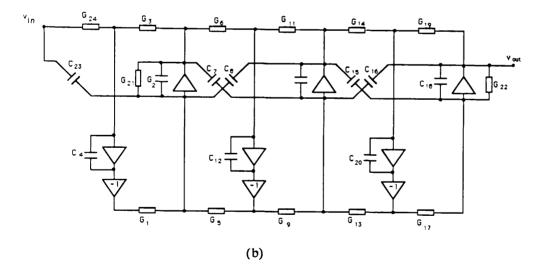

The realisation of the matrix polynomial system by active-RC circuits is considered in Chapter 3. It is shown that the existing ladder simulation methods can be unified into a general family of circuits derived by adopting different matrix decompositions. Novel circuit structures are obtained by employing the LU decomposition drawn from numerical methods. Some of these structures, so-called left-LUD, UL-LU and LU-UL structures have a notable advantage of being free from capacitance-coupled-opamp loops. Due to the flexibility introduced by matrix methods, there is a wide choice of structures available to realise a given prototype. While a number of special techniques are discussed for individual design cases, a unified approach is also proposed to realise general transfer function by very regular circuit structures.

The matrix decomposition methods are extended to SC and digital filter

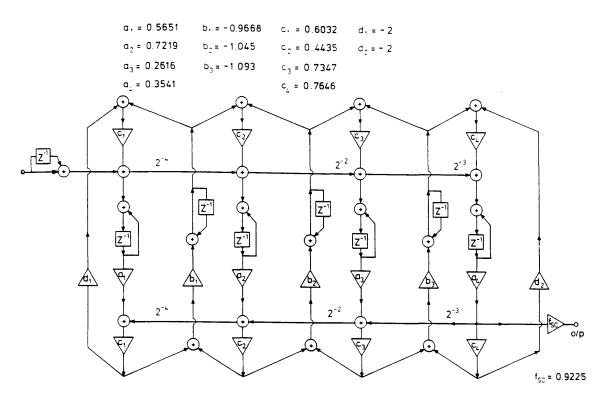

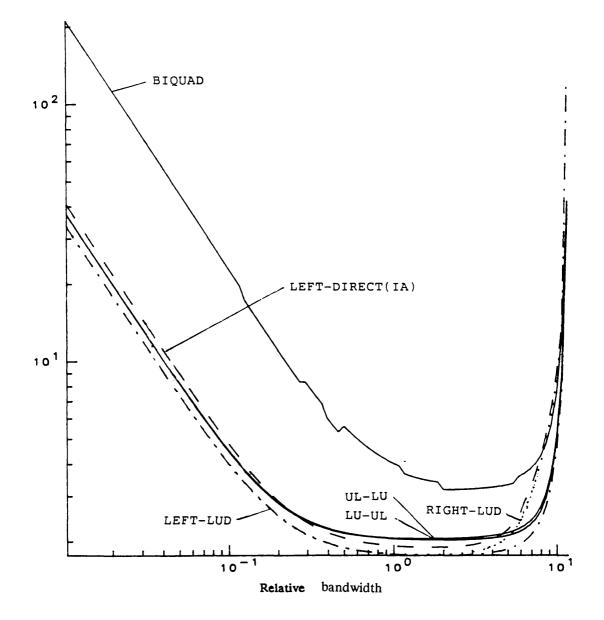

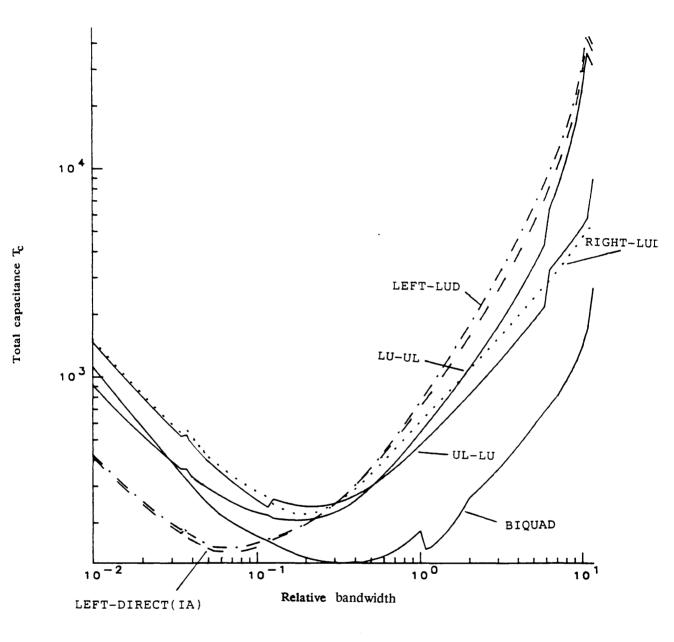

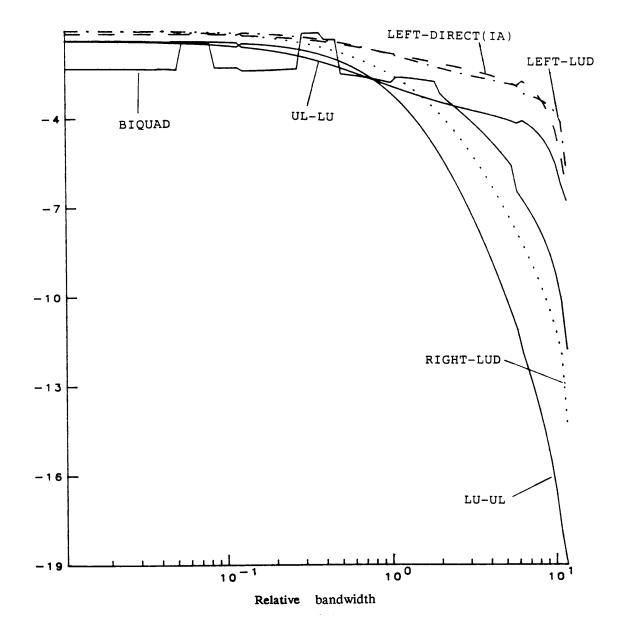

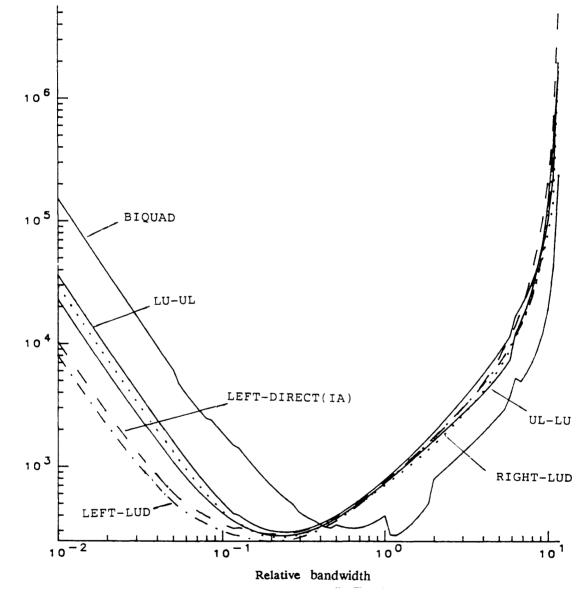

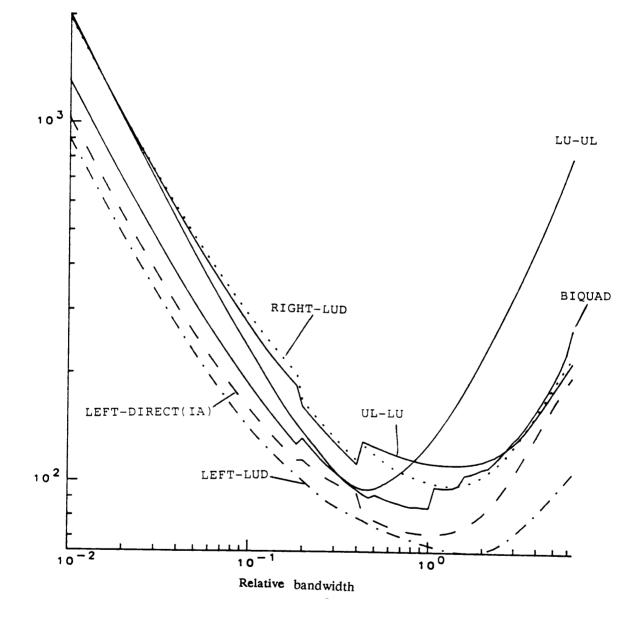

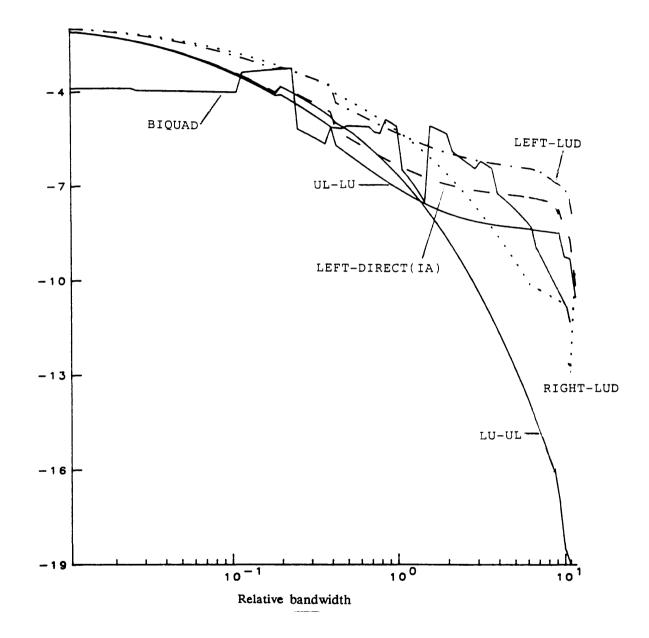

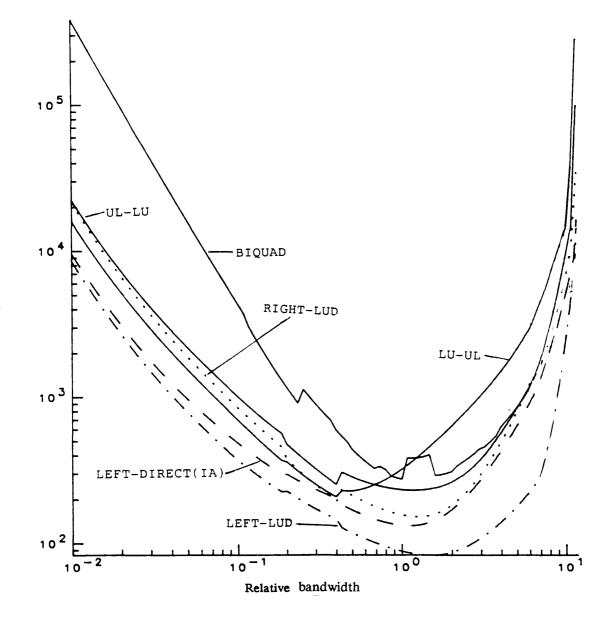

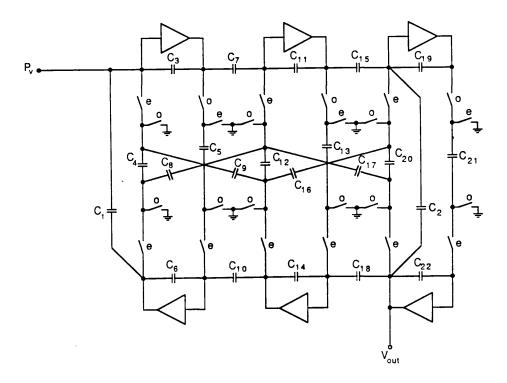

design in Chapter 4. The bilinear transformation is used to convert the prototype from the s-domain to the z-domain. For efficient simulation, a rearrangement is introduced to modify the system into a form realisable by LDI integrators [79]. These so-called bilinear-LDI structures were first discovered by Lee and Chang [51] for SC design by adopting negative elements in the prototype. In this thesis this principle is formalised in terms of matrix principles. The novel LUD approach to SC and digital filter design is discussed in detail. It is shown that negative elements can be placed in the prototypes to cancel the unecessary components in their simulations and to improve the parallelism for digital realisation, which is further enhanced by a new scaling technique. Some detailed comparisons of the new circuit structures with existing ones are given, demonstrating that some significant advantages such as low sensitivity and low capacitance spread, can be gained by employing the new design methods.

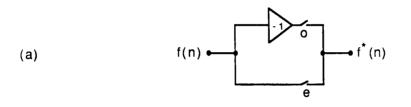

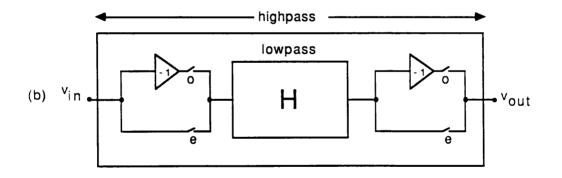

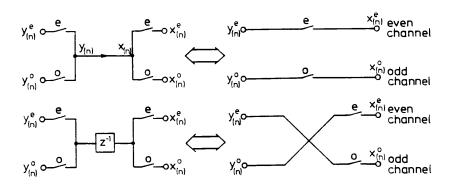

Chapter 5 concerns the design of non-lowpass filters by using frequency transformations. It is shown that circuits with different filtering types can be derived from a lowpass network by simply replacing the LDI integrators with some special operators. Towards the same objective, a novel second order building block is presented for strays-insensitive bandstop switched-capacitor (SC) ladder design. A two channel scheme obviates the need for term cancellation in realising bandstop type operators and is less demanding on opamp settling time. It is shown highpass SC filters can be obtained simply by adding a modulation stage to a corresponding lowpass filter.

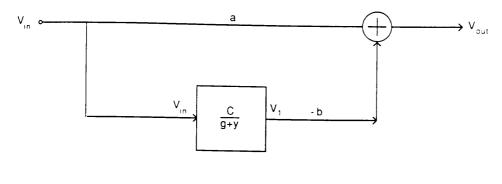

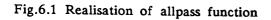

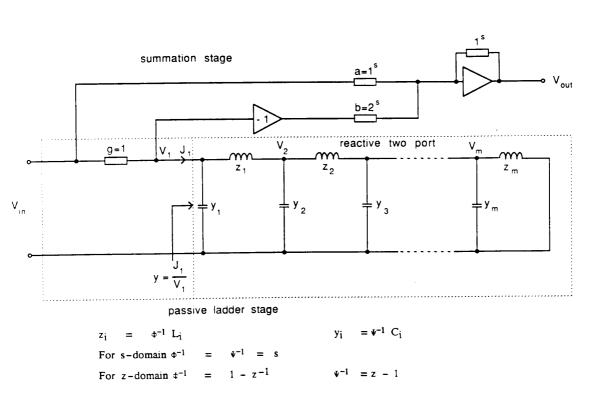

Chapter 6 deals with all-pass filter design for active RLC, active RC, SC and digital realisations. The matrix decomposition approach is readily applied to the ladder simulation part, in this case, a singly-terminated ladder is shown to have advantages. The resulting circuits have the attractive properties of parallel sturctures and very low amplitude sensitivity to component changes. Analogue implementations are canonical in opamp number and digital ones are canonical in multiplier number. Detailed examples are given for SC designs and these are critically assessed for capacitance spread and sensitivities.

Matrix methods are highly suitable for computer software development. They offer a concise form of circuit description which eases data storage and can then be manipulated systematically by well developed algorithms for filter derivation. A computer software package for advanced filter design, PANDDA is developed by the author in co-operation with R. K. Henderson. Its many distinguished features are outlined in Chapter 7 where some practical design examples are also given.

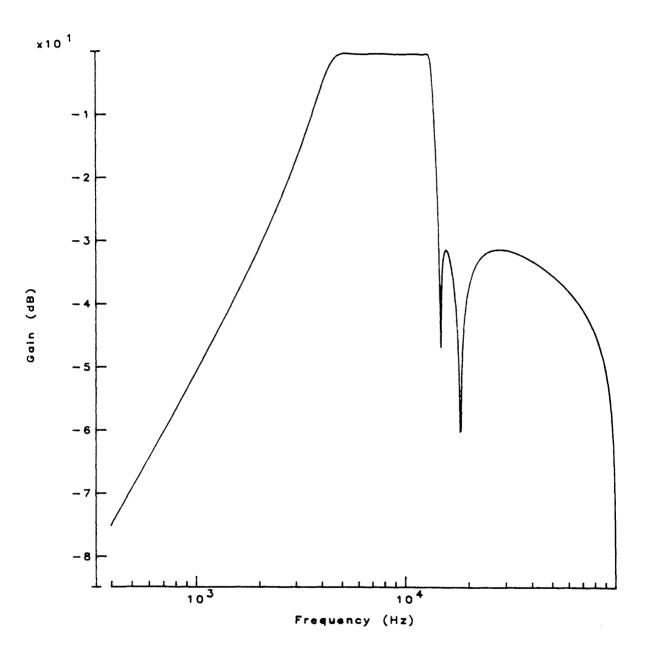

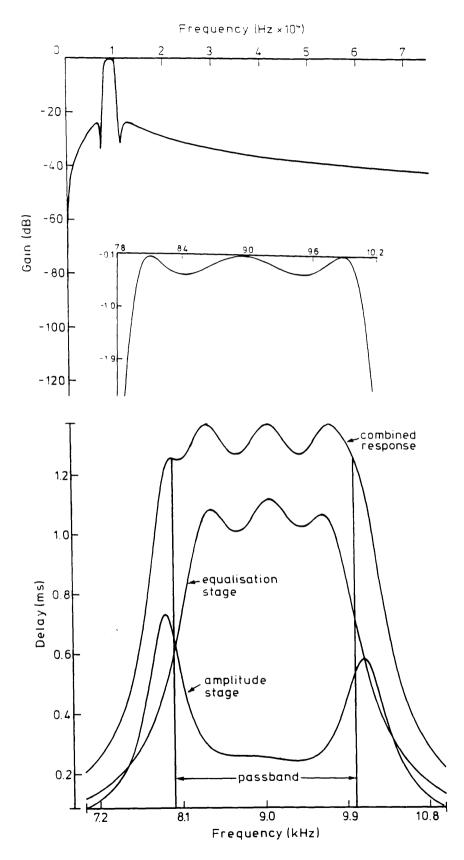

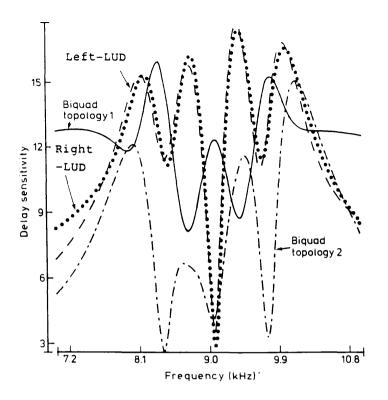

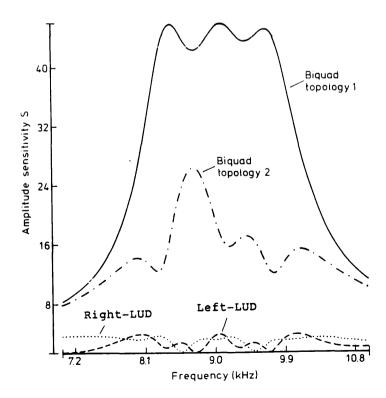

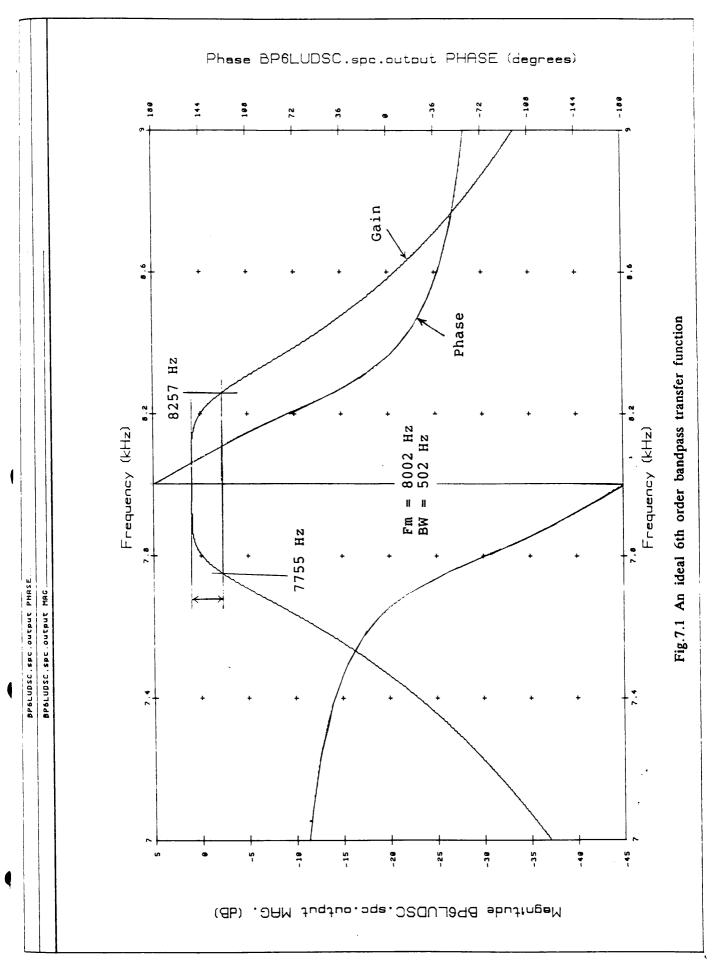

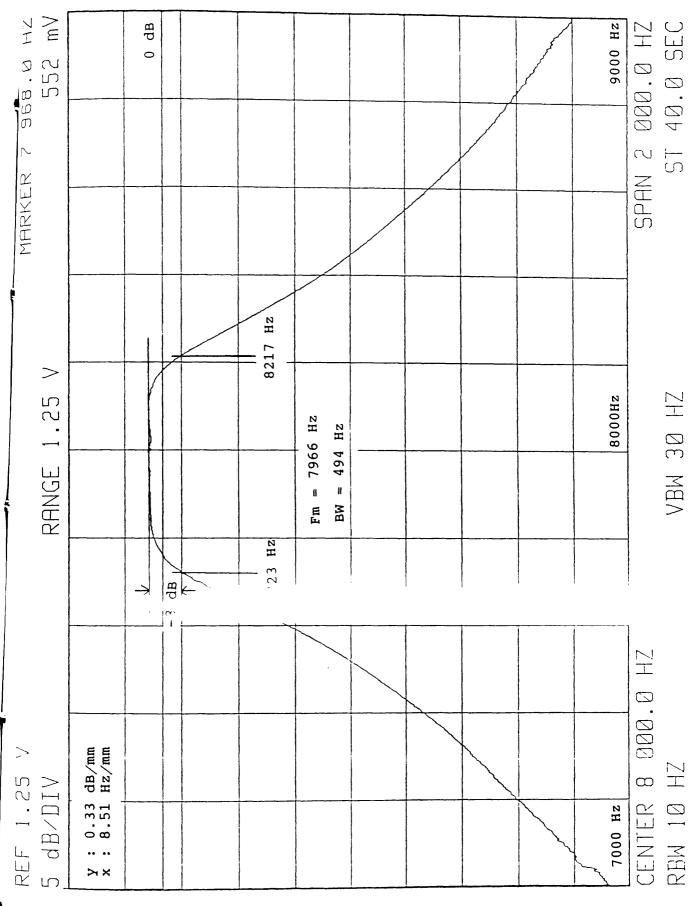

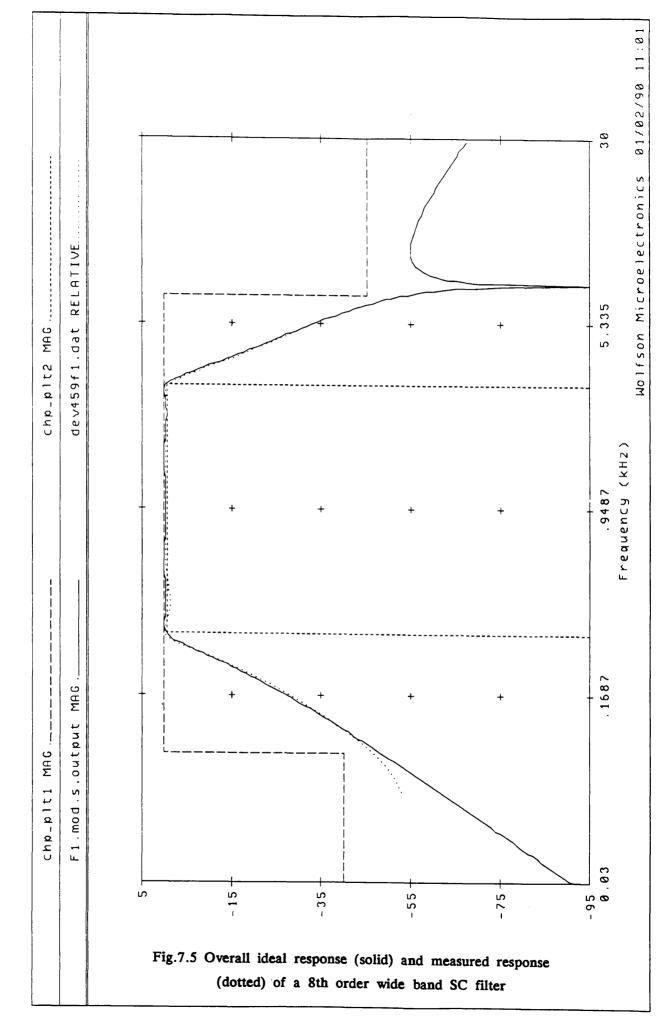

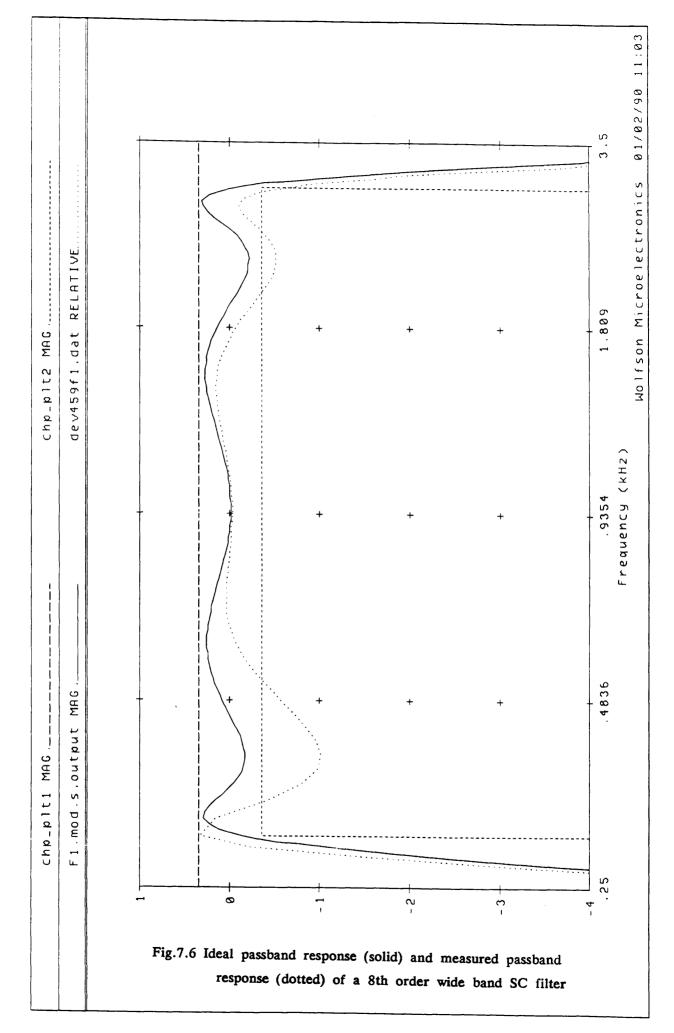

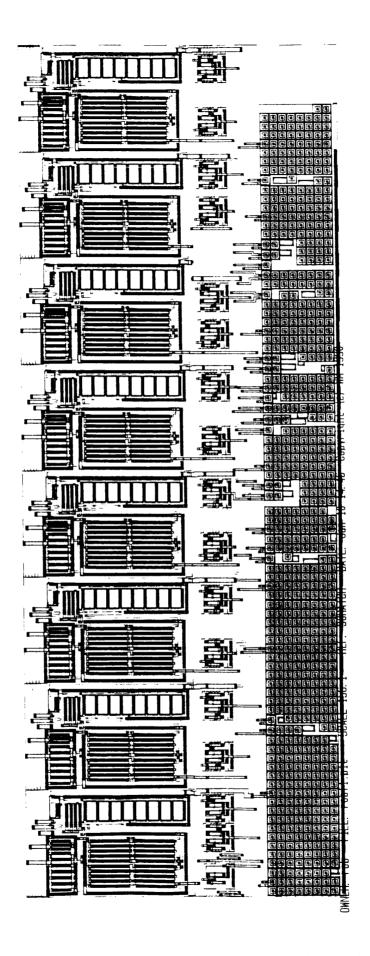

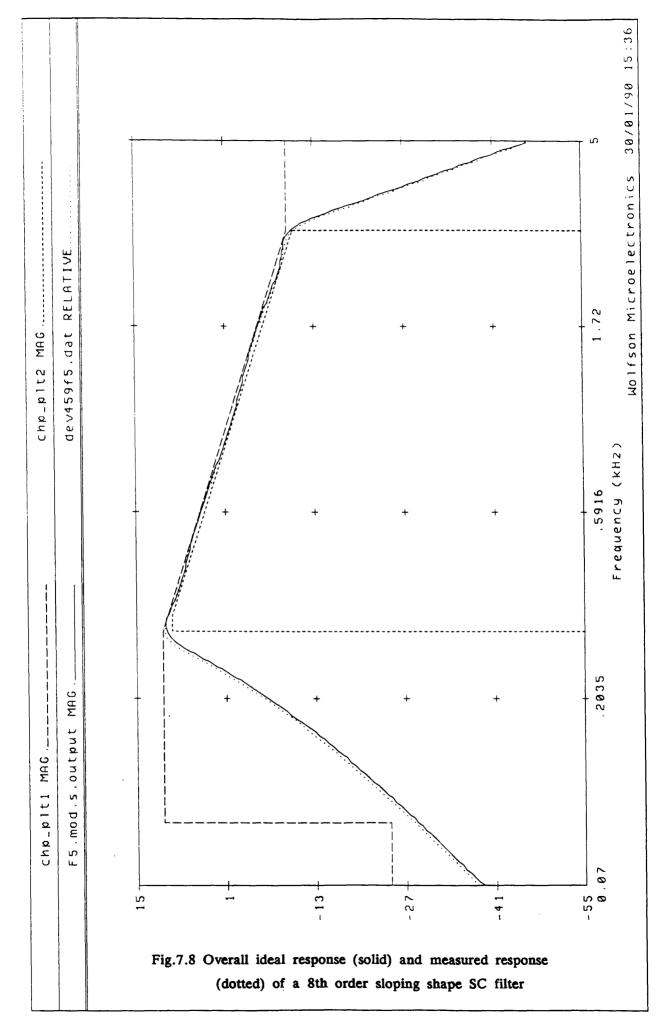

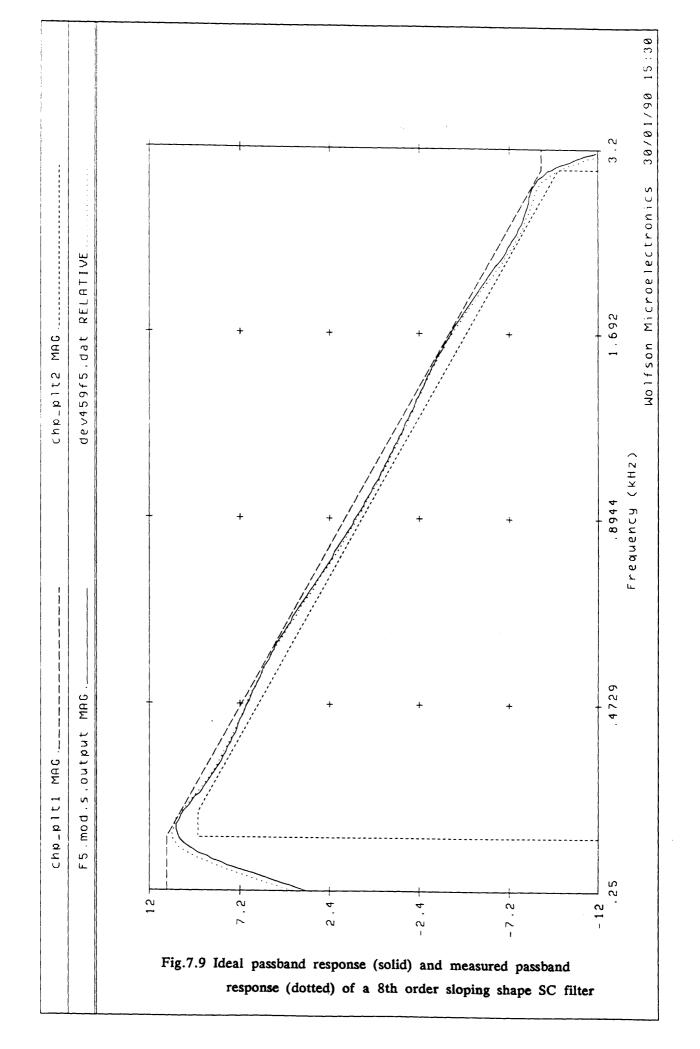

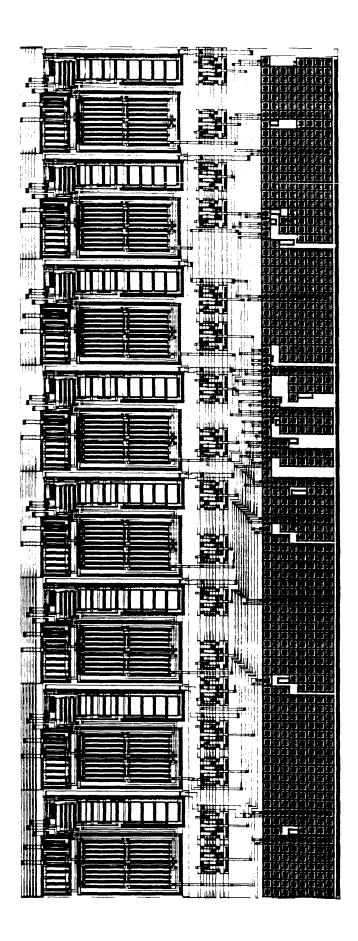

Measured response of SC fabrications by LUD and mixed LUD-biquad methods are illustrated.

Finally the main results obtained in this thesis will be summarised in Chapter 8. Some suggestions for further research in integrated filter design will also be given.

## **1.6 STATMENT OF ORIGINALITY**

The following most significant results of the research work presented in this thesis are, to the best of author's knowledge, original and, as indicated below, some of the results have been or will be published.

Chapter 2 — The theoretical investigation of symmetric matrix systems, proof of boundedness and pseudopassivity, are the subjects of the papers,

Li Ping and J.I. Sewell," On low sensitivity/noise digital filter design", Proc. IEEE 1989 International Conference on Accoustics, Speech and Signal Processing, pp.1063-1066, Glasgow, UK, May 1989.

Li Ping and J.I. Sewell, "High performance circuit structures and symmetric matrix systems", Proc. IEE, vol.136, Part-G, no.6, pp.327-336, Dec. 1989.

Chapter 3, 4 — The LUD structure was first proposed for switched capacitor filter design in,

Li Ping and J.I. Sewell, "The LUD approach to switched capacitor network design", IEEE Trans Circuits Syst., vol.CAS-34, no.12, pp.1611-1614, December 1987.

which is followed by further studies revealing a whole family of circuit derived from matrix principles, as discussed in

Li Ping, R.K. Henderson and J.I. Sewell, "Matrix methods for switched-capacitor filter design", Proc. IEEE ISCAS, pp.1021–1024, Espoo Finland, June 1988.

R.K. Henderson, Li Ping and J.I. Sewell, "A unified approach to the design of canonical integrated ladder filters", to be published in Proc. IEEE ISCAS, New

Orleans USA, May 1990.

The matrix methods have been extended into active- RC and digital circuits in

Li Ping and J.I.Sewell, "Filter realisation by passive circuit simulations," Proc. IEE, vol.135, Part-G, no.4, pp.167-176, August 1988.

Chapter 5 — The frequency transformation techniques for discrete domain filter design is covered in

Li Ping and J.I. Sewell, "Digital Filter Realisation by Passive Circuit Simulation", IEE Saraga Colloqium on Electronic Filters, Colloquium Digest, pp.8/1-8/8, May 1988.

A continuation of this research discovered the TWINTOR circuits for bandstop SC design, as described in

Li Ping, J.I. Sewell, "The TWINTOR in bandstop switched-capacitor ladder filter realisation", IEEE Trans. Circuits Syst., vol.CAS-36, no.7, pp.1041-1044, July 1987.

Chapter 6 — All- pass ladder structures are the subject of a recently completed paper,

Li Ping and J.I. Sewell, "Switched capacitor and active-RC allpass ladder filters", to be published in Proc. IEEE ISCAS, New Orleans USA, May 1990.

Chapter 7 — The author's contribution to PANDDA software package is mainly in the circuit realisation and analysis parts. The development of PANDDA has been progressively reported in the following papers,

R. K. Henderson, Li Ping and J.I.Sewell, "PANDDA : A program for advanced network design : digital and analogue", Digest of IEE Saraga Colloquium on Electronic Filters, pp.4/1-4/8, London 1988.

R. K. Henderson, Li Ping and J.I.Sewell, "A program for digital and analogue filter design: PANDDA", Proc. European Conference on Circuit Theory and Design, pp.289–293, Brighton, U.K., September 1989.

27

### **CHAPTER 2**

### SYMMETRIC MATRIX POLYNOMIAL SYSTEMS

### 2.1 INTRODUCTION

### 2.2 STABILITY CRITERIA

- 2.2.1) Critical stability

- 2.2.2) Absolute stability

### 2.3 CANONICAL SYSTEMS

- 2.3.1) System order

- 2.3.2) Condition for canonical ladder systems

### 2.4 BOUNDEDNESS

- 2.4.1) The concept

- 2.4.2) Boundedness in the continuous domain

2.4.3) Boundedness for a terminated reactance network

#### 2.5 SENSITIVITY FORMULAE

# 2.6 DISCRETE SYMMETRIC MATRIX POLYNOMIAL SYSTEMS

### 2.7 PSEUDOPASSIVITY AND LIMIT CYCLE SUPPRESSION

- 2.7.1) The concept

- 2.7.2) Psudopassivity for symmetric matrix polynomial systems

- 2.7.3) Wave variables

- 2.7.4) Continuous time domain pseudopassive systems

# 2.8 SUMMARY

#### 2.1 INTRODUCTION

#### Background

There are a number of attractive features about filter structures derived from passive RLC network simulations: they show very low sensitivity in the passband which is an important factor for active-RC and switched-capacitor (SC) filter fabrications [19-21,51-64]; they can be made limit cycle free for digital filter implementation, as shown for wave structures [76-83]; and they usually have better dynamic range compared with cascade biquads or other direct-form structures, which can be observed from many practical designs. Limit cycle supression and better dynamic range can improve the noise behaviour of the circuits.

Theories have been proposed to analyse and generalise the properties of passive ladders and their simulations [3,12,15]. A unified investigation has been proposed in [86,87] for digital circuits. It was shown that general low sensitivity filters can be constructed by properly connecting LBR (lossless-bounded-real) sections, which include adaptors for wave digital circuits as specific examples. In general, this approach is mainly concerned with the topological point of view.

The work of this chapter investigates the theoretical aspects of high quality network design based on matrix principles. A difference between the topological [19-21,51-64,76-87] and matrix approaches is that the former analyses the behaviour of local building-blocks while the latter examines the overall system. The two approaches complement each other to provide insight into the filter design problem.

### **Conventions**

Attention is given to the properties of the system descriptions of circuits of the following form,

| Y V - J                       | (2.1a) |

|-------------------------------|--------|

| $Y = s C + s^{-1} \Gamma + G$ | (2.1b) |

where all the matrices symmetric. This will be called a symmetric matrix polynomial system (SMPS). Output functions may be added in the form

29

$$y = D V + E J$$

(2.1c)

but only system (2.1a,b) will be considered since sensitivity and noise problems arise mainly from the feedback loops in (2.1a,b).

The most natural interpretation of system (2.1) is in the formulation of the network equations (nodal, loop, or hybrid) of passive RLC ladders [95,96]. In this case C,  $\Gamma$  and G represent the contributions of capacitors, inductors (inversed values) and conductors respectively and it can easily be shown that they are all non-negative definite, provided that nodal or loop formulations are used for the network with only positive-valued elements. The reverse procedure, from an equation with symmetric non-negative matrices to a network, is not always possible unless negative element values are allowed. Negative elements offer some advantages, such as to provide more regular structures which can be fabricated with greater ease [67]. Questions arise about the stability, sensitivity and noise problems associated with the introduction of negative elements. These will be answered by the theorems developed in this chapter.

In particular, the nodal description of a passive ladder is a tridiagonal SMPS and henceforth we will simply call a tridiagonal SMPS a ladder, as ladders are more familiar to most circuit designers and also as most SMPSs used in this thesis are derived from passive ladder prototypes.

# Relationship between SMPSs and other systems concepts

System (2.1) is also a generalised form of the standard state-space equation. Indeed, (2.1) reduces to a standard state-space system when  $\Gamma=0$ .

$$(sC + G) V = J$$

(2.2)

Alternatively (2.1) can always be rearranged into the form of (2.2) by introducing some intermediate variables. However, the advantage of using the system description of (2.1) is that optimal performance can be achieved by imposing some simple conditions (notably symmetry) on the matrices. Conversely, if the matrices in (2.2) are constrained to be symmetric then the system can only have real poles, which is too restrictive for most applications.

System (2.1) can be further used to produce prototypes for various simulations discussed in detail in succeeding chapters.

#### Aspects covered in this chapter

In the first part of this chapter, some elementary criteria for checking the stability of SMPSs will first be established.

Then the efficiency with which the SMPSs can be realised will be considered. A canonical system is defined to be one which realises a given order of transfer function with the smallest possible matrices. It is shown that the parity of the numerator of the transfer function will decide whether it has a canonical realisation. This knowledge is useful in succeeding chapters for obtaining integrated ladders with minimum implementation cost.

The more sophisticated concepts considered by many authors, boundedness and pseudopassivity, are crucial in predicting the sensitivity and limit cycle behaviour of filter systems. They are now proved to be closely related to the matrix symmetry and to be basic properties of SMPSs.

In active-RC or SC implementations of SMPSs, the component deviations may destroy the symmetry of the system description. From practical observations the sensitivities of active-RC and SC ladder simulations are nevertheless very good, this is attributed to their multi-feedback nature. Sensitivity formulae are presented for asymmetric deviations, clearly indicating that better performance can be assured by more complete symmetry.

#### 2.2 STABILITY CRITERIA

Besides synthesis methods, an optimisation procedure could also be used to adjust the entries of the matrices of (2.1) to make the transfer function fit the prescribed specifications. In this case conditions are required for testing the stability of the resulting system.

#### 2.2.1) Critical Stability

<u>Remark 2.1</u>: System (2.1) is critically stable if C,  $\Gamma$  and G are all symmetric non-negative.

<u>**Proof:**</u> Let {  $s_k = \sigma_k + j\omega_k$  } be the set of roots of detY(s) of (2.1),

det

$$(s_k^2 C + s_k G + \Gamma) = 0$$

(2.3)

So there is a non-zero vector X which satisfies [101] the equation

$$X^*$$

(  $s_k^2 C + s_k G + \Gamma$  )  $X = 0$  (2.4)

$(X^*$  denotes the transposed conjugate of X)

or

$$as_k^2 + bs_k + c = 0$$

(2.5)

with

$$a = X^{*}CX$$

$b = X^{*}GX$   $c = X^{*}\Gamma X$  (2.6)

As C, G, and  $\Gamma$  are all definite non-negative, a, b, and c are all non-negative numbers [101]. But in this case (2.5) has no roots with

$$\operatorname{Re}(\mathbf{s}_{k}) = \sigma_{k} > 0 \tag{2.7}$$

That is, system (2.1) has no poles in the right half plane if C,  $\Gamma$  and G are all symmetric non-negative.

#### 2.2.2) Absolute Stability

The absolute stability condition for system (2.1) is that  $\sigma_k < 0$  for all k. Therefore some extra constraints should be added to ensure that no roots lie on the imaginary axis. This can be checked by evaluating det  $|Y(j\omega)|$ . In most cases system (2.1) is designed to realise a transfer function H(s) which has no poles on the imaginary axis. If the system is properly designed without redundancy, so that the order of the system is equal to the order of H(s), or in other words if it is observable from the output, then it will have no poles on the imaginary axis, as in this case H(s) and the system have the same set of poles.

The non-negative property of the symmetric matrices C,  $\Gamma$  and G can be easily tested. For instance, decompose C into symmetric LU form [97-100],

$$C = L_c D_c L_c^T$$

(2.8)

where  $D_c$  is a diagonal matrix. C is non-negative if and only if all the entries

of  $D_c$  are non-negative. The computational requirement for this test is nearly equal to performing Gaussian elimination.

#### 2.3 CANONICAL SYSTEMS

The system order of (2.1) is defined as the number of the roots of det |Y(s)|. This should be clearly distinguished from the order of the matrices making up the system, although these two parameters are closely related to each other, since higher order systems obviously entail higher order matrix descriptions. As will be seen, the order, or more simply, the size of the matrices decides the size of the realisations by physical networks. For the sake of efficiency, it is usually desirable to design a given order system by matrices with order as small as possible and those systems with minimum size will be said to be canonical. The constraints for a transfer function to have a canonical realisation is explored in this section.

#### 2.3.1) System order

The system polynomial of (2.1) is defined by

$$\Delta(s) = |Y(s)| = |sC + s^{-1}\Gamma + G|$$

(2.9)

Using the Laplace expansion [100,101] repeatedly it can be shown

<u>Remark 2.2</u>: The determinant of  $\Delta(s)$  can be expanded as (let n be the size of the coefficient matrices)

$$\Delta(s) = |C|s^{n} + a_{n-1}s^{n-1} + \dots + a_{-(n-1)}s^{-(n-1)} + |\Gamma|s^{-n} \quad (2.10)$$

The system order is defined by the difference between the highest and lowest index of the power of s in  $\Delta(s)$ . Again by using the Laplace expansion repeatedly, it can be shown that the highest coefficient of s will be accompanied by the highest non-zero cofactor of C, which is determined by the rank of C. Therefore the upper bound of the power of s is the rank of C. Similarly, it can be proved that the upper bound of the power of  $s^{-1}$  is the rank of  $\Gamma$ . The upper bound of the number of roots of det |Y| is then given by rank(C)+rank( $\Gamma$ ). <u>Remark 2.3:</u> An upper bound of the order of the system, m, is given by  $m \leq r_C + r_{\Gamma} \leq 2n$  (2.11) where  $r_C$  and  $r_{\Gamma}$  are the ranks of C and  $\Gamma$  respectively.

#### 2.3.2) Condition for canonical ladder systems

From (2.11) the upper bound for a SMPS is 2n. However, if a SMPS is specially designed to realise an odd order function, then the upper bound will become 2n-1. Thus we have,

<u>Definition 2.1</u>: A SMPS with size n is said to be canonical if it realises an  $2n^{th}$  or  $2n-1^{th}$  order transfer function.

**Definition 2.2:** A doubly-terminated tri-diagonal SMPS, or simply a ladder, meets the following conditions

1) C,  $\Gamma$  and G are all tri-diagonal matrices. So Y is also tri-diagonal.

2) J has only one non-zero element, i.e.  $J = (J_1, 0, ..., 0)$ .

3) G has only two non-zero elements  $g_{11} = g_{in}$  and  $g_{nn} = g_L$ , so that in general

$y_{(i+1,i)} = sc_{(i+1,i)} - s^{-1}\gamma_{(i+1,i)}$ (2.12) 4) The output is the nodal voltage  $v_n$ .

There are some constraints for a transfer function to be realisable by a canonical doubly-terminated SMPS.

#### Theorem 2.1

i) The numerator of the transfer function  $v_n/J_1$  of a canonical even order doubly-terminated ladder is an odd polynomial.

ii) The numerator of the transfer function  $v_n/J_1$  of an odd order doubly-terminated ladder is an odd polynomial if |C| is non-singular or an even polynomial if  $|\Gamma|$  is non-singular.

#### Proof:

From Definition 2.2 a doubly-terminated ladder has the following expanded form

(2.13)

From these properties and Cramer's rule it can be found for the output  $v_n$  [101]

$$\frac{v_n}{J_1} = \frac{\pm \Delta_{1n}}{\Delta(s)}$$

(2.14)

where  $\Delta(s)$  is the determinant of Y and  $\Delta_{1n}$  stands for the determinant of the submatrix of Y by deleting its first row and nth column, which can be seen as the lower-left n-1-th block of Y in (2.13). It can be shown that

$$\frac{n-1}{\pi [sc_{i+1,i} - s^{-1}\gamma_{i+1,i}]} \\

\frac{v_n}{J_1} = \frac{1}{\Delta(s)}$$

(2.15a)

where  $\Gamma=\{\gamma_{i,\,j}\}$  and  $C=\{c_{i,\,j}\}.$  Let  $v_n/J_1$  be expressed in the form of a rational function

$$\frac{v_n}{J_1} = \frac{N(s)}{D(s)}$$

(2.15b)

D(s) and N(s) are denominator and numerators respectively and they are pure

polynomials which means they contain only non-negative powers of s. Consider first the case of an even canonical realisation. From Remark 2.2,  $\Gamma$  must be nonsingular to be canonical and so

$$D(s) = s^n \Delta(s) \tag{2.16a}$$

$$N(s) = s^{n} \pi [sc_{i+1,i} - s^{-1}\gamma_{i+1,i}]$$

(2.16b)

i=1

Here  $c_{i+1,i}$  and  $\gamma_{i+1,i}$  (for all i) cannot both be zero otherwise the transfer function is zero. Suppose  $c_{i+1,i}$  are nonzero for all i then it is seen that N(s) is a 2n-1<sup>th</sup> polynomial with only odd terms. If any  $c_{i+1,i}$  is zero then N(s) will reduce to a 2n-3<sup>th</sup> polynomial (since in this case  $\gamma_{i+1,1}$  must be non-zero) and N(s) will stay odd. It is easy to deduce that N(s) will remain odd for cases of more zero { $c_{i+1,i}$ }. The same reasoning can be applied to the cases that some { $\gamma_{i,i+1}$ } are zero.

Now consider the case of odd order design, where either C or  $\Gamma$  must be singular to make  $\Delta(s)$ , (2.9), odd. If  $\Gamma$  is nonsingular exactly the same reasoning as for even case can used to show that N(s) must be odd. If C is nonsingular then

$$D(s) = s^{n-1} \Delta(s)$$

(2.17a)

$$n-1$$

$$N(s) = s^{n-1} \pi [sc_{i+1,i} - s^{-1}\gamma_{i+1,i}] \qquad (2.17b)$$

$$i=1$$

and it is easily shown that N(s) must be even polynomial.

Theorem 2.1 establishes some necessary conditions for a transfer function to have a canonical realisation. In the authors' experience the conditions are also sufficient for realisability provided that the transfer function is stable.

It is seen from Theorem 2.1 that the constraint on the parity of the numerator is related to the singularity of the matrices C and  $\Gamma$ . The singularities, however, cannot be arbitrarily chosen according to the following theorem.

<u>Theorem 2.2:</u> A doubly terminated ladder has a non-zero response at  $\omega = \infty$  only if C is singular and has a non-zero response at  $\omega = 0$  only if  $\Gamma$  is singular.

<u>Proof:</u> Let  $s = j\omega$ . From (2.10) it can be seen that when  $\omega \rightarrow \infty$   $\Delta(s) \rightarrow |C|s^n + a_{n-1}s^{n-1}$  (2.18) and from (2.15) the numerator is at most to the power of  $s^{n-1}$ . Therefore if |C| is not zero then (2.15) must be zero. Similar reasoning can be used at  $\omega \rightarrow 0$ .

It is mandatory that lowpass transfer functions have non-zero values at  $\omega = 0$ and for highpass and bandstop at  $\omega = \infty$ . This indicates that the singularity of the matrices is pre-determined by the filtering types and therefore the parity of the numerators of odd order cases is also constrained.

Since the singularities of C and  $\Gamma$  mean that their rank can at most be n-1, according to (2.11) a list of the upper bounds for various filtering types by a ladder with size n is obtained in Table 2.1

| CLASSES  | CONSTRAINT                             | UPPER BOUND OF SYSTEM ORDER |

|----------|----------------------------------------|-----------------------------|

| lowpass  | H(0)≠0 Γsingular                       | 2n-1                        |

| bandpass |                                        | 2n                          |

| highpass | H(∞)≢0 C singular                      | 2n-1                        |

| bandstop | H(0)≢0 H(∞)≢0<br>both C and Γ singular | 2n-2                        |

# Table 2.1 Upper bounds for various filtering types by a doubly-terminated ladder with size n

It is easily seen that canonical designs can be achieved only by bandpass, odd order lowpass and odd order highpass. For other cases, constraints given in Theorem 2.2 make it impossible for a canonical realisation. In the succeeding chapters it will be seen that a non-canonical ladder prototype will lead to an unnecessarily large size integrated circuit simulation, unless some complicated procedure is adopted. It will also be shown that the wrong parity of numerator can be easily corrected and a simple technique is introduced to eliminate the error caused by this modification. This results in a unified procedure, with very regular structures, to realise a wide family of transfer functions.

#### 2.4 BOUNDEDNESS

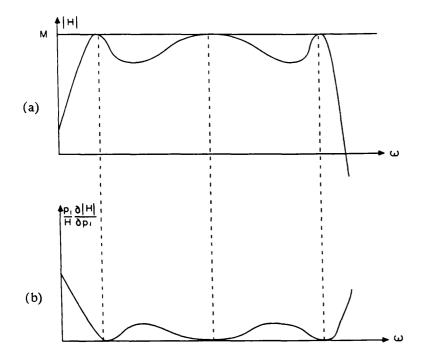

#### 2.4.1) The concept

The concept of boundedness can be traced back to an observation by Orchard about the low sensitivity properties of doubly-terminated ladders [15].

**Definition 2.3:** Boundedness The transfer function, H(P), of a system is said to be bounded with respect to the change of a set of parameters,  $P = \{ p_i \}$ , if there is a positive number M and

$$|H(P)| \leq M \tag{2.19}$$

is always satisfied when P varies within the allowed range.

When a bounded system is properly designed to make |H(P)| attain M at a frequency point in the passband,  $j\omega_m$ , then the deviation of P can only cause |H(P)| to decrease. This means that |H(P)| must have zero derivative with respect to any parameter  $p_i$  at  $j\omega_m$ , and consequently the sensitivity is also zero, i.e.,

$$p_{i} = \frac{\partial |H(P)|}{\partial p_{i}} = 0 \text{ at } s = j\omega_{m}$$

$$(2.20)$$

$$p_{i} = |H(P)| = \partial p_{i}$$

and it may be reasonably expected that over the whole passband the sensitivity will remain small, a reassuring argument used by many other authors for ladders as well as various simulation methods [3,12,73].

Fig.2.1 Illustration of boundedness and low-sensitivity

- (a) Transfer function of a bounded system

- (b) Sensitivity

### 2.4.2) Boundedness in the continuous domain

From network topology it is known that the output power of a doubly terminated ladder is bounded by maximum input power, a reasonable fact since a passive ladder cannot create power within itself. This result can also applied to the system (2.1) in a more abstract sense. Let (2.1) be evaluated on the imaginary axis,  $s = j\omega$ , and denote

$$\mathbf{Q} = \boldsymbol{\omega}\mathbf{C} - \boldsymbol{\omega}^{-1} \boldsymbol{\Gamma} \tag{2.21}$$

The system can be written as,

$$Y V = (jQ + G) V = J$$

(2.22)

Suppose matrix G in (2.22) can be separated according to input and output parts respectively

$$G = G_{in} + G_{out}. \qquad (2.23)$$

Then (2.22) can be written as

$$j Q V + G_{out}V + G_{in}V = J$$

(2.24)

We first prove a general relation.

<u>Theorem 2.3:</u> Assume that in (2.1), (i)  $G_{in} X = J$  has at least one solution. (ii) all matrices are symmetric non-negative definite. Then the following inequality holds,

$$V^* G_{out} V \leqslant \frac{1}{\sqrt{2.25}}$$

where  $R_{in}$  is the Moore-Penrose inverse of  $G_{in}$ .

Proof: According to Moore-Penrose's theories [115,116], Rin is defined by

$$G_{in}R_{in}G_{in} = G_{in} \qquad R_{in}G_{in}R_{in} = R_{in}$$

$$(G_{in}R_{in})^{T} = G_{in}R_{in} \qquad (R_{in}G_{in})^{T} = R_{in}G_{in}$$

$$(2.26)$$

and  $X_s = R_{in}J$  is a solution of  $G_{in}X = J$ , if it has a solution at all, which means

$$G_{in} R_{in} J = J$$

(2.27)

Now multiply (2.24) by  $V^*$ ,

$$j V^* Q V + V^* G_{out} V + V^* G_{in} V = V^* J$$

(2.28)

Take the real part of (2.28)

$$V^*G_{out}V = Re\{V^*J\} - V^*G_{in}V$$

(2.29)

Notice from (2.26) and (2.27)

$$[J^{*}R_{in}J - (J^{*} - 2V^{*} G_{in})R_{in}(J - 2G_{in}V)]/4$$

=

$$[2 J^{*}R_{in}G_{in}V - 2V^{*} G_{in}R_{in}J - 4V^{*} G_{in}R_{in}G_{in}V]/4$$

=

$$Re\{V^{*}J\} - V^{*}G_{in}V$$

(2.30)

From (2.29) and (2.30)

$$V^{*}G_{out}V = [J^{*}R_{in}J - (J^{*} - 2V^{*}G_{in})R_{in}(J - 2G_{in}V)]/4 \quad (2.31)$$

If  $G_{in}$  is non-negative then from (2,26)  $R_{in}$  is also non-negative which means that  $(J^*-2Y^*G_{in})R_{in}(J-2G_{in}V)$  is a non-negative number. Theorem 2.3 follows from (2.31) immediately.

### 2.4.3) Boundedness for Terminated Reactance Network

Equation (2.25) is a general expression which can be applied to multi-input/output systems. To provide some insight of its physical interpretation, consider the special case of a single input/output system. Suppose (2.1) has only one input  $J = [J_1, 0, ..., 0]$  and one output  $v_n$ .  $G_{in}$  and  $G_{out}$  have only one non-zero diagonal entry, respectively, corresponding to the input and output, i.e.,

$$G_{in} = diag(g_{11}, 0, 0, ..., 0)$$

(2.32a)

$$G_{out} = diag(0,0,...0,g_{nn})$$

(2.32b)

Then R<sub>in</sub> can be generated by

$R_{in} = diag(g_{11}^{-1}, 0, 0, \dots 0, )$  (2.33)

Therefore in this case (2.31) reduces to

Therefore in this case (2.31) reduces to

$$g_{nn}|v_n|^2 = [1 - |1 - 2g_{11}v_1/J_1|^2] \frac{1}{4g_{11}} |J_1|^2$$

(2.34)

so

$$|\mathbf{g}_{nn}|\mathbf{v}_{n}|^{2} \leq \frac{1}{4|\mathbf{g}_{11}|} |\mathbf{J}_{1}|^{2}$$

(2.35)

or

$$|v_n| \leq \frac{1}{2(g_{11}g_{nn})^{1/2}} |J_1|$$

(2.36)

A typical example of the system constrained by the conditions of (2.32) is a doubly-terminated ladder, in which case (2.1) are its nodal equations with input and output nodes labelled 1 and n respectively. The physical interpretation of (32) can be seen by rewriting it as

$$g_{nn}|v_{n}|^{2} = [1 - |\rho|^{2}] g_{11}^{-1}|J_{1}|^{2}/4$$

(2.37)

with  $\rho$  defined by

$$\rho = 1 - 2g_{11}v_1/J_1 \tag{2.38}$$

Consider a passive ladder with the source resistor being  $r_{11} = g_{11}^{-1}$  and input impedance of the 2-port ladder including the load is  $z_{in} = y_{in}^{-1}$ .

$$\rho = 1 - 2g_{11}v_1/J_1 = 1 - \frac{2g_{11}}{y_{in}+g_{11}}$$

$$= \frac{y_{in}-g_{11}}{y_{in}+g_{11}} = \frac{r_{11}-z_{in}}{r_{11}+z_{in}}$$

(2.39)

So  $\rho$  is just the reflection function and the upper bound of  $|v_n|$  is attained at  $\rho=0$ . This result is well known in network theory.

In the proof of boundeness, no conditions have been imposed on C and  $\Gamma$  except that they must be symmetric and non-negative. Accordingly, zero-sensitivity with respect to symmetric deviation can be achieved at the frequency points where the transfer function attains its upper bound.

#### 2.5 SENSITIVITY FORMULAE

The above result provides only an estimate of sensitivity for symmetric deviations. More general sensitivity formulae are now derived. To simplify the problem, only single input/output system will be considered.

#### A useful equation

An equation is now derived as the preliminary to the main discussion. Suppose a single input/output system meets the conditions of Theorem 2.3 and (2.32). Let system (2.1a) be excited by another arbitrary input J' instead of J and let the response be U. The system can be written as

$$\mathbf{Y} \mathbf{V}' = \mathbf{J}' \tag{2.40}$$

Left multiplying by V\* gives

$$V^* Y V' = V^* J'$$

(2.41)

Note that when J is a real vector, (- indicates conjugate)

$$(\mathbf{V}^*\mathbf{Y})^{\mathrm{T}} = \mathbf{Y} \ \mathbf{\bar{V}} = (\mathbf{j}\mathbf{Q} + \mathbf{G})\mathbf{\bar{V}}$$

=  $-(-\mathbf{j}\mathbf{Q} + \mathbf{G})\mathbf{\bar{V}} + 2\mathbf{G}\mathbf{\bar{V}}$

=  $2\mathbf{G}\mathbf{\bar{V}} - \mathbf{J}$

=  $(2g_{11}\mathbf{\bar{v}}_{1} - \mathbf{J}_{1}, 0 \dots 0, 2g_{nn}\mathbf{\bar{v}}_{n})^{\mathrm{T}}$

=  $(\overline{\rho}\mathbf{J}_{1}, 0 \dots 0, 2g_{nn}\mathbf{\bar{v}}_{n})^{\mathrm{T}}$  (2.42)

Substitute (2.42) into (2.41) and make some rearrangement to get

$$2g_{nn}v_{n}v_{n}' - \rho J_{1}v_{1}' + V^{*}J' = 0 \qquad (2.43)$$

Again left multiplying (2.40) by  $V^{T}$  and noticing that  $V^{T}Y = J^{T} = [J_{1}, 0, ...0]$ we have

$$V^{T} J' = V^{T} Y V' = J^{T} V' = J_{1} v_{1}'$$

(2.44)

Finally substituting (2.44) into (2.43) leads to the following equation linking the output of the new system with the old system and the input,

$$v_n = (2g_{nn}v_n)^{-1}(\rho V^T - V^*)J'$$

(2.45)

### Sensitivity Formulae

Differentiate (2.11) w.r.t. some network element  $\xi$  to get

-

$$\mathbf{Y} \, \mathrm{d}\mathbf{V}/\mathrm{d}\boldsymbol{\xi} + \mathrm{d}\mathbf{Y}/\mathrm{d}\boldsymbol{\xi} \quad \mathbf{V} = 0 \tag{2.46}$$

.

Here the second term can be viewed as the new input vector for (2.45) and we have

#### Theorem 2.4:

$$dv_n/d\xi = (2g_{nn}v_n)^{-1}(-\rho V^t + V^*) dY/d\xi V \qquad (2.47a)$$

and

$$d|v_{n}|/d\xi = Re[v_{n}dv_{n}/d\xi]/|v_{n}| = (2g_{nn}|v_{n}|)^{-1}Re[(-\rho V^{t} + V^{*})dY/d\xi V]$$

(2.47b)

In particular, if the deviation of  $\xi$  only perturbs the imaginary part of Y, jX say, and  $dY/d\xi = jdX/d\xi$  is symmetric then

$$\begin{aligned} d|v_{n}|/d\xi &= (2g_{nn}|v_{n}|)^{-1} \operatorname{Re}[-j\overline{\rho} \ V^{T}dX/d\xi \ V + j|V^{*}dX/d\xi \ V|] \\ &= (2g_{nn}|v_{n}|)^{-1} \operatorname{Re}[-j\overline{\rho} \ V^{T} \ dX/d\xi \ V] \\ &= -(2g_{nn}|v_{n}|)^{-1} \operatorname{Im}[\rho \ V^{T} \ dX/d\xi \ V] \end{aligned}$$

$$(2.48)$$

So  $d|v_n|/d\xi = 0$  when  $\rho = 0$ . This again confirms the conclusion for single input/output system, that  $|v_n|$  attains its upper bound and has zero-sensitivity at  $\rho = 0$ , if the deviation is symmetric.

#### Application to Passive Networks

When system (2.1) is implemented by a real passive RLC network,  $\xi \in \{R_i, L_i, C_i\}$  and  $dY/d\xi$  is always symmetric. Then a very simple alternative to the topological derivation of sensitivity follows. Let the contribution to Y of a branch admittance  $jq_k$  between nodes a,b be  $jq_kM_{ab}$  where

$$\mathbf{M}_{ab} = \begin{bmatrix} 0 & \vdots & \vdots & 0 \\ \dots & 1 & -1 & \dots \\ \dots & -1 & 1 & \dots \\ 0 & \vdots & \vdots & 0 \\ & & & \mathbf{a} & \mathbf{b} \end{bmatrix} \mathbf{a}$$

(2.49)

So

$$dY/dq_k = j M_{ab}$$

(2.50)

It is easily seen that

$$V^{T} M_{ab} V - v_{k}^{2}$$

and  $V^{*} M_{ab} V - |v_{k}|^{2}$  (2.51)

where  $v_k$  is the voltage across  $jq_k$ . Then (2.47) reduces to

$$dv_n/dq_k = (2g_{nn}|v_n|)^{-1}(-j\rho v_k^2 + |v_k|^2)$$

(2.52a)

and

$$d|v_n|/dq_k = (2g_{nn}|v_n|)^{-1} \text{ Im } [\rho v_k^2]$$

(2.52b)

(2.52b) is zero at the frequency points where  $\rho = 0$  or equivalently  $|v_n|$  attains maximum bound. This is just the well known zero-sensitivity property for doubly-terminated ladders.

#### Application to Digital and Active Networks

In the following chapters it will be shown that system (2.1) can be simulated by digital or active networks. For digital simulations, even in non-ideal cases, it is still possible to keep deviations in Y symmetric by carefully selecting the coefficient quantisations, so the zero-sensitivity property can be preserved. For active-RC and SC simulations, it is difficult to keep deviations of Y symmetric, since the element value drift is a random phenomenon. The component drift may cause the equivalent system description (2.1) to become non-symmetric so that the output may exceed the bound given by (2.25) or (2.36). However in practical active-RC or SC implementations, low sensitivity is still observed, a property due to the multi-feedback nature of the structures. (2.47) are valid for these general cases.

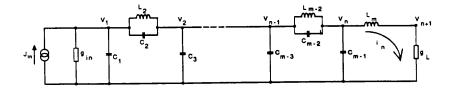

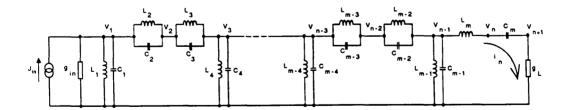

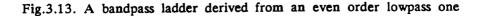

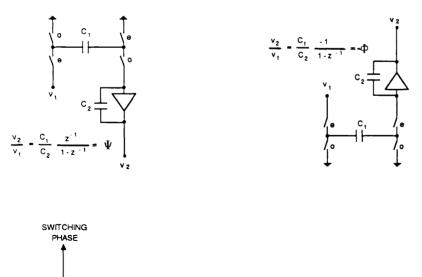

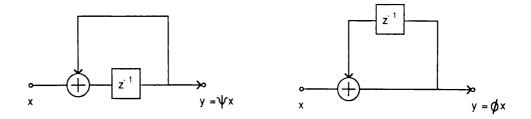

### 2.6 DISCRETE SYMMETRIC MATRIX POLYNOMIAL SYSTEMS