# Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

1-14-2020 2:00 PM

# DC-DC and AC-DC Converters Based on Three-Phase DC-DC Topologies

Adel Ali Abosnina, The University of Western Ontario

Supervisor: Moschopoulos, Gerry, *The University of Western Ontario* A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering © Adel Ali Abosnina 2020

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Abosnina, Adel Ali, "DC-DC and AC-DC Converters Based on Three-Phase DC-DC Topologies" (2020). *Electronic Thesis and Dissertation Repository*. 6791. https://ir.lib.uwo.ca/etd/6791

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

#### Abstract

Power electronics is the field of electrical engineering that uses power semiconductor devices along with passive elements such as inductors, capacitor and transistors to convert electrical power that can be generated by a source to a form that is suitable for user loads. The main focus of this thesis is on the development of new DC-DC and AC-DC topologies that are based on three-phase DC-DC converters. Three-phase DC-DC converters take an input DC voltage, convert it into a high-frequency AC voltage that is then stepped up or down, then rectify and filter this voltage to produce an output DC voltage. They are implemented with a high-frequency three-phase transformer in their topology rather than a single-phase transformer. These converters are very attractive over other topologies that have a single-phase transformer in their topologies for several reasons. First, just one three-phase DC-DC converter can be used instead of using three DC-DC converters in parallel for particular applications; this advantage is especially attractive for higher power applications. In addition, by using three-phase DC-DC converters, the ripple of the source current is significantly reduced and that means less filtering is needed. Moreover, the components of the converter will have less current stress because current is split among three-phases.

In this thesis, new DC-DC and AC-DC converters that are based on three-phase DC-DC topology are proposed. The proposed converters use fewer active switches than other previously proposed converters of similar type, thus resulting in lower cost and simpler operation. For each of the proposed converters, its steady-state characteristics are determined by mathematical analysis and procedure for the design of key converter components is developed. The feasibility of each proposed converter has been confirmed with results that have been obtained from experimental prototypes. For one of the proposed converters, a comparison between the operation of one of the proposed converters operating with traditional silicon devices (Si) and that with the converter operating with new silicon-carbide devices (SiC) was made to examine its performance with both types of devices.

**Keywords**: DC-DC power conversion, renewable energy systems, AC-DC conversion, ZVS, single-stage converters

#### Summary for Lay Audience

Power electronics has a significant impact in a wide spectrum of electrical applications, from personal electrical devices such as cellphones and laptops to large industrial applications such as renewable energy and automotive applications. In general, power electronics is the field of electrical engineering that uses power semiconductor devices along with passive elements such as inductors, capacitor and transistors to convert electrical power that can be generated by a source to a form that is suitable for user loads. The input source can be utility voltage, a battery, solar panels, fuel cells, electric generators, etc. The load can be a motor, telecommunications equipment, medical equipment, a battery, etc. There are four basic types of power converters: -AC-DC, DC-DC, DC-AC and AC-AC- depending on whether the source is AC or DC and whether the load is AC or DC.

The main focus of this thesis is on the development of new DC-DC and AC-DC topologies that are based on three-phase DC-DC converters. These converters are very attractive over other topologies that have a single-phase transformer in their topologies for several reasons because the converter components have less stress, their input and output currents can be closer to being ideally DC, and they are less expensive to implement than three separate DC-DC converters. In this thesis, new DC-DC and AC-DC converters that are based on three-phase DC-DC topology are proposed. For each of the proposed converters, its steady-state characteristics are determined by mathematical analysis and procedure for the design of key converter components is developed. The feasibility of each proposed converter has been confirmed with results that have been obtained from experimental prototypes.

# Acknowledgments

All the praises, and foremost thanks are due to Allah for being my refuge and strength's source in time of ease and hardship. Without His guidance and blessings, nothing is possible.

I would like to express my sincere gratitude to my supervisor, Dr. Gerry Moschopoulos, for his invaluable supervision, and encouragement throughout my Ph.D. studies. I am also thankful to the members of my examination committee.

I would also like to acknowledge financial support from the Ministry of Education of Libya for this work.

I would like to express my deepest gratitude to my parents and my wife for their constant encouragement and support to continue my higher education and finish this research. I also like to express thanks to my brothers and sisters for their best wishes.

# Table of Contents

| Abstractii                                               |  |  |  |

|----------------------------------------------------------|--|--|--|

| Summary for Lay Audienceiii                              |  |  |  |

| Acknowledgmentsiv                                        |  |  |  |

| Table of Contents                                        |  |  |  |

| List of Tablesix                                         |  |  |  |

| List of Figures x                                        |  |  |  |

| Acronyms xv                                              |  |  |  |

| Abbreviations xvi                                        |  |  |  |

| Chapter 11                                               |  |  |  |

| 1 Introduction                                           |  |  |  |

| 1.1 Introduction                                         |  |  |  |

| 1.2 Fundamental Concepts                                 |  |  |  |

| 1.2.1 DC-DC Boost Converters                             |  |  |  |

| 1.2.2 Switching Losses                                   |  |  |  |

| 1.2.3 Isolated Single-Phase DC-DC Full-Bridge Converters |  |  |  |

| 1.3.1 Three-phase DC-DC voltage-fed converters           |  |  |  |

| 1.3.2 Three-Phase DC-DC Current-Fed Converters           |  |  |  |

| 1.3.3 AC-DC Converters                                   |  |  |  |

| 1.3.4. High Gain DC-DC Converter                         |  |  |  |

| 1.1 Thesis Objectives                                    |  |  |  |

| 1.5 Thesis Outline                                       |  |  |  |

| Chapter 2                                                |  |  |  |

| 2              | AN                                                             | A Novel Three-Phase DC/DC PWM Isolated Boost Converter |                                                                                                |    |

|----------------|----------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------|----|

|                | 2.1                                                            | Conve                                                  | rter Operation and Analysis                                                                    | 24 |

|                | 2.2 Duty Cycle Range                                           |                                                        |                                                                                                |    |

|                | 2.3 Converter Features                                         |                                                        |                                                                                                |    |

|                | 2.4                                                            | Design                                                 | Procedure and Example for the Power Stage of the Proposed Converter                            | 37 |

|                |                                                                | 2.4.1                                                  | Maximum input current                                                                          | 38 |

|                |                                                                | 2.4.2                                                  | Input-output voltage gain                                                                      | 38 |

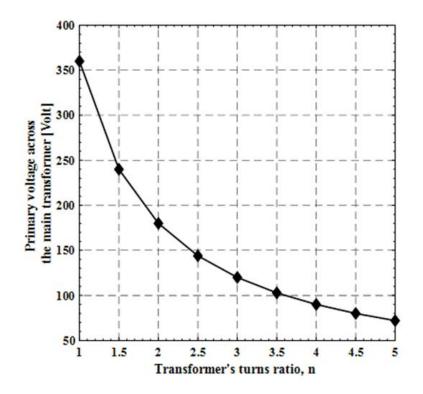

|                |                                                                | 2.4.3                                                  | Duty cycle and main transformer turns ratio                                                    | 39 |

|                |                                                                | 2.4.4                                                  | Determine the value of input boost inductor                                                    | 41 |

|                |                                                                | 2.4.5                                                  | Determine the value of output capacitor                                                        | 41 |

|                |                                                                | 2.4.6                                                  | Current stress in the main switches                                                            | 41 |

|                | 2.5                                                            | Design                                                 | Procedure and Example for the Auxiliary Circuit Stage                                          | 42 |

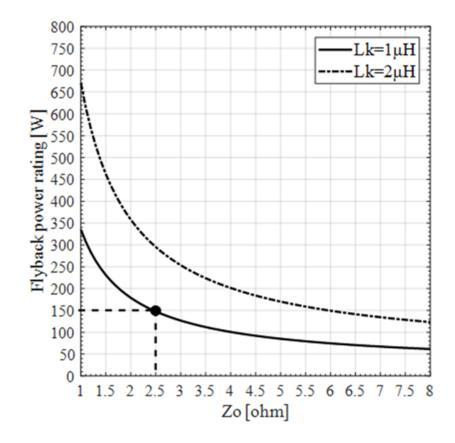

|                |                                                                | 2.5.1                                                  | Power Rating for the flyback snubber                                                           | 44 |

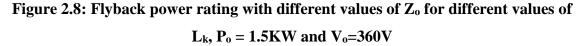

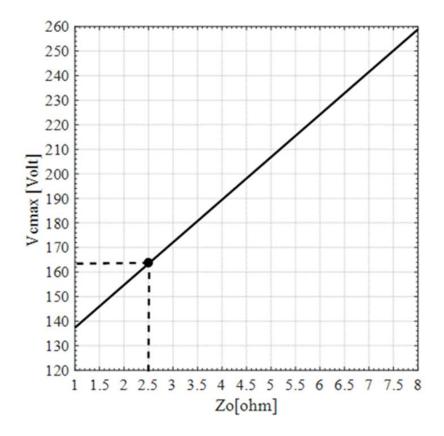

|                |                                                                | 2.5.2                                                  | Peak voltage across the clamping capacitor                                                     | 45 |

|                |                                                                | 2.5.3                                                  | Voltage stress across flyback switch and flyback transformer turns ratio                       | 47 |

|                |                                                                | 2.5.4                                                  | Determine the duty cycle $D_f$ and the characteristic impedance $Z_1$ of the flyback converter | 49 |

|                |                                                                | 2.5.5                                                  | Maximum current in the clamping switch                                                         | 49 |

|                |                                                                | 2.5.6                                                  | Average and RMS currents in the flyback converter switch                                       | 50 |

| 2.6 Conclusion |                                                                |                                                        | ision                                                                                          | 50 |

| Cl             | napte                                                          | er 3                                                   |                                                                                                | 53 |

| 3              | Experimental Results of a Proposed Three-phase DC-DC converter |                                                        |                                                                                                |    |

|                | 3.1                                                            | Experi                                                 | mental results                                                                                 | 53 |

|                | 3.2 Comparison and discussion                                  |                                                        |                                                                                                |    |

|   |       | 3.2.1   | Three-Phase DC-DC Boost Converter with Three-Switch Active Clam | p 57 |

|---|-------|---------|-----------------------------------------------------------------|------|

|   |       | 3.2.2   | Comparison results                                              | 58   |

|   | 3.3   | Conclu  | usion                                                           | 65   |

| C | hapte | er 4    |                                                                 | 67   |

| 4 | A S   | ingle-P | hase ZVS AC-DC Boost Converter with Interleaved Input           | 67   |

|   | 4.1   | Conve   | rter Operation                                                  | 67   |

|   | 4.2   | Conve   | rter Features                                                   | 72   |

|   | 4.3   | Steady  | v State Analysis                                                | 73   |

|   | 4.4   | Conve   | rter Characteristics                                            | 76   |

|   | 4.5   | Design  | n Procedure and Example                                         | 77   |

|   |       | 4.5.1   | Main transformer turns ratio, n                                 | 80   |

|   |       | 4.5.2   | Determine the Value of Duty Cycle                               | 81   |

|   |       | 4.5.3   | Maximum Input Inductor Value                                    | 81   |

|   |       | 4.5.4   | Clamp Capacitor (C <sub>c</sub> )                               | 83   |

|   |       | 4.5.5   | ZVS Turn on Range                                               | 84   |

|   | 4.6   | Experi  | mental Results                                                  | 84   |

|   | 4.7   | Conclu  | usion                                                           | 88   |

| C | hapte | er 5    |                                                                 | 89   |

| 5 | AN    | lovel H | igh-Gain Three-Phase DC-DC PWM Boost Converter                  | 89   |

|   | 5.1   | Conve   | rter Operation and Analysis                                     | 89   |

|   | 5.2   | Conve   | rter Features                                                   | 95   |

|   |       | 5.2.1   | Current ripple reduction                                        | 96   |

|   |       | 5.2.2   | High output gain                                                | 96   |

|   |            | 5.2.3   | Single-stage power processing                                           | . 96 |

|---|------------|---------|-------------------------------------------------------------------------|------|

|   |            | 5.2.4   | Inherent snubber circuit                                                | . 97 |

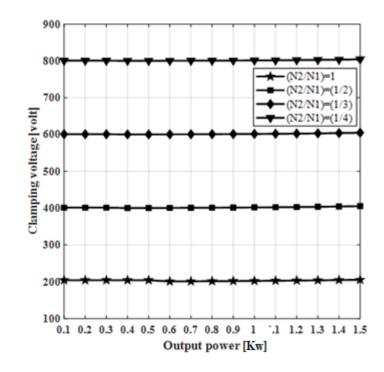

|   |            | 5.2.5   | Reduced peak switch voltage stress                                      | . 98 |

|   | 5.3        | Desigr  | Considerations                                                          | . 98 |

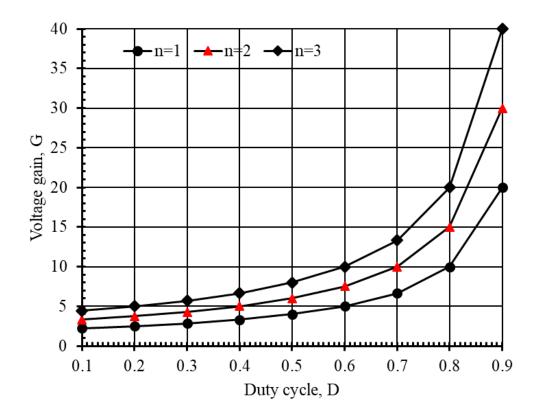

|   |            | 5.3.1   | Input-output voltage gain                                               | . 98 |

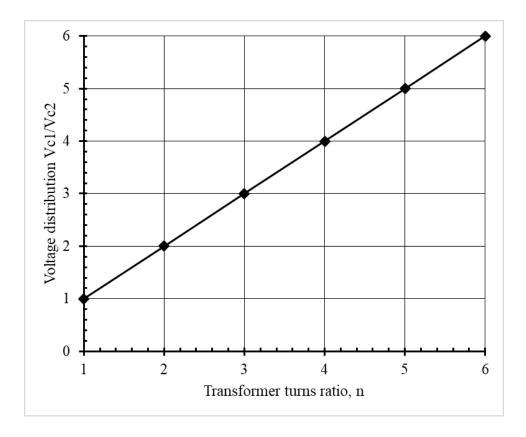

|   |            | 5.3.2   | Transformer turns ratio, n                                              | . 99 |

|   | 5.4        | Desigr  | Procedure and Example of the Proposed Converter                         | 101  |

|   |            | 5.4.1   | Peak input current                                                      | 102  |

|   |            | 5.4.2   | Input-output voltage gain                                               | 102  |

|   |            | 5.4.3   | Determine the value of the duty cycle, D and transformer turns ratio, n | 103  |

|   |            | 5.4.4   | Determine the value of input boost inductor                             | 103  |

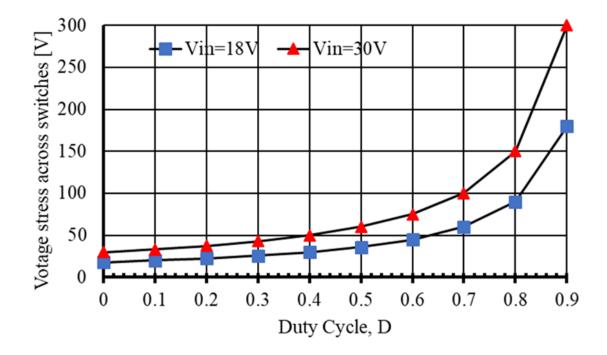

|   |            | 5.4.5   | Voltage stress across switches S <sub>1</sub> -S <sub>3</sub>           | 104  |

|   |            | 5.4.6   | Current stress on switches S <sub>1</sub> -S <sub>3</sub>               | 105  |

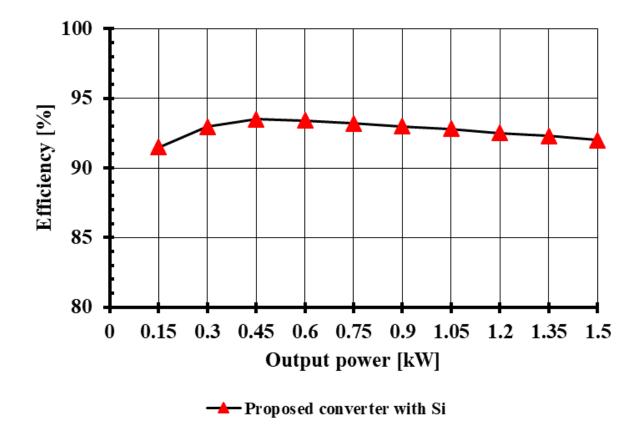

|   | 5.5        | Experi  | mental Results                                                          | 106  |

|   | 5.6        | Conclu  | usion                                                                   | 110  |

| C | hapte      | er 6    |                                                                         | 111  |

| 6 | Sun        | nmary a | and Conclusion                                                          | 111  |

|   | 6.1        | Summ    | ary                                                                     | 111  |

|   | 6.2        | Conclu  | usions                                                                  | 113  |

|   | 6.3        | Contri  | butions                                                                 | 115  |

|   | 6.4        | Sugge   | sted and Future Work                                                    | 116  |

| R | References |         |                                                                         |      |

| C | urric      | ulum V  | itae                                                                    | 123  |

# List of Tables

| Table I: Specifications and key parameters the proposed prototypes                       | 54 |

|------------------------------------------------------------------------------------------|----|

| Table II: Specifications of the proposed converter and the three-phase with active clamp | 60 |

| Table III: Comparison of the two three-phase DC-DC converters                            | 65 |

# List of Figures

| Figure 1.1: DC-DC boost converter                                                                                                                                                  | 3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 1.2: Loss of power during hard switching                                                                                                                                    | 4 |

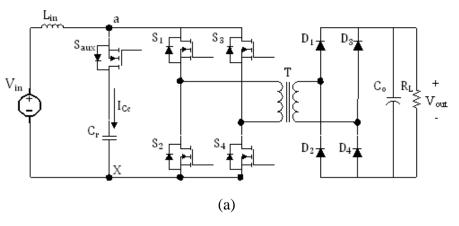

| Figure 1.3: Types of DC-DC full-bridge converter (a) A full-bridge voltage-fed DC-DC converter (figure reproduced from [1]). (b) Full bridge current-fed boost dc-dc converter [2] | 6 |

| Figure 1.4: Example current-fed DC-DC full-bridge converters, (a) ZVS current-fed full bridge converter [3] (b) ZCS current-fed full-bridge converter [4]                          | 8 |

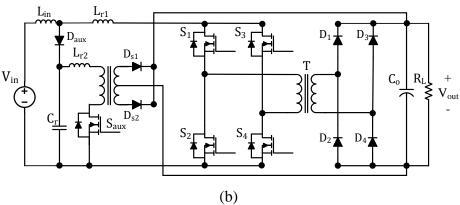

| Figure 1.5: Three phase high frequency DC-DC converter proposed in [5] 1                                                                                                           | 0 |

| Figure 1.6: Three phase ZVS dc-dc converter with the Hybridge rectifier [9] 1                                                                                                      | 0 |

| Figure 1.7: Three phase DC-DC resonant converter [12] 1                                                                                                                            | 2 |

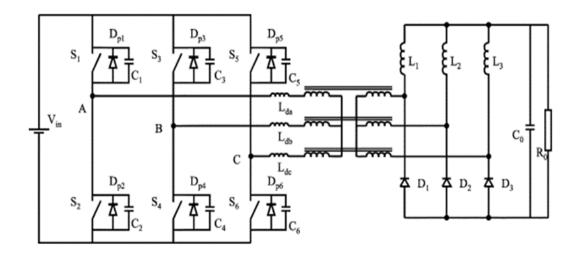

| Figure 1.8: Six-leg three phase high power DC-DC converter [10] 1                                                                                                                  | 2 |

| Figure 1.9: Three-phase current-fed DC/DC converter produced from [14] 1                                                                                                           | 4 |

| Figure 1.10: Three-phase current-fed DC/DC converter with single input inductor and active clamp [16] 1                                                                            |   |

| Figure 1.11: Three-phase current-fed DC/DC converter with three input inductors and auxiliary circuit produced from [15]                                                           | 5 |

| Figure 1.12: (a) Hybrid interleaved parallel AC-DC boost converter [35] (b) Differential interleaved AC-DC boost converter [36]                                                    | 7 |

| Figure 1.13: Two-stage AC-DC converter with three-phase input interleaving 1                                                                                                       | 7 |

| Figure 1.14: Block diagram of a renewable energy system                                                                                                                            | 9 |

| Figure 1.15: Coupled inductor-assisted two quadrant high frequency PWM chopper type DC-                                        |

|--------------------------------------------------------------------------------------------------------------------------------|

| DC converter [62]                                                                                                              |

| Figure 1.16: High-gain three-phase DC-DC reproduced from [22]                                                                  |

| Figure 2.1: Proposed three-phase DC-DC PWM boost converter with flyback snubber 25                                             |

| Figure 2.2: Typical converter waveforms at D=0.5                                                                               |

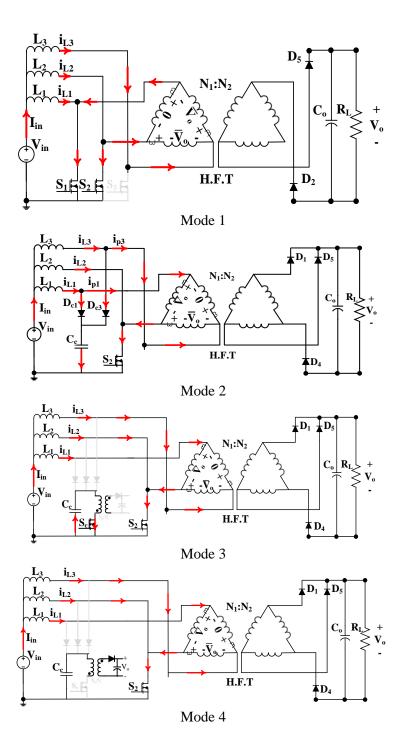

| Figure 2.3: Modes of operation                                                                                                 |

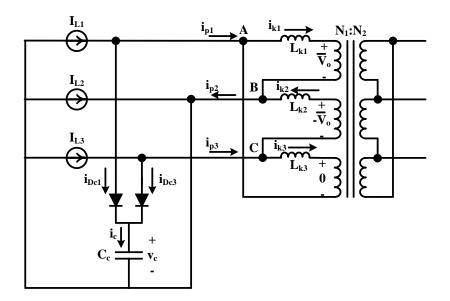

| Figure 2.4: Equivalent circuit of mode 2 using $\Delta$ - $\Delta$ three-transformer configuration                             |

| Figure 2.5: Voltage gain with duty cycle according to the variation of transformer turns ratio, n under CCM                    |

| Figure 2.6: Primary voltage across the main transformer with turns ratio,n                                                     |

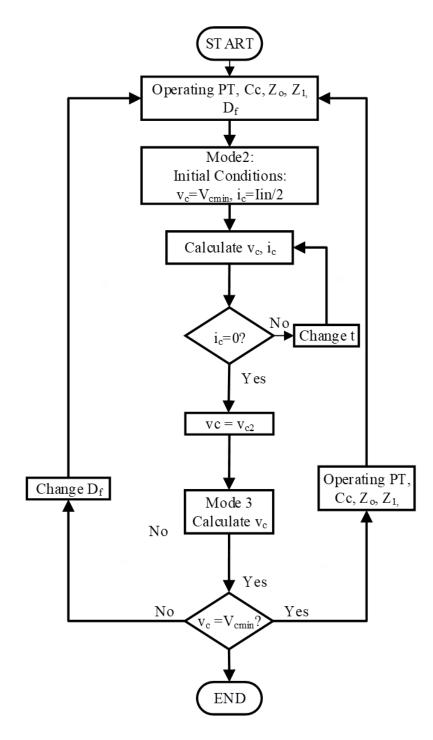

| Figure 2.7: Flowchart of program to determine if converter is operating under steady-state conditions                          |

| Figure 2.8: Flyback power rating with different values of $Z_0$ for different values of $L_k$ , $P_0 = 1.5$ KW and $V_0=360$ V |

| Figure 2.9 : Maximum voltage across the clamping capacitor with different values of $Z_0$ , $P_0 = 1.5$ KW and $V_0=360$ V     |

| Figure 2.10: Variation of the maximum voltage across the clamping capacitor with different values of $C_c$ and $L_k$           |

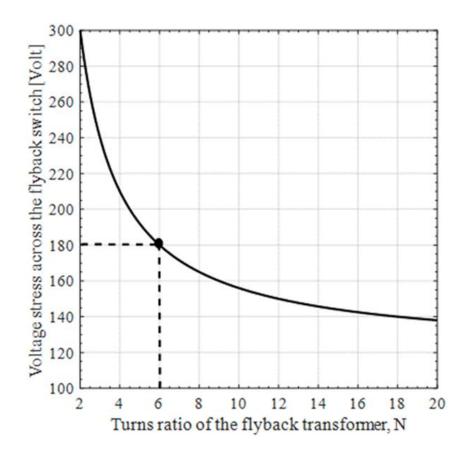

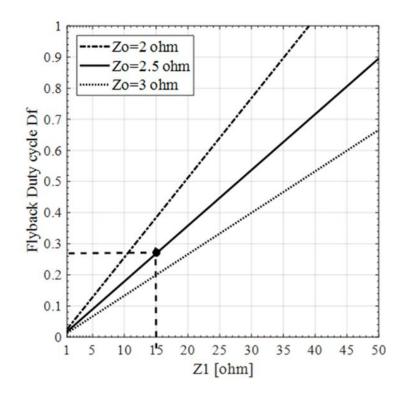

| Figure 2.11: Flyback switch's voltage stress with flyback transformer turns ratio, N                                           |

| Figure 2.12: Flyback duty cycle for different values of $Z_0$ and $Z_1$                                                        |

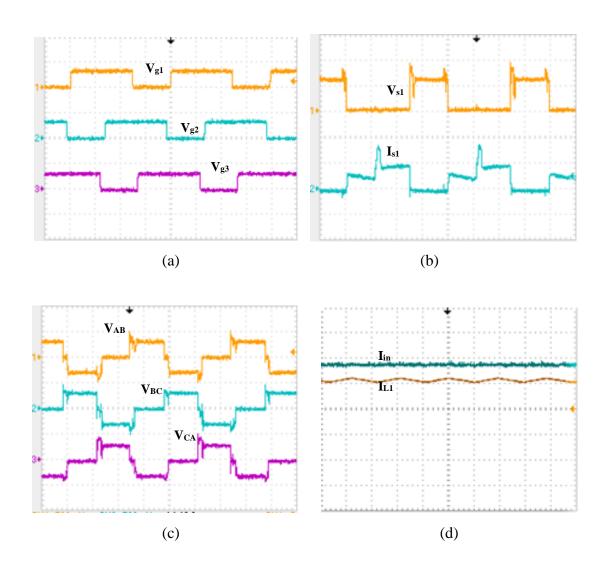

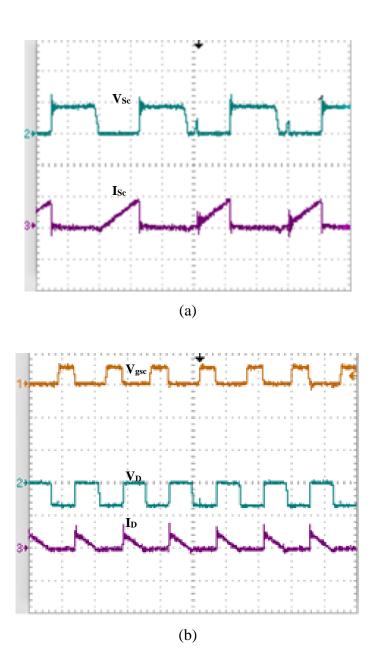

| Figure 3.2: Flyback snubber circuit waveforms: (a) the voltage across the flyback switch and                            |

|-------------------------------------------------------------------------------------------------------------------------|

| the current through it (V: 200V/div., I: 10A/div., t: 2.5µs/div), (b) gating signal and output                          |

| diode voltage and current for flyback snubber (V g : 50V/div., V <sub>D</sub> : 1000V/div., I <sub>D</sub> : 2A/div., t |

| : 5µs/div                                                                                                               |

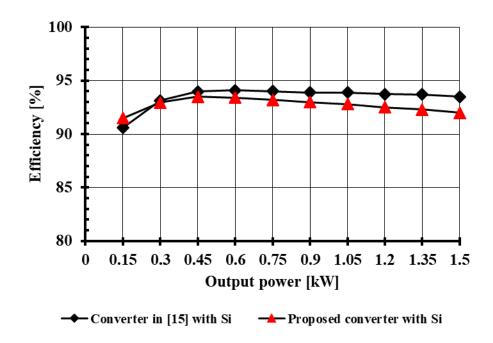

Figure 3.6: Efficiency curves of the proposed converter and converter in [15] using Si

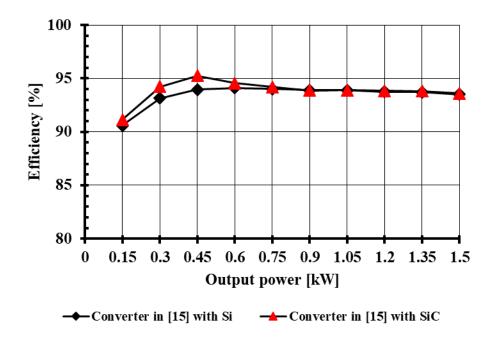

Figure 3.8: Efficiency curves of the converter in [15] using Si and SiC devices ...... 64

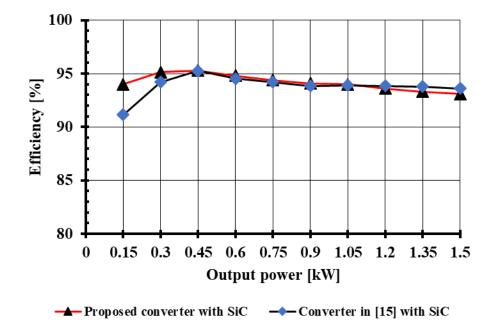

Figure 3.9: Efficiency curves of the proposed converter and converter in [15] using SiC

| Figure 4.3: Modes of operation                                                                           |

|----------------------------------------------------------------------------------------------------------|

| Figure 4.4: Effect of transformer ratio value n on clamping voltage ( $V_{in}=90 V_{rms}$ , $V_o=200V$ , |

| $f_s=50$ KHz, $L_1=100\mu$ H, $L_{k1}=10\mu$ H)                                                          |

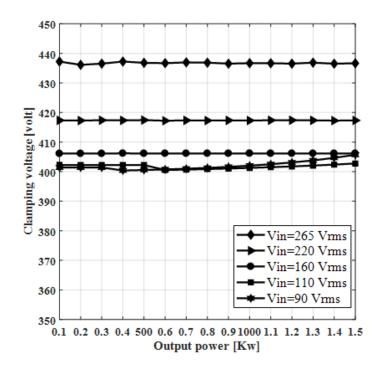

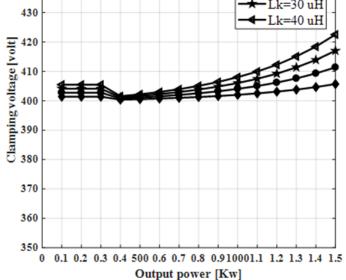

| Figure 4.5: Effect of input voltage on clamping voltage (n=0.5, $V_0$ =200V, f <sub>s</sub> =50KHz,      |

| $L_1 = 100 \mu H, L_{k1} = 10 \mu H$ )                                                                   |

| Figure 4.6: Effect of input inductor on clamping voltage (Vin=90 Vrms, n=0.5, $V_0$ =200V,               |

| $f_s=50$ KHz, $L_{k1}=10\mu$ H)                                                                          |

| Figure 4.7: Effect of leakage inductor on clamping voltage (Vin=90 Vrms, n=0.5, V <sub>0</sub> =200V,    |

| $f_s=50$ KHz, $L_{in}=100\mu$ H)                                                                         |

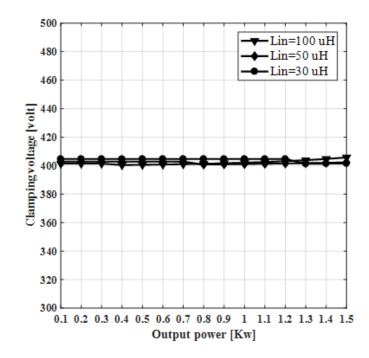

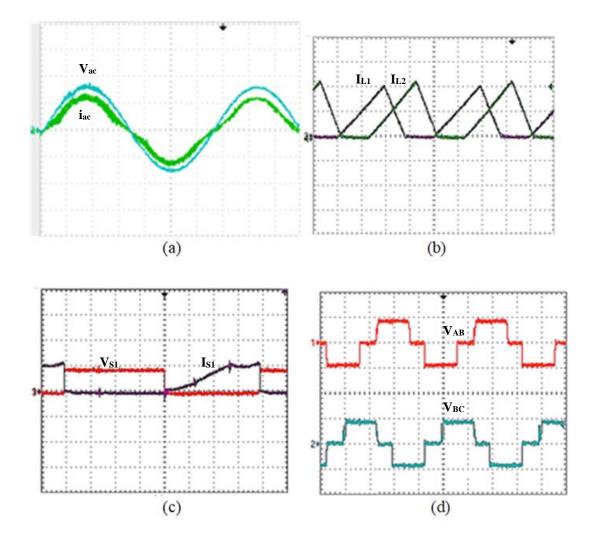

| Figure 4.8: Typical converter's waveforms: (a) input ac voltage and current (V:100V/div,                 |

| I:20A/div, t:5ms/div), (b) current through two of boost inductors (I:10A/div, t:5us/div), (c)            |

| the voltage across one of the main switch and the current through it (V:500V/div, I:20A/div,             |

| t:5us/div), (d) primary voltage waveform across two phases of the transformer (V:500V/div.,              |

| t:5µs /div)                                                                                              |

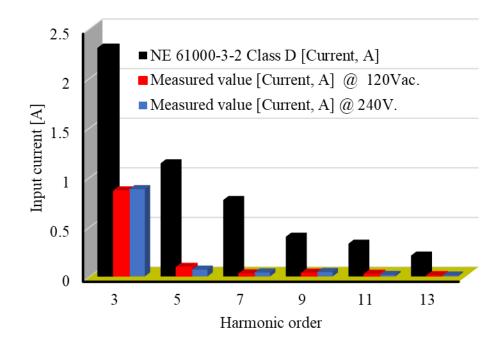

| Figure 4.9: Input current harmonics at $V_{in} = 120 V_{rms}$ and $V_{in} = 240 V_{rms}$ compared with   |

| EN6100-3-2 standard at full load operation                                                               |

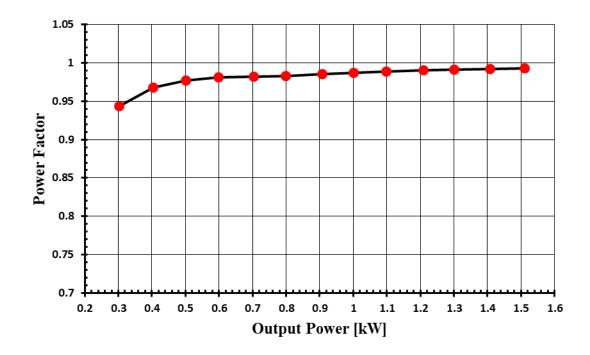

| Figure 4.10: PFC of the proposed converter                                                               |

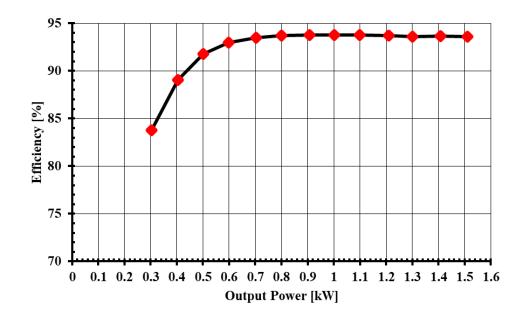

| Figure 4.11: Efficiency of the proposed converter                                                        |

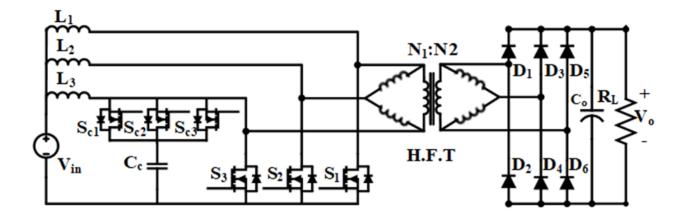

| Figure 5.1: Proposed high-gain three-phase DC-DC PWM boost converter                                     |

| Figure 5.2: Typical converter waveforms                                                                  |

| Figure 5.3: Converter modes of operation                                                                 |

| Figure 5.4: Voltage gain according to duty cycle with different values of transformer turns       |

|---------------------------------------------------------------------------------------------------|

| ratio, n under CCM 100                                                                            |

| Figure 5.5: output voltages distribution according to the variation of transformer turns ratio, n |

| Figure 5.6: Switches voltage stress with duty cycle, D, for different values of input voltage,    |

| V <sub>in</sub>                                                                                   |

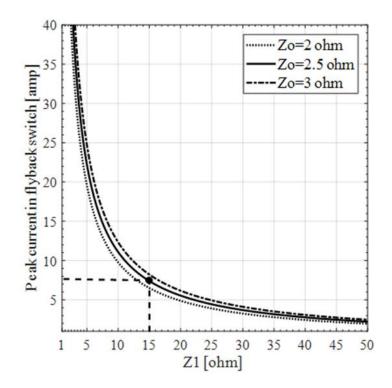

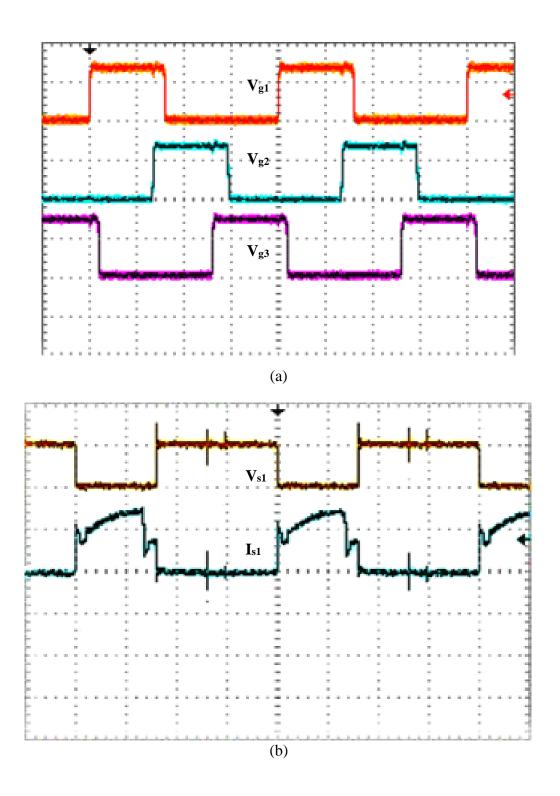

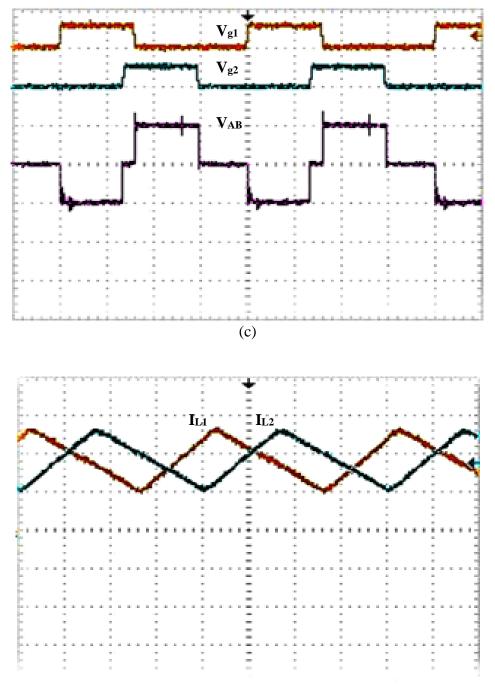

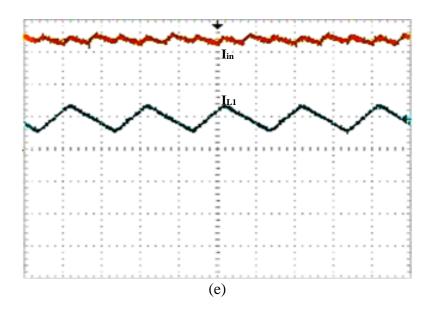

| Figure 5.7: Experimental results: (a) Gating signal waveforms (V:20V/div., t:5µs/div.), (b)       |

| Voltage and current for the main switch (V: 50V/div., I: 5A/div., t: 5µs/div), (c) Gating         |

| signal waveforms for two main switches and primary voltage waveform across the                    |

| transformer (Vg: 50V/div., Vt: 50V/div., t: 5µs/div, (d) Current through two main inductors       |

| (I: 1A/div, t: 5µs/div.), (e) Input current and main inductor current waveform (Iin: 2A/div.,     |

| $I_L: 2A/div, t: 10\mu s/div.)$                                                                   |

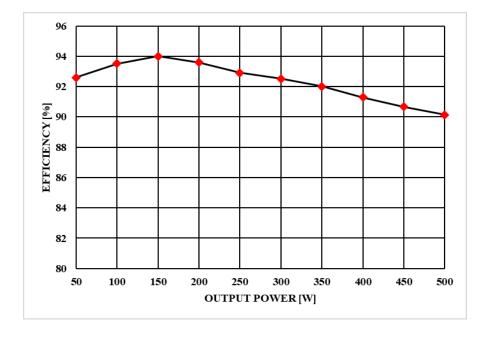

| Figure 5.8: Efficiency curve of the proposed converter                                            |

# Acronyms

- AC : Alternate Current

- AVG: Average Value

- CCM: Continuous Current Mode

- DC: Direct Current

- DCM: Discontinuous Current Mode

- EMI: Electro Magnetic Interference

- GaN: Gallium Nitride

- PF: Pwer Factor

- PFC: Power Factor Correction

- PWM: Pulse Width Modulation

- RMS: Root Mean Square

- Si: Silicon

- SiC: Silicon-Carbide

- THD: Total Harmonic Distortion

- ZCS: Zero Current Switching

- ZVS: Zero Voltage Switching

# Abbreviations

| Co              | Output Capacitor                                           |

|-----------------|------------------------------------------------------------|

| Cc              | Clamping Capacitor                                         |

| D               | Duty Cycle                                                 |

| Df              | Flyback Duty Cycle                                         |

| Dx              | Diode x                                                    |

| D <sub>cx</sub> | Clamping Diode x                                           |

| Dax             | Auxiliary Diode x                                          |

| fs              | Switching Frequency of Main Switches                       |

| <b>f</b> sf     | Switching Frequency of Fyback Switch                       |

| G               | Gain                                                       |

| İDCx            | Current Through Clamping Diode x                           |

| lin             | Input Current                                              |

| I <sub>Lm</sub> | Magnetizing Current                                        |

| lo              | Output Current                                             |

| I <sub>px</sub> | Current through the Primary of Main Transformer in Phase x |

| Is,avg          | Switch Average Current                                     |

- Is,pk Switch Peak Current

- Is,rms Switch RMS Current

- Lin Input Inductance

- L<sub>x</sub> Inductor x

- L<sub>kx</sub> Leakage Inductor x

- L<sub>m</sub> Magnetizing Inductor

- L<sub>o</sub> Output Inductor

- N, n Transformer Turns Ration

- P<sub>in</sub> Input Power

- Po Output Power

- P<sub>fb</sub> Flyback Power Rating

- Rds-on Resistance Between Drain-Source in MOSFET when Switch is ON

- R<sub>o</sub> Output Resistive Load

- S<sub>x</sub> Switch x

- t Time

- Vin Input Voltage

- Vo Output Voltage

- Voltage Across Primary Side of Main Transformer

| Vc, VCc | Voltage Across Cc |

|---------|-------------------|

|---------|-------------------|

- V<sub>Cmin</sub> Minimum Voltage Across Cc

- V<sub>Cmax</sub> Maximum Voltage Across Cc

- Z<sub>0</sub>, Z<sub>1</sub> Characteristic Impedance

- Δ<sub>iL</sub> Inductor Current Ripple

- Δv<sub>o</sub> Output Voltage Ripple

# Chapter 1

# 1 Introduction

#### 1.1 Introduction

Power electronics is the field of electrical engineering that is concerned with the use of power semiconductor devices to convert electrical power from the form that can be used by a source to the form needed by a load. The input source can be utility voltage, a battery, solar panels, fuel cells, electric generators, etc. The load can be a motor, telecommunications equipment, medical equipment, a battery, etc. Power semiconductor devices are implemented along with passive elements such as inductors, capacitor and transistors in power converters. Although all these elements can be arranged in many ways, in many different converter structures called topologies. There are four basic types of power converters: - AC-DC, DC-DC, DC-AC and AC-AC - depending on whether the source is AC or DC and whether the load is AC or DC.

The focus of this thesis is on three-phase DC-DC converters. Although there is no phase associated with DC sources and loads, the term 'three-phase DC-DC' comes from the fact that DC-DC power conversion is typically done by performing DC-AC conversion first then AC-DC conversion. Such an approach is needed if a DC input voltage is to be stepped up or stepped down. As this cannot be done directly with a transformer (unlike AC), what is needed is an intermediate AC voltage produced from the DC source that can be stepped up or down by a transformer then rectified to produce the desired DC voltage. This AC voltage can be single-phase or three-phase and thus fed to a single-phase or three-phase transformer. What the term "three-phase DC-DC" really means is a DC-DC converter that has a three-phase transformer in its topology. It should be noted that the three-phase AC voltage that is applied to the transformer does not have a frequency of 60 Hz, but has a much higher frequency, in the tens of kHz, so that voltage can be stepped up or down using a much smaller transformer.

Three-phase DC-DC converters are attractive because they have several advantageous features over conventional DC-DC converter that have a single-phase transformer in their

topologies. One advantage is that instead of using three DC-DC converters in parallel for particular applications, just one three-phase DC-DC converter can be used; this advantage is particularly attractive for higher power applications. Another advantage is that the input current ripple can be significantly reduced. Current ripple is the AC component that appears on a DC waveform and is a source of power losses that can reduce power conversion efficiency. By using three-phase DC-DC converters, the ripple current of each individual phase can be reduced considerably so that the overall current coming out of the DC source has lower ripple and less thus filtering is needed. A third advantage is that the current stresses on converter components are lower than those found in single-phase DC-DC converters as current is split among three phases.

Three-phase DC-DC converters are attractive for higher power applications. Other applications where three-phase DC-DC converters are attractive are renewable energy applications such as solar power conversion and fuel-cell power converters. Renewable energy sources such as solar cells and fuel cells tend to produce low output DC voltages. The current coming out of these sources can be considerable even for power conversion applications of a few hundred watts because their voltages are low and thus whatever converter is used to convert the low input DC voltage to a higher more practical DC voltage must be able to handle this high current. Since three-phase DC-DC converters are better than conventional DC-DC converters in this regard, therefore they are more suitable for certain renewable energy applications.

In this chapter, basic power electronic concepts that are related to the work performed for this thesis are explained and a literature review of relevant previous work that is related to the thesis topic is performed. The objectives of the thesis are then stated and the chapter concludes with an outline of this thesis.

## 1.2 Fundamental Concepts

In this section of the thesis, several fundamental power electronic concepts that are related to the thesis are presented.

#### 1.2.1 DC-DC Boost Converters

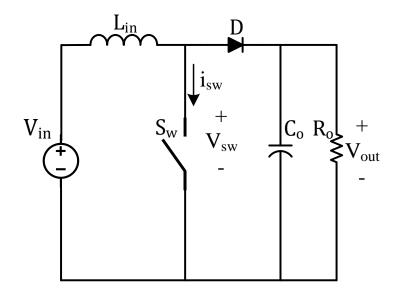

DC-DC converters may either have a transformer in their topologies, in which case they are isolated converters, or they may not, in which case they are non-isolated converters. If it is needed for a DC voltage to be stepped up and a non-isolated converter can be used, then one way of doing so is the conventional DC-DC boost converter shown in Figure 1.1. As can be seen in Figure 1.1, the converter consists of an input inductor  $L_{in}$ , a switch  $S_w$ , a diode D and an output capacitor  $C_o$ . The load represented by  $R_o$  in the figure.

The boost converter works as follows: The converter operates in periodic manner when it is in steady-state. Switch  $S_w$  can be on or off during a switching cycle. When switch  $S_w$  is on, the input voltage  $V_{in}$  is placed across the input inductor  $L_{in}$  and the current through it rises. While this is happening, diode D does not conduct current as it is reverse biased and output capacitor  $C_o$  supplies power to the load. When the switch is off, diode D conducts the full input inductor current and the capacitor is charged. While this is happening,  $L_{in}$  has negative voltage across it as the output voltage is greater than the input voltage and thus the input current falls. If the current falls to zero during the time that the switch is off, then the converter is considered to be operating in discontinuous current mode (DCM).

Figure 1.1: DC-DC boost converter

If the current does not fall to zero, then the converter is considered to be operating in continuous current mode (CCM). Current rises again when the switch is turned on at the start of the next switching cycle.

#### 1.2.2 Switching Losses

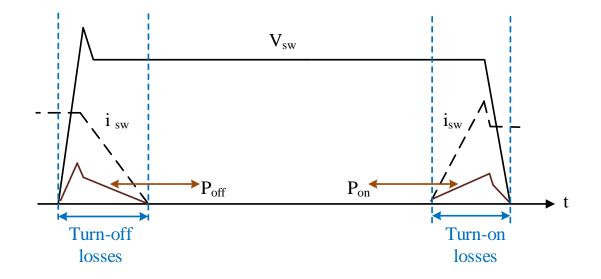

Ideal power electronic converters are 100% efficient and do not dissipate power while they are performing power conversion. In reality, however, power converters operate with certain power losses, some of these being switching losses. Switching losses in power converters occur whenever a converter switch, such as the switch in the boost converter shown in Figure 1.1, is turned on or off. During a switching transition, there is an overlap between the voltage across the switch and the current flowing through it and it is this overlap of voltage and current that creates the losses as shown in Figure 1.2. These switching losses can be reduced if either the switch voltage or the switch current is made to be zero at the time of the transition. As a result, converter efficiency can be increased if converter switches are operated with either zero-voltage switching (ZVS) or zerocurrent switching (ZCS). ZVS and ZCS are considered to be forms of soft-switching in the power electronics literature.

Figure 1.2: Loss of power during hard switching

There are various methods of implementing ZVS or ZCS in power converters. Many of these methods use an auxiliary circuit of some kind, usually connected parallel to the main converter switch(es), that either forces the voltage across the converter switches to zero before they are turned on or diverts the current away from the converter switches before they are turned off. A ZVS turn-off of a switch can be implemented by simply adding a small capacitor across it (or by using the device's output capacitance if it is sufficient) as the capacitor slows down the rate of voltage rise when it is turned off, which reduces the overlap of switch voltage and current and thus reducing switching losses. A ZCS turn-on of a switch can be implemented by adding a small inductor in series with it as the inductor slows down the rate of current rise when it is turned on, which reduces the overlap of switch voltage and current. The auxiliary circuit is activated before a switch is turned on for ZVS or before a switch is turned off for ZCS.

#### 1.2.3 Isolated Single-Phase DC-DC Full-Bridge Converters

DC-DC power conversion can be performed with converters that are more sophisticated than simple converters like the boost converter shown in Figure 1.1. Examples of such converters are isolated DC-DC converters that contain a transformer in their topologies. There are several types of these converters; this section will focus on full-bridge converters having a single-phase power transformer.

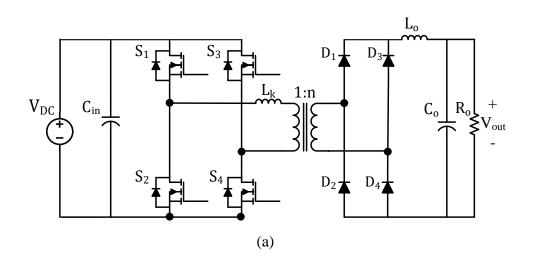

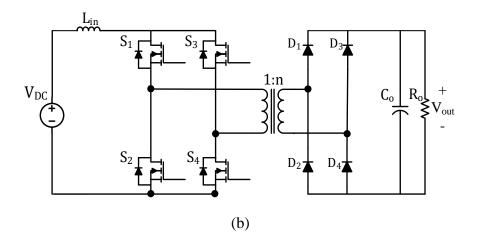

Full-bridge converters have four main switches in their topologies and are used in higher power applications (> 400 W). There are two types of single-phase DC full-bridge converters: voltage-fed converters [1] and current-fed converters [2]. Voltage-fed converters have a DC input that is a voltage source of some kind (a source or a bulk capacitor) that supplies power to the four-switch full-bridge; current-fed converters have a current source of some kind (i.e. a bulk inductor). The basic structure of both converters is shown in Figure 1.3.

The voltage-fed converter shown in Figure 1.3(a) consists of four switches  $S_{1-4}$ , a transformer with turns ratio n, a diode bridge rectifier at the secondary side of the transformer and an output filter that is made up of components  $L_o$  and  $C_o$ .

Figure 1.3: Types of DC-DC full-bridge converter (a) A full-bridge voltage-fed DC-DC converter (figure reproduced from [1]). (b) Full bridge current-fed boost dc-dc converter [2]

The way this converter works is as follows: The four main converter switches are turned on and off in a way that produces an AC square voltage across the primary of the transformer. This AC voltage can be stepped down or up (typically down) by the transformer and then rectified by the diode bridge. The output of the diode bridge is fed to a low pass filter that reduces AC harmonics so that a DC output voltage is produced.

The current-fed full-bridge converter shown in Figure 1.3(b) has a topology that is similar to the voltage-fed converter in Figure 1.3(a) except that the output has just a capacitor  $C_o$

as the output filter instead of an inductive-capacitive LC filter. This is because the converter in Figure 1.3(b) is an isolated version of the boost converter shown in Figure 1.1; just as the boost converter has a capacitive output filter, so too does the current-fed converter in Figure 1.3(b). The converter is the dual of the voltage-fed converter and operates in a similar manner. Instead of an AC square wave voltage being fed to the transformer primary, an AC square wave current is fed instead.

The main difference between the two converters is that the current-fed converter can have short-circuit states that are analogous to the turning on of the switch in a boost converter (which makes the input inductor current rise) while the voltage-fed converter cannot have such short circuit states, which would be destructive; instead it has open-circuit states that place zero voltage across the transformer primary.

Full-bridge converters can be operated with auxiliary circuits that can help the four main converter switches operate with soft-switching. Due to the nature of their topologies, auxiliary circuits are needed more for current-fed than for voltage-fed full-bridge converters. This is mainly because the input inductor of a current-fed full-bridge converter sees inductance in the form of the primary transformer. Since one inductance cannot interface with another inductance if they are carrying different currents, there needs to be some path for the current difference to flow through. An auxiliary circuit connected to the converter can provide such a path.

Examples of current-fed full-bridge converters with auxiliary circuits are shown in Figure 1.4. Figure 1.4(a) shows a full-bridge converter with an auxiliary circuit that allows the main switches to operate with ZVS [3] while Figure 1.4(b) shows a full-bridge converter with an auxiliary circuit that allows the main switches to operate with ZCS [4]. As explained in Section 1.2.2, an auxiliary circuit is activated just before certain key switching transitions to ensure soft-switching operation.

#### 1.3 Literature Review

Since the focus of this thesis is on three-phase DC-DC converters, a literature review of previously proposed converters of this type is performed in this section. As with the

single-phase isolated DC-DC converters discussed in the previous section, there are voltage-fed and current-fed converters. The literature review will cover both types of three-phase DC-DC converter.

## 1.3.1 Three-phase DC-DC voltage-fed converters

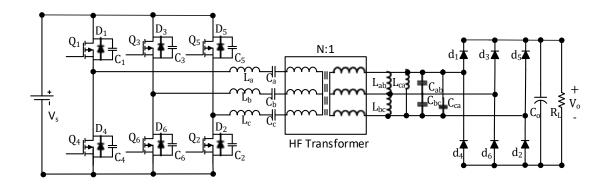

The first three-phase DC-DC converter was proposed by Prasad et al. in [5]; the converter is shown in Figure 1.5. This converter consists of six switches, a three-phase transformer a three-phase diode bridge rectifier connected to the transformer secondary and an output LC filter.

Figure 1.4: Example current-fed DC-DC full-bridge converters, (a) ZVS current-fed full bridge converter [3] (b) ZCS current-fed full-bridge converter [4]

The basic operating principle of this converter is very similar to that of the isolated voltage-fed DC-DC converter discussed in Section 1.2.3 as AC square wave voltages are impressed across the three-phase of the transformer, which are then rectified by the diode bridge then filtered by the LC filter to produce a DC output voltage. The three AC square wave voltages are identical, and each voltage is phase-shifted by 120° with respect to the other AC voltages. The shape and phase of each voltage is achieved by the appropriate turning on and off of the converter switches.

Almost work on the topic of three-phase DC-DC converters has been done by researchers, the literature on the topic is not as vast as what can be found for other types of DC-DC converters such as the forward or flyback converters. The main obstacle is the transformer as more research is needed to improve their design (e.g. implementing all the transformer magnetics on a single core to reduce size) before three-phase DC-DC converters have tremendous potential and research continues to be done on this type of topology.

This particular converter is attractive for a number of reasons compared to using multiple single-phase DC-DC converters as discussed in the Introduction: lower cost, less current ripple and lower component stresses. Most three-phase DC-DC converters are based on this particular topology [6]–[13]. The converter, however, does have a couple of drawbacks. One of these is that the number of semiconductor components in its topology is still considerable. As a result, converters like the one shown in Figure 1.6 [9] have been proposed. This converter is implemented with a secondary rectifier that consists of three diodes and three inductors instead of six diodes. One benefit of doing so, other that reducing the number of diodes in the converter, is that current flowing out of each phase of the transformer secondary flows through only one diode instead of two. Since there are power losses associated with semiconductor devices conducting current, some improvement in converter efficiency can be achieved by using fewer diodes and reducing conduction losses. Although the converter shown in Figure 1.6 may have fewer conduction losses, it still may have significant switching losses.

Another drawback of the converter introduced in [5] is that its switches produce switching losses whenever they are turned on and off; due to this drawback so-called soft-switching resonant converters have been proposed in the literature [7], [8], [12].

Figure 1.5: Three phase high frequency DC-DC converter proposed in [5]

Figure 1.6: Three phase ZVS dc-dc converter with the Hybridge rectifier [9]

Resonant converters use reactive components such as inductors and capacitors as part of passive circuit resonant networks to shape their transformer primary current so that it is sinusoidal. In the case of ZVS resonant converters, the resonant networks are designed so that the primary current lags the primary voltage. This ensures that current is injected in the anti-parallel diode that is part of any active power semiconductor device, along with the switch. This injected current clamps the voltage across a converter switch to near zero voltage so that the switch can be turned on with ZVS and thus with fewer switching losses.

An example of a three-phase resonant DC-DC converter is shown in Figure 1.7. It can be seen that a resonant network has been added to the original three-phase converter shown in Figure 1.5. Although the resonant network helps the converter switches operate with ZVS, the resonant components themselves may be bulky and thus increase converter size and weight.

More recent research such as in [9], [11], [13] has allowed voltage-fed three-phase DC-DC converters to be operated with ZVS without the use of resonant circuits. This has been achieved due to an improved understanding of how these circuits work and the development of new methods for the turning on and off of the converter switches. For even higher power applications, more sophisticated and complex three-phase DC-DC converters can be implemented with more devices. An example of one such converter is the converter shown in Figure 1.8 [10]. It can be seen that this converter has twelve switches instead of six. The switches in this converter conduct less current than do the switches in more conventional six switch topologies. Moreover, as there are more switches, there is more flexibility in how they are turned on and off so that ripple current flowing in the converter can be reduced. For especially high-power applications, this is beneficial as ripple current can be considerable. In addition to lower current ripple, the soft-switching operation of the converter switches can be achieved. This converter, however, is not used for lower power applications due to cost.

Figure 1.7: Three phase DC-DC resonant converter [12]

Figure 1.8: Six-leg three phase high power DC-DC converter [10]

# 1.3.2 Three-Phase DC-DC Current-Fed Converters

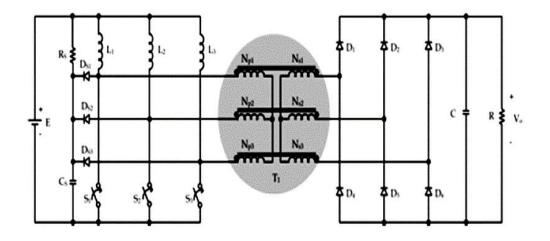

Current-fed converters are the other type of three-phase DC-DC converter. These converters are preferable for applications where the output voltage needs to be higher than the input voltage, as they are like the boost converter described in Section 2.1, and for applications where the input current is high as current can be distributed among the three-phases in a way that reduced input current ripple.

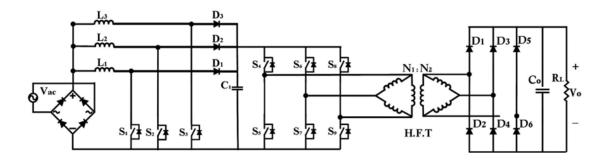

In 2005 a three-phase current-fed DC-DC converter was proposed by Oliveira and Barbi in [14] and is shown in Figure 1.9. It consists of three switches, three inductors, a three-phase high frequency transformer, a three-phase diode bridge rectifier and an output capacitor that acts as a filter. The secondary output section of the converter is similar to

that of the single-phase current-fed DC-DC converters discussed in Section 1.2.3 except that a three-phase diode bridge is used instead of a single-phase bridge. The primary section has three inductors each carrying about the same amount of current, but the ripple in each current is 120° out of phase with the ripple in the other currents so that the use of a bulky input inductor is avoided. The converter switches are operated in a way that ensures square wave AC currents are fed to the three-phase transformer; the input inductor currents rise and fall during any particular switching cycle.

A passive circuit consisting of diodes  $D_{s1}$ - $D_{s3}$  and resistor  $R_s$  and  $C_s$  is added to the converter to suppress or "snub" and voltage spikes that may appear across the switches when they are turned off. What the passive snubber circuit does is that it provides a path for current to flow through when a switch is turned off, thus avoid a situation when inductive current is forced through a switch, which can be destructive.

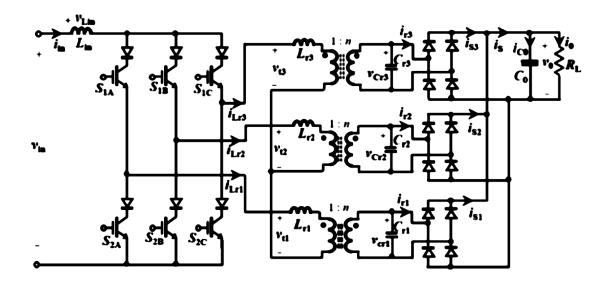

The main drawback of the converter shown in Figure 1.9 is that its switches do not operate with soft-switching. A number of soft-switching three-phase current-fed DC-DC converters have been proposed [15]–[22] with one of the earliest being the converter shown in Figure 1.10. This converter is essentially the three-phase version of the single-phase isolated current-fed DC-DC converter shown in Figure 1.3(b). It can be seen that it consists of six primary switches with an auxiliary circuit consisting of switch  $S_c$  and capacitor  $C_c$  connected across them in parallel. The converter can operate with ZVS due to the auxiliary circuit, but it has only one phase and thus one input inductor instead of three. This inductor must be very bulky in order to reduce ripple current and this converter is more suited to higher power applications with relatively lower input current.

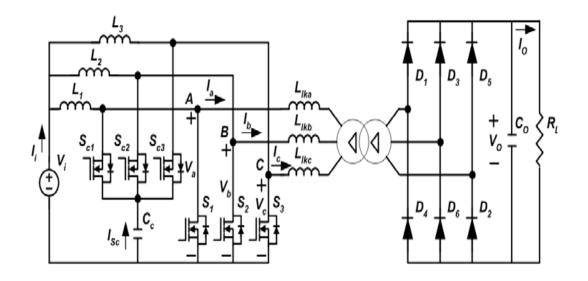

A way of combining the most attractive features of the converters shown in Figure 1.9 and Figure 1.10 is the converter shown in Figure 1.11. This converter has three main power switches and three inductors like the converter in Figure 1.9, but with an auxiliary circuit that can help its main switches operate with ZVS. The converter operates in the same way as the converter shown in Figure 1.9 except that the auxiliary circuit is activated whenever one of the main switches is about to be turned on. The auxiliary circuit consists of three active switches of lower power rating than the main switches and a capacitor. Since the converter has three phases, an auxiliary switch is needed for each phase unlike the converter shown in Figure 1.10, which has only one input phase and thus requires only one auxiliary switch. The converter, however, must still be implemented with six active switches.

Figure 1.9: Three-phase current-fed DC/DC converter produced from [14]

Figure 1.10: Three-phase current-fed DC/DC converter with single input inductor and active clamp [16]

Figure 1.11: Three-phase current-fed DC/DC converter with three input inductors and auxiliary circuit produced from [15]

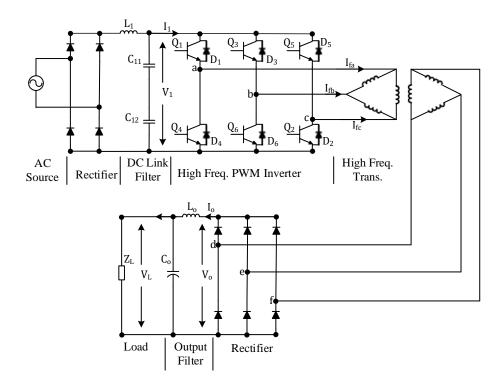

## 1.3.3 AC-DC Converters

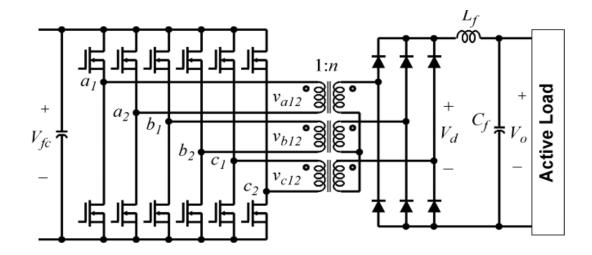

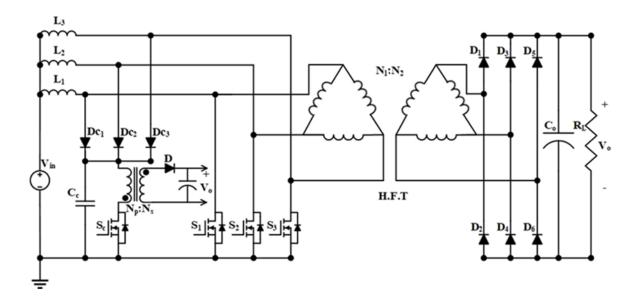

AC-DC power conversion typically involves the use of two power converters: an AC-DC front-end converter followed by a back-end DC-DC converter[23]–[28]. The AC-DC converter is usually some sort of boost converter that is implemented with power factor correction (PFC) to satisfy regulatory agency requirements on harmonic content. While the AC-DC converter is converting AC utility grid voltage to a DC voltage, it is also shaping the input current so that it is sinusoidal and in phase with the input voltage. The DC-DC converter is usually some sort of flyback or forward converter for lower power applications, some sort of half-bridge converter for medium power applications, and some sort of full-bridge converter for higher power applications. The DC-DC converter converter for the front-end converter into the desired output voltage.

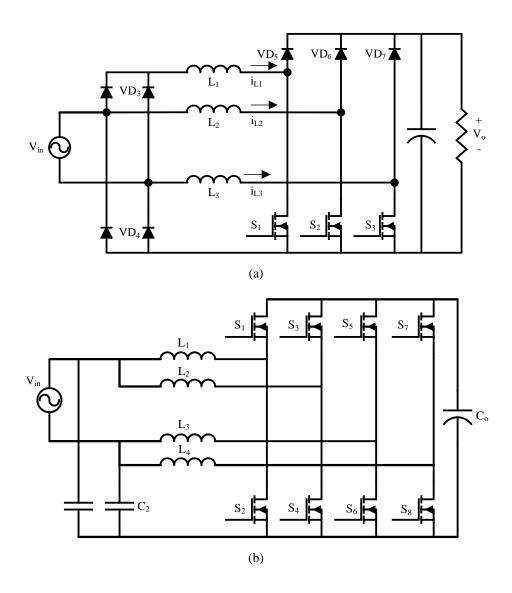

Although two-stage power conversion is popular, it can also be expensive as it requires two separate converters with two separate controllers to be implemented. The cost becomes even higher if additional switches are needed. For example, the interleaving of AC-DC boost converters is popular as a means of reducing input current ripple [29]–[35], but its benefits come at the cost of more boost converter switches and diodes as shown in Figure 1.12. Similarly, three-phase DC-DC converters that use three-phase transformers in their topologies can produce lower output current at higher harmonic frequencies, but such topologies generally need to be implemented with six switches, instead of the typical four switches used in conventional full-bridge topologies as presented in Section 1.3.1 [5]–[13]. An example of a two-stage converter with the AC-DC section implemented with a three interleaved boost converter and the DC-DC section implemented with a three-phase DC-DC bridge converter is shown in Figure 1.13.

Due to the cost and size of two-stage AC-DC converters, single-stage converters – converters that use just one power converter to convert AC input voltage into DC output voltage – have been proposed by power electronics researchers (i.e.[36]–[40], [41]–[45], [46]–[53]. Such converters can be synthesized by combining an AC-DC front-end converter with a DC-DC back end converter, then eliminating redundant components. In addition to having fewer power components, single-stage AC-DC converters are typically implemented with just a single controller to regulate the output voltage instead of two controllers, one for each of the two converter stages, thus further decreasing cost. Although many lower power flyback and forward-based AC-DC single-stage converters have been proposed, considerably fewer higher power AC-DC single stage converter have been proposed have at least one of the following drawbacks:

• The input current in the converter is discontinuous and has high current peaks; this can lead to higher component stresses and more EMI noise. The reason why the converter must operate with discontinuous input current is that the converter operates with just a single controller and with a fixed duty cycle over the entire AC input line period as the converter is simultaneously performing DC-DC conversion. Since the AC input current is not controlled, it must be made to be discontinuous so that it becomes a train of triangular pulses with their amplitudes following the shape of the sinusoidal input voltage [36], [38], [39], [42], [44], [47], [48].

Figure 1.12: (a) Hybrid interleaved parallel AC-DC boost converter [35] (b) Differential interleaved AC-DC boost converter [36]

Figure 1.13: Two-stage AC-DC converter with three-phase input interleaving

- The converter switches do not operate with zero-voltage switching (ZVS) and thus have switching losses that can lower their efficiency. Moreover, the suppression of voltage spikes caused by the interaction of transformer leakage inductance and switch output capacitance is an issue in some converters and sophisticated snubber circuits are needed to suppress them [36], [44], [48]–[51].

- Although the converter has fewer components that a two-stage converter, it remains expensive and bulky [38], [39], [42], [46].

- They are implemented with three separate ac-dc single-stage modules, which increase cost and introduce issues related to the synchronization of all three modules [52].

- Sophisticated or non-standard methods must be used to control the converter. For example, resonant converters that need that need to be controlled using variable switching frequency control methods [37], [43], [53].

# 1.3.4. High Gain DC-DC Converter

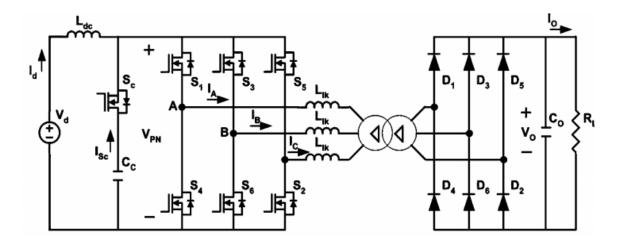

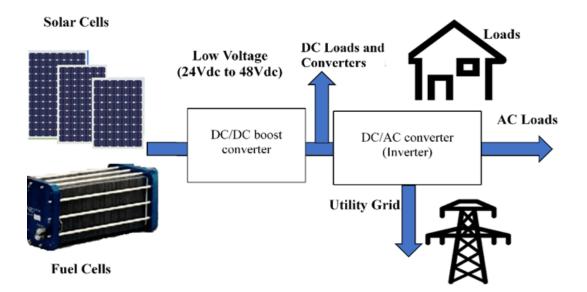

There are a number of applications that require power converters that can convert a low DC source voltage into a much higher DC output voltage. A common application where such power conversion is needed is for renewable energy systems such as the one shown in Figure 1.14.

In this system, input DC voltage is provided either by solar panels or fuel cells. The voltage obtained from such renewable power source is typically very low (< 50V) and needs to be stepped up considerably in order to feed downstream converters and loads. In the system diagram shown in Figure 1.14, inverters that interface with the grid, DC loads or DC-DC converters are supplied by a high DC voltage bus that was stepped up from the low voltage DC source by some sort of boost converter.

The boost converter is typically either a single-switch PWM boost converter or a fullbridge converter [54]–[61]. Although these converters have an input inductor that can

Figure 1.14: Block diagram of a renewable energy system

smooth out input current, considerable input current ripple can still be produced unless an extremely large input filter inductor is used. The ripple can create problems for the DC sources, especially those like batteries, PV cells and fuel cells that have issues with lifetime.

Another issue is that although single-switch PWM boost converters and current-fed fullbridge boost converters can boost input DC voltage, their gains are not sufficiently high for renewable energy applications such as what is shown in Figure 1.14. As a result, many high gain DC-DC converters have been proposed in the literature[62], [63], [72], [64]–[71]. These converters achieve high gain by cascading a boost converter so that they are quadratic converters, using coupled inductors, or using voltage multiplier cells. an example of these converters is shown in Figure 1.15. These converters, however, have at least one of the following problems:

- Their topologies have high conduction losses because current is forced to flow through a number of components in series in order to achieve high voltage gain.

- Their switches are subjected to high voltage spikes unless additional components are added to the circuit to suppress these spikes.

- Their components are subjected to high voltage and/or high current peak stresses.

- Input and output current ripple still remain an issue.

Three-phase DC-DC boost converters with input phases coming out of the DC source have less input current and output voltage ripple as the equivalent converter frequency is three times more than the switching frequency and their switches conduct less current than does the switch in a conventional PWM boost converter.

Current ripple is an important consideration for batteries as exposure to high current ripple can reduce their lifetime. Although they have less current ripple and are suitable for higher power applications due to their multi-switch topologies, little research has been done on increasing the gain of three-phase DC-DC converters and only a few high-gain three-phase DC-DC converters have been proposed [22], [73]–[76]. An example of these converters is shown in Figure 1.16. Although these converters address the issue of high current ripple, they still have some of the above-mentioned drawbacks.

Figure 1.15: Coupled inductor-assisted two quadrant high frequency PWM chopper type DC-DC converter [62]

Figure 1.16: High-gain three-phase DC-DC reproduced from [22]

## 1.1 Thesis Objectives

The main objective of this thesis is to propose new DC-DC and AC-DC converters that are based on three-phase DC-DC technology and that use fewer active switching devices than comparable existing converters. These converters include:

- A new three-phase DC-DC converter with input interleaving and transformer isolations.

- A new single-phase, single-stage AC-DC converter with input current interleaving and transformer isolation that uses a three-phase DC-DC converter in its topology.

- A new non-isolated three-phase DC-DC converter with high output voltage gain that can boost small DC input voltages to much larger ones that can then be used to feed other converters such as DC-AC inverters.

Other objectives of this thesis include:

• The steady-state characterization of these converters so that a design procedure for these converters can be established.

A comparison between the operation of the isolated three-phase DC-DC converter operating with traditional silicon devices (Si) and new silicon-carbide devices to determine how much better converter efficiency can be achieved. SiC devices are said to offer better performance than Si devices but are less readily available and more expensive.

For this work, the primary emphasis has been placed on the reduction on the number of switches that a converter is implemented with as this generally leads to a reduction in converter cost and size. It should be noted that it is not only the number of switches that are reduced, but also the amount of gate drive circuitry, the amount of sensing circuitry for the switches, the number of controllers and their complexity, and the cost and size of prototype space as well.

#### 1.5 Thesis Outline

The outline of this thesis is as follows:

In Chapter 2, a new three-phase DC-DC converter is presented. This converter requires fewer active switches than converters of the same type, has input current interleaving, inherent switch voltage clamping, and an auxiliary circuit that does not interfere with the operation of the main part of the circuit. In this chapter, the general operation of the converter is described as well as the most significant modes of operation that it goes through during a typical switching cycle. Equations for each mode of operation are derived and then used to establish a design procedure that can be used to select key converter components. The design procedure is demonstrated with an example and used to design an experimental converter prototype.

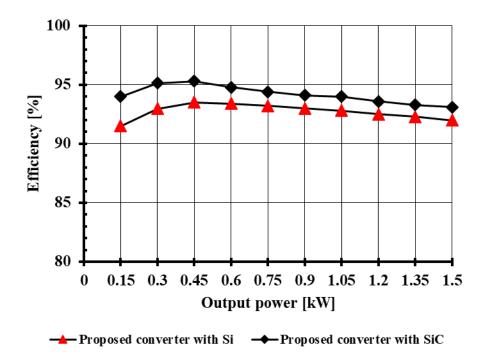

In Chapter 3, experimental results obtained from a prototype of the converter that was introduced in Chapter 2 are presented. Key experimental waveforms are shown as well as efficiency results. These efficiency results are compared to those obtained of a representative active-clamp type three-phase DC-DC converter operating with conventional silicon (Si) semiconductor devices. Further comparisons are made between experimental prototypes that were built with silicon-carbide (SiC) devices and conclusions related to converter performance with SiC devices vs Si devices are made.

In Chapter 4, a new single-phase AC-DC converter with three-phase transformer isolation is introduced. The advantages of this converter are that it has an interleaved input current, it has lower component current stresses and less output ripple than AC-DC converters with single-phase transformer isolation. In this chapter, the general operation of the converter is described and the most significant modes of operation that the converter goes through during a typical switching cycle are explained. Equations for each mode of operation are derived and then used to establish a design procedure that can be used to select key converter components. The design procedure is demonstrated with an example and used to design an experimental converter prototype. Results obtained from an experimental prototype of the proposed AC-DC converter are shown and conclusions are presented.

In Chapter 5, a new three-phase DC-DC converter with high output voltage / input voltage gain is introduced. The proposed high gain converter has high output gain, only three active switches, reduced switch voltage stress, an interleaved input for low input current ripple, and inherent voltage snubbing of the switches. In this chapter, the general operation of the converter is described and the most significant modes of operation that the converter goes through during a typical switching cycle is explained. Equations for each mode of operation are derived and then used to establish a design procedure that can be used to select key converter components. The design procedure is demonstrated with an example and used to design an experimental converter prototype. Results obtained from an experimental prototype of the proposed high-gain DC-DC converter are shown, and conclusions are presented.

In Chapter 6, the contents of the thesis are summarized, the main conclusion and contributions of the thesis are stated, and suggestions for future work are presented.

## Chapter 2

## 2 A Novel Three-Phase DC/DC PWM Isolated Boost Converter

A new three-phase DC-DC PWM boost converter that is suitable for use in renewable energy applications is proposed in this chapter. The number of active switches in the proposed circuit is less than that of other previously proposed converters of the same type, resulting in lower cost and simpler operation. The chapter discusses the operation of the converter, presents a procedure for its design, and demonstrates the procedure with an example.

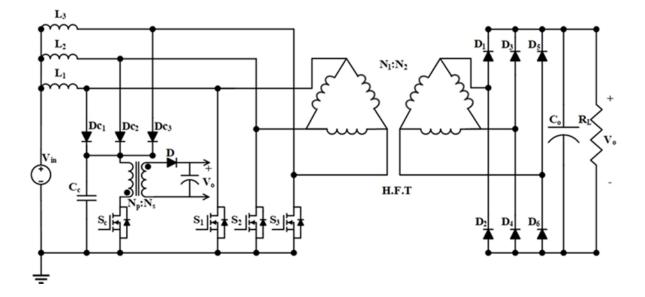

#### 2.1 Converter Operation and Analysis

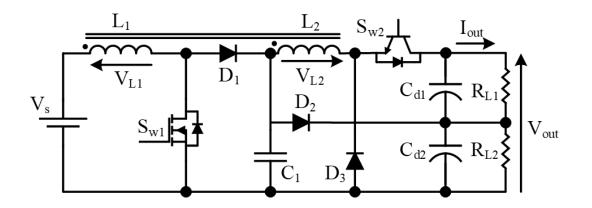

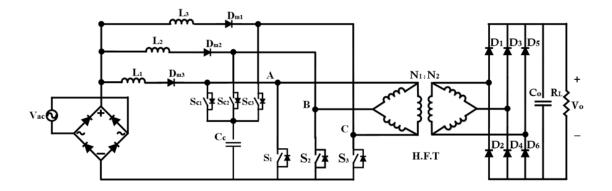

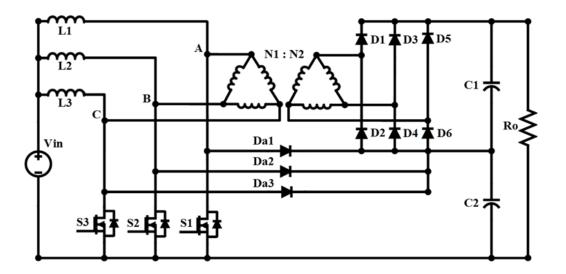

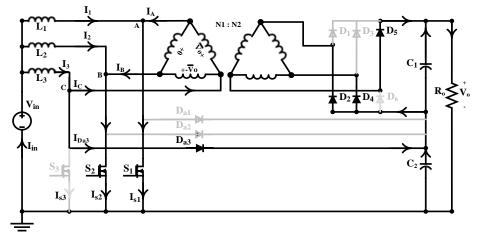

The proposed three-phase boost converter is shown in Figure 2.1. It is a three-interleaved boost converter that consists of three input inductors  $(L_1-L_3)$  and three main switches  $(S_1-S_3)$ . The converter is connected to the output (high voltage side) through three single-phase transformers whose primaries and secondaries are both connected in delta configuration, a three-phase diode bridge rectifier at the transformer secondary, and an output capacitive filter  $C_0$ . The converter is also connected to a flyback snubber through a clamping capacitor  $C_c$  and clamping diodes  $(D_{c1} - D_{c3})$ . The output of the flyback snubber is connected to the high voltage side of the converter. The proposed converter operates as follows: Whenever one of the main switches is turned on, the current through the main inductor that is connected to its drain rises and this inductor stores energy. Whenever one of the main switches is turned off, the current through the inductor that is connected to it starts to fall. The drain voltage of the switch becomes equal to the voltage across clamping capacitor  $C_c$ . If the three main transformers have the same gating signals, but shafted 120° with respect to each other, then a three-phase voltage can be produced across the three-phase transformer; this voltage can be rectified and fed to the output.

A flyback converter is connected to the interleaved boost converter to discharge capacitor  $C_c$  so that its voltage does not become excessive. Energy stored in  $C_c$  is fed to the output instead of being dissipated through a snubber resistor.

Figure 2.1: Proposed three-phase DC-DC PWM boost converter with flyback snubber

The level of the voltage across  $C_c$  depends on how often and for how long switch  $S_c$  is on, with the voltage across  $C_c$  being lower as  $S_c$  is on more frequently and for longer time.

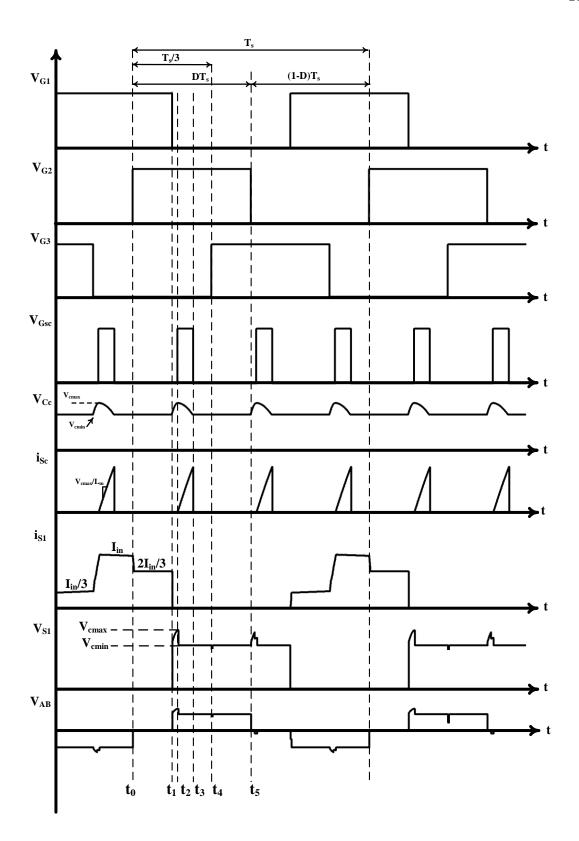

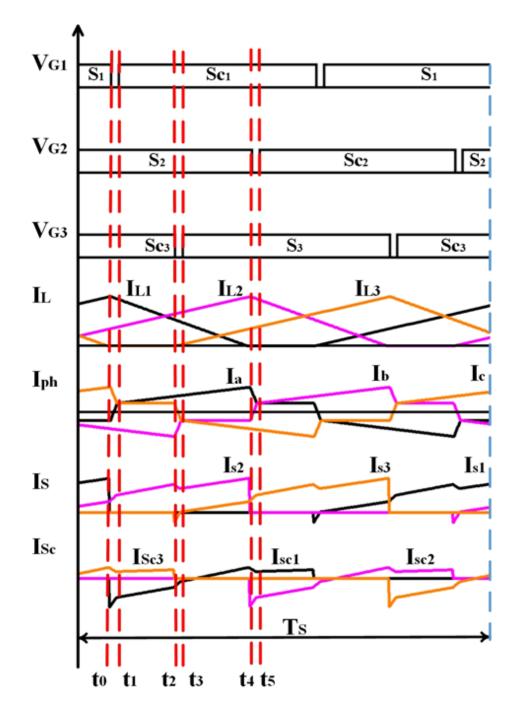

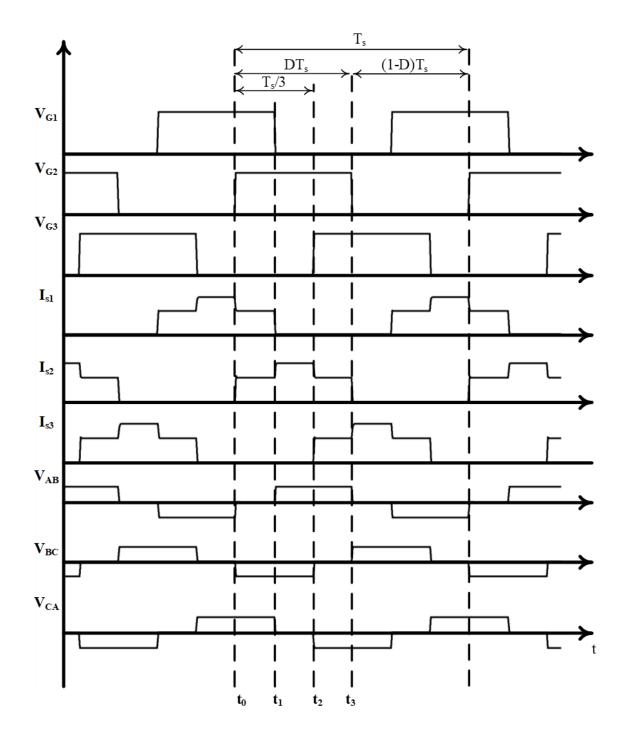

The modes of operation during a third of a steady-state switching cycle are explained in this section. Typical converter waveforms are shown in Figure 2.2 and circuit diagrams for each mode are shown in Figure 2.3. The following assumptions have been made in this section:

- The converter components are ideal

- The input inductors (L<sub>1</sub>, L<sub>2</sub> and L<sub>3</sub>) are large enough to keep the current through them continuous over a switching period.

- Switch  $S_1$  was on before  $t = t_0$  and that it is conducting the full input current before the start of Mode 1 of operation.

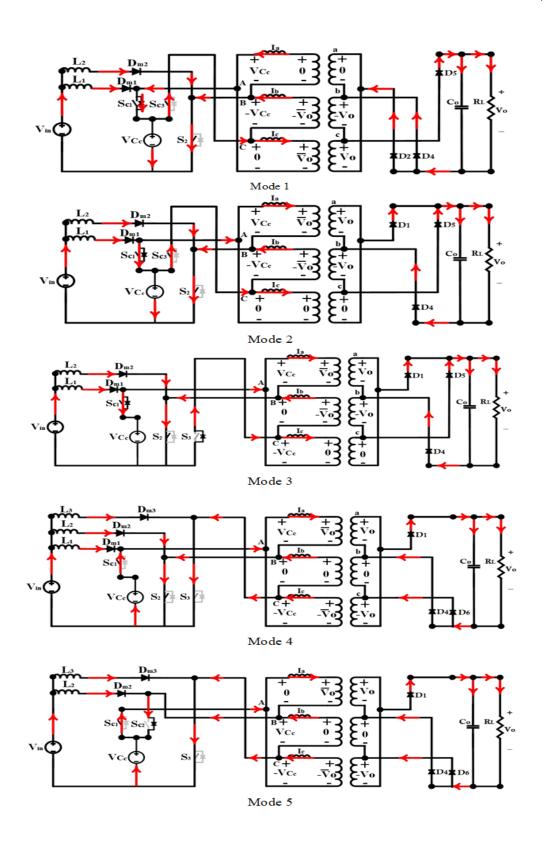

*Mode 1*  $[t_0 < t < t_1]$ : At t = t<sub>0</sub>, switch S<sub>2</sub> is turned on and current from the transformer is transferred to switch S<sub>2</sub>. This current transfer is gradual because of the transformer primary leakage inductance.

Figure 2.2: Typical converter waveforms at D=0.5

The current through  $S_2$  increases as the current through  $S_1$  decreases. Switches  $S_1$  and  $S_2$  are on, and  $S_3$  is off during this mode. Energy is transferred through the three-phase transformer through the windings that have voltage impressed across them. Diodes  $D_2$  and  $D_5$  conduct current in the secondary.

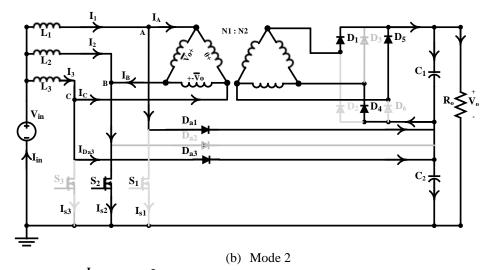

*Mode* 2 [ $t_1 < t < t_2$ ]: At t = t<sub>1</sub>, S<sub>1</sub> is turned off and the currents in diodes D<sub>c1</sub> and D<sub>c3</sub>, i<sub>Dc1</sub> and i<sub>Dc3</sub>, flow into the clamping capacitor. During this mode, the current through main switch S<sub>2</sub> increases as do currents i<sub>p1</sub> and i<sub>p3</sub>. At the converter's secondary side, diode D<sub>1</sub> starts to conduct and diodes D<sub>2</sub> and D<sub>5</sub> continue to conduct. Figure 2.4 shows the equivalent circuit of mode 2 reflected to primary side using  $\Delta$ - $\Delta$  three-transformer configuration.

At the end of this mode, switch  $S_2$  carries all input current, the current  $i_{Dc1}$  ( $t_2$ ) (=  $i_{L1}$  ( $t_2$ ) -  $i_{p1}$  ( $t_2$ )) drops to zero, and the voltage across the clamping capacitor reaches its peak value. This value can be determined using the following three steps:

• First, the current through the clamping capacitor is expressed as

$$i_c(t) = C_c \frac{dv_c(t)}{dt} = i_{Dc1}(t) + i_{Dc3}(t)$$

(2.1)

where,

$$i_{Dc1}(t) = I_{L1} - i_{p1}(t)$$

and,

$$i_{Dc3}(t) = I_{L3} - i_{p3}(t) \tag{2.2}$$

**Figure 2.3: Modes of operation**

Figure 2.4: Equivalent circuit of mode 2 using  $\Delta$ - $\Delta$  three-transformer configuration where,

$I_{L1}$  and  $I_{L3}$  are the input inductor currents of phase A and C respectively in steady state operation,

$i_{Dc1}$  and  $i_{Dc3}$  are the current that flow through the clamping diodes  $D_{c1}$  and  $D_{c3}$  respectively,

$i_{p1}$  and  $i_{p3}$  are the currents that follow through the primary transformer in phase A and C respectively as shown in Figure 2.4, and they can be obtained from (2.3) and (2.4)

$$i_{p1}(t) = i_{k1(t)} - i_{k3}(t) \tag{2.3}$$

$$i_{p3}(t) = i_{k2(t)} + i_{k3}(t) \tag{2.4}$$

where,  $i_{k1}$ ,  $i_{k2}$ , and  $i_{k3}$  are the currents of the leakage inductances of the three-phase transformer.

By substituting (2.2), (2.3), and (2.4) in (2.1), the following first order differential equation will be obtained

$$I_{L_1} + I_{L_3} = C_c \frac{dv_c(t)}{dt} + i_{k_1}(t) + i_{k_2}(t)$$

(2.5)

• Second, by derivative (2.5), it becomes

$$C_c \frac{d^2 v_c(t)}{dt^2} + \frac{di_{k1}(t)}{dt} + \frac{di_{k2}(t)}{dt} = 0$$

(2.6)

where  $i_{k1}$  and  $i_{k2}$  can be obtained from Figure 2.4 as following

$$L_{k_1} \frac{di_{k_1}}{dt} = v_c(t) - \bar{V_o}$$

(2.7)

$$L_{k_2} \frac{di_{k_2}}{dt} = v_c(t) - \bar{V_o}$$

(2.8)

• Third, By substituting (2.7) and (2.8) in (2.6) and the initial value of  $v_c$  is defined as  $V_c(0) = V_{c_{min}}$  and the initial value of the current through the clamping capacitor is  $\frac{I_{in}}{2}$ , the voltage across and the current through the clamping capacitor are obtained as

$$v_{c}(t) = V_{c_{\min}} \cos(\omega_{o} t) + \overline{V_{o}} (1 - \cos(\omega_{o} t)) + \frac{I_{in}}{2} Z_{o} \sin(\omega_{o} t)$$

(2.9)

$$i_{c}(t) = \frac{I_{in}}{2} \cos \omega_{0} t - \frac{V_{cmin} - \bar{V}_{o}}{Z_{0}} \sin \omega_{0} t$$

(2.10)

where,

$\overline{V_o} = \frac{V_o}{n}$ : primary voltage across the main transformer where  $V_o$  is the output voltage of the converter and n is the turn ratio of the main transformer  $\left(n = \frac{N2}{N1}\right)$ ,

$$\omega_o = \sqrt{\frac{1}{L_k C_c}} \tag{2.11}$$

and,

$$Z_o = \sqrt{\frac{L_k}{C_c}}, \quad \frac{1}{L_k} = \frac{1}{L_{k_1}} + \frac{1}{L_{k_2}}$$

(2.12)

At the end of this mode,  $i_c(t) = 0$  and  $v_c(t) = V_{c_{max}}$ . By substituting these values in (2.10) the duration of this mode can be determined, according to,

$$t_2 - t_1 = \frac{1}{\omega_o} \tan^{-1} \left( \frac{I_{in}}{2} \frac{Z_o}{V_{c_{min}} - \bar{V}_o} \right)$$

(2.13)

The peak voltage across voltage across the capacitor at the end of this mode, which also the peak voltage across the switches, becomes

$$V_{c_{max}} = V_{c_{min}} \cos \omega_0 (t_2 - t_1) + \overline{V_o} (1 - \cos \omega_0 (t_2 - t_1)) + \frac{I_{in}}{2} Z_o \sin \omega_0 (t_2 - t_1)$$

(2.14)

where,

$$\omega_o = \frac{1}{C_C Z_o} = \frac{1}{\sqrt{L_k C_c}} \tag{2.15}$$

Since the duration time of this mode is the quarter of the resonant cycle between the equivalent leakage inductance of the transformer,  $L_k$ , and the clamping capacitor,  $C_c$ , (i.e.  $t_2 - t_1 = \frac{\pi}{2} \sqrt{L_k C_c}$ ). By substituting in (2.14), the maximum voltage across the clamping capacitor can be obtained as

$$V_{c_{max}} = \overline{V_o} + \frac{I_{in}}{2} Z_o \tag{2.16}$$

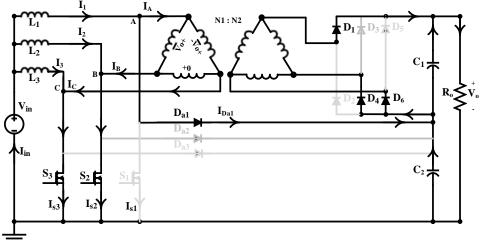

*Mode 3* [ $t_2 < t < t_3$ ]: At t = t<sub>2</sub>, clamping diode D<sub>c1</sub> stops conducting and capacitor C<sub>c</sub> starts discharging. Switches S<sub>1</sub> and S<sub>3</sub> remain off and switch S<sub>2</sub> stays on during this mode. Power is transferred to the output through D<sub>1</sub>, D<sub>4</sub> and D<sub>5</sub>. The flyback transformer also starts to store energy in this mode. Figure 2.3 (Mode 3) shows the equivalent circuit of this mode with switch S<sub>c</sub> turned on. It should be noted that S<sub>c</sub> can be turned on and off at any time during the switching period to discharge C<sub>c</sub>. At the end of this mode the voltage

across the clamping capacitor is  $V_{cmin}$ . The voltage across clamping capacitor and the current through flyback switch can be expressed according to the following equations:

$$L_m \frac{di_{L_m}(t)}{dt} - v_c(t) = 0$$

(2.17)

$$i_c(t) = i_{L_m}(t) = -C_c \frac{dv_c(t)}{dt}$$

(2.18)

where,

$L_m$ : magnetizing inductor of flyback transformer

$i_c(t)$ : the current through the clamping capacitor

$i_{L_m}(t)$ : the current through the magnetizing inductor of the flyback transformer

If the initial value of  $v_c(t)$  is defined as  $v_c(t) = V_{c_{max}}$  and the initial value of the current through the clamping capacitor is zero, the voltage across the capacitor and the current through it can be expressed as

$$V_c(t) = V_{cmax} \cos \omega_1 t \tag{2.19}$$

$$i_c(t) = i_{L_m}(t) = \frac{V_{c_{max}}}{Z_1} \sin \omega_1 t$$

(2.20)

where

$$\omega_1 = \frac{1}{\sqrt{L_m C_c}} \tag{2.21}$$

$$Z_1 = \sqrt{\frac{L_m}{C_c}} \tag{2.22}$$

At the end of this mode, the voltage across the clamping capacitor is regulated to desired value  $V_{cmin}$ , which is just slightly higher than the primary voltage of the main transformer,  $(V_{C_{min}} \approx \overline{V_o})$ , where  $\overline{V_o}$  is the primary voltage across the main transformer. By substituting in (2.19), the duration of this mode (t<sub>3</sub>-t<sub>2</sub>) can be expressed as

$$t_3 - t_2 = \frac{1}{\omega_1} \cos^{-1} \left( \frac{V_{c_{min}}}{V_{c_{max}}} \right)$$

(2.23)

By using (2.16)

$$t_{3} - t_{2} = C_{c} Z_{1} \cos^{-1} \left( \frac{\overline{V_{o}}}{\overline{V_{o}} + \frac{I_{in}}{2} Z_{o}} \right)$$

(2.24)

where

$$\omega_1 = \frac{1}{C_c Z_1} \tag{2.25}$$

The duration of this mode determines how much the auxillary switch will be turned on, thus the duty cycle for the flyback converter can be determined to be

$$D_f = \frac{t_3 - t_2}{T_{sf}} = (t_3 - t_2)f_{sf} = f_{sf} C_c Z_1 cos^{-1} \left(\frac{\overline{V_o}}{\overline{V_o} + \frac{I_{in}}{2}Z_o}\right)$$

(2.26)

*Mode 4* [ $t_3 < t < t_4$ ]: At t = t<sub>3</sub>, the flyback switch is turned off. The energy stored in the flyback transformer is transferred to the output. Note that the main switches have the same on/off state as in the previous mode and that this mode has been included to show how the circuit operates when switch S<sub>c</sub> is turned off. This mode can happen at any time during the switching period.