### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2008

# A versatile, scalable, and open memory architecture in CMOS 0.18 $\mu\text{m}$

Karl Leboeuf University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Leboeuf, Karl, "A versatile, scalable, and open memory architecture in CMOS 0.18  $\mu$ m" (2008). *Electronic Theses and Dissertations*. 8251.

https://scholar.uwindsor.ca/etd/8251

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### A Versatile, Scalable, and Open Memory Architecture in CMOS $0.18 \mu m$

by

### Karl Leboeuf

### A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2008

### Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada

### Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-47093-0 Our file Notre référence ISBN: 978-0-494-47093-0

### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### © 2008 Karl Leboeuf

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

### Declaration of Originality

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material

from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

iv

### Abstract

A lookup table is a permanent memory storate element in which every stored value corresponds to a unique address. Range addressable lookup tables differ in that every stored value corresponds to a *range* of addresses. This type of memory has important applications in a recently proposed central processing unit which employs a multi-digit logarithmic number system that is well suited for digital signal processing applications.

This thesis details the work done to improve range addressable lookup tables in terms of operating speed and area utilization. Two range addressable lookup table designs are proposed. Ideal design parameters are determined. An integrated circuit test platform is proposed to determine the real-world ability of these lookup tables. A case study exploring how non-linear functions can be approximated with range addressable lookup tables is presented.

v

This work is dedicated to many teachers in my life who have helped shape me into what I am today.

### A cknowledgments

I would like to express my sincere thanks and appreciation to Dr. Roberto Muscedere for his support and guidance throughout the progress of this thesis. In addition, I would also like to thank Mr. Ashkan Hosseinzadeh Namin, Ms. Christine Koncan and my family for their unending help and support.

## Contents

| D             | eclar | ation ( | of Originality                         |               |         |         |       | iv   |

|---------------|-------|---------|----------------------------------------|---------------|---------|---------|-------|------|

| A             | bstra | ıct     |                                        |               |         |         |       | v    |

| D             | edica | tion    |                                        |               |         |         |       | vi   |

| A             | cknov | wledgr  | ments                                  |               |         |         |       | vii  |

| $\mathbf{Li}$ | st of | Figur   | es                                     |               |         |         |       | xiii |

| $\mathbf{Li}$ | st of | Table   | 28                                     |               |         |         |       | xvi  |

| $\mathbf{Li}$ | st of | Abbro   | eviations                              |               |         | ×       |       | xvii |

| 1             | Intr  | oduct   | ion                                    |               |         |         |       | 1    |

| 2             | Bac   | kgrou   | nd                                     |               |         |         |       | 5    |

|               | 2.1   | Looku   | ıp Tables                              |               |         | <br>    |       | . 5  |

|               | •     | 2.1.1   | Lookup Table Implementation            |               |         | <br>    |       | . 6  |

|               | 2.2   | A Bri   | ef Review of Domino Logic              |               |         | <br>    |       | . 9  |

|               |       | 2.2.1   | Static CMOS Logic                      |               |         | <br>    |       | . 9  |

|               |       | 2.2.2   | Domino Logic                           |               |         | <br>    |       | . 11 |

|               |       | 2.2.3   | Range Addressable Lookup Tables        |               |         | <br>    | <br>• | . 13 |

| 3             | The   | Rang    | ge Addressable Lookup Table Architectu | $\mathbf{re}$ |         |         |       | 15   |

|               | 3.1   | RALU    | JT Architecture Overview               |               |         | <br>    | <br>• | . 15 |

|               | 3.2   | The A   | Address Decoder                        |               |         | <br>    |       | . 15 |

|               |       | 3.2.1   | Overview of the Beginning Stage        |               | • • • • | <br>••• |       | . 16 |

#### CONTENTS

|   |      | 3.2.2            | The Address Compare Pull-Down Network                                                 | 19 |

|---|------|------------------|---------------------------------------------------------------------------------------|----|

|   |      | 3.2.3            | Overview of the Middle Stage                                                          | 20 |

|   |      | 3.2.4            | Overview of the Final Stage                                                           | 20 |

|   |      | 3.2.5            | Detailed Example of the RALUT Address Decoder                                         | 21 |

|   | 3.3  | Overv            | iew of the Word Lines                                                                 | 24 |

|   | 3.4  | Addre            | ss and Clock Buffering Overview                                                       | 24 |

| 4 | Pro  | $\mathbf{posed}$ | VLSI Implementations in CMOS $0.18 \mu m$                                             | 25 |

|   | 4.1  | Existi           | ng CMOS $0.35 \mu m$ Design                                                           | 26 |

|   |      | 4.1.1            | Selecting an Updated Technology Node                                                  | 26 |

|   | 4.2  | Desig            | n Rescaling                                                                           | 27 |

|   | 4.3  | Propo            | sed CMOS $0.18 \mu m$ Implementation                                                  | 28 |

|   |      | 4.3.1            | Transistor Sizing for the CMOS $0.18 \mu m$ Implementation                            | 28 |

|   | 4.4  | The H            | ligh Performance CMOS $0.18 \mu m$ Implementation                                     | 28 |

|   |      | 4.4.1            | High Performance CMOS $0.18 \mu m$ Implementation Design Goals $\ldots \ldots \ldots$ | 29 |

|   |      | 4.4.2            | Transistor Channel Length                                                             | 29 |

|   |      | 4.4.3            | Keeper Widths                                                                         | 30 |

|   |      | 4.4.4            | NMOS Chain Scaling                                                                    | 30 |

|   |      | 4.4.5            | Transistor Widths                                                                     | 31 |

|   |      | 4.4.6            | High Performance CMOS $0.18 \mu m$ RALUT Test Circuits                                | 31 |

|   |      | 4.4.7            | High Performance Implementation Test Circuit Results and Final Transistor             |    |

|   |      |                  | Sizing                                                                                | 34 |

|   |      | 4.4.8            | Proposed High Performance Design Layout Improvements                                  | 44 |

|   | 4.5  | Result           | s of the CMOS $0.18 \mu m$ and High Performance CMOS $0.18 \mu m$ Designs $\ldots$    | 46 |

|   | 4.6  | Summ             | ary                                                                                   | 47 |

| 5 | Inte | grated           | l Circuit Test Platform Design                                                        | 50 |

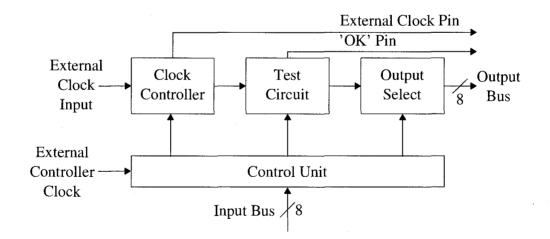

|   | 5.1  | Test I           | C Overview and Testing Strategy                                                       | 51 |

|   | 5.2  | The C            | lock Controller Circuit                                                               | 52 |

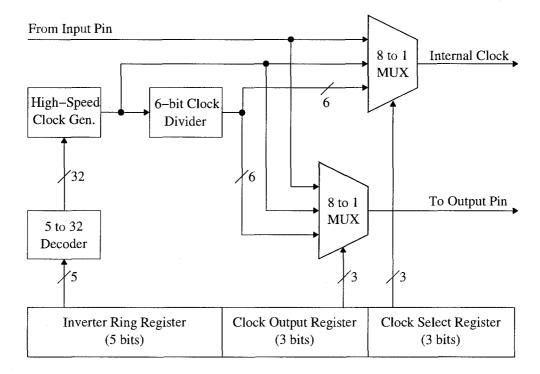

|   | 5.3  | Intern           | al High-Speed Clock Generation Circuit                                                | 53 |

|   |      | 5.3.1            | Phase-Locked Loops                                                                    | 53 |

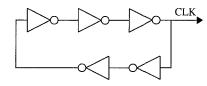

|   |      | 5.3.2            | Inverter Ring                                                                         | 53 |

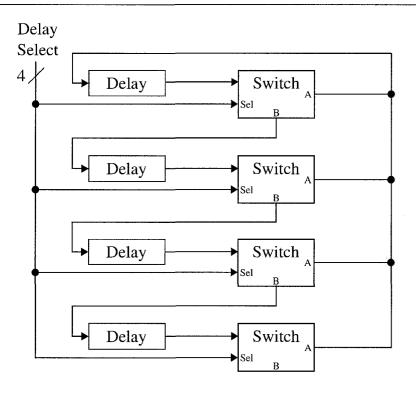

|   |      | 5.3.3            | Inverter Ring Design                                                                  | 54 |

|   |      | 5.3.4            | Proposed Inverter Ring Design Specifications and Simulation Results                   | 56 |

#### CONTENTS

|   | 5.4                  | Test, and Output Select Circuits                                                 | 58 |

|---|----------------------|----------------------------------------------------------------------------------|----|

|   |                      | 5.4.1 Range Addressable Lookup Table Selection                                   | 61 |

|   |                      | 5.4.2 Automatic Test Pattern Generator                                           | 62 |

|   | 5.5                  | The Control System                                                               | 62 |

|   | 5.6                  | Hardware Synthesis                                                               | 64 |

|   | 5.7                  | Simulation                                                                       | 64 |

|   |                      | 5.7.1 Design Rule Check                                                          | 66 |

|   | 5.8                  | IC Design                                                                        | 67 |

|   | 5.9                  | Test IC Summary and Results                                                      | 67 |

| 6 | $\operatorname{Cas}$ | e Study: Range Addressable Lookup Tables in Artificial Neural Networks           | 70 |

|   | 6.1                  | Artificial Neural Networks and Activation Functions                              | 71 |

|   | 6.2                  | A Brief Review of Different Hyperbolic Tangent Function Implementations          | 72 |

|   |                      | 6.2.1 Piecewise Linear Approximation                                             | 72 |

|   |                      | 6.2.2 Lookup Table Approximation                                                 | 72 |

|   |                      | 6.2.3 Hybrid Methods                                                             | 73 |

|   | 6.3                  | Lookup Table Implementation of the Hyperbolic Tangent Function                   | 74 |

|   | 6.4                  | Range Addressable Lookup Table Implementation of the Hyperbolic Tangent Function | 74 |

|   | 6.5                  | Results and Comparison                                                           | 75 |

|   | 6.6                  | Comparison of Different Hardware Implementations                                 | 76 |

|   | 6.7                  | Comparison to FPGA Implementations                                               | 76 |

|   | 6.8                  | Summary                                                                          | 78 |

| 7 | Cor                  | clusions and Future Work                                                         | 79 |

|   | 7.1                  | Conclusions                                                                      | 79 |

|   | 7.2                  | Future Work                                                                      | 80 |

| A | Fina                 | al Transistor Sizing                                                             | 81 |

| в | Ver                  | ilog Code                                                                        | 83 |

|   | B.1                  | Verilog Modules                                                                  | 83 |

|   |                      | B.1.1 Automatic Test Pattern Generator                                           | 83 |

|   |                      | B.1.2 Clock Wrapper                                                              | 84 |

|   |                      | B.1.3 Compare Module                                                             | 84 |

|   |                      | B.1.4 Controller                                                                 | 85 |

|              |                | B.1.5   | n-bit Counter                                                                                                   | 86  |

|--------------|----------------|---------|-----------------------------------------------------------------------------------------------------------------|-----|

|              |                | B.1.6   | Data-out Selector                                                                                               | 86  |

|              |                | B.1.7   | n-bit Decoder                                                                                                   | 87  |

|              |                | B.1.8   | Input Module                                                                                                    | 87  |

|              |                | B.1.9   | Memory Module                                                                                                   | 88  |

|              |                | B.1.10  | n-to-1 Multiplexer                                                                                              | 88  |

|              |                | B.1.11  | n-wide n-to-1 Multiplexer                                                                                       | 88  |

|              |                | B.1.12  | OK Signal Indicator                                                                                             | 89  |

|              |                | B.1.13  | Output Controller                                                                                               | 90  |

|              |                | B.1.14  | HDL Ralut Module                                                                                                | 90  |

|              |                | B.1.15  | Test Circuit                                                                                                    | 91  |

|              |                | B.1.16  | Power Toggle                                                                                                    | 92  |

|              |                | B.1.17  | System Wrapper                                                                                                  | 92  |

|              | B.2            | Verilog | g Test Benches                                                                                                  | 93  |

|              |                | B.2.1   | Compare Module Test Bench $\ldots \ldots \ldots$ | 93  |

|              |                | B.2.2   | Clock Wrapper Test Bench                                                                                        | 94  |

|              |                | B.2.3   | Controller Test Bench                                                                                           | 96  |

|              |                | B.2.4   | OK Signal Test Bench                                                                                            | 97  |

|              |                | B.2.5   | Test Circuit Test Bench                                                                                         | 97  |

|              |                | B.2.6   | Power Toggle Test Bench                                                                                         | 99  |

| $\mathbf{C}$ | Mat            | lab Co  | ode                                                                                                             | 101 |

|              | C.1            | Matlah  | b.m Files                                                                                                       | 101 |

|              |                | C.1.1   | RALUT Point Generator                                                                                           | 101 |

|              |                | C.1.2   | Sigmoid Function                                                                                                | 103 |

| D            | Lay            | outs fo | or the $0.35 \mu m$ , $0.18 \mu m$ , and High Performance $0.18 \mu m$ Designs                                  | 104 |

| E            | $\mathbf{Syn}$ | opsys 1 | Files                                                                                                           | 111 |

|              | E.1            | Verilog | g .v Files                                                                                                      | 111 |

|              |                | E.1.1   | Synopsys .dc Setup                                                                                              | 111 |

|              |                | E.1.2   | Clock Controller Script                                                                                         | 111 |

|              |                | E.1.3   | Test Circuit Script                                                                                             | 112 |

|              |                | E.1.4   | RALUT Wrapper Script                                                                                            | 112 |

| References    | 113 |

|---------------|-----|

| VITA AUCTORIS | 115 |

# List of Figures

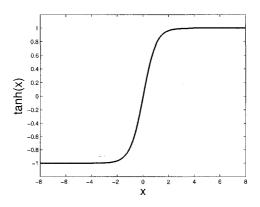

| 1.1  | The Hyperbolic Tangent Function                                                                | 2  |

|------|------------------------------------------------------------------------------------------------|----|

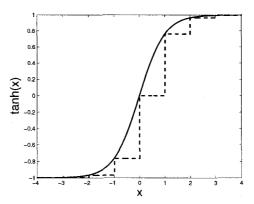

| 1.2  | Lookup Table Approximation of $tanh(x)$ with Eight Points $\ldots \ldots \ldots \ldots \ldots$ | 3  |

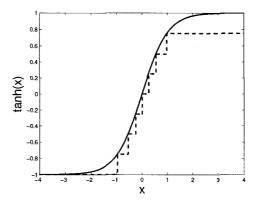

| 1.3  | Range Addressable Lookup Table Approximation of $\tanh(x)$ with Eight Points $\ . \ .$         | .3 |

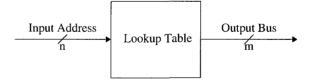

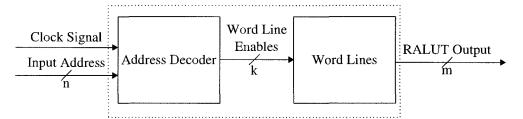

| 2.1  | Lookup Table Block Diagram                                                                     | 5  |

| 2.2  | Lookup Table Internal Block Diagram                                                            | 7  |

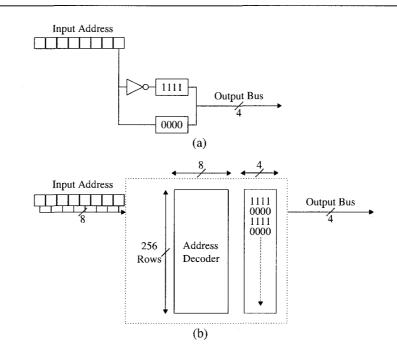

| 2.3  | Hardware Compiler Result (a) Compared with ROM Implementation (b)                              | 8  |

| 2.4  | Schematic for a 2-Input, Static CMOS NAND Gate                                                 | 10 |

| 2.5  | A Domino Logic 2-Input NAND Gate                                                               | 11 |

| 2.6  | A Domino Logic 2-Input NAND Gate, with Keeper Transistor                                       | 12 |

| 2.7  | Block Diagram of the RALUT, with $n$ Address Bits, $m$ Output Bits, and $k$ Rows               | 13 |

| 2.8  | RALUT (a) and LUT (b) Architectures                                                            | 14 |

| 3.1  | Block Diagram of the RALUT, with $n$ Address Bits, $m$ Output Bits, and $k$ Rows               | 16 |

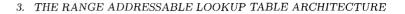

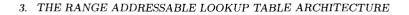

| 3.2  | Block Diagram of a Five Row, Five Stage RALUT Address Decoder                                  | 17 |

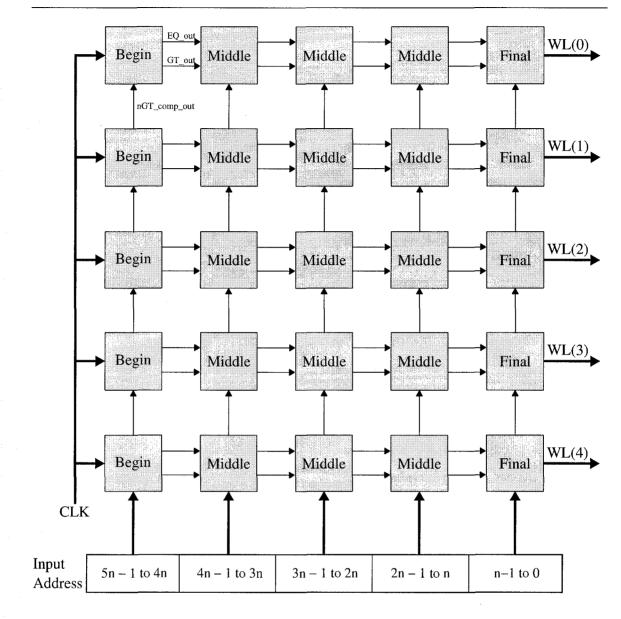

| 3.3  | Block Diagram of the Beginning Stage                                                           | 17 |

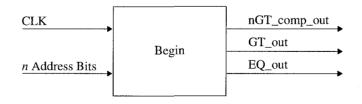

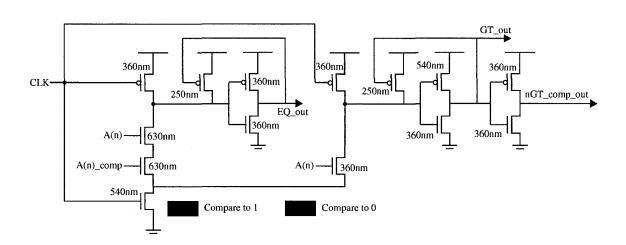

| 3.4  | Schematic of the Begin Stage                                                                   | 18 |

| 3.5  | An Example Pull-Down Network for a 4-Bit Address Decode Stage Comparing to                     |    |

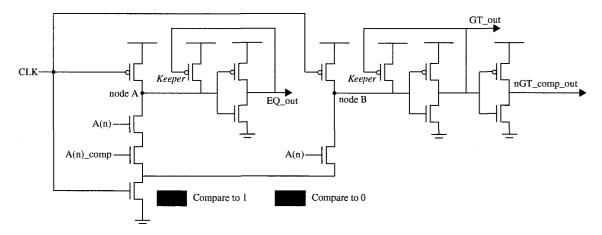

|      | "1100"                                                                                         | 19 |

| 3.6  | Block Diagram of the Middle Stage                                                              | 20 |

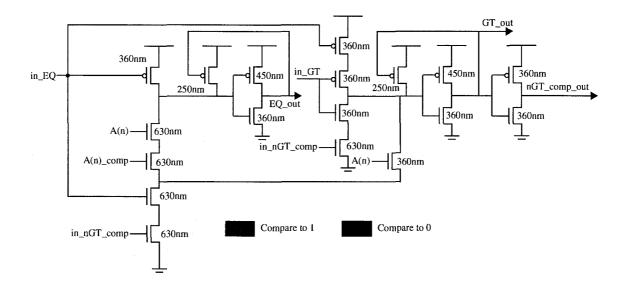

| 3.7  | Schematic of the <i>Middle</i> Stage                                                           | 21 |

| 3.8  | Block Diagram of the Final Stage                                                               | 21 |

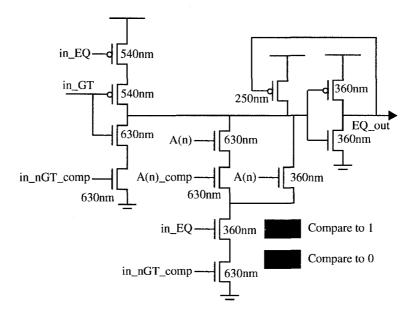

| 3.9  | Schematic of the Final Stage                                                                   | 22 |

| 3.10 | Example of a 5 Row, 12-bit, 4 Stage RALUT Address Decoder Evaluating                           | 23 |

LIST OF FIGURES

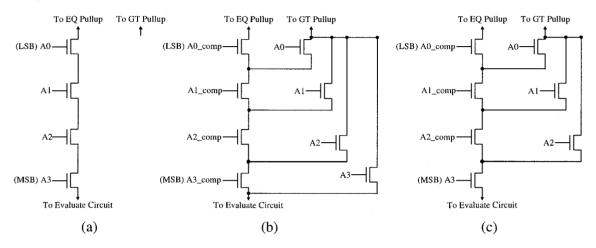

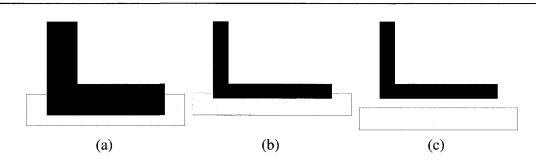

| 4.1  | Pull-Down Networks Used in Test Circuits: (a) '1111', (b) '0000', (c) '1000'                                                                        | 32 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

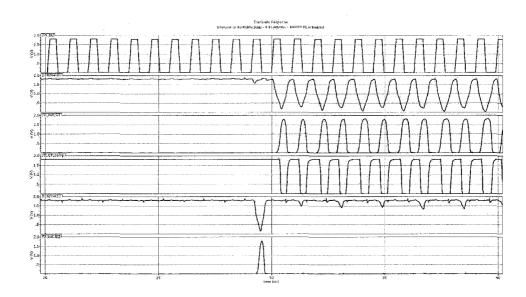

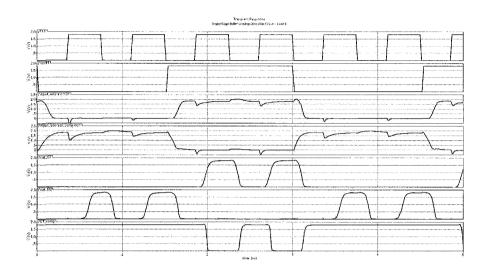

| 4.2  | Simulation Waveforms for the Beginning Address Decode Stage. From top to bottom:                                                                    |    |

|      | clock signal, GT Critical Node, GT_out, GT_out_comp, EQ Critical Node, EQ_out $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ .                         | 35 |

| 4.3  | Simulation Waveforms for the Middle Address Decode Stage with EQ Enabled. From                                                                      |    |

|      | top to bottom: clock signal, GT Critical Node, GT_out, GT_out_comp, EQ Critical                                                                     |    |

|      | Node, EQ_out                                                                                                                                        | 38 |

| 4.4  | Simulation Waveforms for the Middle Address Decode Stage with GT Enabled. From                                                                      |    |

|      | top to bottom: clock signal, GT Critical Node, GT_out, GT_out_comp, EQ Critical                                                                     |    |

|      | Node, EQ_out                                                                                                                                        | 38 |

| 4.5  | Simulation Waveforms for the Final Address Decode Stage with EQ Enabled. From                                                                       |    |

|      | top to bottom: clock signal, GT Critical Node, GT_out, GT_out_comp, EQ Critical                                                                     |    |

|      | Node, EQ_out $\ldots \ldots \ldots$ | 40 |

| 4.6  | Simulation Waveforms for the Final Address Decode Stage with GT Enabled. From                                                                       |    |

|      | top to bottom: clock signal, GT Critical Node, GT_out, GT_out_comp, EQ Critical                                                                     |    |

|      | Node, EQ_out                                                                                                                                        | 40 |

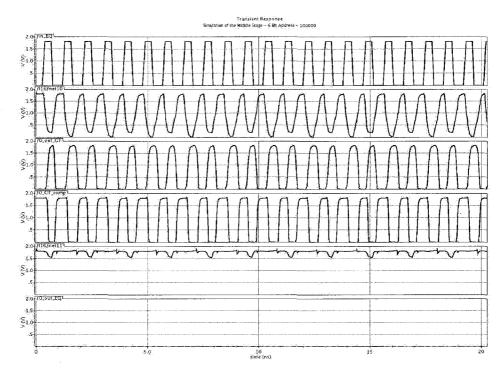

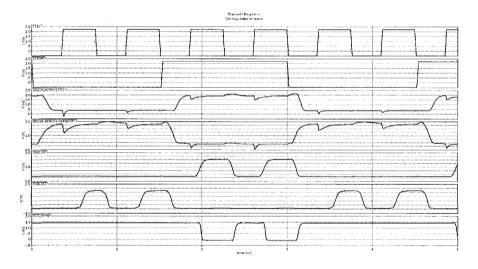

| 4.7  | Single-Stage Buffer Driving 8 Rows From Top to Bottom: Clock, Buffer Input, Buffer                                                                  |    |

|      | Output, Buffer's Complemented Output, Stage's Output Signals EQ_out, GT_out,                                                                        |    |

|      | and nGT_out_comp                                                                                                                                    | 43 |

| 4.8  | Two-Stage Buffer Driving 8 Rows From Top to Bottom: Clock, Buffer Input, Buffer                                                                     |    |

|      | Output, Buffer's Complemented Output, Stage's Output Signals EQ_out, GT_out,                                                                        |    |

|      | and nGT_out_comp                                                                                                                                    | 43 |

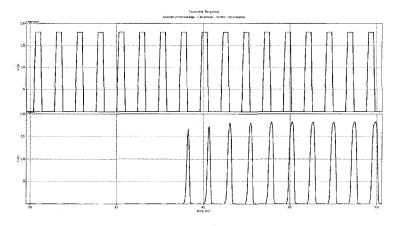

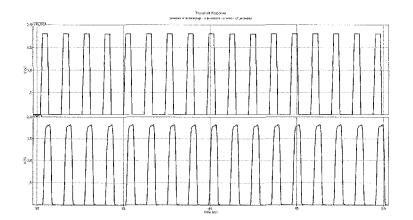

| 4.9  | Simulation Waveforms for the Linedriver Driving 48 Bits, From Top to Bottom: Row                                                                    |    |

|      | 1 Enable Signal, Row 1 Enable Signal Comp, Row 2 Enable Signal, Row 2 Enable                                                                        |    |

|      | Signal Comp, Sample Output Line                                                                                                                     | 44 |

| 4.10 | Overlapping Wires Creating Parasitic Capacitances: (a) Original Placement, (b) Re-                                                                  |    |

|      | duced Overlap Area, (c) Ideal Placement                                                                                                             | 47 |

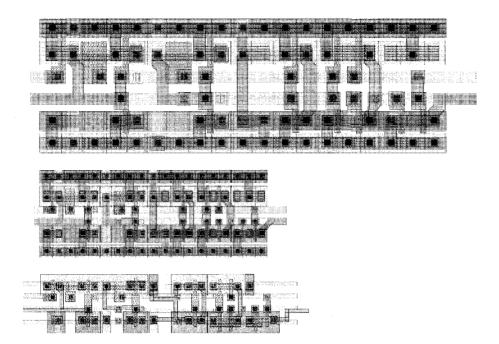

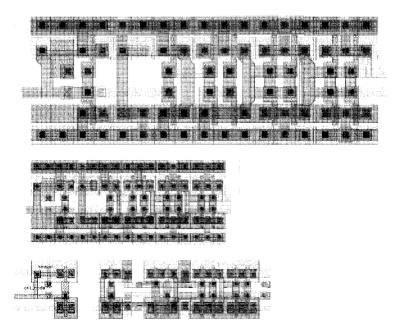

| 4.11 | RALUT Layout Comparison for CMOS $0.35 \mu m$ design (top), CMOS $0.18 \mu m$ design                                                                |    |

|      | (middle), and a<br>rea-reduced, high-performance CMOS $0.18 \mu m$ design (bottom) $~$                                                              | 48 |

| 5.1  | Block Diagram of the IC Subsystems                                                                                                                  | 51 |

| 5.2  | The Clock Selection Circuit Block Diagram                                                                                                           | 52 |

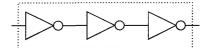

| 5.3  | A 5-Stage Inverter Ring                                                                                                                             | 53 |

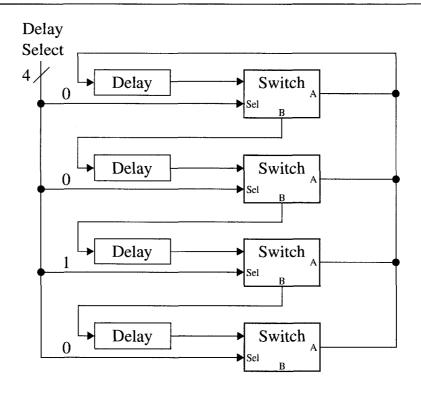

| 5.4  | Inverter Ring with Four Delay Settings                                                                                                              | 55 |

| 5.5  | A Three-Inverter Delay Block                                                                                                                        | 55 |

|      |                                                                                                                                                     |    |

#### LIST OF FIGURES

| 5.6  | Inverter Ring Example Using Control Word "0010"                                                | 56  |

|------|------------------------------------------------------------------------------------------------|-----|

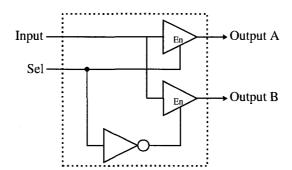

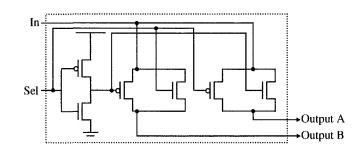

| 5.7  | Schematic for the Switch Block                                                                 | 56  |

| 5.8  | Transistor Schematic for the Switch Block                                                      | 57  |

| 5.9  | Layout for the Switch Block                                                                    | 57  |

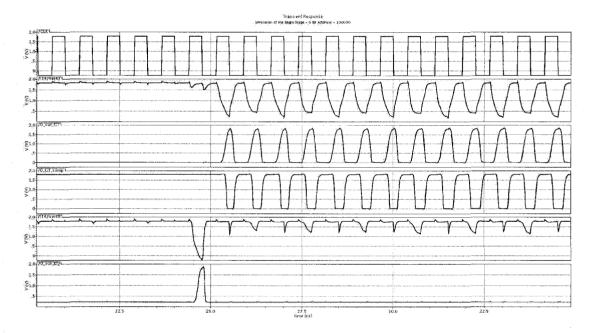

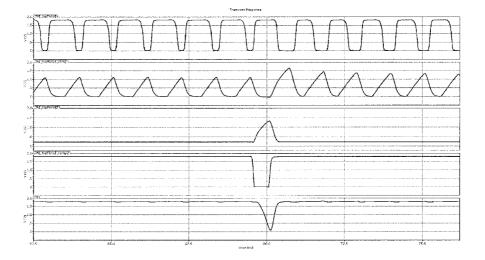

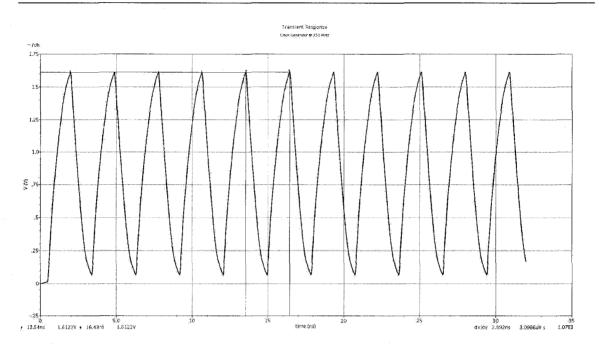

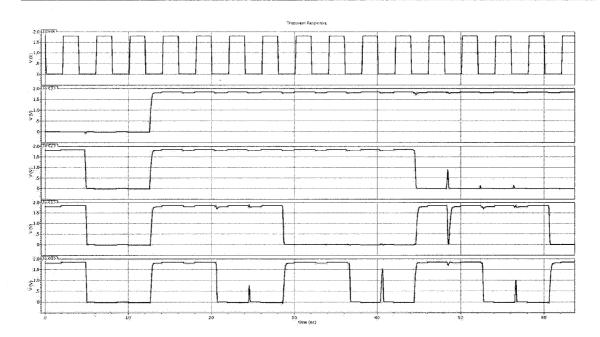

| 5.10 | Simulation Waveform for the Ring Oscillator @ 350 MHz                                          | 58  |

| 5.11 | Simulation Waveform for the Ring Oscillator @ 200 MHz                                          | 58  |

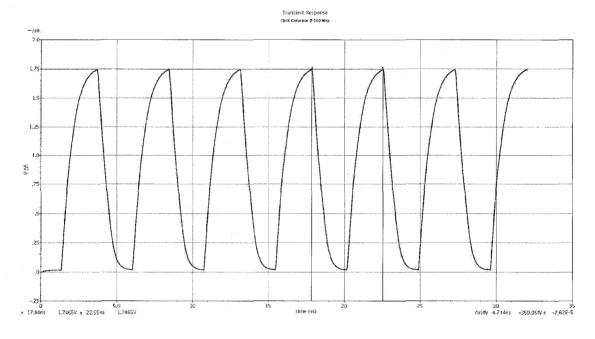

| 5.12 | Simulation Waveform for the Ring Oscillator @ 75 MHz                                           | 59  |

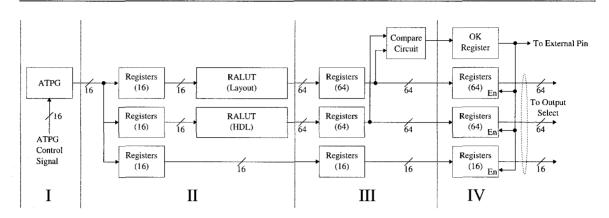

| 5.13 | Test Circuit Block Diagram With Pipelining                                                     | 60  |

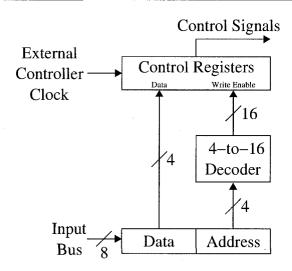

| 5.14 | The IC Register-Based Control System and Input Word                                            | 64  |

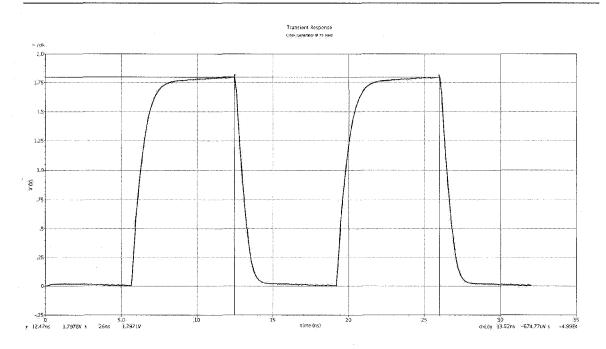

| 5.15 | Simulation Waveforms for the RALUT, from Top to Bottom: Clock Signal, Output                   |     |

|      | Line 3, 2, 1, and $0$                                                                          | 66  |

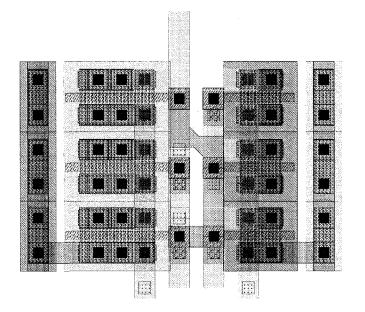

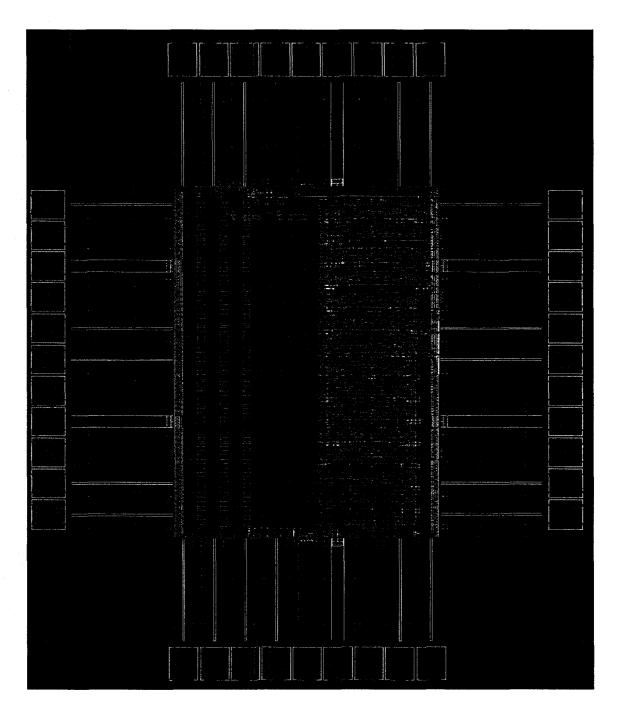

| 5.16 | Complete IC Layout                                                                             | 68  |

| 5.17 | Close-Up View of the IC Core                                                                   | 69  |

|      |                                                                                                |     |

| 6.1  | The Hyperbolic Tangent Activation Function                                                     | 71  |

| 6.2  | Piecewise Linear Approximation of $tanh(x)$ with Five Segments                                 | 73  |

| 6.3  | Lookup Table Approximation of $tanh(x)$ with Eight Points $\ldots \ldots \ldots \ldots \ldots$ | 73  |

| 6.4  | Range Addressable Lookup Table Approximation of $\tanh(x)$ with Eight Points $\ . \ .$         | 75  |

| A.1  | Beginning Stage Final Transistor Sizing                                                        | 81  |

| A.2  | Middle Stage Final Transistor Sizing                                                           | 82  |

| A.3  | Final Stage Final Transistor Sizing                                                            | 82  |

|      |                                                                                                |     |

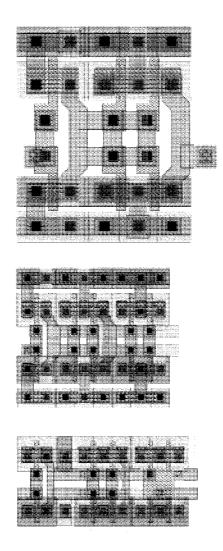

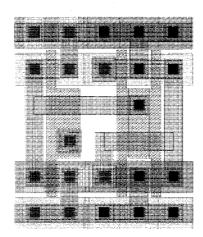

| D.1  | Begin Address Decode Stage Layouts                                                             | 105 |

| D.2  | Middle Address Decode Stage Layouts                                                            | 106 |

| D.3  | Final Address Decode Stage Layouts                                                             | 106 |

| D.4  | Output Bits Layouts, First Row: '0', '1' Second Row: '0', 1' Third Row: '00', '01',            |     |

|      | ·10', ·11'                                                                                     | 107 |

| D.5  | Address Compare Bits From Left to Right: '0' and ''1                                           | 108 |

| D.6  | Linedriver Layouts                                                                             | 109 |

| D.7  | Buffer Layouts                                                                                 | 110 |

# List of Tables

| 2.1  | The NAND Function Input and Output Behaviour                                            | 9  |

|------|-----------------------------------------------------------------------------------------|----|

| 4.1  | Transistor Length and Width Scaling Factors                                             | 27 |

| 4.2  | Beginning Stage Test Circuit Simulation Results in Picoseconds (ps)                     | 36 |

| 4.3  | Summary of Beginning Stage Worst Case Delay and Delay Per Address Bit, Results          |    |

|      | in Picoseconds (ps)                                                                     | 37 |

| 4.4  | Middle Stage Test Circuit Simulation Results in Picoseconds (ps)                        | 39 |

| 4.5  | Summary of Middle Stage Worst Case Delay and Delay Per Address Bit, Results in          |    |

|      | Picoseconds (ps)                                                                        | 39 |

| 4.6  | Final Stage Test Circuit Simulation Results                                             | 41 |

| 4.7  | Summary of Final Stage Worst Case Delay and Delay Per Address Bit, Results in           |    |

|      | Picoseconds (ps)                                                                        | 41 |

| 4.8  | Buffer Test Circuit Results in Picoseconds (ps)                                         | 42 |

| 4.9  | Output Bit Chain Length Test Circuit Simulation Results in Picoseconds (ps)             | 44 |

| 4.10 | Area and Critical Path Delay Comparison for a 16-bit Input, 52-bit Output, 29 Row       |    |

|      | RALUT                                                                                   | 47 |

| 5.1  | 4-Bit LFSR Output States                                                                | 63 |

| 5.2  | Control Unit Signals                                                                    | 63 |

| 6.1  | Complexity comparison of different implementations for 0.04 maximum error               | 75 |

| 6.2  | Complexity comparison of different implementations for 0.02 maximum error $\ . \ . \ .$ | 76 |

| 6.3  | Complexity comparison of different implementations for $0.02$ maximum error, includ-    |    |

|      | ing FPGA implementations                                                                | 78 |

# List of Abbreviations

| ASIC                  | Application Specific Integrated Circuit             |

|-----------------------|-----------------------------------------------------|

| ATPG                  | Automatic Test Pattern Generator                    |

| $\operatorname{BIST}$ | Built-In Self Test                                  |

| CAD                   | Computer Aided Design                               |

| $\operatorname{CMC}$  | Canadian Microelectronics Corporation               |

| CMOS                  | Complimentary Metal-Oxide-Semiconductor             |

| CPU                   | Central Processing Unit                             |

| DRC                   | Design Rule Check                                   |

| DSP                   | Digital Signal Processing                           |

| $\mathbf{FET}$        | Field-Effect Transistor                             |

| $\mathbf{FPGA}$       | Field Programmable Gate Array                       |

| HDL                   | Hardware Description Language                       |

| IC                    | Integrated Circuit                                  |

| IEEE                  | Institute of Electrical and Electronics Engineers   |

| $\mathbf{LFSR}$       | Linear Feedback Shift Register                      |

| LUT                   | Lookup Table                                        |

| MDLNS                 | Multi-Dimensional Logarithmic Number System         |

| MOSFET                | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| MSE                   | Mean Squared Error                                  |

| MUX                   | Multiplexer                                         |

| NAND                  | Not-AND                                             |

| NMOS                  | n-Channel MOSFET                                    |

| PMOS                  | p-Channel MOSFET                                    |

| RALUT                 | Range Addressable Lookup Table                      |

| $\operatorname{RAM}$  | Random Access Memory                                |

| ROM                   | Read Only Memory                                    |

| SPICE                 | Simulation Program with Integrated Circuit Emphasis |

| TLNS                  | Two-Digit Logarithmic Number System                 |

| TSMC                  | Taiwan Semiconductor Manufacturing Company          |

| VHDL                  | VHSIC Hardware Description Language                 |

| VHSIC                 | Very High Speed Integrated Circuit                  |

| VLSI                  | Very Large Scale Integration                        |

|                       |                                                     |

### Chapter 1

### Introduction

Since the first integrated circuit was successfully created in September of 1958, fabrication technology has been constantly advancing; transistors become increasingly small, allowing for faster designs at lower costs. The steady progress of miniaturization has continued almost unimpeded for fifty years until recently. As transistor sizes approach atomic sizes, numerous problems begin to arise and researchers must look elsewhere for performance improvements. Investigation into new types of digital computer architectures is one approach researchers are taking to continue to advance the state of the art of the integrated circuit.

Among these new architectures are processors which employ exotic number systems that excel in performing certain mathematical operations, such as multiplication, division and exponentiation [4], [5]. These are important operations for many digital signal processing applications, such as in a hearing aid processor, and in digital filtering [6], [15], [7]. The multi-digit logarithmic number system has recently been proposed for such purposes, and a processor employing this number system has been designed; the two-digit logarithmic number system CPU [2]. This processor is able to quickly and efficiently perform digital signal processing instructions, however it is reliant on the use of range addressable lookup tables to perform certain crucial operations, including conversion to and from binary [14].

Lookup tables, or LUTs, are a common form of permanent memory used in many applications. Every LUT functions by giving it an input address, causing it to output a particular stored value. Every value stored in the LUT corresponds to a unique input address.

1

Range addressable lookup tables, or RALUTs, function similarly to LUTs, with one key difference. Every value that is stored in the RALUT corresponds to a *range* of input addresses. This difference allows the table size to be significantly reduced for many applications, particularly when approximating non-linear functions.

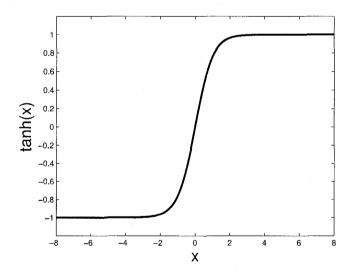

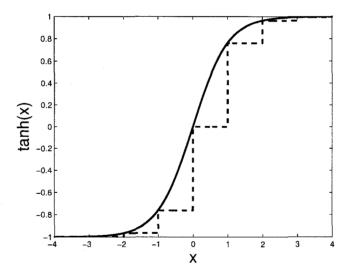

Consider, for example, the hyperbolic tangent function in Figure 1.1. It can be approximated with the use of a lookup table. The input to the lookup table is the quantized x-axis of the function, while the corresponding y-axis values are stored into the LUT, acting as outputs. Any degree of precision is possible, however more precision will require a larger table size. An example of a hyperbolic tangent function approximated by a LUT is shown in Figure 1.2. It is approximated with 8 values, and it can be seen that this is a poor approximation with very large error, particularly in the points close to the x-axis' origin. Notice that in a LUT, the stored values are evenly spaced across in input range.

Figure 1.1: The Hyperbolic Tangent Function

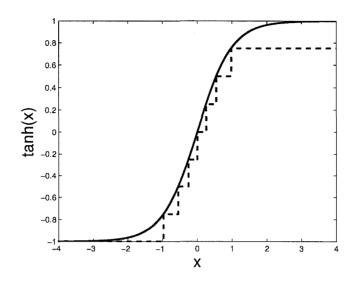

RALUTs were designed to excel at this type of task. Similar to the LUT approximation, they require the input address and stored output values to be quantized. RALUTs possess an important advantage in approximating this type of function, however; the stored y-values can be placed wherever the hardware designer wishes. This allows greater accuracy to be achieved with the same amount of points, as in Figure 1.3. This figure shows the same function being approximated with the same number of points, however the points are placed in a way such that the maximum error is minimized. The points are placed closely together when the function is changing rapidly near the origin, and further apart along the extremities where the function is hardly changing at all. Alternately, if the error in the LUT approximation was acceptable, an RALUT implementation with the same maximum error could be used with as few as 4 stored values, cutting the table size in half,

Figure 1.2: Lookup Table Approximation of tanh(x) with Eight Points

achieving a major area savings.

Figure 1.3: Range Addressable Lookup Table Approximation of tanh(x) with Eight Points

The focus of this thesis is to advance the state of the art of range addressable lookup tables. To achieve this, an existing RALUT design is rescaled to use a newer fabrication process, and then further enhanced, reducing its area utilization and increasing its operating speed. A test platform is proposed to allow real-world performance data to be collected. Finally, a new application for RALUTs is proposed in the area of artificial neural networks.

This thesis consists of seven chapters. In this first chapter, the issue being addressed is presented, and the structure of the remaining chapters is laid out. Chapter two provides pertinent background information. Chapter three presents the RALUT architecture in detail, while chapter four proposess two different RALUT designs along with their performance results. Chapter five details the creation of a test platform for RALUT memory designs, and chapter six describes the utility of RALUTs in the area of artificial neural networks. In the final chapter, concluding remarks, and suggestions for possible directions in future research in this are are made.

### Chapter 2

### Background

This chapter provides the reader important background information regarding lookup tables, a brief review of static CMOS, domino logic, as well as range addressable lookup tables.

### 2.1 Lookup Tables

Lookup tables, or LUTs are a form of non-volatile, read-only memory. They are often used in hardware design to store functions, and are desirable in applications that require high operating speeds. As shown in Figure 2.1, LUTs have two I/O ports, an input address bus and an output bus.

Figure 2.1: Lookup Table Block Diagram

In literature and in practice, LUTs are generally measured with two dimensions: address space and word size. The address space is defined by Equation 2.1; it is simply the number of different addresses that can be referred to by the input bus. For example, a LUT with a 10-bit input bus can refer to 1024 unique addresses.

$$Total Addresses = 2^{Address Bits}$$

(2.1)

The other defining parameter of the LUT, word size, is the width in bits of the output bus. Every stored word in memory is referred to by a unique address. Together, these two dimensions summarize the storage ability of the LUT, and the expression "address space  $\times$  word size" will be referred to as the size of the LUT.

#### 2.1.1 Lookup Table Implementation

#### **ROM Lookup Table Implementation**

Different techniques for implementing LUTs exist. One of the most common methods is ROM implementation, where the input addresses and output values are permanently stored into a hardware array. Important advantages of this approach are simplicity and predictability; given that the address space × word size parameters of the LUT remain constant, the specific words being stored into the LUT do not affect its area utilization or maximum operating speed. Additionally, it is worth mentioning that the only practical limitation of LUT size when using a ROM implementation is silicon area. These are a highly desirable qualities when designing digital systems that make use of LUTs.

One disadvantage of using a ROM array is that a proprietary tool called a "memory compiler" must be used in order to implement them in hardware. Such tools are expensive, and closed-source, meaning that the hardware designer does not have access to the internals of the ROM design. Furthermore, memory compilers are not necessarily versatile; a compiler that works for a CMOS  $0.35\mu m$  process may not function with a CMOS 90nm process.

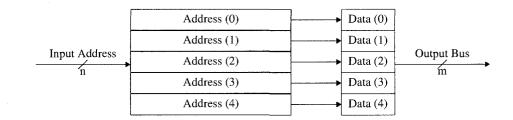

Another problem with ROM implementation is that they consume a very large area as the number of address bits increases. Figure 2.2 shows the internal workings of the ROM implementation of the LUT. It consists of an address decoder, which scales in size with the number of input bits, and the word lines, which scale in size with the number of output bits. Thus, the total area of a ROM LUT scales approximately with Equation 2.2. As the number of input bits increases, the area utilization increases dramatically, possibly rendering the ROM implementation of LUTs impractical for very large addresses.

$$LUT_{Area} \alpha \ 2^n \times (n+m) \tag{2.2}$$

Despite these shortcomings, skillful hardware designers have found a place for the ROM array

Input Address n 2<sup>n</sup> Rows 2<sup>n</sup> Rows 2<sup>n</sup> Rows 1 Note the state of the state of

implementation of LUTs in many different devices, including FPGAs, microcontrollers, and microprocessors.

Figure 2.2: Lookup Table Internal Block Diagram

#### Logic Synthesizer and Logic Gate Implementation

An alternative approach to implementing LUTs is to use a logic synthesizer, sometimes called a hardware compiler, to take the LUT's I/O characterisitcs, and implement it using logic gates. The benefit of implementing LUTs as a series of simple logic gates is that there is a high probability that the design can be simplified, yielding a large area reduction. The reason for this is that the hardware compiler carefully examines the specific I/O behaviour of a particular and "optimizes away" redundant logic. To demonstrate how a hardware compiler can optimize a design, the following explanation will refer to Figure 2.3.

Suppose a designer wanted, for whatever reason, to create a  $256 \times 4$  lookup table where every even address would place the bit pattern "1111" on the output bus, and "0000" for every odd address. Given this specific design, a hardware compiler would most likely only use the least significant bit to determine if the address were even or odd, and simply connect this signal to an inverter. Referring to Figure 2.3 part (a), when the address is even, the least significant bit is '0', and the address passes through an inverter and the first word line is enabled. Since the second word line receives the signal of '0', its contents are not placed on the output bus. The alternate situation occurs when an odd address is used and the least significant bit is '1'. This hardware compiler implementation would require (approximately) a few dozen transistors, while occupying a very tiny area, and operate at very high speeds. As seen in Figure 2.3 part (b), a ROM implementation would fill alternating word lines with these two patterns, occupying the entire  $256 \times 4$  ROM array, which is vastly more area

Figure 2.3: Hardware Compiler Result (a) Compared with ROM Implementation (b)

than the hardware compiler version.

While this expample is an ideal case, it does demonstrate the capability of the hardware compiler. Under most scenarios, such dramatic reductions are not possible, however area utilization *is* typically significantly less than with ROM implementations. The exact area utilization and operating speed depend heavily on the exact bit patterns used in the word lines of the LUT. This is a disadvantage for hardware designers, as precise timing and area information are unknown until the design is synthesized, and it is possible that small design changes made to the word lines will greatly affect these LUT attributes. Another disadvantage is that this approach is not feasible for very large LUT sizes. The processor and memory requirements of the logic synthesizer will increase to the point where a single workstation equipped with a large amount of RAM still requires days or even weeks to determine a gate-level design for the LUT.

This approach does not use a memory compiler, however it does require a standard cell library, and a logic synthesizer tool: a proprietary library and a commercial tool. It is a scalable design, in that any number of input bits, output bits, and rows can be used, with the only theoretical limit being the area utilization. Currently there are no known open source standard cell libraries, and a license for a hardware compiler is extremely expensive, however most digital hardware designers do have access to both of these.

### 2.2 A Brief Review of Domino Logic

Many different logic families exist for implementing logic gates; the building blocks of digital circuit design. The designs presented in this work make use of static CMOS, and domino-logic, a type of dynamic CMOS logic. The goal of this section is to provide a brief overview of these logic styles, and to impress the reader with a fundamental understanding of their mechanics, advantages, and disadvantages.

#### 2.2.1 Static CMOS Logic

Static CMOS is a very common logic style; it is used in almost every type of design [24]. In static CMOS, a direct, low impedance path exists from the output of the gate to either VDD or VSS. PMOS transistors act as the pull-up network, while NMOS transistors form a pull-down network. When the appropriate inputs arrive at the transistors' gates, the circuit evaluates, and the output node is either connected directly to either VDD or VSS.

#### A Static CMOS 2-input NAND Gate

For example, a static CMOS 2-input NAND gate is shown in Figure 2.4. It implements the function described by Table 2.2.1. The NMOS transistors connect the output directly to ground when both inputs A and B are equal to *logic 1*, forming the pull-down network. Similarly, when either (or both) of A or B are at *logic 0*, the PMOS transistors forming the pull-up network connect the output node directly to VDD.

| В | Output |

|---|--------|

| 0 | 1      |

| 1 | 1      |

| 0 | 1      |

| 1 | 0      |

|   | 0      |

Table 2.1: The NAND Function Input and Output Behaviour

#### **Static CMOS Properties**

Static CMOS logic gates are relatively easy to implement, and are not overly sensitive to loading. This is a highly desirable property, as it allows different static CMOS gates to be combined together

Figure 2.4: Schematic for a 2-Input, Static CMOS NAND Gate

with ease to form larger circuits. For this reason, standard cell libraries are composed of this type of logic gate.

Another important feature of static CMOS is near-zero static power consumption. Static power consumption refers to the power being consumed while the device is not switching. In other words, as long as the inputs to the logic gate remain constant, very little power is consumed. The reason why a small amount of power is still being consumed during this operating state is due to charge leakage; a physical phenomenon in which some of the charge carriers are able to "leak" through the transistor's gate oxide. This is not a major issue for fabrication processes larger than 90nm due to the relatively large oxide thickness, however when using fabrication technology at the 90nm node and beyond, this may become a greater concern.

Static CMOS gates do, on the other hand, consume switching power. This is due to the fact that when the gate's output is switching from *logic* 0 to *logic* 1, or vice-versa, both the pull-up network and pull-down network will be conducting current for a very short time interval. In other words, for a short instant (on the order of picoseconds), a short circuit from VDD to VSS is available. In addition to consuming power, this can generate noise, which may be an issue if there are analog circuits operating nearby.

One drawback to static CMOS, is the reliance on PMOS transistors to form the pull-up network. PMOS transistors rely on "holes", rather than electrons as their charge carriers, which are much slower [10]. It is for this reason that PMOS transistors must be significantly larger than an NMOS transistor in order to possess equivalent current drive capability. This results in greater area utilization and slower operating speeds compared to a logic style that relies more heavily on NMOS transistors.

### 2.2.2 Domino Logic

A dynamic logic gate is one in which the output is only valid for a short amount of time after the result is produced. [18] Athough this sounds quite restrictive, dynamic CMOS networks are useful for high-speed system design. Dynamic logic encompasses several different logic families, including domino logic.

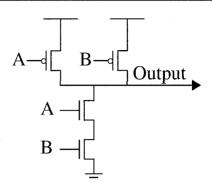

Domino logic uses a clock signal to "precharge" a node, and later "evaluate" the node via an NMOS pull-down network. It is best illustrated via an example, as in Figure 2.5.

Figure 2.5: A Domino Logic 2-Input NAND Gate

In this schematic, when the clock signal is at *logic* 0, the PMOS or "precharge" transistor in this case, pulls the critical node to *logic* 1. This node connects to the gate of the inverter, and the output of the gate at this point is *logic* 0. Also notice that at this time, the NMOS transistor connected to the clock signal, the "evaluate" transistor, is not currently conducting, eliminating any path to ground that the critical node may have had.

As time elapses, the clock makes the transition to logic 1, the precharge transistor stops conducting, while the evaluate transistor opens a path to ground through the NMOS pull-down network. At this point, one of two events may occur. If inputs A and B are both at logic 0, the pull-down network completes the path to ground from the critical node to the evaluate transistor, discharging the critical node, and bringing the gate output to logic 1. Alternately, if either of A or B are low, a path to ground does not exist, and the charge on the critical node remains. The gate output stays at logic 0.

Domino logic's many advantages over static CMOS stem from several facets of its design. First, only the faster NMOS transistors are used to evaluate the circuit, and the lack of a large pullup network greatly reduces parasitic capacitance, significantly enhancing operating speed. Second, power reduction is possible; there is never a short circuit from VDD to VSS as there is in static CMOS. Another advantage is the reduced area utilization made possible by only implementing the pull-down network as opposed to both pull-down and pull-up networks. For example, a 4-input NAND gate would require only two additional NMOS transistors than 2-input gate in Figure 2.5, whereas a static CMOS 4-input NAND gate would require four additional transistors: two NMOS and two PMOS.

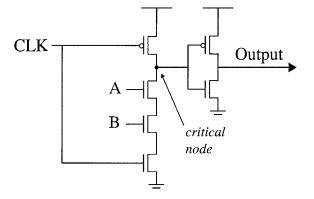

Despite these advantages, domino logic design presents a separate set of challenges. Domino gates are sensitive to charge leakage and charge sharing, and suffer from these effects. As described in the previous section, charge leakage is the physical phenomenon in which some of the charge leaks through the transistor's gate oxide. In addition to dissipating power and creating heat, this is particularly problematic in domino gates; if the charge at the critical node dissipates too rapidly, the output will become invalid. To eliminate this concern, an additional transistor is placed between VDD and the critical node, and controlled by the gate's output, as in Figure 2.6

Figure 2.6: A Domino Logic 2-Input NAND Gate, with Keeper Transistor

This transistor is referred to as the "keeper". Its role is to maintain charge on the critical node that would otherwise bleed away over time due to charge leakage [20]. It is a very weak transistor; it is deliberately sized so that it possesses low current drive. This is done to ensure that when the circuit legitimately attempts to discharge the critical node, the keeper does not overpower the pull-down network, reducing operating speeds.

The other domino logic concern, charge sharing, is the effect of all transistors attached to a common node contributing to the charge stored there. A larger amount of charge will require larger transistors, and more time to dissipate during the evaluate phase, reducing circuit performance. Hardware designers must be aware of this phenomenon, and carefully plan their designs around this problem. It is due to domino logic's sensitivity to this effect that limits its use to hand-designed circuits, rather than standard cell libraries.

### 2.2.3 Range Addressable Lookup Tables

RALUTs were originally proposed in [14] as an efficient way to implement certain non-linear, discontinuous functions used for number conversion as well as addition and subtraction in a multidimensional logarithmic number system (MDLNS) [16] The MDNLS number system is able to perform the multiplication, exponentiation, and devision operations with extreme efficiency, rendering its use extremely beneficial in certain applications such as DSP, cryptography, and multimedia processing. A primary concern of implementing a processor that employs this number system in hardware is number conversion to and from the binary number system, which is traditionally used extensively throughout most hardware designs. The conversion process is relatively time consuming unless some special hardware techniques are used. Lookup tables were proposed, however it was shown that they become very large in size as greater conversion accuracy is needed and a larger address space is required.

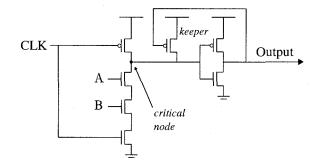

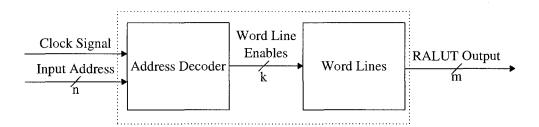

A block diagram showing the main components of the RALUT is shown in Figure 3.1. The architecture is divided into two main sections, the address decoder and the word lines. The input address is connected to the address decoder, and a single word line is enabled and palced on the output bus. There are only k rows, whereas in the LUT there are  $2^n$  rows. As will be shown, the number of rows in a RALUT is not dependent on the number of bits in the input address. Finally, it is worth noting the presence of a clock signal. Although the RALUT functions like a combinational logic circuit, due to its domino logic implementation it will require a clock.

Figure 2.7: Block Diagram of the RALUT, with n Address Bits, m Output Bits, and k Rows

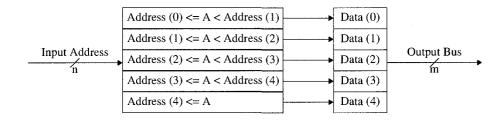

Range addressable lookup tables, or RALUTs, function very similarly to the LUTs described in the previous section. The key difference is that every stored value in a RALUT is referred to by a *range* of addresses, as opposed to a single, unique address, as in Figure 2.8. As shown in the figure, for a RALUT, every address is compared to the values stored in the address decoder. If the input address is larger than a given row, but smaller than the next, that word line is activated.

This architecture allows for a tremendous area savings when implementing specific types of non-

### (a) Lookup Table Architecture

### (b) Range Addressable Lookup Table Architecture

Figure 2.8: RALUT (a) and LUT (b) Architectures

linear and/or discontinuous functions. It is the RALUT's ability to span a large address space, while only using as many rows as are required that allows it to minimize area utilizaton and optimize speed. Equation 2.3 describes how the RALUT will scale in size with the design parameters n, m, and k.

$$RALUT_{Area} \ \alpha \ k \times (n+m) \tag{2.3}$$

### Chapter 3

# The Range Addressable Lookup Table Architecture

This chapter presents a detailed review of the architecture originally proposed in [14]. It begins by giving an overview of the design, and then expands on the individual components of which it is composed.

### 3.1 RALUT Architecture Overview

The RALUT is composed of two main parts; the address decoder, and the output rows. As shown in Figure 3.1, the RALUT uses three external signals. The *n*-bit wide input address and clock signal enter the address decoder portion of the architecture, which is responsible for triggering one of the k word lines. The word lines connect to the output rows, placing an output value on the m bit wide RALUT output bus.

### 3.2 The Address Decoder

At the heart of the RALUT is the address decoder. The address decoder architecture determines which output row to enable. This is performed by comparing the input address bits with the values that are permanently stored into the RALUT's address decoding array. The input address, and

Figure 3.1: Block Diagram of the RALUT, with n Address Bits, m Output Bits, and k Rows

consequently the decoding array, is divided up into groups and compared in stages. This is done to minimize the length of the the domino logic NMOS pulldown network, as long NMOS chains significantly reduce circuit performance. The number of stages used depends on the width of the input address, as well as the number of bits being evaluated by each stage. A block diagram of a five row, five stage RALUT address decoder is shown in Figure 3.2. Omitted for clarity are the input address lines connecting to every row, rather than only the last row as shown in the diagram.

Figure 3.2 also shows the signals emanating from each of the stages. These are used to control the evaluation of subsequent stages. Whenever possible, subsequent stages are prevented from evaluating in order to reduce power consumption due to transistor switching. There are two ways in which this is achieved. First, the EQ\_out and GT\_out signals act as clock signals for subsequent stages by controlling the precharge and evaluate transistors, later evaluation stages in the same row may be disabled. If, for example, EQ\_out does not make the logical transition from logic  $\theta$  to logic 1 in a given beginning stage, the subsequent stage's EQ circuit will not enter into an evaluation mode. The second technique employed to limit power consumption is the use of feedback from other rows. By having every row (except the last) use feedback from the next immediate row in the form of the nGT\_out\_comp signal. If the input address is greater than the stored value in the next, higher-addressed, row, it stands to reason that the input address must be greater than the current row, and that fully evaluating this entire row is redundant. By preventing as much redundant evaluation as possible, transistor switching and thus power consumption is reduced.

It is important to note that only the first stage of the address decoder is driven by the clock. Additional stages are driven by the EQ\_out and GT\_out signals, which will be further explained in the example at the end of this chapter.

#### 3.2.1 Overview of the Beginning Stage

A block diagram of the *beginning* stage is shown in Figure 3.3.

Figure 3.2: Block Diagram of a Five Row, Five Stage RALUT Address Decoder

Figure 3.3: Block Diagram of the Beginning Stage

The most significant n bits of the address are passed to every row of this stage. For every row, the *beginning* stage computes if the address bits being compared are greater than, or equal to its stored value. It then continues on to generate the following signals depending on how the circuit evaluated.

- EQ\_out evalues to *logic* 1 if the input address is exactly equal to the value stored in that particular stage, and *logic*  $\theta$  otherwise

- GT\_out evaluates to *logic 1* if the input address is greater than the stage's stored value, and *logic 0* otherwise

- nGT\_out\_comp is simply the complement of GT\_out

Note that the *beginning* stage is the only stage in this architecture to be driven by the clock signal. Looking closer into the *beginning* architecture, shown in Figure 3.4, is the transistor-level design, showing that the circuit is essentially divided into two parts; one to evaluate the EQ\_out signal, and the other to evaluate the GT\_out and nGT\_comp\_out signals.

Figure 3.4: Schematic of the *Begin* Stage

For the beginning stage, both of these sub-circuits have a very similar, standard domino-logic gate style architecture. The only major difference is the additional inverter added after the GT\_out signal to generate nGT\_comp\_out. When the clock is low, these circuits precharge the critical nodes A and B, meaning the outputs of this stage will be  $EQ\_out = logic0$ ,  $GT\_out = logic0$ , and  $nGT\_comp\_out = logic1$  during this time period. As time elapses, and the clock rises to logic 1, the direct connections between these nodes and VDD are severed, and the evaluate transistor conducts, opening a path to ground at the end of the pull-down network. If the input address is equal to the

value that this *beginning* stage compares to, a direct path to ground exists for node A, discharging it, bringing the output of EQ\_out to *logic 1*. Similarly, if the input address is greater than the compare value, node B discharges, setting GT\_out high and nGT\_comp\_out low.

The way in which EQ and GT are evaluated depends principally on the pull-down network. In Figure 3.4, the pull-down network shows what combination of transistors are used for comparing a bit of the address to '0', and '1' (shown in green and red, respectively). The pull-down network is explained further in the next section.

### 3.2.2 The Address Compare Pull-Down Network

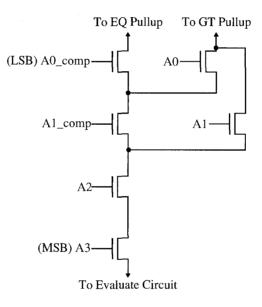

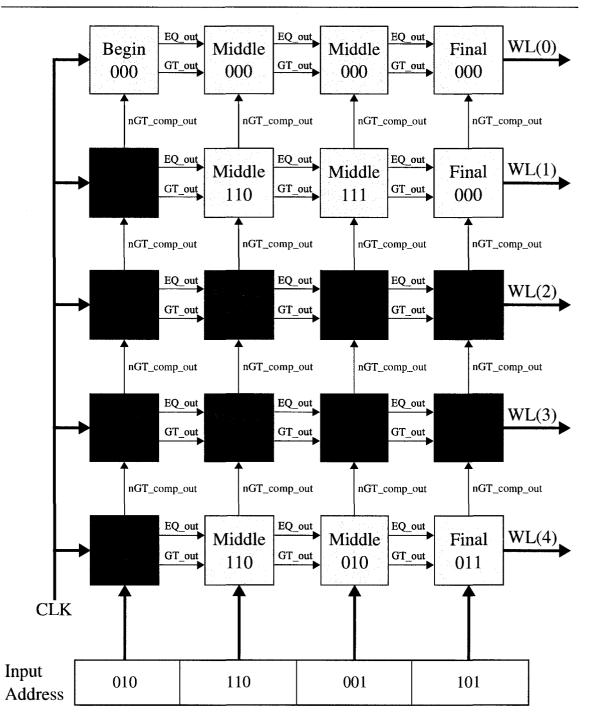

Figure 3.5: An Example Pull-Down Network for a 4-Bit Address Decode Stage Comparing to "1100"

An example of a 4-bit pull-down network used to evaluate the EQ and GT signals is shown in Figure 3.5. Note that the most significant address bit that will be compared is A3, the transistor closest to the evaluate circuit, while the least significant address bits connect to the pull-up circuits. In the case of the *beginning* stage, the EQ pullup is node A, and the GT pullup is node B. Also note that when comparing the input address to a '1', there is no transistor in the GT chain. This is due to the fact that in a binary number system, it is impossible to determine if a number is greater than one using a single digit, rather the next, more significant bit must be examined.

### 3.2.3 Overview of the Middle Stage

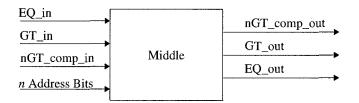

A block diagram showing the input and output signals of the *middle* stage is shown in Figure 3.6. The major differences between this and the *beginning* stage are that this stage uses EQ\_in and GT\_in in place of the clock signal, and nGT\_comp\_in used in the evaluate chain.

Figure 3.6: Block Diagram of the Middle Stage

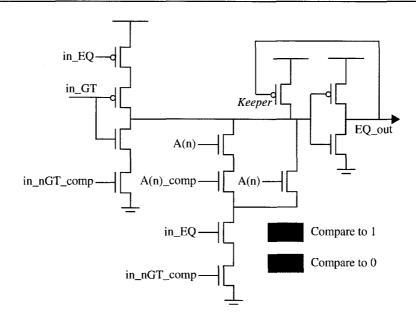

The schematic for the *middle* stage is shown in Figure 3.7. Once again, this stage differs only slightly from *beginning*. The EQ circuit uses in\_EQ from the previous stage as a clock, and an additional transistor, controlled by in\_nGT\_comp, is added to the evaluate path. This extra transistor is responsible for disabling the evaluate stage of the EQ circuit in the event that the input address is greater than the next row's value. The GT circuit uses both the in\_EQ and in\_GT signals to work the precharge and evaluate transistors. For this part of the *middle* stage, note that neither the EQ or GT circuits will evaluate if the input address is greater than the next row due to the additional transistor in the evaluate path of the pull-down network. Additionally, if the previous stage's out\_GT signal is at *logic 1*, and the input address is not yet known to be greater than the next row, the GT\_out signal of this stage will automatically propogate due to the additional transistors added to the GT circuit's parallel pull-down network. This is done to further reduce the amount of switching in order to improve power consumption.

### 3.2.4 Overview of the Final Stage

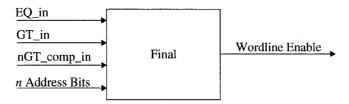

The *final* stage is shown in block diagram form in Figure 3.8. This stage makes use of EQ\_in, GT\_in, and nGT\_comp\_in, however its only output is a word line enable signal, WL.

The schematic for the *final* stage is shown in Figure 3.9. This circuit is essentially the same as the *middle* stage, with the exception that the GT and EQ subcircuits have been combined. The reason for this is that if the input address is not yet known to be greater than the next row's compare value, this stage must determine if it is to be enable its row's output word line.

Figure 3.7: Schematic of the Middle Stage

Figure 3.8: Block Diagram of the Final Stage

### 3.2.5 Detailed Example of the RALUT Address Decoder

This example will refer extensively to the five row, four stage, 12-bit RALUT address decode circuit shown in Figure 3.10. Omitted for clarity are the input address lines going to every row, rather than only the last row. Also omitted are the address and clock buffers. This figure is colour coded to indicate weather a signal is *logic 1* (green), *logic 0*, (red), and if a stage evaluates (green), or if it is disabled to save power (grey).

This RALUT address decoder can enable one of five different word line output rows, shown as WL(0) through WL(4). Evaluation begins as follows. When the CLK signal is at *logic 0*, the *beginning* stage enters its pre-charge state. During this time, the input address may change without affecting the RALUT's output. On the rising edge of CLK, the *beginning* stage of the circuit begins to evaluate.

The most significant three bits of the input address are compared with the *beginning* stage of each row. If the result is equal, as in rows 3 and 4, EQ\_out changes from *logic*  $\theta$  to *logic* 1, acting as

Figure 3.9: Schematic of the Final Stage

clock signal for the next stage's EQ\_out circuit. If the result is not equal however, EQ\_out does not change logic levels and the next stage's EQ\_out circuit remains dormant, saving power. Similarly, GT\_out evaluates to *logic 1* if the input address is greater than the stored value. This signal, in turn, acts as the clock for the next stage's GT\_out circuit, similar to EQ\_out. The last row's *beginning* stage's stored value is greater than the first three bits of the input address. Due to this, both the EQ\_out and GT\_out lines remain low, and the remainder of the final row does not evaluate, saving power.

The nGT\_comp\_out signal connects to the *beginning* stage of the previous row. This signal is simply the complement of that *beginning* stage's GT\_out, and is used to disable the evaluation of the previous row in order to reduce power consumption. In this example, once the first three bits of the input address have been evaluated by the *beginning* stages, it is apparent that the first row will not require further evaluation since the input address is greater than the second row.

The *middle* stages perform similar to the *beginning* stage, with two differences. First, the *middle* stages are not attached to a clock signal, rather they employ the previous stage's EQ\_out and GT\_out as a pre-charge and evaluate mechanism. Second, the *middle* stages have been modified to accept an additional input, the nGT\_comp\_out signal, to disable their evaluate chains when it is at *logic*  $\theta$ .

Once the previous stages have evaluated, the *final* stage determines which of the word lines to enable. Note that this architecture will, regardless of input addresses and stored decoder values,

Figure 3.10: Example of a 5 Row, 12-bit, 4 Stage RALUT Address Decoder Evaluating

fully evalute two entire rows at the most. In this example, rows 3 and 4 are evaluated to the end. The *final* stage will compare the final, and least significant, three bits of the input address with its stored value, as well as the previous stage's EQ\_out and GT\_out signals. Based on these, a single output word line is enabled. In this example, the input address is larger than the value stored in the third row of the address decoder, but smaller than the fourth, and the third word line is enabled. If the fourth row's *final* stage would have had the bit pattern 101 stored, the row would have been exactly equal to the input address, and that world line would have been enabled instead.

Once all stages have evaluated, the word line remains valid until the negative edge of the clock signal, CLK.

### **3.3** Overview of the Word Lines

The word lines are simple in function; given a line enable signal, they simply place the correct output bit pattern on the output bus. The line enable signal connects to a series of buffer, or line drivers, which then connect directly to NMOS and PMOS transistors which either pull-up or pull-down the RALUT output bits depending how they have been configured.

### 3.4 Address and Clock Buffering Overview

The clock signal and input address lines must be sufficiently buffered so that as the RALUT scales in size, these signals can be driven without incident. For example, without buffering, the incoming clock signal would have to drive every *beginning* stage. With smaller designs this might be acceptable, however when using a design with hundreds of rows the rise and fall times of the clock signal will be very high, if the signal is able to even drive the circuit at all.

Buffering is implemented with a simple tree structure. Every input signal enter a single buffer, which branches off to a series of additional buffers, and so on, until the signal reaches the address decoder.

# Chapter 4

# Proposed VLSI Implementations in CMOS 0.18µm

This chapter discusses the design goals, methodology, and results in creating two proposed designs, both of which are in CMOS  $0.18\mu m$ . The first is a rescaling of the existing  $0.35\mu m$  design, in which all layout cells were recreated in the more advanced  $0.18\mu m$  node, however only two different transistor sizes were used: one for NMÓS transistors, and the other for PMOS transistors. This was a very rapid approach to rescaling the design, and was used to meet a fabrication deadline for the test platform outlined in the next chapter. The second proposed design involves carefully resizing individual transistors, and further reducing area utilization to produce a high-performance RALUT. This approach proved to be much more time consuming, however simulation results prove to be optimal.

This chapter is organized as follows. It begins with an overview of the CMOS  $0.35\mu m$  design, followed by an explanation why the CMOS  $0.18\mu m$  technology node was chosen for the new designs. A brief discussion regarding the rescaling of CMOS designs ensues. Next, detailed explanations of the proposed CMOS  $0.18\mu m$  and high performance  $0.18\mu m$  designs are presented. Finally, the chapter ends with a comparison of the results and some summarizing remarks.

### 4.1 Existing CMOS $0.35 \mu m$ Design

This work advances the contributions made in [14] towards a high performance, full-custom RALUT design. As such, an existing full-custom design in an CMOS  $0.35\mu m$  process existed, however many improvements could be made. The existing CMOS  $0.35\mu m$  design consisted of the following items:

- 1. A full-custom cell library, including beginning, middle, and final stages of the address decoder, as well as the input and clock buffers, output bits and output linedriver cells

- 2. A CAD tool designed in SKILL, used in the Cadence software environment to automatically place and configure the design cells based on a user-generated file containing the desired bit patterns