## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2009

## TCP/IP Control Server for a Multi-Drop Test Bench Network

Christopher Rennick University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Rennick, Christopher, "TCP/IP Control Server for a Multi-Drop Test Bench Network" (2009). *Electronic Theses and Dissertations*. 8203.

https://scholar.uwindsor.ca/etd/8203

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# TCP/IP Control Server for a Multi-Drop Test Bench Network

By Christopher Rennick

#### A Thesis

Submitted to the Faculty of Graduate Studies Through the Department of Electrical and Computer Engineering In Partial Fulfillment of the Requirements for The Degree of Master of Applied Science at the University of Windsor

# Windsor, Ontario, Canada 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-70580-3 Our file Notre référence ISBN: 978-0-494-70580-3

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### © 2009 Christopher Rennick

All Rights Reserved. No part of this document may be reproduced, stored, or otherwise retained in a retrieval system or transmitted in any form, on any medium by any means without prior written permission of the author.

.

# **Co-Authorship Declaration**

I hereby declare that this thesis incorporates material that is result of joint research, as follows:

This thesis also incorporates the outcome of a joint research undertaken in collaboration with Stephen Fox under the supervision of Dr. Roberto Muscedere. The details of the collaboration is covered in Chapter 2 of the thesis. In all cases, the key ideas, primary contributions, experimental designs, data analysis and interpretation, were performed by the author.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my thesis, and have obtained written permission from each of the co-author(s) to include the above material(s) in my thesis.

I certify that with the above qualification, this thesis, and the research to which it refers is the product of my own work.

## Abstract

This thesis describes the design, construction and verification process in full for the test server portion of the second generation of an automated testing network. The system was built for, and with, AMD/ATI of Markham, Ontario and will be used to test large batches of their graphics processing units (GPU's). The final test system has the capability to simultaneously test and control several parameters on a large number of test nodes.

The TCP/IP Control Server for a Multi-Drop Test Bench Network was designed to test and control a network of 256 test nodes over an RS-485 network. The contents of this thesis will describe the test server hardware in full, while the test nodes are described in Stephen Fox's thesis. The test server consists of an Ethernet-enable MCU, an Altera Cyclone II FPGA and a custom RS-485 transceiver board used to communicate with the test nodes. To my family and friends, thanks for being there and for providing distractions when I needed them.

To Sandra, thanks for ten years of your love and support.

# Acknowledgements

I would like to sincerely thank Dr. Muscedere for his invaluable assistance and guidance on this project, and for providing me the opportunity to work on such an interesting project with such a reputable industrial partner.

To my committee members, Dr. Khalid and Dr. Kent, I appreciate your time and energy spent on me and this research.

I would like to thank my colleague on this project, Stephen Fox, for his individual contributions to this project and for any aid he provided me.

I would also like to thank Advanced Micro Devices (AMD)/ATI for their funding of this research as well as NSERC for their contributions to the project.

Finally, I would like to thank my parents for their seemingly endless guidance and assistance, without you, this would not have been possible.

# Table of Contents

......

| CO-AUTHORSH    | IP DECLARATION                                             | IV  |

|----------------|------------------------------------------------------------|-----|

| ABSTRACT       |                                                            | V   |

| DEDICATION     |                                                            | VI  |

| ACKNOWLEDGI    | EMENTS                                                     | VII |

| LIST OF TABLES |                                                            | X   |

| LIST OF FIGURE | s                                                          | XI  |

|                | /IATIONS                                                   |     |

| CHAPTER 1.     | INTRODUCTION                                               |     |

| 1.1 PROJECT O  | VERVIEW                                                    |     |

|                | SANIZATION                                                 |     |

| CHAPTER 2.     | TEST SERVER OVERVIEW                                       | 5   |

| 2.1 HISTORY OF | ATE Systems                                                | 5   |

| 2.2 CURRENTLY  | AVAILABLE ATE SYSTEMS                                      | 6   |

| 2.3 TEST SYSTE | M, GENERATION ONE                                          | 7   |

| 2.4 PROPOSED   | Solution                                                   | 9   |

|                | Node Overview                                              |     |

| 2.4.2 Desc     | ription of RS-485                                          |     |

| CHAPTER 3.     | HARDWARE AND SOFTWARE SELECTION                            |     |

| 3.1 HARDWARE   | SELECTION                                                  |     |

| 3.1.1 Micro    | ocontroller Selection                                      |     |

| 3.1.2 Micro    | oprocessor Development Kit Selection                       |     |

| 3.1.3 FPGA     | Selection                                                  |     |

| 3.1.4 FPGA     | Development Kit Selection                                  |     |

| 3.1.5 RS-48    | 35 Transceiver Selection                                   | 21  |

| 3.2 SOFTWARE   | SELECTION                                                  | 22  |

| 3.2.1 MCU      | Compiler and Programmer Selection                          | 22  |

| 3.2.2 FPGA     | Synthesizer and Programmer Selection                       | 23  |

| 3.2.3 Electi   | rical Schematic Editor Selection                           | 23  |

| CHAPTER 4.     | VHDL DESIGN AND VERIFICATION OF FPGA-BASED MULTI-PORT UART | 24  |

| 4.1 VHDL DESI  | GN – SERVER                                                | 25  |

| 4.2 VHDL DESI  | GN – MCU_TO_485 MODULE                                     |     |

|                | Design – MCU_buf Module                                    |     |

|                | Design – FIFO Module                                       |     |

| 4.2.3 VHDL     | Design – RS485_output Module                               | 33  |

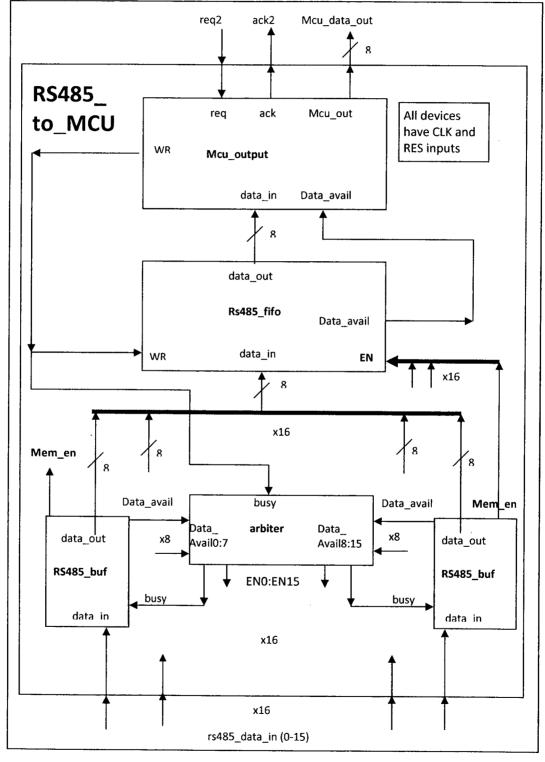

| 4.3 VHDL DESI  | GN – RS485_TO_MCU MODULE                                   | 33  |

| 4.3.1 VHDL     | Design – MCU_output Module                                 | 36  |

| 4.3.2 VHDL     | Design – RS485_fifo Module                                 | 36  |

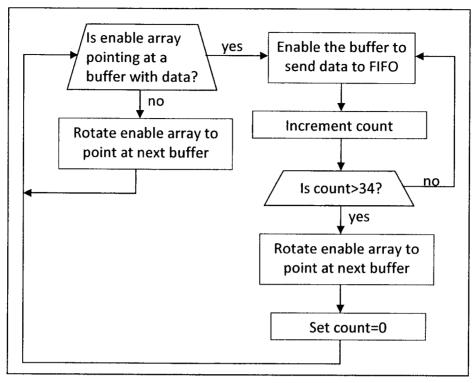

|                | Design – Arbiter Module                                    |     |

| 4.3.4 VHDL     | Design – RS485_buf Module                                  |     |

.

| 4.4 VHDL Da    | SIGN - SERVER_TEST MODULE                                      |     |

|----------------|----------------------------------------------------------------|-----|

| CHAPTER 5.     | DEVELOPMENT OF C CODE FOR TEST SERVER EMBEDDED MICROCONTROLLER | 41  |

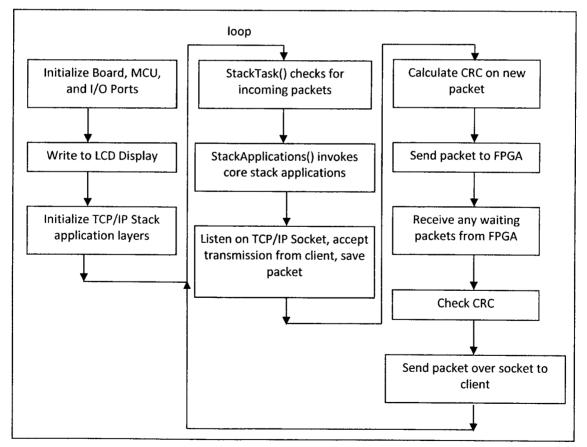

| 5.1 INITIALIZA | TION PROCEDURES                                                |     |

| 5.2 MAIN PR    | DCESSING LOOP                                                  |     |

| 5.2.1 Sta      | ck Operations                                                  |     |

| 5.2.2 Acc      | ept and Store Packet                                           | 44  |

| 5.2.3 Cor      | nmunication with FPGA                                          |     |

| CHAPTER 6.     | PC CLIENT DESIGN                                               | 46  |

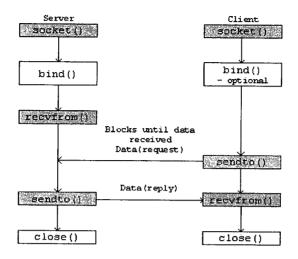

|                | us UDP                                                         |     |

|                | OPERATION                                                      |     |

| 6.2.1 Pac      | ket Sort Algorithm                                             |     |

| 6.3 Changes    | TO ADAPT CLIENT.C CODE TO UNIX/LINUX                           | 51  |

| CHAPTER 7.     | CONCLUSION                                                     | 53  |

| 7.1 TEST SERV  | er Limitations                                                 |     |

| 7.2 THESIS CO  | INTRIBUTIONS                                                   |     |

| 7.3 TEST SERV  | er Verification and Final Results                              | 57  |

| 7.4 FUTURE V   | /ORK                                                           | 57  |

| REFERENCES     |                                                                | 60  |

| APPENDIX A. S  | CHEMATICS AND BILL OF MATERIALS                                | 62  |

| A.1 SCHEMAT    | ICS                                                            | 62  |

|                | ATERIALS                                                       |     |

|                | of Materials – Prototyping Stage                               |     |

| A.2.2 Bill     | of Materials – Final Test Server                               | 69  |

|                | EST SERVER VHDL CODE                                           |     |

| B.1 SERVER.VI  | ID                                                             | 75  |

| B.2 мси_то_    | 485.vhd                                                        | 76  |

| B.2.1 mcı      | bufmem.vhd                                                     |     |

| B.2.2 rs48     | 25_output.vhd                                                  |     |

| B.2.3 fifo.    | vhd                                                            |     |

|                | _buf.vhd                                                       |     |

| B.3 RS485_TC   | )_MCU.VHD                                                      | 83  |

| B.3.1 rs48     | 5buf_mem.vhd                                                   |     |

| В.З.2 тси      | _output.vhd                                                    | 85  |

| B.3.3 rs48     | 5_fifo.vhd                                                     | 87  |

| B.3.4 arbi     | ter.vhd                                                        |     |

| B.3.5 rs48     | 5_buf.vhd                                                      | 89  |

| B.4 Server_t   | EST.VHD                                                        | 92  |

|                | EST SERVER C CODE                                              |     |

| APPENDIX D. P  | C CLIENT C CODE                                                | 109 |

| VITA AUCTORI   | 5                                                              | 125 |

# List of Tables

| Table 2.1. Test Server Component Summary                                  | 11 |

|---------------------------------------------------------------------------|----|

| Table 2.2. Summary of Packet Structure                                    | 12 |

| Table 3.1. Microcontroller Summary                                        | 18 |

| Table 3.2. Summary of Chosen MCU [11]                                     | 18 |

| Table 3.3. Summary of Available MCU Development Kits [12] [13]            | 19 |

| Table 3.4. Available FPGA Summary [14]                                    | 20 |

| Table 3.5. Summary of Chosen FPGA                                         | 20 |

| Table 3.6. Summary of Available FPGA Development Kits [15]                | 21 |

| Table 3.7. Summary of Selected RS485 Transceiver [16]                     | 22 |

| Table 6.1. Acknowledge Values and Their Meaning                           | 48 |

| Table 6.2. Header Differences, Unix vs. Windows [19]                      | 51 |

| Table 6.3. Socket Initialization Differences, Unix vs. Windows [20]       | 51 |

| Table 6.4. Socket Application Shutdown Differences, Unix vs. Windows [20] | 52 |

| Table 6.5. Socket Error Reporting Differences, Unix vs. Windows [20]      | 52 |

| Table 6.6. Conditional Group C Code Example - Header Calls                | 52 |

| Table A.1. Bill of Materials - Prototyping Stage                          | 69 |

\*\*\*\*

# List of Figures

ane

CONTRACTOR OF STREET,

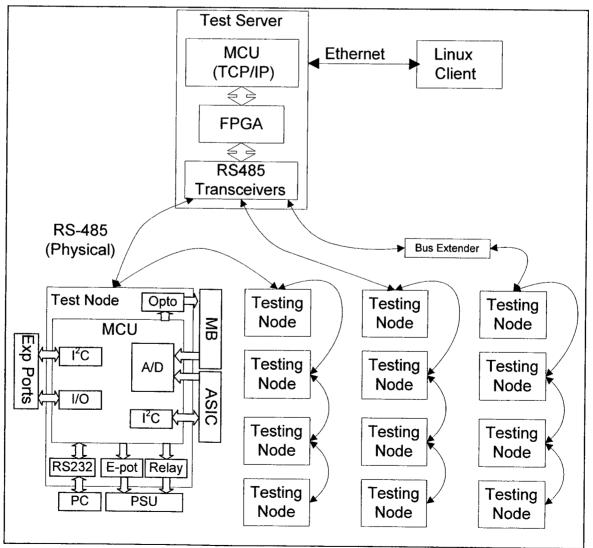

| Figure 1.1. System Overview                                                    | 2   |

|--------------------------------------------------------------------------------|-----|

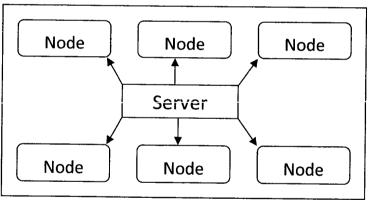

| Figure 2.1. Visualization of Star Topology                                     |     |

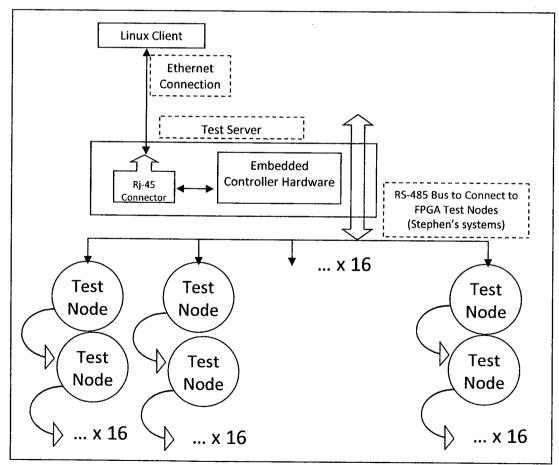

| Figure 2.2. Proposed System Overview                                           |     |

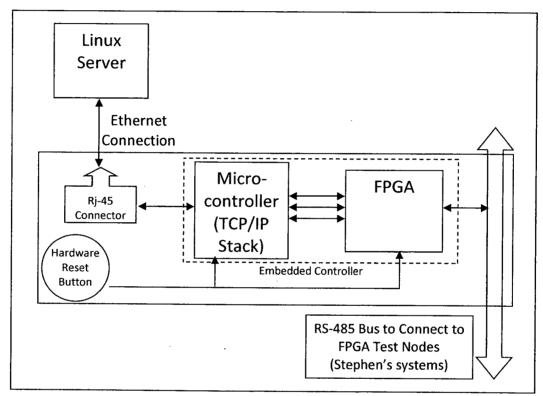

| Figure 2.3. Test Server Layout Overview                                        |     |

| Figure 2.4. Test Node Overview                                                 |     |

| Figure 2.5. Length of Cable vs. Data Rate of an RS-485 Network [6]             |     |

| Figure 2.6. Daisy Chain Topology                                               | 16  |

| Figure 4.1. VHDL Design Flow                                                   | 25  |

| Figure 4.2. Block Diagram of Server Module                                     | 26  |

| Figure 4.3. Waveform of Data Transfer From MCU to FPGA                         | 27  |

| Figure 4.4. Waveform of Data Transfer From FPGA to MCU                         | 27  |

| Figure 4.5. Block Diagram of MCU_to_485 Module                                 | 29  |

| Figure 4.6. Waveform of Reading From Dual-Port RAM Module                      | 32  |

| Figure 4.7. Waveform of Writing To Dual-Port RAM Module                        | 32  |

| Figure 4.8. Block Diagram of RS485_to_MCU Module                               | 35  |

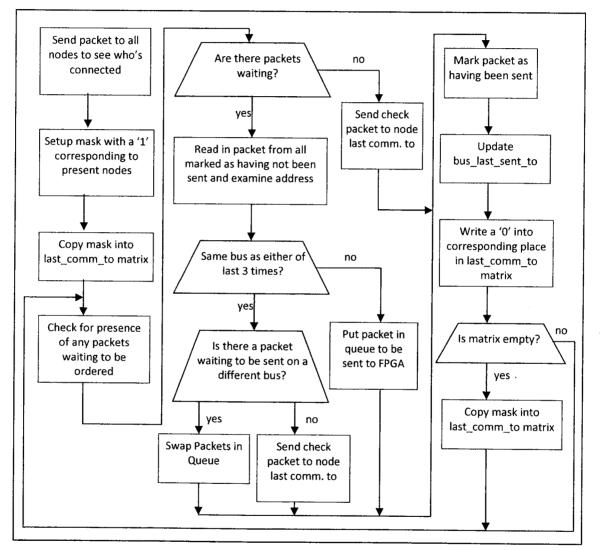

| Figure 4.9. Flowchart of Arbiter Operation                                     | 38  |

| Figure 5.1. Flowchart of MCU Main Processing Loop Operation                    | 43  |

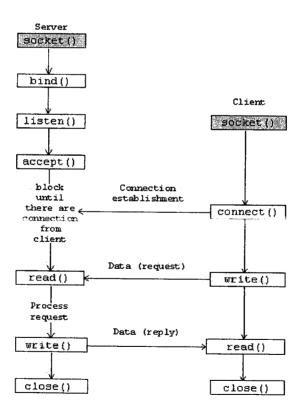

| Figure 6.1. Flowchart of UDP Operation [17]                                    | 47  |

| Figure 6.2. Flowchart of TCP Operation [17]                                    | 47  |

| Figure 6.3. Flowchart of Packet Sort Algorithm                                 | 50  |

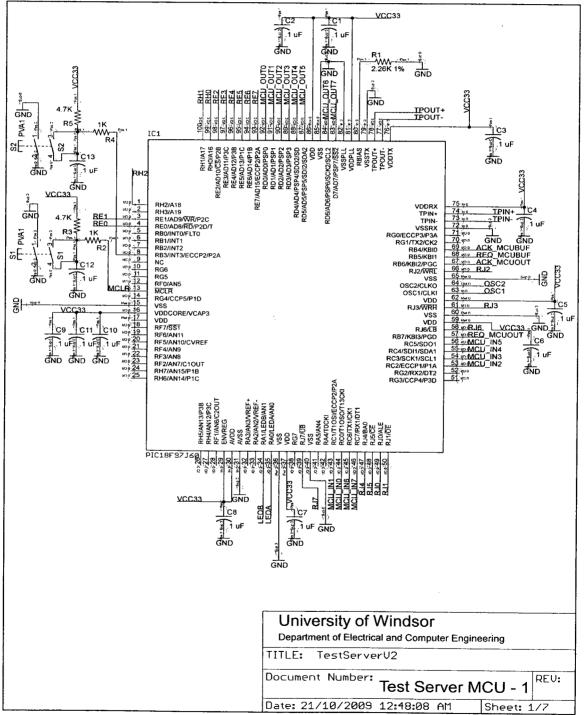

| Figure A.1. Test Server MCU Schematic                                          | 62  |

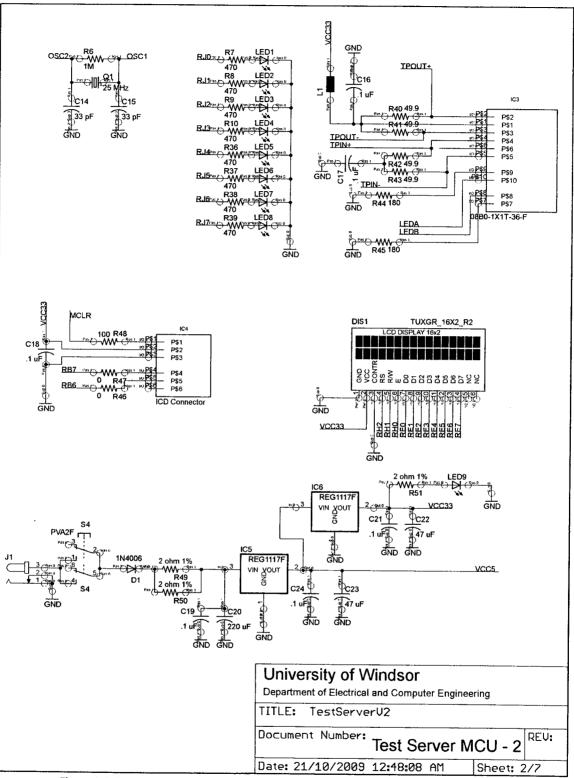

| Figure A.2. Test Server MCU Schematic – Ethernet, ICSP, LCD, LEDs, Oscillator, | and |

| Power                                                                          | 63  |

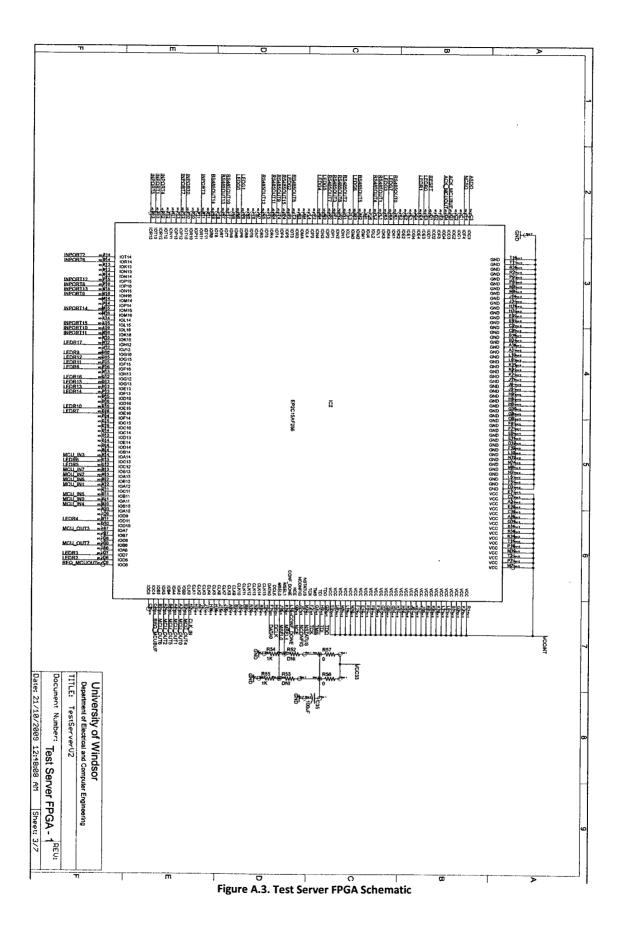

| Figure A.3. Test Server FPGA Schematic                                         | 64  |

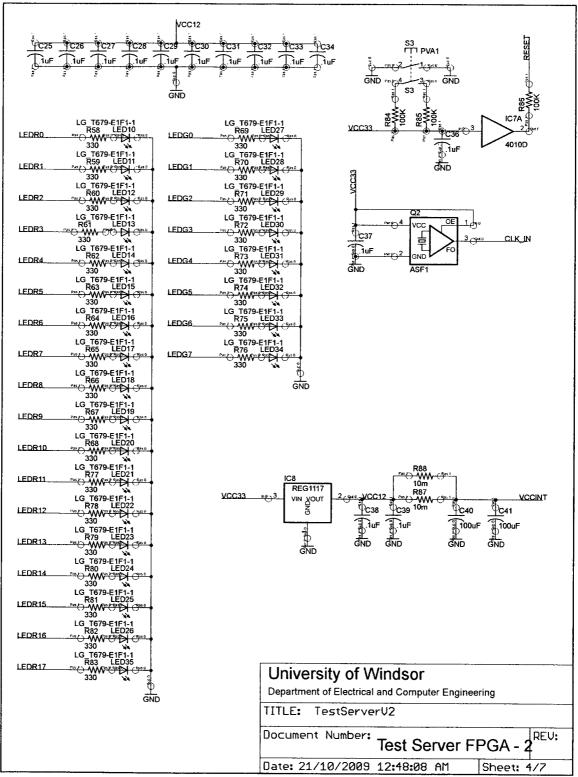

| Figure A.4. Test Server FPGA Schematic - LEDs, Oscillator, Power, and Reset    | 65  |

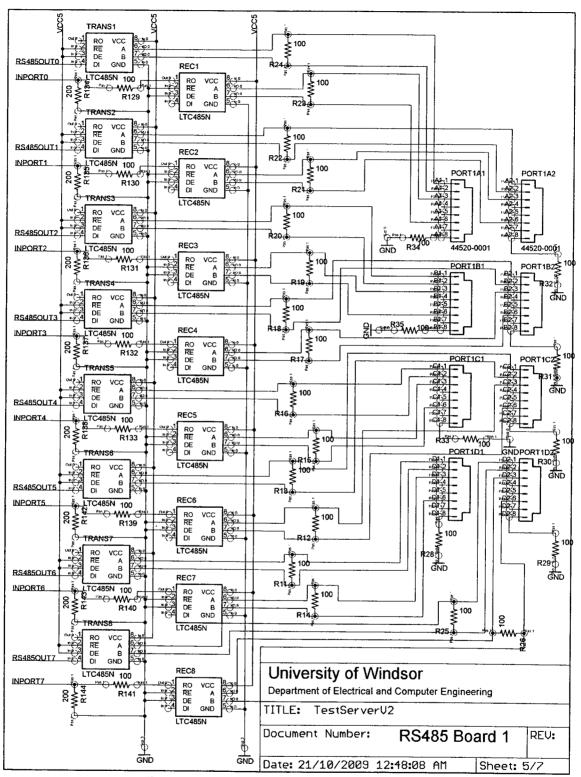

| Figure A.5. RS485 Transceiver Network (First 8) Schematic                      |     |

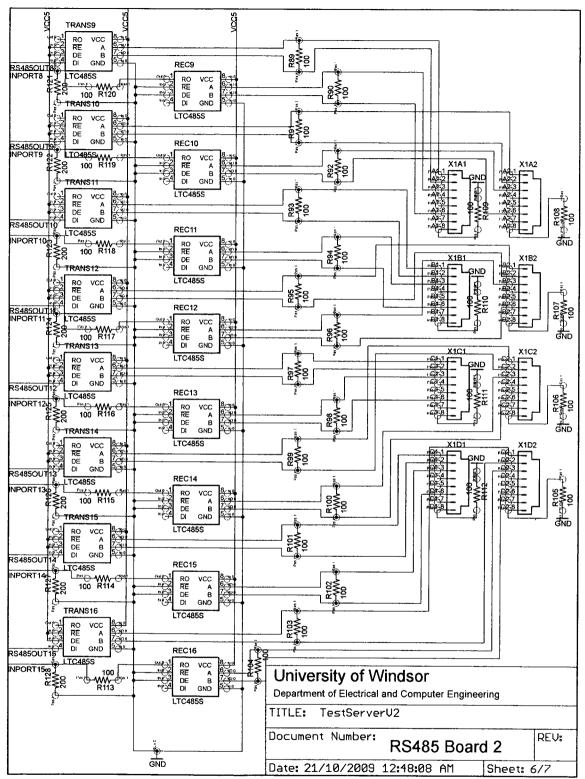

| Figure A.6. RS485 Transceiver Network (Second 8) Schematic | 67 |

|------------------------------------------------------------|----|

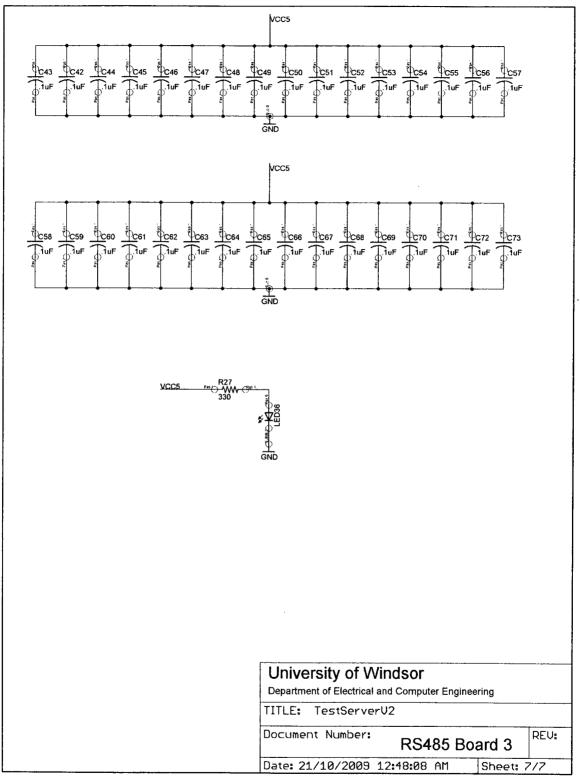

| Figure A.7. RS485 Transceiver Network Schematic – Power    | 68 |

# List of Abbreviations

| A/D    | Analog to Digital                               |

|--------|-------------------------------------------------|

| ASIC   | Application-Specific Integrated Circuit         |

| ATE    | Automated Test Environment/Equipment            |

| D/A    | Digital to Analog                               |

| E-Pot  | Electric Potentiometer                          |

| FPGA   | Field Programmable Gate Array                   |

| FIFO   | First In First Out                              |

| GP I/O | General Purpose Input/Output                    |

| GPU    | Graphics Processing Unit or Graphics Card       |

| НТТР   | Hypertext Transfer Protocol                     |

| I/O    | Input/Output                                    |

| IC     | Integrated Circuit                              |

| ICSP   | In-Circuit Serial Programming                   |

| MAC    | Media Access Control                            |

| MCU    | Microcontroller                                 |

| MPU    | Microprocessor                                  |

| MSI    | Medium Scale Integration                        |

| PC     | Personal Computer                               |

| РСВ    | Printed Circuit Board                           |

| PCI    | Peripheral Component Interconnect               |

| RAM    | Random Access Memory                            |

| ROM    | Read-Only Memory                                |

| SNMP   | Simple Network Management Protocol              |

| TCP/IP | Transmission Control Protocol/Internet Protocol |

| UART   | Universal Asynchronous Receiver/Transmitter     |

| UDP    | User Datagram Protocol                          |

- VHDL VHSIC Hardware Description Language

- VHSIC Very High Speed Integrated Circuits

.

VLSI Very Large Scale Integration

## **Chapter 1. Introduction**

In modern industrial research and development, the time to market, or the length of time that it takes to fully design and test a product and offer it for sale to the general public, needs to be as short as possible, while still maintaining all previous quality control standards. There are many steps in this process, including but not limited to, determining customer wants/desires in a new product, initial design phases outlining the overall functionality of the product, development of any new technologies to enable this product to come to market (if necessary), design of the product in full, complete testing of all features of the new product, final marketing and finally, the sale of the product. Any of these stages can be shortened to quicken the overall time to market, though this thesis is mainly concerned with only one of these stages of development, the testing.

Testing of new products is a very complicated and time consuming process, and just because a certain test on one machine in particular performed flawlessly, does not mean that the same test on a different machine will perform the same way. In other words, when components from outside parties are used in a system, they need to be verified in several different systems to ensure that they are functioning correctly in the system as a whole. This then requires that large batches of a new machine or product need to be tested to make sure that manufacturing and design tolerances do not factor into overall product robustness. If one were to test large batches of machines with a complicated testing procedure one at a time, the testing process would be prohibitively long, thus it is desired to have the ability to test large batches of a new product simultaneously with as little human input as possible.

This thesis and the joint research performed by Stephen Fox, is concerned with the development of an automated test environment (ATE) with the capability to test several key performance criteria on up to 256 separate computers simultaneously.

## **1.1 Project Overview**

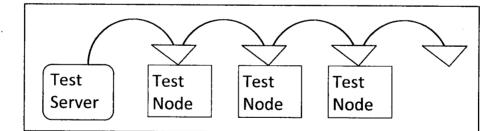

This project has two main deliverables: the test server and the test nodes. This thesis will describe the design and construction of the test server, whereas the thesis of my colleague, Stephen Fox, will describe the design and construction of the test nodes. The test server has the ability to control, and communicate with, a maximum of 16 buses, each with a maximum of 16 nodes for a total maximum node count of 256. The nodes in each bus are in a daisy chain configuration, which was chosen for its simplicity and for its affinity to the RS485 electrical standard which is our chosen communication medium. The basic physical layout of the system is shown in Figure 1.1.

Figure 1.1. System Overview

The system functions as follows: the client reads in a file of 30 byte long packets, which are in hexadecimal format, orders the packets in a manner such that any possibility for contention on a bus is eliminated, and transmits them, one at a time, over the TCP/IP socket to the test server microcontroller. The test server then calculates a CRC-16 checksum number and adds it to the end of the packet, making a packet length of 32 bytes. The checksum is needed to ensure that noise or other external factors did not alter the data during transmission to the node. The test server FPGA will then send the packet out to the correct bus based on the address byte in the packet. The test node that the packet is addressed to will then act on the command passed to it in the "command" field of the packet and will send back any data that is requested. The test server, on receipt of the data from the test node, will re-calculate the CRC and make sure there were no transmission errors; it will then forward the reply over the TCP/IP socket back to the PC client software which is maintaining control and safe operation of the entire system.

### **1.2 Thesis Organization**

This thesis describes the design and construction of the test server for a custom automated test environment (ATE). Chapter 2 will provide an overview of the test server and its capabilities as well as review the structure of the test nodes as designed by my colleague Stephen Fox. Chapter 3 will describe the various pieces of hardware that make up the test server and the associated software tools that were used in the project's development. This chapter will describe the pieces of hardware currently being used in the prototype of the test server and will give recommendations for the hardware that should be used in the production of the server. Chapter 4 will describe the development and design of the VHDL code for the MCU\_to\_485 and RS485\_to\_MCU FPGA modules. Chapter 5 will discuss the PIC microcontroller that was chosen for this project in detail and will also discuss the C code that was written for its operation. Chapter 6 will discuss the design of the PC client software, written in the C programming language, which is controlling the system as a whole. Finally, Chapter 7 will conclude the thesis and will discuss suggestions for future work.

The content of the appendices is as follows: Appendix A consists of the schematics of the test server hardware and the Bill of Materials, Appendix B contains the VHDL code for the test server FPGA, Appendix C contains the C code for the test server microcontroller and Appendix D contains the C code for the PC client.

## Chapter 2. Test Server Overview

## 2.1 History of ATE Systems

ATE systems have had a relatively short life and have developed hand in hand with commercial computers. The first automatic test devices were created in the 1950's by the United States' Department of Defense (DOD), primarily to test missile systems and other military electronics. It should be noted that this development coincides with the increasing availability of digital logic and commercial computers. The U.S. DOD realized that a more repeatable and consistent method of testing new military electronics was needed, and thus a need for automated testing equipment was born. The first ATE systems were created primarily of existing manual instruments which had custom designed digital logic added to allow them to be programmable. This was certainly not an ideal situation, and the end goal was to move to more universal test equipment [1].

A system was desired that had a full set of programmable instruments which could be configured and reconfigured at will, as quickly and easily as possible. The first of these systems was created between 1968 and 1972 and it was called the Versatile Avionics Shop Test (VAST) and it consisted of a test station, a computer and a data transfer unit. It was created to test the avionics systems on F-14A and S-3A aircraft and was deployed on aircraft carriers starting in 1974. The VAST systems eliminated some special support equipment and reduced the number of technicians required to test and maintain the avionic systems, and thus were, at least partially, successful at what it set out to do. A test program set was created to test each individual system, but unfortunately, it could only test one avionic system at a time [2].

As computers continued to improve, so too did the automated test environments, by the mid 1970's, they were capable of testing medium scale integration circuits (MSI) that had hundreds of transistors per chip. During the 1970's another important development happened: buses were introduced which greatly enhanced interfacing between components. This led to the development by Hewlett-Packard of the Hewlett-Packard Interface Bus (HPIB), also referred to as the General Purpose Interface Bus (GPIB). This bus was standardized by the IEEE in 1975 into IEEE 488.1 and it is still widely used to this day, though the standard has been upgraded by the IEEE in the past 30 years. In the early 1980's, the automated test environments started to include more modern embedded systems, including embedded microprocessors, this allowed the systems to become "smarter" and more customizable [1].

The late 1980's and into the 1990's saw the further development of ATE systems, which included standardizing the communication bus to allow multiple vendor's components to communicate easily with each other, and the introduction in the 1990's of "plug and play", which functioned very similar to USB in that components could be plugged in and the system handled installing any drivers to allow that component to work in the system as a whole.

## 2.2 Currently Available ATE Systems

There are currently several large vendors of off the shelf ATE systems. These include National Instruments, Northrop Grumman, and Teradyne [3] [4]. Prices on individual modules from these vendors range in price from \$1,000 to more than \$18,000 depending on the module and many of these ATE systems are the size of a refrigerator. These systems can test virtually all aspects of a custom VLSI design as the modules include A/D converters, D/A converters, signal generators, variable power supplies, signal analyzers, multimeters and radio frequency and high frequency devices. However, many of these systems are designed to test one chip at a time. Clearly the cost, size and the inability to test many systems at once is a large drawback of these devices. There is also a large number of competing standards as to how these units should communicate with each other. There are currently several standard instrument types including using PC standard input/output (I/O) such as USB and Ethernet as well as RS-232 serial connections and also add-in cards like ones which used the GPIB interface. There are also some custom instrument types including VME eXtensions for Instruments (VXI) components which was development in the 1980's, primarily for use by the U.S. military, PCI eXtensions for Instruments (PXI), which was created by National Instruments in 1997 and is based off the Compact PCI bus, and finally LAN eXtensions for Instrumentation (LXI) which uses high-speed LAN as the backplane of the ATE [5].

### 2.3 Test System, Generation One

Approximately three years ago, AMD/ATI realized that the currently available, off-the-shelf ATE systems were not ideal for testing the functionality and performance of their graphics cards when deployed in a motherboard, so they set out to create their own system. This first generation of the project consisted of similar hardware to generation 2, however, to save on the development time, some off-the-shelf components were used that were not an ideal solution for the manner in which they were going to be used.

Generation one consisted of a National Instruments digital I/O board that was connected to a host PC that controlled the entire system. The digital I/O board ran direct connections to each of the test nodes and sent them the control signals directly using a serial connection. This created several problems, but was deemed at the time to be the ideal solution as it could be deployed quickly. The first issue with the system is the increased cost of the National Instruments board as compared to a custom built control board. The cost of a custom board with an FPGA and a microcontroller, similar to what is used in the solution that will be described in this paper, is considerably less than the cost of the National Instruments board. The second major issue is that the

7

overall system had a very large quantity of cabling that was necessary to connect everything; this was mainly due to the topology that was used in deploying the network. When creating a system with one central server which has an output that connects to each individual node, you generally end up with a star network topology as shown in Figure 2.1. The problem with a star is that as nodes get farther away from the server, the cable length to connect them also increases in size. The third problem was due to the communication medium they used to talk to the nodes; they used a common serial connection that used ground as a signal reference, which led to galvanic isolation problems. The problem with this, and it was a large problem that is not easy to overcome, is that "ground" is a relative measurement. There can be a difference in the voltage levels of ground between the different nodes as they are spaced around the room in which the system is deployed and this difference in ground level can cause one node to think a digital '1' is a '0' or a '0' is a '1'.

Figure 2.1. Visualization of Star Topology

With these difficulties in mind, generation two of the test network was deemed the next step in development. The proposed solution for the second generation of this project must then meet several criteria. First of all, it needs the ability to test and control multiple parameters of multiple nodes simultaneously. Secondly, it needs to communicate with these nodes in such a manner that cabling length and complexity is reduced from the first generation and the effects of external noise and differences in ground levels between nodes needs to be eliminated from the system. The system must also be easily upgradeable, as it is impossible to determine what parameters will need to be tested or controlled in the future. Lastly, it needs to be deployed as cheaply and easily as possible.

### 2.4 Proposed Solution

With the criteria and problems defined, as stated in the previous section, the second generation of the system could be designed. We desired the system as a whole to have Ethernet communication to a Linux client as well as the capability to test up to 256 test nodes simultaneously. The decided upon layout of the system can be seen in Figure 2-2. The test network will consist of a test server that can communicate over Ethernet to the client on one side and on the other it needs to communicate to 16 buses of 16 nodes each, laid out in a daisy chain topology which was chosen for its simplicity. Thus the system provides an overall count of 256 nodes.

Figure 2.2. Proposed System Overview

From the above figure, it is apparent that there are three main components to the system as a whole: the Linux client, the test server and the test nodes. This thesis will describe the development of the test server and the Linux client in detail, the design of the test nodes can be seen in Stephen Fox's thesis.

From this abstract design of the system, the functionality of the test server could be determined:

- 1. It needs to be Ethernet capable

- 2. It needs to have enough I/O to communicate effectively with 16 buses of test nodes

- 3. It needs the computing power to handle processing a large throughput of data from the Linux client to the test nodes.

From this early stage it was realized that we would not be able to find a microcontroller that had the I/O capabilities and processing power needed to communicate with 16 buses of test nodes as well as having the ability to communicate over an Ethernet connection, an FPGA of some kind would be needed in the test server to handle the large amount of I/O to the test nodes. Alternatively, an FPGA is not an ideal solution on its own as the nature of the test server lends itself better to being deployed on a microcontroller, and the cost of a microcontroller is significantly less than that of a FPGA, thus both a microcontroller and an FPGA are to be used in the test server. The microcontroller would be used to communicate over the Ethernet connection with the Linux client and the FPGA would be used as a multi-port UART to communicate with the test node network. The layout of the test server can be seen in Figure 2-3.

The final criteria that the system needed to meet was that the effects of the different levels of ground between the nodes and the external electronic "noise" present in the test server be eliminated. This was accomplished with the choice of RS-485 as the communication medium for the test node network and with standard Ethernet cabling terminated with RJ45 connectors, or, more officially, CAT-5e cabling, as the physical transmission medium. RS-485 is a half-duplex, differential electrical

standard that is ideal for a multi-drop communication link (a multi-drop communication link is one in which a single bus has multiple devices connected to it). Though RS-485 is a half-duplex communication medium, it can be made to be full-duplex by using one transceiver for transmitting and another for receiving; this is how RS-485 is implemented in this system. The choice of RS-485 and CAT-5e cabling will be described in more detail in Chapter 3.

Figure 2.3. Test Server Layout Overview

After finalizing the above general layout of the test server hardware, a component list can be created that will outline all hardware needed to construct the test server. This component list is summarized in Table 2-1.

| Table 2.2. researce component Summary |                   |                 |  |

|---------------------------------------|-------------------|-----------------|--|

| Component                             | Manufacturer      | Quantity Needed |  |

| Microcontroller                       | Microchip         | 1               |  |

| FPGA                                  | Altera            | 1               |  |

| RS485 Transceiver                     | Linear Technology | 32              |  |

| <b>RJ45 Female Connector</b>          | Tyco Electronics  | 17              |  |

Table 2.1. Test Server Component Summary

One final decision that had to be made was the format of the packet. It was deemed the best solution to use a packet length that is a factor of two, and since many of the packets that are going to be transmitted are quite short, a smaller packet size is ideal. The chosen packet length is 32 bytes, including the CRC-16 check bytes at the end of the packet. The structure of a packet is shown in Table 2.2.

| Table 2.2. | Summary | of Packet | Structure |

|------------|---------|-----------|-----------|

|------------|---------|-----------|-----------|

| Byte(s): | 1       | 2       | 3           | 4      | 5-30 | 31-32  |

|----------|---------|---------|-------------|--------|------|--------|

| Field:   | Address | Command | Acknowledge | Length | Data | CRC-16 |

#### 2.4.1 Test Node Overview

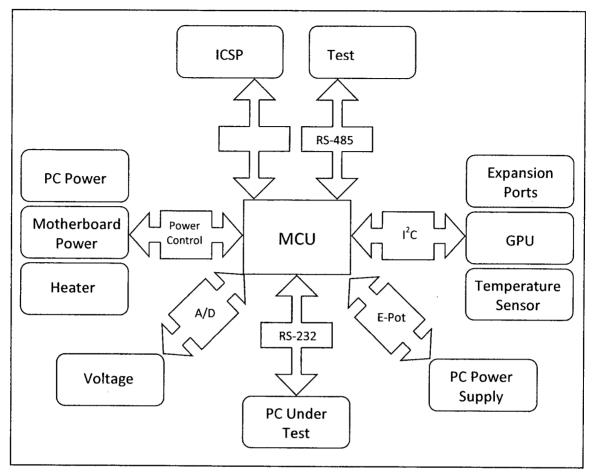

Each test node consists of a PIC microcontroller with in-circuit serial programming ability (ICSP), a power relay board, an external temperature sensor, an analog to digital converter (A/D converter), RS-232, RS-485 and I<sup>2</sup>C communication, and an electric potentiometer (E-Pot). An overview of the test nodes can be seen in Figure 2.4. The in-circuit serial programmer is used for updating the program in the MCU, the power relay board is used for cutting the power to the PC under test and is only used in emergency situations (similar to unplugging the machine from the wall outlet).

The test nodes are capable of controlling and monitoring several different aspects of the PC under test. The nodes can turn the PC under test on/off, cut the power to the PC using a relay board, set and monitor the temperature of the PC under test, and set and monitor the voltage on the 12V and 3.3V voltage rails. The nodes can also communicate with both the PC under test and the GPU in the PC, and finally the node can update its own program using the bootloader mode that has been programmed into the microcontroller. Also, the nodes were designed with expandability in mind; they can be expanded to add extra functionality to each of the individual test nodes.

Figure 2.4. Test Node Overview

The external temperature sensor is used to monitor the temperature of the PC under test and the A/D converter is used to monitor the system voltages. The external temperature sensor has a built-in A/D converter while the one used for monitoring the system voltages is embedded in the MCU. The external temperature sensor is part of the feedback on the temperature control of the system. The final system, when executed at the offices of AMD/ATI in Markham will have a heater element at each node that will allow the user to increase the ambient operating temperature of the test node. The external heating element is controlled by an external relay to the MCU. The RS-232 communication is used to communicate with the PC under test, the RS-485 is used to communicate with the test server, and the I<sup>2</sup>C bus is used to communicate with the

GPU, communicate with the temperature sensor, and also for future expansion of the test node. Finally, the E-Pot is used to alter the voltage from the PC power supply.

#### 2.4.2 Description of RS-485

As mentioned in the previous sections, the test node network is implemented using the RS-485 electrical specification. Though RS-485 does not contain a communication protocol as part of the specification, and thus a custom protocol had to be developed for the system, RS-485 as a physical transmission standard solved many of the problems that affected the first version of this test network. RS-485 was standardized by the Electronic Industries Alliance (EIA) in association with the Telecommunications Industry Alliance (TIA) and thus the official name of the standard is TIA/EIA-485-A. The last revision of the standard was in 1998 [6].

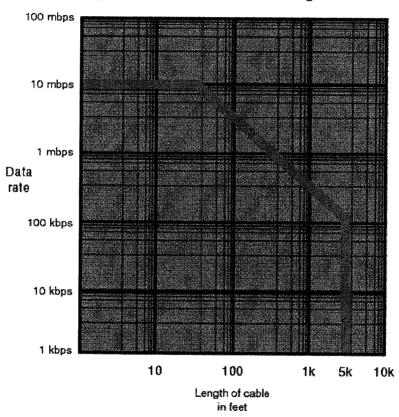

The RS-485 electrical standard is described as a half-duplex, differential signal, multi-nodal, serial communication medium. Half-duplex refers to the fact that communication can only happen in one direction at any point in time, for example, point A can send a message to point B or B can send a message to A, but A cannot send a message to B while B is sending a message to A. A typical example of half-duplex communication is a common "walkie-talkie". Differential signaling means that both the signal itself, and its digital logic inverse, are sent at the same time over two separate wires from the sender to the receiver, these wires are often referred to as a twisted pair, as in reality, the pair of wires is usually physically "twisted" together. In differential signaling, the signal is determined at the receiver by taking the difference between the two signals that are sent by the receiver. This property means that any noise that is introduced to one wire during transmission is introduced to both, and when the difference between the wires is taken at the receiver, the noise is removed from the signal. Finally, a serial signal is one in which each bit of the message is sent one at a time from the sender to the receiver. RS-485 as a standard is designed to support up to 32 nodes on one bus with a maximum length and data transmission rate that are inversely proportionate to one another. In other words, as the data transmission rate increases, the maximum length of the cable between the sender and receiver decreases, and inversely, as the length of the cable increases, the maximum data transmission rate decreases. Theoretically, the standard can support up to 10Mbit/s for a cable up to 10m or 100kbit/s for a cable length of 1200m. If the user wishes to increase the length of the cable at a given transmission rate, or the number of nodes on the bus, an rs-485 repeater is needed to increase the strength of the signal. This tradeoff is shown in Figure 2.5.

Figure 2.5. Length of Cable vs. Data Rate of an RS-485 Network [6]

In the implementation of RS-485 in this project, several things need to be mentioned. The first is that although RS-485 is defined in its standard as a half-duplex communication, this project has executed it as full-duplex by running a second twisted pair of wires for communication and thus an extra transceiver is needed at each end of the communication. The second is that even though RS-485 is a differential

communication standard, there can exist a difference in the voltage level of ground between a transmitter and a receiver, thus a wire is needed to connect the ground signals between the transmitter and receiver to alleviate this issue. In this implementation, we are using Cat-5e cable as the physical transmission medium, and thus have access to 4 twisted pairs, or 8 wires total. Wires 1 and 2 are used for transmission from the test server to the test nodes, where wire 1 is the positive signal and wire 2 is the negative signal. Wires 3 and 6 are used for transmitting from the test nodes to the test server, thus implementing a full-duplex communication, where wire 3 is for the positive signal and wire 6 is the negative signal. Finally, wire 8 is used for the ground signal which connects all ground pins of all nodes on the RS-485 bus together. The last thing that needs to be mentioned in regards to our implementation of an RS-485 network is the topology of the network. Though many topologies exist including star networks, networks with a backbone, ring networks, etc..., we chose to use the daisy-chain topology as shown in Figure 2.6. The main reason to use a daisy-chain configuration is to reduce the reflection of the signal that is present in the physical wire that is transmitting the signal. This reflection is further reduced by adding a termination resistor at either end of the communication network.

Figure 2.6. Daisy Chain Topology

## Chapter 3. Hardware and Software Selection

## **3.1 Hardware Selection**

#### 3.1.1 Microcontroller Selection

After the realization that a microcontroller on its own would not be sufficient to implement both Ethernet functionality and output to the 16 buses of test nodes, a more detailed specification list was arrived at for the microcontroller hardware. The system needs to be able to communicate both with the client computer over an Ethernet connection and the FPGA over some custom direct communication protocol and it needs the processing power and internal data memory to handle the large throughput of data while still being able to do checks and calculations for the checksum digits and any other calculations that may be needed to maintain full functionality of the system.

The need for Ethernet connectivity with the microcontroller created two options: use a microcontroller with built-in Ethernet capability, or run an external Ethernet controller. An external Ethernet controller would pull all TCP/IP stack functionality out of the main microcontroller and thus would save the internal data memory of the MCU for user programming. Unfortunately, running an external Ethernet controller adds complexity to the final board layout and it creates a bottleneck in the communication between the Ethernet controller and the microcontroller which is in control of the system as a whole. Thus it was decided that a microcontroller with built-in Ethernet functionality would be the more desirable solution for the test server. This decision instantly reduced the number of possible microcontroller vendors down to a very small group. These vendors include Microchip, the manufacturers of PIC microcontrollers [7], Freescale Semiconductor [8], Digi International, manufacturer of ARM based microcontrollers [9] and Atmel [10]. A summary of these products can be seen in Table 3.1.

| rusic sizi. Incrocontroller Summary |             |           |         |         |

|-------------------------------------|-------------|-----------|---------|---------|

| Company                             | Microchip   | Freescale | Digi    | Atmel   |

| Microprocessor                      | PIC18FXXjXX | MCF532X   | NSXXXX  | AVR32   |

| Max Processing Speed                | 41.667 MHz  | 240 MHz   | 200 MHz | 66 MHz  |

| Architecture Word Length            | 8 bits      | 32 bits   | 32 bits | 32 bits |

| Program Memory                      | 128 KB      | 128 KB    | 8 KB    | 512 KB  |

| RAM (Bytes)                         | 3,808       | 32K       | 4K      | 64K     |

| Max Pin Count                       | 80          | 256       | 388     | 144     |

| Average Cost                        | \$7.76      | \$40      | Unknown | \$15.17 |

| TCP/IP Stack Software Support       | Yes         | Yes       | Yes     | Yes     |

| Development Kit Available           | Yes         | Yes       | Yes     | Yes     |

Table 3.1. Microcontroller Summary

All listed microcontroller architectures meet the base requirements for the microcontroller in the test server, so other factors were used to choose the ideal microcontroller for the project. Cost is a large concern for this project; costs need to be kept as low as possible or one of the advantages of building a system from scratch is lost to an off-the-shelf system, thus the Freescale chip was deemed too costly. The Digi microcontroller proved difficult to find a vendor that sold the microcontroller separately from a development board and it thus was ruled out as the final deliverable of the project will consist of a custom PCB with the microcontroller mounted on the same board as the RS485 transceivers and the chosen FPGA. The Atmel microcontroller and the PIC microcontroller were the two remaining candidates, but with the PIC microcontrollers reduced cost, the availability of already licensed software compilers at the University and previous experience with the PIC microprocessor; the Microchip PIC18F97J60 microcontroller was chosen as the ideal option. Table 3.2 shows a summary of the PIC18F97J60 MCU.

| Table 3.2. Summary of Chosen MCU [11] |       |  |

|---------------------------------------|-------|--|

| PIC18F97J60                           |       |  |

| Flash Program Memory (bytes)          | 128K  |  |

| SRAM Data Memory (bytes)              | 3,808 |  |

| Ethernet Buffer (bytes)               | 8192  |  |

| 1/0                                   | 70    |  |

- . . . . . . ...  With the choice of the PIC microcontroller as the chosen device for the test server, a development kit needed to be found for the prototyping stage of development. There are two main vendors of PIC based development kits, Microchip and CCS. A comparison between the two development kits is shown in Table 3.3.

| · · · · · · · · · · · · · · · · · · · | jernene in jernene in er ereiepinene mes [12] [10] |             |  |  |  |

|---------------------------------------|----------------------------------------------------|-------------|--|--|--|

| Company                               | CCS                                                | Microchip   |  |  |  |

| MCU Used                              | PIC18F67J60                                        | PIC18F97J60 |  |  |  |

| Program Memory                        | 128K                                               | 128K        |  |  |  |

| I/O Pins available                    | 20                                                 | 70          |  |  |  |

| Access to all MCU Pins?               | No                                                 | Yes         |  |  |  |

| Available Buttons                     | 1                                                  | 4           |  |  |  |

| Available LED's                       | 3                                                  | 8           |  |  |  |

| Includes Programmer?                  | Yes                                                | No          |  |  |  |

| Cost                                  | \$149US=\$162 CDN                                  | \$194.06    |  |  |  |

Table 3.3. Summary of Available MCU Development Kits [12] [13]

Communication with the FPGA requires exactly twenty pins; 8 pins for data to the FPGA, 8 pins for data from the FPGA and 4 pins for request and acknowledge lines, therefore, even though the CCS board has 20 I/O pins available, choosing this board and MCU would eliminate the possibility of any further expansion of the test server MCU. The Microchip development kit, therefore, is the board that was chosen for the prototyping of the test server hardware.

#### 3.1.3 FPGA Selection

Much of the decision on which FPGA to use is based on past experience and on keeping costs as low as possible. Since I have had quite a bit of past experience with Altera's FPGAs and their development environment, Quartus II, it would speed up development time to use an Altera FPGA for the test server. The next major consideration was in finding a low cost FPGA that meet our requirements of running at 25MHz with enough memory bits and logic elements to contain the entire test server hardware. Since the number of logic elements required is not something that can be determined prior to synthesizing the design as a whole, the decision had to be made on clock speed, cost and available internal memory bits. A summary of available Altera devices is shown in Table 3.4.

| Table 3.4. Available FFGA Summary [14]                                                     |             |             |             |            |  |  |  |

|--------------------------------------------------------------------------------------------|-------------|-------------|-------------|------------|--|--|--|

| FPGA family                                                                                | Stratix III | Stratix II  | Cyclone III | Cyclone II |  |  |  |

| Available Speed Grades *                                                                   | 2,3,4       | 3,4,5       | 6,7,8       | 6,7,8      |  |  |  |

| Available Memory bits                                                                      | 2.1M-16.2G  | 419K-9.4M   | 424K-8.2M   | 120K-1.1M  |  |  |  |

|                                                                                            | 47.5K-      |             |             |            |  |  |  |

| Available Logic Elements                                                                   | 337.5K      | 15.6K-180K  | 5K-200K     | 4.6K-68.4K |  |  |  |

| Available User I/O                                                                         | 296-1120    | 366-1170    | 182-413     | 158-622    |  |  |  |

| FPGA Cost                                                                                  | \$540-13500 | \$223-13800 | \$31.40-740 | \$40-500   |  |  |  |

| Min. Cost that meets Specs                                                                 | \$540       | \$223       | \$52        | \$49       |  |  |  |

| Dev. Kit Cost                                                                              | \$3,000     | \$1100-3500 | \$234-4100  | \$176-1700 |  |  |  |

| * Speed grade refers to delay in ns through a macrocell in device, lower equates to faster |             |             |             |            |  |  |  |

Table 3.4. Available EPGA Summary [14]

Upon reviewing the available options for FPGA's from Altera, the Stratix family of devices are too costly, thus the Cyclone family of FPGA's will be the target device. From synthesizing the complete VHDL code that is targeted to the FPGA, the system will need 11,520 logic elements, 68 I/O pins, it must be speed grade 7 or faster and it needs 90,112 of memory bits. The cheapest device in the cyclone II and III families that matches these specifications, and is successfully "fitted" by Altera's Quartus II software, is the EP2C15AF256C7N Cyclone II FPGA. A summary of this device is shown in Table 3-5.

| EP2C15AF256C7N               |         |

|------------------------------|---------|

| Total Logic Elements         | 14,448  |

| Total Memory Bits            | 239,616 |

| Embedded Multipliers         | 52      |

| Speed Grade                  | 7       |

| Functional Temperature Range | 0-85°C  |

| Fable 3.5. | Summary | of | Chosen | <b>FPGA</b> |  |

|------------|---------|----|--------|-------------|--|

|            |         |    |        |             |  |

After coming to the conclusion that an Altera Cyclone II device would be the best choice for the FPGA in the test server, a suitable development kit needed to be found. When the search began for a development kit for this system, the total resource count needed for the VHDL code on the FPGA was unknown. Thus a development kit had to be found that provided more than enough memory bits and logic elements, and access to 52 I/O pins to communicate with the MCU and the RS485 transceiver board. The two main vendors for Altera FPGA based development kits are Altera and Terasic. A summary of their available Cyclone II development kits is shown in Table 3.6.

|                          | Altera                 | Terasic |              |

|--------------------------|------------------------|---------|--------------|

| Development Kit          | Cyclone II Starter Kit | DE2     | DE2-70       |

| FPGA Used                | EP2C20F484C7           | EP2C35  | EP2C70F896C6 |

| Logic Elements Available | 18,752                 | 33,216  | 68,416       |

| Memory Bits Available    | 239,616                | 483,840 | 1,152,000    |

| I/O available            | 315                    | 475     | 422          |

| Price                    | \$187.45               | \$582   | \$704        |

With these kits available, the DE2-70 kit was chosen as it was deemed better to err on the side of caution as far as size goes, or in other words, as only one of these development kits need to be purchased for the entire life of the project, it is better to get the larger board at the beginning to ensure that we will not have to purchase another one due to an underestimate of logic elements needed.

#### 3.1.5 RS-485 Transceiver Selection

For the selection of RS-485 transceiver, there were just a couple criteria that the selected IC needed to meet. The transceiver had to be low power, as 32 of them would be needed in the test server alone, and it needed to be available in both a surface mount and DIP package; surface mount for final PCB manufacture and DIP package for

prototyping. The selected device is the LTC485 IC manufactured by Linear Technologies. Table 3.7 has a summary of the major electrical specifications of the device.

| LTC485                               |                            |  |  |

|--------------------------------------|----------------------------|--|--|

| Max Supply Voltage                   | 12V                        |  |  |

| Recommended Supply Voltage           | 5V                         |  |  |

| Driver Output/Receiver Input Voltage | $\pm 14V$                  |  |  |

| Driver Input/Receiver Output Voltage | $-0.5V$ to $V_{CC} + 0.5V$ |  |  |

| Operating Temperature Range          | 0-70°C                     |  |  |

Table 3.7. Summary of Selected RS485 Transceiver [16]

# **3.2 Software Selection**

### 3.2.1 MCU Compiler and Programmer Selection

For any microcontroller, the first choice that must be made is whether to program in C or in the microcontroller assembly language. For this project, the decision was made for me as the TCP/IP stack that is provided by Microchip for their Ethernetenabled MCU's was written in C, thus a C compiler is needed to create the rest of the code for the MCU. There are a couple vendors that make a C compiler for the Microchip PIC microcontrollers, though the University currently only has licenses for two of them, the CCS compiler and Microchip's MPLab software.

MPLab v8.33 and Microchip's C18 were chosen as the development software and C compiler and CCS's ICD-U40 programmer and CCS load software were chosen to load the program on the MCU. MPLab v8.33 was the newest version of the software upon starting development of the MCU C code. MPLab and the C18 compiler were chosen over the CCS compiler environment as the TCP/IP Stack software was written with Microchip's MPLab software in mind, thus the beginning development of the board would be easier on MPLab than it would in the CCS C compiler as much of the work is done for me by the TCP/IP Stack software. The ICD-U40 programmer and CCS load software were chosen as my partner on this project, Stephen Fox, had already purchased the programmer for his half of this project, thus to save from buying two programmers, the same programmer was used for the test server as for the test nodes.

#### 3.2.2 FPGA Synthesizer and Programmer Selection

For the VHDL synthesizer and programmer, Altera's free Quartus II Web Edition Software Version 7.2 was used. Quartus II was chosen as the synthesizer over more expensive products from vendors such as Cadence or Synopsys as the only software capable of loading the Cyclone II FPGA is the Quartus II fitter and programmer. I have also had a substantial amount of prior experience with using the Quartus II software for development, simulation and verification and thus it was any easy choice to use Quartus II for all necessary VHDL synthesizing, simulating and programming of the FPGA.

#### 3.2.3 Electrical Schematic Editor Selection

CadSoft Eagle v5.3 was used for all electrical schematics. Eagle has the capability to convert your electrical schematics into a layout for PCB manufacture. It also has a built-in components list that includes most popular components which greatly speeds up development time. Eagle is available for Linux, Windows or Mac based computers and the University already had a license for Eagle.

# Chapter 4. VHDL Design and Verification of FPGA-Based Multi-Port UART

An early decision that had to be made was the division of processing and checking tasks that are handled by the FPGA, the MCU, and the client, respectively. To keep the costs down on the FPGA chip itself, as it is the most expensive single component in the test server, it was deemed best to keep the design of the FPGA hardware as simple as possible and leave the processing and checking tasks to the more capable, and less costly, MCU and client. As the slowest portion in the pipeline of the test server is the communication to the nodes over the RS485 connection, which is operating at a speed of 100K Baud as compared to the system clock of 25MHz, the FPGA needs to be able to buffer packets that are waiting to be sent to the nodes as the MCU is not capable of buffering data with its overall lack of data memory. Thus the functionality of the FPGA is essentially to be a multi-port UART with buffering capability.

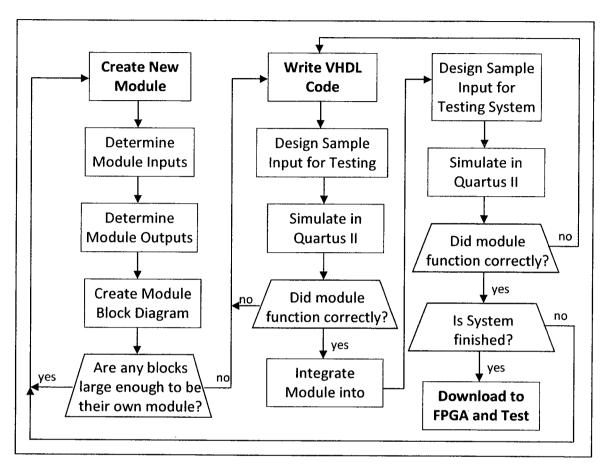

The design of the hardware for the FPGA was done in a top-down manner in VHDL. Thus the design process began with the largest component, the server itself, and determined what it needed for inputs and outputs and what its general functionality needed to be. The task was then subdivided into two halves: the first will handle data coming in from the MCU and being sent out to the RS485 network. This module is called MCU\_to\_485.vhd, it is described in detail in Section 4.2, and its code can be seen in Appendix B. The second half of the server will handle data coming in from the RS-485 network and being sent out to the MCU, and this module is called rs485\_to\_MCU.vhd, it is described in detail in Section 4.3, and its code can also be seen in Appendix B. These two halves are then subdivided into smaller modules as was deemed necessary. The design flow of each module in the system can be seen in Figure 4.1.

Figure 4.1. VHDL Design Flow

# 4.1 VHDL Design - Server

The first portion of the server.vhd code that had to be determined was the system inputs and system outputs, and consequently, the communication protocol with the MCU also had to be designed. Since FPGA's are hardware, and they operate in parallel, as opposed to the MCU which is a serial device (it executes one command at a time from the start of its program to the finish), some kind of arbitration was needed between the two halves of the FPGA and the MCU, or they may both try to speak to the MCU at the same time. There are two methods of doing this, have the two halves of the FPGA talk to each other so that they can never communicate to the MCU at the same time, or have all arbitration handled by the MCU. The first method was attempted originally, but after simulating the hardware, the better solution was to have the MCU handle all arbitration. Thus four handshake lines are needed, one request and one acknowledge line for each half of the server hardware, plus the 8 bit wide data bus from the MCU to the FPGA and the 8 bit wide data bus from the FPGA to the MCU giving a total of 20 communication lines between the MCU and the FPGA. The outputs of the server module were simple, one 16 bit wide bus for sending data out over the RS-485

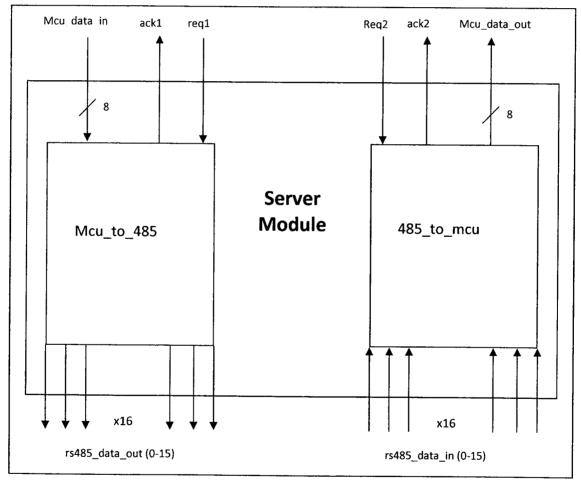

Figure 4.2. Block Diagram of Server Module

network and one 16 bit wide bus for receiving data from the RS-485 network. Thus the server module appears as in Figure 4.2.

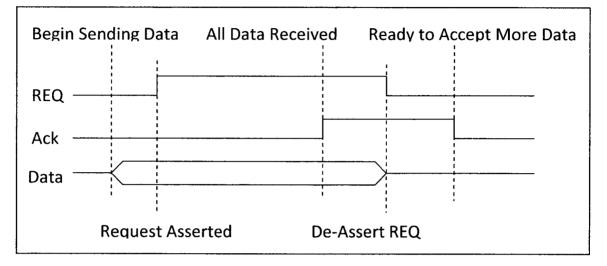

For communication from the MCU to the FPGA, the MCU readies the data to be sent and asserts the Req line, and when the FPGA asserts the ACK line, the data has been successfully received. The MCU then de-asserts REQ and removes the data from the bus and waits for the FPGA to de-assert the ACK line signifying that it is ready to receive again. If the MCU has more data to send, this process is repeated. A waveform diagram of this handshake process is shown in Figure 4.3.

Figure 4.3. Waveform of Data Transfer From MCU to FPGA

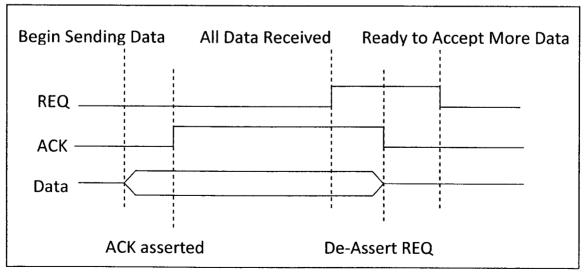

For communication from the FPGA to the MCU, the FPGA readies the data to be sent and asserts the ACK line. When the MCU has received the data, it asserts the REQ line and the FPGA de-asserts the ACK line and removes the data from the bus. The MCU will then de-assert the REQ line and the process is repeated if there is more data to send. A waveform diagram of this process is shown in Figure 4.4.

Figure 4.4. Waveform of Data Transfer From FPGA to MCU

## 4.2 VHDL Design – MCU\_to\_485 Module

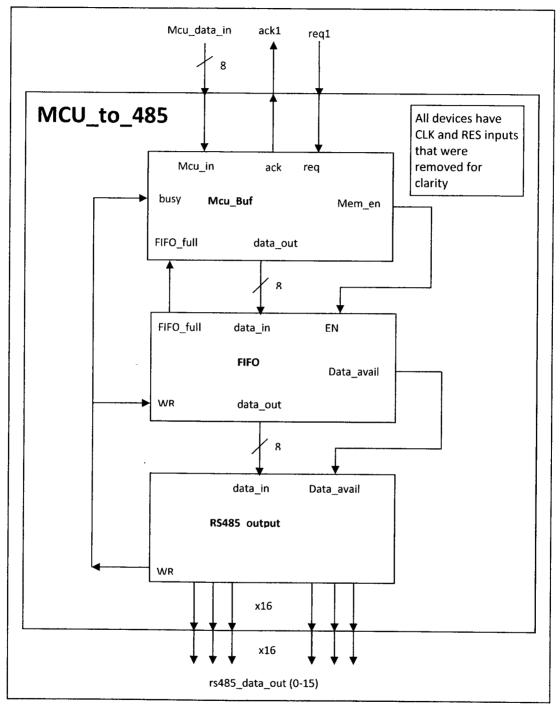

The MCU\_to\_485 module, as stated previously, accepts the 8 bit wide data from the MCU, using a handshake protocol with an acknowledge and a request line, buffers it in a FIFO block and outputs it on the proper RS-485 bus, based on the high order 4 bits of the address byte of the packet. Thus it needs one module to accept the input from the MCU, one module to output the packet serially over the RS-485 connection, and one module to buffer the data. A block diagram of the MCU\_to\_485 module can be seen in Figure 4.5.

There is only a small amount of communication needed between the modules within the MCU\_to\_485 module. Between the MCU\_buf module, which accepts the data from the MCU, and the FIFO module, which buffers all incoming data until it can be sent out; there is an 8 bit wide data bus, the FIFO\_full signal and an enable line. When the MCU\_buf module wants to send data to the FIFO, the EN line is asserted and the data is sent. When the difference between the point in memory that is being written to, and the point in memory that is being read from, is greater than 2048, which is one quarter of the FIFO memory, the FIFO\_full signal is asserted. When it is asserted, the MCU\_buf will not accept any new data until it is de-asserted. It can only be de-asserted by advancing the read address pointer which happens when the rs485\_output module reads data from the FIFO to be sent to the test nodes.

Between the MCU\_buf and RS485\_output module there is only one line common to both and that is the WR /busy signal. When the rs485\_output is ready to accept new data from the FIFO, it de-asserts the WR line and data is sent from the FIFO over an 8 bit wide bus to the RS485\_output module. The WR signal is continuously checked by the MCU\_buf module and when it is logic 1, the MCU\_buf is able to output to the FIFO, when it is logic 0, the MCU\_buf cannot write to the FIFO, thus ensuring that the same position in memory is not written to and read from simultaneously. The final signal that connects the modules together is the data\_avail signal. The FIFO asserts this signal when the difference between the read and write address pointers is 32 or greater. This signifies to the rs485\_output module that there is data waiting in the FIFO to be sent out to the RS-485 network.

Figure 4.5. Block Diagram of MCU\_to\_485 Module

The MCU\_buf module serves three main functions: communicate with the MCU through the handshaking protocol described previously, accept incoming packets one byte at a time, and write the packet, one byte at a time, to the FIFO module. It accomplishes this by utilizing 4 internal 32 byte long buffers that store one packet each. There are two internal pointers that indicate which buffer to use for reading in a new packet and for writing out the last packet to the FIFO, called switch and writing respectively. Switch is incremented when a packet is read in full from the MCU and writing is incremented when a packet is written in full to the FIFO. The module can thus both read in a new packet and write one to the FIFO at the same time. This functionality is desirable as the FIFO module can become unavailable for writing if it is being written to by the RS485\_output module and it is desirable that communication with the MCU not be disrupted in such a case as the MCU has very limited time to output the full packet to the FIFOA.

### 4.2.2 VHDL Design – FIFO Module

The FIFO module consists of a dual-port RAM megafunction, with storage of 8192 bytes, created by the Quartus II software to my specifications and a custom addressing, "wrapper" module that handles turning the RAM block into a FIFO block. This "wrapper" module allows the FIFO to have very simple inputs as all addressing is handled internally. The only input needed to write to the FIFO is to assert the EN line, and the only input needed to read from the FIFO is to de-assert the WR line.

The term FIFO describes the operation of the module, as FIFO is short for First In, First Out and thus the FIFO operates as follows. When a new byte of data is written to the module, the write\_addr pointer is incremented by one and when a byte of data is read from the module, the read\_addr pointer is incremented by one. Since both pointers are initialized to 0 by a hardware reset, the first byte of data written in is the first byte of data read out, thus First In, First Out, or FIFO.

The FIFO module also has two status flags, data\_avail and FIFO\_full. Data\_avail is asserted when there is a difference of 32 or more between the write\_addr pointer and the read\_addr pointer. This signifies that there is a packet that has been written to the FIFO that hasn't been read from the FIFO module. The FIFO\_full flag is asserted when the difference between the write\_addr pointer and the read\_addr pointer is more than 2048. Since the total storage capability of the module is 8192 bytes (or 256 packets), this signifies that the FIFO is one quarter full. When this line is asserted, the MCU\_buf module will not accept any new data until some data is read from the FIFO. This line was necessary to ensure that the data is not being written to the FIFO faster than it is being read from the FIFO.

As previously stated, the FIFO also contains a dual-port RAM megafunction that was created by Quartus to my specifications. The benefit of a dual-port RAM block as opposed to a single-port RAM block is that it can be written to and read from at the same time. This RAM module has two input ports and two output ports labeled port A and port B, and thus also has two address buses, two data input and output buses, and two enable lines. The RAM block was set up to write to the module only using port A and to read from the module only using port B. Thus the port B data input bus and the write enable signal (wren\_b) can both be set to 0, and also since data is never read from port A, the data output of port A is disregarded. Finally, when data needs to be written to, or read from, the RAM module, the "wrapper" module simply sets the port A address to write\_addr and the port B address to read\_addr, respectively. The waveform for reading from the dual-port RAM block can be seen in Figure 4.6 and the waveform for

31

| address_a |                                                                                                                 | obop i | Xi | 0001        | <u> </u> | 6002      | _X <u>!</u> _     | <u>; equo ;</u> |

|-----------|-----------------------------------------------------------------------------------------------------------------|--------|----|-------------|----------|-----------|-------------------|-----------------|

| əddress_b | hand all an a fair a | 0000   | X  | 0003        | X        | 0002      | $\overline{\chi}$ | 0001            |

| elóck     |                                                                                                                 | jun    | ١Ť | ÌĽ          | Ť        |           |                   | Litt            |

| q_s       | XX                                                                                                              | FO :   | X. | <u>; F1</u> | Ż        | <u>F2</u> | <u> </u>          | <b>F</b> 3      |

| d_b       | XX                                                                                                              | EQ FO  | Ż. | <u> </u>    |          | <b>F2</b> | Ż                 | FI              |

| m∈mciry0  |                                                                                                                 |        |    |             | FO       |           |                   |                 |

| nemory1   |                                                                                                                 |        | 1  |             | F1       |           |                   |                 |

| memory2   |                                                                                                                 |        |    |             | <br>F2;  |           |                   |                 |

| memory3   |                                                                                                                 |        |    |             | F3;      |           |                   |                 |

| memory4   |                                                                                                                 | 1.25   |    |             | <br>F4   |           |                   |                 |

Figure 4.6. Waveform of Reading From Dual-Port RAM Module

| (ddress_a  | 60          | 00 X |          | 10001         | XI            | 0602         |              | <u> X 8003</u> |

|------------|-------------|------|----------|---------------|---------------|--------------|--------------|----------------|

| ddress_b   |             | 0000 | <u> </u> |               | X             | 0002         | X            | 0001           |

| elock      | j           |      |          |               |               |              | ٦ <u> </u>   |                |

| data_a     |             | 00   | X        | <u>01 X</u>   | 02            | Υż           | 03           |                |

| data_b     |             | 00   | X        | <u>os X (</u> | <u>- 62 (</u> | Xi           | 01           |                |

| wren_a     |             |      |          |               |               | Ì            |              |                |

| vren_b     |             |      |          |               |               |              |              |                |

| q_a -      | <u>xx X</u> | FO   |          | 00            | <u> </u>      | <u>182 X</u> | 0            |                |

| d_b        | wz Ż        | FO   | 00       | X Fi          | <u> </u>      | F2 X         | <u>102 y</u> | 01             |

| memory0    |             | FO   | X        |               | 0             | 0            |              |                |

| menceryl - |             |      | X        |               | លុង           |              |              | <u>)</u> (11   |

| nemory2    |             |      |          | F2            |               | X 02         | $\chi$       | 03             |

| Asmory3    |             |      |          |               | 3             |              |              |                |

|            |             |      |          |               | 4             |              |              |                |

Figure 4.7. Waveform of Writing To Dual-Port RAM Module

The RS485\_output module serves two main functions, to read in a packet of data from the FIFO, one byte at a time and to write this data serially at a 100K baud transmission rate, to the RS-485 bus that matches the high order 4 bits of the address byte of the packet being sent out. Its operation is thus quite similar to the MCU\_buf module; however, the RS485\_output module performs its function with only one 32 byte internal buffer instead of four.

The RS485\_output module first reads in the packet from the FIFO module by deasserting the WR line and storing each byte as they arrive in the correct place in the output buffer (named outbuff in the VHDL code of the module), it then switches to the sending state of the module. In the sending state, since the system clock is running at 25MHz and the output Baud rate is 100K Baud, the clock needs to be divided by a factor of 250. After the clock is divided, the module examines the high order 4 bits of the first byte of the packet to determine the correct bus to output the data to, it then writes the packet data serially to that particular output port of the module at the correct transmission rate. It should be noted that even though the system is outputting at 100K Baud, the system does not have a data throughput rate of 100Kbps (bits per second) as there is a start bit of logic 0 and a stop bit of logic 1 and the start and finish of each byte, respectively. Thus the effective throughput of the system is actually 80Kbps.

# 4.3 VHDL Design – RS485\_to\_MCU Module