#### Miguel Alexandre Leandro Castilho

Licenciado em Ciências da Engenharia Eletrotécnica e de Computadores

# Design of a Reference Buffer for a Delta-Sigma ADC with Current DAC

Dissertação para obtenção do Grau de Mestre em

Engenharia Eletrotécnica e de Computadores

Orientador: Prof. Dr. Nuno Filipe Silva Veríssimo Paulino, Prof.

Auxiliar, Universidade Nova de Lisboa

Co-orientador: Dr. João Luís Alvernaz de Melo, Senior Mixed Signal

Design Engineer, Adesto Technologies

Júri

Presidente: Prof. Dr. Luís Filipe Lourenço Bernardo, FCT-UNL

Arguente: Prof. Dr. João Pedro Abreu de Oliveira, FCT-UNL

Vogal: Prof. Dr. Nuno Filipe Silva Veríssimo Paulino, FCT-UNL

# Design of a Reference Buffer for a Delta-Sigma ADC with Current DAC Copyright © Miguel Alexandre Leandro Castilho, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa. A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

#### ACKNOWLEDGEMENTS

I would like to thank Professor Nuno Paulino and João Melo for their support, advising and supervising during the development of this thesis. With their help, I was capable of overcoming all the problems that I faced, and I also learn a lot of things while they help me, for they teach me to see the things from a different perspective.

I would also like to thank my friends and colleagues, that support me during this journey, in special to André Toste, Bruno Ambrósio, Carlos Garcia, and José Curva, for all the funny moments, and also for their encouragement and help.

Last but not the least I would like to thank my family, in special to my parents for all of their support during my academic path, because without them this would not be possible.

#### ABSTRACT

In analog to digital conversion, it's necessary to provide a reference voltage to the Analog to Digital Converter (ADC), in order to quantify the input signal. However, as the ADC has a switch constantly commuting on its input it will cause perturbations on the reference voltage provided by the Bandgap circuit. Thus, it will interfere with the normal behaviour of the Bandgap circuit, which will longer be capable of provide the desired reference voltage.

Besides, if the reference voltage is not constant in the desired value the output code generated by the ADC will have errors.

In order to avoid conversion errors it will be needed to introduce a buffer between the Bandgap and the ADC. Thus, taking advantage from the characteristics of the buffer (low output impedance, high input impedance and unitary gain) the system will be capable of recover from the perturbations introduced by the ADC in the reference voltage.

Therefore, in this thesis are studied some of the already existing architectures of buffers, in order to see the advantages and disadvantages of each one. This way were chosen the best three architectures from a theoretical point of view, to implement and simulate, to obtain all the needed information in order to better compare them.

**Keywords:** Buffer, ADC, Bandgap, Unitary gain, Low power consumption, Reference voltage.

#### RESUMO

Em conversão de analógico para digital é necessário fornecer uma tensão de referência ao ADC de forma a quantificar o sinal de entrada. Contudo, como o ADC tem um interruptor a comutar constantemente na sua entrada vão ser introduzidas perturbações na tensão de referência fornecida pelo circuito de Bandgap. Assim, o normal funcionamento do circuito de Bandgap vai ficar em causa, o que vai impossibilitar o fornecimento da tensão de referência desejada.

Alem disso, se a tensão de referência for diferente do desejado então o código na saída do ADC vai apresentar erros.

De forma a evitar erros de conversão será necessário introduzir um buffer entre o Badgap e o ADC. Portanto, ao tirar partido das caracteirísticas do buffer (baixa impedância de saída, alta impedância de entrada, e ganho unitário) o sistema será capaz de recuperar das perturbações introduzidas pelo ADC na tensão de referência.

Portanto, nesta dissertação são estudadas algumas arquiteturas de buffers já existentes, para ver quais são as vantagens e desvantagens de cada uma. Desta forma foram escolhidas as três melhores arquiteturas do ponto de vista teórico, para implementar e simular, para obter toda a informação necessária de forma a compará-las melhor.

**Palavras-chave:** Buffer, ADC, Bandgap, Ganho unitário, Baixo consumo energético, Tensão de referência.

## CONTENTS

| 1 | Intr | oduction                                                   | 1  |

|---|------|------------------------------------------------------------|----|

|   | 1.1  | Context and Motivation                                     | 1  |

|   | 1.2  | Main Contributions and Problem Approach                    | 2  |

|   | 1.3  | Thesis Structure                                           | 3  |

| 2 | Stat | e of the Art                                               | 5  |

|   | 2.1  | Common Drain (CD) Amplifier                                | 5  |

|   | 2.2  | Flipped Voltage Follower (FVF)                             | 7  |

|   | 2.3  | FVF Differential Structure (DFVF)                          | 9  |

|   | 2.4  | Bulk-driven FVF (BdFVF)                                    | 10 |

|   | 2.5  | Level Shifted FVF (LSFVF)                                  | 12 |

|   | 2.6  | Wide bandwidth buffer (Wbb)                                | 14 |

|   | 2.7  | Super Source Follower (SSF)                                | 16 |

|   | 2.8  | Buffer with high linearity and adjustable output impedance | 17 |

|   | 2.9  | Two stage QFG buffer                                       | 19 |

|   | 2.10 | Low Drop-out (LDO) regulators                              | 20 |

|   |      | 2.10.1 Shunt-series LDO (SsLDO)                            | 21 |

|   |      | 2.10.2 Capacitor free LDO (CfLDO)                          | 23 |

|   |      | 2.10.3 Cascaded FVF (CAFVF)                                | 25 |

|   |      | 2.10.4 Buffered FVF (BFVF)                                 | 26 |

|   | 2.11 | Results analysis                                           | 28 |

| 3 | Buff | fer Implementation                                         | 35 |

|   | 3.1  | GM/ID Technique                                            | 35 |

|   | 3.2  | Sizing Methodology                                         | 38 |

|   | 3.3  | Error amplifiers                                           | 39 |

|   |      | 3.3.1 Two stage amplifier with Miller compensation         | 40 |

|   |      | 3.3.2 Current Mirror OTA                                   | 41 |

|   | 3.4  | DAC                                                        | 43 |

|   | 3.5  | Delta-Sigma ADC                                            | 44 |

|   | 3.6  | Common Drain Amplifier                                     | 45 |

|   | 3.7  | Shunt-series LDO (SsLDO)                                   | 46 |

#### CONTENTS

|    | 3.8   | Capacitor free LDO (CfLDO)                  | 49 |

|----|-------|---------------------------------------------|----|

|    | 3.9   | Buffered FVF (BFVF)                         | 52 |

| 4  | Sim   | ulation Results                             | 55 |

|    | 4.1   | Common Drain Amplifier                      | 55 |

|    |       | 4.1.1 Miller compensated amplifier          | 55 |

|    |       | 4.1.2 Current Mirror OTA                    | 60 |

|    | 4.2   | Shunt-series LDO (SsLDO)                    | 63 |

|    |       | 4.2.1 Miller compensated amplifier          | 63 |

|    |       | 4.2.2 Current Mirror OTA                    | 66 |

|    | 4.3   | Capacitor free LDO (CfLDO)                  | 69 |

|    | 4.4   | Buffered FVF (BFVF)                         | 73 |

|    |       | 4.4.1 Miller compensated amplifier          | 73 |

|    |       | 4.4.2 Current Mirror OTA                    | 77 |

|    | 4.5   | Comparison between the different topologies | 80 |

| 5  | Con   | clusions and Future Work                    | 85 |

|    | 5.1   | Conclusions                                 | 85 |

|    | 5.2   | Future Work                                 | 86 |

| Bi | bliog | raphy                                       | 87 |

# LIST OF FIGURES

| 1.1  | High level representation of a buffer                                         | 2  |

|------|-------------------------------------------------------------------------------|----|

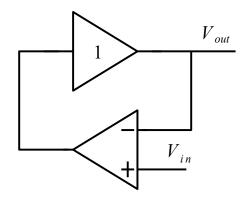

| 1.2  | Buffer with error amplifier                                                   | 3  |

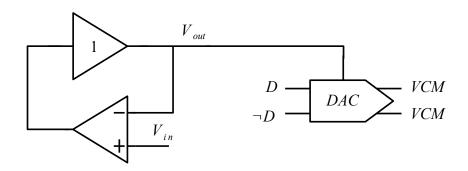

| 1.3  | Buffer with error amplifier providing a reference voltage to a DAC            | 3  |

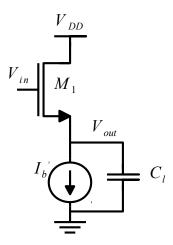

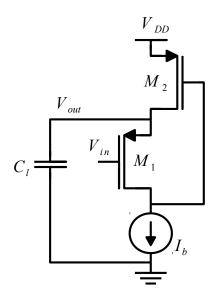

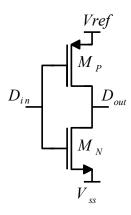

| 2.1  | Common Drain Amplifier                                                        | 6  |

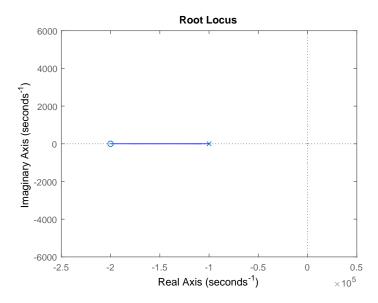

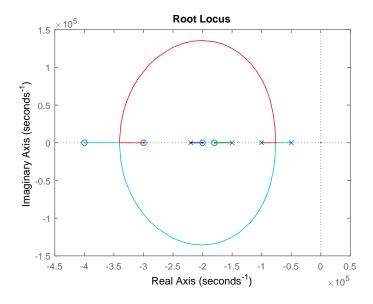

| 2.2  | Root Locus of the CD                                                          | 7  |

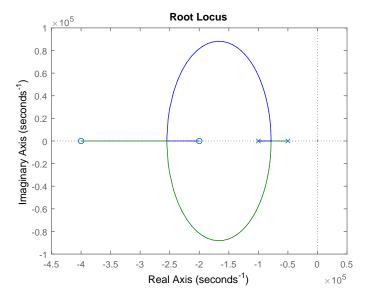

| 2.3  | Flipped Voltage Follower                                                      | 8  |

| 2.4  | Root Locus of the FVF                                                         | 8  |

| 2.5  | FVF Differential Structure                                                    | 9  |

| 2.6  | Root Locus of the DFVF                                                        | 10 |

| 2.7  | Bulk-driven FVF                                                               | 11 |

| 2.8  | Level Shifted FVF                                                             | 12 |

| 2.9  | Root Locus of the LSFVF                                                       | 14 |

| 2.10 | Wide bandwidth buffer                                                         | 14 |

| 2.11 | Root Locus of the Wbb                                                         | 15 |

| 2.12 | Super Source Follower                                                         | 16 |

| 2.13 | Buffer with high linearity and adjustable output impedance                    | 17 |

| 2.14 | Root Locus of the buffer with high linearity and adjustable output impedance. | 18 |

| 2.15 | Two stage QFG buffer                                                          | 19 |

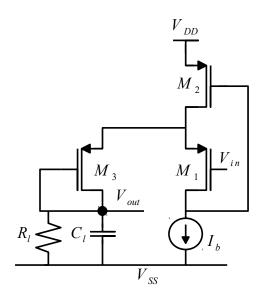

| 2.16 | Shunt-series LDO                                                              | 21 |

|      | Transconductance Amplifier                                                    | 22 |

| 2.18 | Root Locus of the SsLDO                                                       | 22 |

| 2.19 | Capacitor free LDO                                                            | 23 |

|      | Cascaded FVF based LDO                                                        | 25 |

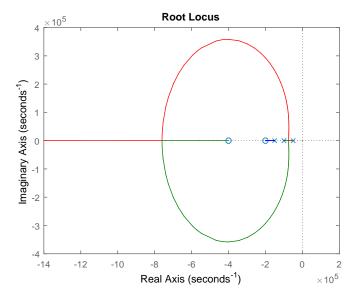

|      | Buffered FVF based LDO                                                        | 27 |

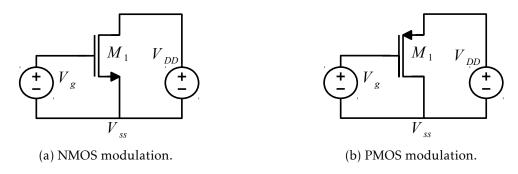

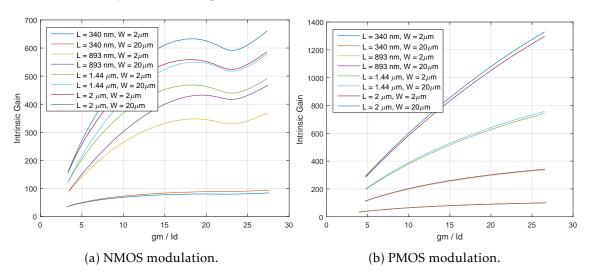

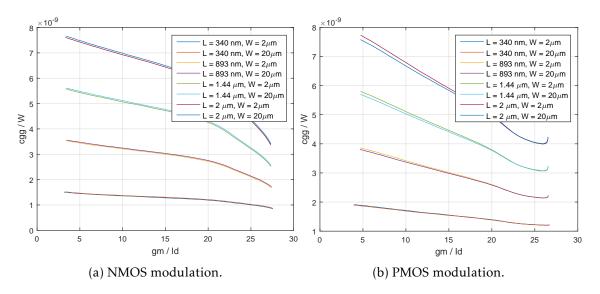

| 3.1  | Transistors modulation                                                        | 36 |

| 3.2  | Intrinsic gain modulation                                                     | 36 |

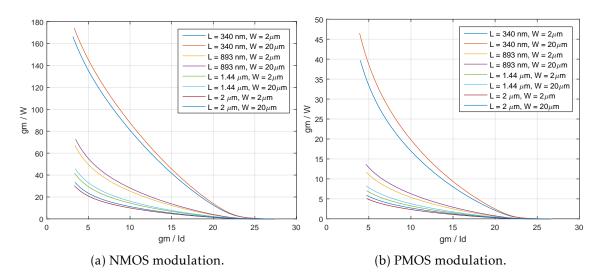

| 3.3  | GM modulation                                                                 | 37 |

| 3.4  | Drain current modulation                                                      | 37 |

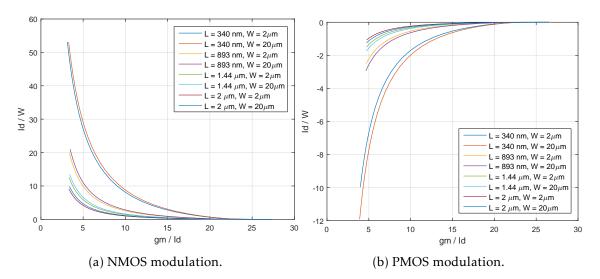

| 3.5  | GDS modulation                                                                | 37 |

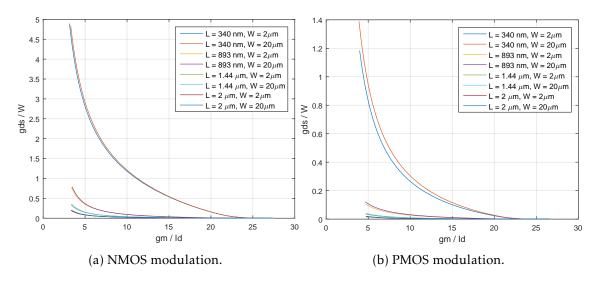

| 3.6  | CGG modulation                                                                | 38 |

| 3.7  | CDS modulation.                                                               | 38 |

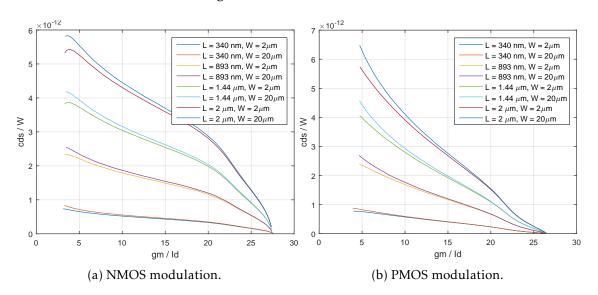

| 3.8  | Flow chart demonstrating the methodology used to size the transistors of ar-  |    |

|------|-------------------------------------------------------------------------------|----|

|      | chitectures used to implement the buffer                                      | 39 |

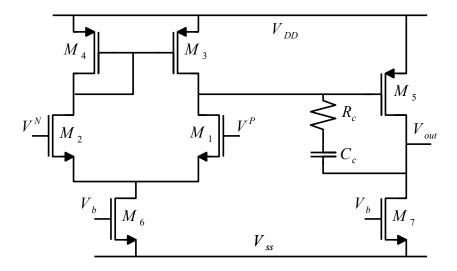

| 3.9  | Miller compensated amplifier                                                  | 40 |

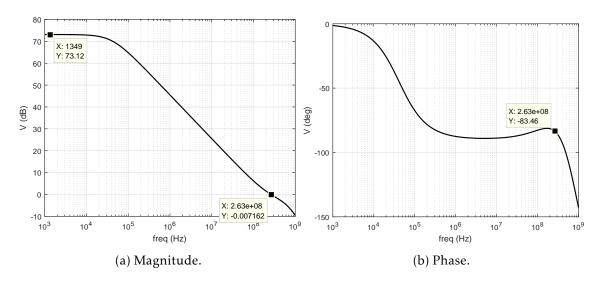

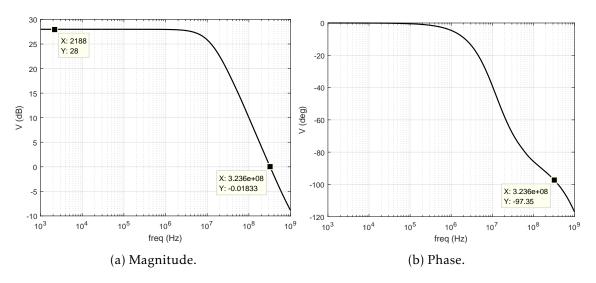

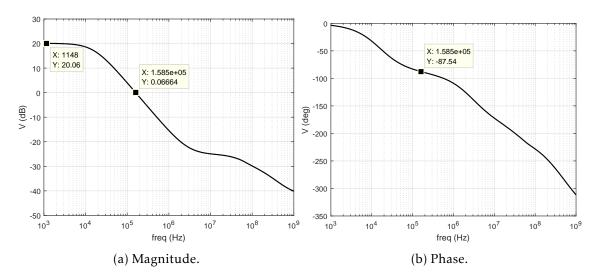

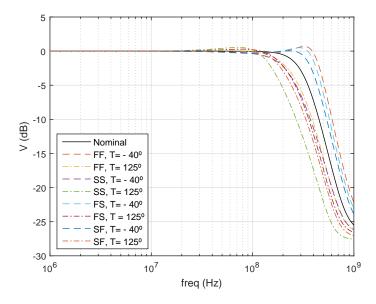

| 3.10 | Frequency response of the Miller compensated amplifier                        | 41 |

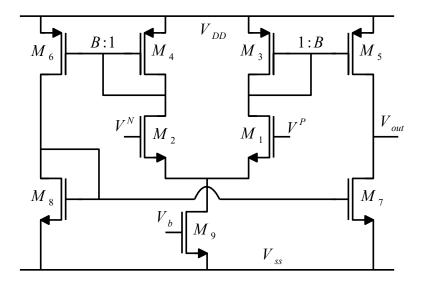

| 3.11 | Current mirror OTA                                                            | 42 |

| 3.12 | Frequency response of the Current Mirror OTA                                  | 42 |

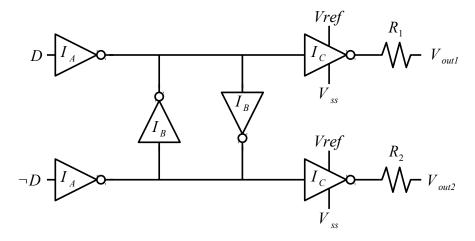

| 3.13 | DAC architecture                                                              | 43 |

| 3.14 | Inverter architecture                                                         | 44 |

| 3.15 | First integrator of the Delta-Sigma ADC                                       | 44 |

| 3.16 | Common Drain Amplifier with the biasing circuit                               | 45 |

| 3.17 | Differential pair                                                             | 47 |

| 3.18 | Frequency response of the Differential pair                                   | 47 |

| 3.19 | Shunt-series LDO with the biasing circuit                                     | 48 |

| 3.20 | Capacitor free LDO                                                            | 49 |

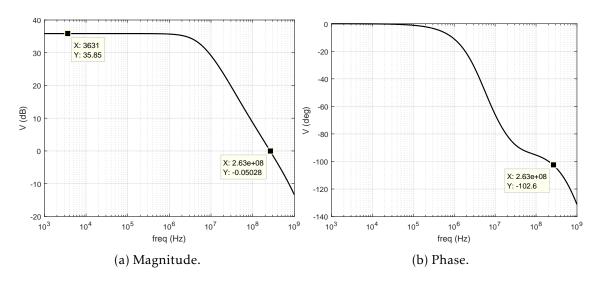

| 3.21 | Frequency response of the fast differential stage                             | 50 |

| 3.22 | Frequency response of the slow operational amplifier                          | 51 |

| 3.23 | Buffered FVF with the biasing circuit                                         | 52 |

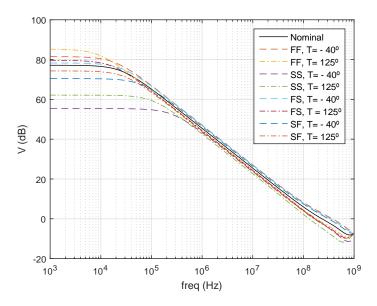

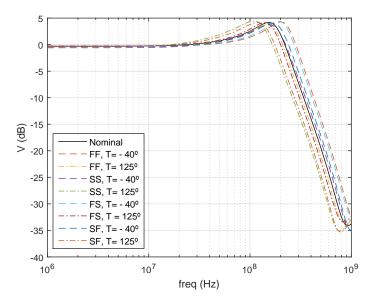

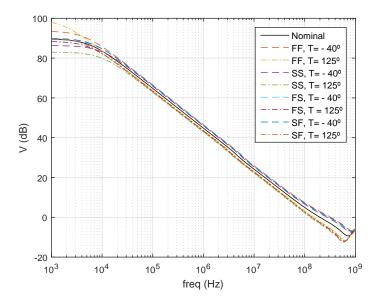

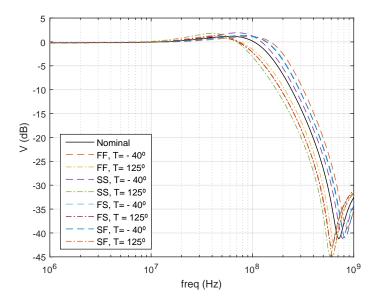

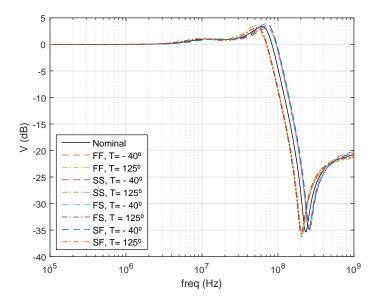

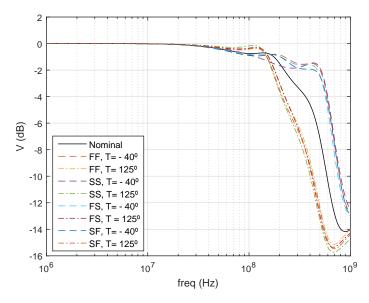

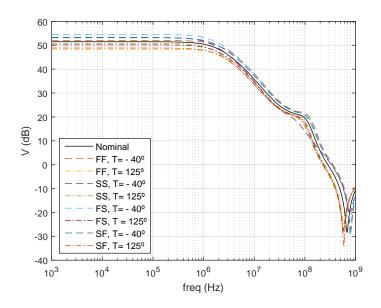

| 4.1  | Gain of the CD amplifier, using the Miller compensated amplifier              | 56 |

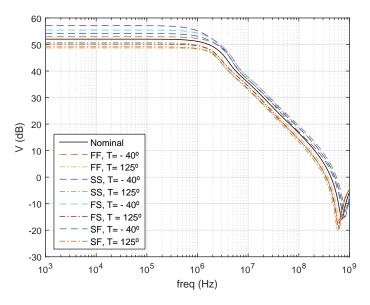

| 4.2  | Positive power supply rejection ratio of the CD amplifier, using the Miller   | 50 |

| 4.2  | compensated amplifier                                                         | 56 |

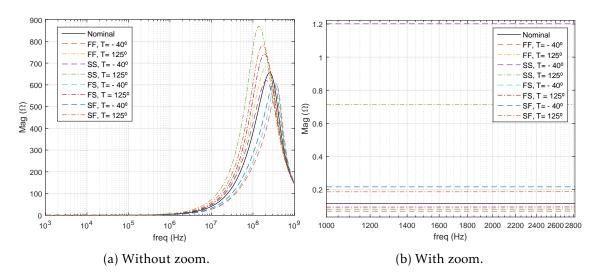

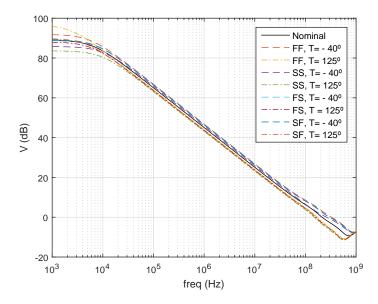

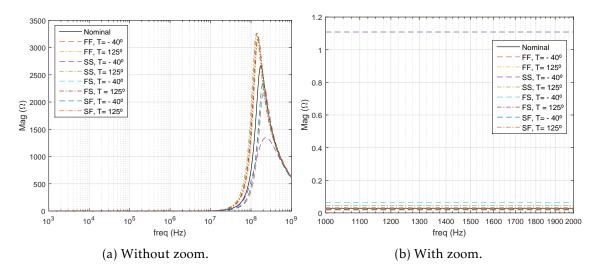

| 4.3  | Output Impedance of the CD amplifier, using the Miller compensated amplifier. | 57 |

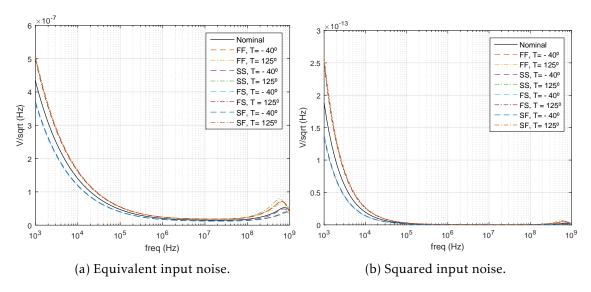

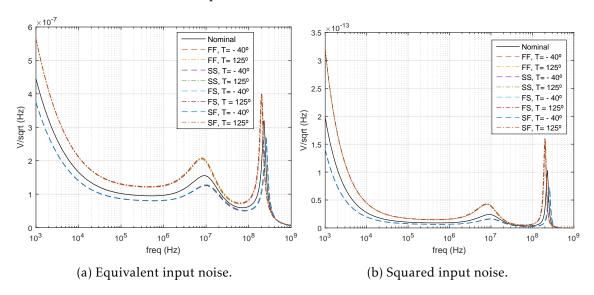

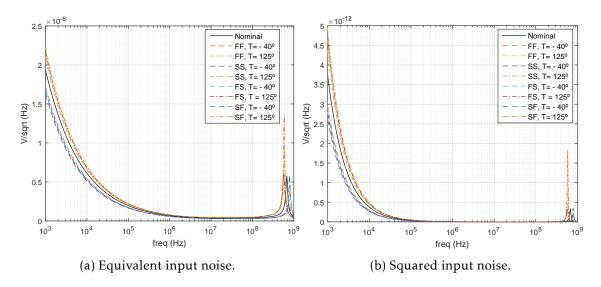

| 4.4  | Input referred noise of the CD amplifier, using the Miller compensated am-    | 37 |

| 1.1  | plifier                                                                       | 57 |

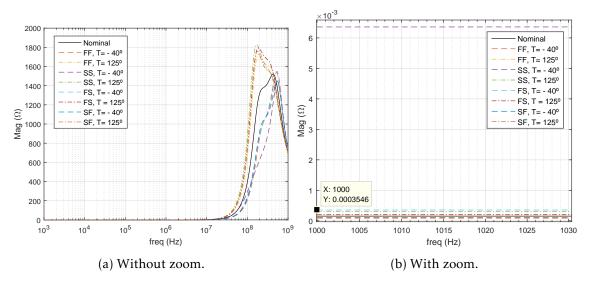

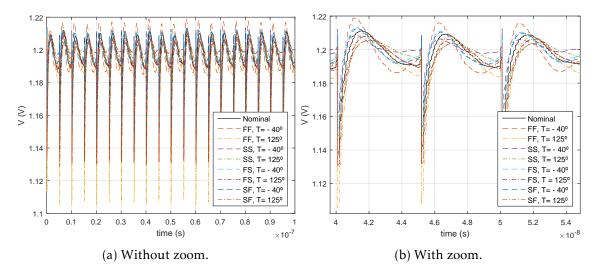

| 4.5  | Output transient voltage of the CD amplifier, using the Miller compensated    | 37 |

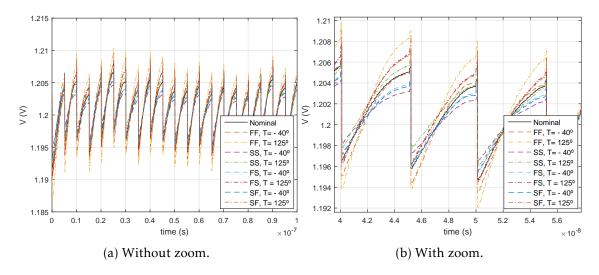

| 1.5  | amplifier                                                                     | 58 |

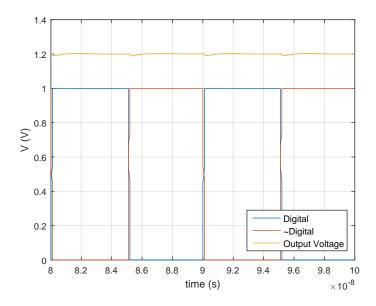

| 4.6  | Perturbation in the output voltage.                                           | 58 |

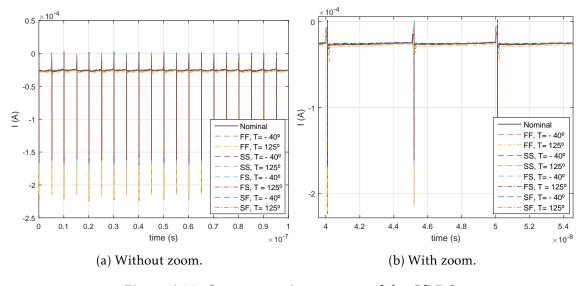

| 4.7  | Output transient current of the CD amplifier, using the Miller compensated    |    |

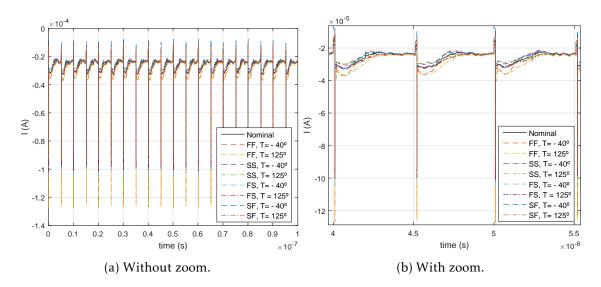

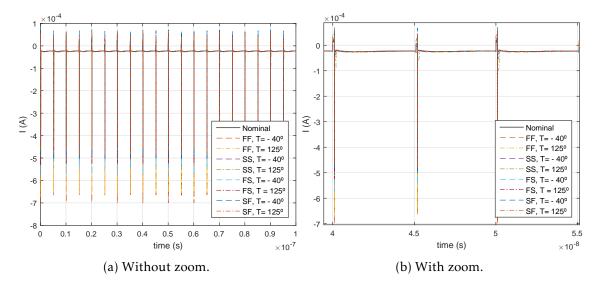

|      | amplifier                                                                     | 59 |

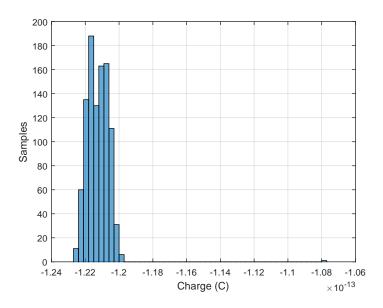

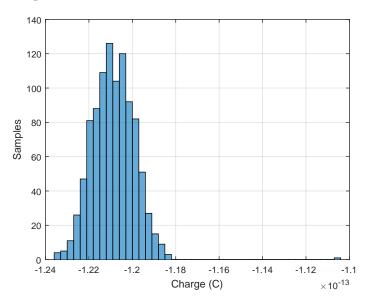

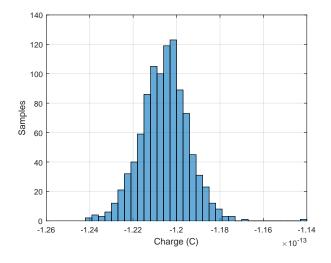

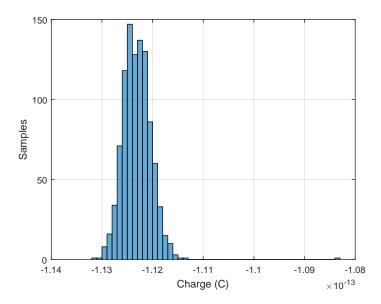

| 4.8  | Charge at the output of the CD amplifier, using the Miller compensated am-    |    |

|      | plifier                                                                       | 59 |

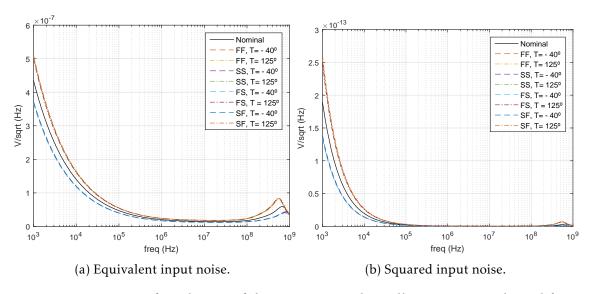

| 4.9  | Gain of the CD amplifier, using the Current Mirror OTA                        | 60 |

| 4.10 | Positive power supply rejection ratio of the CD amplifier, using the Current  |    |

|      | Mirror OTA                                                                    | 60 |

| 4.11 | Output Impedance of the CD amplifier, using the Current Mirror OTA            | 61 |

| 4.12 | Input referred noise of the CD amplifier, using the Current Mirror OTA        | 61 |

|      | Output transient voltage of the CD amplifier, using the Current Mirror OTA.   | 62 |

|      | Output transient current of the CD amplifier, using the Current Mirror OTA.   | 62 |

| 4.15 | Charge at the output of the CD amplifier, using the Current Mirror OTA        | 63 |

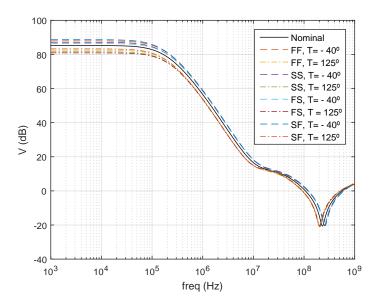

| 4.16 | Gain of the SsLDO, using the Miller compensated amplifier                     | 63 |

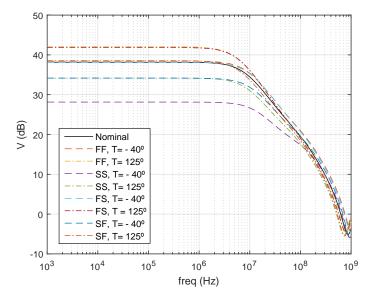

| 4.17 | Positive power supply rejection ratio of the SsLDO, using the Miller compensated applifier | 64 |

|------|--------------------------------------------------------------------------------------------|----|

| 1 10 | sated amplifier.                                                                           |    |

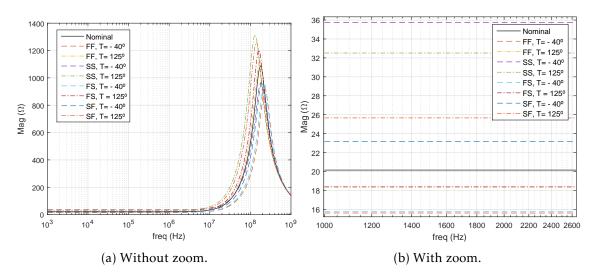

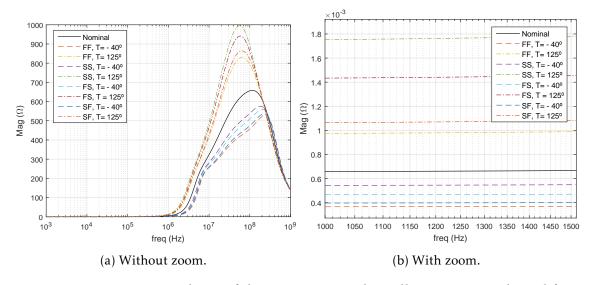

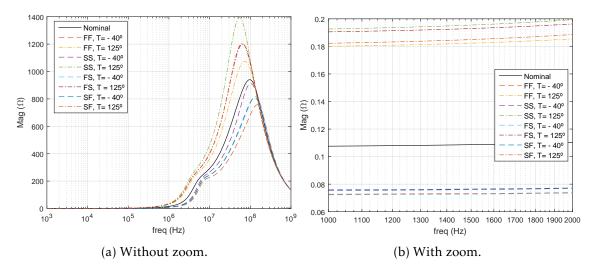

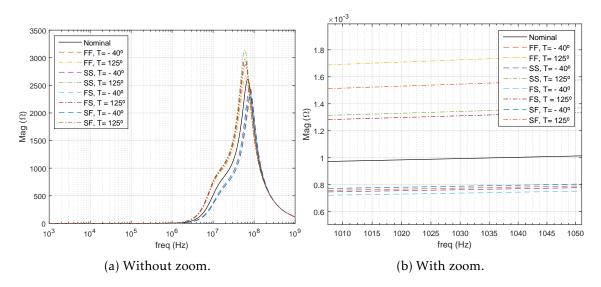

|      | Output Impedance of the SsLDO, using the Miller compensated amplifier                      | 64 |

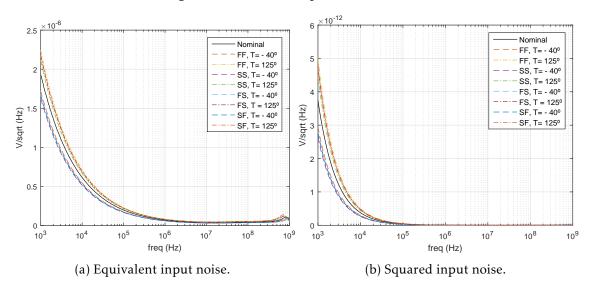

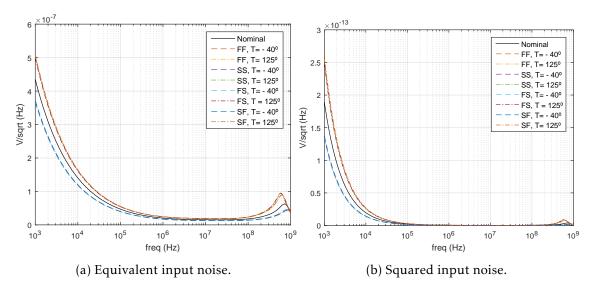

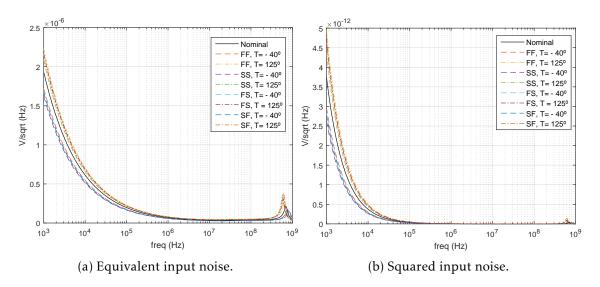

|      | Input referred noise of the SsLDO, using the Miller compensated amplifier.                 | 65 |

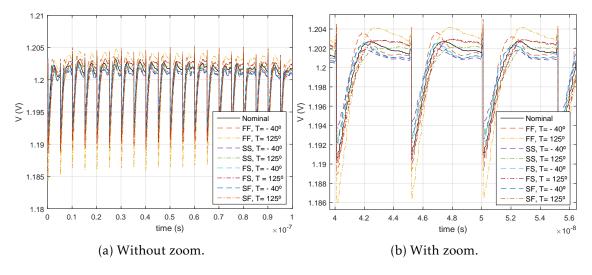

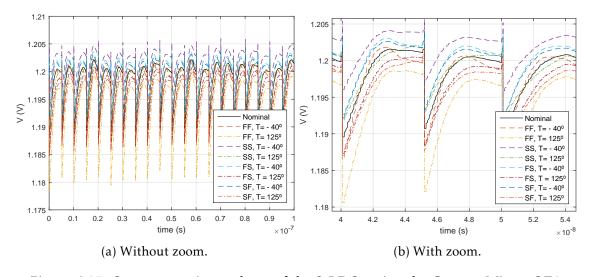

|      | Output transient voltage of the SsLDO, using the Miller compensated amplifier.             | 65 |

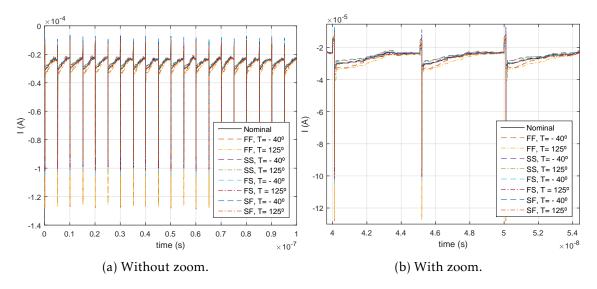

|      | Output transient current of the SsLDO, using the Miller compensated amplifier.             | 66 |

|      | Charge at the output of the SsLDO, using the Miller compensated amplifier.                 | 66 |

|      | Gain of the SsLDO, using the Current Mirror OTA                                            | 67 |

| 4.24 | Positive power supply rejection ratio of the SsLDO, using the Current Mirror               |    |

|      | OTA                                                                                        | 67 |

|      | Output Impedance of the SsLDO, using the Current Mirror OTA                                | 68 |

|      | Input referred noise of the SsLDO, using the Current Mirror OTA                            | 68 |

| 4.27 | Output transient voltage of the SsLDO, using the Current Mirror OTA                        | 68 |

|      | Output transient current of the SsLDO, using the Current Mirror OTA                        | 69 |

|      | Charge at the output of the SsLDO, using the Current Mirror OTA                            | 69 |

| 4.30 | Gain of the CfLDO                                                                          | 70 |

| 4.31 | Positive power supply rejection ratio of the CfLDO                                         | 70 |

| 4.32 | Output Impedance of the CfLDO                                                              | 71 |

| 4.33 | Input referred noise of the CfLDO                                                          | 71 |

| 4.34 | Output transient voltage of the CfLDO                                                      | 72 |

| 4.35 | Output transient current of the CfLDO                                                      | 72 |

| 4.36 | Charge at the output of the CfLDO                                                          | 72 |

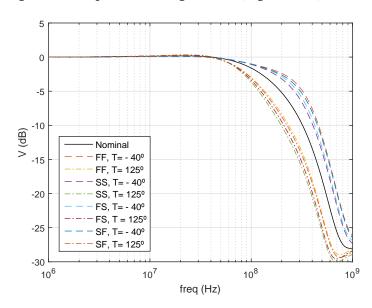

| 4.37 | Gain of the BFVF, using the Miller compensated amplifier                                   | 73 |

| 4.38 | Positive power supply rejection ratio of the BFVF, using the Miller compen-                |    |

|      | sated amplifier.                                                                           | 74 |

| 4.39 | Output Impedance of the BFVF, using the Miller compensated amplifier                       | 74 |

| 4.40 | Input referred noise of the BFVF, using the Miller compensated amplifier                   | 75 |

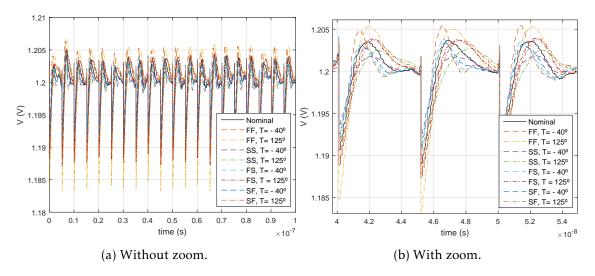

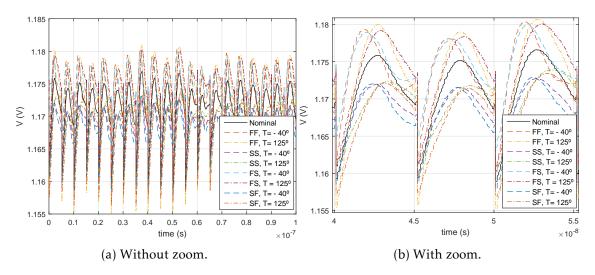

| 4.41 | Output transient voltage of the BFVF, using the Miller compensated amplifier.              | 75 |

| 4.42 | Output transient current of the BFVF, using the Miller compensated amplifier.              | 76 |

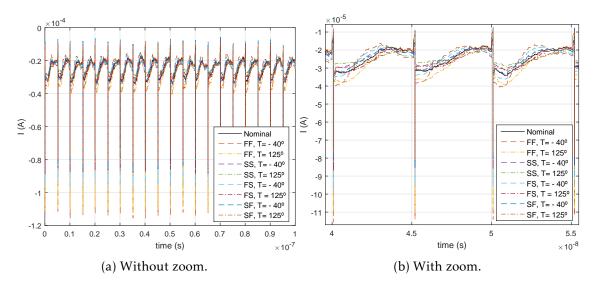

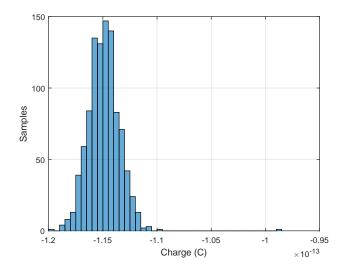

| 4.43 | Charge at the output of the BFVF, using the Miller compensated amplifier                   | 76 |

| 4.44 | Gain of the BFVF, using the Current Mirror OTA                                             | 77 |

|      | Positive power supply rejection ratio of the BFVF, using the Current Mirror                |    |

|      | OTA                                                                                        | 77 |

| 4.46 | Output Impedance of the BFVF, using the Current Mirror OTA                                 | 78 |

| 4.47 | Input referred noise of the BFVF, using the Current Mirror OTA                             | 78 |

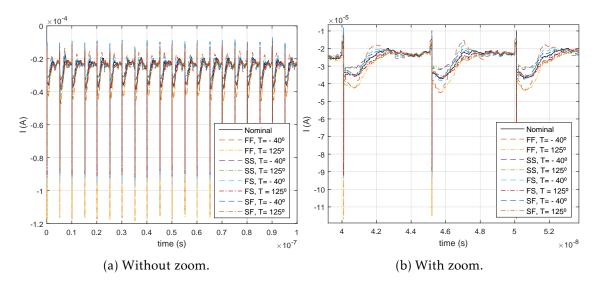

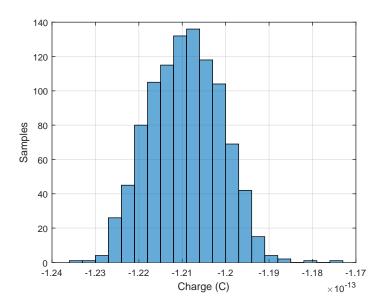

| 4.48 | Output transient voltage of the BFVF, using the Current Mirror OTA                         | 79 |

| 4.49 | Output transient current of the BFVF, using the Current Mirror OTA                         | 79 |

|      | Charge at the output of the BFVF, using the Current Mirror OTA                             | 80 |

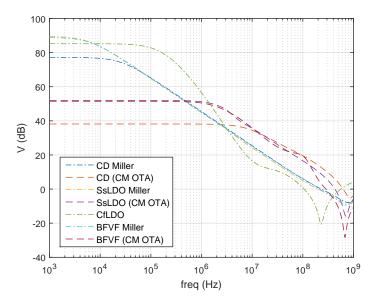

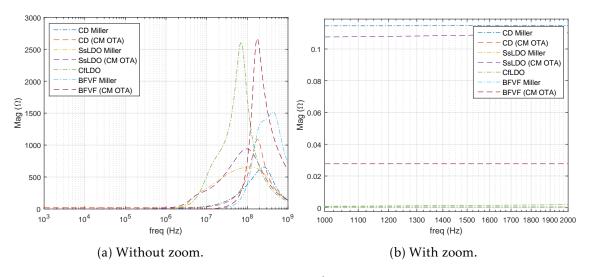

|      | Gain comparison                                                                            | 80 |

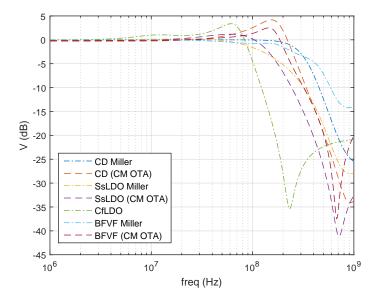

|      | Positive power supply rejection ratio comparison                                           | 81 |

|      | Output Impedance comparison                                                                | 81 |

#### List of Figures

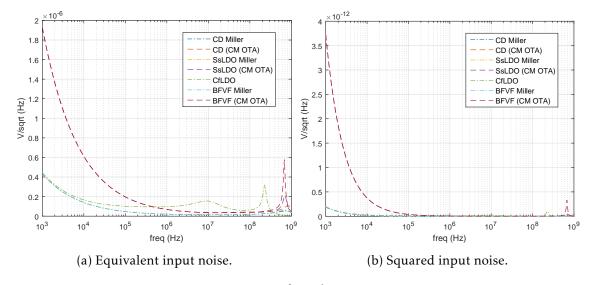

| 4.54 Input referred noise comparison     | 82 |

|------------------------------------------|----|

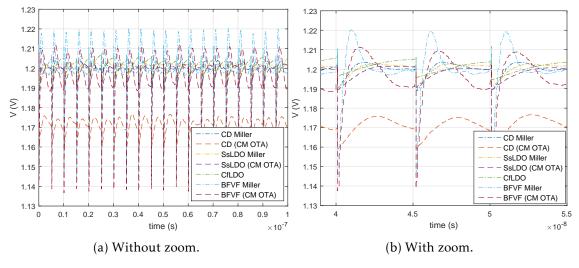

| 4.55 Output transient voltage comparison | 82 |

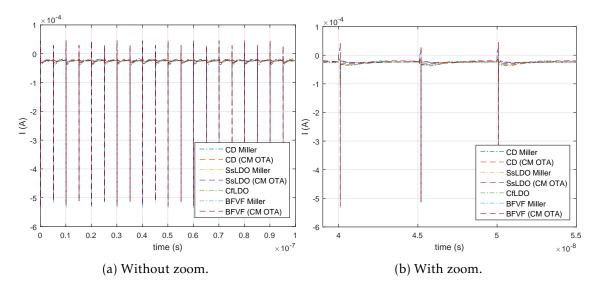

| 4.56 Output transient current comparison | 83 |

# LIST OF TABLES

| 1.1 | Buffer design specifications                         | 2  |

|-----|------------------------------------------------------|----|

| 2.1 | Coarse design of the different topologies (Part 1/2) | 28 |

| 2.2 | Coarse design of the different topologies (Part 2/2) | 28 |

| 2.3 | Comparison of the different topologies (Part 1/4)    | 30 |

| 2.4 | Comparison of the different topologies (Part 2/4)    | 31 |

| 2.5 | Comparison of the different topologies (Part 3/4)    | 32 |

| 2.6 | Comparison of the different topologies (Part 4/4)    | 33 |

| 3.1 | Transistors size of the Miller compensated amplifier | 41 |

| 3.2 | Transistors size of the Current Mirror OTA           | 43 |

| 3.3 | Transistors size of the DAC inverters                | 44 |

| 3.4 | Transistors size of the Common Drain amplifier       | 46 |

| 3.5 | Transistors size of the Differential pair            | 48 |

| 3.6 | Transistors size of the Shunt-series LDO             | 49 |

| 3.7 | Transistors size of the Capacitor free LDO           | 50 |

| 3.8 | Transistors size of the Buffered FVF                 | 53 |

| 4.1 | Comparison of the different topologies               | 84 |

| 5.1 | Best and worse architectures in each characteristic  | 86 |

#### ACRONYMS

AC Alternating Current

ADC Analog to Digital Converter

BdFVF Bulk-driven FVF BFVF Buffered FVF

CAFVF Cascaded FVF

CD Common Drain

CfLDO Capacitor free LDO

CMRR Common mode rejection ratio

CS common source

DAC Digital to Analog Converter

DC Direct Current

DFVF FVF Differential Structure

FVF Flipped Voltage Follower

GBW Gain Bandwidth Product

LDO Low Drop-out LSFVF Level Shifted FVF

OA Operational Amplifier

OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

PSRR Power Supply Rejection Ratio

#### ACRONYMS

QFG Quasi-Floating Gate

SoC system-on-chip

SSF Super Source Follower

SsLDO Shunt-series LDO

THD Total Harmonic Distortion

THD+N Total Harmonic Distortion Plus Noise

Wbb Wide bandwidth buffer

CHAPTER

#### Introduction

This Chapter describes the main features of a voltage buffer as well as its importance in integrated circuit. It also explains the purpose of this project and the special importance of a buffer in analog to digital conversion. Finally, a brief resume of the contents present in each Chapter of this thesis is presented.

#### 1.1 Context and Motivation

A voltage buffer is a circuit that presents three main features: low output impedance, high input impedance and unitary gain. These characteristics make this kind of circuits very useful for applications where it's necessary to connect two different circuits, for the signal to be transferred without one circuit affecting the behaviour of the other one. This can occur due to the large amount of current required when the delta-sigma ADC start the conversion process, which will cause a perturbation in the reference voltage. In analog to digital conversion, the ADC compares the input voltage to a reference voltage to produce the digital binary output code. So if the reference voltage has perturbations, then the generated code may be wrong, which may cause unwanted behaviours on the system where the ADC is inserted.

Figure 1.1 is a high-level representation of a buffer that can be represented as an amplifier with an unitary gain, or it can also be represented with a voltage follower, and with an ideal opamp.

This project consists in the design of a reference buffer for a delta-sigma ADC with current Digital to Analog Converter (DAC). To do so, it will be necessary to study different approaches and see the benefits and the disadvantages of using each one. After that, it's necessary to choose the approach that gives the best results according to the desired specifications, presented in Table 1.1.

Figure 1.1: High level representation of a buffer.

These specifications are very restricted, since the delta-sigma ADC is already implemented and according to that implementation it will be needed to build a buffer capable of achieve such requirements.

| Bandwidth                                    | $100 - 200 \ MHz$               |

|----------------------------------------------|---------------------------------|

| Technology                                   | UMC 130 nm                      |

| Reference Voltage                            | 1.2 V                           |

| Supply Voltage                               | 2.5 V                           |

| Output Impedance (DC)                        | < 500 Ω                         |

| Biasing Current                              | < 200 µA                        |

| η                                            | ≥ 30 %                          |

| Positive Power Supply Rejection Ratio (PSRR) | > 40 dB                         |

| $V_{Ns}$                                     | $<\frac{1.2}{2^{12}}\sqrt{OSR}$ |

| OSR                                          | 100                             |

Table 1.1: Buffer design specifications.

In Table 1.1  $V_{Ns}$  represents the noise of the system and  $\eta$  represents the efficiency of the system. As the supply voltage and the reference voltage of the system have different values it isn't possible to achieve an efficiency of 100%. Thus, in an ideal situation, the maximum efficiency attainable is  $\eta = \frac{1.2 \times i}{2.5 \times i} \times 100 = 48\%$ . Therefore, the results displayed on the last chapters are normalized, which means that 48% is equivalent to 100%.

# 1.2 Main Contributions and Problem Approach

The purpose of this project is to implement a system capable of provide a stable reference voltage to the delta-sigma ADC. To do so it is needed to introduce a buffer between the Bandgap and the ADC. With such a system it's assured that the reference voltage provided by the Bandgap circuit is not affected by the ADC. Since the buffer will be capable of recover from the perturbations that the ADC will cause on its output voltage.

Thus, the first step to do was stablish the conditions in which the circuits will be implemented and simulated. Beforehand, it was noticed that was necessary to use an error amplifier on the feedback of the buffer, in order to the voltage at the output of the buffer be equal to the reference voltage provided to the system. Besides, the error amplifier also

helps to increase the positive PSRR, which means that greater gain of the error amplifier results in a greater PSRR.

In Figure 1.2 is shown an high level representation of the system after adding the amplifier to the feedback of the buffer.

Figure 1.2: Buffer with error amplifier.

Since this buffer is being projected to provide a reference voltage for a delta-sigma ADC with current DAC is also needed to take that into account. Thus, in Figure 1.3, is an high level representation of the system after adding the DAC. As this is a circuit that receives digital signals controlled by a clock, it will introduce perturbations in the reference voltage, which allows to simulate the behaviour of the ADC.

Figure 1.3: Buffer with error amplifier providing a reference voltage to a DAC.

#### 1.3 Thesis Structure

This thesis is structured in five chapters, where are presented the most relevant aspects for the development of this project.

In the Chapter 1 are presented the fundamental aspects of a buffer and the main goals to achieve. In Chapter 2 are introduced some of the already existing architectures, as well as a brief theoretical analysis of them. In Chapter 3 are selected the best three architectures from the theoretical point of view, and are explained the methodologies

used to implement those architectures. In Chapter 4 are displayed the results obtained form the architectures defined in Chapter 3 and is also done a comparison between those architectures in order to see the advantages and disadvantages of each one. Finally, in Chapter 5 are summarized all the considerations and methodologies used and is also suggested some work to develop as a way to improve this project.

C H A P T E R

#### STATE OF THE ART

In this chapter some of the already existing topologies of buffers will be studied. In each section a theoretical analysis of the buffer presented will be made, in order to understand its main features such as the gain, output impedance, noise and output swing. After that, a coarse sizing will be made, in order to see the energetic efficiency of each topology for a certain output impedance. Lastly, at the end of this chapter, a comparison between the different topologies will be made in order to see which are the advantages and disadvantages of each topology.

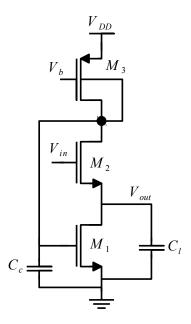

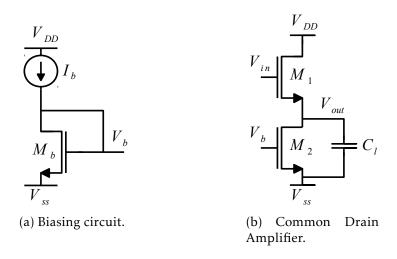

## 2.1 Common Drain (CD) Amplifier

A Common Drain (CD) amplifier (Figure 2.1) is the simplest possible circuit that works as a voltage buffer. However, it has a great disadvantage, because the current through transistor  $M_1$  is dependent of the output current [1], and the gain of the circuit can be less than one for resistive loads [2]. Therefore, if it is desired to obtain a small output impedance, is necessary to increase the aspect ratio of  $M_1$ , resulting in a large power consumption [1]. Another disadvantage of this circuit is the limited sourcing capability by the biasing current, and the absence of linearity in the output [3]. The main advantage of this circuit is its simplicity and the capability of sinking large current from the load [2].

Analysing this circuit, it can be concluded that the output impedance is low and the gain of the circuit is approximately unitary.

$$R_O = \frac{1}{gm_1 + gds_1} \tag{2.1}$$

$$A_V(s=0) = \frac{gm_1}{gds_1 + gm_1} \tag{2.2}$$

Figure 2.1: Common Drain Amplifier.

Based on: [2].

With the gain expression, it is possible to obtain the follow-up error expression, using the the following method:

$$A_{V}(s=0) = \frac{gm_{1}}{gds_{1} + gm_{1}}$$

$$\iff A_{V} = \frac{1}{\frac{gds_{1}}{gm_{1}} + 1}$$

$$\iff A_{V} = \frac{1}{F_{E} + 1}$$

$$(2.3)$$

$$F_E = \frac{gds_1}{gm_1} \tag{2.4}$$

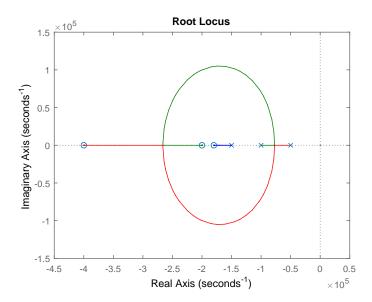

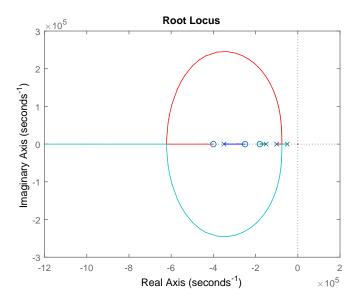

It's also possible to see by the analysis of the circuit that the CD has one zero and one pole. Doing a stability analysis, it can be observed that the circuit is always stable, because both the pole and the zero are stable (Figure 2.2).

Using the exact expression of the gain  $(A_v(s \neq 0))$  can be calculated the expression of the pole, and that is what will define the bandwidth of the circuit.

$$\omega_p = \frac{gm_1 + gds_1}{C_l + csb_1 + cgs_1} \tag{2.5}$$

Finally, the noise and the output swing of the circuit was calculated.

$$V_{Nin}^2 \approx \frac{\gamma 4 K_B T}{g m_1} \tag{2.6}$$

$$\Delta V o_{pp} = V_{dd} - 2V_{dsat} \tag{2.7}$$

The following structures are based on the source follower, and some changes are made to the arrangement of the circuit to reduce its disadvantages.

Figure 2.2: Root Locus of the CD.

#### 2.2 Flipped Voltage Follower (FVF)

The Flipped Voltage Follower (FVF) (Figure 2.3) allows a constant current through the transistor  $M_1$  due to the current source  $I_b$ , and under this condition, the unitary gain is achieved independently of the output current [1], [2]. By adding transistor  $M_2$ , there is no longer the previous limitation of sourcing current. However, this change limits the sinking capability of the FVF because of the biasing current [1]-[3]. The big advantage of using a FVF is the aptitude of using a very low voltage supply. Another improvement can be done to this circuit, adding a resistor on the closed loop between the gate of  $M_2$  and the drain of  $M_1$  [4], resulting in a better bandwidth.

The main application of the FVF is as a voltage buffer with Direct Current (DC) level shifting [5], but it is also used as a current sensing element.

By analysing the circuit, the expressions of the output impedance and the expression of the gain are obtained. Comparing the output impedance of the FVF with the impedance of the CD it can be observed that the FVF impedance is lower. Plus, it's also possible to obtain a unitary gain.

$$R_O \approx \frac{1}{gm_1gm_2rds_1} \tag{2.8}$$

$$A_V(s=0) = \frac{gm_1gm_2}{gm_2gds_1 + gds_1gds_2 + gm_1gm_2}$$

(2.9)

By the expression of the gain it's possible to obtain the follow-up error expression.

$$F_E = \frac{gds_1}{gm_1} + \frac{gds_1gds_2}{gm_1gm_2} \tag{2.10}$$

It's also possible to see that the FVF has a lower noise than the CD although the FVF has

Figure 2.3: Flipped Voltage Follower.

Based on: [2].

two transistors, but as the transistor  $M_1$  is cascode its noise is negligible. In the worst case scenario the output swing is lower than the CD output swing.

$$V_{Nin}^{2} \approx \frac{\gamma 4 K_{B} T g m_{2}}{(g m_{1} g m_{2} r d s_{1})^{2}}$$

(2.11)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.12}$$

With regard to stability, it's also possible to conclude that the system is always stable due to its two stable poles and two stable zeros, which can be visualized in Figure 2.4.

Figure 2.4: Root Locus of the FVF.

Using the exact expression of the gain it's possible to calculate the existing poles and

comparing both expressions it's possible to obtain the dominant pole.

$$\omega_p \approx \frac{gm_2}{cgd_1 + cdb_1 + cgs_2 + cgd_2} \tag{2.13}$$

#### 2.3 FVF Differential Structure (DFVF)

The FVF Differential Structure (DFVF) is a FVF based circuit and it presents a Class-AB behaviour. On the DFVF the output is available as either current or voltage, and this characteristic can be very advantageous, since it allows a simplification of the circuit as well as a reduction in noise and in the number of poles and zeros [2].

The DFVF can be used to build low-power low-voltage Class-AB output stages and can be used as a transconductance Operational Amplifier (OA). As a transconductance OA, the DFVF achieves a large Common mode rejection ratio (CMRR) [2], and if two DFVF are used a fully differential behaviour can be obtained.

Figure 2.5: FVF Differential Structure.

Based on: [2].

Using the small signal analysis, it's possible to obtain the expressions of the gain and output impedance. Comparatively to the FVF circuit, the gain remains equal but the output impedance is different. However, the output impedance of the circuit remains low.

$$R_O \approx \frac{gm_1gm_2 + gds_1gm_3}{gm_1gm_2gm_3 + gm_2gm_3gds_1}$$

(2.14)

$$A_V(s=0) = \frac{gm_1gm_2}{gm_2gds_1 + gds_1gds_2 + gm_1gm_2}$$

(2.15)

With the expression of the gain calculated above, it's possible to get the follow-up error expression.

$$F_E = \frac{gds_1}{gm_1} + \frac{gds_1gds_2}{gm_1gm_2} \tag{2.16}$$

By observation of Figure 2.5 it's possible to see that this circuit continues to have just one transistor contributing to the overall noise, the transistor  $M_2$ . The transistors  $M_1$  and  $M_3$  have a negligible noise, because they are cascode transistors. Also, by observation, it's possible to calculate the output swing.

$$V_{Nin}^{2} \approx \gamma 4K_{B}Tgm_{2} \left( \frac{gm_{1}gm_{2} + gds_{1}(gm_{2} + gm_{3})}{gm_{1}gm_{2}gm_{3}} \right)^{2}$$

(2.17)

$$\Delta V o_{pp} = V_{dd} - 2V_{dsat} - V_{C_l} \tag{2.18}$$

By analysing the exact expression of the gain it's possible to see that this circuit has two zeros and three poles. So, the circuit will always be stable, since both poles and zeros are stable. By doing the root locus (Figure 2.6) it's possible to confirm that.

Figure 2.6: Root Locus of the DFVF.

Comparing the three expressions of the poles present in the circuit it's possible to conclude that the dominant pole is given by:

$$\omega_p \approx \frac{gm_2}{cdb_1 + cgd_1 + cgd_2 + cgs_2} \tag{2.19}$$

#### 2.4 Bulk-driven FVF (BdFVF)

As a way to improve the FVF a bulk-driven transistor can be used instead of an ideal current source (Figure 2.7). This change will allow the circuit to obtain a Class-AB behaviour

instead of a Class-A behaviour, and consequently obtain a symmetrical slew rate instead of an asymmetrical slew rate [6].

To establish the bias current of the circuit is used a voltage  $V_b$  that fixes the  $V_{sg}$  voltage of the transistor  $M_3$ . To guarantee that the bias current is preserved, the node between the drain of the transistors  $M_2$  and  $M_3$  controls the transistors  $M_1$  and  $M_3$  [6]. In the case of  $V_{in}$  rising too fast the voltage in this node decreases and the transistor  $M_3$  starts to provide a larger current. As a consequence of that rise, the transistor  $M_1$  will be turned off, and the output voltage will increase with the input voltage until the circuit reaches a balance state [6].

Figure 2.7: Bulk-driven FVF.

Based on: [6].

By analysing the circuit it's possible to obtain the expressions of the gain and output impedance. As expected, it exhibits unitary gain and the output impedance is also very low.

$$R_O \approx \frac{gds_2 + gds_3}{gds_1(gds_2 + gds_3) + gm_2(gds_3 + gm_1)}$$

(2.20)

$$A_V(s=0) \approx \frac{gm_2(gds_3 + gm_1)}{gds_1(gds_2 + gds_3) + gm_2(gds_3 + gm_1)}$$

(2.21)

From the gain expression it's possible to get the follow-up error expression.

$$F_E = \frac{gds_1(gds_2 + gds_3)}{gm_2(gds_3 + gm_1)}$$

(2.22)

Comparing to the FVF this circuit has one more transistor, so the noise will be slightly higher. In this case, the transistors that will contribute to the noise of the circuit are the transistors  $M_1$  and  $M_3$ , as the transistor  $M_2$  is in cascode configuration its noise is

negligible. In relation to the output swing peak, to peak it remains equal compared to the original FVF.

$$V_{Nin}^2 \approx \frac{4K_B T (gm_1 + gm_3)}{(gm_1 gm_2 (rds_2//rds_3))^2}$$

(2.23)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.24}$$

From the exact expression of the gain, it's also possible to see that this circuit has two poles and two zeros, so the root locus of this circuit will be similar to the root locus of the FVF (Figure 2.4). This way the circuit will be stable, since its poles and zeros remain stable. From the expressions of the two poles that can be obtained from the exact expression of the gain, it's possible to see which is the dominant pole and get its expression.

$$\omega_p \approx \frac{gm_1}{cgd_1 + cgs_1 + cgd_2 + cdb_2 + cgd_3} \tag{2.25}$$

#### 2.5 Level Shifted FVF (LSFVF)

This is another circuit that, as the one mentioned in Section 2.4, also uses a bulk-driven transistor as a current source to improve the performance of the circuit from Class-A to Class-AB (Figure 2.8). However, this one has a level shifted feedback that allows increasing the input and output swing of the circuit [7].

Figure 2.8: Level Shifted FVF.

Based on: [7].

In this case the feedback of the circuit is made by the transistor  $M_4$  that is used as a level shifter in order to increase the swing of the circuit as referred previously. As in Section 2.4, the  $V_b$  at the gate of transistor  $M_3$  is used to set the bias current of transistors

$M_1 - M_3$ , and also to establish the  $V_{sg}$  voltage of transistor  $M_3$ . If the input voltage of the circuit suffers a very fast growth, then the voltage at the nodes X and Y will decrease. The opposite situation (fast decreasing of the input voltage) will make the voltage at node X grow and, as a consequence, the transistor  $M_3$  will provide a larger source current that also gives a larger current in the output capacitance  $C_I$  [7].

Doing the Alternating Current (AC) analysis of the circuit it's possible to obtain the expressions of the gain and output resistance which, as expected presents a unitary gain and a low output impedance, respectively.

$$R_O \approx \frac{gds_2 + gds_3}{gds_1(gds_2 + gds_3) + gm_2(gds_3 + gm_1)}$$

(2.26)

$$A_V(s=0) \approx \frac{gm_2(gds_3 + gm_1)}{gds_1(gds_2 + gds_3) + gm_2(gds_3 + gm_1)}$$

(2.27)

Comparing these expressions with the ones of Section 2.4 it's possible to see that they are equal. In other words, these circuits have the same gain and output impedance. With the gain expression it's possible to obtain the follow-up error expression.

$$F_E = \frac{gds_1(gds_2 + gds_3)}{gm_2(gds_3 + gm_1)}$$

(2.28)

In comparison with the circuit of the Section 2.4, this circuit has one more transistor contributing to the total noise. So, the transistors that will affect the overall noise are the transistors  $M_1$ ,  $M_3$  and  $M_4$ . As explained previously, the noise of transistor  $M_2$  is negligible, because this is a cascode transistor. Relatively to the output swing, it's expected to obtain something similar to the circuit from Section 2.4.

$$V_{Nin}^2 \approx \frac{4K_B T (gm_1 + gm_3 + gm_4)}{(gm_1 gm_2 (rds_2//rds_3))^2}$$

(2.29)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.30}$$

Comparing the expressions (2.29) and (2.23) it's possible to see that the noise of both circuits is very similar and the only change is that this circuit has one more transistor that contributes to the noise.

Looking to the exact expression of the gain it's possible to see that the circuit will introduce one more zero when compared to the circuit described in Section 2.4. Therefore, this circuit has three poles and three zeros, which will result in a stable system (Figure 2.9).

By the approximated expressions of the poles, it's possible to get the expression of the dominant pole.

$$\omega_p \approx \frac{gm_1}{C_c + cgd_1 + cgs_1 + cgs_4 + csb_4} \tag{2.31}$$

Figure 2.9: Root Locus of the LSFVF.

#### 2.6 Wide bandwidth buffer (Wbb)

This buffer is based on the FVF and has the aim of keeping a small load capacitance, while at the same time provides a low power consumption and a large bandwidth, without increasing the transistors dimensions (Figure 2.10). This is achieved through the improvement of the transconductance of the transistors using a feedback strategy [8].

Figure 2.10: Wide bandwidth buffer.

Based on: [8].

To achieve a better bandwidth without increasing the aspect ratio of  $M_1$  it's necessary to improve the transconductance of the transistor  $M_2$  through the feedback loop constituted by the transistors  $M_1$ ,  $M_3$ , and  $M_4$ . In order to obtain a linear circuit, was needed to add

an extra current source represented by the transistor  $M_6$ , which will provide a larger bias current to the transistor  $M_2$ . The resistance  $R_c$  used between the gates of transistors  $M_2$  and  $M_3$  was used to face the peck that appears when a small load capacitance is used to obtain a larger bandwidth [8].

Through circuit analysis it's possible to achieve the approximate expressions of the circuit. As expected, an approximately unitary gain was achieved, as well as a low output impedance.

$$R_O \approx \frac{g m_3 g ds_1 + g m_4 g ds_1 + g m_3 g ds_5 + g m_4 g ds_5}{g m_1 g m_2 g m_4 + g m_2 g m_4 g ds_1 + g m_1 g m_3 g ds_5 + g m_1 g m_4 g ds_5}$$

(2.32)

$$A_V(s=0) \approx \frac{g m_1 g m_2 g m_4 + g m_1 g m_3 g d s_5 + g m_1 g m_4 g d s_5}{g m_1 g m_2 g m_4 + g m_2 g m_4 g d s_1 + g m_1 g m_3 g d s_5 + g m_1 g m_4 g d s_5}$$

(2.33)

Through the gain expression is possible to get the follow-up error expression.

$$F_E = \frac{gm_2gm_4gds_1}{gm_1(gm_2gm_4 + gds_5(gm_3 + gm_4))}$$

(2.34)

Observing the circuit, it's possible to see that there are four transistors contributing to the noise  $(M_2, M_3, M_5 \text{ and } M_6)$ , as well as the resistance  $R_c$ . The transistors  $M_1$  and  $M_4$  have a negligible noise because they are cascode transistors. The output swing will remain equal for the worst case.

Figure 2.11: Root Locus of the Wbb.

$$V_{Nin}^{2} \approx 4K_{B}T \left( \frac{gm_{3}gds_{1} + gm_{4}gds_{1} + gm_{3}gds_{5} + gm_{4}gds_{5}}{gm_{1}gm_{2}gm_{4} + gm_{1}gm_{3}gds_{5} + gm_{1}gm_{4}gds_{5}} \right)^{2}$$

$$\left( \gamma(gm_{2} + gm_{3} + gm_{5} + gm_{6}) + \frac{1}{R_{c}} \right)$$

(2.35)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.36}$$

Analysing the exact expression of the gain, it's possible to conclude that this circuit has four poles and four zeros, resulting in a stable system, as shown in Figure 2.11.

By approximation, all the poles' expressions were calculated allowing to determine the expression of the dominant pole.

$$\omega_p \approx \frac{(1+gm_1)gm_2gm_4 + gds_5gm_1(gm_3 + gm_4)}{(cdb_3 + cgs_3 + cgs_4 + csb_4)gm_1gm_4}$$

(2.37)

## 2.7 Super Source Follower (SSF)

This circuit is an update of the basic Source Follower circuit and it uses negative feedback (through the transistor  $M_2$ ) in order to improve its linearity and its output impedance (Figure 2.12). This feedback is formed by the transistors  $M_1$  and  $M_2$ , and due to it the drain current of  $M_1$  is not affected by the output current as in the Source Follower [9]. However, this circuit has a disadvantage regarding large input signal application, since the transistors parameters will change, causing a signal distortion [9].

Figure 2.12: Super Source Follower.

Based on: [9].

The circuit analysis allows to obtain the expressions of the gain and of the output impedance.

$$R_O \approx \frac{g d s_1}{g m_1 g m_2 + g d s_1 (g d s_2 + g_L + g m_2)}$$

(2.38)

$$A_V(s=0) \approx \frac{gm_1gm_2}{gm_1gm_2 + gds_1(gds_2 + g_L + gm_2)}$$

(2.39)

As expected, the gain obtained is approximately unitary and the output impedance is very low. By the gain expression it's possible to achieve the follow-up error expression.

$$F_E = \frac{gds_1(gds_2 + g_L + gm_2)}{gm_2gm_1} \tag{2.40}$$

Regarding noise, both transistors and the resistance  $R_L$  will affect its overall value. Comparing this circuit with the Source Follower leads to the conclusion of a smaller output swing on the present one.

$$V_{Nin}^{2} \approx 4K_{B}T \left(\frac{gds_{1}}{gm_{1}gm_{2}}\right)^{2} \left(\gamma(gm_{1} + gm_{2}) + \frac{1}{R_{L}}\right)$$

(2.41)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.42}$$

By analysing the exact expression of the gain it's possible to see that this circuit has two poles and two zeros, which constitutes a stable system as can be observed in Figure 2.4. With the calculation of the approximated expressions of the poles it's possible to obtain the dominant pole expression.

$$\omega_p \approx \frac{gm_2}{cdb_1 + cgd_1 + cgd_2 + cgs_2} \tag{2.43}$$

# 2.8 Buffer with high linearity and adjustable output impedance

This circuit is an evolution of the Super Source Follower, in two aspects, linearity, and output impedance (Figure 2.13). In this circuit is added another feedback loop, so the circuit stays with two feedback loops. One loop is used to improve the linearity of the circuit while the other one is used to adjust the output impedance. This way, the output impedance depends on a resistor  $R_1$  and on the size ratio of  $M_2$  and  $M_4$ . To improve the gain of the circuit was used the resistor  $R_{in}$  [9].

Figure 2.13: Buffer with high linearity and adjustable output impedance.

Based on: [9].

Analysing the circuit is possible to obtain the expressions of the output impedance and

gain. As expected, the gain is approximately unitary and the output impedance is low and dependent of  $R_1$ .

$$R_O \approx \frac{gm_2}{(g_1 + gds_4 + g_I)gm_2 + (g_1 + gds_3)gm_4}$$

(2.44)

$$A_V(s=0) \approx \frac{g_1 g m_2 + (g_1 + g d s_2 + g_{in}) g m_4}{(g_1 + g d s_4 + g_L) g m_2 + (g_1 + g d s_3) g m_4}$$

(2.45)

Through the gain expression is possible to get the follow-up error expression.

$$F_E \approx \frac{(gds_4 + g_L)gm_2 + gds_3gm_4}{g_1(gm_2 + gm_4)}$$

(2.46)

By observation of the circuit is possible to see that the transistors  $M_1$ ,  $M_2$  and  $M_4$  will contribute to the overall noise, as well as the resistors  $R_1$ ,  $R_L$  and  $R_{in}$ . The noise of transistor  $M_3$  is negligible because this transistor is folded cascode. Also, by observation, is possible to get the output swing expression.

$$V_{Nin}^{2} \approx 4K_{B}T \left( \frac{gm_{2}}{g_{1}gm_{2} + (g_{1} + gds_{2} + g_{in})gm_{4}} \right)^{2}$$

$$\left( \gamma (gm_{1} + gm_{2} + gm_{4}) + \frac{1}{R_{L}} + \frac{1}{R_{1}} + \frac{1}{R_{in}} \right)$$

(2.47)

$$\Delta V o_{pp} = V_{dd} - 2V_{dsat} \tag{2.48}$$

Considering the exact expression of the gain is possible to see that the circuit has five

Figure 2.14: Root Locus of the buffer with high linearity and adjustable output impedance.

poles and five zeros. This constitutes a stable system as demonstrated in Figure 2.14. By

the approximated expressions of the poles is possible to achieve the expression of the dominant pole.

$$\omega_p \approx \frac{g_1(gm_2 + gm_4)}{(C_1 + cdb_4 + C_I)gm_2} \tag{2.49}$$

## 2.9 Two stage QFG buffer

This buffer introduces a technique of Quasi-Floating Gate (QFG) (Figure 2.15), without using any DC level shift from the input to the output, in order to avoid problems resulting from it, due to the temperature dependence of the DC level shifting circuits. This circuit also allows to obtain Class-AB behaviour without using any additional supply voltage [10].

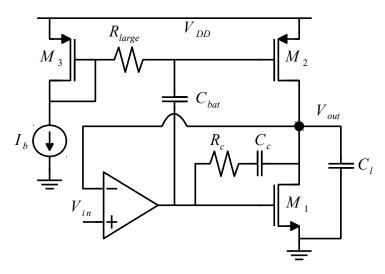

The QFG technique consists in stabilize the gate voltage of one transistor from the DC point of view, but from the signal point of view this voltage can be considered a floating voltage. Is it what happens in the gate of transistor  $M_2$ , and in order to this be possible was added a big resistance, and a capacitor  $C_{bat}$  in the gate of  $M_2$  [10].

Figure 2.15: Two stage QFG buffer.

Based on: [10].

Another characteristic of this circuit is the capability to work with a small quiescent current in order to save static power, and at the same time exhibit a large slew rate due to the large output current. Case the input voltage rises too fast, the output of this circuit is also capable of follow the variation occurred, providing a large current at the load. Due to the big value of  $R_{large}$  the  $C_{bat}$  capacitor will act like a DC voltage, because it will not discharge fast, and this will increase the  $V_{sg}$  voltage of  $M_2$ , which will provide the required current at the output. With the increase of the  $V_{sg}$  voltage at  $M_2$ , its gate voltage decreases, and hence the drain current of  $M_1$  will also decrease below  $I_b$ . Otherwise if the input voltage decreases, then the gate voltage of transistors  $M_1$  and  $M_2$  will decrease,

the drain current of  $M_1$  will increase, and the drain current of  $M_2$  will decrease, which denote the sinking capability of this circuit at the load [10].

Therefore, this kind of circuit is very useful for applications that require an accurate operation with low quiescent power consumption [10].

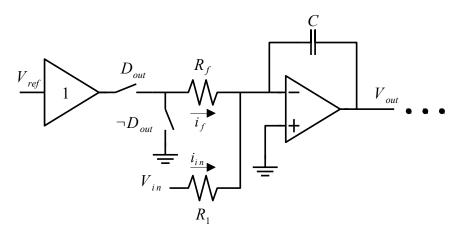

Using a transconductance amplifier (Figure 2.17) and doing an AC analysis in the circuit is possible to obtain the expressions of the gain and output impedance. As expected, the gain is unitary and the output impedance is low.

$$R_O \approx \frac{gout_4}{gm_1gm_4 + (gds_1 + gds_2)gout_4}$$

(2.50)

$$A_V(s=0) \approx \frac{g m_1 g m_4}{g m_1 g m_4 + (g d s_1 + g d s_2) g o u t_4}$$

(2.51)

In the expressions (2.50) and (2.51) the transconductances  $gm_4$  and  $gout_4$  represent the components of the transconductance amplifier. By analysing the gain expression calculated above is possible to get the follow-up error expression.

$$F_E \approx \frac{(gds_1 + gds_2)gout_4}{gm_1gm_4} \tag{2.52}$$

Regarding the noise, is possible to see that this circuit has two transistors ( $M_1$  and  $M_2$ ), and two resistors ( $R_c$  and  $R_{large}$ ) that will contribute to the overall noise. By observation is also possible to calculate the output swing expression.

$$V_{Nin}^{2} \approx \frac{4K_{B}T}{(gm_{1}gm_{4}Rout_{4})^{2}} \left( \gamma(gm_{1} + gm_{2}) + \frac{1}{R_{c}} + \frac{1}{R_{large}} \right)$$

(2.53)

$$\Delta V o_{pp} = V_{dd} - 2V_{dsat} \tag{2.54}$$

Using the exact expression of the gain is possible to see that this circuit has four poles and three zeros, which constitute a stable system (Figure 2.18). Based on the gain expression is possible to calculate the approximated expressions of the poles, and consequently achieve the dominant pole, where  $C_{p4}$  represents the parasitic capacitances of the transconductance amplifier.

$$\omega_p \approx \frac{gm_1}{C_{bat} + C_c + cgd_1 + cgs_1 + C_{p4}}$$

(2.55)

# 2.10 Low Drop-out (LDO) regulators

The Low Drop-out (LDO) regulators are very important components for the system-on-chip (SoC) circuits because there are multiple supply voltages used for the different components that integrate the chip.

The main function of a LDO regulator is to provide the voltage supply that the other circuits need, and at the same time protect them from the disturbances that may happen on the supply voltage [11].

In the next sections, it will be observed some designs of LDO regulators.

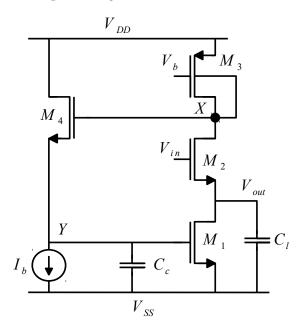

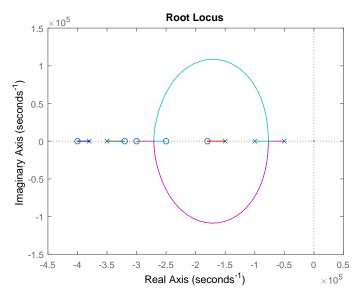

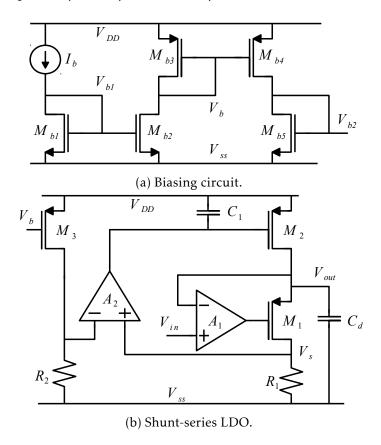

#### 2.10.1 Shunt-series LDO (SsLDO)

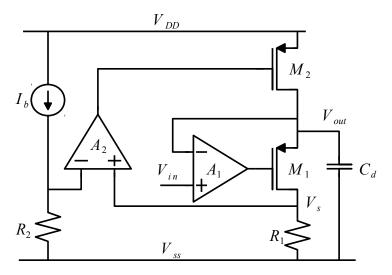

The Shunt-series LDO (SsLDO) regulator allows to obtain a very low output impedance and a gain approximately equal to one (Figure 2.16).

This SsLDO is divided in two control loops, one shunt section and one series section. The shunt section constituted by the amplifier  $A_1$  and the transistor  $M_1$  deals with fast transients, and the series section composed by the amplifier  $A_2$  and transistor  $M_2$  handles low frequency load current fluctuations. Besides that, on its output, there is a capacitor  $C_d$  that takes care of very fast current changes [12]. After analysing this circuit it was

Figure 2.16: Shunt-series LDO.

Based on: [12].

possible to obtain the next expressions of the output impedance and gain, considering  $A_1$  and  $A_2$  as ideal amplifiers.

$$R_O \approx \frac{g_1 + g d s_1}{g_1 g m_1 + A_1 g_1 g m_1 + A_2 g m_1 g m_2 + A_2 g m_2 g d s_1 + A_1 A_2 g m_1 g m_2}$$

(2.56)

$$A_V(s=0) \approx \frac{A_1 g_1 g m_1 + A_2 g_1 g m_2 + A_2 g m_2 g d s_1 + A_1 A_2 g m_1 g m_2}{g_1 g m_1 + A_1 g_1 g m_1 + A_2 g m_1 g m_2 + A_2 g m_2 g d s_1 + A_1 A_2 g m_1 g m_2}$$

(2.57)

In the FVF there's only one transistor that contributes to the noise but on this LDO there is also a resistor that contributes to the noise. Lastly it was calculated the output swing.

$$V_{Nin}^{2} \approx \frac{4K_{B}T}{(A_{1}A_{2}gm_{1}gm_{2}(rds1//R1))^{2}} \left(\gamma gm_{2} + \frac{1}{R_{1}}\right)$$

(2.58)

$$\Delta V o_{pp} = V_{dd} - 2V_{dsat} - V_s \tag{2.59}$$

Replacing the amplifiers  $A_1$  and  $A_2$  by the circuit of Figure 2.17 the gain and output impedance expressions will be calculated once again. This change is needed in order to be possible to get all the expressions of poles and zeros.

Figure 2.17: Transconductance Amplifier.

$$R_{O} \approx \frac{(g_{1} + gds_{1})gout_{3}gout_{4}}{gm_{1}gm_{2}gm_{3}gm_{4} - gds_{1}gm_{2}gm_{3}gout_{4}}$$

(2.60)

$$A_V(s=0) \approx \frac{g m_1 g m_4}{g m_1 g m_4 - g d s_1 g o u t_4}$$

(2.61)

In the expressions (2.60) and (2.61), the transconductances  $gout_3$  and  $gm_3$  are related to the components of  $A_2$ , and the transconductances  $gout_4$  and  $gm_4$  to the components of  $A_1$ . By the gain expression calculated after the change of the amplifiers by the transconductance amplifiers is possible to get the follow-up error expression.

$$F_E = \frac{gds_1gout_4}{gm_1gm_4} \tag{2.62}$$

With this change is also possible to obtain another expression of the input noise.

$$V_{Nin}^{2} \approx \frac{4K_{B}T}{(gm_{1}gm_{2}gm_{3}gm_{4}Rout_{3}Rout_{4}(rds_{1}//R_{1}))^{2}} \left(\gamma gm_{2} + \frac{1}{R_{1}}\right)$$

(2.63)

This expression meets the expected result, because the gain of the transconductance

Figure 2.18: Root Locus of the SsLDO.

amplifier is  $A_v = gmRout$ .

From the analysis of the exact expression of the gain it is possible to conclude that this circuit has five poles and four zeros, but in order to obtain a manageable expression it will be considered that the parasitic capacitance  $cgd_1$  of transistor  $M_1$  is negligible, and thus simplifying the system to have four poles and three zeros. This results in a stable system as shown in Figure 2.18. Further on, if this circuit reveals itself important, then will be considered the most difficult scenario comprising the parasitic capacitances. Taking into account this simplification is possible to obtain the dominant pole expression, where  $C_{p3}$  represents the parasitic capacitances of the transconductance amplifier  $A_2$ .

$$\omega_p \approx \frac{gm_2}{cgd_2 + cgs_2 + C_{p3}} \tag{2.64}$$

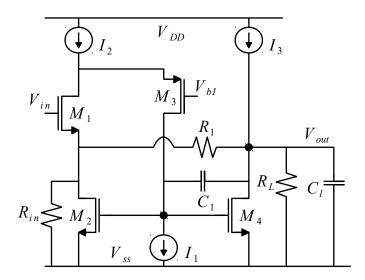

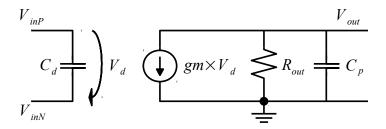

#### 2.10.2 Capacitor free LDO (CfLDO)

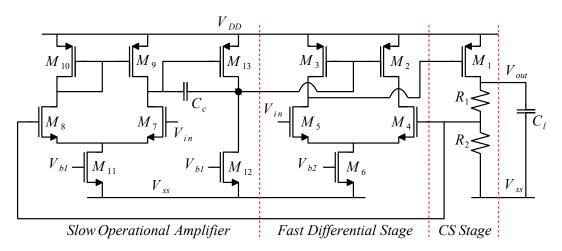

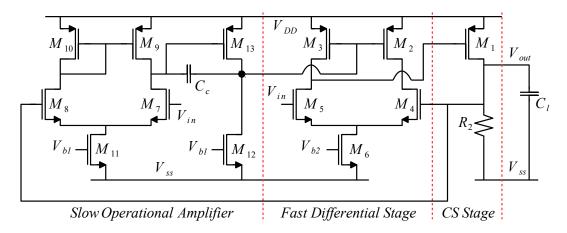

This is a Capacitor free LDO (CfLDO) that presents an architecture with a fast and a slow loop (Figure 2.19). The circuit can be divided into three different parts: (1) a common source (CS) stage at the output, (2) a fast differential stage that has a feedback from the output stage forming the fast loop of the circuit, and (3) a slow operational amplifier that has a feedback from the output stage forming the slow loop of the circuit.

The fast loop of the circuit has the purpose of deleting the spikes caused by a step in the load, that is felt on the output of the LDO. The slow loop has the purpose of controlling the gate voltage of  $M_2$  and  $M_3$ , that allows to stabilize the DC voltage at the output [11].

Figure 2.19: Capacitor free LDO.

Based on: [11].

To facilitate the analysis of the CfLDO stage by stage analysis was made, and the resulting expressions were combined to obtain the final expressions for the gain, output impedance and noise.

In order to obtain the gain expression of the circuit the open loop gain of each stage were calculated, and from those expressions, the closed loop gain was obtained using Mason's

rule.

$$A_{OL2}(s=0) \approx -\frac{(g_1 + g_2)gm_1}{g_2gds_1 + g_1(g_2 + gds_1)}$$

(2.65)

$$A_{OL1}(s=0) \approx -\frac{gm_5}{gds_3 + gds_5} \tag{2.66}$$

$$A_{OL0}(s=0) \approx \frac{g m_{13} g m_7}{(g d s_1 2 + g d s_{13})(g d s_7 + g d s_9)}$$

(2.67)

The above expressions represent the open loop gain of each stage, where  $A_{OL2}$  represents the CS stage,  $A_{OL1}$  represents the fast differential stage, and  $A_{OL0}$  represents the slow operational amplifier. As referenced above, this circuit has two loops so, will be needed to calculate the final expression taking the two loops into account. Therefore, to introduce the fast loop:

$$A_{V21} = \frac{A_{OL2}A_{OL1}}{1 + A_{OL2}A_{OL1}} \tag{2.68}$$

And to introduce the slow loop a similar step was made that allows to obtain the gain expression.

$$A_V = \frac{A_{OL0}A_{V21}}{1 + A_{OL0}A_{V21}} \tag{2.69}$$

$$A_{V} \approx \frac{(g_{1}+g_{2})gm_{1}gm_{13}gm_{5}gm_{7}}{(g_{1}+g_{2})gm_{1}gm_{13}gm_{5}gm_{7} + (g_{1}g_{2}+gds_{1}(g_{1}+g_{2}))(gds_{12}+gds_{13})(gds_{3}+gds_{5})(gds_{7}+gds_{9})}$$

(2.70)

As expected the expression obtained represents a unitary gain, and with this expression is possible to obtain the follow-up error expression.

$$F_E = \frac{(g_1g_2 + gds_1(g_1 + g_2))(gds_{12} + gds_{13})(gds_3 + gds_5)(gds_7 + gds_9)}{(g_1 + g_2)gm_1gm_{13}gm_5gm_7}$$

(2.71)

After with the calculation of the output impedance is possible to verify that this circuit has a low output impedance, as expected.

$$R_O \approx \frac{(g_1 + g_2)(gds_{12} + gds_{13})gds_3gds_9(gm_7 + gm_8)}{g_1gm_1gm_{13}gm_3gm_7gm_8}$$

(2.72)

Considering all the stages of the circuit, the transistors that will contribute to the overall noise are transistors  $M_1 - M_3$ ,  $M_6$ , and  $M_9 - M_{13}$ , the remaining transistors are cascode and as explained previously his noise is negligible. Since this circuit has two resistors they will also contribute to the noise, and, by inspection is possible to get the output swing expression.

$$V_{Nin}^{2} \approx 4K_{B}T \left( \frac{(g_{1} + g_{2})(gds_{12} + gds_{13})^{2}gds_{3}gds_{9}(gds_{7} + gds_{9})(gm_{7} + gm_{8})}{g_{1}gm_{1}gm_{13}gm_{3}gm_{7}gm_{8}} \right)^{2}$$

$$\left( \gamma(gm_{1} + gm_{2} + gm_{3} + gm_{6} + gm_{9} + gm_{10} + gm_{11} + gm_{12} + gm_{13}) + \frac{1}{R_{1}} + \frac{1}{R_{2}} \right)$$

(2.73)

$$\Delta V o_{pp} = V_{dd} - V_{dsat} - V_{R_1} - V_{R_2} \tag{2.74}$$

By observation of the exact expression of the gain is possible to conclude that this circuit has four poles and four zeros, constituting a stable system. In Figure 2.11 can be observed the root locus of an architecture with the same number of poles and zeros. From the gain expression is possible to get the expressions of the poles and observing them, obtain the dominant pole expression.

$$\omega_p \approx \frac{gm_1R_1}{cdb_3 + cdb_5 + cgd_3 + cgd_5} \tag{2.75}$$

Analysing this expression is possible to see that the pole frequency is also dependent of  $R_1$  which means that there is some margin to change the bandwidth of the circuit if needed.

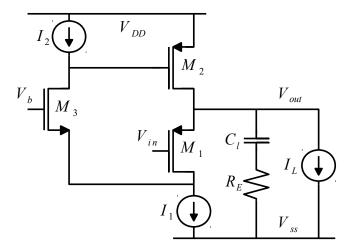

#### 2.10.3 Cascaded FVF (CAFVF)

This architecture is another improved circuit driven from the FVF. As in the Level Shifted FVF (LSFVF), this circuit also introduces another transistor in the feedback loop, that is biased by a voltage  $V_b$  on its gate, and by a bias current on its drain (Figure 2.20). This way, the transistor  $M_3$  can be compared to a common gate amplifier that will provide extra gain in the feedback loop, and also reduce the output impedance [13].

Figure 2.20: Cascaded FVF based LDO.

Based on: [13].

Doing an AC analysis of the circuit is possible to get the expressions of the gain and of the output impedance.

$$R_{O} \approx \frac{g d s_{1} g d s_{3}}{g d s_{1} g m_{2} g m_{3} + g m_{1} g m_{2} g m_{3}}$$

(2.76)

$$A_V(s=0) \approx \frac{gm_1}{gds_1 + gm_1} \tag{2.77}$$

Using the gain expression calculated above is possible to obtain the follow-up error expression.

$$F_E = \frac{gds_1}{gm_1} \tag{2.78}$$

By circuit observation is possible to see that the circuit has one transistor that will contribute to the overall noise  $(M_2)$ , and that the transistors  $M_1$  and  $M_3$  have a negligible noise, because they are cascode transistors. Besides that, the resistor  $R_E$  will also contribute to the noise. And analysing the circuit is possible to get the output swing expression.

$$V_{Nin}^{2} \approx \frac{4K_{B}T}{(gm_{1}gm_{2}gm_{3}rds_{1}rds_{3})^{2}} \left(\gamma gm_{2} + \frac{1}{R_{E}}\right)$$

(2.79)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.80}$$

With the exact expression of the gain is possible to see that this circuit has three poles and three zeros, constituting a stable system. In Figure 2.9 is possible to see an example of a system with the same number of poles and zeros. Calculating the approximated expressions of the poles is possible to get the dominant pole expression.

$$\omega_p \approx \frac{gm_2}{cdb_3 + cgd_2 + cgd_3 + cgs_2} \tag{2.81}$$

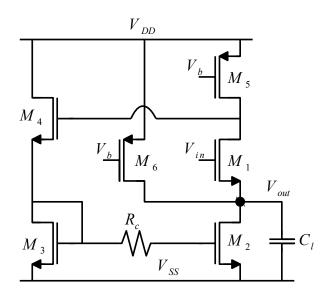

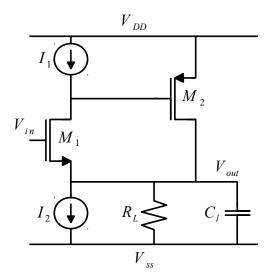

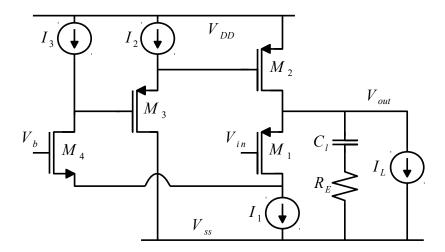

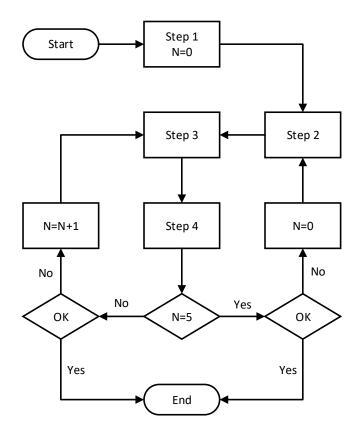

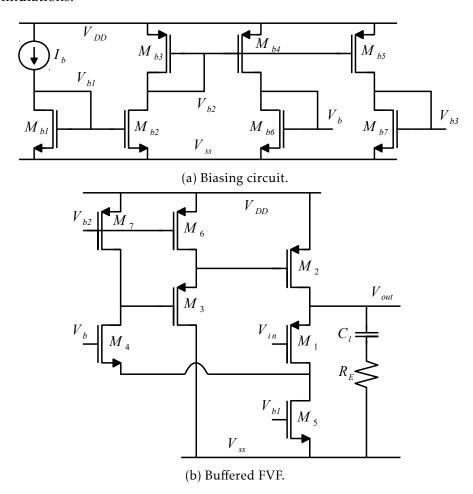

#### 2.10.4 Buffered FVF (BFVF)

This circuit is based on the LSFVF and on the Cascaded FVF (CAFVF) and its aim is to gather the advantages of both topologies (Figure 2.21). This way the circuit is capable of reduce the loading requirement, increase the loop gain in order to improve the load regulation, improve the stability, and allows to have a larger bandwidth. Therefore, this circuit has a feedback loop with two transistors: one that can be interpreted as a common gate amplifier ( $M_4$ ), and the other which can be interpreted as a source follower. In other words, the feedback loop is a junction of the architectures referred above [13].

In this structure, the drain voltage of  $M_1$  is defined by the bias voltage  $V_b$  and by the Vgs voltage of  $M_4$ , which removes the minimum loading constraint present in other topologies. Nevertheless, the bias voltage cannot assume the value we want, because otherwise some transistors may enter the triode region. This way, if the bias voltage is too low, the transistor of  $I_1$  enters the triode region. Otherwise if the bias voltage is too high, the transistor  $M_4$  enters the triode region[13]. Another function of transistor  $M_4$  is to ensure that the transistor  $M_1$  will work in the saturation region, no matter which is the bias current of  $I_1$  [14].

By analysing the circuit in closed loop is possible to get the expressions of both the output

Figure 2.21: Buffered FVF based LDO.

Based on: [13].

impedance and gain.

$$R_O \approx \frac{g d s_1 g d s_4}{g d s_1 g m_2 g m_4 + g m_1 g m_2 g m_4}$$

(2.82)

$$A_V(s=0) \approx \frac{gm_1}{gds_1 + gm_1}$$

(2.83)

As expected, the output impedance is low, and the gain is unitary. Using this expression is possible to get the follow-up error expression.

$$F_E = \frac{gds_1}{gm_1} \tag{2.84}$$

In relation to the noise, is possible to see that this circuit has two transistors and one resistance that will contribute to the overall noise  $(M_2, M_3 \text{ and } R_E)$ . Transistors  $M_1$  and  $M_4$  have a negligible noise because, as explained previously, they are cascode transistors. Also, by observation of the circuit, is possible to calculate the output swing.

$$V_{Nin}^{2} \approx \frac{4K_{B}T}{(gm_{1}gm_{2}gm_{4}rds_{1}rds_{4})^{2}} \left(\gamma(gm_{2} + gm_{3}) + \frac{1}{R_{E}}\right)$$

(2.85)

$$\Delta V o_{pp} = V_{dd} - 3V_{dsat} \tag{2.86}$$

Using the exact expression of the gain, it can be noticed that this circuit has four poles and four zeros. Since all poles and all zeros remain stable, the circuit will also remain stable. Figure 2.11 constitutes an example of a stable system with the same number of roots. Knowing the approximate expressions of the poles, is possible to get the dominant pole.

$$\omega_p \approx \frac{gm_2}{cgd_2 + cgs_2 + cgs_3 + csb_3} \tag{2.87}$$

## 2.11 Results analysis

On this section a coarse design will be made of the architectures studied in the previous sections. To do so it will be assumed that  $\frac{gm_i}{gds_i} \sim 10$  and  $gm = \frac{2I_D}{V_{dsat}}$ . Therefore, the  $V_{dsat}$  voltage established is 50mV for all the cases. Then, the necessary supplied current will be calculated, in order to obtain an output impedance of  $1\Omega$ .

Circuit/Section Characteristics CD **FVF DFVF BdFVF** LsFVF Wbb SSF 50 mIb (A) 25 m2.5 m5 m 5 m 4.26 m6.82 m $Ro(\Omega)$ 1 1

Table 2.1: Coarse design of the different topologies (Part 1/2).

Table 2.2: Coarse design of the different topologies (Part 2/2).

|                 | Circuit/Section |       |       |       |       |       |

|-----------------|-----------------|-------|-------|-------|-------|-------|

| Characteristics | (2.8)           | (2.9) | SsLDO | CfLDO | CAFVF | BFVF  |

| Ib (A)          | -               | 2.5 m | 25 μ  | 400 μ | 250 μ | 250 μ |

| Ro (Ω)          | 1               | 1     | 1     | 1     | 1     | 1     |

To obtain the results displayed on Table 2.1 and Table 2.2 it was necessary to make several assumptions in each architecture:

- Common Drain Amplifier: in this case, it was considered that the current flowing through transistor M<sub>1</sub> is only dependent of the current source. In other words, was considered an ideal situation where the output doesn't affect the transistor, I<sub>out</sub> = 0A;

- FVF Differential Structure: in this case, a greater approximation was made compared to the one considered in the equation (2.14),  $R_O \approx \frac{1}{gm_3}$ . Then, it was assumed that the drain current of transistor  $M_3$  was half the bias current;

- Wide bandwidth buffer: in this case, was considered that the gate current of  $M_4$  is zero and that the current flowing in transistors  $M_2 M_4$  is the double of the current flowing in the remaining transistors;

- Super Source Follower: in this circuit was considered that the gate current of  $M_2$  is zero and that  $I_{D1} = 3 * I_{D2}$ ;

- Buffer with high linearity and adjustable output impedance: the crass design made in the previous architectures is not applicable in this situation, because after normalizing the gm of transistors  $M_2$  and  $M_4$  the output impedance is no longer dependent of gm,  $R_O \approx \frac{R_1}{2}$ ;

- Two stage QFG buffer: in this circuit was considered that the current flowing in transistors  $M_1$  and  $M_2$  is equal, and that the current flowing in the amplifier is also the same;

- **Shunt-series LDO:** in this case, was considered that the bias current of the circuit is equal in the two transistors and in the two transconductance amplifiers;

- Capacitor free LDO: in this situation was considered that the bias voltages  $V_{b1}$  and  $V_{b2}$  are equal, the current that flows in  $M_{12}$  and  $M_{13}$  is equal to  $2 \times I_b$ , the current that flows in  $M_1$  is  $0.5 \times I_b$  and that the current in the remaining transistors is equal to  $I_b$ . It was also considered that the resistors  $R_1$  and  $R_2$  are sized with  $1\Omega$ ;

- Cascaded FVF: in this case, was assumed that the gate current of transistor  $M_2$  is zero, the current flowing in  $M_1$  and  $M_2$  is equal and the drain current of transistor  $M_3$  is twice the current observed in the transistors  $M_1$  and  $M_2$ ;

- **Buffered FVF:** in this architecture was considered that the gate current of transistors  $M_2$  and  $M_3$  is zero, the current flowing in  $M_1$  is equal in  $M_2$  and that transistor  $M_4$  presents two times the current when compared to  $M_1$  and  $M_2$ .

The next Tables summarize all the theoretical analysis made in the previous sections, in order to be easier to compare the differences between them. This way joining the results presented in Tables (2.1 to 2.6) will be possible to choose the best architectures to study with more detail in the next Chapter.

| Table 2.3: Comparison of the different topologies (Part 1/4). |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

|                  | Circuit/Section                            |                                                    |                                                    |                                                         |  |  |

|------------------|--------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|--|--|

| Characteristics  | CD                                         | FVF                                                | DFVF                                               | BdFVF                                                   |  |  |

| Gain             | $\frac{gm_1}{gds_1 + gm_1}$                | $\frac{gm_1gm_2}{gm_2gds_1 + gm_1gm_2}$            | $\frac{gm_1gm_2}{gm_2gds_1 + gm_1gm_2}$            | $\frac{gm_1gm_2}{gds_1(gds_2 + gds_3) + gm_1gm_2}$      |  |  |

| Output impedance | $\frac{1}{gm_1}$                           | $\frac{1}{gm_1gm_2rds_1}$                          | $\frac{1}{gm_3}$                                   | $\frac{gds_2 + gds_3}{gds_1(gds_2 + gds_3) + gm_2gm_1}$ |  |  |

| $\Delta Vo_{pp}$ | $V_{dd} - 2V_{dsat}$                       | $V_{dd} - 3V_{dsat}$                               | $V_{dd} - 2V_{dsat} - V_{C_l}$                     | $V_{dd} - 3V_{dsat}$                                    |  |  |

| $V_{Nin}^2$      | $\frac{\gamma 4K_BT}{gm_1}$                | $\frac{\gamma 4K_BTgm_2}{(gm_1gm_2rds_1)^2}$       | $\frac{\gamma 4K_BTgm_2}{(gm_3)^2}$                | $\frac{4K_BT(gm_1 + gm_3)}{(gm_1gm_2(rds_2//rds_3))^2}$ |  |  |

| Bandwidth        | $\frac{gm_1 + gds_1}{C_l + csb_1 + cgs_1}$ | $\frac{gm_2}{cgd_1 + cdb_1 + cgs_2 + cgd_2}$       | $\frac{gm_2}{cdb_1 + cgd_1 + cgd_2 + cgs_2}$       | $\frac{gm_1}{cgd_1 + cgs_1 + cgd_2 + cdb_2 + cgd_3}$    |  |  |

| Follow-up error  | $\frac{gds_1}{gm_1}$                       | $\frac{gds_1}{gm_1} + \frac{gds_1gds_2}{gm_1gm_2}$ | $\frac{gds_1}{gm_1} + \frac{gds_1gds_2}{gm_1gm_2}$ | $\frac{gds_1(gds_2 + gds_3)}{gm_2(gds_3 + gm_1)}$       |  |  |

Table 2.4: Comparison of the different topologies (Part 2/4).

|                  | Circuit/Section                                                |                                                                                        |                                                                         |  |  |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| Characteristics  | LSFVF                                                          | Wbb                                                                                    | SSF                                                                     |  |  |

| Gain             | $\frac{gm_1gm_2}{gds_1(gds_2 + gds_3) + gm_1gm_2}$             | $\frac{gm_1(gm_2gm_4+gds_5(gm_3+gm_4))}{(gds_1+gm_1)gm_2gm_4+gds_5gm_1(gm_3+gm_4)}$    | $\frac{gm_{1}gm_{2}}{gm_{1}gm_{2} + gds_{1}(gds_{2} + g_{L} + gm_{2})}$ |  |  |

| Output impedance | $\frac{gds_2 + gds_3}{gds_1(gds_2 + gds_3) + gm_2gm_1}$        | $\frac{(gds_1 + gds_5)(gm_3 + gm_4)}{(gds_1 + gm_1)gm_2gm_4 + gds_5gm_1(gm_3 + gm_4)}$ | $\frac{gds_1}{gm_1gm_2 + gds_1(gds_2 + g_L + gm_2)}$                    |  |  |

| $\Delta Vo_{pp}$ | $V_{dd} - 3V_{dsat}$                                           | $V_{dd} - 3V_{dsat}$                                                                   | $V_{dd} - 3V_{dsat}$                                                    |  |  |

| $V_{Nin}^2$      | $\frac{4K_BT(gm_1 + gm_3 + gm_4)}{(gm_1gm_2(rds_2//rds_3))^2}$ | $\frac{4K_BT((gds_1+gds_5)(gm_3+gm_4))^2X_1}{(gm1(gm2gm4+gds5(gm3+gm4)))^2}$           | $\frac{4K_BTX_2}{(gm_1gm_2rds_1)^2}$                                    |  |  |

| Bandwidth        | $\frac{gm_1}{C_c + cgd_1 + cgs_1 + cgs_4 + csb_4}$             | $\frac{(1+gm_1)gm_2gm_4+gds_5gm_1(gm_3+gm_4)}{(cdb_3+cgs_3+cgs_4+csb_4)gm_1gm_4}$      | $\frac{gm_2}{cdb_1 + cgd_1 + cgd_2 + cgs_2}$                            |  |  |

| Follow-up error  | $\frac{gds_1(gds_2+gds_3)}{gm_2(gds_3+gm_1)}$                  | $\frac{gm_{2}gm_{4}gds_{1}}{gm_{1}(gm_{2}gm_{4}+gds_{5}(gm_{3}+gm_{4}))}$              | $\frac{gds_1(gds_2 + g_L + gm_2)}{gm_2gm_1}$                            |  |  |

$$X_{1} = \gamma(gm_{2} + gm_{3} + gm_{5} + gm_{6}) + \frac{1}{R_{c}}$$

$$X_{2} = \gamma(gm_{1} + gm_{2}) + \frac{1}{R_{L}}$$

Table 2.5: Comparison of the different topologies (Part 3/4).

|                  | Circuit/Section                                                                            |                                                                                                    |                                                                 |  |  |

|------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Characteristics  | (2.8)                                                                                      | SsLDO                                                                                              |                                                                 |  |  |

| Gain             | $\frac{g_1gm_2 + (g_1 + gds_2 + g_{in})gm_4}{(g_1 + gds_4 + g_L)gm_2 + (g_1 + gds_3)gm_4}$ | $\frac{gm_1gm_4}{gm_1gm_4 + (gds_1 + gds_2)gout_4}$                                                | $\frac{gm_1gm_4}{gm_1gm_4 - gds_1gout_4}$                       |  |  |

| Output impedance | $\frac{gm_2}{(g_1 + gds_4 + g_L)gm_2 + (g_1 + gds_3)gm_4}$                                 | $\frac{gout_4}{gm_1gm_4 + (gds_1 + gds_2)gout_4}$                                                  | $\frac{(g_1+gds_1)gout_3gout_4}{gm_1gm_2gm_3gm_4}$              |  |  |

| $\Delta Vo_{pp}$ | $V_{dd} - 2V_{dsat}$                                                                       | $V_{dd} - 2V_{dsat}$                                                                               | $V_{dd} - 2V_{dsat} - V_s$                                      |  |  |

| $V_{Nin}^2$      | $\frac{4K_BT(gm_2)^2X_3}{(g_1gm_2+(g_1+gds_2+g_{in})gm_4)^2}$                              | $\frac{4K_BT}{(gm_1gm_4Rout_4)^2}\left(\gamma(gm_1+gm_2)+\frac{1}{R_c}+\frac{1}{R_{large}}\right)$ | $\frac{4K_BT}{(X_4)^2}\left(\gamma gm_2 + \frac{1}{R_1}\right)$ |  |  |

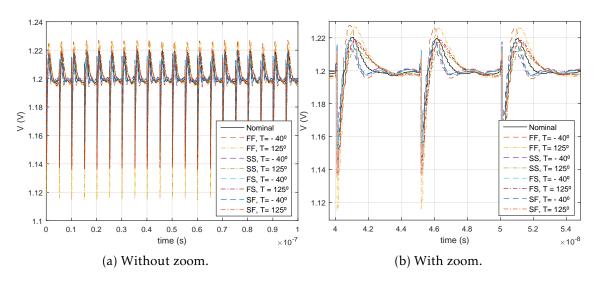

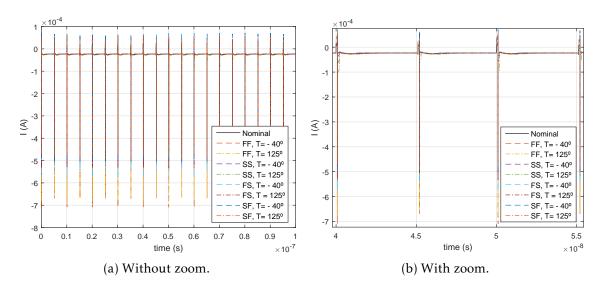

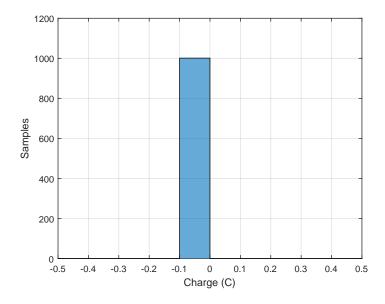

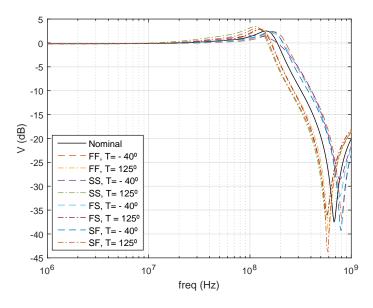

| Bandwidth        | $\frac{g_1(gm_2 + gm_4)}{(C_1 + cdb_4 + C_L)gm_2}$                                         | $\frac{gm_1}{C_{bat} + C_c + cgd_1 + cgs_1 + C_{p4}}$                                              | $\frac{gm_2}{cgd_2 + cgs_2 + C_{p3}}$                           |  |  |