UNIVERSIDAD DE SEVILLA Departamento de Ciencias de la Computación e Inteligencia Artificial

# Optimization of high-throughput real-time processes in physics reconstruction

A Thesis submitted for the degree of Doctor of Philosophy Escuela Técnica Superior de Ingeniería Informática Universidad de Sevilla

Daniel Hugo Cámpora Pérez

Approval of the Thesis Supervisors

PhD. Agustín Riscos Núñez

PhD. Niko Neufeld

A mi compañera de aventuras.

### CONTENTS

| AC | CKNOWLEDGMENTS |                                                                                                             |          |

|----|----------------|-------------------------------------------------------------------------------------------------------------|----------|

| CO | NTE            | NTS OF THE DOCUMENT                                                                                         | 1        |

| I  | DDE            | LIMINARIES                                                                                                  |          |

| 1  |                |                                                                                                             | 0        |

| T  | 1.1            | A Large Hadron Collider beauty experiment                                                                   | 9<br>10  |

|    | 1.1            | 1.1.1       Tracking subdetectors                                                                           | 10       |

|    |                | 1.1.1       Hacking subdetectors       1.1.2         1.1.2       Particle identification system       1.1.2 |          |

|    | 1.2            | The Data Acquisition System                                                                                 | 10       |

|    | 1.2            | 1.2.1 Event readout                                                                                         | 19<br>20 |

|    |                | 1.2.2         Event building                                                                                | 21       |

|    |                | 1.2.3         Event filtering                                                                               | 23       |

|    | 1.3            | The High Level Trigger                                                                                      |          |

|    | 1.9            | 1.3.1 The LHCb software upgrade                                                                             | 26       |

| 2  | ΡΔR            | ALLEL COMPUTING                                                                                             | 29       |

| 2  | 2.1            | Types of parallel processors                                                                                |          |

|    | 2.2            | Memory                                                                                                      | 35       |

|    |                | 2.2.1 The Roofline model                                                                                    |          |

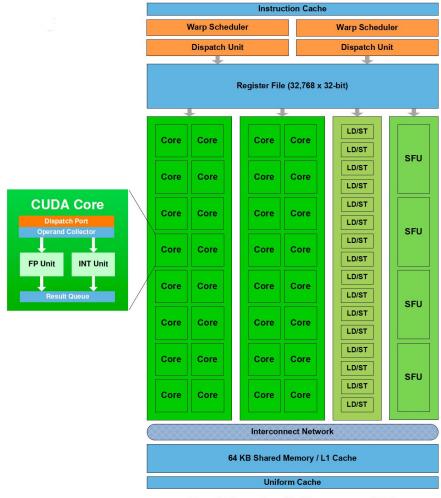

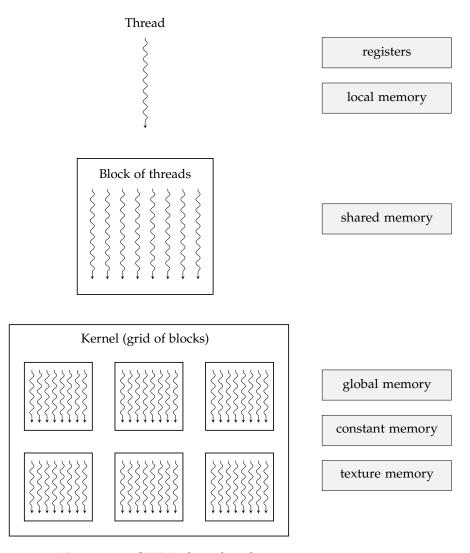

|    | 2.3            | Graphics Processing Units                                                                                   |          |

|    |                | 2.3.1 GPUs as parallel coprocessors                                                                         |          |

|    |                |                                                                                                             |          |

| II |                | ALLEL ALGORITHMS                                                                                            |          |

| 3  |                | CODING ALGORITHMS                                                                                           | 51       |

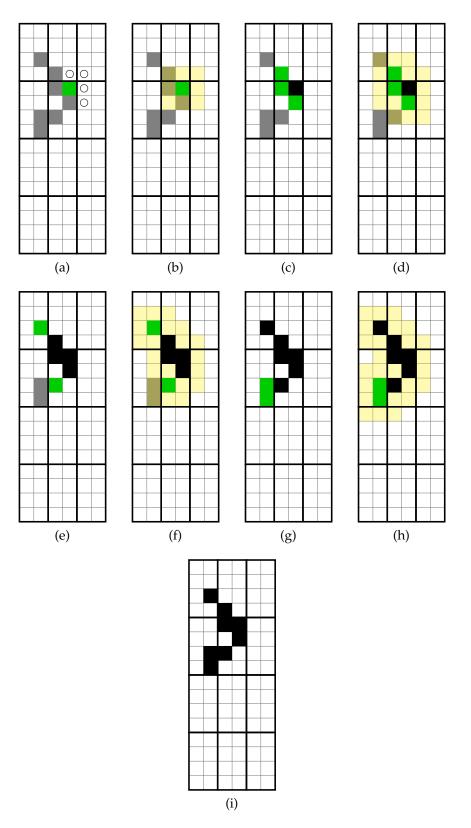

|    | 3.1            | Velo decoding and clustering                                                                                | 51       |

|    |                | 3.1.1 Velo clustering                                                                                       |          |

|    |                | 3.1.2 Velo estimate input size                                                                              |          |

|    |                | 3.1.3 Prefix sum Velo clusters                                                                              | 60       |

|    |                | 3.1.4 Mask clustering                                                                                       |          |

|    |                | 3.1.5 Physics efficiency                                                                                    |          |

|    | 3.2            | UT decoding                                                                                                 | 66       |

|    |                | 3.2.1 Overview of UT decoding                                                                               | 67       |

|    | 3.3            | SciFi decoding                                                                                              | 69       |

|    | 3.4            | Muon decoding                                                                                               | 70       |

| 4  |                | CK RECONSTRUCTION                                                                                           | 73       |

|    | 4.1            | Efficiency indicators                                                                                       | 74       |

|    | 4.2            | Overview of track reconstruction methods                                                                    | 77       |

|    |                | 4.2.1 Local methods                                                                                         | 77       |

|    |                | 4.2.2 Global methods                                                                                        | 79       |

| 5  | VEL            | O TRACKING                                                                                                  | 83       |

|     | 5.1 Discussion                                      | 33         |  |

|-----|-----------------------------------------------------|------------|--|

| 6   | FORWARD TRACKING                                    | 37         |  |

|     | 6.1 Histogramming method                            | 39         |  |

|     | 6.2 Looking Forward                                 | )2         |  |

| 7   | KALMAN FILTER 10                                    | )1         |  |

| -   | 7.1 Discussion                                      | 93         |  |

| III | FRAMEWORK                                           |            |  |

| 8   | <b>B</b> A FRAMEWORK FOR MASSIVELY PARALLEL PHYSICS |            |  |

|     | RECONSTRUCTION 10                                   | 9          |  |

|     | 8.1 Framework design                                | 1          |  |

|     | 8.2 Control flow                                    |            |  |

|     | 8.3 Data flow                                       |            |  |

|     | 8.4 Framework performance                           | 20         |  |

|     | 8.5 Continuous integration                          | 26         |  |

| 9   | TRACKING SEQUENCE PHYSICS EFFICIENCY12              | 29         |  |

|     | 9.1 Velo reconstruction efficiency                  |            |  |

|     | 9.2 UT reconstruction efficiency                    | ;0         |  |

|     | 9.3 Forward tracking efficiency                     | ;1         |  |

| 10  | PERFORMANCE ANALYSIS                                | 9          |  |

|     | 10.1 Methodology                                    | ;9         |  |

|     | 10.2 HLT1 sequence performance analysis 14          | 2          |  |

|     | 10.2.1 Parameter scans                              | -5         |  |

|     | 10.2.2 Velo sequence performance analysis 14        | 8          |  |

|     | 10.3 Integration in Data Acquisition system 15      | ;2         |  |

| IV  | THESIS RESULTS                                      |            |  |

| 11  | CONCLUSIONS 16                                      | 53         |  |

|     | 11.1 Summary                                        | 53         |  |

|     | 11.2 Publications                                   | 58         |  |

|     | 11.3 Future work                                    | <b>'</b> O |  |

| AP  | PENDICES                                            |            |  |

| Α   | A FAST LOCAL ALGORITHM FOR TRACK RECON-             |            |  |

|     | STRUCTION ON PARALLEL ARCHITECTURES 17              | 75         |  |

| В   | AN EFFICIENT LOW-RANK KALMAN FILTER FOR             |            |  |

|     | MODERN SIMD ARCHITECTURES 18                        | 37         |  |

En el verano de 2010 tuve la suerte de ser escogido como *Summer Student* en el CERN. Y a ese comienzo le siguieron nueve largos años aprendiendo y creciendo, tanto en lo profesional como en lo personal. Mucho de lo que he recogido durante mi vida aquí está plasmado en esta tesis.

Tengo a muchos a los que agradecer. A Vero, por la felicidad diaria que es estar junto a ella. Me encanta compartir la vida contigo. A mis padres, por su amor y su apoyo constante. Todo lo que he conseguido es gracias a vosotros.

Quiero agradecer a mis amigos todas las bromas que han hecho la vida más divertida estos años. A mi amigo Lolo, que ha pasado mucho frío, sobre todo en ausencia del gato. A mi amigo Dani García, quien es sutil como un submarino. A los amigasos, Alvaro, Paco, Adri y Dani Arenas, por las infinitas risas que nos hemos echado juntos. A José, por los poemas en portugués. A Andrés, Zapi y Ale, por nuestras discusiones informáticas, y a Miri, por nuestras discusiones artísticas. A los amigos de siempre, Jesús, Rocío, Fran, Seba y Jorge, con los que tengo un vínculo atemporal. A Fer, con el que disfruto entendiendo las tonterías que pasan en el mundo. A Luz, por nuestra cándida amistad. A Vlado, por las discusiones de filosofía y de la vida. A Ome por las tardes de Smash. A Ana, Cris, David y Shenandoah, por hacer Ginebra divertida a ritmo de Swing. A los amigos del club de ajedrez Tenis Betis, que alegraron Ginebra pese al frío. A Miguel, por esas tardes de julio. A mi nueva familia almeriense, por todos los momentos de felicidad.

He tenido la suerte de trabajar en el departamento de Ciencias de la Computación e Inteligencia Artificial junto a geniales compañeros que me han apoyado en todo lo que he necesitado. En especial, muchas gracias a mi tutor y director Agustín Riscos Núñez, quien me ha guiado y me ha enseñado lecciones muy valiosas para convertirme algún día en Jedi. También a Mario de Jesús Pérez Jiménez, quien me ha alentado siempre y ha sido un modelo a seguir. Muchas gracias a David "*man*" Orellana Martín por las bromas lingüísticas y el buen humor diario, y a Luis Valencia Cabrera, al que le debo todavía algún que otro queo. A Miguel Ángel Martínez del Amor por las discusiones *cuderas*, que espero que sigan por mucho tiempo. A Álvaro Romero Jiménez y Carmen Graciani Díaz, que me recibían con brazos abiertos cada vez que volvía a la escuela por navidad. A Luis Felipe Macías Ramos, por los primeros pasos en la burocracia del doctorado. A Miguel Ángel Gutiérrez Naranjo, con el que la filosofía y la informática se mezclan en nuestras discusiones. Muchas gracias a Fernando Sancho Caparrini, por motivarme y ofrecerme siempre nuevas ideas. A Ignacio Pérez Hurtado de Mendoza, por las discusiones de C++. A Juan Antonio e Isabel Nepomuceno, por su cercanía y sus consejos.

I would also like to thank all of those who have made the experience at CERN and its surroundings unforgettable.

Many thanks to my friend Nazim, with whom it is always a pleasure to discuss the craziest life stories. To my friends Kazuya and Naomi, for many travels, experiences and board games together. Many thanks to my musical friends Mireia Crispín Ortúzar, Gonzalo Martínez, Laura Cantagalli and John Duxbury, who share my passion for music and have allowed me to sing my way through Switzerland. Thanks to Schnucki, Donal, Matevz, Gianni, Atsuko, Krina, Laura and Kate for all the happy times together at CERN. To Jacob, for our friendship and for his ability to stand *dilemmas*. To Ramón and Carmen, for the yearly sevillanas and rebujitos we have shared. To Marco, Rossana and Ema for their love and our stories together. To Albi, Ludi and Thomas for our hikes and good moments. To Xavi and Elisabet, for their friendship and support. To Arantza, Luismi, Brij and José Mazorra, for the Allen support and for helping give the thesis some sweet style.

Many colleagues and friends have made working at CERN a wonderful experience. Thanks to Niko Neufeld, who has been my supervisor, friend and office mate for the last seven years, and has propelled my career while making it fun. Thanks to Rainer Schwemmer, for his ingenuity, support and most importantly, our karaoke sessions. To Plácido for our work together in Allen and the everyday discussions. To Flavio, for his contributions to the forward tracking and our friendship. To Laura, for her ARM and POWER powers. To Tommaso, for our fruitful DAQ discussions. Thanks to the LHCb Online team for the support, the hard work and the many barbecues. To those that were involved in the HTCC, especially to Omar, Jon, Sebastien, Christian and Luca, who contributed to the early work in this thesis. Thanks to Conor for our discussions and his comments on the thesis. Thanks to O. Bouizi at Intel and C. Potterat for their contributions to the Kalman filter work. Thanks to A. Hehn at NVIDIA for his help throughout the development of Allen. Big thanks to all the Allen team, especially to Dorothea, Roel and Vava, for all the hard work to make the GPU HLT1 a reality. Thanks a lot to the LHCb collaboration, and especially to Ben, Marco Cattaneo and Marco Clemencic, for all the support received throughout the years.

Finally, I am very grateful to Brian Martin, who has always been a good influence, for opening the doors of the ATLAS netadmin team to me and letting me into the fun of Data Acquisition, and in particular for his help in proof-reading this thesis. Thanks to my *prieteni* Dan, Irina, Stefan and Silvia, and to Eukeni, for my first DAQ steps which have evolved into friendship. Special thanks to Prof. Dr. G. Raven and Prof. Dr. I. Kisel for providing reports for this thesis.

Muchas gracias a todos,

Daniel

The present document is organized in four parts, adding up to a total of 11 chapters. Their contents are succinctly described in the following.

#### Part I: Preliminaries

The **first chapter** introduces some basic notions of particle physics. The LHCb detector, placed at the Large Hadron Collider in the European Organization for Nuclear Research (CERN), and all the subdetectors composing it are briefly discussed. The Data Acquisition system of LHCb is presented in its three constituent steps: Event readout, event building and event filtering. The filtering software to which this thesis contributes is presented as the High Level Trigger. The chapter closes quantifying the challenge the upcoming upgrade detector rates signify.

**Chapter 2** introduces architectural concepts and performance metrics of modern processors. The historical processor evolution from sequential into parallel chips is presented. The types of parallel processors are shown, alongside various categories of parallelism, required to make efficient use of modern processors. The relation of memory performance with processor performance is discussed. Several memory-related fundamental concepts are presented, and a visual tool known as the *Roofline model* to characterize processors with the relation between processor and memory performance is described. The first part ends with a description of Graphics Processing Units (GPUs), an architecture for which much of the software in this thesis has been written. GPUs are presented as coprocessors to tackle parallel workloads, and several examples from the literature are shown.

#### Part II: Parallel algorithms

**Part II** discusses the reconstruction algorithms contributed as part of this thesis. The contributions are organized in five

chapters that cover a variety of relevant problems in High Energy Physics (HEP) applications, and that specifically occur in the High Level Trigger reconstruction sequence of LHCb. All the contributed software targets parallel multi and many-core SIMD architectures. This thesis contributes to the following areas of parallel software for HEP: decoding (chapter 3), clustering (chapter 3, section 3.1), pattern recognition (chapters 4, 5 and 6) and the Kalman filter (chapter 7).

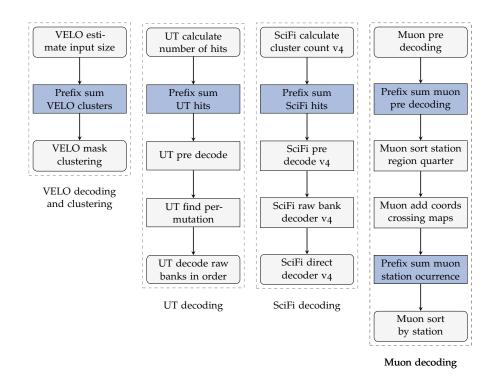

**Chapter 3** presents the decoding sequences of four LHCb subdetectors. For each subdetector, a parallel decoding design is presented, alongside details of the implementation developed. For the *Velo* subdetector, the steps of the design are justified. An original parallel clustering algorithm is described in depth, and a validation of the method is presented. The design of the other three subdetectors parallel decoding algorithms are succinctly described in three respective sections. A similar pattern to the Velo decoding is followed to achieve a parallel implementation taking into account the specifics of each subdetector.

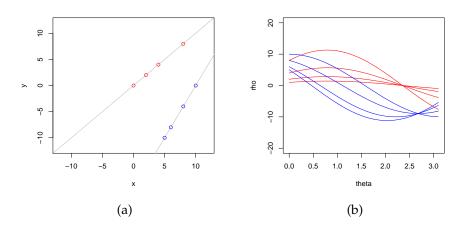

**Chapter 4** introduces the main concepts and techniques related to the problem of pattern recognition of particle trajectories (tracks). The *efficiency indicators* determining the goodness of tracks are discussed, and the specifics of the criteria of LHCb tracking detectors are presented. An overview of tracking methods, categorized into local and global methods, is described and discussed. This chapter lays the foundations for the following discussions on tracking in the next two chapters.

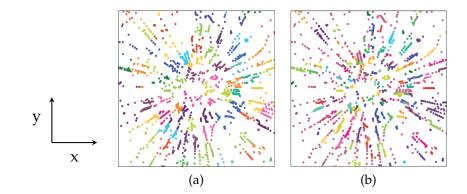

A parallel Velo tracking algorithm *Search by triplet* is presented and discussed in **chapter 5**. The method is described in detail in publication [1], included as appendix A of this thesis. The preexisting sequential method is analyzed and several shortcomings are identified that prevent parallelization. A parallel local method is designed, targeting SIMD architectures, and CPU and GPU versions are developed. Each of the constituent parts of the algorithm are qualified in terms of computational complexity. The algorithm uses efficient memory structures for SIMD architectures, and data reductions based on tight search windows. An iterative two-step tracking procedure guarantees no revisits of detector measurements, resulting in an efficient access pattern to processor memory, using spatial and temporal locality.

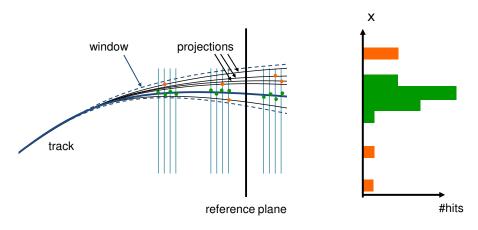

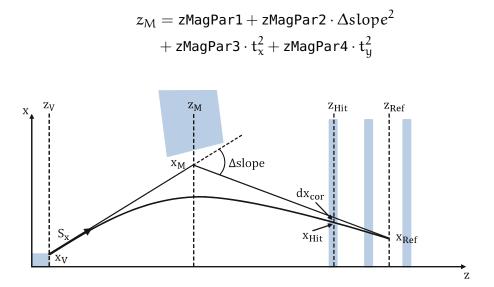

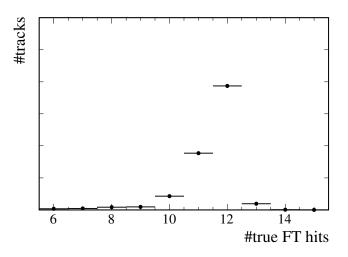

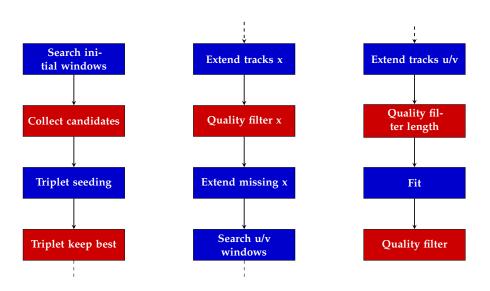

**Chapter 6** presents a parallel algorithm for Forward tracking, which involves extending tracks to the LHCb *SciFi* subdetector.

The bending of particles due to the LHCb magnet is described, alongside a simplified model describing its effect. The sequential algorithm used in previous runs of the detector is presented and discussed in depth. A parallel algorithm *Looking Forward* is presented, which consists of 12 steps. The design is discussed and each of the steps is qualified in terms of computational complexity. A novel triplet seeding method using specialized hardware is presented, which builds triplets similarly to Search by triplet. The algorithm reduces branched code, and runs efficiently on GPU architectures due to their data-parallelism.

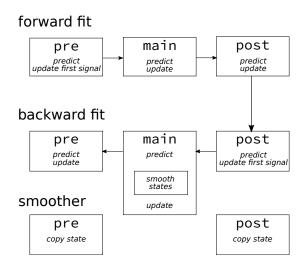

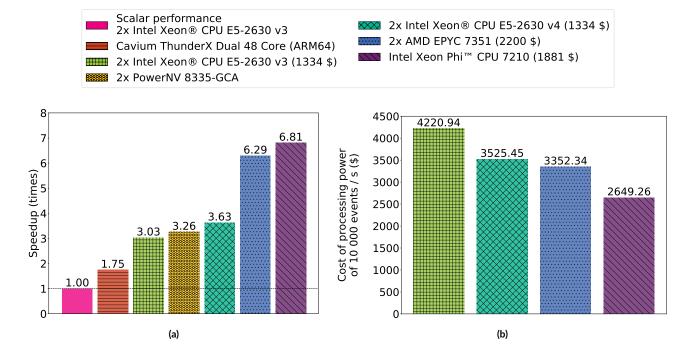

This part ends with the contributions on the Kalman filter in chapter 7. The chapter introduces the Kalman filter formulation and links it with the LHCb detector use case. The publication [2] is presented as part of this thesis in appendix **B**. The existing literature is analyzed, and it is deemed necessary to develop a solution given the specific conditions of the LHCb Kalman filter execution. Three software algorithms are contributed: a proto-application Cross Kalman Mathtest allows to compare performance across CPU and GPU architectures; the Cross-Kalman application mimics the conditions under which the Kalman filter is executed in the LHCb software and serves as a crossarchitecture implementation of the Kalman filter aiming to maximize performance; the findings of the previous two applications are integrated in the LHCb framework in *TrackVectorFitter*, and the performance is validated under LHCb framework run conditions. The applications use a custom scheduler to efficiently use data parallelism in SIMD processors. Roofline models of several processors are shown, demonstrating the arithmetic formulation obtains the peak performance of the processors analyzed.

#### Part III: Framework

The software contributions of this thesis target a variety of architectures. Concretely, the LHCb High Level Trigger 1 reconstruction application was identified as a target where GPUs could be used. However, the LHCb software was not built to efficiently use hardware accelerators. This thesis contributes a framework to run HEP reconstruction on GPUs (chapter 8). During the development of this thesis, a parallel realization of the full High Level Trigger 1 application was completed in this framework. The physics efficiency of the sequence is presented (chapter 9), and the performance of the entire GPU HLT1 sequence is also described (chapter 10).

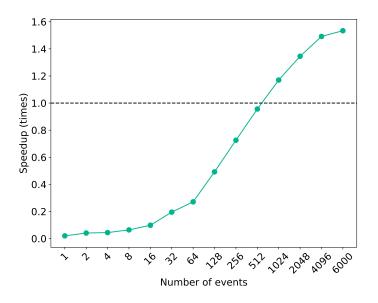

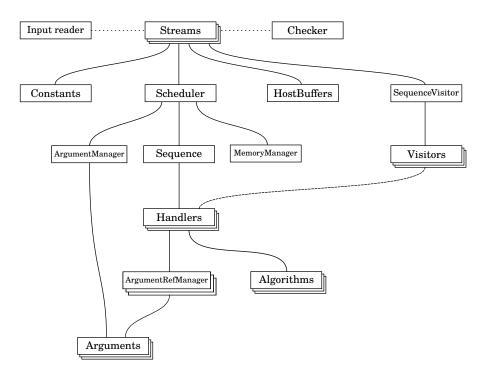

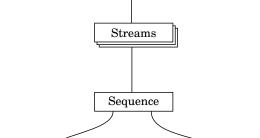

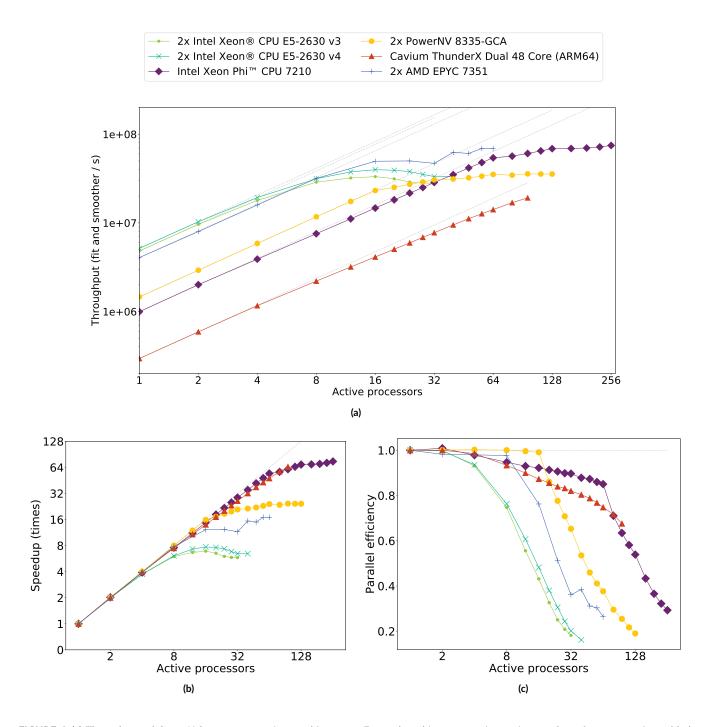

**Chapter 8** presents a framework for massively parallel physics reconstruction *Allen*. The framework allows algorithms to be run in parallel on thousands of collision events concurrently, exploiting many-core architectures. The design of the framework and all its parts are discussed. The control flow permits execution of a defined set of algorithms. The data flow copes with the memory capacity constraints of GPUs. The performance of the framework is presented under various configurations, and Continuous Integration features are shown.

**Chapter 9** discusses the physics efficiency of the tracking sequence. The efficiency of the reconstruction after processing three subdetector algorithms is presented. The efficiency indicators of chapter 4 are used. The HLT1 physics efficiency requirements are shown to be met.

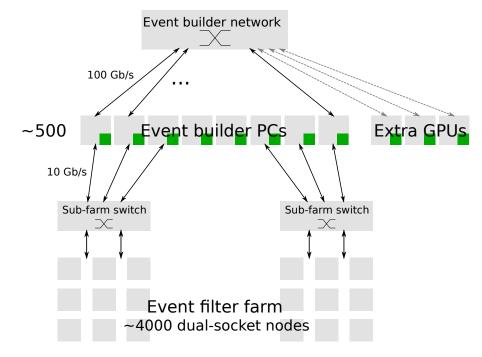

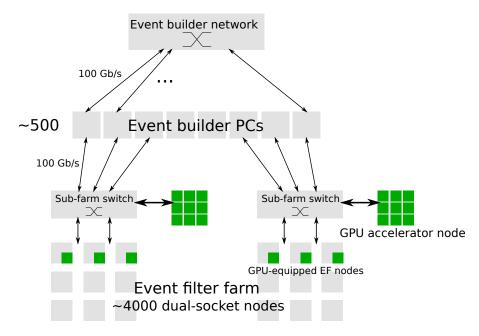

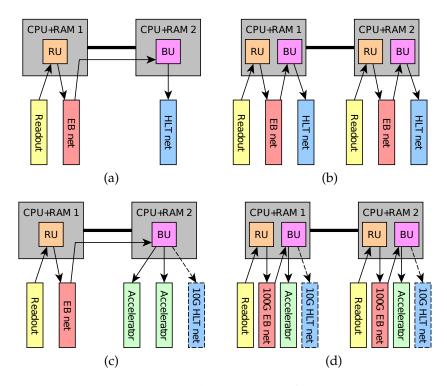

This part finishes with a performance analysis of the HLT1 sequence run on GPUs in Allen, in **chapter 10**. The methodology of the tests is presented, and the HLT1 performance is discussed in depth, on a variety of GPU hardware. Performance is analyzed on its own, and as a function of price and power consumption. The entire sequence is profiled and characterized, and parameters are optimized through scans. Updated results of the Velo sequence described in chapter 5 are presented. Finally, integration considerations into a prospective Data Acquisition System with GPU processing are discussed.

#### Part IV: Thesis results

The conclusions of the thesis are discussed in **chapter 11**. The presented work makes significant contributions in various HEP related software areas. It also represents the first attempt at a reconstruction of the LHCb HLT1 trigger stage on GPUs, to which the framework and much of the tracking sequence have been presented. Future work will further this development and extend upon the results presented here with the intention of making the GPU HLT1 a production-ready environment.

#### CONTRIBUTIONS

It is worth noting the following original contributions of this document.

- The parallel decoding algorithms designs of the subdetectors Velo, UT, SciFi and muons are original contributions of the author. The entirety of the Velo and UT decoding sequences have been implemented by the author, including the Velo clustering design and implementation. The parallel SciFi decoding implementation has been done in collaboration with L. Funke, and the parallel muon decoding implementation in collaboration with D. Pliushchenko.

- The Velo tracking sequence has been designed and implemented by the author. The original work has been presented in the following publication:

- D. H. Cámpora Pérez, N. Neufeld, and A. Riscos Núñez. A Fast Local Algorithm for Track Reconstruction on Parallel Architectures. In: 2019 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW) (2019), pp. 698–707. Included as appendix A.

- The UT tracking sequence has been done in collaboration with P. Fernandez Declara. The following publication stems from this work:

- P. Fernandez Declara, D. H. Cámpora Pérez, J. Garcia-Blas, D. vom Bruch, J. D. Garcia, and N. Neufeld. A parallel-computing algorithm for high-energy physics particle tracking and decoding using GPU architectures. In: *IEEE Access* (2019), pp. 91612–91626.

- The Forward tracking parallel algorithm design and the triplet search therein is original work by the author. The implementation has been done in collaboration with D. vom Bruch and F. Pisani. This work represents the first implementation of the LHCb Forward tracking algorithm on GPUs.

- The Kalman filter applications *Cross-Kalman Mathtest*, *Cross-Kalman* and *TrackVectorFitter* have been designed and implemented by the author. The collaboration with O. Awile and O. Bouizi has led to an in-depth analysis of modern Intel architectures and the elaboration of the Roofline

plots presented as part of [2]. C. Potterat has helped in the comparison of physics efficiency performance figures. The work has been presented in multiple occasions in the course of this thesis:

- D. H. Cámpora Pérez. LHCb Kalman Filter cross architecture studies. In: *Journal of Physics: Conference Series* 898.3 (2017), p. 32052.

- D. H. Cámpora Pérez, O. Awile, O. Bouizi, N. Neufeld. Cross-architecture Kalman filter benchmarks on modern hardware platforms. In: *Journal of Physics: Conference Series* 1085 (Sept. 2018), p. 032046.

- D. H. Cámpora Pérez, O. Awile, and C. Potterat. A High-Throughput Kalman Filter for Modern SIMD Architectures. In: *Euro-Par 2017: Parallel Processing Workshops*. Springer International Publishing, 2018, pp. 378–389.

- D. H. Cámpora Pérez and O. Awile. An efficient lowrank Kalman filter for modern SIMD architectures. In: *Concurrency and Computation: Practice and Experience* 30.23 (Dec. 2018), e4483. Included as appendix B.

- Finally, the *Allen* framework has been designed and originally implemented by the author. Further iterations of the framework are the effort of a collaboration led cooperatively by R. Aaij, D. vom Bruch, and the author. The work of Allen contains at this moment contributions of tens of developers and several external collaborators. The physics efficiency and performance of the framework are the fruits of this collaborative work during the course of 18 months.

Part I

## PRELIMINARIES

#### LHCB

ERN, the European Organization for Nuclear Research, is the biggest particle physics laboratory in the world. At CERN, a wide variety of physics experiments take place, exploring fundamental questions with regards to the composition of the universe, such as what happened in the Big Bang, the difference between matter and antimatter, or the nature of dark energy and dark matter.

The drive for discoveries in the particle physics domain requires the latest technology in all components involved in the detection of particle collisions. At CERN, a network of particle accelerators accelerate particles to a speed close to the speed of light at the Large Hadron Collider (*LHC*) [3], a 27-kilometer synchrotron accelerator. High precision measurements of particle collisions are carried out in the four major particle detectors ATLAS, ALICE, CMS and LHCb. Trigger and data acquisition systems filter data in real-time at a rate of tens of millions particle collisions per second. A global distribution system *Grid* distributes the data around the globe for posterior analysis. All elements in this chain are state-of-the-art, and new technologies are continuously being explored for pushing the limits of science in the search of *new physics*.

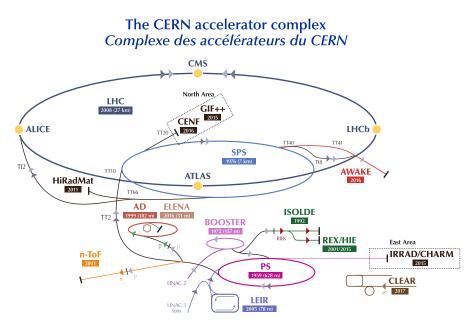

The CERN accelerator complex is depicted in Figure 1.1. Two kinds of particles, protons and heavy ions, are injected into the accelerators at different times. Particles are accelerated through the linear accelerator *LINAC2* and the synchrotrons *Booster*, *PS* and *SPS* prior to being injected into the LHC. The energy of particles is increased within every subsequent accelerator, to a design energy of 6.5 TeV at the LHC. Particles are collided in each of the four major LHC detectors at a combined energy of 13 TeV.

Particles are not accelerated individually, but are rather grouped into *particle bunches*. Hence, instead of individual particle collisions, crossings of particle bunches are discussed. The probability of an actual collision happening when two particle bunches cross is measured by the *average number of collisions per*

Figure 1.1: CERN accelerator complex. Image from [4].

*bunch crossing*  $\nu$ . Each bunch crossing is also referred to as an *event*, and the event rate is measured in Hz. The design event rate of the LHC is 40 MHz, where one event occurs every 25 ns.

Even though the design collision energy is not foreseen to change, other factors impact the collision rate. The *luminosity* is a metric used in accelerator physics to determine the number of particle collisions detected N in a unit of time t to the interaction cross section  $\sigma$ ,

$$L = \frac{1}{\sigma} \frac{dN}{dt}$$

(1.1)

The luminosity of the LHC beam is set to increase in the next data-taking period to start in 2021, hence increasing the collision rate by roughly  $5\times$ . The LHC experiments are in an upgrade phase from 2019 until 2021, whereby many components pertaining to the detectors and data acquisition systems will be either updated or changed completely, in the pursuit of new physics results.

#### 1.1 A LARGE HADRON COLLIDER BEAUTY EXPERIMENT

The Large Hadron Collider beauty (*LHCb*) experiment [3, 5] is one of the four major experiments at the LHC. It is a single-arm forward spectrometer, designed for precision measurements of the decay channels that could explain matter-antimatter asymmetry, also known as *CP violation*.

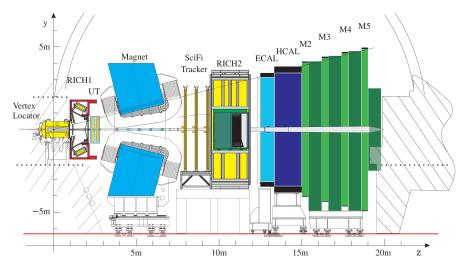

The LHCb detector will be upgraded through 2021 in order to increase precision by 10 times on the main observables of the b and c-quark sectors. The LHCb upgrade detector is depicted in Figure 1.2. The ordinate coordinate system depicts the beam line axis, Z, and is centered at the nominal collision point.

Figure 1.2: LHCb upgrade detector.

When particles collide at the point of collision placed inside the LHCb detector in the high energy conditions of the LHC, the original particles decay into new particles that leave traces in the subdetector instruments conforming the LHCb detector. The process of *reconstruction* consists in reproducing the conditions under which said traces were left in the detector. The quality of the reconstruction achieved can be measured by Monte Carlo simulations in terms of *reconstruction efficiency*. A higher reconstruction efficiency leads to a better identification of the phenomena driving particle decays, and ultimately to a better understanding of the physics foundations therein.

The LHCb detector does not have full coverage. That is, only a subset of produced particles will be detected at LHCb. The coverage angle of the detector in the *forward region* (positive side of horizontal axis in Figure 1.2) is of 300 mrad in the XZ plane, and of 250 mrad in the YZ plane. The LHCb magnet bends charged particle trajectories in the XZ plane, which explains the difference in the coverage angles. A small subset of particle trajectories in the *backward region* are measured at the first tracking subdetector in order to identify collision vertices (cref. 1.1.1). The LHCb detector is composed of three kinds of subdetectors. Tracking subdetectors detect signals in the particles path, from which the momenta and collision vertices are derived. Cherenkov subdetectors measure the velocity of particles. Finally, calorimeters measure the deposited energy of hadrons and electrons. These instruments allow the identification of individual particles by applying relations between momentum, mass and velocity and accounting for relativistic effects.

#### **1.1.1** *Tracking subdetectors*

As particles traverse the tracking subdetectors of LHCb, they interact with detector technology placed in their path. The problem of track reconstruction consists in determining the particle trajectories or tracks left by each individual particle throughout the detector.

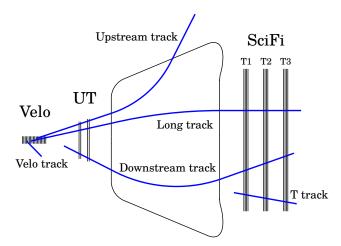

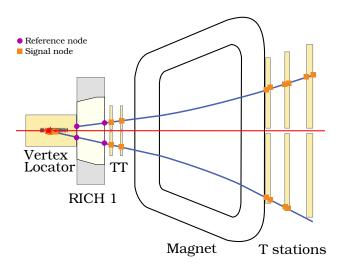

The tracking system of LHCb [6] consists of three subdetectors: The Vertex Locator (*VELO*), the Upstream Tracker (*UT*) and the Scintillating Fibre Tracker (*SciFi*). A magnet, placed between the UT and the SciFi, bends particles as a function of their charge in the XZ plane. Figure 1.3 depicts the tracking system of LHCb, alongside all possible track types.

Figure 1.3: LHCb track types.

The subdetectors visited by each particle determine the particle track type. VELO, upstream and long tracks are produced at the VELO. Even though the LHC beam collisions take place inside the VELO, produced particles may decay in their path, originating new particles in non-primary vertices. Downstream and T tracks are produced from particle decays, and originate from non-primary vertices.

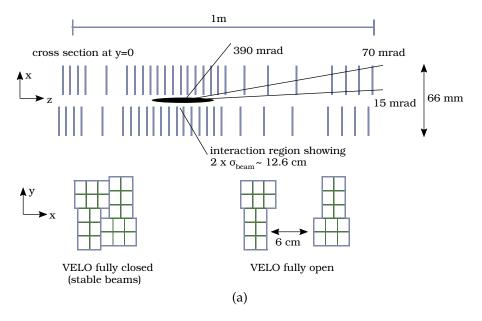

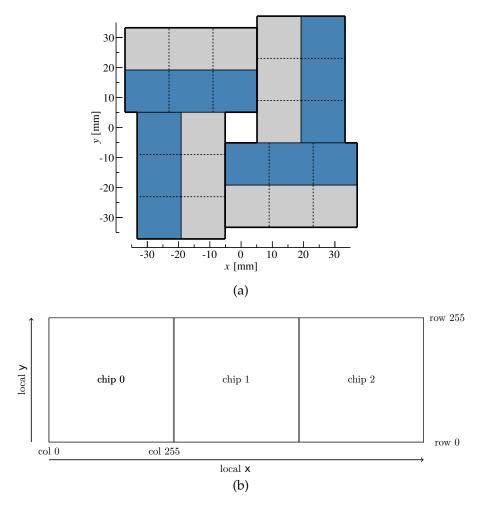

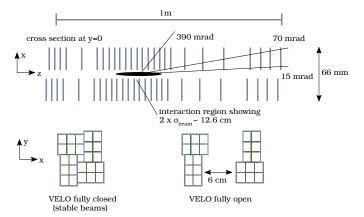

#### VELO

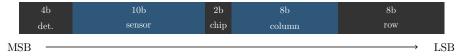

The Vertex Locator [7] is a tracking subdetector placed very closely to the interaction point. It consists of 52 modules placed on sides of the beam line. Each module in turn consists of 12 chips with a resolution of  $256 \times 256$  pixels each. Figure 1.4 depicts the entire detector alongside the beam axis (top), and a detail of one module (bottom). The VELO can be retracted while there is no stable beam in the LHC, in order to avoid damage and increase its lifetime.

Figure 1.4: A schematic of the upgrade Velo detector.

The VELO allows for precision measurement of the collision vertices, as well as creation of seeds for further track reconstruction in subsequent tracking detectors [8]. The LHCb magnet does not influence particle trajectories within the VELO, and hence particles travel in a straight line in this subdetector.

UΤ

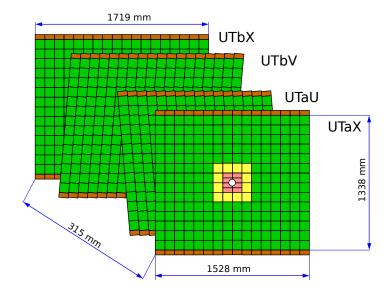

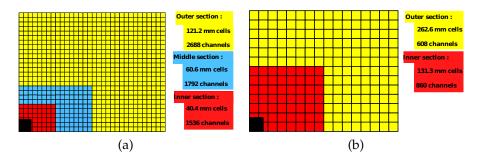

The Upstream Tracker [6] subdetector consists of four planes of silicon strips, named UTaX, UTaU, UTbV and UTbX. The first and last planes have vertical strips, whereas the middle planes are tilted by  $-5^{\circ}$  and  $5^{\circ}$  respectively. Figure 1.5 shows an

overview of the subdetector. By combining the measurements from the tilted U and V planes, the Y coordinate can also be determined. Each UT plane can be divided into 3 regions with different geometries, where the inner-most region has a finer granularity (orange in the Figure), and the outer regions have coarser granularity (yellow and green in the Figure).

Figure 1.5: Overview of the UT subdetector.

The UT adds information to the tracks reconstructed in the Velo and SciFi. The presence of a residual magnetic field allows measuring the charge and momentum of particles. It allows reconstruction of particles produced outside of the Velo, and of low momentum particles that form upstream tracks.

#### SciFi

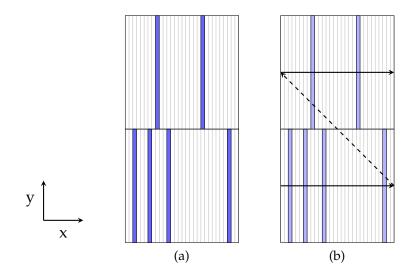

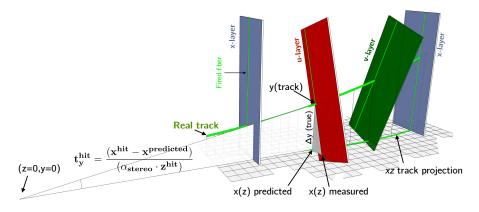

The Scintillating Fibre Tracker [6] consists of three stations placed after the LHCb magnet, in the forward region. They were designed to provide standalone pattern recognition with a high efficiency together with high resolution in the bending plane of the magnetic field. Each station is composed of four layers {x, u, v, x}, with scintillating fibers orientated at { $0^\circ$ ,  $5^\circ$ ,  $-5^\circ$ ,  $0^\circ$ } respectively. A side view of the SciFi tracking stations is shown in Figure 1.6. Each layer is composed of 12 modules, where the two central modules feature a cut-out to allow the beam-pipe to pass through the detector.

Modules are composed of six layers of thin scintillating fibres that react to the passing of charged particles by emitting light

Figure 1.6: (a) Arrangement of the SciFi tracker detection layers. (b) Modules within one U plane. Figure from [6].

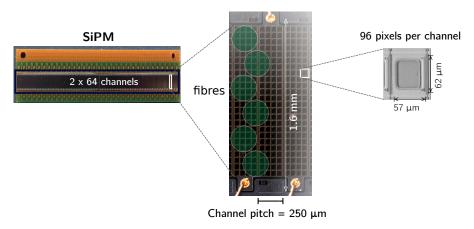

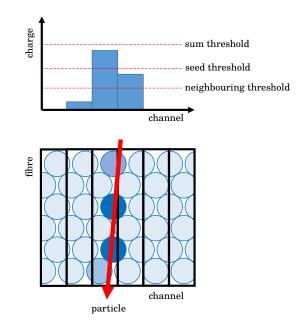

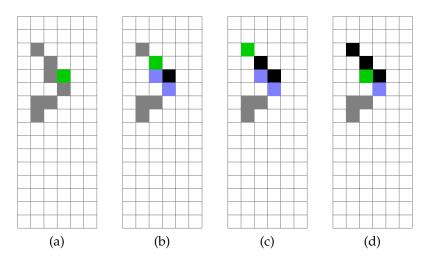

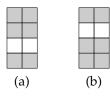

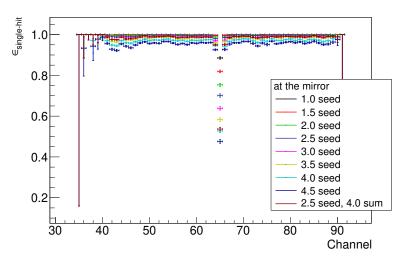

into its fibre ends. Fibres are arranged in parallel, and a fibre is 250 µm in diameter. Silicon Photo-Detectors *SiPMs* are solid state photon detection devices that detect photons into pixel channels. Each SiPM is composed of 2 blocks of 64 channels each. Figure 1.7 depicts a SiPM (left), a detail of several contiguous channels with the placement of six fibres (center), and a pixel (right).

The position of the particle can be determined with a weighted average of neighboring fired pixel channels. Figure **1**.8 depicts this process. Photons produced in each fibre fire SiPM pixels. A weighted average sum is then performed over the fired pixels of each channel in order to determine the position of the particle. The signal is discriminated according to two conditions: There must be at least one channel with a charge over the *seed threshold*, and the sum of all neighboring channel charges over the *neighboring threshold* must be over the *sum threshold* [10].

Figure 1.7: Detail of SiPM. Image from [9].

Figure 1.8: Detection of a particle position as it crosses a module.

The SciFi subdetector allows detection of long, downstream and T tracks. Long tracks have a good momentum resolution. Tracks reconstructed in the SciFi subdetector are further analyzed with the particle identification system.

#### **1.1.2** *Particle identification system*

#### Muon stations

Detection of muons is a fundamental part of the physics program of LHCb. In particular, they are required for detecting very rare decays<sup>1</sup> such as  $B_s \rightarrow \mu^+\mu^-$ ,  $B_s^0 \rightarrow \mu^+\mu^-$  or  $B^0 \rightarrow K^*\mu^+\mu^-$ , which can provide evidence of New Physics.

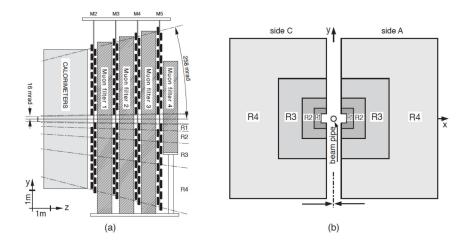

The upgraded LHCb detector will feature four muon stations [11], as shown in Figure 1.9. The stations are placed behind the hadronic calorimeter, and are interleaved with iron walls that act as muon filters. The muon detectors are equipped with Multi–Wire Proportional Chambers *MWPCs*, and the detector is divided in several regions with a varying granularity of MWPCs according to the expected variation in particle rate from the central regions to the periphery.

Figure 1.9: (a) Side view of the Muon Detectors. (b) Station layout with the four regions R1-R4 indicated.

The requirements of this subdetector are to guarantee a high reconstruction and identification performance of muons, while maintaining a low misidentification rate to other particle types. These requirements were already met prior to the LHCb upgrade, and have in fact relaxed for the upgrade as the LHCb trigger system will be fully done in software (cref. 1.3).

#### Cherenkov detectors

The speed of light depends on the refractive index of the medium of tranmission. It is possible that particles move through certain media at a speed faster than the speed of light in that medium. When that occurs, a cone of photons is emitted from the particle

<sup>1</sup> The particles referenced are part of the Standard Model of particle physics.  $\mu$  are fundamental lepton particles, whereas B-mesons and K are two-quark combinations known as mesons.

at an angle  $\theta$ , known as *Cherenkov radiation*. There is a relation between the angle of emission of the cone of photons, the refractive index of the material or radiator n and the velocity of the particle  $\beta$  [12]:

$$\cos(\theta) = \frac{1}{n\beta} \tag{1.2}$$

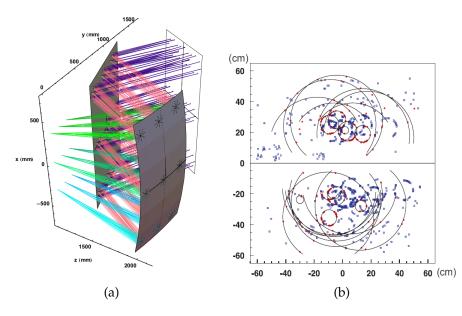

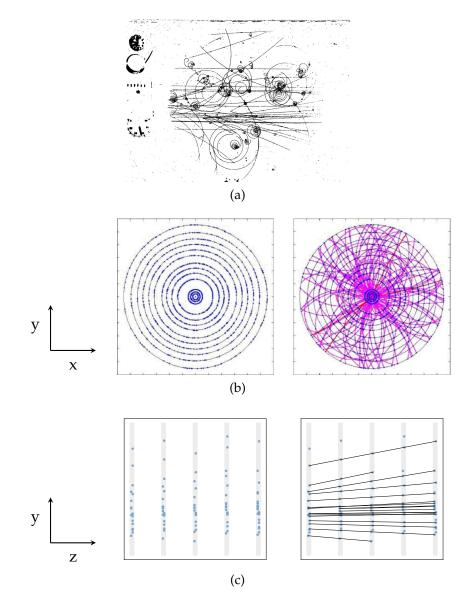

LHCb is equipped with two Ring Imaging Cherenkov (*RICH*) detectors [11], *RICH1* and *RICH2*. Each of them is composed of a radiator gas, mirrors and Multi-anode Photon Multiplier detectors *MaPMTs*. As particles move through either of the RICH radiators of LHCb, a cone of Cherenkov light is produced. The photons produced are reflected on a section of a spherical mirror and a planar mirror, prior to being detected in MaPMTs. Figure 1.10a depicts this process. The resulting image in the MaPMTs, shown in Figure 1.10b, contains slightly deformed circumferences that can be reconstructed and assigned to tracks, for a precise determination of the velocity of the particle.

Figure 1.10: (a) Simulation of Cherenkov photons and their reflection off the mirrors of RICH1. (b) Simulation of detected Cherenkov photons in both sides of RICH1.

The RICH reconstruction yields a precision measurement of the velocity of particles through the radiator gas. When combined with the momentum measured in the tracking stations, this allows identification of individual particles. The RICH system of LHCb provides particle identification of charged hadrons over the momentum range 1.5-100 GeV.

#### Calorimeters

The main purpose of a calorimeter is to measure the energy deposit and position of particles. The LHCb calorimeter system [11, 13] is composed of a hadronic calorimeter (*HCAL*) and an electromagnetic calorimeter (*ECAL*). The system can identify hadrons, electrons and photons. In particular, in LHCb they enable the detection of *B*-decay channels containing a prompt photon or  $\pi^0$ .

Figure 1.11 show a front view of the LHCb calorimeters. The hit density varies by two orders of magnitude between the sections closer to the beam pipe and the outer sections. Therefore, the size of the cells vary accordingly. The ECAL and HCAL absorb energy of photons, electrons and hadrons.

Figure 1.11: (a) Electromagnetic calorimeter (*ECAL*). One quarter of the detector is shown. The cell dimensions of the ECAL are shown. (b) Front face of the hadronic calorimeter (*HCAL*). One quarter of the detector is shown.

#### 1.2 THE DATA ACQUISITION SYSTEM

The upgraded LHCb detector will produce data at an event rate of 30 MHz with an average event size of  $100 \text{ kB}^2$ , for an estimated total throughput of 40 Tb/s. In order to cope with the immense amount of data produced by the detector, data are fed through a data acquisition system and filtered prior to being stored into long-term storage.

<sup>2</sup> The *event size* refers to the size of the raw data of each bunch crossing collision event. The measurements in all subdetectors per LHCb event amount to an expected average 100 kB, and an expected maximum of 150kB.

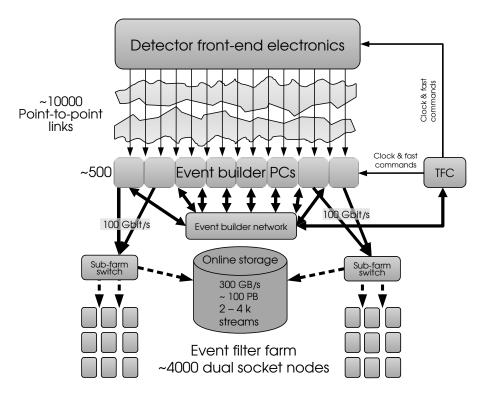

The data acquisition (DAQ) system [14, 15] is a real-time system<sup>3</sup> that distributes the event fragments received from the frontend electronics of the subdetectors composing LHCb, *builds* events by combining the event fragments into coherent selfcontained contiguous blocks of data, and distributes them to an *event filter farm* of commodity servers that filters data by reconstructing events and selecting specific events that are of interest to the current physics understanding.

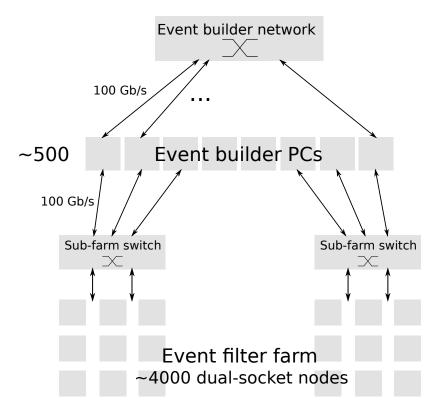

The data acquisition system of LHCb is composed of the readout system, the event builder and the event filter. Figure 1.12 presents an overview of the system, with an estimate of the servers, links and storage required for the upgrade. Data are read out from the detector front-end electronics into around 500 event builder PCs. Each of these PCs distribute the individual event fragments to a single destination at a time following a synchronized round robin scheme, through the event builder network. Data are finally transmitted for further processing to the event filter farm, which is expected to consist of up to 4000 commodity servers.

#### 1.2.1 Event readout

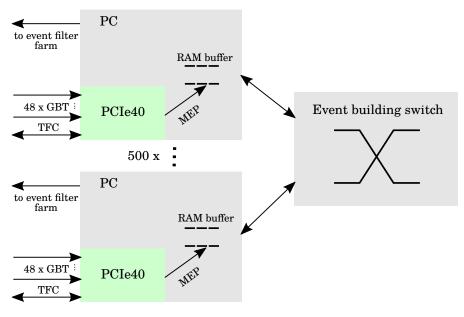

Data from the front-end electronics of the LHCb subdetectors are fed into the DAQ system in a distributed manner to around 500 data acquisition cards, known as *TELL40s*. Data are fed using 10000 simplex optical links, with a custom protocol *GBT* [16], certified to operate under radiation-hardened conditions. The front-end electronics, the TELL40s and the event builder network are synchronized with the LHC collision frequency through the timing and fast control system (*TFC*).

TELL40S are implemented as a PCI form-factor card known as the *PCIe40*, connected to PCI Gen-3 slots of event builder PCs. Each of the TELL40S receive data of a portion of the LHCb detector through a maximum of 48 GBT links adding up to a data rate of around 80 Gb/s. The TELL40S pack the data in multi-event packets (*MEPs*), and transmit the data to a pinned

<sup>3</sup> The term *real-time* is employed here to refer to a DAQ system which requires processing a design throughput. In contrast, *hard* real-time DAQ systems (such as the previous LHCb DAQ in Run 2) must also meet a tight latency requirement. The upgraded DAQ uses a distributed RAM buffer as a readout buffer, relaxing the latency requirement.

Figure 1.12: Overview of the LHCb upgrade data acquisition system.

data buffer of the event builder, ready for the event building stage.

#### 1.2.2 Event building

The process of event building consists in aggregating fragments originating from subdetector signals into one coherent event, which is needed to be able to analyze and filter the event in a posterior step. Multi-event packets originated in the readout stage flow from all *readout units* into a single *builder unit*. The receiving builder unit is chosen following a round-robin selection, thus load balancing the data transmissions and evening the throughput requirements across the builder units. This imposes an all-to-all data dependency between the readout units and the builder units. Once full events are built, they are further sent to the event filter farm for reconstruction and event selection.

Since the data flows in a single direction, it is possible to *fold* the system, by which each node behaves both as a readout and a builder unit, and the full-duplex capacity of each link is used. Figure 1.12 depicts this with a two-sided arrow between the event builder network and the event builder PCs, that act both

as readout and builder units. Figure 1.13 represents the data dependencies of an event builder node. Data are fed from the front-end electronics into the PCIe40 readout card inside event builder PCs. The TFC synchronizes and controls the behavior of said cards. MEPs produced by the TELL40 inside the PCIe40 are fed into a pinned memory location, ready to be sent to a receiving builder unit through the event builder network. Each PC acts both as a sender and a receiver in this scheme. Events are built inside each event builder node, and are finally sent out to the event filtering stage.

Each PC will sustain the population of the MEP buffer, sending and receiving data to the event builder network, operating on the data and sending the data out to the event filter farm. The expected data throughput required in memory for each builder node is around 500 Gb/s. Since there are no data reductions in intermediate steps, the bisection bandwidth of the system is a constant 40 Tb/s until the event filtering stage.

Figure 1.13: Data dependencies of a bidirectional event builder.

The isolated nature of the event building network permits using any high-performance network technology with no regard of interoperability with other networks. An event building simulation software across network technologies *DAQPIPE* [17, 18] has been developed and is currently being used to evaluate the network technology and specifics of the traffic scheduling.

In spite of the challenging nature of the presented setup, a full demonstrator was developed with early incarnations of 100 G technology as of 2014 [14]. More compact solutions may yield a better price performance ratio by condensing the functionality of two event builders in a single node. The choice of the event builder server directly impacts the usability of hardware accelerators (cref. section 10.3) in the event builder as a function of the available PCIe slots, slot width and bandwidth.

#### 1.2.3 Event filtering

Built events from the event builder stage will be sent to an event filter farm. The event filter farm is in charge of reconstructing the events and selecting the interesting ones. Event selection or *triggering* will be performed in two stages in software: The *High Level Trigger 1* (*HLT1*, cref. section 1.3) performs a selection based on PV displacement, momentum and optional muon identification. The available storage in each event filter node will be used as temporary storage for the output of HLT1. A second software trigger stage *High Level Trigger 2* (*HLT2*) will be processed parasitically during the execution of HLT1, and in the downtime periods of the detector (while it is not taking data), in a process often described as *deferred triggering*.

The reduction in data rate from the combined event selection of HLT1 and HLT2 is estimated to be of a factor 1 000. Interesting events are transformed into self-contained and compressed *event signatures*, and are sent to the Online storage and kept temporarily. Event signatures are further sent to the IT storage infrastructure and to the Grid in order to perform physics analyses. The infrastructure of the IT data center or the Grid will not be discussed as they are out of the scope of this thesis.

The event filter farm will be composed of up to 4000 servers with dual socket *x86-64* architecture-based processors. Only a subset of those servers will be newly acquired. Legacy servers based on the *Sandy Bridge* architecture onwards will also be supported by the Online system and the High Level Trigger software.

#### 1.3 THE HIGH LEVEL TRIGGER

LHCb software is written using the Gaudi framework [19], a framework for building High Energy Physics-oriented applica-

tions. The two applications that are related to this thesis are the online trigger application *Moore* and the offline trigger application *Brunel*. Gaudi abstracts the creation of software into algorithms, tools and component libraries. Gaudi applications are steered through Python processes that configure the application, including the sequence of algorithms to be run and any exposed options.

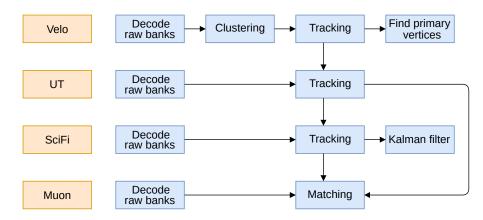

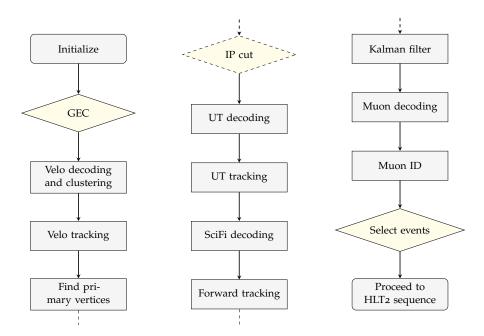

The sole trigger of the upgrade LHCb data acquisition system will be a software trigger known as the High Level Trigger subdivided in two stages, HLT1 and HLT2. HLT1 reconstructs the subdetectors involved in the tracking system and muon stations, whereas HLT2 is a more precise full-detector reconstruction and selection. A schematic of the main processes involved in HLT1 and their data dependencies are shown arrowed in Figure 1.14. The HLT1 must process the entire 30 MHz of events and perform a 30:1 data selection.

Figure 1.14: Main algorithms of High Level Trigger 1 sequence (HLT1).

An overview of the HLT1 processes is presented:

• Velo reconstruction – Raw Velo data are first decoded into 8-pixel containers known as *superpixels* (SPs). Only fired SPs are received as raw data. The problem of Velo clustering consists in transforming the input data into hits in the Velo subdetector, where each hit is represented with its  $\mathbb{R}^3$  coordinates and a unique identifier. The problem involves extracting information from sets of 8-connected pixels, a version of *connected component analysis*. Particle trajectories or *tracks* are then reconstructed from hits. The LHCb magnet does not influence the Velo subdetector, and therefore Velo tracks are straight lines. Velo tracks serve as seeds for the subsequent subdetectors reconstruction.

- Primary vertex finder The vertices where particles originate after the LHC beam collisions are known as *primary vertices*, as opposed to vertices from particles originating in decays. The primary vertex finder combines forward and backward tracks found in the Velo reconstruction, to reconstruct the primary vertices of individual collisions.

- UT reconstruction Raw UT data are decoded into UT hits. The UT reconstruction sorts the UT hits to facilitate finding compatible hits. Velo tracks are extrapolated into the UT planes, and a minimum of three hits in three different planes are required to form a UT track from a Velo track. UT tracks are fitted using a parabolic trajectory, incorporating a slight deviation introduced by the weak effect of the LHCb magnetic field in the UT.

- SciFi reconstruction Raw SciFi data are decoded into pre-sorted and pre-clustered SciFi hits. Only long tracks are reconstructed at the HLT1 stage, by extrapolating Velo and UT tracks into the SciFi stations. For UT tracks, the momentum measured in the UT subdetector is used to obtain a better estimate of the deviation of the particle through the magnetic field. The reconstruction of SciFi long tracks faces computationally expensive problems such as the estimation of particle trajectories through a magnetic field, detector inefficiencies and fake track reductions.

- Kalman filter The Kalman filter is a software estimator widely used in literature to estimate objects trajectories (see chapter 7). In HEP it is commonly used to estimate particle trajectories with a precise error covariance matrix that integrates both the mathematical model of trajectories and the uncertainty due to scattering. A simplified Kalman filter is applied to reconstructed tracks for an accurate estimation of their *impact parameter*, and to reduce fake tracks.

- Muon reconstruction After the decoding of muon stations raw data, the identification of muons can be performed following one of two strategies: Either taking the UT or long tracks as input.

- Data reduction algorithms and selections Configurable data reduction algorithms permit to filter out events according to factors like their detector occupancy or the impact parameter of tracks. Finally, selection algorithms

filter events that have been fully reconstructed, and decide whether to keep or discard them according to predefined criteria in accordance with the LHCb physics program.

## 1.3.1 The LHCb software upgrade

The present chapter conforms the design ambitions of the LHCb upgrade program, as described in the *Technical Design Report* [14].

The LHC detectors such as LHCb evolve during their lifetime. Hardware replacements may be performed during technical stops, improving the resolution and performance of the detector. The experience acquired in the first runs of the detectors revealed possible improvements, which may impact the physics goals of the experiment. The TDR describes the indended upgrades of the detector making educated guesses on the hardware available and the evolution observed in the last years.

In particular, the LHCb upgrade removes the *hardware level trigger* which was used in Runs 1 and 2 of the detector. The hardware level trigger did a 30:1 selection of the events according to partial subdetector information. In contrast, the upgrade software level trigger (HLT) performs a selection based on full detector tracking, which allows to more efficiently select interesting events. In combination with the increased luminosity, the projected data increase to be processed in software is estimated to be  $40 \times$ .

The required hardware and software improvements to cope with the increase in data rate were predicted in the TDR, with associated unknowns in terms of computing infrastructure and the performance of the software codebase on upcoming hardware. However, the code performance and compute resource cost were underpredicted. Progress was closely monitored as algorithms for the new detectors were being written, and in 2016 it was determined that there was a shortfall of between 6 to 10 × less performance than expected.

This figure was far beyond any of the built in contingencies in the budget. As a consequence, the software codebase was benchmarked and profiled, and new algorithms were developed where necessary. In addition, different computing models and alternative hardware architectures were explored to see if they could be exploited within the constraints of the planned system. The LHCb physics reconstruction became therefore a real-time software challenge, whereby the design performance of the system would have to be met within the hardware constraints.

# PARALLEL COMPUTING

RADITIONALLY, software has been written for serial computing [20]. Serial programs are broken down into a discrete list of instructions, and are run sequentially on a single processor. Determinism is preserved by guaranteeing the order of execution of instructions, strictly following the logic specified in the algorithms composing the program.

The performance of a serial program is determined by the time it takes to run, or runtime. The runtime of a program depends on factors related to how the program is written and on the processor it runs on. Comparisons between program runtimes are measured by comparing the slower program to the faster program as equation 2.1 shows. The metric name is *Speedup*, and is measured in a unitless manner in  $\times$  (*times*).

Speedup =

$$\frac{t_{slower}}{t_{faster}}$$

(2.1)

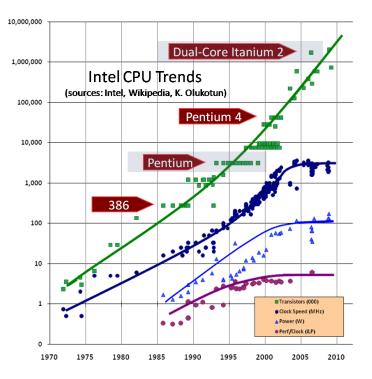

During the last decades, the number of transistors in integrated circuits has increased exponentially. This observation, known as *Moore's Law* [21], has held true since the early days of integrated circuits in the 6os. The scale of integration is classified into *small-scale*, *medium-scale*, *large-scale* and *very large-scale*, referring to the number of *logical gates* in an integrated circuit. Since the 8os, the term *very large-scale integration* (VLSI) has been coined and maintained to refer to any chip with more than 10 000 gates [22]. *Dennard's Scaling Law* [23] can be seen as a consequence of Moore's Law. It states that as transistors shrink in size, they become faster, consume less power and are cheaper to produce. Modern computer processors are chips that consist of billions of transistors.

Three areas that have lowered serial program execution runtimes due to higher transistor integration are clock frequency, execution optimization and cache. The clock frequency determines the time it takes the processor to complete an execution cycle. It holds a linear dependency with the runtime of the program. Execution optimization refers to a set of techniques to minimize the amount of cycles it takes to execute instructions, also known as *cycles per instruction* (CPI). Cache is an on-chip memory with fast access latency and throughput. Modern processors have a hierarchically structured cache into several levels of increasing speed and decreasing size.

Higher clock frequencies, better execution optimizations and bigger and faster caches led to a steady increase in serial programs performance for several decades. However, the trend stopped around 2004 due to heat and power consumption issues. Figure 2.1 shows the evolution of transistor integration, clock speed and power consumption. The red tendency line shows the performance as a function of clock speed flattening around 2004. H. Sutter qualified this phenomenon with the phrase *the free lunch is over* [24], noting that efficient programs would have to evolve and not rely on serial computing alone.

Figure 2.1: Evolution of transistor count, clock speed, power consumption and performance per clock speed. Image from [24].

Parallel computing consists in the simultaneous execution of sections of a problem. Parallel processors are composed of multiple cores. *Multi-core* processors are equipped with up to tens of cores, whereas processors with hundreds of cores or more are called *many-core* processors. Problems that have sections that can be parallelized, also called *parallelizable*, can be executed more efficiently on parallel processors.

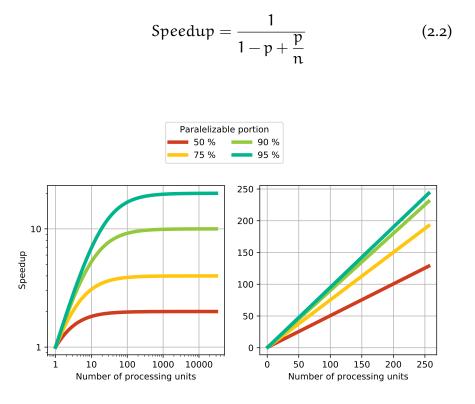

The runtime of a program executed in a parallel processor is measured as the elapsed real time or *wall time* of the program execution, irrespective of the number of computing resources employed to solve it. Amdahl's law [25] establishes a relation between the speedup attainable on a program of a fixed size, with a parallelizable fraction p and n processing units, shown in eq. 2.2. This relation is referred to as *strong scaling*. The number of resources employed affects the runtime of the program, and the parallelizable fraction plays a determining role in the scale of the speedup, as shown in Figure 2.2.

Figure 2.2: Amdahl's law (left) and Gustafson's law (right).

A different perspective can be obtained by fixing the execution time of a process. Gustafson's law [26] defines the theoretical speedup attainable on a program of a fixed execution time, with a parallelizable fraction p and using n processing units, shown in eq. 2.3. Gustafson argues that this relation, known as *weak scaling*, takes into account that as the computing resources increase, more aspects of a problem may be analyzed which would otherwise not be considered. The scaling of both laws is depicted in Figure 2.2. Amdahl's law is shown with a logarithmic scale (left), and Gustafson's law with a linear scale (right).

Speedup =

$$n + (1 - n) \cdot (1 - p)$$

(2.3)

During the last twenty years, processor manufacturers have transitioned to providing an increasing number of cores on processors. In order to make an efficient use of multi- and many-core processors, codebases likewise must transition to using programming models and algorithm designs that take into account the underlying parallel hardware.

### 2.1 TYPES OF PARALLEL PROCESSORS

Flynn's taxonomy [27] divides processors into four categories as a function of the number of concurrent instructions streams and the data instructions the processor operates on, as shown in table 2.1. SISD processors issue one instruction operating on one data at a time. Old desktop machines and mainframes fit in this category. In the MISD category, a processor issues multiple instructions operating on the same data at a time. This model is used in fault tolerant environments. SIMD processors issue a single instruction operating on several data at a time. The SIMD model is implemented in modern processor cores through vectorization or multiple threads (SIMT). Finally, MIMD processors operate on several data independently, issuing multiple instructions operating on multiple data concurrently.

|               | Single Instruction | Multiple Instruction |

|---------------|--------------------|----------------------|

| Single Data   | SISD               | MISD                 |

| Multiple Data | SIMD               | MIMD                 |

Table 2.1: Flynn's taxonomy.

Modern desktop and server processors are realizations of MIMD processors. Various degrees of parallelism [20] co-exist and must be considered in order to make an efficient use of parallel processors. Parallelism can be obtained at the level of *data, instructions, threads* and *processes*.

**Data parallelism** is realized in modern hardware through functional units dedicated to that end. The x86-64 architecture

is a family of 64-bit processors<sup>1</sup>. Multiple data execution is achieved in these processors through the use of wider registers and an extended *Instruction Set Architecture* (ISA). The sets of extensions in x86-64 processors are shown in table 2.2. These extensions are called *vector extensions* and refer to the processor capability to execute a number of instructions (*vector width*) onto its specialized functional units (*vector units*). The availability of an extension can be checked against the processor flags. Similar extensions exist on other hardware architectures, such as *Neon* in ARM processors or *Altivec* in Power processors.

| SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT | 128-bit |

|------------------------------------------------|---------|

| AVX, AVX2                                      | 256-bit |

| KNC, AVX512-family                             | 512-bit |

Table 2.2: Vector extensions and their corresponding register widths.

**Instruction-level parallelism** (ILP) refers to the number of instructions executed in parallel in a processor. Two metrics are associated with this type of parallelism. Sequential processors measure the number of cycles per instruction (CPI, lower is better), whereas for parallel processors instructions per cycle (IPC, higher is better) is used instead. Both metrics are equivalent. It is uncommon for a sequential processor to achieve a CPI smaller than one, and for a parallel processor to achieve an IPC smaller than one in a program is usually an indication the code is not properly optimized.

The following concepts are associated with ILP:

• *Pipelining* – Instruction execution on a processor is a task that can be divided in stages, which are performed by functional units or *ports*. This division permits to pipeline several instructions, such that a different stage is being performed on each instruction. Primitive processor designs divide instructions in *fetch* or *issue* (the next instruction to be executed is retrieved), *decode* (the instruction is identified and the operands are decoded), *execute* (arithmetic operations are carried out), *memory access* (read or store instructions are executed) and *write back* or *commit* (the operation is finally performed). An efficient processor design maximizes the potential parallel use of its ports, accounting for the latency of each stage.

<sup>1</sup> x86-64 has been implemented by various manufacturers, most commonly Intel and AMD.

Pipelining requires knowing or determining the order of execution of instructions in advance. *Jump* instructions break the linear execution order. *Branch prediction* units predict the result of jump conditions and keep a track of last results, improving processor utilization. Certain ISAs allow developers to impact the branch prediction unit by specifying the *likeliness* of a jump to be taken.

• *Multiple issue* – Superscalar processors allow to issue several instructions at a time. This design choice requires a duplication of ports across all stages, and verifying the instructions can be completed in parallel, checking no data dependencies exist. The verification may be done at runtime, in *dynamically scheduled* processors, or at scheduling time on processors that require *static scheduling*, such as VLIW processors.

The requirements to exploit ILP are hard to predict and processor dependent, and often the task to optimize ILP is left to hardware developers.

**Thread-level parallelism** (TLP) consists in specifying different units of work from a control perspective, to be executed independently in processor cores. In contrast with ILP, the control of the work assigned to each thread is left completely to the developer. It is worth distinguishing several types of TLP:

- *Fine-grained multithreading* The developer creates and joins *threads* explicitly, and assigns the work each thread will do. The underlying hardware executing the code can also be specified. This method grants a fine-grained control to the developer of the computing resources utilized and the memory assigned to each resource. In particular, it permits the developer to select processors in multi-socket systems, and cores in processors with simultaneous multi-threads<sup>2</sup>, which impact the performance of applications.

- *Task-based multithreading* The work is divided into tasks, which are then automatically mapped to processor cores. The developer has no control of the assignment of the task to a specific thread. *Dependency graphs* permit to specify a list of data and control dependencies between tasks,

<sup>2</sup> Simultaneous Multi-Threading (SMT) or Hyperthreading is a hardware technology of some processors that exposes multiple logical cores for each physical hardware core. This technology allows processors to prevent stalls by executing multiple threads with the ports of a single core.

such that tasks will be executed as their dependencies are fulfilled.

Finally, **process-level parallelism** (PLP) refers to expressing the work into several independent processes, which are scheduled and managed by the operating system. A process can be assigned a precedence, increasing (decreasing) the probability it will be scheduled. Processes are a coarser-grained level of parallelism, which may be assigned to a specific core or processor. PLP can also be implemented across multiple computing nodes, and message passing libraries such as MPI facilitate the instantiation and communication between processes.

The operating system can interact with processes through signals. When a signal is caught in a process, the execution context is saved and the context is shifted to a function handling the process signal. Once the signal has been handled, and if the process did not terminate, the control is returned to the previously executing context, and computation is resumed.

The four levels of parallelism discussed offer orthogonal considerations when developing a parallel program. A more indepth discussion can be found in [20].

#### 2.2 MEMORY

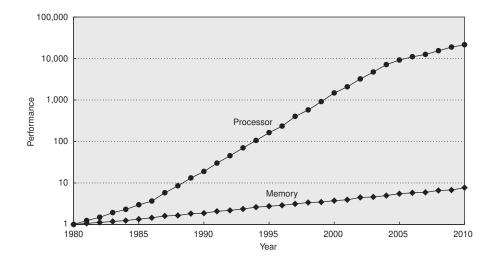

During the last decades, memory performance has not progressed at the same pace of that of processors. Figure 2.3 depicts this effect, normalized to the performance of processors and memory to 1980, where the performance axis is in logarithmic scale. The performance increase of processors until 2005 was of  $1.25 \times$  per year, whereas from there after it is  $1.20 \times$ . In contrast, memory has steadily increased its performance at a rate of  $1.07 \times$ per year.

The gap in performance between memory and processors has widened over the years, and therefore memory access-related issues are increasingly important to produce efficient programs.

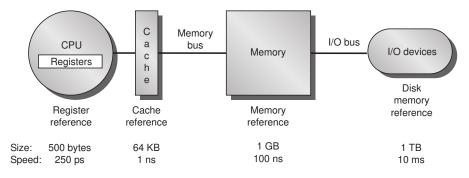

Computer memory is organized in a hierarchical manner, where memory capacity and latency are directly correlated. Processors use low-latency registers to store operands of instructions, with a varying amount of registers available by processor model. On-chip cache memory is organized in layers, identified by its level, commonly L1, L2 and L3. Dynamic random access

Figure 2.3: Memory performance versus processor performance in the last decades. Image from [28].

memory (DRAM) can hold entire applications, and finally I/O devices are used as a persistent storage system. Common sizes and speeds of all these memories are shown in Figure 2.4.

Figure 2.4: Memory hierarchy. Image from [28].

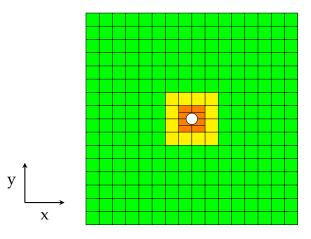

The difference in latency for accessing the next levels in the hierarchy are several orders of magnitude, and it is desirable to trigger memory accesses only when it is necessary. The principle of *locality* is an empirical result that states that when a memory location is accessed (1) it is probable that it will be accessed again shortly, an effect also known as *temporal locality*, and (2) it is probable that increasing memory locations in the immediate vicinity are also accessed, also known as *spatial locality*. The effects of locality are exploited in cache memories. When memory is read, a contiguous chunk of memory of a predetermined size is retrieved, referred to as *cache line*. Memory is kept in cache, and the upper levels of cache and memory are updated only when necessary, according to the cache write policy.

Since cache memories cannot store a complete map of the application's memory, the position of a memory location is transformed to a position in cache. The destination location is determined by shifting the memory location as many bits as required by the cache line size and retrieving the least significant bits. The resulting location may collide with pre-existing data in cache, which requires removing the pre-existing data from cache and updating the upper memory level according to the writepolicy. A number of collisions can be sustained by configuring the cache memory with an *n-way associativity*, which results in a trade-off between memory space and resiliency for memory location collisions.

An indicator of how efficient cache memories are being utilized is the cache *hit* and *miss* rates of a program. The expected hit and miss rates depends theoretically on the program under analysis. Both instruction and data caches exist, although the former is usually ignored as a program's code undergoes many difficult to predict transformations prior to resulting in the list of instructions visible by the processor.

Memory architectures influence memory access times. *Uniform memory access* (UMA) systems guarantees an equal access time to a shared memory across all processing units. In *non uniform memory access* (NUMA) systems, the time to access memory depends on where the memory resides. NUMA systems may be non-uniform at different levels, such as cache or main memory. In some cases control is given to the developer to manage and pin memory for processes in order to avoid inter-domain memory accesses.

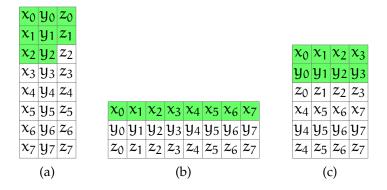

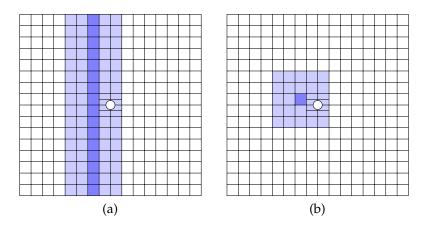

Memory structures play a role in the efficiency of memory operations. In an *array of structures* (AOS), each structure stores its members contiguously. Further elements in the array are stored in this manner, and each structure in the array is stored next to each other. In contrast, an *structure of arrays* (SOA) stores same structure elements in the array contiguously. *Array of structure of arrays* (AOSOA) is a mix between the two previous structures, where a stride size *s* is chosen. Array elements are then stored in SOA in groups of *s* elements, resulting in an array of contiguous SOA structures.

Figure 2.5 shows an AOS, SOA and AOSOA of stride 4, for the structure  $\{x, y, z\}$ . A sequential code would benefit from the AOS datatype, as accesses to one parameter are likely to be followed by accesses to the other parameters by the spatial locality principle. Data-parallel architectures would benefit from SOA – if the vector unit performs the same operation across datatypes, it will fetch all values with one cache line data access. AOSOA datatypes are used in conjunction with a particular vector width, to further optimize the data access pattern by aligning the data boundaries with the vector width. The fetched data with a single access to  $x_0$  is shown in green for all configurations in the figure, assuming the structure elements are double precision floating point numbers, and a cache line size of 64 bytes. If executing on a vector width of 4, (c) is likely the most advantageous, since the x and y values will be populated in cache.

Figure 2.5: From left to right: AOS, SOA and AOSOA of stride 4 for structure  $\{x, y, z\}$ . In green, cache line access triggered by access to  $x_0$ , assuming x, y and z are double precision floating point numbers, and a cache line size of 64 bytes.

When data is not contiguous and requires accesses to multiple memory locations, the terms *gather* and *scatter* are used. Gather and scatter operations are often necessary in data parallel workloads, but an abuse of these operations may lead to an inefficient program. Memory alignment also affects data parallel architectures, which distinguish *aligned data accesses* from *misaligned data accesses*, with different operation microcodes for each. Aligned data accesses are preferred and lead to faster code, where possible.

## 2.2.1 The Roofline model

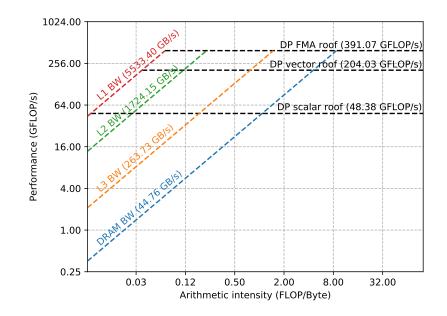

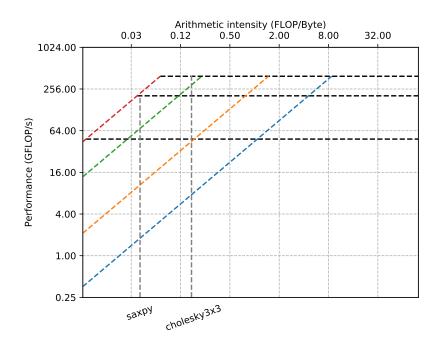

The *arithmetic intensity* of a program is its number of floating point operations divided by its number of bytes loaded and stored into memory, and is measured in  $\frac{FLOP}{B}$ . It is possible

to characterize the performance attainable on a processor, in terms of FLOP/s, as a function of the arithmetic intensity. Conceptually, if the arithmetic intensity of a program is below a threshold defined by the peak processor performance and the fastest memory where the data is expected to reside, then the performance of the program is bound by memory bandwidth rather than by the peak processor performance. Given the gap between memory and processor performance increase in the last decades, it is likely that more and more programs become memory bound.

The *Roofline model* [29] is a visual performance model that characterizes in a condensed manner the peak performance attainable by a processor under various conditions, and the empirical performance obtained by one or several programs. Figure 2.6 shows the Roofline model of processor Intel Xeon Haswell E5-2683. The model is composed of various *roofs*, that depict the peak performance with respect to processor technologies (compute bound), and the peak performance when a program is subject to a particular memory bandwidth (memory bound). Three roofs related to the Haswell processor are shown. A program consisting solely of double precision (DP) floating point *scalar* arithmetic would have a theoretical peak performance of 48.38 GFLOP/s. If the program is vectorized, the theoretical peak performance would be 204.04 GFLOP/s. If the program uses *fused multiply-add* (FMA) instructions, the theoretical peak performance would be 391.07 GFLOP/s.

On the other hand, four roofs are defined that are dependent on memory and cache bandwidth. If the program solely relies on accesses to main memory (DRAM), which has a bandwidth of 44.76 GB/s, then the peak performance is capped by the relation between arithmetic intensity and bandwidth. Similarly, the relation between peak performance and arithmetic intensity of the program if all memory accesses occur in any of the cache levels are also depicted.

For instance, let us consider the pseudo-code for two different programs, shown in listing 2.1. The first is *saxpy*, a well known benchmarking program. Let us assume x and a to be input variables, y to be an input and output variable, and both x and y to have six elements. The second example is the Cholesky decomposition for  $3 \times 3$  matrices. Let us assume that C is an input array of six elements, and L is an output array of six elements. All variables and operations shown are using double precision,

Figure 2.6: Roofline model characterizing processor Intel Xeon Haswell E5-2683.

and FMA units are used, whereby multiplications followed by additions or substractions count as a single operation. Table 2.3 characterizes both sample programs.

| Program     | Loads (B) | Stores (B) | FLOP | Arithmetic intensity (FLOP/B) |

|-------------|-----------|------------|------|-------------------------------|

| saxpy       | 13 · 8    | 6 · 8      | 6    | 0.04                          |

| cholesky3x3 | 6 · 8     | 6 · 8      | 16   | 0.17                          |

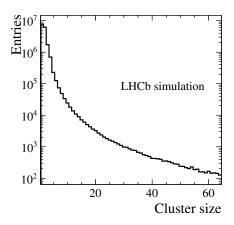

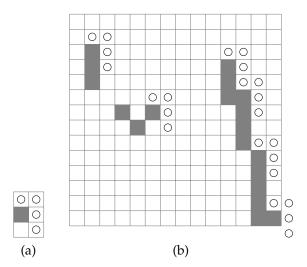

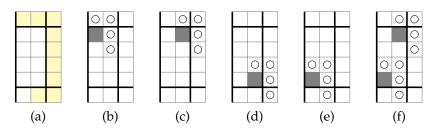

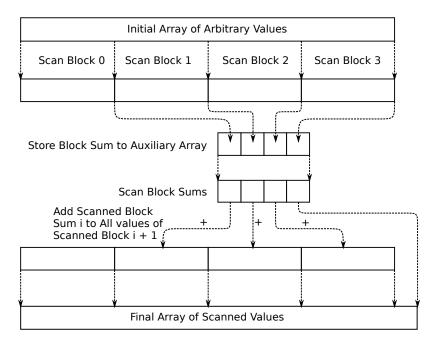

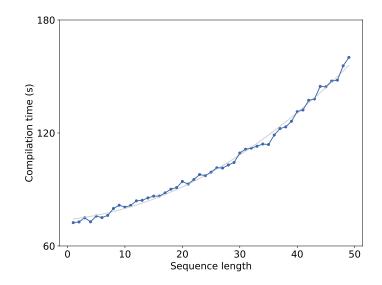

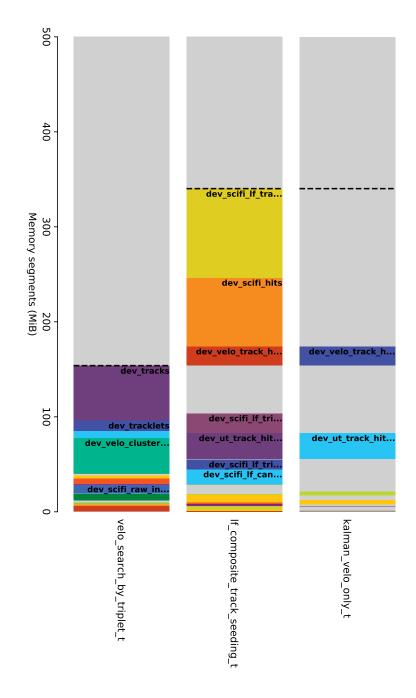

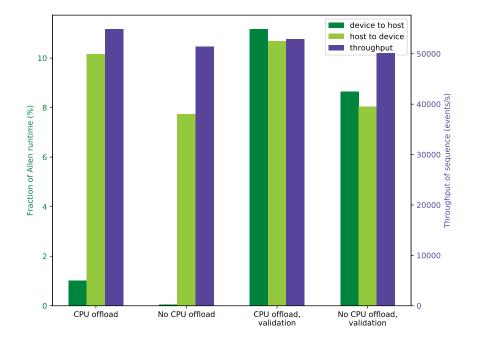

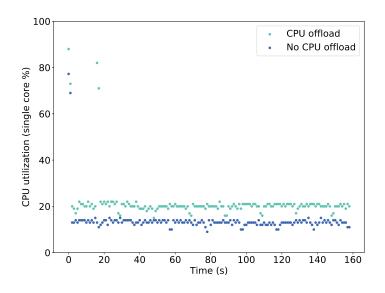

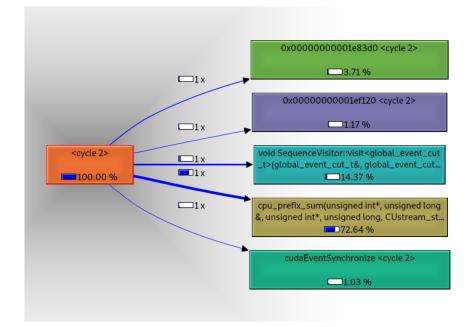

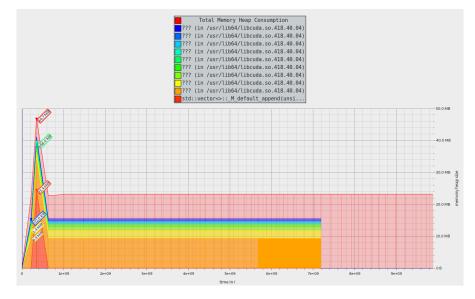

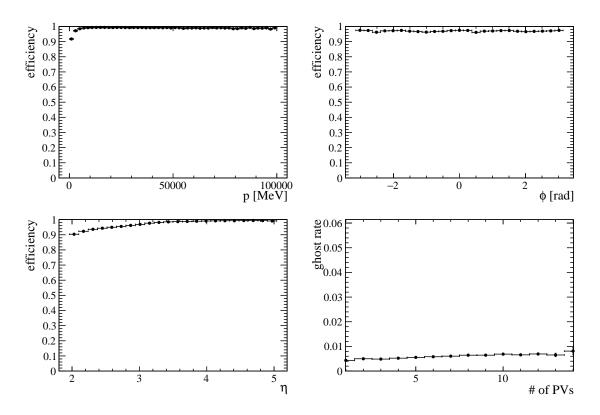

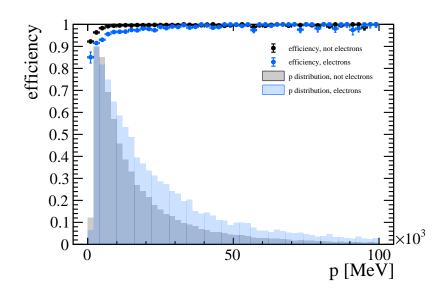

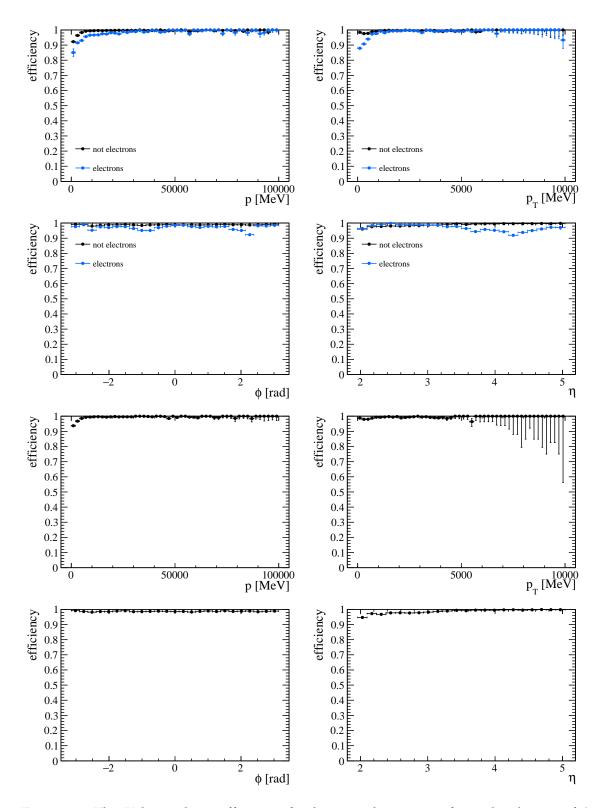

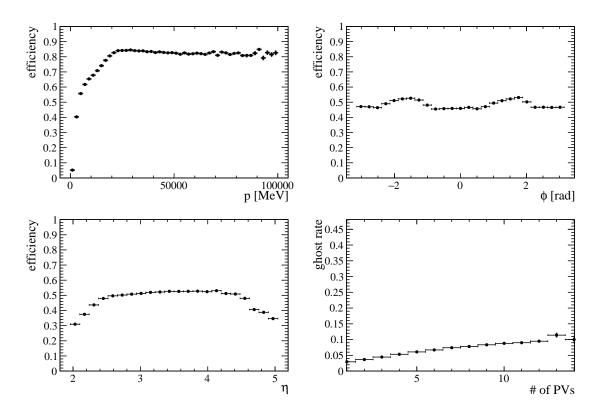

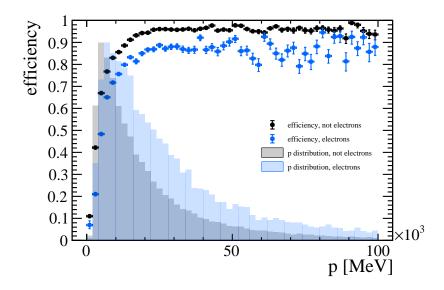

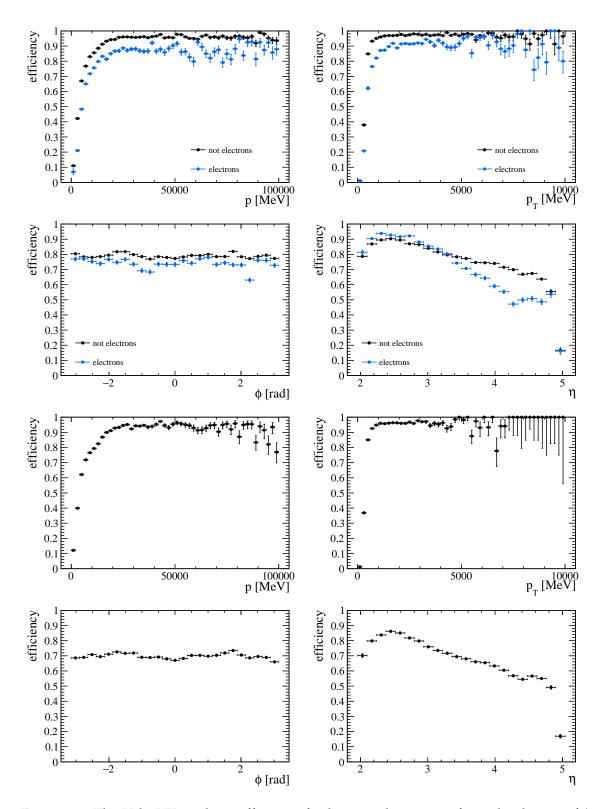

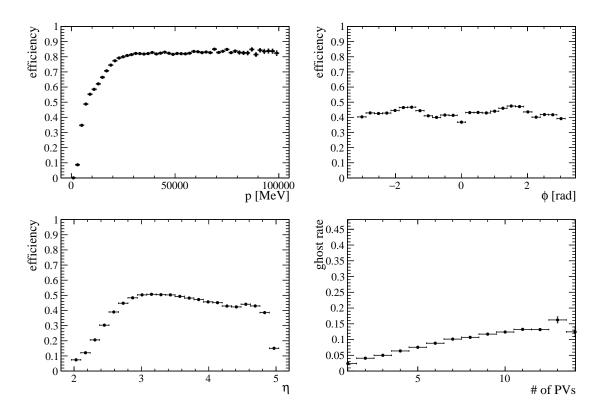

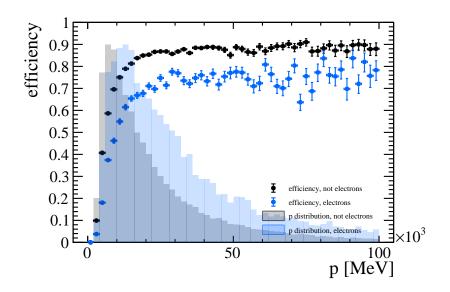

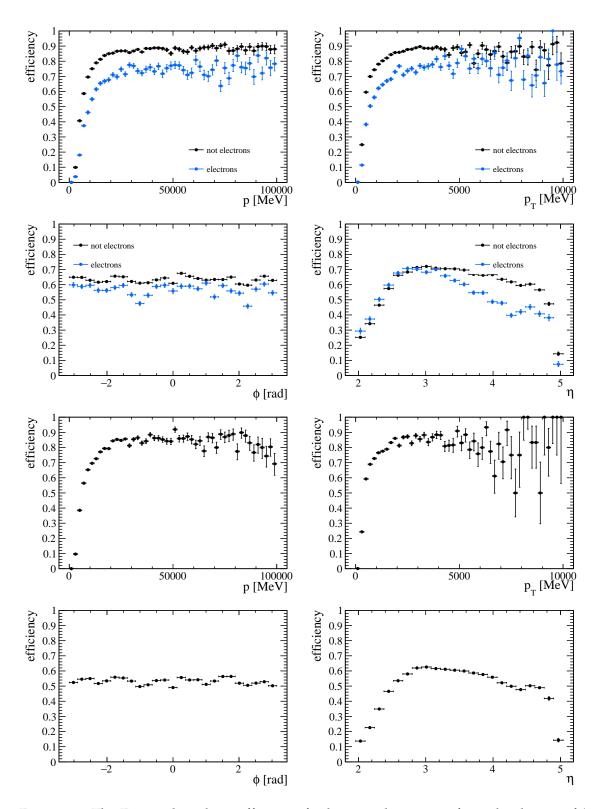

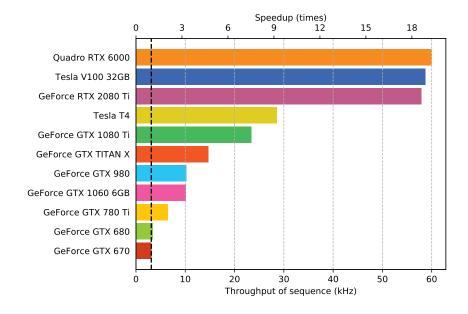

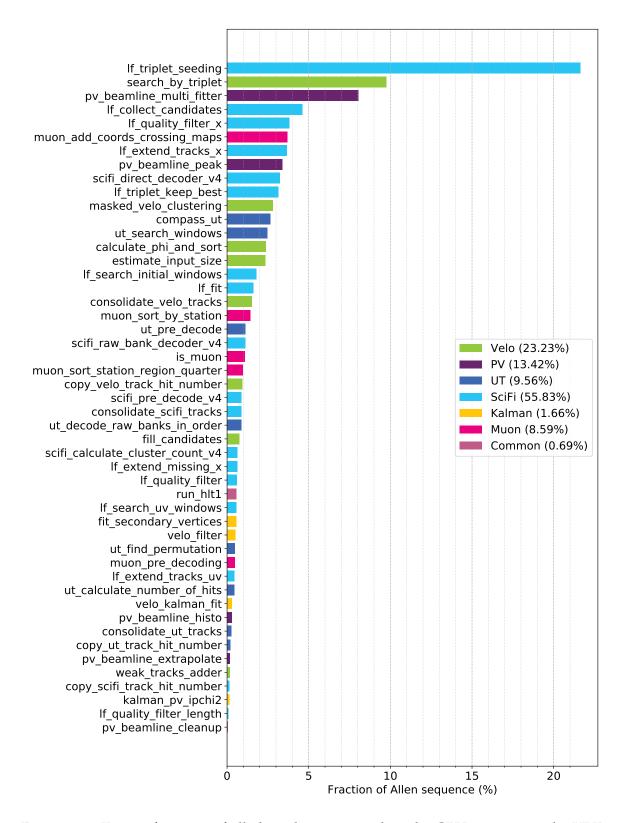

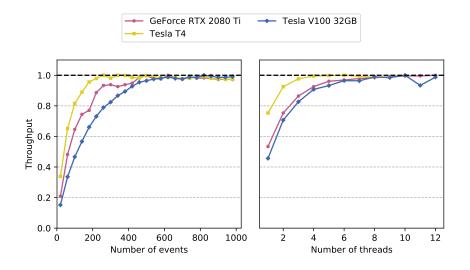

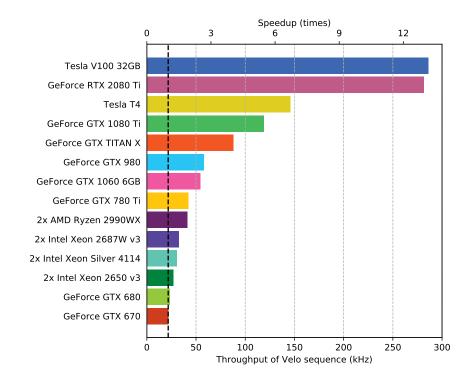

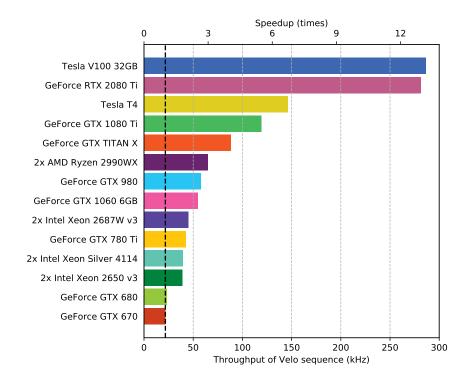

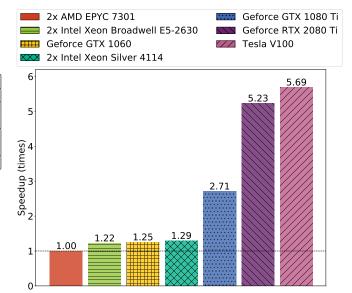

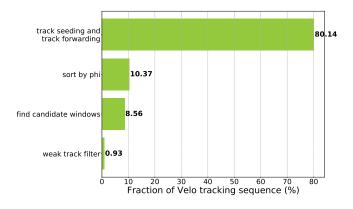

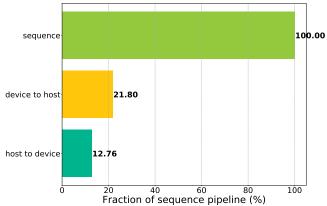

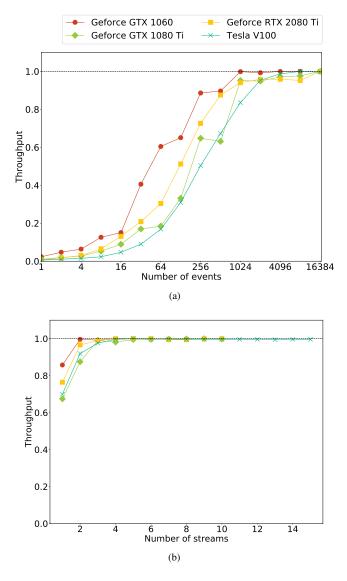

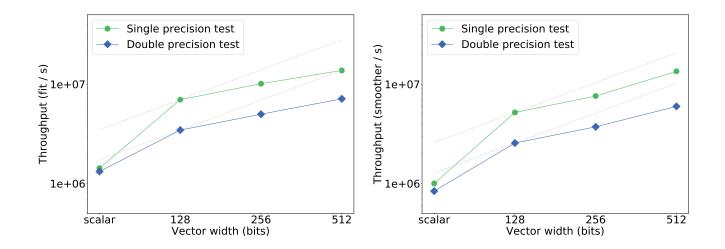

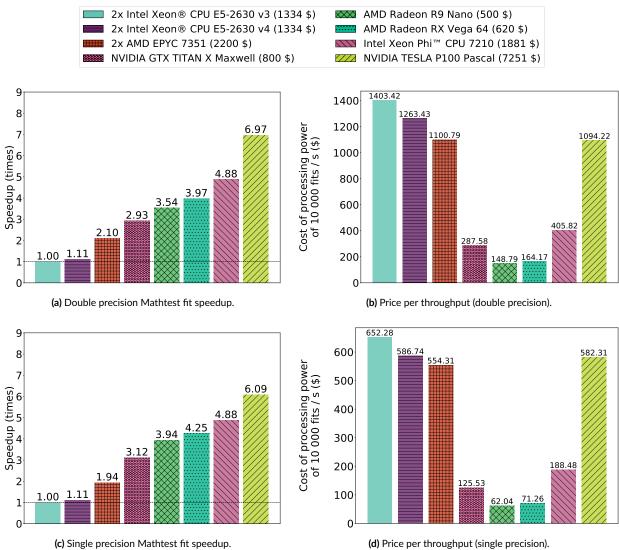

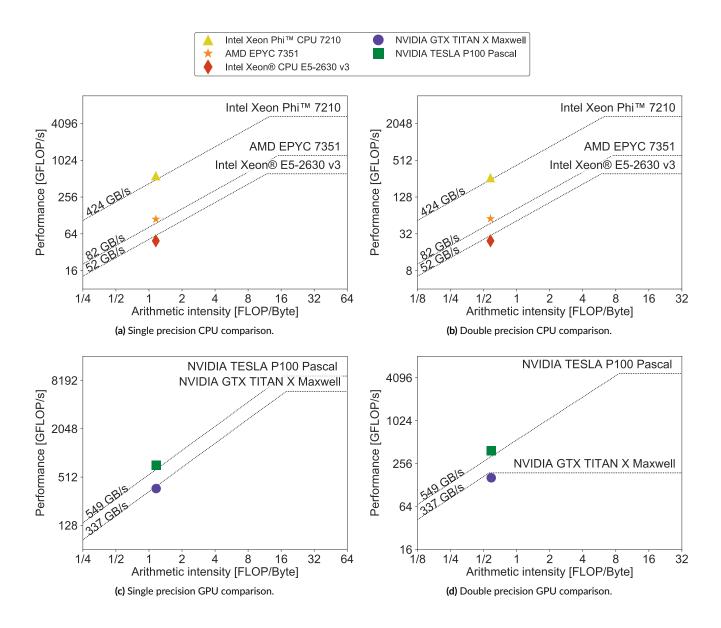

Table 2.3: Arithmetic intensity of sample programs.