# A Chaotic Switched-Capacitor Circuit for Characteristic CMOS Noise Distributions Generation

Norberto Pérez-Prieto, Manuel Delgado-Restituto, Ángel Rodríguez-Vázquez Instituto de Microelectrónica de Sevilla (IMSE-CNM), CSIC-Universidad de Sevilla (Spain) Email: norberto@imse-cnm.csic.es

Abstract—A switched-capacitor circuit is proposed for the generation of noise resembling the typical noise spectral density of MOS devices. The circuit is based on the combination of two chaotic maps, one generating 1/f noise (*hopping* map) and the other generating white noise (*Bernoulli* map). Through a programmable weighted adder stage, the contribution of each map can be controlled and, thereby, the position of the corner frequency. Behavioral models simulations were carried out to prove the correct functionality of the proposed approach.

#### I. INTRODUCTION

Noise signals are required for instrumentation, signal processing, cryptography and communications, among other application areas [1][2][3]. For instance, noise signals are used in instrumentation for testing the dynamic behavior of electronic systems [4]. Noise signals are also used for dithering analogto-digital converters, thus spreading quantization errors and other spurious behaviors over the spectrum [5]. In many of these areas, embedding and compactness requirements call for simpler possible realizations. Actually, embedded noise generators are required for the implementation of Built-In Self-Test (BIST) techniques [6].

In the quest of compact noise source implementations, the use of chaotic discrete maps is a very convenient choice for three reasons: i) discrete maps are dynamical systems, represented by deterministic models in finite differences, which are able to generate random behaviors. Their extremely large sensitivity to the initial conditions makes them highly unpredictable [7]; ii) they are readily realized by using stateof-the-art switched-capacitor circuit techniques and have been profusely demonstrated through monolithic implementations [8]; iii) they intrinsically provide rail-to-rail analog noise signals without further amplification needed.

Two discrete maps of special relevance for noise generation are the Bernoulli map (white noise generator) and the hopping map (1/f) noise generator). As will be shown in this paper, their outputs can be linearly combined to obtain a typical CMOS noise distribution which fits to a 1/f distribution up to a corner frequency (*fc*) where white noise becomes dominant. The position of this corner frequency can be adjusted by weighting the contribution of each noise source.

This paper details the design of a switched-cpacitor circuit for the generation of MOS-like noise distributions and is

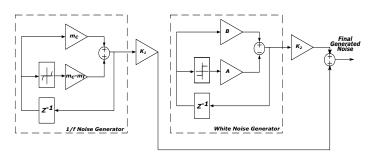

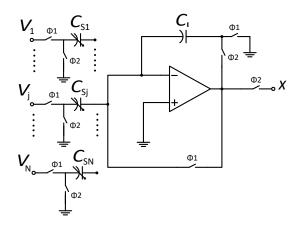

Fig. 1. Block Diagram of proposed system for generating CMOS noise distributions.

organized as follows. Section II describes the discrete maps mentioned above and introduces their circuital implementation. Simulation results with Matlab<sup>®</sup> Simulink<sup>®</sup> and Verilog-A models in Cadence<sup>®</sup> Virtuoso<sup>®</sup> are shown in Section III. Section IV introduces the programmability of the map. Finally, the conclusions are drawn in Section IV.

## II. DISCRETE MAPS FOR GENERATING NOISE DISTRIBUTIONS

Every mathematical model for chaos generation has two components: dynamics and nonlinearity. In the case of chaotic discrete maps, the dynamics is implemented through delays and the nonlinearity is typically carried out with dynamic comparators. The proposed noise generator is based on the combination of two discrete maps, the hopping map and the Bernoulli map, as shown in Fig. 1. The electronic implementations of the dynamics and nonlinearity for both maps are described next.

#### A. The Bernoulli Map

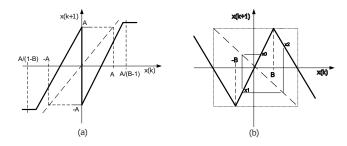

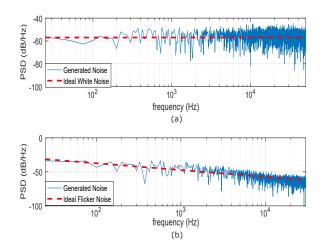

Fig. 2 (a) displays a representation of the Bernoulli map, which is described by the recursive equation

$$x(k+1) = B \cdot x(k) - A \cdot sgn(x(k)) \tag{1}$$

where parameter A sets the definition interval, parameter B defines the slopes of the return map at both sides of the transition and function sgn(x(k)) determines the sign of x at instant k.

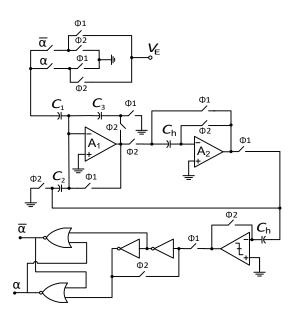

For its electronic implementation (see Fig. 3), the slope *B* is set by the capacitor ratio  $C_2/C_3$  and parameter *A* is defined

Fig. 2. (a) The Bernoulli map implementation without parasitic stable points. (b) The hopping map with transition point examples and margins to not lock in parasitic stable points.

by the dc voltage  $V_E$  scaled by  $C_1/C_3$  [8]. Both ratios are implemented through a weighted adder built around Op-amp  $A_1$ . This adder also adds half delay in the circuit dynamics and amplifier Op-amp  $A_2$  adds the other necessary half delay for implementing (1). Regarding the nonlinearity, it is achieved via a phase-reverse switch arrangement controlled by a dynamic comparator. Thus, digital signal  $\alpha$  determines if parameter A is added or subtracted in the return map.

Care must be taken in guaranteeing the return map does not get locked in parasitic states due to the saturation of Op-amps. To avoid this situation, the dc voltage  $V_E$  has to be chosen so that

$$A < V_{sat+} < A/(B-1) A/(1-B) < V_{sat-} < -A$$

(2)

where  $V_{sat+}$ ,  $V_{sat-}$  denote the positive and negative saturation levels of the Op-amps.

## B. The Hopping Map

The 1/f noise is an ubiquitous noise contribution in MOS technologies which is dominant at low frequencies. The hopping map [7], also known as *zigzag* map [9], has been demonstrated to generate controllable *colored* noise. This map is described as

$$x(k+1) = \begin{cases} m_l \cdot x(k) + K & B < x(k) < m_c \cdot B \\ m_c \cdot x(k) & -B < x(k) < B \\ m_l \cdot x(k) - K & -m_c \cdot B < x(k) < -B \end{cases}$$

(3)

where  $K = (m_c - m_l)B$ ,  $m_c$  being the positive slope,  $m_l$  the negative slope and B the point where the slope change, as it can be seen in Fig. 2 (b).

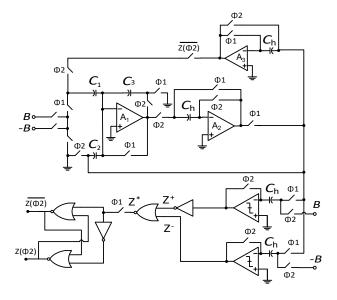

The electronic implementation of this map (see Fig. 4) is similar to the *Bernoulli* although in this case three different states must be defined. The dynamic and the nonlinearity are implemented in the same way: dynamic is achieved by using two Op-amps  $(A_1, A_2)$  to introduce a delay cycle (half cycle each one) and the nonlinearity is realized via a phase-reverse switch arrangement controlled by two dynamic comparators which determine the region of the map where x(k) is situated, i.e,  $Z^+ = Z^- = 0$ ,  $Z^* = 1$  for the central piece,  $Z^+ = Z^* =$  $0, Z^- = 1$  for the left one and  $Z^* = Z^- = 0$ ,  $Z^+ = 1$  for the right one. The Op-amp  $A_3$  introduces a half cycle delay for reaching values of x(k) situated in one of the negative slopes

Fig. 3. SC schematics for the Bernoulli map.

Fig. 4. SC schematics for the hopping map.

of the map, while the Op-amp  $A_1$  and its related capacitor acts as a weighted adder which controls the slopes of the map

$$m_c = \frac{C_2}{C_3} \qquad m_l = \frac{C_2 - C_1}{C_3}$$

(4)

To not get locked at parasitic stable points due to Op-amps saturation voltages, the length of the margins of the map in Fig. 2 (b) must be  $2 \cdot m_c \cdot B$  for being inside the Op-amps saturation levels.

### III. PROGRAMMABILITY OF THE CIRCUIT

The herein proposed architecture generates typical MOS noise distributions by combining the two discrete maps above. This combination is achieved, by a programmable weighted adder (see Fig. 5) with the variable capacitors being realized by

Fig. 5. Weighted adder with programmable gain.

programmable capacitor banks. Similar adders were also used in the implementation of the discrete maps (Op-amps  $A_1$  and related capacitors for both maps). By applying the charge conservation principle, the operation of the weighted adder is defined by

$$\begin{aligned} x(k+1) &= \sum_{j=1}^{N} \frac{C_{Sj}}{C_I} \cdot v_j(k+1/2) \\ x(k+1/2) &= 0 \end{aligned} \tag{5}$$

Based on this, two different programmability levels can be defined in the proposed circuit. First, the weighted adders in the individual discrete maps make their respective slopes tunable, what translates into significant differences in the generated noise distributions such as, for instance, the power exponent of the flicker distribution. Second, the weighted adder which combines both discrete maps adds to the circuit the possibility of changing the gain of each distribution, varying the total integrated noise and the corner frequency of the final distribution.

The proposed noise generation method also offers a low complexity alternative for the synthesis of flicker noise in mathematical packages, such as Matlab<sup>®</sup> Simulink<sup>®</sup>. Default functions in these tools (as DSP.Colorednoise in Matlab<sup>®</sup> [10]) rely on shaping white noise distributions with high-order autoregressive filters, which requires far more computations than by adding the contributions of two simple discrete maps. Hence, this method allows the designer to use the same approach to generate noise from the first mathematical approach to the final IC.

### **IV. SIMULATION RESULTS**

The power spectral density of each map has been obtained in order to prove the correct generation of an uniform distribution, for white noise, and a 1/f distribution, for flicker noise. Furthermore, ideal distributions for both signals (uniform and 1/f) have been generated using Matlab<sup>®</sup> Simulink<sup>®</sup>. Fig. 6 (a) shows a comparison between the ideal uniform distribution and that obtained with the Bernoulli map. It can be observed that the generated noise distribution featured by the map is very similar to the ideal one. In the case of the 1/f noise, the comparison is shown in Fig 6 (b). To better appreciate

Fig. 6. PSD comparison between generated noise from simulation and ideal noise distribution (a) the Bernoulli map. (b) the hopping map.

how the noise generated by the circuit fits to the ideal one, they have been integrated in a frequency band from 25 Hz to 100 kHz. For white noise it is obtained 0.090  $V_{rms}$  for the generated distribution and 0.078  $V_{rms}$  for the ideal one, and for 1/f noise it is obtained 0.101  $V_{rms}$  for the generated and 0.091  $V_{rms}$  for the ideal one. Thus, both distributions could be considered valid approximations of the ideal distributions.

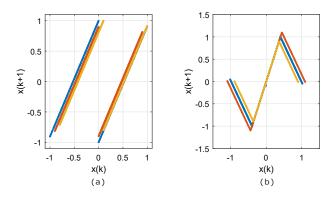

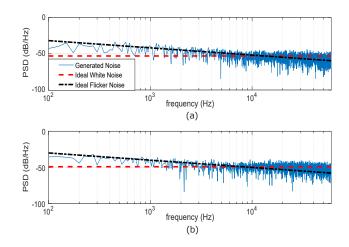

In order to check the performance of the proposed circuit, various simulations were carried on Cadence<sup>®</sup> Virtuoso<sup>®</sup> with behavioral models -using Verilog-A descriptions for the amplifiers- of the circuit components. The robustness of the circuit has been assessed by taking into account capacitor mismatches and reference voltage variations. The most dramatic impact of these non-idealities would be the onset of parasitic stable states, where trajectories may get locked. This potential problem has been tackled by employing structural stability techniques reported in [8] and [11]. Additionally, MonteCarlo simulations have been carried out for addressing the impact of capacitor mismatches, assuming 10% variations of the reference voltages as well. These simulations do not reveal significant changes on the statistical properties of the circuit and, indeed, the return maps of the noise generators are only slightly modified, as shown in Fig. 7. In these plots, the capacitors of both circuits have been nominally set to achieve:  $B = 1.9; A = 1; f_{clk} = 200 kHz$  for the Bernoulli map and  $m_c = 2.5; m_l = -1.7; B = 0.4; f_{clk} = 200 kHz$ for the hopping map. Furthermore, various noise distributions generated by the complete circuit with different corner frequencies  $(f_c)$  have been generated and their corresponding integrated noise (intnoise) from 100 Hz to 30 kHz have been calculated (see Fig. 8). As shown in the caption of this figure (ony two configurations are shown for simplicity), there are no significant deviations in the position of the corner frequency or the integrated noise.

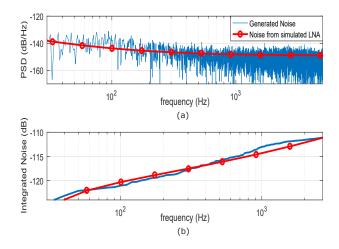

Finally, a comparison has been made between the proposed circuit and noise results from simulations of a LNA for neural recording applications (Fig. 9) in CMOS  $0.18\mu m$  technology,

Fig. 7. Simulation results of implementing maps with capacitor mismatch and variations of the voltage references (a) the Bernoulli map. (b) the hopping map.

previously presented in [12]. Fig. 9 (a) shows that the corner frequency is practically the same for both distributions (around 500 Hz). However, in order to prove the validity of these results, both distributions have been integrated in band from 10 Hz to 5 kHz. The results of this integration show a difference of 0.09  $\mu V_{rms}$  between the integrated noise from LNA (2.82  $\mu V_{rms}$ ) and the integration of the generated noise by the circuit (2.91  $\mu V_{rms}$ ), thus verifying the correct performance of the proposed circuit.

## V. CONCLUSION

An architecture is reported for the generation of typical MOS spectral noise distributions using discrete maps and switchedcapacitor circuits. The distribution can be shaped by properly changing circuit design parameters through capacitor ratios. Such kind of noise source is of interest for applications whose noise sensibility is one the most crucial parameters for the correct performance of the circuit, such as biomedical and another sensing applications.

### ACKNOWLEDGMENT

This work is supported by the Spanish Ministry of Economy & Competitiveness under grant TEC2016-80923-P.

#### REFERENCES

- [1] S. Wiggins, Introduction to applied nonlinear dynamical systems and chaos. Berlin: Springer-Verlag, 1990.

- [2] H. Nejati, T. Ragheb, A. Hosseini, and Y. Massoud, "A programmable input-pulse dependent chaotic oscillator," in 2007 50th Midwest Symposium on Circuits and Systems, Aug 2007, pp. 173–176.

- [3] G. Evans, J. Goes, and N. Paulino, "On-chip built-in self-test of videorate adcs using a 1.5 v cmos gaussian noise generator," in 2005 IEEE Conference on Electron Devices and Solid-State Circuits, Dec 2005, pp. 669–672.

- [4] T. Roinila, M. Vilkko, and T. Suntio, "Fast loop gain measurement of a switched-mode converter using a binary signal with a specified fourier amplitude spectrum," *IEEE Transactions on Power Electronics*, vol. 24, no. 12, pp. 2746–2755, Dec 2009.

- [5] H. Hsieh and C. L. Lin, "Spectral shaping of dithered quantization errors in sigma ndash; delta modulators," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 5, pp. 974–980, May 2007.

- [6] G. Evans, "Adc built-in-self-test based on a pseudorandom uniform noise generator," in *Design of Circuits and Integrated Systems*, Nov 2014, pp. 1–5.

Fig. 8. Different PSDs generated by the SC circuit (a) PSD for  $fc \simeq 11 \pm 0.3kHz$  and  $int_{noise}(100Hz - 30kHz) \simeq 0.201 \pm 0.02V_{rms}$ . (b) PSD for  $fc \simeq 7.5 \pm 0.25kHz$  and  $int_{noise}(100Hz - 30kHz) \simeq 0.144 \pm 0.015V_{rms}$ .

Fig. 9. Comparison between generated noise by discrete maps and simulated results from a LNA in CMOS  $0.18 \mu m$  (a) PSD comparison. (b) Integrated noise comparison.

- [7] M. Delgado-Restituto, A. Rodriguez-Vazquez, S. Espejo, and J. L. Huertas, "A chaotic switched-capacitor circuit for 1/f noise generation," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 39, no. 4, pp. 325–328, Apr 1992.

- [8] M. Delgado-Restituto and A. Rodriguez-Vazquez, "Integrated chaos generators," *Proceedings of the IEEE*, vol. 90, no. 5, pp. 747–767, May 2002.

- [9] A. Beirami, H. Nejati, and W. H. Ali, "Zigzag map: a variability-aware discrete-time chaotic-map truly random number generator," *Electronics Letters*, vol. 48, no. 24, pp. 1537–1538, 2012.

- [10] N. J. Kasdin, "Discrete simulation of colored noise and stochastic processes and 1/f alpha; power law noise generation," *Proceedings of the IEEE*, vol. 83, no. 5, pp. 802–827, May 1995.

- [11] J. L. Valtierra, E. Tlelo-Cuautle, and Á. Rodríguez-Vázquez, "A switched-capacitor skew-tent map implementation for random number generation," *International Journal of Circuit Theory and Applications*, vol. 45, no. 2, pp. 305–315, 2017.

- [12] J. L. Valtierra, A. Rodriguez-Vazquez, and M. Delgado-Restituto, "A 4-mode reconfigurable low noise amplifier for implantable neural recording channels," in 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), June 2016, pp. 1–4.