# Continuous-Time Cascaded $\Sigma\Delta$ Modulators for VDSL: A Comparative Study

Ramón Tortosa, José M. de la Rosa\*, Angel Rodríguez-Vázquez and Francisco V. Fernández

Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC) Edificio CICA-CNM, Avda Reina Mercedes s/n, 41012-Sevilla, SPAIN

# ABSTRACT

This paper describes new cascaded continuous-time  $\Sigma\Delta$  modulators intended to cope with very high-rate digital subscriber line specifications, i.e 12-bit resolution within a 20-MHz signal bandwidth. These modulators have been synthesized using a new methodology that is based on the direct synthesis of the whole cascaded architecture in the continuous-time domain instead of using a discrete-to-continuous time transformation as has been done in previous approaches. This method allows to place the zeroes/poles of the loop-filter transfer function in an optimal way and to reduce the number of analog components, namely: transconductors and/or amplifiers, resistors, capacitors and digital-to-analog converters. This leads to more efficient topologies in terms of circuitry complexity, power consumption and robustness with respect to circuit non-idealities. A comparison study of the synthesized architectures is done considering their sensitivity to most critical circuit error mechanisms. Time-domain behavioral simulations are shown to validate the presented approach.

Keywords: Analog-to-digital converters, sigma-delta modulators, continuous-time circuits.

### **1. INTRODUCTION**

<u>C</u>ontinuous-<u>T</u>ime (CT) <u>Sigma-D</u>elta <u>M</u>odulators ( $\Sigma\Delta$ Ms) have demonstrated to be an attractive solution for the implementation of <u>A</u>nalog-to-<u>D</u>igital (A/D) interfaces in systems-on-chip integrated in deep-submicron standard CMOS technologies <sup>1</sup>. Although most reported  $\Sigma\Delta$ Ms have been implemented using <u>D</u>iscrete-<u>T</u>ime (DT) circuits, the increasing demand for broadband data communication systems has motivated the use of CT circuit techniques. In addition to show an intrinsic antialiasing filtering, CT  $\Sigma\Delta$ Ms provide potentially faster operation with lower power consumption than their DT counterparts <sup>2,3</sup>.

In spite of their mentioned advantages, CT  $\Sigma\Delta Ms$  are more sensitive than DT  $\Sigma\Delta Ms$  to some circuit errors, namely: clock jitter, excess loop delay and technology parameter variations <sup>2,3</sup>. The latter are specially critical for the realization of cascaded architectures. This has forced the use of single-loop topologies in most reported silicon prototypes even thought low oversampling ratios (< 12) are needed <sup>4,5</sup>, whereas very few cascaded CT  $\Sigma\Delta M$  Integrated Circuits (ICs) have been reported <sup>6</sup>.

However, the need to achieve medium-high resolutions ( > 12bits ) within high signal bandwidths (> 20MHz) while guaranteeing stability, has prompted the interest in proper methods for the synthesis of high-order cascaded CT  $\Sigma\Delta Ms$ <sup>7-9</sup>. These methods are based on applying a DT-to-CT transformation to an equivalent DT topology that fulfils the required specifications. In most cases, the use of such a transformation is normally translated into an increase of the analog circuit complexity with the subsequent penalty in silicon area, power consumption and sensitivity to parameter tolerances.

This paper presents a direct synthesis method of cascaded CT  $\Sigma\Delta Ms$  which, dispensing with the DT-to-CT equivalence, make it possible to reduce the analog circuitry complexity and place the zeroes/poles of the quantization noise transfer function in an optimal way, thus yielding to more robust architectures than using a DT-to-CT transformation. As an application, the proposed methodology is used to find optimum CT  $\Sigma\Delta Ms$  for Very high-rate Digital Subscriber Line (VDSL). Three fifth-order cascaded topologies are synthesized: 2-1-1-1, 2-2 and 3-2. These modulators are designed for 12-bit@20-MHz specifications and their performances are compared in terms of time-domain simulations that take into account critical error mechanisms like mismatch and clock jitter error.

\* jrosa@imse.cnm.es; phone +34955056666; fax +34955056686; www.imse.cnm.es

VLSI Circuits and Systems II, edited by José Fco. López, Francisco V. Fernández, José María López-Villegas, José M. de la Rosa, Proceedings of SPIE Vol. 5837 (SPIE, Bellingham, WA, 2005) 0277-786X/05/\$15 · doi: 10.1117/12.607923

#### **2. CASCADED CONTINUOUS-TIME \Sigma\Delta MODULATORS**

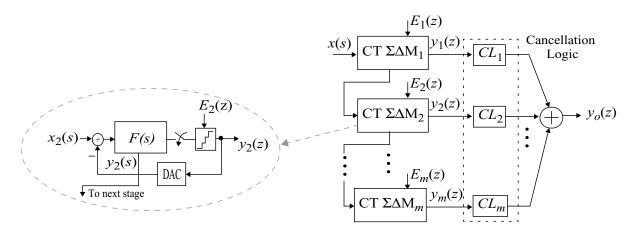

Fig.1 shows the conceptual block diagram of a *m*-stage cascaded CT  $\Sigma\Delta M$ . Each stage, consisting of a single-quantizer CT  $\Sigma\Delta M$ , re-modulates a signal containing the quantization error generated in the previous stage. Once in the digital domain, the outputs,  $y_i$ , of the stages are properly processed and combined (by the cancellation logic) in order to cancel out the quantization errors of all the stages, but the last one in the cascade. This latter error appears at the overall modulator output shaped by a function of order equal to the summation of the orders of all the stages.

Cascaded CT  $\Sigma\Delta$ Ms are normally synthesized from equivalent (well-known) DT systems and use the same digital cancellation logic <sup>8</sup>. This DT/CT equivalence can be guaranteed because the overall open loop transfer function of each stage in Fig.1 is in fact a DT system <sup>2</sup>. Thus, in the case of a rectangular impulsive response of the <u>Digital-to-Analog Converter</u> (DAC), it can be shown that the equivalent DT loop filter transfer function is given by <sup>10,11</sup>:

$$F(z) = \sum_{p_i} \operatorname{Re}\left(\frac{F(s)}{s} \cdot \frac{e^{m_1 T_s \cdot s}}{z - e^{T_s \cdot s}}\right) - \sum_{p_i} \operatorname{Re}\left(\frac{F(s)}{s} \cdot \frac{e^{m_2 T_s \cdot s}}{z - e^{T_s \cdot s}}\right)$$

(1)

where  $f_s = 1/T_s$  is the sampling frequency;  $m_1 = 1 - t_d/T_s$ ;  $m_2 = 1 - (t_d + \tau)/T_s$ ;  $t_d$  and  $\tau$  are respectively the time delay and pulse width of the DAC waveform;  $p_i$  are the poles of F(s)/s and Re(x) stands for the residue of x.

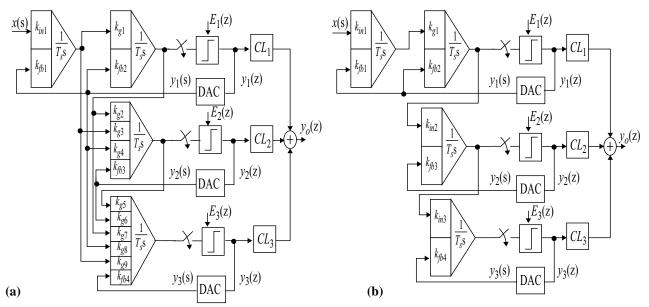

In order to get a functional CT  $\Sigma\Delta M$  while keeping the cancellation logic of the original DT  $\Sigma\Delta M$ , every state variable and DAC output must be connected to the integrator input of later stages<sup>8</sup>. This increases the number of analog components, i.e transconductors, amplifiers and DACs. As an illustration, Fig.2(a) shows a cascaded 2-1-1 CT  $\Sigma\Delta M$  obtained from an existing DT  $\Sigma\Delta M$ <sup>12</sup>. Note that at least eight scaling coefficients ( $k_{g2-9}$ ) and their corresponding signal paths are needed to connect the different stages of the modulator. The number of integrating paths can be reduced – as shown in Fig.2(b) – if the whole cascaded  $\Sigma\Delta M$  is directly synthesized in the CT domain as proposed in the next section.

### **3. PROPOSED SYNTHESIS METHODOLOGY**

The idea of dispensing with the DT-to-CT transformation was previously reported in <sup>3</sup> for single-loop architectures. However, in the case of cascaded architectures, the cancellation logic functions (not present in single-loop  $\Sigma\Delta Ms$ ) must be included in the synthesis procedure to get an optimum architecture.

Let us consider the more general case of the *m*-stage cascaded CT  $\Sigma\Delta M$  shown in Fig.1. The overall output,  $y_o$ , is given by:

$$y_{o}(z) = \sum_{k=1}^{m} y_{k}(z) C L_{k}(z)$$

(2)

Figure 1. Conceptual block diagram of a cascaded CT  $\Sigma \Delta M$ .

Figure 2. Cascaded 2-1-1 CT  $\Sigma\Delta M$  architecture obtained (a) from an equivalent DT  $\Sigma\Delta M$  (b) using the proposed method.

where  $y_k(z)$  and  $CL_k(z)$  represent respectively the output and partial cancellation logic transfer function of the k-th stage.

If the modulator input, x(t), is set to zero, the output of each stage can be written as:

$$y_{k}(z) = \frac{E_{k}(z) + \sum_{i=1}^{k-1} Z \left\{ L^{-1} [H_{D}F_{ik}] \Big|_{nT_{s}} \right\} y_{i}(z)}{1 - Z \left\{ L^{-1} [H_{D}F_{kk}] \Big|_{nT_{s}} \right\}}$$

(3)

where Z stands for the Z-transform,  $L^{-1}$  is the inverse Laplace transform,  $H_D \equiv H_{DAC}(s)$  is the transfer function of the DAC, and

$$F_{ij} \equiv F_{ij}(s) = \frac{\text{Input Quantizer j}}{y_i(s)}$$

(4)

represents the transfer function from  $y_i(s)$  to the input of *j*-th quantizer.

Using the following notation

$$Z_{km} \equiv Z \left( L^{-1} (H_D F_{km}) \big|_{nT_s} \right)$$

<sup>(5)</sup>

the output of each stage is given by:

$$y_k(z) = \frac{E_k(z)}{1 - Z_{kk}} + \sum_{i=1}^{k-1} \frac{Z_{ik} y_i(z)}{1 - Z_{kk}}$$

(6)

and the output of the modulator can be written as:

$$y_o = \sum_{k=1}^{m} y_k C L_k = \sum_{k=1}^{m} \left( \frac{E_k}{1 - Z_{kk}} + \frac{1}{1 - Z_{kk}} \sum_{i=1}^{k-1} Z_{ik} y_i \right) C L_k$$

(7)

Proc. of SPIE Vol. 5837 61

The partial cancellation logic transfer functions  $(CL_k)$  can be calculated by imposing the cancellation of the transfer function of the first m-1 quantization errors  $E_k(z)$  in (7). This gives:

$$CL_{k}(z) = \frac{-Z_{km}CL_{m}}{1-Z_{mm}} = \frac{-Z\left\{L^{-1}[H_{D}F_{km}]\big|_{nT_{s}}\right\}CL_{m}(z)}{1-Z\left\{L^{-1}[H_{D}F_{mm}]\big|_{nT_{s}}\right\}}$$

(8)

where the partial cancellation logic transfer function of the last stage,  $CL_m(z)$ , can be chosen to be the simplest form that preserves the required noise shaping.

Note that the design equations (2)-(8) do not only take into account the single-stage loop filter transfer functions ( $F_{ii}$ ), but also the inter-stage loop filter transfer functions ( $F_{ij}$ ,  $i \neq j$ ). The latter are continuous-time integrating paths appearing only when the modulator stages are connected to form the cascaded  $\Sigma\Delta M$  and must be included in the synthesis methodology to obtain a functional modulator with minimum number of inter-stage paths.

Therefore, the following procedure can be used in a systematic methodology for the synthesis of cascaded CT  $\Sigma \Delta Ms^{\dagger \dagger}$ :

- First, the poles of single-stage transfer functions ( $F_{ii}(s)$ ) are optimally placed in the signal bandwidth for given specifications. This process is carried out entirely in the CT domain and no equivalence to an existing DT modulator needs to be imposed.

- Second, once the individual stages are designed and optimized, cancellation logics are calculated using (8).

For illustrative purposes, the 2-1-1 CT  $\Sigma\Delta M$  of Fig.2(b) was synthesized using (2)-(8) to achieve 16-bit resolution in a 750-kHz bandwidth, with a sampling frequency of 48MHz (oversampling ratio, M = 32)<sup>12</sup>. For simplicity, in order to facilitate the comparison of the performance of both modulators in Fig.2, the coefficients of the first stage  $(k_{in1}, k_{g1}, k_{fb1}, k_{fb2})$  are taken to be equal in both systems and are obtained from a DT-to-CT transformation of the first stage of a DT  $\Sigma\Delta M$  in <sup>12</sup>. The rest of coefficients in Fig.2(b) are taken such that the time constant of the integrators is the inverse of the sampling frequency  $(T_s = 1/f_s)$ :

$$k_{in1} = -k_{fb1} = 1/4; \qquad k_{fb2} = -3/8 k_{g1} = k_{in2} = -k_{fb3} = k_{in3} = -k_{fb4} = 1$$

(9)

Hence, the single-loop and inter-stage transfer functions are given by:

$$F_{11} = \frac{-\left(\frac{3T_s}{8}s + \frac{1}{4}\right)}{\left(sT_s\right)^2} \qquad F_{22} = F_{33} = \frac{-1}{sT_s}$$

$$F_{13} = \frac{-\left(\frac{3T_s}{8}s + \frac{1}{4}\right)}{\left(sT_s\right)^4} \qquad F_{23} = \frac{-1}{\left(sT_s\right)^2}$$

(10)

and the partial cancellation logic transfer functions can be calculated using (8)-(10). Considering a <u>Non-Return-to-Zero</u> (NRZ) DAC, the following cancellation logics are derived:

$$CL_{1} = \frac{z^{-1}}{48}(7 + 29z^{-1} - 7z^{-2} - 5z^{-3})$$

$$CL_{2} = z^{-1}(1 + z^{-1})(1 - z^{-1})^{2}$$

$$CL_{3} = 2(1 - z^{-1})^{3}$$

(11)

<sup>&</sup>lt;sup>††</sup> In this procedure, the modulator order, oversampling ratio and number of bits of internal quantizers are assumed to be determined for given specifications from well-known expressions <sup>1</sup>.

where  $CL_3$  is chosen to have three zeroes at DC, corresponding to the zeroes contributed by the first three integrators.

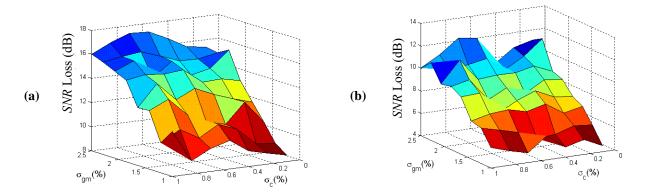

In order to compare the robustness of both modulators in Fig.2, the effect of mismatch on the <u>Signal-to-Noise Ratio</u> (*SNR*) was also simulated using SIMSIDES, a SIMULINK-based time-domain behavioral simulator for  $\Sigma\Delta Ms^{13}$ . For this purpose, maximum values of mismatch were estimated for a 0.13 µm CMOS technology and both modulators in Fig.2 were simulated considering a Gm-C implementation. The results are shown in Fig.3, where the *SNR* loss is represented as a function of the standard deviation of the transconductances ( $\sigma_{gm}$ ) and capacitances ( $\sigma_C$ ). For each point of these surfaces, 150 simulations were carried out using random variations with the standard deviation given in the diagrams. The value of *SNR* loss represented in Fig.3 stands for the difference between the ideal *SNR*, i.e with no parameter variation, and the *SNR* with 90% of the 150 simulations above it. It is shown that the lower analog component count in Fig.2(b) is reflected in a lower variance of the modulator coefficients, leading to a better behavior in terms of sensitivity to mismatch.

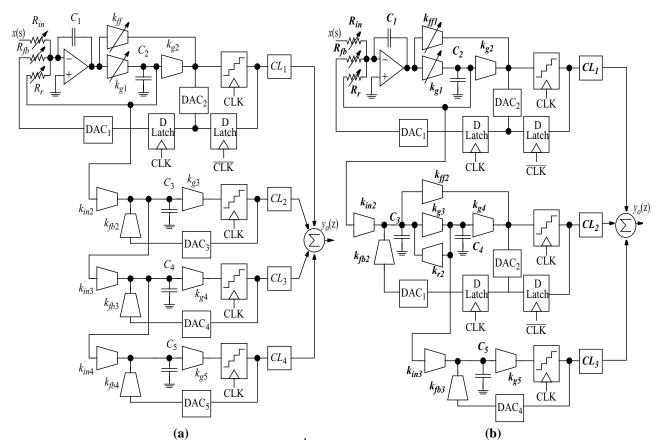

### 4. APPLICATION TO VDSL

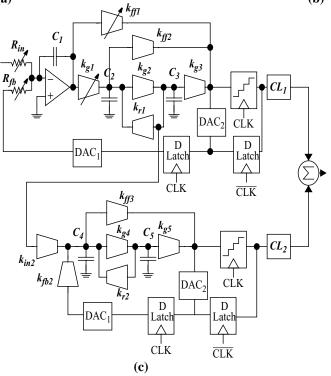

As an application of the proposed methodology, three 5th-order cascaded CT  $\Sigma\Delta Ms$ , shown in Fig.4, were synthesized to cope with VDSL specifications: 12-bit resolution within a 20-MHz signal bandwidth. In order to fulfil these specifications without being limited by the clock jitter error, the sampling frequency,  $f_s$ , and the number of bits of the internal quantizers (and DACs), B, must be properly chosen. In the case of a 5th-order modulators like those shown in Fig.4, the inband jitter noise power is minimized for  $f_s = 240$ MHz and  $B = 4^{-14}$ .

Another critical source of error in CT  $\Sigma\Delta Ms$  is the excess loop delay. As shown in <sup>15</sup> this error can be compensated by adding an extra feedback branch between the output and the input to the quantizer (DAC<sub>2</sub> in Fig.4) and two D-latches. By adding this extra branch with the appropriate gain, the loop impulse response is exactly the same as that of the original. This extra feedback term can be easily included in the calculation of the cancellation logic. In a practical implementation it could be advantageous to make DAC<sub>2</sub> programmable <sup>5</sup>.

Considering the factors above, the CT  $\Sigma\Delta$ Ms in Fig.4 were synthesized using the methodology described in Section 3, taking into account the following considerations:

- The first stage of the 2-1-1-1 architecture (Fig.4(a)) is formed by a resonator which has its poles placed at  $\omega_p = 2\pi \sqrt{7/9} B_w$ , in order to minimize the quantization Noise Transfer Function (NTF) in the signal bandwidth,  $B_w$ . Resistor variations can be tuned out using a combination of a discrete rough tuning of the resistors ( $R_{in}, R_{fb}$  and  $R_r$ ) and a continuous fine tuning of the transconductors  $k_{ff}$  and  $k_{g1}$ . This tuning can be also used to cancel the effect of finite Gain-Bandwidth product (*GB*) of the front-end opamp, due to the fact that this error can be modelled as an integrator gain error <sup>5</sup>. All the other transconductors could be tuned in order to keep the time constant  $C/g_m$  unchanged over C variations.

- An additional resonator has been used in the 2-2-1 architecture (Fig.4(b)), in order to optimally distribute the poles of NTF <sup>16</sup>.

Figure 3. Effect of mismatch on the *SNR* of a cascaded 2-1-1 CT  $\Sigma\Delta M$  obtained from: (a) an equivalent DT  $\Sigma\Delta M$ ; (b) proposed method.

Figure 4. Cascaded CT  $\Sigma\Delta$ Ms synthesized for VDSL: (a) 2-1-1-1; (b) 2-2-1; (c) 3-2.

The 3-2 modulator shown in Fig.4(c) includes a first stage which consists of an integrator and a resonator. This

topology allows the same optimum pole positioning as in the 2-2-1 modulator with one less stage. However, stability problems might arise that compromise the modulator performance.

Table 1 shows the single-loop and inter-stage transfer functions  $(F_{ij})$  for the different architectures in Fig.4 as a function of the loop filter coefficients  $b_{ij}$ . The expressions of  $CL_i$ , obtained from (8) and (11), are also shown. It is important to note that  $b_{ij}$  are found from an iterative simulation-based process that optimizes the first stage of the modulator in order to maximize *SNR* while keeping stability.

The outcome of the optimization process – entirely done in the CT domain – is summarized in Table 2. This table includes the values of loop filter coefficients,  $k_i$  (implemented as transconductances) as well as the capacitances,  $C_i$ , and resistances,  $R_i$  obtained from the optimization process.

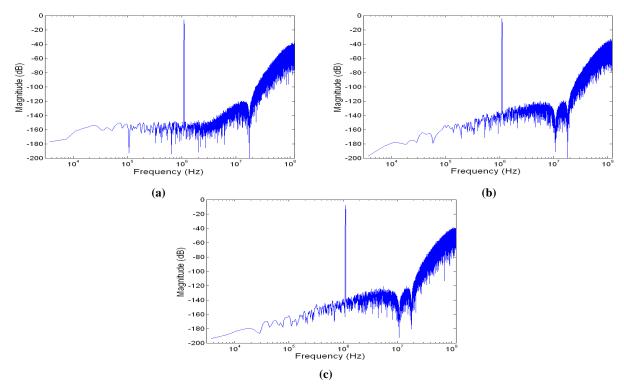

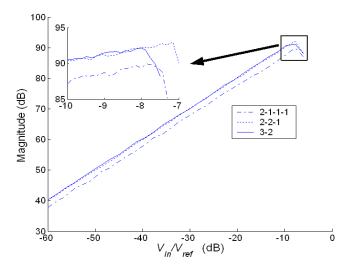

The modulators in Fig.4 were simulated using SIMSIDES <sup>13</sup>. Fig.5 shows the ideal output spectra of the modulators when clocked at  $f_s = 240$  MHz. It can be observed the effect of the resonators poles distributed within the signal bandwidth. The impact on the in-band noise power is better appreciated in Fig.6 that represents the Signal-to-(Noise+Distortion) Ratio (SNDR) vs input amplitude. Note that, although both the 2-2-1 and 3-2 architectures have the same location of the zeroes of the NTF, the 3-2 modulator achieves a worse resolution. This is due to the fact that the optimization process applied to that architecture was more conservative as a consequence of the stability constrains imposed by the 3rd-order stage.

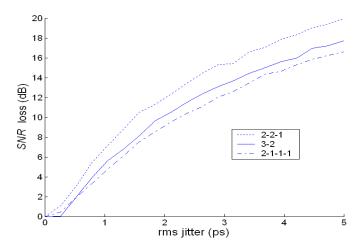

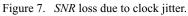

In addition to the ideal performance described above, the effect of most critical limiting factors has been taken into account in the high-level design. Fig.7 shows the *SNR* loss caused by clock jitter error. Note that the 2-1-1-1 architecture seems to be less sensitive to this error than the other architectures. However, it is important to note that the ideal *SNR* of this modulator is lower than the others. Therefore, there is a higher component of quantization noise masking the effect of clock jitter.

Two critical limiting factors in cascaded  $\Sigma\Delta Ms$ , and particularly in their CT implementation, are circuit tolerances and component mismatch. The first one can be controlled by using tuning of time constants <sup>4,5</sup> or digital calibration <sup>6</sup>. However mismatch error still remains. In order to evaluate the impact of this error on the performance of the modulators in Fig.4, maximum values of mismatch were estimated for a 0.13 µm CMOS technology considering a Gm-C implementation. The

Figure 5. Ideal output spectra of the cascaded CT ΣΔMs in Fig.4: (a) 2-1-1-1. (b) 2-2-1. (c) 3-2.

| Modulator | Transfer functions                                                                                                                                      | Cancellation Logic                                                                                                                                                                     |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2-1-1-1   | $F_{14} = \frac{b_{10}}{s^3(s^2 + \omega_p^2)}$                                                                                                         | $CL_{1} = z^{-1}(n_{14} + n_{13}z^{-1} + n_{12}z^{-2} + n_{11}z^{-3} + n_{10}z^{-4})$<br>$CL_{2} = \frac{1}{6}z^{-1}(1 + 4z^{-1} - z^{-2})(1 - 2\cos(T_{s}\omega_{p})z^{-1} + z^{-2})$ |  |  |  |

|           | $F_{24} = \frac{-1}{T_s^3 s^3}$ $F_{34} = \frac{-1}{T_s^2 s^2}$                                                                                         | $CL_{2} = \frac{1}{6}z^{-1}(1+z^{-1})(1-z^{-1})(1-2\cos(T_{s}\omega_{p})z^{-1}+z^{-2})$ $CL_{3} = \frac{1}{2}z^{-1}(1+z^{-1})(1-z^{-1})(1-2\cos(T_{s}\omega_{p})z^{-1}+z^{-2})$        |  |  |  |

|           | $F_{44} = \frac{-1}{T_s s}$                                                                                                                             | $CL_4 = (1 - z^{-1})^2 (1 - 2\cos(T_s \omega_p) z^{-1} + z^{-2})$                                                                                                                      |  |  |  |

| 2-2-1     | $F_{13} = \frac{b_{10}}{s(s^2 + \omega_{p1}^2)(s^2 + \omega_{p2}^2)}$ $F_{23} = \frac{b_{20}}{s(s^2 + \omega_{p2}^2)} \qquad F_{44} = \frac{-1}{T_s s}$ |                                                                                                                                                                                        |  |  |  |

| 3-2       | $F_{12} = \frac{b_{11}s + b_{10}}{s(s^2 + \omega_{p1}^2)(s^2 + \omega_{p2}^2)}$                                                                         | $CL_{1} = z^{-2}(n_{14} + n_{13}z^{-1} + n_{12}z^{-2} + n_{11}z^{-3} + n_{10}z^{-4})$<br>$CL_{2} = (1 - 2\cos(T_{s}\omega_{p1})z^{-1} + z^{-2})(1 - z^{-1}) \cdot$                     |  |  |  |

|           | $F_{22} = \frac{b_{21}s + b_{20}}{s^2 + \omega_{p2}^2} e^{-T_s s} + k_c e^{-T_s s/2}$                                                                   | $(1 - (2\cos(T_s\omega_{p2}) - k_c)z^{-1} + (1 + n_{21} - k_c 2\cos(T_s\omega_{p2}))z^{-2} + (n_{20} + k_c)z^{-3})$                                                                    |  |  |  |

|           | Cancellation Logic Coefficients                                                                                                                         |                                                                                                                                                                                        |  |  |  |

| 2-1-1-1   | s - p                                                                                                                                                   | $T_s \omega_p) - T_s \omega_p + \frac{1}{6} (T_s \omega_p)^3 \bigg]$                                                                                                                   |  |  |  |

|           |                                                                                                                                                         | $(\omega_p)^3 \frac{2 - \cos(T_s \omega_p)}{3} - 4\sin(T_s \omega_p) + 2T_s \omega_p (\cos(T_s \omega_p) + 1)$                                                                         |  |  |  |

|           | $T_{12} = \frac{-b_{10}}{T_s^3 \omega_p^5} [(T_s \omega_p)^3 \frac{1-t_s^3}{t_s^3}]^3$                                                                  | $\frac{4\cos(T_s\omega_p)}{3} + 6\sin(T_s\omega_p) - 2T_s\omega_p(1 + 2\cos(T_s\omega_p))]$                                                                                            |  |  |  |

| 2-2-1     | $_{10} = n_{14} = \frac{-b_{10}}{\omega_{p1}^3 \omega_{p2}^3 (\omega_{p2}^2 - \omega_{p3}^2)}$                                                          | $\frac{1}{\omega_{p1}^{2}} [T_{s}(\omega_{p1}\omega_{p2}^{3} - \omega_{p1}^{3}\omega_{p2}) + \omega_{p1}^{3}\sin(T_{s}\omega_{p2}) - \omega_{p2}^{3}\sin(T_{s}\omega_{p1})$            |  |  |  |

|           | $_{11} = n_{13} = \frac{-2b_{10}}{\omega_{p1}^3 \omega_{p2}^3 (\omega_{p2}^2 - \omega_{p3}^2)}$                                                         | $\frac{1}{\omega_{p1}^{2}}\left[(T_{s}(\omega_{p2}\omega_{p1}^{3}-\omega_{p2}^{3}\omega_{p1})(\cos(T_{s}\omega_{p1})+\cos(T_{s}\omega_{p2})))+\right]$                                 |  |  |  |

|           | $+\omega_{p2}^3\sin(T_s\omega_{p1})(1+\cos(T_s\omega_{p1}))$                                                                                            | $T_s\omega_{p2})) - \omega_{p1}^3 \sin(T_s\omega_{p2})(1 + \cos(T_s\omega_{p1}))]$                                                                                                     |  |  |  |

|           | $_{12} = \frac{-2b_{10}}{\omega_{p1}^{3}\omega_{p2}^{3}(\omega_{p2}^{2} - \omega_{p1}^{2})}[T$                                                          | $_{s}(\omega_{p1}\omega_{p2}^{3} - \omega_{p1}^{3}\omega_{p2})(1 + 2\cos(T_{s}\omega_{p1})\cos(T_{s}\omega_{p2})) +$                                                                   |  |  |  |

|           | $+\omega_{p1}^3\sin(T_s\omega_{p2})(1+2\cos(t))$                                                                                                        | $(T_s \omega_{p1})) - \omega_{p2}^3 \sin(T_s \omega_{p1}) (1 + 2\cos(T_s \omega_{p2}))]$                                                                                               |  |  |  |

|           | $_{20} = n_{22} = \frac{-b_{20}}{\omega_{p2}^3} [T_s \omega_{p2} - si$                                                                                  | $n(T_{s}\omega_{p2})] \qquad n_{21} = \frac{-2b_{20}}{\omega_{p2}^{3}} [\sin(T_{s}\omega_{p2}) - T_{s}\omega_{p2}\cos(T_{s}\omega_{p2})]$                                              |  |  |  |

Table 1: Transfer functions and cancellation logic functions of the modulators in Fig.4

Table 1: Transfer functions and cancellation logic functions of the modulators in Fig.4.(Cont.)

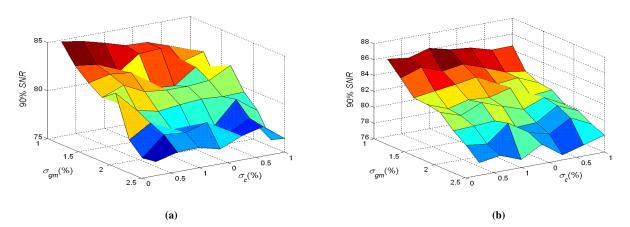

results of this analysis are shown in Fig.8 where the *SNR* is represented as a function of the standard deviation of the transconductances ( $\sigma_{gm}$ ) and capacitances ( $\sigma_C$ ). For each point of these surfaces, a MonteCarlo analysis of 150 simulations was carried out. The value of the *SNR* represented in the vertical axis of Fig.8 is obtained by 90% of the simulations for each case of  $\sigma_{gm}$  and  $\sigma_C$ . Note that even in the worst-case mismatch, the resolution is above the specified (72-dB).

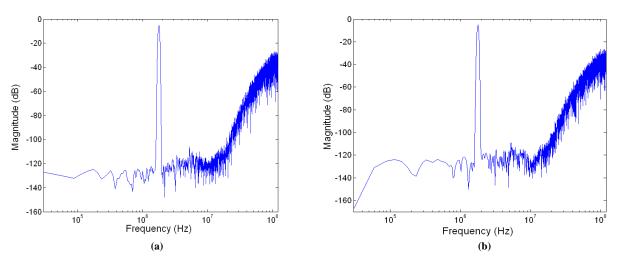

Finally, the modulators in Fig.4 were high-level sized, i.e, the system-level specifications (12-bit@20-MHz) were mapped onto building-block specification using statistical optimization for design parameter selection, and behavioral simulation for evaluation. The results of this sizing process are summarized in Table 3 and Table 4 showing the maximum (minimum) values of the circuit error mechanisms that can be tolerated in order to fulfil the required modulator performance. As an illustration, Fig.9 shows the output spectra of the modulators taking into account the non-idealities listed in these tables. The effective resolution is  $\cong 13.4$  bits and  $\cong 13.2$  bits for the modulators in Fig.4(b) and (c), respectively.

Figure 6. SNDR vs. input amplitude (referred to reference voltage).

| 2-1-1-1 N                           | Aodulator                           | 2-2-1 Modulator                                                     |                             | 3-2 Modulator                           |                         |

|-------------------------------------|-------------------------------------|---------------------------------------------------------------------|-----------------------------|-----------------------------------------|-------------------------|

| $R_{in} = R_{fb} = 2 \text{ kG}$    | $\Omega; R_r = 8.2 \text{ k}\Omega$ | $R_{in1} = R_{fb1} = 2 \text{ k}\Omega; R_{r1} = 9 \text{ k}\Omega$ |                             | $R_{in1} = R_{fb1} = 2 \text{ k}\Omega$ |                         |

| $C_1 = 1.875 \mathrm{pF}$           | $C_{25} = 0.75 \mathrm{pF}$         | $C_1 = 1.875 \text{ pF}$                                            | $C_{25} = 0.75 \mathrm{pF}$ | $C_1 = 10 \text{ pF}$                   | $C_{25} = 1 \text{ pF}$ |

| $k_{g1} = 150 \ \mu S$              | $k_{g2} = 48 \ \mu S$               | $k_{g1} = 166 \ \mu S$                                              | $k_{g2} = 30 \ \mu S$       | $k_{g1} = 312 \ \mu S$                  | $k_{g2} = 130 \ \mu S$  |

| $k_{g35} = 20 \mu S$                | $k_{ff} = 60 \ \mu S$               | $k_{g3} = 200 \ \mu S$                                              | $k_{g4} = 46 \ \mu S$       | $k_{g3} = 26 \ \mu S$                   | $k_{g4} = 182 \ \mu S$  |

| $k_{in24} = k_{fb24} = 180 \ \mu S$ |                                     | $k_{g5} = 20 \ \mu S$                                               | $k_{r2} = 13 \ \mu S$       | $k_{g5} = 104 \ \mu S$                  | $k_{ff1} = 208 \ \mu S$ |

|                                     |                                     | $k_{ff1} = 63 \ \mu S$                                              | $k_{ff2} = 112 \ \mu S$     | $k_{ff2} = 78 \ \mu S$                  | $k_{ff3} = 130 \ \mu S$ |

|                                     |                                     | $k_{in2} = k_{fb2} = 100 \ \mu S$                                   |                             | $k_{in2} = k_{fb2} = 130 \ \mu S$       |                         |

|                                     |                                     | $k_{in3} = k_{fb3} = 180 \ \mu S$                                   |                             | $k_{r1} = 208 \ \mu S$                  | $k_{r2} = 26 \ \mu S$   |

| Table 2: Loop fi | ilter coefficients | of the mod | lulators i | n Fig.4 |

|------------------|--------------------|------------|------------|---------|

|------------------|--------------------|------------|------------|---------|

Table 3: High-level sizing of Fig.4(b)

| Front-end opamp              |          |  |  |  |

|------------------------------|----------|--|--|--|

| GB                           | >600 MHz |  |  |  |

| DC Gain                      | >70 dB   |  |  |  |

| Phase Margin                 | 60°      |  |  |  |

| Parasitic Input Capacitance  | <0.2 pF  |  |  |  |

| Parasitic Output Capacitance | <0.2 pF  |  |  |  |

| Diff. Output Swing           | >0.5 V   |  |  |  |

| Transconductors              |          |  |  |  |

| DC Gain                      | >50 dB   |  |  |  |

| Diff. Input Amplitude        | 0.3 V    |  |  |  |

| Diff. Output Amplitude       | 0.3 V    |  |  |  |

| Third-order non-linearity    | >56 dBV  |  |  |  |

#### Table 4: High-level sizing of Fig.4(c)

| Front-end opamp              |          |  |  |

|------------------------------|----------|--|--|

| GB                           | >600 MHz |  |  |

| DC Gain                      | >60 dB   |  |  |

| Phase Margin                 | 60°      |  |  |

| Parasitic Input Capacitance  | <0.2 pF  |  |  |

| Parasitic Output Capacitance | <0.2 pF  |  |  |

| Diff. Output Swing           | >0.5 V   |  |  |

| Transconductors              |          |  |  |

| DC Gain                      | >60 dB   |  |  |

| Diff. Input Amplitude        | 0.4 V    |  |  |

| Diff. Output Amplitude       | 0.4 V    |  |  |

| Third-order non-linearity    | >53 dBV  |  |  |

Figure 8. SNR loss vs. mismatch for: (a) 2-2-1 CT  $\Sigma\Delta M$ . (b) 3-2 CT  $\Sigma\Delta M$ .

Figure 9. Output Spectra for: (a) 2-2-1 CT  $\Sigma \Delta M$ . (b) 3-2 CT  $\Sigma \Delta M$ .

## **5. CONCLUSIONS**

In this paper a new methodology of synthesizing cascaded continuous-time  $\Sigma\Delta$  modulators has been presented. It has been demonstrated that more efficient topologies in terms of circuit complexity can be generated if the design is directly done in the continuous-time domain and the cancellation logic is taken into account in the synthesis procedure. In order to illustrate the method, several cascaded architectures have been synthesized and designed to achieve VDSL system requirements: 12-bit@20MHz. Behavioral time-domain simulations considering their most critical limiting factors show that these architectures are good candidates for in-coming broadband telecommunication systems.

### ACKNOWLEDGMENTS

This work has been supported by the Spanish Ministry of Science and Education (with support from European Regional Development Fund) under contract TEC2004-01752/MIC.

#### REFERENCES

- 1. A. Rodríguez-Vázquez, F. Medeiro and E. Janssens (Editors): CMOS Telecom Data Converters. Kluwer, 2003.

- J.A. Cherry and W.M. Snelgrove: Continuous-Time Delta-Sigma Modulators for High-Speed A/D Conversion. Kluwer, 2000.

- 3. L. Breems and J.H. Huijsing: Continuous-Time Sigma-Delta Modulation for A/D Conversion in Radio Receivers. Kluwer, 2001.

- M. Moyal, M. Groepl, H. Werker, G. Mitteregger, J. Schambacher: "A 700/900mW/Channel CMOS Dual Analog Front-End IC for VDSL with Integrated 11.5/14.5dBm Line Drivers". *Proc. of the 2003 IEEE Int. Solid-State Circuits Conf.*, pp. 416-417.

- S. Patón, A. Di Giandoménico, L. Hernández, A. Wiesbauer, T. Pötscher and M. Clara: "A 70-mW 300-MHz CMOS Continuous-Time ΣΔ ADC With 15-MHz Bandwidth and 11 Bits of Resolution". *IEEE Journal of Solid-State Circuits*, Vol. 39, pp. 1056-1063, July 2004.

- L. J. Breems, R. Rutten and G. Wetzker: "A Cascaded Continuous-Time ΣΔ Modulator with 67dB Dynamic Range in 10-MHz Bandwidth". *IEEE Journal of Solid-State Circuits*, Vol. 39, pp. 2152-2160, December 2004.

- 7. C.-H. Lin and M. Ismail: "Synthesis and analysis of high-order cascaded continuous-time Sigma-Delta modulators". *Proc. of the 1999 IEEE Int. Conf. on Electronics, Circuits and Systems*, pp. 1693-1696.

- 8. M. Ortmanns, F. Gerfers, and Y. Manoli: "On the Synthesis of Cascaded Continuous-Time Sigma-Delta Modulators". *Proc. of the 2001 IEEE Int. Symposium on Circuits and Systems*, pp. 419-422.

- 9. O. Oliaei: "Design of Continous-Time Sigma-Delta Modulators with Arbitrary Feedback Waveform". *IEEE Transactions on Circuits and Systems-II*, Vol. 50, pp. 437-444, August 2003.

- O. Shoaei: Continuous-Time Delta-Sigma A/D Converters for High Speed Applications. PhD Thesis, Carleton University, 1995.

- H. Aboushady, M. Louerat: "Systematic Approach for Discrete-Time to Continuous-Time Transformation of ΣΔ Modulators". Proc. of the 2002 IEEE Int. Symposium on Circuits and Systems, Vol. 4, pp. 229-232.

- G. Yin and W. Sansen: "A High-Frequency and High-Resolution Fourth-Order ΣΔ A/D Converter in BiCMOS Technology". *IEEE Journal of Solid-State Circuits*, Vol. 29, pp. 857-865, August 1994.

- 13. J. Ruiz-Amaya, J.M. de la Rosa, F. Medeiro, F.V. Fernández, R. del Río, B. Pérez-Verdú and A. Rodríguez-Vázquez: "An Optimization-based Tool for the High-Level Synthesis of Discrete-time and Continuous-Time ΣΔ Modulators in the MATLAB/SIMULINK Environment". *Proc. IEEE Int. Symp. Circuits and Systems*, Vol V., pp. 97-100, 2004.

- 14. R. Tortosa, J.M. de la Rosa, A. Rodríguez-Vázquez, F.V. Fernández: "Analysis of Clock Jitter Error in Multibit Continuous-Time Sigma-Delta Modulators with NRZ Feedback Waveform". Proc. of 2005 IEEE Int. Symp. Circuits and Systems. Accepted for its publication.

- S. Yan, E. Sánchez-Sinencio: "A Continuous-Time ΣΔ Modulator With 88-dB Dynamic Range and 1.1-MHz Signal Bandwidth", *IEEE Journal of Solid-State Circuits*, Vol. 39, pp. 75-86, January 2004.

- 16. R. Schreier: "An Empirical Study of High-Order Single-Bit Delta-Sigma Modulators". *IEEE Transactions on Circuits and Systems-II*, Vol 40, August 1993.

- 70 Proc. of SPIE Vol. 5837