## UNIVERSIDAD DE SEVILLA

DOCTORAL THESIS

## Neuromorphic Deep Convolutional Neural Network Learning Systems for FPGA in Real Time.

*Author:* Ricardo Tapiador Morales

*Supervisor:* Dr. Gabriel Jiménez Moreno Dr. Alejandro Linares Barranco Dr Ángel F. Jiménez Fernandez

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Robotics and Computer Technology Lab. Departamento de Arquitectura y Tecnología de Computadores.

## **Declaration of Authorship**

I, Ricardo Tapiador Morales, declare that this thesis entitled "Neuromorphic Deep Convolutional Neural Network Learning Systems for FPGA in Real Time." and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

#### UNIVERSIDAD DE SEVILLA

## Abstract

Escuela Técnica Superior de Ingeniería Informática. Departamento de Arquitectura y Tecnología de Computadores.

#### Doctor of Philosophy

## Neuromorphic Deep Convolutional Neural Network Learning Systems for FPGA in Real Time.

by Ricardo Tapiador Morales

In this work, it is intended to advance on the knowledge of Deep Learning and pattern recognition and their hardware implementations, such as hardware architectures for frame-based and event-based processing paradigms.

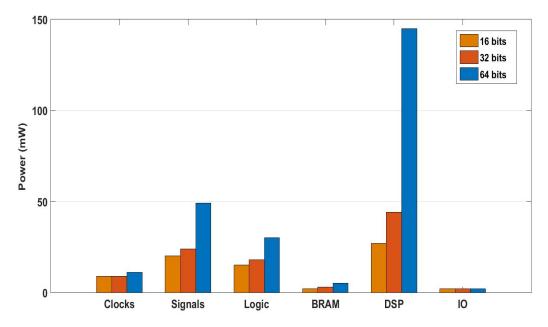

First, frame-based vision systems are studied, along with Deep Learning algorithms for feature extraction in vision sensors, particularly Convolutional Neural Networks. Based on these studies, an FPGA OpenCL implementation for real-time frame-based CNN inference is proposed. Additionally, a second CNN accelerator based on a SoC-FPGA platform called NullHop is presented. Both designs are analyzed in terms of accuracy, latency, power consumption and area.

Next, biological neuron behaviour and neuromorphic vision sensors are studied, in order to adapt the CNN algorithm to the spiking domain. With the aim of inferring Spiking Convolutional Neural Networks, three different spiking convolution processors are presented. These spiking processors are inspired in leakage integrate and fire neurons and they perform the convolution operation with the arrival of events from a neuromorphic vision sensor. The three convolution processors proposed were tested with different stimuli to determine their behaviour and measure their performance..

Finally, a new event-based algorithm for feature extraction, called HOTS, was used to recognize gestures from a neuromorphic vision sensor. The HOTS algorithm uses a novel concept called time-surface, which represents the spatio-temporal activity of events to extract features from events. From this approach, a novel architecture for a VLSI system to infer the HOTS algorithm is presented with a testbench to characterize the system. In addition, a new memory model to reduce memory accesses and memory resources consumption was proposed and tested in a HOTS network.

Lastly, the performance and efficiency of these systems were evaluated. Then, the conclusions obtained are presented and new features and improvements are proposed for future works.

## Agradecimientos

El desarrollo de esta tesis, ha sido sin lugar a dudas uno de los retos más difíciles a los que me he enfrentado. Han sido tres años llenos de experiencias, dificultades y altibajos, que me han hecho avanzar tanto a nivel profesional como personal. Sin embargo, he tenido la suerte de contar con personas que me han ayudado en el camino, motivándome, apoyándome y enseñándome. Estas páginas están dedicada a esas personas.

Me gustaría empezar agradeciendo a mis directores de tesis, Gabriel Jiménez Moreno, Alejandro Linares Barranco y Ángel Jiménez Fernández, por ayudarme en los problemas encontrados a lo largo de la tesis, aconsejándome y guiándome en cada paso que daba con sus sabios consejos, formándome como científico e investigador. Agradecer en particular la labor de uno de mis directores de tesis, Alejandro Linares Barranco por confiar y creer en mí, dándome la oportunidad de entrar y colaborar en el departamento de Arquitectura y Tecnología de Computadores donde he vivido incontables experiencias que jamás olvidare.

Agradecer a los miembros del grupo de Robótica y Tecnología de Computadores por estar a mi lado estos años haciendo de mi lugar de trabajo, un segundo hogar. Gracias a Manuel Domínguez Morales, Elena Cerezuela, Antón Civit Balcells, José Luis Sevillano Ramos, Daniel Cascado Caballero, Francisco Gómez Rodríguez, Lourdes Miró Amarante, Fernando Díaz del Río, Francisco Luna Perejón junto al resto de miembros del grupo de investigación.

Destacar la suerte de tener unos compañeros de trabajo a los que puedo llamar amigos, estas líneas van dedicadas a Antonio Ríos Navarro, Juan Pedro Domínguez Morales y Daniel Gutiérrez Galán. Con los cuales he tenido suerte de compartir muchas experiencias como estancias de investigación, viajes y alguna que otra barbacoa. Muchas gracias por vuestro apoyo, habéis sido de gran ayuda. Muchas gracias al equipo de electrónicos del departamento formado por Alberto Vázquez Baeza y Juan Manuel Montes, quienes siempre se han prestado a ayudarme y me han dado su apoyo en todo momento.

En el ámbito personal agradecer a mis amigos Pedro Castañeda Fernández, Juan Manuel Muñoz Noguera, María Jiménez Fernández, Cristina Santos Serra, Isabel Maria Beasley Bohorquez, Laura Cano García junto al resto del grupo por las partidas de juegos de mesa, conversaciones y múltiples salidas que me han ayudado a despejarme y animarme.

En lo familiar, agradezco a mis abuelos Manuel Morales Guerrero e Isabel Salguero Becerro, quienes me han cuidado desde pequeño viéndome crecer y convertirme en la persona que soy ahora.

Mención especial a Narciso Reguera Rodríguez y Dolores Valenzuela Díaz, a quien tengo el honor de llamarles mis segundos padres, estando junto a mí en los buenos y en los malos momentos tratándome como si fuera su hijo. Gracias de todo corazón.

A Natalia Martin Saborido, quien me ha acompañado durante gran parte de este camino dándome su apoyo, cariño, aportando su gran creatividad a mi vida. Muchísimas gracias.

Por último, las personas más importantes en mi vida a los que le dedico este trabajo, mis padres y mi hermana, Ricardo Tapiador Domínguez, María Isabel Morales Salguero y Cristina Tapiador Morales. Gracias por escucharme y aguantar mis altibajos, por educarme e inculcarme el valor del esfuerzo y la constancia, las cuales han sido clave en mi vida. Muchas gracias familia por todo.

# Contents

| Declaration of Authorship iii |       |         |                                                                                      |     |

|-------------------------------|-------|---------|--------------------------------------------------------------------------------------|-----|

| Abstract v                    |       |         |                                                                                      |     |

| Ag                            | grade | cimient | tos                                                                                  | vii |

| 1                             | Intro | oductio | n                                                                                    | 1   |

|                               | 1.1   | Motiva  | ation                                                                                | 2   |

|                               | 1.2   | Neuro   | -inspired systems                                                                    | 4   |

|                               |       | 1.2.1   | Neuromorphic engineering                                                             | 5   |

|                               |       | 1.2.2   | Address event representation                                                         | 9   |

|                               | 1.3   | Artific | ial Vision                                                                           | 10  |

|                               |       | 1.3.1   | Vision in Biology                                                                    | 10  |

|                               |       | 1.0.1   | 1.3.1.1 Visual System                                                                | 10  |

|                               |       |         | 1.3.1.2 Retina                                                                       | 10  |

|                               |       |         | 1.3.1.2     Internal geniculate nucleus       1.3.1.3     Lateral geniculate nucleus | 10  |

|                               |       |         | 1.3.1.4   Visual Cortex                                                              | 10  |

|                               |       | 1.3.2   | Acquisition of digital images                                                        | 11  |

|                               |       |         | 1 0 0                                                                                |     |

|                               |       | 1.3.3   | Silicon retinas                                                                      | 13  |

|                               | 1 4   | 1.3.4   | JAER                                                                                 | 14  |

|                               | 1.4   | -       | Learning                                                                             | 15  |

|                               |       | 1.4.1   | History of Deep Learning                                                             | 15  |

|                               |       | 1.4.2   | State-of-the-art in CNNs accelerators                                                | 16  |

|                               |       |         | 1.4.2.1 Origami accelerator                                                          | 16  |

|                               |       |         | 1.4.2.2 Snowflake                                                                    | 17  |

|                               |       |         | 1.4.2.3 Eyeriss                                                                      | 17  |

|                               | 1.5   | Spikin  | g Neural Networks                                                                    | 18  |

|                               |       | 1.5.1   | IBM-TrueNorth                                                                        | 18  |

|                               |       | 1.5.2   | NeuroGrid                                                                            | 19  |

|                               |       | 1.5.3   | SpiNNaker                                                                            | 19  |

|                               |       | 1.5.4   | Intel Loihi                                                                          | 20  |

|                               |       | 1.5.5   | DYNAP                                                                                | 21  |

|                               |       | 1.5.6   | Spiking Convolutional Neural Networks                                                | 22  |

| 2                             | Obje  | ectives | and Thesis structure                                                                 | 23  |

|                               | 2.1   | Object  | ives                                                                                 | 23  |

|                               | 2.2   | Thesis  | structure                                                                            | 25  |

| 3                             | Con   | volutio | nal Neural Network Accelerators                                                      | 27  |

|                               |       | 3.0.1   | Convolution layer                                                                    | 28  |

|                               |       | 3.0.2   | Pooling layer                                                                        | 28  |

|                               |       |         | 3.0.2.1 Max-pooling                                                                  | 28  |

|                               |       |         | 3.0.2.2 Average-pooling                                                              | 29  |

|   |      | 3.0.3 Dropout layer                                                                                                                                             |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 3.0.4 Fully-connected layer                                                                                                                                     |

|   |      | 3.0.5 ReLU layer                                                                                                                                                |

|   | 3.1  | OpenCL                                                                                                                                                          |

|   |      | 3.1.1 Platform model                                                                                                                                            |

|   |      | 3.1.2 Execution model                                                                                                                                           |

|   |      | 3.1.3 Memory model                                                                                                                                              |

|   |      | 3.1.4 CNN inference using Altera OpenCL                                                                                                                         |

|   |      | 3.1.5 Results                                                                                                                                                   |

|   | 3.2  | NN-X architecture                                                                                                                                               |

|   | 3.3  | NullHop Accelerator                                                                                                                                             |

|   | 0.0  | 3.3.1 NullHop Architecture                                                                                                                                      |

|   |      | 3.3.2 NullHop FPGA implementation                                                                                                                               |

|   |      | 3.3.2.1 AXI-INTERFACE                                                                                                                                           |

|   |      | 3.3.2.2 Implementation Results                                                                                                                                  |

|   |      | 3.3.2.3 Real-time CNN inference                                                                                                                                 |

|   |      | $5.5.2.5  \text{Real-time CIVIN Interestice} \dots \dots$ |

| 4 | Spil | king Convolution Accelerators 43                                                                                                                                |

|   | 4.1  | Spiking convolution layers                                                                                                                                      |

|   |      | 4.1.1 Spiking convolution                                                                                                                                       |

|   | 4.2  | Subsampling layer                                                                                                                                               |

|   | 4.3  | Leaky integrate-and-fire convolution processor V1                                                                                                               |

|   |      | 4.3.1 Leaky integrate.and-fire neuron model for V1 convolution                                                                                                  |

|   |      | processor                                                                                                                                                       |

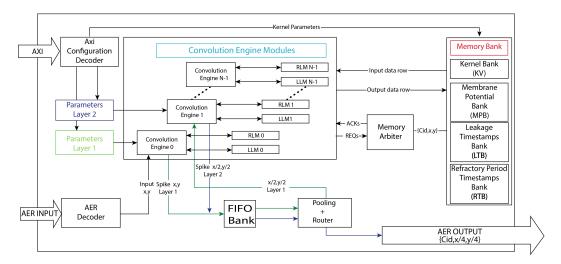

|   |      | 4.3.2 Spiking convolution processor V1 architecture                                                                                                             |

|   |      | 4.3.2.1 Membrane potential, leakage timestamps and kernel                                                                                                       |

|   |      | BRAM banks                                                                                                                                                      |

|   |      | 4.3.2.2 Leakage system                                                                                                                                          |

|   |      | 4.3.2.3 Convolution Engine                                                                                                                                      |

|   | 4.4  | Leaky integrate-and-fire convolution processor V2                                                                                                               |

|   |      | 4.4.1 Leaky integrate-and-fire neuron model for V2 convolution                                                                                                  |

|   |      | processor                                                                                                                                                       |

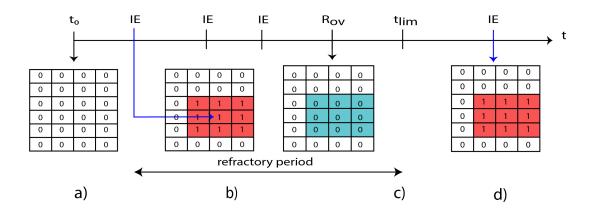

|   |      | 4.4.1.1 Refractory period mechanism                                                                                                                             |

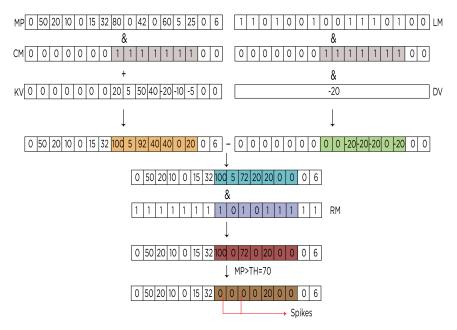

|   |      | 4.4.1.2 Convolution Engine V2                                                                                                                                   |

|   | 4.5  |                                                                                                                                                                 |

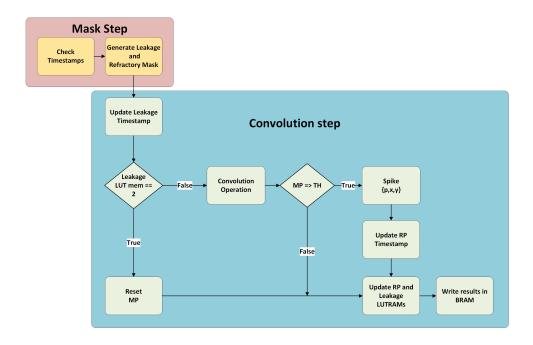

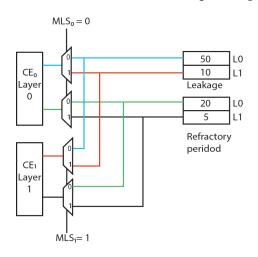

|   |      | 4.5.1 Layer mask selector module                                                                                                                                |

|   |      | 4.5.2 Cycle output system                                                                                                                                       |

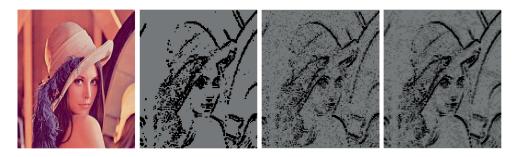

|   | 4.6  | Frame-based to event-based image conversion                                                                                                                     |

|   |      | 4.6.0.1 Scan algorithm                                                                                                                                          |

|   |      | 4.6.0.2 Random algorithm                                                                                                                                        |

|   |      | 4.6.0.3 Bitwise algorithm                                                                                                                                       |

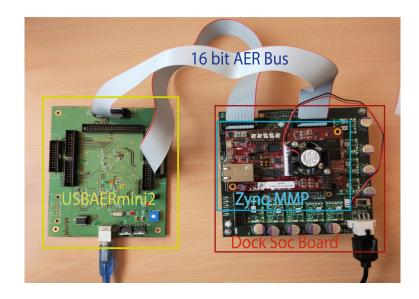

|   | 4.7  | Hardware implementation                                                                                                                                         |

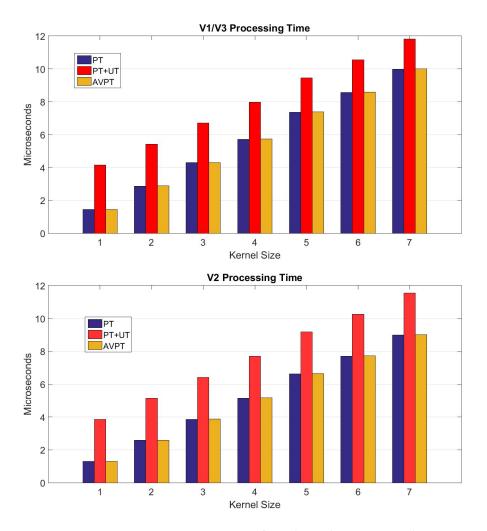

|   | 4.8  | Benchmark scenarios                                                                                                                                             |

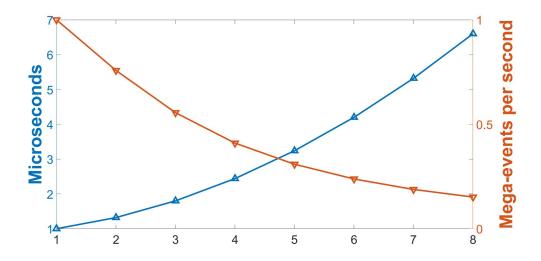

|   | 1.0  | 4.8.1 Slow-Poker processing test                                                                                                                                |

|   |      | 4.8.2 Fast-dot processing test                                                                                                                                  |

|   |      | 4.8.3 Analysis and comparison                                                                                                                                   |

|   | 4.9  | Summary and discussion                                                                                                                                          |

|   |      | ,                                                                                                                                                               |

|   |      |                                                                                                                                                                 |

| 5  | Patte | ern Rec | ognition  | Based on Time Surfaces in Real Time    | 65 |

|----|-------|---------|-----------|----------------------------------------|----|

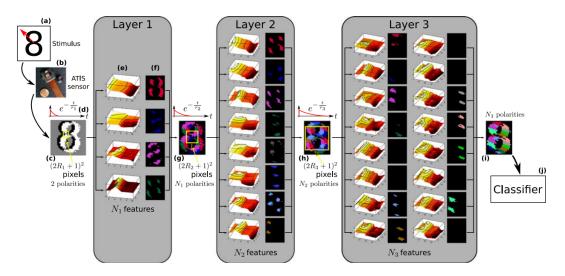

|    | 5.1   | Hierar  | chy of th | e time surface algorithm               | 66 |

|    |       | 5.1.1   | Time su   | rface                                  | 66 |

|    |       | 5.1.2   | Hierarch  | nical time surface network             | 67 |

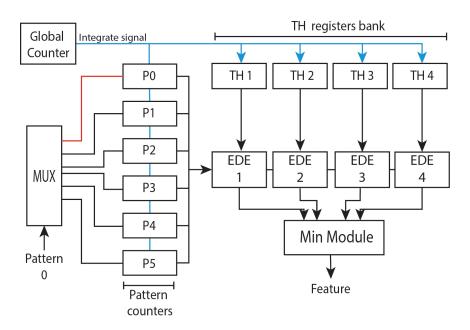

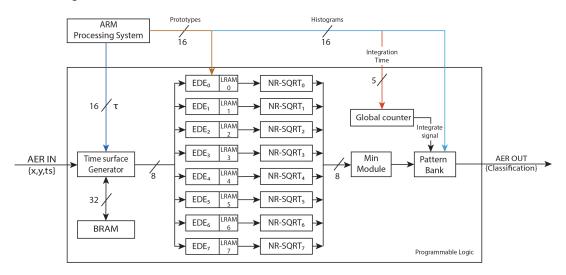

|    | 5.2   | FPGA    | HOTS ac   | celerator                              | 68 |

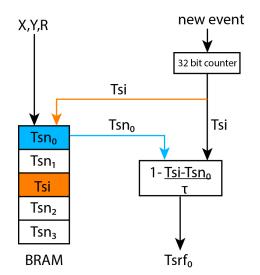

|    |       | 5.2.1   | Time su:  | rface generator module                 | 69 |

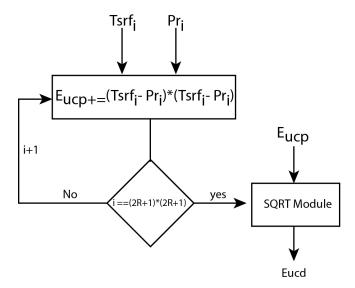

|    |       | 5.2.2   | Euclidea  | an distance estimator                  | 70 |

|    |       |         | 5.2.2.1   | Difference distance computation module | 71 |

|    |       |         | 5.2.2.2   | Babylonian square root module          | 71 |

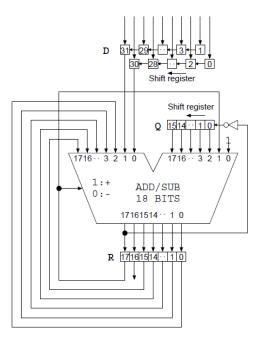

|    |       |         | 5.2.2.3   | Non-restoring square root module       | 71 |

|    |       | 5.2.3   | Histogra  | ams integration and compare modules    | 73 |

|    |       | 5.2.4   |           | re implementation                      | 74 |

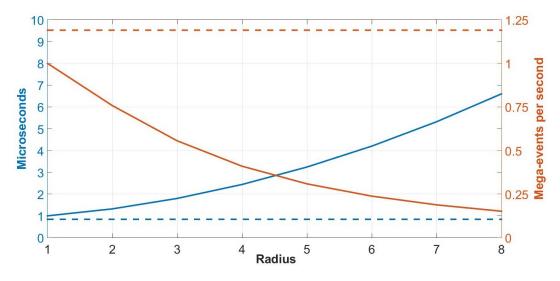

|    |       | 5.2.5   |           | nental results                         | 75 |

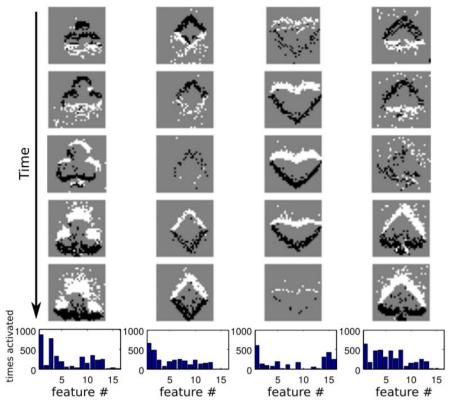

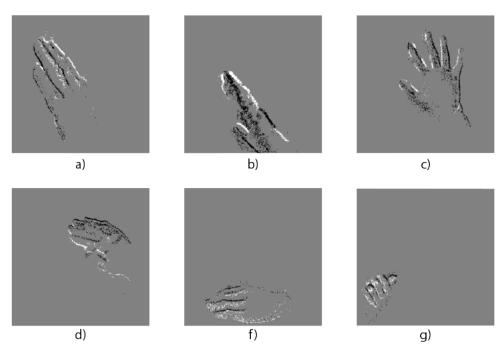

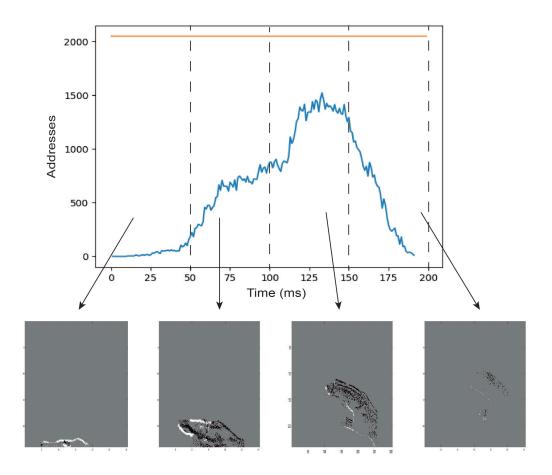

|    |       |         | 5.2.5.1   | Pattern recognition test               | 75 |

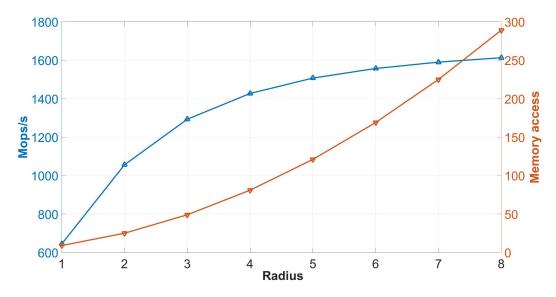

|    |       |         | 5.2.5.2   | Performance test                       | 77 |

|    |       | 5.2.6   | Compar    | ison and discussion                    | 79 |

|    | 5.3   | Event-  | based tin | ne configurable memory                 | 80 |

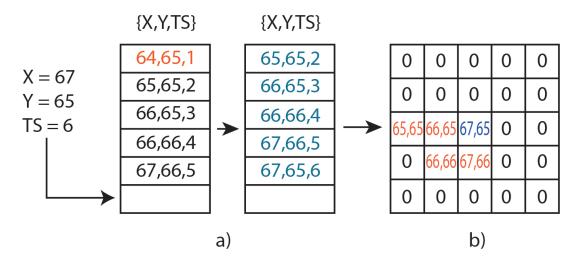

|    |       | 5.3.1   |           | 7 Model                                | 81 |

|    |       | 5.3.2   |           | plementation                           | 82 |

|    |       |         | 5.3.2.1   | -                                      | 82 |

|    |       |         | 5.3.2.2   | Parallel read memory model             | 83 |

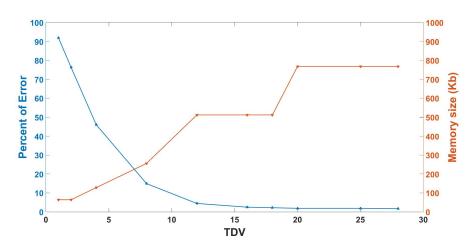

|    |       | 5.3.3   | Experim   | nents and Results                      | 83 |

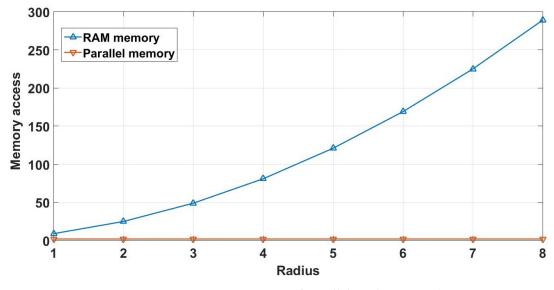

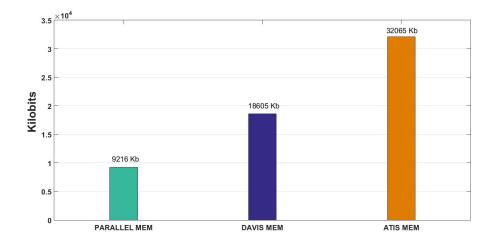

|    |       |         | 5.3.3.1   | One-layer experiment                   | 83 |

|    |       |         | 5.3.3.2   | Multi-layer experiment                 | 85 |

|    | 5.4   | Summ    | ary and l | Discussion                             | 86 |

| 6  | Con   | clusion | s and Fu  | ture works                             | 89 |

|    | 6.1   | Conclu  | isions .  |                                        | 90 |

|    | 6.2   |         |           |                                        | 92 |

|    | 6.3   |         |           |                                        | 93 |

| Bi | bliog | raphy   |           |                                        | 95 |

# **List of Figures**

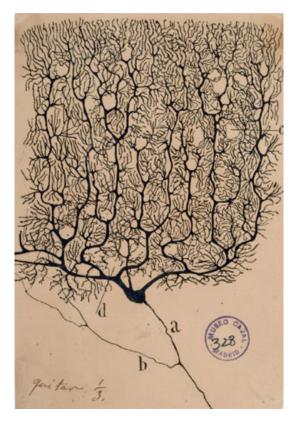

| 1.1        | Neuronal model drawn by Santiago Ramón y Cajal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

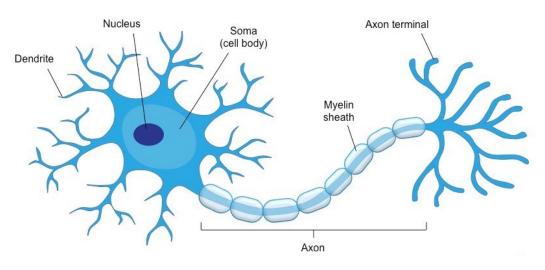

| 1.2        | Biological neuron structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7        |

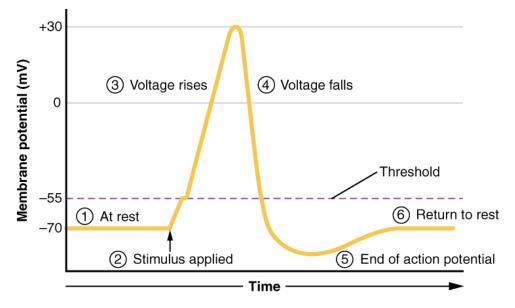

| 1.3        | Diagram of a spike generated by a neuron.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7        |

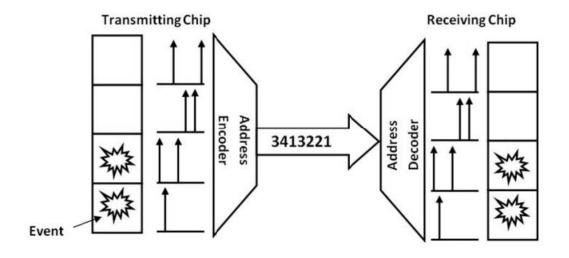

| 1.4        | AER protocol diagram. Image taken from (Liu et al., 2014)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9        |

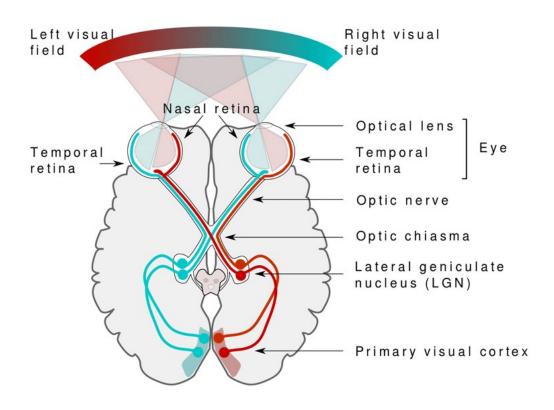

| 1.5        | Neural vision system structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11       |

| 1.6        | The world's first photograph (left) and a photograph of the Hubble                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|            | telescope (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12       |

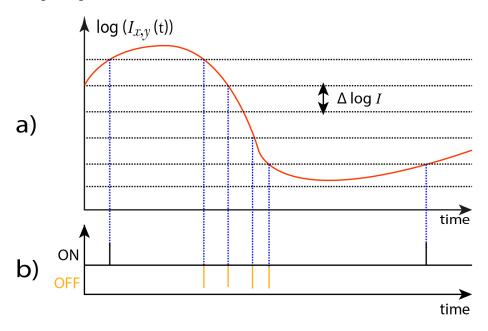

| 1.7        | ATIS operation principles. When a pixel's luminosity change reaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|            | a given threshold (a), it produces a visual event with an (x, y) address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|            | and a polarity, which is either ON or OFF (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14       |

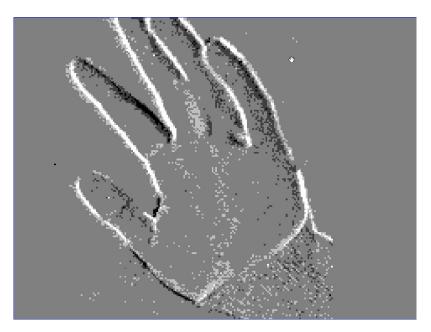

| 1.8        | jAER capture of DVS sensor events.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15       |

| 1.9        | Origami accelerator architecture. Image taken from (Cavigelli and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|            | Benini, 2017)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17       |

| 1.10       | Eyeriss accelerator architecture. Image taken from (Chen et al., 2017).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18       |

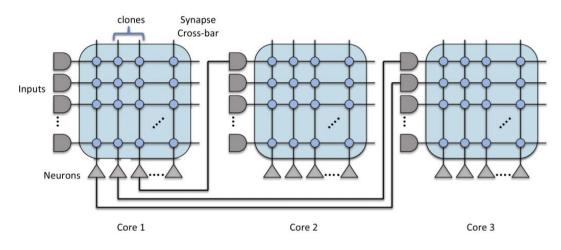

| 1.11       | IBM TrueNorth architecture. Image taken from (Akopyan et al., 2015).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19       |

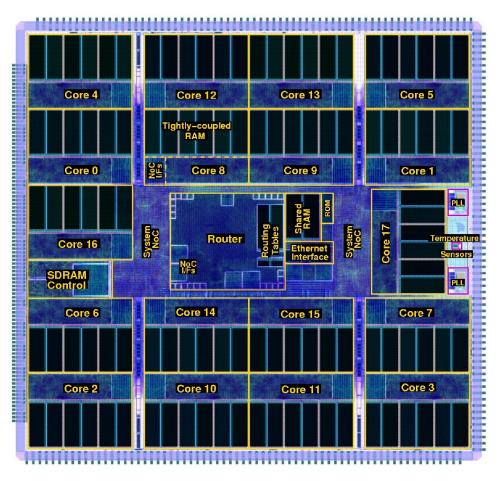

|            | Spinnaker platform layout. Image taken from (Yousefzadeh et al., 2018).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20       |

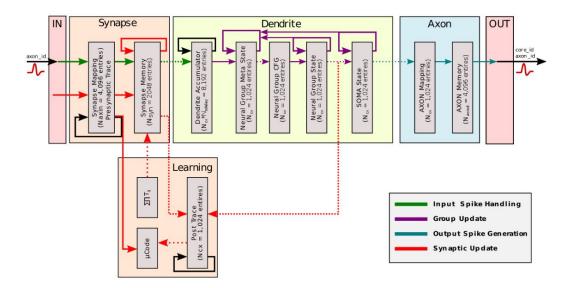

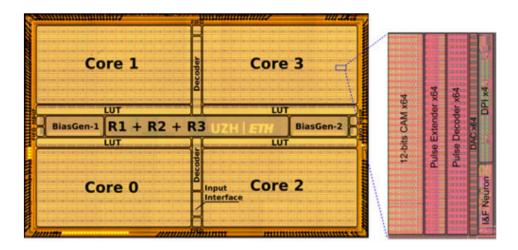

| 1.13       | Intel Loihi core structure. Image taken from (Lin et al., 2018)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21       |

| 1.14       | DYNAP platform layout. Image taken from (Moradi et al., 2018)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21       |

| 0.1        | Marca and the second seco | 20       |

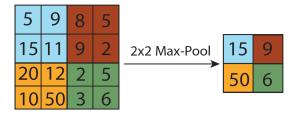

| 3.1        | Max-pooling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28       |

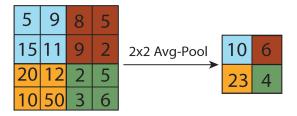

| 3.2        | Avg-pooling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29       |

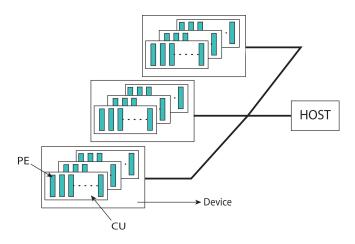

| 3.3        | OpenCL platform model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30       |

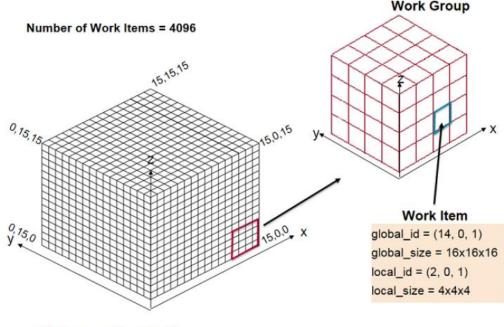

| 3.4<br>2 E | OpenCL index space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31       |

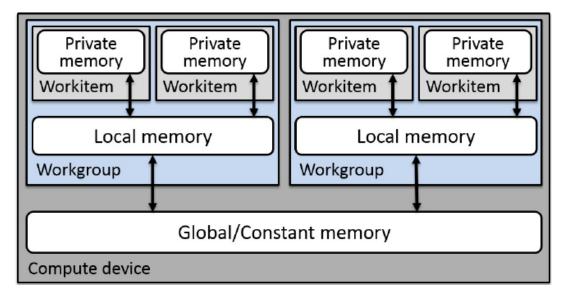

| 3.5        | OpenCL device memory model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32       |

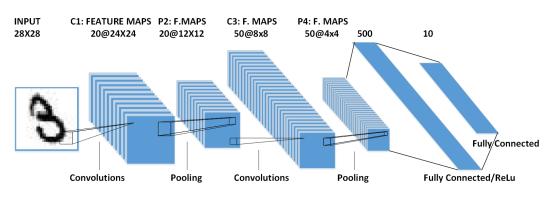

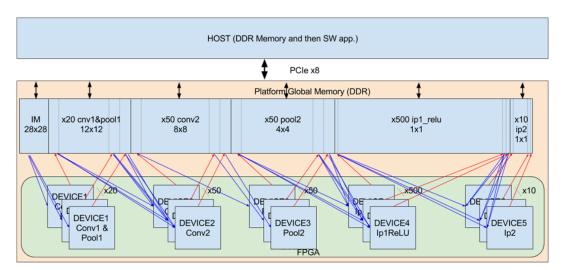

| 3.6        | LeNet5 network architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33       |

| 3.7        | LeNet5 OpenCL implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33       |

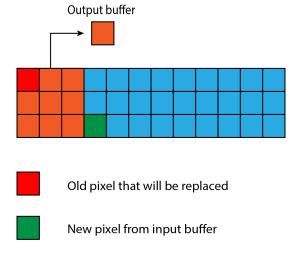

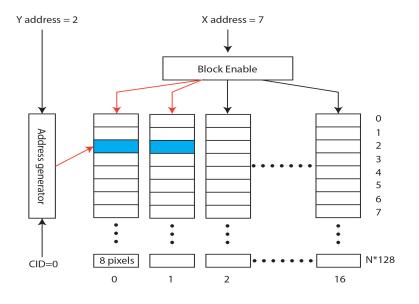

| 3.8        | Input/output data sequencing by rows in a CNN accelerator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35       |

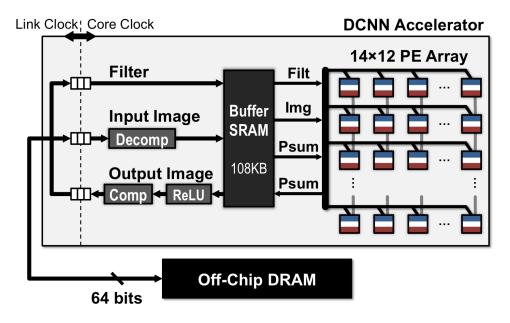

| 3.9        | NN-X architecture. Image taken from (Gokhale et al., 2014)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35       |

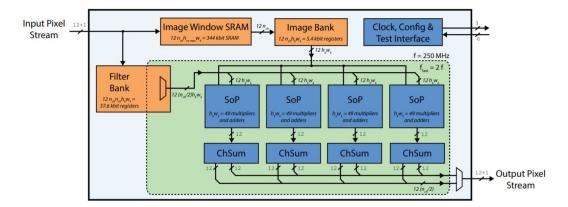

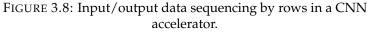

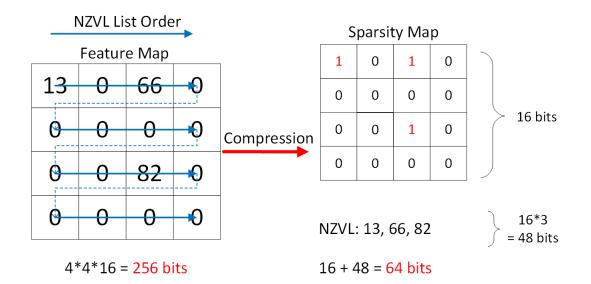

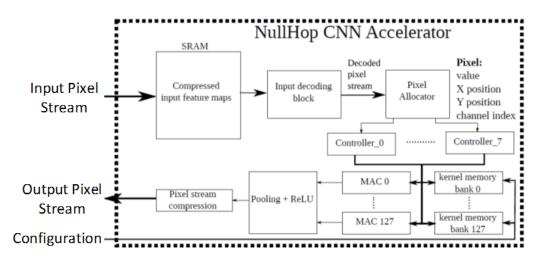

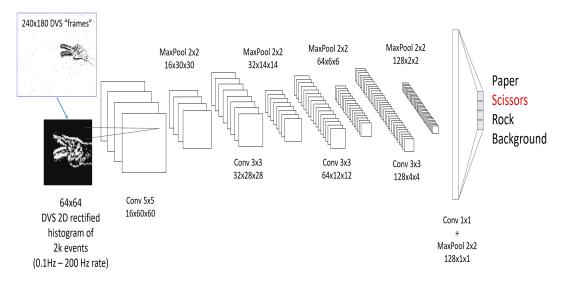

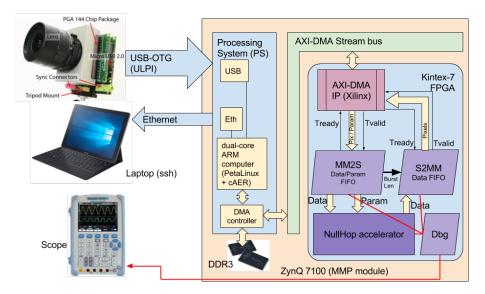

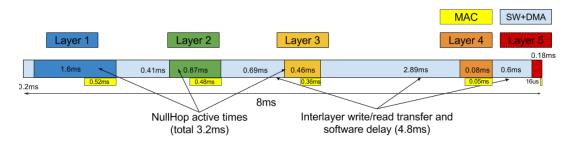

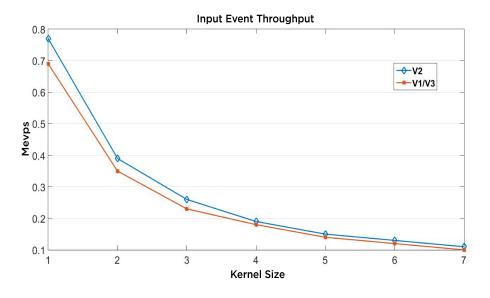

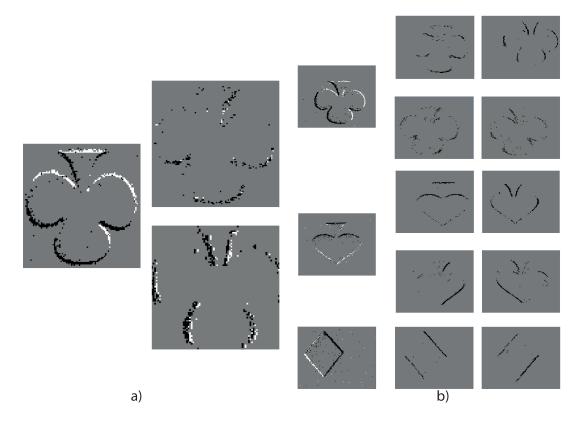

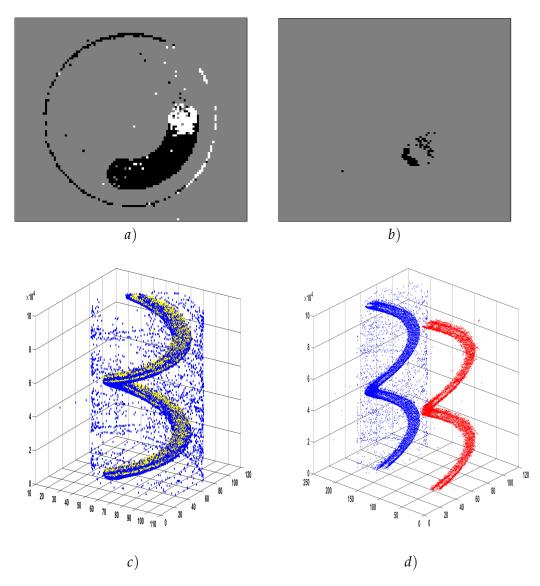

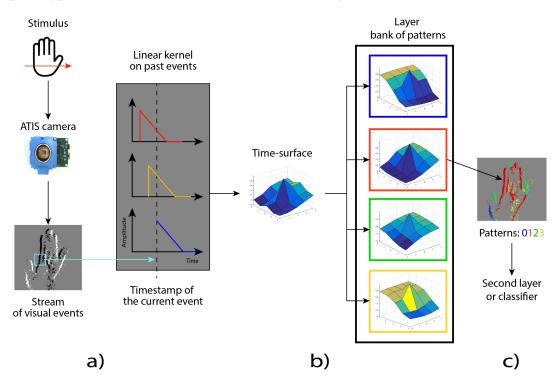

| 3.10       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36<br>37 |