# Energy-Detecting Receivers for Wake-Up Radio Applications

Vivek Mangal

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY 2020

© 2019

Vivek Mangal

All Rights Reserved

# **Abstract**

# Energy-Detecting Receivers for Wake-Up Radio Applications

# Vivek Mangal

In an energy-limited wireless sensor node application, the main transceiver for communication has to operate in deep sleep mode when inactive to prolong the node battery lifetime. Wake-up is among the most efficient scheme which uses an always ON low-power receiver called the wake-up receiver to turn ON the main receiver when required. Energy-detecting receivers are the best fit for such low power operations. This thesis discusses the energy-detecting receiver design; challenges; techniques to enhance sensitivity, selectivity; and multi-access operation.

Self-mixers instead of the conventional envelope detectors are proposed and proved to be optimal for signal detection in these energy-detection receivers. A fully integrated wake-up receiver using the self-mixer in 65 nm LP CMOS technology has a sensitivity of -79.1 dBm at 434 MHz. With scaling, time-encoded signal processing leveraging switching speeds have become attractive. Baseband circuits employing time-encoded matched filter and comparator with DC offset compensation loop are used to operate the receiver at 420 pW power. Another prototype at 1.016 GHz is sensitive to -74 dBm signal while consuming 470 pW. The proposed architecture has 8 dB better sensitivity at 10 dB lower power consumption across receiver prototypes.

Sensitivity and selectivity in an energy-detector first architecture is limited by characteristics of the front-end matching network. Further enhancement in sensitivity is proposed using the concept of interferer as LO, effectively operating as a direct down-conversion receiver. A wake-up receiver prototype in  $0.13 \,\mu m$  CMOS operates at  $550 \, MHz$ , consumes  $220 \, nW$  from  $0.5 \, V$ , and achieves a sensitivity of  $-56.4 \, dBm$  at a  $400 \, kb/s$  chip rate using an 11-bit wake-up code. When a large interferer is present, the receiver operates in an interferer-enhanced mode, leveraging the interferer as a local oscillator to improve the sensitivity; in the presence of a  $-43.5 \, dBm$  interferer, a  $-63.6 \, dBm$

sensitivity is achieved while consuming  $1.1 \mu W$ . The architecture has 10 dB better selectivity for PM/FM interferer, but still gets blocked in the presence of a wide-band AM interferer.

Next, we propose a clockless continuous-time analog correlator to enhance the selectivity to such wide-band AM interferers. The architecture uses pulse-position-encoded analog signal processing with VCOs as integrators and pulse-controlled relaxation delays; it operates as a code-domain matched filter to de-spread asynchronous wake-up codes. A correlator prototype is designed in 65 nm LP CMOS technology, consumes 37 nW from 0.54 V, and performs code-domain filtering for an 11-bit Barker code. The receiver has  $-80.9\,\mathrm{dBm}$  sensitivity at 40 nW power consumption. A 5 dB improved selectivity to AM interference thanks to the correlator is demonstrated. This code-domain matched filtering also provides selectivity to unwanted codes to enable code-division multiple access (CDMA). A selective response to two different codes is presented, demonstrating CDMA for wake-up receivers.

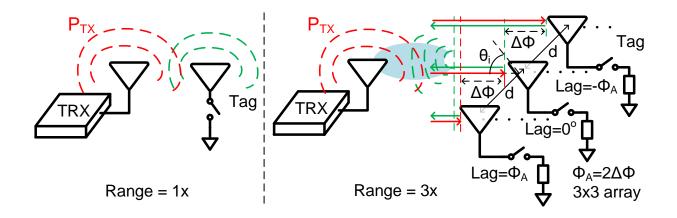

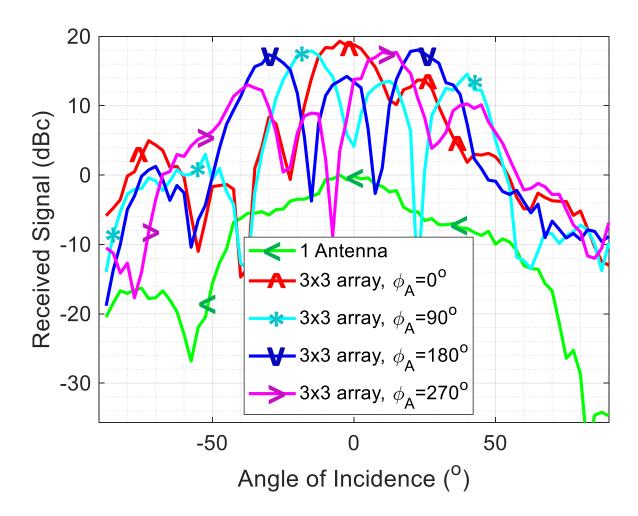

Further enhancement in the link can be achieved using directional antennas, providing spatial gain and selectivity. However, increasing antenna directivity requires a high antenna aperture which is infeasible. Certain applications can leverage a nearby reflector to enhance the directivity. A proof-of-concept directional backscatter tag is proposed to act as a reflector. The tag uses multiple antennas acting as a reflectarray by configuring constant phase gradients depending on the direction of arrival (DoA) of the signal. The DoA is determined using RSSI measurements across different tag reflection configuration. A directional backscatter tag using a 3x3 antenna array with passive loads is implemented. It provides a 19 dB sensitivity enhancement resulting in an up to 3x increase in range compared to backscatter communications with a single antenna tag. This almost-passive tag can operate as a reflectarray for the wake-up receiver to enhance the link.

To sum up, scavenging energy has been studied widely for battery-less applications. However, the same energy and surrounding environment can be leveraged to enhance functionality (e.g. interferer as LO, using a reflector on a wall) to enhance low power operation. Innovations spanning both circuit and system architectures that leverage the ambient energy and environment to enable power-efficient solutions for next-generation wake-up radios are presented in this work.

# **Table of Contents**

| List of T | ables .  |                                           | ⁄ii |

|-----------|----------|-------------------------------------------|-----|

| List of F | igures . |                                           | iii |

| Acknow    | ledgme   | nts                                       | iv  |

| Chapter   | 1: Intr  | roduction                                 | 1   |

| 1.1       | Wake-    | Up Radio                                  | 1   |

|           | 1.1.1    | Wake-Up Latency                           | 3   |

|           | 1.1.2    | False-Alarm Rate                          | 3   |

|           | 1.1.3    | Battery Lifetime                          | 3   |

|           | 1.1.4    | Form Factor                               | 4   |

|           | 1.1.5    | Range                                     | 4   |

| 1.2       | Archit   | ectures for Sub-μW Radios                 | 5   |

|           | 1.2.1    | Duty-Cycled Active RF Amplifier           | 9   |

|           | 1.2.2    | Passive RF Energy-Detecting Receivers     | 10  |

|           | 1.2.3    | Performance Tradeoffs                     | 15  |

|           | 1.2.4    | Selectivity in Energy-Detecting Receivers | 15  |

| 1.3       | Thesis   | Organization                              | 16  |

| Chapter | 2: Noi  | se Analysis for Energy-Detecting Receivers      | 18 |

|---------|---------|-------------------------------------------------|----|

| 2.1     | Noise . | Analysis                                        | 18 |

| 2.2     | Passivo | e Energy Detector Model                         | 20 |

| 2.3     | Sensiti | vity Analysis                                   | 22 |

|         | 2.3.1   | Antenna noise mixed with itself dominates       | 22 |

|         | 2.3.2   | Antenna noise mixed with input signal dominates | 22 |

|         | 2.3.3   | Noise added by the energy detector dominates    | 23 |

| 2.4     | Limite  | d Front-End Passive Gain                        | 24 |

| 2.5     | Optimi  | izing for Sensitivity                           | 26 |

| Chapter | 3: Self | f-Mixers                                        | 28 |

| 3.1     | Self-M  | fixer Operation Principle                       | 28 |

|         | 3.1.1   | Achieving High Enough Resistance                | 29 |

|         | 3.1.2   | Minimizing Capacitance                          | 29 |

|         | 3.1.3   | Conversion Gain and Noise of the Self-Mixer     | 30 |

|         | 3.1.4   | Satisfying Requirements for Optimal Sensitivity | 31 |

| 3.2     | Single  | -Ended RF Input Self-Mixer                      | 31 |

|         | 3.2.1   | Operation of a Single-Stage Self-Mixer          | 31 |

|         | 3.2.2   | Multi-Stage Self-Mixer                          | 33 |

| 3.3     | Differe | ential RF Input Self-Mixer                      | 34 |

|         | 3.3.1   | Operation of a 1-Transistor Self-Mixer          | 34 |

|         | 3.3.2   | Characteristics of a Multi-Stage Self Mixer     | 35 |

|         | 3.3.3   | Biasing Circuit                                 | 36 |

| 3.4     | Impact  | t of Multiple Stages                                                           | 37 |

|---------|---------|--------------------------------------------------------------------------------|----|

|         | 3.4.1   | Sensitivity                                                                    | 37 |

|         | 3.4.2   | Bandwidth                                                                      | 38 |

|         | 3.4.3   | Baseband Power Consumption                                                     | 38 |

| 3.5     | Compa   | arison Between Different Self-Mixers                                           | 38 |

| Chapter | :4: A S | ub-nW Wake-Up Receiver using Self-Mixer                                        | 40 |

| 4.1     | Receiv  | rer Architecture                                                               | 40 |

| 4.2     | Front-  | End Design using Self-Mixer                                                    | 41 |

|         | 4.2.1   | Conversion Gain and Noise of the Self-Mixer                                    | 42 |

|         | 4.2.2   | Gate-Leakage Compensation and Biasing Circuit                                  | 42 |

| 4.3     | Receiv  | rer Prototype Implementation                                                   | 44 |

|         | 4.3.1   | RF Front End                                                                   | 44 |

|         | 4.3.2   | Baseband Voltage Amplifier                                                     | 46 |

|         | 4.3.3   | Baseband Signal Processing with Time-Encoded Signals                           | 46 |

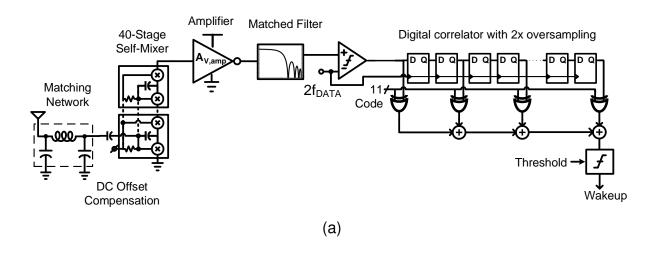

|         | 4.3.4   | Digital Correlator                                                             | 49 |

|         | 4.3.5   | Delay-Locked Loop for DC Feedback                                              | 49 |

| 4.4     | Power   | Consumption Limit                                                              | 51 |

|         | 4.4.1   | Noise Contribution of the Amplifier                                            | 51 |

|         | 4.4.2   | Jitter Contribution from the Voltage-Controlled Delay Line                     | 51 |

|         | 4.4.3   | Jitter Contribution from the Delay Cells that Control the Comparator Threshold | 53 |

|         | 4.4.4   | Threshold Requirement for Low False Alarm                                      | 53 |

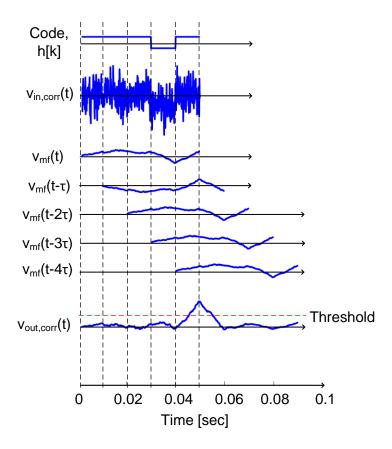

|         | 4.4.5   | SNR Required to Achieve a Desired Missed Detection Ratio                       | 54 |

| 4.5     | Measu   | rement Results                                                               | 55 |

|---------|---------|------------------------------------------------------------------------------|----|

| 4.6     | Conclu  | nsions                                                                       | 57 |

| Chapter | 5: Enh  | nancing Sensitivity and Selectivity in Passive-RF Energy-Detecting Receivers | 60 |

| 5.1     | Interfe | rer as LO                                                                    | 60 |

|         | 5.1.1   | Operation with a Continuous-Wave Interferer                                  | 61 |

|         | 5.1.2   | Operation with a PM/FM Interferer                                            | 62 |

|         | 5.1.3   | Operation with an AM Interferer                                              | 63 |

|         | 5.1.4   | Potential Interferers to the Receiver                                        | 65 |

|         | 5.1.5   | Limitations on Enhanced Sensitivity                                          | 65 |

| 5.2     | Receiv  | rer Architecture and Implementation                                          | 66 |

|         | 5.2.1   | Baseband Implementation - LF-Path                                            | 67 |

|         | 5.2.2   | Circuit Implementation - HF-Path                                             | 69 |

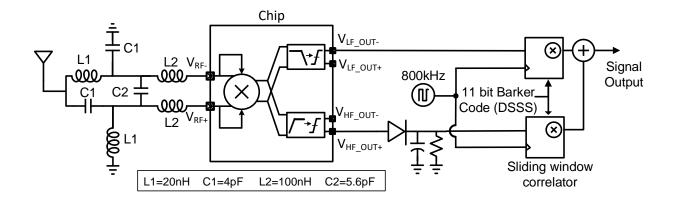

|         | 5.2.3   | Digital Demodulation and Correlation with the Barker Code                    | 70 |

|         | 5.2.4   | Operation in the Presence of Multiple Interferers                            | 71 |

| 5.3     | Experi  | mental results                                                               | 73 |

|         | 5.3.1   | Regular Operation through the LF Path                                        | 73 |

|         | 5.3.2   | Interferer-Enhanced Operation through the HF Path                            | 74 |

| 5.4     | Conclu  | asion                                                                        | 76 |

| Chapter | 6: CD   | MA using Continuous-Time Analog Correlator                                   | 77 |

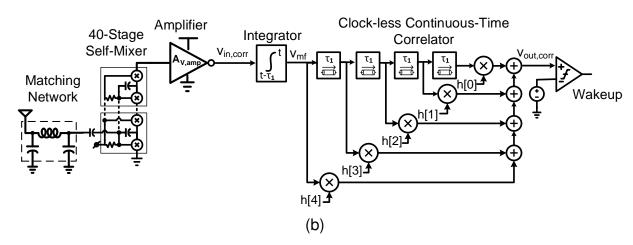

| 6.1     | Clockl  | ess, Analog Correlators vs Clocked, Digital Correlators                      | 79 |

|         | 6.1.1   | Processing Gain                                                              | 79 |

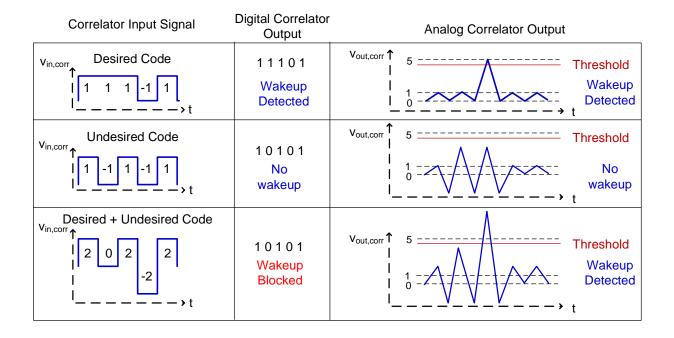

|         | 6.1.2   | Code-Domain Selectivity                                                      | 80 |

|     | 6.1.3  | Required SNR for MDR $\leq 10^{-3}$             | . 81  |

|-----|--------|-------------------------------------------------|-------|

|     | 6.1.4  | Code-Division Multiple Access                   | . 83  |

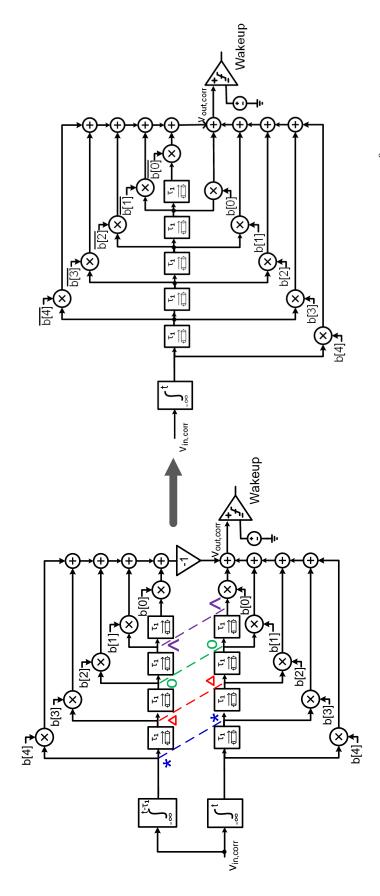

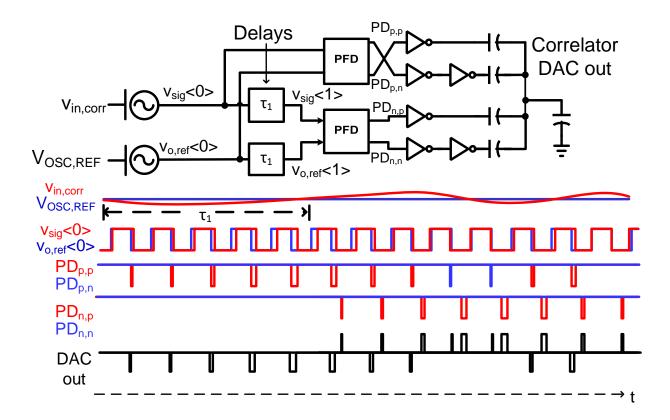

| 6.2 | CT An  | nalog Correlator Circuit Implementation         | . 84  |

|     | 6.2.1  | Matched Filter for a Single Rectangular Bit     | . 86  |

|     | 6.2.2  | Matched Filter for an 11-Bit Code               | . 87  |

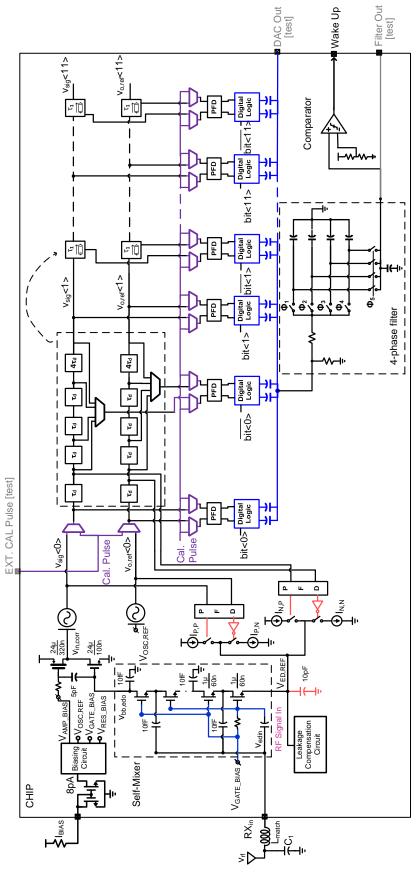

| 6.3 | Systen | m Implementation                                | . 89  |

|     | 6.3.1  | RF Front End                                    | . 89  |

|     | 6.3.2  | Baseband Voltage Amplifier                      | . 90  |

|     | 6.3.3  | Voltage Controlled Oscillators                  | . 90  |

|     | 6.3.4  | Phase-Locked Loop                               | . 90  |

|     | 6.3.5  | Delay Cell Design                               | . 92  |

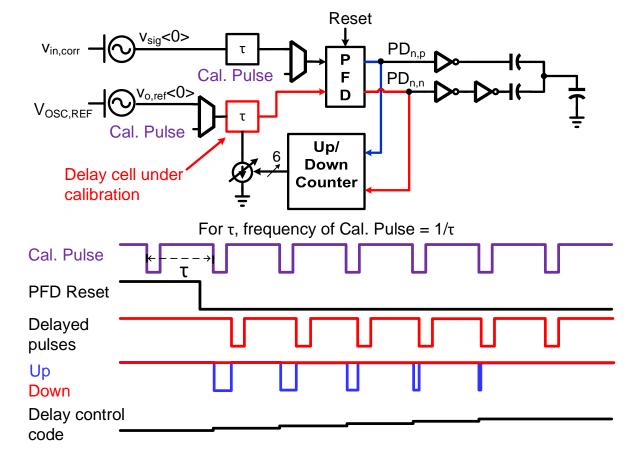

|     | 6.3.6  | Delay-Cell Calibration                          | . 94  |

|     | 6.3.7  | Four-Phase Filter                               | . 95  |

| 6.4 | Design | n Considerations in the Receiver and Correlator | . 95  |

|     | 6.4.1  | Noise                                           | . 95  |

|     | 6.4.2  | VCO Frequency                                   | . 96  |

|     | 6.4.3  | Delay Drift                                     | . 96  |

|     | 6.4.4  | Dynamic Range                                   | . 97  |

|     | 6.4.5  | Non-Linearity                                   | . 98  |

| 6.5 | Measu  | rement Results                                  | . 98  |

|     | 6.5.1  | Correlator Characteristics                      | . 98  |

|     | 6.5.2  | Wake-Up Receiver Sensitivity and Selectivity    | . 98  |

|     | 6.5.3  | CDMA Operation                                  | . 102 |

|         | 6.5.4   | Comparison to the State of the Art              | 102 |

|---------|---------|-------------------------------------------------|-----|

| 6.6     | Concl   | usions                                          | 102 |

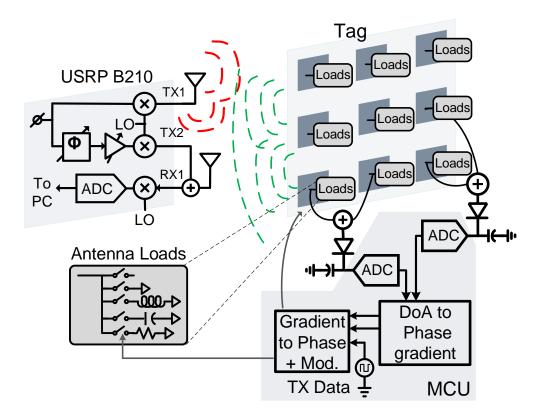

| Chapter | 7: Dire | ectional Backscatter Tags                       | 107 |

| 7.1     | Directi | onal Backscatter Tag                            | 109 |

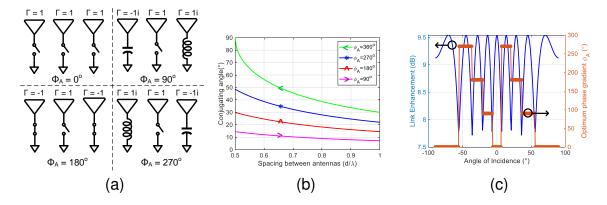

|         | 7.1.1   | Directional Backscattering in a Linear Array    | 109 |

|         | 7.1.2   | Directional Backscattering in an NxN Array      | 109 |

|         | 7.1.3   | Directional Backscattering with QPSK modulation | 110 |

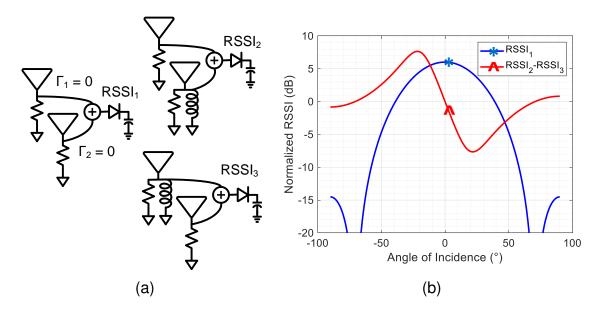

|         | 7.1.4   | Compact DoA Estimation using RSSI               | 110 |

| 7.2     | Design  | of a Proof-of-Principle Demo System             | 110 |

|         | 7.2.1   | Tag Hardware                                    | 111 |

|         | 7.2.2   | Full-Duplex Reader Transceiver using USRP       | 112 |

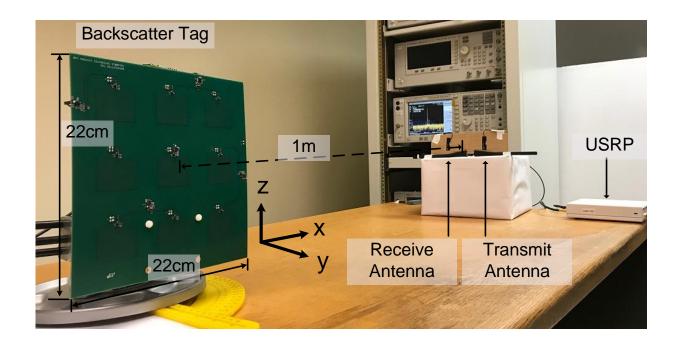

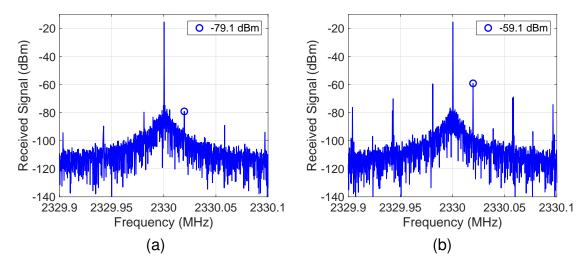

| 7.3     | Measu   | rement Setup and Results                        | 113 |

| 7.4     | Future  | Work                                            | 115 |

| 7.5     | Conclu  | nsions                                          | 117 |

| Chapter | 8: Con  | aclusion and Future Directions                  | 118 |

| Dafaran | 225     |                                                 | 124 |

# **List of Tables**

| 4.1 | Comparison between different receiver architectures for IoE                        | 58  |

|-----|------------------------------------------------------------------------------------|-----|

| 6.1 | Comparison with the state-of-the-art ED wake-up receivers operating at > 400 MHz . | 105 |

# **List of Figures**

| 1.1 | Different applications of a wake-up radio                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | A generic wake-up radio communication protocol                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

| 1.3 | Noise contributions in energy-detector based wake-up receivers                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

| 1.4 | Wake-Up receiver RF front-ends using (a) an uncertain LO architecture; (b) a duty-cycled Active RF; (c) passive energy detector; and (d) an active energy detector                                                                                                                                                                                                                                                                                                            | 7  |

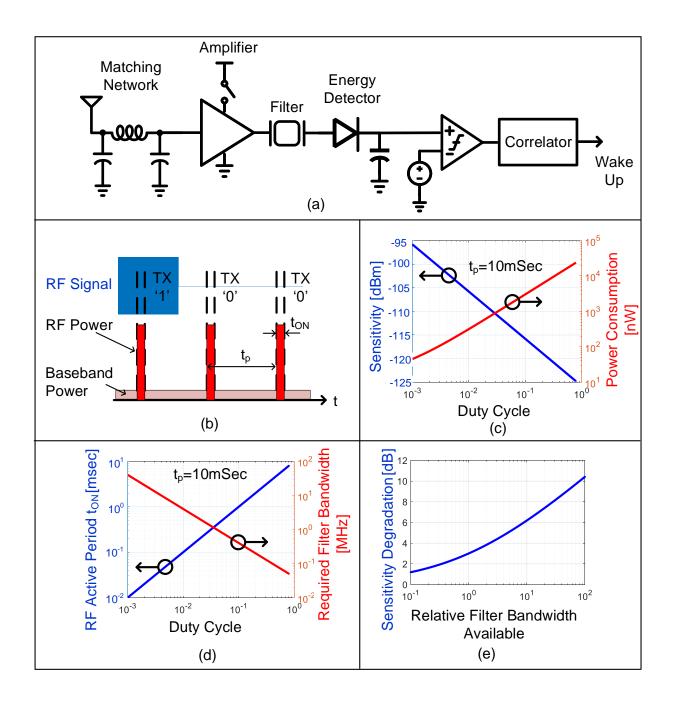

| 1.5 | (a) A receiver architecture using a duty-cycled active RF amplification [19], (b) the operation principle and the power consumption profile for the receiver, (c) sensitivity and power consumption trade-off based on duty-cycle ratio $t_{ON}/t_p$ assuming a very low RF front-end bandwidth $BW_{RF}$ , (d) the required front-end RF filter bandwidth for a 3-dB degradation in sensitivity, and (e) the sensitivity degradation based on the excess RF filter bandwidth | 8  |

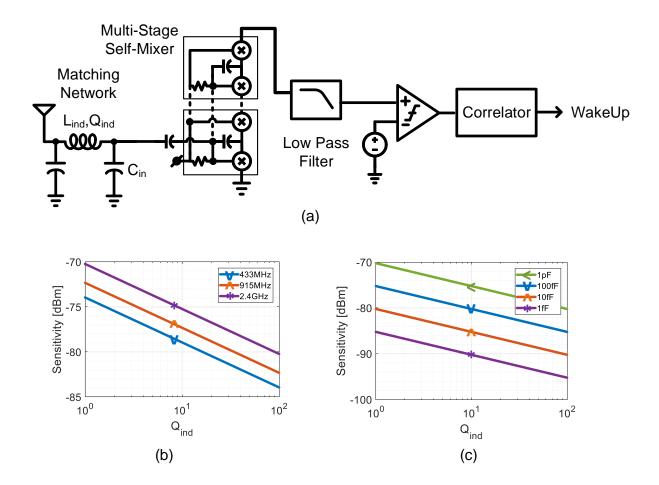

| 1.6 | (a) Passive-RF energy-detecting receiver architecture using a self-mixer, (b) achievable sensitivity at different ISM band frequencies with increasing quality factor $Q_{ind}$ , and (c) achievable sensitivity at 2.4 GHz with increasing quality factor $Q_{ind}$ across different matching network load capacitors                                                                                                                                                        | 12 |

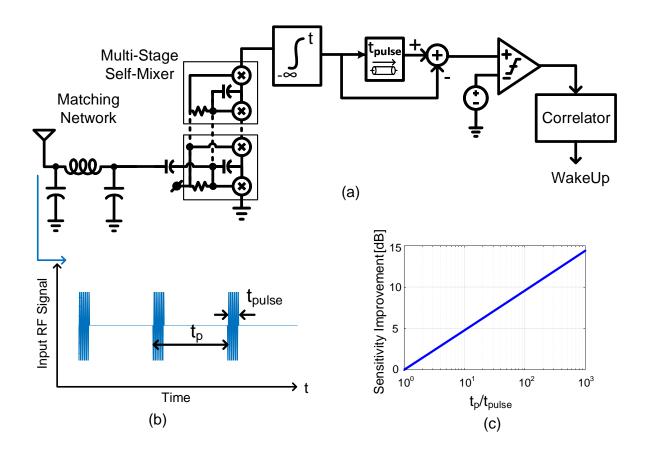

| 1.7 | (a) Receiver architecture to receiver a pulsed-input signal, (b) an example of a pulsed-input RF signal with active time $t_{pulse}$ for every bit period $t_p$ , and (c) the improvement in sensitivity compared to the achievable sensitivity in Fig. 1.6 as a function of $t_p/t_{pluse}$ .                                                                                                                                                                                | 14 |

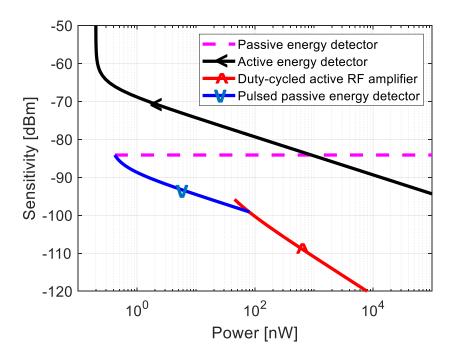

| 1.8 | Performance trade-offs energy detector based wake-up receivers                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 2.1 | Small-signal model including noise sources for an ED receiver; the spectra of signal and noise at the input and the output of the energy detector are also shown                                                                                                                                                                                                                                                                                                              | 19 |

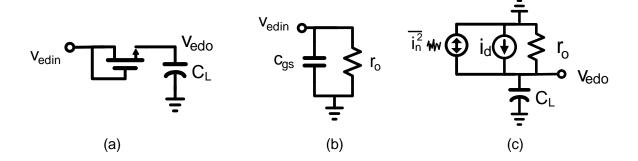

| 2.2 | (a) An energy detector using a diode connected transistor, (b) the equivalent small-signal model at $f_{rf}$ , and (c) the equivalent small-signal model at baseband frequency.                                                                                                                                                                                                                                                                                               | 21 |

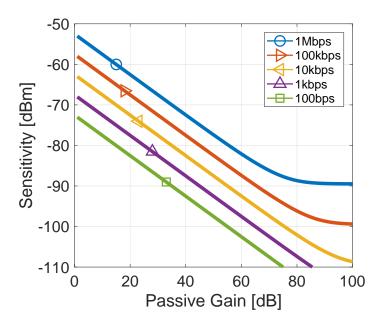

| 2.3 | Sensitivity of the energy-detector receiver for increasing passive gain from the matching network at different desired data rates for a 12.3 dB SNR required at the output of the energy detector                                       | 24 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

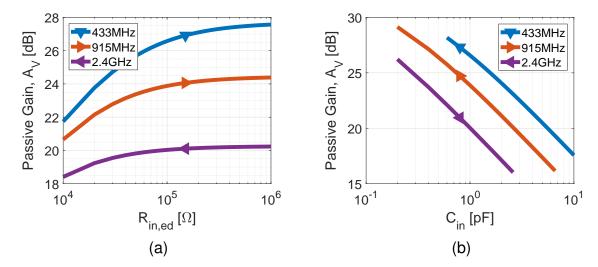

| 2.4 | (a) Passive gain variation with the input resistance at an $C_{in} = 1 \mathrm{pF}$ ; (b) Passive gain variation with input capacitance at an $R_{in,ed} = 100 \mathrm{k}\Omega$ at different ISM band frequencies for an inductor Q=80 | 25 |

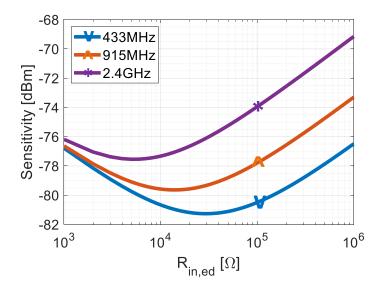

| 2.5 | Achievable receiver sensitivity for a continuous-wave RF input signal as a function of the self-mixer input resistance $R_{in,ed}$ assuming $Q_{ind}$ =80, $C_{in}$ =1 pF, $BW_{BB}$ =200 Hz, $SNR_{req}$ =12.4 dB                      | 26 |

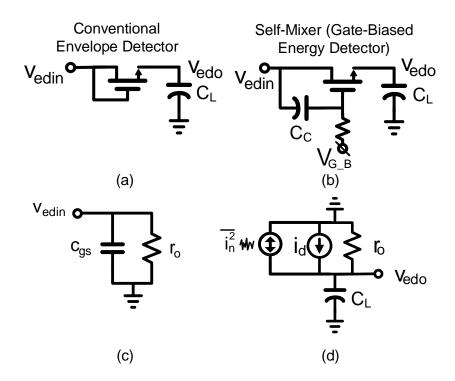

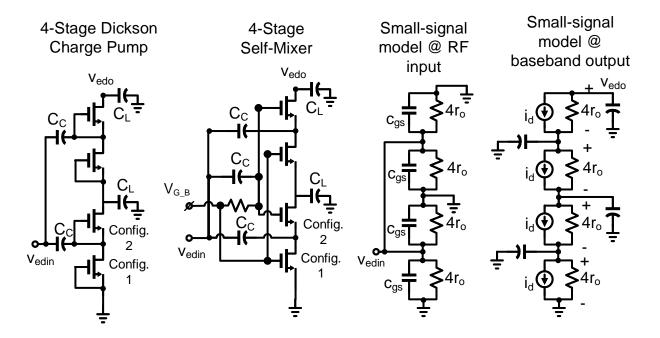

| 3.1 | (a) A conventional envelope detector, (b) one-stage self-mixer, (c) self-mixer small-signal model at RF frequency, (d) and the small-signal model at baseband frequency.                                                                | 29 |

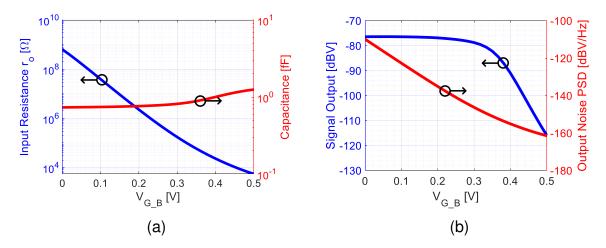

| 3.2 | (a) ED input resistance, capacitance and (b) conversion gain at 5mV RF input signal and noise power spectral density at 100 Hz with increasing $V_{G\_B}$                                                                               | 30 |

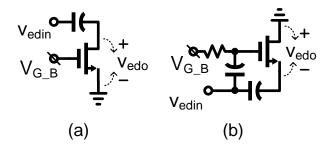

| 3.3 | 1-stage self-mixer configurations for a single-ended self-mixer design                                                                                                                                                                  | 32 |

| 3.4 | Different operating configuration of transistors in a multi-stage self-mixer inspired from Dickson charge pump.                                                                                                                         | 33 |

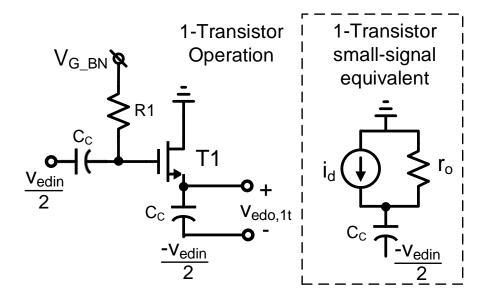

| 3.5 | One-transistor self-mixer operation and it's small-signal model equivalent                                                                                                                                                              | 34 |

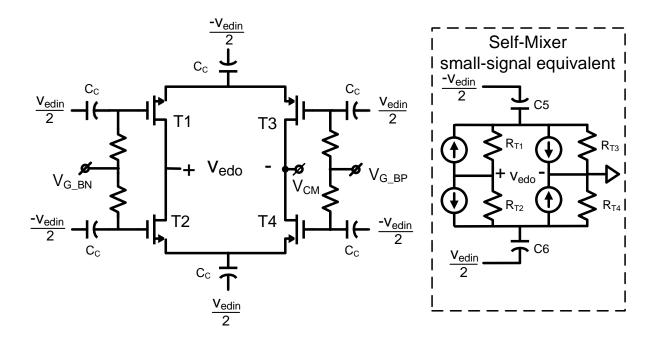

| 3.6 | One-stage self-mixer circuit and its small-signal equivalent by combining an NMOS pair and a PMOS pair one-transistor self-mixer shown in Fig. 3.5                                                                                      | 36 |

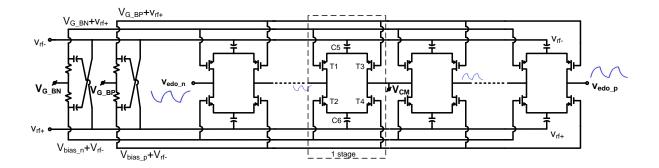

| 3.7 | Proposed multi-stage self-mixer architecture by cascading a 1-stage self-mixer shown in Fig. 3.6. Here, $v_{rf} = v_{edin}/2$                                                                                                           | 37 |

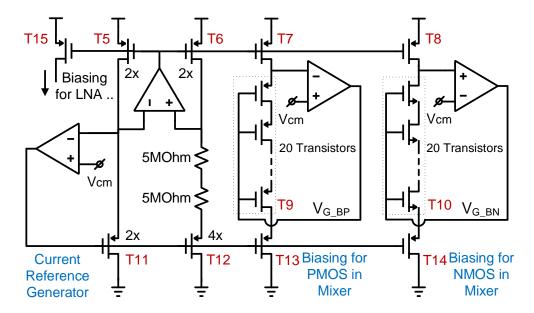

| 3.8 | Biasing circuit generating $V_{bias\_p}$ and $V_{bias\_n}$ for self-mixer (Fig. 3.7) and PTAT current reference for baseband circuits                                                                                                   | 37 |

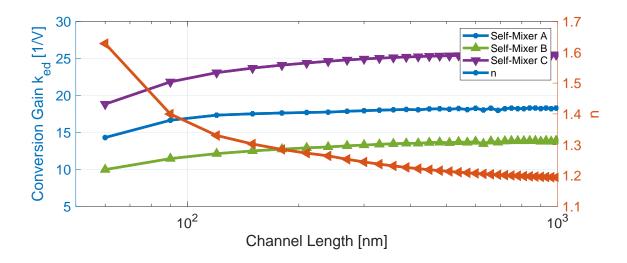

| 3.9 | Simulated conversion gain constant $k_{ed}$ as a function of the channel length for self-mixer A and B shown in Fig. 3.3 and self-mixer C shown in Fig. 3.6 implemented in 65 nm CMOS LP technology                                     | 39 |

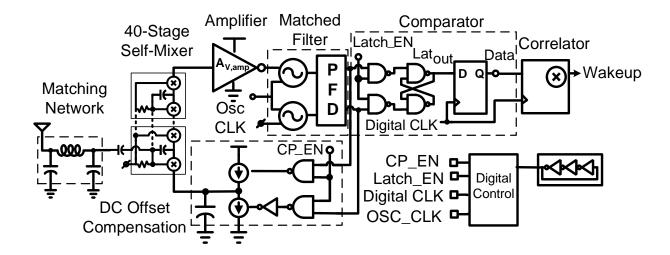

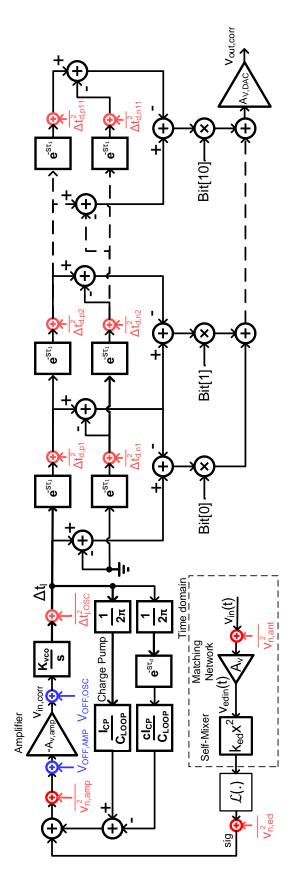

| 4.1 | Proposed architecture using self-mixers and a baseband consisting of a matched filter, DC offset compensation and comparator implemented with time-encoded analog signals followed by a correlator.                                     | 41 |

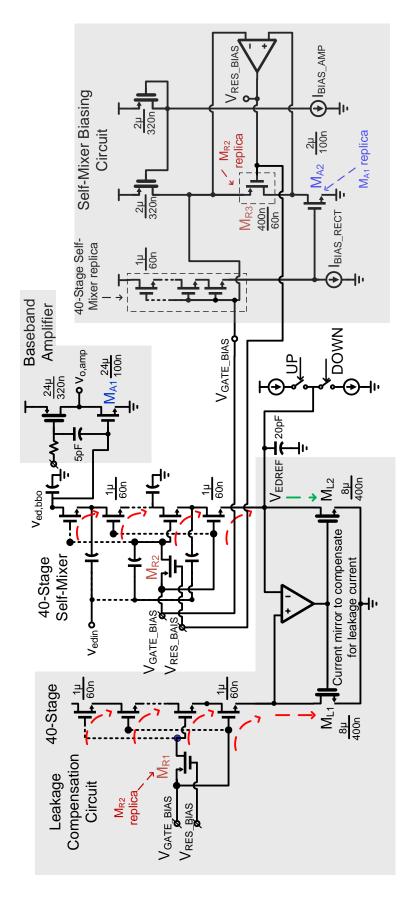

| 4.2  | gate-leakage compensation circuit details. Here, transistors $M_{R1} - M_{R3}$ operate as resistors                                                                                                                                                                                                                                                                                                                                   | 43 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

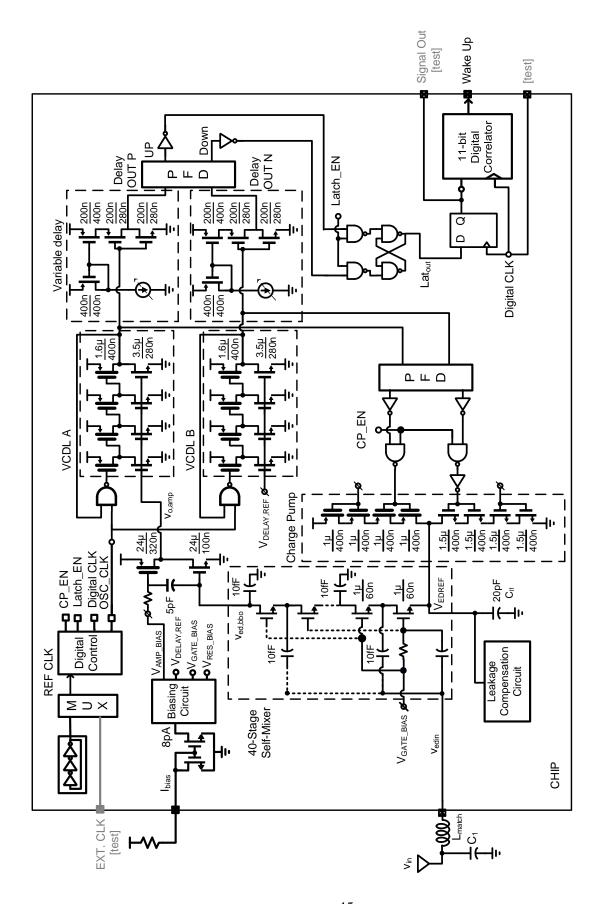

| 4.3  | System architecture with self-mixer, voltage-controlled delay lines (VCDL), charge-pump, variable delay including transistor-level implementation details                                                                                                                                                                                                                                                                             | 45 |

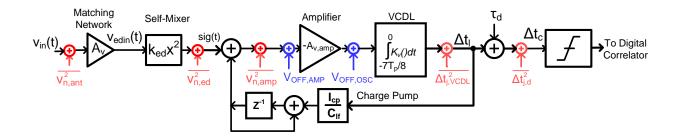

| 4.4  | Multi-domain model of the proposed receiver with added DC offsets and noise from the receiver chain                                                                                                                                                                                                                                                                                                                                   | 46 |

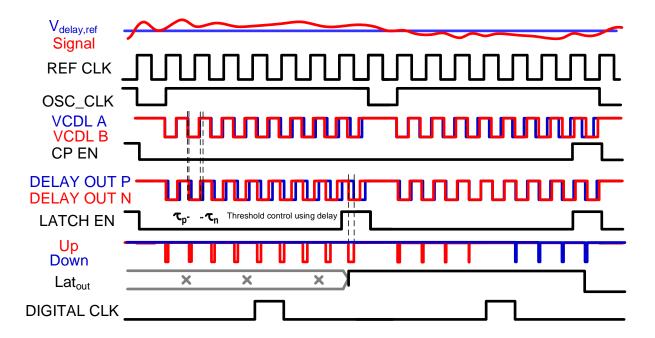

| 4.5  | Operation of the Integrator and comparator using time-encoded signals with VCDLs, SR latch and current starved inverter delay cells                                                                                                                                                                                                                                                                                                   | 47 |

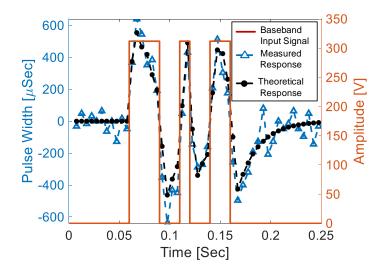

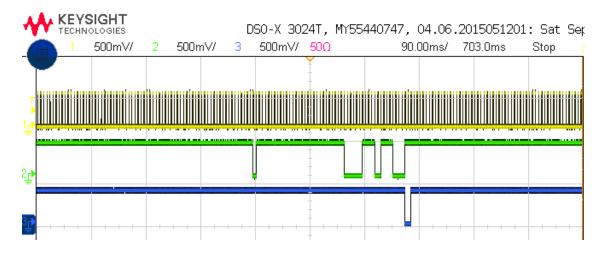

| 4.6  | Theoretical and measured receiver transient response for a -75 dBm RF input signal modulated with the baseband input signal for the 1.016 GHz prototype                                                                                                                                                                                                                                                                               | 50 |

| 4.7  | Time-domain response to a $-79\mathrm{dBm}$ wakeup signal for 434 MHz receiver prototype demonstrating appropriate threshold for low false alarm $< 1/Hr$                                                                                                                                                                                                                                                                             | 54 |

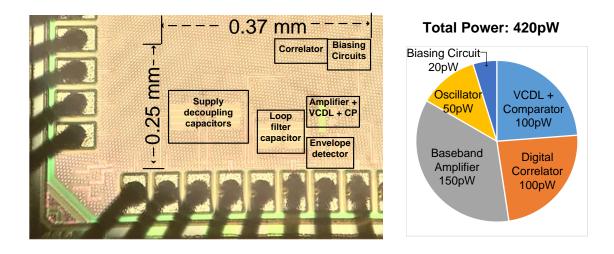

| 4.8  | DIE micrograph and power consumption distribution for receiver prototype at 434 MHz.                                                                                                                                                                                                                                                                                                                                                  | 55 |

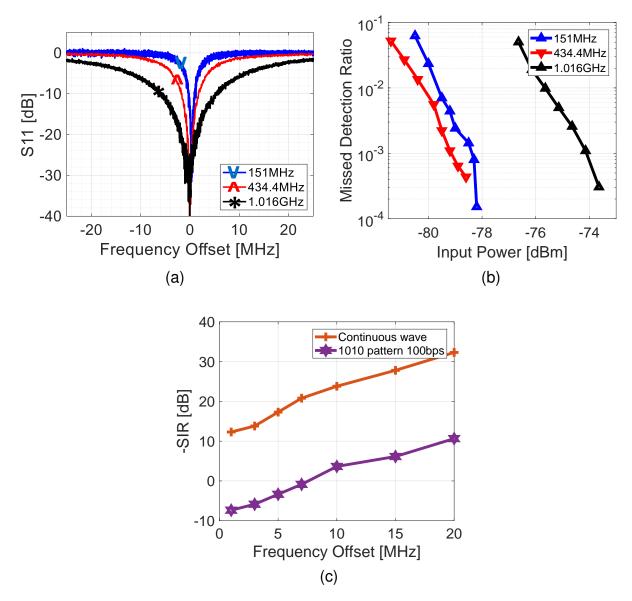

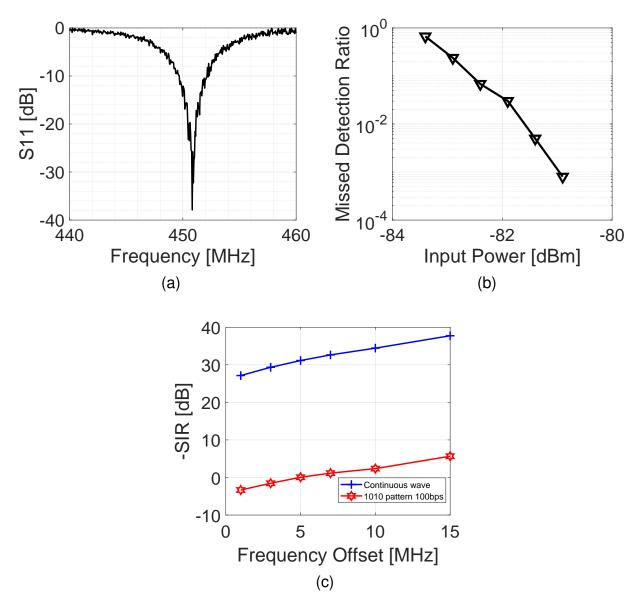

| 4.9  | (a) Input reflection at 434 MHz and 151 MHz; (b) Missed detection ratio for the receiver at 434 MHz; (c) and Signal-to-interference rejection ratio at 434 MHz for a continuous as well as a worst case AM interferer.                                                                                                                                                                                                                | 56 |

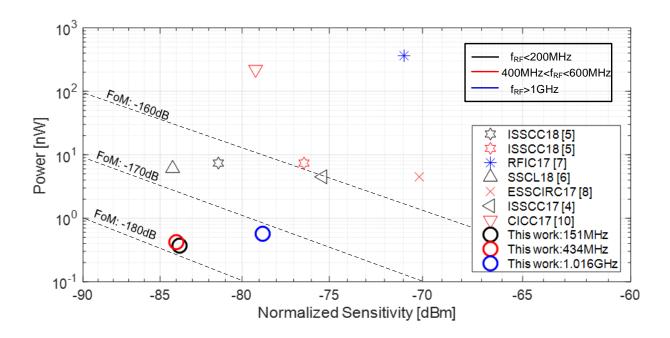

| 4.10 | Receiver performance comparison to the state of the art using normalized sensitivity and FoM described in [24, 34]                                                                                                                                                                                                                                                                                                                    | 59 |

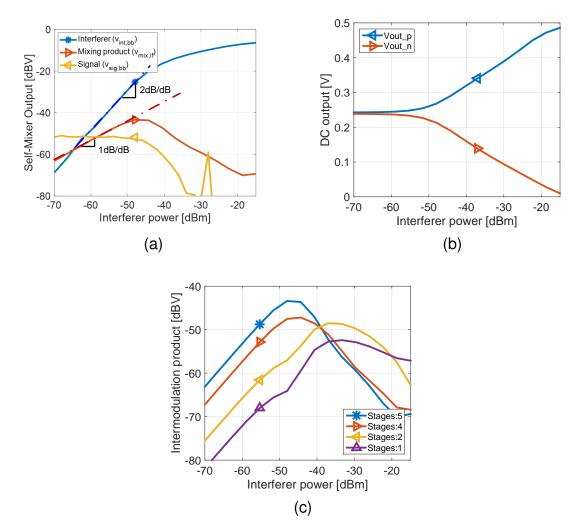

| 5.1  | For an increasing continuous-wave interferer level at 2MHz offset; (a) the simulated level of the components in the self-mixer output for with a $-60  \text{dBm}  400  \text{kbps}$ OOK input signal present; (b) the simulated DC-operating points at nodes $V_{out\_p}$ and $V_{out\_n}$ for self-mixer in Fig. 3.7; (c) and the simulated mixing product $v_{mix,if}$ at different number of stages in the self-mixer in Fig. 3.7 | 62 |

| 5.2  | Proposed receiver architecture implemented using the proposed multi-stage self-mixer and with an additional HF-path (bottom) for the interferer-enhanced operating mode with enhanced sensitivity and selectivity                                                                                                                                                                                                                     | 63 |

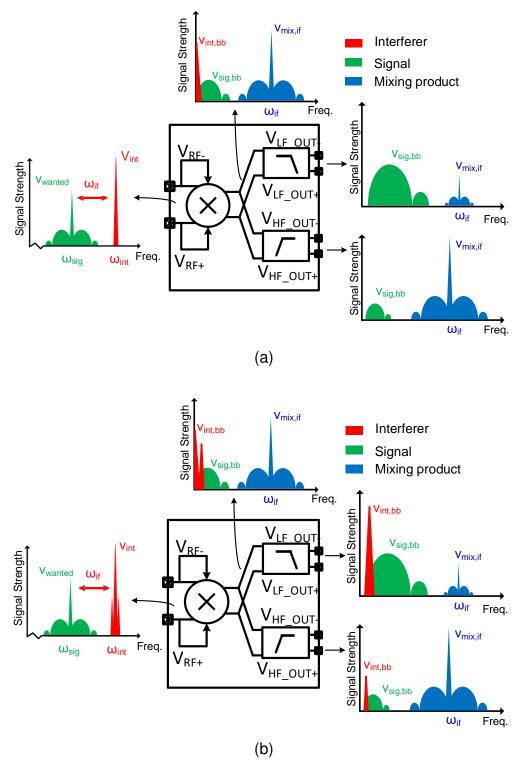

| 5.3  | Signal spectra in the receiver when (a) a narrowband carrier at an offset frequency $\omega_{if}$ and (b) an AM interferer at an offset frequency $\omega_{if}$ is present                                                                                                                                                                                                                                                            | 64 |

| 5.4  | Random 1-0 transmitted data pattern (middle); the LF signal (top) reflects the same pattern; the HF output (bottom) shows the same pattern on a 2 MHz IF carrier in the presence of a 10% AM interferer at 2 MHz offset                                                                                                                                                                                                               | 65 |

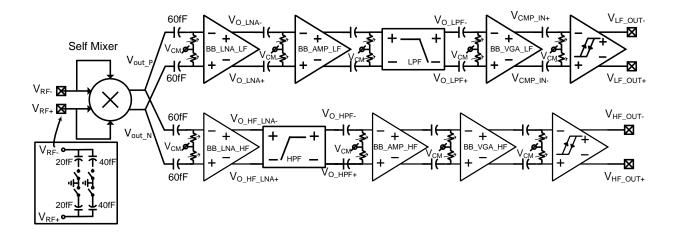

| 5.5  | Proposed on-chip receiver implementation with LF path (top) and HF path (bottom), 2-bit on-chip input capacitance tunability is provided for the matching network                                                                                                                                                                                                                                                 | 67 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

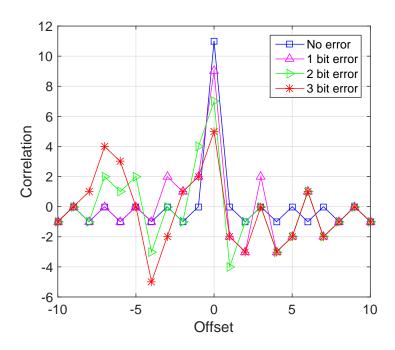

| 5.6  | (a) Circuit implementation of the baseband amplifiers, with sizing table for the different instantiations; (b) third order $g_m$ -C Chebyshev low-pass baseband filter with 1MHz cut-off frequency using C1=C3=64 fF, C2=13.6 fF and a unit $g_m$ of 30 nS; (c) third order $g_m$ -C Chebyshev high-pass baseband filter with 1MHz cut-off frequency using C4=C6=60 fF, C5=141 fF and a unit $g_m$ of 640 nS      | 68 |

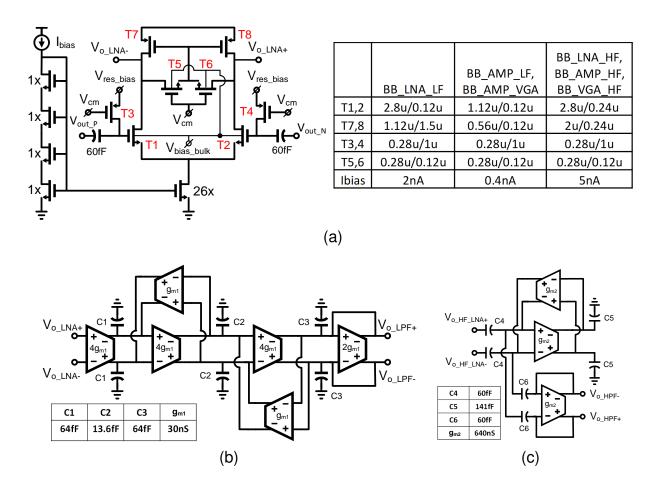

| 5.7  | Correlation between an ideal Barker code and a received Barker code with 1-bit, 2-bit and 3-bit errors at different code offsets. A 3-bit error leads to a symbol error with a correlation of -5.                                                                                                                                                                                                                 | 7( |

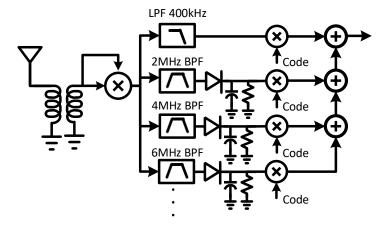

| 5.8  | System architecture for operation in the presence of multiple interferers                                                                                                                                                                                                                                                                                                                                         | 71 |

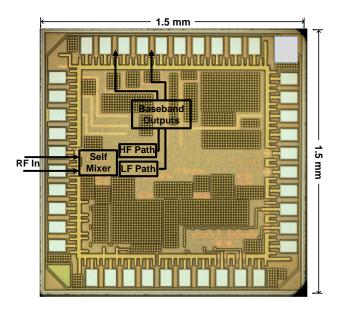

| 5.9  | Chip micrograph implementing the receiver prototype with an area of 0.2mm <sup>2</sup> in 130nm technology node                                                                                                                                                                                                                                                                                                   | 72 |

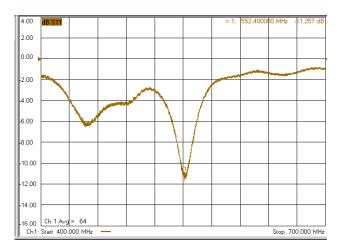

| 5.10 | Measured S11 of the designed energy-detection receiver, the receiver has a -4 dB RF bandwidth of 36 MHz                                                                                                                                                                                                                                                                                                           | 72 |

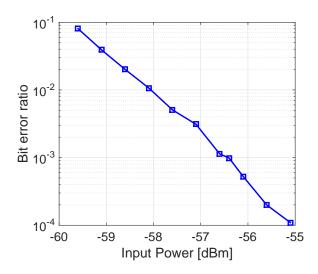

| 5.11 | Bit error ratio for varying input signal strength in regular operation through the LF path in the absence of interferers                                                                                                                                                                                                                                                                                          | 74 |

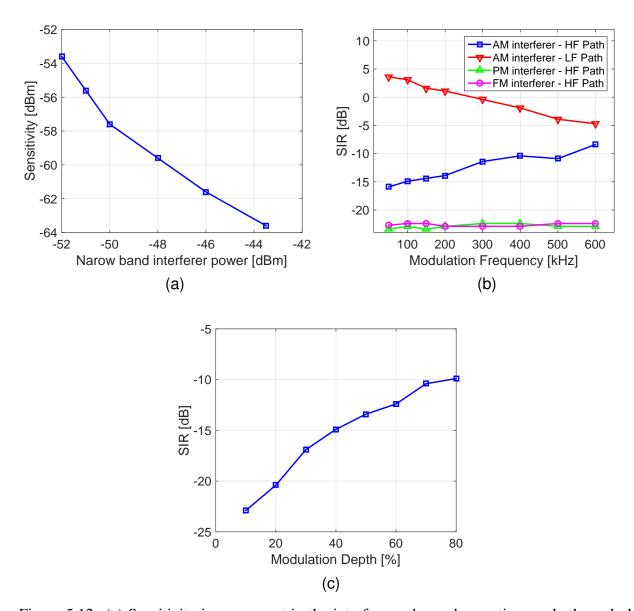

| 5.12 | (a) Sensitivity improvement in the interferer-enhanced operating mode through the HF path in the presence of a 250 kHz-PM interferer, sensitivity degrades with interferer power >-43 dBm; (b) signal-to-interferer ratio (SIR) for AM, PM, and FM interferers with varying modulation frequency of the interferer; (c) SIR for an AM interferer with a 250 kHz modulation bandwidth and varying modulation depth | 75 |

| 6.1  | A wake-up receiver architecture with (a) a digital correlator proposed in [28], (b) an analog correlator                                                                                                                                                                                                                                                                                                          | 78 |

| 6.2  | Operation of a 5-bit analog correlator in Fig. 6.1b to improve the sensitivity of the receiver                                                                                                                                                                                                                                                                                                                    | 80 |

| 6.3  | Response of a digital correlator and an analog correlator for a desired 5-bit Barker code, an undesired code '1,-1,1,-1,1' and a superposition of both                                                                                                                                                                                                                                                            | 81 |

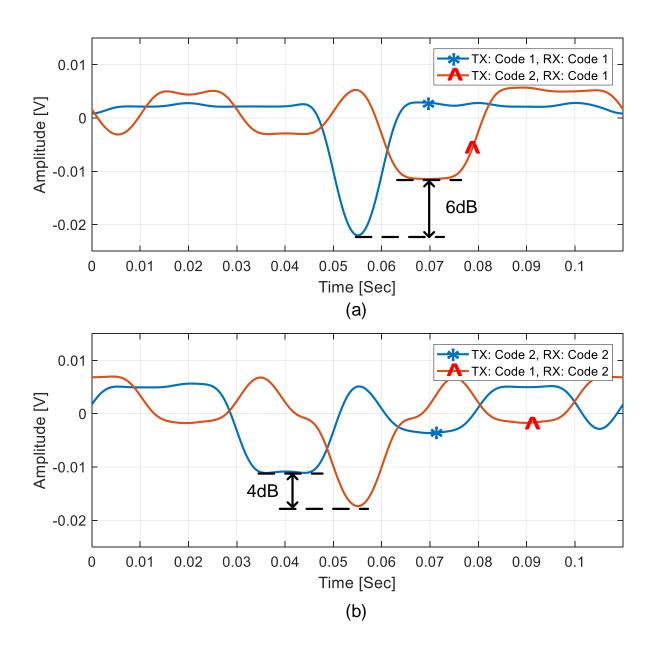

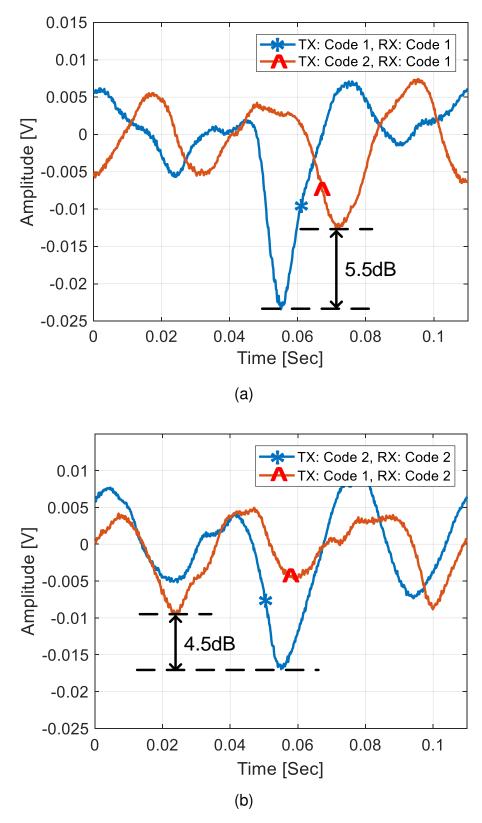

| 6.4  | Simulated responses of the analog correlator to <code1> and <code2>, when configured to receive (a) <code1> and (b) <code2>. Here <code1> is '11100010010' and <code2> is '11111001101'</code2></code1></code2></code1></code2></code1>                                                                                                                                                                           | 82 |

| 6.5  | Equivalent block diagram of a 5-bit analog correlator as in Fig. 6.1b, $\int_{-\infty}^{\infty}$ can be tapped from $\int_{-\infty}^{0}$ with a delay $\tau_1$                                                                                                                                                                                                                             | 85  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6  | Implementation and operation of a matched filter for 1-bit rectangular pulse                                                                                                                                                                                                                                                                                                               | 86  |

| 6.7  | Energy-detector wake-up receiver with a clockless analog correlator for matched filtering; the DC feedback loop through the gate-biased self-mixer and part of the baseband provides automatic biasing                                                                                                                                                                                     | 88  |

| 6.8  | Mixed-domain model with modeled noise and DC offsets for the receiver architecture in Fig. 6.7                                                                                                                                                                                                                                                                                             | 91  |

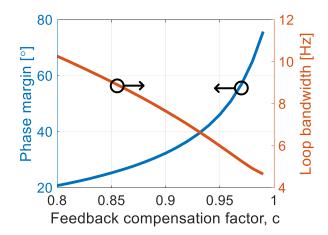

| 6.9  | Phase margin and loop bandwidth achieved using delay based compensation for a varying $c$                                                                                                                                                                                                                                                                                                  | 92  |

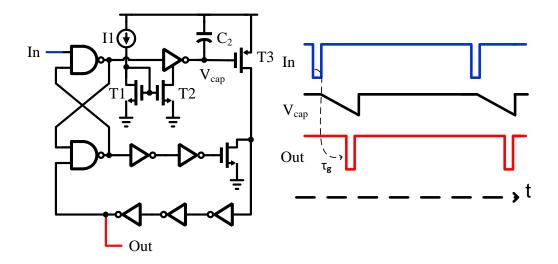

| 6.10 | Unit delay cell implementation providing a delay of $	au_g$                                                                                                                                                                                                                                                                                                                                | 93  |

| 6.11 | Calibration mechanism for delay cells                                                                                                                                                                                                                                                                                                                                                      | 94  |

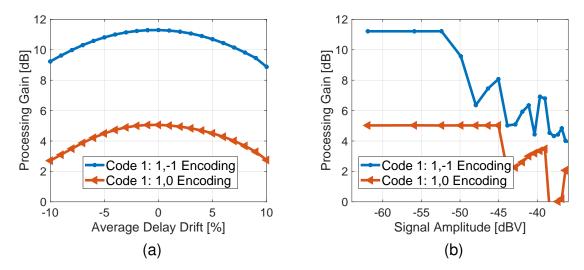

| 6.12 | The correlator processing gain degradation w.r.t. (a) variation in delay $\tau_1$ , (b) increasing input signal strength                                                                                                                                                                                                                                                                   | 97  |

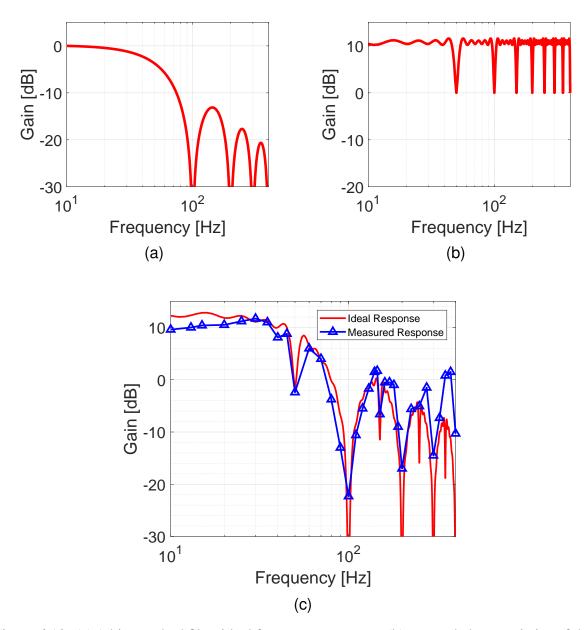

| 6.13 | (a) 1-bit matched filter ideal frequency response; (b) spectral characteristics of the 11-bit Barker code; and (c) ideal vs measured frequency response of the implemented 11-bit matched filter                                                                                                                                                                                           | 99  |

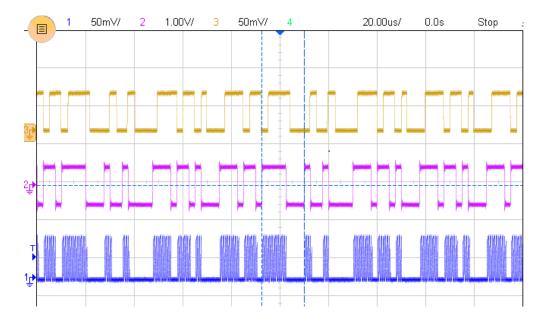

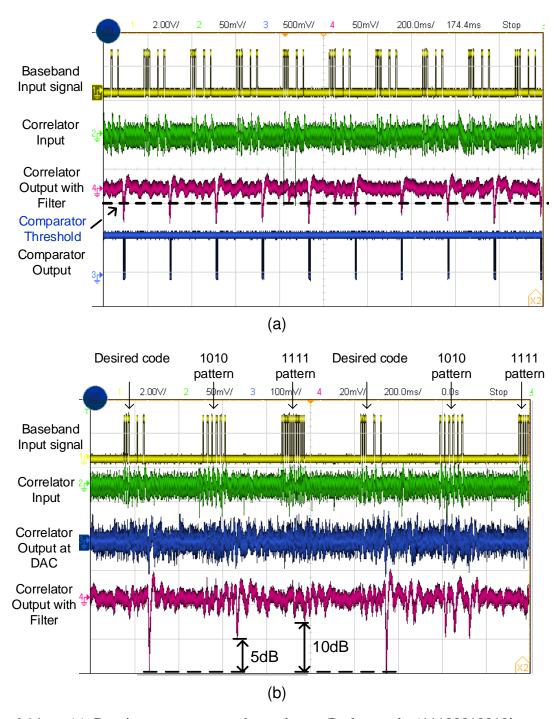

| 6.14 | (a) Receiver response to the wake-up Barker code '11100010010' sent every 220 msec with the comparator threshold at $-20\text{mV}$ ; (b) receiver response to the desired wake-up Barker code, '1010101010' code and to a '11111111111' code at 100 bps chip rate (comparator output not shown due to limited channels available on the oscilloscope). All codes use 50% RZ-OOK modulation | 100 |

| 6.15 | Measured wake-up receiver performance (a) RF Input reflection; (b) Missed-Detection Ratio at 450.8 MHz; (c) Signal to Interference Ratio for a continuous wave and a '1010' pattern AM interferer                                                                                                                                                                                          | 101 |

| 6.16 | (a) Receiver selectivity to <code1>, averaged over 50 responses; (b) Receiver selectivity to <code2> averaged over 50 responses</code2></code1>                                                                                                                                                                                                                                            | 103 |

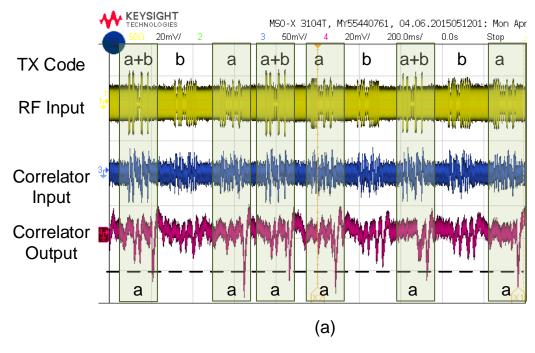

| 6.17 | Receiver response for receiver configured to receive (a) <code1>; (b) <code2></code2></code1>                                                                                                                                                                                                                                                                                              | 104 |

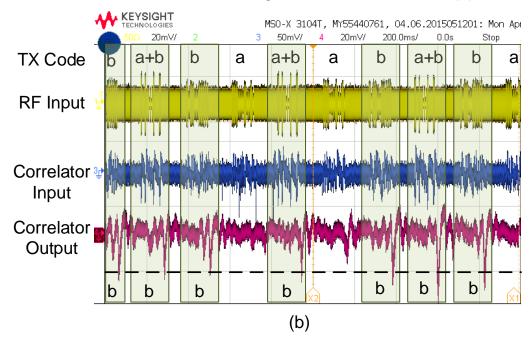

| 6.18 | Chip micrograph implemented in 65 nm LP-CMOS technology                                                                                                                                                                                                                                                                                                                                    | 106 |

| 7.1 | Traditional backscattering with a 1-antenna tag vs proposed directional backscattering with a 3x3 antenna-array tag, that can provide a 3x range                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2 | Analysis of a 3x1 antenna array for backscattering: (a) Available phase-gradient ( $\phi_A$ ) configurations using standard QPSK loads; (b) Calculated conjugating angle for different $\phi_A$ w.r.t. antenna spacing; (c) Evaluated maximum link budget enhancement for a 3x3 antenna array in the horizontal plane and the corresponding required phase gradient $\phi_A$ thanks to directional backscattering w.r.t. angle of incidence, $\theta_i$ , using $0.53\lambda$ antenna spacing |

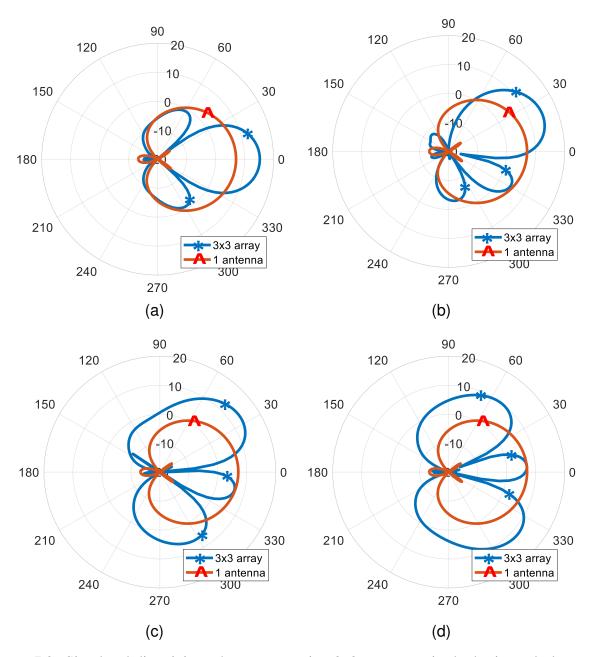

| 7.3 | Simulated directivity enhancement using 3x3 array tags in the horizontal plane with angle of incidence and the corresponding phase gradient ( $\phi_A$ ) of (a) 0°, 0°, (b) 30°, 180°, (c) 45°, 270° and, (d) 60°, 0°                                                                                                                                                                                                                                                                         |

| 7.4 | Direction-of-arrival estimation in the tag over a range of $ \theta_i  < 60^\circ$ : (a) adjacent antenna configurations for RSSI measurements; (b) calculated $RSSI_1$ provides the estimate of $ \theta_i $ , calculated $RSSI_2 - RSSI_3$ provides the sign of $\theta_i$ , the angle of incidence. For $ \theta_i  > 60^\circ$ , phase gradient is $0^\circ$                                                                                                                              |

| 7.5 | Diagram of the proof-of-principle prototype of a 3x3 directional backscatter tag and reader                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.6 | Measurement setup with the 3x3 2.45 GHz backscatter tag turned to a 90° angle of incidence for better visibility                                                                                                                                                                                                                                                                                                                                                                              |

| 7.7 | Received backscattered signal spectrum with normal incidence using (a) one antenna backscatter, (b) $3x3$ array with $0^{\circ}$ phase gradient $(\phi_A)$                                                                                                                                                                                                                                                                                                                                    |

| 7.8 | Received backscattered signal strength at the reader receiver versus angle of incidence(w.r.t. x-axis) with tag rotated in the xy plane for different phase-gradients ( $\phi_A$ ) configurations in the 3x3 tag; the signal strength is relative to the peak signal received for a single-antenna tag                                                                                                                                                                                        |

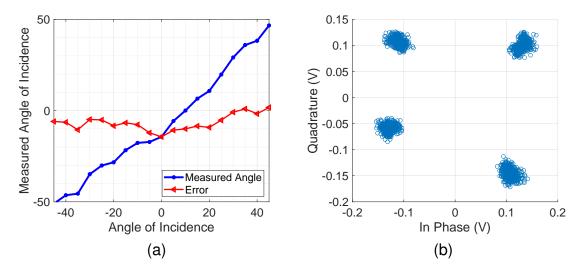

| 7.9 | (a) Measured angle of incidence, (b) Constellation plot for QPSK modulation using a directional backscatter tag with 90° phase gradient                                                                                                                                                                                                                                                                                                                                                       |

# Acknowledgements

The past four years have been the most important part of my career. This dissertation would not have been possible without the generous support from my supervisor, colleagues, friends and family. Hereby, I would like to thank everyone who has helped me on the way to the completion.

My first and foremost gratitude belongs to my academic advisor, Prof. Peter R. Kinget. Your initial directions to understand the fundamental trade-offs was the key to come up with ideas that would later build up the foundation for this thesis. It wasn't easy to convince you to work on a few ideas, but the rigorous reviews ensured that the ideas were well evaluated for their impact on the state of the art before publication. Thanks for making my long stay a productive one. You helped me improve my writing and presentation skills starting from the first paper I ever published to the last I have written yet.

The period after the first publication had few hurdles along the way. I thank all my colleagues and senior mentors including Jianxun Zhu, Yang Xu, Shravan Nagam, Sarthak Kalani, Tanbir Haque, Rabia Tugce Yazicigil, Matt Bajor, Scott Newton, Sharvil Patil for the support and help with the discussions, insights and feedback to get me through.

I would not even have thought of a doctoral degree if I had not received the training and design experience during my bachelors and masters degree at IIT Delhi. Prof. G.S. Visweswaran, Prof. Shouribrata Chatterjee and his Ph.D. students, now professors, Prof. Ganjendranath Chowdary and Prof. Nagarjuna Nallam provided me with the insights, design choices, plenty of layout design experience and a tape-out experience to prepare me and even make me believe that I can pursue a

#### Ph.D.

I would also like to thank Columbia University for the administrative and housing support. I thank Elsa Sanchez, Laura M Castillo, Yoel Rio, Pamela Gordon Rivers, and Dustin King for administrative support. I thank Prof. Timothy Dickson and Prof. Kinget for the opportunity to be a teaching assistant. It helped me improve my advising skills. I also thank the masters and visiting students including Gabriele Atzeni, Louisa, Shobhit, Tom for all the help with different project works.

My appreciation also goes to my doctoral examination committee members Prof. Yannis Tsividis, Prof. Peter R. Kinget, Prof. Shahriar Shahramian, Prof. Patrick Mercier and Prof. Mingoo Seok for timely review of the thesis and evaluation of the defense.

During the four year stay in the United States, I am mostly in debt to my family in India. I used to visit my family only once a year. No matter what I do or where I am, their unconditional love and support make me feel safe and secure. I am eternally grateful, and I wish that someday I could pay them back. Special thanks to my father, who have always supported every career choice that I have ever made.

Lastly, I would like to thank MOSIS and Global Foundaries for silicon donation; Analog Devices, Silicon Labs and NSF ECCS grant 1309721 for partial financial support.

# **Chapter 1: Introduction**

Remote sensors and devices will outnumber smartphones, accounting for more than half of all internet-connected things by 2020 [1]. The potential applications include smart factories and warehouses, smart homes, wearable health devices, smart cars, smart grids, and smart cities (Fig. 1.1). The requirements for these sensors such as battery life, bandwidth, radio range can vary across different applications. Most of the applications require these sensors and devices to be off the power grid, instead depending on batteries or harvested energy. With number of nodes predicted to rise orders of magnitude higher than smartphones, frequent maintenance including battery replacement is infeasible [2]. Thus, the devices need to be extremely energy efficient to extend the lifetime of these sensors.

A key hurdle is to sustain a wireless link with such sensors. Communication to the nodes can be power consuming to the order of 10's of mWs. E.g. a WiFi module consumes 3 mW [3] in standby mode, 214 mW in active receive mode and 660 mW in TX mode at 18 dBm transmit power. The corresponding receiver has a sensitivity of -98 dBm at 1 Mbps data rate. Similarly, a Bluetooth module consumes 29 mW in active receive mode, and 54 mW in active transmit mode at 3 dBm transmit power [4]. The receiver has a sensitivity of -92 dBm at 1 Mbps data rate. Here, a wake-up radio can serve as an important tool to substantially reduce the remote device power consumption and extend its battery life.

#### 1.1 Wake-Up Radio

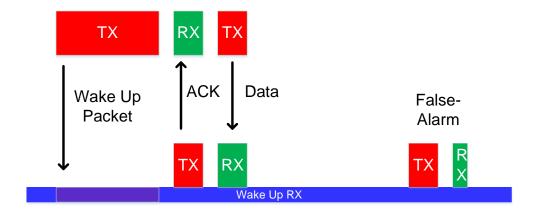

Wake-up is among the most efficient scheme which uses an always ON low-power receiver called the wake-up receiver to turn ON the main receiver when needed. The communication protocol is shown in Fig. 1.2. The sensor node has an always ON wake-up receiver, triggered by a

Figure 1.1: Different applications of a wake-up radio.

Figure 1.2: A generic wake-up radio communication protocol.

defined wake-up signature. Upon detecting the signature, the sensor node acknowledges the signal (ACK) and then turns ON the main receiver for receiving the data.

Message intervals vary for different applications and range from 24 hours to 10 minutes [1]. If a Bluetooth TX/RX is considered with a wake-up receiver, 100 bytes of data at 1 Mbps can be transmitted/received every hour at an average power consumption of 10 nW. Thus, the power consumption of the sensor node using a Bluetooth module can be reduced in the range of 60 nW to 500 pW depending on the desired message intervals. Next we discuss the key metrics for the design of a wake-up receiver and their impact on the system performance.

## 1.1.1 Wake-Up Latency

Wake-up receivers are generally designed to receive a desired signature for reliability. A typical 4-byte wake-up packet is described in [5] consisting of a 1-byte start frame, a 1-byte start sequence and a 2-byte ID. Wake-up latency can be  $1-10\,\mathrm{msec}$  for critical application like factory automation [6] or  $0.1-1\,\mathrm{sec}$  for a less-critical application like smart homes and warehouse. This leads to a minimum desired data-rate of 32 Hz to 32 kHz for a wake-up receiver depending on the application of interest.

## 1.1.2 False-Alarm Rate

Wake-up receivers should be designed to only trigger when a certain code is received. In worst scenario, the random noise in the receiver can lead to a received code, which is the same as a desired code. This leads to a false trigger since no such code was actually transmitted. This is known as a false alarm. It results in an unwanted TX and RX active time leading to a waste of power. In the event of a false wake-up, the main receiver then detects the absence of a frame and turns off. Typically the wake-up receiver should be designed for a false-alarm rate much less than the message rate for a sensor node. For a false-alarm rate of 1/Hr, 2-byte ACK and 2-byte RX using a Bluetooth module results in 370 pW of average power consumption. An even stringent power requirement would require a design for lower false-alarm rate or lower power consumption from the main transceiver.

# 1.1.3 Battery Lifetime

Sensor nodes are required to have at-least 10 years of lifetime without battery replacement, thus requires sufficient charge. Several applications can leverage ambient energy to recharge. A detailed survey was performed in [7] using credit-card sized solar cells in indoor settings. A typical available light energy of  $1.1-2.9 \,\mathrm{J/cm^2/day}$  was measured; assuming a 1% conversion efficiency, the available power is  $1.3 \,\mu\mathrm{W/cm^2}$ . Thus, an  $80 \,\mu\mathrm{m} \times 80 \,\mu\mathrm{m}$  photodiode can provide 6 nW power in an illuminated indoor light setting [8].

However, application like wireless implants in a human body might not allow the use of a battery or a photodiode. Energy harvesting through blood sugar is proposed in [9] for such applications. Energy in a single grain of sugar is enough to provide 6nW of power for a month.

Still, several deployment scenarios don't allow for recharge. High energy density *mm*-scale batteries have been an active area of research recently. A 2 mm Lithium-ion battery is proposed in [10]. Flexible and bio-compatible 2.25 mm x 1.7 mm Lithium-ion battery has been proposed in [11] with an energy density of 200 mWHr/cm<sup>3</sup>. This *mm*-scale battery can provide 6 nW power for 10 years. Thus, different sources of energy for harvesting or battery operation can be used based on the environment where the node is being deployed.

#### 1.1.4 Form Factor

Sensor nodes can vary in size, a credit-card size node might be feasible in a warehouse, but not on a key tracker. A small node requires higher operating frequency for a good air-to-antenna interface, e.g. a 5 cm, short-stub, electrically-small PCB antenna at 433 MHz has a peak antenna gain of -12.5 dBi [12], whereas, the corresponding gain for a 7 cm, long, folded-dipole antenna at 915 MHz is 0 dBi. The 2.4 GHz RF antennas used in [3] is 1.7 cm in length. For an even smaller form factor, the desired operating frequency need to be 5 GHz or even higher.

#### 1.1.5 Range

A small form factor needs operation at higher frequency, but that comes at the cost of range. A 100 m free-space range has a 65 dB or 72 dB path loss at 433 MHz or 915 MHz. Assuming a 20 dBm transmit power, which satisfies TX power regulations for US and Europe in the ISM bands, the required receiver sensitivity for 915 MHz operation is -52 dBm. Non-ideal environment and multipath fading affects the link, further path loss increases with increasing operation frequency. A -84 dBm sensitivity is required from the wake-up receiver to satisfy the requirements for WiFi [1].

Thus, different application requirements pose several constraints on the design as discussed above. Next, we discuss different RF wake-up receiver architectures and their performance trade-

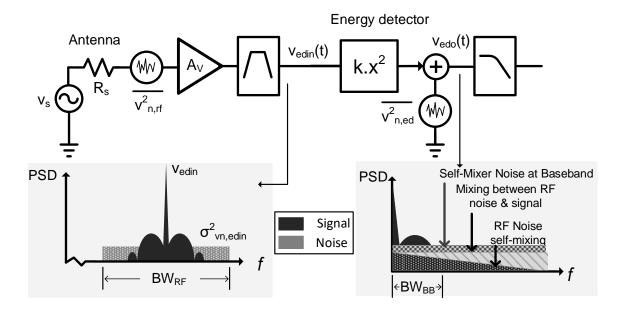

Figure 1.3: Noise contributions in energy-detector based wake-up receivers.

offs to satisfy the requirements.

# **1.2** Architectures for Sub-μW Radios

Conventional receivers including the direct down-conversion receiver can provide excellent selectivity and sensitivity, but at the cost of a power hungry local oscillator(LO). Direct down-conversion receiver architectures have been modified in prior works [13, 14] to reduce the power consumption, but they still consume >  $50 \,\mu\text{W}$ , largely due to the requirement of a crystal oscillator for frequency reference.

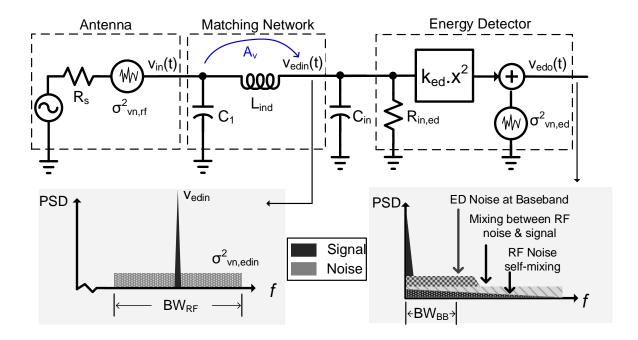

In the absence of an accurate local oscillator, several receiver architectures have been proposed, using a non-linear energy detector to down-convert the RF signal to baseband frequency. A generic block-diagram of an energy-detector based wake-up receiver is shown in Fig. 1.3 with noise contributions in the receiver. The receiver receives the signal from the antenna, with RF amplification  $A_{\nu}$ , followed by a filter with RF bandwidth  $BW_{RF}$ . The output of the filter is fed to an energy-detector to down-convert the RF signal to baseband.

The noise sources in the receiver architecture are also shown in Fig. 1.3. The noise from the antenna is filtered through the RF filter and fed to the energy detector. Due to the non-linear nature of the energy detector, the noise mixes with itself and appears at baseband, the noise also mixes with the input signal and appears as noise at baseband. A low RF bandwidth  $BR_{RF}$  is required to suppress the self-mixed noise from the antenna [15]. Noise is also added by the energy detector at the output. To suppress this noise, a high  $A_{\nu}$  is required from the RF front end.

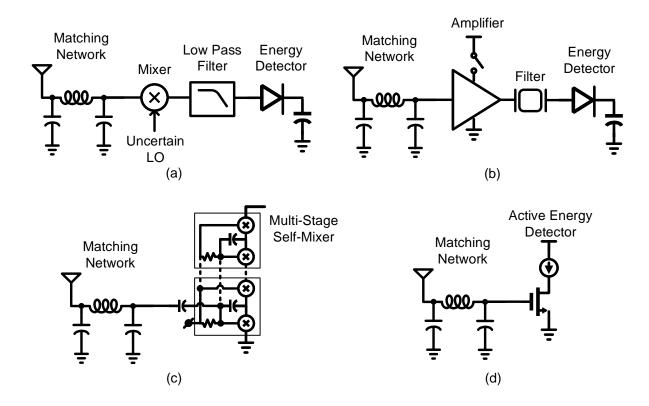

These trade-offs lead to different receiver architectures shown in Fig. 1.4. An uncertain-LO receiver architecture (Fig. 1.4(a)) is proposed in [16] to mitigate the requirement of a crystal oscillator, however the ring oscillator still consumes 10's of  $\mu$ Ws. The power consumption depends on the carrier frequency and the parasitic capacitance in different technology nodes. An energy-detection receiver with active-RF amplification using shifted limiters has been proposed in [17], but consumes > 100  $\mu$ W. Hence, RF amplification or local-oscillator (LO) generation consumes power of the order of 100  $\mu$ W. This can be reduced to 100 nWs by duty-cycling the RF front end (Fig. 1.4(b)). Duty-cycled-RF front end with LO generation is explored in [18]. Duty-cycled-RF amplification is proposed in [19]. The corresponding trade-offs are explored in Section 1.2.1.

RF amplification or LO generation is difficult below 100 nW of power even with duty cycling at a reasonable latency of ≤1 sec, here passive RF front end with active energy detector (Section 1.2.2) or passive energy detector (Section 1.2.2) can be used when power consumption less than 10 nW is desired. Here, the sensitivity is limited by the noise from the energy detector due to the limited passive-RF gain available. Passive-RF front end with passive energy detectors (Fig. 1.4(c)) provide better signal-to-noise ratio(SNR) w.r.t. the active energy detectors (Fig. 1.4(d)) at low power, thus, they provide better sensitivity. Further, a pulsed input signal similar to the power-optimized waveforms (POW) used in [20] can improve the sensitivity for passive-RF ED-first wake-up receivers at the cost of higher power consumption and transmitter complexity. This is explored in Section 1.2.2.

Figure 1.4: Wake-Up receiver RF front-ends using (a) an uncertain LO architecture; (b) a duty-cycled Active RF; (c) passive energy detector; and (d) an active energy detector.

Figure 1.5: (a) A receiver architecture using a duty-cycled active RF amplification [19], (b) the operation principle and the power consumption profile for the receiver, (c) sensitivity and power consumption trade-off based on duty-cycle ratio  $t_{ON}/t_p$  assuming a very low RF front-end bandwidth  $BW_{RF}$ , (d) the required front-end RF filter bandwidth for a 3-dB degradation in sensitivity, and (e) the sensitivity degradation based on the excess RF filter bandwidth.

# 1.2.1 Duty-Cycled Active RF Amplifier

RF amplification consumes  $100 \,\mu\text{W}$  of power at  $900 \,\text{MHz}$  [21]. To reduce this power consumption, the amplifier can be duty cycled 1000x at bit-level to reduce the effective power consumption to  $100 \,\text{nW}$ . Fig. 1.5(a) shows the receiver architecture proposed in [19]. The power consumption profile for the receiver is plotted in Fig. 1.5(b). Here, the RF amplifier is turned on for a period  $t_{ON}$  at an interval of time  $t_p$  (the bit period of the desired signal). This results in the amplifier duty-cycle ratio of  $t_{ON}/t_p$ .

Assuming that the RF filter bandwidth  $BW_{RF}$  is sufficiently low such that the noise mixed with the input signal dominates, the sensitivity for the receiver can be written as [15]:

$$P_{sens} = 8.k_B.T.NF.SNR_{min}/t_{ON}$$

(1.1)

where  $k_B$  is the Boltzmann constant, T is the absolute temperature, NF is the front-end amplifier noise factor and  $SNR_{min}$  is the minimum required SNR for successful signal demodulation. Assuming that the amplifier consumes  $P_{RF}$ , the power consumption is  $P_{RF}t_{ON}/t_p$ . The corresponding power and sensitivity trade-off with varying duty-cycle for  $SNR_{req} = 12.4 \, \mathrm{dB}$  for an 11-bit code,  $t_p = 10 \, \mathrm{msec}$ ,  $P_{RF} = 30 \, \mu \mathrm{W}$  and  $NF = 5 \, \mathrm{dB}$  is plotted in Fig. 1.5(c). The receiver can provide a sensitivity of  $-96 \, \mathrm{dBm}$  at a power consumption of  $30 \, \mathrm{nW}$  for a latency of 110 msec for  $t_{ON} = 10 \, \mu \mathrm{sec}$ .

The receiver has a 3 dB degdaration in sensitivity when the RF filter bandwidth is such that the self-mixed noise from the RF front end is equal to the noise mixed with the input signal. This RF filter bandwidth is plotted in Fig. 1.5(d). The filter bandwidth required using expressions in [15] is  $16.SNR_{req}/t_{ON}$ , this requirement gets more stringent with higher duty cycle, and is not dependent on the RF carrier frequency. For a poorer filter available, the sensitivity degradation with increasing filter bandwidth relative to the desired bandwidth is plotted in Fig. 1.5(e).

## **Preamble Sampling**

An alternative to bit-level duty cycled receiver is preamble sampling. Here, the receiver is duty cycled for detecting the preamble. Upon detection of the preamble, the receiver is turned on for a defined period to receive the wake-up code. A wake-up receiver with preamble sampling is proposed in [18] consuming 17 nW at -80 dBm sensitivity with a latency of 5 sec. The corresponding power consumption for a latency of 110 msec is 770 nW.

Thus, active RF front-end even with duty-cycling still consumes at-least 30 nW of power for less than 1 sec latency. The receiver architecture is best for battery operation, operation on a solar cell etc. where 100 nWs of power is easily available. Further reduction in power consumption and operation at higher carrier frequency will require operation in advanced technology nodes with higher  $f_T$  and high-Q inductors for tuned-RF amplification.

# 1.2.2 Passive RF Energy-Detecting Receivers

Energy-detecting (ED) receivers with a passive RF front end are promising for power consumption  $\leq 10$  nW. Most ED receivers consuming < 10 nW are implemented using an RF matching network to provide the passive gain  $A_{\nu}$  followed by an energy detector (Fig. 1.4(a,b)) [22, 23]. Here, the baseband signal processing can consume power less than 10 nW, and can even reduce to 10's of pWs depending on the required functionality. Dependence on the non-linearity of the transistor leads to poor sensitivity for such ED receivers [22]. Due to relaxed latency constraints for wake-up receivers, by exploiting the latency-sensitivity trade-off, ED receiver sensitivity has been improved in [24, 23, 25]. However, these implementations have optimum sensitivity for RF carrier frequencies less than 200 MHz, which are not suitable for the small form-factor nodes desired in ubiquitous deployment.

Energy detectors can be implemented using active or passive transistors. Active energy detectors using non-linearity of a common-source amplifier is used in [26, 24], however the sensitivity suffers due to the flicker noise and a poor conversion gain at low power. The trade-offs for active energy-detector based receivers are in Section 1.2.2. On the contrary, passive rectifiers with diode-

connected transistors are used to implement passive energy detectors. These perform better than the active counterparts due to the absence of flicker noise [23, 27].

#### **Passive RF Front-End with Passive ED**

The RF front-end for our proposed wake-up receiver architecture in [28] is shown in Fig. 1.6(a). Generally, it is assumed that zero- $V_{TH}$  devices are required for achieving good conversion gain in diode rectifiers. This is a valid assumption for cold-startup in energy harvesting applications. This work proposes self-mixers in Chapter 3 as an alternative to mitigate the requirement with nominal power consumption. Further, the proposed self-mixers serve as an optimal energy detector for wake-up receivers to optimize sensitivity. The sensitivity trade-offs for this receiver is evaluated in Chapter 3 as well.

Here, we assume that the front-end passive gain is limited by the quality factor of the inductor  $Q_{ind}$  with an inductance of  $L_{ind} = 1/(\omega^2 C_{in})$  is available, where  $\omega$  is the RF angular frequency and  $C_{in}$  is the matching network load capacitance. The achievable sensitivity is evaluated in Chapter 3 and can be written as:

$$P_{sens}^{2} = \frac{4k_{B}TR_{in,opt}SNR_{min}}{A_{v}^{4}k_{ed}^{2}R_{s}^{2}t_{p}}.$$

(1.2)

where  $t_p$  is the bit period,  $R_{in,opt} = Q_{ind}/(\omega C_{in})$ , and  $A_v = \sqrt{R_{in,opt}/(2R_s)}$ .

The achievable sensitivity as a function of  $Q_{ind}$  at different RF frequencies for 100 bps datarate with 110 msec latency,  $SNR_{req} = 12.4 \, \mathrm{dB}$  is plotted in Fig. 1.6(b) for  $C_{in} = 1 \, \mathrm{pF}$ . A  $-84 \, \mathrm{dBm}$  sensitivity can be achieved for a 433 MHz operation for an inductor with a  $Q_{ind} = 100$ . The corresponding improvement in sensitivity for a reduced  $C_{in}$  at 2.4 GHz is shown in Fig. 1.6(c), again assuming an inductor with  $L_{ind} = 1/(\omega^2 C_{in})$  and the desired  $Q_{ind}$  is available.

Thus the sensitivity is largely limited by the quality of the front-end matching network, it cannot be improved significantly for a similar latency.

Figure 1.6: (a) Passive-RF energy-detecting receiver architecture using a self-mixer, (b) achievable sensitivity at different ISM band frequencies with increasing quality factor  $Q_{ind}$ , and (c) achievable sensitivity at 2.4 GHz with increasing quality factor  $Q_{ind}$  across different matching network load capacitors.

## **Pulsed Input Signal with Passive ED**

Sensitivity is defined by the average incident power required to wake up a receiver. The power-optimized waveforms [20] carry most of the power in a small time window  $t_{pulse}$  for a bit-period  $t_p$  (Fig. 1.7(b)). The optimal receiver architecture to receive such a signal is shown in Fig. 1.7(a). Since the passive ED is non-linear, the RF to baseband conversion efficiency improves for a high peak-to-average power ratio(PAPR) signal. Thus, the sensitivity can be written as:

$$P_{sens,pulsed} = \sqrt{\frac{t_{pulse}}{t_p}} P_{sens}$$

(1.3)

where  $P_{sens}$  is defined by (1.2). The improvement in sensitivity as a function of  $t_p/t_{pulse}$  is plotted in Fig. 1.7(c) for  $t_p = 10$  msec. The required SNR for false-alarm  $\leq 1$ /Hr only changes by 1dB for  $t_p/t_{pluse}=1000$  due to increased number of samples at the input of the correlator, thus it doesn't significantly impact the sensitivity.

#### Passive RF Front-End with Active ED

For a passive energy detector, the noise contribution of the ED cannot be decreased to improve sensitivity(Chapter 3). However, that is not true for active energy detectors. For active energy detector based wake-up receiver shown in Fig. 1.4(d), the noise contribution from the energy detector can be reduced by increasing the power consumption. For an active ED,  $i_{out} = k_{ed}v_{edin}^2$ , where the voltage input to output current conversion gain constant  $k_{ed} = I_{BIAS}/(2(nV_t)^2)$ , here  $I_{BIAS}$  is the DC current, n is the sub-threshold slope coefficient and  $V_t = k_BT/q$  is the thermal voltage. The noise current power spectral density is  $2k_BTnI_{bias}/(nV_t)$ . Compared to a passive RF front-end with passive ED, the current required for a similar sensitivity is  $n^2V_t^2/(2V_tR_sA_v^2)$ , which leads to  $3.6 \,\mu$ A current for  $A_v$ =20 dB. Sensitivity can further be improved with 0.5 dB/dB increase in current.

Figure 1.7: (a) Receiver architecture to receiver a pulsed-input signal, (b) an example of a pulsed-input RF signal with active time  $t_{pulse}$  for every bit period  $t_p$ , and (c) the improvement in sensitivity compared to the achievable sensitivity in Fig. 1.6 as a function of  $t_p/t_{pluse}$ .

Figure 1.8: Performance trade-offs energy detector based wake-up receivers.

#### 1.2.3 Performance Tradeoffs

The achievable sensitivity w.r.t. the power consumption for a 110msec latency and a passive voltage gain  $A_v = 23 \,\mathrm{dB}$  is plotted in Fig. 1.8 for the wake-up receiver architectures discussed above. A  $0.8 \,\mathrm{pW/Hz}$  of power consumption is assumed (based on Sub-nW RX in Chapter 4) to evaluate the power-sensitivity trade-off for passive energy detectors with pusled RF input. At desired power consumption of  $\leq 10 \,\mathrm{nW}$ , passive-RF front end with passive energy detector is optimal for best sensitivity. At desired power consumption of  $\geq 100 \,\mathrm{nW}$ , duty-cycled RF amplifier with energy detector baseband, provides the best performance.

## 1.2.4 Selectivity in Energy-Detecting Receivers

While energy detectors down-convert the RF signal to baseband with minimal power, the down-converted baseband signal spectrum at frequency  $f_{bb}$  is a function of inter-mixing of the signals with  $\Delta f = f_{bb}$  in the input spectrum. Therefore, the energy detector receiver exhibit no frequency-domain selectivity. The spectral dependence on  $\Delta f$  is exploited in a transmitted LO architec-

ture [17], where the transmitted signal is spread across frequency with a fixed  $\Delta f$ . This improves resilience to narrowband AM interference, but the performance degrades with increasing bandwidth of the interferer. The narrowband interferers can also be treated as LO to downconvert the RF signal to an IF frequency, this improves the selectivity as well as sensitivity for the wake-up receiver(Chapter 5).

For resilience to wideband AM interference, high-Q filters are required before the energy detector. The front-end RF matching network doesn't provide sufficient selectivity at high carrier frequency e.g. in [23], an off-chip transformer operating at 433 MHz provides a 3-dB RF bandwidth of 11 MHz. Thus a SAW filter or a MEMS filter is desired to provide channel selectivity in future.

Frequency-domain selectivity is not available from a ED-first receiver architecture without the front-end RF filter, but code-domain selectivity can still be achieved using an analog correlator at baseband. This is explored in Chapter 6. The code-domain selectivity also enables code-division multiple access(CDMA) using orthogonal codes in the same frequency band. This CDMA operation is also demonstrated in Chapter 6.

An alternative to RF front-end is using Ultrasound for communication. Here, since the carrier frequency is very small, the channel selectivity is provided by the ultrasound transducer itself. Ultrasound has been studied for wake-up applications [29, 30] but the transducers have poor transmit efficiency and the sound waves does not penetrate through walls, thus, it is best suited for applications with short ranges. Here, we will limit our analysis to RF wake-up receivers.

## 1.3 Thesis Organization

This chapter has discussed the challenges in designing a low-power sensor node, requirements for a wake-up receiver, and a brief discussion on the performance trade-offs in designing a wake-up receiver using energy-detecting front end. Chapter 2 further carries an in-depth noise analysis for these energy-detecting receivers with passive-RF front end and derives the requirements from the matching network and the energy detector for achieving the best performance.

Chapter 3 proposes different self-mixer architectures to serve as optimal energy detectors and discusses the design trade-offs. Chapter 4 presents the design of a fully integrated sub-nW wake-up receiver in 65 nm LP CMOS technology employing time-encoded matched filter and comparator with DC offset compensation loop.

For the sub-nW receiver proposed in Chapter 4, sensitivity and selectivity is limited by the front-end design. Chapter 5 proposes the use of interferer as LO to enhance both the sensitivity and the selectivity of the receiver, however, the receiver still gets blocked in the presence of a wideband AM interferer.

In Chapter 6, a clock-less continuous-time analog correlator is proposed which has multi-fold advantages. The correlator provides code-domain selectivity to improve rejection to AM interference. A clock-less architecture with code-domain matched filtering enhances the sensitivity as well. A selective response to two different codes is presented, demonstrating asynchronous CDMA for wake-up receiver application.

Further enhancement in the link is achieved using directional antennas to provide spatial gain and selectivity. A proof-of-concept directional backscatter tag is proposed in Chapter 7, which can be used with the sensor node to act as a reflectarray antenna with enhanced sensitivity and spatial selectivity.

Lastly, we conclude the thesis by highlighting the contributions and discussing directions for future work.

# **Chapter 2: Noise Analysis for Energy-Detecting Receivers**

Energy-detecting receivers use a high-Q RF L-C matching network to provide high passive gain followed by an energy detector for sensing the RF signal (Fig. 2.1). Designing high-Q RF L-C matching networks is difficult at higher carrier frequencies due to increased losses, and as a result the receiver sensitivity often degrades. Thus, optimizing the RF front-end design is critical to maximize sensitivity.

Here, we'll assume an ideal RF front end as shown in Fig. 2.1 to evaluate the impact of the noise from the antenna and the energy detector. Next, we use an ideal rectifier as a passive energy detector, to evaluate the sensitivity as a function of front-end passive gain from the matching network and desired channel bandwidth. Non-idealities due to finite Q-factor of the inductor are introduced to evaluate the practical range of passive gains available, limiting the achievable sensitivity. The chapter concludes by defining the requirements on the energy detector given the front-end matching network to optimize sensitivity.

#### 2.1 Noise Analysis

Fig. 2.1 shows the noise model for an ED receiver with a passive RF front end. The antenna is represented as a voltage source with a source resistance  $R_s$  of 50  $\Omega$  and is matched to the energy detector using a matching network with a passive gain  $A_v$  at frequency  $f_{rf}$ , leading to a 3-dB bandwidth  $BW_{RF}$ , and a noise factor  $N_{MN}$ . The energy detector is assumed to have an input resistance  $R_{in,ed}$  with a conversion gain constant  $k_{ed}$ . Since the energy detector is non-linear, we evaluate the signal-to-noise ratio (SNR) at the output of the energy detector.

Assuming a continuous-wave RF signal with power  $P_{in}$  incident on the antenna with a radiation resistance  $R_s$ , resulting in an RF input signal  $v_{in}(t)$ . The root-mean-square (RMS) signal received

Figure 2.1: Small-signal model including noise sources for an ED receiver; the spectra of signal and noise at the input and the output of the energy detector are also shown.