# Feasibility of Novel Low-cost Deca-Nanometer Vertical MOSFETs for Radio Frequency Application

Thesis submitted in accordance with the requirements of the Department of Electrical Engineering and Electronics University of Liverpool

### **Doctor in Philosophy**

### Author: Lizhe Tan

**Supervisor: Stephen Hall**

October 2008

" Copyright C and Moral Rights for this thesis and any accompanying data (where applicable) are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s. When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g. Thesis: Author (Year of Submission) "Full thesis title", University of Liverpool, name of the University Faculty or School or Department, PhD Thesis, pagination."

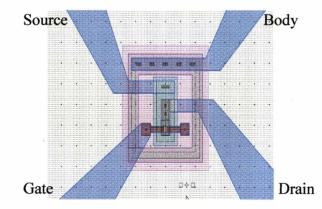

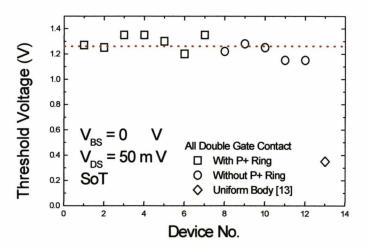

### Abstract

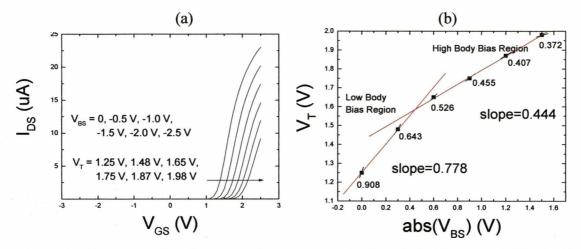

The vertical MOSFET (VMOSFET) is a strong contender for low operating power devices on the ITRS road map, which is presently at the 65 nm technology node. VMOSFETs have already found applications in the power device market and also shown feasibility as both digital and analogue/RF devices. The proposed VMOSFETs are CMOS technology compatible and can be fabricated with a channel length down to sub-0.1µm without the need for expensive deep submicron lithography. This provides an opportunity to fabricate highperformance RF blocks with a low cost process and integrate them with digital ones. On the other hand, VMOSFETs suffer from much higher parasitic capacitances which limits its operation frequency. They can also suffer from severe short channel effects which shift the threshold voltage and increase the off-current.

Previous research has demonstrated the feasibility of some novel concepts to address the above limitations: overlap parasitic capacitance by fillet local oxidation (FILOX) and shortchannel effect by junction stop (JS). In this work, I have investigated in detail, the properties of devices with the above features through experimental, analytical and numerical modelling studies. Furthermore, device performances at RF frequency have been measured and analysed. Finally, a set of compact model parameters has been extracted targeting on the 100nm short channel device with FILOX using EKV model approach.

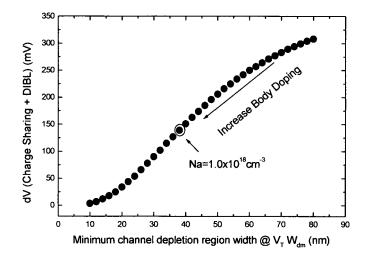

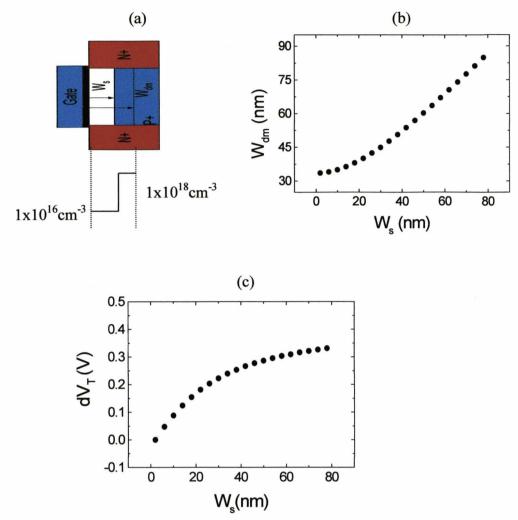

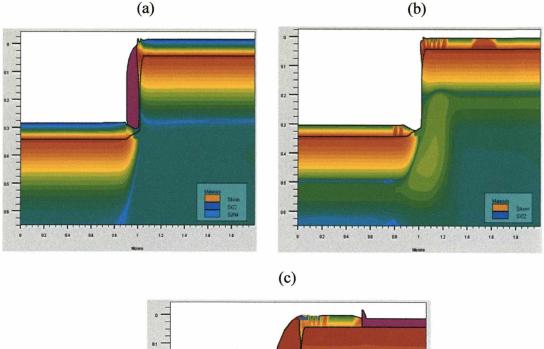

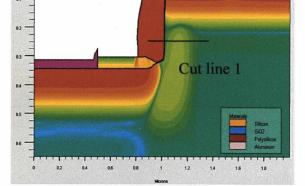

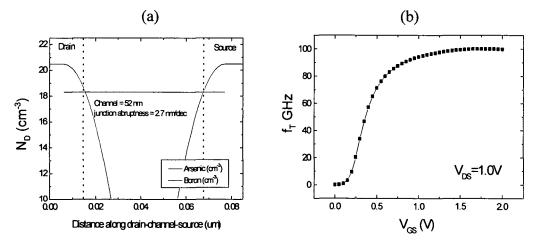

Through the characterisation and numerical simulation of the VMOSFET-JS, we have investigated electrical anomalies and relevant underling physics in different parts of the device through analytical model study and parameters fitting. Numerical simulation also showed the individual impact of symmetrical and asymmetrical junction depths with regard to charge sharing and drain induced barrier lowering (DIBL) which allowed further improvement in the device design, in particular, the possibility of allowing lower body doping and hence higher channel mobility and on-current. It is also shown that there is a critical junction depth above which the JS effect on SCEs reaches its maximum.

FILOX technology has been incorporated into ultra-thin pillar capacitors and assessed by C-V and I-V characterisation. Feasibility for incorporating FILOX into fully-depleted VMOSFET structures is demonstrated. Low levels of leakage current were observed. A VMOSFET-FILOX incorporating a retrograde channel has been designed and fabricated. Theoretically the new design brings increased on-current while maintaining the off-current level. A number of anomalies in experimental devices are explored.

A surface potential based analytical model for source series resistances has been developed. The model shows good agreement with the source series resistance extracted from the 2D simulations using the Z parameters method. Suggestions are made to address

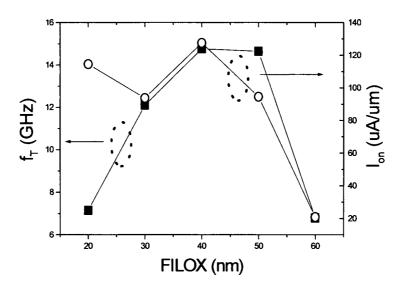

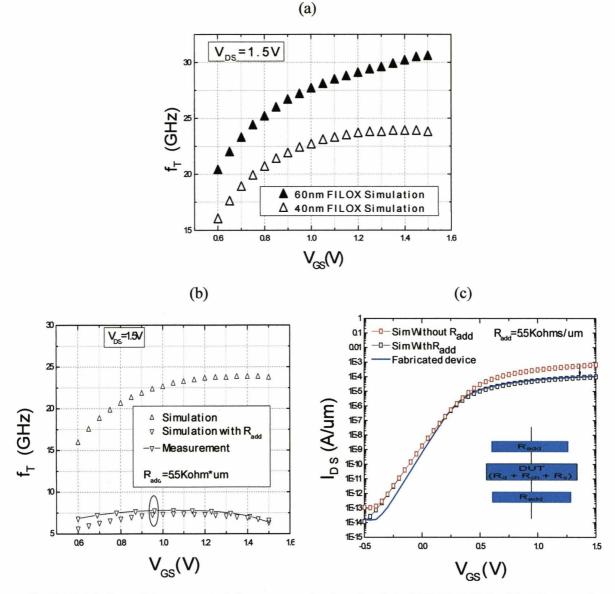

the series resistance limitation on cut-off frequency,  $f_T$  which is shown to be related to FILOX thicknesses and associated process conditions.

Cut-off frequency characterisation has shown that VMOSFET-FILOX with frame gate has only half the  $f_T$  of double gate contact which is shown to be able to achieve a maximum  $f_T$  of 8.6 GHz. The effects on  $f_T$  of bias, channel length, width and FILOX thickness have been investigated in some detail. 3D simulation studies address performance including the influence of corners on the electrical characteristics. The numerical simulation calibrated with the process has suggested the best  $f_T$  can be achieved can reach 30.5GHz for a 60nm FILOX. Device simulation also suggests that if the junction abruptness is improved to an ITRS requested level for a 50nm channel length, the peak  $f_T$  can be boosted to 99.4GHz. Therefore, an almost three-generation-hop in RF performance that can be achieved using a 0.35µm lithography stepper compared to the advanced lateral MOSFETs at the same lithography technology node.

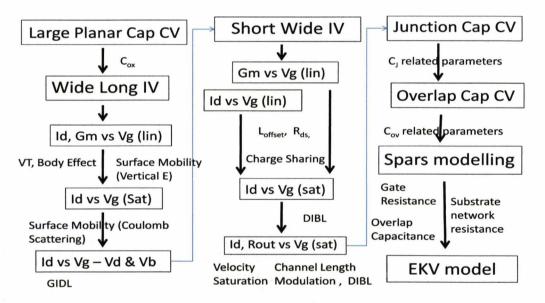

The extraction of the EKV parameters, which model both DC and AC performances, has been conducted using the VMOSFET-FILOX devices with a double gate contact. In the process, some modelling issues have been raised. The problems of realising a truly 'long channel device' for model fitting in contrast to the good fitting for the short channel model and device variations for S-parameters fitting highlight challenges in the compact modelling of vertical MOSFETs. Finally, suggestions to improve process steps are made in order to refine the device performance in accordance with RF requirements.

#### ACKNOWLEDGEMENT

During these four years of taking apart of this project, I have received much support from many wonderful people no matter who are near or far away from me. Without them, it would not be possible for me to accomplish this journey. I would like to take this opportunity to share my endless joyfulness and more importantly to say "Thank you" to them.

I would like to express my deepest gratitude to is Prof. Steve Hall who has guided and inspired me since the beginning of the project and always kept the flame lighting in these four years. Not only being great in supervision on solving the problems met during research, despite of being busy with dealing with the administrative and teaching duties for the Department as required by the role of the head of department, his encouragement and substantial support to the young generation of engineers is also most helpful and memorable. I am very grateful for his support and trust in all kinds.

I would like to express my sincere gratitude to Prof. Peter Ashburn, Dr. Mohammad M. Al Hakim and Dr. Enrico Gili from the team in University of Southampton for kindly providing the samples and comments on my work. Our cooperation has been a wonderful experience and formed such an important part of the project. Also I would like to acknowledge deeply Sean Connor and Arnaud Bousquet from MHS for allowing me to access their workstation and assist me in the laboratory.

I also would like to express my sincere gratitude to my dear colleagues in the research group. Many thanks to Mr William Davey for sharing the same office and lots of wonderful laughs. Many thanks to Dr. Yi Lu and Dr. Ivona Z. Mitrovic for their professional knowledge, useful discussions and suggestions on looking into the problems. Many thanks to Mr Paul Wakinson and Mr Kevin Molloy for their important technical assistance in the labs and office. Many thanks to Mrs Jacqueline Cowan for her kind concern every time I came to the office. It has been a great privilege and a treasured experience for me to study in the Electrical Engineering and Electronics Department, University of Liverpool.

Last and most importantly, I dedicate the thesis to my parents Zaixi Tan, Jianfu Li and my fiancée Sui Liu. Many thanks to them for their support in a numerous ways and their understanding on the fact that I could not always be with them during these years. Without their love and care, this thesis is not possible. Of course, I must thank all my friends who have been giving me encouragement and support in the last four years.

## **Content Table**

| Abstract         | I     |

|------------------|-------|

| Acknowledgement  |       |

| Contents         | IV    |

| List of Figures  | VIII  |

| List of Tables   | XIII  |

| List of Symbols  | XIV   |

| List of Acronyms | XVIII |

| Chapter 1.                      | Literature Review1                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.1                             | Market Value of RF Applications2                                                                                                                                                                                                                                                                                                                                                                            |  |

| 1.2                             | Trend of RF Device Research4                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                 | 1.2.1 III-V Transistors                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                 | 1.2.2 SiGe HBT BiCMOS                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                 | 1.2.3 CMOS Technology                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1.3                             | Si Based Vertical MOSFETs12                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.4                             | Vertical MOSFETs in this Project                                                                                                                                                                                                                                                                                                                                                                            |  |

| 1.5                             | Summary25                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Chapter 2. Theory Consideration |                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 2.1                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                 | Basic Current-Voltage Characteristics in Long Channel MOSFETs29                                                                                                                                                                                                                                                                                                                                             |  |

|                                 | Basic Current-Voltage Characteristics in Long Channel MOSFETs29<br>2.2.1 Universal Drain-Current Model                                                                                                                                                                                                                                                                                                      |  |

|                                 | Basic Current-Voltage Characteristics in Long Channel MOSFETs                                                                                                                                                                                                                                                                                                                                               |  |

| 2.2                             | Basic Current-Voltage Characteristics in Long Channel MOSFETs.292.2.1 Universal Drain-Current Model.302.2.2 I-V Characteristics in the Linear and Saturation Region.322.2.3 I-V Characteristics in the Sub-threshold Region.34                                                                                                                                                                              |  |

| 2.2                             | Basic Current-Voltage Characteristics in Long Channel MOSFETs.       29         2.2.1 Universal Drain-Current Model.       30         2.2.2 I-V Characteristics in the Linear and Saturation Region.       32         2.2.3 I-V Characteristics in the Sub-threshold Region.       34         Short Channel Effect.       35                                                                                |  |

| 2.2                             | Basic Current-Voltage Characteristics in Long Channel MOSFETs.292.2.1 Universal Drain-Current Model.302.2.2 I-V Characteristics in the Linear and Saturation Region.322.2.3 I-V Characteristics in the Sub-threshold Region.34Short Channel Effect.352.3.1 Charge Sharing and Drain Induced Barrier Lowering.35                                                                                             |  |

| 2.2                             | Basic Current-Voltage Characteristics in Long Channel MOSFETs.292.2.1 Universal Drain-Current Model.302.2.2 I-V Characteristics in the Linear and Saturation Region.322.2.3 I-V Characteristics in the Sub-threshold Region.34Short Channel Effect.352.3.1 Charge Sharing and Drain Induced Barrier Lowering.352.3.2 Sub-threshold Degradation.39                                                           |  |

| 2.2                             | Basic Current-Voltage Characteristics in Long Channel MOSFETs.292.2.1 Universal Drain-Current Model.302.2.2 I-V Characteristics in the Linear and Saturation Region.322.2.3 I-V Characteristics in the Sub-threshold Region.34Short Channel Effect.352.3.1 Charge Sharing and Drain Induced Barrier Lowering.352.3.2 Sub-threshold Degradation.392.3.3 Channel Length Modulation and Velocity Saturation.39 |  |

| 2.7       | RF Performance Figure of Merit                                                        | 46 |

|-----------|---------------------------------------------------------------------------------------|----|

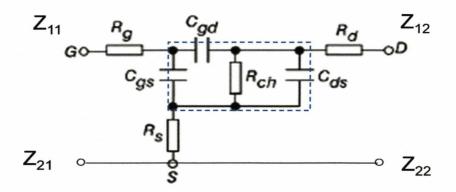

| 2.8       | MOSFET RF Equivalent Circuit                                                          | 49 |

| Chapter 3 | . Characterisation and Numerical Modelling of Vertice<br>MOSFETs with a Junction Stop |    |

| 3.1       |                                                                                       |    |

|           | 3.1.1 Sample Preparation                                                              | 52 |

|           | 3.1.2 Comparison of Transfer Characteristics                                          | 54 |

|           | 3.1.3 Comparison of Output Characteristics and Substrate Currents                     | 60 |

| 3.2       | Carrier Conduction Mechanisms in Gate Oxide                                           | 65 |

| 3.3       | Device Modelling and Calibrations                                                     | 67 |

|           | 3.3.1 Simulation Structure Construction                                               | 68 |

|           | 3.3.2 Calibration of Sub-threshold Region                                             | 69 |

|           | 3.3.3 Calibration of Off-Current Regime and GIDL                                      | 71 |

|           | 3.3.4 Calibration of On-Current                                                       | 73 |

| 3.4       | Summary                                                                               | 74 |

| Chapter 4 | . Short Channel Effects in Vertical MOSFETs with a Junction stop                      | 76 |

| 4.1       | Introduction                                                                          |    |

| 4.2       | Junction effects on CS and DIBL in A Conventional VMOSFET                             |    |

| 4.3       | Junction Depth Design in a VMOSFET-JS                                                 |    |

| 4.4       |                                                                                       |    |

|           | 4.4.1Drain Junction Depth Effects on CS                                               |    |

|           | 4.4.2 Drain Junction Depth Effects on DIBL                                            |    |

| 4.5       | *                                                                                     |    |

| Chapter 5 | . VMOSFETs with Novel Structures                                                      | 92 |

| 5.1       |                                                                                       |    |

|           | 5.1.1 Technology Description                                                          |    |

|           | 5.1.2 Capacitance-Voltage Measurements                                                |    |

|           | 5.1.3 Other Capacitor Properties                                                      |    |

| 52        | VMOSFET-FILOX with a Retrograde Body                                                  |    |

| 5.2       | 5.2.1 Analytical Model                                                                |    |

|           | 5.2.2 Numerical Model                                                                 |    |

|           | 5.2.3 Device Characterisation                                                         |    |

| 5.3       | Summary                                                                               |    |

|           | -                                                                                     |    |

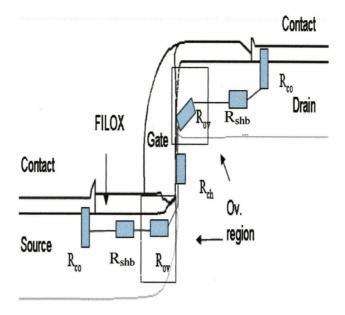

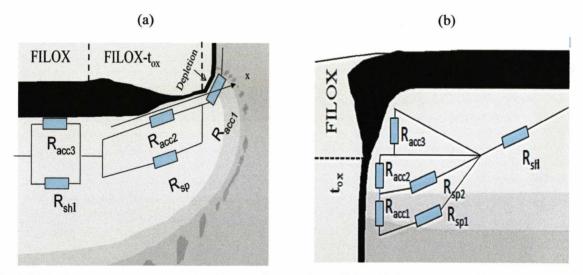

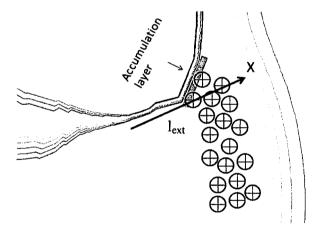

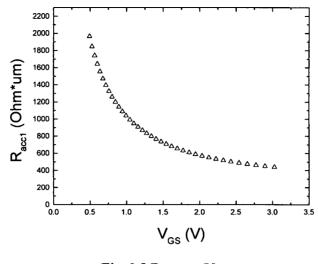

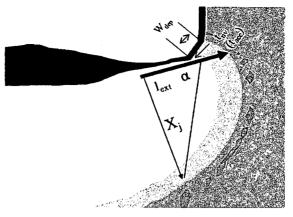

| Chapter 6. | Series Resistance in VMOSFETs with FILOX123                                  |

|------------|------------------------------------------------------------------------------|

| 6.1        | Introduction124                                                              |

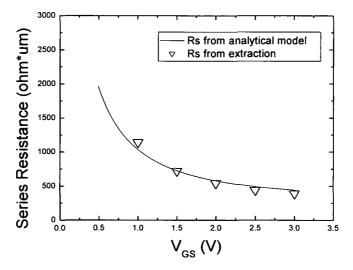

| 6.2        | Analytical Model of the Bottom Junction Resistance125                        |

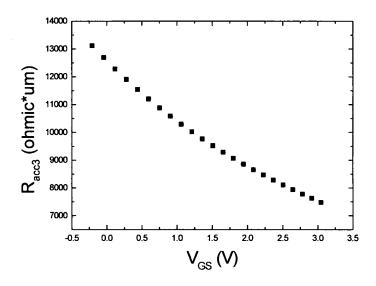

|            | 6.2.1 Analytical Model for Accumulation Resistance, $R_{acc}$ 126            |

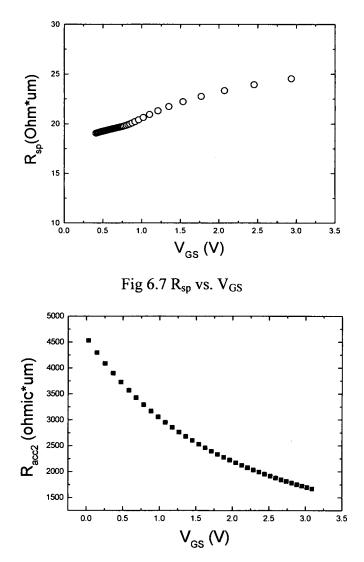

|            | 6.2.2 Analytical Model for Spreading Resistance, R <sub>sp</sub> 130         |

|            | 6.2.3 Analytical Model for $R_{sh1}$ in Parallel with $R_{acc3}$ 133         |

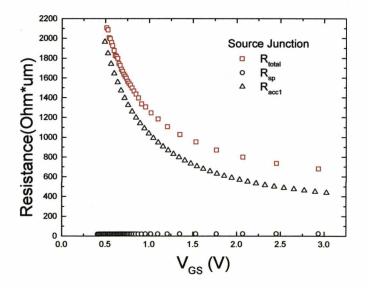

|            | 6.2.4 Discussions on Series Resistance in Bottom Junction and Top Junction   |

|            |                                                                              |

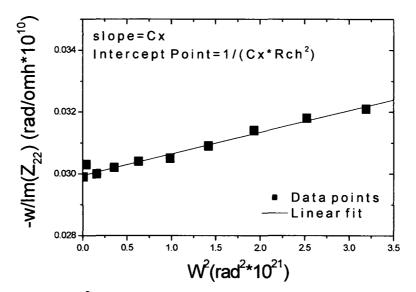

| 6.3        | $R_d$ and $R_s$ Extraction using an RF-Impedance Technique                   |

|            | 6.3.1 Technique Description                                                  |

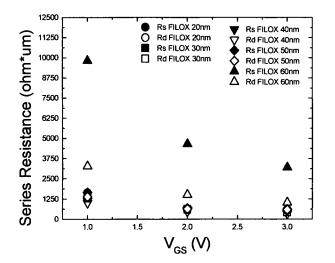

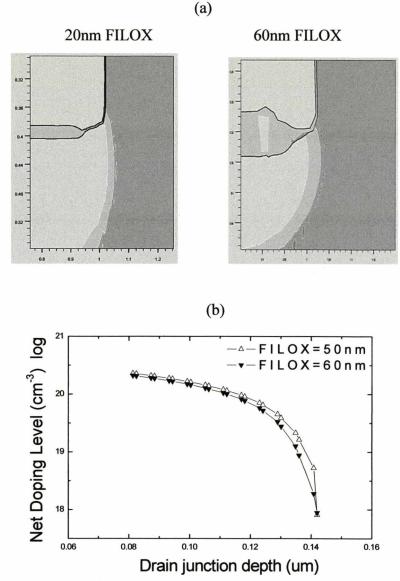

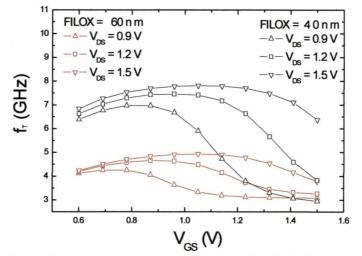

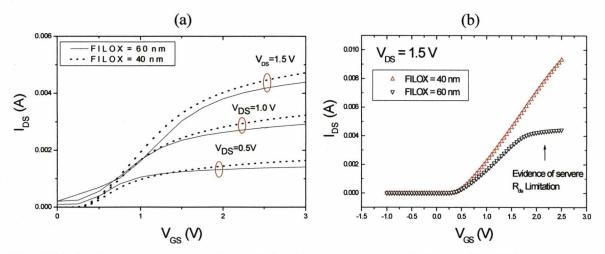

|            | 6.3.2 The Effect of FILOX Thickness on $R_d$ and $R_s$                       |

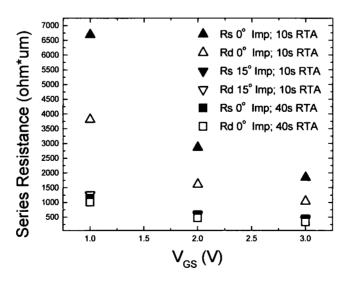

|            | 6.3.3 The Effect of Drain/Source Implantation and RTA on $R_d$ and $R_s$ 143 |

| 6.4        | Summary144                                                                   |

| Chanter 7  | f <sub>T</sub> Characterisation146                                           |

| Chapter /. |                                                                              |

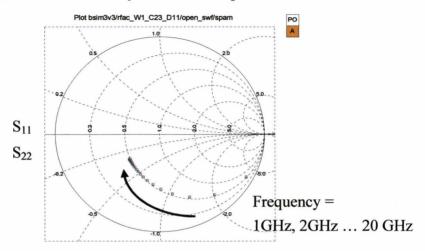

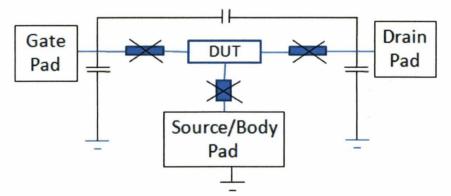

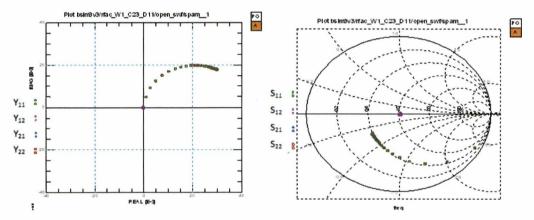

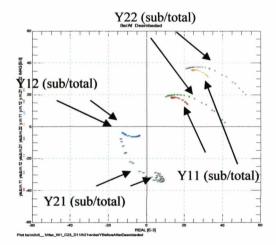

| 7.1        | Calibration and De-Embedding147                                              |

| 7.2        | f <sub>T</sub> Characterisation of Second Batch VMOSFET-FILOX151             |

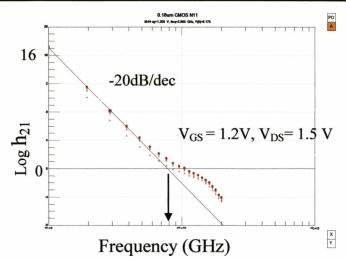

|            | 7.2.1 f <sub>T</sub> Extraction Technique151                                 |

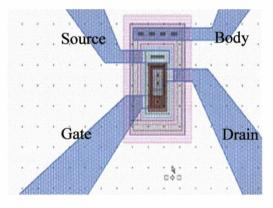

|            | 7.2.2 The Effect of Contact Resistance on $f_T$ 153                          |

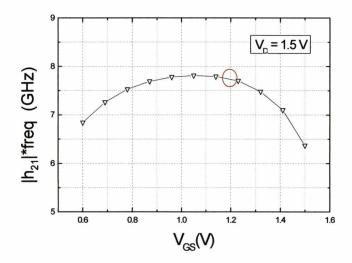

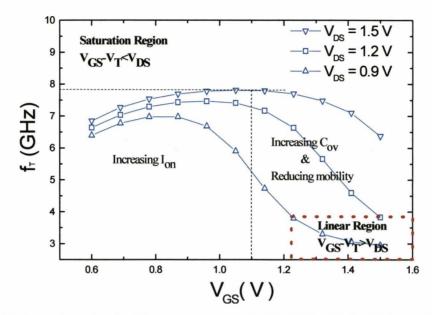

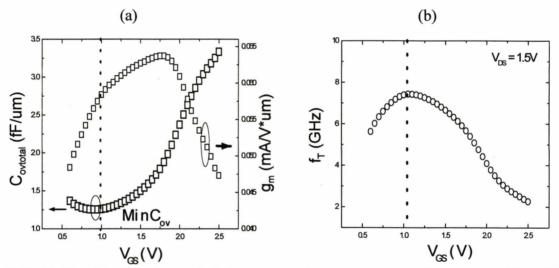

|            | 7.2.3 The Effect of Biases on $f_T$                                          |

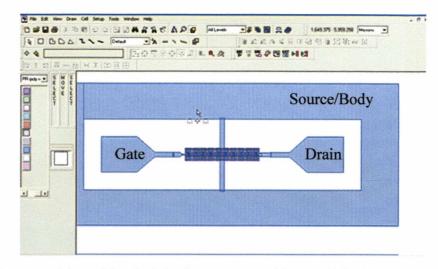

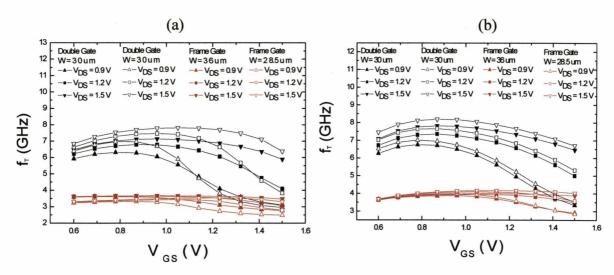

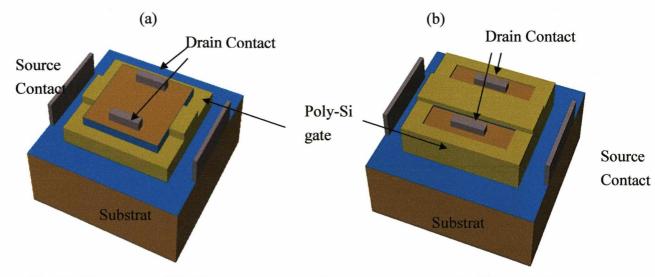

|            | 7.2.4 The Effect of Gate Types on $f_T$ 157                                  |

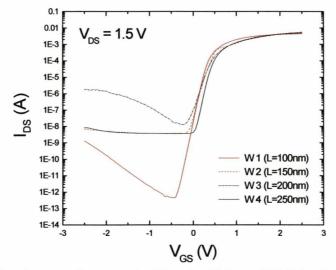

|            | 7.2.5 The Effect of Channel Length and Channel Width on $f_{\text{T}}159$    |

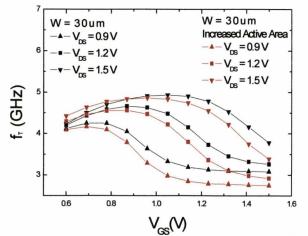

|            | 7.2.6 The Effect of FILOX Thickness on $f_{\text{T}}162$                     |

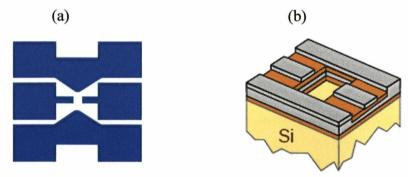

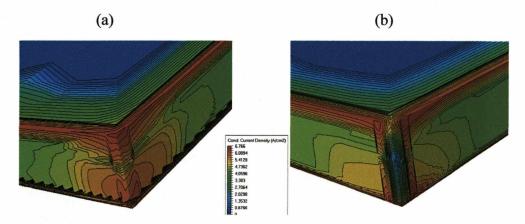

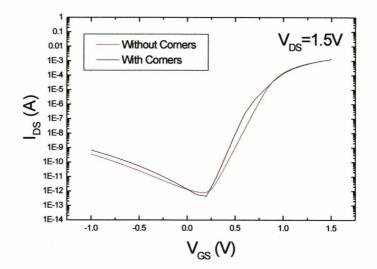

|            | 7.2.7 Corner Effects                                                         |

|            | 7.2.8 50nm Ideal Device Simulation                                           |

| 7.4        | Summary165                                                                   |

| Chapter 8. | EKV Modelling167                                                             |

| 8.1        | Introduction168                                                              |

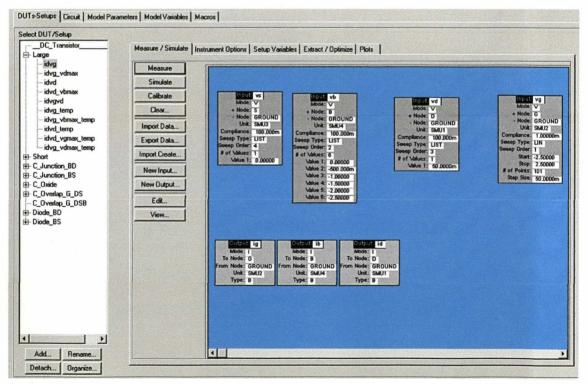

| 8.2        | Data Acquisition168                                                          |

| 8.3        | Extraction Strategy169                                                       |

| 8.4        | Parameter Extraction                                                         |

| 8.5        | Summary181                                                                   |

| Chapter 9. Conclusions & Suggestions for Future Work185 |                                                                                        |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| Conclusions                                             |                                                                                        |  |  |

| Suggestions on Future Work                              | 192                                                                                    |  |  |

|                                                         | 197                                                                                    |  |  |

|                                                         | 206                                                                                    |  |  |

|                                                         | 210                                                                                    |  |  |

|                                                         | 212                                                                                    |  |  |

|                                                         |                                                                                        |  |  |

|                                                         | 215                                                                                    |  |  |

|                                                         | 220                                                                                    |  |  |

|                                                         | Conclusions & Suggestions for Future Work<br>Conclusions<br>Suggestions on Future Work |  |  |

# **List of Figures**

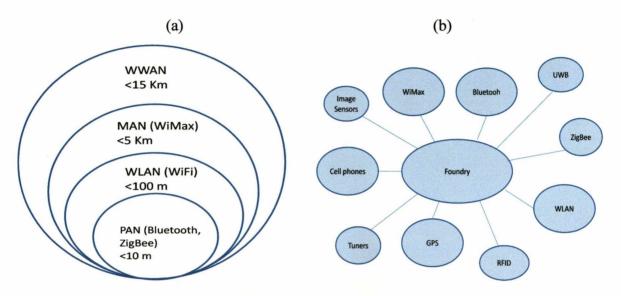

| 1.1  | (a) Wireless application coverage (b) established and emerging markets.                                    | 3    |

|------|------------------------------------------------------------------------------------------------------------|------|

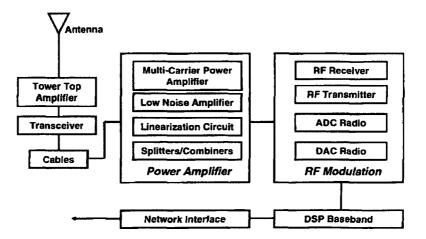

| 1.2  | Block diagram of a typical base station.                                                                   | 4    |

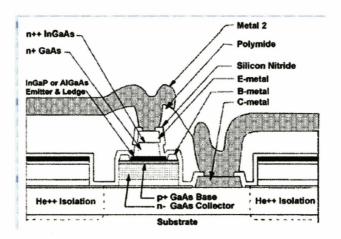

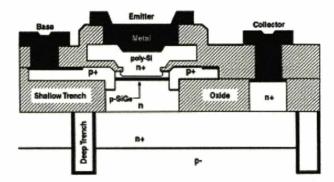

| 1.3  | Cross sectional diagram of npn GaAs HBT.                                                                   | 6    |

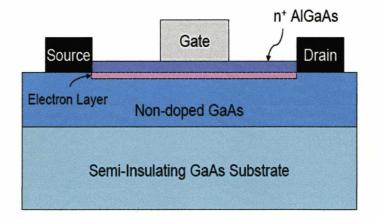

| 1.4  | Cross sectional diagram of GaAs/AlGaAs HEMT.                                                               | 6    |

| 1.5  | Cross sectional diagram of SiGe HBT by IBM.                                                                | 8    |

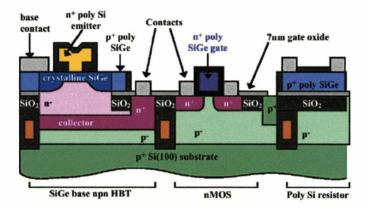

| 1.6  | Cross sectional diagram of SiGe HBT based BiCMOS by IBM.                                                   | 8    |

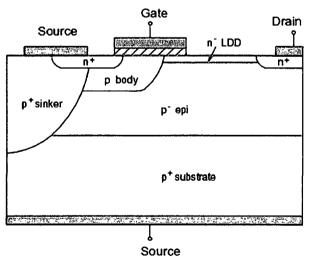

| 1.7  | Cross sectional diagram of a typical Si LDMOS.                                                             | 9    |

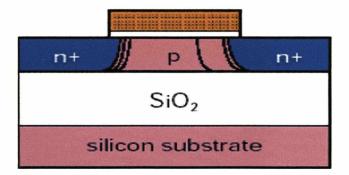

| 1.8  | Cross sectional diagram of a typical SOI.                                                                  | 10   |

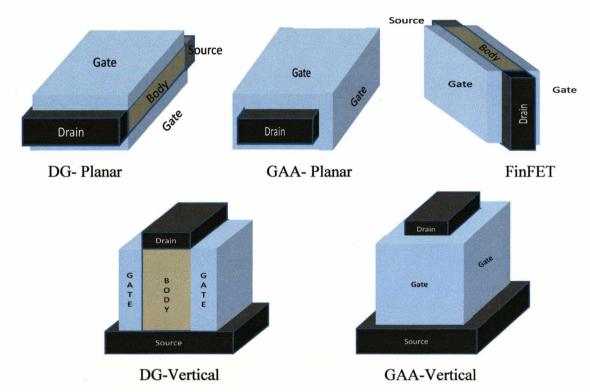

| 1.9  | Basic structures of a Si based planar double gate, planar gate-all-around, FinFET, vertical MOSFETs v      | vith |

|      | double gate and surrounded gate.                                                                           | 13   |

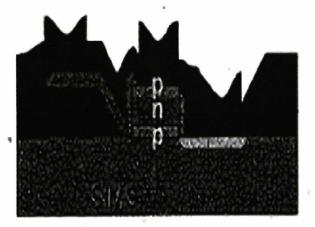

| 1.10 | Cross sectional diagram of selectively grown epitaxial p type VMOSFET.                                     | 14   |

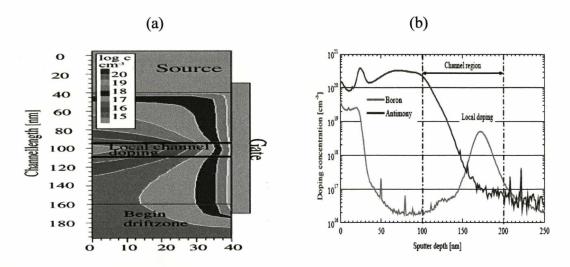

| 1.11 | (a) Simulated electron concentration for delta local doping; (b) corresponded doping profile along the     |      |

|      | pillar height at the surface.                                                                              | 14   |

| 1.12 | Overlap capacitance reduced by depositing SiO2/PolyGate/SiO2 layers in a selective epitaxy grown           |      |

|      | VMOSFET.                                                                                                   | 15   |

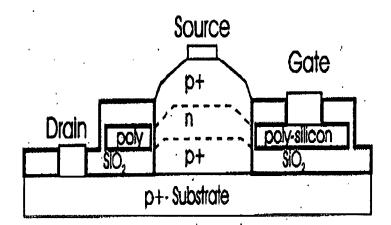

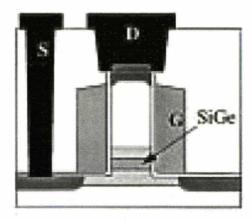

| 1.13 | SiGe source VMOSFET for parasitic bipolar effect reduction.                                                | 16   |

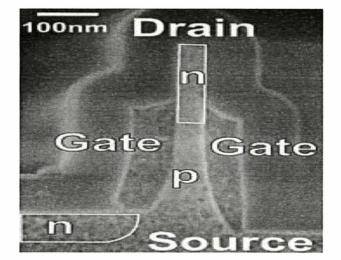

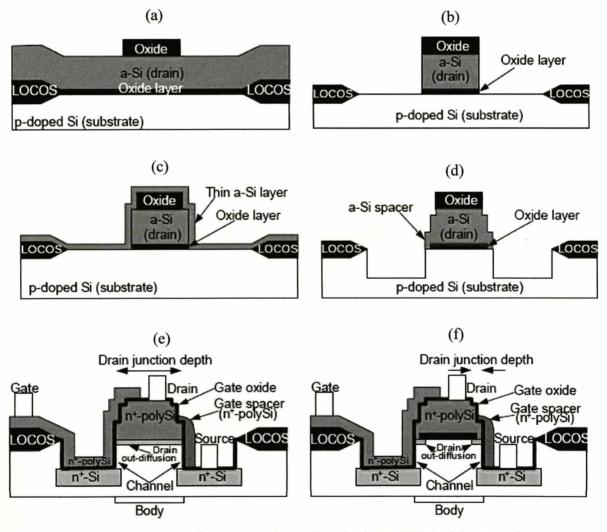

| 1.14 | First reported ion-implanted defined vertical MOSFET with a GAA structure.                                 | 17   |

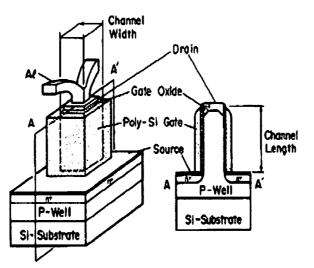

| 1.15 | First reported ion-implanted defined ultra-thin-body vertical MOSFET with a double gate structure.         | 18   |

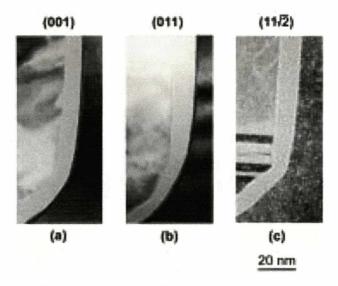

| 1.16 | TEM picture of the gate oxide at the pillar corners featuring different surface orientations. (a) 10 nm ox | kide |

|      | thickness at the (001) sidewall (b) 14 nm oxide thickness at the (011) sidewall; (c) 12 nm oxide thickness | ess  |

|      | at the $11\sqrt{2}$ sidewall.                                                                              | 18   |

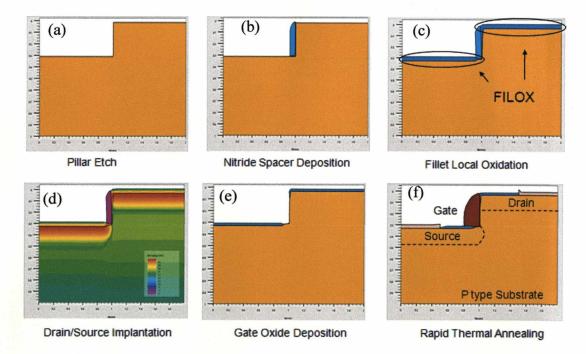

| 1.17 | Brief fabrication process of the ultra-thin-vertical-channel MOSFET.                                       | 20   |

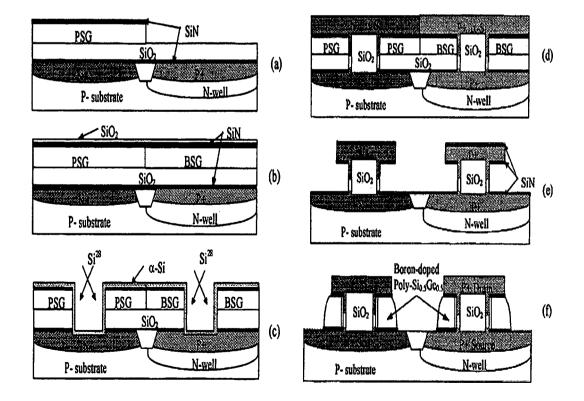

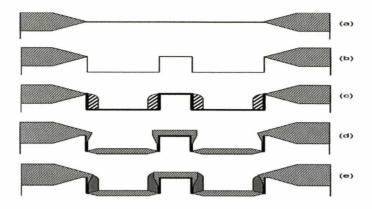

| 1.18 | Fabrication process of an ion implanted Vertical MOSFET with a Fillet Local Oxidation (FILOX).             | 21   |

| 1.19 | Fabrication process of an ion implanted Vertical MOSFET with a Junction Stop structure (JS).               | 24   |

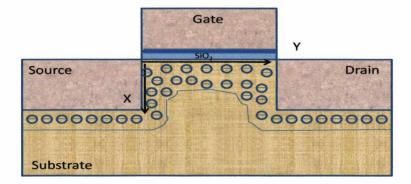

| 2.1  | Basic structure of an nMOSFET. "Y" direction is along the channel; "X" direction is perpendicular to t     | the  |

|      | channel.                                                                                                   | 30   |

| 2.2  | The electric field contours in a lateral MOSFET with a gate bias above threshold voltage and with low      |      |

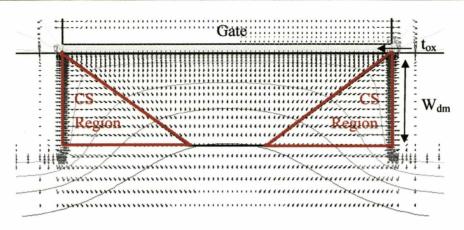

|      | drain bias.                                                                                                | 37   |

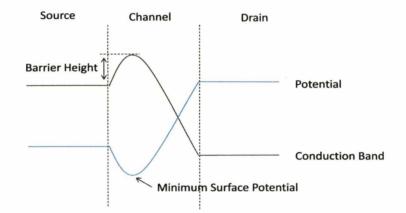

| 2.3  | Potential and band diagram along the channel where the magnitude and the position of minimum surfa         | ce   |

|      | potential determine these values for the source barrier height.                                            | 37   |

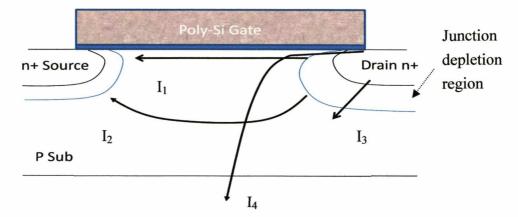

| 2.4  | Drain/source junction leakage mechanism in deep sub-micron.                                                | 42   |

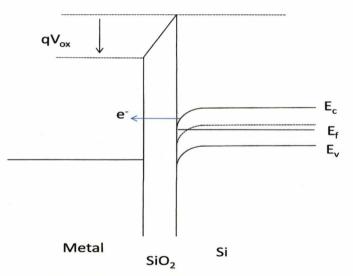

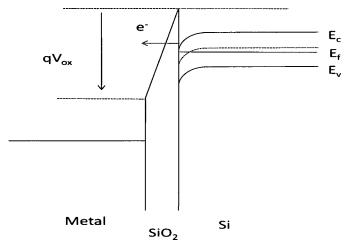

| 2.5  | Band diagram of direct tunneling mechanism.                                                                | 43   |

| 2.6  | Band diagram of Fowler-Nordheim mechanism tunneling.                                                       | 45   |

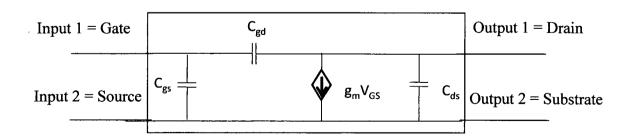

| 2.7  | A simplified two port network of a MOSFET at RF.                                                           | 48   |

| 2.8  | Equivalent circuit of a MOSFET at RF frequency range.                                                      | 50   |

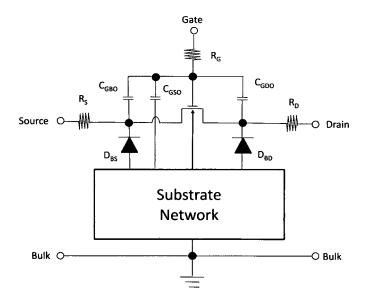

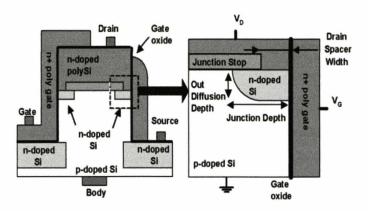

| 3.1  | Vertical MOSFET structure with a junction stop beneath the poly-Si drain contact.                          | 53   |

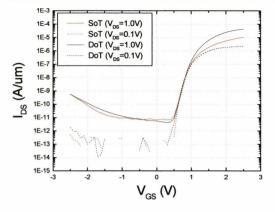

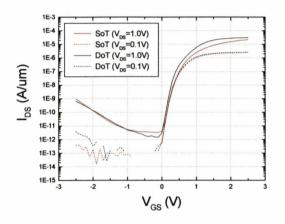

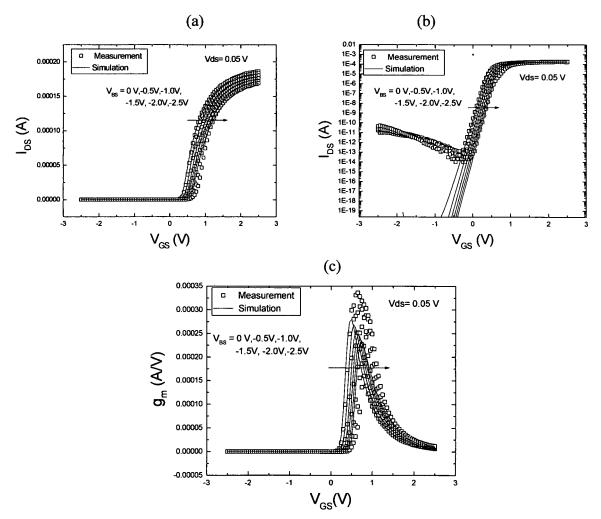

| 3.2        | Transfer characteristics of devices in split # 1: W=32um.                                                       | 55       |

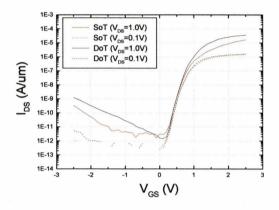

|------------|-----------------------------------------------------------------------------------------------------------------|----------|

| 3.3        | Transfer characteristics of devices in split # 3: W=52 um.                                                      | 55       |

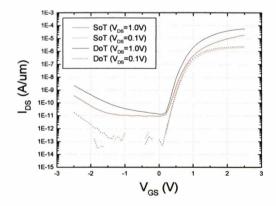

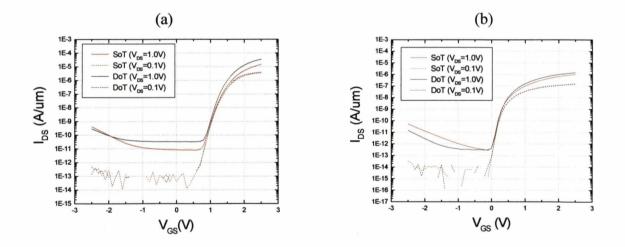

| 3.4        | Transfer characteristics of devices in split# 5: W=52 um.                                                       | 55       |

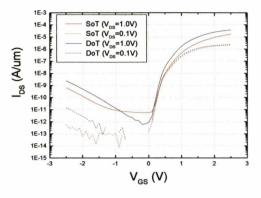

| 3.5        | Transfer characteristics of devices in split#6: W=27 um.                                                        | 56       |

| 3.6        | Transfer characteristics of devices in split#7: W=27 um.                                                        | 56       |

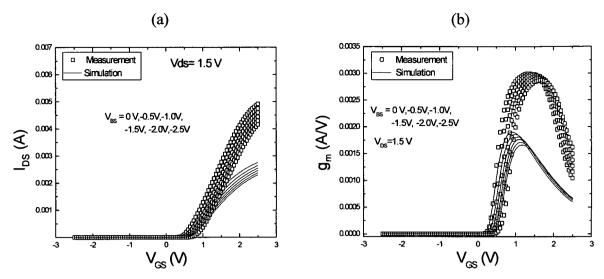

| 3.7        | Transfer characteristics of devices in split#8: (a) & (b) $W = 27$ um with a high $V_T$ ; (c) & (d) $W = 27$ ur | n        |

|            | with a low $V_{T}$ .                                                                                            | 56       |

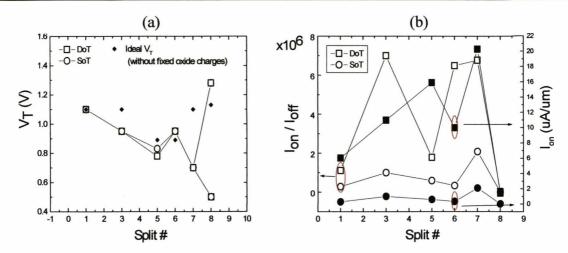

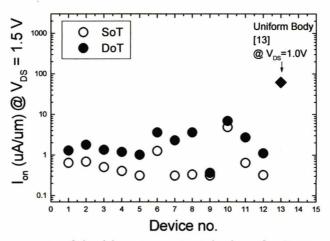

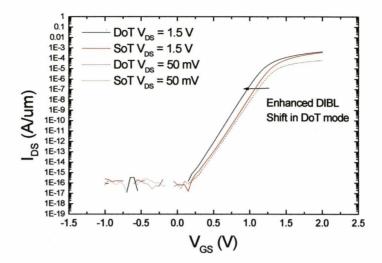

| 3.8        | Comparison of (a) $V_T$ and (b) $I_{on}/I_{off}$ in DoT and SoT modes in different process splits.              | 58       |

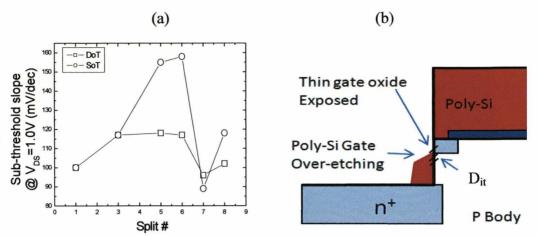

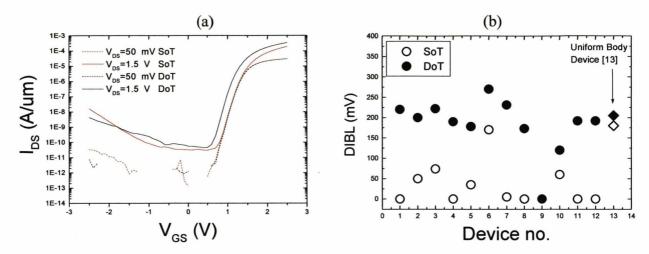

| 3.9        | (a) Comparison of sub-threshold slope in SoT and DoT; (b) Assistant diagram showing high interface              |          |

|            | states density induced on the top of the pillar due to Poly-Si gate over-etching.                               | 60       |

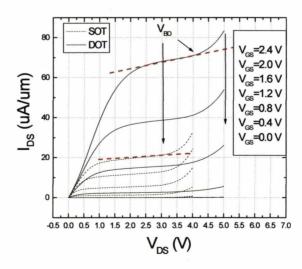

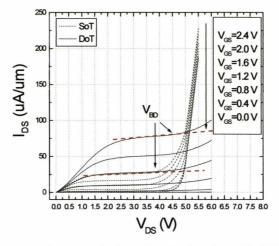

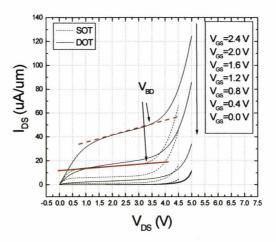

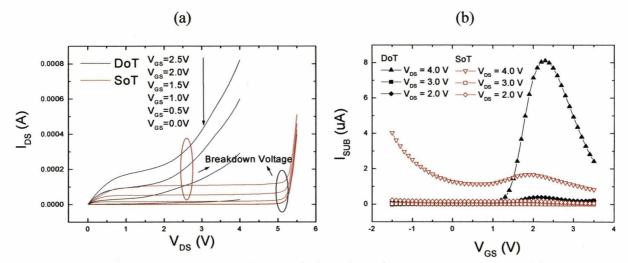

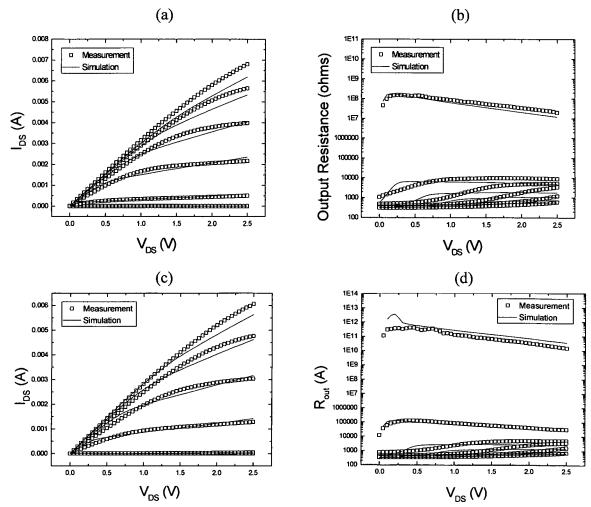

| 3.10       | Output characteristics of a device in split# 1 W=32um.                                                          | 60       |

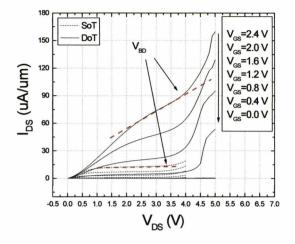

| 3.11       | Output characteristics of a device in split#3 $W = 27$ um.                                                      | 61       |

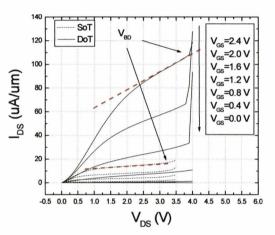

|            | Output characteristics of a device in split#5 W=52 um.                                                          | 61       |

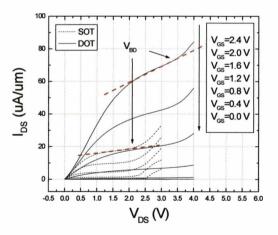

| 3.13       | Output characteristics of a device in split#6 W=27um.                                                           | 61       |

|            | Output characteristics of a device in split#7 W=27 um.                                                          | 62       |

|            | Output characteristics of a device in split#8 $W = 27$ um.                                                      | 62       |

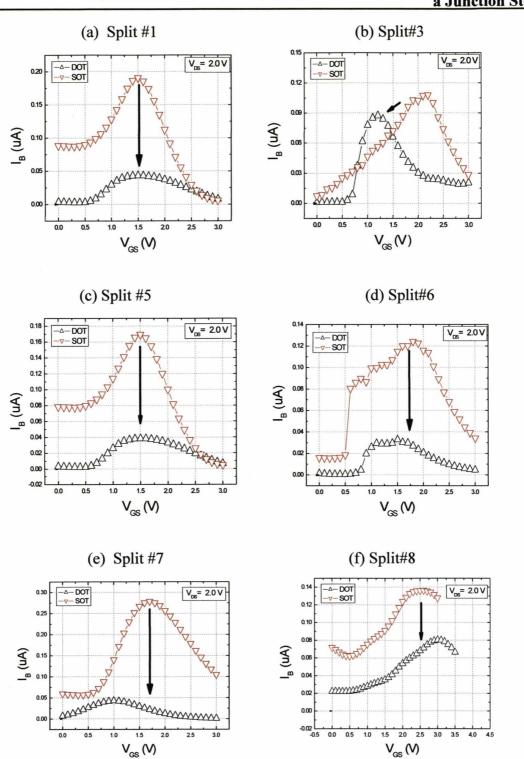

|            | Comparisons of IBVGS curves for both DoT and SoT modes for all the splits with varying drain biases             | .63      |

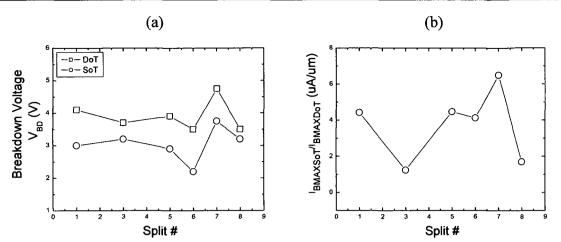

|            | Comparison of breakdown voltage and the ratio of maximum body current in DoT and SoT modes.                     | 65       |

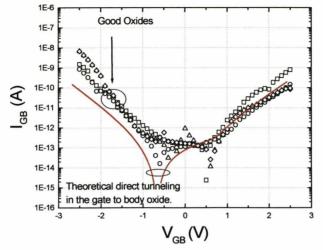

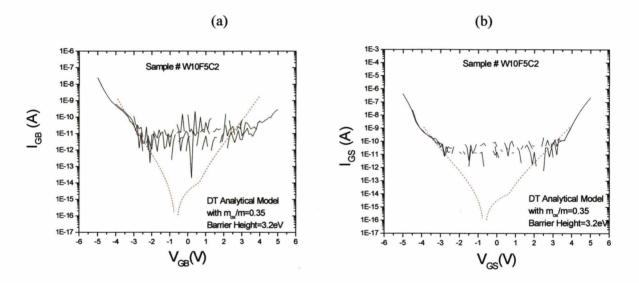

|            | Gate to body oxide current vs. gate bias; tox=3nm; area=2.1x10-9m-2; the source and drain electrodes            |          |

|            | were set to be floating.                                                                                        | 66       |

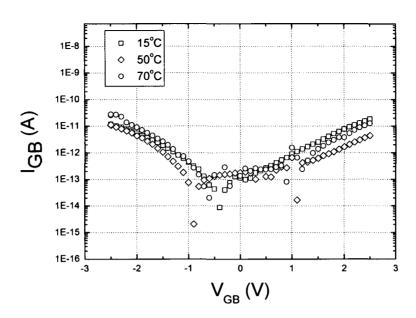

| 3.19       | Temperature dependence of the gate to body oxide leakage.                                                       | 67       |

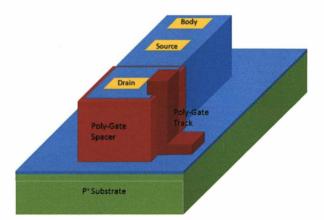

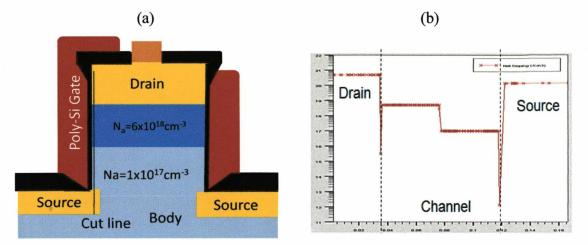

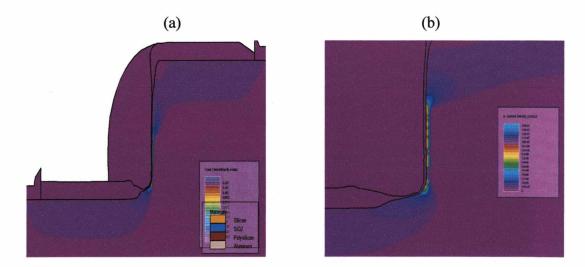

|            | 3D view of a surround gate VMOSFET-JS structure; W= 30µm.                                                       | 68       |

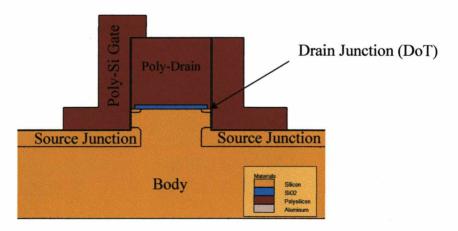

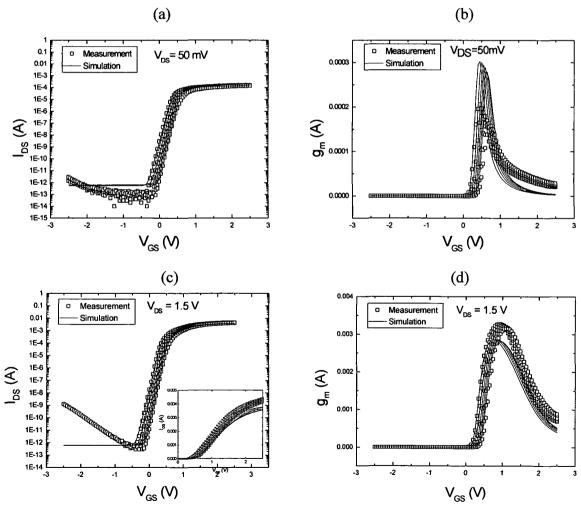

|            | 2D view of VMOSFET-JS structure with a 70nm channel length.                                                     | 68       |

|            | Transfer characteristics of fabricated device compared to the partially fitted device simulation apart fro      |          |

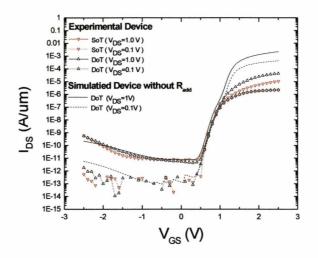

| 0.22       | on-current region. L= 70nm, $t_{ox}$ =3.0nm, $N_a$ =3.0x10 <sup>18</sup> cm <sup>-3</sup> .                     | 70       |

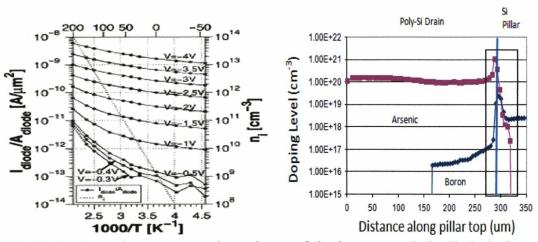

| 3 23       | (a) Reciprocal temperature dependence of the large-area drain diode leakage for different values of             |          |

| 5.45       | reverse bias. The doping level in a drain junction at the pillar top is squared in (b).                         | 71       |

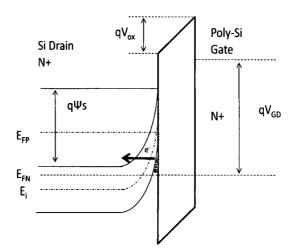

| 3 74       | Band diagram of electron tunnelling in the drain junction surface region under high negative gate bias.         |          |

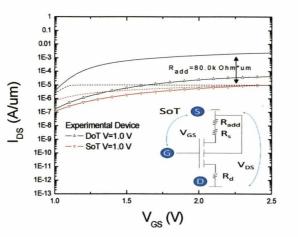

|            | Simulated on-current vs. measured on-current. $V_{GS}=2.5V$                                                     | 72<br>74 |

| 4.1        | (a) Charge sharing and (b) DIBL as a function of bottom junction depth for a VMOSFET and a                      | 7.1      |

| 4.1        | conventional lateral MOSFET.                                                                                    | 79       |

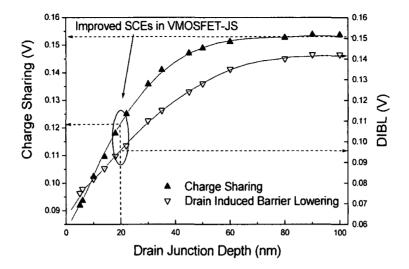

| 4.2        | Simulations of DIBL and CS as a function of reducing drain junction depth in a vertical MOSFET with             |          |

| 7.2        | junction stop (VMOSFET-JS).                                                                                     | 82       |

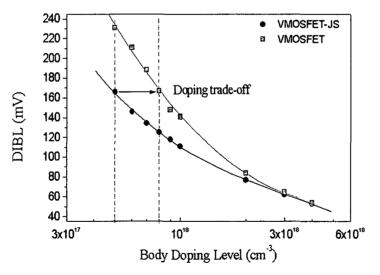

| 4.3        | DIBL as a function of body doping for VMOSFETs and VMOSFET-JSs. The devices are simulated in                    | 02       |

| 4.3        | DoT configuration with a symmetrical drain/source junction depth of 30nm.                                       | 82       |

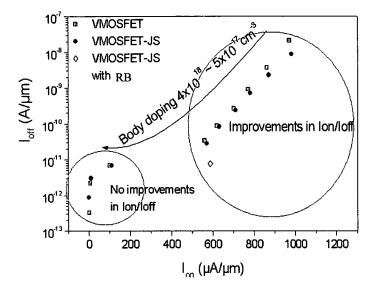

| A A        | $I_{off}$ as a function of Ion for VMOSFET and VMOSFET-JS devices with different body doping levels.            | 82<br>83 |

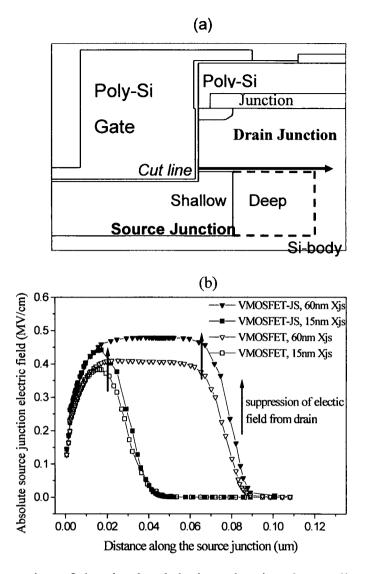

| 4.4<br>4.5 | (a) Cross-section of the simulated devices showing the cut line along which the source electric field wa        |          |

| ч.J        | simulated (b) Absolute source junction field as a function of distance along the source for VMOSFET a           |          |

|            | VMOSFET-JS devices with 60nm and 15nm source junctions.                                                         | 85       |

| ٨٢         | Simulated potential contours in a VMOSFET-JS device with asymmetrical drain and source junctions.               |          |

| 4.6        | Simulated potential contours in a visiosi E1-35 device with asymmetrical drain and source junctions.            | 0/       |

|            |                                                                                                                 |          |

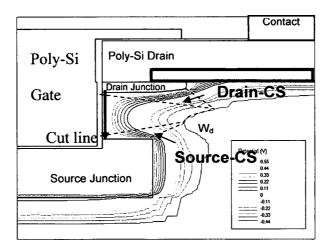

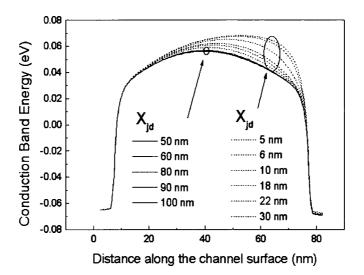

| 4.7  | Conduction band energy (cut line shown in Fig 7) as a function of distance along the channel for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •••  | MOSFET-JS devices with different drain junction depths $(X_{id})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87   |

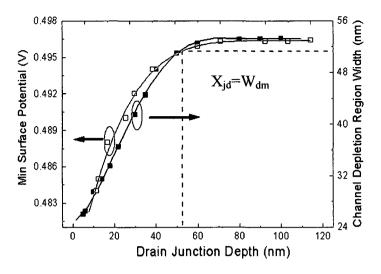

| 4.8  | Minimum surface potential and channel depletion region width as a function of drain junction depth f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | or a |

|      | MOSFET-JS device simulated with $V_{DS}$ =50mV and $V_{GS}$ =1V in DoT configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88   |

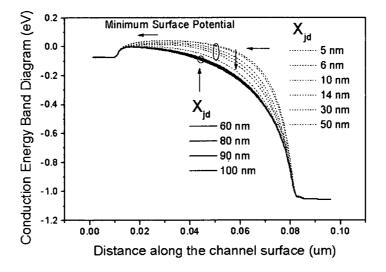

| 4.9  | Conduction band energy as a function of distance along the body surface for VMOSFET-JS devices v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /ith |

| 1.2  | different drain junction depths $(X_{jd})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89   |

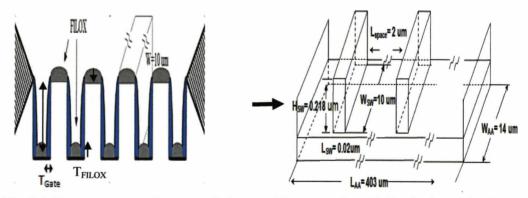

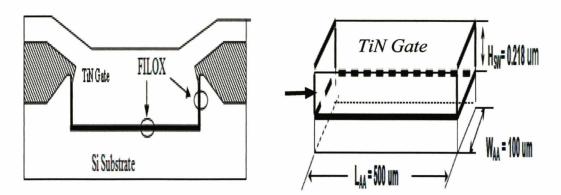

| 5.1  | Process flow for fabrication of TiN surround-gate, ultra-thin pillar.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95   |

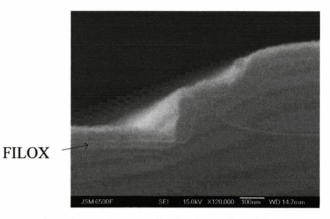

| 5.2  | SEM cross-section through a vertical edge of a pillar capacitor test structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95   |

| 5.3  | Test structure of surrounded gate pillar capacitor (fully depleted device); $t_{ox} = 8.0$ nm, $t_{FILOX} = 8.3$ nm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95   |

| 5.4  | Test structure of a pillar bottom capacitor where HSW: the height of a pillar.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96   |

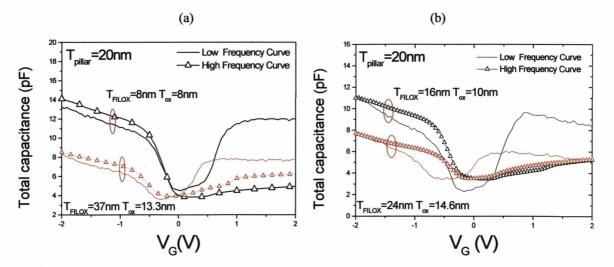

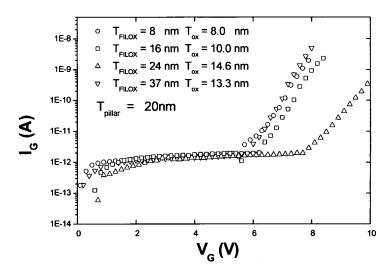

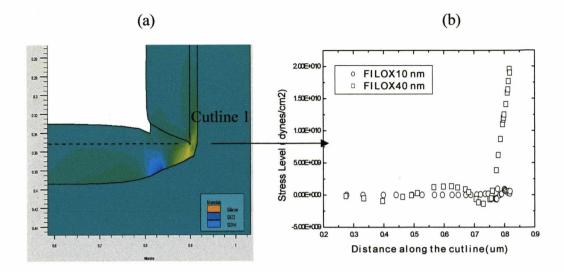

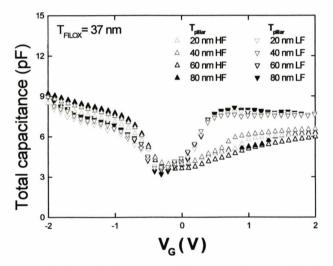

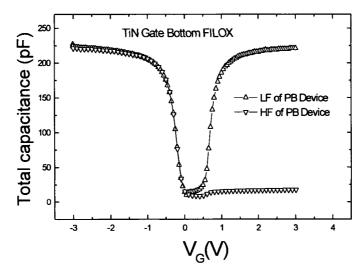

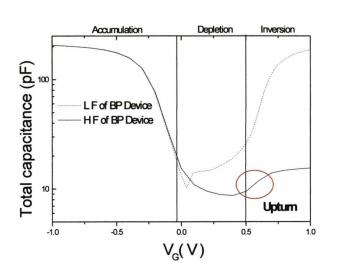

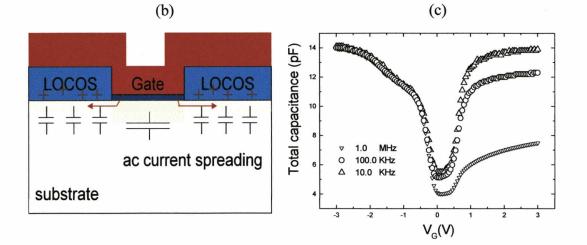

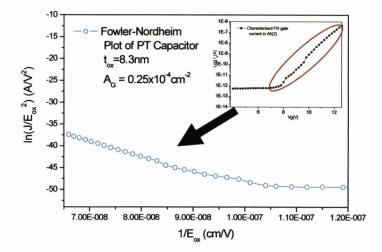

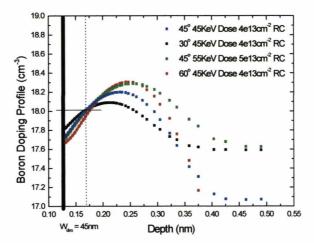

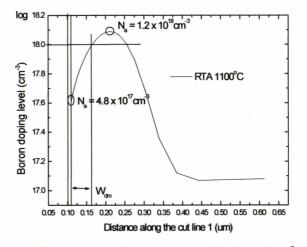

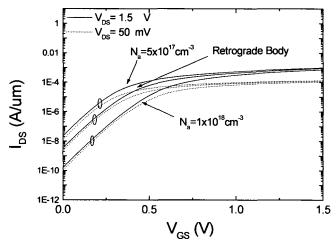

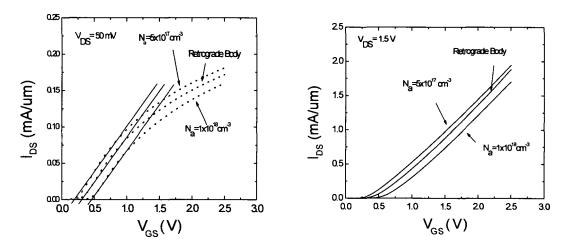

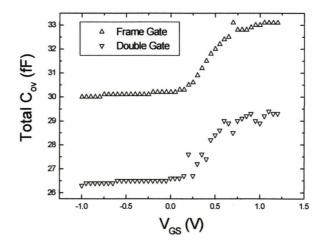

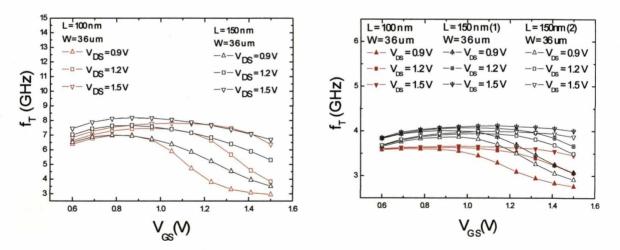

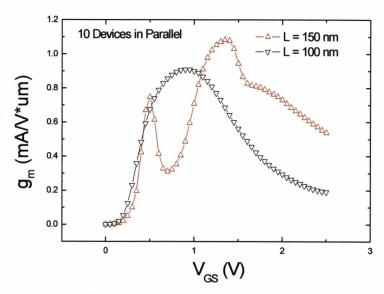

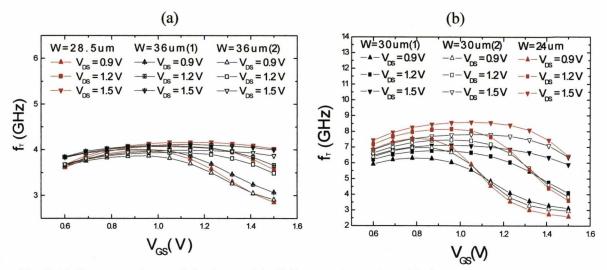

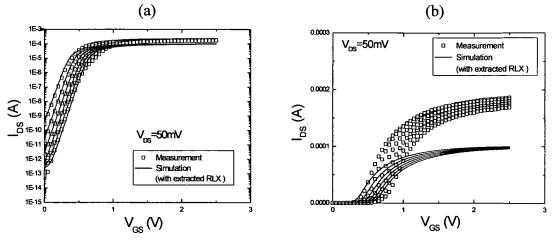

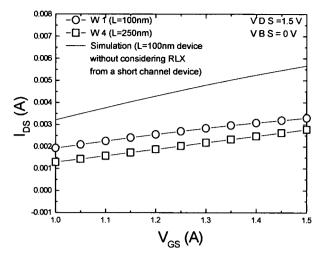

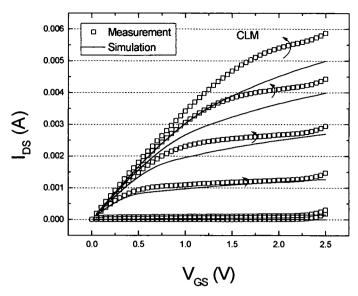

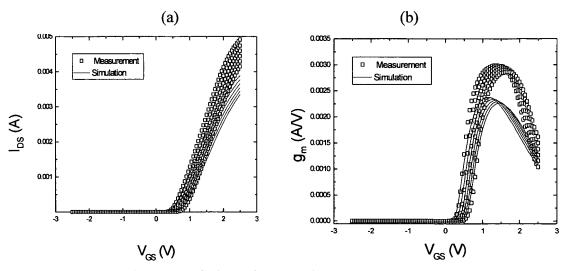

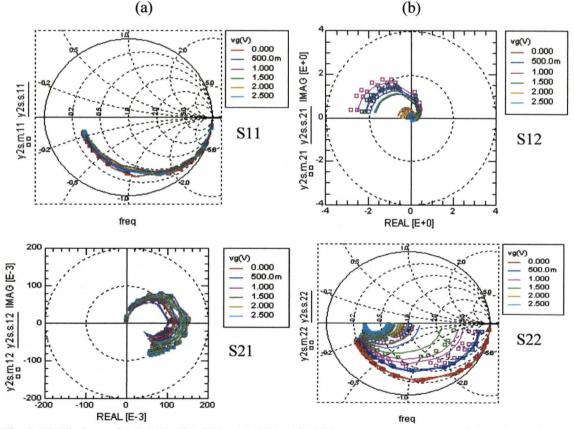

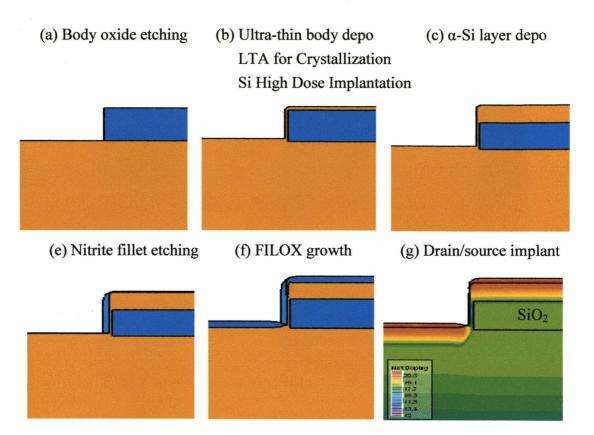

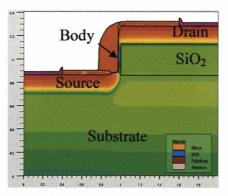

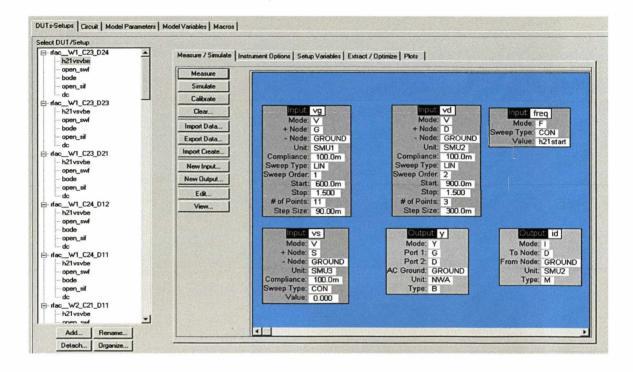

| 5.5  | C-V characteristics of ultra-thin pillar capacitors with (a) 8nm vs. 37nm FILOX; (b) 16nm vs. 24nm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97   |