# DESIGN AND PRACTICAL REALIZATION OF POLYMORPHIC CROSSTALK CIRCUITS USING 65NM TSMC PDK

## A THESIS IN

Computer and Electrical Engineering

Presented to the Faculty of the University

of Missouri-Kansas City in partial fulfillment of

the requirements for the degree

## MASTER OF SCIENCE

by

Bhavana Tejaswini Repalle

B.TECH., Vignan's Lara Institute of Technology and Science, A.P, India, 2015

Kansas City, Missouri 2019

© 2019 BHAVANA TEJASWINI REPALLE ALL RIGHTS RESERVED

# DESIGN AND PRACTICAL REALIZATION OF POLYMORPHIC CROSSTALK CIRCUITS USING 65NM TSMC PDK

Bhavana Tejaswini Repalle, Candidate for the Master of Science Degree

University of Missouri-Kansas City, 2019

#### ABSTRACT

As the technology node scales down, the coupling capacitance between the adjacent metal lines increases. With an increase in this electrostatic coupling, the unwanted signal interference also increases, which is popularly called as Crosstalk. In conventional circuits, the Crosstalk affects either functionality or performance or both. Therefore the Crosstalk is always considered as detrimental to the circuits, and we always try to filter out the Crosstalk noise from signals. Crosstalk Computing Technology tries to astutely turn this unwanted coupling capacitance into computing principle for digital logic gates [1, 2]. The special feature of the crosstalk circuits is its inherent circuit mechanism to build polymorphic logic gates[3]. Our team has previously demonstrated various fundamental polymorphic logic circuits [1-6,16-18]. This thesis shows the design of the large-scale polymorphic crosstalk circuits such as Multiplier-Sorter, Multiplier-Sorter-Adder using the fundamental polymorphic gates, and also analyzes the Power, Performance, and Area (PPA) for these large-scale designs. Similar to the basic and complex polymorphic gates, the functionality of the large-scale polymorphic circuits can also be altered using the control signals. Owing to their multi-functional embodiment in a single circuit, polymorphic circuits find a myriad of useful applications such as reconfigurable system design, resource sharing, hardware security, and fault-tolerant circuit design, etc. [3]. Also, in this thesis, a lot of studies have been done on the variability (PVT analysis) of Crosstalk Circuits. This PVT variation analysis establishes the circuit design requirements in terms of coupling capacitances and fan-in limitation that allows reliable operation of the Crosstalk gates under Process, Voltage and Temperature variations. As an example, I also elaborate on the reason for which the full adder can't be implemented as a single gate in the crosstalk circuit-style at lower technology nodes.

Though we designed a variety of basic and complex logic gates and crosstalk polymorphic gates, the biggest question is "Will these crosstalk gates work reliably on silicon owing to their new circuit requirements and technological challenges?". Trying to answer the above question, the whole thesis is mainly focused on the physical implementation of the crosstalk gates at 65nm. I will detail the steps that we have performed while designing the crosstalk circuits and their layouts, the challenges we faced while implementing the new circuit techniques using conventional design approaches and PDK, and their solutions, specifically during layout design and verification.

The other potential application of crosstalk circuits is in non-linear analog circuits: Analog-to-Digital Converter (ADC) [4], Digital-to-Analog Converter (DAC), and Comparator. In this thesis, I have shown how the deterministic charge summation principle that is used in digital crosstalk gates can also be used to implement the non-linear analog circuits.

#### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Computing and Engineering, have examined a thesis titled "Design and Practical Realization of Polymorphic Crosstalk Circuits Using 65nm TSMC PDK" presented by Bhavana Tejaswini Repalle, candidate for the Master of Science degree, and certify that in their opinion it is worthy of acceptance.

### Supervisory Committee

Mostafizur Rahman, Ph.D., Committee Chair Department of Computer Science & Electrical Engineering

Masud Chowdhury, Ph.D. Department of Computer Science & Electrical Engineering

Ghulam Chaudhry, Ph.D. Chair Department of Computer Science & Electrical Engineering

## CONTENTS

| A  | BSTRACT                                                                    | iii    |

|----|----------------------------------------------------------------------------|--------|

| IL | LUSTRATIONS                                                                | . viii |

| T  | ABLES                                                                      | xi     |

| A  | CKNOWLEDGEMENTS                                                            | xii    |

| 1  | INTRODUCTION AND MOTIVATION                                                | 1      |

| 2  | POLYMORPHIC CROSSTALK CIRCUIT DESIGN                                       | 4      |

|    | 2.1 Basic Polymorphic Crosstalk Gates                                      | 4      |

|    | 2.2 Large – Scale Polymorphic Crosstalk Circuits                           | 6      |

|    | 2.2.1 Multiplier – Sorter Polymorphic Crosstalk Circuit                    | 6      |

|    | 2.2.2 Multiplier – Sorter – Adder Polymorphic Crosstalk Circuit            | 8      |

| 3  | PRACTICAL REALIZATION OF CROSSTALK CIRCUITS                                | 12     |

|    | 3.1 Calibre and TSMC libraries setup                                       | 12     |

|    | 3.2 Physical Implementation of Crosstalk Polymorphic Circuits              | 12     |

|    | 3.3 Observations after installing the PDK                                  | 14     |

|    | 3.4 Choosing the Coupling Capacitance                                      | 18     |

|    | 3.5 Schematic and Symbol Design                                            | 21     |

|    | 3.6 ADE – XL Schematic Simulations in different PVT corners                | 22     |

|    | 3.7 Crosstalk Gates Layout Design                                          | 23     |

|    | 3.8 Physical Verification and Extraction of the layouts                    | 25     |

|    | 3.9 Simulation of the Layout Netlist at different PVT corners              | 29     |

| 4  | PVT VARIATION ANALYSYS                                                     | 31     |

|    | 4.1 Inverter DC characteristics at TSMC 65nm node at different PVT Corners | 31     |

| 4.1.1 Considering only process variation                                      |    |

|-------------------------------------------------------------------------------|----|

| 4.1.2 Considering Process and Temperature Variations                          |    |

| 4.2 Effect of the functionality margins on the fan-in of the crosstalk        | 34 |

| 5 DIFFICULTIES OR ERRORS IN IN LAYOUT DESIGN AND FULL ODETAILS                |    |

| 5.1 Below are the errors and its solutions that we faced in the layout design |    |

| 5.1.1 Grid Settings                                                           |    |

| 5.1.2 Warning caused while performing LVS                                     |    |

| 5.1.3 XDB issue while running Calibre PEX                                     |    |

| 5.1.4 Error while compiling the PEX rules file                                |    |

| 5.2 Details of the Full-Chip                                                  | 40 |

| 6 POTENTIAL MISCELLENEOUS APPLICATIONS                                        | 43 |

| 6.1 Crosstalk DAC                                                             | 43 |

| 6.2 Crosstalk ADC                                                             | 46 |

| 6.3 Comparator                                                                |    |

| 6.4 Discussion                                                                | 49 |

| 7 CONCLUSION AND FUTURE WORK                                                  | 52 |

| REFERENCES                                                                    | 54 |

| VITA                                                                          | 57 |

## ILLUSTRATIONS

| Figure                                                                               | Page   |

|--------------------------------------------------------------------------------------|--------|

| Figure. 1.1 Crosstalk Principle                                                      | 1      |

| Figure. 1.2 Crosstalk AND gate schematic and Simulation Result                       | 2      |

| Figure. 2.1 CT-P AND-OR gate schematic and Simulation Result                         | 4      |

| Figure 2.2 Crosstalk Multiplier – Sorter Circuit Diagram                             | 7      |

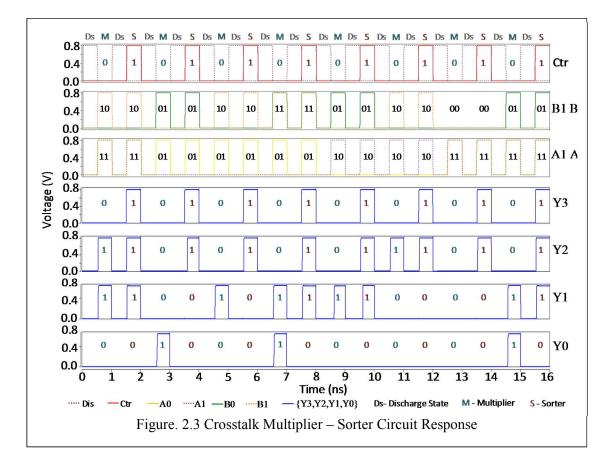

| Figure. 2.3 Crosstalk Multiplier – Sorter Circuit Response                           | 8      |

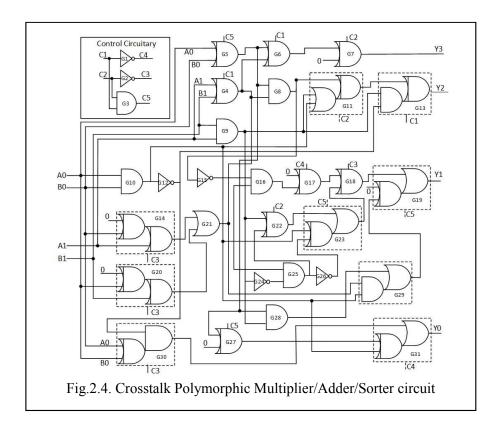

| Figure.2.4 Crosstalk Polymorphic Multiplier/Adder/Sorter circuit                     | 9      |

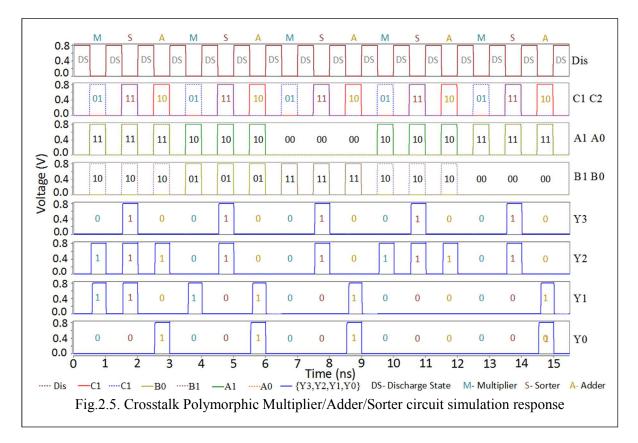

| Figure.2.5 Crosstalk Polymorphic Multiplier/Adder/Sorter circuit simulation response | 10     |

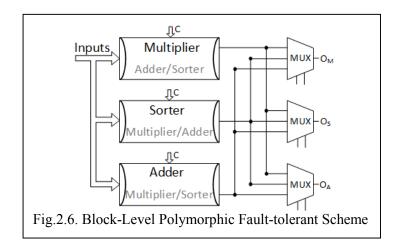

| Figure.2.6 Block-Level Polymorphic Fault-tolerant Scheme                             | 11     |

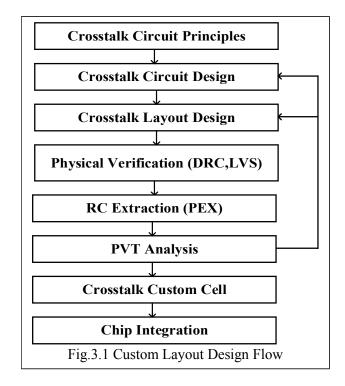

| Figure.3.1 Custom Layout Design Flow                                                 | 14     |

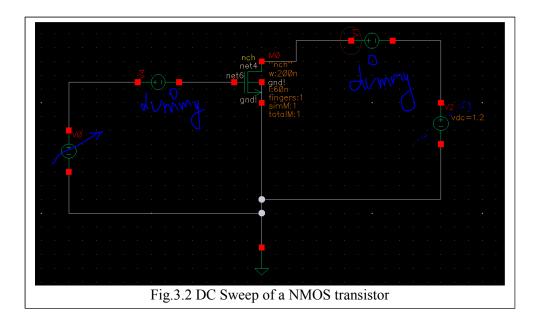

| Figure.3.2 DC Sweep of a NMOS transistor                                             | 15     |

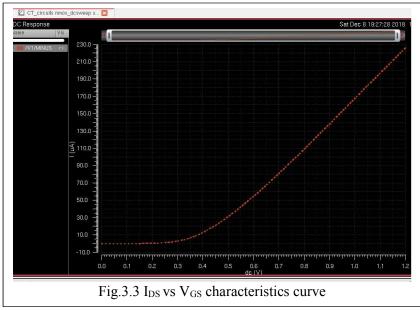

| Figure.3.3 $I_{DS}$ vs $V_{GS}$ characteristics curve                                |        |

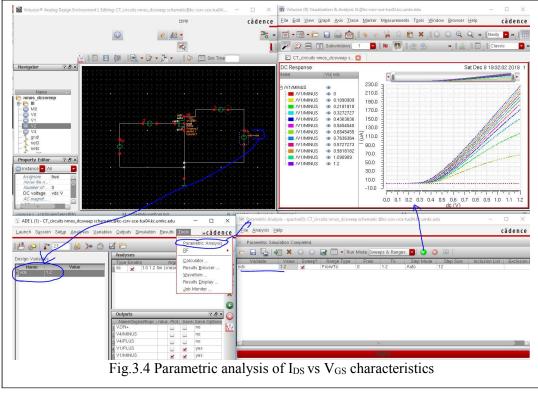

| Figure.3.4 Parametric analysis of I <sub>DS</sub> vs V <sub>GS</sub> characteristics | 16     |

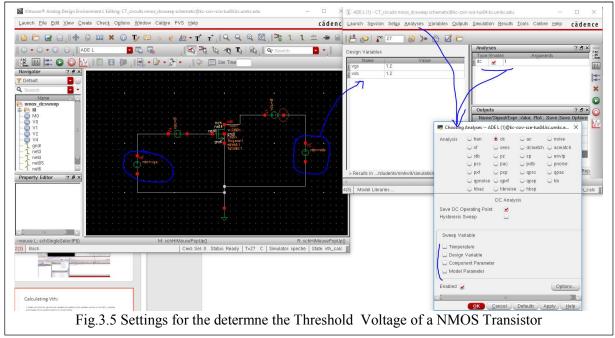

| Figure.3.5 Settings for the determine the Threshold Voltage of a NMOS Transistor     | 16     |

| Figure.3.6 Properties of the NMOS Transistor                                         | 17     |

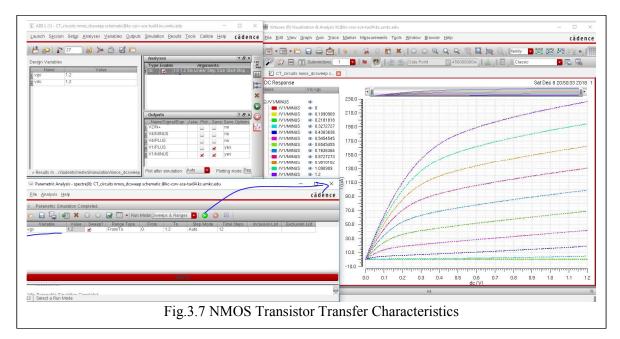

| Figure.3.7 NMOS Transistor Transfer Characteristics                                  | 17     |

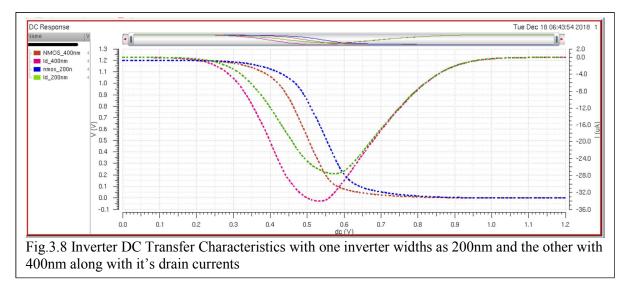

| Figure.3.8 Inverter DC Transfer Characteristics with one inverter widths as 200nm a  | nd the |

| other with 400nm along with it's drain currents                                      |        |

| Figure.3.9 Settings to get the cap values at different nodes                         | 19     |

| Figure.3.10 Settings to print the cap values                                         | 20     |

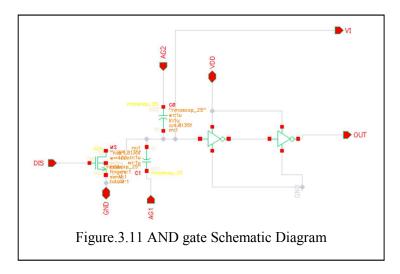

| Figure.3.11. AND gate Schematic Diagram                                              | 21     |

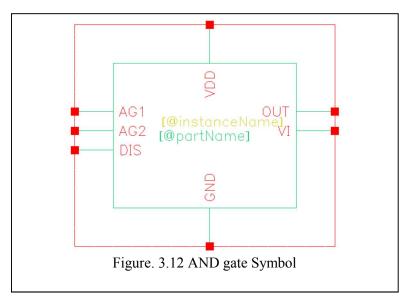

| Figure.3.12. AND gate Symbol                                                           | 21   |

|----------------------------------------------------------------------------------------|------|

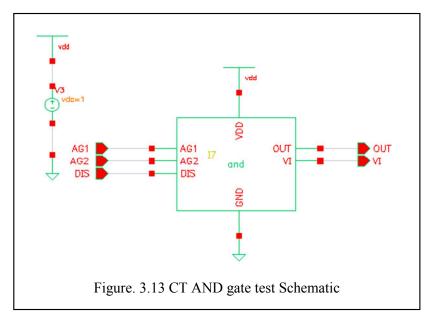

| Figure.3.13. CT AND gate test Schematic                                                | 22   |

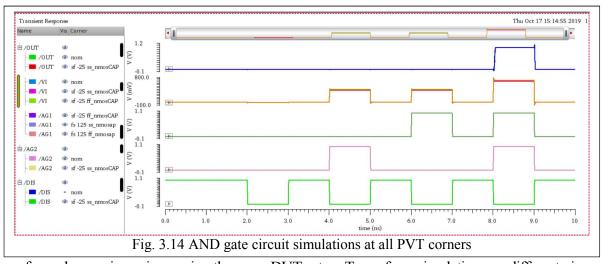

| Figure.3.14 AND gate circuit simulations at all PVT corners                            | 23   |

| Figure.3.15 Setting the grid as per the technology node                                | 24   |

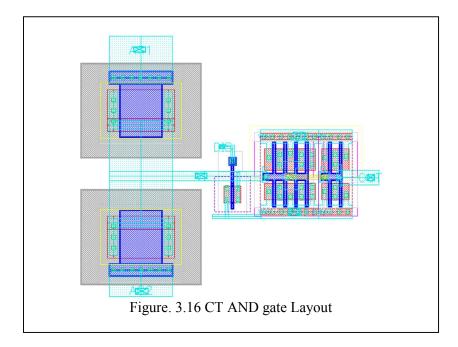

| Figure.3.16 CT AND gate Layout                                                         | 24   |

| Figure.3.17 Calibre Integration with Virtuoso                                          | 25   |

| Figure.3.18 DRC violations at the circuit level                                        | 26   |

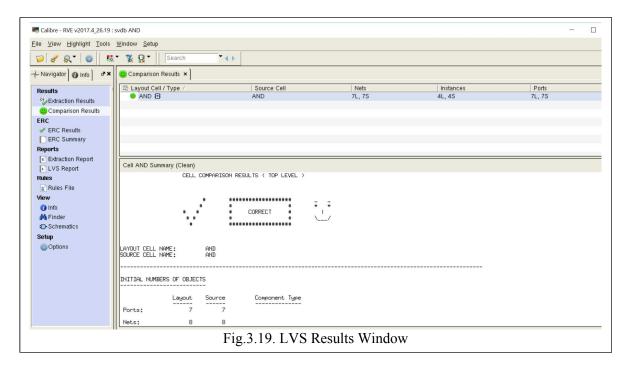

| Figure.3.19 LVS Results Window                                                         | 26   |

| Figure.3.20 PEX Results Window                                                         | 27   |

| Figure.3.21 Calibre View Setup                                                         | 28   |

| Figure.3.22 ADE – XL Window settings                                                   | 29   |

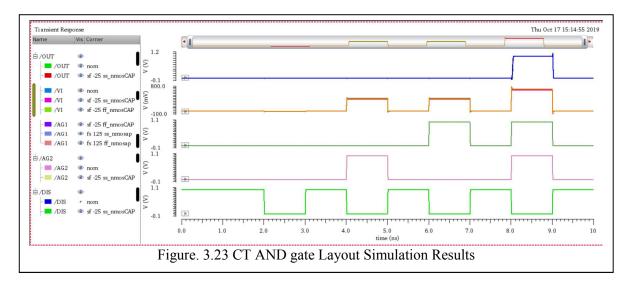

| Figure.3.23 CT AND gate Layout Simulatio Results                                       | 29   |

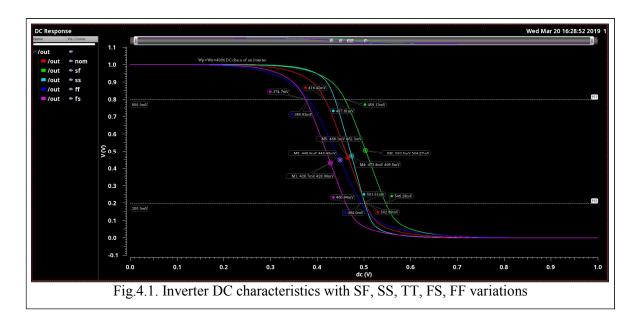

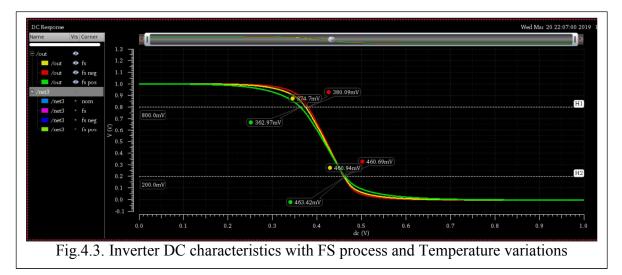

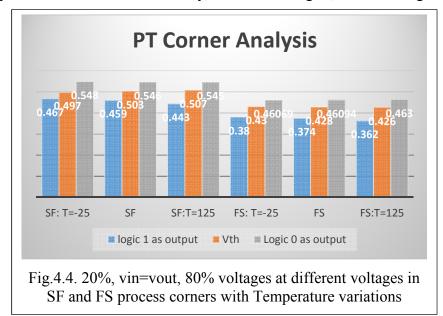

| Figure.4.1 Inverter DC characteristics with SF, SS, TT, FS, FF variations              | 32   |

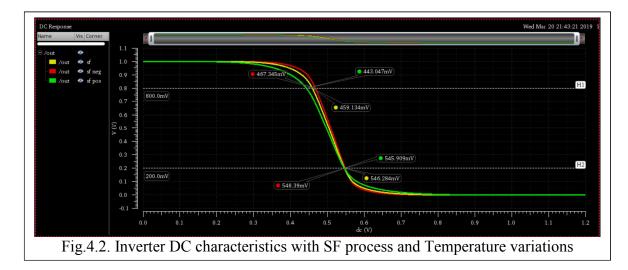

| Figure.4.2 Inverter DC characteristics with SF process and Temperature variations      | 33   |

| Figure.4.3 Inverter DC characteristics with FS process and Temperature variations      | 33   |

| Figure.4.4 20%, vin=vout, 80% voltages at different voltages in SF and FS process corr | iers |

| with Temperature variations                                                            | 34   |

| Figure.5.1 Default Grid settings                                                       | 36   |

| Figure.5.2 Grid settings as per the TSMC 65nm PDK                                      | 37   |

| Figure.5.3 Warning while running the LVS                                               | 37   |

| Figure.5.4 LVS run Settings window                                                     | 38   |

| Figure.5.5 Calibre PEX Warning issue                                                   | 38   |

| Figure 5.6 Calibre PEX Error                                                           | 39   |

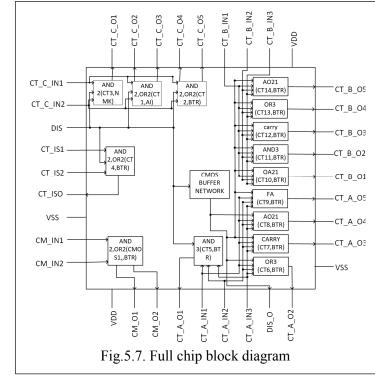

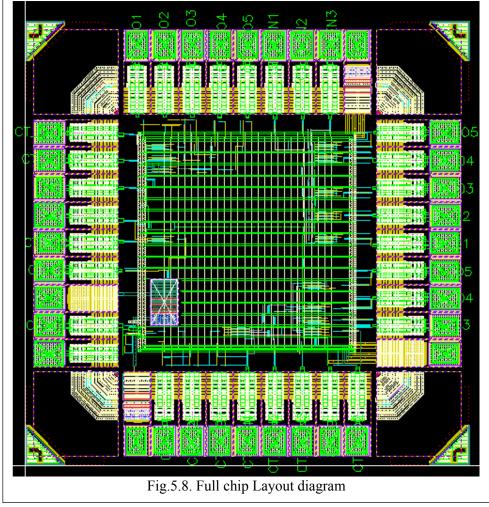

| Figure.5.7 Full chip block diagram                                                        | 39 |

|-------------------------------------------------------------------------------------------|----|

| Figure.5.8 Full chip Layout diagram                                                       | 40 |

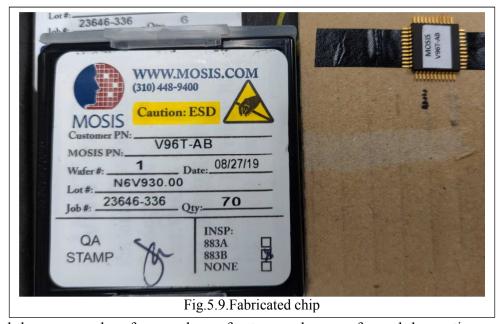

| Figure.5.9 Fabricated chip                                                                | 41 |

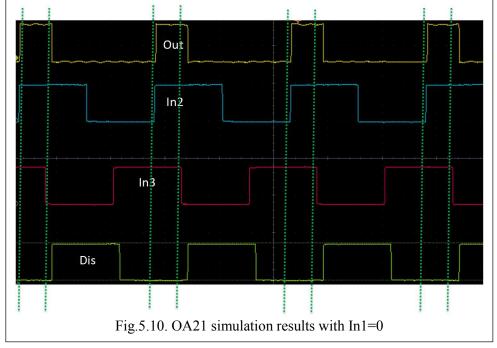

| Figure.5.10 OA21 simulation results with In1=0                                            | 41 |

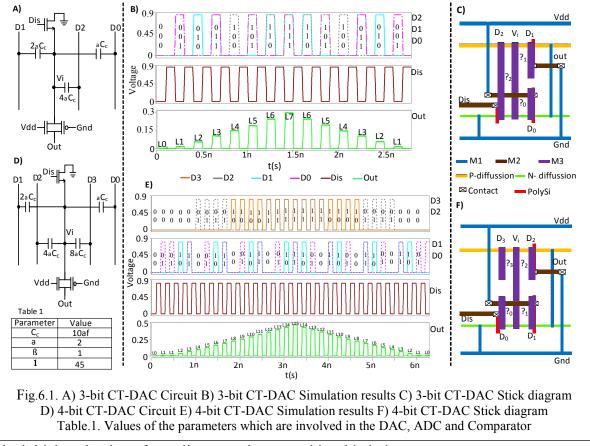

| Figure.6.1 3-bit and 4-bit CT-DAC Circuit, Simulation results, 3-bit CT-DAC Stick diagram | 45 |

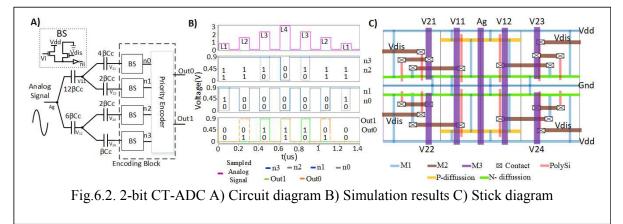

| Figure.6.2 2-bit CT-ADC Circuit diagram, Simulation results and Stick diagram             | 47 |

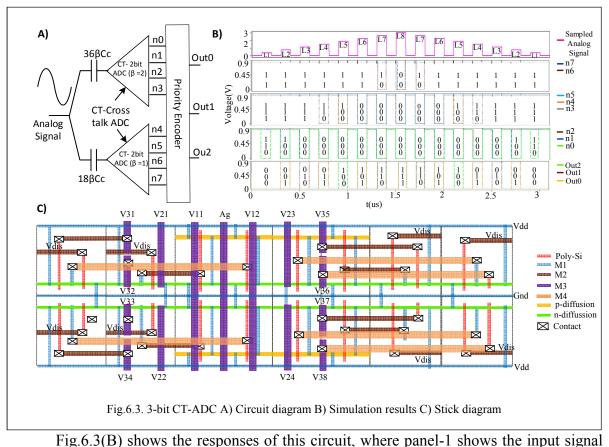

| Figure.6.3 3-bit CT-ADC Circuit diagram, Simulation results and Stick diagram             | 48 |

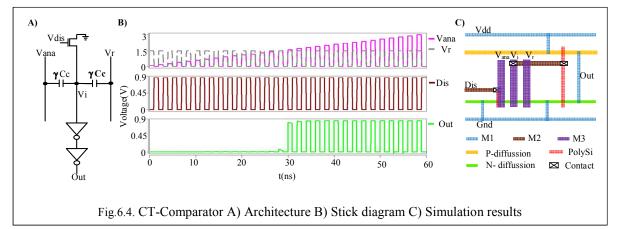

| Figure.6.4 Comparator Circuit diagram, Simulation results and Stick diagram               | 49 |

## TABLES

| Tables                                                           | Page |

|------------------------------------------------------------------|------|

| Table. 1 Crosstalk logic design table for polymorphic gates      | 5    |

| Table.2 TSMC 65nm PMOS and NMOS transistor properties            | 18   |

| Table. 2 Design Metrics for Crosstalk non-linear analog circuits | 50   |

| Table. 3 Benchmarking results of crosstalk circuits with CMOS    | 51   |

#### ACKNOWLEDGEMENTS

Foremost, I would like to express my sincere gratitude to my advisor Dr. Mostafizur Rahman for his continuous motivation and guidance in research and my thesis work. His guidance helped me throughout my master's degree, in writing and reviewing the IEEE papers. He showed me the direction whenever I was stuck in my research and pushed me to find out the reasons for it. He allowed me to audit all his courses which enhanced my knowledge in the field. Moreover, he gave me the freedom to attend all meetings and presentations organized by him from which I have learned a lot.

I am thankful to my fellow lab mate and mentor Naveen Kumar Macha who guided me throughout the Crosstalk work. He gave me the training on the concepts and tools in my earlier days in the VLSI field, also directed me to the topics that I need to learn before getting started on my work. He also gave me guidance on how to express and write my work and present it to my advisor.

I am also grateful to my fellow lab mate and mentor Wafi Danesh for his guidance and support in the Multi-Valued Logic (MVL) research work. He helped me to get acquainted with our research lab and the work and continued his guidance throughout my studies.

I would also like to thank Md Arif Iqbal and Sandeep Reddy Geedipally for their guidance in writing the papers and the knowledge of the tools.

#### CHAPTER 1

#### INTRODUCTION AND MOTIVATION

Device scaling and interconnect bottleneck are among the major challenges for CMOS scaling. Furthermore, signal integrity issues like crosstalk – leakage of charge between capacitively coupled nets among neighboring signal lines are becoming inexorable [1]. Our team proposed the Crosstalk Computing which astutely turns this detrimental effect into an advantage by engineering the interference among signal lines. Crosstalk Technology can potentially solve scaling challenges by reducing device and interconnect scaling requirements while complying with the existing manufacturing paradigm.

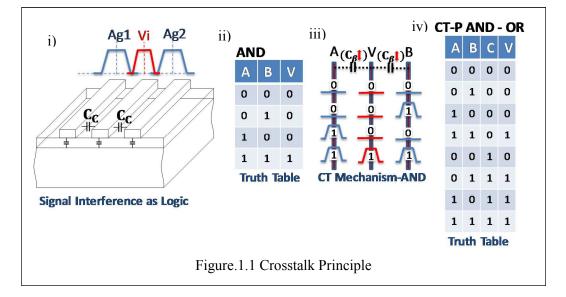

The Fig.1.1(i) illustrates the aggressor-victim scenario of crosstalk-logic. It shows the capacitive interference of the signals for logic computation – the transition of the signals on two rare end aggressor metal lines (Ag1 and Ag2) induce a resultant summation charge on the victim metal line (Vi) through capacitive coupling C<sub>C</sub>. Since this phenomenon follows the charge conservation principle, the victim net voltage is deterministic in nature and possesses the information about signals on two aggressor nets; its magnitude depends upon the coupling

strength between the aggressors and the victim net. The coupling capacitance is directly proportional to the relative permittivity of the dielectric and lateral area of metal lines (which is length times the vertical thickness of metal lines) and inversely proportional to the distance of separation of metal lines. Tuning the coupling capacitance values using the variables mentioned above provides the engineering freedom to tailor the induced summation signal to the specific logic implementation [1]. Fig.1.1 (ii) shows the AND gate truth table where the output of the gate is logic 1 only when both the input signals are logic 1. Fig.1.1 (iii) shows the intuition of the crosstalk AND gate. By incorporating an additional control aggressor, the victim node can be biased to alter the behavior of the AND gate to the OR gate, thus polymorphic gates can be constructed. Fig.1.1 (iv) shows the truth table of polymorphic AND–R gate where the control signal is C. When C=0, the gate should behave as AND gate and when C=1 the gate should behave as the OR gate. This could be enabled by properly engineering the coupling capacitances and the circuit that is specific to Crosstalk Computing.

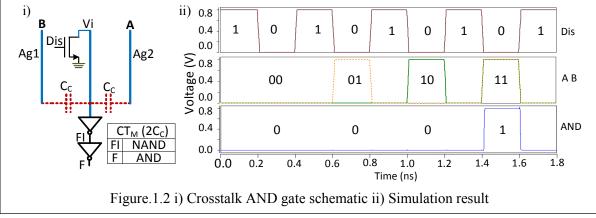

The actual circuit techniques are discussed next. Fig.1.2 (i) shows the Crosstalk AND circuit in which input aggressor nets (A and B acting as Ag1 and Ag2) are coupled to victim net (Vi) through coupling capacitance C<sub>C</sub>. A discharge transistor driven by a '*Dis*' signal and an inverter is connected to '*Vi*' net as shown in the figure. The CT-logic operates in two states, logic Evaluation State (ES) and

discharge state (DS). During ES, the rise transitions on aggressor nets induce a proportional linear summation voltage on Vi (through couplings) which is connected to a CMOS inverter. The inverter acts as a threshold function. During the discharge state (enabled by *Dis* signal), the floating victim node is shorted to ground through the discharge transistor, which ensures correct logic operation during the next logic evaluation state by clearing off the value from the previous logic operation. The simulation response of the designed AND gate is shown in Fig.1.2 (ii). The first panel in the figure shows the discharge pulse (Dis), the second panel shows two input signals (*A* and *B*) with 00 to 11 combinations given through successive evaluation stages (when *Dis*=0). The third panel shows the output response of the AND gate. It is to be noted that, as the victim node is discharged to the ground in every DS (*Dis*=1), the outputs of these gates are also logic high.

The rest of the chapters in this thesis are organized as follows: Chapter 2 presents the implementation of large-scale polymorphic circuits and their Power, Performance, and Area (PPA) results. Chapter 3 elaborates on the variability analysis at different processes, voltage, and temperatures (PVT). It also discusses the realization of the high fan-in gates. Chapter 4 presents the physical implementation of the digital crosstalk circuits using 65nm TSMC PDK and its simulation results. Chapter 5 shows difficulties/errors that occurred while designing the crosstalk circuits in silicon using TSMC 65nm PDK. Chapter 6 discusses the nonlinear analog crosstalk circuits and how we can realize them using the charge conservative principle, and its drawbacks. Chapter 7 concludes with the discussion of the benefits of our approach, and what we envision to accomplish in the near future.

#### CHAPTER 2

#### POLYMORPHIC CROSSTALK CIRCUIT DESIGN

This chapter introduces the design of the basic polymorphic circuits/gates based on the Crosstalk Computing principle and cascading them to build the large-scale polymorphic circuits.

#### 2.1 Basic Polymorphic Crosstalk Gates

The polymorphic logic gates exhibit multiple logic behaviors by virtue of altering a control signal, as a result, it increases the logic expressibility of a circuit. A wide range of polymorphic gates can be implemented using crosstalk circuit techniques, out of which, I show here the circuit reconfigurable AND-OR gates. The technique can be extended to implement many other reconfigurable gates such as OA21-AO21, AND3-AO21, AO21-OR3, etc. All these circuits switch the logic behavior by using an additional control aggressor.

The operation of CT logic gates can be represented functionally using a crosstalk margin function  $CT_MI$ , which specifies that the inverter of the CT-logic gate flips its state only when victim node sees the input transitions through the total coupling greater than or equal to C. For example, as shown in the Fig.1.1(i), AND CT-margin function is  $CT_M(2C_C)$ , which states that the inverter flips its state only when the victim node sees the input transitions through total coupling greater

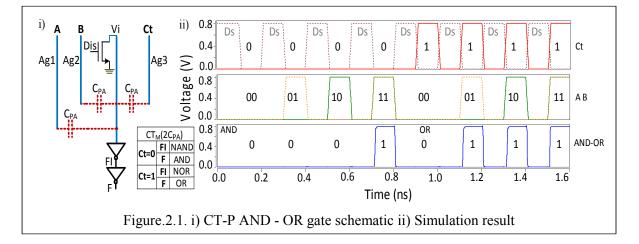

than or equal to  $2C_C$ , i.e. when both inputs are high. For the CT-margin function of  $CT_M(C_C)$ , the same gate behaves like an OR gate [3]. These two functionalities can be implemented in a single gate using the control Signal *(Ct)* as shown in Fig. 2.1.

Fig.2.1 shows the Crosstalk Polymorphic (CT-P) AND-OR circuit and its circuit response. As shown in the circuit diagram, inputs (*A* and *B*) and control aggressor (*Ct*) has the same coupling C<sub>PA</sub>. *FI* stage in the circuit (Fig.2.1(i)) gives inverting functions (NAND/NOR) and the *F* stage gives noninverting functions (AND/OR). The margin function for the AND-OR cell is  $CT_M$  (2C<sub>PA</sub>). When control *Ct=*0 it operates as AND, whereas, when *Ct=*1 the *Ct* aggressor (*Ag3*) augments an extra charge through the coupling capacitance C<sub>PA</sub>, hence the cell is now biased to operate as an OR gate. Therefore, the transition of either *A* or *B* is now sufficient to flip the inverter. The same response can be observed

|                |                        | -              | ΓA             | BL             | E 1             |     |                                    |          |

|----------------|------------------------|----------------|----------------|----------------|-----------------|-----|------------------------------------|----------|

| CROSSTALK LOGI | C DES                  | SIGI           | ΝT             | AB             | LE I            | FOR | POLYM                              | ORPHIC ( |

| Gate           | C <sub>C</sub><br>(fF) | w <sub>1</sub> | w <sub>2</sub> | w <sub>3</sub> | w <sub>Ct</sub> | Ct  | Margin<br>Fuction                  | Function |

| AND3-OR3       | 1                      | 1              | 1              | 1              | 2               | 0   | CT <sub>M</sub> (3C <sub>c</sub> ) | AND3     |

| ANDS-ORS       | T                      | 1              | 1              | 1              | 2               | 1   | $CT_M(C_C)$                        | OR3      |

| AND3-CARRY     | 0.9                    | 1              | 1              | 1              | 1               | 0   | CT <sub>M</sub> (3C <sub>c</sub> ) | AND3     |

| AND3-CARRY     | 0.9                    | T              | T              | T              | Т               | 1   | CT <sub>M</sub> (2C <sub>C</sub> ) | CARRY    |

|                | 4.5                    | 1              | 1              | 1              | 1               | 0   | CT <sub>M</sub> (2C <sub>C</sub> ) | CARRY    |

| CARRY-OR3      | 4.5                    | 1              | 1              | T              | Т               | 1   | CT <sub>M</sub> (C <sub>C</sub> )  | OR3      |

| 0.021 0.021    | 0.7                    | 1              | 1              | 2              | 1               | 0   | CT <sub>M</sub> (3C <sub>c</sub> ) | OA21     |

| 0A21-A021      | 0.7                    | T              | Т              | 2              | Т               | 1   | CT <sub>M</sub> (2C <sub>C</sub> ) | AO21     |

| AND3-AO21      | 0.28                   | 1              | 1              | 2              | 2               | 0   | CT <sub>M</sub> (4C <sub>c</sub> ) | AND3     |

| AND5-AUZI      | 0.28                   | T              | T              | 2              | 2               | 1   | CT <sub>M</sub> (2C <sub>C</sub> ) | AO21     |

| AND3-OA21      | 0.21                   | 1              | 1              | 2              | 1               | 0   | CT <sub>M</sub> (4C <sub>C</sub> ) | AND3     |

| ANDS-OAZI      | 0.21                   | Т              | 1              | 2              | 1               | 1   | CT <sub>M</sub> (3C <sub>C</sub> ) | 0A21     |

| OA21-OR3       | 0.97                   | 1              | 1              | 2              | 2               | 0   | CT <sub>M</sub> (3C <sub>C</sub> ) | 0A21     |

| 0421-013       | 0.57                   | 1              | -              | 2              | 2               | 1   | $CT_M(1C_C)$                       | OR3      |

| AO21-OR3       | 3                      | 1              | 1              | 2              | 1               | 0   | CT <sub>M</sub> (2C <sub>C</sub> ) | 0A21     |

| A021-013       | 5                      | 1              | -              | 2              | 1               | 1   | $CT_M(1C_C)$                       | OR3      |

| CARRY-AO21     | 2.2                    | 2              | 2              | 3              | 1               | 0   | $CT_M(4C_C)$                       | CARRY    |

| CANT-AUZI      | 2.2                    | 2              | 2              | 5              | -               | 1   | CT <sub>M</sub> (3C <sub>C</sub> ) | AO21     |

| OA21-CARRY     | 0.6                    | 2              | 2              | 3              | 1               | 0   | CT <sub>M</sub> (5C <sub>C</sub> ) | OA21     |

| UALI-CANNI     | 0.0                    | 2              | 2              | 5              | -               | 1   | CT <sub>M</sub> (4C <sub>C</sub> ) | CARRY    |

in the simulation plots shown in Fig.2.1(i).

The first panel shows the discharge (*Dis*) and control ( $C_t$ ) signals, the second panel shows the input combinations fed through *A* and *B*, and 3<sup>rd</sup> panel shows the response at stage F. It can be observed that the circuit responds as AND when Ct=0 for first four input combinations (00 to 11), whereas, it responds as OR when Ct=1 during next four input combinations (00 to 11). The polymorphism is shown between many logic functions[3]. Based on coupling capacitance requirements to implement a given logic function, we categorize the logics in Crosstalk Computing into two types. A homogeneous logic if all the aggressors need equal coupling capacitances, and heterogeneous logic if aggressors need unequal coupling capacitances. The polymorphism can be achieved between homogeneous logic: AO21-OA21; and homogeneous to heterogeneous logic: AO21-AND3, AO21-OR3, AO21-CARRY, OA21-AND3, OA21-OR3, OA21-CARRY, etc. Table.1 presents the crosstalk logic design table for CT polymorphic gates. The margin functions, as listed in the table, transform from one functionality to others when Ct transitions from 0 to 1 and vice-versa[5].

2.2 Large – Scale Polymorphic Crosstalk Circuits

This section shows the design of Multiplier-Sorter Crosstalk Polymorphic Circuits and Multiplier-Sorter-Adder Polymorphic Crosstalk Circuits.

#### 2.2.1 Multiplier-Sorter Polymorphic Crosstalk Circuit

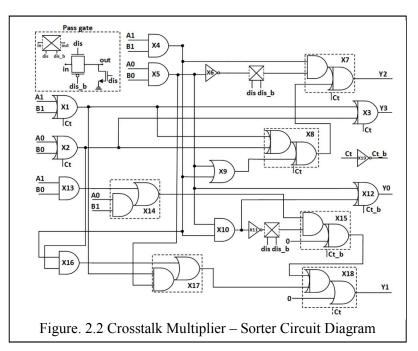

To show the potential of CT polymorphic logic gates, an example circuit of a 2-bit multiplier-sorter (Fig.2.2) is implemented using the above crosstalk polymorphic crosstalk gates. The circuit uses 19 gates in total, 16 CT gates, and 3 inverters. 8 out of 16 CT gates are CT polymorphic gates. Polymorphic gates are efficiently employed to switch between the multiplier and sorter

operations. A control signal *(Ct)* is used switch between this the operations, Ct=0 is a multiplier and Ct=1 is Sorter. Fig.2.3 shows the simulation response of the circuit, where different operation modes of the circuit are annotated on top, which is, Discharge State (DS), Multiplier (M) and Sorter (S). The first panel in the figure shows Dis and Ct signals, second and third panels show the two 2-bit inputs A[1:0] and B[1:0], and the following panels show the 4-bit response of the circuit Y[3:0]. To depict multiplier and sorter operations effectively, the Ct signal is given as 0 and 1 alternately which makes the circuit operate as multiplier and Sorter in successive logic states. Also, common inputs, A[1:0] and B[1:0] are given for adjacent M and S modes. It can be observed from the response graphs (Y[3:0]) that, for the same inputs, the circuit gives the multiplier result when Ct=0 and sorter result when Ct=1. For example, for the first set of input combinations, 10 and 11, the M operation gives 0110 as output and S operation gives 1110. Similarly, for the second set of inputs, 01 and 01, M operation gives 0001 and S operation gives 1100. Similarly, M and S outputs are shown for a few other combinations. The circuit consumes only 88 transistors in total. Thus CT-P circuits are compact, possess maximum

reconfigurable features, and can efficiently implement larger polymorphic circuits in cascaded topology.

#### 2.2.2 Multiplier-Sorter-Adder Polymorphic Crosstalk Circuit

This section demonstrates the block level polymorphism using a circuit example of a 2-bit multiplier-sorter-adder (Fig.2.4) which is implemented using the polymorphic gates discussed above. The circuit uses 31 gates in total, out of which 25 are crosstalk gates, and 6 are inverters. 16 out of 25 crosstalk gates are polymorphic gates that are efficiently employed to switch the circuit between the multiplier, sorter and adder operations using the two control signals *C1* and *C2*. The inset figure shows the control circuitry (*C1-C5*). Fig.2.5 shows the simulation response of the circuit, where different operation modes of the circuit are annotated on top, which are,

Multiplier (M), Sorter (S), and Adder (A). The first panel shows Dis signal, Dis=1 is the discharge state (DS) and Dis=0 is the logic evaluation state.

The second panel shows the control signals CI and C2 whose values as 01, 11 and 10 corresponds to the multiplier, sorter, and adder operations. Third and fourth panels show the 2-bit inputs A[1:0] and B[1:0], respectively. The following panels show the 4-bit response of the circuit, Y[3:0]. The circuit is operated alternately in the multiplier, sorter, and adder modes. In each set of these modes, common input values are fed through A1A0 and B1B0 which effectively demonstrates the transformation of the circuit in accordance with the control signals. For example, for the first set of input combinations, 11 and 10, the multiplier operation gives 0110 as output while the succeeding sorter and adder operations give 1110 and 0101 outputs, respectively. Similarly, for the second set fo inputs, 10 and 01, M, S, and A operations

give 0010, 1100 and 0011 outputs, respectively. In a similar fashion, few other combinations are shown in the next stages. The circuit consumes only 155 transistors in total. Such polymorphic circuits can be employed for fault tolerance at the block level.

For example, as shown in Fig.2.6, Multiplier, Sorter and Adder operations can be implemented as independent blocks, which also possess the dormant other two operations. During the event of fault detection in one of the blocks, the other blocks can be reconfigured and multiplexed to achieve the correct output. The polymorphic blocks can be also used with traditional voter based [2] fault resiliency techniques.

#### CHAPTER 3

#### PRACTICAL REALIZATION OF CROSSTALK CIRCUITS

This chapter discusses, the practical realization of the crosstalk circuits using TSMC 65nm PDK. Because of the novel layout requirements for Crosstalk circuits, I have followed the custom circuit design methodology, involving the following steps, (i) schematic design, (ii) Symbol design, (iii) Functional verification of circuit schematics, (iv) layout design, and (v) layout verification. The following sections describe work in detail, including the tools setup and step by step followed.

3.1 Calibre and TSMC libraries setup:

The invocation of Cadence Virtuoso integrating the Mentor Graphics Calibre tool can be done using a single file. Create tsmc\_65nm.csh file in the home directory and copy the below lines. Work\_65nm is the directory where we installed the TSMC libraries with the help of the README file that TSMC provided. To start the Cadence virtuoso, use the command "source tsmc\_65nm.csh".

cd /home/students/brkf9/work\_65nm module load MentorGraphics/calibre/current module switch Cadence/615/Cadence-615 Cadence/new export CDS\_Netlisting\_Mode=Analog setenv CDS\_Netlisting\_Mode Analog module load PyCellStudio/current virtuoso &

3.2 Physical Implementation of Crosstalk Polymorphic Circuits

We have prototyped our chip using TSMC 65nm logic PDK. The purpose of the current chip prototype is to demonstrate the functionality of the Crosstalk Circuits for proof-of-concept. Though our research envisions for Crosstalk Computing specific 3-D capacitive structures for efficient

implementation, the conventional foundry PDKs lack these features. But, to serve our proof-ofconcept purpose, we have chosen the existing capacitance elements in TSMC PDK for our circuit implementations. The capacitance options present in TSMC 65nm PDK are MOSCAP and MIMCAP. We have implemented the crosstalk circuits using both the capacitance types.

Figure 3.1 shows the custom circuit design followed. The first step to be done to design any Crosstalk circuit is to observe the inverter DC characteristics, find out the inverter trip-point/threshold, and noise margins. The above simulation steps need to be done at various variation corners, i.e., Process (P), Temperature (T), Voltage (V). The threshold voltage and noise margins provide a metastable region of the inverter that needs to be avoided while operating the circuits. Then we calculate the input capacitance of the CMOS inverter. We then compute the capacitances values from the voltage division equations formulated for the Capacitive network at the input of inverter (Vi-node) for Crosstalk Gates [2]. These capacitance values serve as the starting point for our design. Because of the non-linear nature of the Gate capacitances of CMOS transistor and parasitic RCs, we would require to correct the coupling capacitances by observing the simulation response. The optimal circuit response is achieved for all the gates in a few design iterations. We have used Cadence Virtuoso Schematic Editor for circuit design, and Cadence Spectre Engine for circuit simulations. We then design the layouts for the schematics of the final circuit, perform the RC parasitic extraction, simulate extracted circuits and verify the functionality. The functional verification at this stage is also performed considering the PVT variations. If the added parasitics and/or PVT variations disturb the circuit functionality, we might need to perform design iteration and correct the coupling capacitances to fix the functional failures. We observed that this might happen only for high fan-in/complex gates. Then, we perform the physical design verification steps (DRC, LVS, and Antenna Checks) on these custom circuits. The final circuit blocks are then integrated at the full-chip level which will be shown in the following sections. I would discuss next the details of the above design steps, challenges and their solutions adopted, including the tool flows.

#### 3.3 Observations after installing the PDK

We need to observe the characteristics of the PMOS and NMOS transistors and determine its threshold voltage, and input gate capacitance. By knowing these values, we can determine the coupling capacitance values and the inverters sizing ratios required. Observing the on-current, and off-current would also serve as metrics for estimating performance and leakage power. Fig.3.2. shows the experiment setup to extract the transistor characteristics and Fig.3.3 shows the DC transfer characteristic curves.

Perform check and save to see if there are any errors in the schematic diagram. For the  $V_{GS}$  vs  $I_{DS}$  characteristics curve, give the drain to source voltage as 1 volt. If there are no errors, then proceed for the DC simulation. Open the ADE – L from the schematic window and choose the analyses as DC. In the component name section, click on the select component and select the DC voltage at the Gate input and in the sweep range, select 0 volts as the start and 1 volt

as the stop values. In the output's session, select the drain port which indicates that the current flowing through the gate terminal. Now click the play (green in color) button to run the simulation and the result is shown in Fig.3.3. To observe the same plot in Fig.3.3 for different

| Window Expression | ons Info <u>H</u> elp | cādence |

|-------------------|-----------------------|---------|

| a,id              | -134.6a               | 1       |

| qjs               | -7.002a               |         |

| qs                | -72.59a               |         |

| qsi               | -72,59a               |         |

| rdeff             | 216,9                 |         |

| region            | 2                     |         |

| reversed          | 0                     |         |

| rgate             | 20.14                 |         |

| rgbd              | 0                     |         |

| ron               | 5.312K                |         |

| rout              | 19,26K                |         |

| rseff             | 216.9                 |         |

| self_gain         | 6,119                 |         |

| ueff              | 15.8m                 |         |

| vbs               | 0                     |         |

| vdb               | 1.2                   |         |

| vds               | 1.2                   |         |

| vdsat             | 314.4m                |         |

| vdss              | 314.4m                |         |

| vearly            | 4,35                  |         |

| vgb               | 1,2                   |         |

| vgd               | 0                     |         |

| vgs               | 1.2                   |         |

| vgt               | 849.1m                |         |

| vsat_marg         | 885.6m                |         |

| vsb               | -0                    |         |

| vth               | 350.9m                |         |

|                   |                       |         |

$V_{DS}$  values, select the  $V_{ds}$  as the design variable and follow the process as shown in Fig.3.4 To determine the threshold voltage of a device, make sure that the  $V_{ds}$  and  $V_{gs}$  are added to the design variables and follow the process as shown in Fig.3.5. After the simulation completes successfully, go to the "results" in the ADE-L window, then "print", then click on the DC Operating points. When we click on it, a window will pop-up which shows all the parameters related to the NMOS transistor as shown in Fig.3.6. In the properties window, we

can find the threshold voltage as 350.9mV. From Fig.3.3 the average off-current is 206.254nA and the on-current is 225.895uA when the gate and drain voltages are at its maximum. We can also observe that the square law is not followed by the transistors in this 65nm TSMC PDK from the V<sub>DS</sub> vs I<sub>D</sub> curve as shown in the Fig.3.7.

| TABLE 2<br>TSMC 65nm PMOS and NMOS transistor properties |                     |           |  |  |  |  |

|----------------------------------------------------------|---------------------|-----------|--|--|--|--|

| Parameter                                                | NMOS                | PMOS      |  |  |  |  |

| Vth                                                      | 350.9mV             | 295.5mV   |  |  |  |  |

| Ion                                                      | 225.895uA           | 126.986uA |  |  |  |  |

| Ioff                                                     | 206.254nA           | 111.7nA   |  |  |  |  |

| Ron                                                      | 5.312k              | 9.4k      |  |  |  |  |

| Roff                                                     | 850.6k (vth/2*Ioff) | 1.322M    |  |  |  |  |

| Ion/Ioff                                                 | 1095.227            | 1085.35   |  |  |  |  |

| Ron/Roff                                                 | 0.006245            | 0.00711   |  |  |  |  |

Table.3.1 shows the summary of TSMC 65nm PMOS and NMOS transistor properties. The threshold voltage of the PMOS and NMOS are required to design the threshold device of the crosstalk circuits which is the CMOS Inverter. To choose the coupling capacitances for the Crosstalk

gates, we would need to find out the input gate capacitance of the CMOS inverter. The voltage induced on the victim node with different logic combinations/transitions on the input aggressors can be calculated using capacitance division equations [16]. By playing with the crosstalk coupling capacitance values, the voltage induced on the victim node can be tailored to implement logic behavior. Thus, the coupling capacitances serve as the first independent variables that can be engineered/controlled to design various logic gates. The second independent variable that can be helpful in designing various crosstalk gates is the threshold-voltage/trip-point of CMOS inverter. For example, Fig.3.8 shows the DC transfer characteristic curve of a CMOS Inverter for NMOS widths as 200nm and 400nm. We can observe that the characteristic curve moved left by doubling the NMOS size. Thus, the trip point of the CMOS inverter (which provides threshold function) can be increased or decreased by different sizing ratios for PMOS and NMOS transistors. Therefore, we use both coupling capacitance and trip-point of the inverter as the design variables that enable building various crosstalk logic gates.

| gorithm State    | e File Outpu   | t EM/IR Output       | Misc 🔹     | Igorithm   | State File   | Output           | EM/IR Output     | Misc    |

|------------------|----------------|----------------------|------------|------------|--------------|------------------|------------------|---------|

| ANNOTATION       | PARAMETERS     |                      | ŕ          | strobedel  | ay           |                  |                  |         |

| annotate         | 🗌 no 🔲 title 🗌 | 🗌 sweep 🗹 status 🗌   | steps      | FINAL      | OP POINT SET | TINGS            |                  |         |

| CAPTAB PARA      | METERS         |                      |            | Save Fin   | al Op Pt     | ⊻                |                  |         |

| captab           | ¥              |                      |            | Final Op   | Other Params |                  |                  |         |

| timed            | <u>ب</u>       |                      |            | INFOTIM    | MES SETTINGS | s                |                  |         |

| threshold        | 0.0            |                      |            | Info time: | s            | 500p 750p 1      | n 1,25n 1,5n     |         |

| detail           | 🗹 node 🔲 nod   | letoground 🔲 nodeton | ode        | I ran Into | Uther Params |                  |                  |         |

| sort             | ⊻ name 🗌 val   | ue                   |            | ACTIME     | S SETTINGS   |                  |                  |         |

| ADDITIONAL P     | ARAMETERS      |                      |            | actimes    |              |                  |                  |         |

| additionalParams | 1              |                      | L          | acnames    |              |                  |                  |         |

|                  | OK Can         | cel Defaults         | Apply Help |            | 0            | K <u>C</u> ancel | <u>D</u> efaults | Apply H |

Fig.3.9 shows the settings to do to get the cap values at different nodes. In the ADE – L window, go to transient analyses then options then Misc and check the options cap-tab and timed column. Also, in the output tab, give the info times as the time points at which we are interested to find the cap. To print the cap values, go to Results  $\rightarrow$  Print  $\rightarrow$  Cap Table as shown in Fig.3.10. The analysis would give the capacitances values at different info times, which are 314.362af, 322.909af, 322.909af, 343.372af and 314.276af, also, the average value, which is 323.565af.

| _aunch S <u>e</u> ssion Set <u>u</u> p <u>A</u> nalyses ⊻ | ariables <u>O</u> utputs <u>S</u> imulation | <u>Results</u> <u>Tools</u> Calibre         | Help |  |  |

|-----------------------------------------------------------|---------------------------------------------|---------------------------------------------|------|--|--|

| 🛃 🔊   🦵 27 🗌 👌 🎾                                          | ê 🗹 🖻                                       | Plot <u>O</u> utputs<br>Direct <u>P</u> lot | :    |  |  |

| esign Variables                                           | Analyses                                    | Print                                       | h.   |  |  |

| °                                                         | _ Type Enable                               | Annotate                                    | •    |  |  |

| Name Value                                                | 1 dc 🔳 0 1.2 5                              | Vector                                      |      |  |  |

|                                                           | 2 tran 🕑 0 5n                               | Circuit <u>C</u> onditions                  |      |  |  |

|                                                           |                                             | Violations Display                          |      |  |  |

|                                                           |                                             | Reliability Data                            |      |  |  |

|                                                           |                                             |                                             |      |  |  |

|                                                           | <[                                          | <u>S</u> ave<br>S <u>e</u> lect<br>Delete   |      |  |  |

|                                                           | Outputs                                     |                                             |      |  |  |

|                                                           | Name/Signal/Expr                            |                                             |      |  |  |

|                                                           | 1 2 M1/D                                    | –<br>Prin <u>t</u> ing/Plotting Options     |      |  |  |

|                                                           | 3 M0/D                                      |                                             | /es  |  |  |

|                                                           | 4 V0/MINUS                                  |                                             | 10   |  |  |

|                                                           | 5 V0/PLUS                                   |                                             | 10   |  |  |

TSMC Provides three types of capacitances. They are MOSCAP (Metal Oxide Semiconductor Capacitor), MOMCAP (Metal-Oxide-Metal Capacitor) and MIMCAP (Metal-Insulator-Metal Capacitor). We get MIM and MOSCAP in the PDK. The MIM cap offers larger capacitance in a small footprint compared to the MOS CAP. So, we used MIM cap, whenever we require the very large capacitance, instead of using a very large width poly MOSCAP. Next few sections I would discuss the custom circuit design flow on Cadence Virtuoso tools.

### 3.5 Schematic and Symbol Design

After choosing the coupling capacitances and the inverter sizes, open Cadence Virtuoso Schematic Editor and instantiate the transistors, capacitors and the voltage sources and connect them using wires as shown in Fig.3.11. The inverters used in the schematic are from TSMC 65nm Standard Cell Library. However, we might need to customize the transistor sizes and design our own CMOS inverters to meet the Crosstalk logic requirements. There are three ways to simulate the schematic and verify the functionality. One is using a digital vector file, second is by instantiating the voltage pulse

source in the above schematic, and the third way is creating a symbol and then using either digital vector file or simulation sources. We used the third approach. The same setup can be used for the layout simulation also. Fig.3.12 shows the symbol of the schematic shown in Fig.3.11.

It is to be noted that the VI pin is probing the internal victim node of the gate. Observing the *Vi* node voltage would help us both in the design and debug stage, also for extracted layout. Fig.3.13 shows the Design Under Test (DUT) schematic for the Crosstalk AND gate, using its symbol view. 3.6 ADE – XL Schematic Simulations in different PVT corners

Next save DUT by clicking on the check and save option to see if there are any errors present in the schematic, symbol and test schematic. ADE-L can be used to simulate the schematic and layout at only one corner at a time. To simulate at various corners using ADE-L, we need to manually run each corner. However, we can use ADE-XL to automatically run the simulation in all the corners in one go.

Also, we need to select the appropriate model files for transistors and passive elements. To manually, simulate at a particular corner, we can select different model files. The simulations can be

performed on various views using the same DUT setup. To perform simulations on different views, i.e., schematic, caliber extracted, etc., we need to change the view list appropriately in Environment options.

Before starting the simulation, we can select to probe any node that we are interested in the circuit by using using "Outputs  $\rightarrow$  To Be Plotted  $\rightarrow$  Select on the Design". Then select the interested node and run the simulation. After the successful simulation, we can also save the state using "session  $\rightarrow$  Save State" and give a name and folder to save it. This saved state can be used in ADE-XL window later on. After performing all the above simulation setups, Fig.3.14 shows the Crosstalk AND gate schematic simulation response. Next, I will discuss the layout design procedure for this circuit.

3.7 Crosstalk Gates Layout Design

Before starting the layout drawing, we need to set up the grid size which can be found in the PDK documents. For this 65nm PDK, the grid size is 0.005 um. We can change these grid settings in "options"  $\rightarrow$  "display". In the Display Options window as shown in Fig.3.15, change the X snap spacing and Y snap spacing from 0.003 (default) to the grid mentioned in the PDK which is 0.005. Also, change the minor spacing to 0.01 and the major spacing to 0.1. Note that we need to set the snap

| D layout                                                                                                                                 | Jisplay Options                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                         | × |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ① isplay       E         Editor       Shift+E         Selection       Magnifier         DRD Edit       Highlight         Dynamic Display | Display Controls<br>Open to Stop Level<br>Axes<br>Instance Origins<br>Instance Orientation<br>EIP Surround<br>Pin Names<br>Dot Pins<br>Net Expressions<br>Stretch Handles<br>Fig. 3.15 Setting the | <ul> <li>Nets</li> <li>Access Edges</li> <li>Instance Pins</li> <li>Array Icons</li> <li>✓ Label Origins</li> <li>Use True BBox</li> <li>Cross Cursor</li> <li>Row Name</li> <li>Row Site</li> <li>grid as per the tech</li> </ul> | Grid Controls<br>Type one odots olines<br>Dim Major Dots<br>Minor Spacing 0.025<br>Major Spacing 0.125<br>X Snap Spacing 0.003<br>Y Snap Spacing 0.003<br>Spacing 0.003 |   |

spacing for each time we open the layout window, otherwise it will create grid DRC errors and we might need to redo the whole design.

After setting the grid, we can start placing the devices and connect them using metal lines. We can practice the good layout design procedure of checking DRC errors for every few steps when we draw the layout. Fig.3.16 shows the final AND gate layout in which two NMOSCAPs value is 4.8fF and the inverter size is 4x. This inverter was taken from the 65nm TSMC standard cell library.

3.8 Physical Verification and Extraction of the layouts

Physical verification was done using the MentorGraphics caliber tool. To integrate the caliber tool to virtuoso use "module load MentorGraphics/calibre/current". We can see the caliber plug-ins when we instantiate the layout tool as shown in the Fig.3.17.

| 🔯 Virtuoso ® Layout Suite L E                          | Editing: Naveen       | MOSIS AND layout                                    |          |                   |                           |               |                   |      | ×   |

|--------------------------------------------------------|-----------------------|-----------------------------------------------------|----------|-------------------|---------------------------|---------------|-------------------|------|-----|

| Launch <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> | reate Ver <u>i</u> fy | Co <u>n</u> nectivity <u>O</u> ptions <u>T</u> ools | Window   | Ass <u>u</u> ra Q | uantus Cali <u>b</u> re N | CSU PVS       | <u>H</u> elp      | cāde | nce |

| 10 🖂 🛛 🤊 🦿 🖣                                           | è 🗘 🔟                 | 🗙 🥵 🛈 😫                                             | » 🛛 🔍    | » 75              | » Classic                 |               | - 🖓 🖓             |      |     |

| II-, 🧠 🗿 🕂 🖎 I                                         | 👰 살 📮                 | 🦺 🔹 🛛 🕹                                             |          | 🛱 🚽 💷             | (F)Select:0 Sel(N         | l):0 Sel(l):0 | Sel(O):0 X 12.828 |      | »   |

| Palette ? 🗗 🤇                                          | ×                     |                                                     |          |                   |                           |               |                   |      |     |

| Layers 🗗                                               | ×                     |                                                     | 555 III  |                   |                           |               |                   |      |     |

| 🍸 All Layers                                           |                       | / <u>&gt;:</u> a                                    |          |                   |                           |               |                   |      |     |

| 🗹 Valid 🛄 Used 🛄 Routing                               |                       |                                                     |          |                   |                           |               |                   |      |     |

| Filter 🔍 Filter 🔽 🧧                                    |                       |                                                     |          |                   |                           |               |                   |      |     |

| ref drawing                                            | 3                     |                                                     |          |                   |                           |               |                   |      |     |

| AV 🔻 NV 💌 AS 💌 NS                                      | -                     |                                                     | <b>-</b> |                   |                           |               |                   |      |     |

| ∧ Layer Pu V S<br>ref drw ✔ ✔                          |                       |                                                     |          |                   |                           |               |                   |      |     |

|                                                        |                       | Fig.3.17. Calibre                                   | Integra  | ation w           | rith Virtuos              | )             |                   |      |     |

The first step that we need to check after the layout design is DRC checking. Foundry will provide the DRC file which contains the various design rules such as minimum width and minimum spacing for all the layers.

| Calibre - RVE v2017.4_26.19 : AND.drc.re                      | sults                   | Calibre - RVE v2017.4_26.19 : AND.drc.results                                  |

|---------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------|

| <u>File ⊻iew Highlight Tools Window</u>                       | <u>S</u> etup           | <u>F</u> ile ⊻iew <u>H</u> ighlight <u>T</u> ools <u>W</u> indow <u>S</u> etup |

| 🎾 🖋 🔍 🔍 😻 🖉                                                   | Search                  | ▼◆◆   🎾 🖋 泉▼「 🍏   陳   � 茶 �   Search ▼ ◆                                       |

| Thow All The AND, 165 Results (in                             | 35 of 38 Checks)        | Show All T AND, 165 Results (in 35 of 38 Checks)                               |

| 🖾 🍕 Check / Cell                                              | Priority Resul 1        | 🖾 Ag Check / Cell Priority Resul 117 118 119 120                               |

| E X Check OD.DN.1:L                                           | 1                       | 🗉 🗙 Check CSR.R.1:POi 🛛 🙀 🍐                                                    |

| E 🗙 Check DOD.R.1                                             | 1                       | E X Check DM1.R.1 1                                                            |

| E X Check PO.DN.1:L                                           | 1                       | E X Check DM2.R.1 1                                                            |

| E X Check PO.R.8                                              | 1                       | E X Check DM3.R.1 1                                                            |

| EX Check DPO.R.1                                              | 1                       | E X Check DM4.R.1 1                                                            |

| Check M9.DN.1:L                                               | 1                       | EX Check DM5.R.1 1                                                             |

| Check CSR.R.1:NWi                                             | 2                       | E X Check DM6.R.1 1                                                            |

| Check CSR.R.1:OD_25i Check CSR.R.1:DDi                        | 1                       | X Check DM7.R.1     1                                                          |

| Check CSR.R.1:PPi     Check CSR.R.1:NPi                       | 2                       | X Check DM8.R.1 1                                                              |

| E X Check CSR.R.1:NPI                                         | 4                       | X Check DM9.R.1     1                                                          |

| EX Check CSR.R.1:COI                                          | 66                      | 🗉 🗙 Check LUP.1g 4                                                             |

| EX Check CSR.R.1:WARI                                         | 11                      | 🗉 🗙 Check LUP.2g 1                                                             |

| E X Check CSR.R.1:M1 real                                     | 11                      | 🖼 🗙 Check LUP.3.1.1g 5                                                         |

| Check CSR.R.1:M1_real                                         | 1                       | K Check LUP.3.1.2g     10                                                      |

| E X Check CSR.R.1:M2_real                                     | 1                       | E X Check LUP.5.1.1g 5                                                         |

| EX Check CSR.R.1:VIA1i                                        | 2                       | E X Check LUP.5.1.2g 10                                                        |

| E X Check CSR.R.1:ODi                                         | 8                       | EX Check ESD.WARN.1 1                                                          |

| E X Check CSR.R.1:POI                                         | 4 1                     | Check DENSITY_PRINT_FILES 0                                                    |

|                                                               |                         |                                                                                |

| OD.DN.1:L { @ {OD OR DOD} density                             |                         |                                                                                |

| DENSITY ALL_OD CHIP < OD_DN_1L<br>[ AREA(ALL_OD)/AREA(CHIP) ] | INSIDE OF LAYER CHIP× P |                                                                                |

| 3                                                             |                         | EMPTY_AREA AND PO1                                                             |

|                                                               |                         | ľ                                                                              |

| 1                                                             |                         |                                                                                |

|                                                               | Fig.3.18                | . DRC violations at the circuit level                                          |

|                                                               | - 18:0110               |                                                                                |

When the caliber Interactive nmDRC window opens up, we provide the DRC rules deck and every other field in the input and output section will automatically be populated with its appropriate values. Then we can click on Run DRC. After the DRC check is completed, a results window will pop up with all the DRC violations in the design as shown in the Fig.3.18. We can ignore the full-chip level DRC violations at this stage. They can be addressed at the full-chip level. For example, in Fig.3.18, the violations which have \*DN\* pattern relate to the density rules for each layer. We can fix these violations after filling the dummy metal-fills at the full-chip level.

Similarly, the violations which start with D\* pattern, followed by the layer name indicate that the dummy layers related to the drawing layers are missing in the design. These dummy layers are placed in the full chip. We would encounter one more violation "PO.R.8 – floating gate error", which is associated with the discharge transistor gate. This error will be eliminated when the gate of these transistors is connected to the I/O pads in the full chip. Other errors that start with the CSR\* pattern are related to the I/O pad corners that can also be ignored at this stage. We can ignore the

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>₩</u> indow <u>S</u> etup |              |                      |          |             |                            | Н |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|----------------------|----------|-------------|----------------------------|---|

| 🥑 🎻 🔍 🖉 🖉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | K 🛣 🚺 🖉 🖓 🖓 🖓                | Search * 🔹 🕨 |                      |          |             |                            |   |

| Navigator 🕜 Info 🗋 🗗 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ☆ AND ×                      |              |                      |          |             |                            |   |

| esults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No. Layout Net               |              | Source Net           |          | C Total (F) | CC Total (F)               |   |