Wang, Xingsheng (2010) Simulation study of scaling design, performance characterization, statistical variability and reliability of decananometer MOSFETs. PhD thesis.

http://theses.gla.ac.uk/1810/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Simulation Study of Scaling Design, Performance Characterization, Statistical Variability and Reliability of decananometer MOSFETs

Xingsheng Wang

Submitted to University of Glasgow,

Department of Electronics and Electrical Engineering,

in fulfilment of requirements for the degree of

Doctor of Philosophy

May 2010

Copyright © Xingsheng Wang, 2010

## Dedicated to

my parents for their endless support...

#### **Abstract**

This thesis describes a comprehensive, simulation based scaling study – including device design, performance characterization, and the impact of statistical variability – on decananometer bulk MOSFETs. After careful calibration of fabrication processes and electrical characteristics for n- and p-MOSFETs with 35 nm physical gate length, 1 nm EOT and stress engineering, the simulated devices closely match the performance of contemporary 45 nm CMOS technologies. Scaling to 25 nm, 18 nm and 13 nm gate length n and p devices follows generalized scaling rules, augmented by physically realistic constraints and the introduction of high-k/metal-gate stacks. The scaled devices attain the performance stipulated by the ITRS. Device a.c. performance is analyzed, at device and circuit level. Extrinsic parasitics become critical to nano-CMOS device performance. The thesis describes device capacitance components, analyzes the CMOS inverter, and obtains new insights into the inverter propagation delay in nano-CMOS. The projection of a.c. performance of scaled devices is obtained.

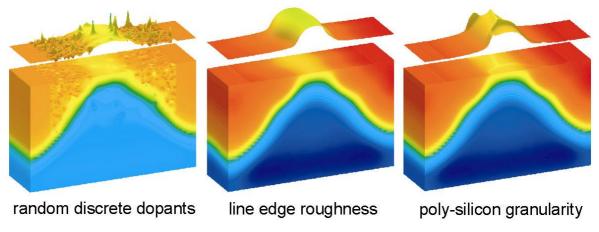

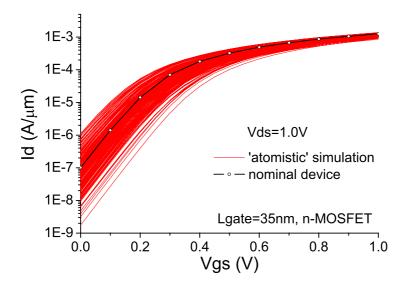

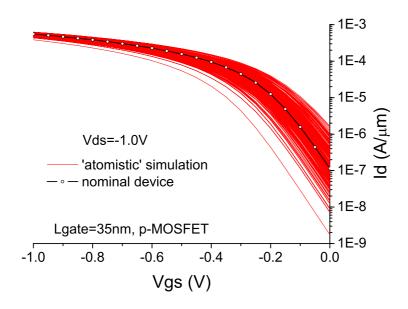

The statistical variability of electrical characteristics, due to intrinsic parameter fluctuation sources, in contemporary and scaled decananometer MOSFETs is systematically investigated for the first time. The statistical variability sources: random discrete dopants, gate line edge roughness and poly-silicon granularity are simulated, in combination, in an ensemble of microscopically different devices. An increasing trend in the standard deviation of the threshold voltage as a function of scaling is observed. The introduction of high-k/metal gates improves electrostatic integrity and slows this trend. Statistical evaluations of variability in  $I_{on}$  and  $I_{off}$  as a function of scaling are also performed.

For the first time, the impact of strain on statistical variability is studied. Gate line edge roughness results in areas of local channel shortening, accompanied by locally increased strain, both effects increasing the local current. Variations are observed in both the drive current, and in the drive current enhancement normally expected from the application of strain. In addition, the effects of shallow trench isolation (STI) on MOSFET performance and on its statistical variability are investigated for the first time. The inverse-narrow-width effect of STI enhances the current density adjacent to it. This leads to a local enhancement of the influence of junction shapes adjacent to the STI. There is also a statistical impact on the threshold voltage due to random STI induced traps at the silicon/oxide interface.

### Acknowledgment

First of all, I would like to express my most sincere gratitude to my supervisors Professor Asen Asenov and Dr. Scott Roy. They guided my PhD researches through more than 3 years. Professor Asenov inspired me with his knowledge, enthusiasm and wisdom in semiconductors, and he gave me countless suggestions and advice on the research fields, and also answered those academic questions once obsessed in my mind. He devoted a lot of time and patience to the reading and correction of this thesis.

I am grateful to Dr. Scott Roy for his valuable comments, advice, encouragement and thesis reading. I thank him for his help to solve those problems when I appeared as a fresh device modeller. His pleasant and optimistic appearance greatly impresses me.

I would also like to thank those Doctors Binjie Cheng, Gareth Roy, and Stanislav Markov for their helpful thesis reading and suggestions. My sincere thanks go to Binjie Cheng for his discussions and suggestions about my research, and also for plenty of personal suggestions from the beginning. Gareth taught me the basics of Linux. Stanislav and I had fruitful discussions. I feel grateful to Andrew R. Brown for his countless patient answers about the 'atomistic' simulator and others. Thanks also go to Dr. Campbell Millar for helpful discussions about programming.

I appreciate the discussions with Dr. Karol Kalna about whatever has been involved, and Dr. Jeremy Watling about high-k gate stack. I thank Dr. Antonio Martinez for discussions reminding me of theoretical studies in physics.

This work is supported partitially by the EPSRC project (EP/E003125/1) "Meeting the design challenges of the nano-CMOS electronics," and partially by the Overseas Research Students Awards Scheme (ORSAS). I acknowledge their support for my PhD studies.

Last but not least, I want to thank my parents. They teach me the life principles. My father wished me to be a scientist expert. Their understanding encourages me, and their sacrificial giving and support drive me.

#### **Publications**

- **X. Wang**, S. Roy, A. R. Brown, and A. Asenov, "Impact of STI on statistical variability and reliability of decananometre MOSFETs," submitted to *IEEE Electron Device Letters*.

- B. Cheng, D. Dideban, N. Moezi, C. Millar, G. Roy, **X. Wang**, S. Roy and A. Asenov, "Statistical-variability compact-modeling strategies for BSIM4 and PSP," *IEEE Design & Test of Computers*, Vol. 27 No. 2, pp.26-35, March/April 2010.

- B. Bindu, B. Cheng, G. Roy, **X. Wang**, S. Roy, A. Asenov, "Parameter set and data sampling strategy for accurate yet efficient statistical MOSFET compact model extraction," *Solid-State Electronics*, Vol.54 No.3, pp.307-315, March 2010.

- B. Benbakhti, K. Kalna, **X. Wang**, B. Cheng, A. Asenov, G. Hellings, G. Eneman, K. D. Meyer and M. Meuris, "Impact of raised source/drain in the In<sub>53</sub>Ga<sub>47</sub>As channel implant-free quantum-well transistor," in *Proc. 11<sup>th</sup> ULIS*, pp.129-132, March 18-19, 2010.

- N. A. Kamsani, B. Cheng, C. Millar, N. Moezi, **X. Wang**, S. Roy and A. Asenov, "Impact of slew rate definition on the accuracy of nanoCMOS inverter timing simulations," in *Proc.* 11<sup>th</sup> ULIS, pp.53-56, March 18-19, 2010.

- B. Cheng, D. Dideban, N. Moezi, C. Millar, G. Roy, **X. Wang**, S. Roy and A. Asenov, "Capturing intrinsic parameter fluctuations using the PSP compact model," in *Proc. Design, Automation and Test in Europe*, pp.650-653, Germany, March 8-12, 2010.

- **X. Wang**, S. Roy, and A. Asenov, "Impact of strain on the performance of high-k/metal replacement gate MOSFETs," in *Proc. IEEE 10th Ultimate Integration on Silicon (ULIS 2009)*, pp.289-292, Aachen Germany, March 18-20, 2009.

- A. Asenov, S. Roy, A. R. Brown, G. Roy, C. Alexander, C. Riddet, C. Millar, B. Cheng, A. Martinez, N. Seoane, D. Reid, M. F. Bukhori, **X. Wang**, U. Kovac, "Advanced simulation of statistical variability and reliability in nano CMOS transistors," in *IEDM Tech. Dig.*, pp. 421, December 2008.

- **X. Wang**, S. Roy, and A. Asenov, "High performance MOSFET scaling study from bulk 45 nm technology generation," in *Proc. of IEEE 9th International Conference on Solid-State and Integrated-Circuit Technology (ICSICT 2008)*, pp. 484-487, Beijing China, October 20-23, 2008.

- B. Bindu, B. Cheng, G. Roy, **X. Wang**, S. Roy, and A. Asenov, "An efficient data sampling strategy for statistical parameter extraction of nano-MOSFETs," in *IEEE Workshop on Compact Modeling*, pp.55-59, Japan, September 8, 2008.

- **X. Wang**, S. Roy, and A. Asenov, "Impact of strain on LER variability in bulk MOSFETs," in *Proc. of IEEE 38th European Solid-State Device Research Conference (ESSDERC 2008)*, pp.190-193, Edinburgh Scotland, September 15-19, 2008.

- **X. Wang**, B. Cheng, S. Roy, and A. Asenov, "Simulation of strain enhanced variability in nMOSFETs," in *Proc. IEEE 9th Ultimate Integration on Silicon (ULIS 2008)*, pp.89-93, Udine Italy, March 12-14, 2008.

# **Contents**

| ABSTRACT                                                | ]         |

|---------------------------------------------------------|-----------|

| ACKNOWLEDGMENT                                          | 11        |

| PUBLICATIONS                                            | ID        |

| CONTENTS                                                | V         |

| LIST OF TABLES                                          |           |

| LIST OF FIGURES                                         |           |

| LIST OF SYMBOLS                                         | XV        |

|                                                         |           |

| CHAPTER I                                               |           |

| 1. INTRODUCTION                                         | 1         |

| 1.1. MOTIVATION                                         |           |

| 1.2. AIMS AND OBJECTIVES                                | 2         |

| 1.3. Thesis outline                                     | 2         |

|                                                         |           |

| CHAPTER II                                              |           |

| 2. MOSFET TECHNOLOGY SCALING, CHALLENGES AND            | BOOSTERS4 |

| 2.1. MOSFET SCALING                                     | 4         |

| 2.1.1. Past scaling trends                              |           |

| 2.1.2. Scaling principles                               |           |

| 2.1.3. Recent scaling trends and ITRS                   |           |

| 2.2. SCALING CHALLENGES OF MOSFETS                      |           |

| 2.2.1. Feature patterning                               | 14        |

| 2.2.2. Power and performance management                 |           |

| 2.2.3. Vertical scaling                                 |           |

| 2.2.4. Lateral effects                                  |           |

| 2.2.5. Hot-carrier degradation and BTI                  |           |

| 2.2.6. Statistical variability                          |           |

| 2.3. Technology boosters                                |           |

| 2.3.1. Strained channel                                 |           |

| 2.3.2. High-k/metal gate                                |           |

| 2.4. Summary                                            | 29        |

| CHAPTER III                                             |           |

| 3. SIMULATION TOOLS AND METHODOLOGY                     | 30        |

| 3.1. Process simulation                                 | 30        |

| 3.1.1. Ion implantation                                 |           |

| 3.1.2. Thermal annealing                                |           |

| 3.1.3. Film formation                                   |           |

| 3.1.4. Process induced stress                           |           |

| 3.1.5. Three dimensional process simulation methodology |           |

| 3.2. DEVICE SIMULATION                                  |           |

| 3.2.1. Transport equations                              |           |

| 3 2 2 Mobility models                                   | 40        |

| 3.2.3. Modelling stress-dependent mobility                                             | 44   |

|----------------------------------------------------------------------------------------|------|

| 3.3. THE GLASGOW 'ATOMISTIC' SIMULATOR                                                 |      |

| 3.3.1. Random discrete dopants (RDD)                                                   | 48   |

| 3.3.2. Line edge roughness (LER)                                                       |      |

| 3.3.3. Poly-silicon granularity (PSG)                                                  | 51   |

| CHAPTER IV                                                                             |      |

| 4. CMOS DEVICE DESIGN AND CHARACTERIZATION                                             | 53   |

| 4.1. Calibration                                                                       | 53   |

| 4.1.1. Extraction of the real device structure                                         |      |

| 4.1.2. Calculations of doping profiles                                                 |      |

| 4.1.3. Calibration methodology                                                         |      |

| 4.1.4. Calibration results                                                             | 58   |

| 4.2. MODERNIZATION OF CMOS DEVICES                                                     | 63   |

| 4.2.1. 45 nm CMOS technology                                                           | 63   |

| 4.2.2. Simulating the 45 nm technology CMOS                                            | 66   |

| 4.3. SCALED CMOS DEVELOPMENT                                                           |      |

| 4.3.1. CMOS scaling design                                                             |      |

| 4.3.2. Scaled CMOS characterization                                                    |      |

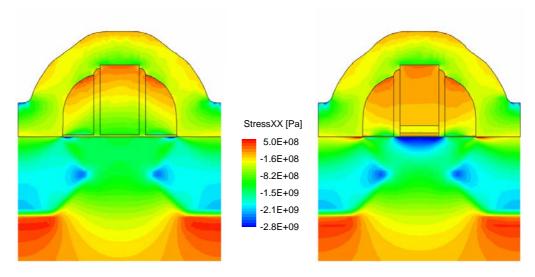

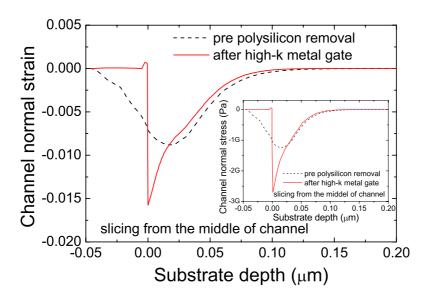

| 4.4. STRAIN SCALING                                                                    |      |

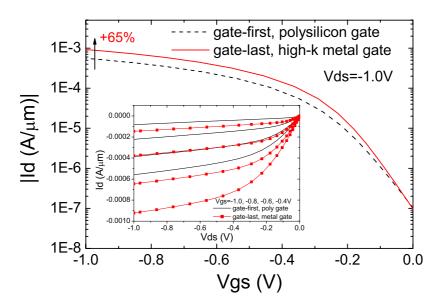

| 4.4.1. Gate-last benefit                                                               |      |

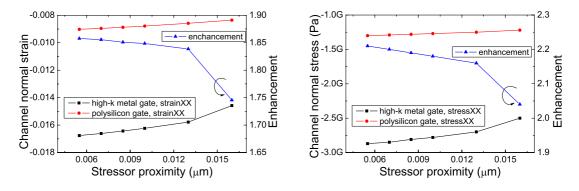

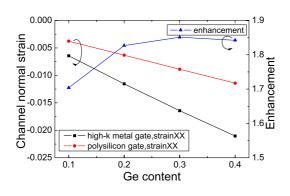

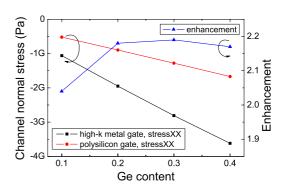

| 4.4.2. Scaling of strain enhancement                                                   |      |

| 4.5. SCALING SUMMARY                                                                   | 82   |

| CHAPTER V                                                                              |      |

| 5. SCALING STUDY OF STATISTICAL VARIABILITY                                            | 84   |

| 5.1. SIMULATION METHODOLOGY                                                            | 84   |

| 5.2. STATISTICAL VARIABILITY OF 35 NM POLY-GATE MOSFETS                                | 86   |

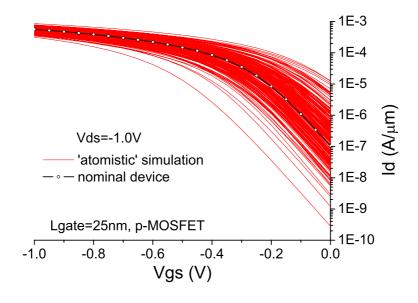

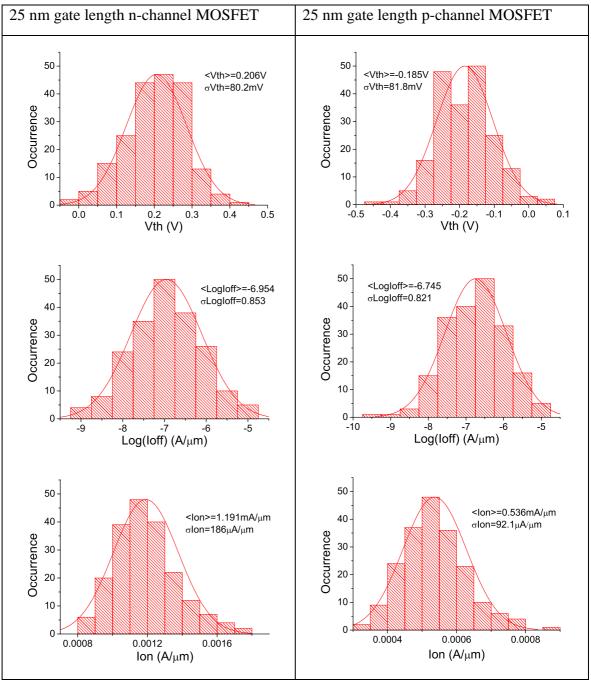

| 5.3. STATISTICAL VARIABILITY OF 25 NM POLY-GATE MOSFETS                                |      |

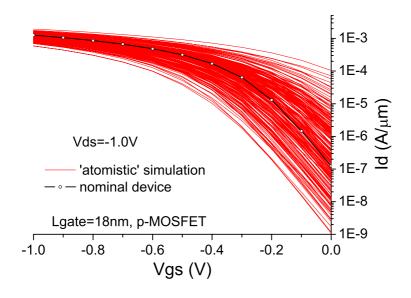

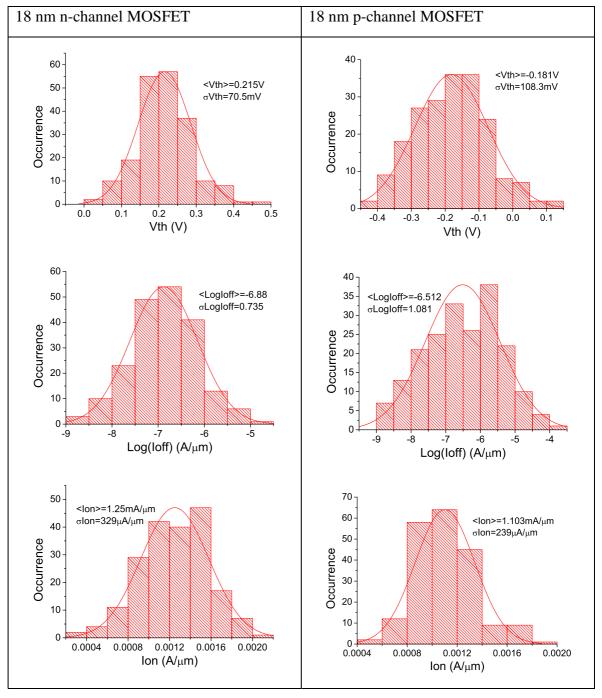

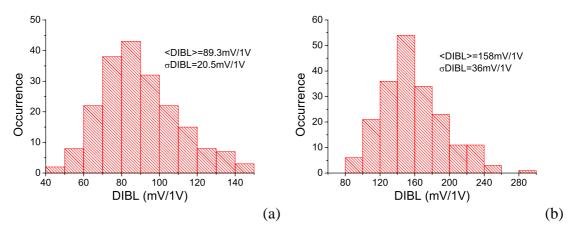

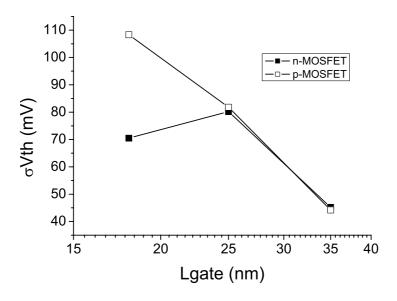

| 5.4. STATISTICAL VARIABILITY OF 18 NM METAL-GATE MOSFETS                               |      |

| 5.5. Summary                                                                           | 98   |

| CHAPTER VI                                                                             |      |

| 6. IMPACT OF STRAIN AND STI ON VARIABILITY                                             | 100  |

| 6.1. STRAIN ENHANCED LER VARIABILITY                                                   | 100  |

| 6.1.1. Simulation methodology                                                          | 101  |

| 6.1.2. LER and strain variability                                                      | 102  |

| 6.1.3. Strain enhanced electrical variability                                          |      |

| 6.2. STI EFFECTS IN DECANANOMETRE MOSFETS                                              |      |

| 6.2.1. STI structure in narrow-channel MOSFETs                                         |      |

| 6.2.2. RDD variability in the presence of STI                                          | 114  |

| 6.3. IMPACT OF STI ON STATISTICAL VARIABILITY AND RELIABILITY OF DECANANOMETRE MOSFETS |      |

| 6.3.1. Simulation methodology                                                          |      |

| 6.3.2. Results and discussions                                                         |      |

|                                                                                        |      |

| CHAPTER VII                                                                            | 4.44 |

| 7. SIMULATION OF DYNAMIC ASPECTS OF CMOS                                               |      |

| 7.1. SMALL SIGNAL A.C. ANALYSIS                                                        |      |

| 7.1.1. Numerical approaches of small-signal a.c. analysis                              |      |

|                                                                                        |      |

| 7.1.3. Split C-V analysis of 25 nm g | gate length pMOSFETs      | 129 |

|--------------------------------------|---------------------------|-----|

|                                      | NM CMOS INVERTERS         |     |

| 7.2.1. Mixed mode simulation         |                           | 132 |

| 7.2.2. a.c. performance of 35 nm M   | MOSFETs in basic circuits | 134 |

| 7.3. SCALING OF THE A.C. PERFORMA    | ANCE OF MOSFETS           | 140 |

| 7.3.1. Small signal analysis of scal | ed MOSFETs                | 140 |

|                                      | η                         |     |

| CHAPTER VIII  8. CONCLUSION          |                           | 144 |

| 8.1. SUMMARY                         |                           | 144 |

| 8.2. Outlook                         |                           | 146 |

| REFERENCES                           |                           | 148 |

# List of tables

| Table 2.1 Scaling principles for MOSFET device and circuit parameters                                                          |

|--------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 High-performance logic technology projection for extended planar bulk MOSFETs in terms of ITRS.                      |

| Table 2.3 Some essential parameters for selected high-k materials and SiO <sub>2</sub> 27                                      |

| Table 2.4 Experimental vacuum (effective) work functions of selected metals on various dielectrics [115][116][117][118]        |

| Table 3.1 Constant mobility model with default parameter values for Si4                                                        |

| Table 3.2 Masetti doping-dependent mobility model with default parameter values for Si.                                        |

| Table 3.3 Arora doping-dependent mobility model with default parameter values for Si 42                                        |

| Table 3.4 Lombardi interface mobility model with default parameter values for Si43                                             |

| Table 3.5 Canali high-field mobility model with default parameter values for Si43                                              |

| Table 3.6 Piezoresistance coefficients for holes and electrons                                                                 |

| Table 3.7 Intel physically-based stress-dependent hole mobility model parameters47                                             |

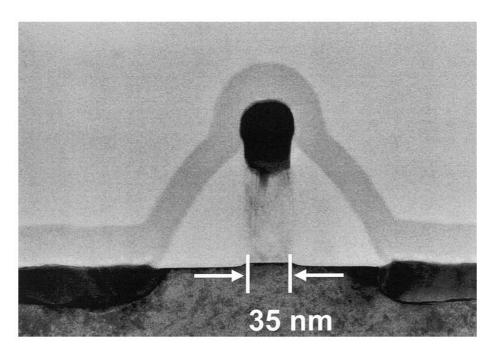

| Table 4.1 Physical dimensions of Toshiba 35 nm gate length MOSFET (* measured)54                                               |

| Table 4.2 Process doping implantation information of 35 nm gate length Toshiba MOSFETs                                         |

| Table 4.3 Simulation and experiment performance parameters                                                                     |

| Table 4.4 45 nm CMOS technology features of various foundries                                                                  |

| Table 4.5 Simulation specifications for scaled CMOS                                                                            |

| Table 4.6 The relationship between on-currents of strained/unstrained gate-first/gate-last devices                             |

| Table 4.7 Strain enhancement of Id,sat in both NMOS and PMOS                                                                   |

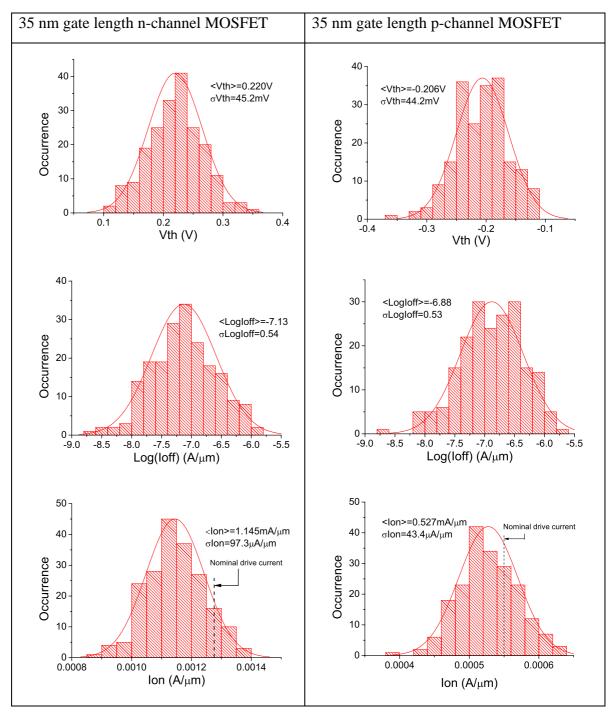

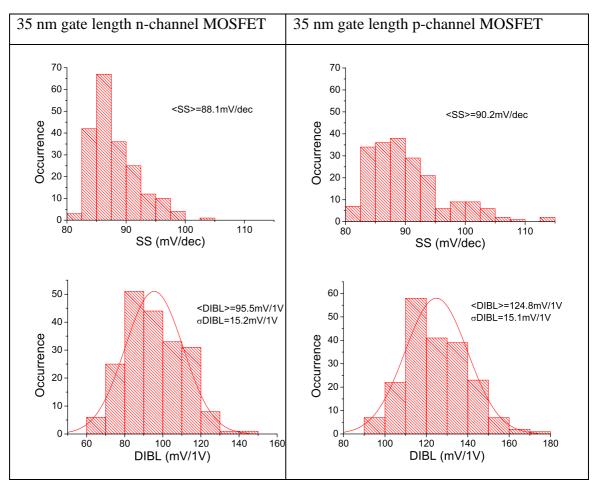

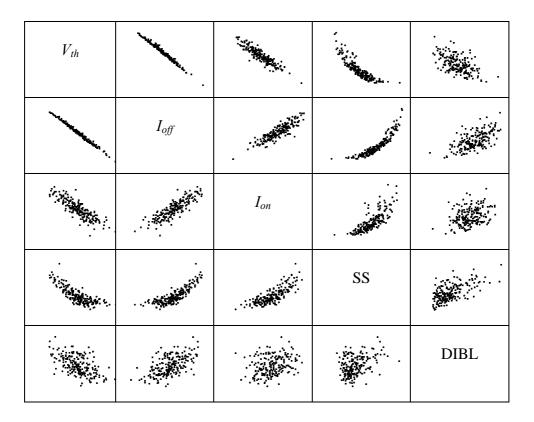

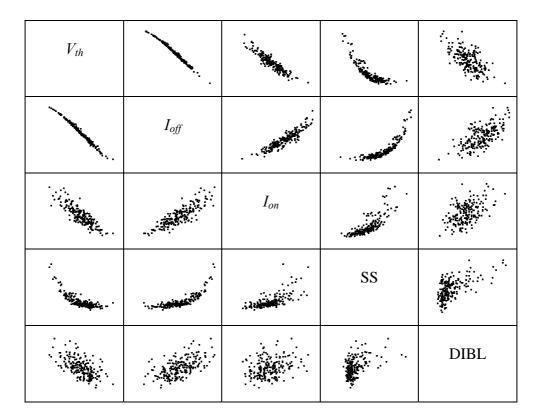

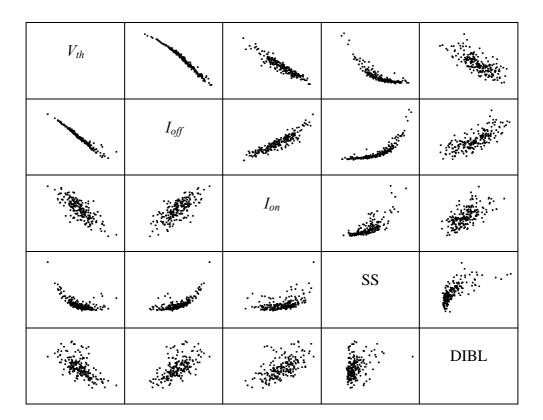

| Table 5.1 Scatter plots between figures of merit in 35 nm physical gate length MOSFETs down-left: nMOSFET, up-right: pMOSFET   |

| Table 5.2 Scatter plots between figures of merit in 25 nm physical gate length MOSFETs down-left: nMOSFET, up-right: pMOSFET94 |

| Table 5.3 Scatter plots between figures of merit in 18 nm physical gate length MOSFETs down-left; pMOSFET_up-right; pMOSFET    |

# List of figures

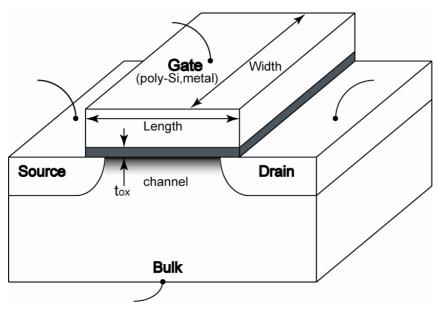

| Figure 2.1  | Schematic view of a surface-channel MOSFET device indicating physical gate length, channel width and physical gate dielectric oxide thickness ( $t_{ox}$ )5                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

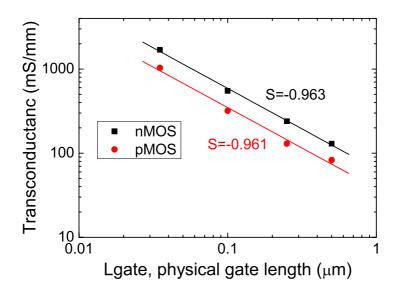

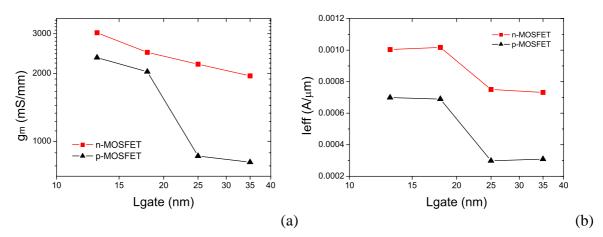

| Figure 2.2  | Saturation transconductance increases with reduction of gate length, indicating the uniform decreasing of gate oxide thickness                                                                                                                                                             |

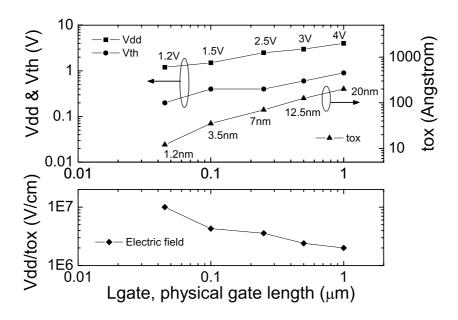

| Figure 2.3  | Supply voltage $(V_{dd})$ , threshold voltage $(V_{th})$ and gate oxide thickness were scaled down with gate length in the past. Meanwhile the vertical gate electric field increased rapidly.                                                                                             |

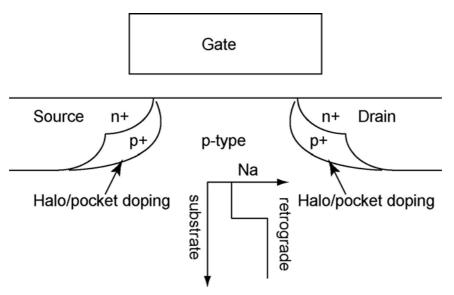

| Figure 2.4  | Schematic view of the doping profile in an n-channel MOSFET, including retrograde doping along substrate depth and halo/pocket doping close to source/drain                                                                                                                                |

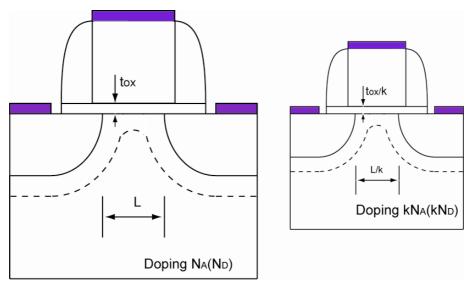

| Figure 2.5  | Schematic view of constant-field scaling principle shows proportional dimension reduction and doping increase                                                                                                                                                                              |

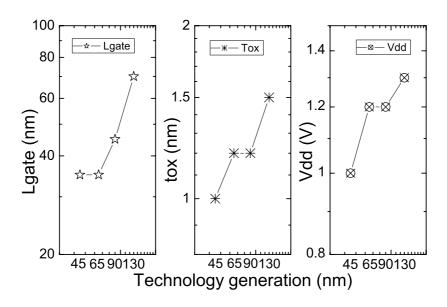

| Figure 2.6  | Evolutions of gate length, gate oxide thickness (EOT) and supply voltage in recent MOSFET technologies by Intel                                                                                                                                                                            |

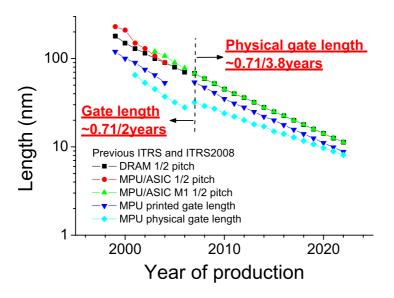

| Figure 2.7  | Summary of feature sizes in the evolution of technology in terms of recording and projection of ITRS editions                                                                                                                                                                              |

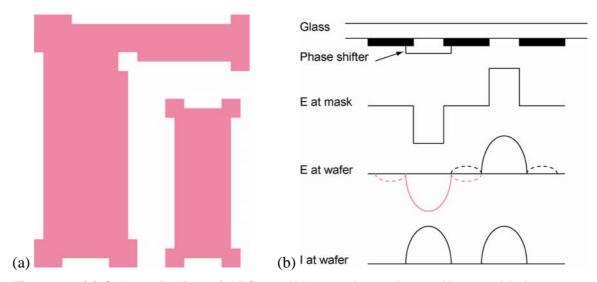

| Figure 2.8  | (a) Schematic view of OPC mask layout shows that serifs are added at corners and line-ends; (b) Phase-shifting mask operates to improve image boundary quality. Ultimately the intensity of image boundary at wafer tends to vanish15                                                      |

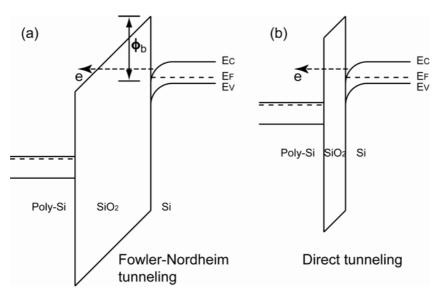

| Figure 2.9  | Band diagram view of Fowler-Nordheim tunnelling (a) and direct tunnelling (b) in MOS capacitors                                                                                                                                                                                            |

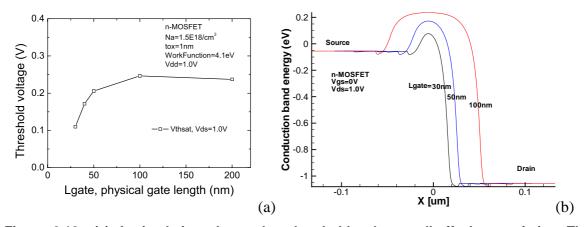

| Figure 2.10 | (a) A simulation shows that threshold voltage roll-off characteristics. The threshold voltage is determined at the drain current $5 \times 10^{-8}$ W/L ampere from $Id-Vg$ ; (b) Gate barrier lowering due to gate length shrinking20                                                     |

| Figure 2.11 | A simulation of a MOSFET demonstrating drain induced barrier lowering (a); The schematic view of charge-sharing model of short-channel effect (b)21                                                                                                                                        |

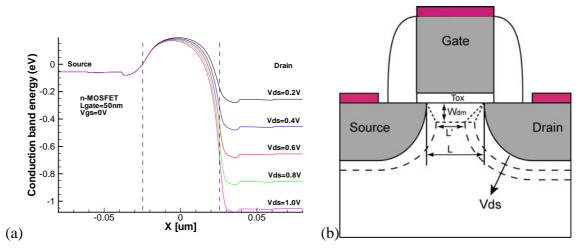

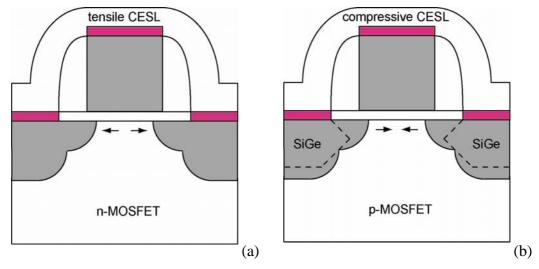

| Figure 2.12 | 2 Schematic demonstration of strained silicon schemes for (a) nMOSFETs and (b) pMOSFETs25                                                                                                                                                                                                  |

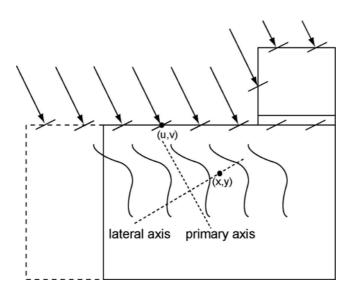

| Figure 3.1  | Schematic view shows the point-response distribution for ion implantation in Sentaurus process simulation. The arrow indicates the incident direction of the implanted ions, which impacts the solid surface. The curves inside the substrate indicate the primary distribution of dopants |

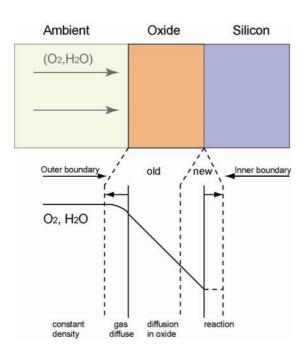

| Figure 3.2  | Illustration of thermal oxidation process on Si wafers. It indicates oxidant diffusion through oxide and its reaction with Si atoms at the interface with oxide                                                                                                                            |

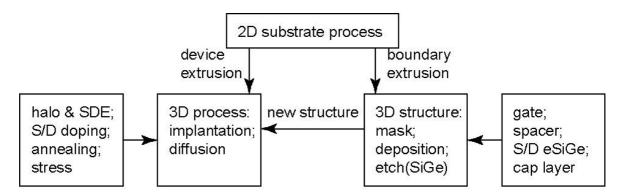

| Figure 3.3  | Schematic view of 3D process strategy. 3D structural changes such as deposition and etching which are used in 3D implantations and thermal processes                                                                                                                                       |

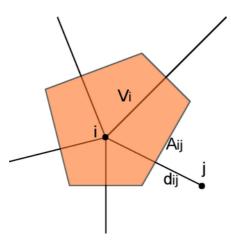

| Figure 3.4  | Schematic view of box discretization method in 2D. $V_i$ is the box volume associated with gird $i$ , $A_{ij}$ is the interface area between boxes of $i$ and $j$ , and $d_{ij}$ is the distance between $i$ and $j$                                                                       |

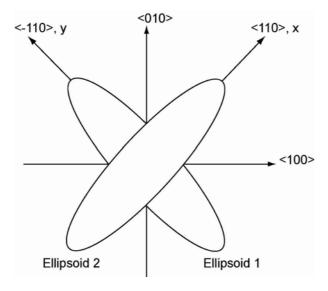

| Figure 3.5  | The simplified heavy hole 2D band structure without stress. Two equivalent ellipsoids are depicted in 2D treatment45                                                                                                                                                                       |

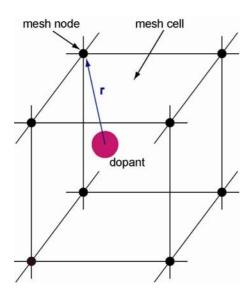

| C            | dopant is assigned to those neighbouring nodes according to various charge assignment schemes                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

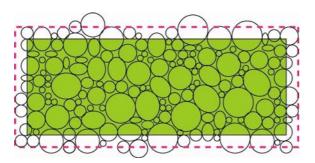

|              | Schematic description of photoresist defined line edge roughness in lithography and etching. Dashed and solid lines represent the printed and physical lines respectively; the circles indicate the polymer segregates of photoresists50                                 |

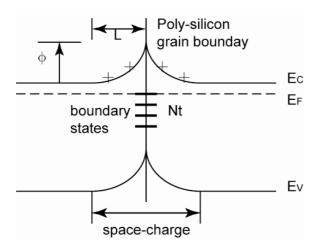

| Figure 3.8 I | Band diagram view of poly-silicon grain boundary states induced Fermi pinning                                                                                                                                                                                            |

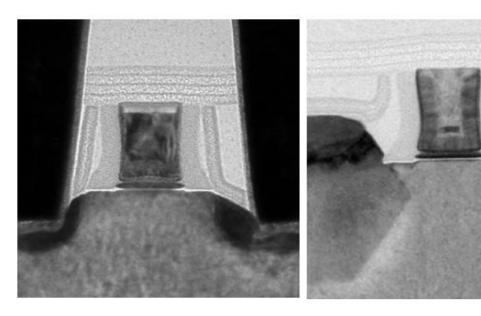

|              | TEM photograph of 35 nm gate length Toshiba MOSFET. Reprinted with permission from Inaba <i>et al.</i> , "High performance 35 nm gate length CMOS with NO oxynitride gate dielectric and Ni salicide," <i>IEEE Trans. Electron Devices</i> , Vol.49 No.12, (© 2002 IEEE) |

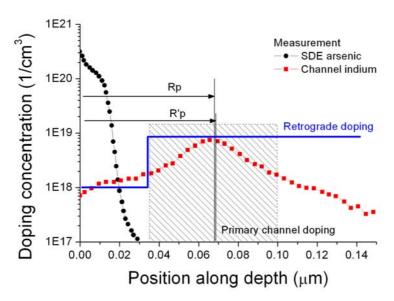

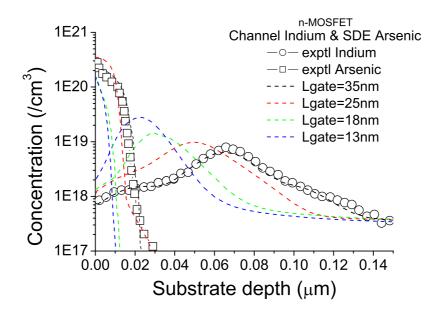

| Figure 4.2 F | Experimental doping profiles of 35 nm gate length Toshiba n-MOSFET56                                                                                                                                                                                                     |

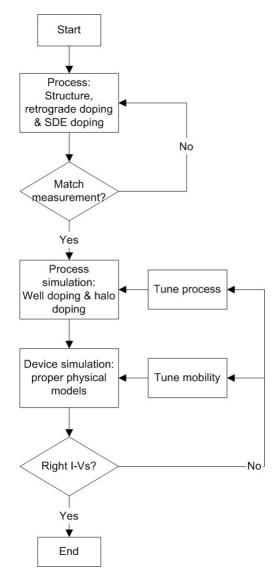

|              | Simplified flowchart of systematic simulation calibration methodology57                                                                                                                                                                                                  |

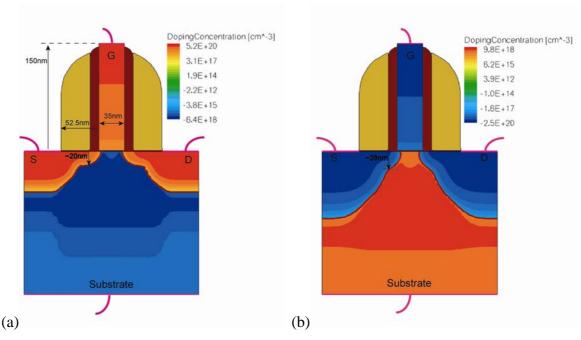

|              | Simulation structures of 35 nm gate length n-MOSFET (a) and p-MOSFET (b) based on Toshiba experimental data58                                                                                                                                                            |

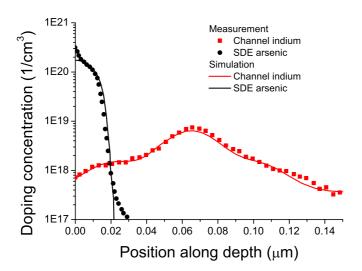

|              | Calibrated Channel retrograde indium and SDE abrupt arsenic doping profiles in n-MOSFETs59                                                                                                                                                                               |

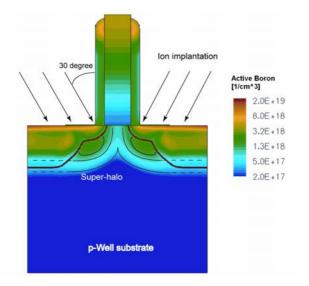

| _            | Halo process and final boron distribution in 35 nm gate length n-MOSFETs showing only two rotation directions of multiple implantations                                                                                                                                  |

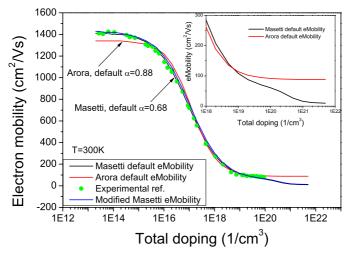

|              | Mobility model choice and modification in device simulation calibration including experimental reference                                                                                                                                                                 |

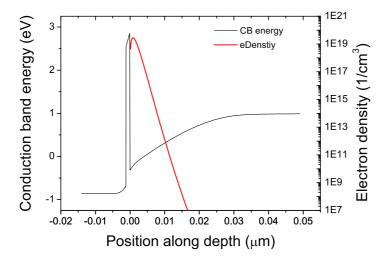

| _            | nversion carrier profile in the channel and the conduction band edge in n-MOSFET at on-state61                                                                                                                                                                           |

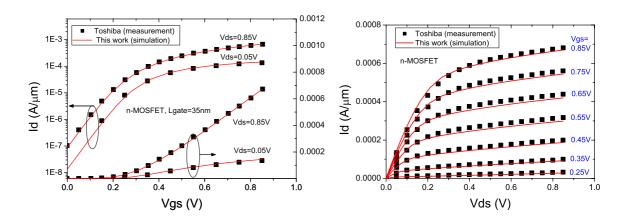

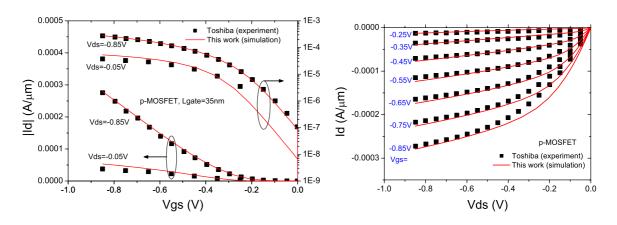

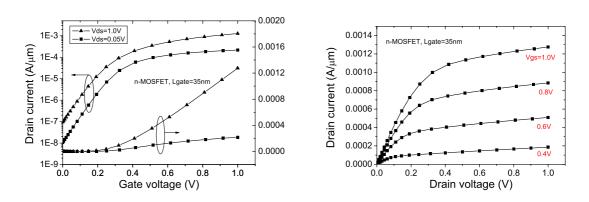

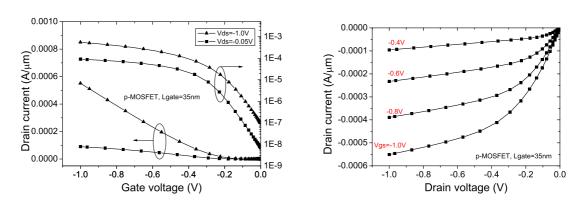

|              | <i>Id-Vg</i> and <i>Id-Vd</i> characteristics calibrations of Toshiba 35 nm gate length n-channel MOSFETs with supply voltage 0.85V                                                                                                                                      |

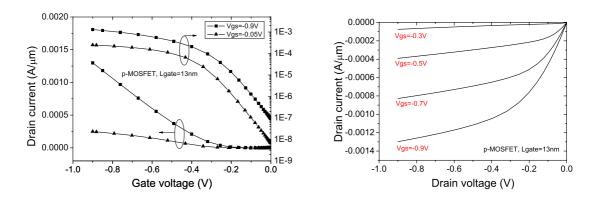

| _            | <i>Id-Vg</i> and <i>Id-Vd</i> characteristics calibrations of Toshiba 35 nm gate length p-channel MOSFETs with supply voltage 0.85V                                                                                                                                      |

|              | Intel 45 nm technology CMOS transistors. The left one is nMOS and the other is pMOS. Reprinted with permission from Auth <i>et al.</i> , "45 nm high-k + metal gate strain-enhanced transistors," in <i>Symp. VLSI Tech. Dig.</i> , (© 2008 IEEE)64                      |

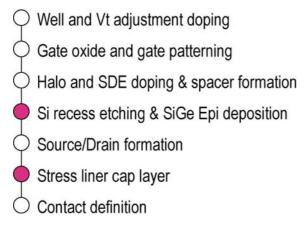

| Figure 4.12  | Process flow in simulations of 45 nm CMOS technology67                                                                                                                                                                                                                   |

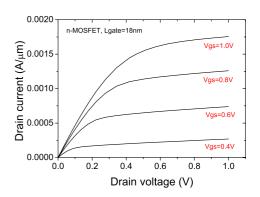

|              | High/low drain voltage <i>Id-Vg</i> characteristics and <i>Id-Vd</i> characteristics of redesigned 35 nm gate length n-MOSFET69                                                                                                                                          |

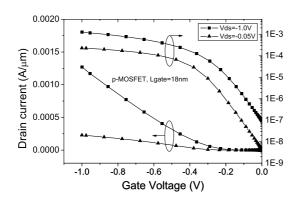

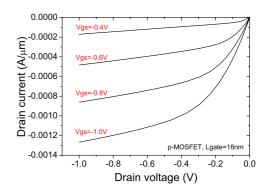

| -            | High/low drain voltage <i>Id-Vg</i> characteristics and <i>Id-Vd</i> characteristics of redesigned 35 nm gate length p-MOSFET69                                                                                                                                          |

| Figure 4.15  | Doping concentration scaling of n-MOSFETs71                                                                                                                                                                                                                              |

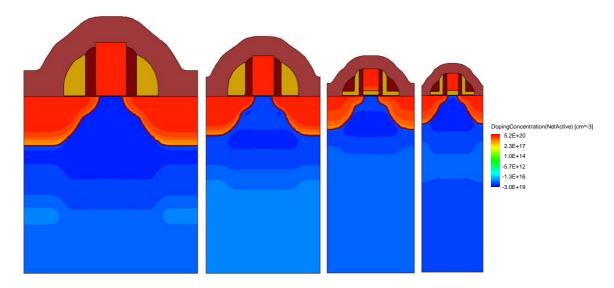

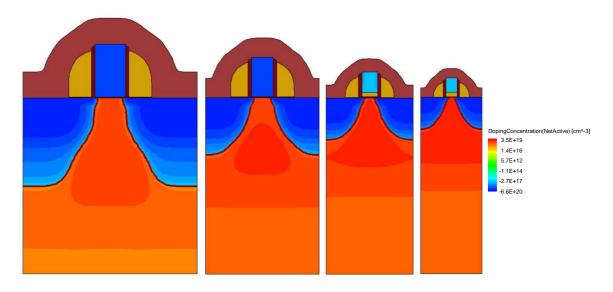

|              | The n-channel MOSFET structures and doping profiles respectively with 35, 25, 18 and 13 nm physical gate length                                                                                                                                                          |

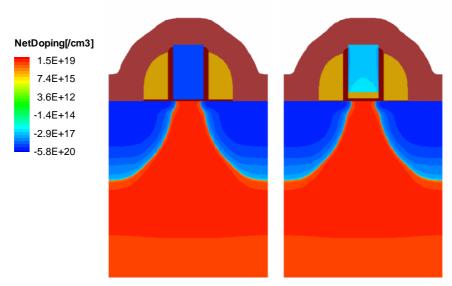

|              | The p-channel MOSFET structures and doping profiles respectively with 35, 25, 18 and 13 nm physical gate length                                                                                                                                                          |

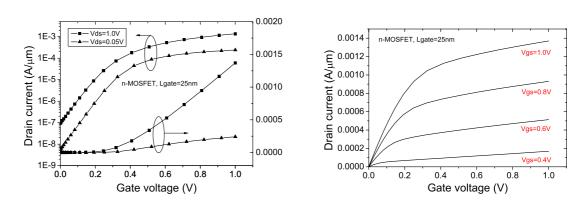

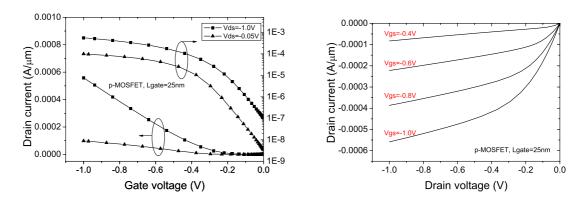

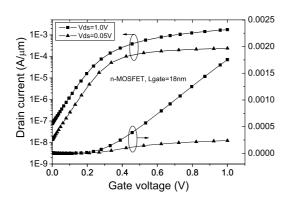

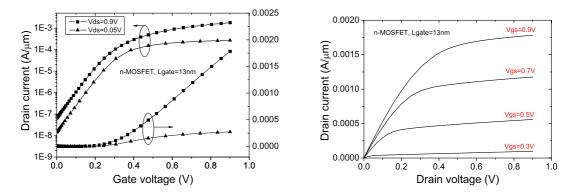

| _            | High/low drain voltage <i>Id-Vg</i> characteristics and <i>Id-Vd</i> characteristics of polysilicon 25 nm gate length n-channel MOSFET                                                                                                                                   |

| _            | High/low drain voltage <i>Id-Vg</i> characteristics and <i>Id-Vd</i> characteristics of polysilicon 25 nm gate length p-channel MOSFET                                                                                                                                   |

| Figure 5.13  | a function of gate length99                                                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

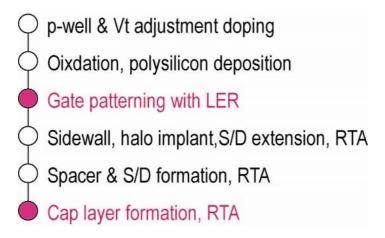

| Figure 6.1   | 3D process flow of modelling LER. LER is introduced at gate patterning and the tensile stressor is a deposited cap layer                                                                                                                                                                                                             |

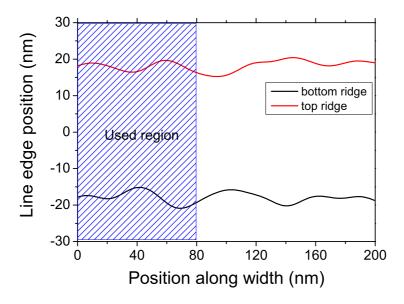

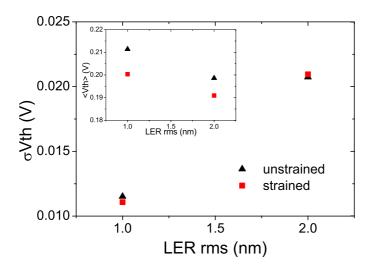

| Figure 6.2 l | LER sample generated by inverse Fourier transform of a Gaussian autocorrelation function. Gate width is along x-axis                                                                                                                                                                                                                 |

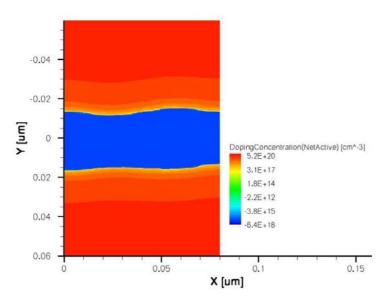

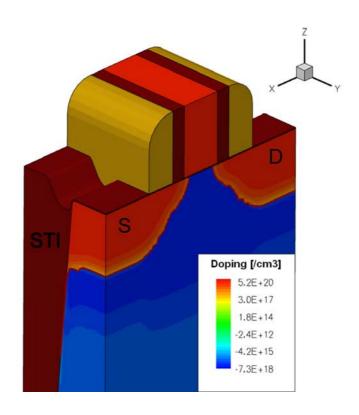

| Figure 6.3   | Channel doping profile 1 nm below the gate SiO <sub>2</sub> /Si interface. Junction line subject to LER is smoothed by the RTA step, but still exhibits fluctuation103                                                                                                                                                               |

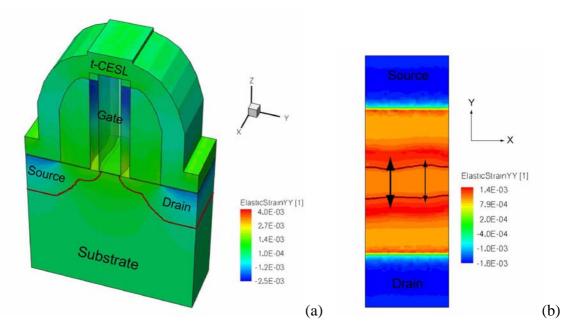

| Figure 6.4 ( | (a) Left graph is the distribution of channel direction normal strain. High tensile strain in the channel is transferred from the nitride cap layer above S/D; (b) Right graph is 2D cross section view of channel direction strain 1nm below the oxide/Si interface. Stronger tensile strain is induced in local channel shortening |

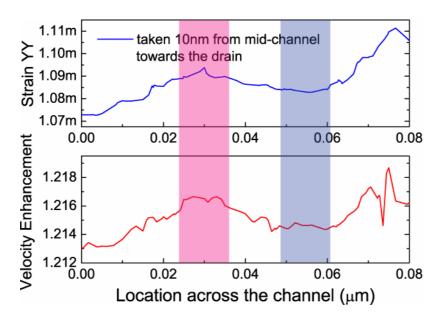

| Figure 6.5   | The upper trace is the 1D elastic strain yy value across the device width at 10nm away from the middle of the channel towards drain, 1nm under the gate dielectric. The bottom trace is the corresponding electron velocity enhancement due to the strain, indicating the strain induced mobility variability in the nMOSFET         |

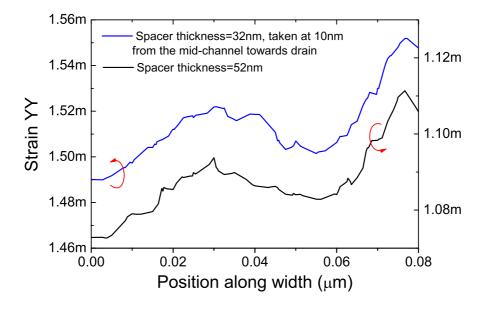

| Figure 6.6   | A thinner spacer guarantees increased strain, but also increases the strain variability due to LER                                                                                                                                                                                                                                   |

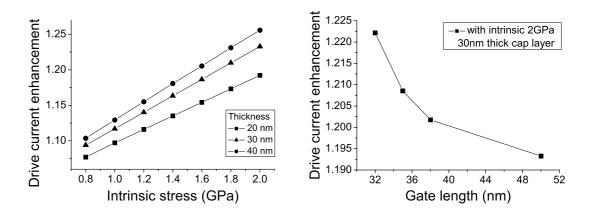

| Figure 6.7   | The left graph shows on-current enhancement dependence on intrinsic stress and tensile cap thickness. The right graph shows the relationship of drive current to gate length, with fixed spacer size                                                                                                                                 |

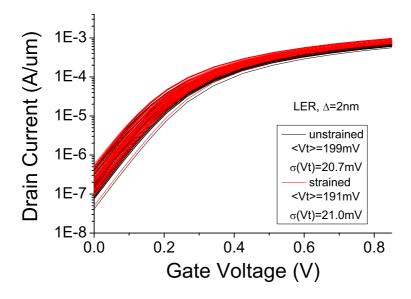

| Figure 6.8 5 | 50 simulated high drain Id-Vg curves of nominal identical devices with/without stress, influenced by LER $\Delta$ =2 nm                                                                                                                                                                                                              |

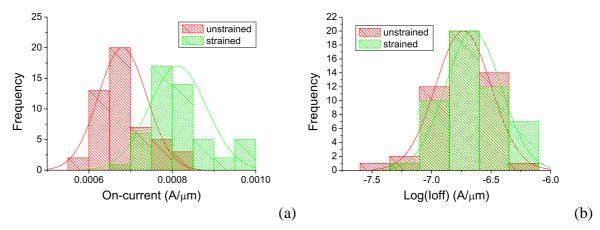

| Figure 6.9   | The left graph (a) shows statistics of on-current variation. Strained devices have larger current on average, but also bigger variation. The right graph (b) shows off-current distribution of devices with/without strain                                                                                                           |

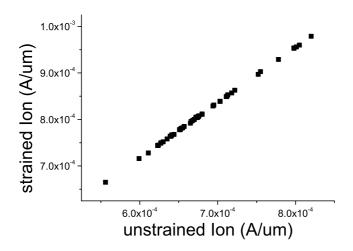

| Figure 6.10  | The correlation of strained device on-currents to unstrained device on-currents.                                                                                                                                                                                                                                                     |

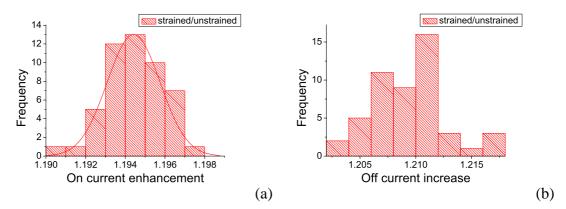

| Figure 6.11  | The left graph shows the statistics of on-current enhancement. The right graph shows the statistical distribution of off-current due to strain, which is wider compared with the drive current enhancement distribution. Strained devices show additional variation due to local fluctuations in mobility enhancement.               |

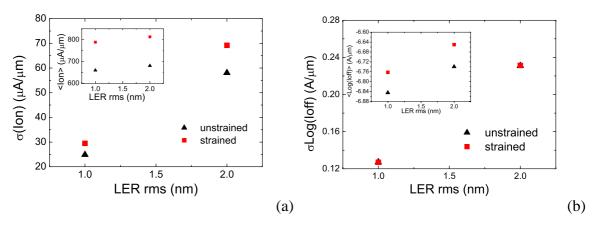

| Figure 6.12  | Statistical results of drive current (a) and off current (b) for LER $\Delta$ =1nm and 2nm                                                                                                                                                                                                                                           |

| Figure 6.13  | Statistical results of saturation threshold voltage for LER $\Delta$ =1nm and 2nm. 109                                                                                                                                                                                                                                               |

| Figure 6.14  | Process simulation of the 35 nm gate length n-MOSFET with edge STI is showing the structure of 35 nm channel width and net active doping111                                                                                                                                                                                          |

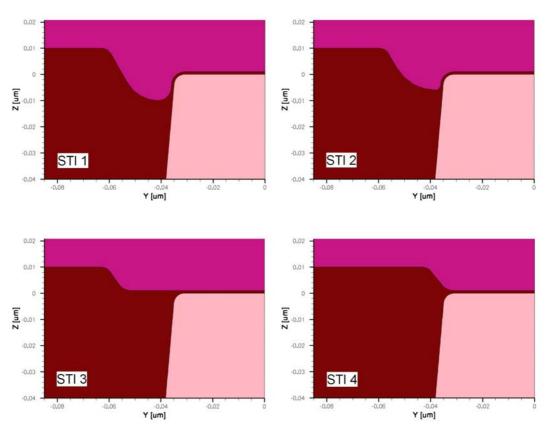

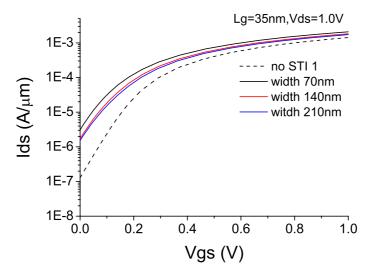

| Figure 6.15  | Various STI geometries are compared and studied to explore the narrow-channel effect                                                                                                                                                                                                                                                 |

| Figure 6.16  | Width dependence of $I_D$ - $V_G$ characteristics of an n-MOSFET in the presence of structure $STI\ I$ , compared with a control device without $STI$ 113                                                                                                                                                                            |

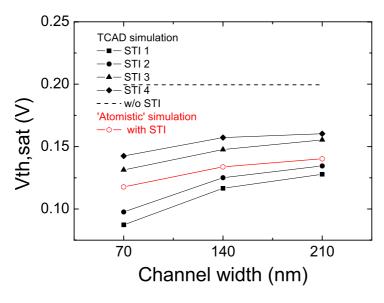

| Figure 6.17  | Width dependence of saturation threshold voltage for different STI architectures                                                                                                                                                                                                                                                     |

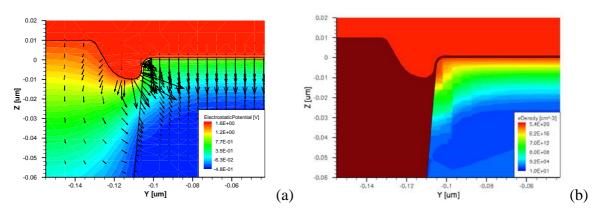

| Figure 6.18  | potential with in-plane electric field, and (b) electron density114                                                                                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

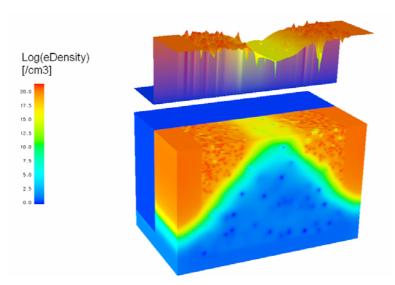

| Figure 6.19  | Electron concentration subject to random dopants, biased at zero, in the presence of the STI structure. The slice for the surface plot is taken at 0nm depth, namely silicon surface.                                                                                                                                                                                                              |

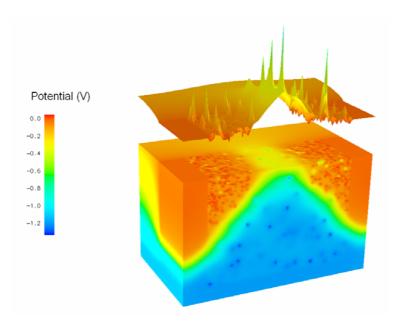

| Figure 6.20  | Electrostatic potential subject to random dopants with STI, biased at zero. The slice is surface potential referred to source contact                                                                                                                                                                                                                                                              |

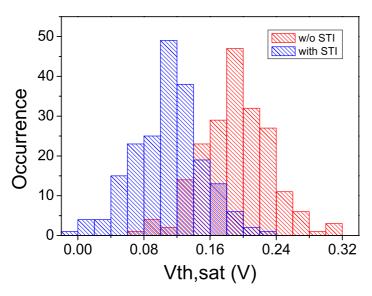

| Figure 6.21  | Saturation threshold voltage distribution under RDD induced variability for devices of channel width 70nm with/without STI                                                                                                                                                                                                                                                                         |

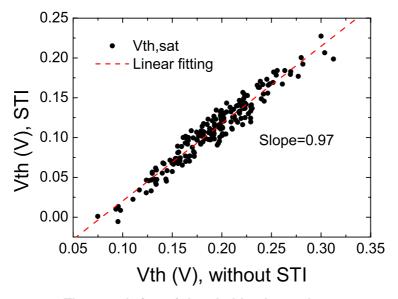

| Figure 6.22  | The correlation of threshold voltages between two sets of devices with/without STI                                                                                                                                                                                                                                                                                                                 |

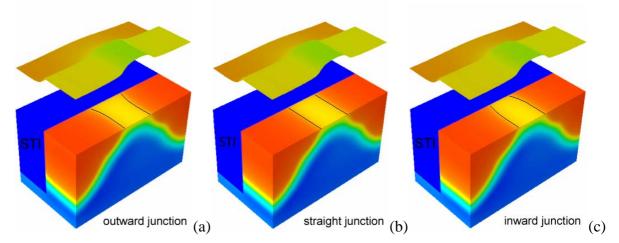

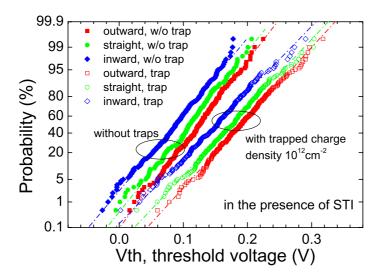

| Figure 6.23  | Simulation domains of shallow trench isolated $35 \times 35$ nm <sup>2</sup> channel area nMOSFETs for three channel junction shapes near STI: outward (a), straight (b), and inward (c) junctions, showing top surface potential (above) and electron density within the device (below) with biasing at $V_{gs}$ =0.5V and $V_{ds}$ =0.05V                                                        |

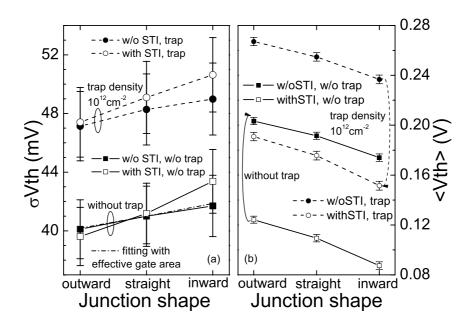

| Figure 6.24  | STI effect on statistical variability and reliability of threshold voltage (a) standard deviation and (b) mean for typical STI-adjacent junction cases119                                                                                                                                                                                                                                          |

| Figure 6.25  | Threshold voltage distribution in the STI devices subject to different junction shapes close to the STI edge, and to degradation                                                                                                                                                                                                                                                                   |

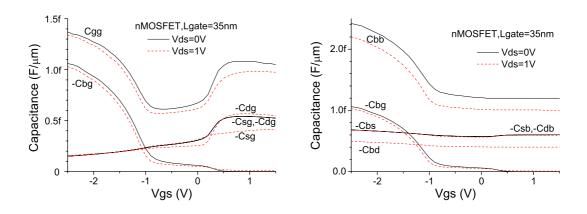

| Figure 7.1   | Capacitance against gate voltage characteristics are given for gate terminal (left) and bulk terminal (right) in a 35 nm nMOSFET. Here Cij is the coupling capacitance between electrodes i and j. Cgg is the total gate capacitance, and Cbb is the total capacitance related with bulk contact                                                                                                   |

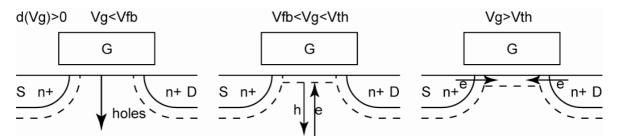

| Figure 7.2 l | Physical view of carrier motion when forming gate capacitance in nMOSFETs, with zero biases of source, drain and bulk, namely source and drain in symmetry                                                                                                                                                                                                                                         |

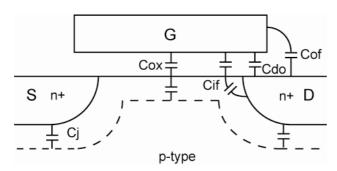

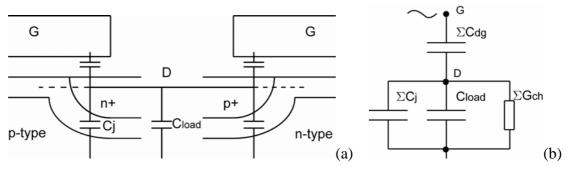

| Figure 7.3   | Schematic view of geometrical distribution of capacitances in nMOSFETs126                                                                                                                                                                                                                                                                                                                          |

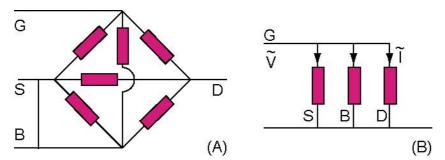

| Figure 7.4   | Two-port ac network of MOSFETs (A) with one port of G-S(B) and other port of D-S(B) and current-gain $H_{21}$ parameter calculation in two-port MOSFETs (B).                                                                                                                                                                                                                                       |

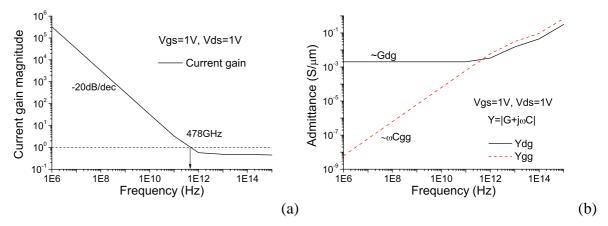

| Figure 7.5   | Current gain magnitude versus frequency (a) and admittances of d-g and g-g versus frequency in 35 nm nMOSFET (b)                                                                                                                                                                                                                                                                                   |

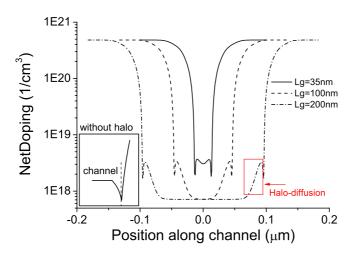

| Figure 7.6 l | Lateral net active doping profiles for variable gate length n-MOSFETs130                                                                                                                                                                                                                                                                                                                           |

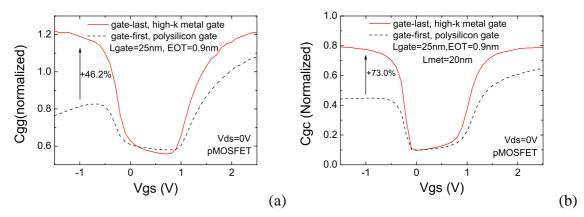

| Figure 7.7 ( | (a) The total capacitance spreads of 25 nm poly-gate and metal-gate pMOSFETs compared at zero drain bias. A 46% increase of inversion capacitance is achieved for the high- $k$ /metal gate device. (b) Intrinsic gate capacitances for poly gate and metal gate pMOSFETs compared at zero drain bias. The intrinsic gate capacitance increases by about 73% in inversion for the metal gate case. |

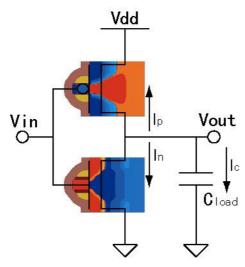

|              | Schematic view of inverter configuration using mixed-mode simulation, where redesigned 35 nm gate length n-MOSFET and p-MOSFET in circuit environment are solved using numerical transient simulation                                                                                                                                                                                              |

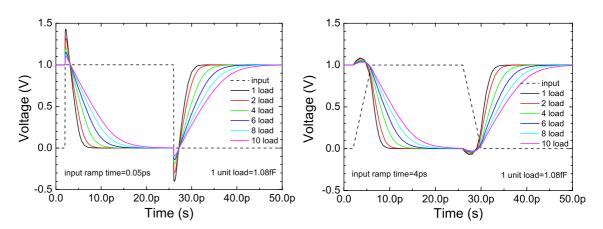

| Figure 7.9   | 35 nm gate length CMOS inverter transfer characteristics with different load capacitance and different input ramp time                                                                                                                                                                                                                                                                             |

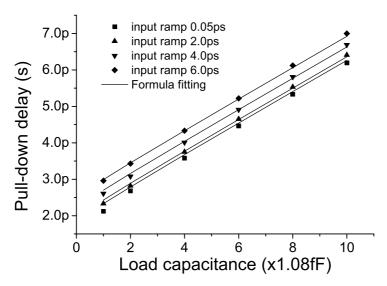

| Figure 7.10  | 35 nm CMOS Inverter propagation delay as a function of capacitances and input ramp time, with Vdd=1.0V                                                                                                                                                                                                                                                                                             |

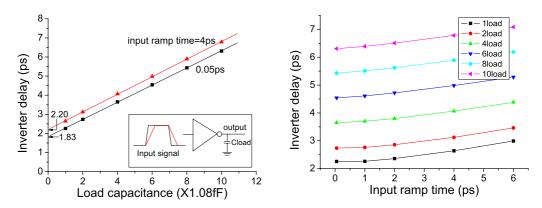

| C           | (a) Conduction components connected with drain contacts of 35 nm CMOS inverters. (b) The equivalent circuit during input initial ramp time1 | 36  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

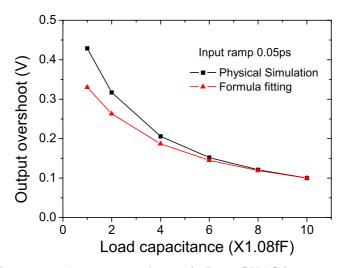

| 0           | Output overshoot of 35 nm CMOS inverters with fast transition of input, Vdd=1V                                                              | 136 |

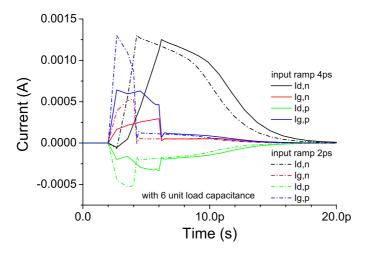

| •           | Gate currents and drain currents of 35 nm gate length nMOS and pMOS around input rise-up switching for different input ramp time            | 137 |

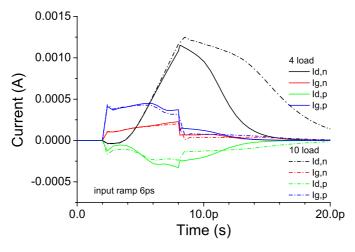

| 0           | Gate currents and drain currents of 35 nm gate length nMOS and pMOS around input rise-up switching for different load capacitances          | 37  |

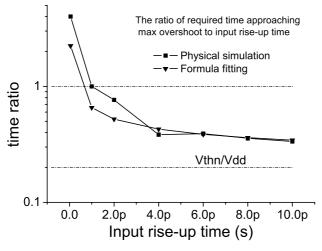

| _           | Analytical estimate of required time reaching maximum overshoot in 35 nm gate length CMOS inverters.                                        |     |

| Figure 7.16 | Physical fitting of 35 nm gate length CMOS inverter delay                                                                                   | 39  |

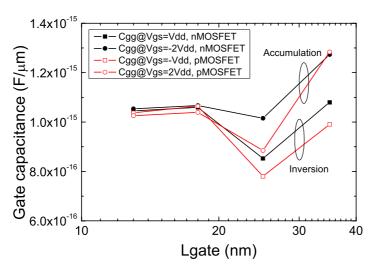

| Figure 7.17 | Scaling of total gate capacitance                                                                                                           | 41  |

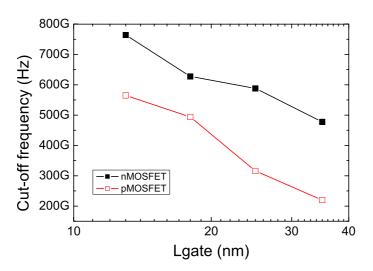

| Figure 7.18 | Cut-off frequencies of scaled MOSFETs.                                                                                                      | 41  |

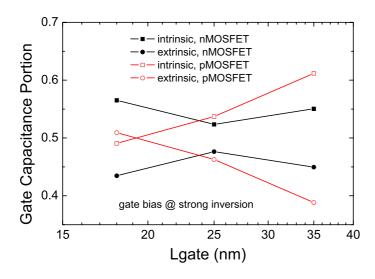

| Figure 7.19 | Intrinsic/extrinsic inversion gate capacitances of scaled MOSFETs1                                                                          | 42  |

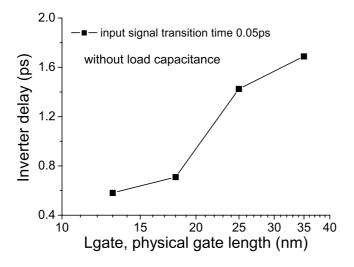

| Figure 7.20 | Intrinsic inverter delays of scaled MOSFETs1                                                                                                | 42  |

# **List of symbols**

| Symbols                                       | Descriptions                                                   | Units               |

|-----------------------------------------------|----------------------------------------------------------------|---------------------|

| α                                             | Scaling factor for electric field                              | -                   |

| $\beta$                                       | Gain factor of a MOS transistor                                | $A/V^2$             |

| $\Delta$                                      | Root mean square (rms) for LER                                 | nm                  |

| $\Delta E_{strain}$                           | Energy band split due to strain                                | eV                  |

| $\Delta z$                                    | Distance of inversion carrier centroid away the interface      | nm                  |

| ${\cal E}$                                    | Permittivity                                                   | F/cm                |

| $\mathcal{E}_{highK}$                         | High-k material permittivity                                   | F/cm                |

| $\mathcal{E}_{ox}$                            | Silicon dioxide permittivity                                   | F/cm                |

| $\mathcal{E}_{\!\scriptscriptstyle Si}$       | Silicon permittivity                                           | F/cm                |

| $\overline{\mathcal{E}}$ , $\mathcal{E}_{ij}$ | Strain tensor, strain component                                | -                   |

| $\phi$                                        | Potential                                                      | Volt (V)            |

| $\phi_i$                                      | Potential defined by $\phi_i = -E_i/q$                         | Volt (V)            |

| Φ                                             | Quasi-Fermi potential                                          | Volt (V)            |

| $arphi_m$                                     | Metal work function                                            | Volt (V)            |

| K                                             | Scaling factor                                                 | -                   |

| Λ                                             | Correlation length for LER                                     | nm                  |

| λ                                             | Wave length                                                    | nm                  |

| $\mu$                                         | Mobility                                                       | $cm^2/Vs$           |

| $\mu_n$                                       | Electron mobility                                              | cm <sup>2</sup> /Vs |

| $\mu_p$                                       | Hole mobility                                                  | cm <sup>2</sup> /Vs |

| $\rho$                                        | Charge density                                                 | C/cm <sup>3</sup>   |

| $ ho_{trap}$                                  | Trap charge density                                            | C/cm <sup>3</sup>   |

| $ar{\sigma}$ , $\sigma_{ij}$                  | Stress tensor, stress component                                | N/cm <sup>2</sup>   |

| τ                                             | Inverter propagation delay                                     | S                   |

| $	au_{int}$                                   | Intrinsic inverter delay                                       | S                   |

| $\omega$                                      | Angular frequency ( $\omega$ = $2\pi f$ )                      | radians/s           |

| $\psi_B$                                      | Difference between intrinsic and extrinsic Fermi leverls       | Volt (V)            |

| A                                             | Area                                                           | $cm^2$              |

| C                                             | Capacitance                                                    | F                   |

| $C_{gc}$                                      | Gate-to-channel capacitance (per unit width)                   | $F(F/\mu m)$        |

| $C_{gg}$                                      | Total gate capacitance (per unit width)                        | $F(F/\mu m)$        |

| $C_j$                                         | P-N junction capacitance (per unit width)                      | $F(F/\mu m)$        |

| $C_{ox}$                                      | Gate oxide capacitance per unit area                           | F/cm <sup>2</sup>   |

| $C_1$ , $C_2$ , $C_3$                         | Fitting coefficients                                           | -                   |

| $D$ , $D_n$ , $D_p$                           | Diffusion coefficient, electron and hole diffusion coefficient | cm <sup>2</sup> /s  |

| E                                             | Electric field                                                 | V/cm                |

| $E_a$                                         | Activation energy in NBTI                                      | eV                  |

| $E_C$ , $E_V$                                 | Conduction, valence band edge energy                           | eV                  |

| $E_F$                                         | Fermi level                                                    | eV                  |

| $E_i$                                         | Intrinsic Fermi level                                          | eV                  |

| f                    | Circuit frequency                                                | Hz                |

|----------------------|------------------------------------------------------------------|-------------------|

| $f_T$                | Cut-off frequency                                                | Hz                |

| $G$ , $G_{ij}$       | Small-signal conductance matrix, small-signal conductance        | siemens           |

| $g_m$                | Small-signal transconductance                                    | siemens           |

| h                    | Planck's constant (6.626×10 <sup>-34</sup> )                     | Js                |

| $\hbar$              | Reduced planck's constant $(\hbar = h/2\pi)$                     | Js                |

| $I_d$                | Drain current                                                    | A                 |

| $I_{dsat}$           | Drain saturation current                                         | A                 |

| $I_{e\!f\!f}$        | Effective drive current                                          | A                 |

| $I_{off}$ , $I_{on}$ | Off-current (per unit width), on-current (per unit width)        | A (A/μm)          |

| $J, J_n, J_p$        | Current density, electron and hole current densities             | A/cm <sup>2</sup> |

| k                    | Boltzmann's constant (1.38×10 <sup>-23</sup> )                   | J/K               |

| l                    | Mean free path                                                   | nm                |

| L                    | Channel length                                                   | nm                |

| $L_{gate}$           | Physical gate length                                             | nm                |

| $L_{met}$            | Metallurgical channel length                                     | nm                |

| n                    | Electron density                                                 | cm <sup>-3</sup>  |

| $n_i$                | Intrinsic electron density                                       | cm <sup>-3</sup>  |

| m                    | MOSFET body-effect coefficient                                   | -                 |

| $m_l$                | Carrier longitudinal mass                                        | kg                |

| $m_t$                | Carrier transverse mass                                          | kg                |

| $N_a$                | Acceptor doping concentration                                    | cm <sup>-3</sup>  |

| $N_a^-$              | Ionized acceptor doping concentration                            | cm <sup>-3</sup>  |

| $N_C$                | Effective density of states of conduction band                   | cm <sup>-3</sup>  |

| $N_d$                | Donor doping concentration                                       | cm <sup>-3</sup>  |

| $N_d^+$              | Ionized donor doping concentration                               | cm <sup>-3</sup>  |

| $N_p$                | Poly-silicon doping concentration                                | cm <sup>-3</sup>  |

| $N_{sub}$            | Substrate doping concentration                                   | cm <sup>-3</sup>  |

| $N_t$                | Trap sheet density                                               | cm <sup>-2</sup>  |

| p                    | Hole desntiy                                                     | cm <sup>-3</sup>  |

| P                    | Power dissipation                                                | W                 |

| $P_{active}$         | Active power dissipation                                         | W                 |

| $P_{passive}$        | Standby power dissipation                                        | W                 |

| $P_d$                | Possibility to travel <i>d</i> without suffering from collisions | -                 |

| $P_{E_b}$            | Possibility to obtain energy $E_b$ (eV)                          | -                 |

| q                    | Electronic charge (1.6×10 <sup>-19</sup> )                       | C                 |

| $Q_{dm}$             | Maximum depletion-layer charge per unit area                     | C/cm <sup>2</sup> |

| $Q_{inv}$            | Inversion charge per unit area                                   | C/cm <sup>2</sup> |

| $R_{net}$            | Net recombination rate                                           | 1/s               |

| S                    | Sub-threshold slope                                              | mV/dec            |

| t                    | Time                                                             | S                 |

| $t_{highK}$          | High-k material thickness                                        | nm                |

| $t_{ox}$             | Silicon oxide thickness                                          | nm                |

| T                    | Temperature                                                      | Kelvin (K)        |

| ν               | Carrier velocity                                          | cm/s     |

|-----------------|-----------------------------------------------------------|----------|

| $v_{sat}$       | Carrier saturation velocity                               | cm/s     |

| V               | Voltage                                                   | Volt (V) |

| $V_d$           | Drain voltage                                             | Volt (V) |

| $V_{dd}$        | Supply voltage                                            | Volt (V) |

| $V_{fb}$        | Flat-band voltage                                         | Volt (V) |

| $V_g$           | Gate voltage                                              | Volt (V) |

| $V_{in}$        | Input node voltage of a logic gate                        | Volt (V) |

| $V_{out}$       | Output node voltage of a logic gate                       | Volt (V) |

| $V_{overshoot}$ | Inverter output overshoot voltage during input transition | Volt (V) |

| $V_{th}$        | Threshold voltage                                         | Volt (V) |

| $V_{th,sat}$    | Saturation threshold voltage                              | Volt (V) |

| W               | Channel width                                             | μm       |

| $W_d$           | Depletion-layer width                                     | nm       |

| $W_{dm}$        | Maximum depletion-layer width                             | nm       |

| $x_j$           | Junction depth                                            | nm       |

| $Y$ , $Y_{ij}$  | Admittance matrix, admittance component                   | siemens  |

# **Chapter I**

#### 1. Introduction

#### 1.1. Motivation

The progressive down-scaling of bulk metal-oxide-semiconductor field effect transistors (MOSFETs) has been the driving force behind the integrated circuit (IC) industry for several decades, continuously delivering higher component densities and greater chip functionality, while reducing the cost per function from one CMOS technology generation to the next. Moore's law boosts IC industry profits by constantly releasing high-quality and inexpensive electronic applications into the market using new technologies. From the 1  $\mu$ m gate lengths of the eighties to the 35 nm gate lengths of contemporary 45 nm technology, the industry successfully achieved its scaling goals, not only miniaturizing devices but also improving device performance.

However, the years of 'happy scaling' are over. Several challenges are facing the further miniaturization of the transistors in Si chips. First, there are the process challenges of continued scaling including, among others, sub-wavelength patterning and the formation of ultra-shallow junctions. Continual process innovation is needed, including immersion optical lithography, and the flash lamp and laser annealing implemented at the 45 nm CMOS technology to achieve high-fidelity patterns and high-activation/low dopant diffusion. Secondly, the scaling of contemporary deep-decananometer gate length transistors results in the deterioration of electrical characteristics due to short-channel, quantum mechanical and transport effects. Countermeasures like halo-doping can suppress the short-channel effect in conventional MOSFETs but at the expense of increased quantum effects and reduced mobility. Novel MOSFET structures such as fully-depleted silicon-on-insulator devices are required to achieve a fundamental improvement in electrostatic integrity. Finally, intrinsic parameter fluctuations, resulting from the discreteness of charge and the granular nature of matter in real decanano devices, hamper the integration of scaled transistors. Statistical variability unavoidably increases drastically

with further scaling. It requires the introduction of novel device architectures and the adaptation of smarter circuit and system design strategies.

It is natural to ask the questions how far the scaling of the conventional bulk MOSFET can continue in the presence of the above technological or physical limitations. This project tries to shine some light on these questions through aggressively scaling contemporary bulk MOSFETs using advanced commercial TCAD tools, and simulating their statistical variability using the Glasgow 'atomistic' simulator.

#### 1.2. Aims and objectives

The aim of this PhD is to study the realistic scaling of bulk MOSFETs and their statistical variability. In order to accomplish this aim, several key research objectives have been identified:

- To study the physical effects governing the operation of aggressively scaled bulk

MOSFETs, and the associated challenges for contemporary CMOS technology;

- To master TCAD process and device simulations, and 'atomistic' simulation techniques;

- To calibrate the simulations in respect of state-of-the-art 45 nm technology n- and p-MOSFETs, and to perform careful scaling to smaller technologies according to the prescriptions and the requirements of the ITRS;

- To perform a statistical variability study on these scaled bulk MOSFETs;

- To investigate the impact of realistic structures such as stressors and shallow trench isolation on the statistical variability and reliability;

- To evaluate the performance of scaled devices, including their impact on timing and speed of simple circuits.

#### 1.3. Thesis outline

This PhD thesis includes eight chapters, formulated in a general structure of introduction-main body-conclusion.

Chapter 1 describes the motivation and the aim and objectives of this PhD study.

Chapter 2 starts with the bulk MOSFET scaling rules and the projections of the ITRS. It then describes several scaling challenges including: feature patterning, power control, poly

depletion effects, quantum effects, short-channel effects, reliability and variability. Finally it explains technology boosters, such as induced strain and high-k/metal gates, that enable further device scaling.

Chapter 3 focuses on the simulation tools and methodology used in this study. It selectively describes the simulation of key process steps, the physics and numerical methods behind the device simulation, and finally the 'atomistic' simulation techniques.

Chapter 4 presents the scaling study based on bulk 45 nm technology MOSFETs. It starts with the calibrations of both the process and the device simulators against the doping and the characteristics of published Toshiba MOSFETs. Then the devices are redesigned adopting the latest technology features including stress engineering to achieve the equivalent performance to the contemporary 45 nm CMOS technology. The careful scaling informed by ITRS proceeds to 25 nm, 18 nm, 13 nm physical gate lengths.

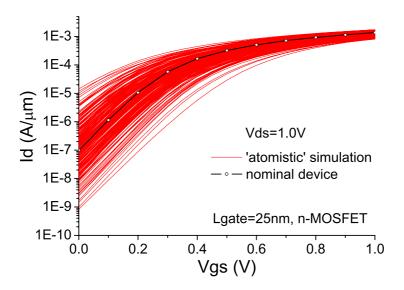

Chapter 5 presents the predictive study of statistical variability of the scaled MOSFETs. The statistical distribution of threshold voltage, on-current, and off-current are obtained for 35 nm, 25 nm and 18 nm gate length MOSFETs. The expected increase in the statistical variability with scaling is observed. This includes the detailed statistical distributions of these key parameters.

Chapter 6 investigates the impact of strain and shallow trench isolation on the statistical variability. The strain variability in channel due to gate line edge roughness is studied. The stress enhances the drive current variation. The shallow trench isolation (STI) enhances the current density near the isolation edge, inducing a threshold voltage lowering in narrow transistors. The impact of STI-adjacent junction shapes on the random dopant induced threshold voltage fluctuations is also investigated.

Chapter 7 presents a systematic study of the a.c. and dynamic performance of the scaled devices. It analyzes the MOSFET capacitances using the split C-V approach. Mixed-mode inverter simulation is performed to analyze the intrinsic and extrinsic inverter delay.

Chapter 8 draws conclusions and proposes future avenues for related research.

# **Chapter II**

# 2. MOSFET technology scaling, challenges and boosters

The advance of the IC industry has been driven by the continuous down-scaling of MOSFETs for several decades. A consistent evolution of MOSFET technologies has been essential in overcoming many perceived 'insurmountable' barriers. Recently, novel materials and processes have been introduced, and new device structures proposed, to ensure further benefits from device miniaturization.

#### 2.1. MOSFET scaling

#### 2.1.1.Past scaling trends

The scaling of the MOSFET devices has continued from its first introduction in integrated circuits four decades ago. This has resulted in doubling the component density on a single chip by proportionally scaling of the transistor dimensions over a period of time. This reduces the cost per function and delivers more functions at the same time, which is the essence of the famous *Moore's law* [1]. At the same time the scaling leads to improved performance while controlling the power consumption by reducing the supply voltage and carefully tuning the design. Schematically shown in Figure 2.1, a MOSFET consists of two back-to-back connected *p-n* junctions. The gate voltage applied across metal-oxide-semiconductor (MOS) capacitor creates an inversion channel connecting the source and the drain, and controls the carrier density in it. From an operational point of view, the MOSFET has two critical structural parameters, namely gate length and gate dielectric thickness. MOSFET scaling affects both lateral and vertical device dimensions. While the reduction of the lateral dimensions increases the transistor density in a chip, the reduction of the oxide thickness is needed to ensure good electrostatic integrity.

Figure 2.1 Schematic view of a surface-channel MOSFET device indicating physical gate length, channel width and physical gate dielectric oxide thickness ( $t_{ox}$ ).

#### 2.1.1.1. Transistor dimensions

With the scaling of the lateral dimensions by a factor of  $1/\sqrt{2}$  each technology generation, the bulk MOSFET area is reduced by one half, doubling the circuit density and enhancing functionality. Since the publication of the famous paper on scaling by Dennard *et al.* in 1974 [2], the gate length of the transistor in modern chips has been reduced by more than two orders featuring 35 nm gate length MOSFETs in the 45 nm technology generation [3]. The equivalent oxide thickness has been reduced from 100 nm to around 1.0 nm in contemporary technology. In addition, the number of transistors in a microprocessor chip, has increased 100,000 times from the first microprocessor Intel 4004 (about 2,300 transistors) released in 1971, by transistor scaling and additional efforts of compacting the physical layout [4][5].

In contemporary MOSFETs the drain current  $I_d$  is determined by [6]

$$I_d / W = C_{ox}(V_g - V_{th})v,$$

(2.1)

where W is the channel width,  $C_{ox}$  is the gate capacitance per unit area, and v is the source end carrier velocity. The saturation transconductance  $g_m$  may be obtained by

$$g_m / W = \frac{\partial I_d}{\partial V_g} / W = C_{ox} \times v = \frac{\varepsilon_{ox}}{t_{ox}} \times v.$$

(2.2)

where  $\varepsilon_{ox}$  is the oxide permittivity. The carrier velocity is usually saturated at short-channel MOSFETs, thus  $g_m/W$  is an index of gate oxide thickness  $t_{ox}$ . Since gate capacitance per unit area is inversely proportional to oxide thickness, both the device current and the

saturation transconductance are closely related to oxide thickness. As demonstrated in Figure 2.2 for several past technology generations [7][8][9][10], saturation transconductance has been increasing linearly with the reduction of gate length. This indicates that in the past the oxide thickness has been scaled at an identical pace with gate length.

Figure 2.2 Saturation transconductance increases with reduction of gate length, indicating the uniform decreasing of gate oxide thickness

#### 2.1.1.2. Supply and threshold voltage scaling

As illustrated in Figure 2.3 the supply voltage has been continuously reduced with the advance of CMOS technology.

Figure 2.3 Supply voltage ( $V_{dd}$ ), threshold voltage ( $V_{th}$ ) and gate oxide thickness were scaled down with gate length in the past. Meanwhile the vertical gate electric field increased rapidly.

In addition, the threshold voltage has also been reduced to maintain appropriate gate voltage overdrive according to equation (2.1). However, the reduction of supply voltage and threshold voltage has lagged the gate length and gate dielectric thickness scaling. The slower reduction of the threshold voltage is due to a combination of factors including increasing channel doping needed to control short-channel effects. The sub-linear threshold voltage scaling in turn has retarded the scaling of the supply voltage.

#### 2.1.1.3. Doping profiles

The MOSFET substrate doping, and especially the channel doping concentration, have been continuously increasing since the beginning of scaling. From the original doping density of approximately  $2.5 \times 10^{16}$  cm<sup>-3</sup> in 1 µm gate length transistors [2], it has already reached more than  $2 \times 10^{18}$  cm<sup>-3</sup> in contemporary 35 nm gate length MOSFETs [11]. In addition to the average increase of the channel doping, the design of the vertical doping profile has also changed. Retrograde doping has been introduced to short channel devices to control short-channel effects and to achieve simultaneously low threshold voltage and elevate mobility by reducing impurity scattering [11]. Halo doping implanted using a small tilt angle effectively blocks lateral field penetration from source/drain, reducing further short-channel effects without affecting adversely the threshold voltage [12]. Figure 2.4 shows the retrograde doping and halo doping.

Figure 2.4 Schematic view of the doping profile in an n-channel MOSFET, including retrograde doping along substrate depth and halo/pocket doping close to source/drain.

In conjunction with the changes in the vertical doping design, structure modifications and changes have been made to the design of the source/drain regions. Lightly doped drain (LDD) was introduced to alleviate reliability concerns during the 5V supply voltage period. High field related impact ionization near the drain junction caused serious reliability

concerns at this stage [13]. The n<sup>-</sup> regions introduced near n<sup>+</sup> source/drain diffusion regions by additional implantation reduces the high field into n<sup>-</sup> region near drain [14] at the expense of additional series resistance [15]. Finally, shallow source/drain extensions (SDE) have been introduced to manage short-channel effects in successive technologies reducing the coupling between the drain voltage and the carrier concentration in the channel. Meanwhile the need of low sheet resistance of SDE requires high doping activation without significant additional diffusion.

At 0.5~0.25 micron technology in 1990s [16], the integration requirements for abrupt transition between the active transistor area and the insulation and better planarity prompted the replacement of the <u>LOCal Oxide</u> of <u>Silicon (LOCOS)</u> horizontal isolation with the vertical <u>Shallow Trench Isolation (STI)</u>. Compared with LOCOS's shortfalls, such as lateral extension of the bird's beak, boron encroachment and oxide thinning, STI achieved high scalability and planarity [17][18]. Inverse-narrow-width effect has created some problems in STI MOSFETs due to enhanced edge conduction by fringing field at the edge of the STI, leading to the threshold voltage lowering with the decrease of MOSFET width [19]. However, improvements, such as sidewall implantation and corner rounding, were adopted to suppress parasitic conduction effect at the corner [20][21].

#### 2.1.2. Scaling principles

#### 2.1.2.1. Constant-field scaling

CMOS technology emerged in 1960's and started to replace bipolar devices in integrated circuits logic and memory applications, where chip density and cost are primary concerns. The applications of high resolution lithographic capability, and the introduction of controllable doping profiling using ion implantation [2] paved the way of device miniaturization achieving the reduction of cost/performance towards large scale integration in early 1970's [2][22][23][24]. At the origin of these efforts a seminal paper by Dennard *et al.* established the rules of so-called constant-field scaling [2].

The essence of constant-field scaling is to maintain a constant electric field while simultaneously reducing dimensions and supply voltage in concert by the same scaling factor  $\kappa$  (>1). This requires an appropriate increase of substrate doping concentration to scale the depletion layer width. This is schematically illustrated in Figure 2.5. This is based on the Poisson's equation (2.3)

$$\nabla_r \cdot (-\varepsilon \nabla_r \phi) = \rho = q(p - n + N_d^+ - N_a^-), \qquad (2.3)$$

where  $N_d^+$ ,  $N_a^-$  are ionized donor and acceptor concentrations respectively,  $\rho$  is charge density and  $\varepsilon$  is material permittivity. In sub-threshold regime where charge density is mainly determined by ionized impurity concentration and carrier density contributions in the channel are negligible, the current continuity equation can be decoupled from the Poisson equation. If the scaled dimensions is  $r'=r/\kappa$ , we apply Poisson's equation to the scaled device,

$$\nabla_{x'} \cdot (-\varepsilon \nabla_{x'} \phi') = \rho'. \tag{2.4}$$

In both equations  $\nabla$  is the gradient operator on dimensional position  $\mathbf{r}$  and  $\mathbf{r}'$ ,  $\phi$  and  $\phi'$  is electrostatic potential,  $\rho$  and  $\rho'$  is space charge density for sub-threshold region respectively for original and scaled devices. The maintenance of constant field requires  $-\nabla_{r'}\phi' = -\nabla_{r}\phi$ . This results in  $\phi' = \phi/\kappa$  and  $\rho' = \kappa\rho$  in the light of  $\nabla_{r'} = \kappa\nabla_{r}$ . This could be achieved by scaling down supply voltage  $V_{dd}$  by the factor  $\kappa$ , and by increasing substrate doping  $N_{sub}$  ( $N_a$  for p-type or  $N_d$  for n-type) by the same factor  $\kappa$ .