Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-26-2009

## Removing Redundant Logic Pathways in Polymorphic Circuits

Hanseok Kim

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

### **Recommended Citation**

Kim, Hanseok, "Removing Redundant Logic Pathways in Polymorphic Circuits" (2009). *Theses and Dissertations*. 2474. https://scholar.afit.edu/etd/2474

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

Removing Redundant Logic Pathways in Polymorphic Circuits

## THESIS

Hanseok Kim, Captain, ROKA

AFIT/GCS/ENG/09-03

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, Department of Defense, or the United States Government.

## Removing Redundant Logic Pathways in Polymorphic Circuits

### THESIS

Presented to the Faculty Department of Electrical and Computer Engineering Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command In Partial Fulfillment of the Requirements for the Degree of Master of Science

> Hanseok Kim, BSCE Captain, ROKA

> > $26 \ \mathrm{March} \ 2009$

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

AFIT/GCS/ENG/09-03

## Removing Redundant Logic Pathways in Polymorphic Circuits

Hanseok Kim, BSCE Captain, ROKA

Approved:

Lt Col J. Todd McDonald, Ph.D. (Chairman) 1 pl Yong C. Kim (Member) Ďг.

Lt Col Stuart H. Kurkowski, Ph.D. (Member)

13 mar 09 date

13 MAR09

date

13 Mar 09

date

### Abstract

Evaluating the quality of software and circuit obfuscators is a research goal of great interest. However, there exists little research about evaluation of obfuscation effectiveness through analyzing and investigating redundancies found in the obfuscated variants.

In this research, we consider programs represented as structural combinational circuits and then analyze obfuscated variants of those circuits through a tool that produces functionally equivalent variants based on subcircuit selection and replacement. We then consider how Boolean logic and reduction affects the size and levelization of circuit variants, giving us a concrete metric by which to consider obfuscation effectiveness. To accomplish these goals, we create an experimental environment based on a set of predefined circuits, a set of predefined algorithms which produce variants of those circuits, and a collection of logic reduction techniques and tools. We build logic reduction techniques using predefined patterns and predefined functions expressed as truth tables.

As a contribution, we characterize and evaluate the effectiveness of obfuscating algorithms based on these reduction techniques. We show, for the circuits we observe, optimization on size is affected by ordering of the specific reduction patterns and functions. We also show, for the circuits we observe, reduction is affected by the specific obfuscating algorithm used to produce the variant. Based on these results, we provide a promising measurement of interest to compare both circuit variants and obfuscating algorithms.

## Acknowledgements

I would first like to express my sincere appreciation to my thesis advisor, Lt Col. Todd McDonald, for his guidance and support throughout the course of this thesis effort. I would also like to thank Dr. Yong C. Kim for his advice and assistance about circuit domain. I could not have completed my work without their support and concerns.

I would like to thank my academic advisor, Lt Col. Stuart Kurkowski, for showing me the right path to finish the Computer Science Master's Degree program at the Air Force Institute of Technology. I would also like to thank IMSO director, Mrs. Annette Robb, for enthusiastically providing me with various assistance needed as international military student.

Most importantly, I would like to thank my loving mother for all her support and for encouraging me to finish my education successfully.

Hanseok Kim

# Table of Contents

|                                                    | Page |

|----------------------------------------------------|------|

| Abstract                                           | iv   |

| Acknowledgements                                   | v    |

| Table of Contents                                  | vi   |

| List of Figures                                    | ix   |

| List of Tables                                     | xiv  |

| List of Abbreviations                              | XV   |

| I. Introduction                                    | 1    |

| 1.1 Background                                     | 1    |

| 1.2 Research Objectives                            | 2    |

| 1.3 Organization                                   | 3    |

| II. Literature Review                              | 4    |

| 2.1 Reverse Engineering                            | 4    |

| 2.2 Obfuscation $\ldots$                           | 4    |

| 2.2.1 Indistinguishability Obfuscation             | 5    |

| 2.2.2 Best-Possible Obfuscation                    | 6    |

| 2.3 CORGI                                          | 7    |

| 2.3.1 Circuit Representation                       | 7    |

| 2.3.2 Experimental Configuration                   | 8    |

| 2.3.3 Subcircuit Selection/Replacement             | 9    |

| III. Methodology                                   | 13   |

| 3.1 Problem Definition                             | 13   |

| 3.2 Generating Circuit Variants                    | 14   |

| 3.2.1 Defining Obfuscation Experiments             | 14   |

| 3.2.2 Selection Options                            | 15   |

| 3.2.3 Replacement Options                          | 15   |

| 3.2.4 Circuits                                     | 16   |

| 3.3 Analysis of Obfuscated Circuit Variants        | 17   |

| 3.3.1 Pattern Recognition                          | 17   |

| 3.3.2 Pattern Classification                       | 20   |

| 3.4 Implementation of Circuit Reduction Algorithms | 23   |

## Page

|    |         | 3.4.1            | Reduce Buffer                                       |

|----|---------|------------------|-----------------------------------------------------|

|    |         | 3.4.2            | Reduce Inverter                                     |

|    |         | 3.4.3            | Reduce Inverter with Successor $XOR/XNOR$ .         |

|    |         | 3.4.4            | Reduce Constant $0/1$                               |

|    |         | 3.4.5            | Reduce Constant $0/1$ with Inverter Inputs $\ldots$ |

|    |         | 3.4.6            | Reduce Two Gates to AND/NAND/OR/NOR                 |

|    |         | 3.4.7            | Reduce Two Gates to Buffer/NOT/Constant $0/1$       |

|    |         | 3.4.8            | Reduce Two $XOR/XNOR$ Gates to Buffer/NOT           |

|    |         | 3.4.9            | Reduce Gate with Opposite Inputs                    |

|    |         | 3.4.10           | Reduce $AND/OR/NAND/NOR$ Gates with Inverter Inputs |

|    |         | 3.4.11           | Reduce V pattern                                    |

|    |         | 3.4.12           | Reduce Diamond pattern                              |

|    | 3.5     | Evaluat          | ion of Circuit Obfuscation                          |

|    |         | 3.5.1            | Experimental Setup                                  |

|    |         | 3.5.2            | Experimental Speculations                           |

| V. | Results |                  |                                                     |

|    | 4.1     | Overvie          | w                                                   |

|    | 4.2     | Circuit          | Reduction                                           |

|    |         | 4.2.1            | The Best Reduction                                  |

|    |         | 4.2.2            | The Worst Reduction                                 |

|    | 4.3     |                  | g and Reduction Round                               |

|    |         | 4.3.1            | The Best Reduction                                  |

|    | 4 4     | 4.3.2            | The Worst Reduction                                 |

|    | 4.4     | Evaluat<br>4.4.1 |                                                     |

|    |         | 4.4.1<br>4.4.2   | Remaining GatesObfuscation Options                  |

|    |         | 4.4.2            |                                                     |

| V. | Conclus |                  |                                                     |

|    | 5.1     |                  | utions                                              |

|    |         | 5.1.1            | Characterizing Circuit Obfuscation                  |

|    |         | 5.1.2            | Applying and Ordering Circuit Reduction Algorithms  |

|    | 5.2     | Future '         |                                                     |

|    |         | 5.2.1            | Improve Reduction Algorithm for the Remaining Gates |

|    |         | 5.2.2            | Increase Search Space                               |

|    |         | 5.2.3            | Increase Metric Space                               |

|    |         | 5.2.4            | Increase Circuit Space                              |

|    |         | 5.2.5            | Generate Colored Graph of Reduced Circuit           |

## Page

| Appendix A.    | Circuit Graphs for $C17 - C17 - C17 \dots \dots \dots$ | 58  |

|----------------|--------------------------------------------------------|-----|

| A.1            | Obfuscated Circuit Variant Graphs                      | 58  |

| A.2            | Reduced Circuit Variant Graphs                         | 71  |

| Appendix B.    | Circuit Graphs for $R17' - C17 - R17''$                | 84  |

| B.1            | Obfuscated Circuit Variant Graphs                      | 84  |

| B.2            | Reduced Circuit Variant Graphs                         | 97  |

| Bibliography . |                                                        | 110 |

| Vita           |                                                        | 112 |

## List of Figures

| Figure |                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

| 2.1.   | ISCAS Benchmark Circuit c17                                                                            | 8    |

| 3.1.   | Original Circuit Graphs                                                                                | 17   |

| 3.2.   | Obfuscated Circuit Variant Graph                                                                       | 18   |

| 3.3.   | Log/Graph Example in CORGI                                                                             | 19   |

| 3.4.   | Decomposing Multiple Fan-out Gate                                                                      | 19   |

| 3.5.   | Redundant Gates                                                                                        | 20   |

| 3.6.   | Gate Replacement using Buffer                                                                          | 21   |

| 3.7.   | Gate Replacement using Inverter                                                                        | 21   |

| 3.8.   | Gate Replacement using Constant                                                                        | 22   |

| 3.9.   | Gate Replacement Example for the Special Case $\ldots$                                                 | 22   |

| 3.10.  | Complex Gate Replacement Example                                                                       | 23   |

| 3.11.  | Reverse Logic Example of Figure 3.9                                                                    | 24   |

| 3.12.  | Reduction Algorithm 1(Reduce Buffer)                                                                   | 25   |

| 3.13.  | Gate Replacement and Truth Table of Reduction Algorithm 2<br>(Reduce Inverter)                         | 26   |

| 3.14.  | Gate Replacement and Truth Table of Reduction Algorithm 3 (Reduce Inverter with Successor $XOR/XNOR$ ) | 27   |

| 3.15.  | Gate Replacement and Truth Table of Reduction Algorithm 4 (Reduce Constant $0/1$ )                     | 29   |

| 3.16.  | Gate Replacement and Truth Table of Reduction Algorithm 5 (Reduce Constant $0/1$ with Inverter Inputs) | 30   |

| 3.17.  | Gate Replacement and Truth Table of Reduction Algorithm 6 (Reduce Two Gates to $AND/NAND/OR/NOR$ )     | 31   |

| 3.18.  | Reduction Algorithm 7 (Reduce Two Gates to Buffer/ $NOT$ /Constant 0/1)                                | 32   |

| 3.19.  | Gate Replacement and Truth Table of Reduction Algorithm 8 (Reduce Two $XOR/XNOR$ Gates to Buffer/NOT)  | 33   |

| Figure |                                                                                                                          | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------|------|

| 3.20.  | Gate Replacement and Truth Table of Reduction Algorithm 9<br>(Reduce Gate with Opposite Inputs)                          | 34   |

| 3.21.  | Reduction Algorithm 10 (Reduce $AND/OR/NAND/NOR$ Gates with Inverter Inputs)                                             | 35   |

| 3.22.  | Reduction Algorithm 11(Reduce V pattern)                                                                                 | 36   |

| 3.23.  | Gate Replacement and Truth Table of Reduction Algorithm 12<br>(Reduce Diamond pattern)                                   | 36   |

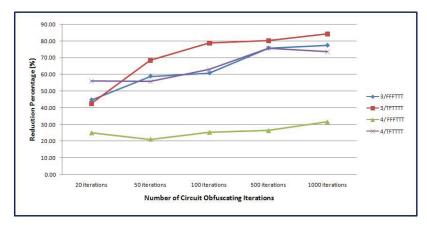

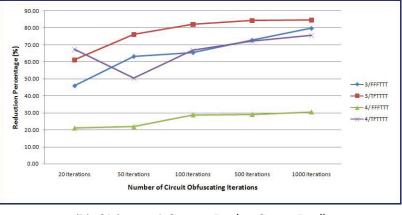

| 4.1.   | Average Reduction Percentage using Obfuscated Circuit Variants                                                           | 43   |

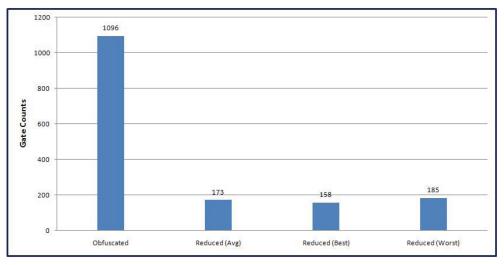

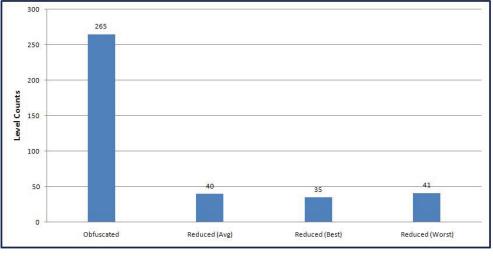

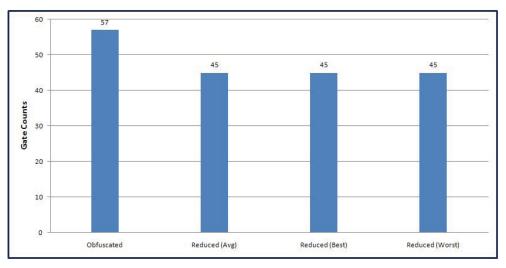

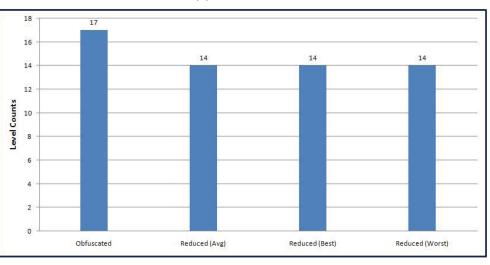

| 4.2.   | Gate Counts and Level Counts of the Best Reduction Result $(C17 - C17 - C17, 3/\text{TFTTTT}, 1000 \text{ iteration})$   | 45   |

| 4.3.   | Gate Counts and Level Counts of the Worst Reduction Result $(R17' - C17 - R17'', 4/\text{FFFTTT}, 20 \text{ iteration})$ | 46   |

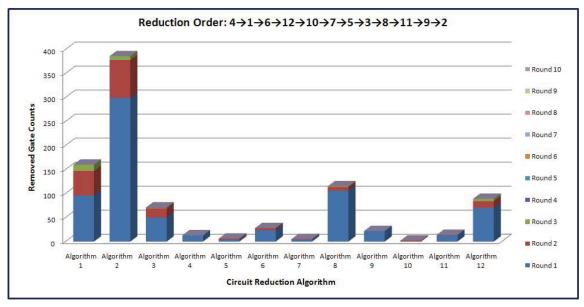

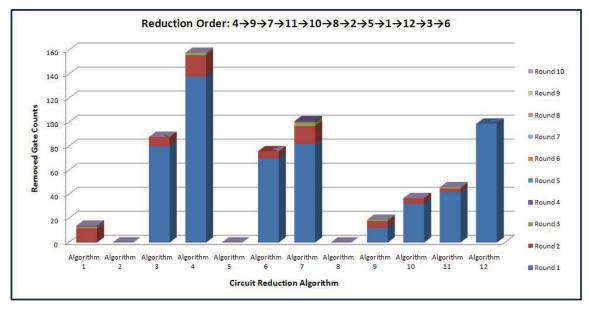

| 4.4.   | Removed Gate Counts of each Reduction Algorithm using Ob-<br>fuscated Circuit $C17 - C17 - C17$ with 3/TFTTTT            | 49   |

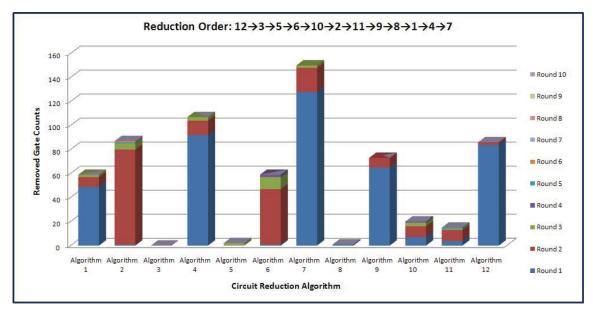

| 4.5.   | Removed Gate Counts of each Reduction Algorithm using Ob-<br>fuscated Circuit $R17' - C17 - R17''$ with 4/FFFTTT         | 52   |

| A.1.   | Obfuscated/ $C17 - C17 - C17/20/3$ /FFFTTT                                                                               | 59   |

| A.2.   | Obfuscated/ $C17 - C17 - C17/50/3$ /FFFTTT                                                                               | 59   |

| A.3.   | Obfuscated/ $C17 - C17 - C17/100/3$ /FFFTTT                                                                              | 60   |

| A.4.   | Obfuscated/ $C17 - C17 - C17/500/3/FFFTTT$                                                                               | 60   |

| A.5.   | Obfuscated/ $C17 - C17 - C17/1000/3/FFFTTT$                                                                              | 61   |

| A.6.   | Obfuscated/ $C17 - C17 - C17/20/3$ /TFTTTT                                                                               | 62   |

| A.7.   | Obfuscated/ $C17 - C17 - C17/50/3/$ TFTTTT                                                                               | 62   |

| A.8.   | Obfuscated/ $C17 - C17 - C17/100/3/TFTTTT$                                                                               | 63   |

| A.9.   | Obfuscated/ $C17 - C17 - C17/500/3/TFTTTT$                                                                               | 63   |

| A.10.  | Obfuscated/ $C17 - C17 - C17/1000/3/TFTTTT$                                                                              | 64   |

| A.11.  | Obfuscated/ $C17 - C17 - C17/20/4$ /FFFTTT                                                                               | 65   |

| A.12.  | Obfuscated/ $C17 - C17 - C17/50/4$ /FFFTTT                                                                               | 65   |

| A.13.  | Obfuscated/ $C17 - C17 - C17/100/4$ /FFFTTT                                                                              | 66   |

Figure

| A.14. | Obfuscated/ $C17 - C17 - C17/500/4$ /FFFTTT       | 66 |

|-------|---------------------------------------------------|----|

| A.15. | Obfuscated/ $C17 - C17 - C17 / 1000 / 4 / FFFTTT$ | 67 |

| A.16. | Obfuscated/ $C17 - C17 - C17/20/4$ /TFTTTT        | 68 |

| A.17. | Obfuscated/ $C17 - C17 - C17/50/4$ /TFTTTT        | 68 |

| A.18. | Obfuscated/ $C17 - C17 - C17 / 100 / 4 / TFTTTT$  | 69 |

| A.19. | Obfuscated/ $C17 - C17 - C17/500/4/TFTTTT$        | 69 |

| A.20. | Obfuscated/ $C17 - C17 - C17 / 1000 / 4 / TFTTTT$ | 70 |

| A.21. | Reduced/ $C17 - C17 - C17/20/3$ /FFFTTT           | 72 |

| A.22. | Reduced/ $C17 - C17 - C17/50/3$ /FFFTTT           | 72 |

| A.23. | Reduced/ $C17 - C17 - C17/100/3$ /FFFTTT          | 73 |

| A.24. | Reduced/ $C17 - C17 - C17/500/3$ /FFFTTT          | 73 |

| A.25. | Reduced/ $C17 - C17 - C17/1000/3/FFFTTT$          | 74 |

| A.26. | Reduced/ $C17 - C17 - C17/20/3$ /TFTTTT           | 75 |

| A.27. | Reduced/ $C17 - C17 - C17/50/3$ /TFTTTT           | 75 |

| A.28. | Reduced/ $C17 - C17 - C17/100/3/$ TFTTTT          | 76 |

| A.29. | Reduced/ $C17 - C17 - C17/500/3/$ TFTTTT          | 76 |

| A.30. | Reduced/ $C17 - C17 - C17/1000/3/TFTTTT$          | 77 |

| A.31. | Reduced/ $C17 - C17 - C17/20/4$ /FFFTTT           | 78 |

| A.32. | Reduced/ $C17 - C17 - C17/50/4$ /FFFTTT           | 78 |

| A.33. | Reduced/ $C17 - C17 - C17/100/4$ /FFFTTT          | 79 |

| A.34. | Reduced/ $C17 - C17 - C17/500/4$ /FFFTTT          | 79 |

| A.35. | Reduced/ $C17 - C17 - C17/1000/4$ /FFFTTT         | 80 |

| A.36. | Reduced/ $C17 - C17 - C17/20/4$ /TFTTTT           | 81 |

| A.37. | Reduced/ $C17 - C17 - C17/50/4$ /TFTTTT           | 81 |

| A.38. | Reduced/ $C17 - C17 - C17/100/4$ /TFTTTT          | 82 |

| A.39. | Reduced/ $C17 - C17 - C17/500/4$ /TFTTTT          | 82 |

| A.40. | Reduced/ $C17 - C17 - C17/1000/4$ /TFTTTT         | 83 |

| B.1.  | Obfuscated/ $R17' - C17 - R17''/20/3$ /FFFTTT     | 85 |

Figure

| D a   |                                                     | ~ ~ |

|-------|-----------------------------------------------------|-----|

| B.2.  | Obfuscated/ $R17' - C17 - R17''/50/3/FFFTTT$        | 85  |

| B.3.  | Obfuscated/ $R17' - C17 - R17''/100/3/FFFTTT$       | 86  |

| B.4.  | Obfuscated/ $R17' - C17 - R17''/500/3/FFFTTT$       | 86  |

| B.5.  | Obfuscated/ $R17' - C17 - R17''/1000/3/FFFTTT$      | 87  |

| B.6.  | Obfuscated/ $R17' - C17 - R17''/20/3/TFTTTT$        | 88  |

| B.7.  | Obfuscated/ $R17' - C17 - R17''/50/3/TFTTTT$        | 88  |

| B.8.  | Obfuscated/ $R17' - C17 - R17''/100/3/TFTTTT$       | 89  |

| B.9.  | Obfuscated/ $R17' - C17 - R17''/500/3/TFTTTT$       | 89  |

| B.10. | Obfuscated/ $R17' - C17 - R17''/1000/3/TFTTTT$      | 90  |

| B.11. | Obfuscated/ $R17' - C17 - R17''/20/4/FFFTTT$        | 91  |

| B.12. | Obfuscated/ $R17' - C17 - R17''/50/4/FFFTTT$        | 91  |

| B.13. | Obfuscated/ $R17' - C17 - R17''/100/4/FFFTTT$       | 92  |

| B.14. | Obfuscated/ $R17' - C17 - R17''/500/4/FFFTTT$       | 92  |

| B.15. | Obfuscated/ $R17' - C17 - R17''/1000/4/FFFTTT$      | 93  |

| B.16. | Obfuscated/ $R17' - C17 - R17''/20/4/TFTTTT$        | 94  |

| B.17. | Obfuscated/ $R17' - C17 - R17''/50/4/TFTTTT$        | 94  |

| B.18. | Obfuscated/ $R17' - C17 - R17''/100/4/TFTTTT \dots$ | 95  |

| B.19. | Obfuscated/ $R17' - C17 - R17''/500/4/TFTTTT \dots$ | 95  |

| B.20. | Obfuscated/ $R17' - C17 - R17''/1000/4/TFTTTT$      | 96  |

| B.21. | Reduced/ $R17' - C17 - R17''/20/3/FFFTTT$           | 98  |

| B.22. | Reduced/ $R17' - C17 - R17''/50/3/FFFTTT$           | 98  |

| B.23. | Reduced/ $R17' - C17 - R17''/100/3/FFFTTT$          | 99  |

| B.24. | Reduced/ $R17' - C17 - R17''/500/3/FFFTTT$          | 99  |

| B.25. | Reduced $/R17' - C17 - R17'' / 1000 / 3 / FFFTTT $  | 100 |

| B.26. | Reduced/ $R17' - C17 - R17''/20/3/TFTTTT$           | 101 |

| B.27. | Reduced/ $R17' - C17 - R17''/50/3/TFTTTT$           | 101 |

| B.28. | Reduced/ $R17' - C17 - R17''/100/3/TFTTTT$          | 102 |

| B.29. | Reduced/ $R17' - C17 - R17''/500/3/TFTTTT$          | 102 |

|       |                                                     |     |

| Figure |                                             | Page |

|--------|---------------------------------------------|------|

| B.30.  | Reduced/ $R17' - C17 - R17''/1000/3/TFTTTT$ | 103  |

| B.31.  | Reduced/ $R17' - C17 - R17''/20/4/FFFTTT$   | 104  |

| B.32.  | Reduced/ $R17' - C17 - R17''/50/4/FFFTTT$   | 104  |

| B.33.  | Reduced/ $R17' - C17 - R17''/100/4/FFFTTT$  | 105  |

| B.34.  | Reduced/ $R17' - C17 - R17''/500/4/FFFTTT$  | 105  |

| B.35.  | Reduced/ $R17' - C17 - R17''/1000/4/FFFTTT$ | 106  |

| B.36.  | Reduced/ $R17' - C17 - R17''/20/4/TFTTTT$   | 107  |

| B.37.  | Reduced/ $R17' - C17 - R17''/50/4/TFTTTT$   | 107  |

| B.38.  | Reduced/ $R17' - C17 - R17''/100/4/TFTTTT$  | 108  |

| B.39.  | Reduced/ $R17' - C17 - R17''/500/4/TFTTTT$  | 108  |

| B.40.  | Reduced/ $R17' - C17 - R17''/1000/4/TFTTTT$ | 109  |

# List of Tables

| Table |                                                                                                                                               | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1.  | Experimental Setup for Circuit Reduction                                                                                                      | 37   |

| 4.1.  | Average Reduction Percentage using Obfuscated Circuit Variants                                                                                | 43   |

| 4.2.  | Gate Counts and Level Counts of the Best Reduction Result $(C17 - C17 - C17, 3/\text{TFTTTT}, 1000 \text{ iteration}) \ldots \ldots \ldots$   | 45   |

| 4.3.  | Gate Counts and Level Counts of the Worst Reduction Result $(R17' - C17 - R17'', 4/\text{FFFTTT}, 20 \text{ iteration}) \ldots \ldots \ldots$ | 46   |

| 4.4.  | Removed Gate Counts of each Reduction Algorithm using Ob-fuscated Circuit $C17-C17-C17$ with 3/TFTTTT Option $~$ .                            | 48   |

| 4.5.  | Removed Gate Counts of each Reduction Algorithm using Obfuscated Circuit $R17'-C17-R17''$ with 4/FFFTTT Option $% C^{2}$ .                    | 51   |

| 4.6.  | Remaining Redundant Gate Counts in the Reduced Circuit Vari-<br>ants                                                                          | 53   |

| 4.7.  | Evaluation of Circuit Obfuscation Option's Strength                                                                                           | 54   |

## List of Abbreviations

| Abbreviation |                                                             | Page |

|--------------|-------------------------------------------------------------|------|

| CORGI        | Circuit Obfuscation via Randomization of Graphs Iteratively | 2    |

| VBB          | Virtual Black Box                                           | 5    |

| PPT          | Probabilistic Polynomial time Turning machine               | 5    |

| ISCAS        | International Symposium of Circuits and Systems             | 8    |

| IEEE         | Institute of Electrical and Electronics Engineers           | 8    |

# Removing Redundant Logic Pathways in Polymorphic Circuits

### I. Introduction

#### 1.1 Background

Software obfuscation remains a research area of great interest. If possible, proving or demonstrating that we can protect software from adversarial actions holds great interest to both military and civilian communities. In general, obfuscation seeks to find suitable variants of an original program or circuit that accomplishes the same function as the original. The suitability of the variant is determined by whether or not the variant demonstrates some security property of interest [8]. In most cases, we link the security property to driving up the cost of reverse engineering or demonstrating that recovery of certain program information is equivalent to the work of solving a known hard problem [6, 7, 13].

If we consider simple straight-line programs represented as combinational circuits, we can focus more precisely on what actually defines obfuscation and consider measurements of those attributes. In this research, we experiment with and characterize a polymorphic circuit generator that creates functionally equivalent circuits by using a mixture of random and deterministic subcircuit selection/replacement algorithms applied sequentially. Using this approach, such a generator, when given an original circuit P, produces a circuit P' with the same function by using a sequence of iterative selections and replacements on circuit P. Each individual selection and replacement represents an obfuscation on a small scale: the engine replaces each subcircuit selected with a functionally equivalent replacement subcircuit.

Our research focuses on how to characterize and measure circuit obfuscation that uses such selection/replacement algorithms. Specifically, we analyze the nature of the structural and logic changes produced by subcircuit selection/replacement. Based on the logic and component properties of the selection and replacement operations themselves, we characterize specific trends that occur within a circuit that undergoes transformation. A question of great interest is "how much" of the transformations introduced via subcircuit selection and replacement algorithms can be "undone" via optimization or logic minimization. The answer to this question possibly provides a measurable basis to characterize the degree of "actual" obfuscation that is taking place. By looking at the effect of subcircuit transformations themselves, we formulate an approach for answering this question and organize our research accordingly.

### 1.2 Research Objectives

Based on these goals, we describe the main objectives of our research as follows:

- 1. Produce and analyze obfuscated variants of combinational circuits created using iterative subcircuit selection and replacement.

- 2. Devise methods to remove identifiable artifacts of circuit variants based on logic and component analysis.

- 3. Characterize circuit obfuscation effectiveness using reduction methods and determine principles of successful deobfuscation.

To accomplish these objectives, we utilize a polymorphic circuit generator (CORGI, Circuit Obfuscation via Randomization of Graphs Iteratively) developed by McDonald *et al.* [14–16, 18, 21] known as *CORGI*. The whitebox obfuscation aspect of the *CORGI* framework specifically uses subcircuit selection and replacement as its transformation basis.

To accomplish our first objective, we generate the obfuscated circuit variants using specific generation options defined by *CORGI*. We then use the circuit transformation history (or journal) produced during a *CORGI* experiment to identify obfuscation patterns that occur. Using these patterns, we create a strategy for reduction based on the logic attributes associated with each pattern. For the second objective, we define patterns that have specific logic that is conducive to reduction or minimization. Classic examples of such reduction may be seen in whitebox circuit structures such as buffers, double inverters, constant 0/1gates, and so forth. Using this approach, we devise ten circuit reduction algorithms which represent the pattern-based approach of logic minimization. We also create two reduction algorithms that use functional identification (based on the truth table) to find logic structures suitable for minimized replacement. These algorithms try to find whitebox structures whose functions are simple AND, OR, NAND, and NORlogic patterns.

For the last objective, we characterize obfuscation by using these circuit reduction techniques under various experimental conditions. We consider the effect of using these patterns in a combined fashion based on either predetermined order or random sequences and present conclusions based on our observations. We analyze our results to see how size correlates with various approaches to producing the circuit variant (the obfuscating algorithm). Ultimately, we provide results which give definable measures for the effectiveness of obfuscation and give a basis for comparing obfuscating algorithms themselves.

### 1.3 Organization

We organize the remainder of the thesis as follows. Chapter II provides an overview of reverse engineering and obfuscation and explains the *CORGI* circuit generation engine. Chapter III defines our methodology including analysis of circuit obfuscation log files and creation of circuit reduction algorithms. Chapter IV presents the results of experiments using circuit reduction techniques and our analysis. Chapter V gives our conclusions along with our contributions and discussion of future work for our reduction techniques.

## II. Literature Review

This chapter presents a background review of the literature pertaining to the research subjects related to this research work. Section 2.1 describes the concept of reverse engineering. Section 2.2 summarizes theoretical obfuscation with the description of virtual black box obfuscation, indistinguishability obfuscation, and best-possible obfuscation. Section 2.3 shows that the overview of *CORGI*, Circuit Obfuscation via Randomization of Graphs Iteratively [18].

#### 2.1 Reverse Engineering

Aronson, R.B. [1] defines reverse engineering as

"the process of systematic evaluation of a product for the purpose of replication."

Chikofsky and Cross [5] describes reverse engineering as

"the process of analyzing a subject system to identify the system's components and their interrelationships and create representations of the system in another form or at a higher level of abstraction."

As we can see from these definitions, reverse engineering can be used to reproduce commercial or military systems by analyzing them. Since it makes possible to reduce cost and time, there are many researches and attempts to reverse engineering for their advantages. Reverse engineering is used in many situations such as when the original manufacturer of a product no longer produces a product, when there is inadequate documentation of the original design, and when the original manufacturer no longer exists, but a customer needs the products [2]. In contrast to these beneficial motivations, reverse engineering can be exploited with negative objectives such as copying other nations' technologies, devices or information that have been obtained by the industrial spy. Obfuscation is defense against the malicious exploitations of reverse engineering.

### 2.2 Obfuscation

Meriam-Webster Dictionary [17] presents obfuscate as

"to make obscure" or "to be evasive, unclear, or confusing"

Wiktionary Dictionary [19] describes obfuscation as

"The option to alter computer code, preserving its behavior but concealing its structure and intent"

In other words, obfuscation provides an ability to hide system structure and intent in order to make other people confused. Barak et al. [3] introduced the first formalized publication of program (or circuit) obfuscation. They claim that an obfuscator must have the following property:

- 1. functionality property, For every program P, O(P) describes a program that compute the same function as P.

- 2. polynomial slowdown property, The size and run time of O(P) are at most polynomial larger than that of P. That is, there is a polynomial p such that for every program P,  $|\mathcal{O}(P)| \leq p(|P|)$ .

- 3. virtual black-box (VBB) property, For any probabilistic polynomial time turning machine (PPT) A, there is a PPT S and a negligible function  $\alpha$  such that for all programs P,

$$|\Pr[A(\mathcal{O}(P)) = 1] - \Pr[S^{P}(1^{|P|}) = 1]| \le \alpha(|P|)$$

(2.1)

We say that the obfuscator  $\mathcal{O}$  is efficient if it runs in polynomial time.

Unfortunately, Barak, et al. [3] proved that it is impossible to construct a universal obfuscator under such requirements. In terms of results, there exists a set of programs that cannot be obfuscated under the VBB definition. As an alternative to VBB obfuscation, Barak et al. propose the idea of indistinguishability obfuscation.

2.2.1 Indistinguishability Obfuscation. We define an indistinguishability obfuscator in the same way as a circuit obfuscator, without replacing the "virtual black box" property with the following:

• indistinguishability property, For any PPT A, there is a negligible function  $\alpha$  such that for any two circuits  $C_1, C_2$  which compute the same function and are of the same size k,

$$\left|\Pr[A(\mathcal{O}(C_1))] - \Pr[A(\mathcal{O}(C_2))]\right| \le \alpha(k) \tag{2.2}$$

As we can know in VBB obfuscation, the VBB property compares an obfuscated circuit to a simulator that has only black box access to the original circuit. However, the indistinguishability property compares the obfuscations of two different circuits,  $C_1$  and  $C_2$ . Since this property weakens the VBB definition, it demonstrates that obfuscation (at least in the information theoretic sense) is not achievable but may be achievable under other definitions that are of interest.

2.2.2 Best-Possible Obfuscation. In another study, Goldwasser and Rothblum [9] clarify the notion of best-possible obfuscation that guarantees that when an obfuscated program O(P) leaks some information, any other program P which computes the same functionality also leaks the same information. The best-possible obfuscation is defined in the same way as circuit obfuscator, without substituting the "virtual black box" property by the following:

• Computational/Statistical/Perfect Best-Possible Obfuscation, For all large enough input lengths, for any polynomial size circuit adversary A, there exists a polynomial size simulator circuit S such that for any circuit  $C_1 \in C_n$ and for any circuit  $C_2 \in C_n$  that computes the same function as  $C_1$  and such that  $|C_1| = |C_2|$ , the two distributions  $A(O(C_1))$  and  $S(C_2)$  are computationally/statiscally/perfectly indistinguishable.

Goldwasser and Rothblum [9] prove that all best-possible obfuscators are indistinguishability obfuscators. They also show that an efficient best-possible obfuscator is an efficient indistinguishability obfuscator. Unfortunately, there is no feasible obfuscator including the indistinguishability obfuscation or best-possible obfuscation concepts until now.

### 2.3 CORGI

Many obfuscators are widely available through both commercial and open source products that replace an original program with an obfuscated program. To facilitate research aimed at defining the fundamental nature of whitebox obfuscation in the circuit realm, McDonald et al. developed a circuit generating algorithm known as CORGI, Circuit Obfuscation via Randomization of Graphs Iteratively, at the Air Force Institute of Technology (AFIT). CORGI operates on programmatic logic embodied in Boolean logic circuits using iterative sequences of probabilistic and deterministic transforms. CORGI analysis primarily revolves around running experiments on some original combinational logic circuit and producing one or more variants under a set of experimental options. Analysis typically considers whether CORGI produces a distribution of circuits with a specific (hiding) property or characteristic of interest. Such experiments give basis for either characterizing one algorithm choice over another or with defining metrics that reflect security properties of interest. The major components of a CORGI experiment are circuit representation, experimental configuration, subcircuit selection, and subcircuit replacement. We give a brief summary of these components as follows:

2.3.1 Circuit Representation. While sequential circuits have memory and feedback loops (cycle), combinational circuits have no state. Since we can decompose sequential circuits into combinational circuits, CORGI considers only combinational logic. Independent observations by Huth and Ryan [11] also point out that we only need a simple grammar to compute everything that can be computed by large languages like C and Java. As another benefit, a simple logic grammar provides understandability because we need only three logic functions: NOT(!), AND(&), and OR(||). There are other commonly used logic functions such as NAND, NOR,

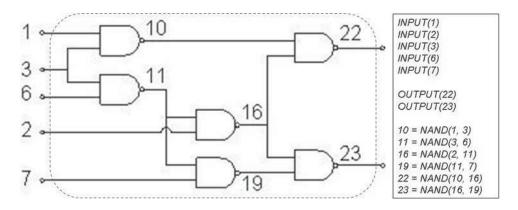

Figure 2.1: ISCAS Benchmark Circuit c17

XOR, and XNOR, but we can represent these functions using various combinations of NOT, AND, and OR.

Combinational logic circuits are widely used within both the hardware and software domain. At the 1985 International Symposium of Circuits and Systems (ISCAS), the Institute of Electrical and Electronics Engineers, Inc. (IEEE) introduced a set of benchmark circuits, ISCAS-85 benchmark circuits [10]. They are particularly useful for our research because they embody a variety of functions with a varying degree of input size, output size, and circuit size. A list of these circuits can be found at [4]. The smallest circuit, c17, is shown in Figure 2.1, with its syntactic listing in BENCH format. c17 is of interest to us because it represents a small-scale NAND-only logic component (i.e., small input size, small output size, small gate size) which might be found in abundance within a larger circuit or component.

2.3.2 Experimental Configuration. To create semantically equivalent circuit variants, CORGI uses a two-step iteration process which includes subcircuit selection followed by subcircuit replacement. We have two selection/replacement options such as random and smart [12]. If we leave the choices of the algorithm completely open to a probabilistic dice-roll made by the algorithm, we term the selection/replacement option as random. If some criteria or user preference is used to guide or replace a probabilistic choice made by the algorithm, we term the selection/replacement option

as smart. *CORGI* has four options which guide subcircuit selection or replacement under these possibilities:

- 1. Random selection: Select a subcircuit  $C_{sub} \subset C$  at random.

- 2. Random replacement: Select a replacement circuit  $C_{rep} \in \delta_{C_{rep}}$  at random.

- 3. *Smart selection*: Only select subcircuits which have a particular property. If the subset of allowable selections contains more than one subcircuit, then one may be selected at random or based on another user-specified criteria.

- 4. *Smart replacement*: Similar to smart selection, only select replacement circuits from the library which have a particular property. If the subset of allowable selections contains more than one subcircuit, then one may be selected at random or based on another user-specified criteria.

We define an obfuscation experiment as a 5-tuple:  $(C, n, \xi, \sigma, \tau)$  [12]. C is an original circuit, n is the number of iterations,  $\xi$  is a set of selection algorithms with cardinality  $|\xi| = n$  where  $s_i \in \xi$  implies the selection algorithm performed during iteration  $i, \sigma$  is a set of selection algorithms with cardinality  $|\sigma| = n$  where  $r_i \in \sigma$ implies the replacement algorithm performed during iteration i, and  $\tau$  is a set of gates which are given selection priority during the incremental execution of the experiment.

2.3.3 Subcircuit Selection/Replacement. Given an experiment defined as the tuple  $(C, n, \xi, \sigma, \tau)$ ,  $\xi$  represents a set of selection algorithms and  $s_i \in \xi$  implies the selection algorithm used during iteration *i*. A subcircuit selection operation is defined as  $C_{sub} = s(C, x, \gamma, \tau)$  [12] with several characteristic attributes. A circuit *C* is the input to the algorithm, *x* is the (intermediate gate) size of the selection subcircuit,  $\gamma \in S$  is the particular strategy (whether smart or random), and  $\tau$  is an optional set of gates that provide limiting criteria for the selection strategy itself.

The set S of possible selection strategies (described below) must include all members defined until now and CORGI has the following set currently:  $S = \{\text{Random-SingleGate, RandomTwoGates, RandomLevelTwoGates, LargestLevelTwoGates, Out-$

putLevelTwoGates, FixedLevelTwoGates, RandomAlgorithm}. The output of the algorithm  $C_{sub}$  is a circuit whose signature and  $SIZE(C_{sub})$  constructs the basis for functionally equivalent alternatives and replacement. For example, iteration *i* that uses the RandomLevelTwoGate strategy would be described as  $s_i = s(C, 1, \text{RandomLevelTwoGate}, \emptyset)$ , if we assume no experiment level criteria for selection/replacement.

Let  $\Phi$  represent the set of all gates in a circuit C and let  $g_x$  represent a gate  $g_x \in \Phi$ .  $\Phi$ . CORGI has six different subcircuit-selection strategies [12] for the experiment. The RandomAlgorithm strategy chooses any selection strategy in a random, uniform manner for a single iteration of the experiment and there are selection strategies as follow:

- 1. RandomSingleGate: Choose  $g_1 \in \Phi$  in a random, uniform manner.

- 2. RandomTwoGates: Choose  $g_1 \in \Phi$  in a random, uniform manner. Choose  $g_2 \in \Phi$  where  $g_2 \neq g_1$  and where the replacement of the circuit  $(g_1, g_2)$  does not create a cycle.

- 3. RandomLevelTwoGates: Choose  $g_1 \in \Phi$  in a random, uniform manner. Choose  $g_2 \in \Phi$  where  $g_2 \neq g_1$  and where  $level(g_2) = level(g_1) \pm 1$  or  $level(g_2) = level(g_1)$  and where the replacement of the subcircuit  $[g_1, g_2]$  does not create a cycle.

- 4. LargestLevelTwoGates: Choose  $g_1 \in \Phi$  such that  $|level(g_1)| = \ell_{max}$  where  $\ell_{max}$  represents the maximum size of all levels within the circuit:  $\ell_{max} = \bigcup\{|level(g_x)| \mid g_x \in \Phi\}$ . Choose  $g_2 \in \Phi$  where  $g_2 \neq g_1$  and where  $level(g_2) = level(g_1) 1$  or  $level(g_2) = level(g_1)$  and where the replacement of the subcircuit  $[g_1, g_2]$  does not create a cycle.

- 5. OutputLevelTwoGates: Choose  $g_1 \in \Phi$  where  $g_1$  is a distinguished intermediate gate (i.e, an output of the circuit). Choose  $g_2 \in \Phi$  where  $g_2 \neq g_1$  and where  $level(g_2) = level(g_1) - 1$  or  $level(g_2) = level(g_1)$  and where the replacement of the subcircuit  $[g_1, g_2]$  does not create a cycle.

- 6. FixedLevelTwoGates: Choose g<sub>1</sub> ∈ Φ where, for some user-provided level criteria k, level(g<sub>1</sub>) = k. Choose g<sub>2</sub> ∈ Φ where g<sub>2</sub> ≠ g<sub>1</sub> and where level(g<sub>2</sub>) = level(g<sub>1</sub>) − 1 or level(g<sub>2</sub>) = level(g<sub>1</sub>) and where the replacement of the subcircuit [g<sub>1</sub>, g<sub>2</sub>] does not create a cycle.

- 7. RandomAlgorithm: Choose any selection strategy  $\gamma \in S$  in a random, uniform manner. We may also weight one algorithm more heavily than others, and we do so programmatically.

Given an experiment defined as the tuple  $(C, n, \xi, \sigma, \tau)$ ,  $\sigma$  represents a set of replacement algorithms and  $r_i \in \sigma$  implies the replacement algorithm used during iteration *i*. A subcircuit replacement operation is defined as  $C_{rep} = r(C_{sub}, z, \psi, \Omega)$  [12] with several characteristic attributes.  $C_{sub}$  is the circuit chosen for replacement, *z* is the requested gate size of the replacement circuit,  $\psi$  indicates criteria that determines how we generate the replacement circuit library, and  $\Omega$  indicates the basis choice of the replacement circuit.

Let  $\delta$  represent the circuit family, i.e. the set containing all circuits  $C_{X-Y-S-\Omega}$ . X is the input size, Y is the output size, S is the maximum number of gates, and  $\Omega$  is the basis, where  $\Omega \in \{\text{AND, NAND, OR, NOR, XOR, XNOR, NOT}\}$ . CORGI first creates a set of circuits  $\delta_{X-Y-S-\Omega}$ . From this set of circuits, CORGI chooses randomly and uniformly as alternative variant for  $C_{sub}$  from the functionally equivalent subset  $\delta_{C_{sub}} \subset \delta_{n-m-s-\Omega}$ . CORGI then replaces  $C_{sub}$  with  $C_{rep}$ , where  $C_{rep} \in \delta_{C_{sub}}$ .

CORGI uses true/false queries that form a Boolean 6-tuple [12], which we define as  $\psi$  in the description of a replacement operation:  $r(C_{sub}, z, \psi, \Omega)$ . We may vary these options for every replacement opportunity in an experiment, but typically choose a set of options  $\psi$  that remain constant for the entire sequence of iterations. There are true/fase options for every replacement opportunity in the experiment as follow:

1. *RedundantGates*: Should we allow gates that are identical to other gates based on the inputs? That is to say, can we have two gates in a circuit such that the truth table for each gate, based on all *circuit* inputs, is the same?

- 2. AllowConstants: Should we allow the circuit immediate access to the constants True and False? Gates that exhibit these properties may exist in a circuit, but it may change the properties of a set of circuits if these constants are available immediately.

- 3. DoubleInputs: Should we allow both inputs to a gate to originate in the same place? For example, if DoubleInputs = true, CORGI can produce buffer using AND(input\_1, input\_1), NOT using NAND(input\_1, input\_1), Constant 0 using XOR(input\_1, input\_1), and Constant 1 using XNOR(input\_1, input\_1).

- 4. SymmetricGates: Are gates symmetric? That is to say, should we consider a gate with inputs  $(X_1, X_2)$  as equivalent to a gate with inputs  $(X_2, X_1)$ ? This will depend on which gate types are used.

- 5. SimpleOutputs: Which gates may be outputs? In an ideal circuit, any gate may be an output. However, if we want to index a circuit by output signature, outputs must be restricted to a specific set of gates. If SimpleOutputs = true, we require outputs of the circuit to all be lowest level sinks in the graph of the circuit. This option also prevents, for example, gates that are considered as outputs but never actually used-which we refer to as dangling gates.

- 6. ExactCount: Does the set contain all circuits within a certain size bound or only all circuits of an exact size? For example, if our circuit size is S = 4 and ExactCount = false, enumerating δ<sub>X-Y-S-Ω</sub> will create a family of circuits with gate size 1, 2, 3, and 4, versus a family of circuits with gate size 4 if ExactCount = true.

### III. Methodology

### 3.1 Problem Definition

The fundamental and important goal of this research is to analyze obfuscated variants of combinational circuits to find effective methods for removing artifacts of the creation process itself. We compare this goal to how cryptanalysts use knowledge of a cryptosystem under study to find weaknesses which might compromise the security of the overall encryption scheme. In our case, we consider whether knowledge of the individual transformations that comprise an iterative selection/replacement algorithm help us remove the redundant logic pathways that are introduced by the algorithm into the variants that it produces. By examining not only the end-product of an obfuscation experiment but also the creational history that produced it, we can possibly determine if certain logic structures repeatedly arise. If those structures are conducive to minimization or reduction, then we may standardize such patterns (if they are found in the final variant) to a reduced form. The effort of finding variant logic that is conducive to standardization provides the background data by which we propose and implement a family of circuit reduction algorithms.

Once we find repeating logic patterns of interest, our next goal is to devise a method to remove those same identifiable patterns that appear in circuit variants produced by a polymorphic circuit generator (i.e, CORGI). We accomplish this by using the reverse logic of the identified patterns based on its specific logic attributes. As an example, one reverse pattern may change a structure from three gates into two gates as an inverse of a transformation that modifies two gates into three gates. To achieve this goal, we describe in this chapter the algorithms we introduce that use predetermined reduction patterns such as removing buffers, removing double inverters, removing constant 0/1, and so forth. We also implement algorithms that are based on predefined functions expressed as truth tables such as AND, OR, NAND, NOR, etc. to broaden the types of patterns we may identify. The development of such circuit reduction algorithms help to characterize the overall nature of whitebox structural changes applied to a circuit by an obfuscating engine, ultimately giving

us a better approximation to how much real variation or obfuscation a polymorphic circuit generator creates.

As a last goal of this research, we desire to characterize and evaluate circuit obfuscation based on these techniques so that we may compare obfuscating algorithms one with another. An underlying assumption of our analysis is that circuits with smaller size are easier to analyze and reverse engineer than larger ones. We desire to know whether the ordering and arrangement of the reduction algorithms produce better results (in terms of reduced size) and understand the reasons why if that is the case. In terms of effectiveness, we ultimately want to determine at which point overlapping selections and replacements produce irreducible or hard to reduce variation. By moving towards these goals, we can begin to understand whether combinations of small (inefficient or rudimentary) changes to a circuit produce logic structures and pathways that cannot be removed (or understood) by reverse engineers. In this work, we would like to know specifically what the effect of highly random, small replacements on small circuits will produce towards that end.

#### 3.2 Generating Circuit Variants

3.2.1 Defining Obfuscation Experiments. As explained in the Chapter II, CORGI implements experimentation by using a sequence of two-step iterations where each iteration includes a subcircuit selection followed by subcircuit replacement. In this research, we specifically consider random selection and random replacement options to generate circuit variants that we need. We also establish feasible CORGI obfuscation options such as subcircuit selection algorithm, library generation option and replacement gate size as described in next subsections. The number one criteria that establishes an experiment is the number of iterations. Larger iterations, as we would expect, produce circuits with larger size if we continually replace a selected subcircuit with a subcircuit that is larger in size.

3.2.2 As previously stated, CORGI has several dif-Selection Options. ferent strategies that describe how to select a subcircuit for replacement. For our purposes, we consider only RandomSingleGate, RandomTwoGates, RandomLevelTwoGates, LargestLevelTwoGates, OutputLevelTwoGates, and FixedLevelTwoGates strategies. Of these, two are purely random (RandomSingleGate and RandomTwoGates) whereas the other four are smart in that they have predefined criteria. To maximize randomness of the algorithm while having some small degree of determinism, the RamdomAlgorithm strategy, for each iteration of an experiment, chooses one of the six algorithms mentioned here uniformly as the selection strategy. We can also guide a CORGI experiment to have certain high-level goals that are independent of the selection algorithm chosen. For example, we can define experiments with a goal that all gates within the circuit are replaced topologically over time. Such high-level goals help tailor individual selection strategies by providing a set of possible candidates for one or more of gates that are chosen. We consider such high-level goals to be deterministic, experiment-level options.

3.2.3 Replacement Options. When generating possible replacements for subcircuits during the iterations of an experiment, we choose FFFTTT and TFTTTT as Boolean values of the library generation option. As previously explained, CORGI uses true/false queries that form a Boolean 6-tuple as the library generation option. These options consist of RedundantGates, AllowConstants, DoubleInputs, Symmetric-Gates, SimpleOutputs, and ExactCount. Since the RedundantGates option and the DoubleInputs option generate more redundancies on the obfuscated circuit [12], we define two additional versions of each CORGI experiment, one using FFFTTT and one using TFTTTT. By using these two specific option families, we can evaluate circuits that have an expected high number of patterns that we expect would be easily reduced versus circuits that we believe would have higher irreducible logic.

As another experiment option, we can choose, for a given subcircuit selection, the size of the subcircuit that we replace it with. In our particular experiments, we choose three or four for the replacement gate size. Namely, if the *RandomAlgorithm* strategy chooses the *RandomSingleGate* algorithm, the experiment selects subcircuits containing only one gate and replaces it with subcircuits containing three or four gates. If the *RandomAlgorithm* strategy chooses any other algorithm in our subset of interest, the experiment selects subcircuits containing exactly two gates and replaces them with subcircuits containing three or four gates. Therefore, with the assumption that big replacement can be decomposed into a set of small replacements, we use only three or four for the replacement gate size.

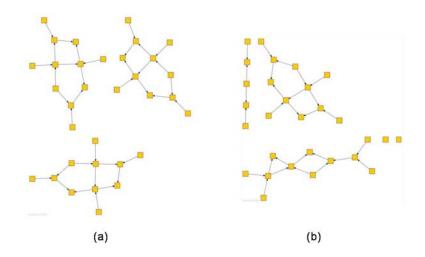

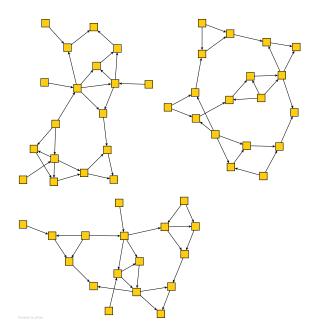

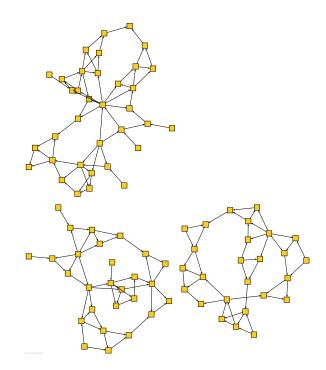

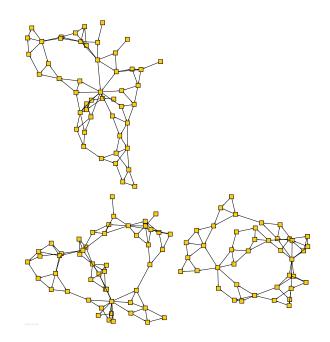

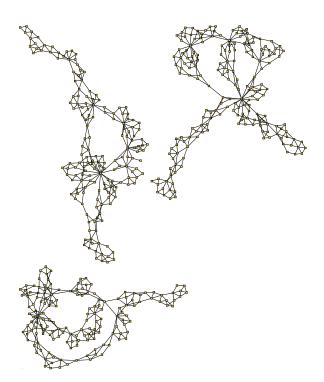

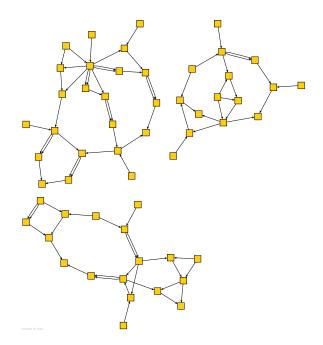

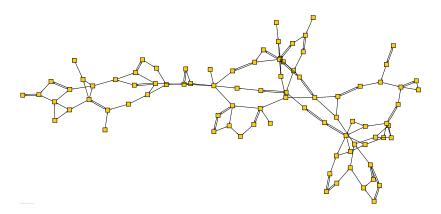

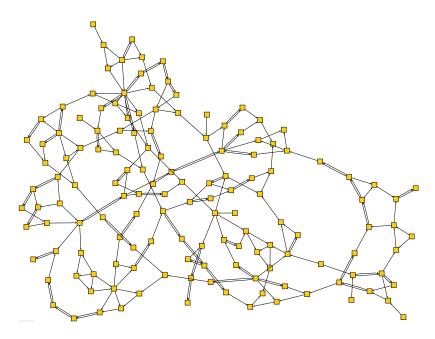

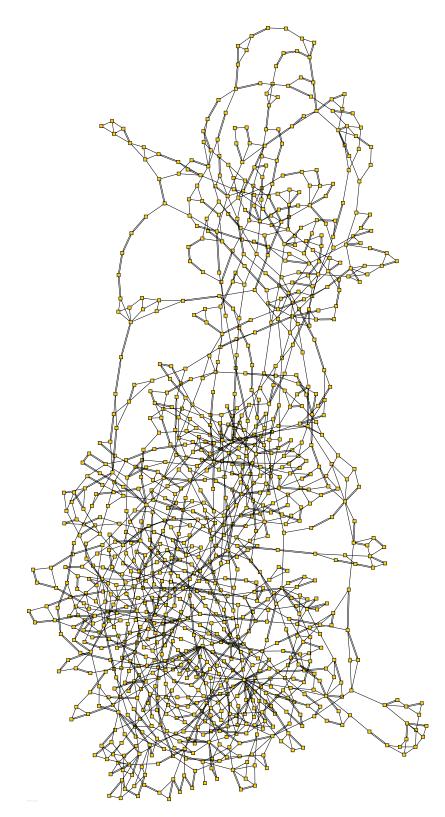

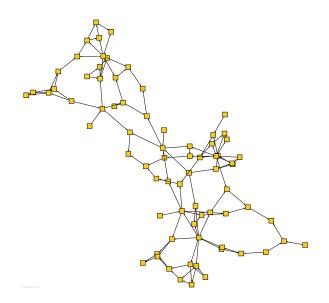

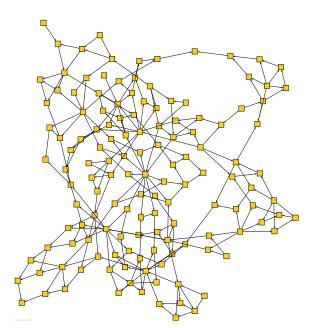

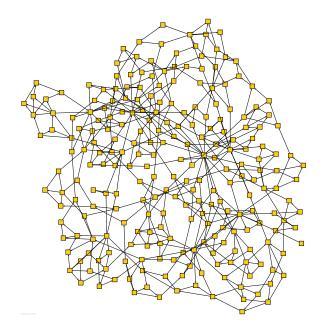

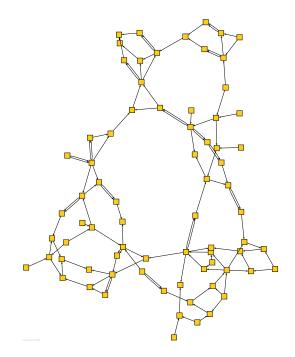

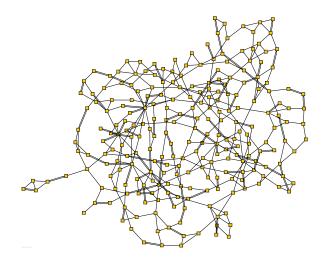

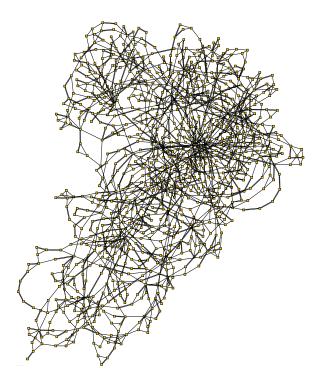

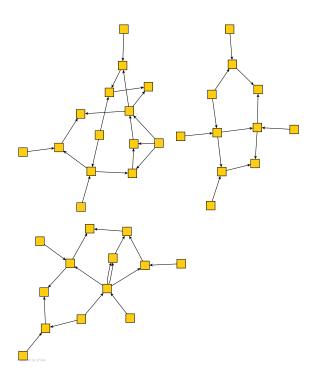

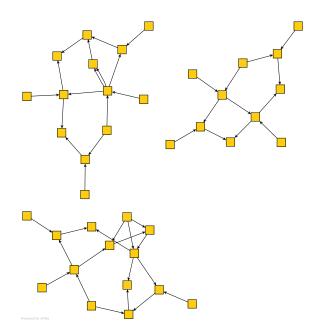

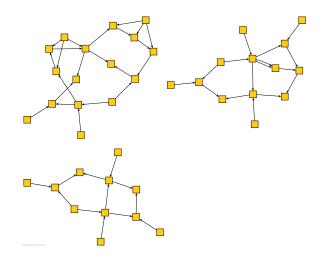

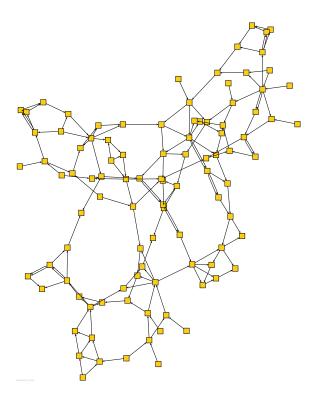

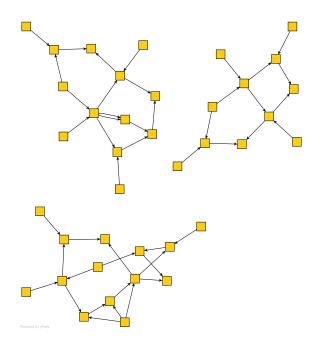

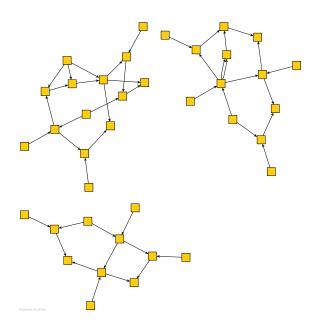

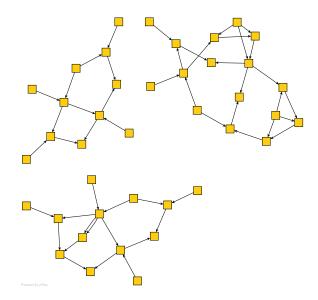

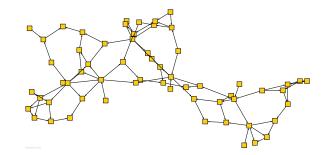

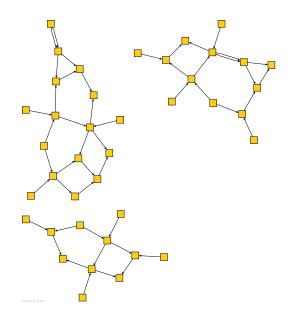

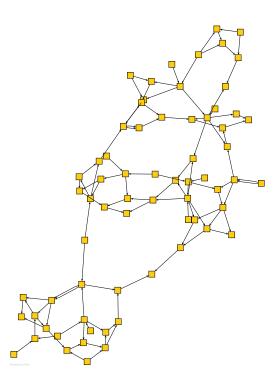

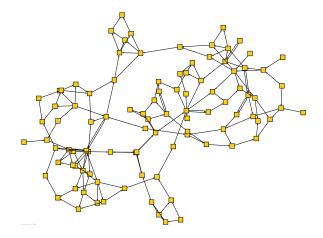

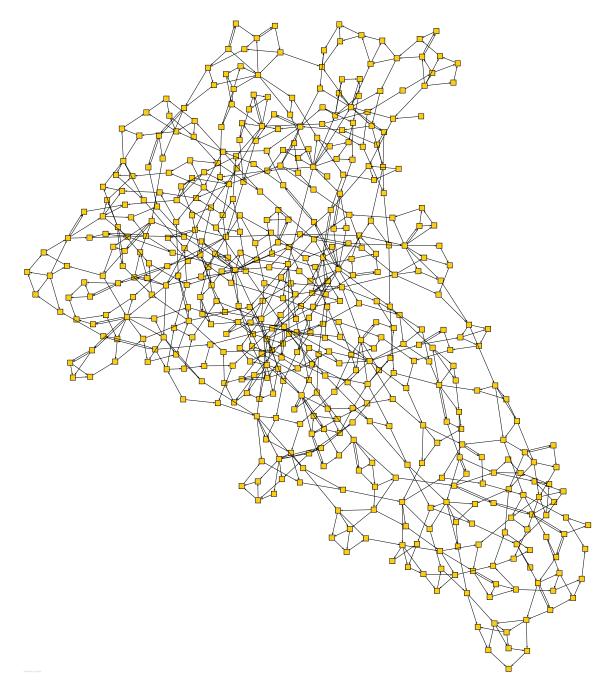

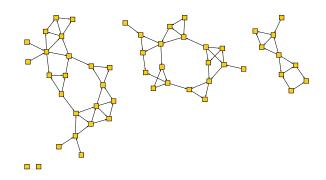

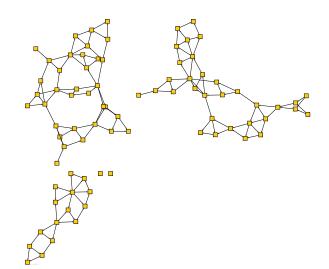

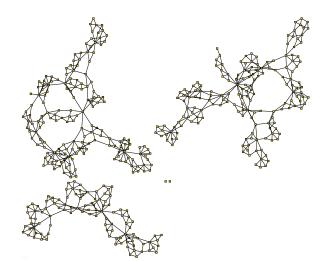

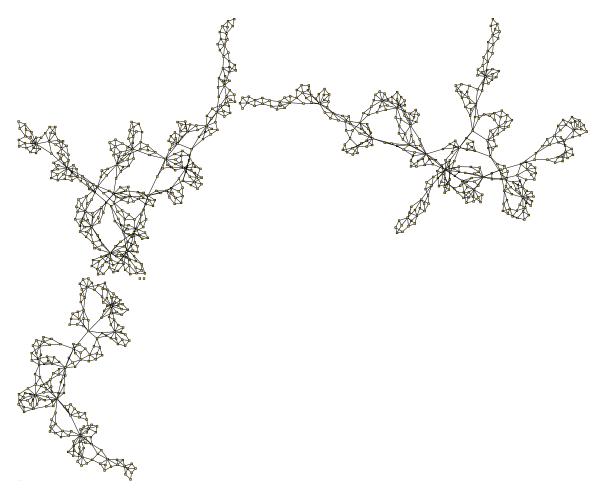

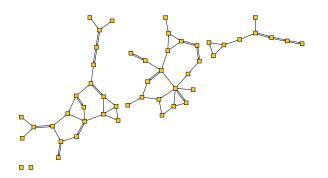

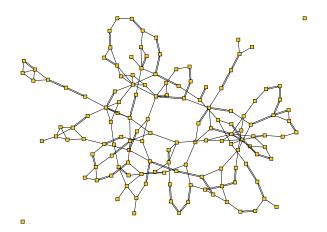

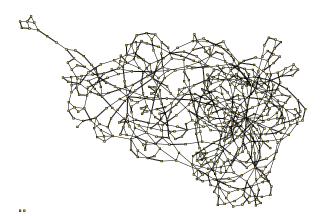

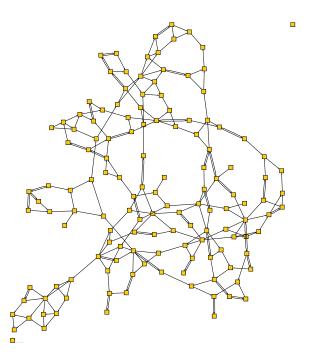

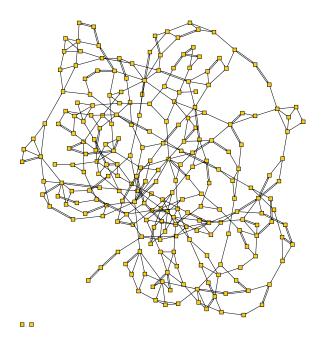

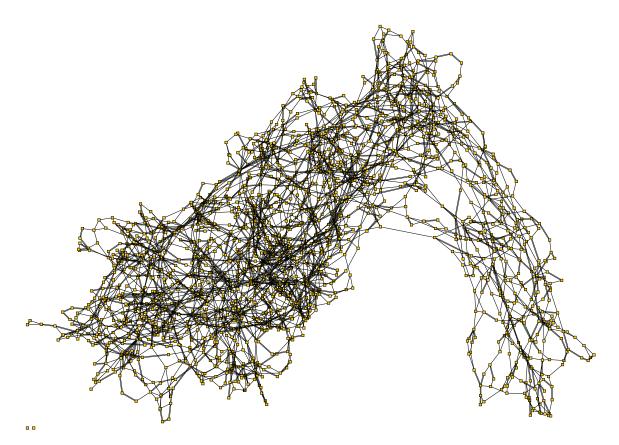

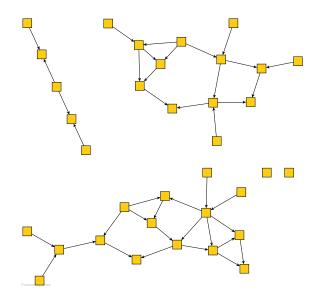

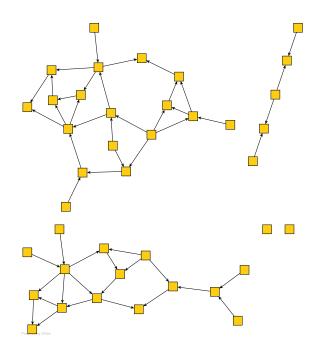

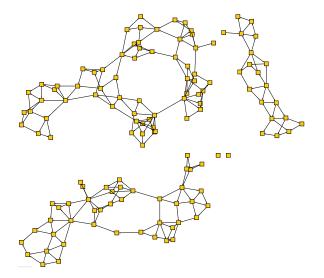

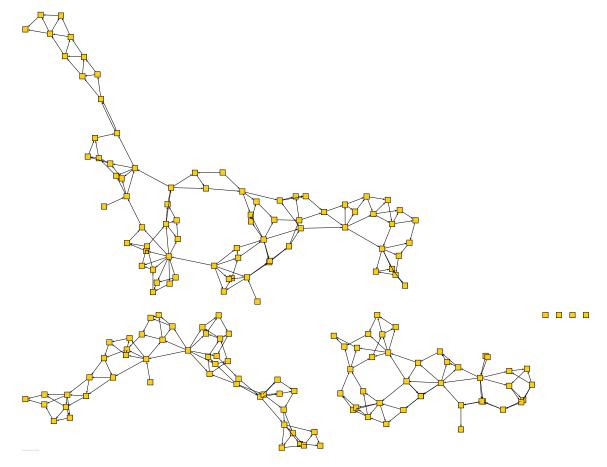

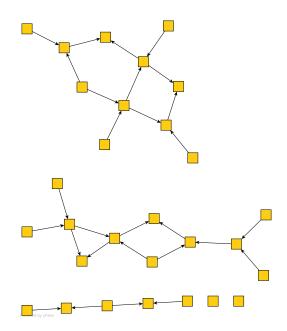

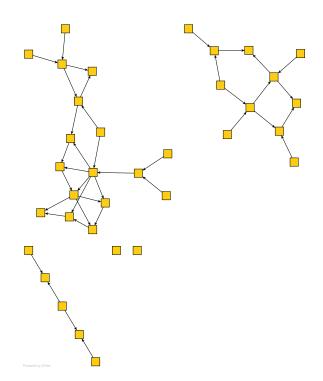

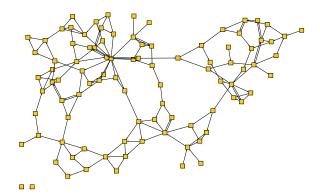

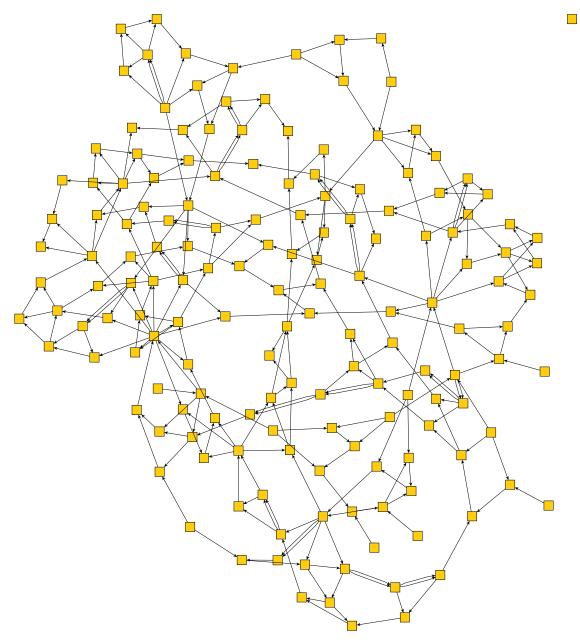

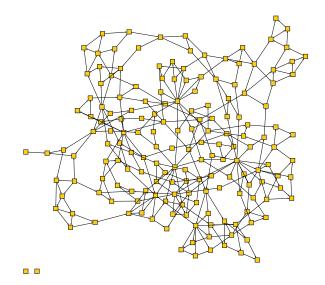

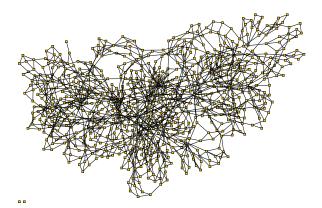

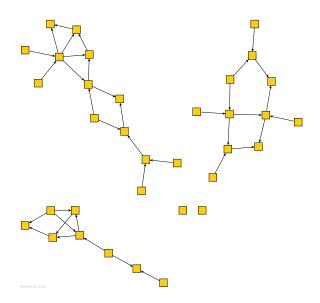

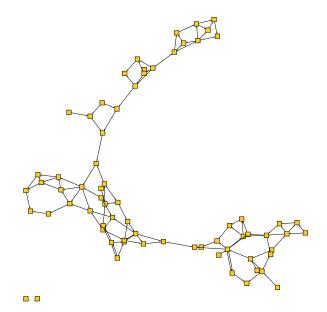

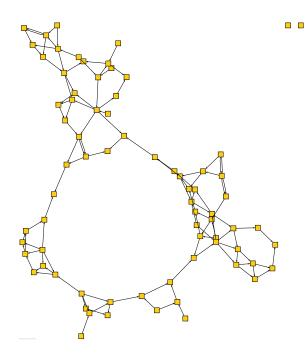

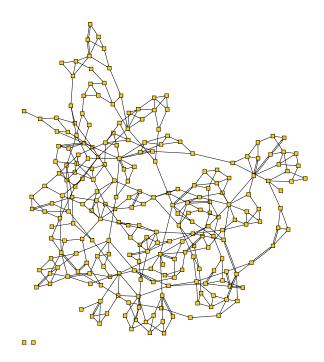

3.2.4 Circuits. To conduct CORGI experiments using the above options, we must also consider the actual circuits under consideration. We use two different circuits that are merged (in parallel) from three independent circuits. Figure 3.1 illustrates the graphs of these circuits. Figure 3.1(a) shows a composite circuit with three copies of the C17 circuit; Figure 3.1(b) shows a composite circuit based on one C17 circuit and two randomly generated circuits with roughly equal number of inputs, outputs, and gate size to C17.

These circuits illustrate a rudimentary visual feature that is useful for considering the effects of both circuit variation and circuit reduction. When we examine the graphs of circuit variants produced by *CORGI*, the variants demonstrate one of two properties in terms of their graph: 1) either the variant circuit graph contains two or three independent (but larger) subgraphs, or 2) the variant circuit graph contains a single graph with merged nodes. As a very simple measure, variants that do not exhibit a merged graph would be considered harder to analyze or reverse engineer than variants that do exhibit independent subgraphs. If our proposed reduction sequences can take a variant with a merged single graph and reduce it to a circuit with independent subgraphs, we may also conclude that the actual obfuscation was not effective (at least in terms of hiding the topography of components).

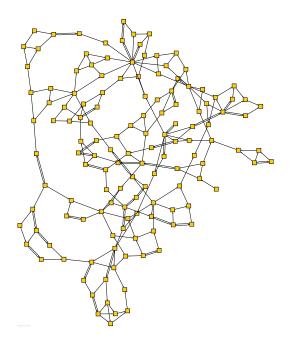

For our purposes, we setup CORGI experiments to run 1000 iterations of selection/replacement and take checkpoints of the variation process at the 20, 50, 100, 500,

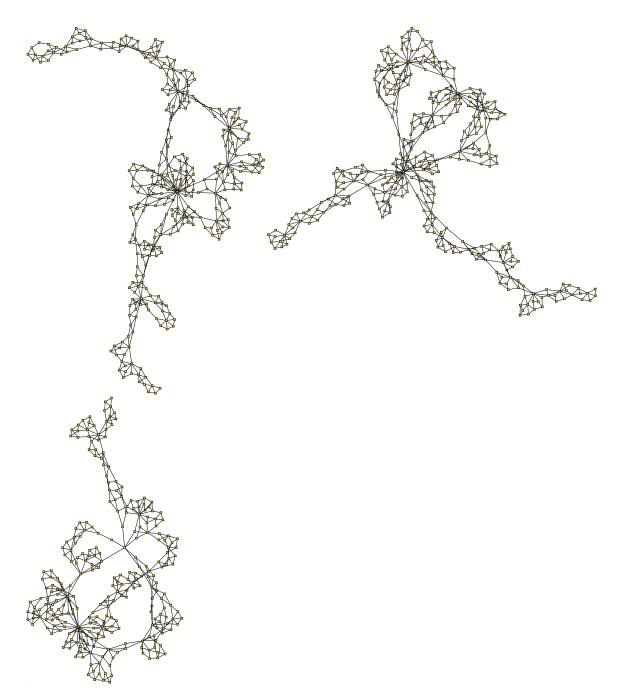

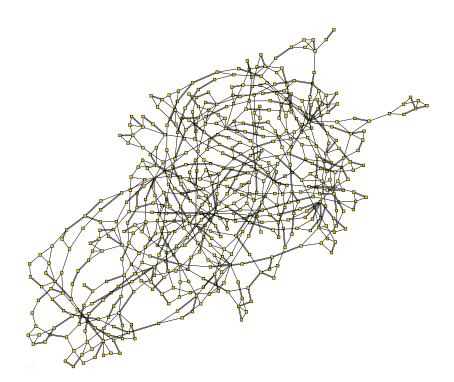

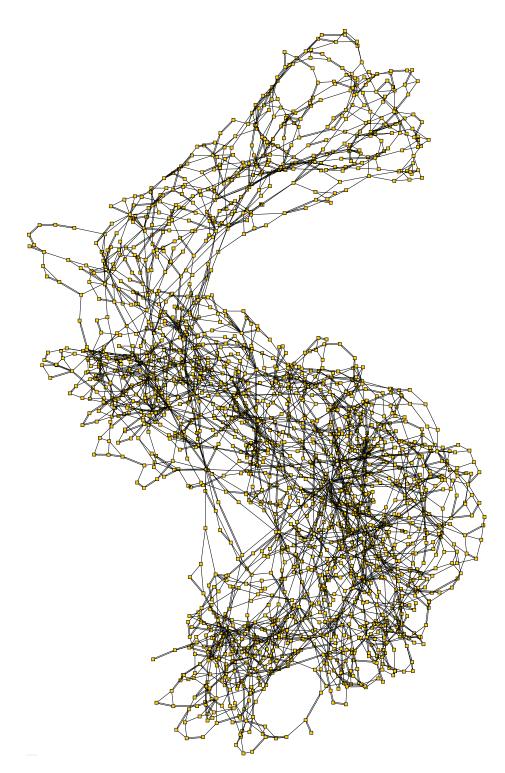

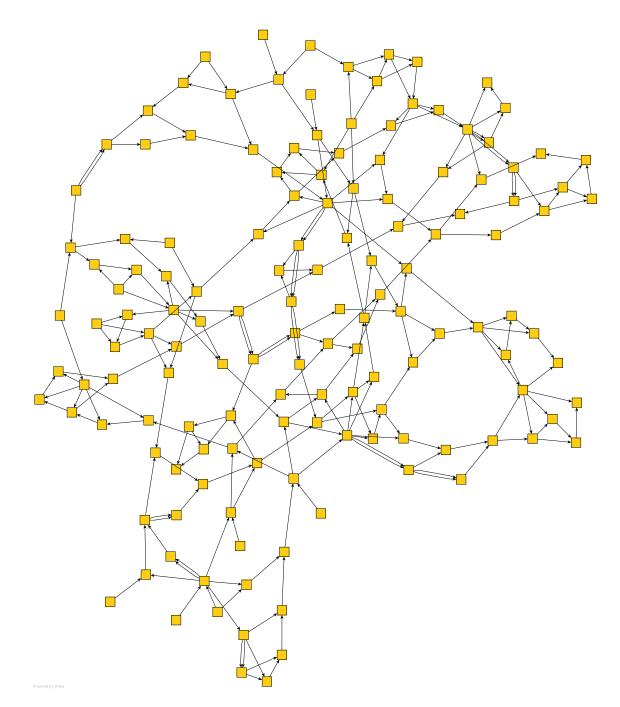

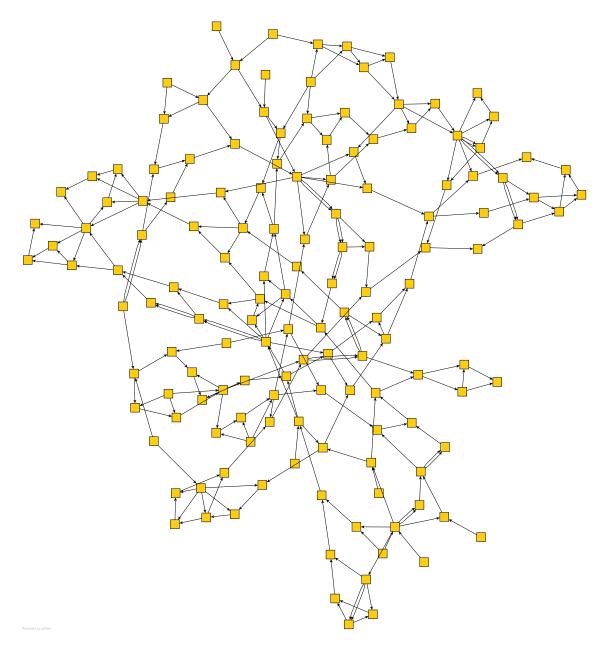

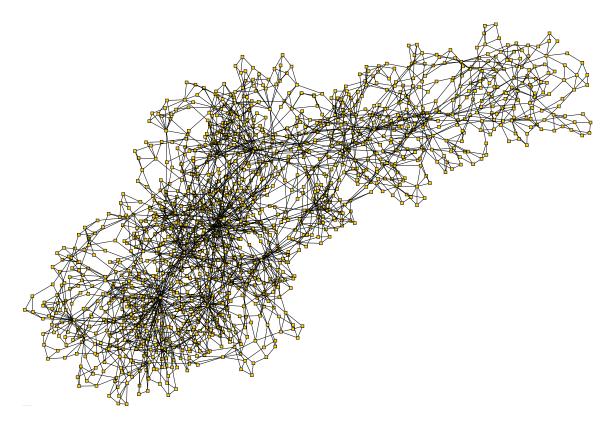

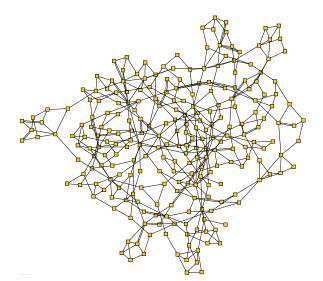

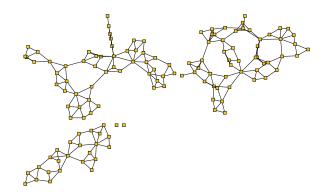

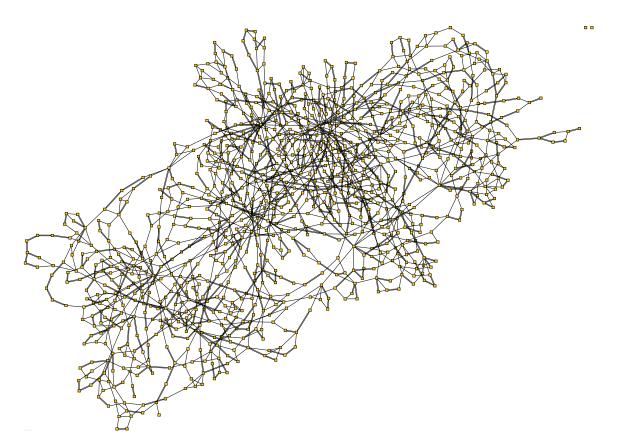

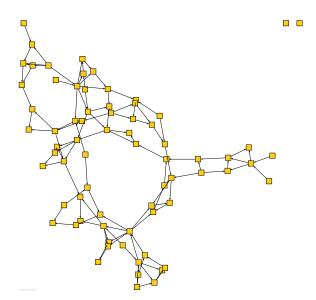

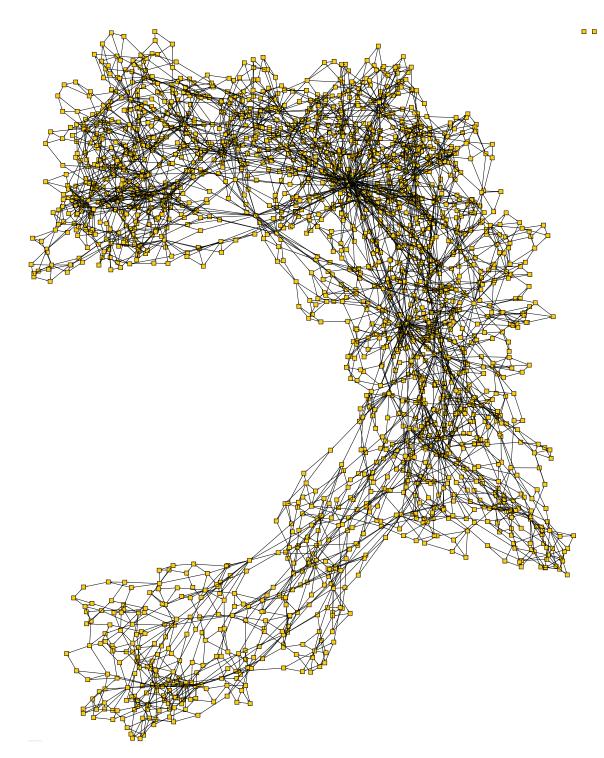

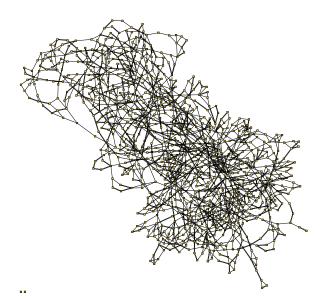

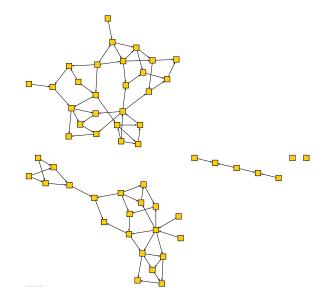

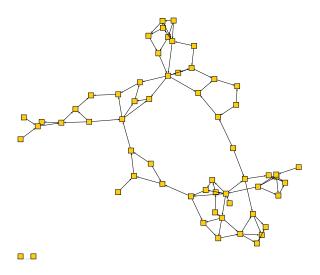

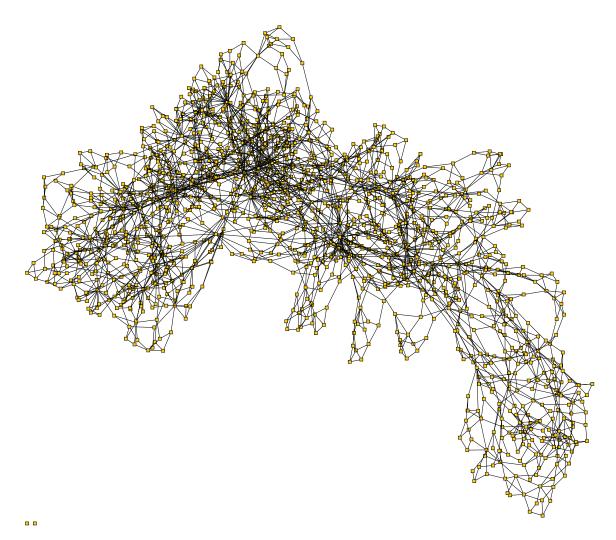

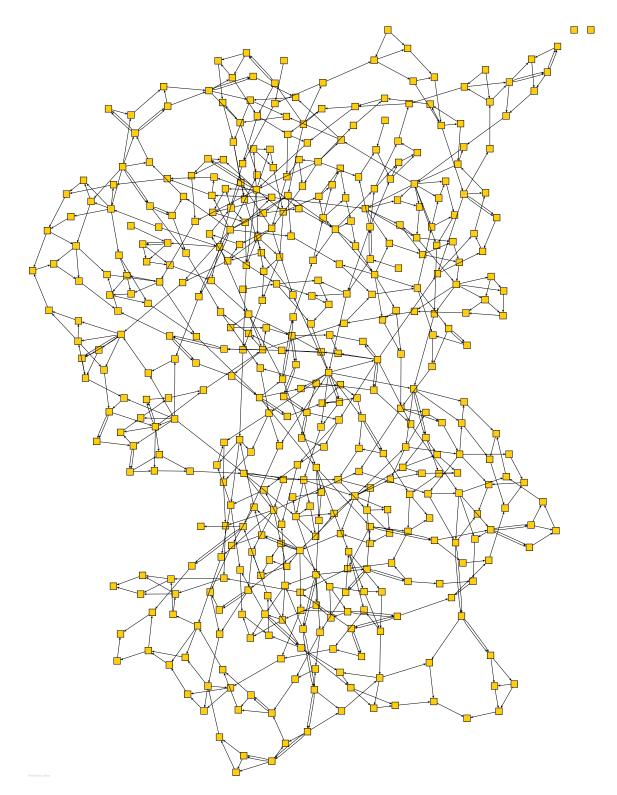

Figure 3.1: Original Circuit Graphs. (a) circuit C17 + C17 + C17. (b) circuit R17' + C17 + R17''.

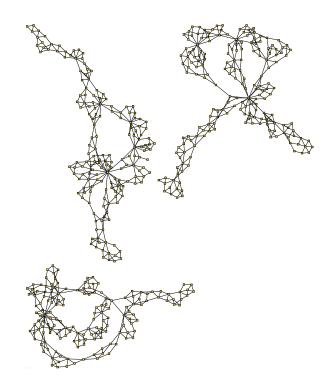

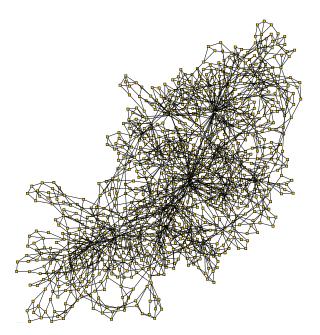

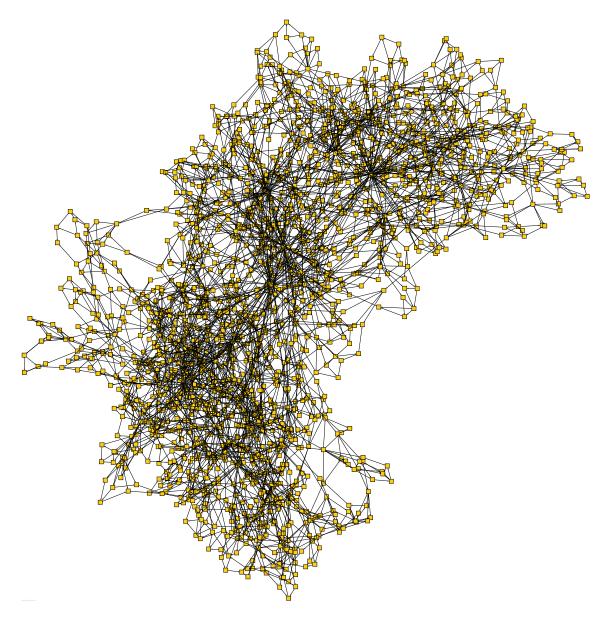

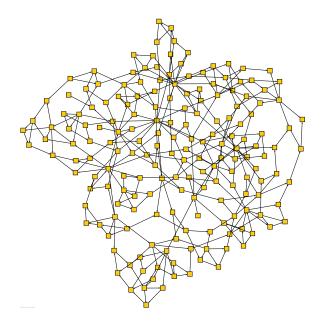

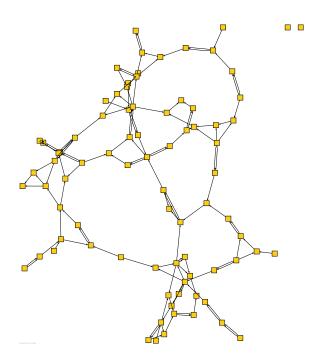

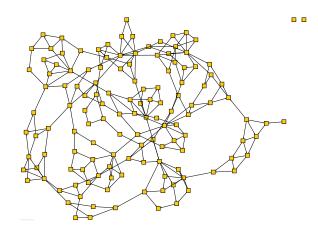

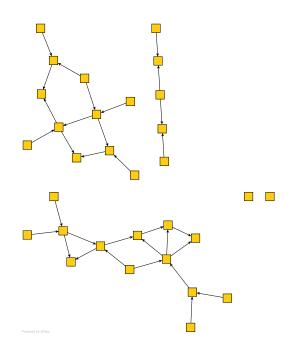

and 1000 iteration points. Given the starting size of our original circuits at around 20 gates, 1000 iterations represents an extreme upper bound on circuit size blowup for circuits in real world applications. Figure 3.2 illustrates a variant circuit graph produced by an experiment on the C17 + C17 + C17 circuit seen in Figure 3.1(a). The experiment uses 500 iterations with a 3 gate replacement size and *FFFTTT* as the library generation option. Appendix A.1 and B.1 shows the circuit variants for the original circuits C17 + C17 + C17 and R17' + C17 + R17'' at different iteration levels.

### 3.3 Analysis of Obfuscated Circuit Variants

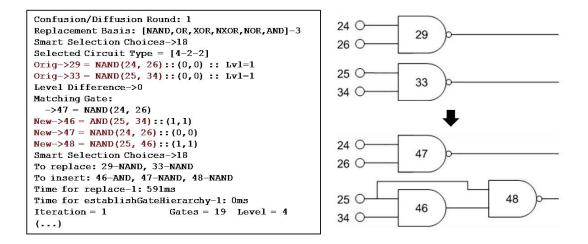

3.3.1 Pattern Recognition. To discover kinds of patterns associated with iterative substitution/replacement algorithms, we manually analyze variants of combinational circuits using log files from CORGI experiments. For example, Figure 3.3 illustrates the log file and corresponding circuit variant graph generated by CORGI. It shows that two gates, NAND(24, 26) and NAND(25, 34), are replaced with three gates, AND(25, 34), NAND(24, 26) and NAND(25, 46). Since NAND(24, 26) does not change except gate number, we consider only the change induced by replacing

Figure 3.2: Obfuscated Circuit Variant Graph after applying 500 iterations, 3 gates replacement, and FFFTTT library generation option to circuit C17 + C17 + C17.

NAND(25, 34) with AND(25, 34) and NAND(25, 46). By analyzing this transformation, we realize that subcircuits with a NAND gate may be replaced with a subcircuit consisting of an AND gate followed by a NAND gate. At the logic level, we may begin to reason about this using a pattern-based approach.

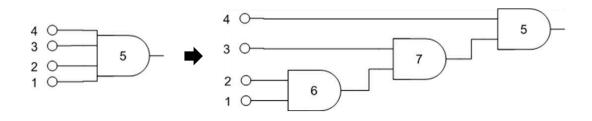

In current or typical *CORGI* experimentation, combinational replacement logic manifests primarily as a collection of dual (two-input) fan-in gates. We know also that all combinational circuits with multiple fan-in gates can be decomposed into dual fan-in gates as shown in Figure 3.4. Therefore, as a simplifying assumption for our research, we consider subcircuits with two input gates.

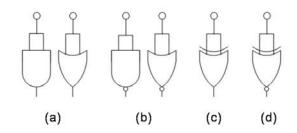

To further our analysis, we examined circuit variants generated by iteratively selecting two gates and replacing them with three gates. Our analysis of these variants revealed the presence of many redundant buffers, inverters, and constant 0/1 gates as shown in Figure 3.5. When using the *CORGI* replacement generation option *TFTTTT*, these patterns occur quite often, mainly because this option allows gates

Figure 3.3: Log/Graph Example in CORGI

Figure 3.4: Decomposing Multiple Fan-out Gate

Figure 3.5: Redundant Gates

- (a) Buffer

- (b) Inverter

- (c) Constant 0

- (d) Constant 1

to have the same input value (i.e., a gate with a single input signal feeding both inputs of the gate).

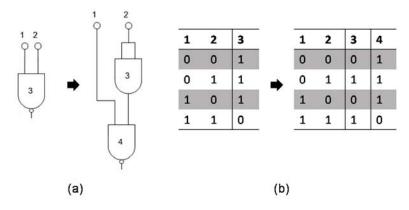

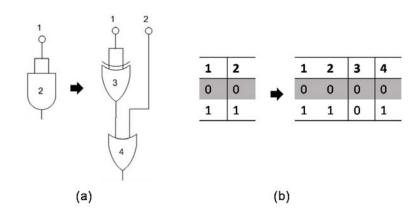

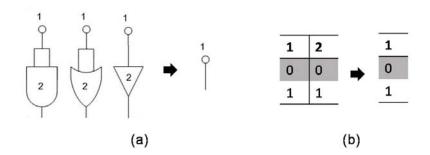

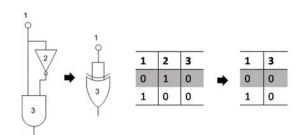

3.3.2 Pattern Classification. Even though CORGI generates patterns that are typically considered reducible logic forms (at least when one gate and two gate selections are in view), the overall effect of iteration may exploit these rudimentary gates so that they combine with other gates in later substition/replacement operations. However, when these patterns are not reused and replaced in later experiments, they become easily identifiable by basic pattern matching. Figure 3.6, 3.7 and 3.8 illustrates the configurations of these basic patterns. The graph in Figure 3.6(a) shows that when CORGI replaces one gate with two gates, it is possible that a buffer can be inserted. We can relate this gate replacement operation to its truth table equivalent and show in Figure 3.6(b) their correlation. Similarly, the gate replacement using an inverter/constant would be possible using gate replacement from one gate into two gates as shown in Figure 3.7(a) and 3.8(a).

CORGI also generates more specialized gate replacement as shown in Figure 3.9. The graph in Figure 3.9(a) shows when there is one NAND gate, the gate can be merged with XNOR gate. Likewise, we can relate this structural gate replacement using its truth table form as shown in Figure 3.9(b). As an important facet about this type of replacement, we note that it is logically related to a larger family of gate

Figure 3.6: Gate Replacement using Buffer (a) Gate Replacement

(b) Truth Table

Figure 3.7: Gate Replacement using Inverter(a) Gate Replacement(b) Truth Table

Figure 3.8: Gate Replacement using Constant (a) Gate Replacement

(b) Truth Table

Figure 3.9: Gate Replacement Example for the Special Case(a) Gate Replacement(b) Truth Table

replacements. For example, if the original gate in Figure 3.9(a) is an AND gate, a functional equivalent to this would be the XNOR and AND gate pair seen in the right side of the figure. The basis of our circuit reduction algorithm is to essentially find such patterns and use their smaller equivalent structural form, while retaining the overall circuit logic.

In contrast to two gate selection/three gate replacement, gate replacements from two gates to four gates generated a wider variety of structural patterns, as we would expect. Figure 3.10 illustrates an example of this replacement type. In this case,

Figure 3.10: Complex Gate Replacement Example(a) Gate Replacement(b) Truth Table

we need to utilize truth table analysis in order to understand the logical effect of the replacement. We consider these complex gate replacements specifically when we implement circuit reduction techniques, which we describe in the next section.

#### 3.4 Implementation of Circuit Reduction Algorithms

As the previous section describes, our methodology for creating reduction algorithms begins by analyzing the circuit variants produced by *CORGI*. If we consider the reverse pattern of the underlying logic that we observe, we have a basis to understand how to remove or reduce such logic that still exists in the final circuit variant. For example, if there exists a change from a single NAND(1,2) to XNOR(1,2) and NAND(3,2) as shown in Figure 3.9, we can consider the reverse structural change of this from XNOR(1,2) and NAND(3,2) to NAND(1,2) as shown in Figure 3.11.

Building upon our investigation of sample circuit variants, we build a wide variety of predetermined reduction patterns that appear most frequently, giving us a possibility to easily remove induced redundancy introduce by the variation process. Ultimately, our goal would be to remove all new gates introduced by an obfuscating algorithm. Realistically, we would like to remove as many as possible using just basic pattern matching. Using this approach, we define and implement 10 patterns for circuit reduction algorithms and describe them in sections 3.4.1 - 3.4.10.

Figure 3.11: Reverse Logic Example of Figure 3.9(a) Gate Replacement(b) Truth Table

When complex gate replacements are in view, like those seen in Figure 3.10, we use truth table analysis to increase our pattern search space above those provided by our 10 basic circuit reduction techniques. Using this approach, we define and implement two truth-table based reduction algorithms and describe them in sections 3.4.11 - 3.4.12.

3.4.1 Reduce Buffer. This algorithm implements the following reduction logic:

- For each gate, if it is an *AND/OR* gate that has both inputs from the same source, remove it as shown in Figure 3.12.

- For each gate, if it is a buffer, remove it as shown in Figure 3.12.

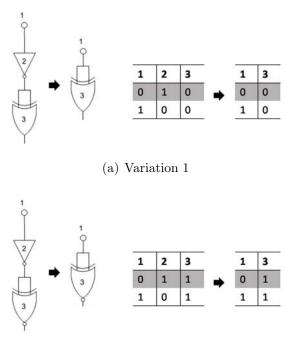

3.4.2 Reduce Inverter. This algorithm implements the following reduction logic:

• For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a predecessor of the gate is a NOT gate, remove them as shown in Figure 3.13(a).

Figure 3.12: Reduction Algorithm 1(Reduce Buffer)(a) Gate Replacement(b) Truth Table

- For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a predecessor of the gate is a buffer, remove it and change the buffer into a NOT gate as shown in Figure 3.13(b).

- For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a predecessor of the gate is a positive gate(AND/OR/ XOR), remove it and change the positive gate(AND/OR/XOR) into a negative gate(NAND/NOR/XNOR) as shown in Figure 3.13(c).

- For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a predecessor of the gate is a negative gate(NAND/ NOR/XNOR), remove it and change the negative gate(NAND/NOR/XNOR) into a positive gate(AND/OR/XOR) as shown in Figure 3.13(d).

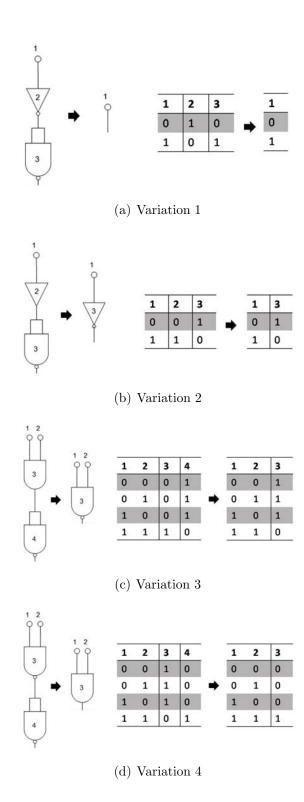

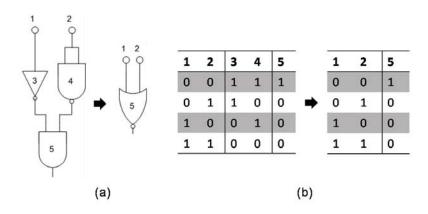

3.4.3 Reduce Inverter with Successor XOR/XNOR. This algorithm implements the following reduction logic:

- For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a successor of the gate is an XOR gate, remove it and change the XOR gate into an XNOR gate as shown in Figure 3.14(a).

- For each gate, if it is an inverter(NAND/NOR/NOT) that has both inputs from the same source and a successor of the gate is an XNOR gate, remove it and change the XNOR gate into an XOR gate as shown in Figure 3.14(b).

Figure 3.13: Gate Replacement and Truth Table of Reduction Algorithm 2 (Reduce Inverter)

(b) Variation 2

Figure 3.14: Gate Replacement and Truth Table of Reduction Algorithm 3 (Reduce Inverter with Successor XOR/XNOR)

3.4.4 Reduce Constant 0/1. This algorithm implements the following reduction logic:

- For each gate, if it is a constant 0 that its next gate is an AND gate, remove it and change the AND gate into a constant 0 as shown in Figure 3.15(a) and 3.15(b).

- For each gate, if it is a constant 0 that its next gate is a NAND gate, remove it and change the NAND gate into a constant 1. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 0 that its next gate is an OR/XOR gate, remove it and change the OR/XOR gate into a buffer. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 0 that its next gate is a NOR/XNOR gate, remove it and change the NOR/XNOR gate into a NOT gate. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 1 that its next gate is a NOR gate, remove it and change the NOR gate into a constant 0. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 1 that its next gate is an *OR* gate, remove it and change the *OR* gate into a constant 1. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 1 that its next gate is an AND/XNOR gate, remove it and change the AND/XNOR gate into a buffer. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

- For each gate, if it is a constant 1 that its next gate is a NAND/XOR gate, remove it and change the NAND/XOR gate into a NOT gate. The gate replacement and truth table of this logic resemble Figure 3.15(a) and 3.15(b) except change of gate types.

3.4.5 Reduce Constant 0/1 with Inverter Inputs. This algorithm implements the following reduction logic:

• For each gate, if it is a constant 0/1 that has only an inverter as input, remove the inverter as shown in Figure 3.16(a) and 3.16(b).

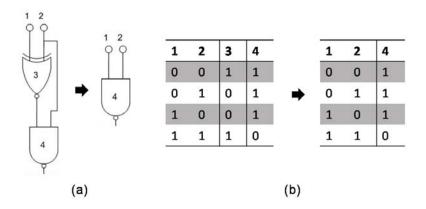

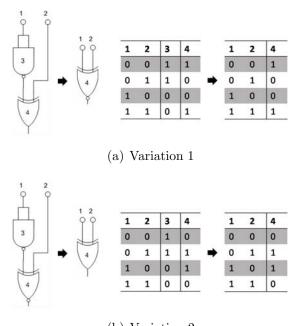

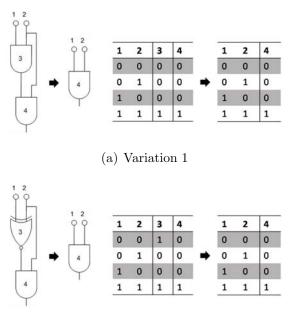

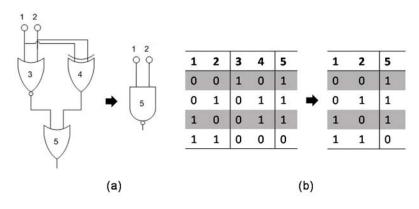

3.4.6 Reduce Two Gates to AND/NAND/OR/NOR. This algorithm implements the following reduction logic:

Figure 3.15: Gate Replacement and Truth Table of Reduction Algorithm 4 (Reduce Constant 0/1)

(b) Variation 2

Figure 3.16: Gate Replacement and Truth Table of Reduction Algorithm 5 (Reduce Constant 0/1 with Inverter Inputs)

- For each gate, if it is an AND/XNOR gate and its next gate is an AND gate, remove it as shown in Figure 3.17(a) and 3.17(b).

- For each gate, if it is an AND/XNOR gate and its next gate is a NAND gate, remove it. The gate replacement and truth table of this logic resemble Figure 3.17(a) and 3.17(b) except change of gate types.

- For each gate, if it is an *OR/XOR* gate and its next gate is an *OR* gate, remove it. The gate replacement and truth table of this logic resemble Figure 3.17(a) and 3.17(b) except change of gate types.

- For each gate, if it is an *OR/XOR* gate and its next gate is a *NOR* gate, remove it. The gate replacement and truth table of this logic resemble Figure 3.17(a) and 3.17(b) except change of gate types.

(b) Variation 2

Figure 3.17: Gate Replacement and Truth Table of Reduction Algorithm 6 (Reduce Two Gates to AND/NAND/OR/NOR)

3.4.7 Reduce Two Gates to Buffer/NOT/Constant 0/1. This algorithm implements the following reduction logic:

- For each gate, if it is an AND gate and its next gate is an OR gate, remove it and change the OR gate into a buffer as shown in Figure 3.18.

- For each gate, if it is an *OR* gate and its next gate is an *AND* gate, remove it and change the *AND* gate into a buffer. The gate replacement and truth table of this logic resemble Figure 3.18 except change of gate types.

- For each gate, if it is an AND gate and its next gate is a NOR gate, remove it and change the NOR gate into a NOT gate. The gate replacement and truth table of this logic resemble Figure 3.18 except change of gate types.

- For each gate, if it is an *OR* gate and its next gate is a *NAND* gate, remove it and change the *NAND* gate into a *NOT* gate. The gate replacement and truth table of this logic resemble Figure 3.18 except change of gate types.

Figure 3.18: Reduction Algorithm 7

(Reduce Two Gates to Buffer/NOT/Constant 0/1)

(a) Gate Replacement

(b) Truth Table

- For each gate, if it is a *NOR* gate and its next gate is an *AND* gate, remove it and change the *AND* gate into a constant 0. The gate replacement and truth table of this logic resemble Figure 3.18 except change of gate types.

- For each gate, if it is a *NOR* gate and its next gate is a *NAND* gate, remove it and change the *NAND* gate into a constant 1. The gate replacement and truth table of this logic resemble Figure 3.18 except change of gate types.

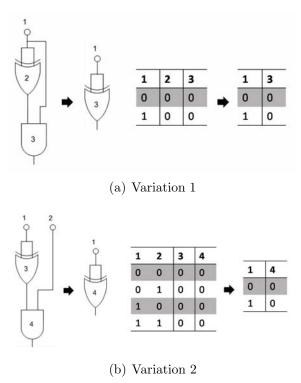

3.4.8 Reduce Two XOR/XNOR Gates to Buffer/NOT. This algorithm implements the following reduction logic:

- For each gate, if it is an XOR/XNOR gate and its next gate is an XOR/XNOR gate, remove it and change the XOR/XNOR gate into a buffer as shown in Figure 3.19(a) and 3.19(b).

- For each gate, if it is an XOR/XNOR gate and its next gate is an XNOR/XOR gate, remove it and change the XNOR/XOR gate into a NOT gate as shown in Figure 3.19(c) and 3.19(d).

Figure 3.19: Gate Replacement and Truth Table of Reduction Algorithm 8 (Reduce Two XOR/XNOR Gates to Buffer/NOT)

(a) Variation 1

(b) Variation 2

Figure 3.20: Gate Replacement and Truth Table of Reduction Algorithm 9 (Reduce Gate with Opposite Inputs)

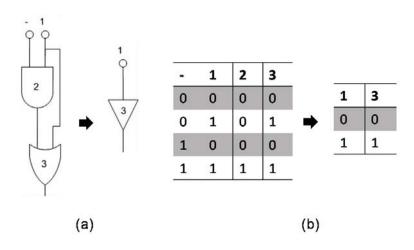

3.4.9 Reduce Gate with Opposite Inputs. This algorithm implements the following reduction logic:

- For each gate, if it is an AND/NOR/XNOR gate that has only opposite inputs, change them into a constant 0 as shown in Figure 3.20(a).

- For each gate, if it is an *OR/NAND/XOR* gate that has only opposite inputs, change them into a constant 1 as shown in Figure 3.20(b).

3.4.10 Reduce AND/OR/NAND/NOR Gates with Inverter Inputs. This algorithm implements the following reduction logic:

- For each gate, if it is an AND gate that has only inverters as inputs, change it into a NOR gate and remove the inverters as shown in Figure 3.21.

- For each gate, if it is an *OR* gate that has only inverters as inputs, change it into a *NAND* gate and remove the inverters. The gate replacement and truth table of this logic resemble Figure 3.21 except change of gate types.

Figure 3.21: Reduction Algorithm 10

(Reduce AND/OR/NOT Gates with Inverter Inputs)

(a) Gate Replacement

(b) Truth Table

- For each gate, if it is a *NAND* gate that has only inverters as inputs, change it into an *OR* gate and remove the inverters. The gate replacement and truth table of this logic resemble Figure 3.21 except change of gate types.

- For each gate, if it is a *NOR* gate that has only inverters as inputs, change it into an *AND* gate and remove the inverters. The gate replacement and truth table of this logic resemble Figure 3.21 except change of gate types.

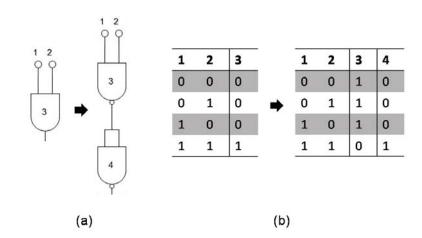

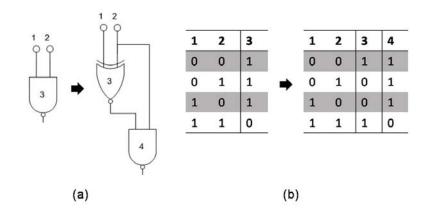

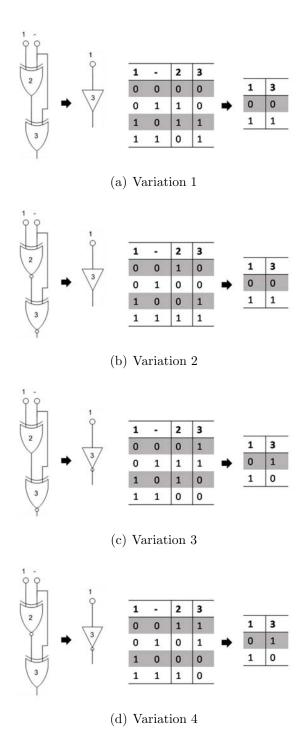

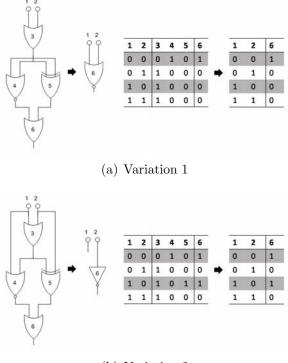

3.4.11 Reduce V pattern. For each V pattern, if it has a truth table equal to predefined functions such as AND, OR, NAND, NOR, XOR, XNOR, buffer, NOT, constant 0/1, and combinations of these, change the pattern into the equivalent reduced form as shown in Figure 3.22.

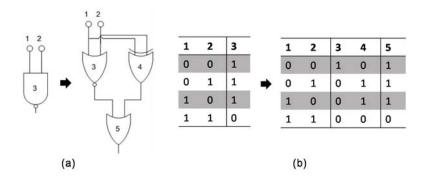

3.4.12 Reduce Diamond pattern. For each Diamond pattern, if it has a truth table equal to predefined function such as AND, OR, NAND, NOR, XOR, XNOR, buffer, NOT, constant 0/1, and combinations of these, change the pattern into the equivalent reduced form as shown in Figure 3.23(a) and 3.23(b).

Figure 3.22: Reduction Algorithm 11(Reduce V pattern)(a) Gate Replacement(b) Truth Table

(b) Variation 2

Figure 3.23: Gate Replacement and Truth Table of Reduction Algorithm 12 (Reduce Diamond pattern)

|           | Obfusca  | ted Options |             | Reduction Options  |           |           |  |  |

|-----------|----------|-------------|-------------|--------------------|-----------|-----------|--|--|

| Selection | Gate     | Library     | Obfuscation | Circuit            | Reduction | Reduction |  |  |

| Algorithm | Replaced | Generation  | Iteration   | Type               | Algorithm | Round     |  |  |

| Random    | 3        | FFFTTT      | 20          | C17 - C17 - C17    | Random    | 10        |  |  |

| Algorithm | 4        | TFTTTT      | 50          | R17' - C17 - R17'' | Algorithm |           |  |  |

|           |          |             | 100         |                    |           |           |  |  |

|           |          |             | 500         |                    |           |           |  |  |

|           |          |             | 1000        |                    |           |           |  |  |

Table 3.1:

Experimental Setup for Circuit Reduction

## 3.5 Evaluation of Circuit Obfuscation

Experimental Setup. 3.5.1As described in Section 3.2, we generate functionally equivalent variants of two different circuits (C17 - C17 - C17, R17' - C17 - R17'')using a specific set of experiment options. We summarize these experimental configuration options in Table 3.1. Using these options, we produce a total of 20 different variants for each circuit, giving us a set of 40 circuits with which to consider the effect of reduction. For each particular circuit in our variant set, we normalize them by applying our set of 12 reduction techniques (described in Sections 3.4.1 - 3.4.12) in a sequential manner. We define a reduction round as the application of these 12 individual reduction algorithms one after the other, where the reduced circuit form produced by one reduction technique becomes the input to the next reduction technique. We note that there exists at least 12! possibilities for ordering the individual techniques themselves within a reduction round. We therefore define a reduction experiment as a starting circuit variant and the application of an ordered sequence of our 12 reduction algorithms, in some iterative fashion. As the final experiment parameter, we may run multiple reduction rounds (i.e., apply the same 12 individual techniques again) on the same variant in an iterative manner. As Table 3.1 illustrates, we use 10 reduction rounds and a random ordering of the individual reduction algorithms for our experimental purposes. Once we choose a random ordering, that ordering remains the same for the entire 10 rounds of a reduction experiment. Because full enumeration of all possible algorithm orderings is not computationally feasible (O(n!)), we chose a random approach as the best starting point to characterize how much circuit reduction is affected by algorithm ordering. We also look to see if there is a lower bound on the number of rounds where we no longer observe size reduction on the variant circuit. We use 10 as a rough upper bound on number of rounds to run for each reduction experiment based on our observations while running over 500 different reduction experiments. Based on a fixed reduction round size of 10, we can apply our set of circuit reduction algorithms at most 120 times, where no algorithm is applied more than 12 times itself.

Given the set of 40 circuit variants under consider, we describe the basic algorithm for our experimental approach in the following pseudocode. Let each reduction technique be represented by a function  $R_k$  which takes as input a circuit C and produces a functionally equivalent version C'; k is in the range 1..12, representing one of the algorithms described in Sections 3.4.1 - 3.4.12. The specific algorithm  $R_k$  takes a circuit and iterates through the entire gate list of the circuit. As this process occurs, if the particular pattern indicated by the reduction technique is encountered, the appropriate reduction is performed. The algorithm accomplishes this by traversing through a single pass of the circuit gate list.