Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

9-12-2019

## Adaptive-Hybrid Redundancy for Radiation Hardening

Nicolas S. Hamilton

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Electrical and Electronics Commons, and the Hardware Systems Commons

#### **Recommended Citation**

Hamilton, Nicolas S., "Adaptive-Hybrid Redundancy for Radiation Hardening" (2019). *Theses and Dissertations*. 2377. https://scholar.afit.edu/etd/2377

This Dissertation is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

## ADAPTIVE-HYBRID REDUNDANCY FOR RADIATION HARDENING

DISSERTATION

Nicolas S. Hamilton, Major, USAF AFIT-ENG-DS-19-S-005

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

The views expressed in this document are those of the author and do not reflect the official policy or position of the United States Air Force, the United States Department of Defense or the United States Government. This material is declared a work of the U.S. Government and is not subject to copyright protection in the United States.

#### ADAPTIVE-HYBRID REDUNDANCY FOR RADIATION HARDENING

### DISSERTATION

Presented to the Faculty Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

> Nicolas S. Hamilton, M.S. Major, USAF

> > September 12, 2019

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.  $\rm AFIT\text{-}ENG\text{-}DS\text{-}19\text{-}S\text{-}005$

### ADAPTIVE-HYBRID REDUNDANCY FOR RADIATION HARDENING

#### DISSERTATION

Nicolas S. Hamilton, M.S. Major, USAF

Committee Membership:

Scott R. Graham, Ph.D. Chair

Major Timothy J. Carbino, Ph.D. Member

> James C. Petrosky, Ph.D. Member

Major J. Addison Betances, Ph.D. Member

#### Abstract

An Adaptive-Hybrid Redundancy (AHR) mitigation strategy is proposed to mitigate the effects of Single Event Upset (SEU) and Single Event Transient (SET) radiation effects. AHR is adaptive because it switches between Triple Modular Redundancy (TMR) and Temporal Software Redundancy (TSR). AHR is hybrid because it uses hardware and software redundancy. AHR is demonstrated to run faster than TSR and use less energy than TMR. Furthermore, AHR allows space vehicle designers, mission planners, and operators the flexibility to determine how much time is spent in TMR and TSR. TMR mode provides faster processing at the expense of greater energy usage. TSR mode uses less energy at the expense of processing speed. AHR allows the user to determine the optimal balance between these modes based on their mission needs and changes can be made even after the space vehicle is operational. Radiation testing was performed to determine the SEU injection rate for simulations and analyses. A Field Programmable Gate Array (FPGA) was used to expedite testing in hardware.

## AFIT-ENG-DS-19-S-005

For my wife and kids

### Acknowledgements

First and foremost, I am thankful for the opportunities in life that God has blessed me with so that I have been able to arrive at the point in my life where I have been afforded the opportunity to earn a PhD. I am also thankful to my wife and children who have supported me in my work, particularly for my wife kicking me out of the house and making me work from work rather than from the home office where I was not able to get much done. I would also like to thank Dr. Graham and Maj Carbino who both served as my primary advisors at different times and have guided me in my research. I also thank Dr. Petrosky and Maj Betances for the invaluable insights they provided into radiation effects and the intricacies of VHDL design respectively. Finally, the great team at Sandia National Laboratories Ion Beam Lab were instrumental in helping me perform radiation testing, without which I could not make the necessary radiation comparisons to previous works.

Nicolas S. Hamilton

## Table of Contents

|      | Pa                                                                                     | age                                                      |

|------|----------------------------------------------------------------------------------------|----------------------------------------------------------|

| Abst | ract                                                                                   | iv                                                       |

| Dedi | cation                                                                                 | . v                                                      |

| Ackr | owledgements                                                                           | vi                                                       |

| List | of Figures                                                                             | . x                                                      |

| List | of Tables                                                                              | xv                                                       |

| I.   | Introduction                                                                           | .1                                                       |

|      | 1.1 Research Context1.2 Assumptions1.3 Research Questions1.4 Dissertation Organization | .4<br>.5                                                 |

| II.  | Background                                                                             | . 7                                                      |

|      | <ul> <li>2.1 Introduction</li></ul>                                                    | .7<br>.8<br>.9<br>10<br>11<br>12<br>28<br>29<br>31<br>32 |

| III. | AHR MIPS Development                                                                   | 36                                                       |

|      | <ul> <li>3.1 Introduction</li></ul>                                                    | 38<br>38<br>41<br>46<br>46                               |

|      | 3.3.2       TMR MIPS Programs         3.4       TSR MIPS                               |                                                          |

## Page

|     |          | 3.4.1 TSR MIPS Development                   | . 55 |

|-----|----------|----------------------------------------------|------|

|     |          | 3.4.2 TSR MIPS Programs                      | . 55 |

|     | 3.5      | Adaptive-Hybrid Redundancy (AHR)             |      |

|     |          | 3.5.1 AHR Controller Finite State Machine    | . 65 |

|     |          | 3.5.2 AHR MIPS Architecture                  |      |

|     |          | 3.5.3 AHR MIPS Programs                      | . 72 |

|     | 3.6      | Summary                                      | . 74 |

| IV. | AH       | R MIPS Performance Evaluation                | . 75 |

|     | 4.1      | Introduction                                 | . 75 |

|     | 4.2      | Functional Verification                      | . 77 |

|     |          | 4.2.1 Basic MIPS Verification                | . 77 |

|     |          | 4.2.2 TMR MIPS Functional Verification       | . 79 |

|     |          | 4.2.3 TSR MIPS Functional Verification       | . 79 |

|     |          | 4.2.4 AHR MIPS Functional Verification       | . 80 |

|     | 4.3      | Error Free Software Simulation               | . 80 |

|     |          | 4.3.1 Time Simulation and Analysis           |      |

|     |          | 4.3.2 Energy Analysis                        |      |

|     |          | Error Free Software Simulation Results       |      |

|     | 4.5      | Error Free HITL Simulation                   |      |

|     |          | 4.5.1 First Attempt Methodology              |      |

|     |          | 4.5.2 First Attempt Results                  |      |

|     |          | 4.5.3 Second Attempt Methodology             |      |

|     |          | 4.5.4 Second Attempt Results                 |      |

|     | 4.6      | Summary                                      | 118  |

| V.  | Erro     | or Injection Development                     | 119  |

|     | 5.1      | Introduction                                 | 119  |

|     | 5.2      | Error Rate Determination                     | 119  |

|     |          | 5.2.1 Radiation Testing                      | 119  |

|     |          | 5.2.2 Radiation Testing Results and Analysis | 128  |

|     | 5.3      | Error Injection Architecture                 | 139  |

|     | 5.4      | Software Simulation with Error Injection     |      |

|     |          | 5.4.1 Runtime Calculations                   | 146  |

|     |          | 5.4.2 Energy Calculations                    | 188  |

|     | 5.5      | HITL Simulation with Error Injection         | 191  |

|     | 5.6      | Summary                                      | 192  |

| VI. | Erre     | or Injection Analysis and Results            | 193  |

|     | 6.1      | Introduction                                 | 193  |

|     | 6.2      | Software Simulation with Error Injection     |      |

|     | <b>-</b> | 6.2.1 TMR MIPS Error Injection Results       |      |

|     |          | J                                            | -    |

## Page

|       |       | 6.2.2 TSR MIPS Error Injection Results      | 95  |

|-------|-------|---------------------------------------------|-----|

|       |       | 6.2.3 AHR MIPS Error Injection Results      | 96  |

|       | 6.3   | HITL Simulation with Error Injection        | 225 |

|       | 6.4   | Results Summary                             | 227 |

| VII.  | Con   | clusions                                    | 228 |

|       | 7.1   | Contributions                               | 230 |

|       | 7.2   | Future Work                                 | 233 |

|       |       |                                             |     |

| Appe  | endix | A. AHR MIPS Architecture Detailed Diagrams2 | 235 |

| Bibli | ograj | phy                                         | 238 |

# List of Figures

| Figure |                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------|------|

| 1      | Dual Modular Redundancy Simplified Block Diagram                                                              | 14   |

| 2      | TMR MIPS Simplified Block Diagram                                                                             | 17   |

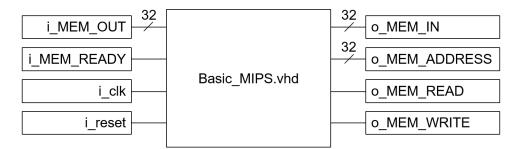

| 3      | Basic MIPS Inputs and Outputs                                                                                 | 41   |

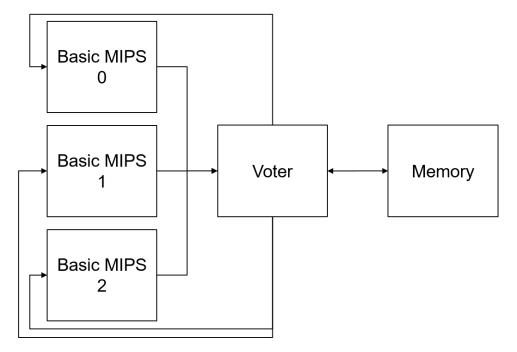

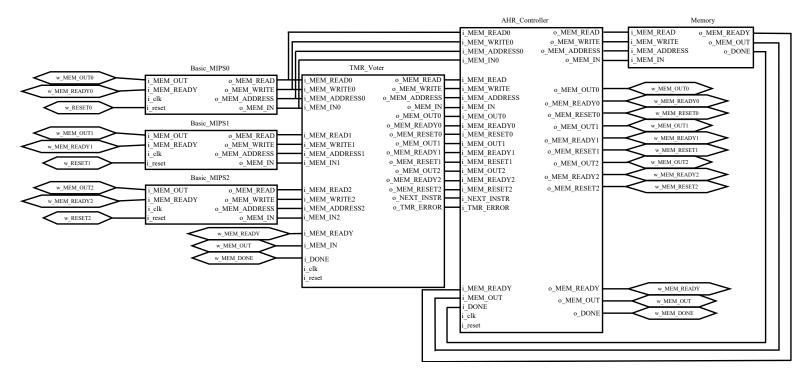

| 4      | TMR MIPS Block Diagram                                                                                        | 47   |

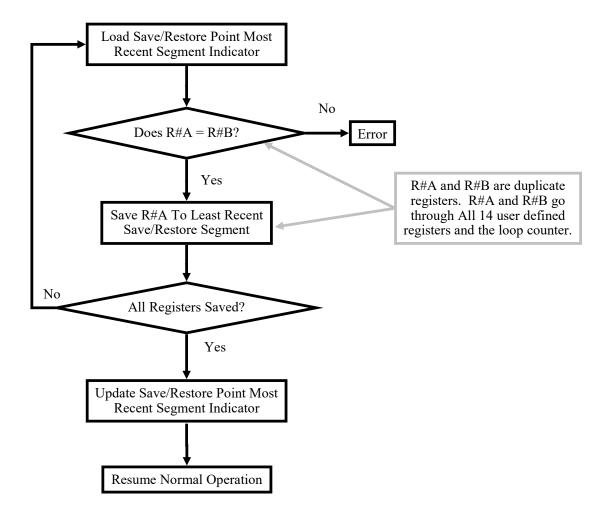

| 5      | TMR MIPS Type A Error Recovery Flow Chart                                                                     | 49   |

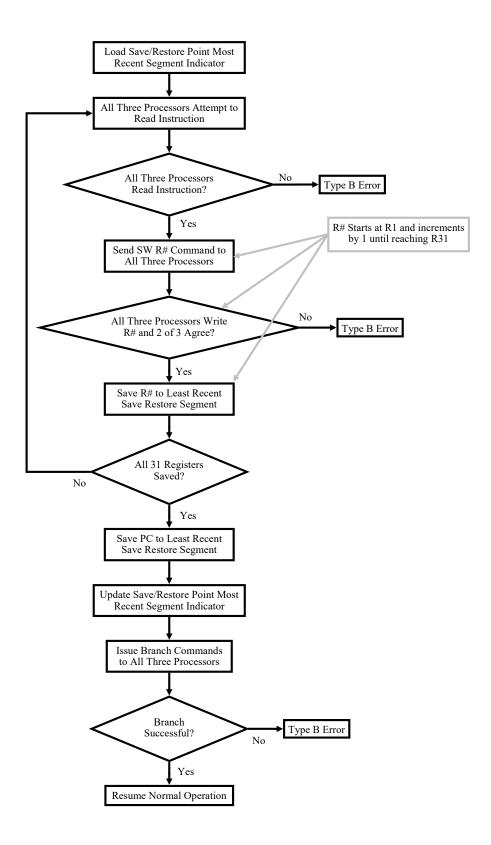

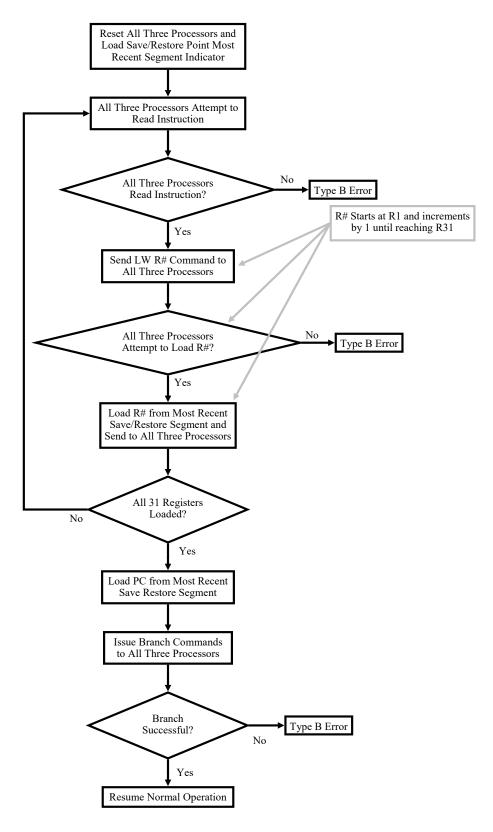

| 6      | TMR MIPS Save/Restore Point Creation Flow Chart                                                               | 51   |

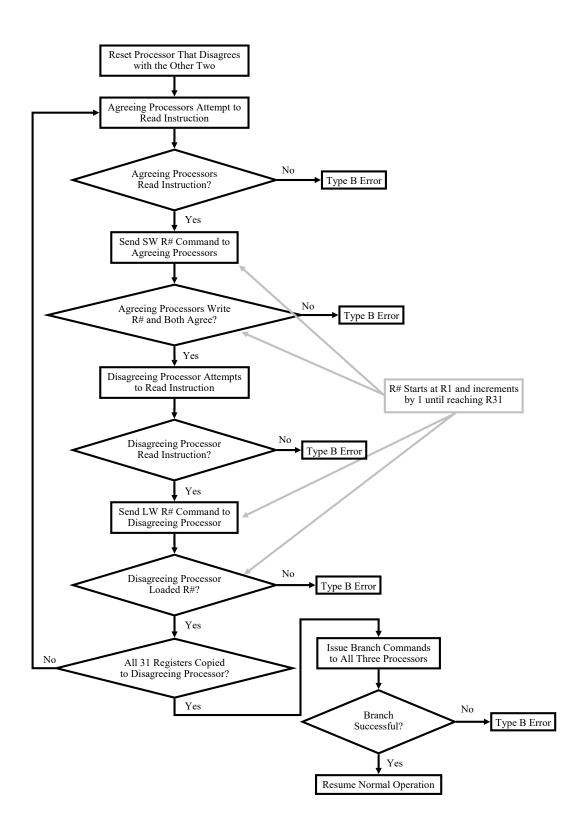

| 7      | TMR MIPS Type B Error Recovery Flow Chart                                                                     | 53   |

| 8      | TSR MIPS Save/Restore Point Creation Flow Chart                                                               | 61   |

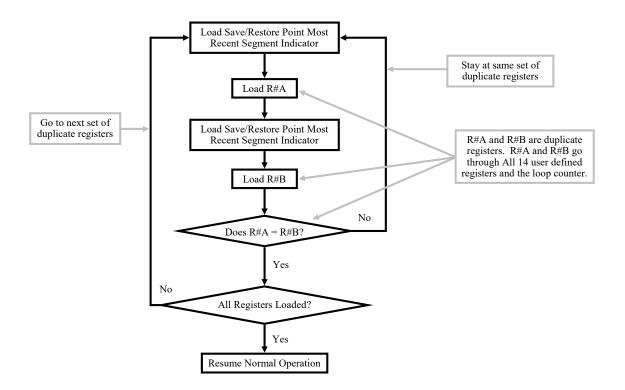

| 9      | TSR MIPS Error Recovery Flow Chart                                                                            | 63   |

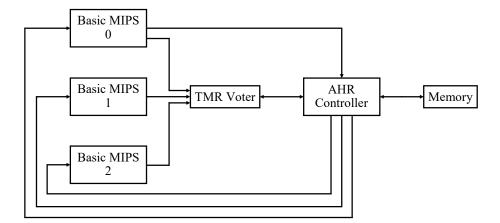

| 10     | AHR MIPS Simplified Block Diagram                                                                             | 72   |

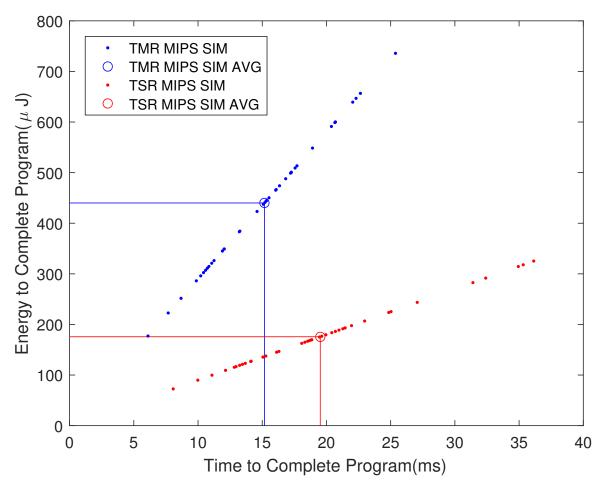

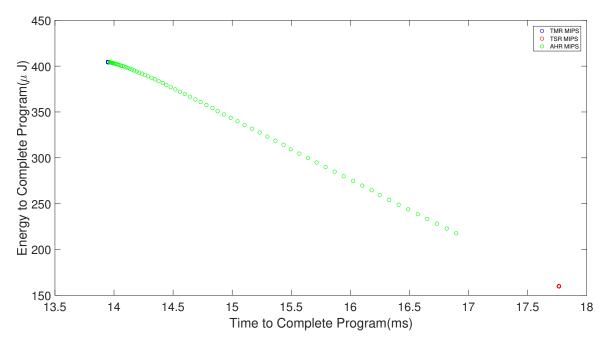

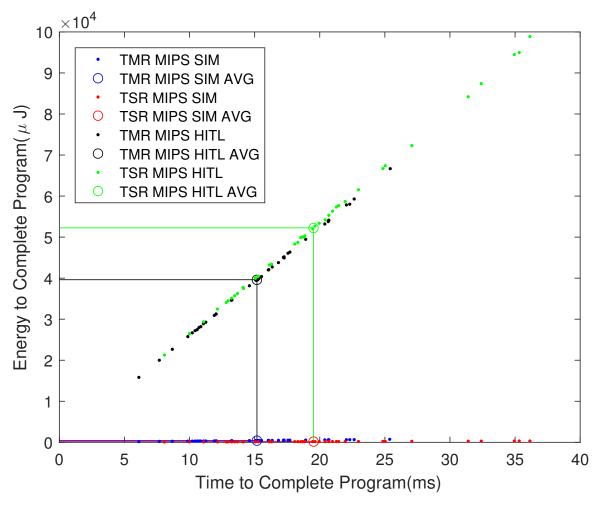

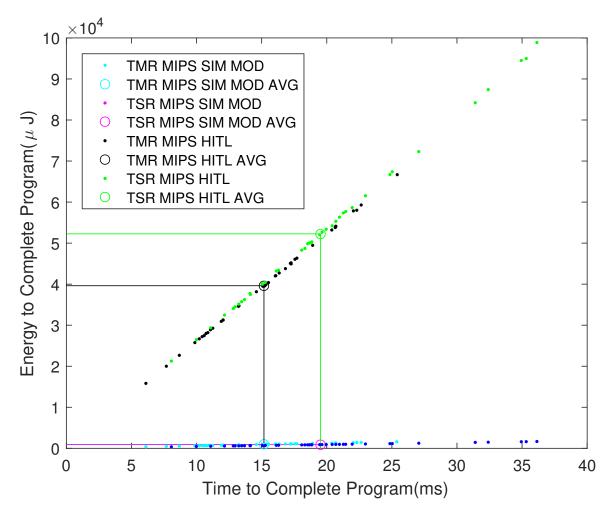

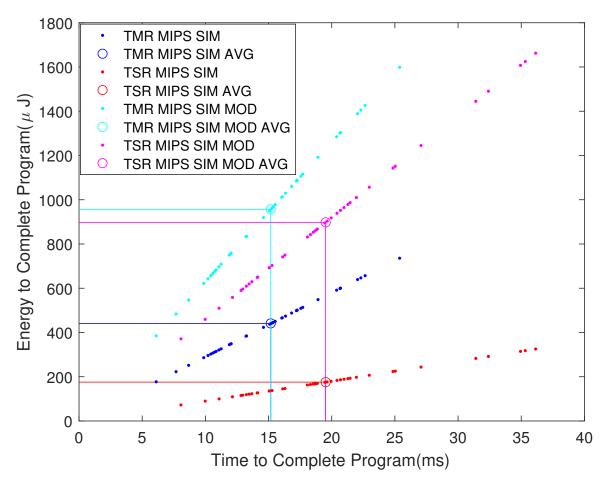

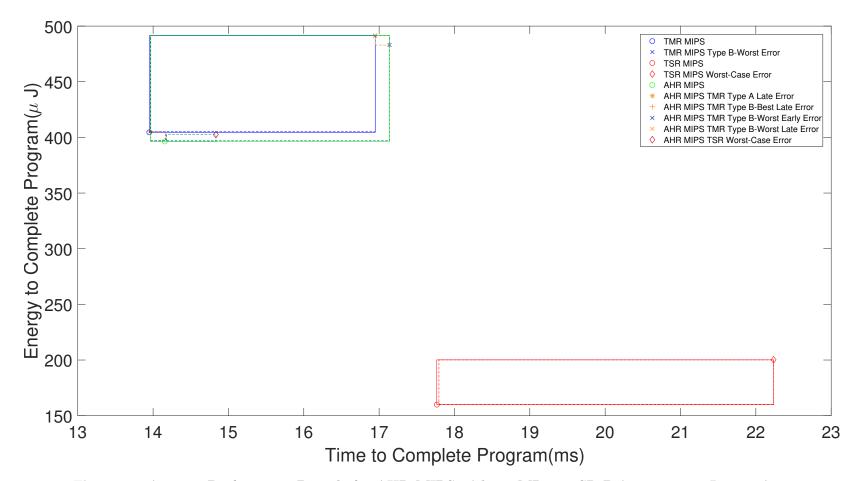

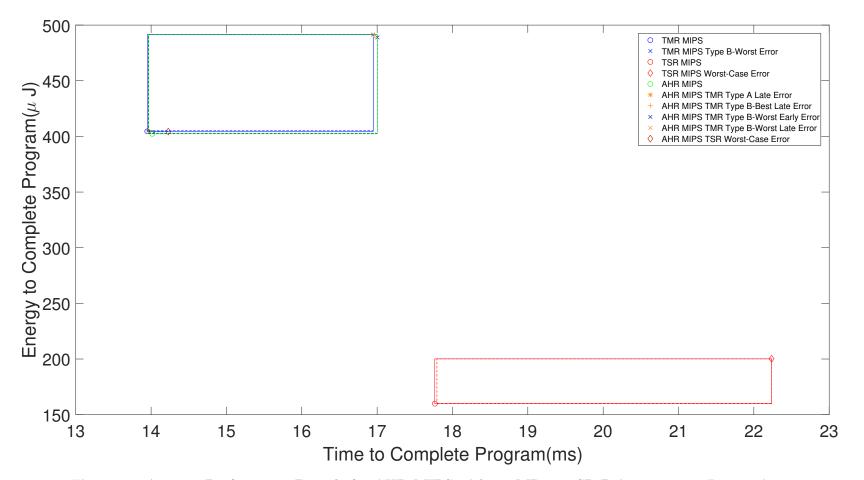

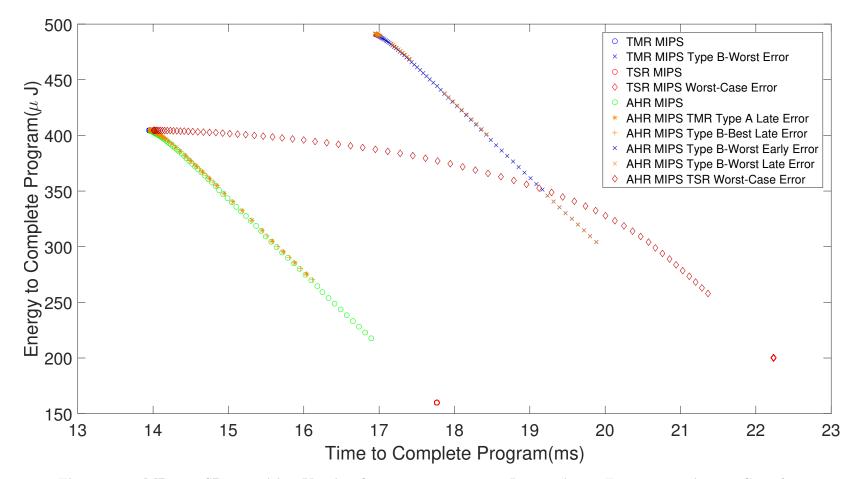

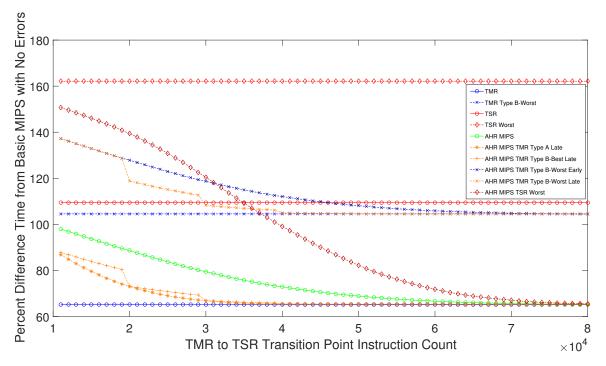

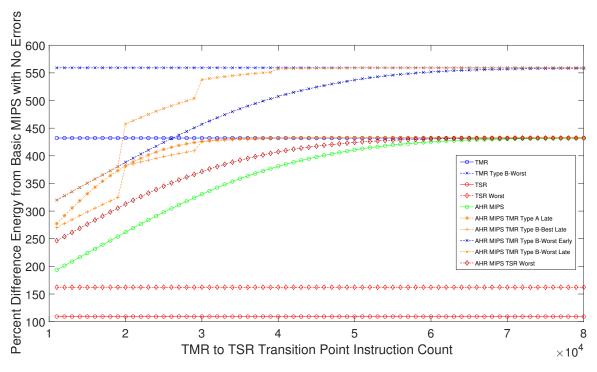

| 11     | First HITL Attempt Software Simulation Energy vs.<br>Time to Complete                                         | 93   |

| 12     | Error Free Software Simulation Energy vs. Time to<br>Complete                                                 | 94   |

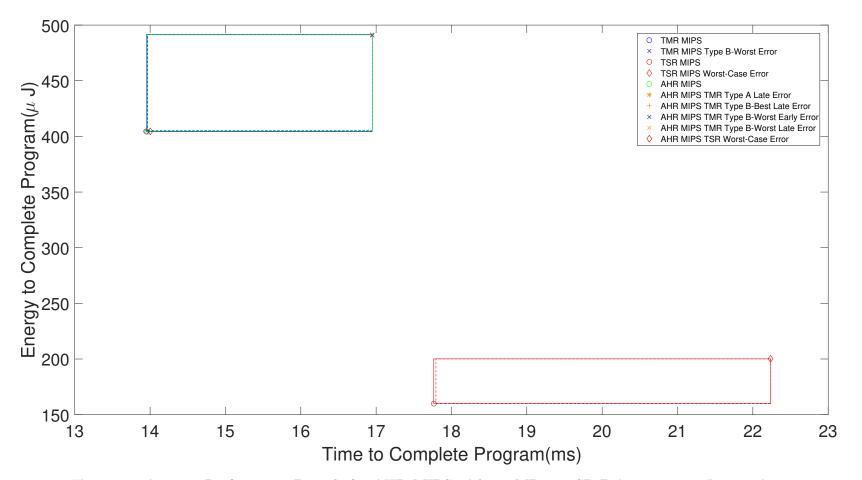

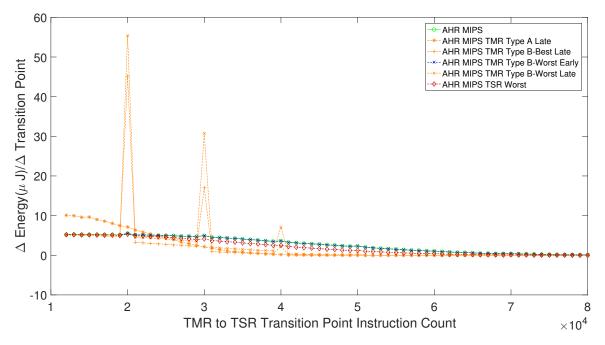

| 13     | AHR MIPS TMR to TSR Transition Varying from<br>11,000 to 80,000 Instructions - Energy vs. Time to<br>Complete | 98   |

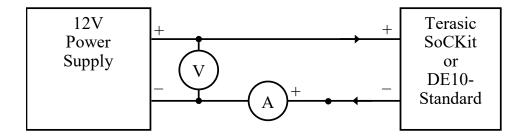

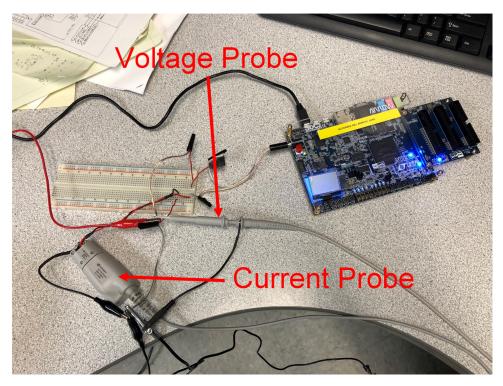

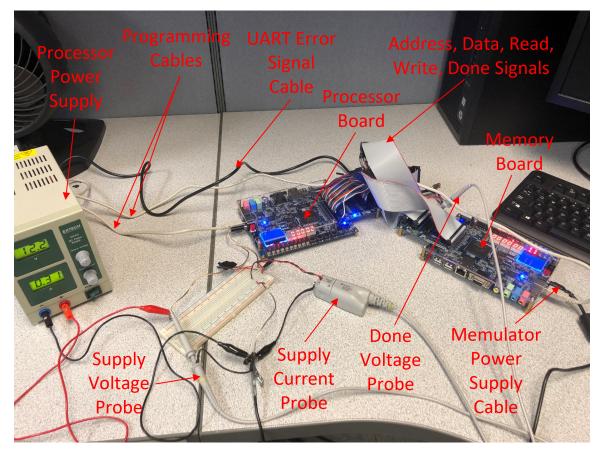

| 14     | HITL Simulation Current and Voltage Measurement<br>Setup                                                      | 99   |

| 15     | Voltage and Current Probe Connections                                                                         | 100  |

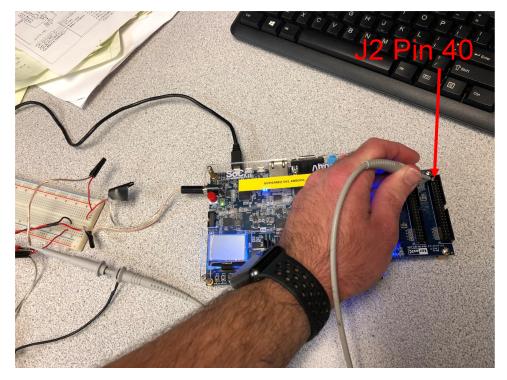

| 16     | DONE Signal Oscilloscope Connection                                                                           | 100  |

| 17     | First HITL Attempt Energy vs. Time to Complete                                                                | 106  |

| 18     | First HITL Attempt Energy vs. Time to Complete with<br>Updated Energy Estimates                               | 109  |

| 19     | First HITL Attempt Software Simulation Energy with<br>Updated Energy Estimates                                | 111  |

| Figure |                                                                                                                               | Page  |

|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 20     | HITL Attempt 2 Experimental Setup                                                                                             | . 115 |

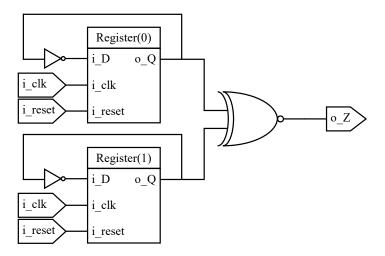

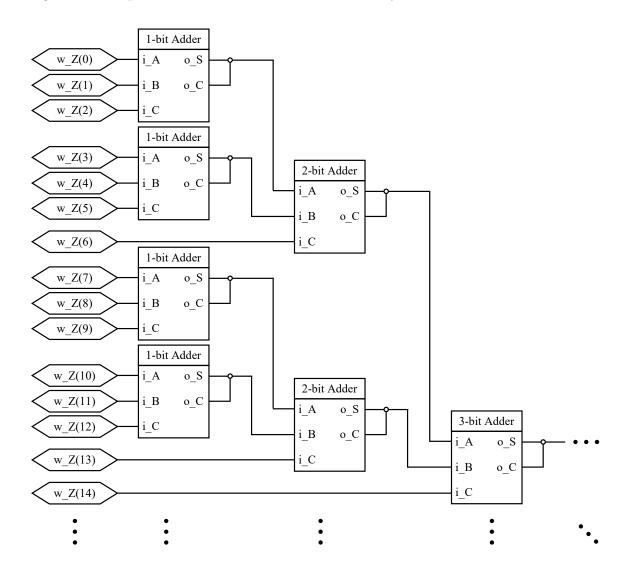

| 21     | Checkerboard Location Register Pair with XNOR Gate                                                                            | . 121 |

| 22     | Subset of Checkerboard Adder Network Showing First<br>Three Levels to Add Error Signals from the First 15<br>Memory Locations | . 122 |

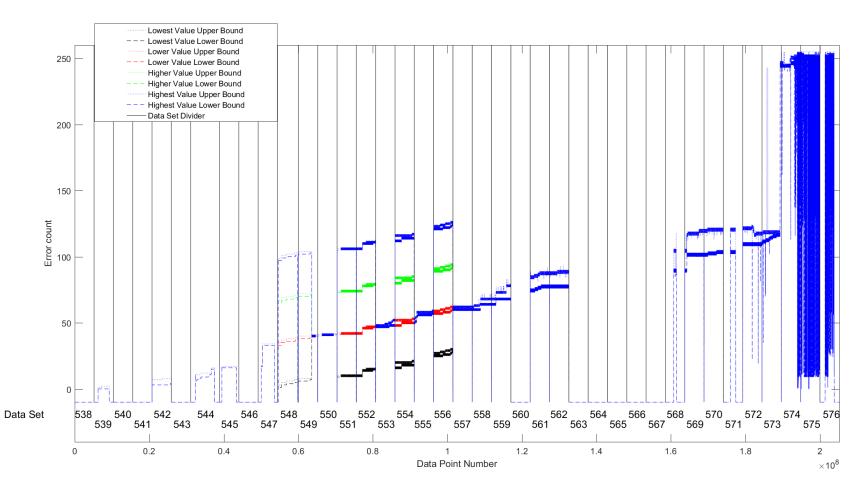

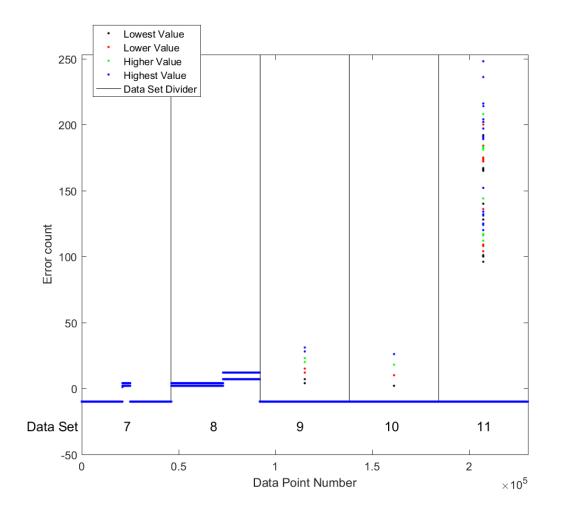

| 23     | Neutron Test 538-576                                                                                                          | . 130 |

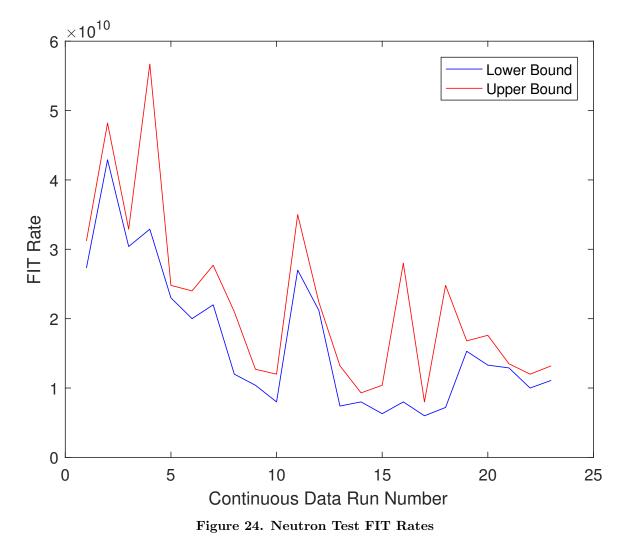

| 24     | Neutron Test FIT Rates                                                                                                        | . 133 |

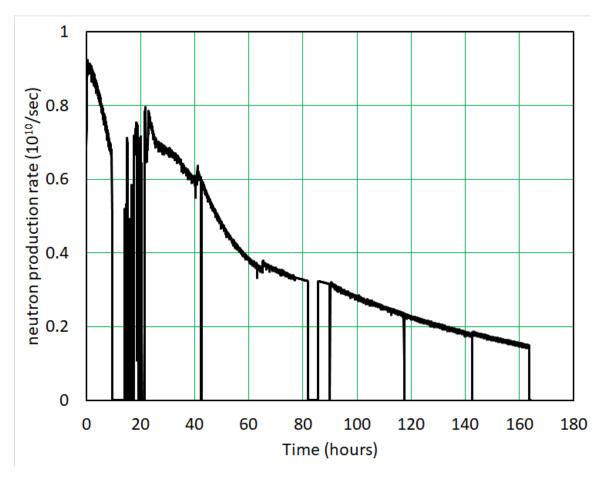

| 25     | Neutron Test - Neutron Production Rate                                                                                        | . 134 |

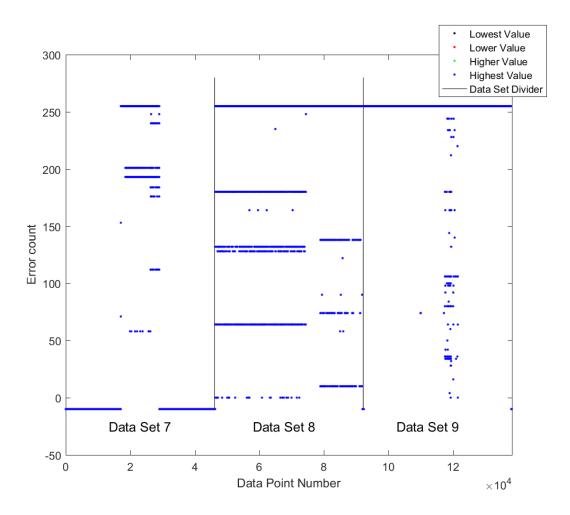

| 26     | Carbon Test One                                                                                                               | . 136 |

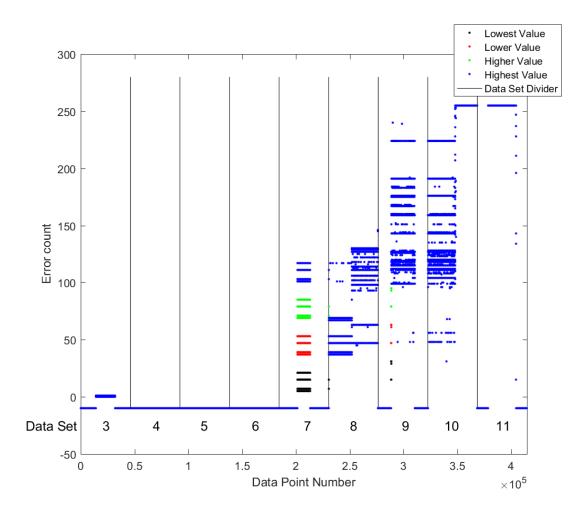

| 27     | Carbon Test Two                                                                                                               | . 137 |

| 28     | Carbon Test Three                                                                                                             | . 138 |

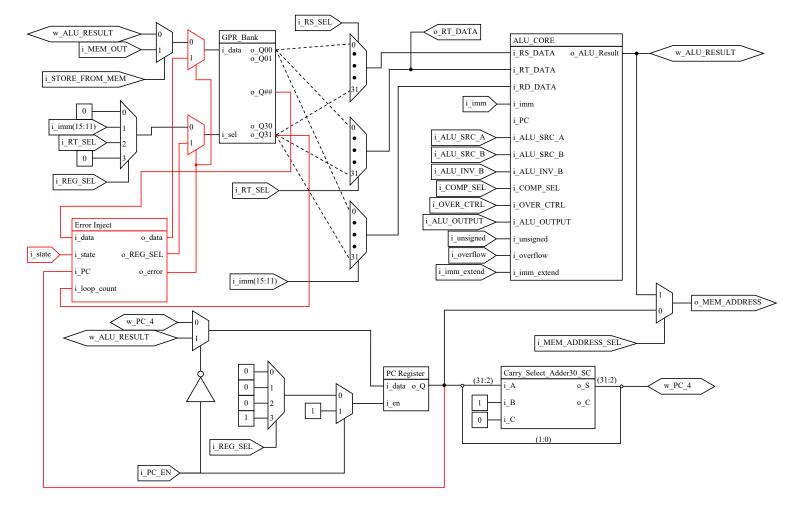

| 29     | Basic MIPS Datapath with Error Injection Schematic                                                                            | . 144 |

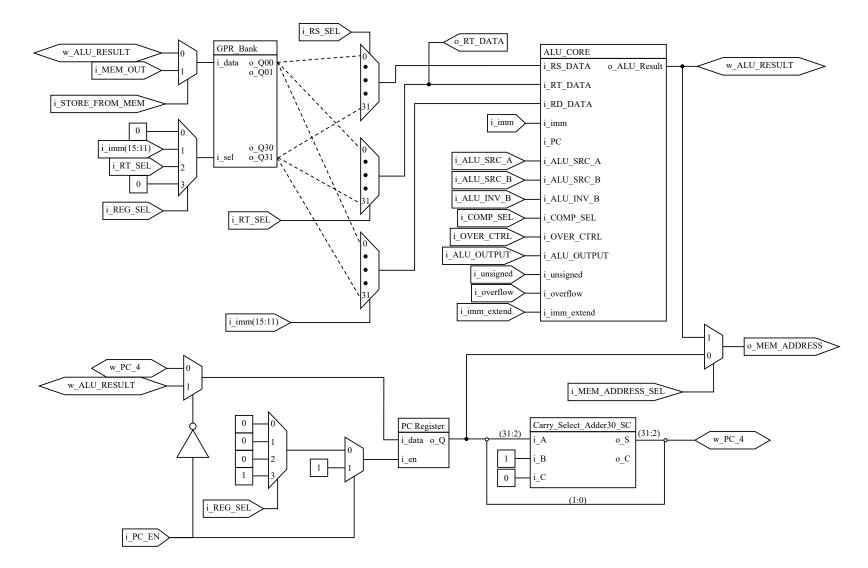

| 30     | Basic MIPS Datapath Schematic                                                                                                 | . 145 |

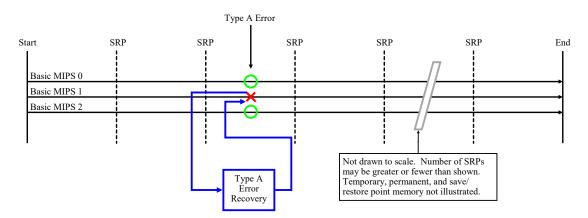

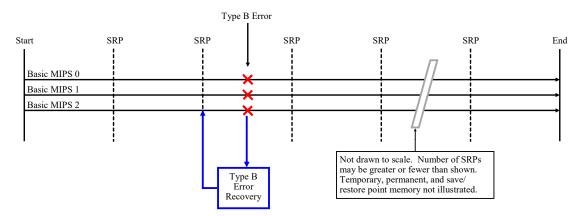

| 31     | TMR MIPS Type A Error Timing Diagram                                                                                          | . 147 |

| 32     | TMR MIPS Type B Error Timing Diagram                                                                                          | . 148 |

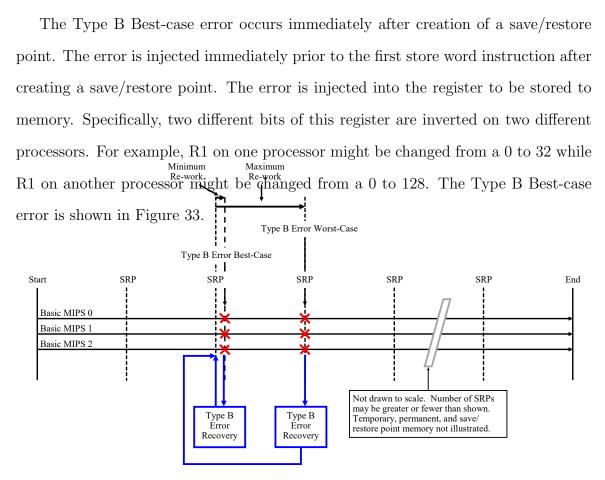

| 33     | TMR MIPS Type B Best- and Worst-Case Error         Timing Diagram                                                             | . 149 |

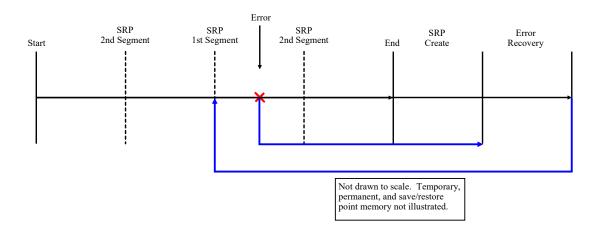

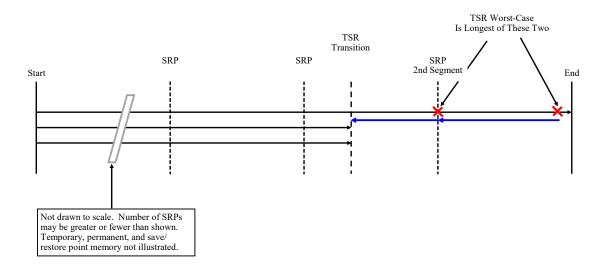

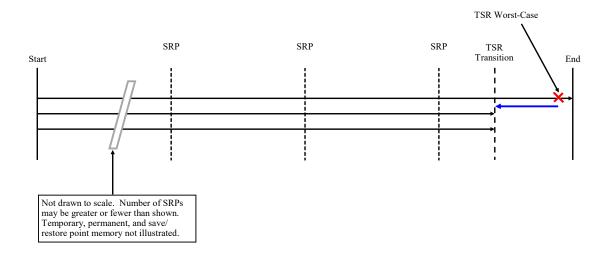

| 34     | TSR MIPS Error Timing Diagram                                                                                                 | . 156 |

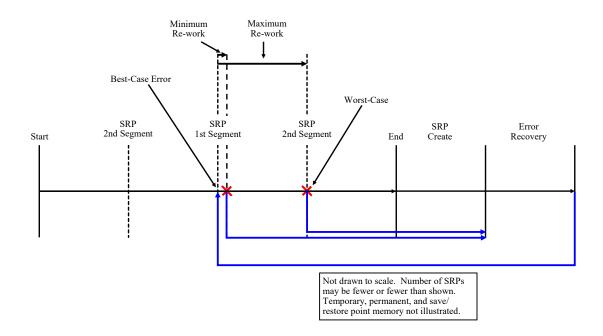

| 35     | TSR MIPS Best- and Worst-Case Error Timing Diagram                                                                            | . 157 |

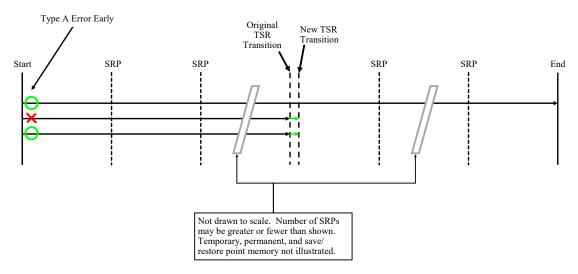

| 36     | AHR MIPS TMR Type A Early Error Timing Diagram                                                                                | . 160 |

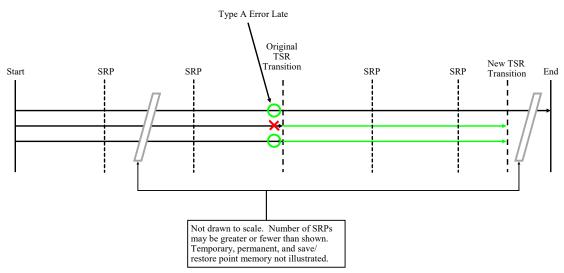

| 37     | AHR MIPS TMR Type A Late Error Timing Diagram                                                                                 | . 162 |

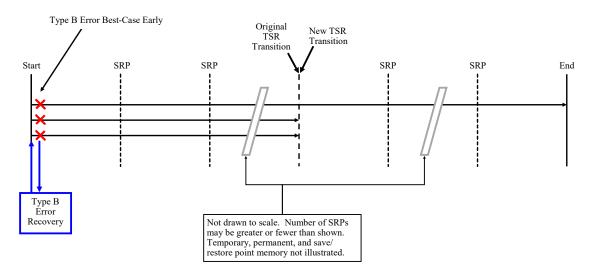

| 38     | AHR MIPS TMR Type B Best-Case Early Error<br>Timing Diagram                                                                   | . 164 |

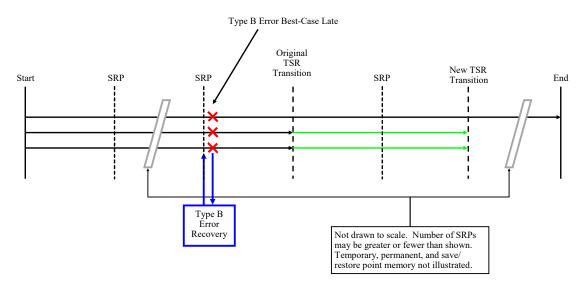

| 39     | AHR MIPS TMR Type B Best-Case Late Error Timing<br>Diagram                                                                    | . 165 |

## Figure

| 40 | AHR MIPS TMR Type B Worst-Case Early Error<br>Timing Diagram                              |

|----|-------------------------------------------------------------------------------------------|

| 41 | AHR MIPS TMR Type B Worst-Case Late Error<br>Timing Diagram                               |

| 42 | AHR MIPS TSR Best-Case Early Error Timing<br>Diagram 1                                    |

| 43 | AHR MIPS TSR Best-Case Early Error Timing      Diagram 2      181                         |

| 44 | AHR MIPS TSR Best-Case Early Error Timing      Diagram 3                                  |

| 45 | AHR MIPS TSR Best-Case Early Error Timing      Diagram 4                                  |

| 46 | AHR MIPS TSR Worst-Case Early Error Timing      Diagram 1      183                        |

| 47 | AHR MIPS TSR Worst-Case Early Error TimingDiagram 2184                                    |

| 48 | AHR MIPS TSR Worst-Case Early Error Timing      Diagram 3                                 |

| 49 | AHR MIPS TSR Worst-Case Early Error Timing      Diagram 4      185                        |

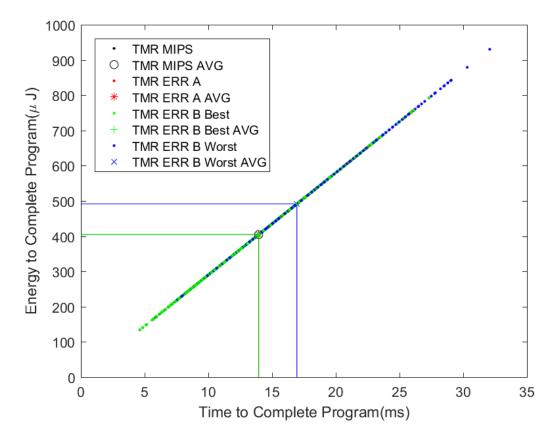

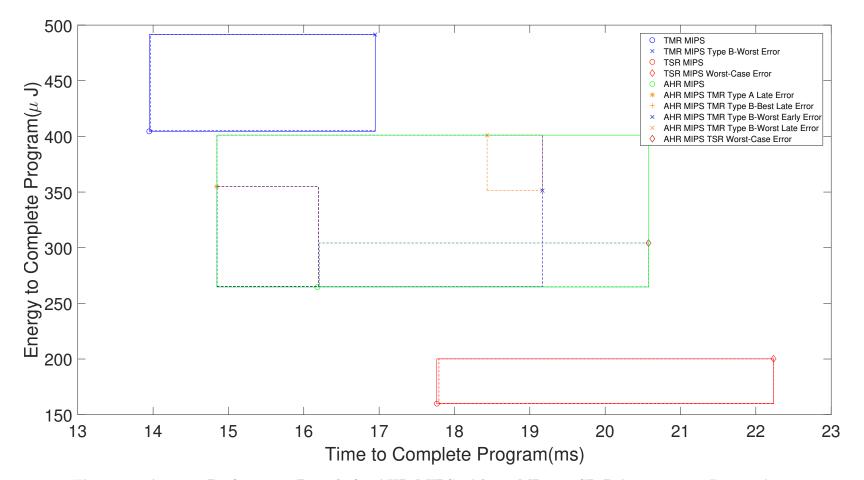

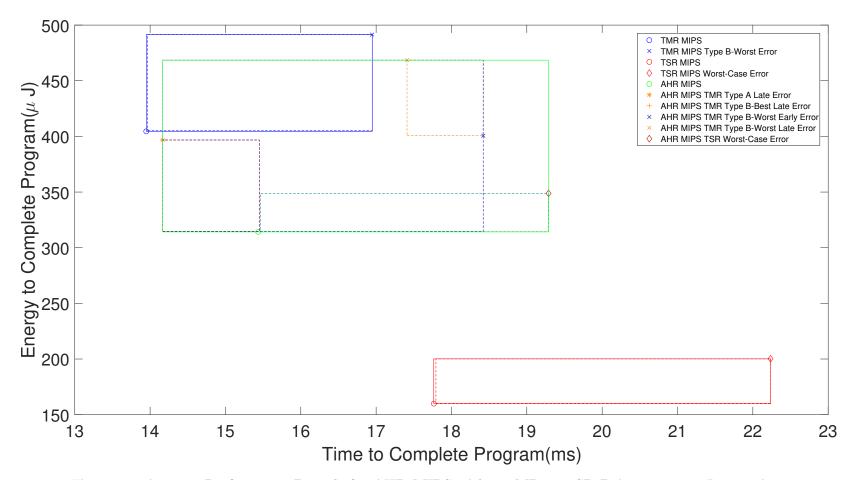

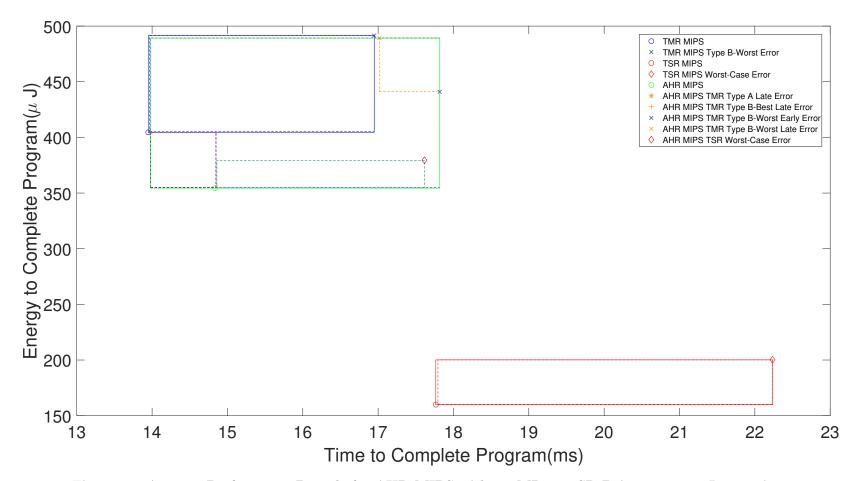

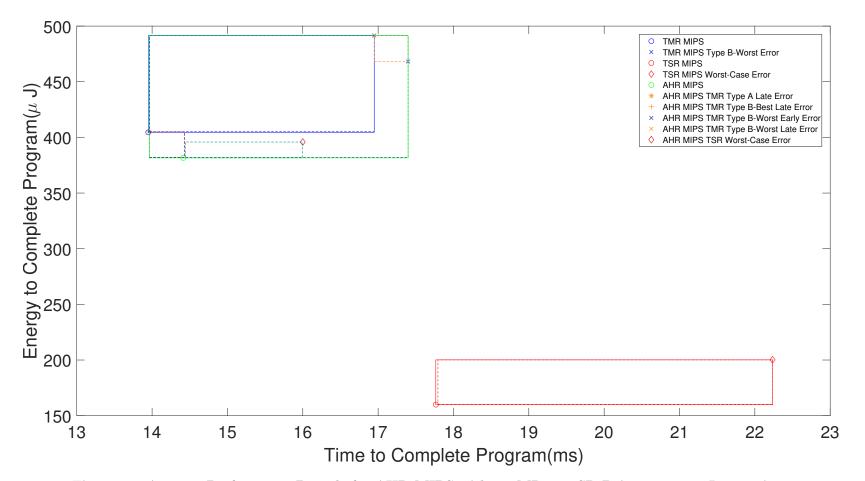

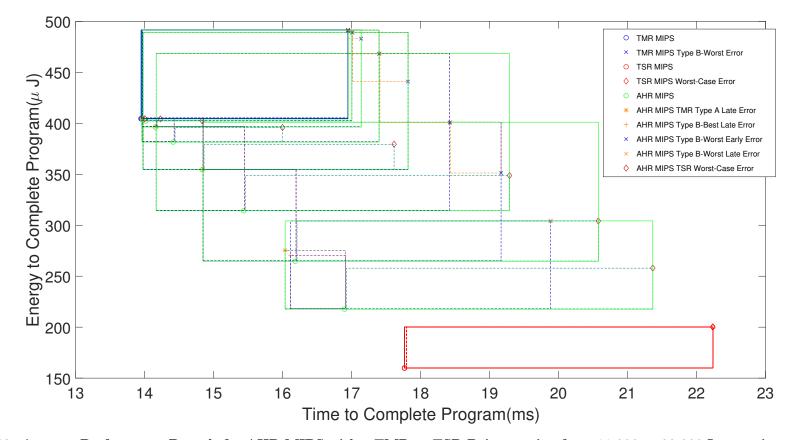

| 50 | Software Simulation of TMR MIPS Errors - Energy vs.<br>Time to Complete                   |

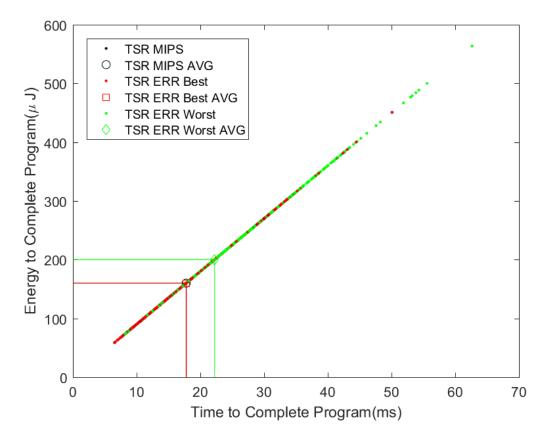

| 51 | Software Simulation of TSR MIPS Errors - Energy vs.<br>Time to Complete                   |

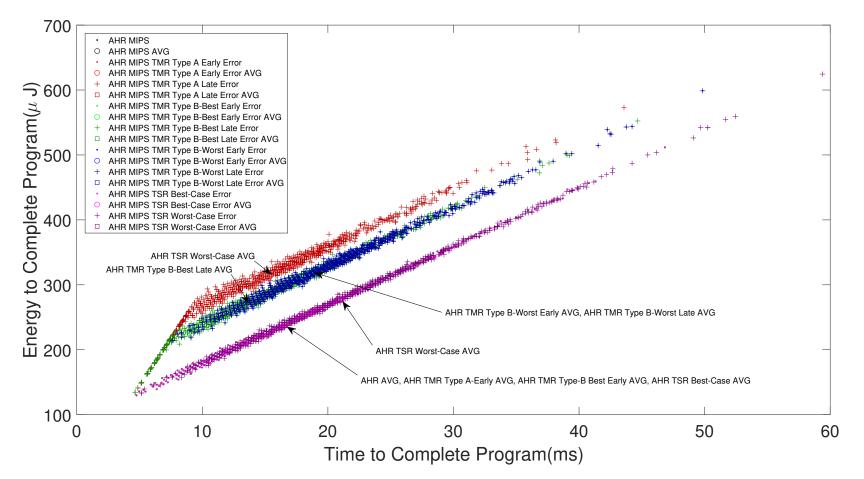

| 52 | Software Simulation of AHR MIPS Errors - Energy vs.<br>Time to Complete                   |

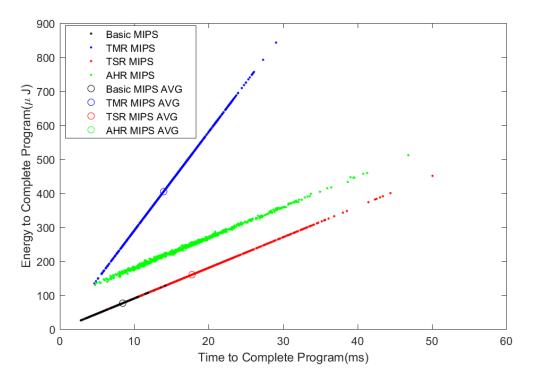

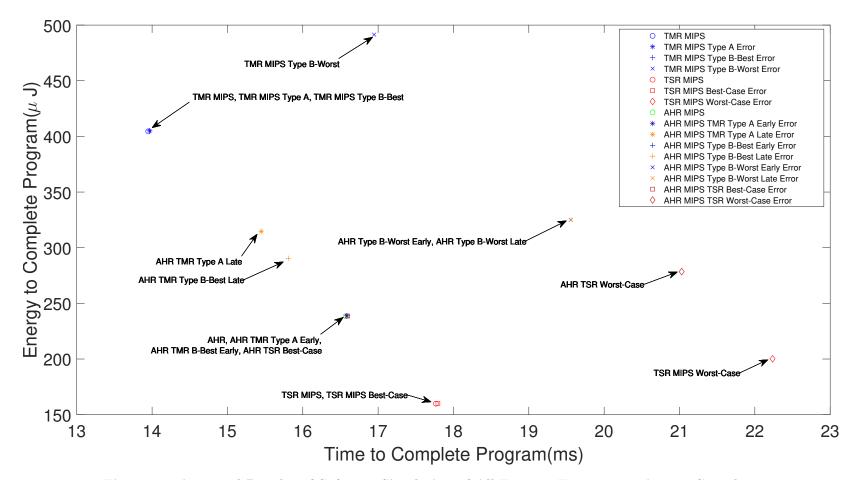

| 53 | Averaged Results of Software Simulation of All Errors -<br>Energy vs. Time to Complete    |

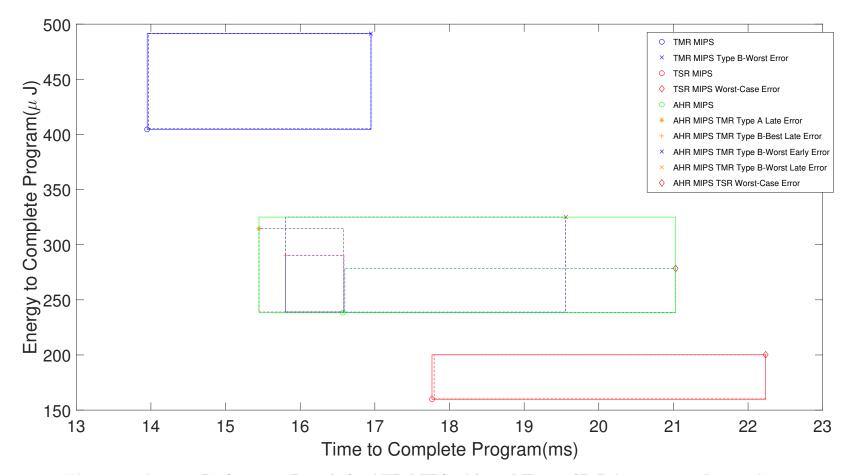

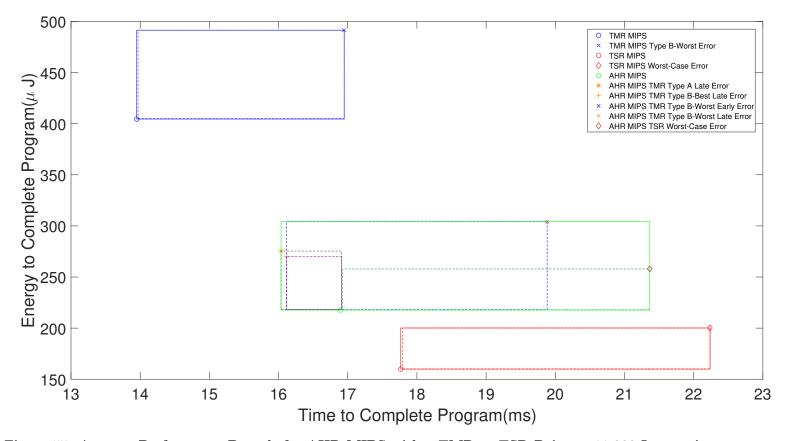

| 54 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 15,000 Instructions |

## Figure

| 55 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 11,000 Instructions                                            |

|----|--------------------------------------------------------------------------------------------------------------------------------------|

| 56 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 20,000 Instructions                                            |

| 57 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 30,000 Instructions                                            |

| 58 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 40,000 Instructions                                            |

| 59 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 50,000 Instructions                                            |

| 60 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 60,000 Instructions                                            |

| 61 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 70,000 Instructions                                            |

| 62 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point at 80,000 Instructions                                            |

| 63 | Average Performance Bounds for AHR MIPS with a<br>TMR to TSR Point varying from 11,000 to 80,000<br>Instructions                     |

| 64 | TMR to TSR Transition Varying from 11,000 to 80,000<br>Instructions - Energy vs. Time to Complete                                    |

| 65 | AHR MIPS TMR to TSR Transition Varying from11,000 to 80,000 Instructions - Energy vs. Time toComplete                                |

| 66 | AHR MIPS TMR to TSR Transition Varying from11,000 to 80,000 Instructions - Energy vs. Time toComplete                                |

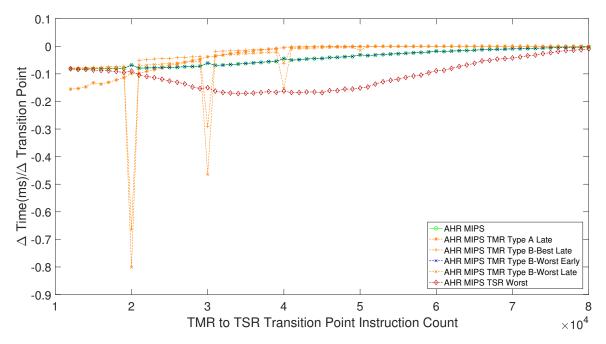

| 67 | Time Difference Between Successive Steps of TMR to<br>TSR Transition Point When Varying from 11,000 to<br>80,000 in Steps of 1,000   |

| 68 | Energy Difference Between Successive Steps of TMR to<br>TSR Transition Point When Varying from 11,000 to<br>80,000 in Steps of 1,000 |

| Figure |                                       | Page |

|--------|---------------------------------------|------|

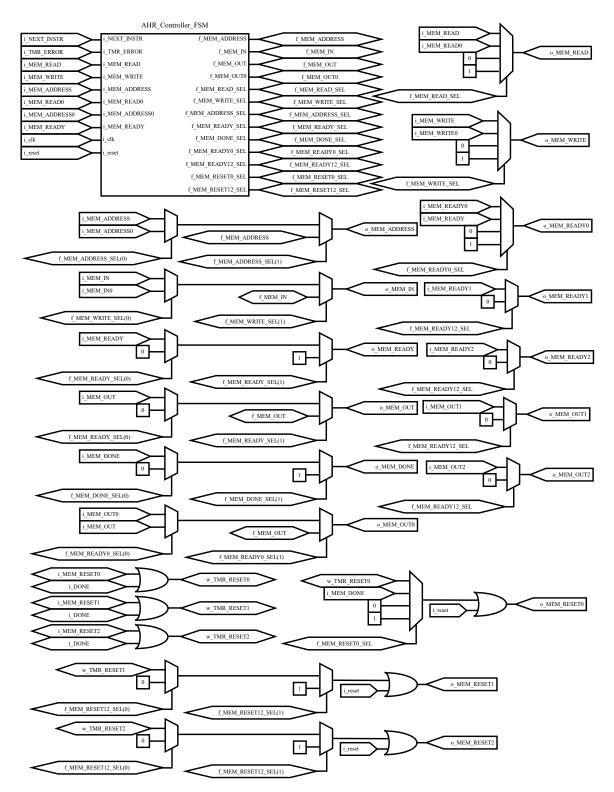

| 69     | AHR Controller Detailed Block Diagram | 236  |

| 70     | AHR MIPS Detailed Block Diagram       | 237  |

## List of Tables

| Table |                                                                                   | Page  |

|-------|-----------------------------------------------------------------------------------|-------|

| 1     | Simple Software Redundancy Example                                                | 21    |

| 2     | List of Implemented Basic MIPS Instructions                                       | 39    |

| 3     | Basic MIPS Code Example                                                           | 45    |

| 4     | TSR MIPS Code Example                                                             | 57    |

| 5     | TSR MIPS save/restore Point Creation Instructions<br>Example                      | 60    |

| 6     | TSR MIPS Error Recovery Code Example                                              | 64    |

| 7     | AHR MIPS Program Structure                                                        | 73    |

| 8     | Software Simulation Individual Instruction Timing<br>Results in Nanoseconds       | 89    |

| 9     | Software Simulation Key Timing Parameter Results in<br>Nanoseconds                | 91    |

| 10    | PowerPlay Results                                                                 | 92    |

| 11    | PowerPlay Results for Processor and Memulator<br>Together                         | . 108 |

| 12    | Memulator Error Codes                                                             | . 114 |

| 13    | TMR MIPS and TSR MIPS HITL Timing Results With<br>Error Injection for One Program | . 226 |

#### ADAPTIVE-HYBRID REDUNDANCY FOR RADIATION HARDENING

### I. Introduction

#### 1.1 Research Context

Space electronic components experience radiation effects at a much higher rate than terrestrial components, which are protected by the Earth's atmosphere. These effects disrupt low level computing elements in unpredictable ways and must be mitigated if the computed results are to be trusted. The typical approach is to apply some form of radiation hardening to the processors. However, this is a significant effort amortized over fewer processors, making these processors expensive. In addition, it takes years to develop a radiation hardened version of a processor, therefore a radiation hardened version of a state-of-the-art processor is necessarily two or more generations behind commercially available state-of-the-art processors.

Space data processing has traditionally been performed on the ground because of computing limitations; however, newer sensors generate significantly more data than current bandwidth limitations allow. As a result, space vehicle designers are interested in solutions to perform more processing on-board space vehicles.

Another consideration when using radiation hardened processors is that they typically use more power than their commercial counterparts, and when incorporated into a space vehicle, require the space vehicle to provide more power generation and energy storage in the form of larger solar panels and batteries. Larger solar panels and batteries directly increase the cost of the space vehicle. The added weight of the larger solar panels and batteries directly increase the vehicle's launch costs. Researchers and space vehicle designers seeking to increase space based processing capability and reduce power requirements, vehicle weight, and launch costs are turning to commercial-off-the-shelf (COTS) state-of-the-art processors and Field Programmable Gate Arrays (FPGAs). Rather than hardening these technologies directly, designers may be able to mitigate errors caused by radiation through on board redundancy. One way to accomplish this is by running multiple processors in parallel and using a voter to determine the correct output. Alternatively, redundancy could be incorporated in the software. These approaches are discussed in Chapter II.

The motivation for using these approaches is to field space systems sooner and at lower cost. This is especially true for United States Air Force satellites tasked with command, control, communications, computers, intelligence, surveillance, and reconnaissance (C4ISR) missions. The Air Force often designates these types of systems as being in the interest of national security and as such, follow the most stringent radiation hardening protocols. According to a 2014 article in Space News, GPS III satellites cost about \$547 million each [32]. If Air Force satellites could utilize COTS processors and FPGAs, the Air Force could potentially save millions of dollars on development and procurement of radiation hardened processors for future C4ISR and GPS satellites.

FPGAs and COTS processors share some advantages and disadvantages, but differ in others. One significant difference is that FPGAs can be reconfigured at any time, including after deployment. Both are susceptible to Single Event Upsets (SEUs) and Single Event Transients (SETs), though in slightly different ways. FPGAs are more vulnerable to SEUs which affect configuration memory. They are also vulnerable to SEUs and SETs affecting user logic. COTS processors are vulnerable to SEUs and SETs affecting their registers. FPGAs and COTS processors both suffer from Total Ionizing Dose (TID) and Enhanced Low Dose Rate Sensitivity (ELDRS) effects which cause permanent damage over time. This research does not examine the hardening techniques designed to mitigate TID and ELDRS, but instead focuses on SEU and SET mitigation. Furthermore, this research does not examine hardening through design changes at the transistor level or shielding of FPGAs and COTS processors but rather on redundancy.

FPGA SEU and SET vulnerabilities are minimized when implementing mitigation strategies such as internal scrubbing of configuration memory and user logic redundancy. COTS processors also utilize logic redundancy, but not internal scrubbing because they do not have configuration memory. This research focuses on mitigation strategies employing redundancy in much the same way as previous approaches discussed in Chapter II. The main difference between this research and previous research is that previous research typically implemented a single redundancy method which could not be changed once implemented on a space vehicle. This meant that the space vehicle was constrained to the power and performance penalties incurred by the redundancy method for the duration of its mission.

Two such redundancy methods are triple modular redundancy (TMR) and temporal software redundancy (TSR). Each redundancy method has its benefits and drawbacks. This research seeks to enhance the benefits and minimize the drawbacks by switching between redundancy techniques in real-time depending upon the radiation environment, processor loading, and energy consumption. This can be achieved by using a controller to switch between redundancy methods. This flexible form of redundancy is called Adaptive-Hybrid Redundancy (AHR) and provides satellite designers tradespace between energy consumption, and time to complete a processing task. The ability to switch between redundancy methods makes this approach adaptive while the use of both hardware and software redundancy methods makes it hybrid. The AHR processor proposed in this research switches between TMR and TSR.

#### 1.2 Assumptions

To maintain focus and scope, the following assumptions are made throughout the remainder of this dissertation.

- The only radiation effects considered are Single Event Upsets (SEUs) and Single Event Transients (SETs)

- (a) All other radiation effects do not occur

- (b) Multiple-bit upsets (MBUs) where a single radiation strike causes errors in two or more adjacent registers are highly unlikely and do not occur

- 2. The processor refers only to the Controller and Datapath of a processor

- (a) The Controller consists of a finite state machine with a state register, instruction register, and instruction decoding logic that translates instructions into control signals for the Datapath

- (b) The Datapath consists of general purpose registers (GPRs) that store data to be processed, a program counter (PC) register, logic to update the GPRs and PC register, an arithmetic logic unit (ALU) used to process data, and logic to control the disposition of processed data. The function of the Datapath is controlled by control signals from the Controller

- (c) Modern processors are typically super-scalar and make use of combinational logic and many additional registers for branch prediction and other applications. The additional combinational logic and registers used by super-scalar processors are also considered to be part of the processor

- 3. The processor and all components therein are subject to SEUs and SETs with few exceptions

- (a) The TMR Voter in TMR MIPS described in Section 3.3 is immune to errors

- (b) The AHR Controller in AHR MIPS described in Section 3.5.1 and the multiplexers used by the AHR Controller for signal routing described in Section 3.5.2 are immune to errors

- 4. Memory refers to the location where instructions and data are stored prior to being read by the processor. It is also the location where the processor may write data. In practical applications, this memory may be cached memory, random access memory (RAM), read only memory (ROM), a hard disk drive (HDD), or a solid-state drive (SSD)

- 5. Memory is immune to all errors

- (a) Memory hardening is not implemented in this research

- (b) Memory may be hardened by error correcting codes (ECCs), redundancy, shielding, or any combination of these methods

#### **1.3** Research Questions

This research seeks to answer the following questions:

- 1. Can multiple redundancy methods be incorporated into the redundancy design?

- 2. Is it possible to allow flexibility in redundancy methods for the duration of a space vehicle's lifetime?

- 3. Is it possible to switch between these methods based on mission needs?

4. What are the timing and energy tradespaces available to a designer, mission planner, or operator?

#### 1.4 Dissertation Organization

The remainder of this document is organized as follows. Chapter II provides background for this research. Chapter III develops the AHR architecture. Chapter IV evaluates AHR against TMR, TSR, and an unmitigated processor in a perfect environment with no errors present. Chapter V discusses how an error rate and error injection method were devised and mathematical tools were developed to evaluate the performance of AHR when compared to TMR and TSR when subjected to errors. Chapter VI presents the results of evaluating AHR against TMR and TSR when errors are injected. Chapter VII presents conclusions and contributions of this research as well as suggestions for future work.

### II. Background

#### 2.1 Introduction

This chapter lays the foundation for the development of Adaptive-Hybrid Redundancy (AHR). It begins with a discussion of radiation effects in Section 2.2 that delves into radiation effects known as Single Event Effects (SEEs) with an emphasis on Single Event Upsets (SEUs) and Single Event Transients (SETs). The discussion continues with the mitigation of those radiation effects in Section 2.3, which provides an overview of many mitigation strategies that have previously been applied in radiation environments. Section 2.4 examines a method for making comparisons between orbital radiation environments and experimental radiation environments with the goal of making a comparison between a particular flight experiment and an experiment performed in this research.

These first three sections are followed by a brief introduction to the hardware upon which AHR is implemented for this research in Section 2.5. Finally, Section 2.6 discusses previous methods to evaluate radiation vulnerability and redundancy techniques and leads to the selection of the evaluation methods used in this research.

#### 2.2 Single Event Effects

SEE is a broad term applied to effects caused by radiation striking a computer processor which have immediate impacts on the internal state and outputs. (In contrast, there are also effects caused by long term radiation exposure which do not immediately affect the internal state or output of the processor, which are also problematic, but outside the scope of this research.) While all SEEs have an immediate impact or effect, some impacts may be permanent, such as Single Event Gate Rupture (SEGR), Single Event Burnout (SEB), or Single Event Latchup (SEL). SEL can be corrected before device failure if a gate's power is cycled, but SEGR and SEB cannot be corrected this way. Still others are truly transient, but may have permanent computational or program effects if left unmitigated. These include the SET, SEU, and Single Event Functional Interrupt (SEFI) [17, 26, 65, 108]. Because they are more common, and because this research is primarily concerned with onboard mitigation techniques, this chapter will focus on SEUs and SETs; however, the related categories of SEGR, SEB, SEL, and SEFI are included to complete the discussion on SEEs.

#### 2.2.1 Permanent Single Event Effects

Both the SEGR and the SEB are caused when radiation strikes a transistor with sufficient energy to cause immediate and permanent failure. SEGR results from a failure of the insulating layer between the gate and depletion region of the transistor; which effectively destroys the gate. In contrast, SEB arises when radiation activates some parasitic component inherent in the chip. In each of these categories of radiation events, the effects are permanent and non-recoverable [26, 65].

#### 2.2.2 Semi-Permanent Single Event Effects

The mechanism causing Single Event Latchups (SELs) is distinct from the mechanism that causes SEGR, SEU, and SET, but somewhat similar to SEB. To better understand SELs, consider that some computer chip technologies make use of CMOS gates where the silicon comprising the gates are placed on top of a doped base material. This doped base material allows for the formation of parasitic P-N-P-N transistors between NMOS and PMOS transistors. In normal operation, these parasitic transistors are off, but a radiation strike has the potential to activate them. Once turned on, these parasitic transistors form a positive feedback loop that causes the parasitic transistors to draw more current. If the feedback loop is not broken, the logic gate could burn out and fail. Some CMOS technologies have current sensors that detect current spikes caused by SELs; then turn off power to the logic gate or a portion of the computer chip where the logic gate is located. Turning off the power stops the positive feedback loop and prevents the SEL from becoming destructive. Power is then restored and normal operation resumes. SELs can also be prevented by using silicon on insulator CMOS technology or other means of isolating NMOS and PMOS transistors so that parasitic transistors cannot form [26, 65, 108].

Single Event Functional Interrupts (SEFIs) can be the result of SETs that are stored in registers and SEUs that propagate throughout a computer processor over several clock cycles. The propagated errors influence various intermediate and final results that the processor is tasked with computing. They may also affect the flow of a program that is running on a processor if that program contains any branch or jump instructions that are impacted by SEU and SET propagation. SEFIs may also occur when radiation triggers a built-in-self-test mode or a reset of a processor [17, 26, 65, 108].

#### 2.2.3 Transient Single Event Effects

Single Event Transients (SETs) are caused when ionizing radiation produces a voltage and current pulse in a transistor. That pulse has the capability to propagate energy through neighboring combinational logic. The pulse may travel through several, or only a few gates, depending upon a number of factors. First, the pulse may be attenuated or amplified depending upon the parameters of the gates through which the pulse passes (i.e., length, width, depth, doping concentrations, type of gate, etc.). Second, the pulse may be logically masked, which can occur when a logic 1 pulse encounters an AND gate where another signal is a logic 0. Because both inputs would have to be a logical 1 for the output to change, the erroneous logic 1 pulse has no further effect. Third, the pulse may be temporally masked; this can occur when a pulse reaches the input to a memory element, such as a register or flip-flop, but does not arrive with sufficient voltage and duration during the memory element's setup and hold time. On the other hand, if the pulse is not masked, it may be stored in one or more registers, and will likely result in incorrect computation [4, 5, 15, 24, 26, 41, 60, 65, 81, 89, 90, 108].

Single Event Upsets (SEUs) are caused when ionizing radiation strikes a transistor that is part of a memory element with sufficient charge to directly flip that memory element. In other words, the radiation causes a memory element storing a logic 0 to store a logic 1 or vice versa [8, 16, 17, 26, 33, 65, 105, 108]. While this is a problem generally, SEUs can be particularly bothersome for Field Programmable Gate Arrays (FPGAs). FPGAs often utilize SRAM cells in their configuration memory to instantiate a user design. They govern the routing of signals as well as the implementation of specific logic functions. Beyond merely changing the value of an operand, configuration memory SEUs can alter the users desired functional logic and even create short circuits. At a minimum, these errors have the potential to prevent the FPGA from accomplishing its designed task. In extreme cases, configuration logic SEUs may permanently damage the FPGA.

#### 2.3 Mitigating SEUs and SETs

There are numerous methods through which SEUs and SETs may be mitigated. These include shielding, hardware modifications, software modifications, and redundancy.

Hardening can be achieved through physical shielding at the circuit level, system level, and various levels in between. The ability to shield at various levels depends on how much is known about the layout of a processor. Shielding could be applied to specific critical circuits like power transistors that ensure proper power distribution or transistors tasked with clock distribution; however, specific circuit shielding only works if the exact physical locations of circuits are known. Shielding can also be applied to an entire processor by placing metal over the processor. Physical shielding is not within the scope of this research as this research focuses on hardening through redundancy.

Hardware modifications, software modifications, and redundancy for SEU and SET mitigation are further discussed. These modifications can be divided into two distinct levels. The first is circuit level hardening and the second is system level hardening. At the circuit level, hardening is achieved by making changes to transistors or adding components to combinational logic and memory elements. System level hardening is achieved through redundancy of components at the logic gate level, system level, or any level in between. System level hardening may also be achieved through software redundancy. Circuit level hardening is discussed first, then system level hardening.

#### 2.3.1 Circuit Level Hardening

Some methods of circuit level radiation hardening make changes to the material properties of the transistor. Hughes et al. discuss a radiation hardened gate made of heavily doped n-type silicon where they built and tested gates before and after irradiation and demonstrated positive results [43]. Uemura et al. make changes to the transistors' physical dimensions and also create cancellation regions between transistors to "cancel out" trapped charges that would otherwise cause a multi-node upset. They also discuss the use of triple well versus double well technologies in their mitigation approach [102].

Other methods of circuit level radiation hardening require changes to the circuitry

comprising combinational logic and the memory cells. One such modification is the introduction of a special filter into combinational logic to mitigate SETs. These filters prevent short pulses from passing, but allow longer pulses to pass [82]. This effectively eliminates radiation induced pulses while permitting desired signals to pass. Filters can also be added in memory elements to prevent bit flips caused by SEUs. Filters can be composed of delays created by inverter chains coupled with a guard gate or a simpler filter comprised of resistors and/or capacitors [3, 17, 29, 64, 82, 85]. Another modification changes the structure of memory elements to mitigate SEUs. One example modification of the simple SRAM cell is the Dual Interlocked storage Cell (DICE) [11], which effectively blocks transient pulses from causing upsets to the memory cell. Another SRAM cell modification, called the Soft Error Interception Latch [47], implements multiple delay elements and gates to stop any pulses from propagating and causing an upset to the memory cell. Unfortunately, adding filters and changing the basic structure of the SRAM cell unavoidably require costly and time consuming processor redesign as well as changes to the fabrication process. The addition of filters also typically cause an increase in the amount of time required to store a value to the SRAM cell.

#### 2.3.2 System Level Hardening

System level hardening through redundancy can be achieved in hardware, software, or a hybrid of hardware and software. Hardware redundancy can take place at the gate level, the processor level, or somewhere in between. Hardware redundancy may use multiple copies of specific circuits or subcircuits where inputs are driven by a single source and outputs can be compared to determine the correct result for that circuit. Hardware redundancy may also employ error correcting codes in various stages. Some hardware redundancy strategies make use of both, and they are further discussed in the subsections on Hardware Redundancy and Hybrid Redundancy. Software redundancy typically performs a single instruction on a processor multiple times and compares the results of each iteration to determine the correct result to forward to the next stage. Hybrid designs make use of both hardware and software redundancy; some designs will place more emphasis on the hardware or software while others will utilize both equally. The following pages provide specific examples of various hardware, software, and hybrid redundancy strategies.

#### 2.3.2.1 Hardware Redundancy

Multiple Copies of Circuits or Subcircuits This section discusses some examples of hardware redundancy where there are multiple copies of circuits or subcircuits.

The first example is of redundant registers to store the processor's state. The processor's state consists of all user defined registers, the program counter, and the instruction register. The registers are assumed to be radiation hardened and immune to SEUs while the processor's combinational logic is vulnerable to SETs. At any given time, the current state is being written to one set of the redundant registers while the other set of registers stores the previous state. If a SET occurs, it may impact the set of registers to which the processor is currently writing data. The SET can be detected by the processor, which is able to continue processing using the set of registers that hold the previous state. The set of registers which were potentially impacted by the SET are then overwritten when the processor processes the data from the previous state and stores the updated state [34].

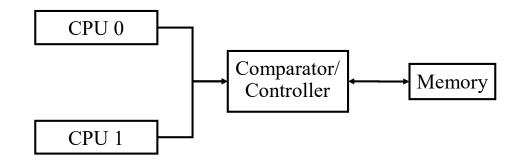

The second example illustrates the use of dual modular redundancy (DMR). DMR makes use of two processors and a single comparator/controller. Both processors run in lockstep (meaning that they simultaneously receive identical inputs, including the

clock) and produce outputs that are checked by the comparator. The controller periodically interrupts the two processors to create a save/restore point in memory that saves the processor's internal state at a particular moment in time. If the two processors ever disagree on their outputs, the comparator/controller can then go back by restoring the internal state of both processors to the most recent save/restore point. (This approach assumes that the save/restore point is saved in radiation hardened memory [20, 22, 27].) In some implementations, the two processors are implemented differently (i.e. two different chips from the same manufacturer or different manufacturers), but designed to produce identical results [95]. Figure 1 provides a simple illustration of DMR.

Figure 1. Dual Modular Redundancy Simplified Block Diagram

A different method of DMR makes use of two processors that do not run in lockstep. In this example, two cores of a four core processor are utilized such that one core runs a program and the second core runs the same program, but a fixed number of instructions behind the first core. The first core provides values loaded from memory to the second core so the second core does not have to load them from memory. The first core also provides the second core the outcome of its branch decisions. The second core compares the address information provided by the first core to its own as well as the first core's branch outcomes to its own branch decisions to determine if an error has occurred. In the event that the program needs to store data to memory, the store only occurs after the second core processes the store instruction and determines that the address and data to be written to memory match those of the first core [30].

Another approach uses two processors, similar to DMR, but only one processor runs the program while the second processor acts as a watchdog to detect errors. The watchdog monitors the main processor's inputs and outputs to detect errors in the flow of the program and the data being written to memory [58]. While the watchdog approach cannot detect every error that DMR detects, it is able to detect errors at a lower cost in terms of size of the second processor and power used by the second processor. In one particular watchdog approach, signatures are embedded into the program so the watchdog can determine whether the program flows correctly (i.e. ensures no illegal/incorrect program branches are taken). The main processor is designed to ignore the embedded signatures while the watchdog processor compares the embedded signatures to the ones it computes in real time [72].

The next example uses Triple Modular Redundancy (TMR) at a low level. An ARM Cortex-R4 processor was modified such that all flip-flops were replaced with three copies of the same flip-flop, followed by a voter. Different delay elements were added at the inputs to the flip-flops to reduce the probability of a SET causing more than one of the three flip-flops to store an erroneous value [74].

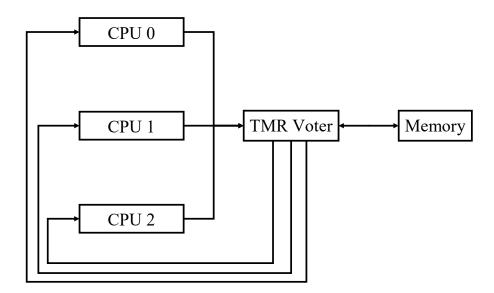

In another TMR example, TMR is implemented at the system level. In this configuration, three copies of the same processor operate on the same inputs and their outputs are examined by a voting circuit. All three processors produce the same outputs when there are no errors. If the output of one of the three processors differs, it is assumed to have encountered an error, and the correct output is determined by majority vote. The voter circuity resets the "incorrect" processor and sets the processor's internal state to match the internal state of the two correct processors. If all three processors disagree on the output (i.e. no majority exists), the voter resets all three processors and restores them to a previously saved internal state (the TMR restoration process is identical to the DMR restoration process). This approach also assumes that the save/restore point is saved in radiation hardened memory [6, 7, 10, 45]. TMR is such a commonly used mitigation technique that some FPGA manufacturers incorporate TMR into their hardware documentation as a means to harden their processors [12]. TMR is considered the "gold standard" by the U.S. Air Force for protecting electronics aboard spacecraft and launch vehicles. Figure 2 provides a simple illustration of TMR. This research uses this TMR approach in the development of Adaptive-Hybrid Redundancy (AHR). This is the simplest of the TMR approaches presented in this chapter, which makes it an ideal candidate for evaluating AHR. TMR is selected over DMR because TMR is considered the "gold standard" for U.S. Air Force space systems.

Figure 2. TMR MIPS Simplified Block Diagram

While full TMR is very effective, it is also costly in terms of energy. The next TMR approaches described are more energy conscious. In one approach, TMR is only implemented when radiation levels exceed some threshold, as measured by an external radiation sensor. However, when radiation levels are below the threshold, a single processor is used, thereby minimizing power consumption [55]. In other approaches, TMR is selectively implemented for critical subcircuits on an FPGA or critical processors in a larger computer system rather than implementing TMR for every subcircuit or an entire processor. [31, 91]. These approaches reduce power consumption as fewer components are triplicated.

Another TMR approach has no independent voting circuitry. In this example, all three processors compare the outputs of the other two processors to their own outputs to detect errors. Upon detecting an error, the processors execute exception handling code. One of the processors is designated as the "master" processor, and when an error occurs, the first processor to complete error handling becomes the master and reboots the other two. If the new master fails to correctly reboot the other two processors, the next processor to finish exception handling detects this and becomes the master and reboots the other two processors. The "master" processor loads its own internal state into the two rebooted processors to ensure all three processors have the same internal state before resuming normal operations [56].

Hardware redundancy may also be achieved by using TMR and NMR (N-Modular Redundancy) systems where permanently failed processors are replaced with spares. NMR is like TMR where there are N processors rather than three processors and outputs are decided by majority vote. Replacements are needed when a processor fails due to Total ionizing Dose (TID), Enhanced Low Dose Rate Sensitivity (ELDRS), SEB, SEGR, SEL, or some other permanent damage. In this way, a TMR system can continue with three functioning processors or an NMR system with N functioning processors even after a permanent failure. As in the previous TMR with voting example, temporary faults are corrected by copying the system state of the correct processors to faulty processors [87].

Another NMR system uses a total of four processors where two processors are on one FPGA and two processors are on another FPGA. All four processors receive the same inputs. The outputs of the two processors on the same FPGA are compared. Next, the output of the two FPGAs are compared. At this stage, processors in error are identified. Because the number of processors is even, if one pair of processors reach one result and another pair of processors reaches a different result, error recovery must follow the same approach as if all processors are in error as discussed for TMR. If two processors agree on a result and the other two processors have differing results, the two that agree are assumed to be correct and the internal states of the other two processors are corrected to match the internal states of the correct processors [21, 94]. Yet another distinct approach is halfway between DMR and TMR. In this approach, two "main" processors proceed in lockstep, periodically saving checkpoints, until an error occurs at a checkpoint. The two main processors proceed to another checkpoint after the one at which the error occurred while a third processor starts from a prior, error-free checkpoint. The third processor proceeds past the checkpoint at which the error occurred and catches up with the main processors at the following checkpoint. All three processors are compared and the erroneous processor can be identified and corrected if the third processor matches one of the main processors. The third processor is turned off after this checkpoint. If there is no agreement between the third processor and the main processors at this checkpoint, the main processors are restored to the last error-free checkpoint [75].

**Error Correcting Codes** Error correcting codes (ECCs) began with simple parity bits; these bits indicated whether there were an even or odd number of logic 1s in a byte or other grouping of bits (i.e. 16-bit half-word, 32-bit word, and etc.). Unfortunately, parity bits can only detect when an odd number of bits are in error. If there are an even number of errors, the errors go undetected. Additionally, the number of errors and the location of the error or errors is unknown [10]. Newer ECCs incorporate multiple bits such that the number of errors and location of the errors is precisely known.

The most common ECCs can detect and locate two errors while being able to correct a single error through the use of combinational logic. These codes are commonly referred to as single error correcting-dual error detecting (SEC-DED) codes [10, 54, 93] Some of these codes can be expanded to detect and correct more errors.

Other ECCs are designed to survive addition and multiplication operations. These codes include AN (cyclic code with ring of integers modulo  $2^n - 1$  for some n), Bose-Chaudhuri-Hocquengham (BCH) codes, Modified Reflected Binary (MRB) code, number theoretic transforms, and residue codes [10, 19, 40, 48, 52, 53, 54, 76].

While ECCs are more commonly used to protect memory, they may also be used to protect registers in a processor. In one example, ECCs were used to only protect the most vulnerable registers while parity bits were used to detect errors in the remaining registers [50].

## 2.3.2.2 Software Redundancy

Redundancy achieved through software is also referred to as Temporal Software Redundancy (TSR) and is characterized by duplicating instructions, spreading them out over time, and comparing results at critical points in a program.

One simple implementation of software redundancy is called Error Detection by Duplicated Instructions (EDDI) and duplicates all instructions except for store instructions [71]. The instructions are duplicated such that the original instruction and its duplicate use different registers for the arguments and different registers for the results. The use of different registers means that the outcomes of the duplicated instructions are independent of one another in terms of radiation events. This implementation also adds a check prior to every store instruction. This check ensures a match between the value to be stored to memory and the values' duplicate along with the address to which it is to be stored and the address' duplicate. If the values or addresses do not match, an error has occurred and error recovery must begin. If both values and addresses match, the store word instruction is executed [71]. This is better explained by looking at the following example in Table 1 which compares a simple program with a program incorporating EDDI.

| Instruction | Original        | Redundant       |

|-------------|-----------------|-----------------|

| Number      | Set             | Set             |

| 1           | LUI R1 1        | LUI R1 1        |

| 2           | LUI R2 2        | LUI R15 1       |

| 3           | ADD R3 R1 R2    | LUI R2 2        |

| 4           | SW R3 R0 OFFSET | LUI R16 2       |

| 5           |                 | ADD R3 R1 R2    |

| 6           |                 | ADD R17 R15 R16 |

| 7           |                 | BNE R3 R17 ERR  |

| 8           |                 | SW R3 R0 OFFSET |

Table 1. Simple Software Redundancy Example

In this example, LUI R1 1 is a load upper immediate instruction that loads the immediate value, 1, into the upper 16-bits of a 32-bit register named R1. ADD R3 R1 R2 is an addition command that adds the contents of registers R1 and R2 and stores the sum in register R3. SW R3 R0 OFFSET is a store instruction that stores the contents of register R3 to the memory location specified by R0 plus a constant offset specified by OFFSET. The register R0 always contains the value 0. The original program loads 1 and 2 into registers R1 and R2 so that they contain the values  $1 \cdot 2^{16}$ and  $2 \cdot 2^{16}$  respectively, adds the two values and stores the result of  $3 \cdot 2^{16}$  to R3, and stores R3 to memory location OFFSET. The redundant program does the same thing as the original set until the add instruction, but does it twice. The second time it performs each operation, the results are stored in different registers. If no errors occur, R15 = R1, R16 = R2, and R17 = R3. Additionally, the values of R15, R16, and R17 do not depend upon the values of R1, R2, and R3 because they were computed independently. The next big difference is the comparison performed on line 7. The BNE R3 R17 ERR instruction is a branch if not equal instruction. The instruction decides that if R3 does not equal R17, code execution should jump to some error recovery instructions at the location specified by the branch distance as ERR. If R3 does equal R17, instruction 8 is performed which stores R3 to the memory location specified by OFFSET.

Each register and its duplicate must be maintained so long as it is needed by future instructions. For example, if R1 and R15 are used to compute another value to be stored in R4 and R18, R1 and R15 must not be overwritten. One particular question asked why the redundant set could not perform original instructions 1, 2, and 3 followed by original instructions 1, 2, and a modified form of redundant instruction 6 "ADD R17 R1 R2". This would still achieve the desired independence between R3 and R17 for the comparison of redundant instruction 7; however, R1 and R2 would have no duplicates and be unprotected from errors should R1 and R2 be needed for future instructions. Additionally, the LUI instruction is the only Basic MIPS instruction that does not require any previously computed values stored in another register. If R1 and R2 were assigned as the result of an ADD, AND, SUB, or any other instruction, recomputing R1 and R2 based on the same values supplied by the register arguments to the ADD, AND, or SUB instruction would not make them independent, and therefore susceptible to identical errors.

This research uses the EDDI TSR approach in the development of Adaptive-Hybrid Redundancy (AHR). This is the simplest of the TSR approaches that will be presented in this chapter, which makes it an ideal candidate for evaluating AHR. While more complicated forms of TSR could be implemented, it could obfuscate some of the results such that the advantages of AHR over TMR or TSR alone would not be readily apparent.

Some implementations of this approach created a compiler that would automatically convert a non-duplicated program like the one shown in Table 1 to a redundant set like the one shown in Table 1 [71, 101]. Oh's specific implementation also sought to minimize the time penalty incurred by the additional instructions by making use of a pipelined architecture in a super-scalar processor [71]. While Oh et al. and Tokponnon et al. did not specify the nature of the error recovery instructions; it is worth noting that duplication more than doubles the total number of instructions when the additional error recovery instructions are added. Oh and McCluskey also developed a method that does not duplicate all instructions in order to realize energy savings [69].

Oh et al. further improved upon their work by adding signature detection instructions to ensure that programs were followed sequentially and that branch instructions were executed properly [70]. These signature detection instructions ensured that errors affecting the program counter (PC) were detected. When combined with instruction duplication, a more robust software redundancy method called SWIFT was created [79]. This was further strengthened by SWIFT-R which modifies SWIFT by triplicating all instructions rather than duplicating all instructions. This is essentially software implementation of TMR with additional protections for PC errors [80].

Reis et al. also discussed two additional software redundancy methods in the same paper. In the one referred to as trump, an instruction duplication method creates duplicate instructions that are AN-encoded where AN-encoding could be applied [80]. The other, referred to as Mask, "enforces statically known invariants to eliminate faults that can be reasoned away. Using these invariants, Mask can remove faults that would otherwise be deleterious, thus increasing reliability without redundant execution." [80]. The paper goes on to discuss hybrids between SWIFT-R, trump, and Mask. SWIFT-R and SWIFT-R/trump provide the greatest protection but have normalized run times that are nearly twice as long as a program that implements no redundancy. The trump and trump/Mask methods provide minimal protection and have normalized runtimes that are 36% longer than an unprotected program.

Software signature detection has also been used purely to detect illegal branches

while not simultaneously protecting against data errors. In one particular example, a program is broken into blocks and each block is assigned a parity value that depends upon its predecessor block. This parity value is computed at compile time. Signature checking instructions are inserted into the blocks that also compute the parity values at runtime. If runtime and compile time signatures do not match, then an illegal branch has occurred in the code. This particular example provides no recovery method when an error is detected [103].

## 2.3.2.3 Hybrid Redundancy

Hybrid redundancy refers to any amalgamation of one or more redundancy methods, and more particularly if those methods are fundamentally different. Hybrids can include hardware/software, hardware/ECC, software/ECC, hardware/software/ECC, methods that combine processor and memory hardening, and many more.

The first example of hybrid redundancy is specific to FPGAs and cannot be applied to other computer processors because the mitigation approach focuses upon SEUs affecting an FPGA's configuration memory. The primary means by which FPGA designers can overcome configuration memory SEUs is by implementing internal scrubbing. Internal scrubbing is the process where configuration memory is reprogrammed from an external, radiation hardened source to correct any errors that occur. This process takes time and must be performed periodically to ensure errors are corrected as soon as possible after they occur. However, errors can still occur between internal scrubbing intervals. To ensure these errors do not cause problems, additional mitigation is needed in the form of user logic redundancy. By making user logic redundant, a configuration error affecting one of two or more redundant user logic components will not be able to alter the desired system state or outputs. Redundancy gives the periodic internal scrubbing an opportunity to correct configuration errors before there are enough errors to affect desired system state or outputs. One approach utilizes internal scrubbing with dual redundancy of user logic [23]. This mitigation approach also uses dynamic partial reconfiguration (DPR) instead of periodic internal scrubbing of the entire configuration memory [23]. DPR consists of constantly reading the configuration memory to detect errors, then only reconfiguring portions of configuration memory that contain errors [92]. DPR saves a significant amount of time and energy [23]. TMR for user logic in concert with internal scrubbing is another common strategy [57, 65, 73]. Another study paired TMR with DPR to take advantage of the ability of TMRs majority voting scheme to process faster than DMR (which has to return to a previously saved system state every time it encounters an error) and the time and energy savings provided by DPR.[59].

The next example of hybrid redundancy uses TMR (or NMR) for computer processors and ECCs to protect memory. A majority voting system is in place so the processors in agreement (2 of 3, 3 of 5, and etc.) determine the correct outputs and processors that are in error are periodically reset so that their states match the state of the processors in agreement [42]. A very similar approach selectively implements TMR for critical circuits to minimize the overall impact of SETs while still utilizing an ECC to protect memory [88].

Another approach performs a single calculation twice on the processor and uses a radiation hardened comparator to compare the results. If there is no match, the calculation is re-performed twice more. The first calculation of each round is compared and the second calculation of each round is compared. The ones that match are assumed to be the correct result [13]. This is a hybrid between software instruction redundancy and hardware radiation hardening.

Czajkowski also discusses redundancy achieved through temporal and spatial redundancy by placing duplicated instructions on different cores of a single processor and separated by a clock cycle. If the results of the two instructions do not match, the instruction is carried out a third time on a third core. If the results of two out of three executions of the same instruction match, processing continues to the next instruction, if not, recovery operations are started [14].

One hybrid method uses a primary processor to run programs and a second processor that checks the first for faults. The second processor only checks certain error prone portions of the primary processor. Software recovery is used to restore the primary or secondary processor when a fault is detected. This method is an alternative to the DMR approach, but is smaller and more energy efficient [83].

Another hybrid technique implements NMR in virtual processors running in lockstep in the same way that NMR runs on physical processors. The approach examined the differences between DMR, TMR, and quadruple modular redundancy (4 processors). The voter and recovery operations are also implemented as virtual processes [46].

Reinhardt and Mukherjee discuss three different architectures. The first detects errors by comparing outputs of two identical threads running at the same time on different processors [78]. The second compares the outputs of two identical threads running at different times on the same processor [78, 104]. Vijaykumar et al. improved this second architecture by adding error recovery so that errors are corrected rather than only being detected [104]. The third compares the outputs of two identical threads at different times on two different processors where one thread leads the other in execution by a fixed minimum amount of time [62, 78, 84].

Another approach that also uses a redundant thread running simultaneously also makes use of ECCs to protect the processor's cache memory and some registers. This approach creates redundant threads at runtime for each instruction. Errors are detected when the results of each thread are compared before committing the results. When an error is detected, the processor "rewinds" to the last committed change, which is immediately prior to the start of the instruction that resulted in the error. This method may also recover from errors by majority voting on the results of redundant threads when there are three or more redundant threads [77].

Another hybrid method combines TMR with ECCs to protect memory [49]. This approach has two layers of protection. ECCs protect each word stored in memory. Each word is also triplicated for added redundancy. The correct output for a specific word stored in memory is the majority vote of the three copies of the word stored in memory.

A different hybrid uses a specialized compiler to determine which instructions in a program are critical to its output at compile time and flags those instructions. A modified super-scalar out-of-order processor detects those flags at runtime and creates one or more replicas of the instruction at runtime. After the processor processes a flagged instruction and its replicas, it compares the results before storing them. If any of the results differ, the processor performs error recovery operations [63].

While ECCs were previously discussed as a hardware redundancy method, they have also been implemented by software in a hybrid approach. This approach assumes that hardware ECCs are unavailable or too expensive for an application. A software program was created that would periodically scrub memory to create codes for words in memory which did not have codes and update codes for words that already had ECC protection. The program allocated space in memory to store the code words since the memory was not designed to accommodate ECCs. The research examined vertical Hamming, vertical cyclic, 2-dimensional, and Reed-Solomon codes and determined that all codes provided a level of protection far greater than unprotected memory, but not as much protection as hardware implemented ECCs [86].

## 2.3.2.4 Adaptive Redundancy

One method of adaptively responding to changes in error rates chooses an error correcting method that minimizes errors, delays, and energy in cached memory. It utilizes three different software modular redundancy schemes with varying levels of error protection and performance costs. When error rates are low, the lowest cost redundancy scheme with the least error protection is used. As error rates increase, the intermediate cost redundancy scheme with greater error protection is used followed by the one with the highest cost and greatest error protection. As error rates decrease, lower cost redundancy is used [106]. This adaptive method could potentially be applied to TMR, NMR, backup redundancy, hybrid redundancy, or any other redundancy methodology implemented in hardware and/or software to minimize performance costs for a given radiation environment. While Wang et al. apply this adaptive approach to cached memory, this research applies this approach to the processor. The use of adaptive redundancy for a processor has not been extensively explored in the literature before. The only example discovered was previously mentioned in which TMR is turned on and off based on the radiation environment detected by a radiation sensor [55]. This example only provides a choice between redundancy and no redundancy. No examples were found in literature that allowed a choice between different redundancy techniques for a processor.

## 2.3.3 Summary of Mitigation Techniques

All of the mitigation techniques discussed in this section, with the exception of the TMR adaptive approach, are fixed once implemented on a space vehicle. The TMR adaptive approach is not a viable option since it affords no error protection in the event that a SEU occurs when the processor is in single processor mode. These fixed redundancy methods each come with fixed energy and processing speed advantages

and disadvantages that cannot change for the duration of a space vehicle's mission. This research seeks to answer whether it is possible to implement multiple redundancy methods and switch between them in order to provide a tradespace in terms of energy and processing speed performance.

## 2.4 Radiation Comparisons

Although making comparisons between different radiation experiments is inherently difficult, even a rough order of magnitude comparison is valuable in the task of evaluating radiation hardening and mitigation efforts. Radiation experiments vary widely in the types of radiation, energy levels, and flux levels used. Experiments that cause SEUs and SETs use particle radiation which are known to cause SEUs and SETs rather than x-rays and gamma rays which are not known to cause SEUs and SETs. Particle experiments may use protons, neutrons, or heavier ions which can be as "light" as helium or as "heavy" as gold (or heavier) in terms of atomic number. Indeed, many elements across the periodic table can and have been used in radiation experiments. In addition, the energy level also plays a major role. The energy level of particles depends on the velocity to which the particles are accelerated before striking their target. If these concerns were not enough, the flux also plays a role. Flux is essentially a particle flow rate or density measure; it describes the number of particles that pass through a cross sectional area over a certain period of time.

In addition to these factors, the materials used to construct the electronic device (i.e. silicon, doping levels, device sizes, and etc.) also have an impact on the rate at which SETs and SEUs occur. As a result, comparing the results of one radiation experiment to another is inherently difficult. Typically, any radiation comparisons are made on a case by case basis and any data on radiation comparisons have come from past empirical data. One method of comparing SEU rates with different radiation environments is provided by Normand et al. [66, 67]. In these papers, a comparison is made between SEU rates of identical microelectronics exposed to broad spectrum (10 MeV to 1 GeV) neutrons and 400 MeV protons [67] at Los Alamos National Laboratories. The SEU rate comparison was nearly one-to-one across all of the different microelectronic devices that were tested. One additional piece of information from Normand et al. is that the neutrons had a flux of  $1 \times 10^9 \frac{n}{cm^2 \cdot hr}$ , but the proton flux was unspecified [67]. This neutron flux will be important when making SEU rate comparisons when discussing the results of neutron experiments conducted in this research. Those results are presented in Section 5.2.2.1

While these comparisons are inherently difficult, some similarities may be noted between experiments where similar radiation environments are used. For example, the Cibola flight experiment saw a peak proton flux between 10 and 100 MeV as shown in Figure 1 in [108]. Normand et al. suggested that 200 to 300 MeV protons could also replicate the neutron environment in [66], but did not provide test data to support that claim. Assuming that the Cibola proton environment is similar enough to Normand's proton environment, it could be argued that the Cibola SEU rate could be used to predict the SEU rate in an equivalent neutron environment. This is an unfounded assumption, but making this assumption enables a rough order of magnitude comparison between the Cibola SEU rate and the SEU rate seen in the neutron experiment conducted in this research.

Some other problems with this assumption are the unknown proton fluence levels in Normand's work. Additionally, the goal of Normand's work was to match the SEU rates of microelectronics in a known neutron environment by using proton radiation at varying energy levels using identical electronic devices. Note that the electronic devices used in this research (Intel Cyclone V FPGA on a Terasic DE10-Standard board) differ from the Xilinx FPGAs used by the Cibola flight experiment. The Cibola flight experiment experienced a mitigated SEU rate of 0.78 SEUs/device/day, or a failure-in-time FIT rate of  $3.25 \times 10^7$  [108]. This is a good goal for mitigated SEU vulnerability and will serve as a point of comparison for the radiation experiments performed in this research. The Cibola flight experiment's mitigation technique was TMR combined with configuration memory scrubbing.

## 2.5 Hardware Selection

This research attempts to implement the proposed Adaptive-Hybrid Redundancy (AHR) on an Intel Cyclone V FPGA. Intel FPGAs were chosen because they have not been publicly studied for radiation hardness to the extent that other brands of FPGAs, such as Actel and Xilinx FPGAs, have been studied. This research sought to add to the body of knowledge on radiation hardness of FPGAs by examining an Intel FPGA rather than a more extensively researched brand of FPGA. The Cyclone V was chosen over other available Intel FPGAs because it is representative of an inexpensive Commercial-Off-the-Shelf (COTS) FPGA.

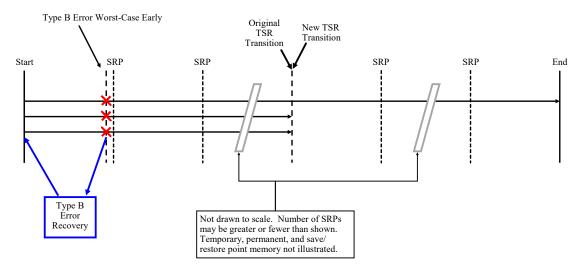

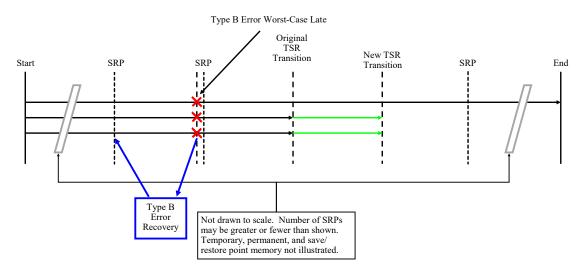

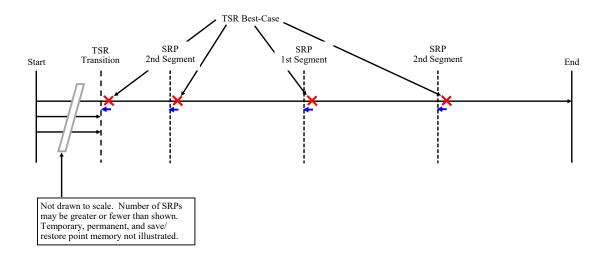

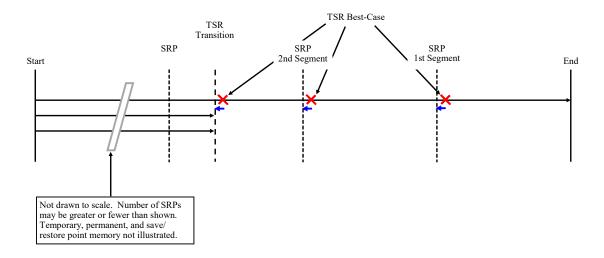

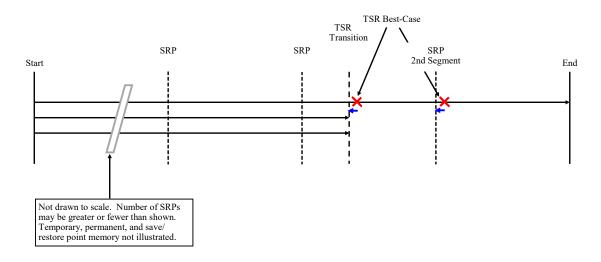

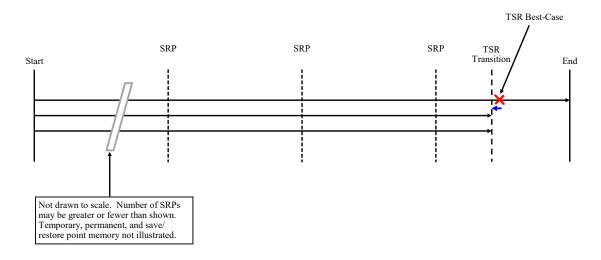

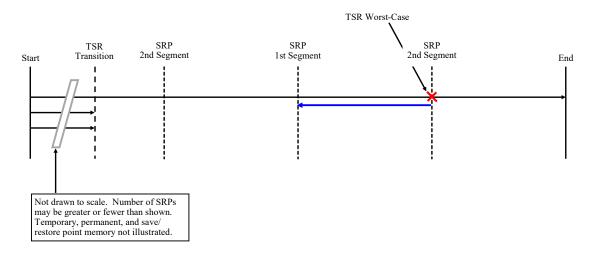

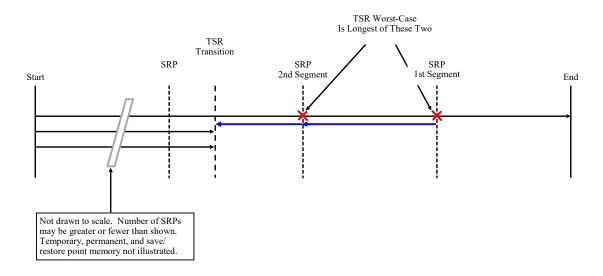

The Cyclone V's unmitigated vulnerability to SEUs and SETs must be understood in order to determine the appropriate rate at which to inject errors into AHR simulations. It is also necessary to determine a baseline with which to compare AHR's performance in the presence of radiation. This will allow a determination to be made about whether AHR is providing mitigation by lowering the number of undetected and uncorrected errors. This research will examine the unmitigated vulnerability of the Cyclone V to configuration and user logic SEUs as well as user logic SETs.