## Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

9-1-2013

## Enhancing Electromagnetic Side-Channel Analysis in an Operational Environment

David P. Montminy

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the <u>Other Computer Engineering Commons</u>, and the <u>Other Electrical and Computer Engineering Commons</u>

#### Recommended Citation

Montminy, David P., "Enhancing Electromagnetic Side-Channel Analysis in an Operational Environment" (2013). *Theses and Dissertations*. 888.

https://scholar.afit.edu/etd/888

This Dissertation is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

## DISSERTATION

David P. Montminy, Major, USAF AFIT-ENG-DS-13-S-01

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| the official poli | pressed in this dissertation are those of the author and do no<br>licy or position of the United States Air Force, Department of<br>States Government. |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                                                                                                                                                        |  |

|                   |                                                                                                                                                        |  |

|                   |                                                                                                                                                        |  |

|                   |                                                                                                                                                        |  |

## DISSERTATION

Presented to the Faculty of the

Graduate School of Engineering and Management

of the Air Force Institute of Technology

Air University

In Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

David P. Montminy, B.S.E.E., M.S.C.E.

Major, USAF

September 2013

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

## DISSERTATION

David P. Montminy, B.S.E.E., M.S.C.E.

Approved:

Rusty O. Baldwin, Ph.D. (Chairman)

Mark E. Oxley

Mark E. Oxley, Ph.D. (Member)

Michael A. Temple, Ph.D. (Member)

Date

28 June 2013

Date

28 June 2013

Date

Accepted:

HEIDI R. RIES, Ph.D.

Interim Dean, Graduate School of Engineering and Management

31 pl 2013

## To my parents and grandparents,

The values you instilled in me as a child continue to served me well.

To my wife and children,

The love and support you have given me over the last three years has kept me strong and focused. This dissertation would not have been possible without your support.

## Acknowledgements

Special thanks to my advisor Dr. Rusty Baldwin, whom I was lucky enough to first choose as my advisor for my master's degree. His continued support and encouragement over the years led me back to AFIT for a PhD. With gentle guidance he allowed me to explore my interests while keeping my research focused. I would also like to thank my research committee, Dr. Temple and Dr. Oxley for the numerous document reviews and feedback sessions.

David P. Montminy

## Table of Contents

|                  |          |                                 | Page |

|------------------|----------|---------------------------------|------|

| Acknowledgemen   | nts      |                                 | iv   |

| List of Figures  |          |                                 | xii  |

| List of Tables . |          |                                 | XV   |

| Abstract         |          |                                 | xvi  |

| 1. Introdu       | ection . |                                 | 1    |

| 1.1              | Motiva   | tion                            | 2    |

| 1.2              | Researc  | ch Contributions                | 3    |

| 1.3              | Organiz  | zation                          | 4    |

| 2. Backgro       | ound     |                                 | 6    |

| 2.1              | Introdu  | action                          | 6    |

| 2.2              | Crypto   | graphy Preliminaries            | 7    |

|                  | 2.2.1    | Block Ciphers                   | 7    |

|                  | 2.2.2    | Advanced Encryption Standard    | 8    |

|                  | 2.2.3    | Cryptanalysis of Block Ciphers  | 12   |

| 2.3              | Side-Cl  | nannel Leakage                  | 14   |

|                  | 2.3.1    | Power Consumption               | 14   |

|                  | 2.3.2    | Electromagnetic Emissions       | 16   |

|                  | 2.3.3    | Other Side-Channels             | 19   |

|                  | 2.3.4    | Leakage Models                  | 19   |

| 2.4              | Side-Cl  | nannel Attacks                  | 22   |

|                  | 2.4.1    | Types of Implementation Attacks | 23   |

|    |        |          |                                             | Page |

|----|--------|----------|---------------------------------------------|------|

|    |        | 2.4.2    | Adversary Models                            | 23   |

|    |        | 2.4.3    | Power and EM Analysis                       | 24   |

|    |        | 2.4.4    | Simple Side-Channel Analysis                | 25   |

|    |        | 2.4.5    | Differential Side-Channel Analysis          | 26   |

|    |        | 2.4.6    | Profiling Attacks                           | 29   |

|    | 2.5    | Counte   | rmeasures                                   | 33   |

|    |        | 2.5.1    | Masking                                     | 33   |

|    |        | 2.5.2    | Hiding                                      | 34   |

|    | 2.6    | Collecti | ing Electromagnetic Emissions               | 35   |

|    |        | 2.6.1    | Electronic Noise                            | 36   |

|    |        | 2.6.2    | Improving Collections                       | 36   |

|    | 2.7    | Pre-Pro  | ocessing Processing Techniques              | 38   |

|    |        | 2.7.1    | Detecting Compromising Frequency Components | 39   |

|    |        | 2.7.2    | Trace Alignment                             | 42   |

|    |        | 2.7.3    | Frequency-Based Analysis                    | 44   |

|    | 2.8    | Algebra  | aic Cryptanalysis                           | 45   |

|    |        | 2.8.1    | Describing a Cipher                         | 45   |

|    |        | 2.8.2    | Solving a System of Equations               | 48   |

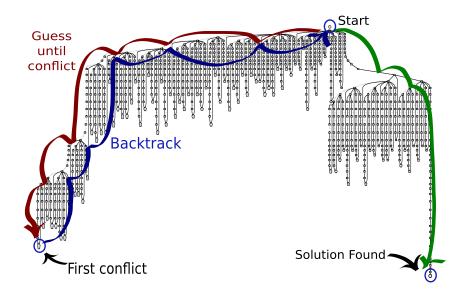

|    |        | 2.8.3    | Using SAT Solvers                           | 48   |

|    |        | 2.8.4    | Algebraic Side-Channel Analysis             | 50   |

|    |        | 2.8.5    | Related Key Recovery Techniques             | 53   |

|    | 2.9    | Summa    | ry                                          | 55   |

| 3. | Method | ology .  |                                             | 57   |

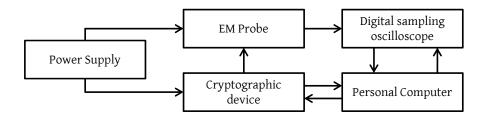

|    | 3.1    | Data C   | ollection                                   | 57   |

|    | 3.2    | Targete  | ed Devices                                  | 60   |

|    |        | 3.2.1    | PIC Microcontrollers                        | 60   |

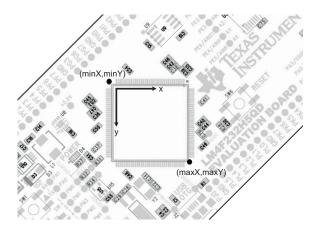

|    |        | 3.2.2    | ARM Cortex-M4F                              | 62   |

|    |        |          |                                             |      |

|     |          |                                              | Page |

|-----|----------|----------------------------------------------|------|

| 3.3 | Signal   | Processing Techniques                        | 65   |

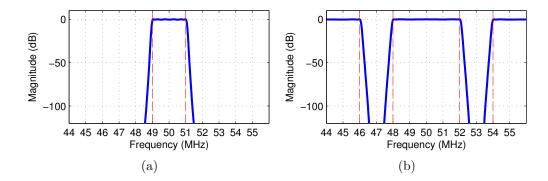

|     | 3.3.1    | Filtering                                    | 65   |

|     | 3.3.2    | Decimation                                   | 67   |

|     | 3.3.3    | Alignment                                    | 67   |

| 3.4 | Correla  | tion-Based Electromagnetic Analysis          | 68   |

|     | 3.4.1    | CEMA Attack Methodology                      | 68   |

|     | 3.4.2    | Example CEMA Attack                          | 71   |

|     | 3.4.3    | Known-Key Correlation Analysis               | 72   |

|     | 3.4.4    | Comparing Effectiveness of CEMA Attacks      | 73   |

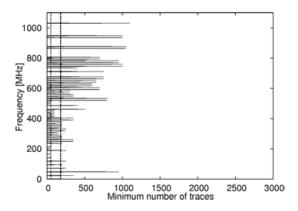

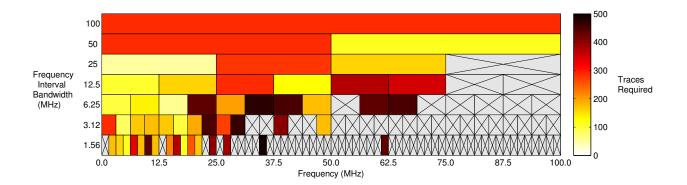

| 3.5 | Identify | ring Information Leaking Frequencies         | 74   |

|     | 3.5.1    | Frequency Interval Break Down Approach       | 75   |

|     | 3.5.2    | Overlapping Frequency Interval Approach      | 76   |

| 3.6 | Templa   | te Attacks                                   | 79   |

|     | 3.6.1    | Class Identification                         | 81   |

|     | 3.6.2    | Classifier Training                          | 81   |

|     | 3.6.3    | Classifying Observed Traces                  | 82   |

|     | 3.6.4    | Class Selection                              | 83   |

|     | 3.6.5    | Distinguishing Feature Selection             | 83   |

|     | 3.6.6    | Comparing Effectiveness of Template Attacks  | 85   |

| 3.7 | Algebra  | aic Cryptanalysis                            | 86   |

|     | 3.7.1    | Generating a System of Equations for AES-128 | 86   |

|     | 3.7.2    | Converting to a SAT Problem                  | 87   |

|     | 3.7.3    | Solving the System of Equations              | 89   |

|     | 3.7.4    | Unique Contributions of this SAT Solver Tool | 89   |

| 3.8 | Summa    | rv                                           | 90   |

|    |         |           |                                           | Page |

|----|---------|-----------|-------------------------------------------|------|

| 4. | Key Sch | nedule Re | edundancy Attack                          | 91   |

|    | 4.1     | Introdu   | ction                                     | 91   |

|    | 4.2     | Backgro   | ound                                      | 93   |

|    |         | 4.2.1     | Key Schedule Background                   | 93   |

|    | 4.3     | Related   | Work                                      | 94   |

|    | 4.4     | The Att   | tack                                      | 97   |

|    |         | 4.4.1     | Data Collection                           | 97   |

|    |         | 4.4.2     | Targeted Intermediate Values              | 98   |

|    |         | 4.4.3     | Template Attack                           | 100  |

|    |         | 4.4.4     | Reconciling Round Key-Byte Guesses        | 101  |

|    | 4.5     | Results   | and Comparison                            | 102  |

|    |         | 4.5.1     | Evaluating Performance                    | 102  |

|    |         | 4.5.2     | Comparison of Distinguishing Features     | 103  |

|    |         | 4.5.3     | Experimental Results                      | 104  |

|    |         | 4.5.4     | Comparison                                | 108  |

|    | 4.6     | Conclus   | sion                                      | 110  |

| 5. | Improvi | ng Cross  | -Device Template Attacks                  | 112  |

|    | 5.1     | Introdu   | ction                                     | 112  |

|    | 5.2     | Cross-D   | Pevice EM leakage                         | 114  |

|    |         | 5.2.1     | Compensating for Device Differences       | 116  |

|    | 5.3     | Experin   | nental Methodology                        | 117  |

|    |         | 5.3.1     | Targeted Devices                          | 117  |

|    |         | 5.3.2     | Template Attack Methodology               | 117  |

|    |         | 5.3.3     | Distinguishing Feature Data Normalization | 119  |

|    | 5.4     | Results   |                                           | 120  |

|    |         | 5.4.1     | Selected Features                         | 120  |

|    |         | 5.4.2     | Baseline Standard Template Attack         | 122  |

|    |         |           |                                                               | Page |

|----|---------|-----------|---------------------------------------------------------------|------|

|    |         | 5.4.3     | MVN Technique Results                                         | 125  |

|    |         | 5.4.4     | PCA-based Attack                                              | 127  |

|    |         | 5.4.5     | Comparison of Attacks                                         | 128  |

|    | 5.5     | Conclus   | ion                                                           | 131  |

|    | 5.6     | Constru   | cting a Master Template                                       | 132  |

| 6. | Cross-D | evice Att | eacks on Complex Microprocessors                              | 134  |

|    | 6.1     | Introdu   | ction                                                         | 134  |

|    | 6.2     | Related   | Work                                                          | 135  |

|    | 6.3     | Method    | ology                                                         | 136  |

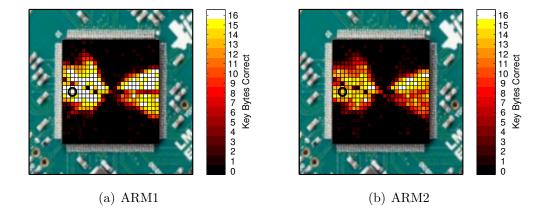

|    |         | 6.3.1     | Device Leakage Cartography                                    | 136  |

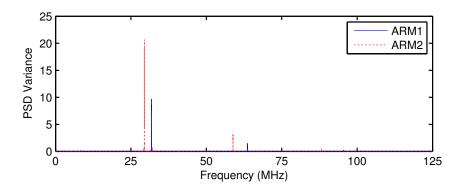

|    |         | 6.3.2     | Identifying Unrelated Signals                                 | 137  |

|    |         | 6.3.3     | Combining Techniques                                          | 140  |

|    | 6.4     | Results   |                                                               | 141  |

|    |         | 6.4.1     | Effectiveness of Cross-Device Methods                         | 141  |

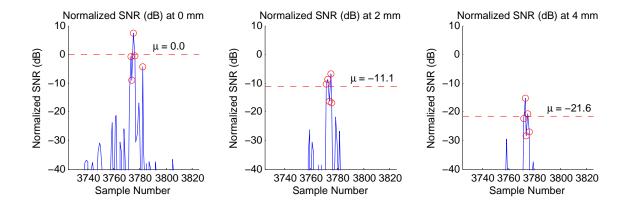

|    |         | 6.4.2     | Probe Position Tolerance                                      | 144  |

|    |         | 6.4.3     | Comparison of Successful CEMA and Template Attacks Locations  | 147  |

|    |         | 6.4.4     | Notch-Filtering for CEMA Attacks                              | 149  |

|    | 6.5     | Conclus   | ion                                                           | 150  |

| 7. |         |           | cromagnetic Attacks on a 32-bit Microprocessor Defined Radios | 152  |

|    | 7.1     | Introdu   | ction                                                         | 152  |

|    | 7.2     | Backgro   | und                                                           | 154  |

|    |         | 7.2.1     | Triggering and Alignment                                      | 154  |

|    |         | 7.2.2     | Software Defined Radios                                       | 155  |

|    | 7.3     | Related   | Work                                                          | 156  |

|    | 7.4     | Baseline  | e Attack Performance                                          | 157  |

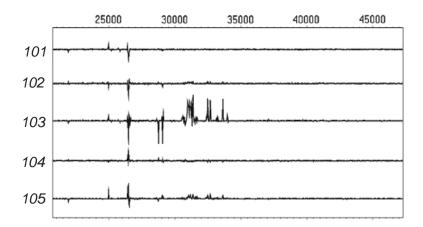

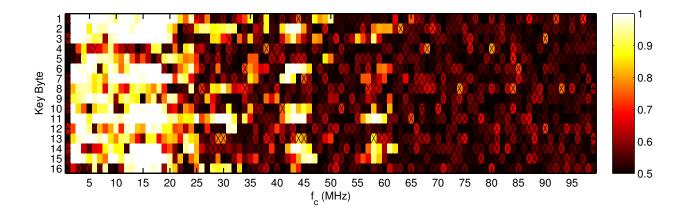

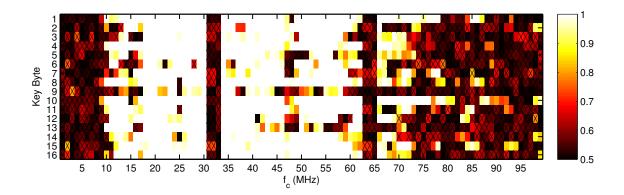

|             | 7.4.1   | Electromagnetic Cartography Scan                       |

|-------------|---------|--------------------------------------------------------|

|             | 7.4.2   | Correlation-Based Frequency-Dependent Leakage Analysis |

|             | 7.4.3   | Baseline Results                                       |

| 7.5         | Softwar | re Defined Radio Methodology                           |

|             | 7.5.1   | Sub-Nyquist Sampling                                   |

|             | 7.5.2   | Software Defined Radios                                |

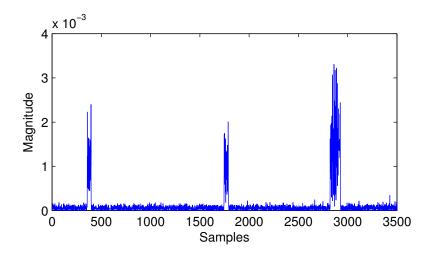

|             | 7.5.3   | Identifying and Aligning Encryption Operations         |

|             | 7.5.4   | Additional Processing for the RTL-SDR $$               |

| 7.6         | Softwar | re-Defined Radio Results                               |

|             | 7.6.1   | USRP                                                   |

|             | 7.6.2   | RTL-SDR                                                |

|             | 7.6.3   | Additional Observations                                |

|             | 7.6.4   | Comparison of the Baseline and SDR Results             |

| 7.7         | Conclu  | sion and Future Work                                   |

| Conclus     | sion    |                                                        |

| 8.1         | Researc | ch Summary                                             |

|             | 8.1.1   | Algebraic Cryptanalysis                                |

|             | 8.1.2   | Cross-Device Template Attacks                          |

|             | 8.1.3   | Software Defined Radios (SDR)                          |

| 8.2         | Recomi  | mendations for Future Research                         |

|             | 8.2.1   | Algebraic Cryptanalysis                                |

|             | 8.2.2   | Cross-Device Template Attacks                          |

|             | 8.2.3   | Software Defined Radios                                |

| Appendix A. | Constr  | ucting and Solving Systems of Equations                |

| A.1         | Conjun  | ctive Normal Form                                      |

|              |                                                                | - |

|--------------|----------------------------------------------------------------|---|

| A.2          | SAT Solvers                                                    |   |

| A.3          | Converting MQ to SAT                                           |   |

|              | A.3.1 Step 1: Convert the Polynomial System to a Linear System |   |

|              | A.3.2 Step 2: Linear System to CNF Expression                  |   |

|              | A.3.3 Step 3: DIMACS CNF Form                                  |   |

| A.4          | Methods for Solving Non-linear Multivariate Systems of         |   |

|              | Equations                                                      |   |

| Appendix B.  | Writing AES-128 for a SAT Solver                               |   |

| B.1          | SR Polynomial Generator                                        |   |

|              | B.1.1 Variable Names                                           |   |

| B.2          | ANF to CNF Converter                                           |   |

|              | B.2.1 Specifying Known Values                                  |   |

|              | B.2.2 SAT Solver                                               |   |

| B.3          | Example Code                                                   |   |

|              | B.3.1 Full System of Equations                                 |   |

|              | B.3.2 Key Schedule Only System of Equations                    |   |

|              | B.3.3 Known Values Format                                      |   |

|              | B.3.4 Helper Functions                                         |   |

| Appendix C.  | List of Acronyms                                               |   |

| Ribliography |                                                                |   |

## List of Figures

| Figure |                                                                | Page |

|--------|----------------------------------------------------------------|------|

| 2.1    | AES Cipher Structure                                           | 10   |

| 2.2    | Lumped Capacitor Model of a CMOS Inverter                      | 15   |

| 2.3    | EMI Coupling Modes                                             | 17   |

| 2.4    | Hamming Weight Leakage Example                                 | 21   |

| 2.5    | Hamming Distance Leakage Example                               | 22   |

| 2.6    | Simple Side-Channel Analysis                                   | 25   |

| 2.7    | Differential Power Analysis                                    | 28   |

| 2.8    | Filtered Traces Required to Perform a Successful Attack        | 41   |

| 2.9    | Visualization of SAT Solver Search Path                        | 50   |

| 3.1    | Riscure Inspector Tool Suite                                   | 58   |

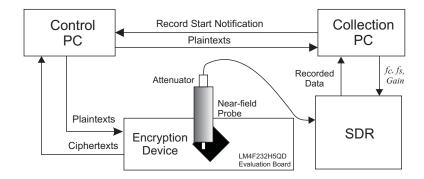

| 3.2    | Side-Channel Collection Setup                                  | 59   |

| 3.3    | Jig Configuration for ARM Collections                          | 64   |

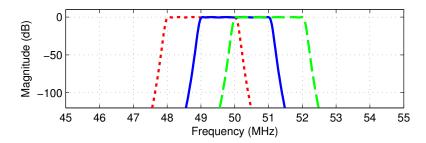

| 3.4    | Impulse Response Magnitude for Bandpass and Notch Filters      | 66   |

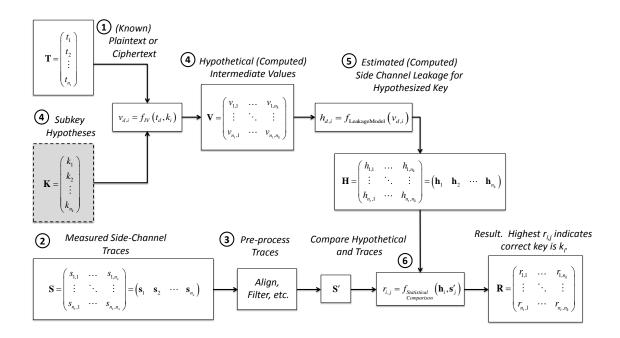

| 3.5    | Differential Side-Channel Analysis Process                     | 68   |

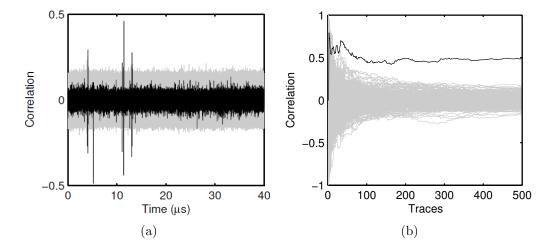

| 3.6    | Visualization for Correlation Coefficients                     | 72   |

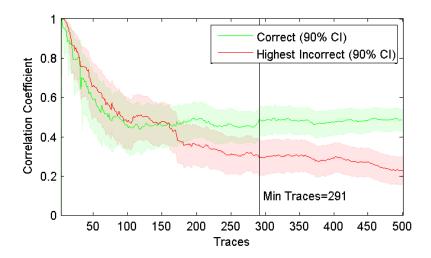

| 3.7    | Traces Needed for CEMA Attack Confidence                       | 75   |

| 3.8    | Traces Needed for Filtered Traces                              | 76   |

| 3.9    | Comparing CEMA Confidence for Multiple Bytes                   | 79   |

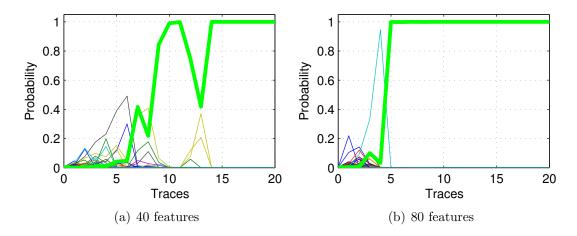

| 3.10   | Comparison of Posterior Probabilities for Two Template Attacks | 86   |

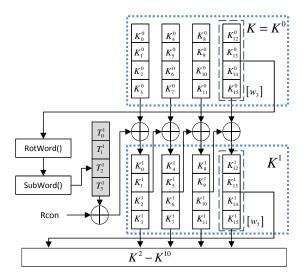

| 4.1    | One Round of the AES-128 Key Schedule                          | 94   |

| 4.2    | Estimated SNR                                                  | 103  |

| 4.3    | Distinguishing features for $h=0 \text{ mm}$                   | 104  |

| 4.4    | Distinguishing features for $h = 5 \text{ mm}$                 | 105  |

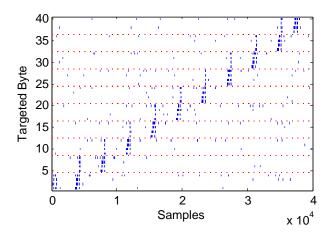

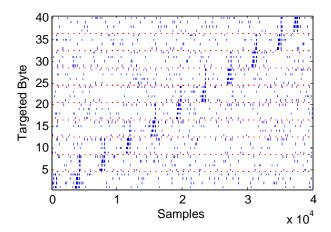

| 5.1    | Distribution of samples from 40 devices                        | 115  |

| 5.2    | Distinguishing Features for 40 Devices                         | 121  |

| Figure |                                                                           | Page |

|--------|---------------------------------------------------------------------------|------|

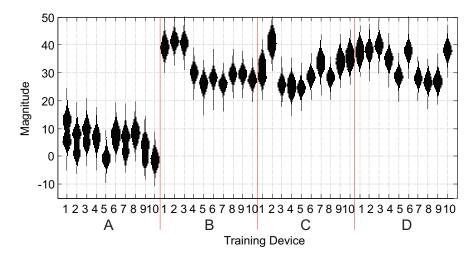

| 5.3    | Magnitude of Eigenvector Elements for 40 devices                          | 123  |

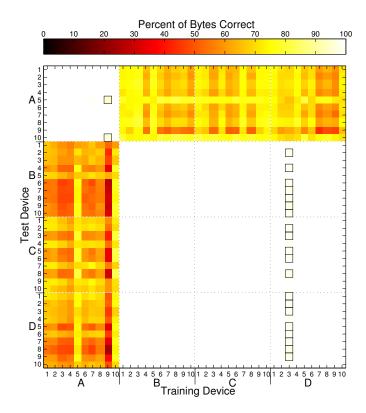

| 5.4    | Standard Cross-Device Template Attack Results                             | 124  |

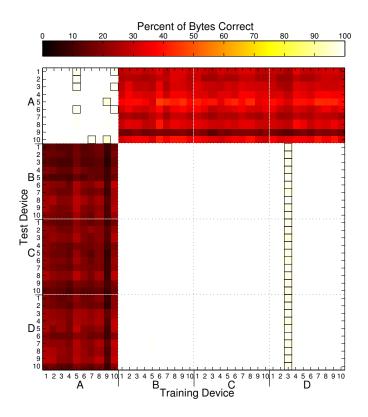

| 5.5    | MVN Technique Cross-Device Template Attack Results                        | 126  |

| 5.6    | MVN Technique Cross-Device PCA Template Attack Results                    | 128  |

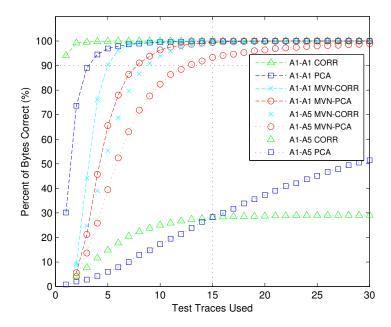

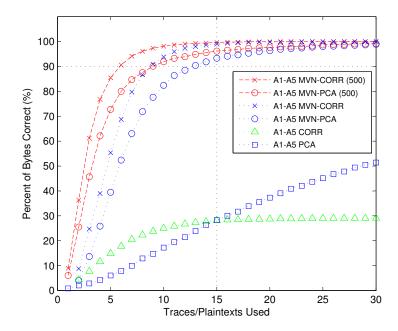

| 5.7    | Comparison of Attack Performance                                          | 129  |

| 5.8    | Effect of Increasing Test Traces Used for Normalization                   | 130  |

| 5.9    | Combined Template Attack Performance with MVN                             | 133  |

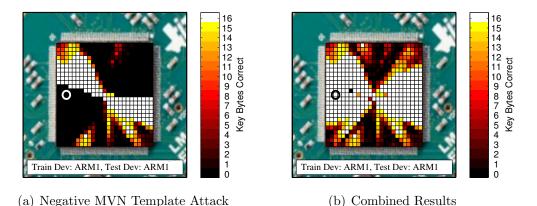

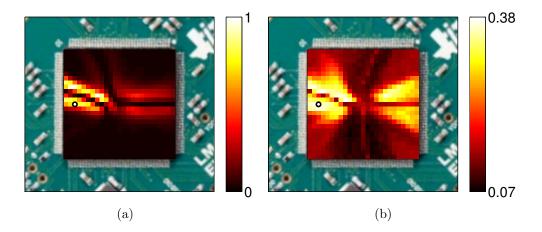

| 6.1    | CEMA Attack Performance by Location                                       | 138  |

| 6.2    | Variance of Power Spectral Density                                        | 139  |

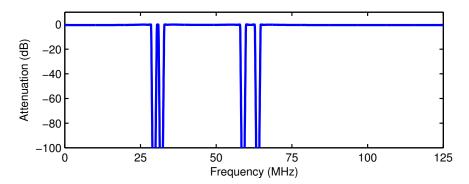

| 6.3    | Impulse Response of ARM Notch Filter                                      | 140  |

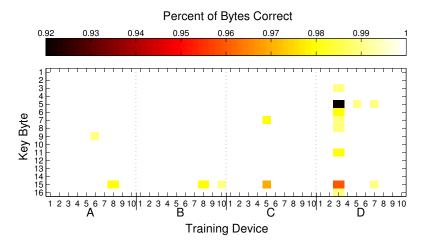

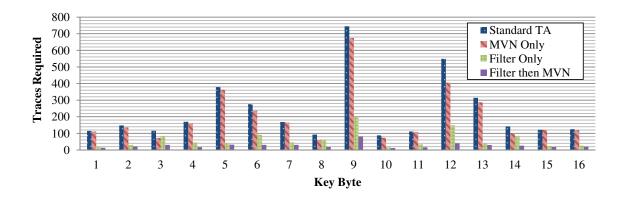

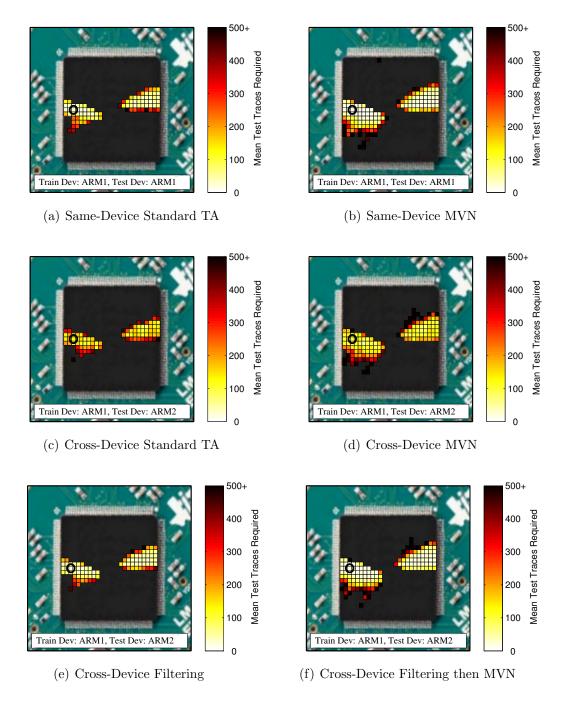

| 6.4    | Traces Required with Pre-processing per Key-Byte                          | 142  |

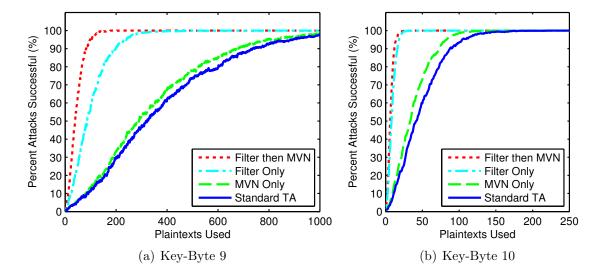

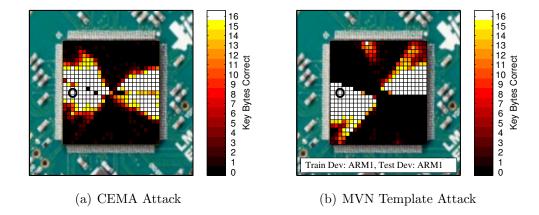

| 6.5    | Success Rate for Cross-Device Template Attacks                            | 143  |

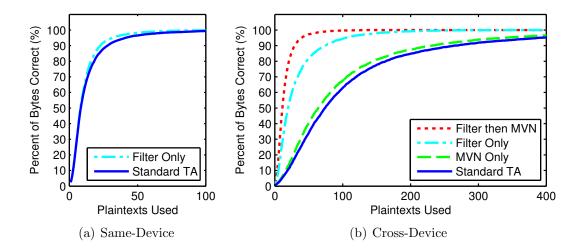

| 6.6    | Pre-processing Techniques on Same- and Cross-Device Attacks               | 144  |

| 6.7    | Traces Required for Preprocessing and Probe Placement                     | 146  |

| 6.8    | CEMA Attack Performance by Location                                       | 148  |

| 6.9    | Template Attack Performance with Negative MVN                             | 149  |

| 7.1    | Device PSD and Mean Correlation Plots                                     | 159  |

| 7.2    | Magnitude of Overlapping Bandpass Filter Impulse Response                 | 160  |

| 7.3    | Maximum Normalized Power Spectral Density                                 | 162  |

| 7.4    | Two Computer Collection Setup                                             | 164  |

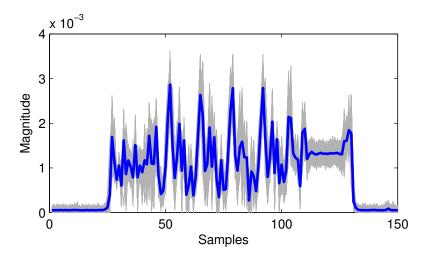

| 7.5    | Magnitude of Collected Trace                                              | 169  |

| 7.6    | Comparison of 250 traces collected with USRP2                             | 170  |

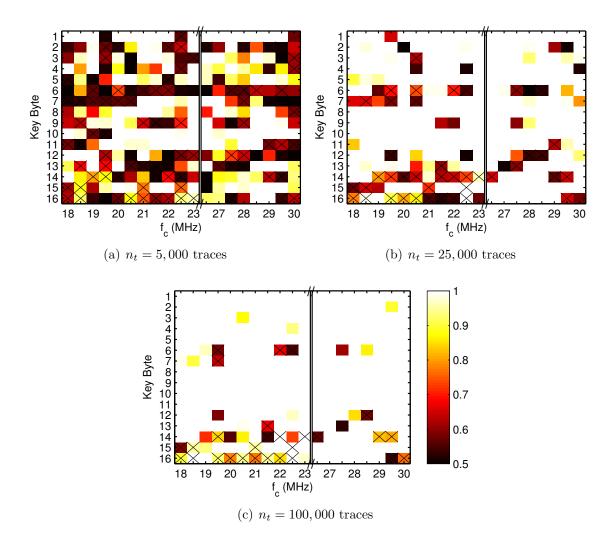

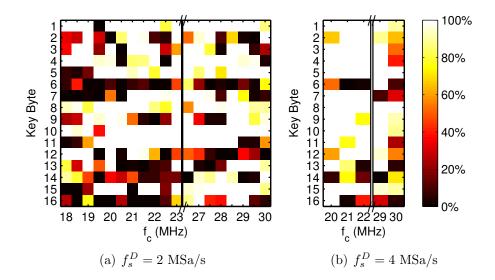

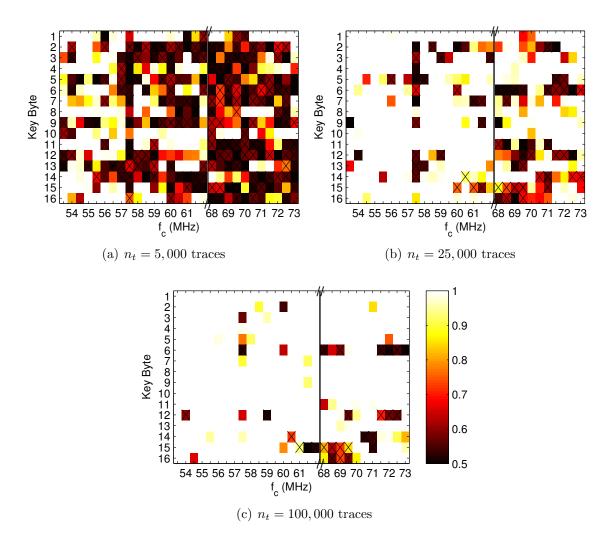

| 7.7    | Confidence $r_{max} \geq r_{next}$ for $f_s^D = 2$ MSa/s USRP2-based CEMA | 173  |

| 7.8    | Confidence $r_{max} \geq r_{next}$ for $f_s^D = 4$ MSa/s USRP2-based CEMA | 174  |

| 7.9    | CEMA attack success rate for USRP2                                        | 176  |

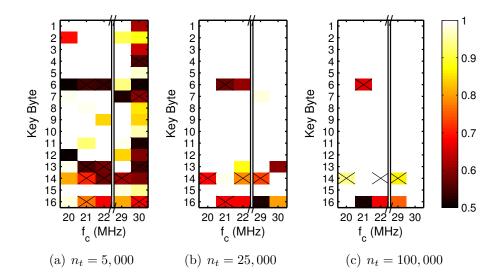

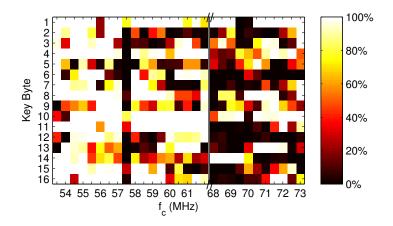

| 7.10   | Confidence $r_{max} \ge r_{next}$ for RTL-SDR-based CEMA                  | 178  |

| 7.11   | Percent of CEMA attacks correct for 5,000 RTL-SDR test traces             | 179  |

| Figure |                                                            | Page |

|--------|------------------------------------------------------------|------|

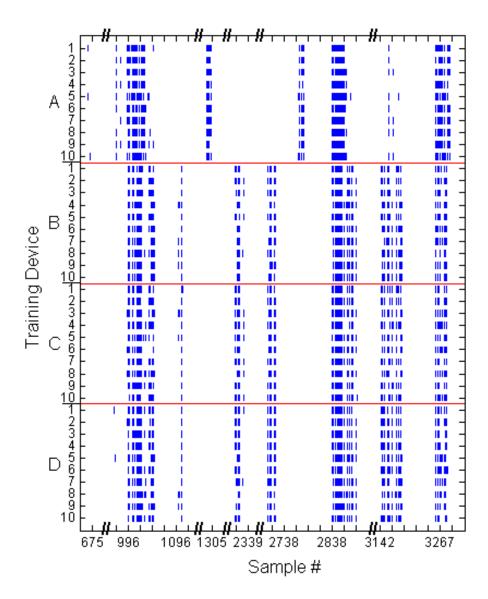

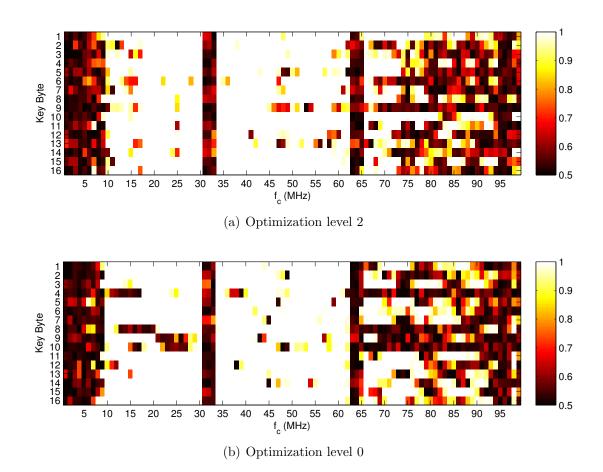

| 7.12   | Byte Extraction Confidence for Compiler Settings           | 182  |

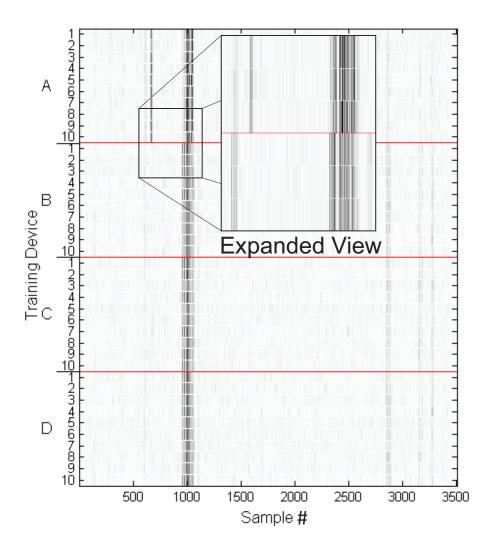

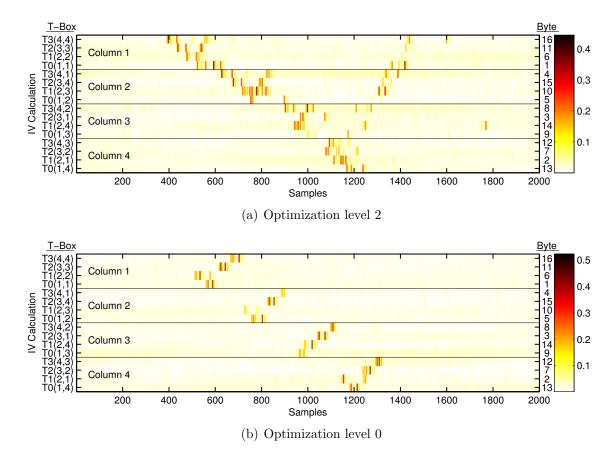

| 7.13   | Temporal Leakage Map for Two Optimization Levels           | 183  |

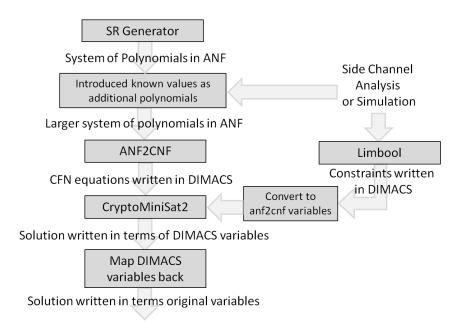

| B.1    | Data Flow from System of Polynomial to SAT Solver Solution | 203  |

## List of Tables

| Table |                                                                    | Page |

|-------|--------------------------------------------------------------------|------|

| 3.1   | Tested PIC Micro-Controller Device Classes                         | 60   |

| 4.1   | Calculated SNR for Probe Height                                    | 103  |

| 4.2   | KSRA Attack Percent Correct                                        | 106  |

| 4.3   | SubBytes Attack Percent Correct                                    | 109  |

| 5.1   | Standard Template Attack Performance                               | 122  |

| 5.2   | Cross-device Extraction Rates with MVN                             | 125  |

| 5.3   | Cross-device Extraction Rates with MVN and PCA $\ \ldots \ \ldots$ | 127  |

| 7.1   | Confidence Key Byte Selected has Highest Correlation               | 162  |

#### Abstract

Side-channel analysis has been used to determine the secret key from cryptographic devices in a controlled laboratory environment. In many cases, it is assumed that a powerful attacker is able to place a near-field probe within close proximity of a device, modify the device to gain precise timing information, and have access to a training device having side-channel emissions identical to those produced by the target device. Attacks in a laboratory setting utilize expensive digital storage oscilloscopes. To make side-channel attacks more effective in an operational environment, this research identifies ways to 1) reduce the control an attacker must have on a cryptographic device, and 2) reduce the cost of required attack equipment.

A new unknown-plaintext attack is developed to exploit redundancy in the AES key schedule and successfully extract keys from "poor" quality collections. Algebraic cryptanalysis is used to determine the correct key schedule even when maximum likelihood-based template attacks do not identify correct intermediate values by attacking more intermediate values and exploiting the redundancy of the key schedule, the new attack is superior to known plaintext attacks when only a small number of traces for a target device are available. The quality of collected traces is intentionally degraded to show the attack robustness, and a novel thresholding technique is developed to identify possible values for each targeted key schedule byte. Even with poor quality traces, the new attack is successful in 97.5% of trials where a standard template attack that does not employ algebraic cryptanalysis fails 100% of the time.

Profiling attacks assume an adversary has access to a training device identical to the target device being attacked. Although it was previously assumed the side-channel emissions from similar devices were identical, or at least similar, this assumption is challenged here by performing template attacks using traces collected from 40 16-bit microcontrollers. When the standard template attack methodology fails to produced adequate results, each step is evaluated to identify device-dependent variations. A simple pre-processing technique, i.e., normalizing the trace means and variances from the training and test devices, is evaluated for various test data set sizes. Normalization improves the key-byte extraction success rate from 65.1% to 100% for same part number cross-device template attacks and from 39% to 82.8% for attacks using similar devices for training. Additionally, a procedure is developed to create a single set of templates using training data from multiple devices that can be used to attack all 40 devices at a 99.95% byte extraction success rate.

The new mean and variance normalization technique is also shown to compensate for differences in probe placement, increasing the number of locations at which successful attacks can be performed by 226% on a 32-bit microcontroller. When combined with a new technique that identifies and filters signals in collected traces that are unrelated to the encryption operation, the number of traces required to perform successful attacks is reduced by 85.8% on average. These simple techniques can be performed on the same traces collected for a standard template attack—improving the results through post-collection processing only.

Finally, the use of Software Defined Radios (SDRs) to collect side-channel emissions is introduced and eliminates the need for an attacker to modify the target device. Side-channel emissions are collected passively, and encryption operations are identified in the collected emissions. A correlation-based frequency-dependent leakage mapping technique is introduced to evaluate a 32-bit microprocessor and shows how individual key bytes leak at different frequencies. Key-byte dependent leakage is observed in both SDR collected and triggered oscilloscope-based collections used to validate the SDR methodology; this research is the first to demonstrate effective differential side-channel attacks using SDRs. Successful attacks are demonstrated using two different SDRs, including a commercial \$20 USD digital television receiver with modified drivers.

### 1. Introduction

Modern cryptographic algorithms provide confidentiality and authenticity but their security relies on computational intractability [132]. The algorithms themselves are public knowledge but secret keys are used to encrypt and decrypt the information. Cryptographic systems based on reusable keys can be broken through a brute force attack, with the amount of time required to do so being an exponential function of key length. Security is achieved by making the amount of work needed to attack the cipher greater than the ability of an adversary to muster [114]. A cryptographic system is considered to be computationally secure if the number of calculations needed to decode the message or determine the key is impossible through practical means.

Modern ciphers are typically implemented on electronic devices that produce both intentional and unintentional emissions. The intentional emissions are the ciphertext resulting from an encryption operation or the plaintext resulting from a decryption operation. Using only the input and intentional emissions, i.e., the plaintext and ciphertext, the key used during the encryption cannot be determined because the computational complexity of the cipher is very high. The unintentional emissions are called side-channels. The side-channels that can be used to extract information from a device depend on the implementation, but may include power consumption [67], acoustic, electromagnetic (EM) [2], optical [116], and photonic [109] emissions, as well as variations in computation time [66].

Side-channel analysis (SCA) effectively bypasses the computational complexity of a cipher by attacking the implementation instead of the cipher itself [67]. Using the side-channel emissions from a device, properties of the intermediate values calculated by the cipher can be determined. When side-channel analysis is used to attack a device, the attack is referred to as a *side-channel attack* and cryptographic devices are a common target. The goal of a side-channel attack against a cryptographic device is to determine the secret key being used for encryption and decryption. If the operations being performed by the device are key dependent it may be possible to determine the key from a single observation of the side-channel. If only the data being processed changes, as is the case with the Advanced Encryption Standard (AES), differential statistics must be used to determine the secret key [67].

#### 1.1 Motivation

The field of SCA has continued to grow since timing and power consumption based attacks were first demonstrated by Kocher et al. in the 1990s [66,67]. Although the effectiveness of these attacks has been demonstrated in laboratory environments, many rely on the assumption that a powerful adversary has complete control over the cryptographic device being attacked [73]. It is frequently assumed the attacker 1) knows the plaintext or ciphertext being processed, 2) can place the EM probe within close proximity of the encryption device, and 3) can modify the cryptographic device to add a trigger; the trigger identifies when the encryption operation is being performed, providing precise timing information for collections made with a digital storage oscilloscope. For attacks based on profiling a similar device, it is assumed that similar devices produce EM emissions identical to the target device [24]. While these assumptions are practical in a academic setting, they may not be rational in operational scenarios where modifying the device is not an option or there is no access to a digital storage oscilloscope.

The objective of this research was to identify ways to reduce the number of assumptions needed for EM-based SCA attacks to make these attacks more practical in an operational scenario. Ideally, these new techniques would not reduce attack effectiveness. However, if a given technique reduces attack effectiveness but makes the attack possible by a less powerful attacker, it would still be considered useful.

### 1.2 Research Contributions

First, algebraic cryptanalysis is used to enhance an attack on the key schedule of the AES. By attacking the key schedule, the attack can be performed without knowledge of the plaintexts or ciphertexts associated with each collected side-channel emission [82]. Since the key is fixed and the key schedule is recalculated for each encryption operation on the target device, the side-channel emissions from multiple encryption operations can improve the key extraction rate. Uncertainty in the key extraction phase of the attack is reconciled using a satisfiability solver and an algebraic description of the cipher. A novel technique is developed to identify possible values of portions of the key schedule. The robustness of the attack is demonstrated by intentionally degrading the quality of the results by gradually moving the EM probe away from the encryption device [82].

Template attacks are a form of two-stage profiling attack, with the initial stage obtaining 'a priori' knowledge of the side-channel leakage for a specific device [24]. The profiling stage estimates the multivariate probability densities of the observable side-channels for the targeted intermediate value of the internal calculations performed within a cryptographic device. It is assumed that a powerful attacker would be able to procure a training device identical to the device being attacked. Although template attacks were originally proposed using power consumption data, they were extended to EM emissions [122]. For the attack to be successful, the EM emissions from the training device must be sufficiently similar to the EM emissions from the test device. While previous research assumed implicitly this to be true by collecting training data from the same device being attacked [3, 9, 24, 73, 92], this

assumption is challenged by performing template attacks with 40 PIC and 2 ARM microcontrollers [83,85].

When attacks performed with different training and test devices show degraded performance, each step of the template attack methodology is analyzed and evaluated. A number of simple, yet powerful, techniques are developed to improve cross-device template attacks [85]. A cross-device template attack is defined as a template attack that specifically uses traces from two different physical devices for the training and classification phases. These techniques identify and remove device dependent EM signals and compensate for differences in the distribution of collected EM emissions from different devices. In addition to differences between devices, these techniques effectively compensate for differences in collection parameters including probe type and placement [83]. Additionally, a process for creating a master template to attack any device within a family of devices is developed and shown to be effective.

Finally, the requirement for an attacker to have control of the target device is eliminated by collecting EM emissions using a Software Defined Radio (SDR) [84]. SDRs down-convert EM emissions from a device allowing data collection at reduced sampling rates, allowing side-channel data to be collected in real-time. Although individual traces must be identified in post-processing, the trigger signal is no longer necessary. The use of a SDR also dramatically reduces the cost of performing side-channel analysis [84].

### 1.3 Organization

This dissertation is organized as follows. Chapter 2 contains background information and a summary of recent publications that pertain to this research. Chapter 3 describes common methodology used in two or more of the focus areas. The next three chapters each contain the unique methodology and results from the four focus areas described above. Chapter 4 develops an algebraic cryptanalysis-based key

schedule redundancy attack. Chapter 5 improves the effectiveness of cross-device template attacks for PIC microcontrollers. In Chapter 6, cross-device attacks are expanded to more complex 32-bit microcontrollers and a new method is developed to identify and remove interfering signals. Chapter 7 introduces the used of SDRs to collect the EM emissions from a microprocessor. Finally, Chapter 8 concludes the dissertation and recommends areas for further study.

## 2. Background

#### 2.1 Introduction

Modern cryptographic algorithms provide confidentiality and authenticity services based on computational hardness assumptions [132]. Algorithms to secure information are public knowledge but secret keys are used to encrypt and decrypt the information. While cryptographic systems based on reusable keys can be broken through a brute force attack, the amount of time needed is an exponential function of the length of the key. Effective security is achieved by making the amount of work needed to attack the cipher more than the ability of an adversary to muster [114]. A cryptographic system is considered to be computationally secure if the number of calculations needed to decode the message or determine the key is impossible by any practical means.

In his article on the communication theory of secrecy systems, Claude Shannon said, breaking a good cipher should require "as much work as solving a system of simultaneous equations in a large number of unknowns [114]". In theory, a technique known as algebraic cryptanalysis can break ciphers by describing the cipher as a system of polynomial equations and solving this system to obtain the secret key. In practice, the multivariate systems of polynomial equations derived from modern ciphers are large and complex and it is not possible to solve the system in a reasonable amount of time [26]. To break the cipher, the complexity of such systems of equations must be reduced.

The complexity of solving the system can be reduced by finding a weakness in the algorithm, or by determining intermediate values calculated by an implementation of a cipher. A category of relatively low cost, non-intrusive attacks are called side-channel attacks. Side-channel analysis (SCA) can determine the properties of intermediate values calculated by a physical implementation of a cipher by

collecting and processing the side-channel emissions from the device performing the cryptographic operation [73].

The target of the side-channel attacks, the Advanced Encryption Standard (AES), and cryptanalysis techniques used against block ciphers are introduced in Section 2.2. The type of side-channels produced by modern electronic devices is discussed in Section 2.3. Next, how SCA is used to identify intermediate values is discussed in Section 2.4, followed by a brief discussion on countermeasures, and collecting and pre-processing of side-channel emissions. Finally, the process and benefit of combining algebraic cryptanalysis with SCA attacks is explored in Section 2.8.

## 2.2 Cryptography Preliminaries

Information prior to encryption is referred to as *plaintext*. Encrypted information is called *ciphertext*. *Encryption* is the process of converting plaintext to ciphertext. Similarly, *decryption* is the process of converting ciphertext to plaintext. The *cipher* is a pair of algorithms used to encrypt and decrypt information.

In symmetric key cryptography, the two communicating parties share a piece of secret information, the key, and a public encryption system. *Breaking* a cipher consists of "finding a weakness in the cipher that allows the cipher to be exploited with a complexity less than brute-force [110]".

2.2.1 Block Ciphers. Block ciphers are symmetric key ciphers that operate on groups of bits called blocks. The block cipher is keyed to a family of permutations which operate on n-bits at a time. A permutation is selected from the family using a key; the same key for both encryption and decryption [125]. Two commonly used ciphers are the Data Encryption Standard (DES) and AES.

The rounds of a block cipher are usually based on substitution boxes (S-boxes), bit permutations, arithmetic operations, and exclusive-ORs (XOR). S-boxes are non-linear substitution tables that map input bits to output bits. They are typically the

only part of a block cipher that is non-linear [16]. An iterated block cipher applies the round functions sequentially, taking the result of one round as the input to the next round.

Modern block ciphers can be traced back to Claude Shannon [114]. Shannon discussed the block ciphers based on the concepts of diffusion and confusion [28]. Diffusion spreads the influence of all parts of the block cipher inputs to all parts of the output, the ciphertext. For a block cipher, the inputs include the plaintext and the key. Confusion attempts to make the relationship between the ciphertext, the plaintext and the key complicated. In modern ciphers diffusion is typically achieved using permutations or linear transformations. Simple operations are repeated multiple times to achieve the desired level of security. Encryption/decryption operations are key dependent because key material is introduced in each round.

2.2.2 Advanced Encryption Standard. The Advanced Encryption Standard (AES) was developed to replace the Data Encryption Standard (DES) and triple-DES. The U.S. National Institute of Standards and Technology (NIST) conducted an open competition to develop AES which was to be as secure as triple-DES but much more efficient [39]. A block cipher called Rijndael was selected as the AES. Since Rijndael was announced as the AES in October 2000, AES has been used throughout the U.S. government and been adopted by banks, industry and governments around the world.

AES is a symmetric block cipher that processes blocks of 128 bits using cipher keys with lengths 128, 192 and 256 bits [88]. The basic processing unit for AES is a byte. The AES algorithm operations are performed on a two-dimensional array of bytes called the *State*. The State is a four row by four column matrix, with a byte in each cell. One round of AES is composed of the following four different byte-oriented transformations. [88]:

1. AddRoundKey: The state matrix is XOR-ed with the round key.

- 2. SubBytes: Each byte of the state matrix is substituted for another byte value based on a one-to-one non-linear invertible mapped called S-box,

- 3. ShiftRows: The last three rows of the state matrix are cyclically shifted columnwise using different offsets,

- 4. MixColumns: The state matrix is mixed column by column using a linear operation.

One round key, based on the original cipher key, is produced by the key expansion routine for each round. The final round does not include the MixColumns operation and another AddRoundKey operation is performed to produce the ciphertext.

SubBytes is the only non-linear step in each round. To resist linear and differential cryptanalysis (Ref. Section 2.2.3.1), the S-box was specifically chosen to be non-linear and have a high algebraic complexity. Confusion is achieved using carefully chosen S-boxes in AES. The S-box is based on the inversion over a field of order 2<sup>8</sup> [39]. The S-box is defined in [88]. Since inversion and matrix multiplication are computationally expensive, the S-box is frequently precomputed and stored in a table.

A key expansion routine generates the key schedule containing each of the round keys. The number of rounds is determined by the key size. AES performs 10, 12, and 14 rounds for key sizes of 128, 192, and 256 bits of key length respectively. Eleven round keys are produced by the key expansion routine for AES-128. The first round key is simply the cipher key and the subsequent round keys are calculated using the following transformations.

- 1. SubWord: The SubBytes transformation is performed on each byte of the fourbyte input word to produce a four byte output word,

- 2. RotWord: Performs a cyclic permutation on the four-byte input word, and

- 3. AddRcon: Bit-wise XOR with the round constant.

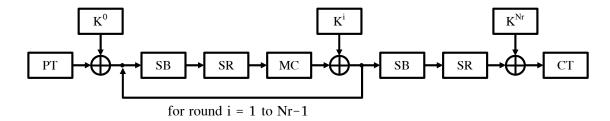

Figure 2.1 AES Cipher Structure [88].

The round constant is designed to eliminate symmetries [39]. For a given implementation, the round keys are either calculated "on the fly", or pre-calculated and stored in memory. On devices with a low amount of memory the round keys are generated as needed, writing over the previous round key in the process. More detailed information on the structure of the key schedule for AES-128 is presented in Chapter 4. The  $N_r = 10$  rounds of AES-128 is shown graphically in Figure 2.1. For conciseness the round transformations are abbreviated AddRoundKey (ARK), SubBytes (SB), ShiftRows (SR) and MixColumns (MC) in Figure 2.1.

In a 32-bit microprocessor, the operations performed in the round transformation can be combined into a single look-up-table, called a T-Box to create a faster implementation [38]. The  $8 \times 32$ -bit tables defined

$$T_{0}[a] = \begin{bmatrix} SB[a] \bullet 02 \\ SB[a] \\ SB[a] \end{bmatrix} \qquad T_{1}[a] = \begin{bmatrix} SB[a] \bullet 03 \\ SB[a] \bullet 02 \\ SB[a] \end{bmatrix}$$

$$T_{2}[a] = \begin{bmatrix} SB[a] \\ SB[a] \bullet 03 \\ SB[a] \bullet 02 \\ SB[a] \end{bmatrix} \qquad T_{3}[a] = \begin{bmatrix} SB[a] \\ SB[a] \\ SB[a] \bullet 03 \\ SB[a] \bullet 03 \\ SB[a] \bullet 02 \end{bmatrix}$$

$$T_{3}[a] = \begin{bmatrix} SB[a] \\ SB[a] \\ SB[a] \bullet 03 \\ SB[a] \bullet 03 \\ SB[a] \bullet 02 \end{bmatrix}$$

combine the SubBytes, ShiftRows and MixColumns operations.

The complete round transformation for a 32-bit block is calculated

$$e_c = T_0[a_{0,c}] \oplus T_1[a_{1,c-1}] \oplus T_2[a_{2,c-2}] \oplus T_3[a_{3,c-3}] \oplus k_j,$$

(2.2)

where c denotes the column of the output e,  $a_{r,c}$  denotes the row r and column c of one byte of the input state a, and  $k_j$  is corresponding 32-bit portion of the round key for round j. Column indices are taken modulo  $N_b = 4$  for AES-128. For AES-128, row  $r = n_b \mod 4$  for byte number  $n_b = 1, ..., 16$ .

Hence, each of the four 32-bit portions of the round output are implemented with four table lookups and four XORs. After performing the initial AddRoundKey, the T-box implementation is used to calculate the first 9 rounds of AES-128. In the 10th round, since the MixColumns operation is not performed, the SubBytes and ShiftRows operations are performed separately.

2.2.2.1 Modes of Operation. Since AES only encrypts data one block at a time, but the amount of data that must be encrypted is typically greater than one block, modes of operation have been developed. A mode of operation is a scheme that allows a block cipher to perform encryption and decryption on groups of plaintexts. NIST special publication 800-38A lists the modes of operations recommended for use with AES: Electronic Codebook (ECB), Cipher Block Chaining (CBC), Cipher Feedback (CFB), Output Feedback (OFB), and (CTR) [87].

In ECB mode the message is divided into blocks and each block is encrypted separately. The drawback of this approach is blocks with identical plaintexts are encrypted into identical ciphertexts. Patterns in the ciphertext may reveal information about the message being sent. However, since each block is encrypted separately, encryption of multiple blocks can be performed in parallel.

CBC, CFB, and OFB incorporate the output of previous encryption operations and utilize initialization vectors. In CTR mode the input blocks, called counters,

are encrypted using AES and the output of the encryption operation is XORed with the plaintext to produce the ciphertext. Since other modes incorporate additional information and restrict the order in which traces can be processed for side-channel analysis, only ECB mode is considered in this dissertation. For side-channel analysis using ECB mode allows for each trace to be analyzed independently.

- 2.2.3 Cryptanalysis of Block Ciphers. The goal of cryptanalysis is to break ciphers. The goal of most attacks is to recover the encryption or decryption key. Attacker's capabilities may vary. In this regard, the amount of information an adversary has access to changes the types of attacks that are possible. However it is assumed the attacker has full knowledge of the encryption algorithm and the key is always secret. Below is a taxonomy of cryptographic attacks adapted from [28] listed from most practical to most hypothetical.

- 1. Ciphertext-only: The adversary only has access to encrypted messages and some information about the distribution of the plaintext messages. Most modern ciphers are not susceptible to this type of attack.

- 2. Known plaintext: In addition to the ciphertext, the attacker has full or partial knowledge of corresponding plaintext messages. Since messages contain common words or patterns, such as headers, this type of attack is realistic.

- 3. Chosen plaintext or ciphertext: In a chosen plaintext attack the adversary has the ability to choose the plaintext messages to be encrypted. In a chosen ciphertext attack, the adversary can choose the ciphertext to be decrypted and has access to the corresponding plaintext. Although less common, this scenario is still realistic.

- 4. Adaptive chosen plain text or ciphertext: The adversary adapts his choices of the text to be encrypted and decrypted based on information learned during the attack.

5. Related Key: The adversary exploits a known relationship between keys (e.g., they only change by a certain number of bits). This attack is conducted in conjunction with one or more of the scenarios above.

This attack model applies to both algebraic cryptography attacks and sidechannel analysis. Proposed attacks cover the entire range of attack types, but known plaintext attacks are most common [28].

2.2.3.1 Linear and Differential Cryptanalysis. Linear cryptanalysis and differential cryptanalysis are the most established methods of attacking block ciphers. Statistical in nature, the attacker constructs probabilistic patterns through as many rounds of the cipher as possible. The goal is to distinguish the cipher from a random permutation and recover the key.

Linear cryptanalysis looks for the effective linear expression for a cipher [76]. A linear approximate is constructed by building a statistical linear path between input and output bits of each S-box. The linear approximate is the probability that S-box inputs coincide with an S-box output bit. Since this method is based on statistics developed for a specific key, it requires a large number of known plain-texts. Once each S-box is described as a linear approximate the entire algorithm is represented without any intermediate values.

Differential cryptanalysis analyzes the effect of particular differences in plaintext pairs on the differences in corresponding ciphertexts. Using these differences, probabilities can be assigned to possible keys to identify the most probable key [16]. Typically this type of attack is done with chosen plaintext, but can be done with known plaintext if a sufficient number are available [76].

AES was developed to be resistant to both linear and differential cryptanalysis. The wide tail strategy employed in AES maximizes the level of mixing within each round to provide fast diffusion ensuring security against differential and linear cryptanalysis [39].

Due to their statistical basis these attacks require enormous amounts of known or chosen plaintext/ciphertext and are therefore impractical for complex ciphers [5]. Conversely, a relatively new form of attack, algebraic cryptanalysis, requires very few, if any, known plaintexts.

2.2.3.2 Algebraic Cryptanalysis. Algebraic cryptanalysis breaks ciphers by solving polynomial systems of equations and exploiting the intrinsic algebraic structure of the cipher. Typically an attacker converts the encryption transformation into a large system of low degree multivariate polynomial equations and solves the system to reveal information about the key. A number of methods have been proposed for solving these systems of equations. If a cipher is well constructed, however, the system of equations will not be directly solvable. Since the systems are typically very sparse, over-defined, and structured, it is believed they can be solved faster than generic non-linear equation systems [5]. The used of algebraic cryptanalysis against AES is discussed in Section 2.8.

## 2.3 Side-Channel Leakage

A side-channel is an unintended observable phenomenon that is correlated with the internal state, operations or data being processed within a device. These correlations can be exploited to recover the leaked information. Electronic devices can leak information via a number of side-channels including power consumption [67], acoustic, electromagnetic (EM) [2], and optical [116] emissions, as well as variations in computation time [66]. Although initial research focused on timing, power consumption and EM emissions, optical analysis is becoming more practical [109].

2.3.1 Power Consumption. Digital circuits consume power during operation. The received energy is dissipated as heat and EM emissions. Many modern integrated circuits are based on Complementary Metal Oxide Semiconductors (CMOS) transistor technology that are the basis of various types of devices includ-

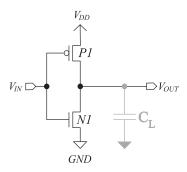

Figure 2.2 Lumped capacitor model of a CMOS inverter [73].

ing general purpose microprocessors and Field Programmable Gate Arrays (FPGAs). The power consumption of CMOS devices consists of static power consumption and dynamic power consumption. CMOS cells are based on complementary pull-up and pull-down networks. For constant input signals, the pull-up and pull-down networks never conduct at the same time. For the inverter shown in Figure 2.2, P1 is conducting and N1 is insulating when the input is set to GND. When the input is set to  $V_{DD}$ , P1 is insulating and N1 is conducting. For constant input signals there is only a small leakage current which contributes to the static power consumption,  $P_{stat} = I_{leak} \cdot V_{DD}$  [73].

Dynamic power consumption occurs when internal transistors change state. However, the power consumed by internal state changes is much lower than the power consumed by changing the CMOS cell output signal, therefore it can be ignored. When the value of the cell output does not change, only static power is consumed, but transitioning from  $0 \to 1$  or  $1 \to 0$  requires both static and dynamic power. One component of dynamic power consumption is due to the CMOS cell drawing a charging current from the power supply to change the output capacitance  $C_L$  during a transition.  $C_L$  is the intrinsic capacitance of the CMOS cell and the extrinsic capacitance of wires connected to subsequent CMOS cells. The second component of dynamic power consumption is due to the temporary short circuit that occurs when a CMOS cell switches and both pMOS and nMOS transistors conduct simultaneously. Dynamic power consumption is much higher than static power

consumption, in fact it is the primary source of power consumption. Furthermore, dynamic power consumption is always data dependent [73].

There are many factors that affect the power consumption of a microprocessor, including the instruction being executed and the memory address the instruction was retrieved from. Additionally, the data memory address, and the contents of the data being manipulated, and location of the data registers being accessed affect power consumption [95].

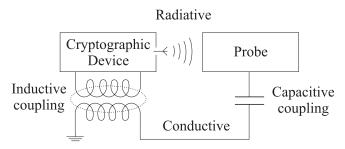

2.3.2 Electromagnetic Emissions. Electromagnetic (EM) emissions are caused by three types of coupling: conductive, inductive and radiative. This coupling is caused by time-varying current flows due to transistors turning on and off. Conductive coupling occurs when there is a physical conductive path between a source and a receptor allowing the signal to be transmitted through the system. Conductive emissions can be observed in the power supply, ground line, and cables attached to the device [2, 20].

An EM field is created when current flows through a wire. When two conductors are separated by less than a wavelength, mutual-inductive coupling or magnetic coupling can occur. Through EM induction, current flowing in one wire can induce a voltage across the ends of another wire. Low frequency signals are typically transmitted by inductive coupling. High frequency signals are more easily transmitted by capacitive coupling, whereby energy is transferred between to device nodes due to the capacitance between the two nodes. Inductive and capacitive coupling occur when the conductors are typically less than a wavelength apart. Radiative coupling occurs when the source and the receptor are separated by more than a wavelength; part of the source circuit acts as an antenna and transmits undesired EM waves [93].

EM emissions from digital electronics can be either differential-mode or commonmode radiation. Differential-mode radiation is generated by a flow of current around loops formed by conductors in the circuit during the circuit's normal operation.

Figure 2.3 EMI coupling modes [40].

The loops act as small antennas that primarily radiate magnetic fields. Differential-mode radiation emission is proportional to the loop area, frequency squared, and the differential-mode current in the loop. Common-mode radiation is caused by parasitics in the circuit and unintentional voltage drops in the conductors. Differential-mode currents flowing through the ground impedance produce a voltage drop in the device ground system, causing some grounded circuits to rise above the real ground potential. Bond wires and pins connected to the affected ground act like antennas radiating components of the common-mode potential as electric fields. Common-mode radiation is proportional to frequency, cable length and the common-mode current in the circuit [93].

2.3.2.1 Direct and Unintentional Emissions. The EM emissions from a device can be separated into two broad categories: direct and unintentional [2]. Direct emissions result from of intentional current flows, which consist of short bursts of current with sharp rising edges. These short bursts result in emissions observable over a wide frequency band. Components of the emissions at higher frequencies may be more useful if less interference or noise is present at higher frequencies. Isolating direct emissions can be very difficult in complex circuits due to interference by other signals [1]. To capture direct emissions with minimal interference, tiny near-field probes should be placed as close as possible to the signal source.

Modern CMOS devices have electronic and EM field coupling between components in close proximity, producing compromising *unintentional* emissions [2]. Mod-

ulations of a carrier signal, such as the harmonic rich "square-wave" clock may be produced within the device. As a result, odd harmonics of the clock can be strong carriers of modulated signals. Non-linear coupling between a carrier signal and a data signal can result in an amplitude modulated signal emanating from the device. The coupling between circuits can result in angle (or frequency) modulated signals. The modulated signals can propagate further than the direct emissions enabling attacks from further distances. Once collected, the data signals can be recovered using amplitude and angle demodulation techniques [2].

2.3.2.2 Exploiting Electromagnetic Emissions. Each current carrying component of a device produces EM emissions based on its physical and electrical characteristics as well as the data being processed [2]. An attacker that can analyze emissions and determine how the data being processed corresponds to the emissions would be able to compromise the system. As a result, methods originally developed for power analysis have also been applied to EM Analysis (EMA) [47].

Since power measurements are collected by placing a resistor in series with the power or ground of the cryptographic device physical access to the device is required. EM measurements are less invasive because physical contact with the device is not necessary. Even so, to reduce noise and increase the signal strength EM measurements are typically performed as close as possible to the chip using a near-field probe. Ideally, the probe is placed near the part of the device with the most intense data-dependent signal. This is typically near the CPU, data lines or power supply lines [47]. Although no physical contact to the device is required, it is assumed the attacker has the ability to place the probe in the near-field.

The phenomenon of compromising power and EM emissions has been known and exploited for decades. Declassified TEMPEST documents reveal vulnerabilities of United States cryptographic systems to EM analysis in 1962 and Soviet guidelines for radio frequency interference indicated they recognized the threat before the

United States [20]. Academic research on the vulnerability of cryptographic devices to EM analysis has flourished in the last decade when attacks performed using power analysis were extended to collected EM emissions [47,94]. Since power and EM attacks are related and many of the same techniques apply, attacks are not grouped by side-channel and are presented in Section 2.4

2.3.3 Other Side-Channels. Although the power and EM side-channels are the most commonly attacked, other side-channels have been used to attack cryptographic systems. By carefully measuring and analyzing the amount of time required to perform a cryptographic operation, a secret key can be determined when the length of the operation depends on the secret key [66]. The optical side-channel has been used to enhance side-channel attacks. By observing photon emissions from switching of transistors, the active area of an integrated circuit can be identified to allow targeted EM and power attacks [116]. Attacks based on acoustic emissions have been demonstrated on desktop computer CPUs [111], keyboards [10, 138] and dot matrix printers [51].

Differential fault injection extends existing side-channel analysis methods by actively injecting faults into a system in the hope the internal state of the system will be revealed. Faults can be induced in a variety of ways including over-clocking, powering at unsupported voltages, or even targeting the device with radiation [17].

2.3.4 Leakage Models. At the transistor level the static and dynamic power consumption can be modeled with approximations that describe the power consumption well. For more complex circuits, power models and simulations can estimate the power consumption, efficiency and security. Highly accurate models require a high level of memory, time to simulate, and intricate knowledge of the device. Analog simulations use transistor netlists and circuit parasitics to calculate power consumption. Precise circuit parasitics will result in a precise simulation. Logic level simulations requiring fewer resources are less accurate, but still require

a netlist containing all logic cells in the circuit and the connections between them. More accurate logic level simulations will contain signal delays, rise and fall times and accurate power models for each cell. Analog and logic level models required detailed knowledge that is typically only available to the device designers [73].

Models based on Hamming Weight and Hamming Distance are presented in the next two sections. Although these models are not as accurate, they are useful because they do not required detailed information about the layout and device being used.

2.3.4.1 Hamming Weight Model. A model based on the Hamming Weight (HW) assumes the power consumption is proportional to the number of bits equal to 1 in the processed value and does not require any information about the values processed before or after [73]. Although CMOS power consumption depends on whether a transition occurs and not on the values being processed, HW models can still be useful for some applications. The utility of each model depends on the implementation.

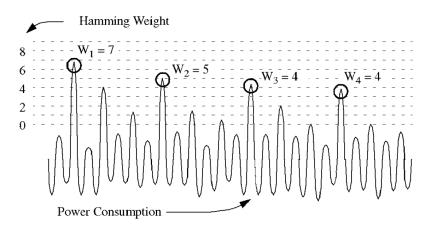

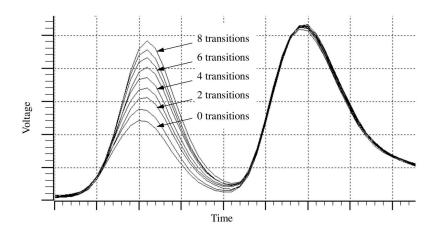

In the best case, the preceding or succeeding values are known, for example, a precharged bus on a microprocessor. If all of the bits of a data bus are set to 0 before the value of interest is placed on the bus, the HW is determined only by the values being placed on the bus [78]. Figure 2.4 shows an example of how the power consumption changes based on the HW of the data being processed.

2.3.4.2 Hamming Distance Model. Hamming Distance (HD) is the number of bit-level transitions  $(0 \to 1 \text{ or } 1 \to 0)$  that occur during a certain interval. As discussed above, power consumption is primarily caused by the output of logic cells transitioning from one state to another. The HD model is a simplified power model based on a count of the transitions over a period of time. For simplicity it is assumed that the power required for transitions from  $0 \to 1$  and  $1 \to 0$  are equal. The parasitic capacitances of wire and cells and the static power consumption

Figure 2.4 HW information revealed by the a power consumption side-channel [78].

are also ignored for simplicity. The HD of two values  $v_0$  and  $v_1$  is equal to the HW of  $v_0 \oplus v_1$ . Since HW is equal to the number of bits that are set to one,  $HD(v_0, v_1) = HW(v_0 \oplus v_1)$  [73].

To calculate HD, consecutive data values processed in part of a circuit must be known or guessed. HD can be effective for modeling the power consumption of registers and buses when the values placed in the register or on a bus are determined by the algorithm being attacked, known plaintext or ciphertext value, and key guesses. Advanced HD models assign the power consumption for the transitions between  $0 \to 1$  and  $1 \to 0$  differently. Figure 2.5 shows how the number of transitions effects the power leakage of an 8-bit smartcard microcontroller.

The worst case is when the preceding and succeeding values are random and uniformly distributed. If this occurs the HW and HD models will not be highly correlated with the power consumption. However, since the power consumed for the transitions between  $0 \to 1$  is not truly equal to the power consumed by  $1 \to 0$  transition, the HW model will still be weakly related in some way to the actual power consumption [73].

Figure 2.5 HD power leakage from an 8-bit smart-card microcontroller performing a load operations [78].

2.3.4.3 Applying Power Models to Electromagnetic Emissions. Combining Ohm's law (I = V/R) with with Joule's law (P = IV), the power in a resistive circuit current is directly proportional to the current squared  $(P = I^2R)$ . It follows that models that describe power consumption also correspond with EM emissions. If the power consumption of a device is data dependent, the EM emission will also be data dependent.

Before introducing how these models can be used to extract information from a device, it is helpful to understand the cipher being targeted by the attacks. Block ciphers are presented in the following section. Side-channel attacks that used HW and HD models are introduced in Section 2.4.

# 2.4 Side-Channel Attacks

Modern cryptographic ciphers, including AES, were developed assuming that the hardware used to implement them was secure. Given that assumption, the focus was on proving the underlying mathematical structure of the cipher is computationally secure. When developing a cryptographic cipher it is generally assumed that the cryptographic systems behave like a black box in which plaintext is securely turned into ciphertext.

Rather than attack the cryptographic algorithm itself in the hopes of finding a mathematical vulnerability, side-channel analysis targets the devices used to implement the cryptographic algorithms. The goal of Side-Channel Analysis (SCA) is to learn information about the internal state, data or operations being performed. Side-channel attacks can also be used to bypassing or compromise the system's security.

2.4.1 Types of Implementation Attacks. Attacks on cryptographic devices can be active or passive [73]. During a passive attack the device performs its normal operations with little or no interference by the attacker. In an active attack, the device, its environment or inputs are manipulated to make the device behave abnormally. The abnormal behavior is analyzed to compromise the secret key.

Attacks can be invasive [8], semi-invasive [117] and non-invasive. In an invasive attack there is no limitation to what can be done to the device. The devices are typically depackaged to access specific components of the device using a probing station. If the probing station only observes the component, the attack is passive. If signals in the device are changed to alter the function of the device, the attack is active. Invasive attacks typically require expensive specialized equipment. In a semi-invasive attack the device is depackaged but, no direct electrical contact is made with the chip surface. Active semi-invasive attacks may induce faults using X-rays, EM fields, light or lasers. In a non-invasive attack, the device is attacked without altering the device leaving no evidence of an attack. Active non-invasive attacks attempt to cause faults without depackaging the device. The faults can be introduced by clock glitches, power glitches or by changing the operating environment. In general, side-channel attacks are non-invasive or semi-invasive.

2.4.2 Adversary Models. Similar to the cryptanalysis model in Section 2.2.3, the abilities and knowledge attackers possess varies. The power of an adversary is determined by the amount of knowledge and control he theoretically has over the

cryptographic system during a particular attack. A *weak* attacker will have very restricted access, while a *powerful* attacker will have complete control of the device.

Powerful attackers are able to choose the number and contents of device inputs, and are able to observe the encryption/decryption operation in an ideal environment. Measures may be taken to optimize the quality of the observed side-channel, such as decapsulation and adding a hardware trigger to precisely determine when the cryptographic operation begins [73]. In extreme cases, the attacker may have the ability to load new keys into the device or a similar training device. The attacker may also collect multiple traces for each plaintext and average the traces together to reduced environmental noise in the trace.

A weak adversary has less control over the device. The adversary has the ability to observe the device being attacked in some way, but no special measures are taken to improve the quality of the collected traces. As a result, the traces may be noisy and timing may be poor. Typically it is assumed that the adversary is able to collect either the plaintext or the ciphertext from the device. In extreme cases, only the side-channel can be observed.

2.4.3 Power and EM Analysis. The introduction of power analysis in 1999 by Kocher et al. gave rise to a new field of side-channel attacks and countermeasures [67]. By observing and analyzing the power consumption of a device performing a cryptographic operation, information about the device's operation and data the device is processing can be determined. A side-channel attack targets a vulnerability in the implementation rather than attacking the cryptographic algorithm. Depending on the implementation and resolution of measurement devices an attack may be performed with a single trace. A trace is a set of side-channel emission measurements over the length of the cryptographic operation of interest. Any observable behavior that can be correlated to the internal operation of a device can reveal information about the device.

Figure 2.6 SPA analysis from an RSA implementation [68].

A large number of attack types have been developed, but the three most important distinguishing characteristics are the analysis approach, the number of traces used, and the number of phases involved in an attack.

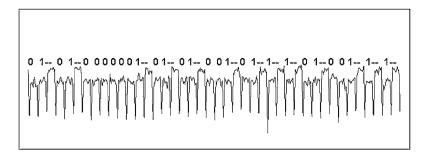

2.4.4 Simple Side-Channel Analysis. Some cryptographic implementations are susceptible to Simple Side-Channel Analysis (SSCA) in which information about the device's operation and key material is determined from direct interpretation of the power or EM emission traces. In [67] Kocher et al. introduced simple power analysis (SPA) noting that weaknesses in the implementation of an algorithm such as conditional jumps based on key bit's value and computational intermediates, reveal information about the key. Processing time may vary for various reasons including conditional branches, cache misses, pipeline stalls, interfacing with memory and external devices [66]. As a result, SPA can determine the sequence of operations for a cryptographic implementation. If the order or length of operations are dependent on key bit values, the value of the key bits may be determined from the power trace. The techniques used for SPA were extended to EM emissions in [94] and called simple EM power analysis (SEMA).

Figure 2.6 shows power traces from a device implementing public-key cryptography algorithm RSA<sup>1</sup> [68]. In this implementation, a square operation is performed in every iteration of the exponentiation loop but a multiplication is only performed

<sup>&</sup>lt;sup>1</sup>The RSA algorithm is named for Ron Rivest, Adi Shamir and Leonard Adleman [33].

when a bit of the exponent is 1. Each 1 bit in the secret key appears as a shorter bump followed by a taller one, each 0 bit appears only as a shorter bump. The key can be read directly from the measured power consumption.

Differential Side-Channel Analysis. Even when SSCA is not possible, differential side-channel analysis (DSCA) can be used whenever a physical, measurable property of the device depends on the data it processes. Differential Power Analysis (DPA), introduced in [67], takes small variations in power consumption between multiple traces to find correlation between the intermediate values in the cryptographic computation and the measured power consumption. Although the variations are small, by collecting a large number of traces, the implementation can be broken using statistical functions tailored to the target algorithm and device [67]. A DPA attack uses the power traces from multiple observed encryption operations, typically with different plaintext/ciphertext. Using the recorded plaintext or ciphertext and traces from the operations, the attacker calculates differential statistics based on a key block guess. DPA is capable of extracting information even when the variations in side-channel are too subtle to be identified using SPA. The techniques used in DPA were extended to EM emissions and called differential EM analysis (DEMA) [94]. The step-by-step process for conducting model-based DPA is explained in Section 3.4. Differential attacks typically assume a powerful adversary that can arbitrarily change the plaintext to perform desired encryption operations. At a minimum the attacker must have knowledge of the plaintext or ciphertexts associated with each trace.

Differential attacks can be used even if detailed knowledge of the implementation is not known. While SSCA requires the attacker recognize when certain operations occur in side-channel leakage, DSCA techniques identify the points in time when side-channel leakage is correlated with a hypothetical intermediate values in the cryptographic operation. As a result, the attacker only needs to know the underlying algorithm so that hypothetical intermediate values can be calculated, to

carry out an attack. Even when the algorithm is not known, an attacker can perform SSCA and DSCA to learn details about the implementation sufficient to perform a successful attack [73].

The number of observations required to successfully perform DSCA depends on the implementation, statistical technique, environmental factors and countermeasures protecting the device. The number of traces required can vary from a few dozen to millions [73].