### Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-21-2013

# Firmware Counterfeiting and Modification Attacks on Programmable Logic Controllers

Zachary H. Basnight

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Controls and Control Theory Commons

#### Recommended Citation

Basnight, Zachary H., "Firmware Counterfeiting and Modification Attacks on Programmable Logic Controllers" (2013). *Theses and Dissertations*. 853.

https://scholar.afit.edu/etd/853

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

#### THESIS

Zachry H. Basnight, First Lieutenant, USAF

AFIT-ENG-13-M-06

### DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

### AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

#### DISTRIBUTION STATEMENT A

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, the Department of Defense, or the United States Government. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This material is declared a work of the U.S. Government and is not subject to copyright protection in the United States.                                                                                  |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

#### **THESIS**

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Master of Science in Cyber Operations

Zachry H. Basnight, B.S.C.S. First Lieutenant, USAF

March 2013

**DISTRIBUTION STATEMENT A**APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

Zachry H. Basnight, B.S.C.S. First Lieutenant, USAF

| Approved:                          |                    |

|------------------------------------|--------------------|

| Maj Jonathan Butts, PhD (Chairman) | S Mac 13 Date      |

| Maj Thomas Dube, PhD (Member)      | 8 MAR 13<br>Date   |

| Juan Lopez Jr. (Member)            | Ø8 MARZØ13<br>Date |

#### **Abstract**

Recent attacks on industrial control systems (ICSs), like the highly publicized Stuxnet malware, have perpetuated a race to the bottom where lower level attacks have a tactical advantage. Programmable logic controller (PLC) firmware, which provides a softwaredriven interface between system inputs and physically manifested outputs, is readily open to modification at the user level. Current efforts to protect against firmware attacks are hindered by a lack of prerequisite research regarding details of attack development and implementation. In order to obtain a more complete understanding of the threats posed by PLC firmware counterfeiting and the feasibility of such attacks, this research explores the vulnerability of common controllers to intentional firmware modifications. After presenting a general analysis process that takes advantage of various techniques and methodologies applied to similar scenarios, this work derives the firmware update validation method used for the Allen-Bradley ControlLogix PLC. A proof of concept demonstrates how to alter a legitimate firmware update and successfully upload it to a ControlLogix L61. Possible mitigation strategies discussed include digitally signed and encrypted firmware as well as preemptive and post-mortem analysis methods to provide protection. Results of this effort facilitate future research in PLC firmware security through direct example of firmware counterfeiting.

#### **Table of Contents**

|     |         | I                                                                | Page |

|-----|---------|------------------------------------------------------------------|------|

| At  | stract  |                                                                  | iv   |

| Ta  | ble of  | Contents                                                         | v    |

| Lis | st of F | gures                                                            | viii |

| Lis | st of A | cronyms                                                          | X    |

| I.  | Intro   | luction                                                          | 1    |

|     | 1.1     | Background                                                       |      |

|     | 1.2     | Motivation                                                       |      |

|     | 1.3     | Research Goals                                                   |      |

|     | 1.4     | Approach                                                         |      |

|     | 1.5     | Impact                                                           |      |

|     | 1.6     | Organization                                                     | 4    |

| II. | Back    | ground                                                           | 6    |

|     | 2.1     | Industrial Control Systems                                       | 6    |

|     | 2.2     | Industrial Control System Security                               |      |

|     | 2.2     | 2.2.1 History                                                    |      |

|     |         | 2.2.1.1 Past Incidents                                           |      |

|     |         | 2.2.1.2 Stuxnet                                                  | 9    |

|     |         | 2.2.2 Future Threats                                             |      |

|     | 2.3     | Programmable Logic Controller Security                           | 11   |

|     | 2.5     | 2.3.1 Programming Layer                                          | 11   |

|     |         | 2.3.2 Hardware Layer                                             |      |

|     |         | 2.3.3 Firmware Layer                                             | 15   |

|     | 2.4     | Previous Works on Reversing Firmware                             |      |

|     | 2       | 2.4.1 Discovering Backdoors in Ethernet Modules                  | 16   |

|     |         | 2.4.2 Creating Custom Firmware for Ethernet Modules              | 18   |

|     |         | 2.4.3 General Processes for Reverse Engineering Embedded Devices | 19   |

|     |         | 2.4.4 Hardware Debugging                                         | 21   |

|     |         | 2.4.5 Checksum Algorithms                                        | 23   |

|     | 2.5     | Summary                                                          |      |

|     |         | ~ <del>~~~~~</del> j                                             | _0   |

|      |        |          |                                                 | Page |

|------|--------|----------|-------------------------------------------------|------|

| III. | . Metł | nodolog  | y                                               | 28   |

|      | 3.1    | Proble   | m Definition                                    | 28   |

|      | 3.2    |          | ach and Scope                                   |      |

|      | 3.3    | Test E   | nvironment and Tools                            | 30   |

|      | 3.4    | Revers   | sing Process                                    | 30   |

|      |        | 3.4.1    | Firmware Acquisition                            |      |

|      |        | 3.4.2    | Binary Analysis                                 | 31   |

|      |        | 3.4.3    | Disassembly                                     | 33   |

|      |        | 3.4.4    | Derivation of Firmware Update Validation Method | 34   |

|      |        | 3.4.5    | Reversing Process Considerations                | 34   |

|      | 3.5    | Vulner   | rability Assessment                             | 35   |

|      |        | 3.5.1    | Firmware Update Validation Method Analysis      | 35   |

|      |        | 3.5.2    | Demonstration                                   | 37   |

|      | 3.6    | Summ     | ary                                             | 38   |

| IV.  | Reve   | ersing P | rocess, Testing, and Demonstration              | 39   |

|      | 4.1    | Revers   | sing Process                                    | 39   |

|      |        | 4.1.1    | Firmware Acquisition                            |      |

|      |        | 4.1.2    | Binary File Analysis                            |      |

|      |        |          | 4.1.2.1 Manual Inspection                       |      |

|      |        |          | 4.1.2.2 Binary Comparison                       |      |

|      |        |          | 4.1.2.3 Embedded File and Filesystem Analysis   |      |

|      |        | 4.1.3    | Firmware Disassembly                            |      |

|      |        |          | 4.1.3.1 Processor Determination and Disassembly |      |

|      |        |          | 4.1.3.2 Rebuilding Functions                    |      |

|      |        |          | 4.1.3.3 Determining Base Address                |      |

|      |        |          | 4.1.3.4 Inspecting Strings                      |      |

|      |        |          | 4.1.3.5 Rebuilding Symbols                      |      |

|      |        | 4.1.4    | Derivation of Firmware Update Validation Method |      |

|      |        |          | 4.1.4.1 Disassembly Analysis                    |      |

|      |        |          | 4.1.4.2 Black Box Testing                       |      |

|      |        |          | 4.1.4.3 Hardware Debugging                      |      |

|      | 4.2    | Firmw    | are Update Validation Method Analysis           |      |

|      |        | 4.2.1    | Verification of Correctness                     |      |

|      |        | 4.2.2    | Design Analysis                                 |      |

|      |        | 4.2.3    | Refinement                                      |      |

|      | 4.3    |          | nstration                                       |      |

|      |        | 4.3.1    | Firmware Modification                           |      |

|      |        | 4.3.2    | Device Exploitation                             |      |

|      | 4 4    | Discus   |                                                 | 72   |

|     |        |          |            |         |        |         |       |     |     |     |    |       |  |       |   |      | P | age |

|-----|--------|----------|------------|---------|--------|---------|-------|-----|-----|-----|----|-------|--|-------|---|------|---|-----|

|     | 4.5    | Summ     | ary        |         |        |         |       |     |     |     |    | <br>• |  |       |   | <br> |   | 79  |

| V.  | Conc   | clusions | and Futu   | re Wo   | rk     |         |       |     |     |     |    | <br>• |  |       |   | <br> |   | 80  |

|     | 5.1    | Conclu   | usions     |         |        |         |       |     |     |     |    |       |  |       |   | <br> |   | 80  |

|     | 5.2    |          | cance      |         |        |         |       |     |     |     |    |       |  |       |   |      |   |     |

|     | 5.3    | _        | Work       |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 83  |

|     |        | 5.3.1    | Direct E   |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 83  |

|     |        | 5.3.2    | Preventa   |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 83  |

|     |        | 5.3.3    | Detection  |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 85  |

|     |        |          | 5.3.3.1    |         | rect M |         |       |     |     |     |    |       |  |       |   |      |   | 85  |

|     |        |          | 5.3.3.2    |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 86  |

|     | 5.4    | Summ     | ary        |         |        |         |       |     |     |     |    |       |  |       |   |      |   | 87  |

| Αŗ  | pendi  | x A: Co  | ontrolLog  | ix Firn | nware  | Opera   | ation | Flo | wcl | har | ts | <br>• |  |       |   | <br> |   | 88  |

| Αŗ  | pendi  | x B: Co  | ontents of | Firmw   | vare U | pdate   | Pack  | age |     |     |    |       |  |       |   | <br> |   | 90  |

| Αŗ  | pendi  | x C: VI  | BinDiff E  | xample  | es     |         |       |     |     |     |    |       |  |       |   | <br> |   | 92  |

| Αŗ  | pendi  | x D: Ph  | ıysical Co | mpone   | ent An | ıalysis |       |     |     |     | •  |       |  | <br>• |   | <br> | • | 94  |

| Αŗ  | pendi  | x E: So  | urce Code  | e       |        |         |       |     |     |     |    | <br>• |  |       |   | <br> |   | 98  |

| Αŗ  | pendi  | x F: ID  | A Scripts  |         |        |         |       |     |     |     |    | <br>• |  |       |   | <br> |   | 99  |

| Αŗ  | pendi  | x G: AI  | RM DS-5    | Debug   | gger S | cripts  |       |     |     |     |    | <br>• |  |       |   | <br> | • | 102 |

| Bil | bliogr | aphy .   |            |         |        |         |       |     |     |     |    |       |  |       | _ |      |   | 103 |

### **List of Figures**

| Figu        | re                                                                     | Pag | ge |

|-------------|------------------------------------------------------------------------|-----|----|

| 2.1         | Typical structure of a SCADA system [55]                               |     | 7  |

| 2.2         | Operational layers of a programmable logic controller                  | 1   | 12 |

| 3.1         | Reversing Process                                                      | 3   | 32 |

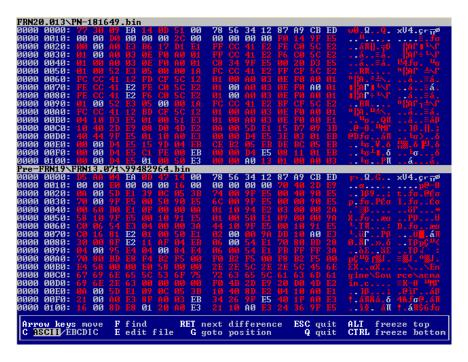

| 4.1         | Contents of PN-86270.RES in HxD                                        | 4   | 41 |

| 4.2         | Beginning of FRN19.011 binary in HxD                                   | 4   | 12 |

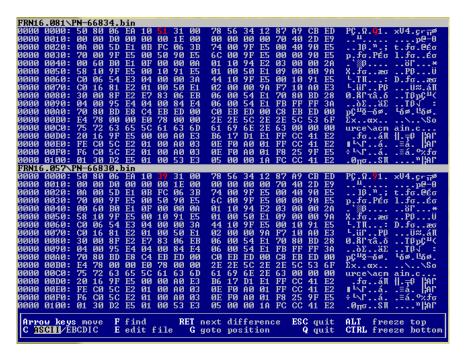

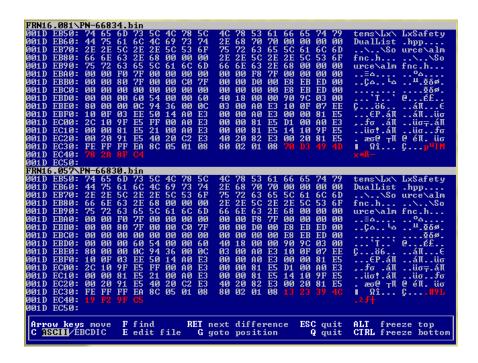

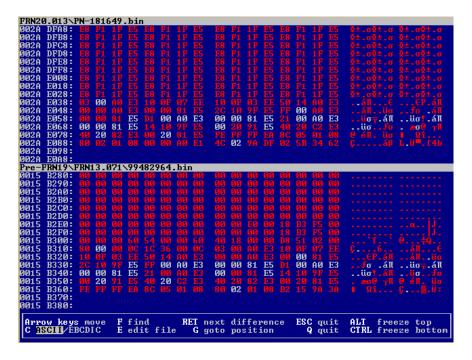

| 4.3         | VBinDiff of the beginning of FRN20.013 and FRN13.071                   | 4   | 43 |

| 4.4         | List of gzip file candidates identified by Binwalk                     | 4   | 46 |

| 4.5         | Initial IDA disassembly status                                         | 4   | 46 |

| 4.6         | IDA status after function identification                               | 4   | 17 |

| 4.7         | ARM compiler version string                                            | 4   | 19 |

| 4.8         | BigDigits library copyright string                                     | 4   | 19 |

| 4.9         | OUTPUT_COMPENSATION data structure strings                             | 4   | 50 |

| 4.10        | Example symbol string usage                                            | 4   | 51 |

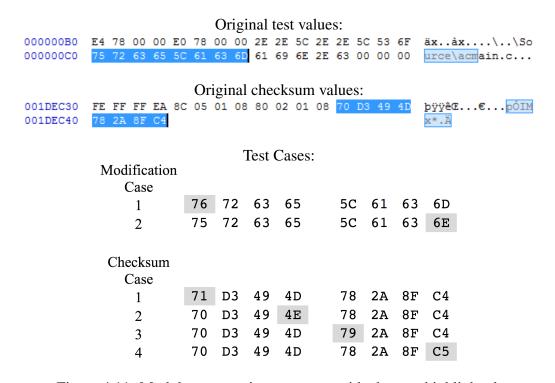

| 4.11        | Modular summation test cases with changes highlighted                  | 4   | 57 |

| 4.12        | Terminal commands for RevEng search cases                              | 4   | 59 |

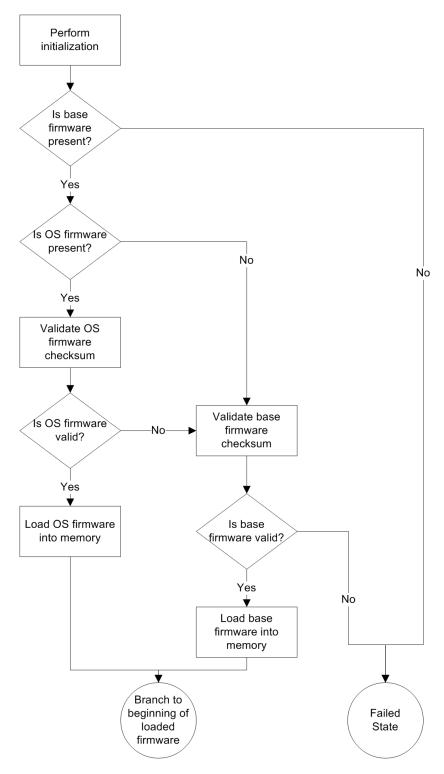

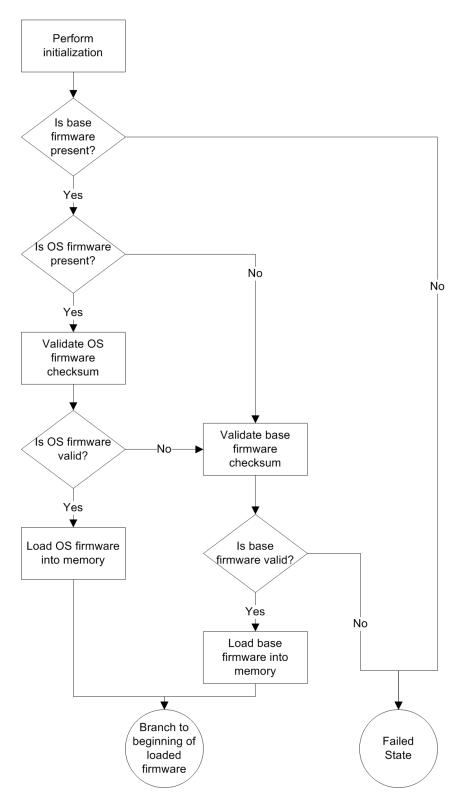

| 4.13        | Flow chart of ExecLoader.s                                             | 6   | 55 |

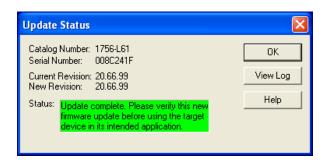

| 4.14        | Modification of FRN 16.081 version number in function to 20.066.099    | 7   | 71 |

| 4.15        | Modification of FRN 16.081 version number in header to 20.066.099      | 7   | 71 |

| 4.16        | Successful firmware update to FRN 16.081 with spoofed 20.66.99 version |     |    |

|             | number                                                                 | 7   | 72 |

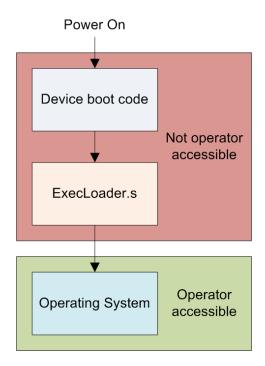

| <b>A.</b> 1 | Overview of ControlLogix L61 operation                                 | 8   | 88 |

| A.2         | Flow chart of ExecLoader.s                                             | 8   | 39 |

| B.1         | Contents of PN-86270.RES in HxD                                        | Ç   | 91 |

| Figu | re                                                        | Pa | ge |

|------|-----------------------------------------------------------|----|----|

| B.2  | Beginning of FRN19.011 binary in HxD                      |    | 91 |

| C.1  | VBinDiff of FRN16.081 and FRN16.057 beginning             |    | 92 |

| C.2  | VBinDiff of FRN16.081 and FRN16.057 end                   |    | 92 |

| C.3  | VBinDiff of FRN20.013 and FRN13.071 beginning             |    | 93 |

| C.4  | Length-corrected VBinDiff of FRN20.013 and FRN13.071 end  |    | 93 |

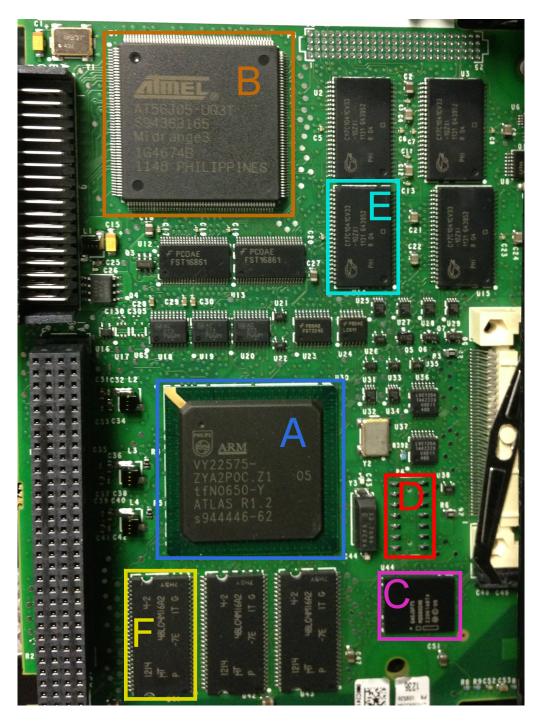

| D.1  | Circuit board of the 1756-L61/B                           |    | 94 |

| D.2  | 14-pin ARM JTAG pin configuration as viewed in Figure D.1 |    | 96 |

#### **List of Acronyms**

Acronym Definition

ARM Advanced RISC Machine

ASCII American Standard Code for Information Interchange

CISC complex instruction set computing

CRC cyclic redundancy check

cramfs compressed read-only memory (ROM) file system

DCS distributed control system

ELF executable and linkable format

FRN firmware revision number

IC integrated circuit

ICE in-circuit emulator

ICS industrial control system

IDA Interactive Disassembler

IDS intrusion detection system

IEEE Institute of Electrical and Electronics Engineers

IO input/output

IP internet protocol

IPS intrusion prevention system

IT information technology

JFFS2 Journalling Flash File System version 2

JTAG Joint Test Action Group

LRC longitudinal redundancy check

LZMA Lempel-Ziv-Markov chain algorithm

MD message digest

Acronym Definition

NIST National Institute of Standards and Technology

OS operating system

PE portable executable

PLC programmable logic controller

RAM random-access memory

RISC reduced instruction set computing

ROM read-only memory

RSA Rivest, Shamir, Adleman

SCADA supervisory control and data acquisition

SHA secure hash algorithm

TAP test access port

TCP transmission control protocol

UART universal asynchronous receiver/transmitter

XML Extensible Markup Language

XOR exclusive or

YAFFS Yet Another Flash File System

#### I. Introduction

#### 1.1 Background

Modern industrial applications necessitate the utilization of advanced automation and management networks collectively referred to as industrial control systems (ICSs). Such systems are responsible for the precise and consistent operation of many applications associated with national critical infrastructure. As ICSs become increasingly reliant on modern information technology (IT) solutions, including internet protocol (IP)-based networking and embedded computing, related security concerns also arise [55]. The progressive amalgamation of these technologies from two traditionally distinct cultures creates an apparent schism in the cyber security capabilities of IT and ICS environments. ICS cyber security implementations lag behind the sophistication of more dedicated IT solutions by comparison.

Cyber attacks on ICSs are increasing in number and scale [24]. Incidents like the 2010 Stuxnet worm exemplify this fact and provide insight into the future of cyber-based threats. Similar to traditional attacks on IT systems, ICS attacks are targeting lower level control to allow for more powerful and flexible system manipulation. The allure of ICS attacks, and the ultimate goal of such malicious manipulation, is the ability to elicit physical manifestations through cyber means. As the final link between cyber and physical components of ICSs, programmable logic controllers (PLCs) are critical in the proper operation of such systems. PLCs are embedded devices programmed to manage and control physical components responsive to system inputs and requirements. The lowest abstraction

layer controlling PLC interpretation of programming, the firmware, represents a significant potential threat if compromised. Indeed, the malicious modification or counterfeiting of controller firmware allows complete control over the device and any physical system components under its purview.

#### 1.2 Motivation

Defensive strategies to mitigate firmware threats must be established. In order to develop effective defense strategies, the threat must be thoroughly understood. Currently, little information detailing this threat is readily available. However, if an attacker is able to successfully manipulate the firmware on a PLC, they can directly control the behavior of the device to affect the control system while simultaneously masking such actions from the operator or control software. Although the risk exists, the extent to which an attacker is capable of exploiting the risk is unknown. There are currently no known examples of firmware modification attacks on PLCs [24]. Furthermore, research requiring the availability of malicious or counterfeit firmware lacks test samples for use in analysis. The creation of custom counterfeit firmware samples can aide in the development of detection and forensic analysis techniques.

#### 1.3 Research Goals

The goal of this thesis is to determine the feasibility of firmware modification attacks on PLCs. Specifically, this research investigates and assesses the vulnerability of a common PLC to counterfeit firmware updates. This research proposes that common PLCs are vulnerable to such an attack as a result of design weaknesses associated with firmware update validation methods. This may be verified by a successful demonstration of counterfeit firmware uploaded to a common PLC.

#### 1.4 Approach

To test a PLC's vulnerability to counterfeit firmware attacks, the firmware update validation method is derived through reverse engineering techniques. The firmware update validation method is analyzed for weaknesses that facilitate firmware counterfeiting. Weaknesses are exploited to create a counterfeit firmware sample that is uploaded and executed on a PLC. This approach is applied to a relevant test environment, consisting primarily of an Allen-Bradley ControlLogix L61 controller, to allow for a realistic assessment of the potential vulnerability on a common PLC.

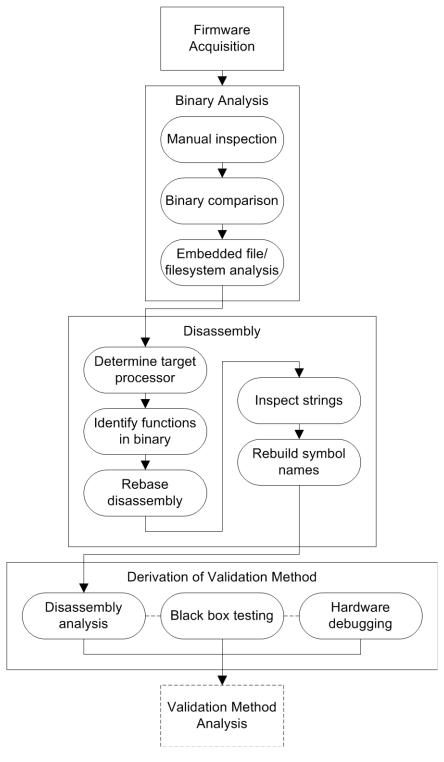

The process to derive the firmware update validation method is based on a review of previous research describing techniques related to the reverse engineering of PLCs and other types of embedded devices. By combining and organizing these techniques, a general process is conceived for deriving the firmware update validation method of a PLC. The major steps in the process are: (i) firmware sample acquisition, (ii) binary analysis of firmware, (iii) firmware disassembly, and (iv) derivation of the firmware update validation method. Step (iv) is further broken down into three approaches: (a) disassembly analysis, (b) black box analysis, and (c) hardware debugging analysis.

Firmware samples are obtained directly from the vendor website as firmware update packages. The firmware binaries are extracted from these packages. Following sample acquisition, binary analysis of the firmware files determine likely image formats and identify sections of interest related to validation (e.g., header information and candidate checksum fields). Firmware disassembly requires the determination of the target processor architecture, disassembly of binary to assembly code, identification of assembly functions, determination of the firmware base address, string analysis, and rebuilding function names in the disassembly.

For derivation of the firmware update validation method, disassembly analysis consists of searching for strings or recovered function names relevant to validation. Black box

analysis uses characteristics of common validation algorithms to narrow the search space as well as brute force techniques to attack the firmware update validation method. Hardware debugging is also used to physically connect to the controller. This enables direct access to the execution path of the processor and device memory including the executive loader, which is typically inaccessible to the user. These techniques result in a preliminary candidate for the firmware update validation method, which is then confirmed, analyzed, and exploited to the extent possible.

In order to provide a more complete understanding of the prerequisites for successful firmware modification, the advantages and limitations of techniques used in the derivation process are discussed. The effectiveness of each technique is considered in relation to any time or cost requirements as well as the complexity of their implementation.

#### 1.5 Impact

This research examines and determines the feasibility of counterfeit firmware attacks on a common PLC. Demonstrating this ability helps distinguish the true nature of the threat posed by firmware counterfeiting. The described reversing process identifies prerequisite capabilities of an attacker and limitations of any potential attack. This information provides the insight necessary to develop defensive and forensic analysis techniques for firmware modification attacks. In addition to the analysis enabled by this process, direct results enable the creation of realistic counterfeit firmware samples for analysis in future research. This aids in the development of effective strategies and tactics for preventing and detecting firmware modification attacks.

#### 1.6 Organization

Chapter 2 discusses ICS security and reviews associated work in the area of embedded firmware. Chapter 3 details the approach taken by this research and presents the process applied to derive the firmware update validation method on the test controller. Chapter 4

applies the process to a PLC and analyzes the results. Finally, Chapter 5 concludes the research by discussing significance and relevant future work.

#### II. Background

#### 2.1 Industrial Control Systems

An industrial control system (ICS) comprises a set of components used for the automated management and control of an industrial process. The term may refer to a multitude of different control system schemes, devices, and implementations, which include the control of production industry processes like automotive assembly plants as well as critical infrastructure systems including the electrical power grid, water treatment systems, and chemical industry. This thesis focuses on the protection of such critical infrastructure.

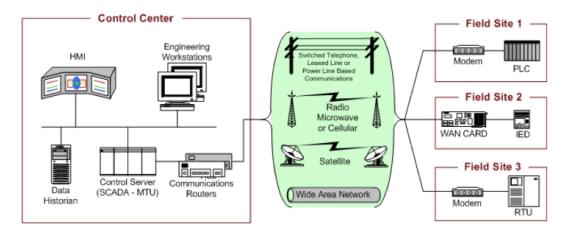

As an example, supervisory control and data acquisition (SCADA) systems represent one specific type of ICS. SCADA systems are typically used in the control and management of geographically dispersed industrial systems [55]. In the structure illustrated in Figure 2.1, the human user interacts with the control system through a human machine interface (HMI). The HMI functions as the operator's main method of monitoring and altering physical components to provide external oversight of correct operation. The HMI connects to a master terminal unit (MTU) that acts as the central automated supervisory unit of the SCADA system. The MTU monitors and manages the various physical sites composing the system, but it does not directly control end nodes. This responsibility is placed on field devices. Specifically, remote terminal units (RTUs) are field devices designed to control physical aspects of the system. SCADA systems branch out over various communication channels to assorted RTUs that control and monitor actual physical objects in the system such as valves and sensors. Another type of ICS, called a distributed control system (DCS), is a type of system that focuses more specifically on the control of localized processes. Unlike SCADA systems, DCSs are typically implemented in scenarios where the entire control system is contained within the same local network.

Figure 2.1: Typical structure of a SCADA system [55].

A commonly used device in ICSs is the PLC. PLCs are embedded computer systems specifically designed to control and, to an extent, independently monitor the physical system components under their supervision. PLCs are commonly used in DCSs and often times in place of RTUs in SCADA systems due to their enhanced capabilities. As the name implies, PLCs enable customized control of system components by providing a user-programmable interface between physical inputs and outputs. PLCs typically require proprietary software installed on a standard computer (usually running Microsoft Windows) to provide a method of programming the controller. Examples of such programming software include Rockwell Software's RSLogix series for managing Allen-Bradley controllers and Siemens's Simatic Step 7 for Simatic controllers. With these applications, engineers commonly utilize a graphical programming language called ladder logic to create a representation of how the controller should respond to given inputs. By creating virtual projects in the programming application, a user is able to view the logic currently running on a PLC as well as write new ladder logic to the device for execution.

#### 2.2 Industrial Control System Security

The history of ICSs encompasses decades of steady advancement building to the complex systems present today. However, the evolution of these systems does not lend itself well to a satisfactory development of security practices and implementations. While such development continues to progress through the influence of regulation and research, it is often outpaced by advancing threats [13]. This section provides an overview of growing threats to ICSs and their significance on the future of ICS security.

#### 2.2.1 *History*.

#### 2.2.1.1 Past Incidents.

Cyber incidents related to ICSs are certainly not new; however, much has changed regarding the subject in a relatively short amount of time. A true history of ICS cyber incidents is difficult to compile considering low reporting rates due both to unrecognized incidents as well as the implications of recognized incidents on the reputation of those involved. Without any obligatory reporting procedures, only highly visible incidents are publicly reported.

The incident widely considered the first reported cyber attack against critical infrastructure took place in 1997 [1, 21]. In March, a teenager successfully hacked into a local service provider's loop carrier and disabled it. This resulted in the disruption of communications to and from the Worcester Regional Airport air traffic control tower. Also affected were communications for airport security, fire department, and weather service, as well as about 600 homes in the nearby area of Rutland, MA. The attack was executed using a dial-up modem connected to the disabled loop carrier. Three years later, in 2000, another attack took place in Queensland, Australia [54]. After three months of what was thought to be system glitches at the Maroochy Water Services plant, intentional malicious action was discovered. The actions were traced back to a disgruntled contractor who had failed to procure a new job with the Maroochy Shire Council. Over the course of the three

months he had used a laptop and radio transmitter to create problems in the system and consequently released a total of around 1 million liters of sewage into local waterways.

In addition to these early attacks on critical infrastructure, the combined proliferation of computer worms and viruses over the past decades has led to unintentional effects resulting from the propagation of malware to ICSs. The first major reported incident of such a situation occurred in 2003 by means of the Sobig worm [42]. The Sobig worm managed to propagate to critical areas on CSX train systems, causing the shutdown of train signaling and dispatch services along the east coast of the United States. As a result, a cascade of delays was created, affecting many trains for hours. The same year was also marked by the Davis-Besse incident [45]. As a result of uncontrollable propagation of the Slammer worm, the safety monitoring system at the Davis-Besse Nuclear Power Station in Ohio was disabled. Fortunately, the plant was idled at the time, so no reactors were active. There also remained an analog backup safety system that remained unaffected; however, the fact that the worm could so easily impact the power station with no specific intent is concerning. Slammer was originally introduced into the unsecured network of a plant contractor. From there it was able to propagate across a T1 line that completely bypassed the plant firewall. In another 2005 case, the Zotob worm unintentionally attacked DaimlerChrysler [47]. By exploiting a buffer overflow in Microsoft's Plug and Play service, Zotob propagated onto DaimlerChrysler manufacturing plant networks and forced random system reboots [40, 48]. These disruptions shut down 13 manufacturing plants across 6 states for about an hour.

#### 2.2.1.2 Stuxnet.

In 2010, the Stuxnet worm was discovered. This malware is now infamous as the epitome of advanced ICS threats. Reports indicate that Stuxnet was a highly targeted attack against specifically configured PLCs controlling particular ICS processes [12, 14]. The reports suspect that the initial infection vector was through the use of removable media

devices. These may have been planted for unsuspecting employees to find and use, or the attackers may have breached physical security to deliver the worm [19]. Once introduced to a computer running Microsoft Windows, Stuxnet bypasses antivirus software and detects if Step 7 software is installed. If so, the worm replaces the main function library used by Step 7 with a malicious version. Stuxnet also places itself in any other removable media attached to the computer and any Step 7 project files for future propagation. When the malicious Step 7 library is loaded by a program, it runs a routine to search for specific PLC models that are connected to specific frequency converter drives used to control motor speeds. If such a PLC is found, Stuxnet injects malicious programming to the PLC that alters the motor speed, causing damage. In addition to the injection of malicious programming, the malicious Step 7 function library also masks the modified PLC code from the operator on an infected computer.

#### 2.2.2 Future Threats.

In June of 2011, the National Institute of Standards and Technology (NIST) released the most recent version of their Guide to ICS Security [55]. The authors note that ICS technology is advancing by integrating with more traditional IT system solutions like IP-based communications and standard computers. As this occurs, ICSs become less isolated and more vulnerable to security threats. Traditional IT security solutions may be applicable to modern ICSs in some regards, but special consideration must be made in areas where traditional IT has no experience. Because of the cyber-physical link ICSs provide, issues such as human safety [21, 42, 45] and environmental [54] effects may be impacted by any gap in security.

A common trend witnessed in traditional computer malware is a race to the bottom where lower level attacks have the advantage over more overt and limited high level attacks. For example, user mode malware may be easily detectable as a file or running process and may be limited by security features present in the operating system. Alternatively, kernel

mode malware is able to hide itself with rootkit functionality and may control kernel level processes inaccessible to a user mode program.

A similar trend is developing in the field of ICS security. Already, attacks like Stuxnet focus on the PLC given that it provides a link between the ICS and components affecting the physical world. At the highest level of PLC control, many current exploits focus on application layer vulnerabilities using hard-coded passwords to access control interfaces. Stuxnet takes this a step further by modifying the programming on PLCs and masking the change from operators using rootkit functionality on the Step 7 Windows machines. However, these modifications are not malicious to the PLC itself. The PLC is designed to be remotely programmable and the code loaded on the PLC by Stuxnet is valid operating code, so the device is only a conduit for the attack. Stuxnet takes advantage of the malicious Step 7 function library to hide modifications from infected Step 7 machines [19]. The PLC continues to run as it is instructed and the operator cannot observe modifications to the code; however, if the PLC is accessed from a non-infected Step 7 machine, the modifications are visible. The logical progression of attacks is to affect the PLC in such a way that no external observer can readily detect malicious modifications.

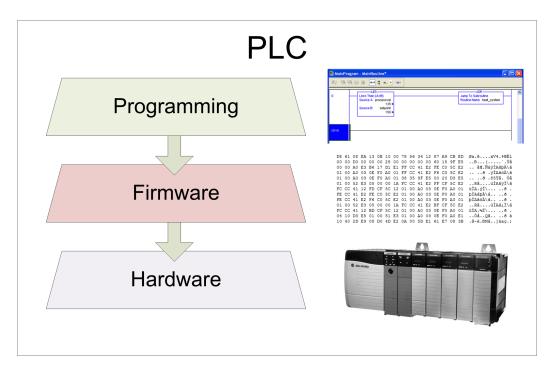

#### 2.3 Programmable Logic Controller Security

Specific focus on cyber security from the perspective of PLCs remains a serious issue in ICSs. In a 2012 paper, McMinn *et al.* describe the existence of three operational layers on a PLC: (i) programming, (ii) firmware, and (iii) hardware [33]. This section discusses the major vectors available to attack PLCs and their related concerns following this model (see Figure 2.2).

#### 2.3.1 Programming Layer.

The programming layer is the main channel of interaction between ICS operators and the PLC. Through this layer, a user provides the device with logic required to operate the

Figure 2.2: Operational layers of a programmable logic controller.

controller's given application. Many different languages are used at the programming layer including modified implementations of traditional languages such as C or BASIC [27]; however, the typical method used to program controllers is a graphical language called ladder logic. Ladder logic provides engineers, who may be unfamiliar with traditional programming languages, an intuitive interface to the controller. Programming software used to upload the logic to the PLC (e.g., RSLogix) compiles the graphical language to low level code for execution before uploading the code to the device. The programming uploaded to the device is analogous to a desktop application run on a traditional computer. For the PLC, the programming dictates how the controller responds to input. Because the program loaded on the controller is managed by programming software, modifications solely made to the program can be readily detected, as mentioned in the Stuxnet discussion.

#### 2.3.2 Hardware Layer.

The hardware layer consists of the physical chips and components that make up the PLC. Among other components, this layer includes the microprocessor, volatile run-time memory, and non-volatile storage memory. Security at this layer is based on physical protection. From a malicious perspective, three main vectors are available to attack the hardware layer: physical manipulation of the hardware, software exploitation of hardware design flaws, and supply chain compromise to intentionally create vulnerabilities. Of these, physical manipulation is the least likely in an operational scenario as this would require the attacker to have intimate access to the device, possibly for extended periods of time. Such an attack implies an insider threat scenario, in which case more straightforward methods of attack like direct malicious reprogramming are possible. The second vector of attack at the hardware layer reduces to a software-based attack where physical design flaws are exploited by software running on the device. This requires exploitation through either the programming layer or the firmware as discussed in the following section.

The remaining attack vector is supply chain compromise. If an attacker can compromise the supply chain of components for a device, they may be able to influence their design and engineer vulnerabilities, providing backdoors to the system. Detection of supply chain compromise is a difficult and costly endeavor. The analysis and reverse engineering of a physical component in an attempt to detect malicious logic requires a significant amount of time. Modern microprocessors have become so complex that such methods are not feasible in many cases. In those cases where it is, the device is likely destroyed in the process. For these reasons, researchers are investigating viable alternatives using side channel methods [57]. By analyzing changes in signal metrics such as timing and power, comparisons are made to known-good reference circuits to determine if any differences are present in the test device. This method assumes that the modification of a circuit results in a noticeable change in the power requirement or timing of the

circuit. However, many challenges remain in this area of research. Not only is a trusted baseline required for comparison, but the possible implementations of malicious logic are so numerous and complex that choosing appropriate detection metrics is difficult.

Presenting a comprehensive approach, Baldwin *et al.* explore the issue of supply chain trust from a strategic perspective and propose new policies to integrate "system security engineering" into the current Department of Defense acquisition life cycle [7]. This proposal follows a cradle-to-grave approach to security. Pre-development planning focuses on security from the start by analyzing possible vulnerabilities of system components. Supply chain risk management is discussed and encompasses various techniques to minimize the threat of supply chain compromise. For critical components, a full scope supply chain analysis is performed to identify all suppliers involved with component production. The concept of trusted suppliers is introduced where strict requirements are imposed for such vendors. The purchasing of components should also follow diverse redundancy and anonymous buyer practices to minimize the probability of compromise. System testing focuses specifically on critical components as they interact with the rest of the system as well as many other non-hardware based secure design practices throughout the system life cycle.

While a serious issue warranting concern, hardware layer security is ultimately immaterial in the context of current production systems. At some point, assumptions must be made about the security of the hardware. Indeed, these assumptions are already made by vendors and consumers by the fact that the devices are in use. This fact reinforces the concept that while strict physical security, thorough quality control, and a secure supply chain are important, these are complex issues requiring more specialized and long-term solutions unconcerning many field devices in current production or operation.

#### 2.3.3 Firmware Layer.

Bridging the low level hardware layer to the upper level programming layer is the firmware layer. Firmware is the low level software run on the device to support higher level operations. For this reason, firmware is commonly referred to as the operating system (OS) of embedded devices. In a broader sense, however, firmware also includes lower level functionality like bootloader code to initialize and load the OS.

This layer in a PLC that controls the basic behavior of the device including communication with management systems and execution of the user-level program written to the device. Firmware handles all interactions between the user and the device hardware, including physical inputs and outputs. The functional analogy of OS firmware is further extended when discussing potential threats to the PLC. The traditional operation of a rootkit on a standard computer is equivalent in concept to how an attacker may take advantage of OS firmware in a controller to hide modifications. Rootkits typically exploit kernel-level processes to gain privileged access to OS functionality. Using this access, rootkits are able to modify the underlying behavior of the OS. In the same way, an attacker with access to the firmware on a PLC has potentially limitless control over the device including the ability to covertly alter device behavior in a malicious fashion.

In some embedded devices, firmware is programmed from the factory and designed such that it remains static and not reprogrammable. In such cases, firmware is relatively safe from modification attacks. However, modern embedded devices including PLCs are commonly designed with the capability to update the firmware. This ability allow vendors to patch bugs present in the firmware as well as enable new features without requiring physical updates of the hardware. Given a device with reprogrammable firmware, the procedure of performing the update is usually the responsibility of the user, typically through the application of an update software package. Since a user has access to update the

firmware, however, the process facilitates an attacker's ability to upload modified firmware to a device.

#### 2.4 Previous Works on Reversing Firmware

#### 2.4.1 Discovering Backdoors in Ethernet Modules.

In a December 2011 web article, independent security researcher Ruben Santamarta describes a process used to discover backdoor accounts and passwords for a Modicon Quantum PLC Ethernet module [51]. While the goal of his research was not to modify the firmware, but to uncover these backdoors, the process he follows is applicable to search for validation algorithms in firmware.

To begin the reversing process, Santamarta obtains a copy of firmware for the target controller. He does so by downloading the firmware from the vendor website. An entire update package is obtained, where the actual firmware binary is contained within. Therefore, the binary image itself is found and extracted from the rest of the package. An inspection of the the update package contents reveals the location of the firmware image to extract. Santamarta advises that other files in the update package may contain useful information about the firmware and continues examining the firmware itself.

The first step is a manual inspection of the binary image using a binary file editor. This procedure reveals a file header followed by a zlib-compressed section, identified by its leading binary signature. After decompressing this section, he proceeds to identify the processor type, which is a PowerPC. While he does not go into detail about his method of processor type determination, Santamarta references a presentation by Igor Skochinsky [53] detailed in Section 2.4.3.

Following this determination, Santamarta begins the process of disassembly by loading the binary file into the Hex-Rays Interactive Disassembler (IDA), a disassembler tool. At this point, he presents a common process for reconstructing the firmware code in IDA. The process begins by collecting information from strings contained in the firmware

image. A copyright string identifies the firmware as VxWorks-based OS. Next, since IDA is not able to automatically detect functions in this binary image, Santamarta describes a method to resolve functions in the disassembly by searching for common function prologue bytes. He then commands IDA to treat these addresses as functions by disassembling their code and adding them to an internal database. Santamarta provides the source code of the IDA script he uses to perform this task.

Now that IDA has disassembled and identified functions in the image using the standard prologue, Santamarta "rebases" the image by altering the code base address to that which it assumes at runtime. He suggests that the true base address may be located in the firmware header or other documentation, but determines this is not so for his case. Instead, he uses the "[load immediate] instructions' trick" [58]. This method consists of searching the disassembly for instructions that load an immediate (i.e., absolute) address value into a register. The technique presumes that a significant number of immediate addresses refer to locations in the firmware itself, and therefore have the same base address. Candidate base addresses are then tested by rebasing the firmware and determining if the immediate addresses correctly align with target data such as strings or other functions.

After successfully rebasing the firmware, Santamarta rebuilds the function symbols, or names. He begins by searching the firmware for a symbol table. This is identified as a section of the code containing a regularly repeating data structure that includes function name strings. He discovers such a table and, using another IDA script, parses the symbol table and relabels the disassembled functions with their proper names. This enables Santamarta to use symbol names in finding sections of the firmware relevant to his goal of discovering backdoor accounts. Indeed, he finds many undocumented accounts for the Ethernet module.

#### 2.4.2 Creating Custom Firmware for Ethernet Modules.

In a 2009 paper, Peck and Peterson demonstrate a successful upload of customized firmware to an Allen-Bradley ControlLogix Ethernet module [44]. Their goal is to show that an attacker can learn how to upload custom firmware to a field device Ethernet card using commonly available tools. They justify their choice of Ethernet card targets by describing the vulnerable state of Ethernet modules and their ease of access through remote network means. Peck and Peterson proceed to explain their method of reversing the Ethernet module firmware and subverting the card's validation algorithm.

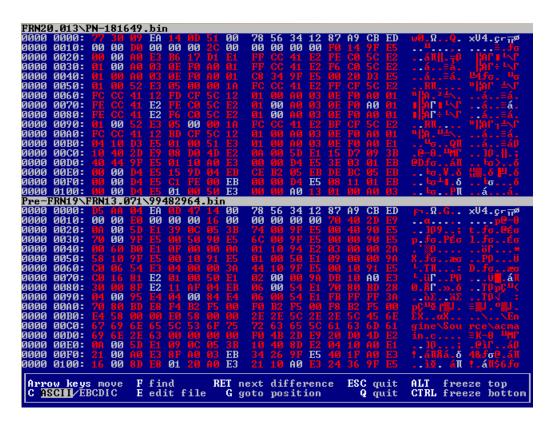

Peck and Peterson first acquire multiple firmware samples for the target Ethernet module. These samples are downloaded from the manufacturer website. Peck and Peterson explain the importance of obtaining multiple samples for comparison as a way to identify static fields in the images. With firmware samples available, Peck and Peterson begin inspecting the binary files, looking for and identifying different segments that exist in the image (e.g., blocks of code, filesystems, or strings).

After the manual inspection, Peck and Peterson utilize a binary analysis tool called Deezee, which searches binary files for embedded zlib-compressed sections, extracts, and decompresses them [38]. Using this tool, Peck and Peterson discover a zlib-compressed section containing the symbol table for the firmware, identified by a regularly repeating pattern of addresses and string symbol names. Further analysis of the symbol table reveals function addresses listed as absolute values. Using these addresses they infer the base address of the image.

Peck and Peterson next attempt to disassemble the firmware code using IDA. However, a known processor type is required, so they initially assume that the target uses an ARM core. They are incorrect, but infer from the result of the attempted disassembly that the true processor type is PowerPC. Another attempt with this target processor type is successful and produces disassembled code. A rebase of the image is then performed using the base

address derived from the symbol table. Finally, Peck and Peterson use a script to add the symbol names to the disassembly.

Peck and Peterson continue to search for the firmware validation algorithm used by the Ethernet module. By searching through the symbol names, they discover a function named nv\_RamValidateChecksumsWriteFlash. An examination of this function reveals a subfunction call that performs a checksum validation calculation. Peck and Peterson reverse engineer this function to derive the entirety of the checksum validation algorithm used by the firmware. Their target device uses a 2-byte summation of the image header and a 2-byte summation of the remaining firmware image, both of which are located in the header.

With knowledge of the validation algorithm, as well as the location of the checksum values, Peck and Peterson customize the firmware with a proof-of-concept that instructs the Ethernet card to continually ping a specific IP address in addition to its normal operation. The authors note the importance of taking care not to disrupt default operation of the device. Finally, the customized firmware is uploaded to the Ethernet module using the ControlFlash firmware programming software Rockwell Software provides. While they admit that a custom flash program could be written to accomplish the task, Peck and Peterson argue that it is simpler to use the vendor supplied software.

#### 2.4.3 General Processes for Reverse Engineering Embedded Devices.

In a presentation at the 2010 Recon security conference, Igor Skochinsky, a software developer on the Hex-Rays IDA team, provides an introduction on reverse engineering embedded firmware [53]. In Skochinsky's process, he first retrieves a firmware image. He provides various methods for doing so, the first of which is obtaining a firmware update from the vendor. Skochinsky notes that this method for acquiring firmware is straightforward and that the updates obtained may also contain firmware upload programs, filesystems, or bootloader images in addition to the main firmware, which may be relevant.

One may also take advantage of external communications with the device. While taking more time and effort, a communication program on a separate computer from the device could be reverse engineered to reveal methods of instructing the device to transmit sections of memory containing firmware code. Another technique is the use of a universal asynchronous receiver/transmitter (UART) port on the device. This method is complex, possibly involving the identification of and connection to physical UART pins on the device if no standard serial port is present. After physical connection, it may be possible to dump the firmware from the device using certain commands sent over UART, depending on the device's support for UART. Similarly, Skochinsky also discusses the use of hardware debugging tools to dump the contents of memory, as discussed in Section 2.4.4. Finally, Skochinsky mentions the tactic of reading flash memory directly from the storage device; however, this typically requires the physical removal of an embedded flash chip from the board by desoldering.

With possession of the firmware, Skochinsky next characterizes the image. This begins by identifying any filesystems embedded in the firmware. He discusses various common filesystems utilized by embedded systems, how to identify them (typically using binary signatures), and how to unpack them into a usable form and access the files within. Following this, Skochinsky's discusses how to identify the embedded operating system type. Again, he walks through various embedded operating systems and how to identify them. Identification usually involves locating copyright strings containing the developer or operating system name. The final characterization before code disassembly is identification of the processor type. Skochinsky begins by explaining the differences between major design types (e.g., reduced instruction set computing (RISC) versus complex instruction set computing (CISC)), then discusses the general attributes of several popular embedded architectures and how to identify them by signature byte patterns common to that architecture's instruction coding.

Skochinsky's final step is disassembly of the firmware code. If the firmware is contained in a structured image such as an executable and linkable format (ELF) or other OS-specific format, a disassembler like IDA may be able to automatically disassemble the code, determining much of the code structure from the wrapper. However, if the firmware format is raw binary, additional work is required to create the equivalent disassembly. The first step of this process is determining the correct base address for the binary. Skochinsky suggests initializing the base address to 0, then searching the code for hints of the true base address if the use of 0 fails to produce complete disassembly. Such hints include self-relocating algorithms that copy code using the correct base address, initialization code that uses the base address to load code from non-volatile flash memory to volatile randomaccess memory (RAM), jump tables that contain absolute addresses, or string table offsets to compare with the addresses of strings they point to. After successfully rebasing the code, Skochinsky discusses recovering symbol information. He explains the extraction of symbols from a Linux kernel and provides an example of the VxWorks symbol structure. Skochinsky also suggests searching for a demonstration or evaluation copy of the OS type, if it is known, to allow for comparisons between it and unknown code in the disassembly.

#### 2.4.4 Hardware Debugging.

Hardware debugging is commonly used in the production of embedded systems as a method to test and verify system components as well as debug software at the processor level. One common hardware debugging standard is the Institute of Electrical and Electronics Engineers (IEEE) Standard 1149.1 Standard Test Access Port and Boundary Scan Architecture [25]. This standard is often referred to as Joint Test Action Group (JTAG), after the name of the consortium that created the standard [43]. Boundary scanning with JTAG requires a specialized hardware debugger connected to the test board through special pins called test access ports (TAPs). The standard specifies certain pin signals required to control the device under test. Four signal pins and an optional fifth are the

minimum defined by the standard: clock synchronization (TCK), mode select (TMS), data input (TDI), data output (TDO), and the optional reset signal (TRST). JTAG operates on a per-chip basis, so an integrated circuit (IC) on the target board must be designed to support JTAG. Typically, these chips are microprocessors. Given multiple components on a board that support JTAG boundary scanning, the same TAPs can be used to access all of them. This is known as chaining.

In a 2006 paper, Breeuwsma provides an introduction on JTAG and how to take advantage of it for forensic imaging of embedded applications [10]. Breeuwsma describes three main modes of operation for a JTAG-enabled device: normal operation mode, external test mode, and debug mode. Normal mode bypasses boundary-scan functionality to allow normal operation of the chip. External test mode provides basic JTAG functionality. In this mode, the processor core of the target is disabled. Instead, the input/output (IO) pins of the target chip are driven by values stored in the boundary-scan test register called test vectors. Using test vectors, the hardware debugger can completely control the IO signals on the target. This is useful for hardware validation and low level debugging operations including direct memory accesses.

Debug mode is an advanced operating mode allowed by JTAG to facilitate software testing and debugging. This mode requires special circuitry built into the target chip not specifically defined by the standard. Therefore, it is not uncommon for the implementation of debug mode to vary among different chips. In some cases, JTAG enabled components may lack debug circuitry altogether and only support external test mode. However, if the chip is designed with support for this mode, software executing on the chip may be debugged in real time. Depending on the target's implementation, debug mode may also enable access to memory on the target system without requiring specifically crafted test vectors as with external test mode.

Breeuwsma continues by describing techniques to identify JTAG TAPs on a device. The general process beings by searching for test pads on the target circuit board and eliminating as many as possible from the list of TAP candidates. Breeuwsma provides a list of characteristics common to JTAG TAPs that bound the search space. Such characteristics include the fact that TAP signals should remain constant while the system is running with no debugger attached. TAP traces should also not connect to non-IC components like capacitors (however, pull-up or pull-down resistors may be present). Lastly, TAP signals should not be driven by an output. After applying these rules for elimination, Breeuwsma provides additional detail on TAP characteristics to confirm those remaining candidates as TAPs.

#### 2.4.5 Checksum Algorithms.

As discussed in Section 2.3.3, firmware on embedded devices such as PLCs is often updated by manufacturers. Firmware update processes typically include the use of validation methods to confirm that the newly uploaded image is not corrupt [44]. This section provides an overview of various types of algorithms commonly used for data validation with a specific focus on the validation of firmware updates.

A hash function is defined as a function that maps data of an arbitrary length to a fixed-length value called the hash value [34]. A checksum algorithm, then, is any type of hash function used for the purposes of validating data integrity [59]. The resulting hash value generated by a checksum algorithm is referred to as the checksum value or, succinctly, the checksum. There exist various algorithms used for calculating checksums that fall into five general categories: parity checks, modular summations, cyclic redundancy check (CRC), non-cryptographic hashes, and cryptographic hashes. Parity check algorithms, typically synonymous with longitudinal redundancy checks (LRCs) [39], calculate a checksum value by applying the *exclusive or* (XOR) operation to each *n*-bit word over the data set. This produces an *n*-bit checksum value representing the "parity" of each bit position in every

word [28]. Parity algorithms have the advantage of being computationally inexpensive and straightforward implementations; however, they are less accurate in detecting data errors then other algorithm types mentioned here. Typically, the only variation between parity check implementations is the bit width of each word in the calculation.

Modular summation algorithms are based on the addition of each *n*-bit word in a data set with the next. The resulting sum is represented using a given modulus to create a checksum value of the desired bit width. Note that the term "checksum" is sometimes used by other works in reference to modular summation algorithms specifically; hence, there is common cause for confusion. This thesis, however, uses the term "checksum" in reference to the resulting value of any hash function used for the purposes of validating data integrity. Another specific type of modular summation algorithm is the Fletcher algorithm [20]. This algorithm calculates a modular summation as before, but also includes a second modular sum of those simple sums, creating two values that compose the checksum. Fletcher algorithms can be calculated with various moduli to achieve bit widths of 16, 32 or 64 bits. Each of these widths has a commonly used modulus associated with it. A further specific variation of the Fletcher algorithm is the Adler-32 algorithm which uses the specific modulus of 65,521 for both sums [17]. Modular summation algorithms allow for more accurate error detection than parity checks while remaining straightforward to implement. However, the variability of different modular summation methods is much higher than parity algorithms. Since several different schemes are based on the summation concept, determination of a specific algorithm is more difficult than for parity checks.

A CRC is a type of algorithm that uses polynomial division on a data set to produce a checksum value representing the remainder of this division. The specific process used in the CRC calculation is detailed by Ramabadran and Gaitonde [46]. In general, implementation include a series of incremental XOR operations over the data, where the result of each increment is dependent on the polynomial, the data, and the preceding

result. A CRC is based on variable parameters including width of the checksum value, the static polynomial value, initial checksum value, the final XOR value applied to the resulting checksum, and whether or not input and output bytes are reflected for endianness. Therefore, the specifics of CRC algorithm implementations are highly variable. CRCs have the benefit of more accurate error detection rates than modular summations [32]. While more computationally complex than the above algorithms, CRCs remain less complex than the remaining categories.

Dedicated hash functions are categorized as either non-cryptographic or cryptographic. While, by definition, all the algorithms discussed here are hash functions, these two categories refer to functions specifically designed to minimize collisions. A collision occurs when a hash function is applied to two unique sets of data and the resulting calculations produce identical hash values. Since the previous categories of algorithms are not designed specifically to prevent this outcome, they remain vulnerable to collisions. Thus, dedicated hash functions are better suited to detect changes in input data, but usually at the cost of computational speed and complexity.

The difference then between non-cryptographic and cryptographic hash algorithms is that in addition to their sensitivity to accidental modifications of data, like previous functions, cryptographic hash algorithms are also capable of detecting intentional modifications. Specifically, cryptographic hash functions are not feasibly vulnerable to collisions or reversal. To a lesser extent than previous categories, one is still feasibly able to find collisions in non-cryptographic hash functions or reverse them to determine a data set that produces a given hash value. Cryptographic hash functions, however, are not considered vulnerable to such attacks in any feasible manner. For example, it may be technically possible to find a collision in a cryptographic hash function through brute force, but the computational resources required to do so in a reasonable amount of time

are unrealistic. Many cryptographic hash functions exist, most notably the secure hash algorithm (SHA) family of algorithms [41].

Given that embedded devices are typically limited in available memory and computational ability, less complex checksum algorithms are more feasible than cryptographic hash functions for such applications [32]. However, there exists a trade off between the simplicity of an algorithm and its ability to accurately detect changes in data. For these reasons, modular summation and CRC algorithms are commonly used as validation methods for embedded systems. Their balance of computationally inexpensive calculation and reasonably accurate detection rates of unintentional errors make them popular in applications such as Ethernet, transmission control protocol (TCP), and the VxWorks embedded OS [26, 44]. As discussed by Maxino and Koopman, however, some embedded applications may also take advantage of completely proprietary checksum algorithms, especially in the case of embedded control networks [32].

### 2.5 Summary

Much of the nation's critical infrastructure relies on ICSs to monitor and automate control processes. As these systems evolve from traditionally isolated and specialized implementations to adopt common IT solutions, they become exposed to cyber attacks. This is witnessed as ICS cyber incidents progress from isolated attacks to unintentional impacts caused by computer malware, culminating in the highly targeted Stuxnet attack on control systems. As these attacks advance, focus is shifted from targeting highlevel application systems to direct threats against PLCs. PLCs consist of a user-level programming layer, a low-level firmware layer, and a physical hardware layer. The ability of firmware to completely dictate behavior of the device with no direct operator oversight presents an attack vector accessible by legitimate means and capable of masking malicious activity, unlike the observable programming layer and inaccessible hardware layer. Previous works discuss various techniques for reverse engineering embedded devices

with a specific focus on PLCs and firmware modification. Other works on the topics of hardware debugging and checksum algorithms as they relate to embedded devices augment such techniques to provide a comprehensive survey of the field.

### III. Methodology

This chapter outlines the methodology by providing a problem definition and general approach, briefly describing the procedure and purpose of each step in the conceived process, and finally detailing the factors considered in assessing advantages and limitations of the composed techniques.

#### 3.1 Problem Definition

Strategically, the intended result of this research is to further defensive measures and forensic analysis techniques targeted toward advanced ICS threats by determining the feasibility of firmware modification attacks on PLCs. Specifically, the goal of this effort is to investigate and assess the vulnerability of a common PLC to counterfeit firmware updates. The achievement of this goal provides valuable information and insight regarding the feasibility, technical requirements, and characteristic implementation of future firmware related threats to PLCs.

This research proposes that common PLCs are vulnerable to firmware modification attacks as a result of design weaknesses in firmware update validation methods. A design weakness is defined as a failure of the device to properly detect intentional modifications to firmware. An appropriately counterfeited firmware is expected to be accepted through the standard firmware update process of the controller and execute on the device in no distinguishably different manner than any given legitimate firmware, save for any modifications present in the counterfeit version.

# 3.2 Approach and Scope

The process to derive the firmware update validation method is based on a thorough review of previous research involving the reverse engineering of similar embedded devices (see Section 2.4). Relevant tactics and procedures are compiled into a general process to

identify the firmware update validation method. The approach is applied to a production PLC that is both commercially available and commonly used in ICS implementations. Through this application, the constituent techniques of the reversing process are assessed for advantages and limitations in their ability to derive the firmware update validation method. Furthermore, feasibility of the threat posed by firmware modification attacks on PLCs is determined by a successful upload of counterfeit firmware. The reversing process provides a basis for the strategic intent of furthering defensive and analytic research on the topic.

The scope of this research is limited to PLC firmware counterfeiting. In a layered operational model, each layer is functionally independent of every layer above it and functionally dependent on every layer below it. Given the layered operational model of a PLC, the firmware layer is independent of the programming layer or any higher layer control mechanisms because the firmware dictates how those higher layer actions are interpreted. For this reason, no layers higher than the firmware layer are considered in the scope of this research. Similarly, the firmware layer is dependent on every layer below it to consistently interpret its actions. Therefore, as the only layer below the firmware, the hardware layer is considered in the scope of this research. External to the operational model, the only other considered system component is the firmware update procedure. Specifically, this research is based on legitimate firmware update procedures only. This includes any interaction with the device that the firmware interprets as a legitimate firmware update request, including the manufacturer supplied firmware update procedure or any procedure sufficiently similar to initiate a firmware update. No other external mechanisms or components are considered in the scope of this approach including, but not limited to, auxiliary controller components or the interaction of firmware updates with any external system.

#### 3.3 Test Environment and Tools

The testing environment for this research includes an Allen-Bradley ControlLogix 1756-L61, Series B, Standard Controller module manufactured by Rockwell Automation. This hardware is accompanied by standard firmware available from the manufacturer which is applied to the device using Rockwell's standard ControlFlash update software. Since the scope of this evaluation is bounded to the PLC hardware and firmware layers with standard update procedures, this specific test environment is equivalent to the intended manufacturer configuration. The L61 controller module is accompanied in this test environment by a standard ControlLogix 1756-PA72/C power supply, 1756-A7 chassis/backplane, and 1756-ENBT Ethernet communications module to support operation and testing. However, none of these additional components are considered by the research presented here. Thus, results of this evaluation are accurate for any standard L61 controller within the given scope.

Additional tools used throughout the evaluation process include the Notepad++ standard text editor and the HxD binary file editor. The binary analysis step of the process takes advantage of the binary file difference tool Visual Binary Diff (VBinDiff) to perform a binary file comparison as well as the static binary analysis tool BinWalk for embedded file and filesystem analysis. Firmware disassembly takes advantage of the IDA tool extensively for further analysis. Brute forcing techniques discussed as part of black box testing use the CRC RevEng tool by Gregory Cook. Finally, the explored hardware debugging techniques include the use of the Advanced RISC Machine (ARM) RealView in-circuit emulator (ICE) device along with the ARM Development Studio 5 (DS-5) debugging software.

### 3.4 Reversing Process

An integration of related works discussed in Section 2.4 results in the general reversing process illustrated by Figure 3.1. This section details the steps in the process: (i) firmware sample acquisition, (ii) binary analysis of firmware, (iii) firmware disassembly, and (iv) derivation of the firmware update validation method. While the presented process is based

on several common methods previously discussed, the nature of reverse engineering is at times as much an art as it is a science. The process externally requires intuition and experience on behalf of the investigator. The success and effectiveness of each step may rely in part on this variable aspect of the process. Nonetheless, the process serves as a roadmap to follow in deriving operation of the system.

## 3.4.1 Firmware Acquisition.

In order to begin reverse engineering the firmware, sample copies are first obtained. The primary method for accomplishing this is by procuring firmware updates from the vendor, which are typically available from online sources. The firmware binary images are then extracted from these update packages. Should this not be possible, alternative measures are taken such as memory acquisition through JTAG or desoldering the flash chip to directly read its contents. As many different firmware samples are obtained as possible to enable a thorough binary file analysis and comparison.

### 3.4.2 Binary Analysis.

This initial interaction with the firmware involves an examination of the raw binary files intent on gaining general knowledge required for a detailed inspection. Three techniques are applied: manual inspection, binary file comparison, and embedded file/filesystem analysis. A manual inspection reveals information about the general structure and contents of the binary file. In addition to static fields discussed by Peck and Peterson [44], dynamic fields of the firmware are also identified. Both are determined through the binary comparison of different firmware samples with the goal of identifying header contents and organization as well as fields in the image used for validation purposes. Embedded file and filesystem analysis is intended to detect the existence of any embedded files or filesystems in the firmware, which may contain information relevant to the firmware code operation or organization.

Figure 3.1: Reversing Process.

#### 3.4.3 Disassembly.