### Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-14-2014

# Complex VLSI Feature Comparison for Commercial Microelectronics Verification

Michael K. Seery

Follow this and additional works at: https://scholar.afit.edu/etd

### **Recommended** Citation

Seery, Michael K., "Complex VLSI Feature Comparison for Commercial Microelectronics Verification" (2014). *Theses and Dissertations*. 623. https://scholar.afit.edu/etd/623

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

# COMPLEX VLSI FEATURE COMPARISON FOR COMMERCIAL MICROELECTRONICS VERIFICATION

THESIS

Michael K. Seery, Second Lieutenant, USAF

AFIT-ENG-14-M-67

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

# AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

DISTRIBUTION STATEMENT A: APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, the Department of Defense, or the United States Government.

This material is declared a work of the U.S. Government and is not subject to copyright protection in the United States.

# COMPLEX VLSI FEATURE COMPARISON FOR COMMERCIAL MICROELECTRONICS VERIFICATION

### THESIS

Presented to the Faculty Department of Electrical and Computer Engineering Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering

> Michael K. Seery, B.S.C.E. Second Lieutenant, USAF

> > March 2014

### DISTRIBUTION STATEMENT A: APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

AFIT-ENG-14-M-67

# COMPLEX VLSI FEATURE COMPARISON FOR COMMERCIAL MICROELECTRONICS VERIFICATION

Michael K. Seery, B.S.C.E. Second Lieutenant, USAF

Approved:

//signed//

Mary Y. Lanzerotti, PhD (Chairman)

//signed//

Kenneth M. Hopkinson, PhD (Member)

//signed//

Maj Samuel J. Stone, PhD (Member)

6 Mar 2014

Date

5 Mar 2014

Date

5 Mar 2014

Date

### Abstract

Shortcomings in IC verification make for glaring vulnerabilities in the form of hardware backdoors, or extraneous operation modes that allow unauthorized, undetected access. The DARPA TRUST program addressed the need for verification of untrusted circuits using industry-standard and custom software. The process developed under TRUST and implemented at the AFRL Mixed Signal Design Center has not been tested using real-world circuits outside of the designated TRUST test cases.

This research demonstrates the potential of applying software designed for TRUST test articles on microchips from questionable sources. A specific process is developed for both transistor-level library cell verification and gate-level circuit verification. The relative effectiveness and scalability of the process are assessed.

### Acknowledgments

Sincere appreciation is due to Dr. Mary Lanzerotti for continued guidance as advisor and committee chair. Also deserving of recognition are Dr. Ken Hopkinson and Dr. Samuel Stone at the Air Force Institute of Technology for serving as committee members on this research, and Mr. Brad Paul, Mr. Len Orlando, Dr. Michael Myers, Dr. Brian Dupaix and Mr. Dave Lucking at AFRL MSDC for their advice, teaching and research contributions.

Michael K. Seery

### **Table of Contents**

|      |                   |                            | Page  |

|------|-------------------|----------------------------|-------|

| Ab   | stract            |                            | . iv  |

| Ac   | know              | ledgments                  | . v   |

| Tał  | ole of            | Contents                   | . vi  |

| Lis  | t of F            | igures                     | . ix  |

| Lis  | t of T            | ables                      | . xi  |

| Lis  | t of A            | cronyms                    | . xii |

| I.   | Intro             | duction                    | . 1   |

|      | 1.1<br>1.2        | Trust                      | . 3   |

|      | 1.3<br>1.4<br>1.5 | Justification              | . 4   |

|      | 1.6<br>1.7        | Assumptions and Scope      | . 6   |

| II.  | Back              | ground                     | . 8   |

|      | 2.1               | Microchip Acquisition      | . 8   |

|      | 2.2<br>2.3        | Trusted Foundries          | . 12  |

|      | 2.4               | Impact                     | . 20  |

|      | 2.5<br>2.6        | Response       DARPA TRUST |       |

|      | 2.7               | Conclusion                 | . 28  |

| III. | Meth              | nodology                   | . 29  |

|      | 3.1<br>3.2<br>3.3 | Introduction               | . 30  |

|      |                   | 3.3.1 Cell Recognition     |       |

# Page

|     |        | 3.3.2     | Enhanced Design Rule Check                                      | 38       |

|-----|--------|-----------|-----------------------------------------------------------------|----------|

|     |        | 3.3.3     | Timing Check                                                    | 38       |

|     |        | 3.3.4     | Hierarchical Extraction / TRUST Structural Database             | 39       |

|     |        | 3.3.5     | Equivalence Check & Advanced Mapping                            | 40       |

|     |        | 3.3.6     | Exploitable Logic Check                                         | 40       |

|     |        | 3.3.7     | Conformal for Custom Layouts                                    | 41       |

|     |        |           | 3.3.7.1 Transistor-Level                                        | 41       |

|     |        |           | 3.3.7.2 Gate-Level                                              | 41       |

|     |        |           |                                                                 | 11       |

| IV. | . Resu | lts       |                                                                 | 43       |

|     | 4.1    | Transis   | tor-level Testing                                               | 43       |

|     |        | 4.1.1     | Preliminary Results with Circuit A                              | 43       |

|     |        |           | 4.1.1.1 Generation                                              | 43       |

|     |        |           | 4.1.1.2 Verification                                            | 47       |

|     |        | 4.1.2     | Further experimentation with Circuit A                          | 50       |

|     |        |           | 4.1.2.1 Serial ordering                                         | 51       |

|     |        |           | 4.1.2.2 NC-Verilog drain-source assignment                      | 53       |

|     | 4.2    | Gate-le   | evel Testing                                                    | 59       |

|     | 1.2    | 4.2.1     | Circuit B                                                       | 59       |

|     |        | 1.2.1     | 4.2.1.1 Generation                                              | 59       |

|     |        |           | 4.2.1.2 Verification                                            | 63       |

|     |        | 4.2.2     | Circuit C                                                       | 65       |

|     |        | 4.2.3     | Circuit D                                                       | 66       |

|     |        | 4.2.3     | 4.2.3.1 Generation                                              | 66       |

|     |        |           | 4.2.3.1 Generation                                              | 69       |

|     |        | 4.2.4     |                                                                 | 09<br>74 |

|     | 12     |           | Circuit E                                                       |          |

|     | 4.3    | Summa     | ary                                                             | 77       |

| V.  | Cond   | clusion a | and Future Work                                                 | 78       |

|     | 5.1    | Summa     | ary                                                             | 78       |

|     | 5.2    |           | Work                                                            | 78       |

|     |        | 5.2.1     | Circuit <i>A</i> – 1                                            | 79       |

|     |        | 5.2.2     | Circuit <i>A</i> + 1                                            | 79       |

|     |        | 5.2.3     | SCR and Other Netlists                                          | 79       |

|     |        | 5.2.4     | Additional Tools                                                | 80       |

|     |        | 5.2.5     | Circuit Prototype E2 and Further Complexity Scaling (Circuit F) | 80       |

|     |        | 5.2.6     | Fabrication                                                     | 81       |

|     | 5.3    |           |                                                                 | 81       |

|     | 5.5    | Conciu    | 31011                                                           | 01       |

|              |     |      |  |  |      |  |  |  |  |  |  |  |  | Pa | age |

|--------------|-----|------|--|--|------|--|--|--|--|--|--|--|--|----|-----|

| Bibliography | ••• | <br> |  |  | <br> |  |  |  |  |  |  |  |  |    | 82  |

### List of Figures

| Figu | re                                                                              | P | age |

|------|---------------------------------------------------------------------------------|---|-----|

| 1    | Total reported or suspected hardware counterfeits, 2005-2008 [9]                |   | 14  |

| 2    | Companies reporting suspected or confirmed counterfeit microcircuits, by type   |   |     |

|      | [9]                                                                             | • | 15  |

| 3    | Functional test on example adder [5]                                            | • | 26  |

| 4    | Transistor-level test on example adder[5]                                       | • | 27  |

| 5    | TRUST tools forward design flow [33]                                            |   | 30  |

| 6    | Standard and reverse EDA design methodologies (Adapted from [25])               | • | 32  |

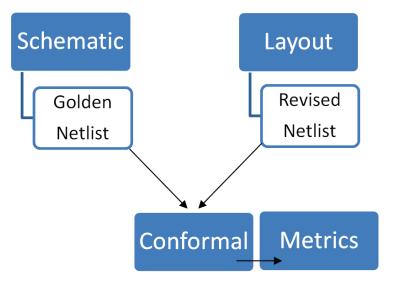

| 7    | Netlist matching toolflow                                                       |   | 37  |

| 8    | Iterative netlist matching process [33]                                         |   | 40  |

| 9    | Conceptual process for preliminary results                                      |   | 44  |

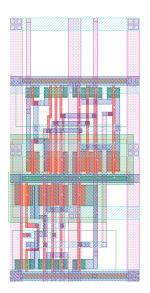

| 10   | Circuit A layout.                                                               |   | 44  |

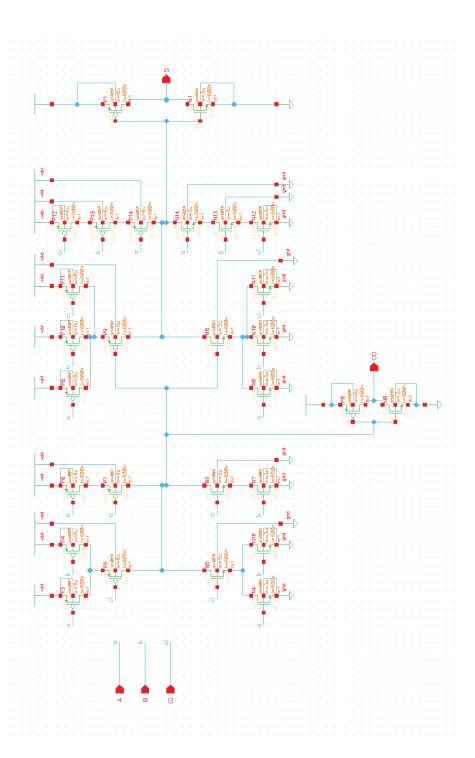

| 11   | Circuit A initial schematic.                                                    |   | 45  |

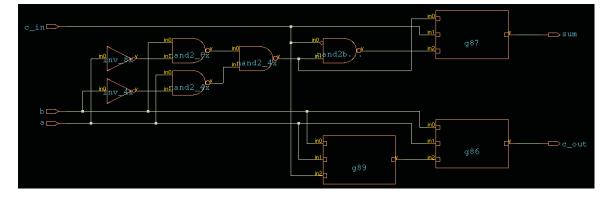

| 12   | Comparison of initial Circuit A layout (left) and schematic (right) netlists as |   |     |

|      | generated by Cadence software.                                                  | • | 46  |

| 13   | Processing Circuit A for Verification                                           | • | 48  |

| 14   | VDD, GND and Z points unmapped by Cadence Conformal                             |   | 49  |

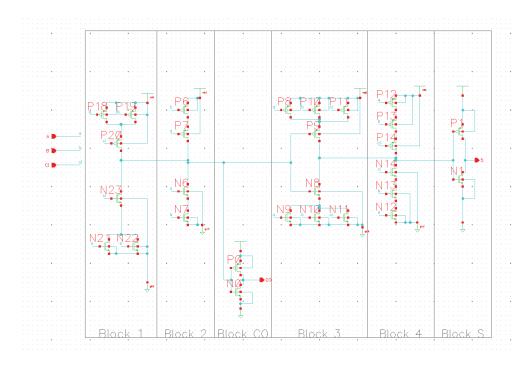

| 15   | Circuit A logical blocks                                                        | • | 51  |

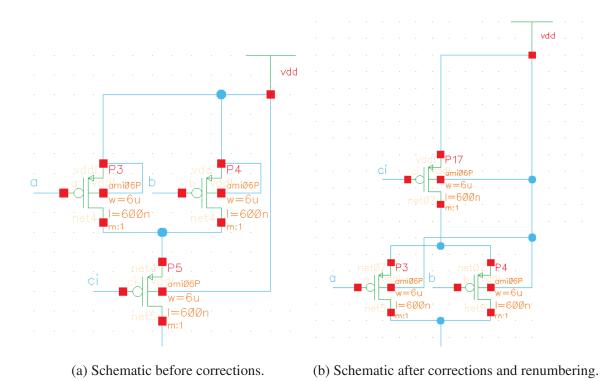

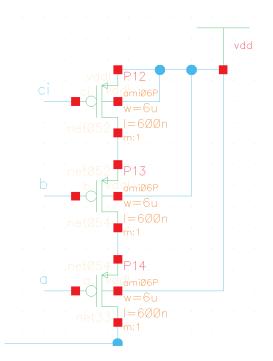

| 16   | Circuit A block 1 PMOS schematic before and after serial order corrections      |   | 52  |

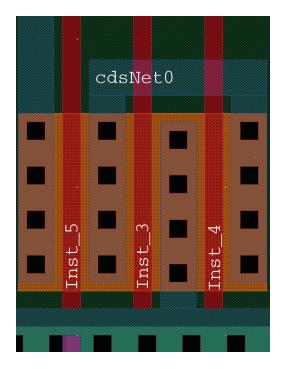

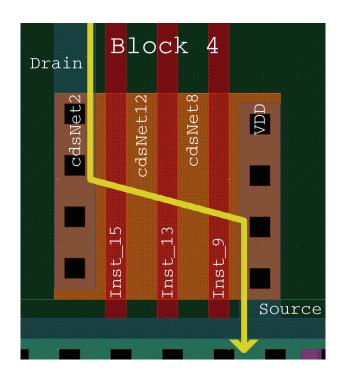

| 17   | Circuit A block 1 PMOS transistors showing ordered series layout                |   | 53  |

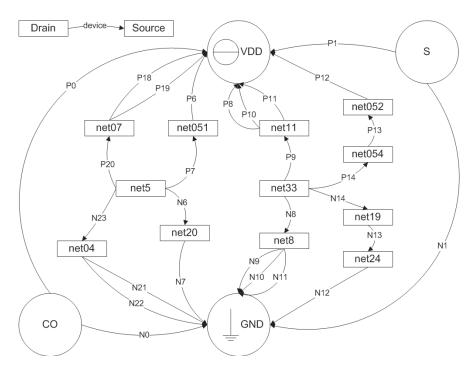

| 18   | Circuit A netlist directed graphs, with legend                                  | • | 56  |

| 19   | Left-to-Right Schematic.                                                        |   | 57  |

| 20   | Left-to-Right Layout.                                                           |   | 57  |

| Figu | re                                                                                 | Page |

|------|------------------------------------------------------------------------------------|------|

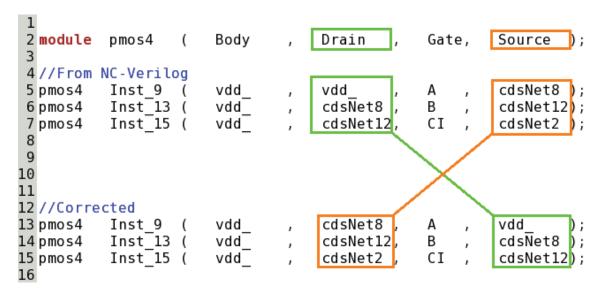

| 21   | Representative Left-to-Right Netlist Modification. Green indicates drains          |      |

|      | changed to sources; Red indicates the opposite.                                    | 58   |

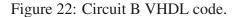

| 22   | Circuit B VHDL code.                                                               | 59   |

| 23   | Circuit B RTL Compiler TCL script.                                                 | 61   |

| 24   | Circuit B Verilog code.                                                            | 62   |

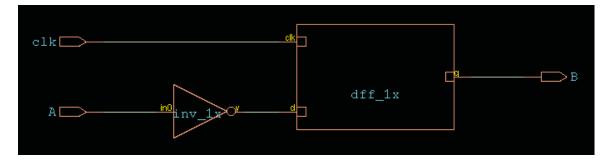

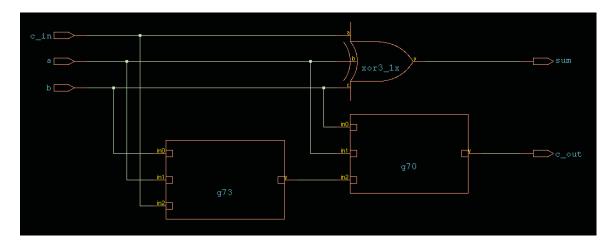

| 25   | A symbolic schematic of Circuit B, the clocked inverter.                           | 62   |

| 26   | The Assura LVS GUI, configured to incrementally verify Circuit B                   | 62   |

| 27   | Conformal showing mapped points in Circuit B                                       | 63   |

| 28   | Processing Circuit B for Verification.                                             | 64   |

| 29   | A symbolic schematic of Circuit C at the top level.                                | 66   |

| 30   | VHDL for Circuit D                                                                 | 67   |

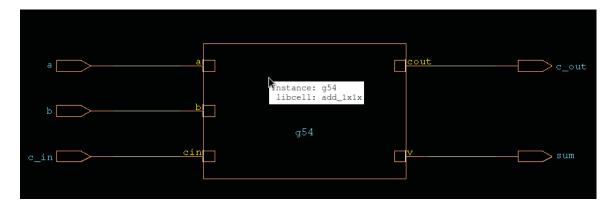

| 31   | A schematic of the single-cell Circuit Prototype D1                                | 67   |

| 32   | Circuit D Tcl script modifications for Circuit Prototype D2                        | 68   |

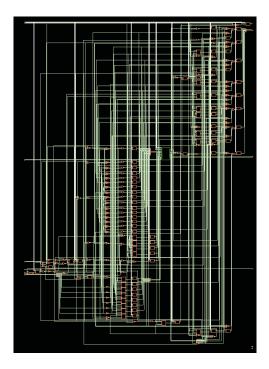

| 33   | A schematic of the complex Circuit Prototype D2                                    | 68   |

| 34   | Circuit D Tcl script modifications for Circuit Prototype D3                        | 69   |

| 35   | A schematic of Circuit Prototype D3                                                | 69   |

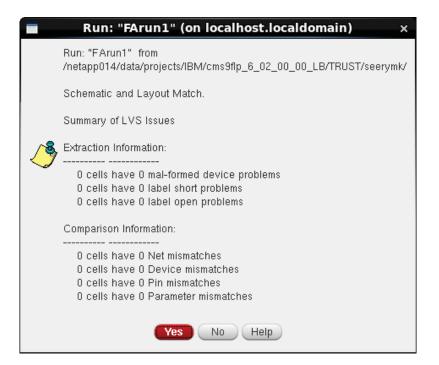

| 36   | Assura layout versus schematic (LVS) showing successful results for Circuit D.     | 70   |

| 37   | Cadence Encounter script to initialize, floorplan, place, route and export Circuit |      |

|      | D                                                                                  | 72   |

| 38   | Cadence Virtuoso graphical user interface (GUI) showing stream-in configura-       |      |

|      | tion for Circuit D                                                                 | 73   |

### List of Tables

| Table |                                                           | Pa | age |

|-------|-----------------------------------------------------------|----|-----|

| 1     | Defense vs. Commercial Requirements [15]                  |    | 10  |

| 2     | DARPA TRUST Metrics                                       |    | 27  |

| 3     | Tools used in TRUST                                       |    | 36  |

| 4     | Circuit A Results                                         |    | 47  |

| 5     | Circuit A device correspondence                           |    | 55  |

| 6     | Circuit Prototype E1 RTL Compiler Estimates               |    | 75  |

| 7     | Circuit Prototype E1 foundational Conformal verification. |    | 76  |

### List of Acronyms

| Acronym | Definition                                  |

|---------|---------------------------------------------|

| AES     | Advanced Encryption Standard                |

| AFB     | Air Force base                              |

| AFRL    | Air Force Research Laboratory               |

| AFIT    | the Air Force Institute of Technology       |

| ASIC    | application-specific integrated circuit     |

| CAD     | computer-aided design                       |

| CMOS    | complementary metal-oxide semiconductor     |

| CMP     | chemical-mechanical polishing               |

| COTS    | commercial off-the-shelf                    |

| DARPA   | Defense Advanced Research Projects Agency   |

| DMEA    | Defense Microelectronics Activity           |

| DoD     | Department of Defense                       |

| DoS     | denial of service                           |

| DoDI    | Department of Defense instruction           |

| DSB     | Defense Science Board                       |

| DTICS   | Defense Trusted Integrated Circuit Strategy |

| EDA     | electronic design automation                |

| FIB     | focused ion beam                            |

| FLIR    | forward-looking infrared                    |

| GDSII   | Graphical Design System II                  |

| GUI     | graphical user interface                    |

| HDL     | hardware description language               |

| HIP     | hard intellectual property                  |

| Acronym  | Definition                                            |

|----------|-------------------------------------------------------|

| IARPA    | Intelligence Advanced Research Projects Activity      |

| IBM      | International Business Machines Corporation           |

| I2C      | Inter-Integrated Circuit                              |

| IC       | integrated circuit                                    |

| I/O      | input/output                                          |

| IP       | intellectual property                                 |

| IRIS     | Integrity and Reliability of Integrated Circuits      |

| LVS      | layout versus schematic                               |

| MOSIS    | the Metal Oxide Semiconductor Implementation Service  |

| MSDC     | Mixed Signal Design Center                            |

| МТО      | Microsystems Technology Office                        |

| NCSU     | North Carolina State University                       |

| NIST     | National Institute of Standards and Technology        |

| NP       | non-deterministic polynomial-time                     |

| OA       | OpenAccess                                            |

| PDK      | process design kit                                    |

| QC       | Quality Control                                       |

| RTL      | register transfer language                            |

| SCR      | standard cell recognition                             |

| SEMATECH | the Semiconductor Manufacturing Technology Consortium |

| TAPO     | the Trusted Access Program Office                     |

| Tcl      | Tool Command Language                                 |

| TiF      | trust in fabrication                                  |

| TF       | Trusted Foundry                                       |

| TSDB     | TRUST structural database                             |

| Acronym | Definition                                                       |

|---------|------------------------------------------------------------------|

| TSN     | Trusted Systems and Networks                                     |

| TRUST   | Trusted Integrated Circuits                                      |

| ULR     | unknown library recognition                                      |

| US      | United States                                                    |

| VHDL    | Very-High-Speed Integrated Circuit Hardware Description Language |

| VLSI    | very large scale integration                                     |

### COMPLEX VLSI FEATURE COMPARISON FOR COMMERCIAL MICROELECTRONICS VERIFICATION

### I. Introduction

D EFENSE related very large scale integration (VLSI) circuits are typically low-volume products that are not highly profitable for commercial manufacturers [5]. However, the degree of technological specialization required to produce them requires contracting of commercial foundries [8]. Furthermore, the migration of previously domestic foundries to international markets due to economic incentives raises issues of trust. Recent events have brought these issues more to light: an early article on threats arising from breaches of trust appeared in *BusinessWeek* in 2008 [16]. Similar articles have been written more recently outlining the nature of the trust challenge from the civilian perspective [31].

The Department of Defense (DoD) depends on a reliable supply of custom hardware [12]. However, the demand presented is small in volume compared to the demand for commercial circuits - in most cases, military order sizes are one one-thousandth or less of a comparable commercial order [15]. Furthermore, custom defense hardware has a strict set of specifications beyond commercial chip requirements for environmental factors, reliability and useful life [24]. Not only must the supply chain provide functional, trusted hardware, but it also must be competitive with available commercial technologies [8]. The disparity is surmountable, but a 2005 report by the Office of the Secretary of Defense identified addressing the challenge to be both difficult and critically necessary to overcome in the interest of national security.

### 1.1 Trust

The largest complicating factor, however, is trust. "Trust" has a very specific definition when referencing DoD "trusted" suppliers. Trust in the context of electronic hardware and information processing, as provided to National Semiconductor Corporation (now Texas Instruments, Inc.), refers to:

"the ability of the Department of Defense to have confidence that a system functions as intended and is free of exploitable vulnerabilities, either intentionally or unintentionally designed or inserted as part of the system at any time during its life cycle." [3]

This statement was intended as a definition of trusted software, and it was composed by the DoD for its Trusted Software Initiative. Given the commonality between the software and hardware trust challenges, is a valid extrapolation [20].

The Defense Trusted Integrated Circuit Strategy (DTICS) memorandum dated 10 October 2003 initiated the programmatic changes that have occurred that led to the founding of the Trusted Foundry (TF) program. It cites requirements for facility and product identification (that is, the clearance, capacity and capability of trusted foundries), near-term acquisition solutions and research initiatives to ensure a healthy domestic integrated circuit (IC) market [11]. As it is defined in the memorandum, *trust* is the ability to certify that designs sensitive to national security concerns are secure in the hands of a commercial manufacturer [11].

A final definition of *trust*, for these purposes, comes from former Acting Under Secretary of Defense for Acquisition, Technology, and Logistics Michael Wynne, who stated in 2004 that *trust* is "the confidence in one's ability to secure national security systems by assessing the integrity of the people and processes used to design, generate, manufacture, and distribute national security critical components" [34].

Since the challenges of volume and performance have made DoD production facilities fiscally untenable, private contractors have been handed the task of fabricating

the United States (US) military's ICs. This privatization presents a security challenge that is difficult to address [22]. Due to financial incentives, many corporations now rely on overseas foundries, further exacerbating the issue. Domestic trust is difficult enough; placing a high degree of trust in foreign owned and operated foundries is an undesirable position for the DoD due to the increased opportunities for tampering and counterfeiting outside the United States [8].

#### **1.2 Research Problem**

ICs are difficult to verify at the individual device level. Shortcomings in IC verification make for glaring vulnerabilities in the form of hardware backdoors, or extraneous operation modes that allow unauthorized, undetected access [28]. A circuit could be ordered that has a certain function, and appears functional, but has a device that popular media have dubbed a "kill switch" [1] such that an adversary could disable it at a crucial moment. The problem of verifying circuits is so difficult that the Defense Advanced Research Projects Agency (DARPA) has funded two programs to enhance DoD verification and reverse engineering capabilities. These two programs are TRUST and Integrity and Reliability of Integrated Circuits (IRIS). Furthermore, DARPA's intelligence community analog, Intelligence Advanced Research Projects Activity (IARPA), has funded a sister program to consider the intelligence aspects of using private foundries.

### 1.3 Justification

A threat is not significant unless it carries with it an impact. The potential for compromised microelectronics to impact defense systems, at small and large scales, is undeniable and significant. Defense technology frequently prevents loss of life, and facilitates the judicious application of force. It follows that verification of defense microelectronics is critical to national defense [8].

In a letter to members of the US Senate Committee on Armed Forces, Moshe Gavrielov (President and CEO of Xilinx) noted that counterfeit parts present not only an immediate threat, but also a prolonged one [14]. Such parts can be likened to a time bomb, poised to cripple a system unexpectedly.

The same Senate Committee released a report on counterfeit electronic parts which noted that exact prediction of the impact of failing electronics is in fact a difficult problem. Often, commercial-grade components are illegally remarked to bear military-grade designations. These parts may not fail until subjected to environmental stresses outside the normal, commercial specification [6]. It is probable that the moment at which a device is most stressed is the same moment it will be most crucial - an observation acceded by the President of the Semiconductor Industry Association, Brian Toohey [29].

### **1.4 DARPA TRUST**

As part of a multifaceted national response to these potential vulnerabilities, DARPA, in 2007, issued contracts in support of a new program known as TRUST. This program set a tiered schedule for contractors to pursue competitively, and provided development funding. The goal was to develop the capability to match a physical device with the register transfer language (RTL) that was used to create it, demonstrating that all components are included and no extraneous devices exist. DARPA TRUST emphasizes the weak links in the supply chain that could be introduced by untrusted manufacturing facilities, and attempts to provide another option than foundry verification in obtaining trusted products. Testing on chips as directed by the program requires performance to design specifications, at a minimum, and not to exceed those specifications in a way that adds unintended functionality. These specifications includes mitigating the risk of modified hardware on the chip as well as interference from microchip peripherals such as packaging, circuit integration and radio sidechannels. It also addresses the threat of chip

modification after installation, and attempts to provide a means of assessing such a condition.

This research intends to increase the capability of the DoD to conduct feature extraction on integrated circuits in support of DARPA TRUST and IRIS. This capability is valuable to the intelligence community as well as for the test and evaluation of commercial off-the-shelf (COTS) circuits for defense applications currently acquired through the Trusted Access Program Office (TAPO) and the TF program.

#### **1.5 Proposed Methodology**

This research builds on previous algorithms implemented in software by contractors in pursuit of the DARPA TRUST program. The candidate selected came from Raytheon, but testing has not been performed on it using real-world circuits outside of the TRUST test cases. Adaptive, a contractor specializing in workflow documentation, has been hired to reestablish, document and automate the existing feature matching and comparison process. This research will build on the existing toolset by investigating success and failure cases of the software across various inputs, ranging from trivial to complex, and attempt to expand those capabilities.

Complex digital designs, found by survey of available, licensed sources, will be synthesized using the Cadence Encounter Suite to generate a unique set of test cases that will explore the limits of the TRUST tools in both transistor count and standard cell usage. The intellectual property (IP) for these designs will be leveraged from preexisting public domain cores or licensed to AFRL or the Air Force Institute of Technology (AFIT) for implementation. This experimentation will present a challenge to the known limitations of the TRUST tools.

#### **1.6** Assumptions and Scope

Successful tests will see a match between the input and final product; failures will be deemed useful to the research if the device structure causing the failure can be determined and assessed. These designs are expected to meet with high Type I error, or Probability of False Alarm ( $P_{FA}$ ) in the feature extraction process initially, which is by nature an iterative process. The open-source designs do not initially contain malicious insertions. Therefore, the initial test metric will be  $P_{FA}$  and will seek to be minimized. A low  $P_{FA}$  will indicate successful verification of a non-malicious circuit.

In order to test the other significant verification metric, Probability of Detection  $(P_D)$ , extraneous logic must be inserted in an open-source circuit. Future work will include  $P_D$ analysis, and analysis of  $P_{FA}$  in real-world circuits containing extraneous insertions. This effort is outside the scope of this initial research into the area. It is understood that the two metrics represent a tradeoff in the verification process, controllable by parametrization of the tool flow, and thereby are a multiobjective optimal matching problem, expected to be computationally intensive.

#### **1.7** Materials and Equipment

The bulk of the research will be performed in the AFRL Mixed Signal Design Center (MSDC) (Wright-Patterson Air Force base (AFB), OH), while some testing will be performed in the AFIT VLSI Laboratory in Building 640. Testing will require the allocation of feasible designs from available sources, including open-source repositories and may possibly include existing designs from other AFIT projects. Cadence design tools will be used to generate Graphical Design System II (GDSII) databases for these inputs which will in turn be used as input to the feature matching and comparison suite.

The equipment required for this experimental investigation is available in the current lab area assigned to this research at MSDC and AFIT, and includes Linux and Windows workstations with sufficient hardware to execute the software package on complex test

cases as well as run Cadence design tools. Licenses for all Cadence products are already purchased through the VLSI course curriculum. In the event that equipment at both facilities becomes unavailable due to breakage or competing experiments, most of the testing can be accomplished from any workstation equipped with Cadence design software, and capable of running MSDC's tool set.

### **II.** Background

VLSI circuits in the defense industry face a unique challenge, as described in Chapter 1. Low demand volume does not strongly incentivize commercial suppliers due to profit concerns. In-house manufacturing is often impractical due to mission requirements that call for a high degree of technological specialization. Recent market trends have driven many foundries to overseas locations, where trust and security challenges exist due to their environment. This issue has been in the public spotlight frequently over the last decade, and continues to be addressed.

### 2.1 Microchip Acquisition

The DoD critically depends on a reliable supply of custom hardware [12]. However, the demand presented is small in volume compared to the demand for commercial circuits - in most cases, military order sizes are one one-thousandth or less of a comparable commercial order [15]. Furthermore, custom defense hardware has a strict set of specifications beyond commercial chip requirements for environmental factors, reliability and useful life [24]. The problem is surmountable, but a 2005 report by the Office of the Secretary of Defense identified addressing the challenge to be both difficult and critically necessary to overcome in the interest of national security. Not only must the supply chain provide functional, trusted hardware, but it also must be competitive with available commercial technologies [8].

The report refers to the demand as "unique". The DoD is unlike any commercial customer in the world. When reliability of a defense-purposed IC is in question, vulnerabilities may exist in defense systems, which may have far-reaching consequences. This high reliability requirement makes the systems expensive due to redundancy and custom (e.g. radiation hardened) design processes.

A presentation from the DARPA Microsystems Technology Office (MTO) describes the applications of DoD custom circuits to be often irrelevant to any commercial application. There is little to no demand for key defense technologies including radiation hardening, high power microwave and millimeter wave radio and various custom sensors, for instance, outside the defense industry; the chips designed for these systems will be uninteresting to the majority of other significant customers [5]. This means less return on the considerable investment of masks and materials necessary to fabricate the devices. Designs that are so severely limited in their reusability are clearly less valuable to a fabrication company than recyclable ones, simply for the sake of not "reinventing the wheel" when new, related work is called for in another product.

Further complicating the problem, the DoD demand itself is small in comparison to the private sector. For foundries, profit generally depends on volume - a factor the DoD simply doesn't bring to the table. For instance, there have been only 63 Lockheed-Martin F-35s built as of last year, each including a multitude of custom components [18]. Sixty-three is an insignificant order size compared to the production volume of most desktop microprocessors. However, the DoD has sought to adhere to the DTICS memorandum, which originally indicated the necessity of a trusted microchip supply chain to a successful national-level information superiority strategy [11]. The DoD need demands that defense technologies must improve at a rate similar to commercial devices, without regard for the decreased production volume, in order for that strategy to be viable [21]. This process can quickly become prohibitively expensive for defense circuitry. According to the Defense Science Board (DSB) report, the expense is only mitigable by massive manufacturing volume and the large (300 mm) wafer size used for high-performance consumer microelectronics.

Volume is a significant factor in constraining the technology limit for defense circuits, but it is not the only factor. The Defense Microelectronics Activity (DMEA)

quantified some of these factors, as shown in Table 1, as a resource for the Professional Council of Federal Scientists and Engineers. This table shows that many other factors differentiate defense from commercial microchip requirements. Specifically, the areas cited are lifespan of both individual systems and production resources, environmental hardiness, reliability in hostile environments and market share. Each category exhibits a clear difference, which serves to make defense microchip supply a challenge.

|                         | Commercial                               | Defense                                   |

|-------------------------|------------------------------------------|-------------------------------------------|

| System life span        | < 5 years                                | 20 to 40 years                            |

| Quantities required     | Very high volume (10 <sup>6</sup> units) | Very low volume ( $10^2$ to $10^3$ units) |

| Fab production lifespan | ~2 years                                 | Decades                                   |

| Environmental           | 0 to 70 °C                               | -55 to 125 °C                             |

| Reliability / Quality   | Lower; ~10 years, non-hostile            | High, hostile                             |

| Market Share            | > 90%                                    | < 0.1%                                    |

Table 1: Defense vs. Commercial Requirements [15]

DoD contracting methods complicate the process by distributing the design across multiple contractors. Since no one party is responsible for the entire supply chain, each design step is complicated by being "blind" to the rest of the system, beyond immediate specifications [32]. Although this separation has the added benefit of mitigating risk through increasing the difficulty of integrating malicious hardware discreetly, it also impedes rapid manufacturing.

The largest complicating factor, however, is trust. "Trust" has a very specific definition when referencing DoD "trusted" suppliers. Trust in the context of electronic hardware and information processing, as provided to National Semiconductor Corporation (now Texas Instruments, Inc.), refers to:

"the ability of the Department of Defense to have confidence that a system functions as intended and is free of exploitable vulnerabilities, either intentionally or unintentionally designed or inserted as part of the system at any time during its life cycle." [3]

This was intended as a definition of trusted software, and was composed by the DoD for its Trusted Software Initiative. Given the commonality between the software and hardware trust challenges, is a valid extrapolation [20].

The DTICS memorandum dated 10 October 2003 initiated the programmatic changes that have occurred that led to the founding of the TF program. It cites requirements for facility and product identification (that is, the clearance, capacity and capability of trusted foundries), near-term acquisition solutions and research initiatives to ensure a healthy domestic IC market [11]. As it is defined in the memorandum, trust is the ability to certify specifically that designs highly sensitive to national security concerns are secure in the hands of a commercial manufacturer [11].

A final definition of trust, for these purposes, comes from former Acting Under Secretary of Defense for Acquisition, Technology, and Logistics Michael Wynne, who stated in 2004 that trust is "the confidence in one's ability to secure national security systems by assessing the integrity of the people and processes used to design, generate, manufacture, and distribute national security critical components [34]."

Since the challenges of volume and performance have made DoD production facilities fiscally untenable, private contractors have been handed the task of fabricating the US military's ICs. This privatization presents a security challenge that is difficult to mitigate [22]. Due to financial incentives, many corporations now rely on overseas foundries, further exacerbating the issue.

The DSB Task Force report [8] gave some key recommendations to develop a long-term solution. These addressed shortcomings in the current plan of action as well as proposing new solution aspects that could set the stage for successful systems

development in the future. Their recommendations for the current strategy include implementing a broad national incentive to keep foundries domestic, including revising import and export legislation, with emphasis on maintaining the US as a dominant market player. The goal of these recommendations is to secure a reliable, long-term source for high-security (i.e. classified) ICs and develop a better categorization system for DoD systems based on trust, performance demand and volume. The report also focuses on increasing awareness of the longevity of any future proposed solutions.

The report includes recommendations for additional actions, as well. It calls for sponsorship of technologies of interest to the DoD within the private sector, specifically radiation hardening techniques for existing designs and new processes, anti-tamper design methodologies and hardware obfuscation of circuitry. There is also a call for an industry-involved consortium similar to the Semiconductor Manufacturing Technology Consortium (SEMATECH), but with DoD interests at its core, with the goal of coordinating and encouraging industry efforts toward defense objectives. Furthermore, it calls for the intelligence community to support the anti-tamper effort by characterizing the threat posed by espionage in non-secure foundries, and developing strategies to mitigate the risk as it is understood.

### 2.2 Trusted Foundries

The DTICS memo [11] generated two directive-type memoranda, which were recently (5 Nov 2012) superseded by Department of Defense instruction (DoDI) 5200.44. DoDI 5200.44 established policy and assigns responsibilities in the areas of general trust and security in technology manufacturing, and in so doing defined the TF program [13].

The contract with International Business Machines Corporation (IBM) in 2004 that was the first for the TF program is an excellent example of the program's efforts. Trust accreditation was ensured for multi-project wafers, dedicated runs, IC production, design tool flow and mask set production, and the rest of the production flow was left open to

other competitors. As of 2011 there were 46 trusted manufacturers in the US, each of whom is capable of trusted activity in a subset of various production factors [23].

These factors include:

- Foundry services in various materials and process sizes

- Mask manufacturing

- Mask data parsing

- Aggregation

- Design

- Brokering

- Test

- Packaging and assembly

- Post-processing

The TF program is task-driven, by means of five necessary components presented as the "program benefits." Each benefit is an objective provision for internal DoD customers [32].

The first benefit is technology, which is required to keep pace with the industry development roadmap. DoD technologies are, by definition, specific to the defense industry. Due to this specificity, a slower schedule for defense development than commercial industry development is to be expected [8]. However, it is the goal of the TF program to keep the development of DoD technologies proportional to industry growth, lagging with a known and constant gap [23]. The DSB report recommends federal domestic subsidy programs to ensure that defense sector research occurs proportional to research in commercial technologies [8].

Secondly, security is a prime factor in any defense technology. The DoD requires protection from corruption, tampering and counterfeiting due to these technologies' extremely sensitive purposes. Adversarial intervention in the IC design and fabrication

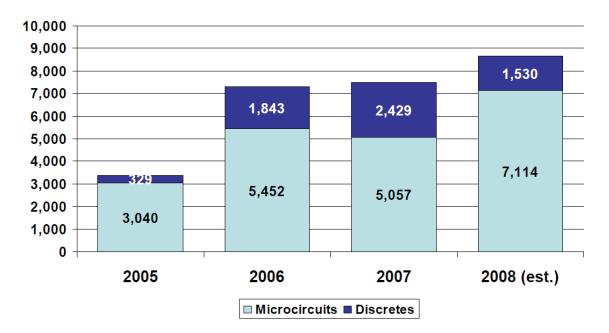

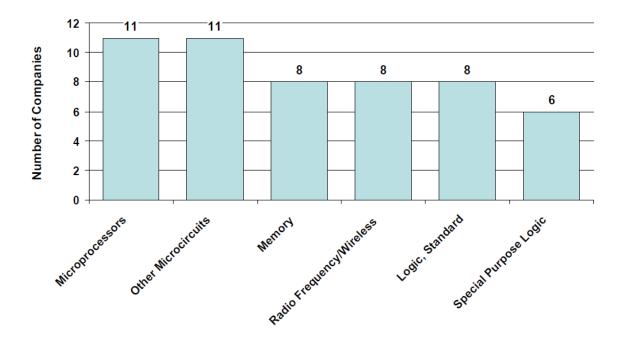

process has the potential to be catastrophic, and is an unacceptable vulnerability [8]. In recent years, the number of identified hardware counterfeiting events in DoD systems has proved significant. In 2008, an estimated 9,356 counterfeit incidents were reported in the defense IC supply chain [7]. Figure 1 shows a summary of counterfeiting incidents reported or suspected between 2005 and 2008. Figure 2 shows the distribution of their types. These data do not include the numerous counterfeits that manufacturers find difficult to detect and may miss: 22 percent of manufacturers surveyed in a 2010 Department of Commerce report found counterfeit chips difficult to identify due to improved fabrication quality in overseas counterfeit operations [10]. According to data collected by the Department of Commerce, the problem is growing [9].

Figure 1: Total reported or suspected hardware counterfeits, 2005-2008 [9].

The third benefit is that of access. The TF program aims to guarantee the availability of fabrication facilities capable of the technologies, volumes and clearance required for all

Figure 2: Companies reporting suspected or confirmed counterfeit microcircuits, by type [9].

DoD projects. Furthermore, every attempt is made to secure fabrication contracts with preferential "Gold Customer" [23] agreements, even despite small production volumes.

The fourth provision is for IP. To ensure the feasibility of DoD custom design projects, the TF program approves and provides access to commercial IP designs. Furthermore, the Program maintains library locations for DoD-owned IP, to include classified components [22].

Finally, an emphasis is placed on cost avoidance. Contracts and acquisition chains that the program establishes are not permitted to accrue penalties from manufacturers for small volume or prototype-scale production [32]. Contracts eliminate top-level overhead costs and fees for foundry access, capacity reservation and indemnification (the "reparations" for incidental, additional costs incurred by the manufacturer) [23].

### 2.3 Threats

Numerous threats exist to the trust of microelectronics production created by the migration of industry to foreign countries. Collectively, breaches of trust in hardware are referred to as *trojans*: "malicious, undesired, intentional modification[s] of an electronic circuit or design, resulting in the incorrect behaviour of an electronic device when in operation," according to the Australian Department of Defence [2]. Shortcomings in trust appear in a number of variations, according to the Under Secretary of Defense for Acquisition, Technology, and Logistics [23]. Specifically, these are:

- Counterfeiting.

- Reverse engineering.

- Overproduction.

- Tampering.

- Quality control.

Counterfeiting, the presentation notes, is a problem for both overseas and domestic foundries. It is the fabrication of one circuit under the guise of another design. As a result of counterfeiting, the product the customer receives is not the design the customer submitted. Integrated circuits are difficult to verify, but the TF program has increased focus on device-level verification of chips to mitigate the counterfeiting risk [23].

Adversarial reverse engineering is another concern. Manufacturing circuits geographically closer to adversaries increases the risk of circuits falling into their hands. Even without the design files, an adversary could physically disassemble the circuit to identify its function, and later replicate it with a custom design or target its weak points in US systems.

Overproduction is a concern due to unauthorized use. A foundry with a secure design could overproduce it, and sell the extras to its host nation or an adversary. The DoD

requires logistical control over its products, and the program seeks to guarantee that the number of circuits ordered matches the number of circuits produced.

Tampering, similar to counterfeiting, is the concern that the submitted design may be modified slightly before receiving the finished product. It could include hardware backdoors, kill switches or any number of elements that generally compromise security or reliability. It differs from counterfeiting in its motive: whereas counterfeiting is usually motivated by greed, tampering is an act of espionage or sabotage [26].

Finally, poor manufacturing capabilities are a significant concern. If a chip is manufactured in the cheapest possible manner, many oversights could be made in the Quality Control (QC) of production. A chip made to minimum standards may not have the expected useful lifetime when implemented on a project. Early failure of parts in defense systems could have substantial impact, to include loss of life.

Through these venues, specific hardware trojans could be implemented in production systems. Trojans are classified on various levels - by their mode of attack, their implementation and their trigger.

In seeking to understand the problem of counterfeit microelectronics, it is necessary to categorize exactly how chips with malicious insertions operate. A hardware trojan is any purposeful modification of a microelectronic circuit that induces unintended operation with ill intent for the intended user. This classification has been attempted using multiple approaches in the past, which were summarized by a public technical report produced by the Australian Department of Defence [2]. Chakraborty, Narasimhan and Bhunia proposed that any hardware trojan is uniquely identifiable by the combination of its trigger mechanism and its payload. Trigger mechanisms fall into combinational, sequential or analog categories; payloads can be digital, analog or "other," a category reserved for effects-based payloads [4].

A combinational or rare-value trigger occurs when various signals are asserted simultaneously, regardless of past machine states. The effects may appear as bugs, triggered randomly, or in the simultaneous presence of specific conditions. Sequential triggers act on a series of states which the device must occupy. As an abstract example, a trojan of this type may be triggered when an on-chip timer counts up, rather than down. The series of upward output states would trigger the payload. Analog triggers, by contrast, do not use digital states, but instead use on-chip sensor output or device activity levels to initiate their actions.

Digital payloads may activate or deactivate a circuit node, or modify memory addresses or content. These are likely to be hard-coded modifications due to timing restrictions for extraneous logic to function as intended. Analog payloads, on the other hand, may serve to bridge multiple signals (that is, short-circuit them), incite unauthorized activity by imposing a rogue signal or may induce an additional delay or long line that causes an unintentional critical path, and incorrect output due to intermediate signals not meeting their internal deadlines. Other payloads, which are based on output effects, may cause a denial of service by simply disabling the chip, or may cause information leakage to an unauthorized recipient node on- or off-chip.

However, this simplified approach does not address the physical characteristics, which a taxonomy proposed by Wang, Tehranipoor and Plusquellic does. Their contributions qualify the uniqueness of hardware trojans with different placements, structures, sizes and types [7]. For instance, an insertion consisting of a dozen transistors may be implemented differently by placing those transistors together in a block or by distributing them throughout other devices on the chip. This aspect is critical, because placement and routing are a difficult problem to solve in the design of a chip, and by that logic, verification is complicated when an insertion is well-hidden.

Rajendran et. al. take a very different approach: in addition to activation, effect and location, they characterize trojans by design phase and abstraction level [27]. These categories are highly applicable to the DoD trusted microelectronics challenge, because they address attributes of trojans that are relevant to the supply chain that produces them. Design phase specifies where in the supply chain the breach of trust occurred and also gives insight into the nature of the modification. If, for instance, the insertion was made by modifying a mask file, two consequences are evident: first, that the mask phase of the trusted supply chain has been compromised and second, that the illicit modification is likely due to a vulnerability in physical device proximity, which can be most easily exploited with a modified mask.

Verification of commercial microelectronics is a necessary subset of the overarching DTICS challenge. The Department of Commerce has shown that, even despite many refinements in the defense IC supply chain, counterfeits still exist in DoD depots [10]. Since the supply chain cannot be perfectly trusted, it is necessary to, as was policy in the Cold War, trust, but verify. Understanding the nature of the exploits that are caused by breaches of trust is necessary to this end, and this chapter has presented various ways the categorization may be performed, as presented by other authors previously.

According to an in-depth review by the Australian Department of Defence, the vast majority of trojans seek to either modify device functionality through faults or backdoors, impede normal operation through unmet specifications (e.g. timing constraints), leak information through existing channels or through sidechannels such as electromagnetic radiation, or execute denial of service (DoS) [2].

Trojans are further described by their implementation in hardware. Some hardware modifications allow unauthorized access in software running on the device; these "malicious processors" require significant foreknowledge of the complete production system [2]. Others seek to create information leakage or timing issues by the rerouting of

otherwise optimized interconnect. Still others seek to create an eventual fault, fuse or unintentional circuit in the chip through early wearout of a very specific component, such as could happen through oxide breakdown or electron migration in a particular point in a chip.

Another property appropriate for the classification of trojans is their trigger mechanism. The last type addressed is considered always-on. These trojans do not require external activation, and are a simple, ever-present hazard. In addition to these, a trojan could be internally triggered through either combinational activation (using a "cheat code") or sequential activation (a "time bomb" or counter activation). Lastly, a trojan could be externally triggered, as through magnetic or radiative interference. Trigger mechanisms are counter-intuitive in that, whereas it would seem logical that a complex trigger would be difficult to detect, in practice small, simple triggers composed of the minimum number of malicious structures are in fact the hardest to detect [2].

A conference presentation at the 2010 Symposium on Circuits and Systems found some majority distributions of these classifications for cases of hardware trojans by means of a survey of an open academic competition. In 90% of the cases, the design phase served as the entry point for the trojan; in 50%, the activation mechanism was in direct input from the user; and the physical location in hardware of 75% of the trojans was in the input/output (I/O) subsystem of the chip [27].

### 2.4 Impact

In a letter to members of the US Senate Committee on Armed Forces, Moshe Gavrielov (President and CEO of Xilinx) noted that counterfeit parts present not only an immediate threat, but a prolonged one [14]. Such parts can be likened to a time bomb, poised to cripple a system quite unexpectedly.

The same Senate Committee released a report on counterfeit electronic parts, in which it noted that exact prediction of the impact of failing electronics is in fact a very

difficult problem. Often, commercial-grade components are illegally remarked to bear military-grade designations. These parts may not fail until subjected to environmental stresses outside the normal, commercial specification [6]. It is probable that the moment at which a device is most stressed is the same moment it will be most crucial - an observation acceded by the President of the Semiconductor Industry Association, Brian Toohey [29].

Real-world examples of these threats exist. The Senate report on counterfeit electronic parts cites the following three incidents, all involving aircraft, of suspect counterfeit electronics.

### SH-60B

Interference filters in the forward-looking infrared (FLIR) targeting system for Hellfire missiles on an anti-submarine helicopter were suspected by the manufacturer in 2009 to be counterfeit, but were not reported until 2011. The originating manufacturer of the counterfeit component was a Chinese fabrication facility. Failure of the part would not be "flight safety critical," but would prevent missiles' targeting systems from acquiring their targets, leading to mission failures.

# C-130J and C-27J

A memory chip obtained from a Chinese manufacturer for a central cockpit display in Air Force cargo aircraft was suspected to be counterfeit by the installing contractor in 2010. Early wearout of the chip presented the potential for the crucial in-flight display to present a degraded image, lose flight telemetry data or even experience catastrophic avionics subsystem failure.

# **P-8**A

A component of the ice detection module in a Navy anti-surface warfare aircraft was found "rattling around inside the module". Further investigation in 2011 revealed the mostly-untested component to be remanufactured from used products.

Failure would cause the ice detection module to fail, and would create the potential for undetected in-flight icing, a critically dangerous condition that threatens crew safety [6].

#### 2.5 Response

These examples and others in the Senate report demonstrate that the magnitude of the threat is not to be overlooked. The US Government responded to the growing potential for counterfeit microelectronics by implementing a number of programs and policies, each of which seeks to improve the problem by reducing the probability that counterfeit chips will be incorporated into production systems.

In 2004, the Deputy Secretary of Defense DTICS memorandum qualified the need for trusted commercial suppliers for leading-edge microelectronics technologies. The memo called for five key strategic areas for improvement: [11]

- 1. Facilities Identification.

- 2. Product Identification.

- 3. Near Term Solutions.

- 4. Research Initiatives.

- 5. Healthy Commercial IC Industry.

The DTICS memorandum drove the DSB Task Force to publish a report the next year on the state of the microelectronics supply chain [8]. That report contained both a cross section of the industry, identified as the Task Force's findings, as well as concrete recommendations for the future of the supply chain.

According to the DoD Trusted Systems and Networks (TSN) instruction [13], DMEA is the accreditation authority for the TF program, and thus for all custom defense application-specific integrated circuit (ASIC) procurement and supplier certification. The

DMEA is the authority on military-grade microelectronics, specifically their lifespan planning, obsolescence and replacement strategies. As such, the TF program, with its acquisitions authority derived from the DMEA, is tasked with securing trusted fabrication facilities for defense-grade microelectronics, to include classified production.

Microchips, after fabrication, must be verified to ensure that no variations were made to the design. Microelectronics verification is a difficult process which can be both microscopically small and intricately complex. TAPO, which is responsible for implementing design and fabrication channels to the TF program, is also tasked with this verification process. The office tests chips for specified operation criteria, but does not yet have the capability to conduct in-depth malicious logic insertion checks.

As part of a multifaceted national response to these potential vulnerabilities, DARPA, in 2007, issued contracts in support of a new program known as TRUST. This program set a tiered schedule for contractors to pursue competitively and provided development funding. The goal was to develop the capability to match a physical device with the RTL that was used to create it, demonstrating that all components are included and no extraneous devices exist.

DARPA TRUST emphasizes the weak links in the supply chain that could be introduced by untrusted manufacturing facilities, and attempts to provide another option than foundry verification in obtaining trusted products. This research intends to increase the capability of the DoD to conduct feature extraction on integrated circuits in support of DARPA TRUST and IRIS. This capability is valuable to the intelligence community as well as for the test and evaluation of COTS circuits for defense applications currently acquired through TAPO and the TF program.

### 2.6 DARPA TRUST

DARPA built the TRUST program to combat an unknown, highly technologically advanced adversary interested in degrading or destroying military capabilities or collecting

unauthorized intelligence by means of creatively modifying hardware between design and delivery. Adversarial agents do exist in the world that possess the motivation, opportunity, talent, manpower and time to conduct operations against the nation's microelectronics resources; the threat is considered credible [5]. The program seeks to provide evidence that electronic components meet provided specifications and do not exceed those specifications in such a way that would compromise the operation of the device or provide for unauthorized operation. Furthermore, DARPA TRUST emphasizes the weak links in the supply chain that could be introduced by untrusted manufacturing facilities, and attempts to provide another option than foundry verification in obtaining trusted products.

Testing on chips as directed by the program requires performance to design specifications - no more, and no less. These specifications includes mitigating the risk of modified hardware on the chip as well as interference from microchip peripherals such as packaging, circuit integration and radio sidechannels. It also addresses the threat of chip modification after installation, and attempts to provide a means of assessing such a condition.

There are multiple points at which the custom fabrication process can be vulnerable to interloping. In the case of an untrusted foundry, the fabrication facility presents a clear opportunity to an adversary. The TF program seeks to nullify this issue by providing fabrication facilities that can be trusted, however the program is not considered a long-term solution [8].

Mask generation is another opportunity for undesired influence from third parties. The masks used to etch the die lithographically can be modified to have weak points or "extra" devices, unbeknownst to the foundry using the masks. At an even earlier stage, the chip designer uses tools that must be trusted: VLSI computer-aided design (CAD) and the use of commercial cell libraries challenge trust-conscious designers, since they promote

the use of "black box" tools. If the trusted designer cannot verify the contents of the "black boxes", then the producer of the component must itself be trusted [5, 25].

There are sometimes untrusted fabrication processes at other stages as well, which TRUST indirectly addresses. The foundry interface is a critical link: intercepted mask generation files could be modified and retransmitted to the foundry. This emphasizes the need for secure digital communication channels and trust-hardy design processes. After fabrication, as well, chips are vulnerable to tampering (in the test, dice and packaging phases). TRUST does not directly address these stages, but trusted design methods discovered by TRUST may make such tampering difficult or impossible [25].

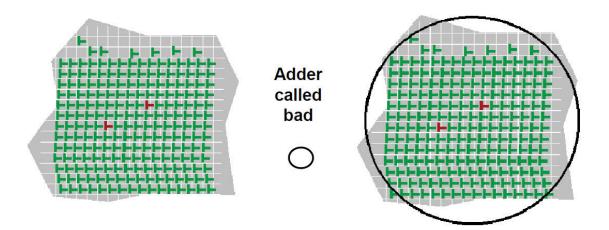

The challenge of verifying a digital circuit is immense. Just a few transistors in a sea of millions may be to blame, and they are physically identical to their neighbors. Delicacies of interconnect and placement are imperative to locating malicious logic. The DARPA MTO TRUST Project Presentation uses the example of a 64-bit adder containing two malicious insertions. The first causes an always-on state in an otherwise conditional gate, and the second is an event-triggered condition for a certain adder input. The result is an erroneous arithmetic output in the 61st bit of one possible adder output at the cost of only two trojan transistors. These transistors are in an array of 2048 transistors over the adder region, which are in a field of  $10^6$  transistors in the entire chip.

Two levels of testing are available to identify the chip as being malicious. Mathematical variables  $P_D$ , the probability of correctly identifying malicious transistors, and  $P_{FA}$ , the probability of identifying a benign transistor as malicious, are used to describe the types of test.

Functional testing can verify that the adder does not produce a correct output, but cannot locate the malicious insertion. This limitation is demonstrated in Figure 3. Functional testing has  $P_D = 1$ , which is excellent for identifying unusable chips. However,  $P_{FA}$  for functional testing is unacceptably large for purposes of locating the malicious

logic. Furthermore, it is important to note that functional testing will not necessarily identify all malicious logic in a circuit, if the insertion does not modify the current output of the device. In other problem cases, in which output is not currently modified, functional testing will not identify the malicious insertion or modification. Functional testing has the added benefit of, at the system level, being a non-destructive, non-invasive test [2].

Figure 3: Functional test on example adder [5].

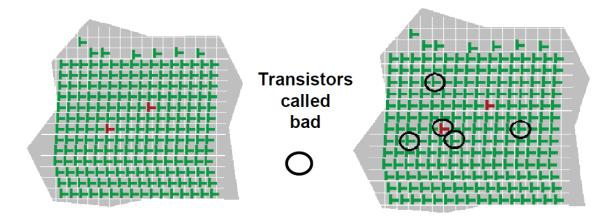

Transistor-level testing, the emphasis of the TRUST program, improves on the ability to locate the insertions, but may sacrifice the 100% detection rate of functional testing on this problem instance. However, it is also capable of identifying latent malicious transistors that do not necessarily modify the current output of the circuit. This capability is shown in Figure 4. In the adder example,  $P_D$  is only 0.5 - that is, only one of the two transistors inserted was identified. However,  $P_{FA}$  is over 500 times smaller, greatly refining the search space.

It is important, from an intelligence perspective, to identify the physical location of malicious logic. Knowing how a trojan was implemented allows an analyst to predict future attack vectors, and identify the stage at which the trusted supply chain may have

Figure 4: Transistor-level test on example adder[5].

been compromised. By this means, adaptive, rather than reactive, solutions to the trust problem can be implemented.

Apart from this sample problem, the TRUST program uses phased, guided metrics for  $P_D$ ,  $P_{FA}$ , problem size and solution runtime. The requirements are reproduced in Table 2.

| Metric                          | Phase 1 | Phase 2 | Phase 3 |

|---------------------------------|---------|---------|---------|

| $P_D$                           | 80.0%   | 90.0%   | 99.0%   |

| P <sub>FA</sub>                 | 1E-3    | 1E-4    | 1E-6    |

| Problem Size (Transistor Count) | 1E5     | 1E6     | 5E7     |

| Algorithm Runtime (Hrs)         | 480     | 240     | 120     |

Table 2: DARPA TRUST Metrics

# 2.7 Conclusion

The TRUST program and the problems it addresses are important challenges facing the nation. The impact of these challenges is present in many fields; particularly, the initiative to defend the nation is justified in focusing efforts on trust in ICs.

### **III.** Methodology

#### 3.1 Introduction

TRUST issues arise when defense-related integrated circuits are fabircated [8]. Market pressure has driven many fabrication facilities overseas, where manufacturing is less expensive but trust is not feasible [6].

The DARPA TRUST program addressed the need for the DoD to identify potentially malicious circuits. This identification, when applied to known microchips, is known as verification. To verify a circuit means to apply a process, such as that described in this paper, to a circuit in order to affirm the accuracy and precision of its contents. This research aims to investigate capabilities, limitations and potential improvements to this microchip verification software when applied to real-world circuits. Under the TRUST program, performers developed a suite of software tools, leveraging commercial electronic design automation (EDA) software, to aid in this identification [5]. Upon completion of the TRUST program, the software suite was delivered to the AFRL MSDC for evaluation and reproduction of performer metrics. However, full capabilities are unexplored. The techniques implemented have demonstrated potential in verifying test cases from DARPA, but are completely untested on real-world circuit verification [32].

Real-world circuits are constrained by transistor throughput and varying usage of technology standard cell libraries. This research builds on the existing toolset by investigating success and failure cases in real-world circuits of the software across various inputs, ranging from trivial to complex, and attempts to expand those capabilities by documenting best practices. The challenge being addressed is, how does software designed for performance on DARPA TRUST test articles perform on microchips from questionable sources?

### **3.2 TRUST at AFRL**

In early 2012, Raytheon transitioned its candidate, selected by the TRUST program, to AFRL MSDC. Raytheon had developed tools to attempt to satisfy the demands of the TRUST program test cases, and experienced success [25]. Its team participated in all three phases described in Table 2, but no tools could complete the final phase in its entirety.

The program's metrics for its three programmatic test phases are included in Table 2.

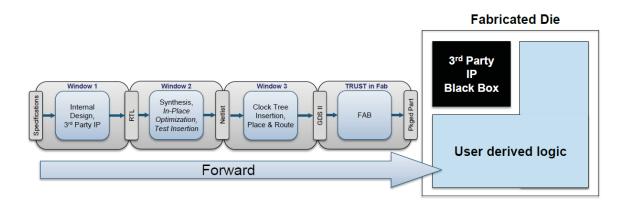

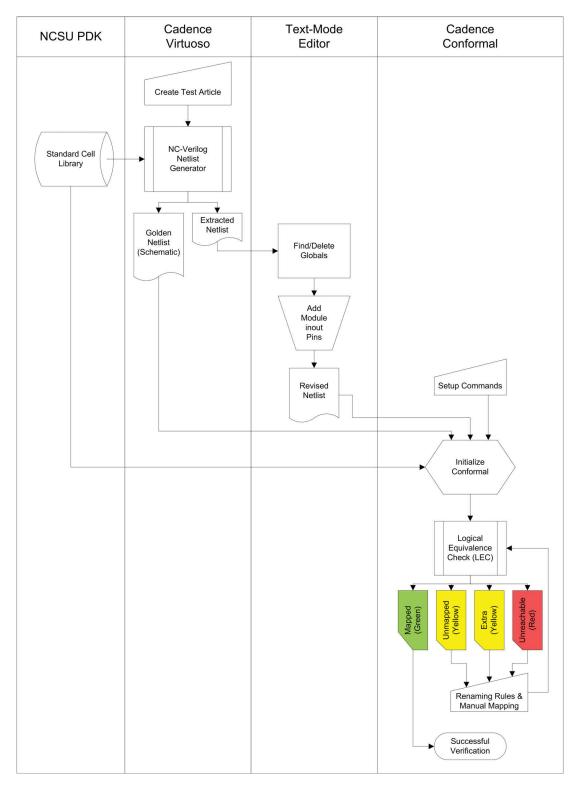

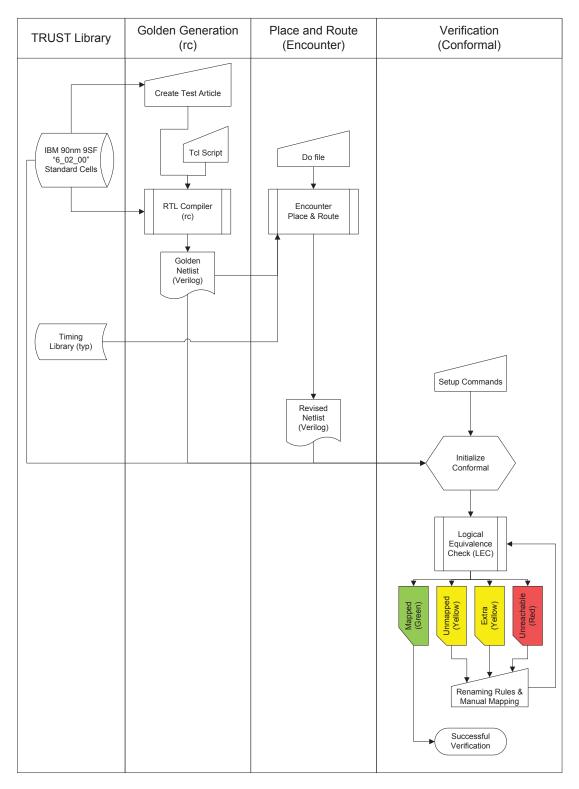

A description of the methods and capabilities of the current TRUST verification toolset is appropriate. In order to verify a microchip, some comparison must be made between the code used to produce the device, and the physical device itself. Figure 5 shows the forward design flow as it relates to the TRUST tools [33]. Each design phase is a state known as a window, and the transitions between the windows are the static design states, such as RTL code or a netlist. It is at these transitions that comparisons can occur, as will be discussed below.

Figure 5: TRUST tools forward design flow [33].

The conventional fabrication flow is a linear process, outlined by the following steps:

# 1. Design in RTL

2. Inclusion of necessary IP cores

- 3. Device synthesis and optimization

- 4. Test insertion

- 5. Clock insertion

- 6. Place and route

- 7. Mask generation

- 8. Fabrication

- 9. Functional testing

- 10. System integration

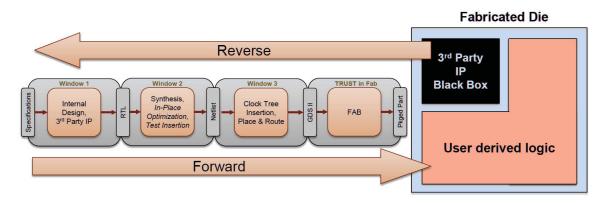

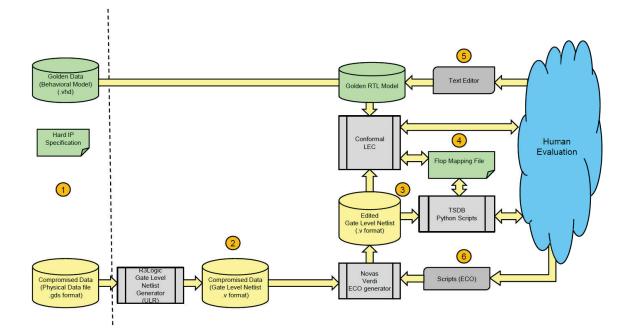

The EDA standard design methodology for ASICs is shown in Figure 6. This design methodology allows for clear break points in the design process as one moves from derivation of specifications to final implementation and fabrication. To reverse the methodology, the physical chipset must be delayered, capturing the metallization and associated connections before generating an electronic equivalent representation (netlist) [24]. Once delayering has been performed, the TRUST tools allow the forward data (golden) to be compared with the reverse data for potential modifications and identification [33].

Figure 6: Standard and reverse EDA design methodologies (Adapted from [25]).

#### **3.3 Test Methodology**

Performance is quantified by means of mathematical variables  $P_D$ , the probability of correctly identifying extraneous structures, and  $P_{FA}$ , the probability of misidentifying a benign transistor as extraneous. Two levels of testing, which are differentiated using these variables, are available to identify a chip as being illicitly modified:

**Functional testing** can verify that a device fails to produce a correct output, but cannot locate the insertion that causes the error. Functional testing has  $P_D$ =1 in cases where an insertion causes an output error, which is excellent for identifying chips that are not operational. However,  $P_{FA}$  for functional testing is unacceptably large for purposes of locating the extraneous logic. Furthermore, it is important to note that functional testing will not necessarily identify inserted logic in a circuit, when the insertion does not modify the current output of the device. In other problem cases, in which output is not modified under the test conditions (for instance, consider a series of latches that only modify output after the millionth clock cycle), functional testing will not identify the malicious insertion or modification. Functional testing has the benefit of, at the system level, being a non-destructive, non-invasive test [2]. **Transistor-level testing** improves on the ability to locate the insertions, but may sacrifice the 100% detection rate that functional testing exhibits for circuit modifications that alter the final output. However, it is also capable of identifying latent, extraneous transistors that do not necessarily modify the current output of the circuit. Transistor-level testing is the emphasis of the TRUST program [5].

The TRUST software uses a derivative technique known as *gate-level testing*. Gate-level testing takes into account the standard cells used in an intellectual property library, identifying instances of the cells and examining the resulting logical structures. For example, a 4-transistor logical NOR gate (that is, the inverse of a logical OR gate) is likely to be instantiated multiple times in a single design. Modern design methodology calls for the design of a standard NOR cell, and the instantiation of this cell across the chip. Leveraging this methodology, the exact pattern of 4 transistors used to generate the NOR cell is easily recognized by automated tools in the Cell Recognition phase described in section 3.3.1. Instead of matching 4 transistors, the software needs only match the NOR cell pattern. Furthermore, more in-depth logical analysis can be performed using the known output pattern of - in this case - the logical NOR gate. This vastly reduces the computation requirements, since basic logical operators and even complex structures, like adders, can be summarized as standard cells.

Functional testing is not sufficient for system integration to occur in defense microelectronic systems. Therefore, the process must be verified at a lower level by working backward through the linear steps until initial design elements can be compared directly against physically fabricated components. Reversal steps are available for nearly every stage, but not all are viable for device comparison [24].

Reverse fabrication is a process known as delayering. Delayering can be accomplished by chemical-mechanical polishing (CMP) or via a focused ion beam (FIB) process. CMP is a coarse grinding process that removes most material indiscriminately,

but is not effective for certain metal interconnect layers. FIB offers finer granularity, but is a slow and expensive process. A method involving stages of each delayering method, known as hybrid delayering, allows a technician to capture images of the device and regenerate the mask (that is, the GDSII file) for each layer [25].

The masks represent the first opportunity for comparison; given RTL, the forward design process can be followed until the mask files are generated, and the results compared to the actual mask files. Unfortunately, due to inconsistencies between routing algorithms, and necessary rounding and approximation in the non-deterministic polynomial-time (NP)-hard problem of VLSI routing, these mask files cannot be expected to be physically identical, despite that they may be functionally identical [33]. Furthermore, device-level comparison between non-identical masks is intractable without descending to an earlier stage in the design flow.

The mask files are not the end of the reverse-direction flow, though. Processing the materials through a device recognition algorithm allows transistors to be recognized, and a picture of the existing components on the chip to be created. This picture is, in fact, a textual listing of devices and their interconnection known as a netlist.

Netlists are an intermediate step prior to mask generation in the forward direction, and are useful for circuit analysis because they list the raw device interconnections. However, their format poses a challenge in the reverse direction because they lack human-readable node and wire names. Given that the algorithm producing the netlist was different for each direction, the forward and reverse netlists are not physically identical even when they may be functionally identical. However, unlike with mask files, it is possible to generate a matching between the unnamed nodes of the untrusted (reverse-generated) netlist and the named nodes of the trusted, golden netlist generated in the forward direction [24].

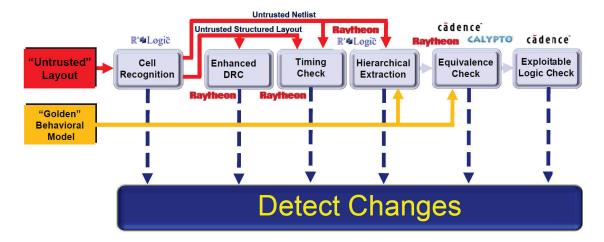

It is at this level that the TRUST toolset performs its comparisons. In an iterative process, node group matchings are made based on various factors, and those matchings are used to infer further matchings. Ideally, a finite number of iterations will yield an exact matching between golden nodes and untrusted nodes, indicating a circuit that is precisely to specification. In the event that complete matching is not possible, the extraneous or omitted logic can be clearly identified, and its function (or lack thereof) deduced. Each stage in the process is a fundamental building block to the overall algorithmic process, and will be discussed in detail.

The tools used by the various design stages are listed for reference in Table 3.

A survey of complex digital designs in the public domain will yield a representative sample of real-world designs. These designs, with varying functionality, will be synthesized using the Cadence Encounter suite to generate a unique set of test cases that will stress the TRUST software in both transistor count and standard cell usage. The equipment required for this experimental investigation is available in the current laboratory area assigned to this research at MSDC and AFIT, and includes Linux and Windows workstations with sufficient hardware to execute the software package on complex test cases as well as run Cadence design tools. The IP for these designs will be leveraged from preexisting public domain cores or licensed to AFRL or AFIT for implementation.