# Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-23-2018

# Methods of Reverse Engineering a Bitstream for Field Programmable Gate Array Protection

Daniel J. Celebucki

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Information Security Commons, and the Theory and Algorithms Commons

#### Recommended Citation

Celebucki, Daniel J., "Methods of Reverse Engineering a Bitstream for Field Programmable Gate Array Protection" (2018). *Theses and Dissertations*. 1800.

https://scholar.afit.edu/etd/1800

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

#### METHODS OF REVERSE ENGINEERING A BITSTREAM FOR FIELD PROGRAMMABLE GATE ARRAY PROTECTION

#### THESIS

Daniel J. Celebucki, 2d Lt, USAF AFIT-ENG-MS-18-M-018

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

### AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# METHODS OF REVERSE ENGINEERING A BITSTREAM FOR FIELD PROGRAMMABLE GATE ARRAY PROTECTION

#### THESIS

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command in Partial Fulfillment of the Requirements for the Degree of Master of Science in Cyber Operations

Daniel J. Celebucki, B.S.E.E. 2d Lt, USAF

March 2018

DISTRIBUTION STATEMENT A APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# METHODS OF REVERSE ENGINEERING A BITSTREAM FOR FIELD PROGRAMMABLE GATE ARRAY PROTECTION

#### THESIS

Daniel J. Celebucki, B.S.E.E. 2d Lt, USAF

Committee Membership:

Scott. R. Graham, PhD Chair

$\begin{array}{c} {\rm Maj~J.~Addison.~Betances,~PhD} \\ {\rm ~Member} \end{array}$

Sanjeev. Gunawardena, Ph<br/>D ${\bf Member}$

#### Abstract

Field Programmable Gate Arrays (FPGAs) are found in numerous industries including consumer electronics, automotive, military and aerospace, and critical infrastructure. The ability to be reprogrammed as well as large computational power and relatively low price make them a good fit for low-volume applications that cannot justify the Non-Recurring Engineering (NRE) costs associated with producing Application-Specific Integrated Circuits (ASICs). FPGAs however, have seen a variety of security issues stemming from the fact that their configuration files are not inherently protected.

This research assesses the feasibility of reverse engineering the bitstream format for a previously unexplored FPGA, as well as the utilization of the knowledge gained during that process to create a bitstream parser and perform a bitstream modification attack. The reverse engineering process utilizes Tool Command Language (TCL) scripts to automate the modification of various configuration options and then synthesize the resulting bitstream. Various configuration options for Input/Output Blocks (IOBs) are mapped to their respective locations in the bitstream and the encoding format for the configuration of several Look-Up Tables (LUTs) is discovered.

This information is then utilized to create a bitstream parser that takes a bitstream as an input and outputs configuration information for IOBs. Additionally, a bitstream modification attack is performed that changes the original design logic by modifying the bitstream directly to change the configuration values of a LUT. Both the parser and bitstream modification attack are shown to work validating the information gained through the reverse engineering process.

### Acknowledgements

I would like to thank my advisor, Dr. Scott Graham, for his advice and mentorship during the thesis process. I would also like to thank my committee and professors for helping me learn the skills needed to complete this reasearch. Finally, I would like to thank my family for their continued love and support which has allowed me to pursue my goals.

Daniel J. Celebucki

## Table of Contents

|      |                          | Page                                                                                                                                                     |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abst | ract                     | iv                                                                                                                                                       |

| Ackı | nowle                    | edgements                                                                                                                                                |

| List | of Fi                    | gures viii                                                                                                                                               |

| List | of Ta                    | ables xii                                                                                                                                                |

| I.   | Intr                     | oduction                                                                                                                                                 |

|      | 1.3                      | Background and Motivation1Problem Statement2Research Objectives2Organization2                                                                            |

| II.  | Bac                      | kground4                                                                                                                                                 |

|      | 2.1<br>2.2               | Reverse Engineering                                                                                                                                      |

|      | 2.3<br>2.4               | Bitstream Synthesis                                                                                                                                      |

|      | 2.5                      | Field Programmable Gate Array Attacks13Side-Channel Analysis13Hardware Trojans14Bitstream Modification15Bitstream Reverse Engineering16Covert Channels16 |

| III. | Exp                      | erimentation Methodology                                                                                                                                 |

|      | 3.1<br>3.2<br>3.3<br>3.4 | Assumptions                                                                                                                                              |

|      | 3.5                      | Configurable Logic Blocks                                                                                                                                |

|       |                          | Page                                                                                                                                                                                                                                              |

|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 3.6<br>3.7               | Bitstream Modification Attack                                                                                                                                                                                                                     |

| IV.   | Res                      | ults and Analysis                                                                                                                                                                                                                                 |

|       | 4.1                      | Input/Output Blocks47Pullmode47Slew Rate and Drive57Input/Output62                                                                                                                                                                                |

|       | 4.2                      | Configurable Logic Blocks                                                                                                                                                                                                                         |

|       | 4.3<br>4.4               | Bitstream Modification Attack                                                                                                                                                                                                                     |

|       | $4.5 \\ 4.6$             | Comparison To Other Reverse Engineering Attempts       71         Overall Analysis       72                                                                                                                                                       |

| V.    | Con                      | clusion                                                                                                                                                                                                                                           |

|       | 5.1<br>5.2<br>5.3<br>5.4 | Motivation and Research Goals74Conclusions75Contributions75Future Work76Switching Matrix76Further Parser Development76More Sophisticated Bitstream Modification Attacks77Automated Reverse Engineering77Concluding Thoughts and Recommendations77 |

| Appe  | endix                    | A. Scripts                                                                                                                                                                                                                                        |

| Bibli | ogra                     | phy90                                                                                                                                                                                                                                             |

## List of Figures

| Figure | P                                                                                           | age  |

|--------|---------------------------------------------------------------------------------------------|------|

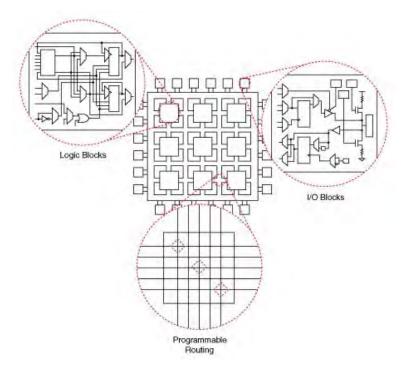

| 1.     | FPGA Architecture showing CLBs, IOBs, and Interconnects [20]                                | 6    |

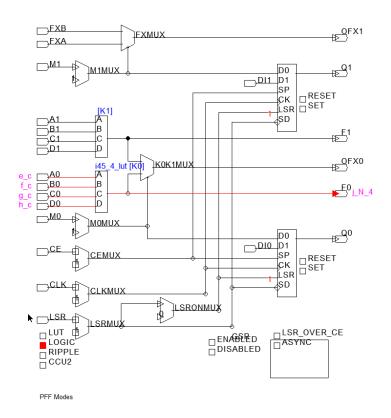

| 2.     | Example configurable logic block                                                            | 7    |

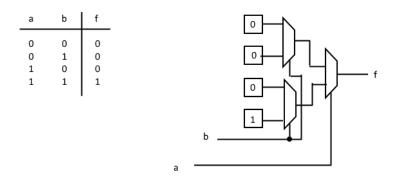

| 3.     | 2-input look-up table example                                                               | 8    |

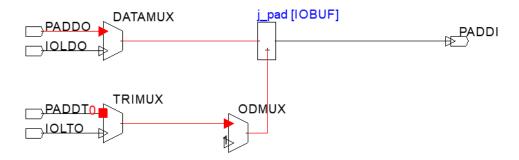

| 4.     | Example input-output block                                                                  | 9    |

| 5.     | Virtual representation of routing paths within an FPGA                                      | 9    |

| 6.     | The process for bitstream generation from HDL [14]                                          | . 10 |

| 7.     | FPGA receiving encrypted bitstream from designer [17]                                       | . 12 |

| 8.     | Lattice Diamond software GUI showing HDL editor, File List view, and Tcl Console            | . 21 |

| 9.     | Lattice Diamond software showing the Process view                                           | . 22 |

| 10.    | Lattice Diamond New Project GUI                                                             | . 23 |

| 11.    | TCL script running generating bitstream files for analysis                                  | . 23 |

| 12.    | Bitstream files generated, renamed, and moved by the TCL script                             | . 24 |

| 13.    | Results of bitstream comparison tool comparing two bitstreams.                              | . 25 |

| 14.    | Results of bitstream printing tool outputting binary for a bitstream.                       | . 25 |

| 15.    | Lattice Diamond Spreadsheet View                                                            | . 27 |

| 16.    | Indices in the bitstream responsible for the pullmode configuration option for various pins | . 30 |

| 17.    | Indices related to changes of the pullmode for pin V5                                       | . 33 |

| 18.    | Pins Groups 1 through 4 showing the differences in changing indices                         | . 34 |

| Figure | Page                                                                                                                                                      |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

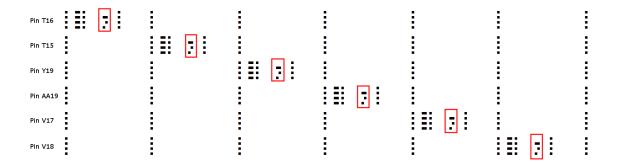

| 19.    | Pins from Groups 5 and 6 showing the differences in changing indices                                                                                      |

| 20.    | Look Up Table initialization value based on the desired truth table                                                                                       |

| 21.    | HDL used to generate a three input AND gate                                                                                                               |

| 22.    | Bitstream values at R2C40D Look Up Table 1 indices for a three input AND gate                                                                             |

| 23.    | HDL used to generate a more complicated logic function 40                                                                                                 |

| 24.    | Bitstream values at R2C40D Look Up Table 1 indices for a more complicated logic function                                                                  |

| 25.    | HDL used to generate the OR gate for the bitstream modification                                                                                           |

| 26.    | LPF constraints used to generate the OR gate for the bitstream modification                                                                               |

| 27.    | Indices that were modified to transform an OR gate into an AND gate                                                                                       |

| 28.    | Pins and their configuration options used in the bitstream parser test                                                                                    |

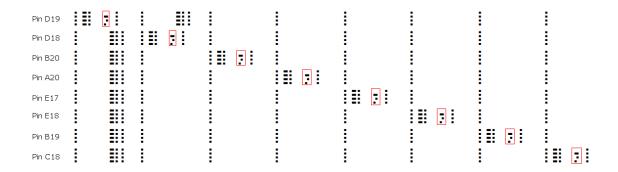

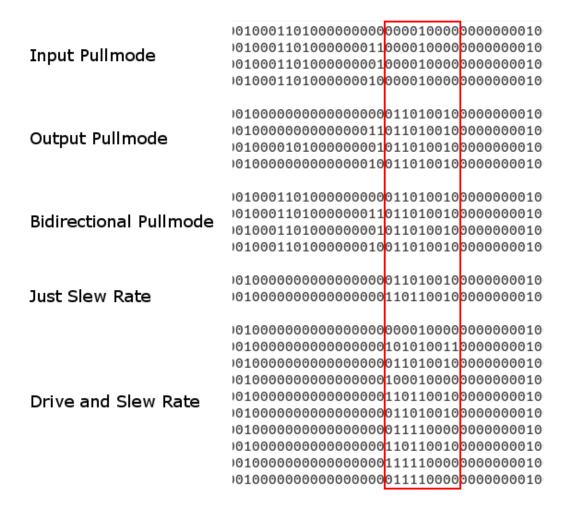

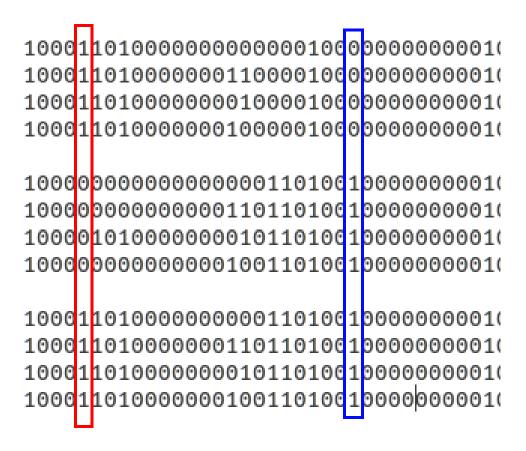

| 29.    | Selection of bitstreams related to the pullmode configuration of group 1 input pins with 1's replaced with black space and 0's replaced with white space  |

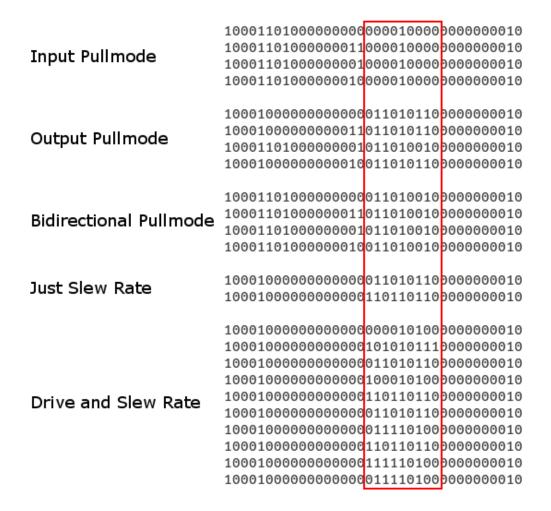

| 30.    | Selection of bitstreams related to the pullmode configuration of group 1 output pins with 1's replaced with black space and 0's replaced with white space |

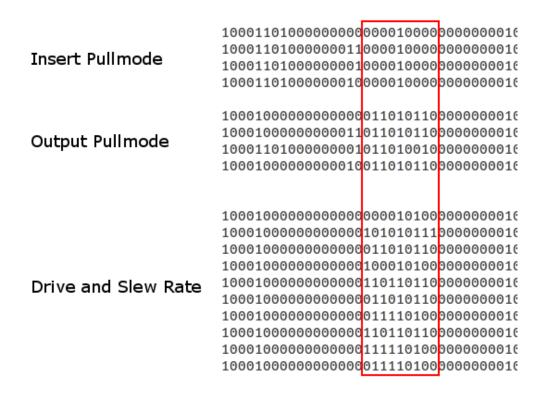

| 31.    | Selection of bitstreams related to the pullmode configuration of group 2 pins with 1's replaced with black space and 0's replaced with white space        |

| 32.    | Selection of bitstreams related to the pullmode configuration of group 3 pins with 1's replaced with black space and 0's replaced with white space        |

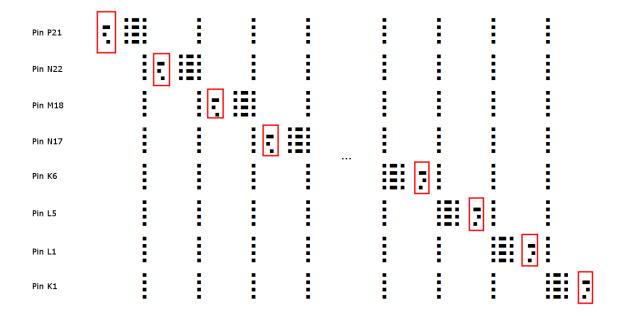

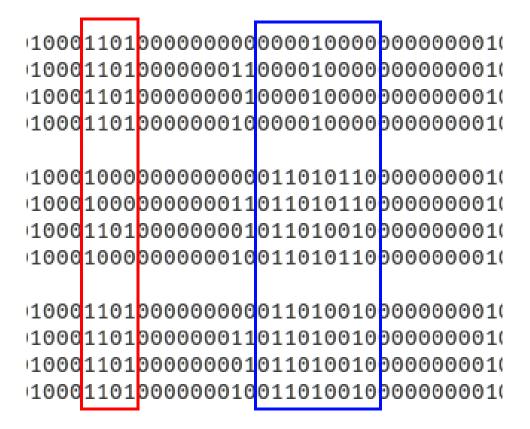

| Figure |                                                                                                                                                                         | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

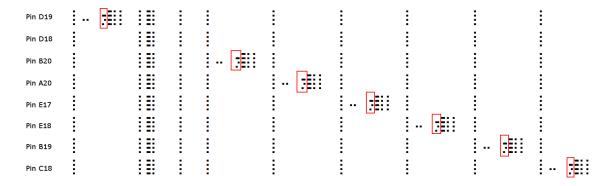

| 33.    | Selection of bitstreams related to the pullmode configuration of group 4 pins with 1's replaced with black space and 0's replaced with white space                      | 52   |

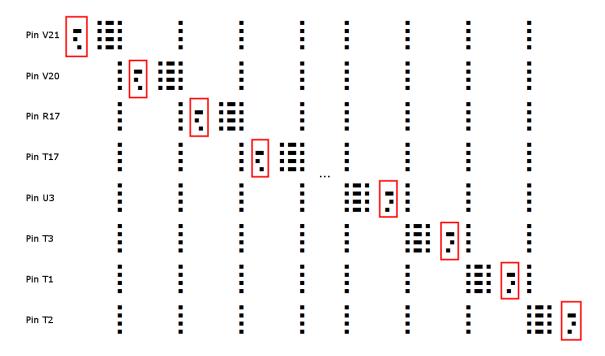

| 34.    | Selection of bitstreams related to the pullmode configuration of group 5 pins with 1's replaced with black space and 0's replaced with white space.                     | 54   |

| 35.    | Selection of bitstreams related to the pullmode configuration of group 6 pins with 1's replaced with black space and 0's replaced with white space                      | 56   |

| 36.    | Comparison of bitstreams generated for pin D19                                                                                                                          | 58   |

| 37.    | Comparison of bitstreams generated for pin D17                                                                                                                          | 59   |

| 38.    | Comparison of bitstreams generated for pin T16                                                                                                                          | 60   |

| 39.    | Indices related to changing slew rate and drive for pin C21                                                                                                             | 61   |

| 40.    | Comparison of bitstreams generated for pin C21                                                                                                                          | 61   |

| 41.    | Comparison of two bitstreams for pin T15 showing there was no difference between the 8 mA drive level with fast slew rate and the 12 mA drive level with slow slew rate | 62   |

| 42.    | Portions of bitstreams related to indices controlling input, output, and bidirectional options for pin D19                                                              | 63   |

| 43.    | Portions of bitstreams related to indices controlling input, output, and bidirectional options for pin D17                                                              | 65   |

| 44.    | Bitstreams from a Look Up Table 1 in Configurable<br>Logic Block R2C40D with different configuration values                                                             | 67   |

| 45.    | Continuation of bitstreams from a Look Up Table 1 in Configurable Logic Block R2C40D with different configuration values.                                               | 67   |

| 46.    | Mask for R2C40D Look Up Table 1                                                                                                                                         | 68   |

| 47.    | Various dip switch states showing the correct function of an OR gate.                                                                                                   | 69   |

| 48.    | Various dip switch states showing the correct function of an AND gate after a bitstream modification attack                                                             | 70   |

| Figure |                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------|------|

| 49.    | Results of testing the parser to parse a bitstream using pins with a variety of pullmodes, slew rates, and drive |      |

|        | levels                                                                                                           | 71   |

### List of Tables

| Table |                       | Page |

|-------|-----------------------|------|

| 1.    | Pullmode Groups       | 32   |

| 2.    | Valid Drive Strengths | 36   |

| 3.    | Derived Truth Table   | 41   |

#### Acronyms

ASIC Application-Specific Integrated Circuit

**CLB** Configurable Logic Block

CMOS Complementary Metal-Oxide-Semiconductor

FPGA Field Programmable Gate Array

GUI Graphical User Interface

**HDL** Hardware Description Language

ICS Industrial Control System

**IOB** Input/Output Block

**IP** Intellectual Property

**LED** Light Emitting Diode

LPF Lattice Preference File

**LUT** Look-Up Table

**mA** milliamp

NCD Native Circuit Description

**NRE** Non-Recurring Engineering

**RPM** Revolutions Per Minute

SRAM Static Random Access Memory

TCL Tool Command Language

# METHODS OF REVERSE ENGINEERING A BITSTREAM FOR FIELD PROGRAMMABLE GATE ARRAY PROTECTION

#### I. Introduction

#### 1.1 Background and Motivation

FPGAs are used in the military, automotive, and consumer industries and their prevalence is increasing [7]. Although these devices continue to increase in capacity and speed [24], they still face a number of security issues [8, 3, 22, 15].

Reverse engineering is one of these issues. When considering FPGAs, reverse engineering usually consists of "transforming an encoded bitstream into a functionally equivalent description of the original design" [7]. However, the reverse engineering effort can also be partial, meaning the full functionality of the design is not reproduced but data from the bitstream such as encryption keys or LUT content is still extracted. Reverse engineering itself can be considered a security issue but it can also enable other security threats by making use of information gained during the reverse engineering process.

One such threat that can be enabled is bitstream modification or injection. This attack focuses on directly modifying the encoded bitstream in order to produce a change in the original design. Because the original design is not known, modifications to the bitstream are difficult, and usually result in a broken design or the design not loading. Bitstream injection was considered improbable before 2013 when Chakraborty demonstrated that presynthesized ring oscillators could be injected into the bitstream in locations that had not been utilized by the original design [3]. The

ring oscillators were used to dissipate power increasing the circuit operating temperature. While impressive, injecting into unused portions of an FPGA cannot be used to interact with the original design. This research focuses on utilizing the knowledge gained through reverse engineering to protect FPGAs against security threats as well as execute a more advanced bitstream modification attack.

#### 1.2 Problem Statement

This research presents the process and results of reverse engineering a bitstream in order to show that this knowledge can be used to both protect or attack FPGAs. As FPGAs increase in prevalence, identifying security threats and ways to defend against these threats becomes increasingly important.

#### 1.3 Research Objectives

The goal of this research is to assess whether reverse engineering the bitstream format for a LatticeECP3 LFE3-35EA-8FN484C FPGA can be used to protect or attack an FPGA. There are two main hypotheses. The first is that a parser can be created that can detect malicious modifications to a bitstream by utilizing the information gained by reverse engineering the bitstream. The second is that a bitstream modification attack that directly influences the original design of that bitstream can be carried out using information from reverse engineering that bitstream.

#### 1.4 Organization

Chapter II provides background relevant to the understanding of this research. FPGA structure and programmability is discussed along with various security features and threats. Chapter III discusses the target system, assumptions, design decisions, and methodology to reverse engineer a bitstream, create a bitstream parser, and

perform a bitstream modification attack. Chapter IV discusses the results of the reverse engineering process, effectiveness of the bitstream parser, and the results of the bitstream modification attack. Chapter V concludes with a summary and a discussion of future objectives for continuing research.

#### II. Background

This chapter provides background information and context related to Field Programmable Gate Arrays (FPGAs). Information describing the composition of FPGAs as well as the process behind their configuration is provided.

#### 2.1 Reverse Engineering

Reverse engineering is the process of analyzing a subject system to identify the system's components and their interrelationships and to create representations of the system in another form or at a higher level of abstraction [4]. Reverse engineering is typically used by adversaries trying to gain knowledge about a system when they lack design information or details. Reverse engineering can be used on both hardware and software systems but the objective is typically different. When considering a hardware system, the objective is usually to duplicate the system. When reverse engineering software, the objective is usually to gain a design-level understanding of the system to aid maintenance, strengthen enhancement, or support replacement [4].

When considering FPGAs the objective of reverse engineering is usually to understand the bitstream format. This is because if the bitstream format is known, the netlist can be recovered [21, 2, 6]. Although the netlist is not the same as the Hardware Description Language (HDL) design file, the netlist contains all the components that make up the hardware design being implemented on the FPGA. If one can reverse engineer the bitstream format they can then use that knowledge to recover the netlist, often considered to be proprietary, and even referred to as Intellectual Property (IP).

#### 2.2 Field Programmable Gate Arrays

FPGAs were first introduced in 1984 by Xilinx and over the next three decades increased in capacity and speed by factors of 10000 and 100 respectively [23]. Unlike traditional Application-Specific Integrated Circuits (ASICs), which are customized for a particular use, FPGAs are reprogrammable. This reprogrammability is accomplished using a combination of Configurable Logic Blocks (CLBs), Input/Output Blocks (IOBs) and interconnects. Figure 1 shows an example FPGA architecture highlighting the CLBs, IOBs, and interconnects. CLBs are made up of various digital circuits such as Look-Up Tables (LUTs), multiplexers, adders, and flip flops. The CLBs can then be configured to perform different combinational functions. The interconnects are used to connect the various CLBs to create the desired circuit. IOBs provide connections to external stimulus. The trade off for this reconfigurability is that ASICs are more compact and power efficient than an FPGA implementing the same circuit.

FPGAs are configured using a HDL which is synthesized into what is generally referred to as a 'bitstream'. The HDL code describes the structure and behavior of the circuit while the bitstream is a series of 0's and 1's which specify the configuration options of the CLBs, IOBs, and interconnects to produce that circuit. Each FPGA vendor has their own proprietary bitstream format and the details of that format are not usually released to the public.

Depending on the type of FPGA (Static Random Access Memory (SRAM), Flash, or Antifuse) the bitstream is programmed and stored in different ways [19]. SRAM FPGAs use internal volatile static latch cells to store configuration data and need to be programmed after every power cycle [24]. After they are powered on the bitstream is transferred from an external non-volatile memory source to the FPGA. Flash FPGAs use internal non-volatile memory to store the configuration data which means

Figure 1. FPGA Architecture showing CLBs, IOBs, and Interconnects [20].

no external bitstream transfer is necessary. It also allows for faster power-on and information transfer through power-cycles [24]. Antifuse FPGAs program through a pulse which form low-resistance connections between the internal nodes making it one-time programmable. Regardless of the type of FPGA the configuration is largely the same. The bitstream's ones and zeros are used to tie high and low voltages to LUT initialization values, multiplexer selectors, switching matrix transistors, etc. Every configurable option on the FPGA is represented somewhere in the bitstream and is tied to high and low voltage states based on the values in different locations in the bitstream.

#### Configurable Logic Blocks.

CLBs are what allow the FPGA to implement custom logic. Although there can be some differences between the hardware implementation of a CLB depending on the manufacturer of an FPGA, they commonly include LUTs, multiplexers, and flip-flops. Figure 2 shows an example CLB with two LUTs and two flip-flops.

Figure 2. Example configurable logic block.

Instead of a traditional ASIC that uses hardware logic gates to implement the digital logic for the desired circuit, FPGAs utilize LUTs to implement the logic. Figure 3 shows an example of how a 2-input LUT utilizes multiplexers to implement digital logic. Instead of using an AND gate with a and b as the inputs, the LUT utilizes the inputs a and b as the selectors for the multiplexers and then, via the appropriate bits in the bitstream, initializes the inputs to the multiplexers as the output values for the truth table desired. This produces a circuit that is logically equivalent to an AND gate. If the user wants to implement a different circuit, the input values to the multiplexers can be changed allowing a new digital circuit without actually changing the FPGA hardware. LUTs trade space for reprogrammability in that the actual

hardware needed to implement the LUT is much larger than the hardware needed to implement the same digital circuit that the LUT is replicating. However, LUTs can be reprogrammed to implement any desired logic function as long as it fits within the bounds of the truth table. Designs that require more inputs than the LUT has available can be implemented by daisy chaining multiple LUTs together.

Figure 3. 2-input look-up table example.

#### Input Output Blocks.

IOBs are used to connect the internal logic of the FPGA to external components. At their most basic they consist of a physical pad that serves as the bridge between the FPGA and the rest of the system along with a number of multiplexers. Since the IOBs usually allow both input and output to the same physical pad, the choice of whether a certain pin will be an input or output is decided at configuration time. There are also other configuration options that determine the physical characteristics of the signal at the pin such as pullmode, slew rate, drive, etc. These configuration options vary from FPGA to FPGA. Figure 4 shows an example IOB that is configured as an output.

Figure 4. Example input-output block.

#### Switching Matrix.

The switching matrix is the largest portion of the FPGA (in terms of silicon area consumed) and is responsible for connecting the CLBs and IOBs to produce the desired digital logic circuit [9]. The reason that the switching matrix is so large is that nearly every CLB and IOB must be able to connect to each other. The large number of routes that need to be accommodated results in a large switching matrix. Figure 5 shows the routing paths of a simple digital circuit. The configuration of the switching matrix, which is determined by specific bits in the bitstream instantiates these routes.

Figure 5. Virtual representation of routing paths within an FPGA

#### 2.3 Bitstream Synthesis

An HDL file is transformed into a bitstream through a number of steps. Figure 6 shows the process that is used for most FPGAs. First the HDL code is synthesized into a netlist. The netlist contains the list of components in the circuit and the nodes they are connected to. The map function maps the components in the netlist to the components that are found on the FPGA the designer is compiling to. Place then takes the mapped list of components and selects the locations of those components on the FPGA. Since the FPGA will most likely have numerous copies of the same components, place decides which of those components will actually be part of the circuit. Route then makes the connections between all of the placed components on the board. After the circuit has been placed and routed it can be converted into a bitstream file that will configure the correct components and connections on the board to create the circuit.

Figure 6. The process for bitstream generation from HDL [14].

#### 2.4 Field Programmable Gate Array Security

As FPGAs gained popularity, the issue of security rose in importance for both vendors and customers. Vendors wanted to protect their hardware designs and technology from being reverse engineered, copied, or modified by other vendors. They were also concerned with the protection of "soft cores" or HDL modules that were created to program an FPGA. The protection of soft cores is the primary security concern for customers because it protects their designs from being reverse engineered

or copied by competitors [8].

Unlike ASICs which are difficult to modify once they have been created and require sophisticated and expensive technology in order to reverse engineer the design, FPGAs merely need a configuration file which specifies the design to be implemented. This allows a competitor to start the reverse engineering process from a configuration file instead of the hardware. This is why bitstream formats are kept secret. If the format was publicly accessible, as soon as the competitor extracted the bitstream they could reverse the design. However, this does not protect the bitstream from reverse engineering, it only prolongs the process. Once a competitor figures out the format they can reverse the bitstream into a more useful file type.

FPGA vendors and customers have used a number of methods to protect their designs from competitors including obfuscation, encryption, and reconfiguration. For the rest of this thesis FPGA security will refer to the protection of soft cores from reverse engineering, copying, or modification rather than the protection of the actual FPGA hardware design unless specified otherwise.

#### Obfuscation.

One method that can be used to increase security is to obfuscate the design. Obfuscation is the process of intentionally modifying the description or structure of a circuit in order to conceal its functionality to make it more difficult to reverse engineer [10]. Although this method may not stop a competitor from reverse engineering the design, obfuscation may increase the cost of reverse engineering to the point where it is cheaper for the competitor to invest in creating their own design instead.

There are two approaches to hardware obfuscation, passive obfuscation and active obfuscation. Passive obfuscation alters the comprehensibility of the HDL code so that it is difficult for a human to understand but will still compile with the same

functionality. Active obfuscation on the other hand, alters the functionality of the circuit. Many times active obfuscation is key based where a key or sequence of keys must be applied to the input to unlock the normal function of the circuit. If the key is not applied the circuit will function incorrectly [10].

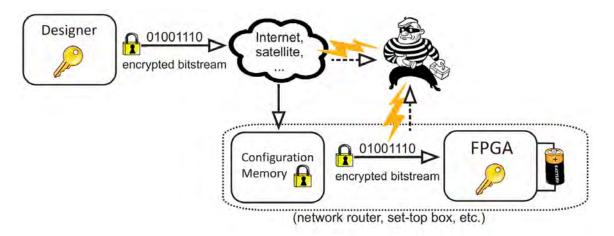

#### Encryption.

In order to protect the intellectual property of their customers, FPGA vendors offer a bitstream encryption feature on high-end models. Figure 7 shows an example of how bitstream encryption works. In this example a FPGA based network router is being updated. Both the designer and the FPGA share the same secret key. The designer encrypts the new bitstream and sends it to the router. The FPGA has an internal decryption engine and decrypts the bitstream after it is loaded from configuration memory. After decryption, it configures itself according to the new bitstream. Even if the bitstream is intercepted over the Internet or when the bitstream is being loaded from configuration memory, the attacker will be unable to decrypt the bitstream without the secret key [17].

Figure 7. FPGA receiving encrypted bitstream from designer [17].

However, encryption alone is not sufficient for system security in a number of

#### situations including [11]:

- Applications requiring FPGAs with low-energy and cost requirements or small form-factors. These FPGAs may not have encryption blocks because of their constraints.

- 2. Remote upgrades of the design using a new encryption key. In these cases the encryption keys must be sent with the bitstream leaving them vulnerable to an attacker who can intercept them.

- 3. Devices that remain in the field for many years. They are susceptible to physical attacks such as side channel analysis [17].

#### 2.5 Field Programmable Gate Array Attacks

As vendors and designers have come up with different ways to protect their intellectual property, adversaries and competitors have come up with their own ways to reverse engineer, copy, and modify those designs. Security follows a cyclical nature with new attacks emerging followed by security measures to defeat those attacks, finally followed by new attacks and the cycle continues [8]. Two types of attacks that have been particularly noteworthy in the past decade are side-channel analysis attacks and implanting hardware trojans.

#### Side-Channel Analysis.

Side-channel analysis attacks exploit physical information leakage of operations executed within a device in order to extract secret data. Many times the secret data is related to the cryptographic key stored on the device used to decrypt the bitstream [17]. Side-channel analysis can come in a variety of forms depending on which external

characteristics are measured. Three types of side-channel analysis related to FPGAs are [8]:

- 1. Power analysis: Power is consumed in two ways in integrated circuits. Dynamic power consumption is due to Complementary Metal-Oxide-Semiconductor (CMOS) gates changing state according to the logic transition. Static power consumption is due to current flowing between the source and drain terminals and through gate oxide. This is referred to as "gate leakage". By analyzing the electrical current patterns of an integrated circuit, information about the data it is processing may be revealed to the attacker.

- 2. **Electromagnetic analysis:** Electromagnetic fields are caused by current changes during execution of a function. These fields can be detected outside of the device using finely tuned antennas and analyzed to uncover the secret data.

- 3. Timing analysis: The timing of different functions such as conditional branching, memory access, and algorithmic operations are often related to the key state during cryptographic operations. An example of this would be comparing a password one character at a time. If the function took different amounts of time for a match and miss then the attacker could determine the password.

#### Hardware Trojans.

Hardware Trojans are malicious, hard-to-detect hardware modifications. They have become a potent threat to ensuring trustworthiness of integrated circuits due to outsourcing steps in the manufacturing process [3]. They can be used for a variety of functions including decreasing the lifetime or reliability of the device, functional failure, or leakage of secret keys. They are also a significant threat to FPGAs since the bitstream used to configure the device could potentially implement a Trojan.

Without the source code used to generate the bitstream it can be very difficult to detect their presence. Additionally, it is possible to insert a Trojan into an FPGA design by modifying the bitstream [3]. In this case, the attacker does not need any knowledge of the design to insert the Trojan. Instead the Trojan is inserted at a location in the bitstream that was not being utilized.

#### Bitstream Modification.

Bitstream modification can be performed by both an adversary that intercepts the bitstream, or an insider. Consider the situation where an Industrial Control System (ICS) company is licensing the IP that it uses for its FPGAs. If an adversary can intercept the bitstream, it could be modified and the ICS company would be unable to tell since they only receive a bitstream file. Chakraborty showed that this is a real threat since a bitstream can be modified to introduce hardware trojans without actually knowing the HDL used to create the bitstream [3]. In this case they inserted ring oscillators to increase the temperature of the FPGA thereby accelerating its aging. This attack could be implemented by an insider that is responsible for loading the bitstream onto the board, or by an adversary that intercepts the original bitstream and delivers the modified bitstream to the company.

An adversary that is able to reverse engineer the target FPGA could go farther by gleaning information about the bitstream and then making changes to the bitstream directly. This information allows the adversary to make more effective changes without having to understand the totality of the design. If the adversary is able to completely reverse engineer the bitstream file then they will have absolute control in understanding and changing the bitstream.

#### Bitstream Reverse Engineering.

Bitstream reverse engineering is a significant threat to the security of the intellectual property of designers. Since the bitstream is a string of 0's and 1's that configure the components on the board, until the competitor can determine how the bitstream is configuring those components the design is still protected. However, researchers have shown that given enough time, a bitstream can be reverse engineered into the netlist which describes the design [21, 6].

Once the netlist has been generated the design can be understood, modified, and synthesized to run on other FPGAs. However, the process is time intensive. In order to isolate a configuration option many bitstreams must be generated, with each containing slight differences. The bitstreams can then be compared to see how configuration changes affect the makeup of the bitstream. This process then has to be repeated over and over again for each configuration option. Additionally, some configuration options are difficult to isolate because a change to a certain configuration option can also affect other configuration options.

#### Covert Channels.

A covert channel allows two cooperating entities to communicate secretly, in violation of a security policy, by manipulating shared resources [16, 12]. This is similar to a side-channel however, a side-channel leaks information to other parties, and does not require the cooperation of malicious entities. Covert channels are further divided into storage channels and timing channels. Storage channels communicate by modifying a storage location such as a hard drive or system memory. Timing channels communicate by performing operations that affect the real response time observed by the receiver. To show a covert channel example consider the case where a vehicle with an FPGA wants to fool an emissions test. The emissions test will most likely

use the same sequence of inputs to test the vehicle such as throttle the engine to 2000 Revolutions Per Minute (RPM) and hold for 3 minutes, increase to 4000 RPM for one minute, etc. In order to fool the test a storage channel between the IOBs and a set of CLBs could be implemented. The IOBs could write the values of the RPM values to some location in memory that is then checked by the CLBs controlling ignition timing and other factors that affect emissions. If the CLBs see a certain sequence of RPM values they would know that they are in the middle of an emissions test and possibly change ignition timings or other engine factors in order to reduce emissions. A timing channel could be implemented to achieve the same feat by increasing or decreasing the delay for the signal between the IOBs and the CLBs to communicate different RPM values. If a certain sequence of delays is recognized the outputs are then changed to produce fewer emissions.

#### III. Experimentation Methodology

This chapter explains the methodology used to reverse engineering an Field Programmable Gate Array (FPGA) bitstream format as well as utilize the knowledge gained through the reverse engineering process to perform a bitstream modification attack.

#### 3.1 Assumptions

There are a number of assumptions that must be made in order for this research to succeed. The first is that the bitstream is either not encrypted, or that the decrypted bitstream can be recovered somehow. Encrypted bitstreams impede the ability to parse information about the bitstream or execute a bitstream modification attack because the mapping of the configuration options to the bitstream is no longer constant. Reverse engineering the bitstream format using encrypted bitstreams would be much more difficult and even if some progress was made, changing the encryption key would negate any work done.

The second assumption that is made is that the bitstream is not obfuscated in any way. This means that the bitstream file is exactly the file that is loaded into the configuration memory in order to program the FPGA. If this bitstream was obfuscated and went through some sort of decoder hardware before being loaded into the configuration Static Random Access Memory (SRAM) the reverse engineering process could be significantly harder.

These are both valid assumptions to make because not all FPGAs offer encryption options and even those that do have had their encryption broken [17, 18]. Additionally, assuming that the bitstream is not obfuscated is completely valid for most situations because the common situation is to have the bitstream directly loaded into the

configuration memory instead of passing it through some decoding hardware [25, 1].

#### 3.2 Target System

The target system for this paper was the LatticeECP3 LFE3-35EA-8FN484C FPGA. Although this work could have been performed on any FPGA, this one was chosen for a number of reasons. Both Xilinx and Altera have had numerous scientific research articles published on their FPGAs with both having been explored to some degree in regards to reverse engineering their bitstream [21, 22]. Lattice, on the other hand has seen much less attention on anything other than the extremely small iCE40 FPGAs [5]. This allows for comparisons to be made between the reverse engineering process for the Lattice FPGAs and the processes for the Xilinx and Altera FPGAs. Additionally, since any FPGA could be studied and we had decided on a Lattice FPGA due to the reasoning above, we decided to pursue a investigate a midgrade FPGA with enough computational power to implement many different designs. To reverse engineer a bitstream, the primary tool needed is the synthesis software that transforms a Hardware Description Language (HDL) design into a bitstream. Having the physical device, with the actual FPGA is only needed to test bitstream modification attacks.

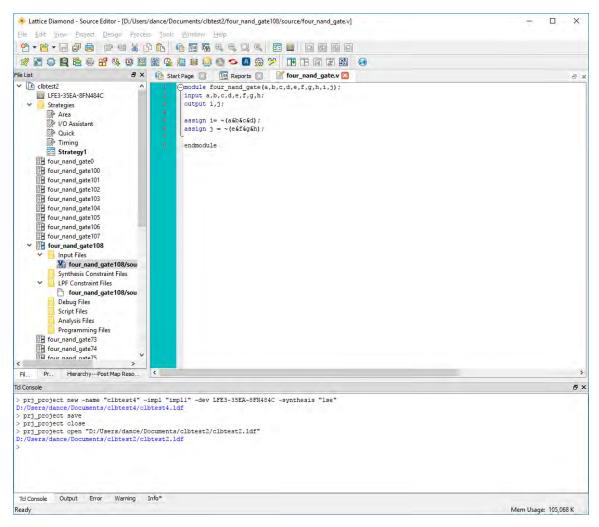

All bitstreams were synthesized using the Lattice Diamond software, version 3.9.1. with the specified FPGA as the target device, and utilized the Lattice Synthesis Engine for synthesis of the bitstreams. The synthesis of bitstreams was performed using Tool Command Language (TCL) scripts that were evaluated by the pnmain.exe application. This allowed for the scripting of bitstream generation.

The Lattice Diamond software is free to download from Lattice Semiconductor and allows HDL code to be synthesized into bitstreams for various Lattice FPGAs. A free license allows synthesis for lower end FPGA models and purchasing a license allows synthesis for higher end models. The tool organizes designs using projects and implementations and has a number of views to show information about the project. Figure 8 shows an example view with the HDL editor as the main view, the implementations within the project shown on the left side and the TCL Console shown below. Figure 9 shows the process view instead. Projects share the same target FPGA and can contain different implementations. Implementations are groups of files such as HDL, Lattice Preference File (LPF), analysis, and programming files that are used to synthesize a bitstream for the target device. A project can contain any number of implementations but only one implementation can be active at a time. Additionally, only one process can be running on a project at any given time.

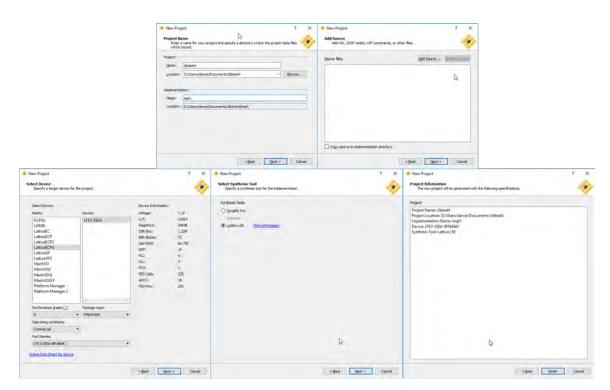

Projects can be created using the New Project Wizard shown in Figure 10 or by using TCL commands. When actions are selected within the Graphical User Interface (GUI) they are then translated into TCL commands and then evaluated in the console. Figure 8 shows an example of this happening. After the new project selections were made using the GUI in Figure 10 the following line appears and is executed in the TCL console which can be seen in the bottom pane of Figure 8:

prj\_project new -name "clbtest4" -impl "impl1" -dev LFE3-35EA-8FN484C

-synthesis "lse"

This is the TCL command that is generated by the GUI and is evaluated by the Lattice Diamond software to create a new project. Additionally, projects can be modified and synthesized without ever using the GUI by running TCL scripts through the command line TCL console. Projects can be created, source files can be added or removed, and bitstreams can be generated all without interacting with the GUI. This was pivotal to the reverse engineering effort because manually configuration for producing bitstreams would be very time consuming and likely suffer from numerous human input errors.

Figure 8. Lattice Diamond software GUI showing HDL editor, File List view, and Tcl Console.

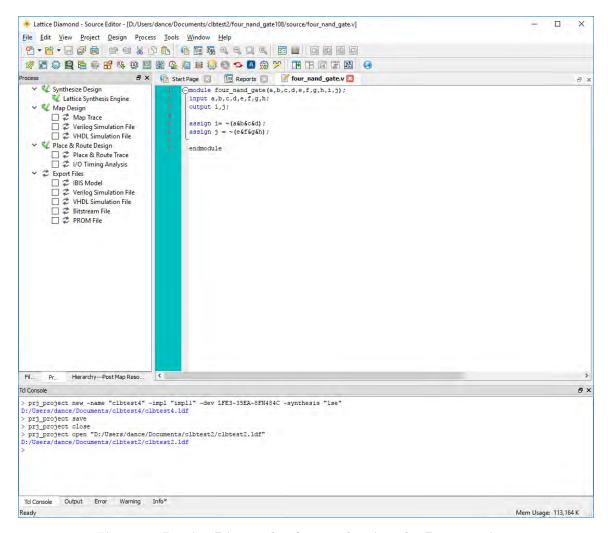

#### 3.3 Bitstream Reverse Engineering Process

This section serves to describe the general process used when reverse engineering certain configuration options for the Lattice LFE3-35EA-8FN484C FPGA. The first step was to downselect to a specific configuration option to reverse engineer. This could be a specific pin set as an input or output, a logic function initialized in a Configurable Logic Block (CLB), a certain intersection in the switching matrix, etc. Upon selecting the configuration option to be investigated, the option was exercised

Figure 9. Lattice Diamond software showing the Process view.

through all possible values, generating a corresponding bitstream for each value. This was done using TCL scripts that would modify either the LPF or the HDL file and then synthesize the bitstream. These scripts all followed a similar pattern. The TCL script would open a Lattice Diamond project that already had a prepared HDL file and LPF, copy the HDL design and LPF into a new implementation and set it as the active implementation, modify the LPF or HDL file, synthesize the bitstream, and then repeat. Listing A.1 shows an example of one of these TCL scripts that was used to generate bitstreams for the pullmode option for each of the pins. A single script

Figure 10. Lattice Diamond New Project GUI.

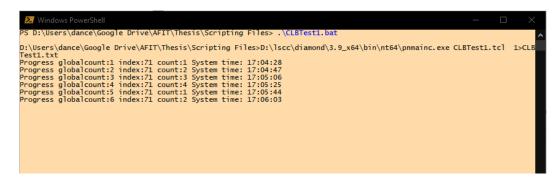

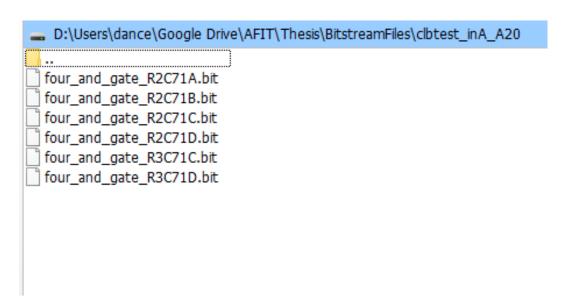

could exercise configuration options for any number of components on the board. The script would name and relocate the bitstream files as it synthesized each one so that all files were in a single location. Figures 11 and 12 show the script executing and the resulting output bitstream files. The TCL scripts were executed via batch files that would call the TCL file so that groups of TCL scripts could be executed sequentially.

Figure 11. TCL script running generating bitstream files for analysis.

Figure 12. Bitstream files generated, renamed, and moved by the TCL script.

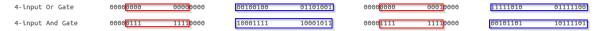

After the bitstreams were generated they were analyzed in an Ubuntu 14.04 virtual machine, harnessing the many advanced shell scripting commands. The bitstreams were analyzed using the program found in Listing A.2 which takes bitstream files as inputs and outputs the location of differences between these files and the values at those locations. Figure 13 shows an example of this program being used. The two .bit files are the bitstreams that are compared and the numbers in the leftmost column represent locations in the bitstreams where the two files differ. The hex values on the same row as one of those locations represents the values of the bitstreams in hex at those locations. After comparison, the binary of bitstreams was usually analyzed and compared to each other. This made it easier to see trends that were more difficult to notice when observing the hex outputs. Figure 14 shows an example of the bitstream printing tool found in Listing A.3 being used to print the binary from index 0 through index 20. The tool is able to print both the binary or hex depending the flag specified.

While analyzing these bitstreams it became obvious that the configuration options

Figure 13. Results of bitstream comparison tool comparing two bitstreams.

Figure 14. Results of bitstream printing tool outputting binary for a bitstream.

that could be exercised in isolation should be reversed first. If an option affected other parts of the design it was difficult to isolate which portions of the bitstream were responsible for that change because many indices could change at once. For example, switching a pin from an input to an output could result in greater than 50 changes in the bitstream because the switching matrix was also affected. Isolating which parts of the bitstream were responsible for the shift from input to output and which portions were the switching matrix was very complicated, involving many bitstreams, and lots of comparison and contraction.

However, much like corner pieces in a jigsaw puzzle, configuration options that manifested few changes in the bitstream when exercised could be used as figurative footholds to help reverse other configuration options by observing similar patterns or eliminating certain locations in the bitstream based on previously reversed options.

# 3.4 Input/Output Blocks

This section describes the process of mapping the relationship between the bitstream file and the configuration of the Input/Output Blocks (IOBs).

IOBs have two main advantages when considered in a reverse engineering perspective. The first is that there are far fewer of them than either CLBs or the switching matrix. There are 295 pins on the target FPGA while there are 33264 Look-Up Tables (LUTs) as shown in Figure 10. Additionally, the IOBs and CLBs make up a very small percentage of the board when compared to the switching matrix [9]. Their smaller number means that it takes less time to synthesize bitstreams for all of them in order to compare how the configuration options manifest differently in the bitstreams.

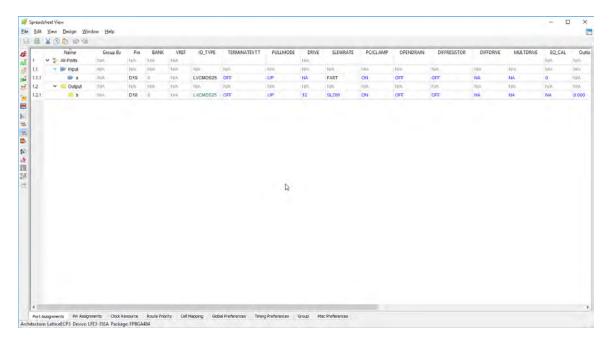

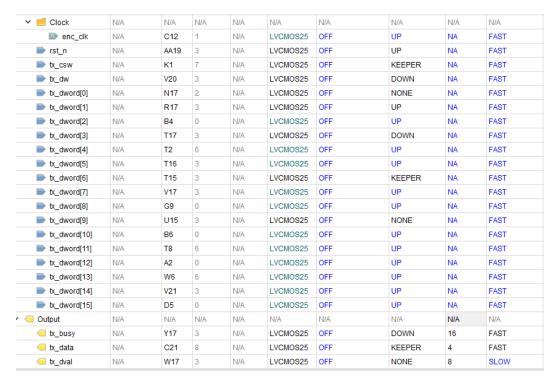

The second advantage is that their configuration options can be changed very easily using either the spreadsheet view shown in Figure 15 or the LPF. The spreadsheet view shows all of the inputs and outputs for a given design and their configuration options. These options can be changed by double-clicking an option and selecting one of the given values. These changes are then translated into commands that are written to the LPF.

Being able to change configuration options directly ensures that the changes that manifest in the bitstream are both isolated and reflective of the actual configuration option. Consider the case of the LUTs which will be explained in more detail in a future section. There are two ways that the configuration values of a given LUT could be changed. The first would be to write a variety of HDL files using different logic operators that are then translated into LUT configuration values. The second is to initialize those LUTs using supported HDL primitives and selecting the configuration values specifically. Method two is better suited for the reverse engineering effort because the bitstreams will definitely reflect the configuration values specified. Method

Figure 15. Lattice Diamond Spreadsheet View.

one on the other hand leaves the relationship obscured because the synthesis engine initializes the LUTs. If the synthesis engine is performing optimizations it is very difficult to know if the changes in the bitstream are actually reflective of the desired configuration option changes. Additionally, since changes made to the configuration options in the spreadsheet view were present in the LPF, modifying the LPF directly enabled automated bitstream generation.

There were three main goals when reverse engineering the IOBs. The first was to map all of the configuration options for each pin to their respective indices and values in the bitstream file. The second was to determine whether a pin was an input or output based on the bitstream file. And finally, to determine whether a pin was connected to logic blocks in the design. The following sections describe the methodology for reversing that configuration option.

### Pullmode.

The pullmode is responsible for describing how the signal will be interpreted at the pin. The pullmode can be set to four options:

- Up: Input is attached to a pull-up resistor, i.e., the pin is tied to logical "1".

- **Down**: Input is attached to a pull-down resistor, i.e., the pin is tied to ground or logical "0".

- **Keeper**: Neither pull-up nor pull-down. Drives a weak 0 or 1 to match the level of the last logic state present on the pad to prevent the pad from floating.

- None: The input is not set to any of these modes.

Each of these options can be toggled using either the spreadsheet view or by modifying the LPF directly.

For the remainder of this document an index refers to the byte address in the bitstream after the header. When discussing changes in a bitstream due to a design change both the number of indices that change as well as the locations within those indices are discussed. A change in the pullmode of a pin had between 3 and 6 indices of change reflected in the bitstream. This was especially isolated when compared to other design changes such as moving the location of a CLB which could result in 70 - 100 indices changing. This isolation made pullmode a key candidate for reverse engineering.

Satisfied that this configuration option was sufficiently isolated, a TCL script synthesized bitstreams for every pullmode option for every pin, with each pin set as an input and then again with each pin set as an output. The pseudocode for that script is shown below. The objective was to determine which indices were responsible for the pullmode option for each pin as well as answer whether there was a common

pattern used for every pin to identify the pullmode. The hypothesis was that each pin would have a different location in the bitstream that would store its configuration options and that the values at those locations would each follow the same pattern in terms of representing the pullmode in the bitstream.

# Algorithm 1 Pullmode Bitstream Generation

- 1: for Pin p in all I/O Pins do

- 2: **for** pullmode **val** in UP,DOWN,KEEPER,NONE **do**

- 3: Replace IOBUF line in LPF with "IOBUF PORT "a" PULLMODE=val"

- 4: end for

- 5: Replace Location line in LPF with "LOCATE COMP "<input/output pin name>" SITE p"

- 6: end for

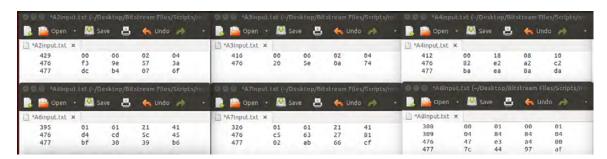

After the script generated the 2296 bitstreams, they were then compared to find the indices in the bitstream responsible for the pullmode configuration option for each pin. As shown in Figure 16, relatively few indices changed for each pin. Each text file in the picture was generated by comparing the four bitstreams (pull-up, pull-down, bus keeper, and none) that were generated for each pin and listing all of the indices in the bitstreams that were different from any of the other bitstreams. In each text file, the first column with hex values refers to the values in the bitstream associated with pullmode pull-up, the second refers to pull-down, the third refers to bus keeper, and the fourth column refers to none. The numbers on the leftmost column are the indices in the bitstream where the changes occurred. So for instance, when comparing the four bitstreams that were generated for pin A2 when set as an input, the only differences between the four bitstreams appear in bytes 429, 476, and 477. It should be noted that indices 476 and 477 appear in almost every one of the listed comparison files. Recall that each index points to a specific byte in the bitstream. If any bit in

that byte is different, then the value at that index will change. Because we are searching for specific bits, it may be necessary to examine the values at the bit level rather than the byte level. However, with the bitstreams generated it was impossible to know whether all of the indices listed for each pin were necessary to configure the different pullmode options or if just a subset of the indices shown for each pin was necessary.

Figure 16. Indices in the bitstream responsible for the pullmode configuration option for various pins.

To solve this problem the bitstream generation script was again executed with different logic designs mapped to different portions of the FPGA. The reasoning for this was to isolate the indices responsible for the pullmode configuration option. Based on the hypothesis above, if the same generation script was executed with different combinational logic designs and mapped that logic to different portions of the FPGA, the indices that are responsible for pullmode configuration must have the same value across all of the different runs while indices that are affected by the switching matrix and CLBs would change. The following gates and placements were used.

- 1. 1 Input NOT Gate at R2C73D

- 2. 1 Input NOT Gate at R23C53A

- 3. 2 Input AND Gate at R3C70B

- 4. 1553 Encoder Placed by the compiler

When exploring which designs and placements were necessary to isolate the indices, the need to vary the CLBs in sufficiently diverse ways became clear. This was achieved by using a NOT gate, an AND gate, and the Intellectual Property (IP) core for a MIL-STD-1553 encoder. The encoder represented a larger design while the simple gates represented smaller designs. Each of the gates were then placed in different slices within CLBs on different portions of the FPGA and the 1553 encoder was placed by the tool. This proved to be enough variation initially and if none of the indices expressed different values additional variation could be introduced before considering that all of the indices listed were necessary to represent the pullmode configuration. After the bitstreams were generated for the additional logic designs, the bitstreams for each pin were compared and printed to text files. This comparison resulted in four comparison files for each pin created using the four bitstreams generated for each logic design. The four comparison files for each pin were then collated into a single text file in order to see how the indices and the values of those indices changed as the same pin exercised the same pullmodes across 4 different designs. Examples of these files can be seen in Figures 18 and 19. It should be noted that the indices never changed between different logic designs but the values at those indices sometimes changed. The indices whose values did not change between designs were assumed to be responsible for the pullmode configuration option and were examined more thoroughly.

To answer the question of why not just assume that all indices listed are responsible for pullmode, there are a few reasons that suggest otherwise. Firstly, the number of indices that changed for each pin when comparing bitstreams for each of the pullmodes was not constant. Some pins had only 3 indices change where as other pins had 6 indices change. Why would a designer decide to use more indices to represent the same change in different pins? Additionally, each pin had indices that were different

but some pins also had indices that were the same. Why would a designer have the same information located in two separate places when creating larger files will increase the time needed to configure the FPGA and also increase the complexity of the process used to parse the bitstream? It seemed more likely that some indices were being changed as a result of some other variation that was changing as a result of changing the pullmode.

Table 1. Pullmode Groups

| Group Number | Indices                                 |

|--------------|-----------------------------------------|

| Group 1      | 476 or 477                              |

| Group 2      | 440404 or 440405                        |

| Group 3      | 667296 or 667297                        |

| Group 4      | 895054 or 895055                        |

| Group 5      | Offset Pattern: 1, 2, 433, 434, 435     |

| Group 6      | Offset Pattern: 427, 428, 433, 860, 861 |

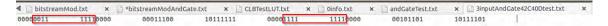

After collating the comparison files for each pin and noticing that the indices of change were the same, the indices changing for each pin were printed and then sorted numerically. The pins were then organized into 6 groups based on the indices responsible for their changes. Any pins that shared the same indices were grouped together as well as pins that shared a pattern in the offset of their indices. The grouping is shown in Table 1. Group 1 consisted of all pins with changes in indices 476 or 477. Group 2 consisted of all pins with changes in indices 440404 or 440405. Group 3 consisted of all pins with changes in indices 667296 or 667297. Group 4 consisted of all pins with changes in indices 895054 or 895055. Group 5 consisted of all pins not in one of the previous groups with an offset pattern of 1, 2, 433, 434, 435. Pin V5 is an example with its indices shown in Figure 17. Its second index of change 887693 is 1 greater than its first index of change 887692. Additionally, its third index of change is 2 greater than the first, its fourth index is 433 greater than the first index, etc. Finally, Group 6 consisted of all pins not in one of the first four

groups with an offset pattern of 427, 428, 433, 860, 861.

| USinput.txt | ×  |    |    |    |

|-------------|----|----|----|----|

|             |    |    |    |    |

| 887692      | a0 | a1 | a1 | a0 |

| 887693      | 95 | 15 | 15 | 95 |

| 887694      | 71 | 74 | 74 | 71 |

| 888125      | 10 | 11 | 10 | 11 |

| 888126      | 68 | e8 | 68 | e8 |

| 888127      | a7 | a2 | a7 | a2 |

Figure 17. Indices related to changes of the pullmode for pin V5.

Group 5 and Group 6 may seem as if the criteria for the pins was arbitrarily picked. However, these pins did not lend themselves to an easy partitioning in the same way that Groups 1 through 4 did. These pins behaved differently than Groups 1 through 4 in that there were always 6 indices of change and the values at those indices did not change when different logic designs and placements were used. Figure 18 and Figure 19 show these differences. Pins A2, K1, R17, and AA4 are from Groups 1, 2, 3, and 4 respectively. Pins V5 and AB20 are from Groups 5 and 6 respectively. Pins in the first four groups always have 3 or 4 indices of change, share common indices with other pins in the group, and the values at those indices sometimes change depending on the design logic or placement. Pins in Groups 5 and 6 always had 6 indices of change and the values of those indices did not change with different design logic or placements. Since there wasn't an apparent strategy to partition the pins not in the first four groups, the offsets of the indices of each of the pins was calculated. Two clear patterns emerged. The remaining pins either had an offset of 1, 2, 433, 434, 435 or 427, 428, 433, 860, 861. These two offsets were then used to separate the pins into Groups 5 and 6. The pins were then analyzed as groups to find the relationship between the pullmode options and the representation in the bitstream.

| *A2input,txt  | ×         |           |          |            | *K1input.txt  | ×         |            |         |         |

|---------------|-----------|-----------|----------|------------|---------------|-----------|------------|---------|---------|

| 2 Input And   | Gate Loca | ation: R  | 3C70B    |            | 2 Input And ( | ate Loca  | ation: R3C | 70B     |         |

| 429           | 00        | 06        | 02       | 04         | 440395        | 40        | 43         | 41      | 42      |

| 476           | 8c        | e1        | 28       | 45         | 440404        | 3a        | 30         | bc      | b6      |

| 477           | e8        | 80        | 33       | 5b         | 440405        | 92        | 32         | f1      | 51      |

| MIL-STD-1553  | Encoder   |           | n: Decid | ed by Tool | MIL-STD-1553  |           |            | Decided | by Tool |

| 429           | 00        | 06        | 02       | 04         | 440395        | 40        | 43         | 41      | 42      |

| 476           | 43        | 2e        | e7       | 8a         | 440404        | 1e        | 14         | 98      | 92      |

| 477           | 3e        | 56        | e5       | 8d         | 440405        | 70        | do         | 13      | b3      |

| 1 Input Not   | Gate Loca | ation: R  | 2C73D    |            | 1 Input Not ( | iate Loca | ation: R2C | 73D     |         |

| 429           | 00        | 06        | 02       | 04         | 440395        | 40        | 43         | 41      | 42      |

| 476           | f3        | 9e        | 57       | 3a         | 440404        | 3a        | 30         | bc      | b6      |

| 477           | dc        | b4        | 07       | 6f         | 440405        | 92        | 32         | f1      | 51      |

| 1 Input Not   | Gate Loca | ation: R  | 23C53A   |            | 1 Input Not ( | ate Loca  | ation: R23 | C53A    |         |

| 429           | 00        | 06        | 02       | 04         | 440395        | 40        | 43         | 41      | 42      |

| 476           | f3        | 9e        | 57       | 3a         | 440404        | 3a        | 30         | bc      | b6      |

| 477           | dc        | b4        | 07       | 6f         | 440405        | 92        | 32         | f1      | 51      |

| *R17input.tx  | t ×       |           |          |            | *AA4input.tx  | t ×       |            |         |         |

| 2 Input And 0 | Gate Loca | tion: R3  | 3C70B    |            | 2 Input And ( | Gate Loc  | ation: R3C | 70B     |         |

| 666881        | 00        | 30        | 20       | 10         | 895029        | 01        | 61         | 21      | 41      |

| 667296        | 41        | a0        | 7f       | 9e         | 895054        | bc        | с3         | 16      | 69      |

| 667297        | c5        | 42        | 3c       | bb         | 895055        | 37        | de         | 93      | 7a      |

| MIL-STD-1553  | Encoder   | Location  | : Decide | ed by Tool | MIL-STD-1553  | Encoder   | Location:  | Decided | by Tool |

| 666881        | 00        | 30        | 20       | 10         | 895029        | 01        | 61         | 21      | 41      |

| 667296        | 41        | a0        | 7f       | 9e         | 895054        | 03        | 7c         | a9      | d6      |

| 667297        | c5        | 42        | 3c       | bb         | 895055        | 1d        | f4         | Ь9      | 50      |

| 1 Input Not 0 | Gate Loca | tion: R2  | 2C73D    |            | 1 Input Not   | Gate Loc  | ation: R2C | 73D     |         |

| 666881        | 00        | 30        | 20       | 10         | 895029        | 01        | 61         | 21      | 41      |

| 667296        | 41        | a0        | 7f       | 9e         | 895054        | bc        | с3         | 16      | 69      |

| 667297        | c5        | 42        | 3с       | bb         | 895055        | 37        | de         | 93      | 7a      |

| 1 Input Not ( | Gate Loca | ition: R2 | 23C53A   |            | 1 Input Not   | Gate Loc  | ation: R23 | C53A    |         |

| 666881        | 00        | 30        | 20       | 10         | 895029        | 01        |            | 21      | 41      |

| 667296        | 41        | a0        | 7f       | 9e         | 895054        | bc        | с3         | 16      | 69      |

| 667297        | c5        | 42        | 3c       | bb         | 895055        | 37        | de         | 93      | 7a      |

Figure 18. Pins Groups 1 through 4 showing the differences in changing indices.

| _   | *V5input.txt |           |            |         |         | *AB20input.t | XC X     |            |         |         |

|-----|--------------|-----------|------------|---------|---------|--------------|----------|------------|---------|---------|

|     |              |           | ation: R3C | 70B     |         | 2 Input And  | Gate Loc | ation: R3C | 70B     |         |

| 8   | 87692        | a0        | a1         | a1      | a0      | 887266       | f0       | f8         | f8      | f0      |

| 8   | 87693        | 95        | 15         | 15      | 95      | 887693       | 95       | 5b         | 5b      | 95      |

| 8   | 87694        | 71        | 74         | 74      | 71      | 887694       | 71       | 14         | 14      | 71      |

| 8   | 88125        | 10        | 11         | 10      | 11      | 887699       | fo       | f8         | f0      | f8      |

| 8   | 88126        | 68        | e8         | 68      | e8      | 888126       | 68       | a6         | 68      | a6      |

| 8   | 88127        | a7        | a2         | a7      | a2      | 888127       | a7       | c2         | a7      | c2      |

| MIL | -STD-1553    | Encoder   | Location:  | Decided | by Tool | MIL-STD-1553 | Encoder  | Location:  | Decided | by Tool |

| 8   | 87692        | a0        | a1         | a1      | a0      | 887266       | f0       | f8         | f8      | f0      |

| 8   | 87693        | 3f        | bf         | bf      | 3f      | 887693       | a6       | 68         | 68      | a6      |

| 8   | 87694        | d2        | d7         | d7      | d2      | 887694       | 42       | 27         | 27      | 42      |

| 8   | 88125        | 10        | 11         | 10      | 11      | 887699       | fo       | f8         | f0      | f8      |

| 8   | 88126        | 22        | a2         | 22      | a2      | 888126       | 7a       | b4         | 7a      | b4      |

| 8   | 88127        | 0a        | 0f         | 0a      | 0f      | 888127       | 6f       | 0a         | 6f      | 0a      |

| 1 I | nput Not     | Gate Loca | ation: R2C | 73D     |         | 1 Input Not  | Gate Loc | ation: R2C | 73D     |         |

| 8   | 87692        | a0        | a1         | a1      | a0      | 887266       | fo       | f8         | f8      | f0      |

| 8   | 87693        | 95        | 15         | 15      | 95      | 887693       | 95       | 5b         | 5b      | 95      |

| 8   | 87694        | 71        | 74         | 74      | 71      | 887694       | 71       | 14         | 14      | 71      |

| 8   | 88125        | 10        | 11         | 10      | 11      | 887699       | fo       | f8         | f0      | f8      |

| 8   | 88126        | 68        | e8         | 68      | e8      | 888126       | 68       | a6         | 68      | a6      |

| 8   | 88127        | a7        | a2         | a7      | a2      | 888127       | a7       | c2         | a7      | c2      |

| 1 I | nput Not     | Gate Loca | ation: R23 | C53A    |         | 1 Input Not  | Gate Loc | ation: R23 | C53A    |         |

| 8   | 87692        | a0        | a1         | a1      | a0      | 887266       | f0       | f8         | f8      | fo      |

| 8   | 87693        | 95        | 15         | 15      | 95      | 887693       | 95       | 5b         | 5b      | 95      |

| 8   | 87694        | 71        | 74         | 74      | 71      | 887694       | 71       | 14         | 14      | 71      |

| 8   | 88125        | 10        | 11         | 10      | 11      | 887699       | f0       | f8         | f0      | f8      |

| 8   | 88126        | 68        | e8         | 68      | e8      | 888126       | 68       | a6         | 68      | a6      |

| 8   | 88127        | a7        | a2         | a7      | a2      | 888127       | a7       | c2         | a7      | c2      |

Figure 19. Pins from Groups 5 and 6 showing the differences in changing indices.

#### Slew Rate and Drive.

Slew rate and drive were two other configuration options that were reverse engineered for the IOBs. The slew rate is the maximum voltage change per unit time in a node of a circuit. Each bidirectional or output pin can have a slew rate of either fast or slow. Input pins are always set to a slew rate of fast. Fast corresponds to high-speed performance while slow corresponds to low-noise performance. The drive attribute is applicable to all output and bidirectional pins and specifies the strength of the output signal in milliamps (mAs). Table 2 shows the different drive strengths available at each supply voltage. Additionally, not all drive levels are available for each Input/Output type. The I/O type used for all of the bitstreams was LVCMOS25 which did not allow a drive strength of 2 mA.

Initially, the slew rate and drive configuration options were approached with the same methodology that was used for pullmode. Generate bitstreams with all possible values of the single configuration option for each pin and then analyze. However, after generating bitstreams for both of these options independently it became clear that these options could affect each other. For example, after generating and analyzing the differences between fast and slow slew rate for all pins with a drive level of 12 mA, the same pins were analyzed at a drive level of 8 mA. It was impossible to discern the slew rate of the 8 mA pins using the information from the 12 mA drive level pins. Because of this, bitstreams were synthesized for each drive level for each slew rate and then analyzed together. After the bitstreams were generated they were compared against each other for each pin and then their binary was printed at those locations in order to visually recognize patterns between the bitstreams.

Once again the pins were analyzed in groups that corresponded to the groups they were split into during the pullmode analysis.

Table 2. Valid Drive Strengths

| Drive Strength | VCCIO | VCCIO | VCCIO | VCCIO | VCCIO |