#### Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

6-16-2011

## Combinational Circuit Obfuscation through Power Signature Manipulation

Hyunchul Ko

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the <u>Programming Languages and Compilers Commons</u>, and the <u>Software Engineering</u> <u>Commons</u>

#### **Recommended** Citation

Ko, Hyunchul, "Combinational Circuit Obfuscation through Power Signature Manipulation" (2011). *Theses and Dissertations*. 1402. https://scholar.afit.edu/etd/1402

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

### COMBINATIONAL CIRCUIT OBFUSCATION THROUGH POWER SIGNATURE MANIPULATION

#### THESIS

Hyunchul, Ko, Captain, ROKA

AFIT/GCS/ENG/11-05

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

### Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, the Department of Defense or the United States Government. This material is declared a work of the U.S. Government and is not subject to copyright protection in the United States.

# COMBINATIONAL CIRCUIT OBFUSCATION THROUGH POWER SIGNATURE MANIPULATION

#### THESIS

Presented to the Faculty Department of Electrical and Computer Engineering Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command In Partial Fulfillment of the Requirements for the Degree of Master of Science

> Hyunchul, Ko, B.S.C.S Captain, ROKA

#### JUNE 2011

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

AFIT/GCS/ENG/11-05

# COMBINATIONAL CIRCUIT OBFUSCATION THROUGH POWER SIGNATURE MANIPULATION

Hyunchul, Ko, B.S.C.S Captain, ROKA

Approved:

/signed/

Yong C. Kim, Ph.D., Chairman

/signed/

Michael R. Grimaila, Ph.D., CISM, CISSP, Member

/signed/

Major Jeffrey M. Hemmes, Ph.D., Member

1 June, 2011

date

1 June, 2011

date

1 June, 2011

date

#### Abstract

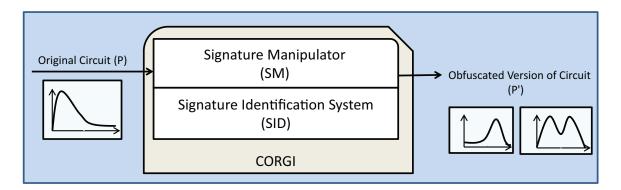

Reverse engineering is a current threat to both the military and the commercial sector of system. One method for protecting the system against the threat of reverse engineering is obfuscation. The obfuscation could transform an internal logic of system into an equivalent one that is harder to reverse-engineer. In a recent research, Yasinsac and McDonald proposed the Random Program Model (RPM) which consists of randomly selecting sub-circuits from original circuits and replacing these sub-circuits with randomly selected, semantically equivalent new one for a circuit obfuscation and implemented such obfuscation techniques in Java, which is referred to Circuit Obfuscation via Randomization of Graphs Iteratively (CORGI) [6].

The previous obfuscation methods in CORGI are mainly focusing on hiding the structural and functional information on a circuit against white-box analysis. In other words, the final variants from the previous version of CORGI are likely to leak the significant information through the side-channel such as time, power consumption, and electro-magnetic emission. For this reason, this research primarily focuses on hiding the side-channel information rather than the internal structure of circuit. This is the first known work that focuses on generalized side-channel signature characterization and provides the tool to minimize the signature leakage.

In this effort, the proposed research is conducted in four steps, namely the circuit signature estimation, characterization, signature manipulation, and signature validation. During the signature estimation and characterization phase, the power signature of the circuit is estimated both statically and dynamically via probabilistic signature estimation, then verified with dynamic simulation with HSPICE. Once the signature is estimated by both static and dynamic techniques, the signature of the circuit is characterized and classified as one of the four predefined power signature. After characterization phase, a power signature manipulation method is applied to

alter its original power signature to a different class of power signature. Finally, the altered power signature is verified via both static and dynamic signature analysis. In addition, the proposed signature manipulation method is applied on RSA circuit on Xilinx Virtex5 FPGA against adversarial power analysis. Ultimately, this research expects that the new signature manipulation method in this research can give more burdens to adversarial to compromise critical systems.

#### Acknowledgements

First and foremost, I owe a large debt of gratitude to my wife for her encouragement and support over the last 20 months. I especially want to thank her for enduring the life away from our home country. You have been a magnificent part of my life and my academic achievements. I could not have done any of this without you.

I also owe a large debt of gratitude to my thesis advisor, Dr. Yong C. Kim, for his patience, availability and enthusiasm. I have become interested in topics and made decisions that I would never have. To the remainder of my committee, Maj. Jeffrey M. Hemmes and Dr. Michael R. Grimaila, thank you for your suggestions and advice. Lastly, I would like to express my appreciation to members of Program Encryption Group and VLSI Group who have shared many difficulties for this research. Especially, Daniel Koranek who helped me to overcome obstacles and get back on track more times than I can count. Thank You.

Hyunchul, Ko

## Table of Contents

|                                 |                                             |                                                                                                                 | Page                                                                                                                          |

|---------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Abstract                        |                                             |                                                                                                                 | iv                                                                                                                            |

| Acknowledgemer                  | nts                                         |                                                                                                                 | vi                                                                                                                            |

| List of Figures                 |                                             |                                                                                                                 | Х                                                                                                                             |

| List of Tables .                |                                             |                                                                                                                 | XV                                                                                                                            |

| List of Abbrevia                | tions                                       |                                                                                                                 | xvi                                                                                                                           |

| I. Introdu<br>1.1<br>1.2<br>1.3 | Motiva<br>Probler                           | tion                                                                                                            | $     \begin{array}{c}       1 \\       1 \\       3 \\       3 \\       3 \\       4 \\       4 \\       4     \end{array} $ |

| 1.4                             | -                                           |                                                                                                                 | 4<br>4                                                                                                                        |

| II. Literatu<br>2.1<br>2.2      | 2.1.1<br>2.1.2<br>Circuit<br>2.2.1          | Engineering          Black-Box Analysis          White-Box Analysis          Obfuscation          CORGI         | 6<br>6<br>7<br>8<br>8                                                                                                         |

| 2.3                             | 2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>Side Cl | Random Sub-Circuit Selection and ReplacementComponent IdentificationComponent FusionComponent EncryptionAttacks | 9<br>10<br>10<br>11<br>11                                                                                                     |

| 2.3<br>2.4                      |                                             | Analysis                                                                                                        | 11                                                                                                                            |

|                                 | 2.4.1                                       | Power Dissipation Model                                                                                         | 13                                                                                                                            |

|                                 | 2.4.2                                       | Simple Power Analysis (SPA)                                                                                     | 16                                                                                                                            |

|                                 | 2.4.3                                       | Differential Power Analysis (DPA)                                                                               | 16                                                                                                                            |

| III. | Method  | ology .  |                                                  | 17 |

|------|---------|----------|--------------------------------------------------|----|

|      | 3.1     | Problem  | n Definition                                     | 17 |

|      | 3.2     | Estima   | tion and Simulation                              | 18 |

|      |         | 3.2.1    | Static Approach                                  | 19 |

|      |         | 3.2.2    | Signature Identification System                  | 25 |

|      |         | 3.2.3    | Constraints on Static Approach                   | 25 |

|      |         | 3.2.4    | Dynamic Approach                                 | 26 |

|      |         | 3.2.5    | Improving Dynamic Simulation Process using CORGI | 31 |

|      |         | 3.2.6    | Constraints on Dynamic Approach                  | 32 |

|      | 3.3     | Charac   | terization and Classification                    | 32 |

|      | 3.4     | Implem   | entation and Manipulation                        | 34 |

|      |         | 3.4.1    | Signature Manipulator (SM)                       | 34 |

|      |         | 3.4.2    | Power Signature Obfuscation Methods in SM        | 35 |

|      | 3.5     | Evaluat  | tion and Validation                              | 40 |

|      | 3.6     | Summa    | ry                                               | 44 |

| IV.  | Analysi | s and Re | sults                                            | 45 |

|      | 4.1     |          | ses                                              | 45 |

|      |         | 4.1.1    | c264: 4-bit multiplier                           | 45 |

|      |         | 4.1.2    | 34-bit Ripple Carry Adder (RCA)                  | 46 |

|      | 4.2     | Estima   | tion and Simulation Results                      | 46 |

|      |         | 4.2.1    | c264: 4-bit multiplier                           | 47 |

|      |         | 4.2.2    | 34-bit Ripple Carry Adder(RCA)                   | 51 |

|      | 4.3     | Charac   | terization and Classification Results            | 54 |

|      |         | 4.3.1    | c264: 4-bit multiplier                           | 54 |

|      |         | 4.3.2    | 34-bit Ripple Carry Adder (RCA)                  | 57 |

|      | 4.4     | Implem   | entation Results                                 | 57 |

|      |         | 4.4.1    | c264: 4-bit multiplier                           | 58 |

|      |         | 4.4.2    | 34-bit Ripple Carry Adder (RCA)                  | 58 |

|      | 4.5     | Evaluat  | tion and Validation Results                      | 58 |

|      |         | 4.5.1    | Accuracy of Signature Detection                  | 58 |

|      |         | 4.5.2    | Availability of Signature Manipulation           | 62 |

|      |         | 4.5.3    | Verification of the Final Circuit Variant        | 67 |

|      | 4.6     | Summa    | ry                                               | 73 |

## Page

| V. Conclus     | $ ions \dots \dots$ | 75  |

|----------------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1            | Conclusions                                                                                                               | 75  |

|                | 5.1.1 Provided power signature detection and charac-<br>terization                                                        | 75  |

|                | 5.1.2 Provided power signature manipulation method                                                                        | 75  |

|                | 5.1.3 Provided visually randomized power signature against side-channel analysis                                          | 76  |

| 5.2            | Contributions                                                                                                             | 76  |

| 5.3            | Future Work                                                                                                               | 76  |

| Bibliography . |                                                                                                                           | 78  |

| Appendix A.    | Power Signature Estimation Results 1                                                                                      |     |

| A.1            | Power Signature for c264 Circuit Variant per Algorithm<br>produced by SID                                                 | 80  |

| Appendix B.    | Power Signature Estimation Results 2                                                                                      | 85  |

| B.1            | Power Signature for c264 Circuit Variant per Algorithm<br>produced by SPICE Simulation                                    | 85  |

| B.2            | Power Signature for c5355 and c499 Circuit Variant per<br>Algorithm produced by SPICE Simulation                          | 85  |

| Appendix C.    | Power Signature Estimation Results 2                                                                                      | 98  |

| C.1            | Power Signature for 34-bit RCA Circuit Variant per Algorithm produced by SPICE Simulation                                 | 98  |

| Vita           |                                                                                                                           | 110 |

## List of Figures

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

| 2.1.   | The Concept of Reverse/Forward Engineering $[2]$                    | 7    |

| 2.2.   | Black-Box Analysis [12]                                             | 7    |

| 2.3.   | White-Box Analysis [12]                                             | 8    |

| 2.4.   | Revision History and Proposed Features in CORGI                     | 9    |

| 2.5.   | Component Encryption [13]                                           | 11   |

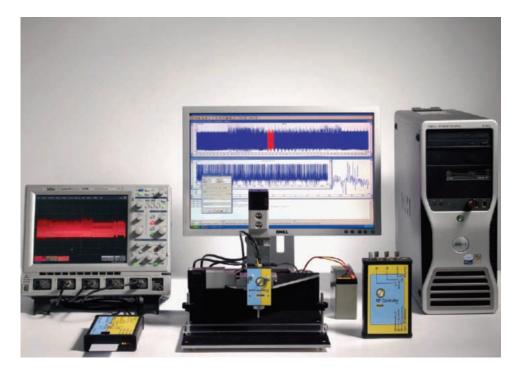

| 2.6.   | The integrated equipments for power analysis                        | 13   |

| 3.1.   | Desirable Manipulation                                              | 20   |

| 3.2.   | Custom Circuit c(3-2-8)                                             | 23   |

| 3.3.   | Truth Table with Switching Activity for $c(3-2-8)$                  | 23   |

| 3.4.   | Custom Circuit c(3-2-8) with Switching Activity $\ldots \ldots$     | 24   |

| 3.5.   | Comparison for Switching Activity by Level                          | 24   |

| 3.6.   | The Predictable Power Signature For c(3-2-8) $\ldots$               | 25   |

| 3.7.   | The System Overview of SID                                          | 26   |

| 3.8.   | SPICE Netlist expression of c17                                     | 28   |

| 3.9.   | Netlist Expression                                                  | 29   |

| 3.10.  | The Waveform of Transient Analysis In SPICE                         | 30   |

| 3.11.  | Six Power Signatures of c264                                        | 31   |

| 3.12.  | The Summary of Procedure for SPICE Simulation                       | 33   |

| 3.13.  | Implementing SPICE-Netlist Exporter in CORGI                        | 33   |

| 3.14.  | Four Types of General Power Signature                               | 35   |

| 3.15.  | Four Types of Power Signature according to a structure of a circuit | 36   |

| 3.16.  | A sample circuit signature generated by SID                         | 37   |

| 3.17.  | A sample circuit signature generated by SPICE                       | 38   |

| 3.18.  | The System Overview of SAM                                          | 39   |

| 3.19.  | Impact Measurement                                                  | 42   |

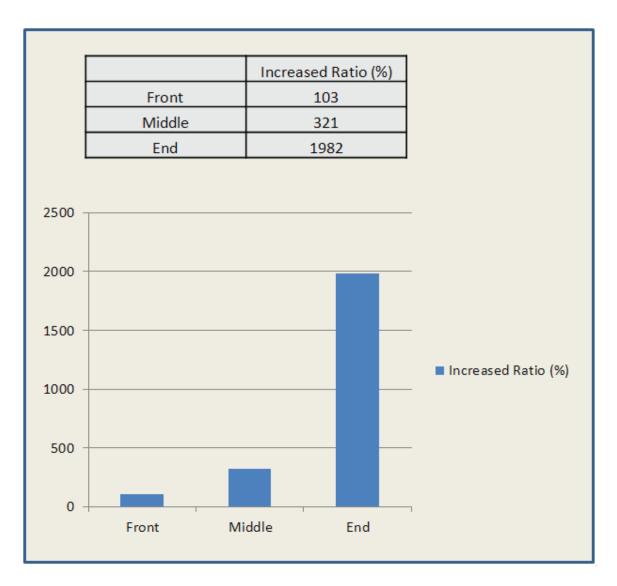

| 3.20. | Increased power ratio by the divided time interval $\ldots$ .                                               | 43 |

|-------|-------------------------------------------------------------------------------------------------------------|----|

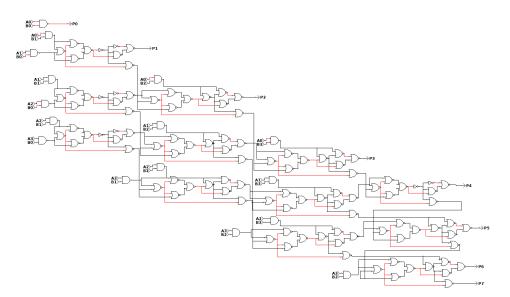

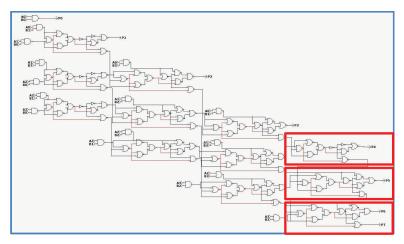

| 4.1.  | 4-bit multiplier represented in gate form                                                                   | 45 |

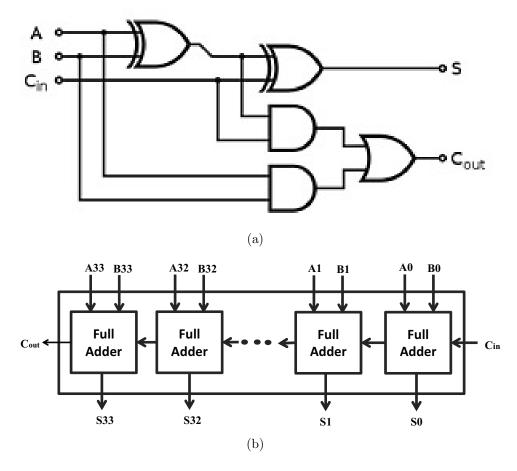

| 4.2.  | Ripple Carry Adder                                                                                          | 46 |

| 4.3.  | c<br>264 Power Signature Estimation in Static Approach<br>                                                  | 48 |

| 4.4.  | Power signature of c264 under Pseudo-Random Input $\ . \ . \ .$                                             | 49 |

| 4.5.  | Binary multiplication of two positive 4-bit integer values                                                  | 49 |

| 4.6.  | Six Different Power Signatures by User-defined Input Sequence                                               | 50 |

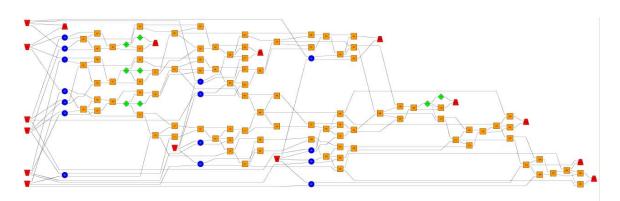

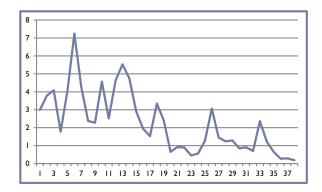

| 4.7.  | 34-bit RCA Power Signature Estimation in Static Approach                                                    | 52 |

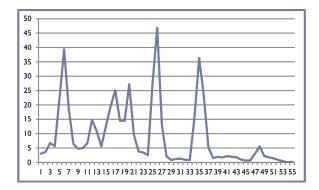

| 4.8.  | Power Signatures of 34-bit RCA by Pseudo-Random Input Pat-<br>terns                                         | 53 |

| 4.9.  | Power Signatures of 34-bit RCA by User-defined Input Patterns                                               | 55 |

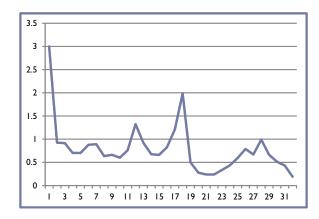

| 4.10. | Power signature of 4-bit multiplier generated by SID $\ldots$ .                                             | 56 |

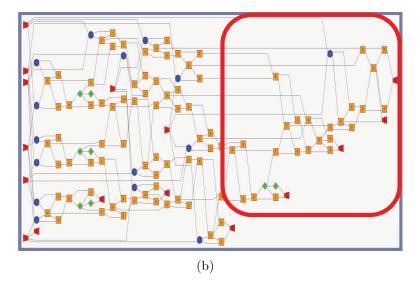

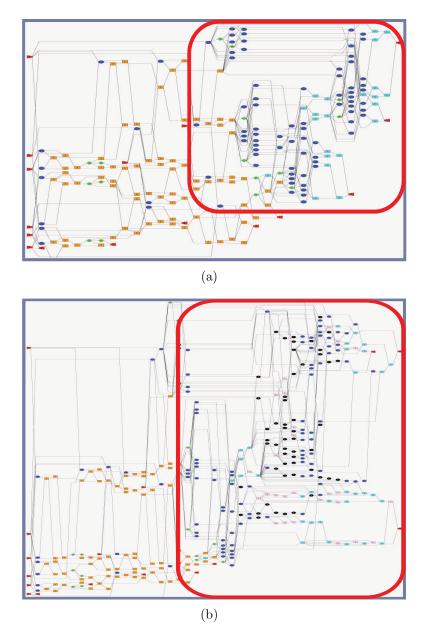

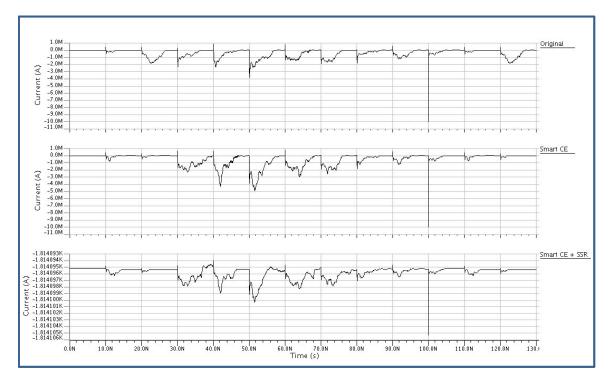

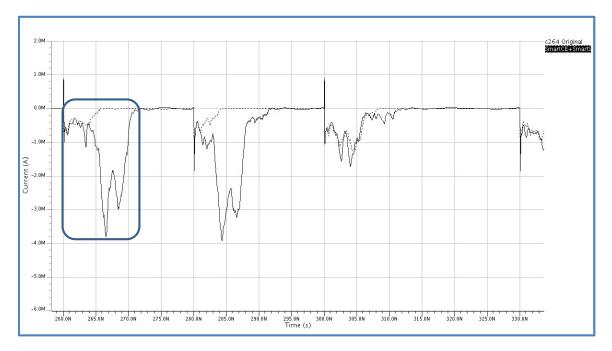

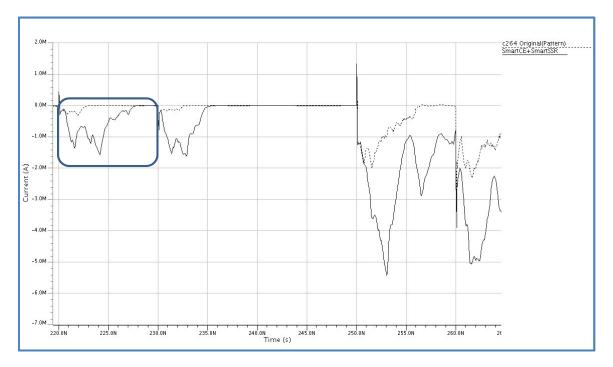

| 4.11. | Smart Component Encryption and Smart SSR for c264 $\ldots$ .                                                | 59 |

| 4.12. | Smart Component Encryption and Smart SSR for c264 $\ldots$ .                                                | 60 |

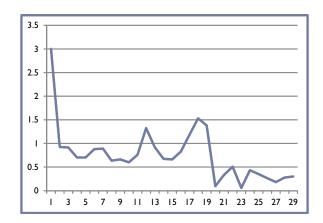

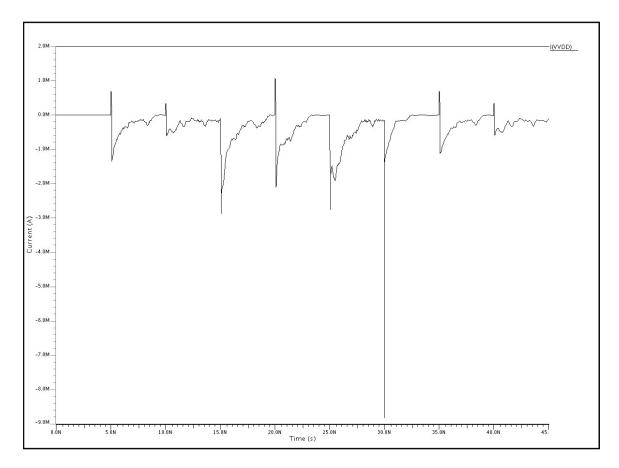

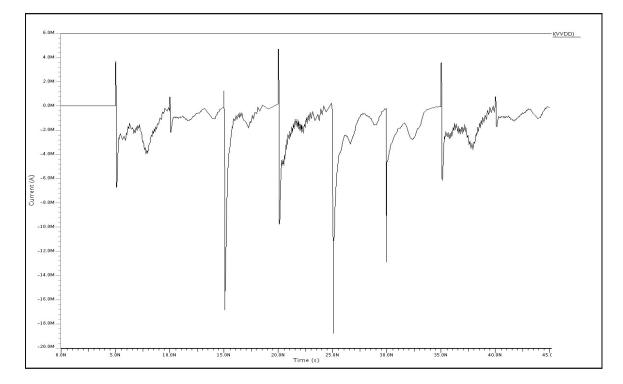

| 4.13. | Smart SSR for 34-bit RCA                                                                                    | 61 |

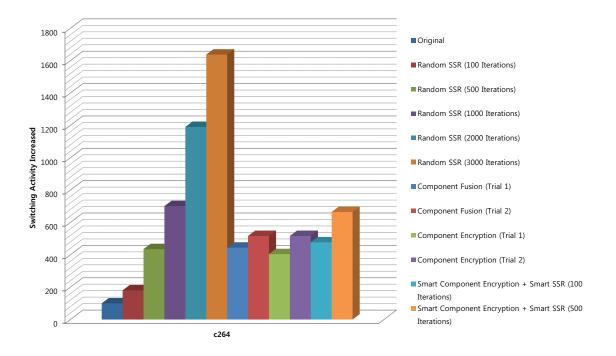

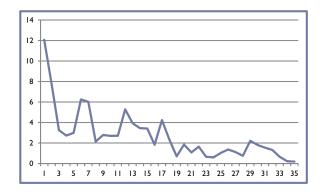

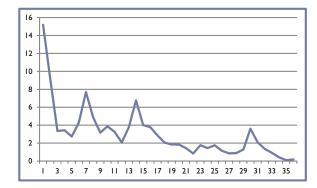

| 4.14. | Total Switching Activity Increased                                                                          | 64 |

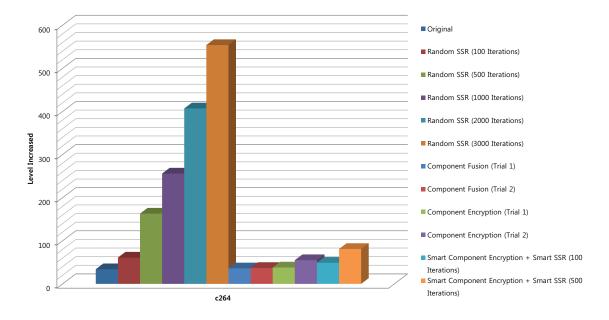

| 4.15. | Level Count                                                                                                 | 65 |

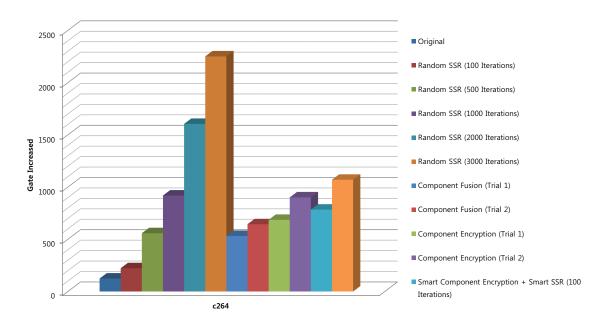

| 4.16. | Gate Count                                                                                                  | 65 |

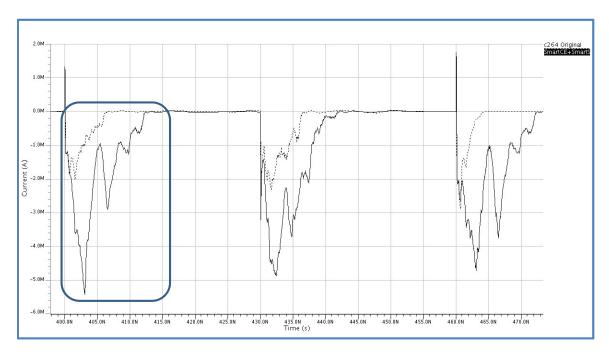

| 4.17. | Comparison Between Original c264 and Obfuscated version of c264 by Smart Component Encryption and Smart SSR | 68 |

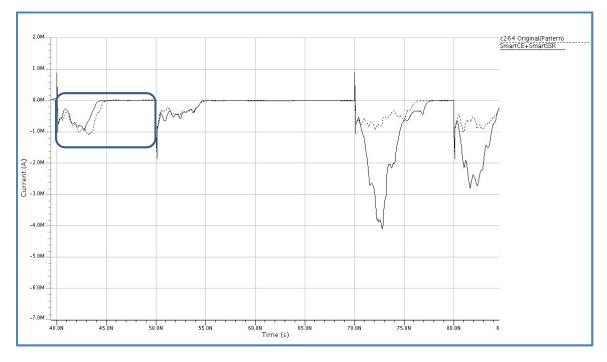

| 4.18. | Evaluation of c264 generated by Smart Component Encryption<br>and Smart SSR                                 | 69 |

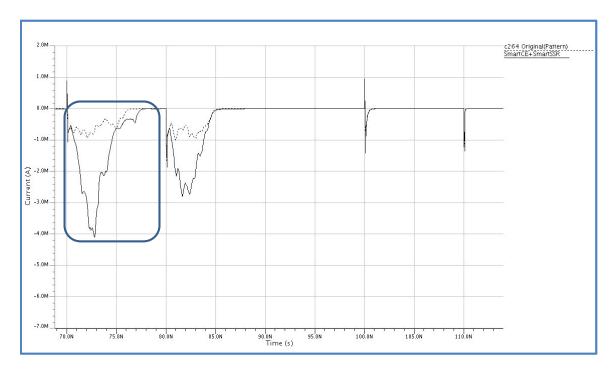

| 4.19. | Evaluation of $c264$                                                                                        | 70 |

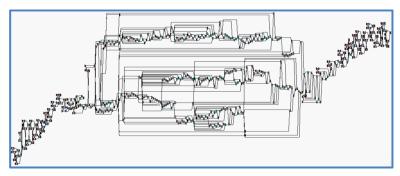

| 4.20. | Conducting side-channel analysis using FPGA based Encryption<br>System designed by Falkinburg               | 71 |

| 4.21. | Randomizing Power Signature                                                                                 | 73 |

| 4.22. | randomized signature from SM                                                                                | 73 |

| A.1.  | Power Signature of Obfuscated c264 Circuit Variant after apply-                                             |    |

|       | ing Random SSR with 100 iterations                                                                          | 80 |

| T  | •   |          |   |   |        |

|----|-----|----------|---|---|--------|

| ы  | ъ.  | $\alpha$ | 1 | r | $\sim$ |

| Т. | 11  | 21       | л |   | C      |

| _  | - ( | <u> </u> |   | - | ~      |

| A.2.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Random SSR with 500 iterations                                                                            | 80       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| A.3.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Random SSR with 1000 iterations                                                                           | 81       |

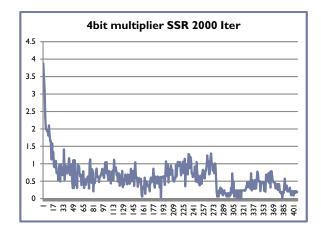

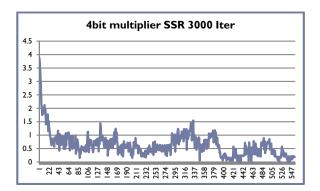

| A.4.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Random SSR with 2000 iterations                                                                           | 81       |

| A.5.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Random SSR with 3000 iterations                                                                           | 81       |

| A.6.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Component Fusion Try 1                                                                                    | 82       |

| A.7.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Component Fusion Try 2                                                                                    | 82       |

| A.8.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Component Encryption Try 1                                                                                | 82       |

| A.9.  | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Component Encryption Try 2                                                                                | 83       |

| A.10. | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Smart Component Encryption selecting Rear Level Compo-<br>nents Try 1                                     | 83       |

| A.11. | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Smart Component Encryption selecting Rear Level Compo-<br>nents Try 2                                     | 83       |

| A.12. | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Smart Component Encryption and Smart SSR selecting rear<br>level components and gates with 100 iterations | 84       |

| A.13. | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Smart Component Encryption and Smart SSR selecting rear<br>level components and gates with 500 iterations | 84       |

| A.14. | Power Signature of Obfuscated c264 Circuit Variant after apply-<br>ing Smart Component Encryption and Smart SSR selecting rear                                                   |          |

| B.1.  | level components and gates with 1000 iterations                                                                                                                                  | 84<br>85 |

| B.2.  | Power Signature for c264 By User-defined $Input(case1)$                          | 86  |

|-------|----------------------------------------------------------------------------------|-----|

| B.3.  | Power Signature for c264 By User-defined Input(case2)                            | 87  |

| B.4.  | Power Signature for c264 By User-defined Input(case3)                            | 87  |

| B.5.  | Power Signature for c264 By User-defined Input(case4)                            | 88  |

| B.6.  | Power Signature for c264 By User-defined Input(case5)                            | 88  |

| B.7.  | Power Signature for c264 By User-defined Input(case6)                            | 89  |

| B.8.  | Comparing Power Signature with Random SSR                                        | 90  |

| B.9.  | Comparing Power Signature with Component Fusion                                  | 91  |

| B.10. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR         | 92  |

| B.11. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case1) | 92  |

| B.12. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case2) | 93  |

| B.13. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case3) | 93  |

| B.14. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case4) | 94  |

| B.15. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case5) | 94  |

| B.16. | Comparing Power Signature with Smart Component Encryption<br>+ Smart SSR (Case6) | 95  |

| B.17. | Power Signature for c5355 By Random Sequence                                     | 96  |

| B.18. | Power Signature for c499 By Random Sequence                                      | 97  |

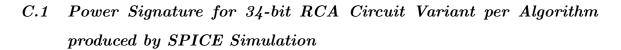

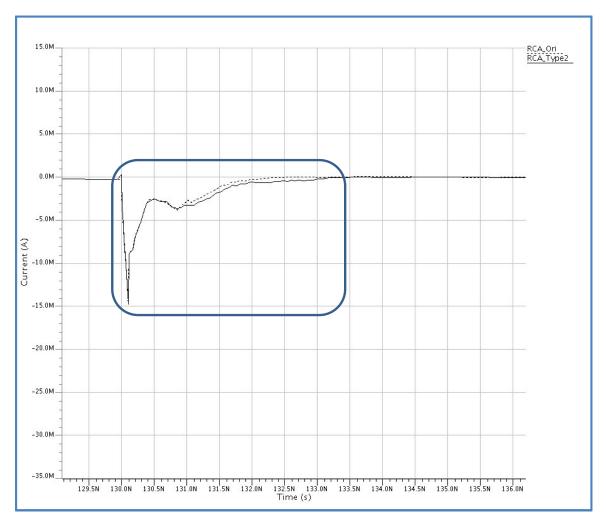

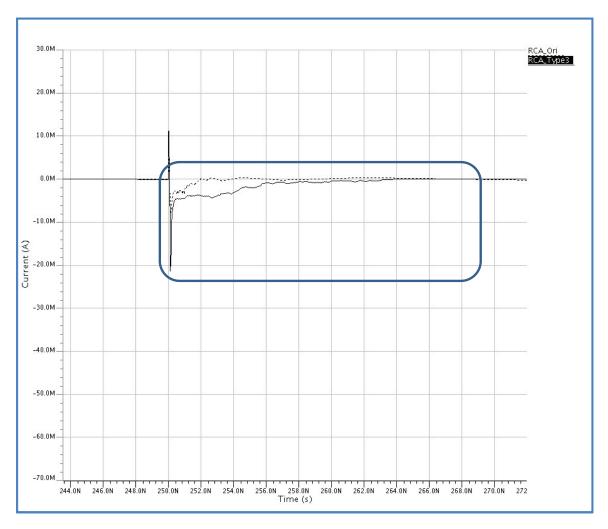

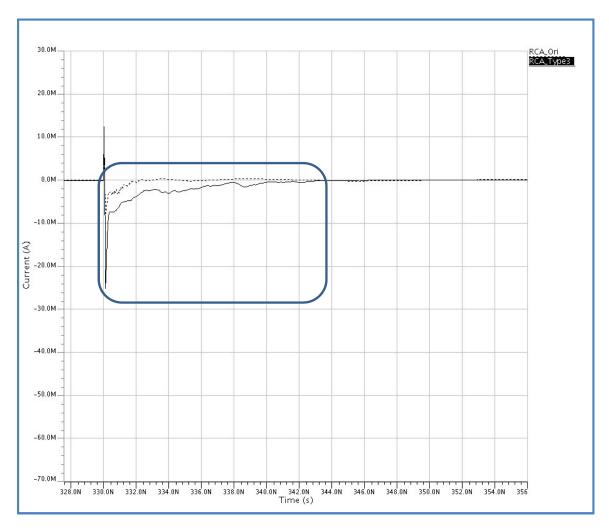

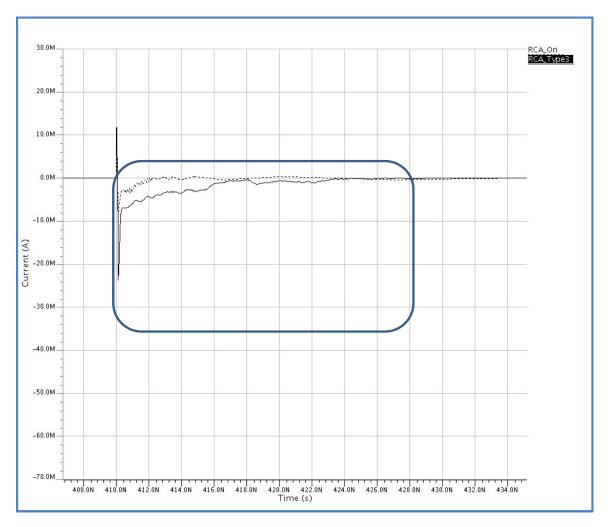

| C.1.  | Comparing Power Signature with Smart SSR (Case1)                                 | 98  |

| C.2.  | Comparing Power Signature with Smart SSR (Case2)                                 | 99  |

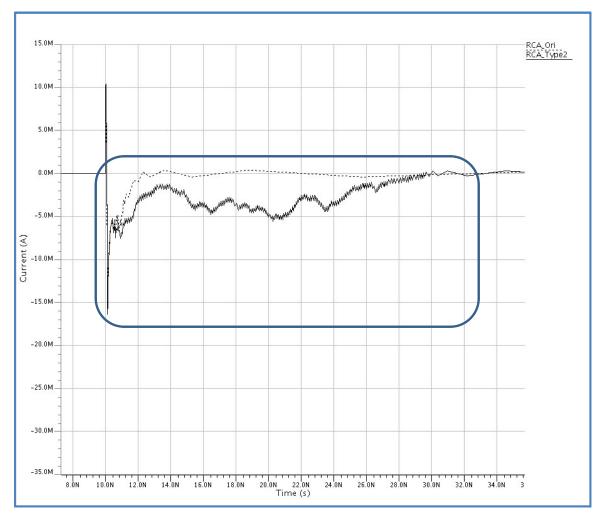

| C.3.  | Comparing Power Signature with Smart SSR (Case3)                                 | 100 |

| C.4.  | Comparing Power Signature with Smart SSR (Case4)                                 | 101 |

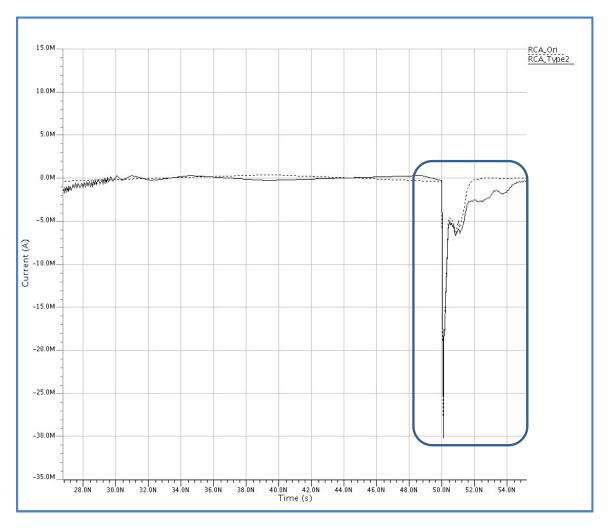

| C.5.  | Comparing Power Signature with Smart SSR (Case5)                                 | 102 |

| C.6.  | Comparing Power Signature with Smart SSR (Case6) $\ldots$ . | 103 |

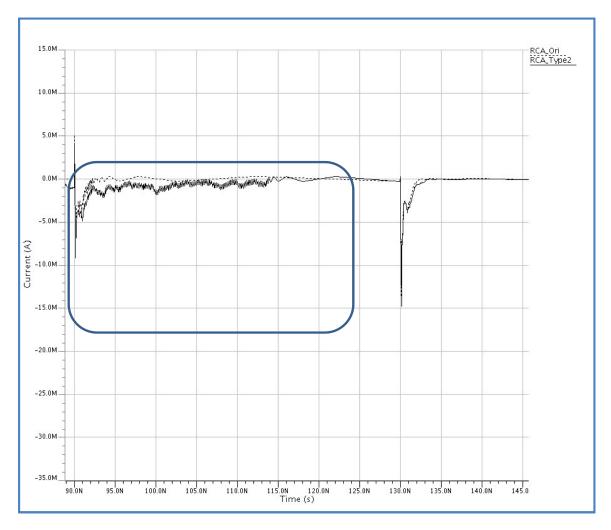

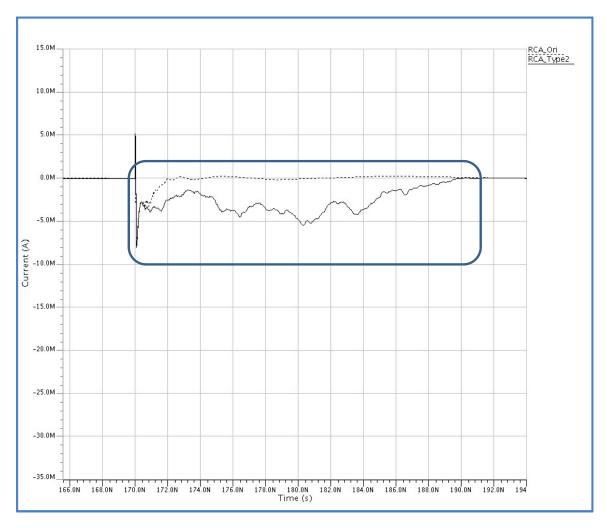

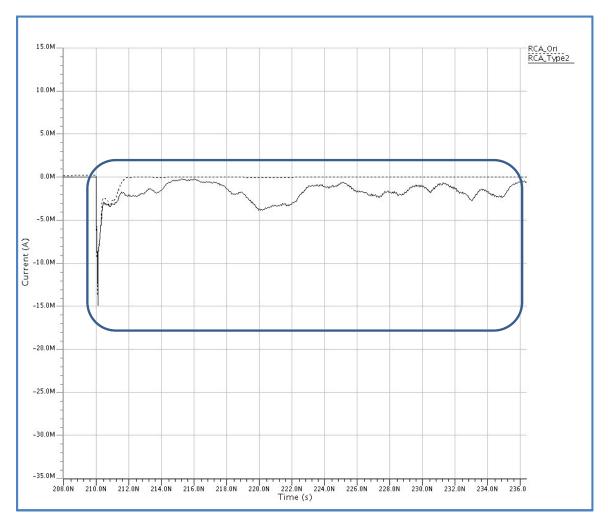

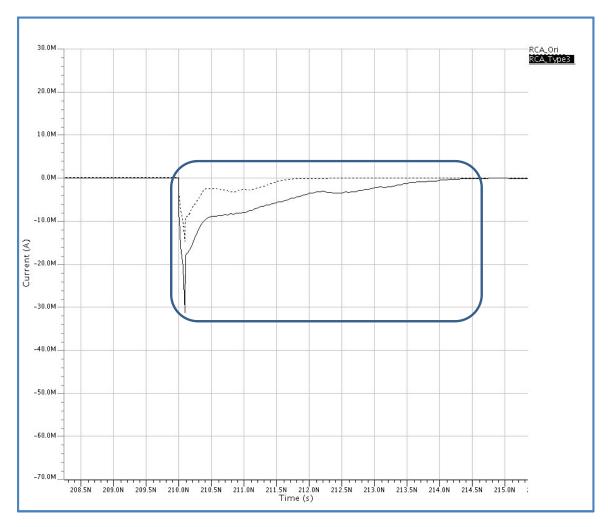

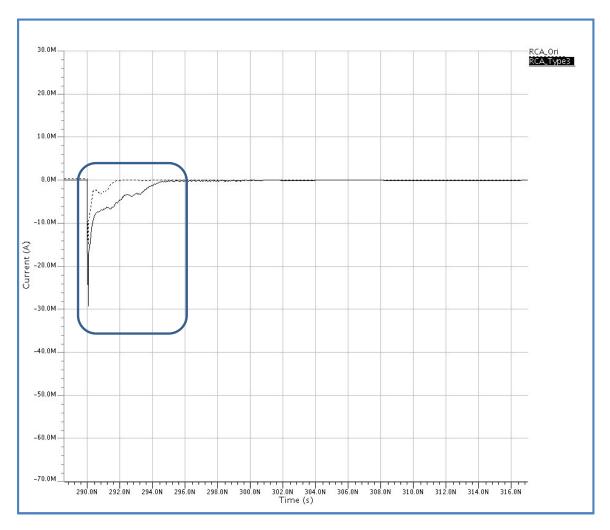

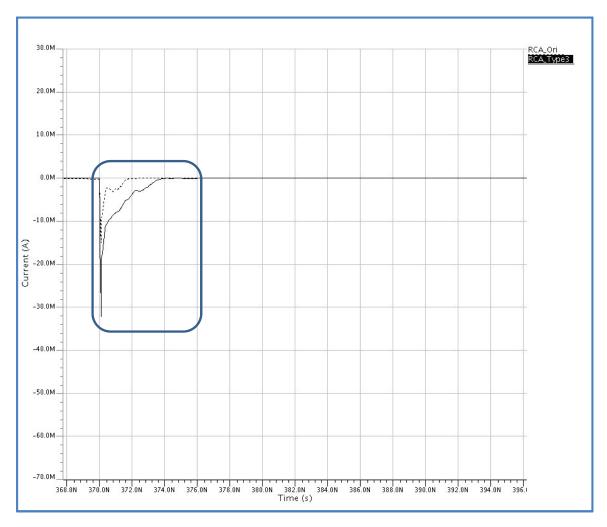

|-------|-------------------------------------------------------------|-----|

| C.7.  | Comparing Power Signature with Smart SSR (Case1) $\ldots$   | 104 |

| C.8.  | Comparing Power Signature with Smart SSR (Case2) $\ldots$ . | 105 |

| C.9.  | Comparing Power Signature with Smart SSR (Case3) $\ldots$ . | 106 |

| C.10. | Comparing Power Signature with Smart SSR (Case4) $\ldots$ . | 107 |

| C.11. | Comparing Power Signature with Smart SSR (Case5) $\ldots$ . | 108 |

| C.12. | Comparing Power Signature with Smart SSR (Case6) $\ldots$ . | 109 |

## List of Tables

| Table |                                                                                               | Page |

|-------|-----------------------------------------------------------------------------------------------|------|

| 3.1.  | The Truth Table for Two Input NAND Gate                                                       | 21   |

| 3.2.  | Smart Selection Strategies For Smart SSR                                                      | 40   |

| 3.3.  | Smart Selection Strategies For Smart CE                                                       | 40   |

| 4.1.  | User-defined Input Sequence for c264                                                          | 51   |

| 4.2.  | User-defined Input Sequence for 34-bit RCA                                                    | 54   |

| 4.3.  | Power Signature Pattern for c264                                                              | 57   |

| 4.4.  | Power Signature Pattern for 34-bit RCA                                                        | 57   |

| 4.5.  | Metrics of c264 variants                                                                      | 63   |

| 4.6.  | Evaluation of Changing Power Signature with Rear-level Selec-<br>tion Strategy for c264       | 67   |

| 4.7.  | Evaluation of Changing Power Signature with Middle-level Selection Strategy for 34-bit RCA    | 72   |

| 4.8.  | Evaluation of Changing Power Signature with Rear-level Selec-<br>tion Strategy for 34-bit RCA | 72   |

## List of Abbreviations

| Abbreviation |                                                             | Page |

|--------------|-------------------------------------------------------------|------|

| RPM          | Random Program Model                                        | iv   |

| PEG          | Program Encryption Group                                    | 3    |

| SID          | Signature IDentification                                    | 4    |

| SM           | Signature Manipulator                                       | 4    |

| ТА           | Timing analysis Attack                                      | 12   |

| FA           | Fault injection Attack                                      | 12   |

| PA           | Power analysis Attack                                       | 12   |

| MOSFET       | Metal Oxide Semiconductor Field Effect Transistor           | 14   |

| SPA          | Simple Power Analysis                                       | 16   |

| DPA          | Differential Power Analysis                                 | 16   |

| SPICE        | Simulation Program with Integrated Circuit Emphasis $\ .$ . | 26   |

| PRBS         | Pseudo Random Bit Generator Source                          | 47   |

## COMBINATIONAL CIRCUIT OBFUSCATION THROUGH POWER SIGNATURE MANIPULATION

#### I. Introduction

In our modern world, protecting one's own intellectual property is important. Likewise, because of increases in the importance of the intellectual property contained in software and hardware, protecting properties from adversarial actions is of great interest to both military and civilian communities. Traditionally the conceptual distinction between hardware and software has been apparently divided in that the hardware is usually referred to as logic circuit designs on the physical technology but the software is referred to as a set of codes or instructions [19]. With the increasing use of hardware description languages, however, circuits are increasingly implemented in a software-like manner.

In this context, there will soon cease to be a distinction between logic circuit designs for implementation in physical hardware and logic circuit designs implemented as software. In other words, any circuit can easily be mapped to a piece of software which computes the same functions. A general software, in turn, could be translated to logic circuits. Based on this assumption, rather than viewing the two as distinguished categories, hardware protection and software protection both will be regarded as a circuit protection in our research.

#### 1.1 Motivation

Protecting a smart card is one of the good examples in the domain of this research. Such a smart card can be applied in many applications such as mobile communications, banking, and electronic signatures. Since 2008, the Dutch public transit system has used special plastic cards with an embedded smart chip that allows passengers to use all transportation throughout the entire country without having to

buy individual tickets [21]. But, those cards were successfully attacked by students and hackers. One of attackers, Karsten Nohl [15], released his approach of deducing functionality from circuit images and applying it to the internal circuitry of the transit card at the Black Hat 2008 security conference. Breaking the Mifare Classic chip using Nohl's approach makes it possible for anyone to use all transportation in Holland at no cost. As a result, the Dutch government invested about \$2 billion in their new transit system to cover its weakness from adversarial reverse-engineering attacks.

Unlike Nohl's approach in the Dutch public transit system, there is another method for revealing the secrets of smart cards. This method have been proposed that use side-channel information such as timing measurements, power consumption, electromagnetic emissions and faulty hardware [22]. Of all the sources of side-channel information, power measurements are the most difficult to control [8]. Current technological constraints result in different power consumptions when manipulating a logical one compared to manipulating a logical zero [22]. An attacker of a smartcard can monitor such power differences and obtain useful side-channel information. Kocher et al. [8] claim one can monitor the actions of a single transistor within a smartcard using such a power analysis. In [8], the authors outline a specific power analysis attack against smartcards running the encryption algorithm.

From these lessons learned, it is motivated that circuit protections are extremely significant for preventing these types of attacks on both critical software and hardware. With these motivation, our research group has considered circuit protection for embedded systems and developed several methods to prevent from reverse-engineering. This research assume that one of the known methods for protection from reverse-engineering is obfuscation which means the ability to efficiently rewrite a program so that an adversary gains no advantage beyond having observable program with input and output behavior.

#### 1.2 Problem Statement

Program Encryption Group (PEG) had developed obfuscation algorithms and techniques for achieving white-box protection by hiding functional and structural information in circuits. However, the previous white-box obfuscation technique does not check nor provide protection against Side-Channel Analysis (SCA) attacks. The circuit variants generated by CORGI might be particularly susceptible to SCA attacks which is performed by the information such as timing, power consumption, electromagnetic radiation, heat, noise, and more. With these side-channel information, an adversary can gain access to the internal of a circuit and break an encryption technique on a circuit without having the internal structural and functional information. In many cases, attacker can combine side-channel information with the observed structural or functional information of a circuit to exploit it [1]. Therefore, it is reasonable for this research to start focusing on the circuit protection against side-channel analysis.

#### 1.3 Research Objectives and Contributions

The objective of this research is to detect and characterize power signature which is the abstract form of power consumption during operation, and to manipulate such a signature to increase the level of obfuscation. To achieve the objective, this research is broken down into four different sections with an ultimate goal of manipulating the side-channel information.

- 1. Estimation and Simulation

- 2. Characterization and Classification

- 3. Implementation and Manipulation

- 4. Evaluation and Validation

1.3.1 Estimation and Simulation. The power signature estimation is performed by the two approaches, namely static and dynamic approach. The static approach is achieved in probabilistic and statistical way without dynamic factors such as input patterns. Additionally, it is implemented on CORGI, which is referred to as Signature IDentification (SID) system. Dynamic approach, on the other hand, is performed by simulation process using an external tool considering input patterns. This dynamic simulation technique provides better accuracy compared to static one since it operates at the transistor level and its output is varied depending on input patterns.

1.3.2 Characterization and Classification. The estimated circuit's signatures from the previous section need to be characterized and classified. This is in order to set a baseline and a metric for evaluating how much the signature is changed after applying manipulation process.

1.3.3 Implementation and Manipulation. To achieve the primary goal of this research, power signature manipulation technique is designed and implemented on CORGI, which is called a Signature Manipulator(SM). SM is capable of providing a suitable transformation of the power signature of the circuit by manipulating switching activity of a circuit.

1.3.4 Evaluation and Validation. In order to evaluate the final circuit variant generated by SM, dynamic and static estimation approaches are used again to measure how much the signature is manipulated from the original one. Lastly, it is needed to validate the final variant obtained by the power signature manipulation method whether it provides the protection of the secret key from adversarial power analysis. The proposed signature manipulation method is applied on RSA circuit on Xilinx Virtex5 FPGA against adversarial power analysis.

#### 1.4 Organization

The remainder of the thesis is organized as follows. Chapter II provides an overview of background information in the realms of software obfuscation and sidechannel analysis. Chapter III defines our methodology which includes a technique that measures power signature in dynamic and static ways, characterizes the signature, manipulates the circuit's signature using new manipulation algorithm, evaluates the proposed method using static and dynamic analysis, and validates the final variant using the FPGA based Encryption system test-bed. Chapter IV presents the results of experiments using power signature estimation and manipulation techniques, and Chapter V gives our conclusions along with our contributions and discussion of future work for the power signature manipulation method.

#### **II.** Literature Review

This chapter presents a background review of the literature pertaining to a circuit obfuscation technique against SCA attack. We organize this chapter in the following manner. Section 2.1 describes the concept of reverse engineering, Section 2.2 provides a brief introduction to obfuscation principles and previous circuit obfuscation techniques including the overview of *CORGI*, Section 2.3 introduces the side-channel attacks, and Section 2.4 covers the concepts of power dissipation model and the different types of power analysis.

#### 2.1 Reverse Engineering

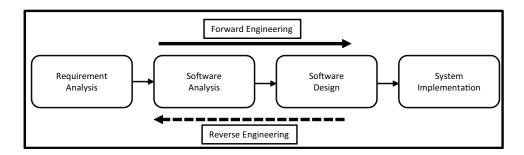

Reverse engineering is the process of analyzing a system to recognize the system's components and their interrelationships, and to create representations of the system in another form or at a higher level of abstraction [3]. There are different reasons for reverse engineering. The first one is creating the necessary documentation for maintenance, strengthen enhancement, or support replacement. A second reason is an adversarial purpose for compromising the existing technology by an industrial spy [11]. From the view of software engineering, reverse engineering is the reverse process of *forward engineering* [2]. Forward engineering consists of moving from high-level abstractions and logical, implementation-independent designs to the physical implementation of a system. In other words, it is a process of taking requirements, and creating designs and an implementation from these requirements [3]. This process is shown in Figure 2.1. Whereas forward engineering ends with a software product, reverse engineering starts with the product and is going backward of forward engineering.

2.1.1 Black-Box Analysis. The main purpose of black box analysis is to predict the intent of a system based on only its inputs and outputs without any information related to as internal structure of system. In the case of logic circuits, black-box analysis is the simplest way to reverse engineer a circuit in a brute force approach [12]. Identifying the overall function requires enumerating all possible input

Figure 2.1: The Concept of Reverse/Forward Engineering [2]

Figure 2.2: Black-Box Analysis [12]

combinations and evaluating the circuit's output. This is impractical for a circuit with a large number of inputs due to the requirement of a high computing power and large search space.

2.1.2 White-Box Analysis. Unlike black-box analysis, white-box analysis focuses on the internal structure of a system. This approach provides an adversary with a better functional understanding than black-box analysis because it can be performed without having enumerating all possible input combinations. Adversaries can directly access the underlying white-box structure of a circuit in the real world. Therefore, protecting against white-box analysis is much more challenging than blackbox protection. White-box protection has been the primary focus in the PEG research group.

Figure 2.3: White-Box Analysis [12]

#### 2.2 Circuit Obfuscation

This research assume that general programs are themselves abstractions of Boolean logic because they have collections of straight-line logic. Thus, a program logic can be represented in a software as Boolean logic circuits [6]. In this regard, there is a connection between protecting original functions of circuit and protecting a software, either directly or indirectly. For this reason, protecting circuits is the primary focus of PEG's research to make secure software. To hide programmatic logic or original functions of circuit, obfuscation is one of known protections against reverse engineering. Obfuscation is a process that produces a semantically equivalent variant of a program. Thus, the obfuscated program still has the same number of inputs and outputs and performs the same logic function but has a different white-box structure [6]. This obfuscation technique based on the white-box structure of a program attempts to confuse a reverse engineer.

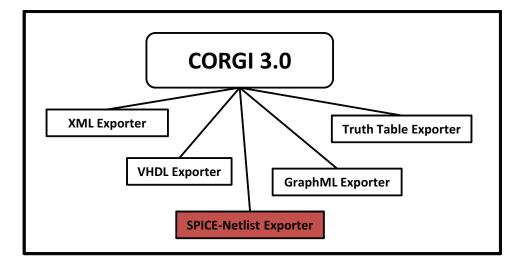

2.2.1 CORGI. To achieve the main purpose of the program encryption group, McDonald and Kim developed Java-based a circuit obfuscator known as Circuit Obfuscation via Randomization of Graphs Iteratively CORGI at the Air Force Institute of Technology (AFIT). CORGI mainly provides the feature of representation and obfuscation of a combinational circuit. As seen in Figure 2.4, The first version of CORGI, called CORGI 1.0, provides a random based obfuscation technique, namely random sub-circuit selection and replacement. Since then, algorithms

| CORGI<br>Version                       | 1.0                                 | 1.5                                         | 2.0                                                       | )                                 | 3.0                                                    |

|----------------------------------------|-------------------------------------|---------------------------------------------|-----------------------------------------------------------|-----------------------------------|--------------------------------------------------------|

| Semantic-<br>preserving<br>replacement | Subjection<br>election<br>represent | Boundary                                    | Contract<br>Contract                                      |                                   | Power Signature<br>Manipulation                        |

| Semantic-<br>changing<br>replacement   |                                     |                                             | Component<br>Encryption                                   |                                   |                                                        |

| AUTHOR                                 | Norman, James                       | Parham                                      | Koranek                                                   |                                   | Ко                                                     |

| Target                                 | Random<br>sub-circuits              | Component<br>boundaries                     | Entire circuit,<br>Entire components<br>given priority    | Entire<br>components              | Entire circuit,<br>Entire components<br>given priority |

| Protection                             | White-box Protection                |                                             |                                                           |                                   | Side-Channel Protection                                |

|                                        | Random<br>replacement               | Boundary blurring<br>strategies             | Component merging;<br>Randomized<br>sub-circuit synthesis | Component<br>boundary encryption; | Power Signature<br>Manipulating<br>strategies          |

| Limitations                            | < 5 gate selection                  | 142 gate components,<br>~2000 gate circuits | < 17 input<br>Sub-circuits                                | < 17 input<br>components          | < 17 input<br>subcircuits                              |

| Date                                   | March 2008                          | March 2010                                  | June 2010                                                 |                                   | June 2011                                              |

Figure 2.4: Revision History and Proposed Features in CORGI

and techniques for circuit obfuscation have been improved. In 2010, CORGI 2.0 was designed in a deterministic approach for obfuscation method. Additionally, CORGI 2.0 provides component-level obfuscation technique rather than a single gate-level technique against a white-box analysis attack. Now, this research, on the other hand, is toward to version 3.0 in order to achieve the signature protection against an adversarial side-channel analysis attack.

2.2.2 Random Sub-Circuit Selection and Replacement. Random SSR Method selects a sub-circuit in the entire original circuit at random and then replaces it by requesting a sub-circuit to be replaced from the circuit library(CXL). Then, CXL provides a random, semantically equivalent sub-circuits. From this action, the original sub-circuit is removed from the circuit, and the sub-circuit obtained from CXL is inserted into the original place. This is not a single step, but an iterative process.

But such a random SSR does not guarantee that the final circuit variant from the large number of iterations will be more secure.

2.2.3Component Identification. Parham [16] focused on larger set of gates than a single gate. Such a set of gates is called a component. Component consists of one or more gates which has an own function such as a multiplexer and an adder. Therefore, it is possible for an adversary to focus their attention on such a component after they failed for the reverse-engineering by knowing a gate level structure alone. For this reason, Parham designed a component identification tool based on the assumption that adversaries may use component identification techniques for determining the overall function of the system [16]. The component ID enumerates a sub-circuit and compares it with the known pre-defined components in a library. If the matched sub-circuit were found, the component was identified. This algorithm makes it possible to automatically identify the existing component without visual searching process. But, the pre-defined library modules are limited for applying possible components and circuits. For example, if there is a circuit having components which does not exist in a library, it is not possible to identify the components in the circuit.

2.2.4 Component Fusion. In order to overcome the limitation on random SSR in CORGI 1.0, Koranek developed new obfuscation method in CORGI 2.0, which is called *component fusion* [13]. Component Fusion provides a deterministic selection strategy instead of random selection. With the new obfuscation method, the obfuscator selects both components identified by Parham's component ID tool and the subcircuits connecting to the identified components for replacement. Next, component fusion synthesize all selected gates together to eliminate the border of components. This is accomplished by using the ESPRESSO two-level optimizer [13]. As a result, component fusion contributes to prevent from discovering components in a circuit.

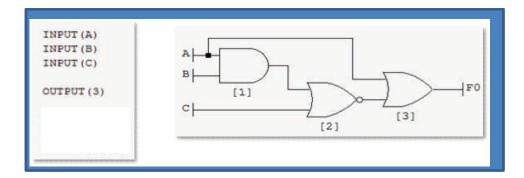

Figure 2.5: Component Encryption [13]

2.2.5 Component Encryption. Component fusion guarantees to hide the existing components in a circuit, but it might still remain the original signals in a circuit. To overcome this limitation on component fusion, Koranek [13] developed another deterministic method for obfuscating the existing signals in a circuit - Component Encryption. As seen in Figure 2.5, component encryption is implemented by selecting the signals between components, generating encryption and decryption logic on the connected components, and then synthesizing the generated logic and the each connected component. With component encryption, the number of signals and the semantics between components are successfully changed.

#### 2.3 Side-Channel Attacks

Even if the circuitry is protected from the reverse engineering attack based on white-box analysis, the circuitry might still leak significant information related to the circuit's function. An attacks on a circuit using leaked side information is called a side-channel attack. Side-channel attacks are mainly divided into the categories of Timing Analysis Attacks(TA), Fault Injection Attacks(FA), and Power Analysis Attacks(PA) [12].

- 1. **Timing Analysis**: Timing Analysis is the method which focuses on the variation of the timing in processing by modifying the speed of the circuit clock, either speeding it up or slowing it down to achieve a desired information about the circuit implementation.

- 2. Fault Injection: The purpose of fault injection is to cause the targeted digital system or circuity to be malfunction to reveal useful information for additional attacks. Fault injections include a variety of attacks:raising voltage glitches and clock glitches, modifying the temperature, and so on.

- 3. Power Consumption Analysis: By observing the power usage across a circuit, an attacker can gain insight into what signals are changing the most in the circuit. Particularly, if a circuit is being used to compute some mathematical function, more power will be used in the area of the circuit dedicated to this function.

Of course, there are other types of side channel attacks. However, the previous three techniques are the main technologies known as the side-channel attacks on digital systems. This research tries to prevent combinational circuits from power consumption analysis as well as white box analysis.

#### 2.4 Power Analysis

In general, power analysis techniques are performed by obtaining the power transient directly from physical circuitry with physical equipments as shown in Figure 2.6. However it is very costly to set up the all physical environments for power analysis. As an alternative, power analysis for CMOS digital circuits can be done at several levels of abstractions [20]. The techniques can be divided into from low-level technique to statistical and probabilistic technique by trading off between accuracy and speed.

Figure 2.6: The integrated equipments for power analysis(http://www.riscure.com)

2.4.1 Power Dissipation Model. In general, power is a secondary consideration behind speed and area for many chips. As chip density and operating frequency increases, power consumption skyrockets and becomes the primary concern in terms of high performance and life-time for CMOS design [14]. Various methods [10] to estimate power consumption have been proposed for low-power design. Even if the general purpose of power estimation is different from the purpose of this research, power analysis attacks (and more generally side-channel attacks) are also performed by using the power dissipation model. For this reason, the fundamental power consumption model will be discussed in this section. The power consumption in a digital system is given by the following expression [14]:

$$P_{total} = P_{dynamic} + P_{short} + P_{static} \tag{2.1}$$

where:  $P_{total}$ : Total power dissipation;  $P_{dynamic}$ : Dynamic circuit power dissipation;  $P_{short}$ : Short circuit power dissipation;  $P_{static}$ : Static circuit power dissipation

The three terms in the order written represent the dynamic, short, and static dissipation respectively of the circuit [14] [18]. The second term, short dissipation refers to the power consumed due to the small current from source to ground appearing at the output of a CMOS gate during switching from one logic level to another, at the moment that both output transistors drive current [7]. In more technical terms, current can only flow while both pMOS and nMOS networks are partially ON.

$$P_{short} = V_{DD} \sum_{i} I_{short} \tag{2.2}$$

Where:  $V_{DD}$ : supply voltage;  $I_{short}$ : short circuit current

The third term, static dissipation,  $P_{static}$ , does not depend on the circuit activity and is determined by the target technology, undesired short circuits and (MOSFET) leakage current. This static power dissipation is the product of total leakage current and the supply voltage.

$$P_{static} = V_{DD}I_{static} \tag{2.3}$$

Where:  $V_{DD}$ : supply voltage;  $I_{static}$ : leakage current

The most important term among the three terms is the first one, namely the dynamic dissipation, since it is consumed by charging and discharging the parasitic capacitors present in all circuit nodes. Additionally, it is known that the dynamic power usually accounts for about 70% of the power consumed in a combinational circuit [7]. Thus, the power in a digital CMOS circuit can be determined using the

following formula for dynamic power:

$$P_{dynamic} = \sum_{i} V_{DD}^2 C_{load} \alpha_{0 \to 1} f \tag{2.4}$$

$V_{DD}$  is the supply voltage at node i, and  $C_{load}$  is the load capacitance at node i.  $\alpha_{0\to 1}$  is the power consuming switching activity at node i, and f is the frequency of operation of the circuit [18].

To make more sense of the previous expression, let us begin by reviewing more definitions for deriving the average power dissipation over some time interval T.

$$P_{dynamic} = \frac{E}{T} = \frac{1}{T} \int_{o}^{T} P(t)dt = \frac{1}{T} \int_{o}^{T} i_{DD}(t) V_{DD}dt$$

(2.5)

Where:

E : energy consumed over the interval ; T : time interval; P(t): instantaneous power on time t;  $i_{DD}$  : supply current;  $V_{DD}$  : supply voltage;

Based on the previous expression, the average dynamic power can be written as:

$$P_{avg-dynamic} = \frac{1}{T} \int_{o}^{T} i_{DD}(t) V_{DD} dt = V_{DD}^2 C_{load} f_{switching}$$

(2.6)

Since most gates do not switch every clock cycle, it is often more convenient to express switching frequency  $f_{switching}$  as an activity factor  $\alpha_{0\to 1}$  times the clock frequency f. Now the average power dissipation may be rewritten as:

$$P_{dynamic} = \alpha_{0 \to 1} V_{DD}^2 C_{load} f \tag{2.7}$$

Where:

$\alpha_{0 \rightarrow 1}$  : the probability of a  $0 \rightarrow 1$  power consuming transition.

By reviewing the power dissipation model so far, it is learned that the power consumption in CMOS devices is proportional to the switching activity. Thus,  $\alpha_{0\to 1}$  is the principal parameter for the domain in an adversarial power analysis as well as general low-power circuit design.

2.4.2 Simple Power Analysis (SPA). SPA is one of the attacking method for a cryptography system. It is implemented by directly interpreting power consumption during cryptographic operations to recovering the main key or logic in a system [8]. By observing the power consumption on a smart card, SPA can directly attack the secret key information embedded in the card since the amount of power consumed varies depending on the microprocessor instruction performed. For example, SPA can be used for breaking RSA or DES implementations by revealing differences during the cryptographic operations. It is known that many current smart cards are vulnerable to SPA [9].

2.4.3 Differential Power Analysis (DPA). DPA has a much more complicated process, and is much more difficult to prevent than SPA. SPA is more likely to observe the power consumption, on the other hand, DPA uses the technique for statistical analysis and error correction to extract the exact correlated to secret keys. DPA has largely two steps: Data collection and data analysis [9]. Data collection is implemented by sampling the power consumption for a smart card during the cryptographic operations. Data analysis is performed by reducing the unnecessary signals and applying digital signal interpretation and statistical technique to conduct attacks.

#### III. Methodology

#### 3.1 Problem Definition

The fundamental goal in the program encryption group is to provide combinational circuit protections by proposing more secure and advanced methods for circuit obfuscation in order to increase the cost of reverse engineering. To meet this goal, PEG has proposed various methods for obfuscating a combinational circuit based on hiding the structural and functional information of the original circuit against a white-box analysis. The structural information normally means the information about the number and the type of gates, signals, components, and so on. However, this research focuses more on dealing with the side-channel information than on the structural information for obfuscating a combinational circuit.

As discussed in Chapter II, observing power consumption over a circuit is the most well-known method among the wide variety of side-channel attacks. The main functionality or the encryption key in a circuit could be easily detected by using the power analysis attacks. Therefore, our method in this research takes into account manipulating the power signature of the original circuit.

The process for this research is divided into four steps as follows:

#### 1. Estimation and Simulation

- Estimating power signature using an internal tool in static approach and simulating a circuit using an external tool in the dynamic approach

#### 2. Characterization and Classification

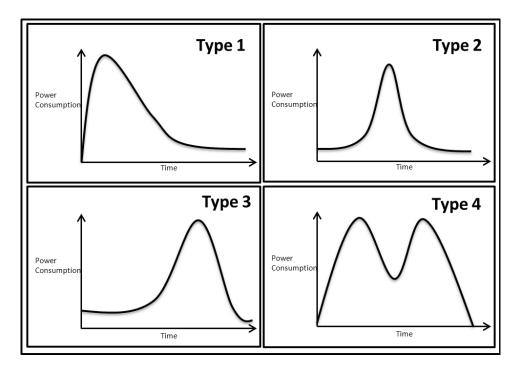

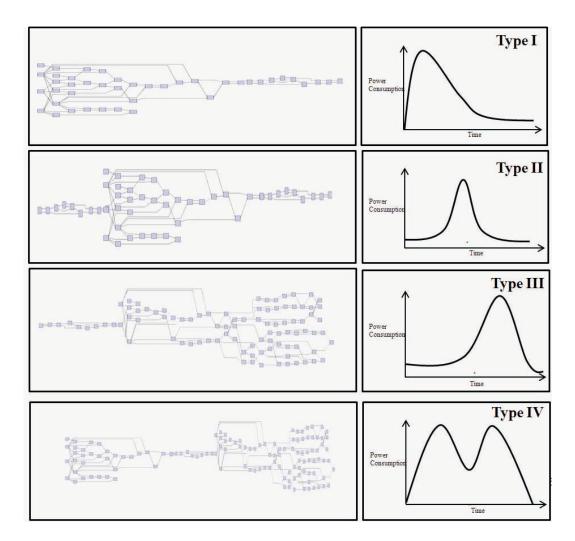

- Characterizing the original power signature and classifying it by the pre-defined four types of power signature patterns

#### 3. Implementation and Manipulation

- Implementing Signature Manipulator (SM) in CORGI and manipulating the original power signature by using SM

#### 4. Evaluation and Validation

- Evaluating the SM using static and dynamic analysis and validating the pro-

posed method applying on Xilinx Virtex5 FPGA against an adversarial power analysis.

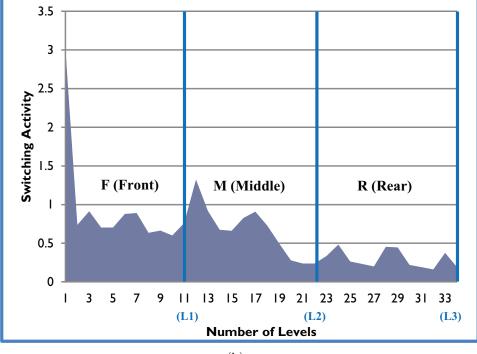

The first step is an estimation and simulation to measure power signature for combinational circuit using an internal and external tool. For power estimation, two approaches are executed in this research, namely static and dynamic technique. Static approach is performed in probabilistic and statistical way by using an internal tool, which is referred to as SID. In static approach, SID can provide the predictable power signature from the switching activity estimation technique without considering input pattern. In dynamic approach, simulation process is executed by using SPICE simulator, which is one of the well-known circuit simulators to simulate power consumption of a circuit at the transistor level under dynamic input patterns. Second, characterization and classification are performed. This process mainly focuses on characterizing the original power signature and classifying it as one of the four predefined power signature patterns. Third, implementation and manipulation processes are executed for the primary goal of this research which is to transform the class of the original power signature. Signature Manipulator (SM) is designed by manipulating the amount of switching activity. Lastly, evaluation and validation processes will be performed to quantify how much power signature is transformed by the proposed signature manipulation techniques and to verify the ability to protect an encryption key in the circuit against adversarial power analysis.

#### 3.2 Estimation and Simulation

As mentioned previous, this section discusses both static and dynamic approaches for estimating power signature in combinational circuits. The static technique is performed without the circuit's input pattern. It can provide an power signature in statistical and probabilistic way based on the assumption that the circuit's inputs are uniformly distributed. For this reason, this technique is referred as static. This simplified no simulation-based approach is implemented in CORGI, which is called SID. In dynamic technique, on the other hand, the final result can be varied depending on what type of the input patterns. Thus, this technique is called dynamic. The dynamic approach is performed by simulation process given pseudo-random or user-defined input vectors per clock cycle.

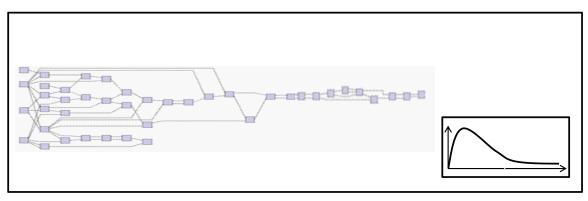

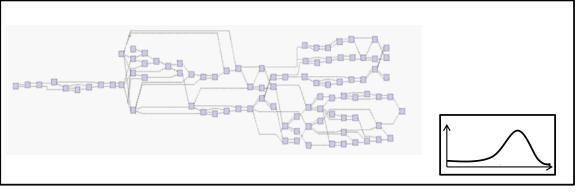

3.2.1Static Approach . These types of techniques usually attempt to estimate an average power dissipation in a probabilistic and statistical way without considering dynamic factors such as an input pattern. These no simulation-based techniques are referred to as static approach in this research. The easiest way to predict power signature in this static approach can be performed by just looking at the overall structure of circuit. For instance, Figure 3.1 provides two examples of a circuit's structure. In Figure 3.1(a), front-loaded shape of power signature can be predicted, because most gates are located in the front part of circuit. Likewise, in the Figure 3.1(b), rear-loaded shape of power signature can be expected by the overall structure of a circuit. But, it is not easy for this technique to apply every other cases. In order to achieve more accurate result, this research examines the previous works for static approach. From the previous works, it is found that most techniques in this approach focus on the dynamic circuit power dissipation among three factors of Eq.2.1, power dissipation model, as seen in Chapter II, because the dynamic circuit power dissipation usually accounts for about 70% of the power consumed in a combinational circuit [18]. Thus, most methods aimed at optimizing this term will have the highest effect on static power signature estimation and manipulation.

$$P_{dynamic} = \alpha_{0 \to 1} V_{DD}^2 C_{load} f \tag{3.1}$$

As seen in Eq.3.1, the parameters of the dynamic power expression consist of  $V_{DD}$ ,  $C_{load}$ , f, and  $\alpha_{0\to1}$  as explained in chapter II. At the logic-level, the switching activity of a circuit,  $\alpha_{0\to1}$  is the prime factor out of four terms for static power estimation and manipulation in this research. It is widely accepted that the switching activity is strongly related to power consumption in combinational logic circuits since significant power is consumed only during logic transitions. Therefore, the switching

(a)

(b)

Figure 3.1: Power Signature Example associated with Circuit's Structure

(a) The Front loaded Circuit Example

(b) The Rear Loaded Circuit Example

Table 3.1:

The Truth Table for Two Input NAND Gate

| 1 |   |   |   |  |  |  |

|---|---|---|---|--|--|--|

|   | А | В | Ο |  |  |  |

|   | 0 | 0 | 1 |  |  |  |

|   | 0 | 1 | 1 |  |  |  |

|   | 1 | 0 | 1 |  |  |  |

|   | 1 | 1 | 0 |  |  |  |

- Minterms of NAND gate =  $Z(X, Y) = \overline{XY} + \overline{X}Y + X\overline{Y} = \sum m(0, 1, 2)$

- Maxterms of NAND gate =  $\overline{Z}(X, Y) = XY = \prod M(3)$

activity will be employed to both estimate and manipulate the power signature in static approach.

In static approach, Menon et al. [17] proposed a method to estimate an switching activity at an each gate and calculate the total switching activities for a combinational circuit in their research. The switching activity definition given in [17] assumed that the switching activity for a logic gate is the average rate at which its output switches from 0 to 1 or 1 to 0. The procedure proposed in [17] is given by the following expression:

$$P_0 \times P_1 = \frac{|R|}{|R| + |F|} \times \frac{|F|}{|R| + |F|}$$

(3.2)

where:

- $P_0$ : The probability of Zero;  $P_1$ : The probability of One; |F|: The cardinality of the set of minterms of the logic function;

- |R|: The cardinality of the set of maxterms of the logic function

For example, consider a two input NAND gate whose inputs are statistically independent and uniformly distributed. It means that the four possible states for inputs A and B (00, 01, 10, 11) are equally likely. F is a set with minterms corresponding to the 1's of the function, and R is a set corresponding to the 0's of the function. Thus, |F| = 3 and |R| = 1 are given by the Table 3.1.

Then,  $P_0 = \frac{1}{4}$  and  $P_1 = \frac{3}{4}$ . Calculating by the Eq.3.2,  $P_{0\to 1} = \frac{1}{4} \times \frac{3}{4} = \frac{3}{16}$ and  $P_{1\to 0} = \frac{3}{4} \times \frac{1}{4} = \frac{3}{16}$ , where  $P_{0\to 1}$  and  $P_{1\to 0}$  are the transition probabilities of the outputs switching from  $0 \to 1$  and  $1 \to 0$  respectively. Since power is drawn from the battery source only when the output changes from 0 to 1, the discussion on switching activity in [18] accounted only the power consuming transition of  $0 \to 1$ , so the switching activity of the two input NAND gate equals to  $\frac{3}{16}$  [17]. As a result, the switching activity probability can be written as:

$$\alpha_{0\to 1} = P_0 \times P_1 = P_0 \times (1 - P_0) \tag{3.3}$$

For an another example of an inverter, on the other hand, the switching activity probability with uniformly distributed inputs is given by  $P_0 \times (1-P_0) = \frac{1}{2}(1-\frac{1}{2}) = \frac{1}{4}$ .

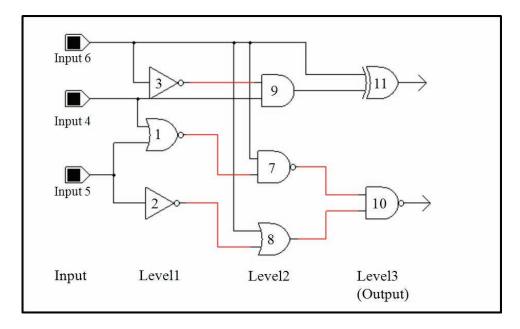

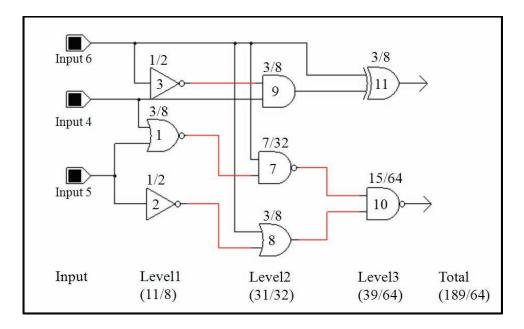

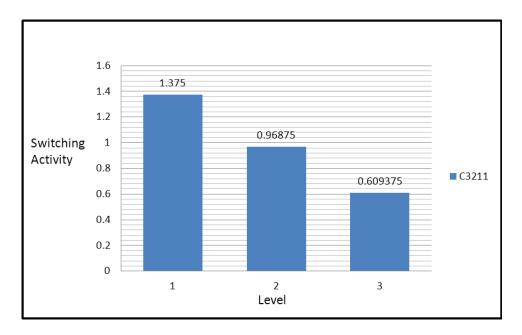

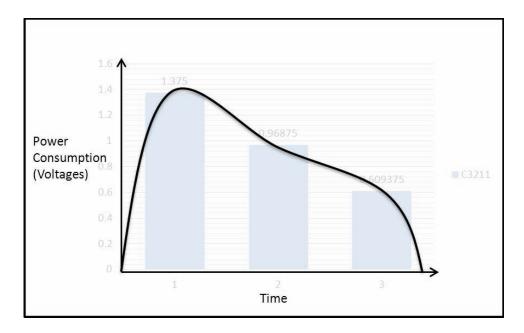

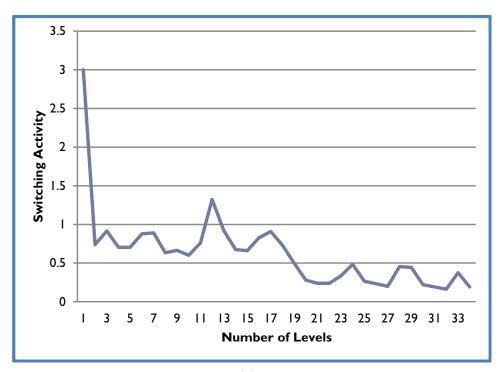

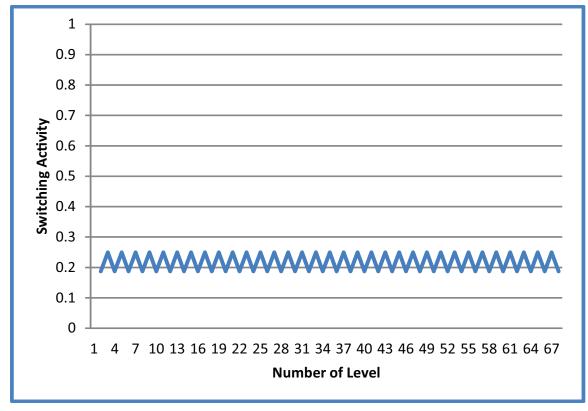

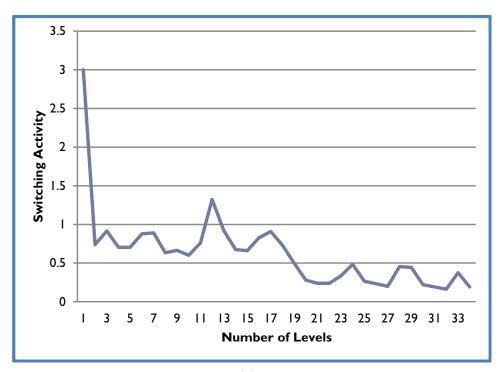

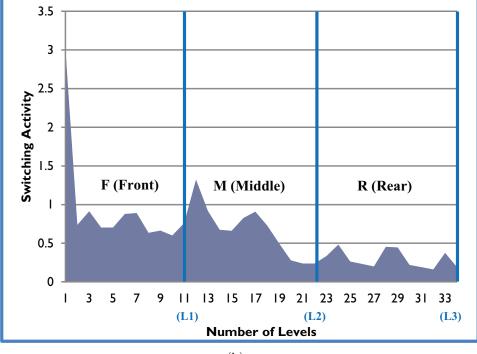

The following example illustrates using the switching activity estimation technique on a circuit with more gates. The custom circuit in Figure 3.2 consists of three inputs, two outputs, eight gates, and three levels. In order to apply the Menon's technique to this circuit, a truth table is generated for the circuit. Then, the switching activity at each gate can be also obtained as shown in Figure 3.3 and Figure 3.4. But, what this research mainly want to measure is the power signature of a circuit rather than the individual or total switching activity for a circuit. For this reason, this switching activity estimation technique needs to be improved for predicting the power signature. So, it is revised by comparing the total switching activities by the level. Figure 3.5 shows the variation of the switching activities by the level of the circuit. Finally, the switching activity variation can be predicted by converting Figure 3.5 to Figure 3.6, which is comparable to the power signature simulated by SPICE in dynamic approach. Of course, this technique is limited in terms of the accuracy compared to dynamic simulation. However, this technique is much faster and easier to use than dynamic approach. Additionally, it is accurate enough for this research to make a decision for selection strategy of power signature manipulation algorithm later. Even if some limitations exist in this fashion, it has been widely applied in the problem of optimization of total power consumption as well as the domain of power estimation.

Figure 3.2: Custom Circuit c(3-2-8)

|          | In4                   | In5   | 3      | 1        | 2      | 9        | 7         | 8       | Out 11   | Out10     |

|----------|-----------------------|-------|--------|----------|--------|----------|-----------|---------|----------|-----------|

| In6      |                       |       | NOT(6) | NOR(4,5) | NOT(5) | AND(3,4) | NAND(1,6) | OR(6,2) | XOR(9,6) | NAND(8,7) |

| 0        | 0                     | 0     | 1      | 1        | 1      | 0        | 1         | 1       | 0        | 0         |

| 0        | 0                     | 1     | 1      | 0        | 0      | 0        | 1         | 0       | 0        | 1         |

| 0        | 1                     | 0     | 1      | 0        | 1      | 1        | 1         | 1       | 1        | 0         |

| 0        | 1                     | 1     | 1      | 0        | 0      | 1        | 1         | 0       | 1        | 1         |

| 1        | 0                     | 0     | 0      | 1        | 1      | 0        | 0         | 1       | 1        | 1         |

| 1        | 0                     | 1     | 0      | 0        | 0      | 0        | 1         | 1       | 1        | 0         |

| 1        | 1                     | 0     | 0      | 0        | 1      | 0        | 1         | 1       | 1        | 0         |

| 1        | 1                     | 1     | 0      | 0        | 0      | 0        | 1         | 1       | 1        | 0         |

|          | Switching<br>Activity |       | 1/2    | 3/8      | 1/2    | 3/8      | 7/32      | 3/8     | 3/8      | 15/64     |

| (189/64) |                       | Level |        | 11/8     |        |          | 31/32     |         | 39/      | /64       |

Figure 3.3: Truth Table with Switching Activity for c(3-2-8)

Figure 3.4: Custom Circuit c(3-2-8) with Switching Activity

Figure 3.5: Comparison for Switching Activity by Level

Figure 3.6: The Predictable Power Signature For c(3-2-8)

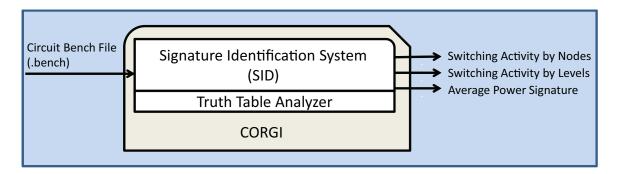

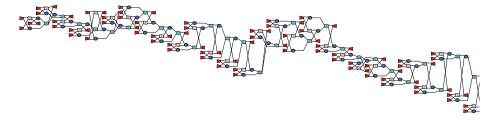

3.2.2 Signature Identification System. The SID is a tool designed for making power signature measurement an easier task based on the static approach. Although there is a tool to support the dynamic technique like SPICE simulator, an automatic tool for supporting the static approach does not exist. Thus, the automatic system is implemented using CORGI in this research. Figure 3.7 provides an overview of the SID system.

The previous implementations of CORGI do not support signature detection nor manipulation. Now, the SID is implemented based on the components of CORGI to support the statistical power estimation technique. In general, hardware description files such as VHDL, SPICE netlist are needed for the SPICE-like simulation tools; however, the SID just needs a simple circuit netlist as an input, and then the total switching activities and the predictable power signature can be automatically generated after computing the switching activity at each node and level.

3.2.3 Constraints on Static Approach. Static estimation is more simple than dynamic simulation using SPICE in terms of easy of use and speed for estimation. But the results obtained with the SID is limited on accuracy. Therefore, The results

Figure 3.7: The System Overview of SID

from the static signature predictor SID should be validated with the results obtained with the dynamic simulation tool, such as HSPICE.

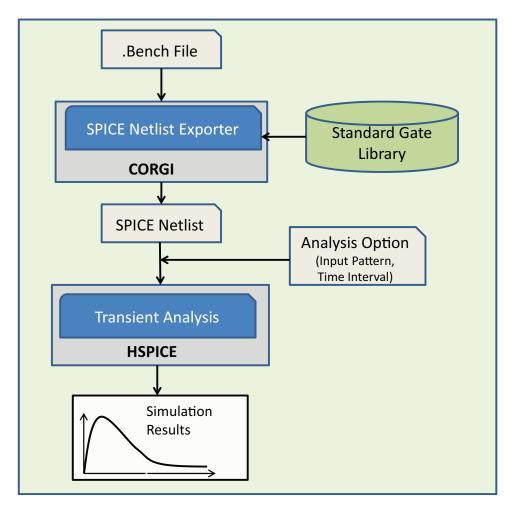

3.2.4Dynamic Approach. Most techniques in this area operate mainly at the transistor level to estimate power consumption. These techniques are sometimes referred to as "low-level technique". Additionally, the reason why it is called dynamic approach is that the output will be varied depending on dynamic vectors such as input pattern and time interval. For this reason, this approach is sometimes called a pattern-dependent technique in other researches [10]. A good example of this approach is a simulation using SPICE(Simulation Program with Integrated Circuit Emphasis), which is an electronic circuit simulator. The SPICE is one of the wellknown simulation tool which models the behavior of a circuit containing digital and analog devices. With the SPICE-like simulators, using dynamic technique can test and measure the power consumption of a circuit before touching the physical equipments. Accordingly, simulating the circuit with SPICE is the industry-standard way to verify circuit's operation at the transistor level before committing to manufacturing an integrated circuit in these days.

Originally, SPICE was developed at the Electronics Research Laboratory of the University of California, Berkeley in the early 1970s. Since then, SPICE has been widely distributed and used so far. ELDO is one of the commercial versions of SPICE simulator which will be used in this research for measuring power signature for a circuit as dynamic approach. In order to carry out this simulation, the circuit must be described in SPICE format. This format is called the SPICE netlist, which has basically a transistor level description. Before running this simulation, it is required to know an element of description for a gate with nMOS and pMOS transistors using MOSFET Model. For this SPICE simulation, the SPICE netlist needs more efforts to describe the information from scratch such as the all types of gates in a circuit, how they are connected each other, what types of input pattern will be using, and how much amount of time will be assigned for simulation. Figure 3.8(b) shows the SPICE Netlist description of c17, which is one of the ISCAS 85 benchmark circuits [5]. Additionally, Figure 3.9 describes the two input NAND gate in C17 in a SPICE netlist format and schematic representation of the NAND gate in MOSFET Model generated by open software, Netlist Viewer.

3.2.4.1 Analysis using SPICE. The type of analysis in SPICE are largely divided into three types. These types of analysis are summarized as follows [23]:

# 1. DC Analysis

:A DC-level-based analysis that provides data to predict the DC response of an output to a DC voltage at the input

#### 2. AC Analysis

:A frequency-based analysis that predicts the output amplitude or phase shift through a circuit as a function of a fixed amplitude frequency applied to the input. This input frequency is over a specified range and thus frequency is over a specified range and thus frequency versus output response date is provided

#### 3. Transient Analysis

:A time-based analysis that provides an oscilloscopic display of an output. The output display typically is a result of an input stimulus to the circuit and is in the form of time versus voltage or current.

(b)

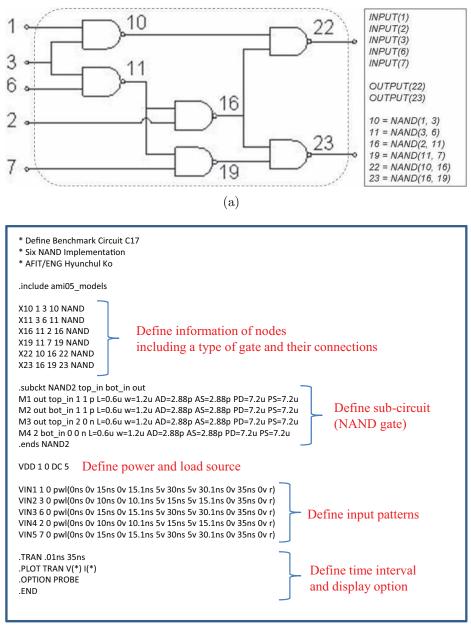

Figure 3.8:(a) c17 Benchmark Circuit(b) SPICE Netlist expression of c17

.subckt NAND2 top\_in bot\_in out M1 out top\_in 1 1 p L=0.6u w=1.2u AD=2.88p AS=2.88p PD=7.2u PS=7.2u M2 out bot\_in 1 1 p L=0.6u w=1.2u AD=2.88p AS=2.88p PD=7.2u PS=7.2u M3 out top\_in 2 0 n L=0.6u w=1.2u AD=2.88p AS=2.88p PD=7.2u PS=7.2u M4 2 bot\_in 0 0 n L=0.6u w=1.2u AD=2.88p AS=2.88p PD=7.2u PS=7.2u .ends NAND2

(a)

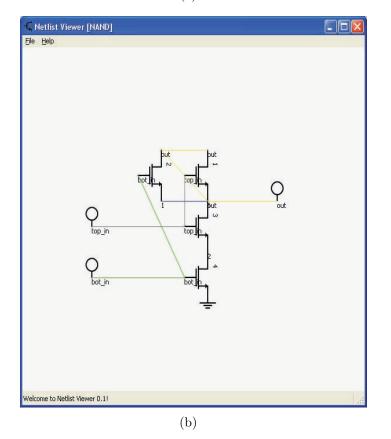

Figure 3.9:

- (a) SPICE Netlist expression of a two input NAND gate

- (b) Schematic representation of (a) generated by Netlist Viewer

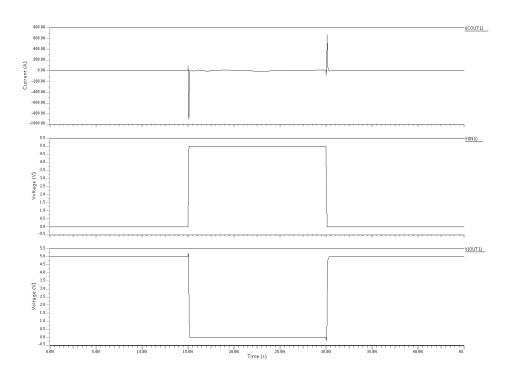

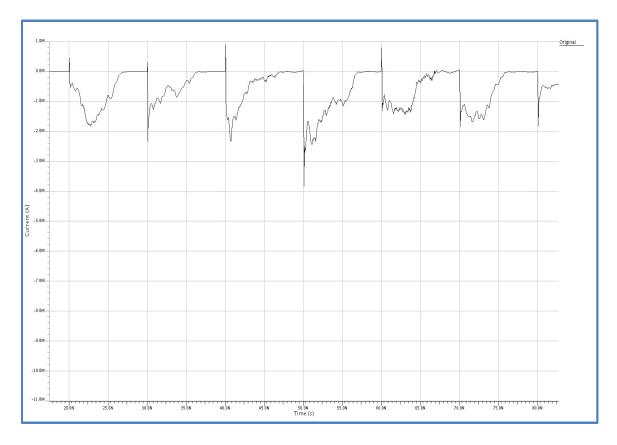

Figure 3.10: The Waveform of Transient Analysis In SPICE

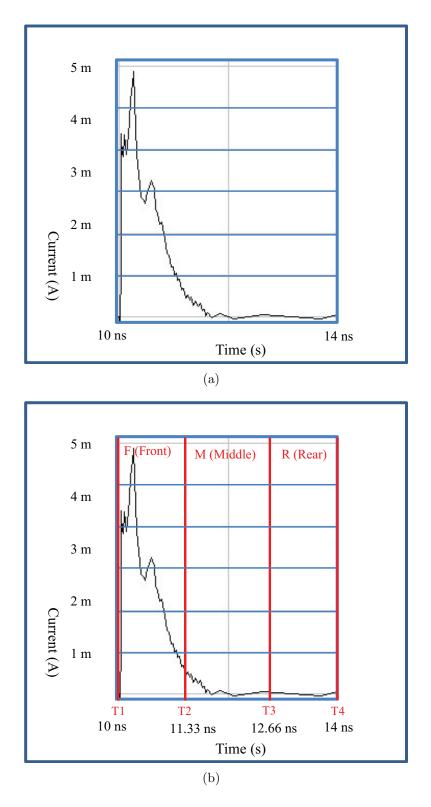

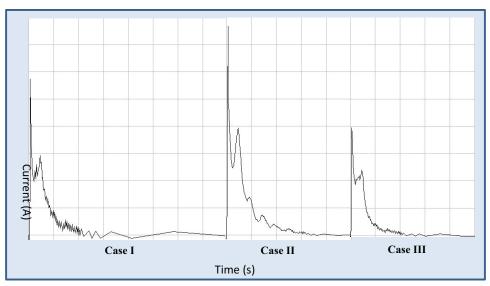

Among the three types of analysis, the transient analysis is the primary type of analysis used in this research. It allows to measure power signature of a circuit by simulating instantaneous voltages and currents consumption. It also support a various set of inputs, both random and user-defined inputs. Figure 3.10 shows the waveform of voltages and currents over a specific time interval for an inverter generated by the transient analysis.

The waveform of voltages provides the logic transitions over the time, but the current waveform shows the power signature which the power analysis is mainly looking for. Based on the power dissipation model, namely  $P = V_{DD}I$  as mentioned in Chapter II, SPICE has an option to generate the power variation calculated by the expression during the time interval. However, the overall shape of current (I) curve is virtually identical to the shape of power signature, because voltage  $(V_{DD})$  does not changed significantly during the simulation process. The current (I) is the primary variable factor in the power dissipation model. Thus, by looking at the current wave-

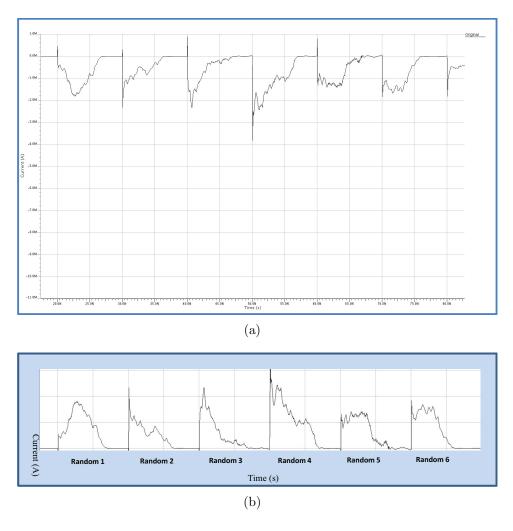

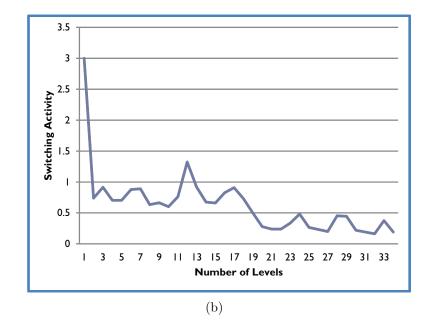

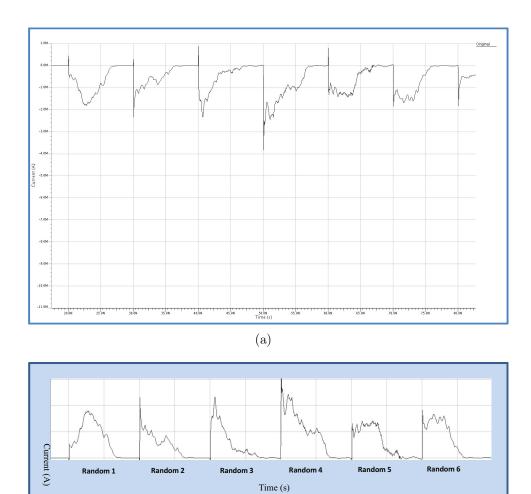

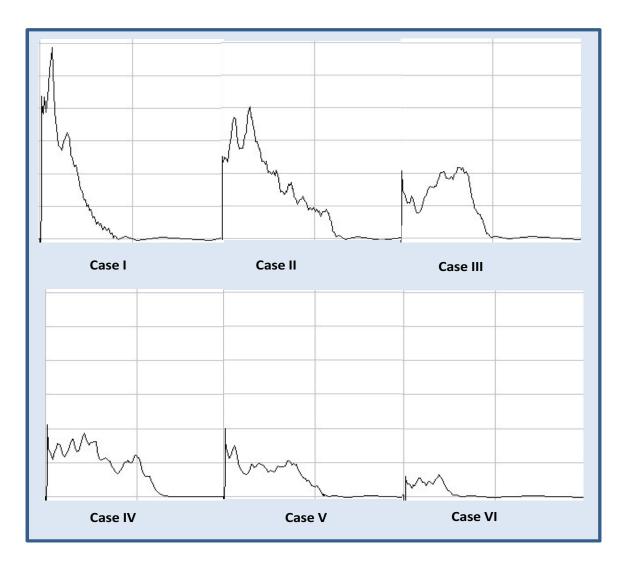

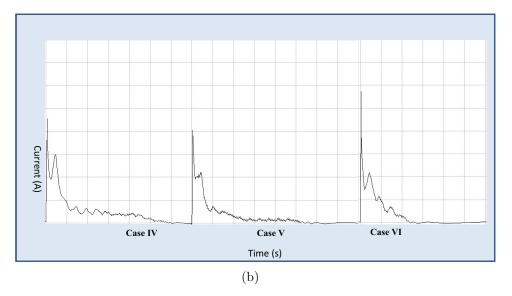

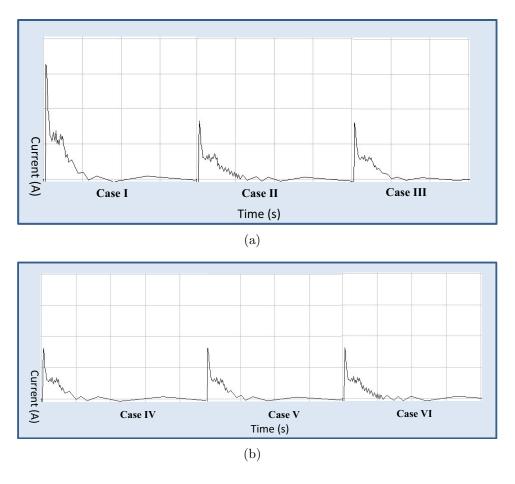

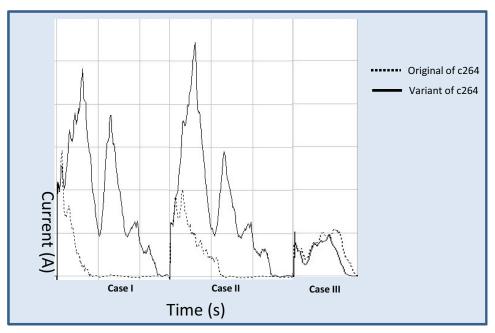

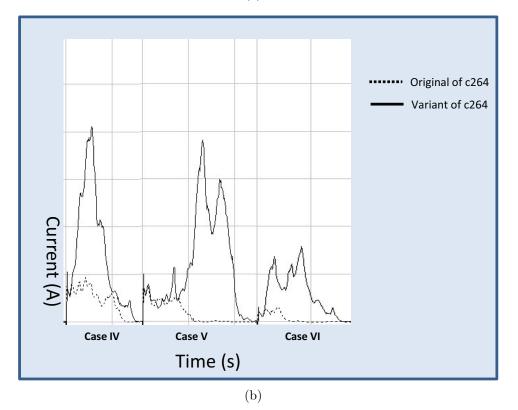

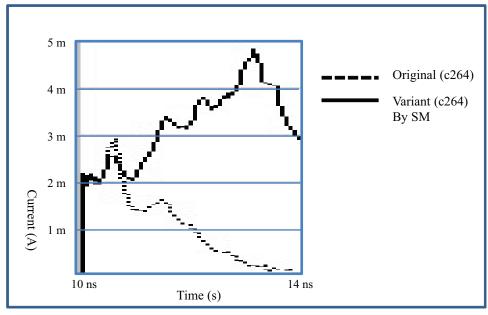

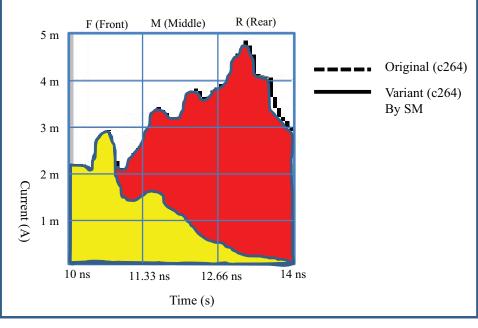

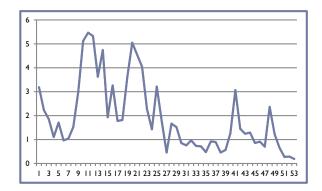

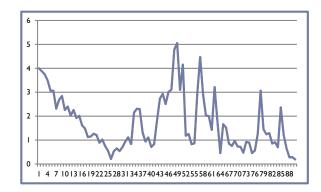

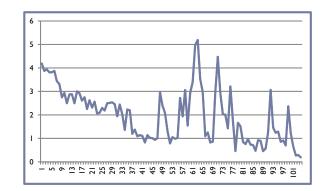

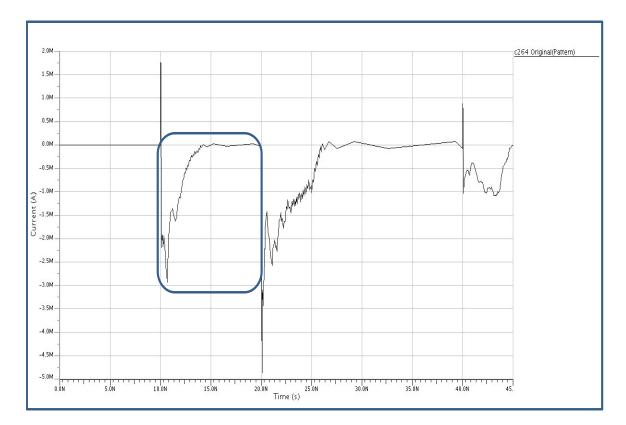

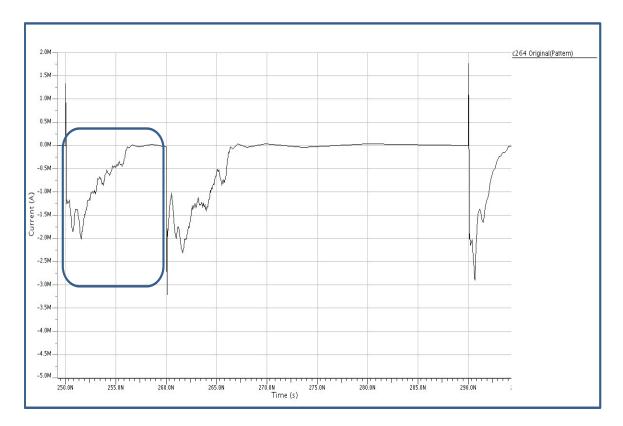

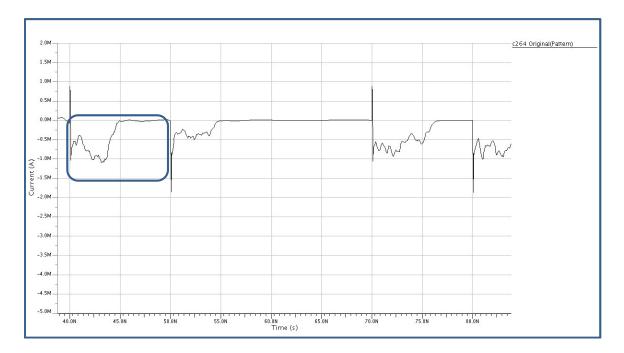

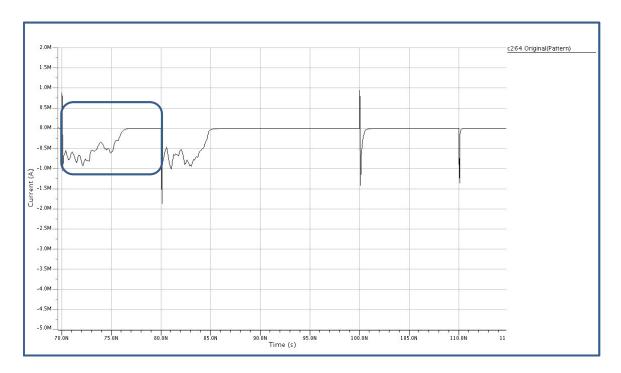

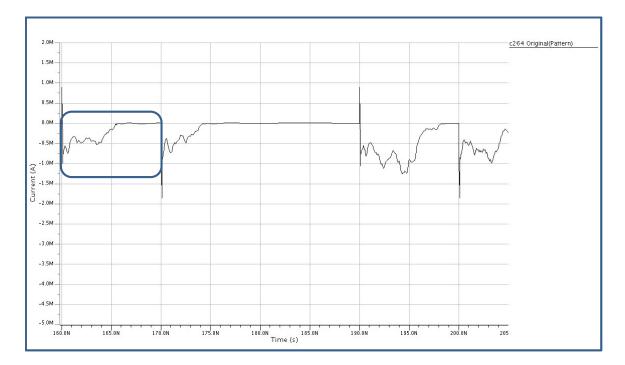

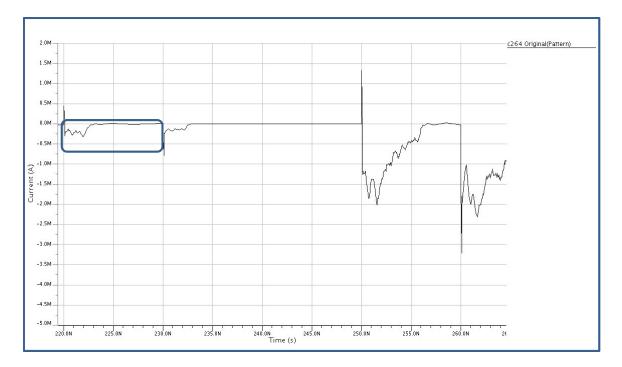

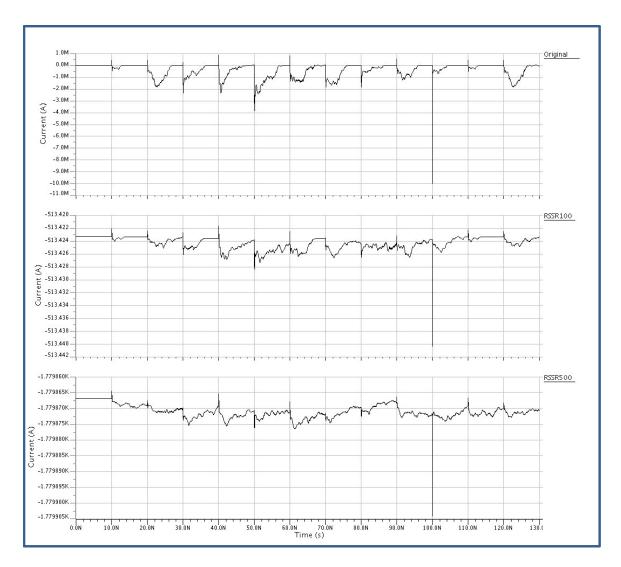

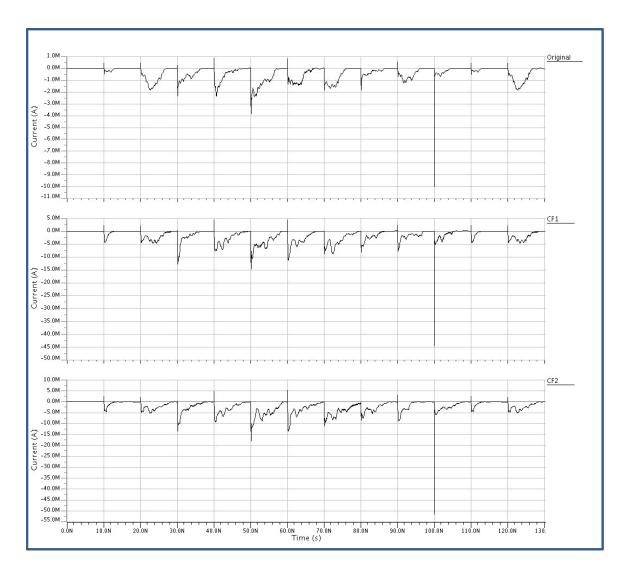

Figure 3.11:(a) Six Cycles of Current Waveform of c264 generated by ELDO spice simulator(b) Six Power Signatures of c264

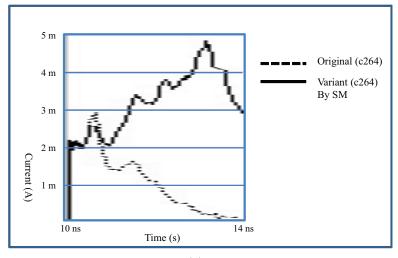

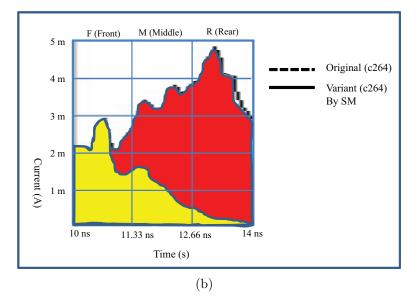

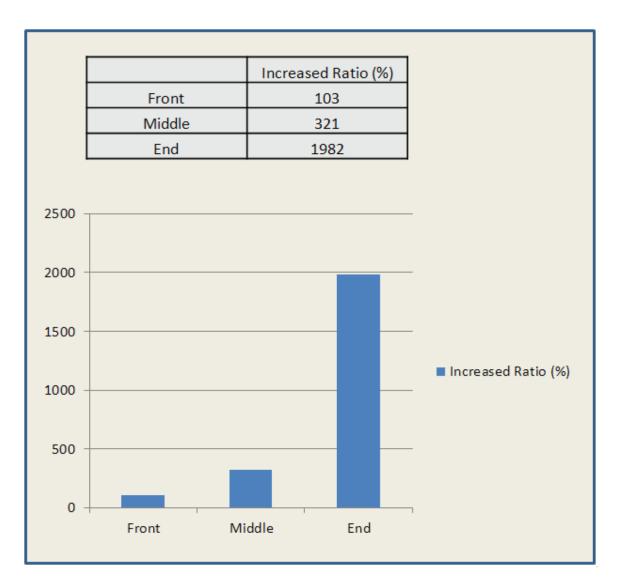

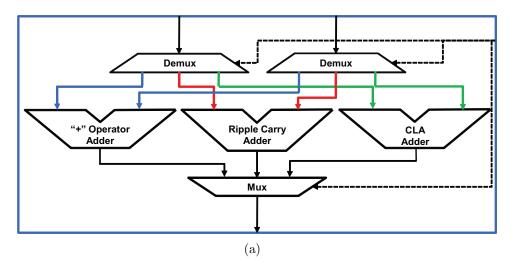

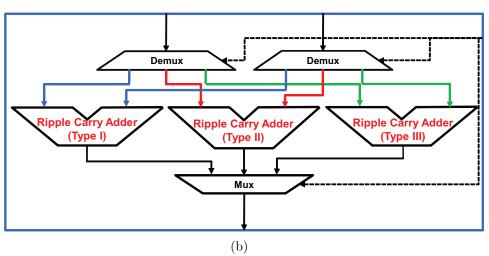

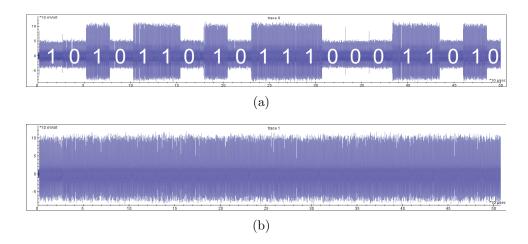

form, the abstract form of power signature can be readily obtained. For instance, Figure 3.11(a) shows the six cycles of the current waveform of c264 generated by ELDO simulator. By making an each cycle of wave form downside-up, each power signature can be obtained as shown in Figure 3.11(b).