# Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-22-2012

# Towards Quantifying Programmable Logic Controller Resilience Against Intentional Exploits

Henry W. Bushey

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Computer Sciences Commons

**Recommended** Citation

Bushey, Henry W., "Towards Quantifying Programmable Logic Controller Resilience Against Intentional Exploits" (2012). *Theses and Dissertations*. 1087. https://scholar.afit.edu/etd/1087

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

# TOWARDS QUANTIFYING PROGRAMMABLE LOGIC CONTROLLER

# **RESILIENCE AGAINST INTENTIONAL EXPLOITS**

THESIS

Henry W. Bushey, Captain, USAF

AFIT/GCO/ENG/12-03

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

DISTRIBUTION STATEMENT A. APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, Department of Defense, or the United States Government. This material is declared a work of the United States Government and is not subject to copyright protection in the United States.

# TOWARDS QUANTIFYING PROGRAMMABLE LOGIC CONTROLLER RESILIENCE AGAINST INTENTIONAL EXPLOITS

# THESIS

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science

Henry W. Bushey, B.S.E.E.

Captain, USAF

March 2012

Distribution Statement A. Approved for public release; distribution is unlimited.

AFIT/GCO/ENG/12-03

# TOWARDS QUANTIFYING PROGRAMMABLE LOGIC CONTROLLER RESILIENCE AGAINST INTENTIONAL EXPLOITS

Henry W. Bushey, B.S.E.E. Captain, USAF

Approved:

//SIGNED//\_\_\_\_\_ Maj Jonathan Butts, Ph.D. (Chairman)

//SIGNED//\_\_\_\_\_ Mr. Juan Lopez, Jr. (Member)

<u>2Mar2012</u> Date

5Mar2012

Date

//SIGNED//\_\_\_\_\_\_ Dr. Robert Mills, Ph.D. (Member) <u>2Mar2012</u> Date

#### Abstract

Supervisory Control and Data Acquisition (SCADA) systems control and monitor services for the nation's critical infrastructure. Recent cyber induced events (e.g., Stuxnet) provide an example of a targeted, covert cyber attack against a SCADA system that resulted in physical effects. Of particular note is how Stuxnet exploited the trust relationship between the human machine interface (HMI) and programmable logic controllers (PLCs). Current methods for validating system operating parameters rely on message exchange and network communications protocols, generally observed at the HMI. Although sufficient at the macro level, this method does not provide detection of malware that exhibits physical effects via covert manipulation of the PLC, as demonstrated by Stuxnet. In this research, an alternative method that leverages direct analysis of PLC input and output to derive the true state of SCADA end-devices is introduced. The behavioral input-output characteristics are modeled using Petri nets to derive metrics for quantifying resilient properties of systems against malicious exploits. The results yield metrics that are applicable towards quantifying resilience in PLCs and implementing real-time security solutions. These findings enable detecting programming changes that affect input and output relationships, identifying the degree of deviation from a baseline program, and minimizing performance losses against disruptive events.

# Acknowledgments

I would like to thank my advisor Maj Jonathan Butts for his insightful guidance throughout the entirety of my thesis development. I would also like to thank my committee members, Lt Col David Robinson, Dr. Robert Mills, and Mr. Juan Lopez for exposing me to their wealth of knowledge during my research. A warm thank you is also extended to my classmates who journeyed through the GCO program alongside me. Finally, I'd like to acknowledge a loving appreciation to my wife and children who support me through everything.

# **Table of Contents**

|                                                                  |                                                                                                                                                                                                                                                                                                                                              | Page        |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Abstract                                                         |                                                                                                                                                                                                                                                                                                                                              | iv          |

| Acknowled                                                        | lgments                                                                                                                                                                                                                                                                                                                                      | V           |

| Table of Co                                                      | ontents                                                                                                                                                                                                                                                                                                                                      | vi          |

| List of Figu                                                     | ires                                                                                                                                                                                                                                                                                                                                         | X           |

| List of Tab                                                      | les                                                                                                                                                                                                                                                                                                                                          | xiv         |

| List of Equ                                                      | ations                                                                                                                                                                                                                                                                                                                                       | xvi         |

| I. Introduc                                                      | tion                                                                                                                                                                                                                                                                                                                                         | 1           |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                  | Motivation<br>Research Statement<br>Research Approach<br>Assumptions/Limitations<br>Thesis Organization                                                                                                                                                                                                                                      | 3<br>3<br>4 |

| II. Literatu                                                     | re Review                                                                                                                                                                                                                                                                                                                                    | 8           |

| 2.1.2<br>2.1.3<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3 | Background<br>Supervisory Control and Data Acquisition (SCADA)<br>Resilience Overview<br>Petri Nets Overview<br>Related Work<br>Survivable SCADA Systems<br>Redundant SCADA Network Architecture<br>Mechanisms to Provide Integrity in SCADA Devices<br>Resilient ICS: Concepts, Formulation, Metrics, and Insights<br>Summary of Literature |             |

| III. Metho                                                       | dology                                                                                                                                                                                                                                                                                                                                       |             |

|                                                                  | Problem Definition<br>Goal 28<br>Hypothesis                                                                                                                                                                                                                                                                                                  |             |

| 3.1.2<br>3.2                                                     | Hypothesis<br>System Boundaries                                                                                                                                                                                                                                                                                                              |             |

| 3.3                                                              | System Doundaries                                                                                                                                                                                                                                                                                                                            |             |

| 3.4                                                              | System Parameters                                                                                                                                                                                                                                                                                                                            |             |

| 3.5                                                              | Factors                                                                                                                                                                                                                                                                                                                                      |             |

| 3.6                                                              | Workload                                                                                                                                                                                                                                                                                                                                     | 34          |

| 3.7 A         | pproach                                                           |    |

|---------------|-------------------------------------------------------------------|----|

|               | stablish Baseline for PLC Instance #1                             |    |

|               | haracterize Baseline Program as Petri Net                         |    |

|               | stablish Delta Baseline Program                                   |    |

|               | pply Workload (Attacks to Baselines)                              |    |

|               | erformance Metrics                                                |    |

|               | valuation Technique                                               |    |

|               | irect Measurement via PLC                                         |    |

| 3.9.2 P       | etri net Analysis                                                 | 45 |

|               | xperimental Design                                                |    |

|               | ummary of Methodology                                             |    |

| IV. Results a | nd Analysis                                                       | 48 |

| 4.1 R         | esults of Simulation Scenarios                                    | 48 |

| 4.1.1 D       | Derivation of Tangible State Table                                | 48 |

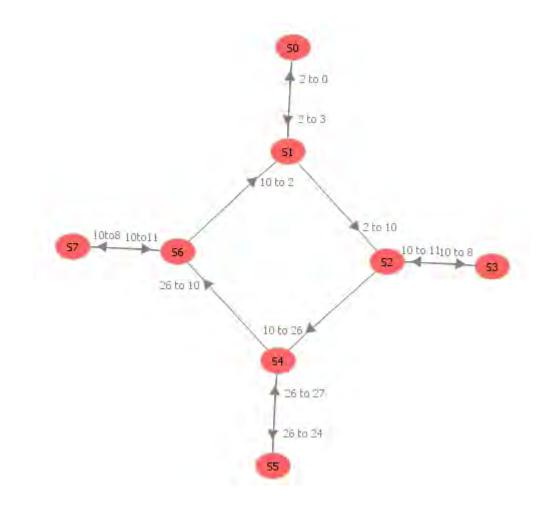

| 4.1.2 D       | Derivation of Reachability Graph                                  | 49 |

|               | Derivation of Reachability Matrix                                 |    |

|               | Differentiating Between Reachability Matrices                     |    |

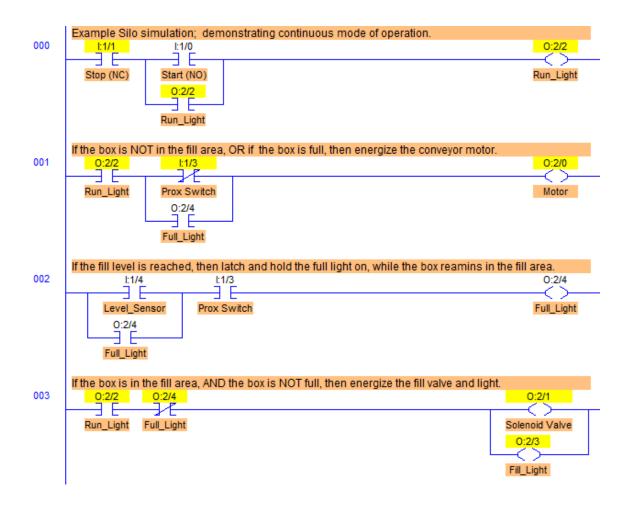

|               | Differentiating Between Ladder Logic                              |    |

|               | ummary of Results                                                 |    |

| 4.2 A         | nalysis of Results                                                | 58 |

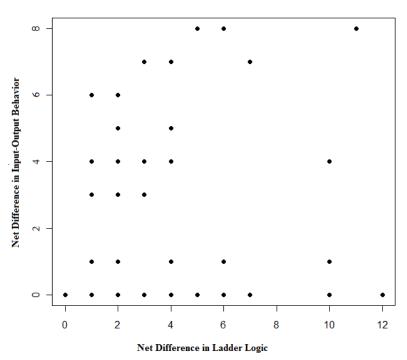

| 4.2.1 S       | catter Plot of Results                                            | 59 |

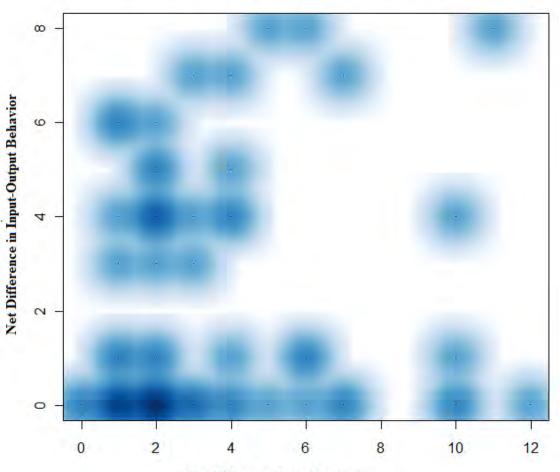

| 4.2.2 St      | mooth Densities Plot of Results                                   | 60 |

|               | Correlation Results                                               |    |

|               | Deservations from Differentiation Tables and Correlation Analysis |    |

|               | ummary of Analysis                                                |    |

|               | ignificant Findings                                               |    |

|               | pplicability to the Resilience Framework                          |    |

|               | pplicability to Real-Time Hardware Solutions                      |    |

|               | ummary of Findings                                                |    |

|               | ummary of Results and Analysis                                    |    |

| V. Conclusio  | ons and Recommendations                                           | 70 |

| 5.1 R         | esearch Summary                                                   | 70 |

| 5.1.1 St      | ummary of Experimental Methodology                                | 70 |

| 5.1.2 St      | ummary of Analysis                                                | 71 |

| 5.1.3 St      | ummary of Meeting Goals                                           | 72 |

|               | uture Work                                                        |    |

| 5.2.1 R       | eal-time Application of Metrics in Hardware                       | 72 |

|               | nhancing Benchmark Tools for Resilience                           |    |

|               | Iternate Experimentation Method Strictly Utilizing Petri Nets     |    |

|               | oncluding Remarks                                                 |    |

| Appendix A    |                                                                   | 75 |

| Baseline Program                                              | 75  |

|---------------------------------------------------------------|-----|

| Attack Baseline Program for Instance 1                        |     |

| Attack Baseline Program for Instance 2                        |     |

| Attack Baseline Program for Instance 3                        | 84  |

| Attack Baseline Program for Instance 4                        |     |

| Attack Baseline Program for Instance 5                        |     |

| Attack Baseline Program for Instance 6                        |     |

| Attack Baseline Program for Instance 7                        |     |

| Attack Baseline Program for Instance 8                        | 99  |

| Attack Baseline Program for Instance 9                        | 101 |

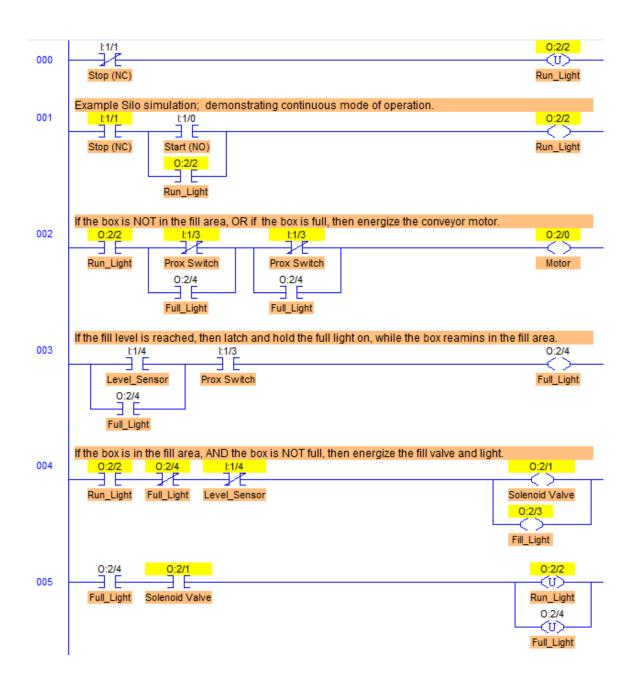

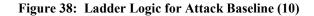

| Attack Baseline Program for Instance 10                       |     |

| Delta Baseline Program for Instance 1                         | 107 |

| Delta Baseline Program for Instance 2                         |     |

| Delta Baseline Program for Instance 3                         | 109 |

| Delta Baseline Program for Instance 4                         | 110 |

| Delta Baseline Program for Instance 5                         | 111 |

| Delta Baseline Program for Instance 6                         | 112 |

| Delta Baseline Program for Instance 7                         | 113 |

| Delta Baseline Program for Instance 8                         | 114 |

| Delta Baseline Program for Instance 9                         | 115 |

| Delta Baseline Program for Instance 10                        | 116 |

| Attack Delta Baseline Program for Instance 1                  | 117 |

| Attack Delta Baseline Program for Instance 2                  |     |

| Attack Delta Baseline Program for Instance 3                  | 119 |

| Attack Delta Baseline Program for Instance 4                  | 120 |

| Attack Delta Baseline Program for Instance 5                  | 121 |

| Attack Delta Baseline Program for Instance 6                  |     |

| Attack Delta Baseline Program for Instance 7                  |     |

| Attack Delta Baseline Program for Instance 8                  |     |

| Attack Delta Baseline Program for Instance 9                  |     |

| Attack Delta Baseline Program for Instance 10                 | 128 |

|                                                               | 100 |

| Appendix B                                                    | 129 |

| Baseline Program                                              | 120 |

| Attack Delta Baseline Program (for PLC Instance 9)            |     |

| Attack Baseline Program (for PLC Instance 1)                  |     |

| Attack Baseline Program (for PLC Instance 1)                  |     |

| Attack Baseline Program (for PLC Instance 2)                  |     |

| Attack Baseline Program (for PLC Instance 4)                  |     |

| Attack Baseline Program (for PLC Instance 4)                  |     |

| Attack Baseline Program (for PLC Instance 6)                  |     |

| Attack Baseline Program (for PLC Instance 0)                  |     |

| Attack Baseline Program (for PLC Instance 7)                  |     |

| Attack Baseline Program (for PLC Instance 9)                  |     |

| $f$ mark baseline i togram (101 i Le instance $\mathcal{I}$ ) | 140 |

| Attack Baseline Program (for PLC Instance 10) |  |

|-----------------------------------------------|--|

| Bibliography                                  |  |

# List of Figures

| Figure 1: SCADA Components (Stouffer, 2008)                                  | Page<br>9 |

|------------------------------------------------------------------------------|-----------|

| Figure 2: Example Traffic Light Petri Net                                    |           |

| Figure 3: Queiroz's Summary for Sample Data (Queiroz, 2010)                  |           |

| Figure 4: Germanus' Middleware Building Blocks (Germanus, 2010)              |           |

| Figure 5: Germanus' (2010) Redundant P2P Model                               |           |

| Figure 6: Shah's (2008) Verification Function Overview                       |           |

| Figure 7: Wei's Resilience Curve (Wei, 2009)                                 |           |

| Figure 8: PLC SUT Diagram                                                    |           |

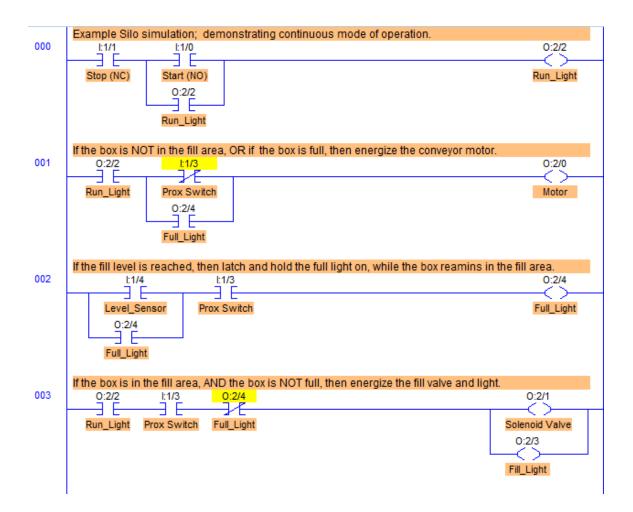

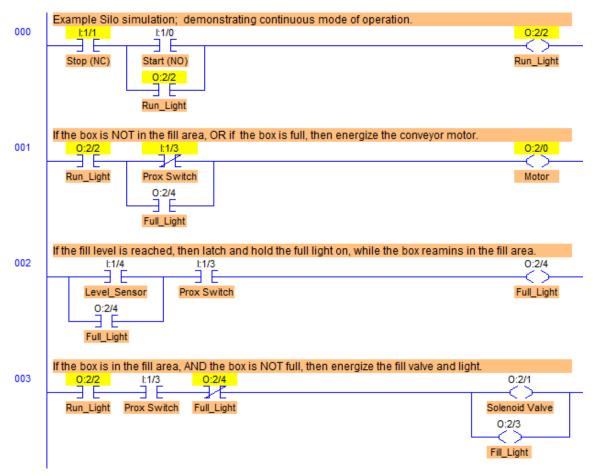

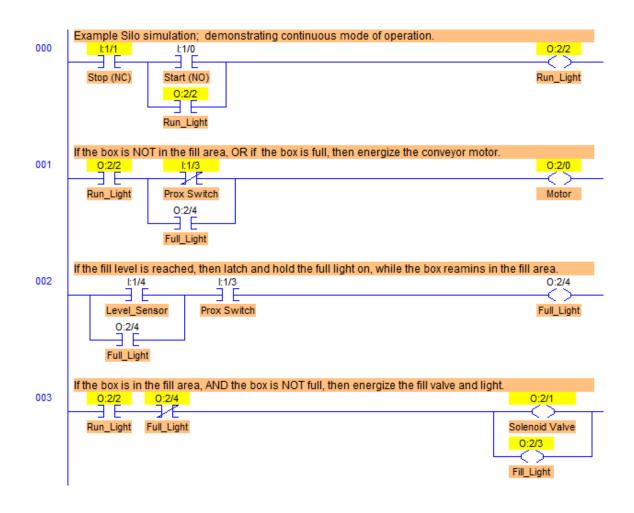

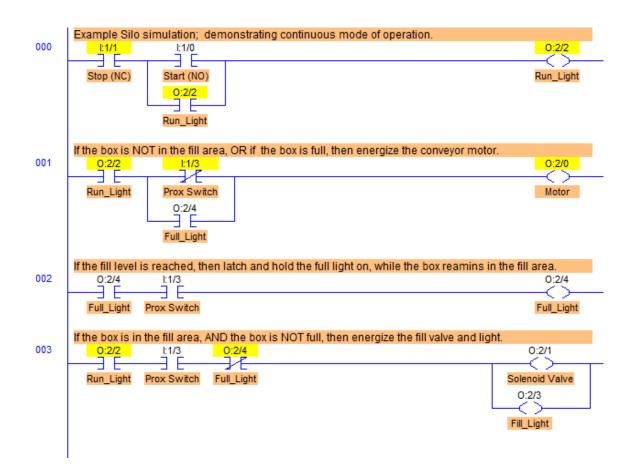

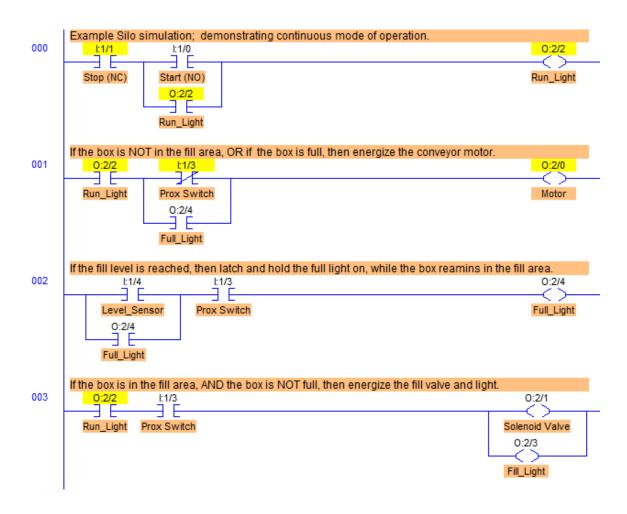

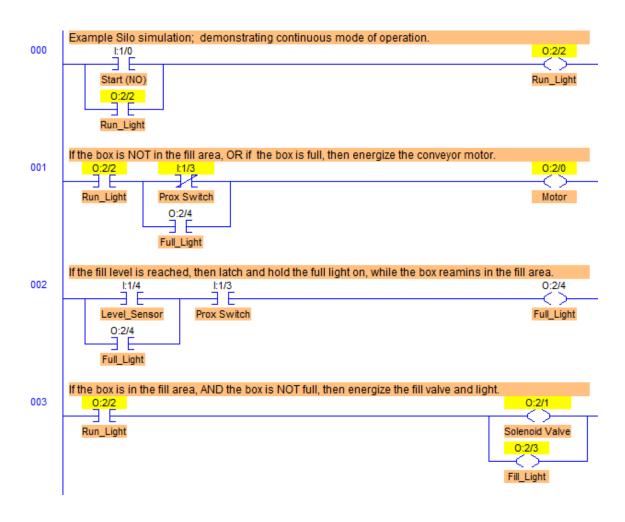

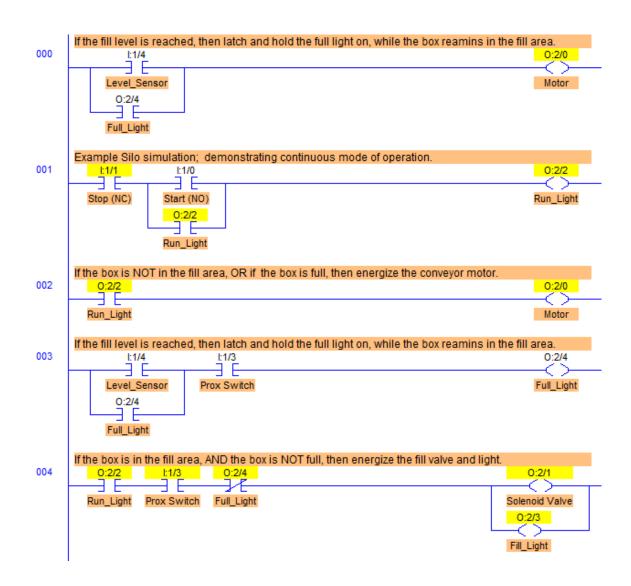

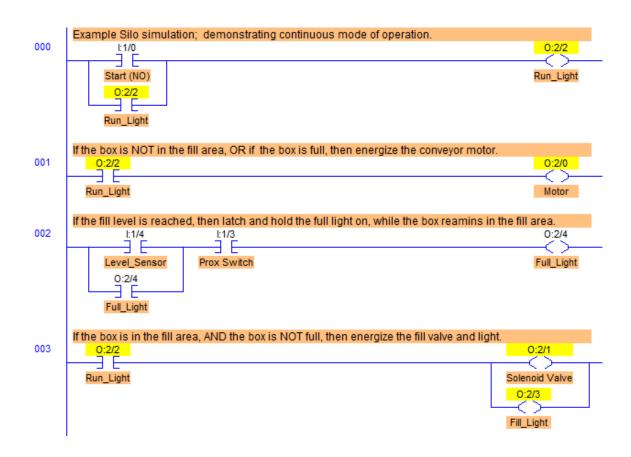

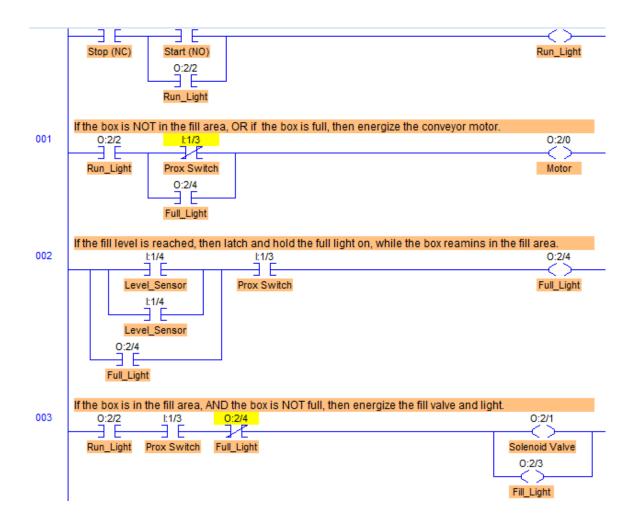

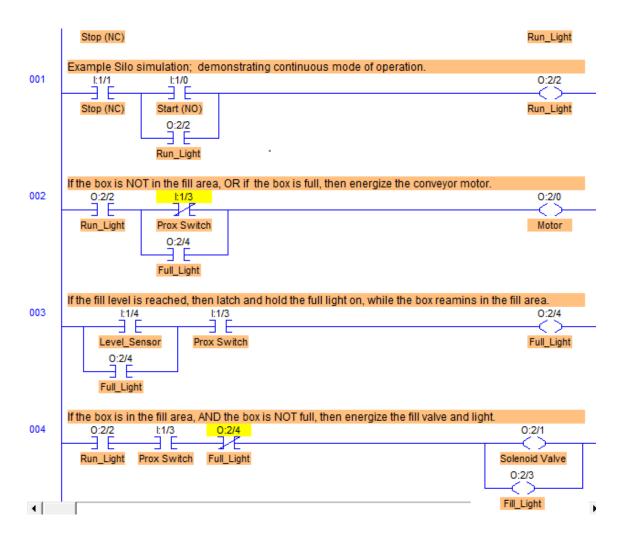

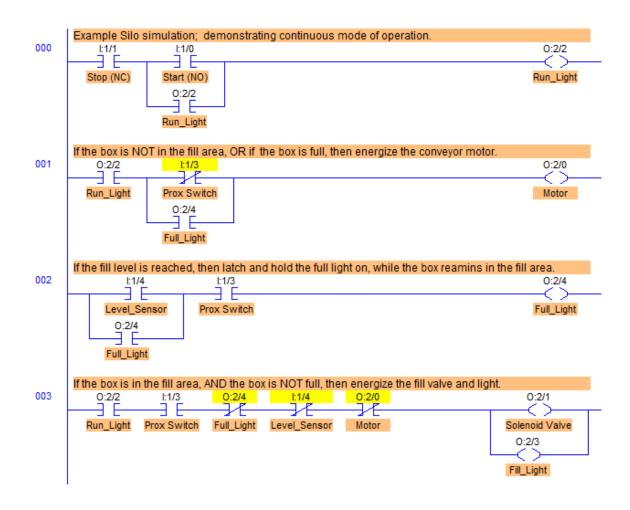

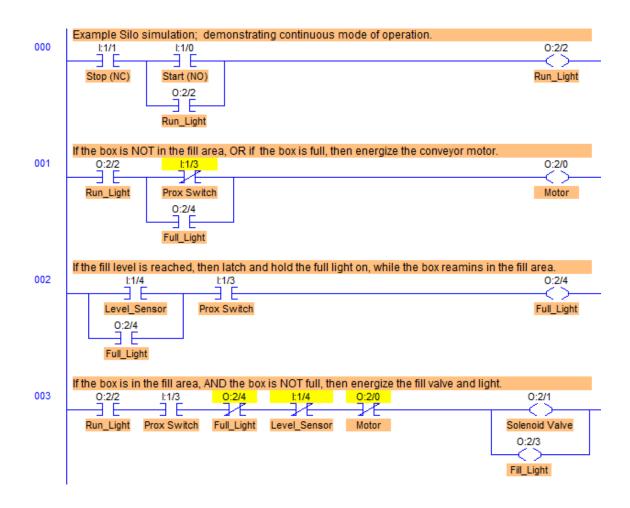

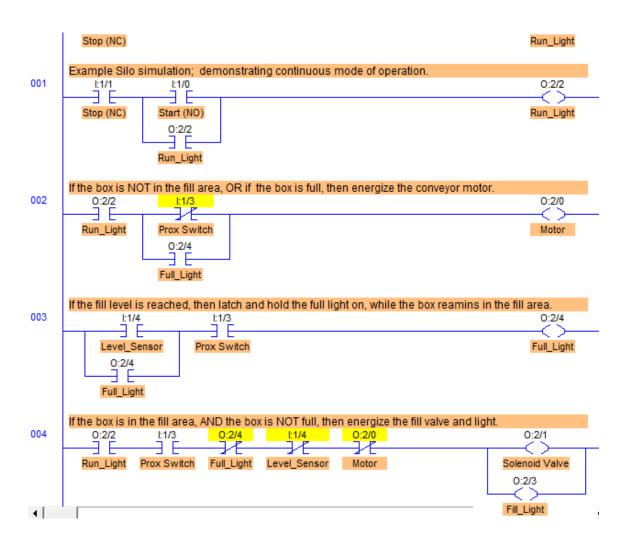

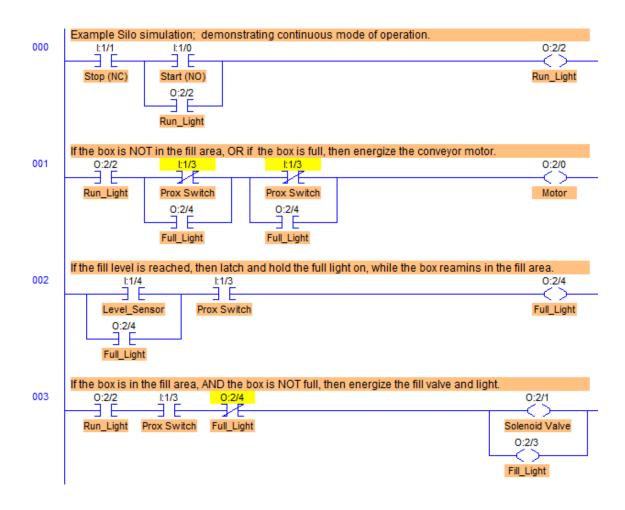

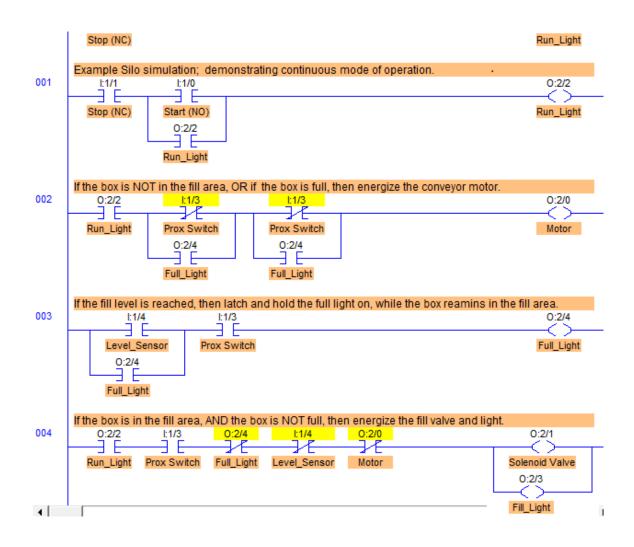

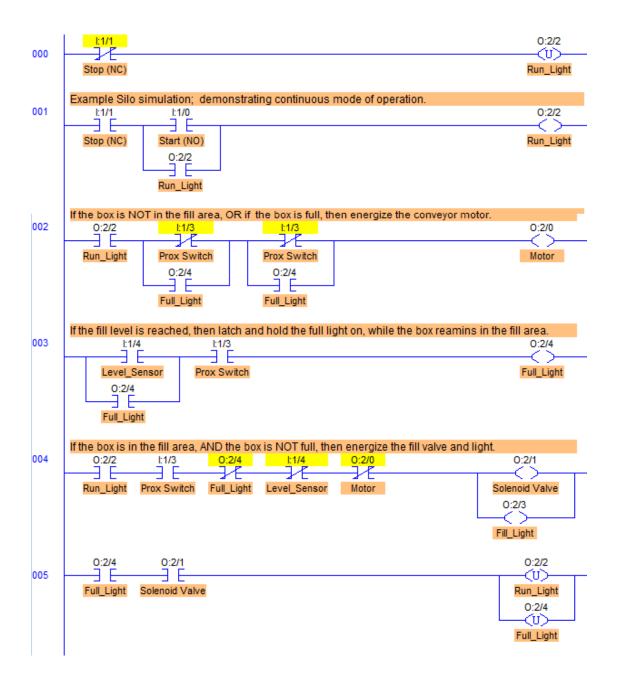

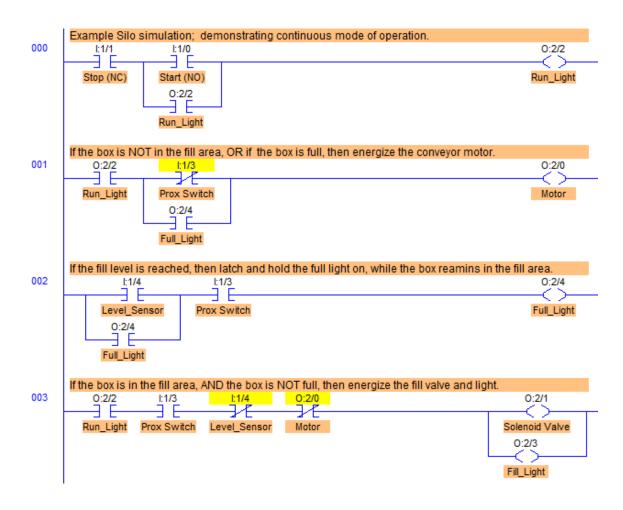

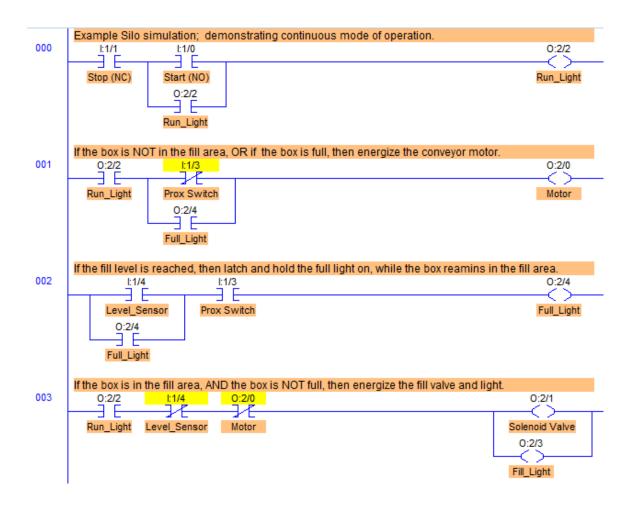

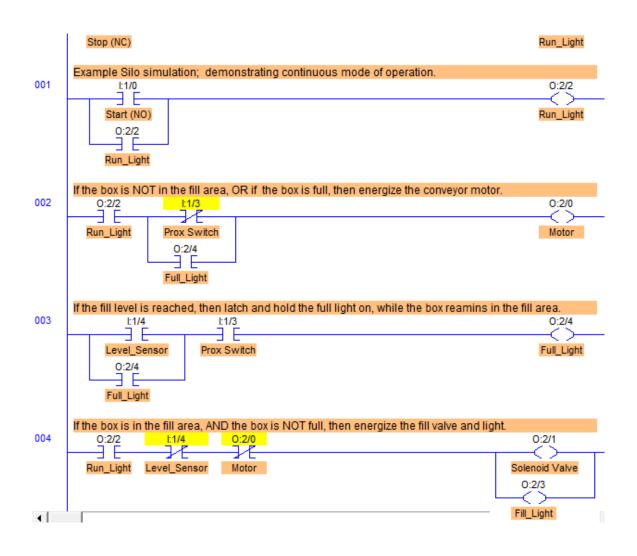

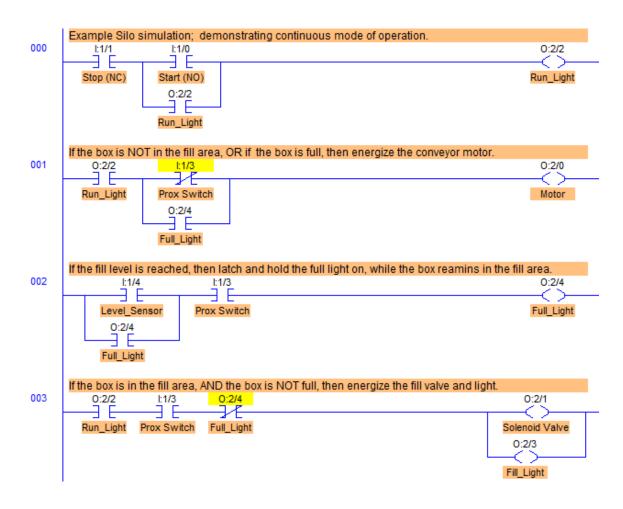

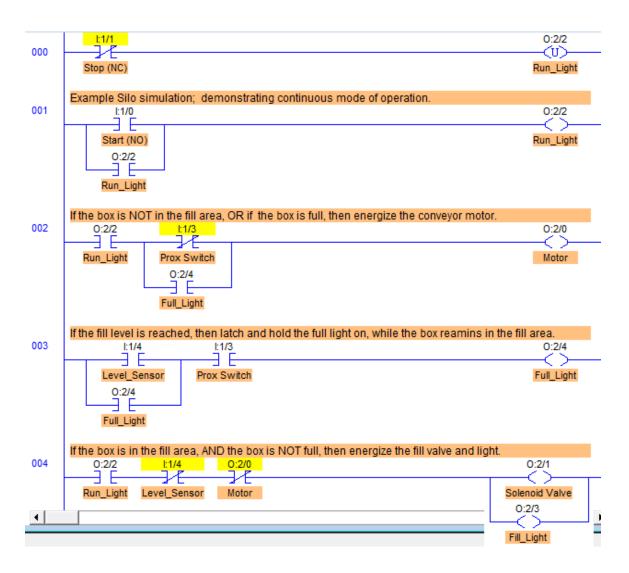

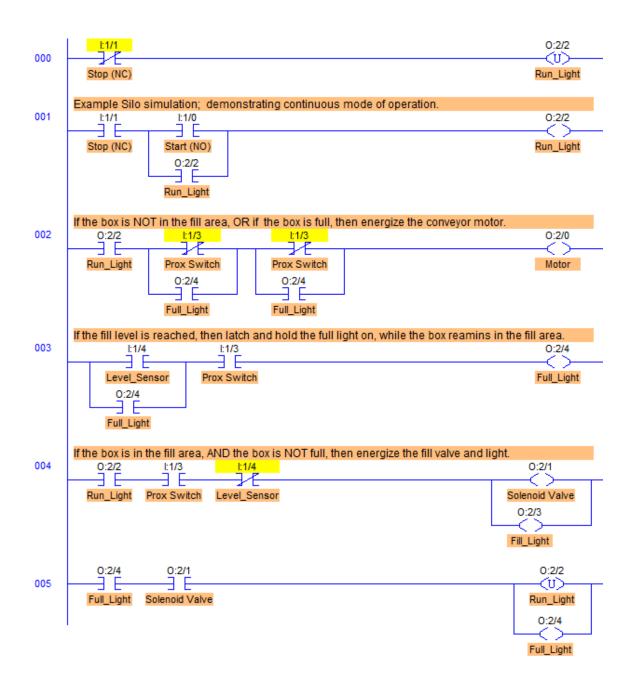

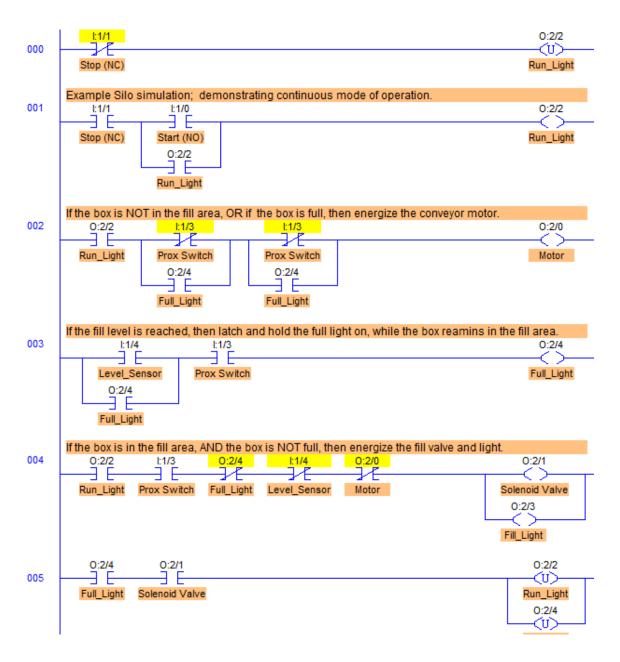

| Figure 9: Ladder Logic of Baseline Program                                   |           |

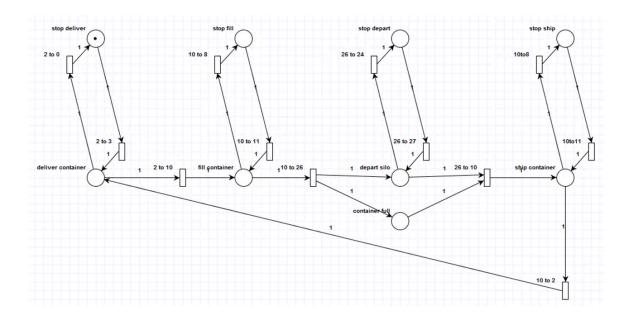

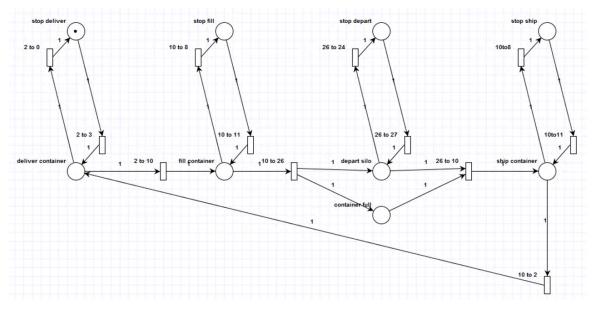

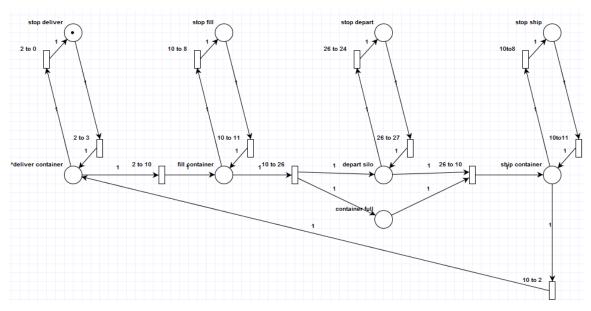

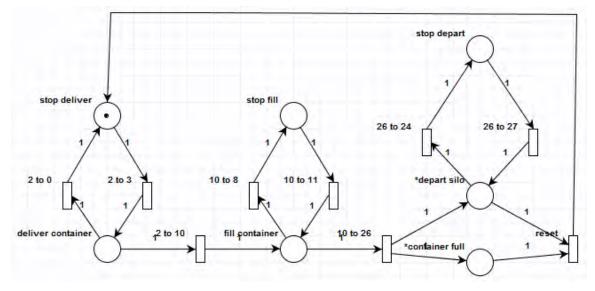

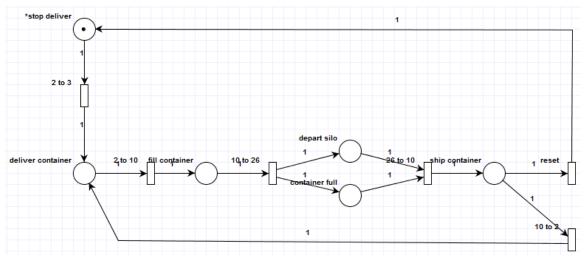

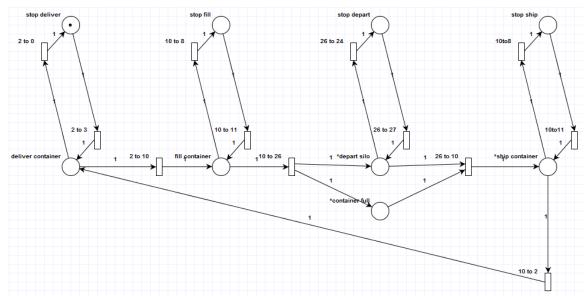

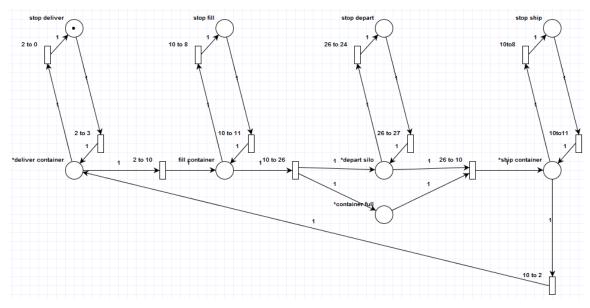

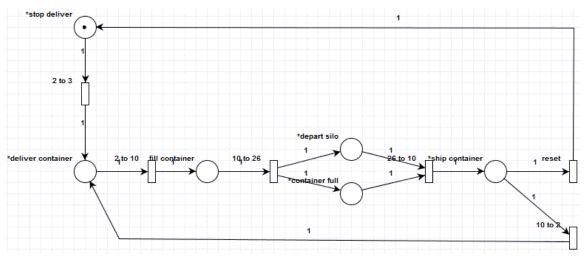

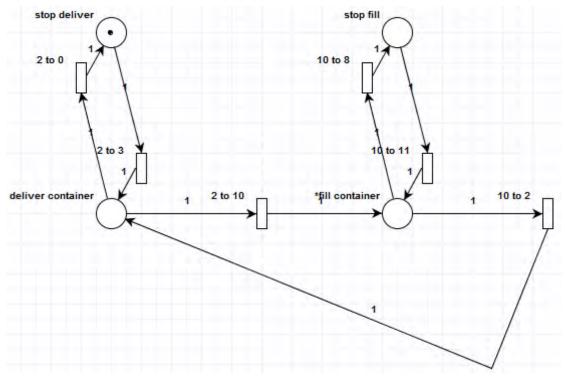

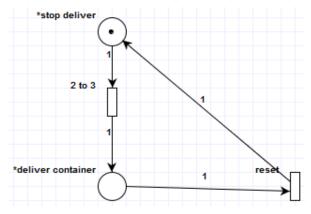

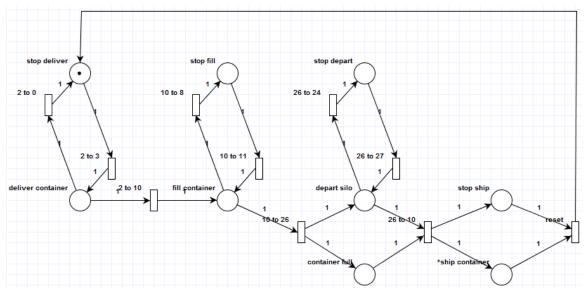

| Figure 10: Petri Net of Baseline Program                                     |           |

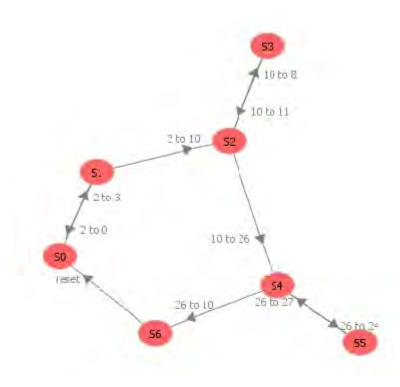

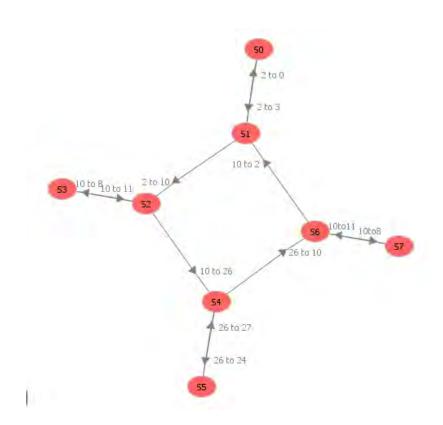

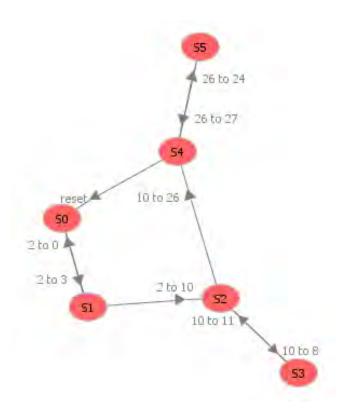

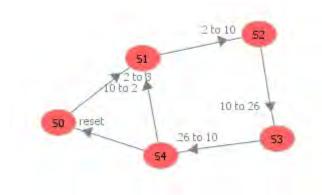

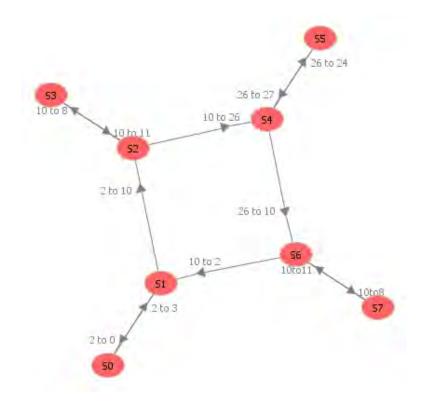

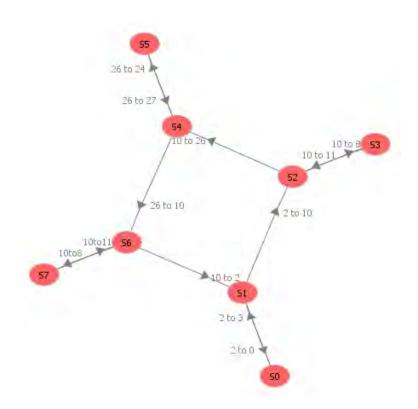

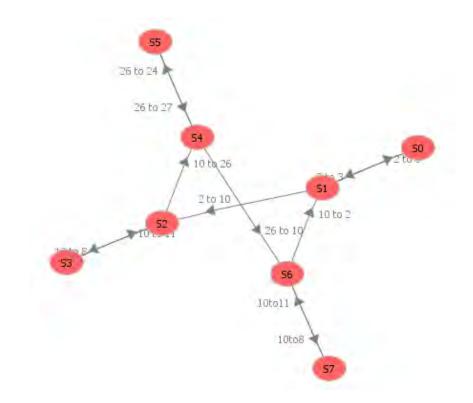

| Figure 11: Reachability Graph for Baseline                                   | 50        |

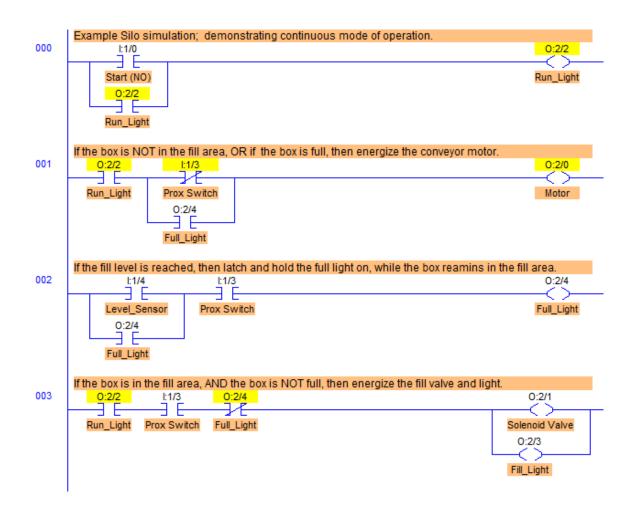

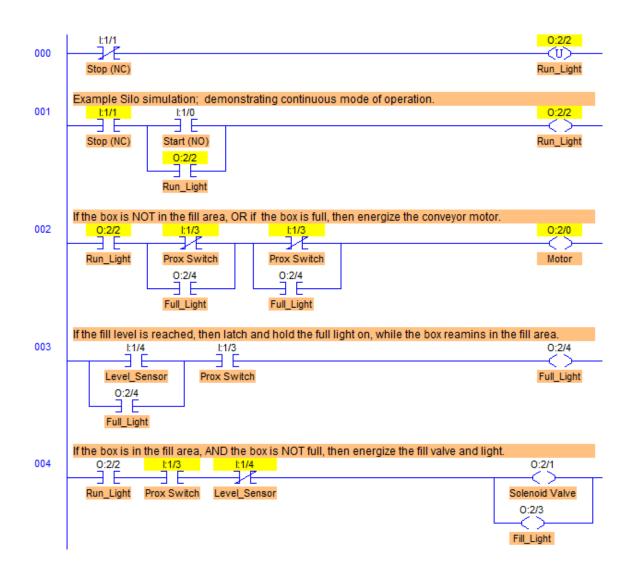

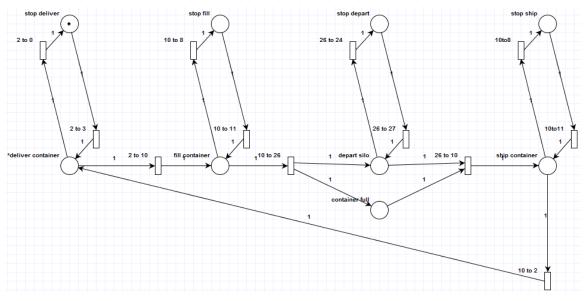

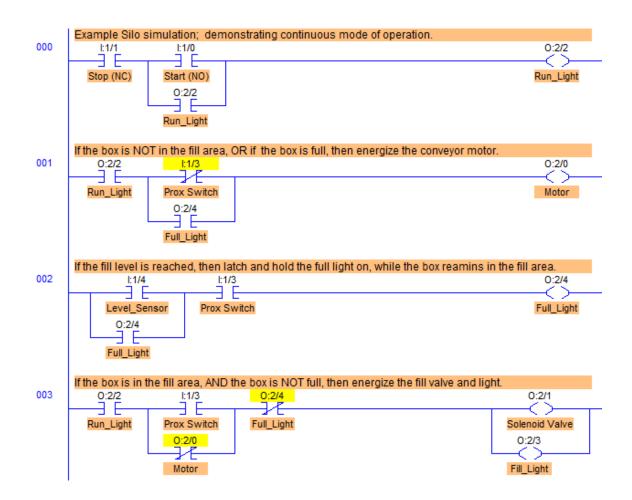

| Figure 12: Baseline PLC Ladder Logic                                         |           |

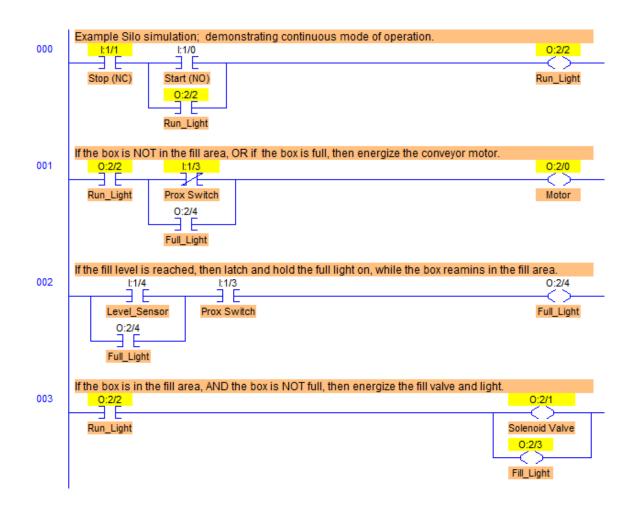

| Figure 13: Attack Baseline PLC Ladder Logic for Instance #1                  |           |

| Figure 14: Scatter Plot Between Ladder Logic and I/O Deltas                  | 59        |

| Figure 15: Scatter Plot Revealing Overlap Densities                          |           |

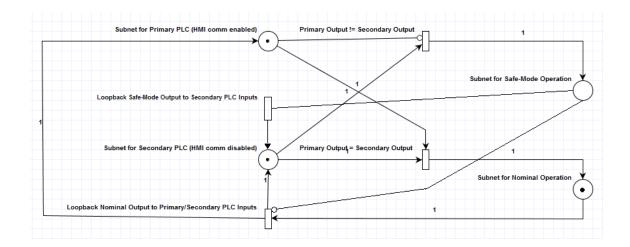

| Figure 16: High-Level Petri Net Utilizing I/O Analysis (Nominal Operation)   |           |

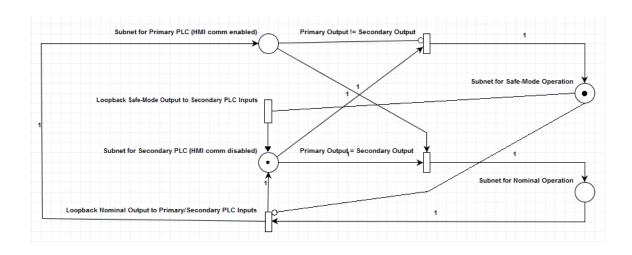

| Figure 17: High-Level Petri Net Utilizing I/O Analysis (Safe-Mode Triggered) | 69        |

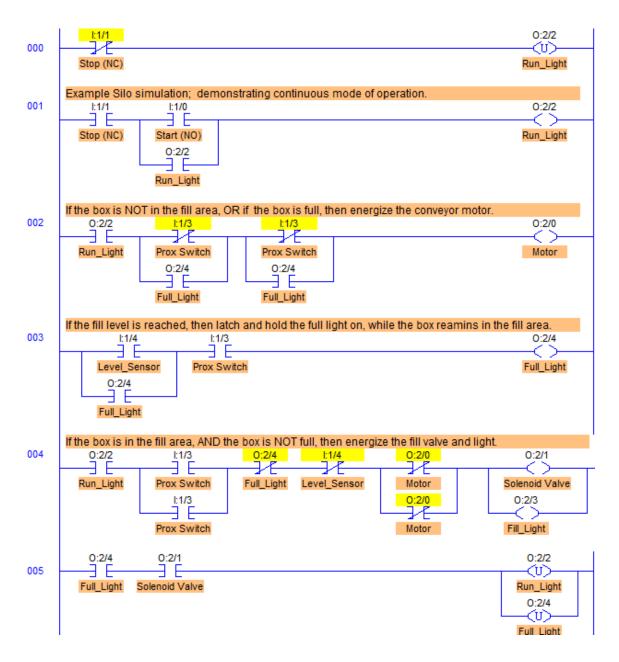

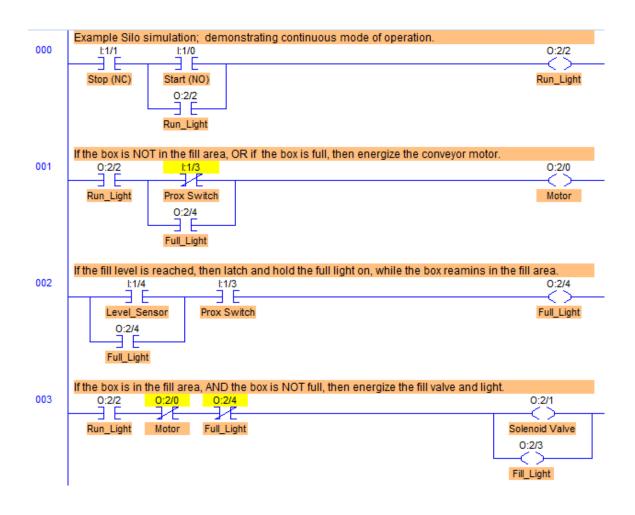

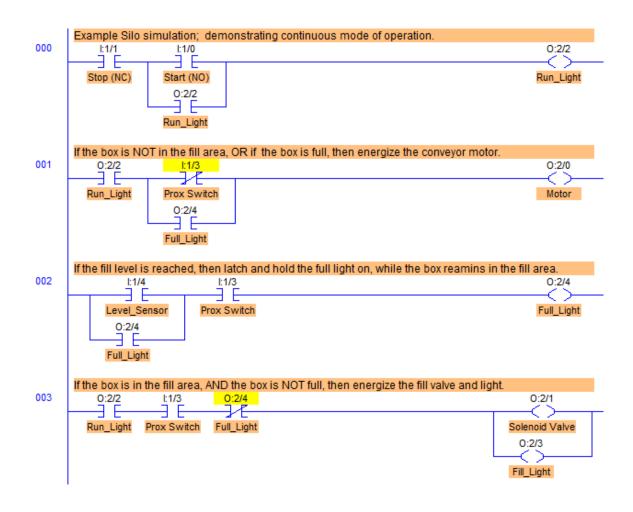

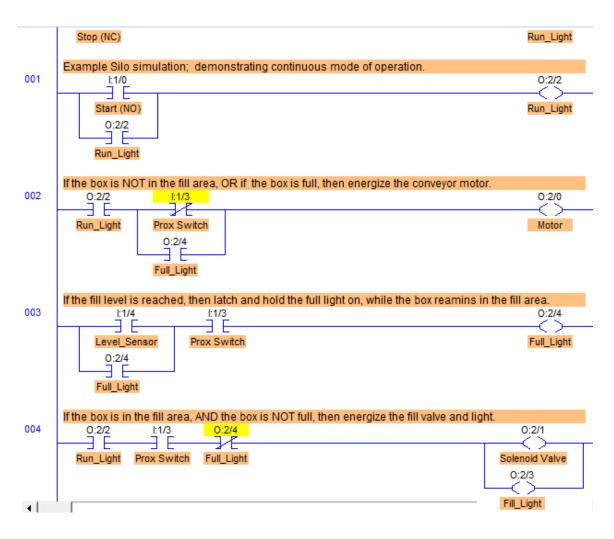

| Figure 18: Ladder Logic for Baseline (all)                                   |           |

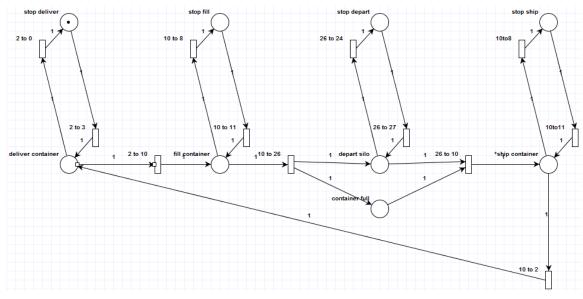

| Figure 19: Petri Net for Baseline (all)                                      |           |

| Figure 20: Ladder Logic for Attack Baseline (1)                              |           |

| Figure 21: Petri Net for Attack Baseline (1)                                 |           |

| Figure 22: | Ladder Logic for Attack Baseline (2)  | . 81 |

|------------|---------------------------------------|------|

| Figure 23: | Petri Net for Attack Baseline (2)     | . 82 |

| Figure 24: | Ladder Logic for Attack Baseline (3)  | . 84 |

| Figure 25: | Petri Net for Attack Baseline (3)     | . 85 |

| Figure 26: | Ladder Logic for Attack Baseline (4)  | . 87 |

| Figure 27: | Petri Net for Attack Baseline (4)     | . 88 |

| Figure 28: | Ladder Logic for Attack Baseline (5)  | . 90 |

| Figure 29: | Petri Net for Attack Baseline (5)     | . 91 |

| Figure 30: | Ladder Logic for Attack Baseline (6)  | . 93 |

| Figure 31: | Petri Net for Attack Baseline (6)     | . 94 |

| Figure 32: | Ladder Logic for Attack Baseline (7)  | . 96 |

| Figure 33: | Petri Net for Attack Baseline (7)     | . 97 |

| Figure 34: | Ladder Logic for Attack Baseline (8)  | . 99 |

| Figure 35: | Petri Net for Attack Baseline (8)     | 100  |

| Figure 36: | Ladder Logic for Attack Baseline (9)  | 101  |

| Figure 37: | Petri Net for Attack Baseline (9)     | 102  |

| Figure 38: | Ladder Logic for Attack Baseline (10) | 105  |

| Figure 39: | Petri Net for Attack Baseline (10)    | 105  |

| Figure 40: | Ladder Logic for Delta Baseline (1)   | 107  |

| Figure 41: | Ladder Logic for Delta Baseline (2)   | 108  |

| Figure 42: | Ladder Logic for Delta Baseline (3)   | 109  |

| Figure 43: | Ladder Logic for Delta Baseline (4)   | 110  |

| Figure 44: | Ladder Logic for Delta Baseline (5)   | 111  |

| Figure 45: | Ladder Logic for Delta Baseline (6)                                       | 112 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 46: | Ladder Logic for Delta Baseline (7)                                       | 113 |

| Figure 47: | Ladder Logic for Delta Baseline (8)                                       | 114 |

| Figure 48: | Ladder Logic for Delta Baseline (9)                                       | 115 |

| Figure 49: | Ladder Logic for Delta Baseline (10)                                      | 116 |

| Figure 50: | Attack Ladder Logic for Delta Baseline (1)                                | 117 |

| Figure 51: | Attack Ladder Logic for Delta Baseline (2)                                | 118 |

| Figure 52: | Attack Ladder Logic for Delta Baseline (3)                                | 119 |

| Figure 53: | Attack Ladder Logic for Delta Baseline (4)                                | 120 |

| Figure 54: | Attack Ladder Logic for Delta Baseline (5)                                | 121 |

| Figure 55: | Attack Ladder Logic for Delta Baseline (6)                                | 122 |

| Figure 56: | Attack Ladder Logic for Delta Baseline (7)                                | 123 |

| Figure 57: | Attack Ladder Logic for Delta Baseline (8)                                | 124 |

| Figure 58: | Attack Ladder Logic for Delta Baseline (9)                                | 125 |

| Figure 59: | Petri Net for Attack Delta Baseline (9)                                   | 126 |

| Figure 60: | Attack Ladder Logic for Delta Baseline (10)                               | 128 |

| Figure 61: | Graph for Baseline (1-10), Delta Baseline (1-10) and Attack Delta Baselin | e   |

| (1-8,10    | 0)                                                                        | 129 |

| Figure 62: | Graph for Attack Delta Baseline (9)                                       | 131 |

| Figure 63: | Graph for Attack Baseline (1)                                             | 133 |

| Figure 64: | Graph for Attack Baseline (2)                                             | 135 |

| Figure 65: | Graph for Attack Baseline (3)                                             | 137 |

| Figure 66: | Graph for Attack Baseline (4)                                             | 139 |

| Figure 67: | Graph for Attack Baseline (5)  | 141 |

|------------|--------------------------------|-----|

| Figure 68: | Graph for Attack Baseline (6)  | 143 |

| Figure 69: | Graph for Attack Baseline (7)  | 145 |

| Figure 70: | Graph for Attack Baseline (8)  | 147 |

| Figure 71: | Graph for Attack Baseline (9)  | 148 |

| Figure 72: | Graph for Attack Baseline (10) | 150 |

# List of Tables

| Table 1: Intentional SCADA Incidents                                                | Page<br>11 |

|-------------------------------------------------------------------------------------|------------|

| Table 2: Non-Intentional SCADA Incidents                                            | 12         |

| Table 3: Examples of Petri Net Places and Transitions (Abhishek, 2005)              | 16         |

| Table 4: Example Traffic Light System Response                                      | 32         |

| Table 5: Parameters                                                                 | 33         |

| Table 6: Ten PLC Attack Instances                                                   | 35         |

| Table 7: Tangible States for Baseline                                               | 49         |

| Table 8: Reachable Markings for Baseline                                            | 51         |

| Table 9: Reachable Markings for Attack (Instance #1)                                | 53         |

| Table 10: Net Difference in Input-Output Behavior (Instance #1)                     | 54         |

| Table 11: Net Difference in Symbolic Ladder Logic (Instance #1)                     | 57         |

| Table 12: Net Difference in Symbolic Ladder Logic                                   | 57         |

| Table 13: Net Difference in Input-Output Behavior                                   | 58         |

| Table 14: Tangible States for Baseline (all), Delta Baseline (all) and Attack Delta |            |

| Baseline (1-8, 10)                                                                  | 129        |

| Table 15: Matrix for Baseline (1-10), Delta Baseline (1-10) and Attack Delta Base   | eline      |

| (1-8,10)                                                                            | 130        |

| Table 16: Tangible States for Attack Delta Baseline (9)                             | 131        |

| Table 17: Matrix for Attack Delta Baseline (9)                                      | 132        |

| Table 18: Tangible States for Attack Baseline (1)                                   | 133        |

| Table 19: Matrix for Attack Baseline (1)                                            | 134        |

| Table 20: | Tangible States for Attack Baseline (2)  | 135 |

|-----------|------------------------------------------|-----|

| Table 21: | Matrix for Attack Baseline (2)           | 136 |

| Table 22: | Tangible States for Attack Baseline (3)  | 137 |

| Table 23: | Matrix for Attack Baseline (3)           | 138 |

| Table 24: | Tangible States for Attack Baseline (4)  | 139 |

| Table 25: | Matrix for Attack Baseline (4)           | 140 |

| Table 26: | Tangible States for Attack Baseline (5)  | 141 |

| Table 27: | Matrix for Attack Baseline (5)           | 142 |

| Table 28: | Tangible States for Attack Baseline (6)  | 143 |

| Table 29: | Matrix for Attack Baseline (6)           | 144 |

| Table 30: | Tangible States for Attack Baseline (7)  | 145 |

| Table 31: | Matrix for Attack Baseline (7)           | 146 |

| Table 32: | Tangible States for Attack Baseline (8)  | 147 |

| Table 33: | Matrix for Attack Baseline (8)           | 147 |

| Table 34: | Tangible States for Attack Baseline (9)  | 148 |

| Table 35: | Matrix for Attack Baseline (9)           | 149 |

| Table 36: | Tangible States for Attack Baseline (10) | 150 |

| Table 37: | Matrix for Attack Baseline (10)          | 151 |

# List of Equations

|                                               | Page |

|-----------------------------------------------|------|

| Equation 1: Spearman's Rank Order Coefficient | 61   |

# TOWARDS QUANTIFYING PROGRAMMABLE LOGIC CONTROLLER RESILIENCE AGAINST INTENTIONAL EXPLOITS

#### I. Introduction

This chapter provides an overview of this research. Section 1.1 introduces the motivation; Section 1.2 provides the research goals; Section 1.3 describes an overview of the research approach; Section 1.4 lists key assumptions and limitations; and Section 1.5 outlines the thesis organization.

# 1.1 Motivation

Supervisory Control and Data Acquisition (SCADA) systems provide automated control and monitoring for the nation's critical infrastructure. Implemented in many industry sectors as early as the 1960's, security was not initially a priority for SCADA design and development; however, recent intentional and unintentional events have highlighted concerns associated with SCADA security (Stouffer, 2008). Non-intentional events have traditionally been addressed with redundant and fault tolerant architectures. However, current solutions for intentional malicious actions are not sufficient for addressing the threat.

A primary risk factor associated with intentional malicious events is the trend to incorporate business enterprise networks for cost saving purposes. Indeed, interconnecting critical systems via LAN and WAN technologies enables entry points for attacks via the Internet, internal workstations, or communication links between the control center and field sites (Stouffer, 2008). As demonstrated by Stuxnet, an attack can propagate via the enterprise network to execute code on field devices that results in physical damage to the underlying system (Falliere, 2011).

Stuxnet is a recent example of an intentional malicious cyber event. Stuxnet targeted a specific programmable logic controller (PLC) manufacturer and configuration. PLCs control physical end-devices (e.g., sensors, pumps, motors, valves) at the edge of SCADA systems. Stuxnet functionally alters the PLC's parameters such that specific drive motors were driven beyond nominal specifications (Falliere, 2011). Additionally, Stuxnet masks modification of the PLCs functions from the SCADA system operator. Stuxnet demonstrates a novel threat to SCADA security since it both altered physical parameters to the system and concealed the modifications.

The Stuxnet example demonstrates SCADA systems are vulnerable to rootkit-like exploits. Current methods of validating the functional parameters of a PLC primarily consider the message exchange and network communications protocols, generally observed at the human machine interface (HMI). Although sufficient at the macro level, this method does not provide detection of malware which exhibits physical effects and masks the operations from the HMI or communication channel.

Establishing a resilient SCADA system can help mitigate risks associated with malicious exploits. Resiliency requires that a system be self-aware, robust and adaptive (National Infrastructure Advisory Council, 2009). Additionally, determining the resilience of a system requires that a system's susceptibility to degradation and capability to recover be quantifiable. Establishing a quantifiable measure of resilience for SCADA systems is key to protecting critical infrastructure assets.

# **1.2** Research Statement

The goal of this research is to provide a method to quantify the identification and absorption of malicious alterations by monitoring and characterizing field device inputs and outputs to PLCs. By focusing on the field device at the micro level, intentional malicious actions can be observed that otherwise would mask effects at the HMI, as was the case in Stuxnet. This research investigates metrics that align with characteristics of resilience. Traits such as self-awareness are a foundational characteristic of resilience and may provide a basis for tangible mechanisms to maintain the integrity of a PLC's nominal functions in the presence of malicious events.

# 1.3 Research Approach

Establishing a metric to assess a PLC's resilience requires both data that reflects nominal PLC functionality and a definition of resilience which makes the metric applicable. The data used for this research is derived from PLC simulations executed on LogixPro<sup>®</sup> 500 software. The definition for resilience is taken from the National Infrastructure Advisory Council (2009).

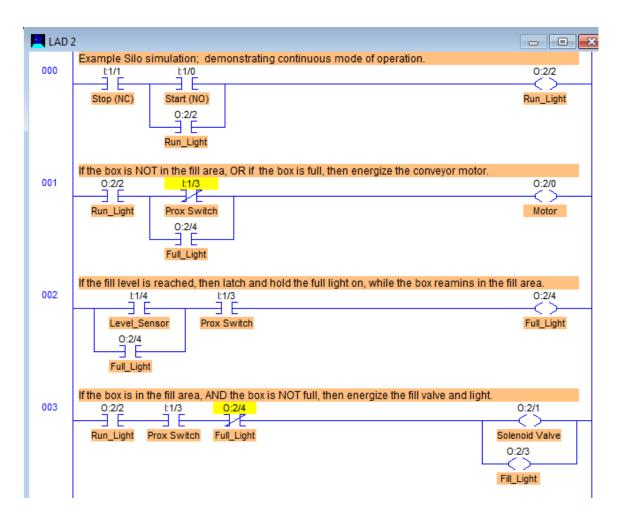

The PLC simulations consist of various programs that emulate instances of a PLC. Each PLC instance is subjected to malicious exploit test cases. The simulated PLC programs are then observed for input-output behavior. The behavior is characterized into formal Petri nets to facilitate analysis of the data and to allow for graphical and mathematical analysis of defined system events (Zurawski, 1994).

This research establishes four program types for each instance. The first two types of programs form two baselines for a PLC instance. The first baseline establishes the nominal ladder logic to execute a defined set of system processes. The second baseline alters the original baseline's ladder logic to protect against a known malicious exploit. The second pair of programs is formed when *attacks* alter the logic of the first two baselines. The formation of these four PLC programs forms the basis from which equivalent Petri nets are derived.

The method of characterizing a PLC program via a Petri net is by defining the inputs, outputs, and input-output interdependencies of the PLC program. The inputs of the PLC program characterize the transitions between observable process events. The outputs of the PLC program characterize the observable process events. The input-output interdependencies characterize the association between the transitions and observable process events. The resulting Petri nets allow for graphical and mathematical analysis of the emulated PLC instances. These results facilitate identification of metrics which are applicable to assessing resilience.

The Petri nets are created and simulated with PIPEv4.0 software. PIPEv4.0 allows for non-deterministic analysis of the Petri nets (Bonet, 2007). The results establish a set of tangible states and a reachability graph for each Petri net. The tangible states and graphs are combined into a matrix which lists the input-output behavior for each Petri net. Comparative analysis of the matrices provides several metrics that directly address, or indirectly support, the key aspects of resilience.

# **1.4** Assumptions/Limitations

In this research, the specific attack applied to the baseline program assumes knowledge of the original baseline program. Similarly, the protective baseline program utilizes knowledge of the attack. These assumptions lead to the creation of four distinctly defined program categories: (i) baseline, (ii) attack baseline, (iii) delta baseline, and (iv) attack delta baseline. This research does not focus on ladder logic programming, but rather seeks to identify measures for differentiating between programs of known quantities. By formulating known programs, the analysis is assured of presenting findings consistent with true input-output behavior for a PLC system under nominal, attack, and protected instances.

The Petri net's simulation software, PIPEv4.0, has limited expressive capabilities. Indeed, the drawing functions are limited to basic places, transitions, and arcs; however, the software performs sufficient simulations and analysis for the instances presented. A useful element not utilized in the experimentation is the presence of inhibitor arcs. Due to the lack of inhibitor arcs, some Petri nets illustrate transitions which have similar, yet unique, properties. For example, a transition labeled *10 to 8* signifies the same PLC input sequence as a transition labeled *10to8*; however, the next output state taken by the PLC is determined by the current place(s) which is enabling the transition *10 to 8* (also *10to8*). Note that a labeled transition (e.g., *10 to 8*) within a Petri net refers to the change in decimal value, from ten to eight, within the PLC's input module.

The assumptions, and limitation, do not alter the applicability of this research or the significance of its findings. Utilizing known programs as a basis for differentiating input-output behavior is necessary and sufficient for this research. Bonet compared PIPE to several other Petri net tools and preferred PIPE's interface and analysis modules (Bonet, 2007). The key analysis modules used are:

- GSPN analysis Checks for safeness and boundedness, and generates a tangible state table

- Reachability graph Checks for safeness and boundedness, and generates a graph of all possible firing sequences between reachable states

- Simulation Performs step-wise and fully automated simulation for a Petri net

Additionally, the Petri net modeling interface analysis fully captures the defined process requirements for each PLC instance. The appropriate enabling states for each transition are representative of the proposed PLC programs.

#### **1.5** Thesis Organization

Chapter 1 provides an introduction for this research. This includes the motivation for this research, research statement, research approach, assumptions, and the organization for this document.

Chapter 2 presents fundamental concepts and related work associated with this research. Background topics include SCADA, resilience, and Petri nets. Related work includes efforts related to SCADA security and resilience.

Chapter 3 describes the experimental methodology. First, a definition of the system boundaries is provided. Second, the factors and workload applied to the system are defined. Finally, details for characterizing the PLC instances into Petri nets and the method for performance evaluation are presented.

Chapter 4 provides the details for the results and analysis of the PLC instances. A corollary analysis of the resulting metrics is performed to identify statistically relevant observations. Then significant findings from the analysis of the metrics and their applicability toward resilience are discussed.

Chapter 5 reviews the key points of this research and provides recommendations for follow-on research. Finally, concluding remarks for this research are provided.

#### **II.** Literature Review

This chapter addresses fundamental concepts and related work. Section 2.1 details background topics in SCADA, resilience and Petri nets. Section 2.2 discusses several works closely related to SCADA security and resilience.

# 2.1 Background

The background topics relevant to this research include SCADA, resilience, and Petri nets. An overview of SCADA architecture is presented along with discussion on security vulnerabilities of associated subcomponents. Additionally, the definition of resilience is discussed, and Petri nets are discussed as a practical means of modeling processes.

### 2.1.1 Supervisory Control and Data Acquisition (SCADA)

SCADA systems provide an efficient means of monitoring and controlling processes across large geographical regions. SCADA systems are implemented in most modern industrial facilities, such as utilities and manufacturing. Approximately 90 percent of the nation's critical infrastructures are privately owned; a majority of these implementing SCADA as part of their enterprise network (Stouffer, 2008). Indeed, SCADA systems allow industries to streamline operating processes that cover vast geographical regions. To further enhance operating efficiency, industries have now integrated the SCADA system with their business enterprise networks (Stouffer, 2008).

# 2.1.1.1 Components of SCADA

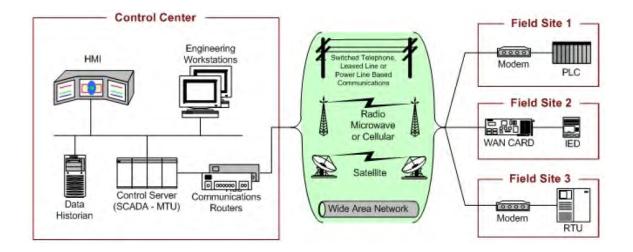

A SCADA system consists of a control center, communication links, and field sites (Figure 1) (Stouffer, 2008). The control center is comprised of the following:

- Human Machine Interface displays status of field sites in graphical form.

- Engineering Workstations allows for operator control of field sites.

- Data Historian storage and analysis of processed data.

- Control Server or Master Terminal Unit (MTU) operates SCADA functions, and processes data between control center and field sites.

Figure 1: SCADA Components (Stouffer, 2008)

Communication links, routers, and modems relay and convert signals for processing between field sites and the control center. Field sites consist of end-devices that collect data from various sensors (e.g., pressure, flow, or temperature) and transmit the appropriate data to the MTU. The end devices represented in Figure 1 include programmable logic controllers (PLC), intelligent electronic devices (IED), and remote terminal units (RTU) (Stouffer, 2008). These devices perform similar functions in that they locally control devices (e.g., motors, sensors, valves) and are able to communicate with the control center.

While PLCs and RTUs share similarities, they differ by their interaction to enddevices. RTUs may communicate with other processing units prior to control of an enddevice, while PLCs are directly linked to end-devices. PLCs are also more capable of tightly controlling sequential physical processes. The PLC replaces what traditionally were multiple solid state relays, switches, and mechanical timers; however, PLC's flexible programming facilitates configuration changes to physical process requirements.

### 2.1.1.2 SCADA Security Issues

SCADA systems are designed to provide cost effective control and data acquisition. Security was not initially a priority of SCADA design and development. However, in the past decade focus on SCADA security has grown due to both intentional (Table 1) and unintentional events (Table 2) (Stouffer, 2008) (Falliere, 2011). Non-intentional events have traditionally been addressed with redundant and fault tolerant architectures. Only recently has intentional consequences of malicious events drawn the attention of security experts in the SCADA domain.

| Name                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Worcester Air<br>Traffic<br>Communications | In March 1997, a teenager in Worcester, Massachusetts disabled part of the public switched telephone network using a dial-up modem connected to the system. This knocked out phone service at the control tower, airport security, the airport fire department, the weather service, and carriers that use the airport. Also, the tower's main radio transmitter and another transmitter that activates runway lights were shut down, as well as a printer that controllers use to monitor flight progress. The attack also knocked out phone service to 600 homes and businesses in the nearby town of Rutland (Thomas, 1998). |

| MAROOCHY<br>Shire Sewage Spill             | In the spring of 2000, a former employee of an Australian organization that develops manufacturing software applied for a job with the local government, but was rejected. Over a two-month period, the disgruntled rejected employee reportedly used a radio transmitter on as many as 46 occasions to remotely break into the controls of a sewage treatment system. He altered electronic data for particular sewerage pumping stations and caused malfunctions in their operations, ultimately releasing about 264,000 gallons of raw sewage into nearby rivers and parks (Smith, 2001).                                    |

| Stuxnet Siemens<br>Worm                    | Stuxnet is a threat targeting a specific industrial control system likely in Iran, such as a gas pipeline or power plant. The ultimate goal of Stuxnet is to sabotage that facility by reprogramming PLCs to operate as the attackers intend them to, most likely out of their specified boundaries. Stuxnet was discovered in July 2010, but is confirmed to have existed at least one year prior and likely even before. The majority of infections were found in Iran (Falliere, 2011).                                                                                                                                      |

#### Table 1: Intentional SCADA Incidents

The introduction of business enterprise networks to the SCADA domain has increased vulnerability to malicious attack. Injection points of attack can occur via the Internet, the enterprise network, internal workstations, or communication links between the control center and field sites (Stouffer, 2008). The end goal of a SCADA specific attack may include affecting the physical process by altering the end devices (e.g., motors, sensors, valves); such was the case with the Stuxnet worm. Stuxnet executed code on specific PLCs that caused physical damage to specific drive motors (Falliere, 2011). Stuxnet was not detected by SCADA operators due to a rootkit that masked the deviant behavior.

| Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSX Train<br>Signaling System | In August 2003, the Sobig computer virus was blamed for shutting down train signaling systems throughout the east coast of the U.S. The virus infected the computer system at CSX Corp.'s Jacksonville, Florida headquarters, shutting down signaling, dispatching, and other systems. According to Amtrak spokesman Dan Stessel, ten Amtrak trains were affected in the morning. Trains between Pittsburgh and Florence, South Carolina were halted because of dark signals, and one regional Amtrak train from Richmond, Virginia to Washington and New York was delayed for more than two hours. Long-distance trains were also delayed between four and six hours (Niland, 2003).                                                                                                    |

| Davis-Besse                   | In August 2003, the Nuclear Regulatory Commission confirmed that in January 2003, the Microsoft SQL Server worm known as Slammer infected a private computer network at the idled Davis-Besse nuclear power plant in Oak Harbor, Ohio, disabling a safety monitoring system for nearly five hours. In addition, the plant's process computer failed, and it took about six hours for it to become available again. Slammer reportedly also affected communications on the control networks of at least five other utilities by propagating so quickly that control system traffic was blocked (Poulsen, 2003).                                                                                                                                                                           |

| Northeast Power<br>Blackout   | In August 2003, failure of the alarm processor in First Energy's SCADA system prevented control room operators from having adequate situational awareness of critical operational changes to the electrical grid. Additionally, effective reliability oversight was prevented when the state estimator at the Midwest Independent System Operator failed due to incomplete information on topology changes, preventing contingency analysis. Several key 345kV transmission lines in Northern Ohio trip due to contact with trees. This eventually initiates cascading overloads of additional 345 kV and 138 kV lines, leading to an uncontrolled cascading failure of the grid. A total of 61,800 MW load was lost as 508 generating units at 265 power plants tripped (Minkel, 2008). |

| Zotob Worm                    | In August 2005, a round of Internet worm infections knocked 13 of DaimlerChrysler's U.S. automobile manufacturing plants offline for almost an hour; stranding workers as infected Microsoft Windows systems were patched. Plants in Illinois, Indiana, Wisconsin, Ohio, Delaware, and Michigan were knocked offline. While the worm affected primarily Windows 2000 systems, it also affected some early versions of Windows XP. Symptoms include the repeated shutdown and rebooting of a computer. Zotob and its variations caused computer outages at heavy-equipment maker Caterpillar Inc., aircraft-maker Boeing, and several large U.S. news organizations (Roberts, 2005).                                                                                                      |

# Table 2: Non-Intentional SCADA Incidents

### 2.1.2 Resilience Overview

In general terms, resilience is the ability of a system to continue to operate through disruptions. This notion encompasses a multitude of other terms such as robustness, dependability, and survivability. These characteristics are important to the protection and healing of a system. This section surveys various resilience models from other domains for applicability to SCADA systems (e.g., PLCs).

#### 2.1.2.1 Defining Resilience

Resilience has been researched in other domains in which biological, psychological and community resilient models have been formulated. Biological resilience presents itself in the study of immune systems (VanBreda, 2001). Psychological resilience has been studied in the mental capacity for individuals to perform through adversity (VanBreda, 2001). Community and organizational resilience is demonstrated through the ability of a group or region to recover from catastrophic events (Tierney, 2007; Cutter, 2008). In each of these domains, a common structure of resilience is presented. For example, the components of psychological resilience can be categorized into the following three parts (VanBreda, 2001):

- Inner Self Mechanism monitoring your physical, meditative, and mental awareness

- Relationship Mechanism monitoring the taking and giving awareness as well as your self-relationship

- Method monitoring your habits

This structure of resilience incorporate self awareness and self monitoring mechanisms from the psychological domain in order to initiate the actions required to maintain functional capacity and ability to recover.

Similarly, Tierney (2007) presents resilience in a community or organization as:

- Robustness the ability of systems, system elements, and other units of analysis to withstand disaster forces without significant degradation or loss of performance

- Redundancy the extent to which systems, system elements, or other units are substitutable, that is, capable of satisfying functional requirements, if significant degradation or loss of functionality occurs

- Resourcefulness the ability to diagnose and prioritize problems and to initiate solutions by identifying and mobilizing material, monetary, informational, technological, and human resources

- Rapidity the capacity to restore functionality in a timely way, containing losses and avoiding disruptions

Trivedi (2009) states that while qualitative descriptions of resilience across domains have been accomplished, applicable quantitative measures are still deficient. This statement is particularly applicable to computer systems. His work attempts to quantify metrics that compare availability, performance, and survivability for computer systems (Trivedi, 2009). Similarly, quantifying resilience of SCADA systems is necessary to measure their ability to perform when perturbations or disruptions to the system occur.

#### 2.1.2.2 Resilience Framework

While there are numerous definitions of resilience across various domains, The

National Infrastructure Advisory Council (NIAC) provides perhaps the most fitting

definition with respect to SCADA. NIAC (2009) define infrastructure resilience as:

"the ability to reduce the magnitude and/or duration of disruptive events. The effectiveness of a resilient infrastructure or enterprise depends upon its ability to anticipate, absorb, adapt to, and/or rapidly recover from a potentially disruptive event." (p. 8)

This definition provides a framework for resilience according to the following

four characteristics:

- 1. The ability to anticipate a potentially disruptive event requires that the system has a self awareness of its baseline and is able to monitor its current state.

- 2. The ability to absorb potentially disruptive events requires that the system has mechanisms in place to minimize the amount, if any, of performance loss.

- 3. The ability to adapt requires that the system have contingencies available that allow for flexible system adjustments to maintain operational availability.

- 4. The ability to recover from a disruptive event requires mechanisms (either automated or manual processes) which allow the system to perform up to its baseline.

### 2.1.3 Petri Nets Overview

Petri nets are named after its creator Carl A. Petri in 1962 (Zurawski, 1994).

Initial development in 1962 concentrated on the study of communication via automata.

Zurawski and Zhou provide a simple definition (Zurawski, 1994):

"Petri nets as, graphical and mathematical tools, provide a uniform environment for modeling, formal analysis, and design of discrete event systems." (p. 567) In its graphical form, Petri nets consist of four basic parts: (i) places, (ii) transitions, (iii) arcs, and (iv) tokens. The places and transitions are indicative of nodes within a graph and arcs relate to pairs of places and transitions. The tokens represent places which are active (marked). Table 3 lists examples of places and transitions.

| Places              | Transitions        |

|---------------------|--------------------|

| pre/post condition  | event              |

| input/output data   | computational step |

| input/output signal | signal processor   |

| resources           | tasking            |

| buffer              | processor          |

Table 3: Examples of Petri Net Places and Transitions (Abhishek, 2005)

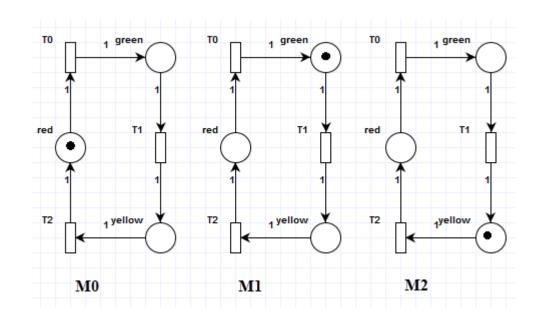

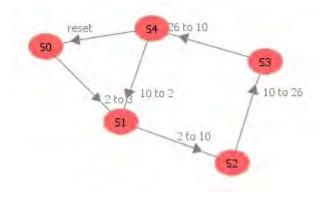

#### 2.1.3.1 Simple Petri Net Example

Figure 2 illustrates three markings of a Petri net modeling a simple traffic light, with one light for red, yellow, and green (Abhishek, 2005). Places are represented by circles, transitions as blocks (or bars), arcs as directed arrows, and tokens as dots. The initial marked graph ( $M_0$ ) shows that a token is active in the red place, which is interpreted as the red light being active (or illuminated). Note that there is only one token in the red place of the initial marked graph ( $M_0$ ) to emphasize that only one red light exists for this example. The presence of multiple tokens in one place may be interpreted as the existence of more than one red light in the system.

The basic rules for transitioning a Petri net from one marked graph  $(M_0)$  to the next  $(M_1)$  involves the action of the transitions (Peterson, 1977). The execution of a transition is called firing. In order for a transition to fire, the transition must be enabled.

A transition is enabled, and may fire, if all its input places contain at least one token. Note that even though a transition is enabled, it is not strictly required to fire. The firing of a transition results in moving a token from the input places to all output places. In the traffic light example, all transitions have only one input and output place, so it is easily shown that the number of tokens in the Petri net remain unchanged (at one). Figure 2 shows all possible states of the Petri net (based on the initial state of M<sub>0</sub> with one token). The sequence of places is limited to one light (red, green, or yellow) illuminated in any specific instance, and limited to one repeating sequence ( $R \rightarrow G \rightarrow Y$ ).

Figure 2: Example Traffic Light Petri Net

#### 2.1.3.2 Formal Definition of a Petri Net

A Petri net *C* consists of four subsets,  $C = \{P, T, I, O\}$ , such that *P* is a set of places, *T* is a set of transitions, *I* is a set of input functions for each transition, and *O* is a

set of output functions for each transition (Peterson, 1981). The formal definition for the traffic light example in Figure 2 is represented as:

- $C = \{P, T, I, O\}$

- $P = \{red, green, yellow\}$

- $T = \{T0, T1, T2\}$

- $I(T0) = {red}, I(T1) = {green}, I(T2) = {yellow}$

- $O(T0) = \{green\}, O(T1) = \{yellow\}, O(T2) = \{red\}$

### 2.1.3.3 Petri nets in Application

Petri nets have been applied to modeling of performance, reliability, fault recovery, and fault tolerance in various systems such as operating systems, queues, traffic control and mathematics (Peterson, 1981). Additionally, modeling of manufacturing processes similar to SCADA applications have also been analyzed (Zurawski, 1994). However, the analysis of these systems focuses primarily on fault tolerance and reliability within the systems' designs. Utilizing Petri nets to analyze systems for intentional exploits (e.g., malware) is significant to increasing the security posture of SCADA systems.

Properties of Petri nets that are practical for analysis of SCADA applications are concurrency, safeness and boundedness (Peterson, 1977). Concurrency allows for the modeling of parallel processes that occur between the multiple devices that interact in a SCADA system. Safeness and boundedness addresses the potential issue of state explosion when analyzing a system. Safeness implies no more than one token may be present in each place of a Petri net. It follows that if a Petri net is safe, then it is also bounded. This results in a finite set of reachable markings since tokens are not created without bound. These properties well suit the defined configuration and deterministic interdependencies present in SCADA systems. Properly defining places and transitions for a Petri net based on SCADA system processes should result in a finite set of states.

### 2.2 Related Work

The related works section examines analysis and resiliency concepts relating to SCADA security. Queiroz (2010) and Germanus (2010) present individual models for SCADA security analysis at a macro-level, while Shah (2008) explores SCADA security protocol at a micro-level. Wei (2009) provides an exploratory analysis of resilience metrics that may be utilized to assess industrial control systems.

### 2.2.1 Survivable SCADA Systems

Queiroz (2010) presents a model to quantify SCADA system performance against a denial of service (DoS) attack. The model focuses on the interplay of four main components of a SCADA system: RTU, MTU, HMI Server, and Data Historian. The availability of each component is modeled as queues that allow each service to handle a specific number of requests. The aggregate output of each component's availability is compiled into a Bayesian table, which incorporates the interdependencies, and then quantifies the survivability of the SCADA system. Figure 3 provides a summary for two sets of sample data. The thresholds for each of the SCADA components (i.e., normal, degraded, unavailable) and survivability (i.e., yes, no) for the system is pre-determined prior to model analysis.

| RTU      | MTU    | HMI<br>Server | Historian<br>Database | Survivable |

|----------|--------|---------------|-----------------------|------------|

| Normal   | Normal | Normal        | Normal                | YES        |

| Degraded | Normal | Unavailable   | Degraded              | NO         |

|          |        |               |                       |            |

Figure 3: Queiroz's Summary for Sample Data (Queiroz, 2010)

Quieroz's research contributes to part two of the previously defined resilience framework (i.e., the ability to absorb potentially disruptive events requires that the system has mechanisms in place to minimize the amount, if any, of performance loss). Interdependencies of a particular SCADA system may be analyzed to determine if the architecture is survivable against a DoS attack. The result of the analysis can be used to improve the absorptive capacity for the SCADA system. Quieroz's approach is sufficient for system wide analysis of a SCADA system and the timing interdependencies between network nodes. However, it does not account for hardware or software faults. They assume that each node itself is not prone to failure; only that the communication between the nodes is interrupted which causes degradation of node availability, and subsequently system survivability.

The Quieroz (2010) approach ignores traditional fault tolerance or the presence of malware. Hardware faults are traditionally classified in the domain of fault tolerance, while software faults may include malware exploits such as Stuxnet. Additionally,

Quieroz's contribution towards resilience resides at the macro level of the SCADA system. No observations are made to determine the specific behavior of one particular node. This approach does not address part one of the resilience framework (i.e., the ability to anticipate a potentially disruptive event requires that the system has a self awareness of its baseline and is able monitor its current state) and lacks the sensitivity to detect malware. While the model works well in determining susceptibility to DoS attacks and improving a SCADA system's absorptive capacity, it is insufficient in monitoring the current state of the SCADA system to aid real-time monitoring of system behavior at a micro-level (e.g., end-device control via PLC).

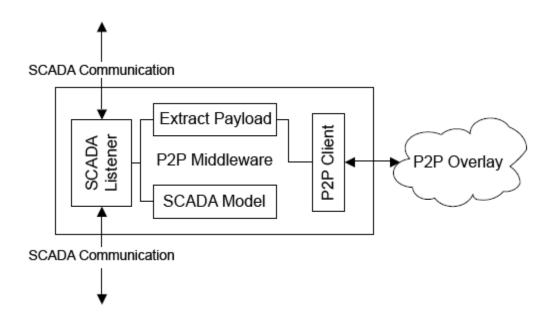

## 2.2.2 Redundant SCADA Network Architecture

Germanus (2010) presents a model in which communication between the RTU and MTU is performed via redundant links throughout the SCADA system. The model implements the redundant paths as middleware that are assumed to be free from security vulnerabilities. This model may improve the SCADA system's resilience against DoS and man-in-the-middle (MITM) attacks. DoS attacks may be mitigated by using the redundant paths available on the network links. MITM attacks may be mitigated by the data integrity checks associated with the middleware. Figure 4 illustrates the middleware model that passively extracts SCADA communication and relays it across the peer-topeer (P2P) overlay.

Figure 4: Germanus' Middleware Building Blocks (Germanus, 2010)

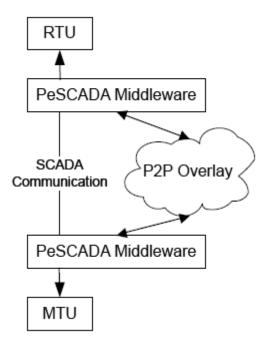

The advantages to this model are flexibility, interoperability, and minimal intrusiveness. The flexibility allows the system to withstand link failures which addresses part two of the resilience framework (i.e., the ability to absorb potentially disruptive events requires that the system has mechanisms in place to minimize the amount, if any, of performance loss). Figure 5 illustrates the interoperability and minimal intrusiveness of Germanus' model which facilitates deployment of the model to existing SCADA systems since the P2P overlay uses middleware as an interface between existing RTU and MTU links (Germanus, 2010).

Figure 5: Germanus' (2010) Redundant P2P Model

The model expands on Quieroz's research contribution to SCADA resilience in two ways. First, it can be implemented real-time on existing SCADA system infrastructure. Second, the redundant network paths provide increased node availability, and therefore increase survivability of the SCADA system.

Similar to Quieroz's research, Germanus' analysis resides at the macro-level of the SCADA system. Detection of hardware and software faults local to either the RTU or MTU is undetected since it is isolated to the SCADA system's communication links. Local behavior of any particular RTU is still only monitored through the HMI. However, the P2P overlay is able to provide real-time feedback of link or message abnormalities and partially addresses part one of the resilience framework since it will detect systemic behavior.

#### 2.2.3 Mechanisms to Provide Integrity in SCADA Devices

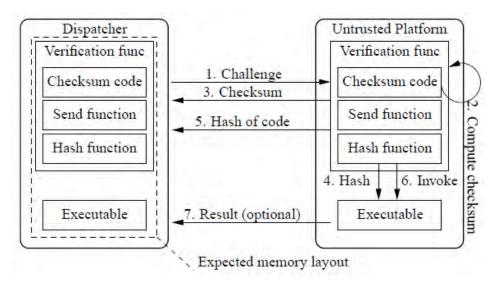

Shah (2008) presents a method to verify the executable code of a PLC. The method implements a challenge-response protocol between the PLC and an external dispatcher. A verification function resides on both the PLC and dispatcher. Figure 6 summarizes the steps of the verification protocol. Steps one through three assures that the verification function is trustworthy, while steps four and five assure that the executable code of the PLC is untampered (Shah, 2008). Steps one through five of Shah's challenge-response protocol is as follows:

- 1. The dispatcher sends a random challenge to the PLC.

- 2. The verification function of the PLC computes a checksum.

- 3. PLC returns the results to the dispatcher.

- 4. Verification function of the PLC creates a hash of the executable code.

- 5. PLC sends the hash result to the dispatcher which compares it against the known hash.

Figure 6: Shah's (2008) Verification Function Overview

This method of verifying executable code on the PLC approaches SCADA resilience from the local node level as opposed to the system-level approaches of Quieroz and Germanus. Shah's method addresses the first part of the resilience framework (i.e., the ability to anticipate a potentially disruptive event requires that the system has a self awareness of its baseline and is able monitor its current state) since it is able to detect changes to the executable code on the PLC. It also provides flexibility since it may be implemented in existing PLCs currently deployed in the field; however, it requires that the verification function be integrated with the PLC.

Shah's method incurs several logistical issues. The paper acknowledges that the verification functions of the PLC and dispatcher are different for each PLC manufacturer (Shah, 2008). While the challenge-response protocol is general across platforms, the verification functions differ based on the PLC architecture. Another logistical issue is that the PLC must be taken off-line to perform the challenge-response protocol between the dispatcher and PLC. This presents operational impacts to most SCADA systems since most PLCs run real-time applications.

Shah (2008) also acknowledges that the verification process only assures that no malicious code is present at the time the verification function is performed between the dispatcher and PLC. It does not prevent timed attacks in which the adversary may execute malicious code on the PLC between verification timelines. Additionally, the method does not address the second part of the resilience framework (i.e., the ability to absorb potentially disruptive events requires that the system has mechanisms in place to minimize the amount, if any, of performance loss) since no processes are in place to reduce the effect of malicious code once detected.

### 2.2.4 Resilient ICS: Concepts, Formulation, Metrics, and Insights

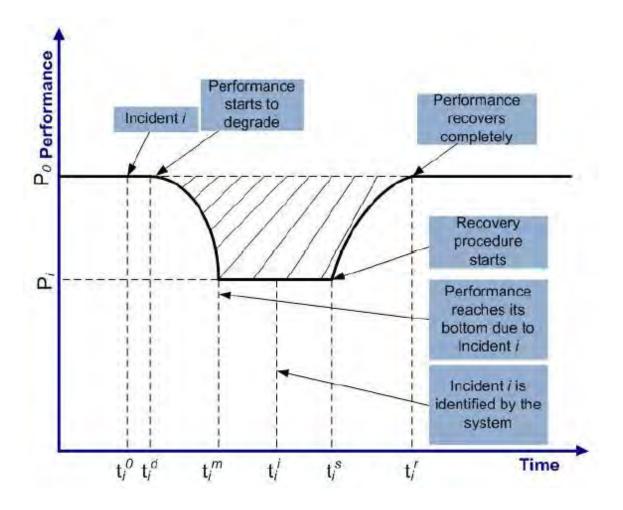

Industrial control systems (ICS) are deployed in sectors such as agriculture, utilities, and transportation. Wei (2009) presents a set of resilience metrics that may be used to quantify performance of a system. Figure 7 identifies the trigger points for a resilient system across a timeline. The trigger points are utilized to define equations for protection time, degradation time, identification time, recovery time, performance degradation, performance loss, total loss, and overall potential critical loss.

Figure 7: Wei's Resilience Curve (Wei, 2009)

Subsets of the defined equations that apply to the first and second parts of the resilience framework are (Wei, 2009):

- Protection time time that the system tolerates an incident without degradation

- Degradation time time that the system incurs to reach its minimum performance level

- Identification time time from incident occurrence to system identification

- Performance degradation difference between baseline performance and degraded performance due to incident

The four definitions presented by Wei address the detection of the incident and the level of mitigation the system performs. These definitions, or slight variations of them, may aid in analyzing various models that seek to improve resilience in SCADA systems.

# 2.3 Summary of Literature

This chapter presented the relevant background and related works associated with quantifying resiliency of PLCs through the use of Petri nets. Knowledge of SCADA architecture and security vulnerabilities is a foundational element. A formal definition of resilience and Petri nets is also relevant to key areas of Chapters 3 and 4 of this research. The various SCADA security analysis techniques presented at both the macro and micro-levels provide a basis of comparison for the proposed methodology of Chapter 3. The related work on resilient metrics for ICS is insightful to the hypothesis of this research and gives relevance to findings in Chapter 4.

### **III.** Methodology

This chapter presents the methodology for characterizing the PLC ladder logic programs into equivalent Petri nets for evaluating metrics to assess resilience. Section 3.1 describes the goal and hypothesis for this research. Section 3.2 identifies the system boundaries. Section 3.3 describes the system services. Section 3.4 lists the parameters of the system. Section 3.5 defines the factors that apply to the system. Section 3.6 describes the workload applied to the system. Section 3.7 details the approach for characterizing the ladder logic into equivalent Petri nets. Section 3.8 identifies the performance metrics derived from the experimentation. Section 3.9 describes the evaluation method used to form resilience metrics. Section 3.10 outlines the experimental design.

## **3.1 Problem Definition**

Improving the resilience of ICS allows critical infrastructures to withstand degrading events, and recover to a nominal functional capability within an acceptable period. However, determining resilience requires that a system's susceptibility to degradation and capability to recover is quantifiable. Narrowing the scope of research to a micro-level component of a SCADA system provides a basis to facilitate evaluation of potential resilience metrics.

#### 3.1.1 Goal

The primary goal of this research is to identify metrics that may assess a PLCs performance with respect to the resilience framework presented in Chapter 2. A

complimentary goal is to identify metrics that are applicable to real-time physical mechanisms. The resilience curve (Figure 7) identifies trigger points that are utilized in evaluating resilience performance; however, the *mechanisms* for the triggers are absent. Achieving both research goals may result in applicable mechanisms which appropriately assess resilience in controlled (e.g., benchmark) and real-time (e.g., operations) environments. This research may reveal comparative metrics that help determine if awareness of the system state is discernible. Self-awareness is a foundational characteristic of the resilient framework and provides a basis for tangible mechanisms to implement trigger points in real-time hardware protection schemes.

### 3.1.2 Hypothesis

The hypothesis of this research is that a PLC's ability to identify and absorb malicious alterations is quantifiable by monitoring system outputs in response to system inputs. The approach to derive the metrics for resilience assessment uses comparative analysis of various instances of PLC programs.

# 3.2 System Boundaries

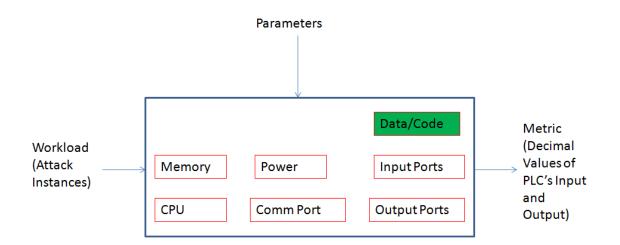

The system under test (SUT) is the PLC processes. Figure 8 illustrates the SUT and associated inputs and outputs. The workload applied to the SUT includes various attack instances as detailed in *Section 3.6*. The parameters applied to the SUT are primarily fixed attributes of the PLC emulation provided by LogixPro<sup>®</sup> 500; the varying parameter during experimentation is the protection scheme applied to each specific PLC

instance. The metric produced from the SUT is the decimal input and output values produced during program execution.

Figure 8: PLC SUT Diagram

System components that comprise the PLC include: Memory, Data/Code, CPU, Input Ports, Output Ports, Power Supply, and Communication Port. The component under test (CUT) is the data/code or programming logic of the system. Data/code is programmed in ladder logic from a laptop with the accompanying LogixPro<sup>®</sup> 500 software package associated with the PLC. The program is loaded to the PLC which executes the ladder logic and produces observable output signals in response to input signals.

# 3.3 System Services

A PLC provides four primary services: (i) execution of the ladder logic program, (ii) monitoring of input signals, (iii) production of output signals, and (iv) providing data back to the master device of a SCADA system. It is assumed that accurate data are transmitted to the master device (i.e., no spoofing of output states), and that input signals are only injected at valid input ports (i.e., no spoofing of input states). It is also assumed that the programs (i.e., baseline and enumerated versions) are not subject to hardware faults or undesired software faults. These assumptions isolate the boundary of the system from external influences, and assure the integrity of the applied inputs and observed outputs.

The primary services monitored are the applied inputs and the behavior of the outputs. The observed PLC output signals are a direct result of the PLC program code execution and the input signal status. Applying inputs to the PLC produces output signal states that affect the end-devices (e.g., motors, lights, actuators). These behavioral responses of the output states in response to the input states are measurable in the observed status of the end-devices. The PLC's interaction with the end-devices fall into one of three observable response categories:

- Valid Nominal input results in nominal output processes

- Degraded Nominal input results in deviant but safe output processes. A safe outcome is defined as a non-nominal output response in which the system's interactions with end-devices do not cause catastrophic losses (e.g., minor perturbations)