University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2019

# Simulation, Analysis, and Optimization of Heterogeneous CPU-GPU Systems

Christopher Giles University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Giles, Christopher, "Simulation, Analysis, and Optimization of Heterogeneous CPU-GPU Systems" (2019). *Electronic Theses and Dissertations, 2004-2019.* 6710. https://stars.library.ucf.edu/etd/6710

### SIMULATION, ANALYSIS, AND OPTIMIZATION OF HETEROGENEOUS CPU-GPU SYSTEMS

by

## CHRISTOPHER EDWARD GILES B.S. University of Central Florida, 2007 M.S. University of Central Florida, 2011

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2019

Major Professor: Mark Heinrich

© 2019 Christopher Edward Giles

## ABSTRACT

With the computing industry's recent adoption of the Heterogeneous System Architecture (HSA) standard, we have seen a rapid change in heterogeneous CPU-GPU processor designs. State-ofthe-art heterogeneous CPU-GPU processors tightly integrate multicore CPUs and multi-compute unit GPUs together on a single die. This brings the MIMD processing capabilities of the CPU and the SIMD processing capabilities of the GPU together into a single cohesive package with new HSA features comprising better programmability, coherency between the CPU and GPU, shared Last Level Cache (LLC), and shared virtual memory address spaces. These advancements can potentially bring marked gains in heterogeneous processor performance and have piqued the interest of researchers who wish to unlock these potential performance gains. Therefore, in this dissertation I explore the heterogeneous CPU-GPU processor and application design space with the goal of answering interesting research questions, such as, (1) what are the architectural design trade-offs in heterogeneous CPU-GPU processors and (2) how do we best maximize heterogeneous CPU-GPU application performance on a given system. To enable my exploration of the heterogeneous CPU-GPU design space, I introduce a novel discrete event-driven simulation library called KnightSim and a novel computer architectural simulator called M2S-CGM. M2S-CGM includes all of the simulation elements necessary to simulate coherent execution between a CPU and GPU with shared LLC and shared virtual memory address spaces. I then utilize M2S-CGM for the conduct of three architectural studies. First, I study the architectural effects of shared LLC and CPU-GPU coherence on the overall performance of non-collaborative GPU-only applications. Second, I profile and analyze a set of collaborative CPU-GPU applications to determine how to best optimize them for maximum collaborative performance. Third, I study the impact of varying four key architectural parameters on collaborative CPU-GPU performance by varying GPU compute unit coalesce size, GPU to memory controller bandwidth, GPU frequency, and system wide switching fabric latency.

This dissertation is dedicated to my wife and children. Without your endless love and support, my research and this dissertation would not have been possible.

### ACKNOWLEDGMENTS

First and foremost, I would like to thank Dr. Mark Heinrich who guided me through my academic activities and served as my principal advisor and mentor for many years. Dr. Heinrich's tireless advisement over the years has enabled me to improve upon my research greatly and made the authoring of this dissertation possible. I consider myself truly blessed to have had the opportunity to work with Dr. Heinrich. Second, I would like to thank the members of my dissertation committee Dr. Mark Heinrich, Dr. Rickard Ewetz, Dr. Mingjie Lin, Dr. Sumanta Pattanaik, and Dr. Elena Flitsiyan for their invaluable insight and direction towards my research and the finalization of this dissertation. Third, I would like to thank my fellow laboratory cohorts Christina Peterson, Ramin Izadpanah, Anahita Davoudi, Osama Tameemi, and Pierre LaBorde for their continuous help and encouragement, through thick and thin, and for making the journey fun. Fourth, I would like to thank my Mom and Dad whose enduring patience and resolute support over my life is the greatest gift anyone has ever given me. Thanks Mom and Dad! Finally, I would like to thank the United States Department of the Navy and the Science, Mathematics, and Research for Transformation (SMART) Scholarship program committee. As a SMART Scholarship recipient, I was provided the opportunity to pursue the degree of Doctor of Philosophy while maintaining a positive work and family life balance. Receiving the SMART Scholarship was a defining moment for me and propelled me towards graduation. Thank you for this opportunity and for your confidence in selecting me as a SMART recipient.

# TABLE OF CONTENTS

| LIST OF FIGURES                                           | ĸi |

|-----------------------------------------------------------|----|

| LIST OF TABLES                                            | v  |

| LIST OF ALGORITHMS                                        | V  |

| CHAPTER 1: INTRODUCTION                                   | 1  |

| 1.1 Research Contributions                                | 4  |

| 1.2 Dissertation Organization                             | 6  |

| CHAPTER 2: DISCRETE EVENT-DRIVEN SIMULATION METHODOLOGIES | 7  |

| 2.1 Background and Motivation                             | 7  |

| 2.2 KnightSim Implementation Methodology                  | 9  |

| 2.2.1 Events as KnightSim Contexts                        | 0  |

| 2.2.2 Initialization                                      | 2  |

| 2.2.3 Scheduling                                          | 4  |

| 2.3 KnightSim Modeling Methodology                        | 7  |

| 2.3.1 Switching Fabric Implementation Methodology         | 9  |

|      | 2.3.2   | Power Simulation Methodology                      | 22 |

|------|---------|---------------------------------------------------|----|

| 2.4  | Paralle | l KnightSim Implementation Methodology            | 23 |

| 2.5  | Paralle | l KnightSim Modeling Methodology                  | 25 |

|      | 2.5.1   | Data Hazards                                      | 26 |

| 2.6  | Knight  | Sim and Parallel KnightSim Performance Results    | 27 |

|      | 2.6.1   | Experimental Setup                                | 28 |

|      | 2.6.2   | Experiment 1: Determining Event Engine Usage      | 29 |

|      | 2.6.3   | Experiment 2: Single-Threaded Performance Results | 30 |

|      | 2.6.4   | Experiment 3: Multithreaded Performance Results   | 32 |

| 2.7  | Summa   | ary and Conclusions                               | 35 |

| CHAP | TER 3:  | HETEROGENEOUS CPU-GPU SYSTEM SIMULATION           | 37 |

| 3.1  | Backgr  | round and Motivation                              | 38 |

| 3.2  | M2S-C   | GM Implementation Methodology                     | 41 |

|      | 3.2.1   | x86 System Emulation                              | 41 |

|      | 3.2.2   | x86 CPU Timing Model                              | 44 |

|      | 3.2.3   | Southern Islands GPU System Emulation             | 46 |

|      | 3.2.4   | Southern Islands GPU Timing Model                 | 48 |

|     | 3.2.5 | Memory System Timing Models |                                                              | 51 |

|-----|-------|-----------------------------|--------------------------------------------------------------|----|

|     |       | 3.2.5.1                     | Cache Timing Model                                           | 53 |

|     |       | 3.2.5.2                     | Switch Timing Model                                          | 58 |

|     |       | 3.2.5.3                     | GPU Hub Timing Model                                         | 62 |

|     |       | 3.2.5.4                     | System Agent, Memory Controller, and SDRAM Timing Models     | 62 |

|     | 3.2.6 | Memory                      | System Coherence Protocols                                   | 64 |

|     |       | 3.2.6.1                     | CPU L1 Instruction and Data Cache MESI Protocol State Tables | 66 |

|     |       | 3.2.6.2                     | CPU L2 Cache MESI Protocol State Table                       | 68 |

|     |       | 3.2.6.3                     | CPU L3 Cache MESI Protocol State Table                       | 71 |

|     |       | 3.2.6.4                     | GPU L1 Vector and L2 Cache MESI Protocol State Tables        | 77 |

|     | 3.2.7 | Virtual N                   | Iemory System                                                | 82 |

| 3.3 | M2S-C | CGM Benc                    | hmarks                                                       | 85 |

|     | 3.3.1 | Benchma                     | ark Set 1: OpenMP and Non-Collaborative GPU-Only OpenCL      |    |

|     |       | Benchma                     | arks                                                         | 85 |

|     | 3.3.2 | Benchma                     | ark Set 2: Collaborative CPU-GPU OpenCL Benchmarks           | 85 |

|     |       | 3.3.2.1                     | Backpropagation                                              | 86 |

|     |       | 3.3.2.2                     | Block Matrix Multiply                                        | 87 |

|     |       | 3.3.2.3                     | Edge Detection                                               | 87 |

|      | 3.3.2.4          | K-Nearest Neighbor                                          | 8  |

|------|------------------|-------------------------------------------------------------|----|

|      | 3.3.2.5          | Write                                                       | 8  |

| 3.4  | M2S-CGM Valid    | dation Results                                              | :9 |

|      | 3.4.1 Experim    | ental Setup                                                 | 9  |

|      | 3.4.2 Experim    | ent 1: CPU OpenMP Parallel Performance Results 9            | 0  |

|      | 3.4.3 Experim    | ent 2: CPU-GPU OpenCL Parallel Performance Results 9        | 1  |

| 3.5  | Summary and Co   | onclusions                                                  | 2  |

| CHAF |                  | OGENEOUS CPU-GPU SYSTEM ARCHITECTURAL EXPERI-               | )4 |

| 4.1  | Background and   | Motivation                                                  | 15 |

| 4.2  | Coherent Hetero  | ogeneous CPU-GPU System Implementation Methodology 9        | 8  |

| 4.3  | Study 1: Archite | ectural Affects of Shared LLC and CPU-GPU Coherence On Non- |    |

|      | Collaborative GI | PU-Only Execution Performance                               | 13 |

|      | 4.3.1 Experim    | nental Setup                                                | )4 |

|      | 4.3.2 Experim    | ental Results                                               | )4 |

| 4.4  | Study 2: Optimiz | zing Collaborative CPU-GPU Execution Performance 10         | )6 |

|      | 4.4.1 Experim    | nental Setup                                                | 17 |

|      | 4.4.2 Experim    | nental Results                                              | )9 |

| 4.5    | Study 3: Future Architectural Impacts to Collaborative CPU-GPU Execution 11  | 5 |

|--------|------------------------------------------------------------------------------|---|

|        | 4.5.1 Experimental Setup                                                     | 5 |

|        | 4.5.2 Experimental Results                                                   | 6 |

| 4.6    | Experimental Observations                                                    | 2 |

| 4.7    | Summary and Conclusions                                                      | 3 |

| CHAP   | TER 5: RELATED WORK                                                          | 5 |

| 5.1    | Related Work in Sequential Discrete Event-Driven Simulation Methodologies 12 | 5 |

| 5.2    | Related Work in Parallel Discrete Event-Driven Simulation Methodologies 12   | 7 |

| 5.3    | Related Work in Computer Architectural Simulation Systems and Heterogeneous  |   |

|        | CPU-GPU benchmarks                                                           | 8 |

| 5.4    | Related Work in Heterogeneous CPU-GPU Architectural Studies                  | 9 |

| CHAP   | ER 6: CONCLUSIONS AND FUTURE WORK                                            | 3 |

| 6.1    | Future Work                                                                  | 4 |

| APPEN  | DIX: SETJMP AND LONGJMP ASSEMBLY ROUTINES                                    | 6 |

| LIST C | F REFERENCES                                                                 | 9 |

# **LIST OF FIGURES**

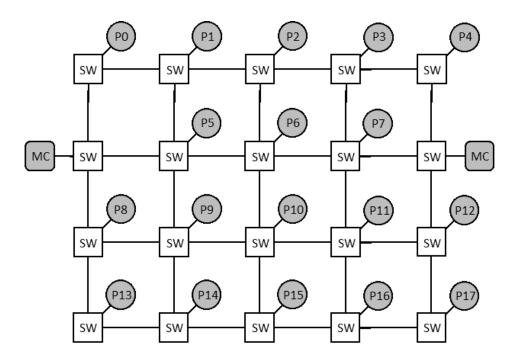

| Figure 2.1: An 18 Core CPU Computer Architectural Model                     | 18 |

|-----------------------------------------------------------------------------|----|

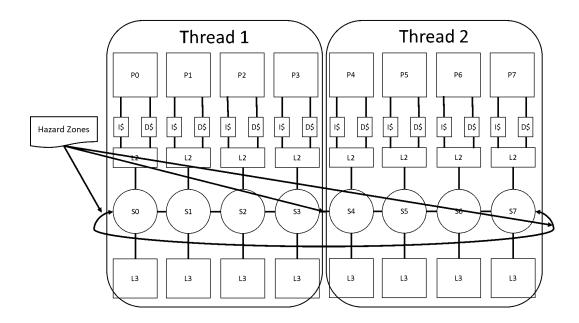

| Figure 2.2: Parallel KnightSim Hazard Zones                                 | 26 |

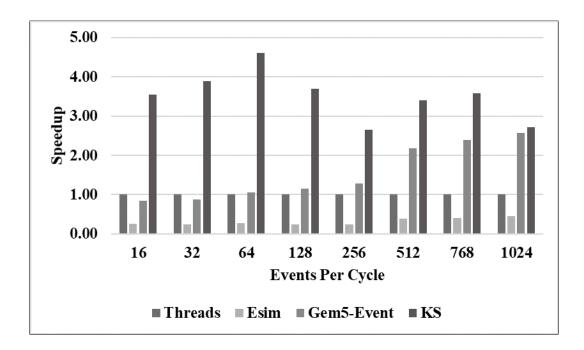

| Figure 2.3: Single Threaded Performance Results                             | 32 |

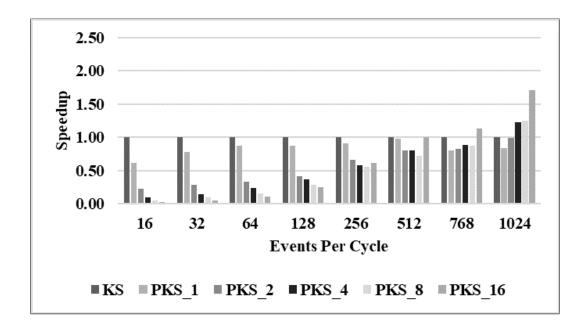

| Figure 2.4: Multithreaded Performance Results Without Work                  | 33 |

| Figure 2.5: Multithreaded Performance Results With Work                     | 34 |

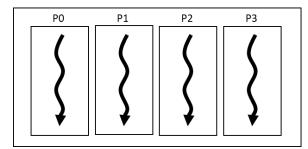

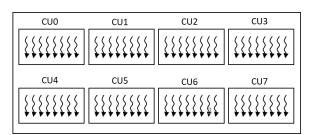

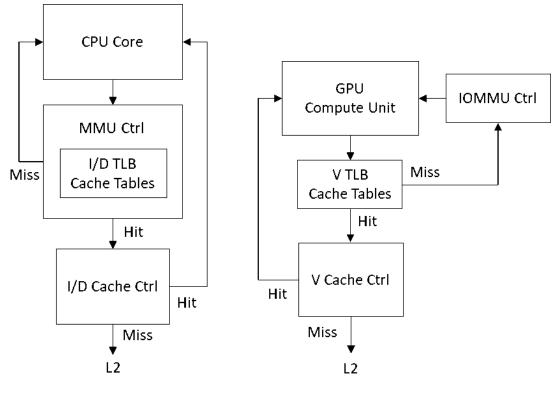

| Figure 3.1: CPU and GPU Architectural Differences                           | 38 |

| Figure 3.2: Simulated Heterogeneous System Node Architectural Block Diagram | 39 |

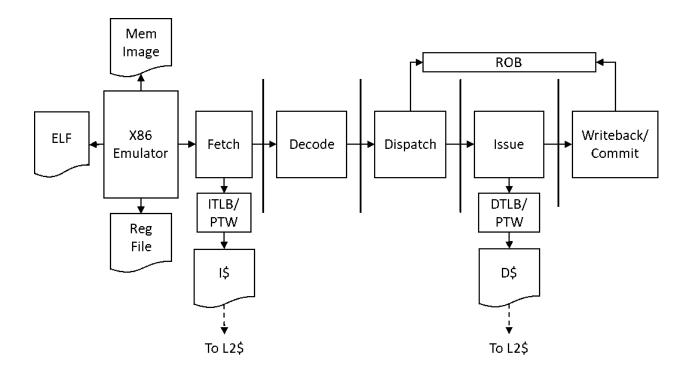

| Figure 3.3: Simulated CPU Implementation Approach                           | 42 |

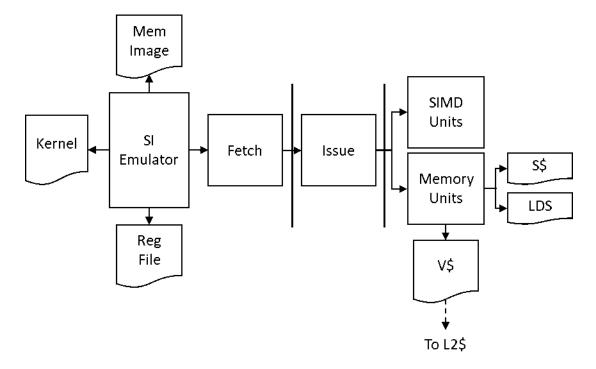

| Figure 3.4: Simulated GPU Implementation Approach                           | 47 |

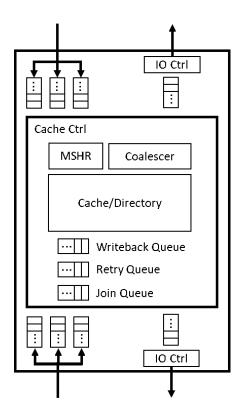

| Figure 3.5: Cache Architecture                                              | 54 |

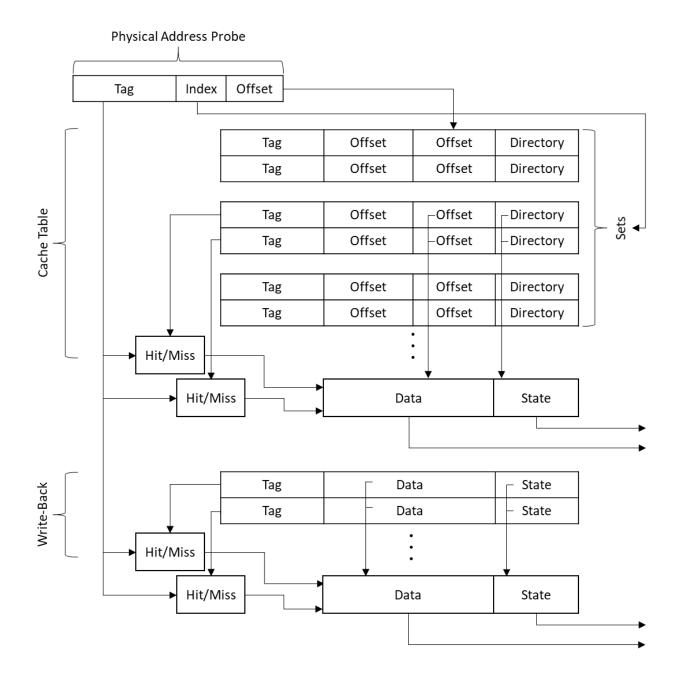

| Figure 3.6: Architecture of a Two Way Set Associative Cache With Write-Back | 57 |

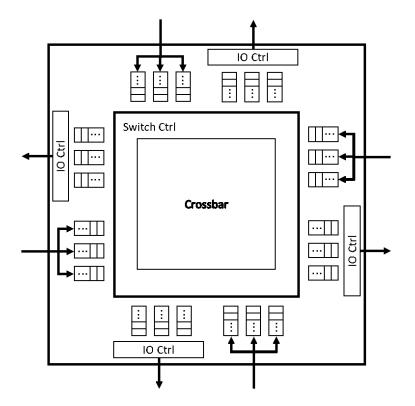

| Figure 3.7: Switch Architecture                                             | 59 |

| Figure 3.8: Switch Crossbar Architecture                                    | 60 |

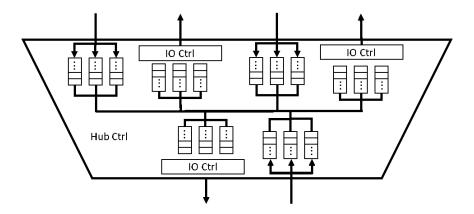

| Figure 3.9: GPU HUB Architecture                                            | 61 |

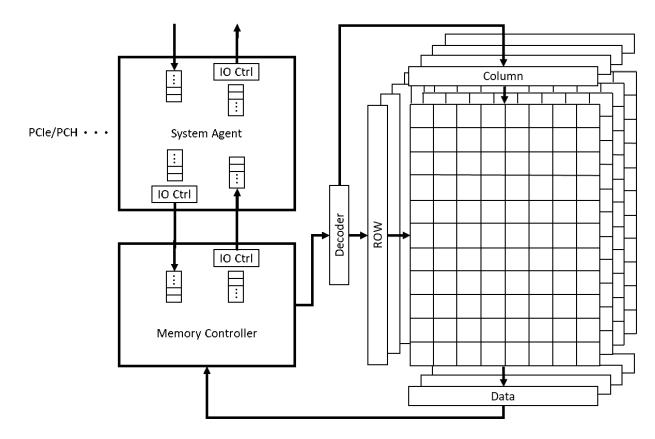

| Figure 3.10: System Agent, Memory Controller, and SDRAM Architecture        | 63 |

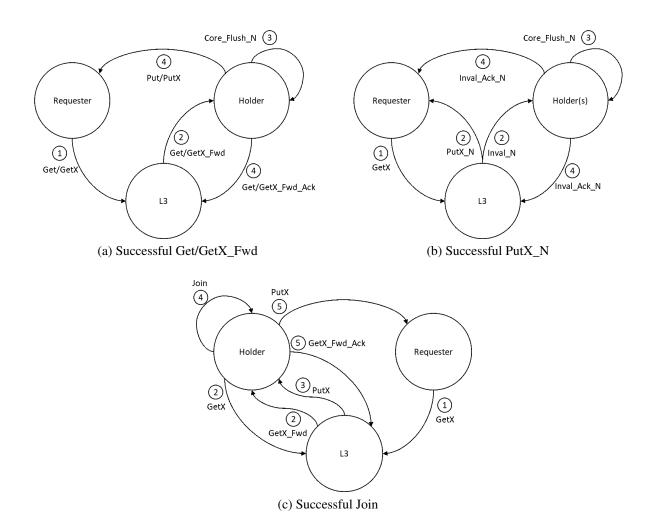

| Figure 3.11: Common Network-Based Coherence Protocol Cases                                               |

|----------------------------------------------------------------------------------------------------------|

| Figure 3.12: CPU and GPU Virtual Memory Mechanisms                                                       |

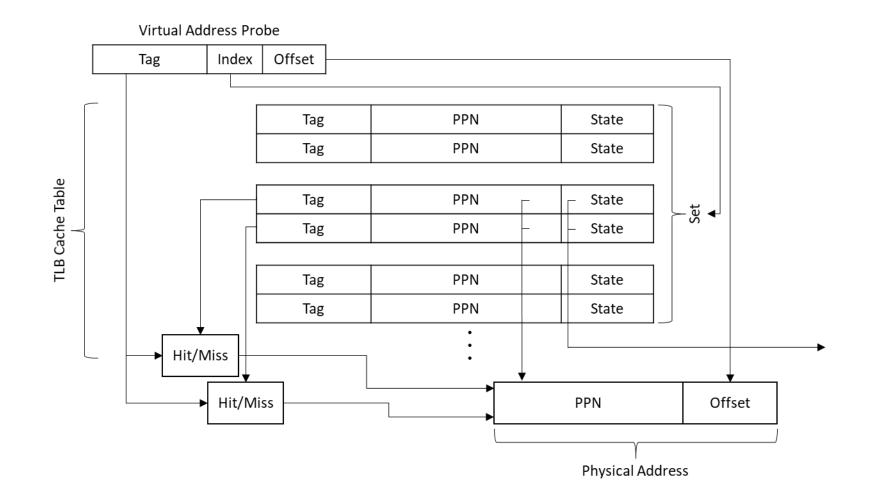

| Figure 3.13: Architecture of a Two Way Set Associative TLB Cache                                         |

| Figure 3.14: Rodinia OpenMP Benchmark Results                                                            |

| Figure 3.15: Rodinia OpenCL Benchmark Results                                                            |

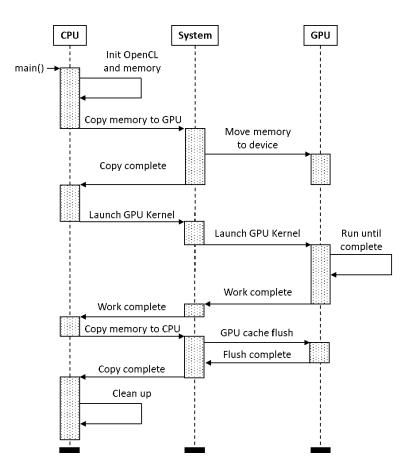

| Figure 4.1: Non-Coherent CPU-GPU Execution Sequence                                                      |

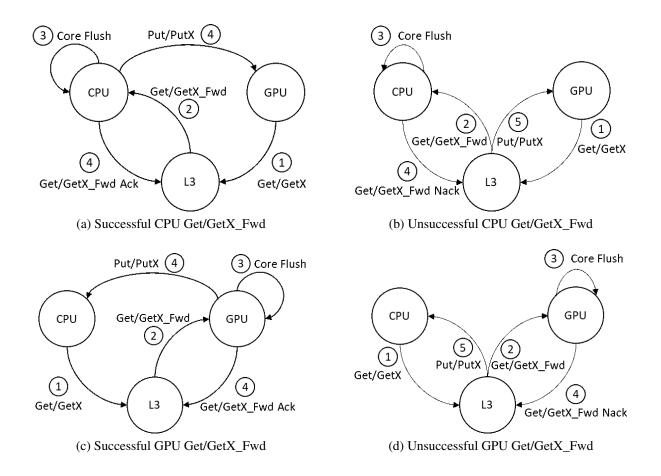

| Figure 4.2: Coherent Memory Block Movement Between CPU and GPU                                           |

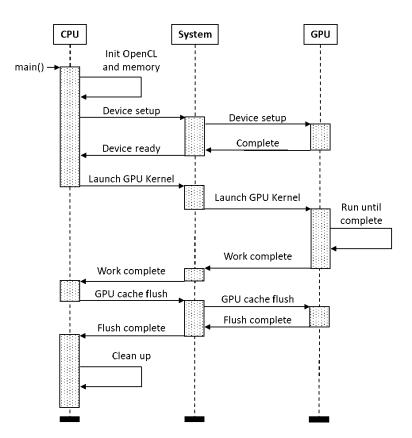

| Figure 4.3: Coherent Non-Collaborative Without Shared LLC CPU-GPU Execution Sequence      quence      99 |

| Figure 4.4: Coherent Non-Collaborative With Shared LLC CPU-GPU Execution Sequence100                     |

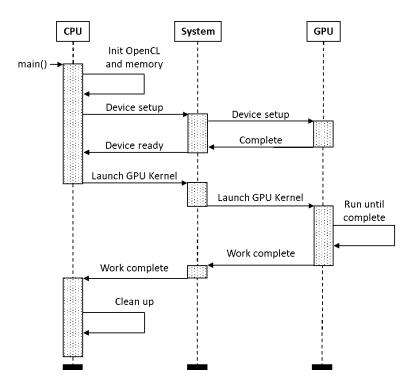

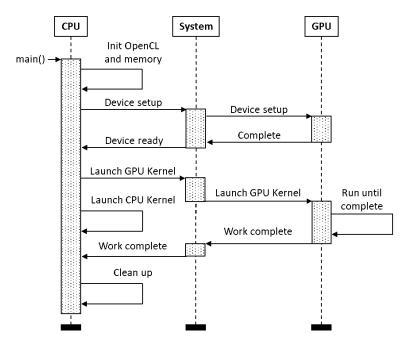

| Figure 4.5: Collaborative CPU-GPU Processing Execution Sequence                                          |

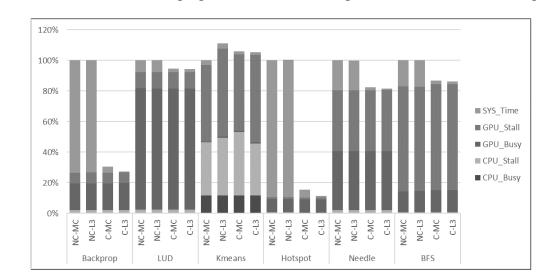

| Figure 4.6: Coherent Non-Collaborative Experimental Results                                              |

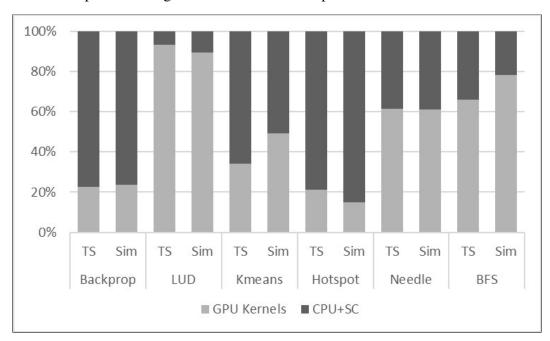

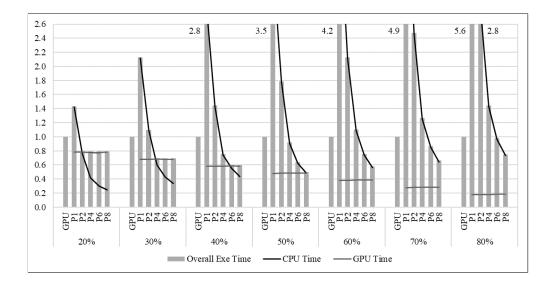

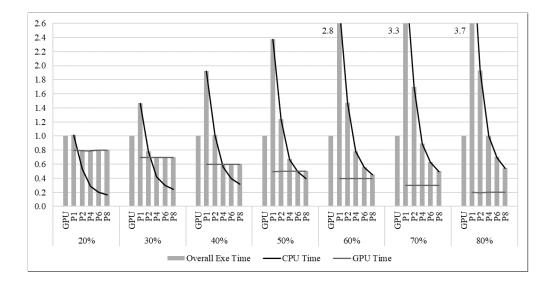

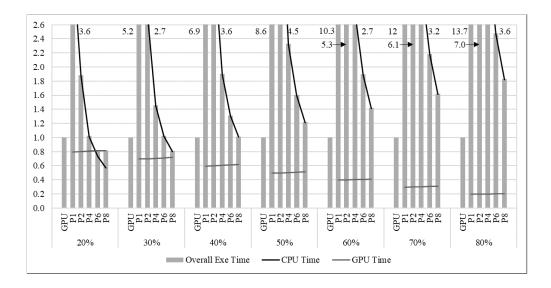

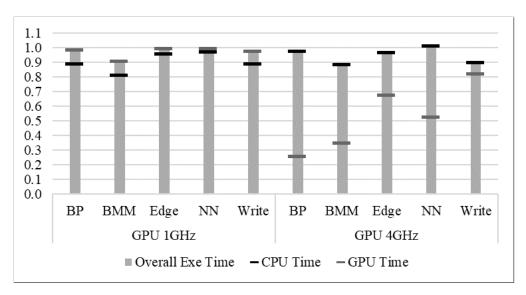

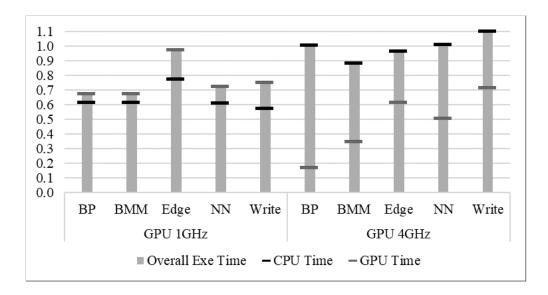

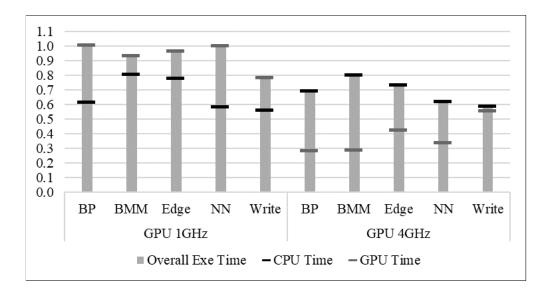

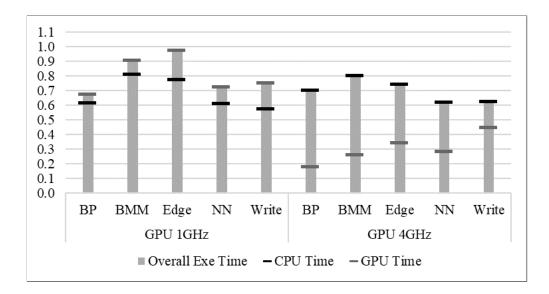

| Figure 4.7: Backprop Collaborative Execution Profile                                                     |

| Figure 4.8: Block Matrix Multiply Collaborative Execution Profile                                        |

| Figure 4.9: Edge Detection Collaborative Execution Profile                                               |

| Figure 4.10: Nearest Neighbor Collaborative Execution Profile                                            |

| Figure 4.11: Write Collaborative Execution Profile                                                       |

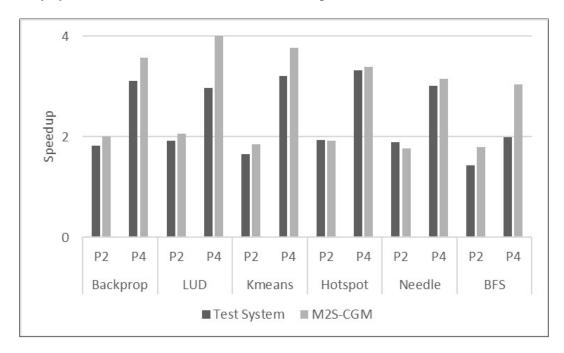

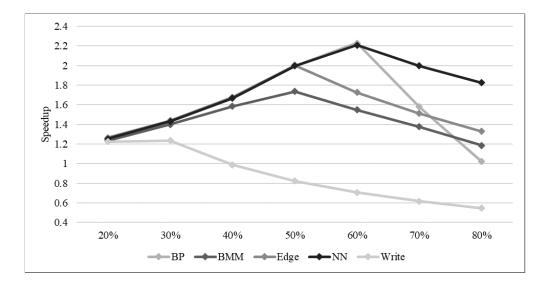

| Figure 4.12: Best Case Overall Speedups                                           |

|-----------------------------------------------------------------------------------|

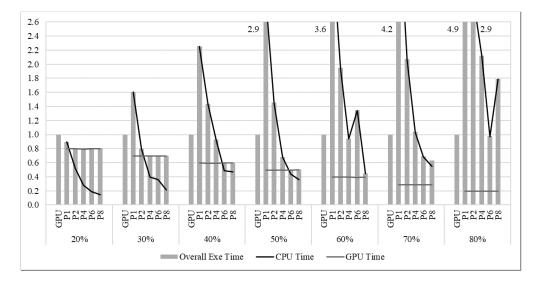

| Figure 4.13: Increasing GPU Bandwidth and Frequency                               |

| Figure 4.14: Increasing GPU Bandwidth, Frequency, and Coalesce Size               |

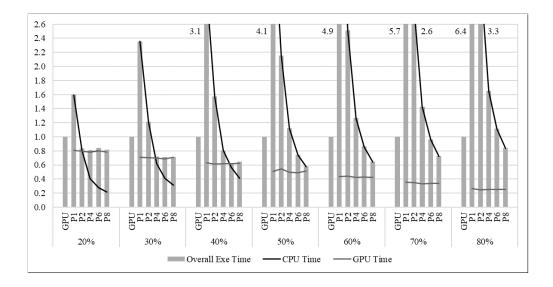

| Figure 4.15: Decreasing Switching Fabric Latency                                  |

| Figure 4.16: Decreasing Switching Fabric Latency and Increasing Coalesce Size 118 |

# LIST OF TABLES

| Table 2.1: Measure of Event Engine Usage                                                    |

|---------------------------------------------------------------------------------------------|

| Table 3.1: CPU L1 Instruction Cache MESI Coherence Protocol State Table       66            |

| Table 3.2: CPU L1 Data Cache MESI Coherence Protocol State Table       67                   |

| Table 3.3: CPU L2 Cache MESI Coherence Protocol State Table       69                        |

| Table 3.4: CPU L3 Cache MESI Coherence Protocol State Table: Fetches and Loads       72     |

| Table 3.5: CPU L3 Cache MESI Coherence Protocol State Table: Upgrades and Stores       . 73 |

| Table 3.6: GPU L1 Vector Cache MESI Coherence Protocol State Table       78                 |

| Table 3.7: GPU L2 Cache MESI Coherence Protocol State Table       80                        |

| Table 4.1: Initial System Configuration    109                                              |

| Table 4.2: Optimal Collaborative Benchmark Configurations       114                         |

# LIST OF ALGORITHMS

| Algorithm 2.1: A KnightSim Context                |

|---------------------------------------------------|

| Algorithm 2.2: KnightSim Globals                  |

| Algorithm 2.3: Eventcount Initialization          |

| Algorithm 2.4: Context Initialization             |

| Algorithm 2.5: Context Scheduling: Advance        |

| Algorithm 2.6: Context Scheduling: Await          |

| Algorithm 2.7: Context Scheduling: Pause          |

| Algorithm 2.8: Context Scheduling: Context Select |

| Algorithm 2.9: Switch Control Globals             |

| Algorithm 2.10: Switch Control                    |

| Algorithm 2.11: Thread Context Select             |

| Algorithm 2.12: Thread Control                    |

| Algorithm Appx.1: Setjmp i386                     |

| Algorithm Appx.2: Longjmp i386                    |

| Algorithm Appx.3: Setjmp x86_64                   |

| Algorithm Appx.4: Longjmp x86_64                  |

## **CHAPTER 1: INTRODUCTION**

With the computing industry's recent adoption of the Heterogeneous System Architecture (HSA) standard we have seen a rapid change in heterogeneous CPU-GPU processor design and implementation [1]. State-of-the-art heterogeneous processors tightly integrate multicore CPUs and multi-compute unit GPUs together on a single die. This results in a single cohesive package that brings together the MIMD processing capabilities of the CPU and the SIMD processing capabilities of the GPU with new HSA features including coherency between the CPU and GPU, shared Last Level Cache (LLC) [2, 3, 4], and shared virtual memory address spaces [5, 6]. In addition, high-level programming languages, like OpenCL 2.0, have been updated to make use of these new HSA features [7]. These advancements can potentially bring marked gains in heterogeneous processor performance and have piqued the interest of researchers who wish to unlock these potential performance gains. First with the advent of *zero copy* memory management between the CPU and GPU [3, 8, 9], where memory objects are passed between the CPU and GPU by pointer reference only, and now with the recent advent of collaborative CPU-GPU processing, where the CPU and GPU jointly process work in a coherent and shared virtual memory environment.

Recent research has shown that the collaborative CPU-GPU execution approach can result in measurable speedups over the preceding non-collaborative GPU-only approach [4, 10, 11, 12]. In the non-collaborative GPU-only approach workloads are only executed on the GPU and the entirety of the CPU is relegated to only performing the controlling functions of the GPU. However, the recent research presented here has been conducted on fixed physical systems comprising a single point of reference regarding architectural and application configuration with limited or no trade space analyses on impacts to overall system performance. Therefore, in this dissertation I explore the heterogeneous CPU-GPU processor and application design space with the goal of answering interesting research questions, such as, (1) what are the architectural design trade-offs in heterogeneous CPU-GPU processors and (2) how do we best maximize heterogeneous CPU-GPU application performance on a given system.

To enable my exploration of the heterogeneous CPU-GPU processor and application design space, I introduce a novel discrete event-driven simulation library called KnightSim, a novel computer architectural simulator called M2S-CGM, and implement a set of heterogeneous CPU-GPU benchmarks. KnightSim is a fast discrete event-driven simulation methodology that is intended for use in the development of future computer architectural simulations. KnightSim extends an older proven event driven simulation methodology known as "The Threads Package". The Threads Package has previously been used in at least two publicly known computer architectural simulators [3, 13]. KnightSim implements events as independently executable x86 "KnightSim Contexts". By design, KnightSim Contexts encapsulate all of the functionality and interfaces associated with a single target simulated system element in an individually executable package. This implementation methodology enjoys several benefits from this approach. First, occupancy and contention, which have been proven to be a critical determinant of system performance [14], are automatically modeled by KnightSim Contexts. Other simulation methodologies, like those of Gem5 and Multi2Sim, do not do this and require additional events, state flags, and levels of abstraction to achieve a realistic occupancy and contention model. Second, executing a KnightSim Context only requires a long jump, see Sec. 2.2.1. This mechanism is faster as compared to scheduling and running an event's call-back function because a KnightSim Context's stack is not created and torn down each time the context is executed. Finally, KnightSim Context execution can be performed in parallel because each KnightSim Context is independently executable in a multithreaded environment. These properties make KnightSim a promising tool for use in the development of computer architectural simulations.

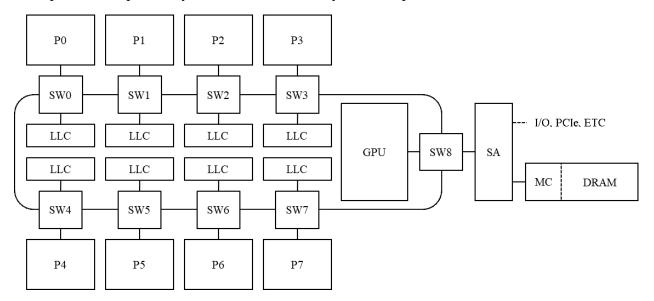

M2S-CGM provides end-to-end simulation of the system elements required to simulate modern and future non-coherent and coherent heterogeneous CPU-GPU processor architectural models. M2S-CGM extends the multicore out-of-order x86 CPU model and multi-Compute Unit (CU) Southern Islands GPU model found in Multi2Sim [15] and adds a novel highly detailed CPU-GPU memory system model. M2S-CGM's memory system model provides coherence protocols, execution-driven discrete models of system wide occupancy and contention, CPU and GPU cache structures, directories, virtual memory mechanisms, switching fabrics, a system agent, a memory controller, and SDRAM. I provide a validation of M2S-CGM and establish that M2S-CGM provides good correlation to modern computing systems and that the information ascertained from its use is reliable and can be used for trade-off decisions in proposed architectural implementations. This provides researchers the ability to conduct a range of experiments with varying degrees of configurability in the memory system for both the CPU and GPU. In addition, I implement a set of benchmarks comprising both non-collaborative GPU-only and collaborative CPU-GPU implementations of Backpropagation, Block Matrix Multiply, Edge Detection, Nearest Neighbor, and Write. Backpropagation and Nearest Neighbor are ported from the Rodinia benchmark suite [16] and Block Matrix Multiply, Edge Detection, and Write are hand implemented. These benchmarks are fully compatible with M2S-CGM, are representative of a range of scientific applications, are well-suited for execution on the GPU, and have distinct collaborative CPU-GPU memory access patterns.

I then utilize M2S-CGM for the conduct of three architectural studies. First, I study the architectural affects of shared LLC and CPU-GPU coherence on the overall performance of noncollaborative GPU-only applications. In this study I found that enabling coherence between the CPU and GPU and sharing the LLC can lead to measurable performance gains over non-coherent CPU-GPU executions. Additionally, the results of my first study make it apparent that new performance gains are possible if applications make better usage of the CPU during GPU kernel execution time. This motivated my decision to implement my own collaborative CPU-GPU benchmarks to support the second and third study. In my second study I profile and analyze my set of collaborative CPU-GPU benchmarks and determine how to best optimize them for maximum collaborative performance. I establish collaborative performance profiles for each of my benchmarks and use them to conduct a detailed performance analysis and report the results in this dissertation. My collaborative CPU-GPU performance profiles show overall collaborative speedups while varying CPU cores/threads from one to eight and CPU workload percentage from 20% to 80%. The results identify each benchmark's optimization points and show that my set of collaborative CPU-GPU applications can achieve speedups as high as 2.23x over that of the non-collaborative GPU-only versions. In addition, the results provide a few rules of thumb regarding how best to reason about what an unprofiled collaborative CPU-GPU application's optimized settings could be. Finally, I utilize my set of benchmark's again and study the impact of varying four key architectural parameters on collaborative CPU-GPU performance. In the study I vary GPU compute unit coalesce size, GPU to memory controller bandwidth, GPU frequency, and system wide switching fabric latency. My results show that future looking architectural changes can lead to a theoretical average speedup of 3.33x over the average speedups of our benchmark's best case collaborative CPU-GPU executions and reach a theoretical average speedup of 6.3x over that of our benchmark's non-collaborative GPU-only executions.

#### 1.1 Research Contributions

This dissertation makes the following research contributions:

• I present a detailed discussion, with pseudocode, of the implementation of KnightSim and Parallel KnightSim and present the results of a performance analysis of KnightSim, Parallel KnightSim and three different event-driven simulation methodologies that are widely in use today. KnightSim and Parallel KnightSim simplify computer architectural simulator programmability and introduce a new cycle level parallel processing capability that can speedup

future architectural simulation.

- I present M2S-CGM and provide five benchmarks comprising both non-collaborative GPUonly and collaborative CPU-GPU implementations. M2S-CGM and its benchmarks enable execution-driven simulation-based research within the collaborative CPU-GPU design space where previously not possible.

- I present the results of my first architectural study regarding the effects of shared LLC and CPU-GPU coherence on the overall performance of non-collaborative GPU-only applications. This work provides new directions to researchers by establishing that the CPU and GPU should be made coherent and share LLC and virtual address spaces. This eliminates the need for expensive underlying mechanisms like memory copies between the CPU and GPU and paves the way for higher levels of CPU-GPU parallelism.

- I present the results of my second architectural study regarding the analysis and optimization of collaborative CPU-GPU applications and determine how to best optimize them for maximum collaborative performance. This work establishes a method for determining how to best optimize collaborative CPU-GPU applications and motivates future research regarding the development of profiling tools for heterogeneous CPU-GPU applications.

- I present the results of my third architectural study regarding the impacts of varying four key architectural parameters on collaborative CPU-GPU performance. My results provide new directions in heterogeneous CPU-GPU processor design and establish that computer architectural researchers should focus on increasing GPU compute unit coalesce size, GPU frequency, and lowering switching fabric latency in future heterogeneous CPU-GPU processors.

- To the best of my knowledge this dissertation presents the first in-depth simulation backed study of the collaborative CPU-GPU trade space that includes optimizing operating points

and analyzing the performance impact of key architectural parameters.

• Ready-made and fully working implementations of KnightSim, Parallel KnightSim, M2S-CGM, and the benchmarks presented in this dissertation are made available as free software and can be found on GitHub.

#### 1.2 Dissertation Organization

This dissertation is organized as follows. Chapter 2 provides a background regarding discrete event-driven simulation methodologies then introduces and discusses the implementation and modeling methodologies of KnightSim and Parallel KnightSim. A detailed performance analysis is performed comparing KnightSim and Parallel KnightSim to that of three other mainstream discrete event-driven simulation methodologies. The work presented in chapter 2 extends my work previously presented in [17, 18]. Chapter 3 provides a background in heterogeneous CPU-GPU processors and applications and then introduces and discusses the implementation of M2S-CGM. Significant discussion is provided regarding M2S-CGM's x86 CPU, AMD Southern Islands GPU, and memory system simulation models. M2S-CGM is validated by comparison of M2S-CGM to a physical test system. The work presented in chapter 3 extends my work previously presented in [3]. Chapter 4 provides a background regarding the organizational use of the GPU in heterogeneous CPU-GPU applications and presents the results of three architectural studies. The architectural studies presented are based upon the culmination of all the work previously presented in this dissertation. The work presented in chapter 4 extends my work previously presented in [3, 19]. Chapter 5 covers the related work to my own. And finally, Chapter 6 draws conclusions to this dissertation and discusses new directions for future research.

# CHAPTER 2: DISCRETE EVENT-DRIVEN SIMULATION METHODOLOGIES

This chapter discusses a novel context-based event-driven simulation methodology called Knight-Sim, as presented in [17, 18], and includes a significant expansion in discussion. KnightSim extends an older event-driven simulation library called "The Threads Package" by (1) incorporating corrections to functional issues that were introduced by the recent additions of stack protection, pointer mangling, and source fortification in the Linux software stack, (2) incorporating optimizations to the event engine, and (3) introducing a novel parallel implementation. The chapter starts by providing a sufficient background regarding event-driven simulation methodologies so that readers can understand the subject matter of the chapter. Then, a thorough discussion of the implementation methodologies of both KnightSim and Parallel KnightSim is given with expanded discussion regarding their usage in computer architectural functional and power modeling. The chapter concludes with a performance analysis and draws comparisons of both KnightSim and Parallel KnightSim to that of three other mainstream event-driven simulation methodologies in use today.

#### 2.1 Background and Motivation

One of the most fundamental building blocks in any computer architectural simulation system is its event engine. A computer architectural simulation system's event engine provides the mechanism with which the simulator will carry out its simulation tasks. Additionally, the event engine introduces a temporal property in execution by allowing developers to specify a time when a given simulation task should take place. In the context of computer architectural simulation systems, the time when a simulation task begins is typically at the start of a desired simulated clock cycle. At the time of writing this dissertation, most event engines used in mainstream computer architectural simulation systems utilize an implementation technique where events are registered at initialization and are provided a single callback function to execute. In essence, the event engine's scheduler will call the user provided function that is linked by the event when the number of developer specified cycles transpires. The event engine's scheduler maintains execution order by performing a heapify on a global event queue, or another equivalent approach, as new events are scheduled. When all events scheduled for a given cycle transpire, the cycle count is allowed to increment forward in time. In this approach, creating realistic computer architectural models of simulation elements requires the amalgamation of multiple events along with other primitives, like state flags, for execution control. Developers must carefully endeavor to model the latency, occupancy, and contention incurred by the modeled element.

A lesser known, but proven approach to event-driven simulation is an approach based on execution contexts. In this approach contexts are similar to the traditional events described above, but are more like micro kernels as they are individually executable on a given CPU core. In practical usage, each context represents a simulation element and encompasses all of the simulation element's functionality and data. Whole systems are then modeled as collections of contexts functionally working together. Context scheduling is explicitly handled between the contexts themselves with the use of an advance and await mechanism, which is further explained in this chapter. Ultimately, contexts are grouped logically, like the real hardware being modeled, and await advancement from a neighboring context. During execution, contexts can pause and assess a latency. When the context is paused no work will be performed by the context. This mechanism also results in automatically modeling occupancy and contention amongst contexts. The intrinsic properties of contexts providing a means to automatically model occupancy and contention makes the context-based approach an ideal approach for use in computer architectural simulation systems and serves as the motivation behind creating KnightSim and Parallel KnightSim.

#### 2.2 KnightSim Implementation Methodology

The makeup of a KnightSim Context is shown in Alg. 2.1. The context is defined by functions that encapsulate all of the user's desired functionality and interfaces associated with the simulated element. During simulation execution, contexts await until they are notified that they should execute by an advance from one or more previously running contexts, but will not execute until they are ready. Contexts currently in the run state may pause any number of simulation cycles or await a future event to assess a latency. Simulation cycle time increases once all contexts have either entered a pause or await state.

| Alg | Algorithm 2.1 A KnightSim Context                                |                                        |  |  |  |

|-----|------------------------------------------------------------------|----------------------------------------|--|--|--|

| 1:  | <pre>procedure USER_FUNCTION(context* ctx)</pre>                 |                                        |  |  |  |

| 2:  | long long $i \leftarrow 1$ ;                                     |                                        |  |  |  |

| 3:  | \\Other local variables here                                     |                                        |  |  |  |

| 4:  | loop                                                             |                                        |  |  |  |

| 5:  | <i>await</i> ( <i>my_eventcount</i> , <i>i</i> ++, <i>ctx</i> ); |                                        |  |  |  |

| 6:  | \\Do work after being advanced                                   |                                        |  |  |  |

| 7:  | pause(1, ctx);                                                   | ▷ Charges a latency for work performed |  |  |  |

| 8:  | \\Finish doing work                                              |                                        |  |  |  |

| 9:  | <pre>advance(neighboring_eventcount,ctx);</pre>                  |                                        |  |  |  |

| 10: | \\Clean up and return to await state                             |                                        |  |  |  |

| 11: | end loop                                                         |                                        |  |  |  |

| 12: | return                                                           |                                        |  |  |  |

| 13: | end procedure                                                    |                                        |  |  |  |

The context's assessed latency during the paused or await state provides the mechanism to automatically model the occupancy of that context as no other work can be performed by the context during that time. Contention is automatically modeled as contexts must compete for modeled system resources. Individual contexts stall by pausing or awaiting as they wait for access to a particular resource. These additional stalls result in longer access latency for current and subsequent invocations as contexts wait for modeled hardware resources to become available. In the following subsections I provide discussion and present details regarding the implementation methodology of KnightSim.

Algorithm 2.2 KnightSim Globals 1: globals 2: if wordsize == 64 then **typedef long int** \_*jmp\_buf*[8]; 3: else if *x*86\_64 then 4: **typedef long long int** \_*jmp\_buf*[8]; 5: 6: else **typedef int** \_*jmp\_buf*[6]; 7: 8: end if 9: typedef struct context{ 10: \_jmp\_buf *buf*; ▷ Buffer for CPU registers 11: unsigned long long count; 12: void (\*start)(struct context\*); ▷ Context's function at execution 13: **char**\* *stack*; ▷ Context's unique stack 14: 15: int stacksize: 16: struct context \* next\_ctx; ▷ Context's batch list pointer

17: } context;

18:

19: typedef struct eventcount{

20: struct context\* next\_ctx;

21: unsigned long long count;

22: } eventcount;

23: end globals

2.2.1 Events as KnightSim Contexts

KnightSim implements events as KnightSim Contexts, which are independently executed by the CPU at runtime. A context is represented by a struct that defines the context itself, and one or more eventcounts [20]. Pseudocode describing the implementation of contexts and eventcounts is shown in Alg. 2.2.

The context structure comprises a jump buffer, count, function pointer, stack pointer, stack size, and context pointer. The jump buffer is a primitive data type that is utilized by my hand implemented

setjmp() and longjmp() assembly functions, see the Appendix. My implementations of setjmp() and longjmp() correct functional issues introduced by the recent additions of stack protection, pointer mangling, and source fortification in the Linux software stack. Usage of the standard Libc setjmp() and longjmp() functions will render this methodology non-functional in modern Linux distributions. Determination of the correct data type and size of the context's jump buffer is shown at the top of Alg. 2.2. The context's count is used to synchronize the context with an eventcount's state. The context's function pointer is assigned the address of the user's provided entry function. The stack pointer points to an allocated region of memory of user provided stack size. Each context's stack is unique, resides in user memory space, and contains that context's execution data. Contexts execute in a shared memory space and can operate on global C/C++ objects as well. The context pointer is used to form a singly linked list that comprises a batch of contexts that are ready to run at a given cycle. When a context enters the pause or await state the next context in the list is executed until the list is empty.

Eventcounts are objects that provide a mechanism with which to determine if a context should be placed in the run or await state. Eventcounts comprise a count that is used as an incrementer and a pointer to a context that is awaiting an advance of the eventcount. The eventcount's count records the number of times the eventcount has been advanced. Contexts await the advance of eventcounts and when the counts of both an eventcount and context are equal the awaiting context runs. Typically, each context will have at least one unique eventcount assigned to it, but this is not required.

Context batches are stored via a hash table and are formed as each context enters the pause state. Contexts are added to the table by hashing the context's designated future execution cycle with the global hash table's number of rows minus one. The global hash table's number of rows is set as a power of two and must be large enough to ensure that pausing contexts form batches of only one future execution cycle. I find that a hash table size of 512 is more than sufficient to meet this requirement. This is an optimized approach that maintains a high level of performance and does not require a modulus operation. Selecting the next context batch to run requires hashing the current global cycle count with the global hash table's number of rows minus one. A count of the number of unique context batches referenced by the hash table is kept. Simulation ends when the global hash table count is set to zero or the simulation's execution reaches a desired end point.

| Algorithm 2.3 | Eventcount | Initialization |

|---------------|------------|----------------|

|---------------|------------|----------------|

```

1: procedure EVENTCOUNT_INIT(void)

```

- 2: **eventcount**\* *ec*  $\leftarrow$  NULL;

- 3:  $ec \leftarrow (eventcount*)malloc(sizeof(eventcount));$

- 4:  $ec \rightarrow count \leftarrow 0;$

- 5:  $ec \rightarrow next\_ctx \leftarrow \text{NULL};$

- 6: **return** *ec*;

- 7: end procedure

```

Algorithm 2.4 Context Initialization

```

```

1: procedure CTX_INIT((*func)(context*), int size)

```

- 2: **context**\* *ctx*  $\leftarrow$  NULL;

- 3:  $ctx \leftarrow (context*)malloc(size of(context));$

- 4:  $ctx \rightarrow count \leftarrow sim\_cycle;$

```

5: ctx \rightarrow stack \leftarrow (char*)malloc(size);

```

6:  $ctx \rightarrow stacksize \leftarrow size;$

```

7: ctx \rightarrow start \leftarrow func;

```

```

8: ctx \rightarrow buf[ip] \leftarrow context\_start();

```

- 9:  $ctx \rightarrow buf[sp] \leftarrow stack\_top\_ptr;$

- 10:  $ctx \rightarrow next\_ctx \leftarrow \text{NULL};$

```

11: ctx_hash_insert(ctx,ctx->count&ROWS);

```

```

12: return

```

```

13: end procedure

```

#### 2.2.2 Initialization

▷ Stack overflow check

▷ User defined function

Prior to simulation execution each user created eventcount and context is initialized. Eventcount initialization is straightforward and comprises the allocation of the eventcount with the use of

malloc(), the initialization of the eventcount's count to zero, and the initialization of the eventcount's context pointer to NULL, as shown in Algo. 2.3. Context initialization is shown in Alg. 2.4 and comprises the allocation of the context itself with the use of malloc(), initialization of the context's count, allocation of the context's stack with use of malloc(), assignment of the stack size, assignment of the user's provided entry function, manipulation of the instruction and stack pointers in the context itself into the applicable context batch. The entry function embodies the functionality of the element this context will simulate, as shown in Alg. 2.1. During initialization the context's count is assigned the global cycle count. Contexts may be created and destroyed at any time, before and during simulation execution.

The context's jump buffer is uninitialized after being created. Thus, I assign a starting instruction pointer and stack pointer by hand to give the context our desired starting position and unique stack memory. This manual configuration of the context's jump buffer is what makes each context independently executable. I ignore other CPU registers at initialization because they will be obtained the first time setjmp() is called. Additionally, I push a pointer to the context onto the context's stack for retrieval later. This allows us to resolve information about the context after the context's initial jump.

The pseudocode shows an instruction pointer assignment as the head of a context\_start() function. On initial execution, each context will first jump to the head of this function and then retrieve the pointer to itself. The context's start() function is then called and passed a pointer to the context itself for future access. Program execution is now placed at the head of the user's provided entry function with resolution of the assigned context, see Alg. 2.1. Additionally, the pseudocode shows a stack pointer assignment as the top of the allocated stack that is calculated as shown in Equ. 2.1 for both 32bit and 64bit Linux environments.

$$stack\_top\_ptr = stack\_ptr + stack\_size - sizeof(int)$$

(2.1)

The assignment of the instruction and stack pointers to the context's jump buffer is architecture dependent and must be accounted for at time of compilation. The instruction pointer and stack pointers are assigned to jump buffer positions *five* and *four* in the 32bit Linux x86 environment and are assigned to jump buffer positions *seven* and *six* in the 64bit Linux x86 environment.

#### 2.2.3 Scheduling

Pseudocode showing the mechanisms responsible for providing KnightSim Context scheduling is shown in Alg. 2.5, Alg. 2.6, Alg. 2.7, and Alg. 2.8.

```

Algorithm 2.5 Context Scheduling: Advance

1: procedure ADVANCE(eventcount* ec, context* ctx)

2:

ec \rightarrow count ++;

if ec->next_ctx and ec->next_ctx->count == ec->count then

3:

4:

ec \rightarrow next\_ctx \rightarrow next\_ctx \leftarrow ctx \rightarrow next\_ctx;

5:

ctx \rightarrow next \ ctx \leftarrow ec \rightarrow next \ ctx;

ec \rightarrow next\_ctx \leftarrow NULL;

6:

7:

end if

return

8:

9: end procedure

```

Placing KnightSim in the simulation state simply requires obtaining a pointer to the first context in the initial context batch and performing a longjmp() to the context's starting position. Subsequently, each context resides in either an await, ready to run, or running state until the end of simulation. In the single-threaded version of KnightSim only one context is ever in the running state at a time. A transition between these states is accomplished with use of the advance(), await(), and pause() functions. A running context executes its assigned tasks and advances one or more eventcounts as a product of its work by use of the advance() function. By advancing an eventcount, the designated eventcount's count is incremented and the eventcount's context pointer is checked. If the counts of both the context and eventcount are equal the context is removed from the eventcount and inserted next into the current context batch as a context that should run this cycle.

| Algorithm 2.6 Context Scheduling: Await                       |                                            |

|---------------------------------------------------------------|--------------------------------------------|

| 1: procedure AWAIT(eventcount* ec, count value, context* ctx) |                                            |

| 2:                                                            | if $ec \rightarrow count \ge value$ then   |

| 3:                                                            | return;                                    |

| 4:                                                            | end if                                     |

| 5:                                                            | $ctx \rightarrow count \leftarrow value;$  |

| 6:                                                            | $ec \rightarrow next\_ctx \leftarrow ctx;$ |

| 7:                                                            | $ctx \leftarrow ctx -> next_ctx;$          |

| 8:                                                            | if !set jmp(ec->next_ctx->buf) then        |

| 9:                                                            | if ctx then                                |

| 10:                                                           | longjmp(ctx -> buf);                       |

| 11:                                                           | else                                       |

| 12:                                                           | sim_cycle++;                               |

| 13:                                                           | <pre>longjmp(context_select());</pre>      |

| 14:                                                           | end if                                     |

| 15:                                                           | end if                                     |

| 16:                                                           | return                                     |

| 17: end procedure                                             |                                            |

|                                                               |                                            |

After a context completes its tasks, the context then transitions to the await state by use of the await() function. The context will assign itself a count on which it will await, remove itself from the current context batch, assign itself to the designated eventcount's context pointer, and store the current position in its jump buffer. Simulation execution can then jump to the next context in the current context batch or, if this batch is finished, increment the global cycle count and select the next batch. A running context may also assess a latency with the use of the pause() function. Assessing a latency stops the current context from running until a future global cycle count is reached, where the context will then automatically resume execution. The pausing context

is removed from the current context batch and added to a context batch in the global hash table that is awaiting the same future global cycle count. If the addition to the global hash table results in a new context batch record the global hash table's count is incremented. Lastly, I store the current position in the pausing context's jump buffer. Simulation execution can then jump to the next context in the current context batch or, if this batch is finished, increment the global cycle count and select the next context batch.

\_\_\_\_\_

```

Algorithm 2.8 Context Scheduling: Context Select

1: procedure CONTEXT_SELECT(void)

context* ctx_ptr \leftarrow NULL;

2:

if table_count then

3:

do

4:

ctx\_ptr \leftarrow table[sim\_cycle\&ROWS];

5:

while !ctx_ptr and sim_cycle++;

6:

7:

table[sim\_cycle\&ROWS] \leftarrow NULL;

8:

table count-;

else

9:

10:

sim_end();

11:

end if

return ctx_ptr->buf;

12:

13: end procedure

```

The next context batch is selected with the context\_select() function. I select the next context batch by iterating through the global hash table until I obtain a valid pointer to a batch of contexts. The global cycle count is incremented with each required iteration and reference of the hash table. Each removal of a context batch from the hash table results in a decrement of the global hash table's count. As mentioned before, simulation ends when the global hash table's count reaches zero.

#### 2.3 KnightSim Modeling Methodology

Using KnightSim to create computer architectural simulation models, like the one shown in Fig. 2.1, is straightforward. The figure shows a functional architecture block diagram of a modern processor comprising 18 CPU cores, a mesh switching fabric, and two memory controllers. To implement this in KnightSim the developer would establish the appropriate number of contexts necessary to model the desired system and assign each context the appropriate generic control function. The control function encapsulates the tasks that each particular type of simulation element performs at the developers desired level of granularity. For example, emulation elements, CPU pipeline stages, caches, IO controllers, switches, memory controllers, DRAM, and etc. The computer architectural model, in whole, is represented as the collection of these simulation elements cooperatively working together, like the real hardware.

Figure 2.1: An 18 Core CPU Computer Architectural Model

In this example each processor core, cache, switch, and memory controller could be modeled as individual contexts that execute at the appropriate cycles. Alternatively, a more fine-grained approach would be to model each processor core, cache, switch, and memory controller as a collection of contexts that comprise the sub-elements of the modeled component. In all cases the desired level of simulation granularity is left to the developer to decide. In the presented approach, each modeled CPU core would fetch and then emulate a target instruction, then update the state of its modeled pipeline stages and associated resources. CPU flow control is provided based on the state of the CPU's modeled pipeline resources and the memory system. Interaction with the first and subsequent levels of the memory system is accomplished with an appropriate advancement and memory system element load or store. This process continues throughout the memory system and switching fabric. In a large computer architectural simulation model, long chains of contexts represent the interdependence between discrete hardware elements. During long stalls contexts await and simulation execution time advances to the appropriate simulation cycle.

In the following section I present and discuss a simulation model of the switching fabric shown in Fig. 2.1. The example switching fabric model demonstrates advanced usage of KnightSim for modeling of complex system elements and highlights the ease of use and power of KnightSim's modeling methodology. In addition to the example switching fabric shown here, researchers can refer to CGM [3], where an entire memory system comprising configurable cache structures, cache directories, translation lookaside buffers, page table walkers, switching fabrics, crossbars, a system agent, memory controller, and other discrete system elements such as a GPU hub and IOMMU is modeled using the techniques presented in this dissertation.

#### 2.3.1 Switching Fabric Implementation Methodology

Alg. 2.9 and Alg. 2.10 provides pseudocode showing the implementation of the mesh switching fabric illustrated in Fig. 2.1. The example demonstrates how to model a switch and crossbar with a user-defined number of ports and virtual lanes. The switch pseudocode is written with the intent of clearly showing KnightSim's modeling methodology. More fine-grained and sophisticated implementations are possible. The model consists of a single context and its main control function, switch\_ctrl(), where all derivative switch-related tasks are encapsulated.

#### Algorithm 2.9 Switch Control Globals

```

1: globals

```

- 2: **#define** *CYCLE etime*->*count*»1

- 3: **#define** *P\_PAUSE*(*p\_delay*) *pause*((*p\_delay*)«1)

- 4: **#define** *ENTER\_SUB\_CLOCK if*(!(*etime*->*count* & 0*x*1)) *pause*(1);

- 5: **#define** *EXIT\_SUB\_CLOCK if* (*etime*->*count* & 0*x*1) *pause*(1);

- 6: **int** *switch\_pid* = 0;

- 7: **eventcount** \*\* *sw\_ec*;

- 8: **struct switch\_t** \*\* *sw*;

- 9: end globals

Variables pertinent to the individual switch model are located along the top of the main switch\_ctrl() function. Context variables are all initialized and stored within each individual contexts. Any number of switches can be created and chained together utilizing this single switch\_ctrl() function. Therefore, each switch is assigned a global my\_pid for dereferencing the correct switch structure and eventcount during execution. The await() function takes as an argument a count to assign to the context as it waits. So, a context await variable is needed to manage this interaction and is initialized with the value of one. This causes the switch to enter the await state at the beginning of the switch's main execution loop where it then awaits advancement by one or more connected system elements, usually a connected I/O controller.

Arguably, one of the most powerful features of KnightSim is the ability to easily model interactions in the sub-clock domain. In relation to computer architectural simulations, this provides an easy way to model arbitration in the system. After advancement by one or more connected elements the switch then enters the sub-clock domain. During which all elements seeking to advance the switch have completed their advancement and have entered the await or pause state. The switch can then perform arbitration and scheduling functions with complete knowledge of all its advancing elements. In modeling the sub-clock domain, the global cycle count can be divided any number of times with the use of macros intended to adjust the cycle time. As shown at the top of Alg. 2.9, ENTER\_SUB\_CLOCK and EXIT\_SUB\_CLOCK adjust the cycle count such that two cycles represent one cycle for the system at large. The sub-clock domain is then modeled on the odd cycle count which is the half cycle to the system.

After returning to the regular clock domain with use of EXIT\_SUB\_CLOCK, the switch then charges a latency for its work with the P\_PAUSE macro. The switch will pause and then resume from this point after the specified number of cycles passes. The charged latency provides the mechanism to automatically model the occupancy of the switch. Upon resuming, the switch then records the number of successfully formed links, moves data from the specified input ports to the specified output ports, and advances the specified output port I/O controller. If a specified output port is full the switch can not successfully form the link and will automatically retry each cycle until success. The switch's retry stalls form a part of the system wide contention model regarding these resources.

## Algorithm 2.10 Switch Control

```

1: procedure SWITCH CTRL(context* ctx)

int my_pid = switch_pid + +;

2:

count step = 1;

3:

▷ Context await count

packet* net_packet = NULL;

4:

loop

5:

await(&sw_ec[my_pid], step, ctx);

6:

calc_passive_power(&sw[my_pid],CYCLE);

7:

ENTER_SUB_CLOCK

8:

xbar link(&sw[my pid]);

9:

EXIT_SUB_CLOCK

10:

P_PAUSE(\&sw[my_pid] \rightarrow latency, ctx);

11:

for i \leftarrow 0 to sw[my_pid] \rightarrow num_ports - 1 do

12:

13:

if xbar_link_success(&sw[my_pid],i) then

14:

sw[my_pid]->num_links++;

net_packet \leftarrow dequeue(\&sw[my_pid], i);

15:

enqueue(&sw[my_pid],i,net_packet);

16:

advance(&sw_io_ec[xbar_out(&sw[my_pid],i, ctx)]);

17:

end if

18:

end for

19:

step + = sw[my_pid] - num_links;

20:

calc_active_power(&sw[my_pid],&sw[my_pid]->num_links,CYCLE);

21:

sw[my_pid] \rightarrow num_links = 0;

22:

switch_update_state(&sw[my_pid]);

23:

24:

end loop

▷ Should never return

return:

25:

26: end procedure

```

Prior to returning to the top of the switch's main execution loop the switch resets its state and prepares for the arrival of new work. The switch's step value must be incremented via the number of links made. This accounts for the number of advancements and the work performed that cycle. In the case that the switch fails to service a request, the main execution loop will continue to run until all outstanding requests are serviced and the step variable's value returns to one larger than

the switch's eventcount value.

### 2.3.2 Power Simulation Methodology

The methodology behind creating accurate power simulation models is also shown in the example switch model. This is accomplished by calculating the individual element's passive and active power expenditures throughout execution. Each element has a finite number of possible derivative states it can enter. In the modeled switch example, individual switch elements are either in the run/ready state or are in the await state. Calculations determining the expenditure of power during these two states would be performed with the equivalent calc\_passive\_power() and calc\_active\_power() functions as shown.

The await state is straightforward and represents the period of time the element passively utilizes or leaks power. After being advanced the switch wakes up and calculates the passive or leaked power usage over the period of cycles the switch was awaiting. This is accomplished by utilizing a variable value representing the passive power used by the element per cycle. Upon exiting simulation one final calculation must be made to reconcile the difference between the element's last await and the end of simulation.

During the run/ready state several derivative outcomes may occur that would influence the amount of power utilized by the element. This necessitates a user-provided state-based power profile for the modeled element. The power profile maps each possible outcome to an assigned value representing the active power used in that state. The nature of the switch's main execution loop makes it easy to determine the possible states of the switch model during the run/ready state. In the example, the number of links formed while in the run/ready state can be used to estimate the level of effort performed by the switch.

When added together the passive and active power usage determines the overall power expenditure for the modeled element. The expenditure for each modeled element can be aggregated to determine the power expenditure for the entire system or portions of the system thereof. Impacts to power from proposed architectural changes can then be accurately modeled and taken into account by researchers.

# 2.4 Parallel KnightSim Implementation Methodology

I developed KnightSim with an eye towards ultimately parallelizing it. Therefore, parallelizing KnightSim only requires a few changes which I highlight in this section. In general, the approach to parallelizing KnightSim is summarized best as splitting a given cycle's context batch into a balanced group of smaller context batches and then executing the group of context batches over an appropriate number of threads. This results in a discrete event-driven simulation methodology that automatically parallelizes event execution at the cycle level.

| Algorithm 2.11 Thread Context Select                       |                                                                                                                    |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1: <b>procedure</b> THREAD_CONTEXT_SELECT( <i>int id</i> ) |                                                                                                                    |  |  |  |

| 2:                                                         | if table_count then                                                                                                |  |  |  |

| 3:                                                         | <b>context</b> * $ctx\_ptr \leftarrow table[sim\_cycle&ROWS][id]; \triangleright$ Check for thread's context batch |  |  |  |

| 4:                                                         | if ctx_ptr then                                                                                                    |  |  |  |

| 5:                                                         | $table[sim\_cycle\&ROWS][id] \leftarrow NULL;$                                                                     |  |  |  |

| 6:                                                         | <pre>sync_sub_and_fetch(&amp;table_count,1);</pre>                                                                 |  |  |  |

| 7:                                                         | $long jmp(ctx\_ptr->buf);$ > Jump to first context's last position                                                 |  |  |  |

| 8:                                                         | else > Return to cycle barrier                                                                                     |  |  |  |

| 9:                                                         | long jmp(threads[pthread_self()%NUMTHREADS].buf);                                                                  |  |  |  |

| 10:                                                        | end if                                                                                                             |  |  |  |

| 11:                                                        | end if                                                                                                             |  |  |  |

| 12:                                                        | return                                                                                                             |  |  |  |

| 13: end procedure                                          |                                                                                                                    |  |  |  |

Parallel KnightSim utilizes a pool of POSIX threads of configurable size and a 2D global hash table. The 2D global hash table's rows each represent a future cycle and each thread is assigned a

column. As shown in Algo. 2.11, at the start of each cycle each thread consults the appropriate row and column of the 2D global hash table to determine if there is a context batch to run this cycle or not. If a thread finds a context batch it removes the context batch from the 2D global hash table and then independently executes each context in its assigned context batch one after the other until the end of the context batch list is reached.

Threads maintain global cycle synchronization by use of a global cycle barrier, as shown in Algo. 2.12. After each thread completes the execution of its assigned context batch each thread will then return and enter the global cycle barrier. All returning threads but the last to arrive at the global cycle barrier spin while waiting for the global cycle count to be incremented. The last thread to arrive performs the global cycle count increment, which releases all threads and places overall execution in the next cycle.

| Algorithm 2.12 Thread Control |                                                             |                                                  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| 1:                            | 1: <b>procedure</b> THREAD_START( <b>void</b> * <i>id</i> ) |                                                  |  |  |  |  |

| 2:                            | <b>volatile bool</b> $lflag \leftarrow false;$              |                                                  |  |  |  |  |

| 3:                            | <i>thread_set_affinity</i> (( <b>long</b> ) <i>id</i> );    |                                                  |  |  |  |  |

| 4:                            | while $(gflag! = lflag)$ {};                                | ▷ Wait for sim execution                         |  |  |  |  |

| 5:                            | : set jmp(thread_buf[pthread_self() mod SIZE]);             |                                                  |  |  |  |  |

| 6:                            | $lflag \leftarrow !lflag;$                                  | ▷ Invert the local status flag                   |  |  |  |  |

| 7:                            | ifsync_sub_and_fetch(&threadnum,1) then                     |                                                  |  |  |  |  |

| 8:                            | while $(gflag! = lflag)$ {;                                 | ▷ wait for the last thread to arrive             |  |  |  |  |

| 9:                            | else                                                        |                                                  |  |  |  |  |

| 10:                           | <pre>sim_cycle++;</pre>                                     |                                                  |  |  |  |  |

| 11:                           | $threadnum \leftarrow \texttt{SIZE};$                       |                                                  |  |  |  |  |

| 12:                           | $gflag \leftarrow lflag;$                                   | $\triangleright$ Last thread resets the flags    |  |  |  |  |

| 13:                           | end if                                                      |                                                  |  |  |  |  |

| 14:                           | <pre>context_select((long)id);</pre>                        | Contexts select and run their respective batches |  |  |  |  |

| 15:                           | return                                                      |                                                  |  |  |  |  |

| 16:                           | 16: end procedure                                           |                                                  |  |  |  |  |

# 2.5 Parallel KnightSim Modeling Methodology

Using Parallel KnightSim for the creation of parallelized computer architectural models starts out in the same manner as described in Sec. 2.3. Individual system simulation elements are modeled as regular KnightSim contexts. The developer then specifies the number of threads he or she wishes to utilize during simulation execution and assigns the contexts to individual threads. A Parallel KnightSim execution with a single thread specified is an equivalent execution to the nonparallelized version of KnightSim. However, Parallel KnightSim incurs additional overhead due to the introduction of thread management that is not present in the non-parallelized version of KnightSim. Therefore, it is recommended that the parallelized version of KnightSim not be used for sequential (single-threaded) executions.

An optimized approach to parallelizing an 8 CPU core simulation model with accompanying switching fabric and L1, L2, and L3 caches is shown in Fig. 2.2. In the figure, each box represents a single computer architectural simulation element that can be simulated by a single KnightSim context type as discussed in Sec. 2.3. The developer then divides up the contexts and assigns them to a target thread as illustrated by "Thread 1" and "Thread 2". This is done by assigning a thread ID to each context at initialization time thereby splitting the contexts into a context batch for thread 1 and a context batch for thread 2. This process can be done for any number of threads, however performance gains are dependent on producing an optimized thread to context batch ratio.

KnightSim Contexts form chains as they advance neighboring context's eventcounts and modify shared data structures. In the scope of a single thread only one context is ever running at a time, so, a thread's execution of its context batch can be treated as sequential execution. This means that thread safety is not of concern to a thread's local context batch. However, contexts that share data or eventcounts between two or more threads can run into classic multithreaded programming data hazards. The following subsection discuss ways to workaround these issues.

Figure 2.2: Parallel KnightSim Hazard Zones

## 2.5.1 Data Hazards

As discussed in Sec. 2.4, Parallel KnightSim automatically parallelizes event execution at the cycle level. However, data race conditions can occur between contexts that share data and that are being executed by two or more threads in a given cycle. Fig. 2.2 depicts where data races can occur and labels them as hazard zones. In this example the two threads share and modify data (e.g. eventcounts and input/output queues) related to the switches along the edge of each thread's context boundary as a result of one thread's switch advancing another thread's switch. Parallel KnightSim automatically accounts for internal thread safety issues by appropriately handling the advance and await of hazardous eventcounts. Developers are only required to specify at initialization time whether or not a particular context and its eventcount(s) are hazardous. The developer then only needs to be concerned about thread safety on the simulator side. For example, a modeled message queue that is shared between two contexts executed by two different threads could pose a thread safety issue.

On the simulation side, data race conditions can be avoided by assigning contexts that share data to the same context batch so that they are run by the same thread during execution. In places where a natural division of the contexts is not possible, the inclusion of fine-grained thread-safe techniques, such as mutexes and lock-free data structures, in only the hazard contexts will eliminate data race conditions. Another simple approach to avoid data hazards is to have paired hazardous contexts wait for execution on different sub-clocks. This approach guarantees that they do not execute at the same time and thus will not interfere with each other. Ultimately, optimized parallel simulation performance is gained by balancing the simulation model's size and simulated architectural structure with a properly specified number of threads and context-to-thread assignment. Developers should endeavor to reduce the number of serialization points in the architectural model, which will lead to better parallel performance gains.

### 2.6 KnightSim and Parallel KnightSim Performance Results

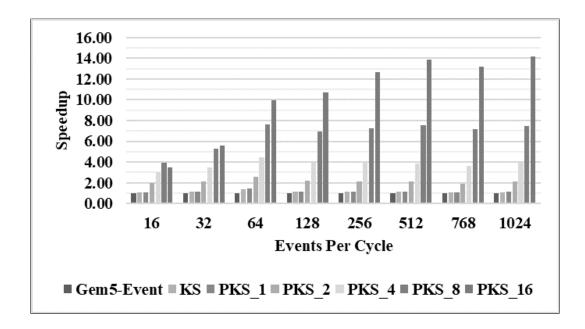

For performance evaluations, direct performance comparisons between KnightSim, Parallel KnightSim, and the discrete event-driven simulation engines found in Gem5 [21], Multi2Sim [15], and M2S-CGM [3] are made. Comparisons are made to this selection of discrete event-driven simulation engines because, at the time of authoring this dissertation, the simulators in which they are used are relevant, widely recognized, and have been used in recent computer architectural simulation related publications. For the purposes of these experiments, the discrete event-driven simulation engines found in Gem5, Multi2Sim, and M2S-CGM are referred to as Gem5-Event, Esim, and The Threads Package respectively. In the results, KnightSim and Parallel KnightSim are referred to as KS and PKS\_N respectively. For PKS, the "\_N" denotes the number of specified threads used in each PKS trial.

## 2.6.1 Experimental Setup

All experiments are conducted on a test system comprising a 16 core Intel Xeon E5-2697A v4 processor running at 2.6 GHz - 3.6 GHz with ample system memory running at 2400 MHz. In all test cases execution time is measured over the equivalent simulate() function. Measured execution times do not include time spent in regions of code associated with setup, initialization, or cleanup activities. Additionally, any non-essential code, like asserts, from each test application has been removed.

Gem5-Event and Esim employ a similar implementation approach that establishes an event list with associated callback functions upon initialization. During execution, events are scheduled to run in either the current cycle or a future cycle using an equivalent schedule\_event() function. Scheduled events are placed in a data structure and removed for execution at a later simulation cycle. Gem5-Event declares class objects as sim objects whose member functions can be declared as events. Therefore, I implement an event in Gem5-Event as a single class member function that is initially scheduled to run by the class's constructor during initialization time. Esim declares domain event handlers that are meant to handle a number of domain specific sub events. Thus, I implement an event in Esim as a single domain level event that is registered and scheduled to run at initialization time. For both Gem5-Event and Esim, each time an event is executed the event schedules itself to run again in one cycle.