Electronic Theses and Dissertations, 2004-2019

2019

## GaN Power Devices: Discerning Application-Specific Challenges and Limitations in HEMTs

Andrew Binder University of Central Florida

Part of the Electrical and Computer Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Binder, Andrew, "GaN Power Devices: Discerning Application-Specific Challenges and Limitations in HEMTs" (2019). *Electronic Theses and Dissertations, 2004-2019*. 6690. https://stars.library.ucf.edu/etd/6690

## GAN POWER DEVICES: DISCERNING APPLICATION-SPECIFIC CHALLENGES AND LIMITATIONS IN HEMTS

by

#### ANDREW BINDER

B.S. University of Arkansas, 2013

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2019

Major Professor: Jiann S. Yuan

© 2019 Andrew Binder

#### **ABSTRACT**

GaN power devices are typically used in the 600 V market, for high efficiency, high power-density systems. For these devices, the lateral optimization of gate-to-drain, gate, and gate-to-source lengths, as well as gate field-plate length are critical for optimizing breakdown voltage and performance. This work presents a systematic study of lateral scaling optimization for high voltage devices to minimize figure of merit and maximize breakdown voltage. In addition, this optimization is extended for low voltage devices (< 100 V), presenting results to optimize both lateral features and vertical features. For low voltage design, simulation work suggests that breakdown is more reliant on punchthrough as the primary breakdown mechanism rather than on vertical leakage current as is the case with high-voltage devices. A fabrication process flow has been developed for fabricating Schottky-gate, and MIS-HEMT structures at UCF in the CREOL cleanroom. The fabricated devices were designed to validate the simulation work for low voltage GaN devices. The UCF fabrication process is done with a four layer mask, and consists of mesa isolation, ohmic recess etch, an optional gate insulator layer, ohmic metallization, and gate metallization. Following this work, the fabrication process was transferred to the National Nano Device Laboratories (NDL) in Hsinchu, Taiwan, to take advantage of the more advanced facilities there. Following fabrication, a study has been performed on defect induced performance degradation, leading to the observation of a new phenomenon: trap induced negative differential conductance (NDC). Typically NDC is caused by self-heating, however by implementing a substrate bias test in conjunction with pulsed I-V testing, the NDC seen in our fabricated devices has been confirmed to be from buffer traps that are a result of poor channel carrier confinement during the dc operating condition.

#### **ACKNOWLEDGMENTS**

First, I would like to express thanks to my research advisor, Professor Jiann S. Yuan, whose guidance, support, and expert technical advice has made all this work possible. Professor Yuan has been an excellent advisor to me; he has given me incredible opportunities during my graduate studies, and provided essential lab resources and software tools to conduct the research work. I am deeply grateful for his guidance and support.

I would like to thank the members of my dissertation committee, Dr. Kalpathy Sundaram, Dr. Vikram Kapoor, Dr. Tania Roy, and Dr. Lee Chow for the assistance they provided and their time in evaluating my dissertation and providing valuable feedback. In addition I would like to thank Dr. Sundaram for his guidance and the opportunities he has given me along the way.

I am incredibly grateful to my industry mentors Dr. Patrick Shea and Dr. Balakrishnan Krishnan for their guidance on my projects and the professional advice they have given me. They have invested considerable time both in my academic and professional development; their profound knowledge on semiconductor devices and fabrication has been instrumental during the course of my research.

I am grateful to all my colleagues: Qutaiba Hasan, Aiman Salih, Wen Yang, Safayat Shochib, Sakeenah Khan, Jie Lin, and Shayan Taheri. Qutaiba has been a great friend with which I have had many great conversations and good laughs. I would like to thank my colleagues working on semiconductor devices, Wen, Aiman, Sakeenah, and Safayat, for the discussions and help in my research.

Lastly, I would like to thank my family, especially my wife Laura for her support, all the late night meals, and for her empathy and encouragement through the years. My parents have my deepest gratitude for their direction and guidance throughout my life.

## TABLE OF CONTENTS

| LIST ( | OF FIGURES                                           | • | <br> | ix  |

|--------|------------------------------------------------------|---|------|-----|

| LIST ( | OF TABLES                                            |   | <br> | xvi |

| CHAI   | PTER 1: INTRODUCTION                                 | • | <br> | . 1 |

| 1.1    | GaN Overview and Materials Advantages                |   | <br> | 1   |

| 1.2    | Heterostructure Design                               |   | <br> | 3   |

| 1.3    | Device Structures                                    |   | <br> | 5   |

|        | 1.3.1 Enhancement-Mode Structures                    |   | <br> | 6   |

|        | 1.3.2 Modern Device Structures                       |   | <br> | 8   |

| 1.4    | Failure Mechanisms                                   |   | <br> | 10  |

| 1.5    | Dissertation Organization                            | • | <br> | 12  |

| CHAI   | PTER 2: LATERAL SCALING AND OPTIMIZATION FOR HIGH-VO |   |      |     |

| 2.1    | Introduction                                         |   | <br> | 16  |

| 2.2    | Device Design and Simulation Model                   | • | <br> | 16  |

|        | 2.2.1 Theoretical Analysis                           | • | <br> | 16  |

|        | 2.2.2 Device Description                             |   |      | 17  |

| 2.3  | Result | s and Discussion                                                                                 | 19 |

|------|--------|--------------------------------------------------------------------------------------------------|----|

| 2.4  | Concl  | asion                                                                                            | 24 |

| СНАР |        | FABLESS DESIGN APPROACH FOR LATERAL OPTIMIZATION OF                                              |    |

|      |        | LOW VOLTAGE GAN POWER HEMTS                                                                      | 26 |

| 3.1  | Introd | uction                                                                                           | 26 |

| 3.2  | Device | e Structure and Simulation Methodology                                                           | 28 |

|      | 3.2.1  | GaN HEMT Device Structures                                                                       | 28 |

|      | 3.2.2  | Simulation Methodology and Simulation Parameters                                                 | 30 |

|      | 3.2.3  | Definitions for Parameter Extraction                                                             | 35 |

| 3.3  | Result | s and Discussion                                                                                 | 37 |

|      | 3.3.1  | Sentaurus Simulation: Design of Experiment                                                       | 37 |

|      | 3.3.2  | $\label{thm:continuous} \mbox{Gate-to-Drain Length: Breakdown Voltage and FOM Optimization} \ .$ | 42 |

|      | 3.3.3  | Gate Length: Breakdown Voltage and FOM Optimization                                              | 45 |

|      | 3.3.4  | Gate-to-Source Length: Breakdown Voltage and FOM Optimization                                    | 48 |

|      | 3.3.5  | Impact of On-State Resistance and Gate Charge Individually on FOM                                | 50 |

|      | 3.3.6  | Gate Field Plate and Discussion of Results                                                       | 51 |

| 3.4  | Conclu | asion                                                                                            | 52 |

| CHAP | TER 4: | EFFECTS OF HETEROSTRUCTURE DESIGN ON PERFORMANCE                                                 |    |

|      | FOR LOW VOLTAGE GAN POWER HEMTS                        | 54 |

|------|--------------------------------------------------------|----|

| 4.1  | Introduction                                           | 54 |

| 4.2  | Device Structure and Simulation Methodology            | 56 |

|      | 4.2.1 Device Structure                                 | 57 |

|      | 4.2.2 Simulation Methodology and Simulation Parameters | 59 |

|      | 4.2.3 Definitions for Parameter Extraction             | 62 |

| 4.3  | Results and Discussion                                 | 63 |

|      | 4.3.1 Channel Layer Optimization                       | 63 |

|      | 4.3.2 Barrier Layer Optimization                       | 67 |

|      | 4.3.3 AlN Interlayer Optimization                      | 71 |

|      | 4.3.4 Buffer Layer Optimization                        | 74 |

| 4.4  | Conclusion                                             | 75 |

| СНАР | PTER 5: GAN HEMT FABRICATION                           | 76 |

| 5.1  | UCF HEMT Fabrication Process                           | 76 |

|      | 5.1.1 UCF Mask - Test Structures                       | 81 |

| 5.2  | NDL Fabrication Process                                | 83 |

| 5.3  | Fabrication Results                                    | 88 |

|      | 5.3.1 UCF Devices                                      | 88 |

|         | 5.3.2   | NDL Devices                                       | 89  |

|---------|---------|---------------------------------------------------|-----|

| 5.4     | Concl   | usion                                             | 91  |

| СНАР    |         | EXPERIMENTAL RESULTS AND TRAP INDUCED PERFORMANCE |     |

|         |         | ANALYSIS                                          | 93  |

| 6.1     | Introd  | uction                                            | 93  |

| 6.2     | Device  | e Structure and Fabrication Details               | 95  |

| 6.3     | Result  | s and Discussion                                  | 95  |

|         | 6.3.1   | Static versus Pulse I-V Characterization          | 96  |

|         | 6.3.2   | Trap Characterization via Pulse I-V               | 99  |

|         | 6.3.3   | Substrate Biasing Effects                         | .00 |

| 6.4     | Summ    | nary                                              | .06 |

| СНАР    | TER 7:  | CONCLUSION                                        | .08 |

| APPE    | NDIX :  | UCF FABRICATION PROCESSING STEPS                  | .1( |

| I ICT C | SE DEEI | EDENICEC 1                                        | 10  |

## LIST OF FIGURES

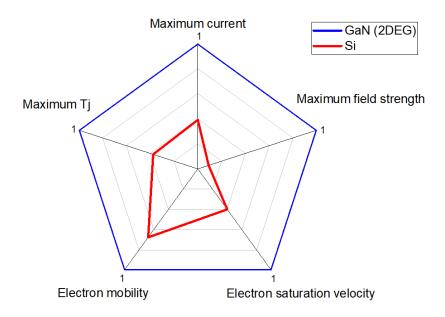

| 1.1 | Merits of using GaN compared to silicon from a materials perspective.     | 2  |

|-----|---------------------------------------------------------------------------|----|

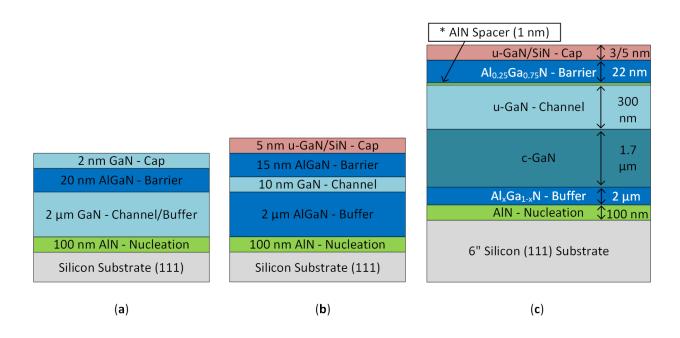

| 1.2 | GaN heterostructure types showing (a) the single heterostructure (Al-     |    |

|     | GaN/GaN), (b) the double heterostructure (AlGaN/GaN/AlGaN),               |    |

|     | and (c) an advanced double heterostructure design                         | 3  |

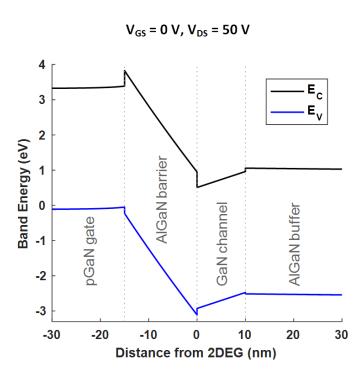

| 1.3 | Energy band diagram for an enhancement-mode AlGaN/GaN HEMT.               | 5  |

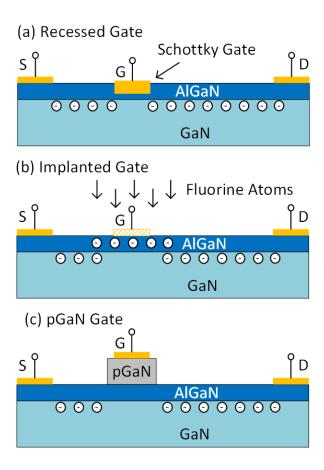

| 1.4 | Enhancement-mode structures for AlGaN/GaN devices showing (a)             |    |

|     | recessed gate, (b) implanted gate, and (c) pGaN gate technologies         | 6  |

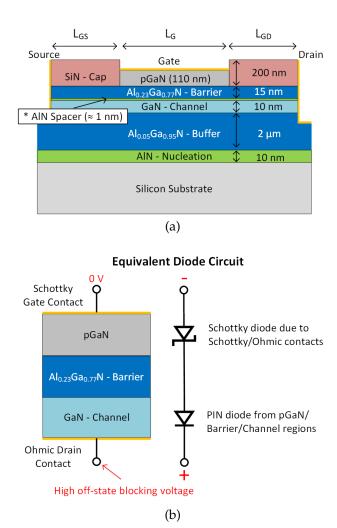

| 1.5 | (a) Device structure for a pGaN gate HEMT and (b) equivalent circuit      |    |

|     | model of series diodes for off-state operation                            | 7  |

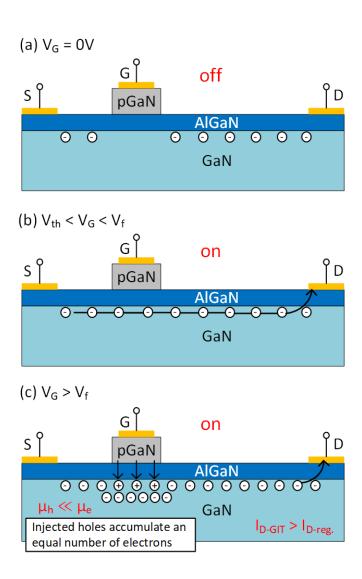

| 1.6 | Gate injection transistor (GIT) operating with (a) zero gate voltage, (b) |    |

|     | in the on-state but below the forward voltage, and (c) in the on-state in |    |

|     | injection condition                                                       | 8  |

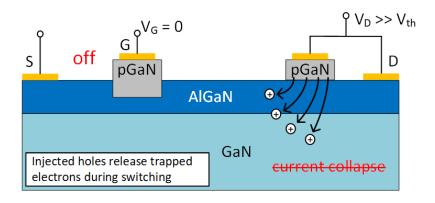

| 1.7 | HD-GIT device operating in the off-state                                  | 10 |

| 1.8 | (a) Failure mechanisms in GaN HEMTs and (b) leakage current evalua-       |    |

|     | tion of breakdown mechanisms                                              | 11 |

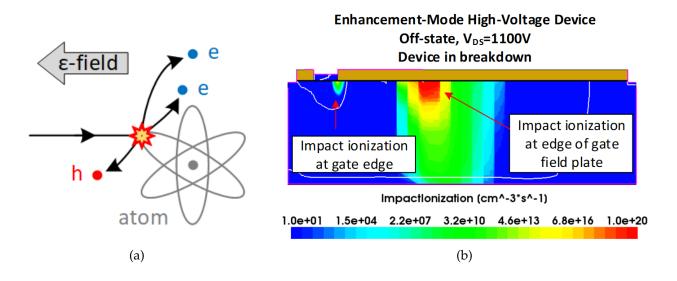

| 1.9 | (a) Simplified impact ionization model and (b) impact ionization oc-      |    |

|     | curring in a high voltage device.                                         | 12 |

| 2.1 | Cross-section representation of proposed AlGaN/GaN/AlGaN enhancement              | ent |

|-----|-----------------------------------------------------------------------------------|-----|

|     | mode DHFET with gate field plate                                                  | 18  |

| 2.2 | Breakdown voltage and FOM analysis for DHFET-based device at $L_{\it GFP}$        |     |

|     | = 5 μm                                                                            | 19  |

| 2.3 | Electric field profiles of proposed DHFET with gate field plate for $L_{\it GFP}$ |     |

|     | = 5 μm                                                                            | 20  |

| 2.4 | Electric field profiles as $L_{GD}$ is reduced                                    | 21  |

| 2.5 | Breakdown voltage and FOM as a function of $L_{GD}$ and $L_{GFP}$                 | 21  |

| 2.6 | Optimization plots for breakdown voltage and figure of merit                      | 22  |

| 2.7 | 3D optimization of breakdown voltage as a function of FOM, $L_{GFP}$ ,            |     |

|     | and $L_{GD}$ for proposed DHFET                                                   | 23  |

| 2.8 | Optimization of on-state resistance and gate charge as a function of              |     |

|     | $L_{GD}$ and $L_{GFP}$                                                            | 24  |

| 3.1 | (a) Single heterostructure: the most basic design; (b) double heterostruc-        |     |

|     | ture: has improved breakdown voltage and on-state resistance per-                 |     |

|     | formance compared to single heterostructure design; (c) advanced                  |     |

|     | heterostructure design builds off the double heterostrucuture and in-             |     |

|     | cludes a carbon doped semi-insulating layer and thicker channel region            |     |

|     | to reduce defect density near channel                                             | 29  |

| 3.2 | Enhancement mode, p-GaN gate, DHFET structure used in simulations.                | 30  |

| 3.3 | Equivalent circuit model of series diodes for off-state operation                 | 31  |

| 3.4  | applied bias                                                                                                                                                                                                           | 34 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Breakdown voltage shown both in linear (a) and log (b) scales                                                                                                                                                          | 36 |

| 3.6  | Curves used to extract $R_{DS(on)}$ (a) and $Q_G$ (b)                                                                                                                                                                  | 36 |

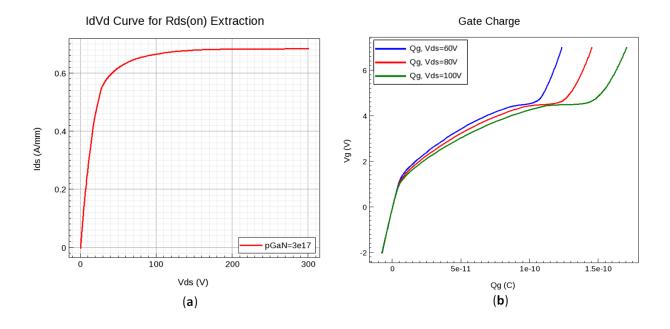

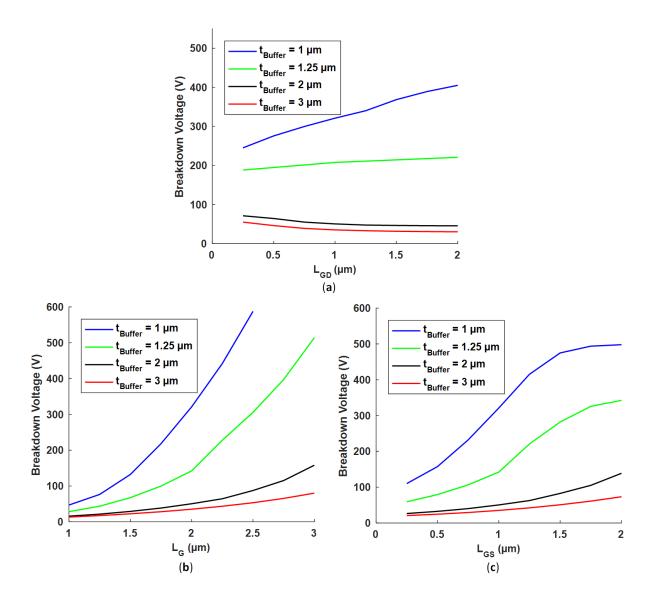

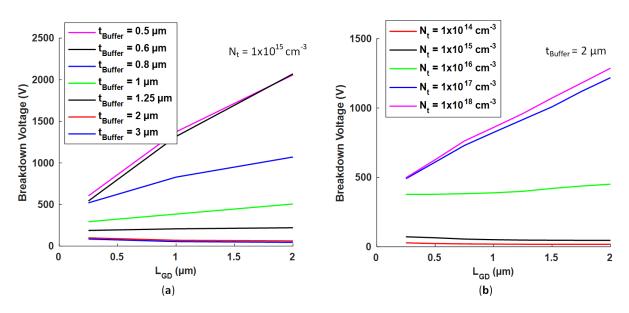

| 3.7  | Simulation results for $L_{GD}$ (a), $L_{G}$ (b), and $L_{GS}$ (c) demonstrating the impact of buffer layer thickness on breakdown voltage                                                                             | 39 |

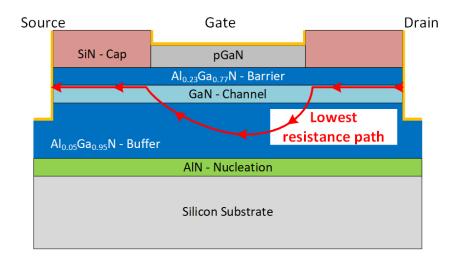

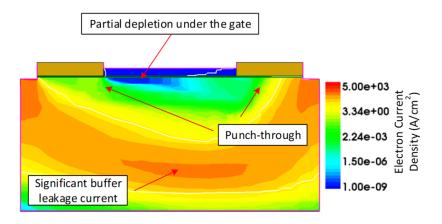

| 3.8  | (a) for high voltage devices: breakdown is caused by parasitic conduction at the buffer/substrate interface; (b) for medium to low voltage devices: breakdown can be caused by buffer leakage current or punchthrough. | 41 |

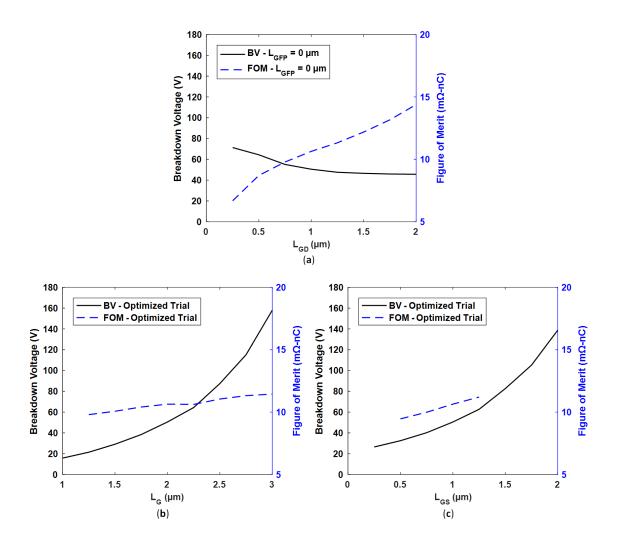

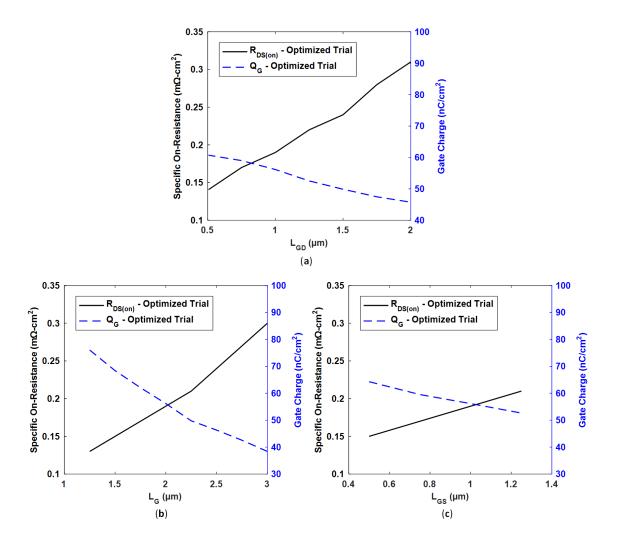

| 3.9  | Simulation results for $L_{GD}$ (a), $L_{G}$ (b), and $L_{GS}$ (c) presenting breakdown voltage and FOM trends to enable optimization of device performance                                                            | 42 |

| 3.10 | Influence of buffer thickness (a) and buffer trap density (b) on breakdown voltage                                                                                                                                     | 43 |

| 3.11 | Lowest resistance current leakage path for device in off-state                                                                                                                                                         | 44 |

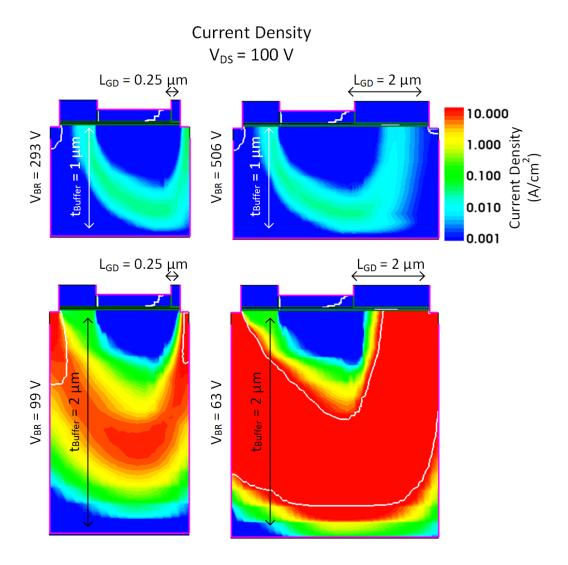

| 3.12 | Current density plots showing breakdown voltage as buffer thickness and gate-to-drain distance vary                                                                                                                    | 46 |

| 3.13 | Cross-section view of leakage current contributing to breakdown in the off-state                                                                                                                                       | 47 |

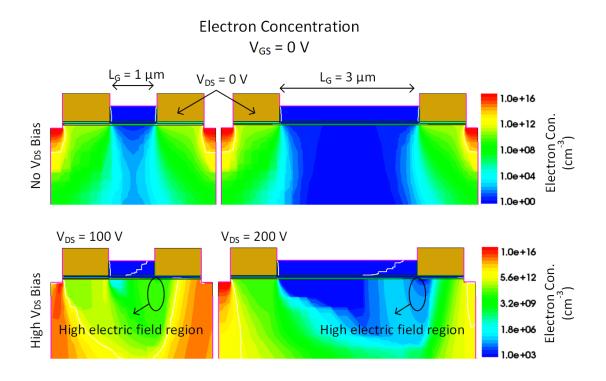

| 3.14 | Larger gate length suppresses punch-through and lowers impact ionization.                                                                                                                                              | 47 |

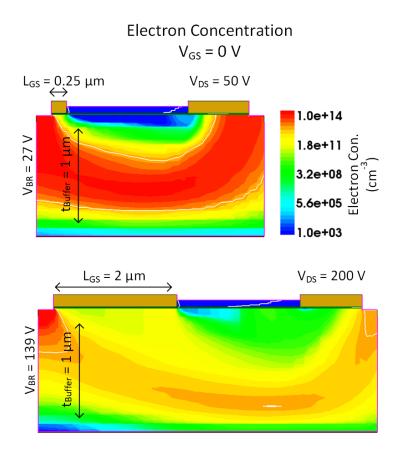

| 3.15 | Longer gate-to-source length increases buffer resistance and there-by                  |    |

|------|----------------------------------------------------------------------------------------|----|

|      | increases breakdown voltage                                                            | 48 |

| 3.16 | Lateral scaling effect for on-state resistance and gate charge for $L_{GD}$            |    |

|      | (a), $L_G$ (b), and $L_{GS}$ (c)                                                       | 49 |

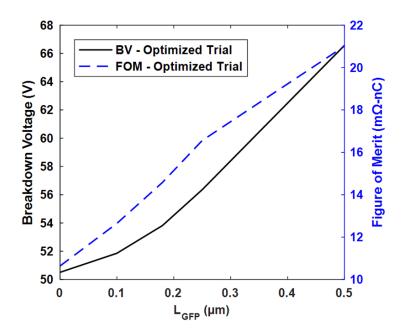

| 3.17 | Simulation results for $L_{GFP}$ presenting breakdown voltage and FOM                  |    |

|      | trends to enable optimization of device performance ( $L_{GD}=L_{GFP}+1$               |    |

|      | μm)                                                                                    | 52 |

| 4.1  | Enhancement mode, p-GaN gate, DHFET structure used in simulations.                     | 58 |

| 4.2  | Example of the HD-GIT structure showing (a) gate injection operation                   |    |

|      | in on-state to increase drain current and (b) hybrid-drain injection of                |    |

|      | holes in off-state to eliminate current collapse.                                      | 59 |

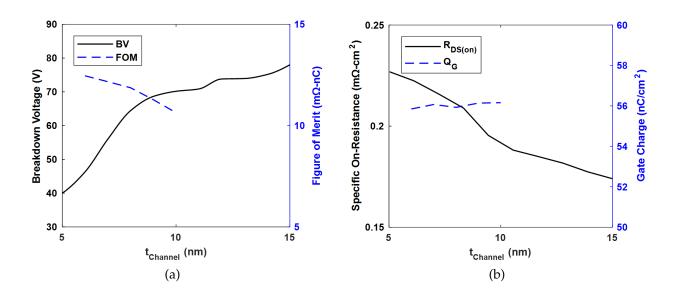

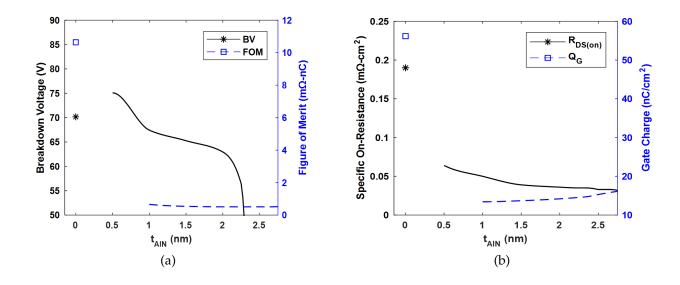

| 4.3  | Simulation results for $t_{Channel}$ presenting (a) breakdown voltage and              |    |

|      | FOM trends as well as (b) on-state resistance and gate charge trends                   | 64 |

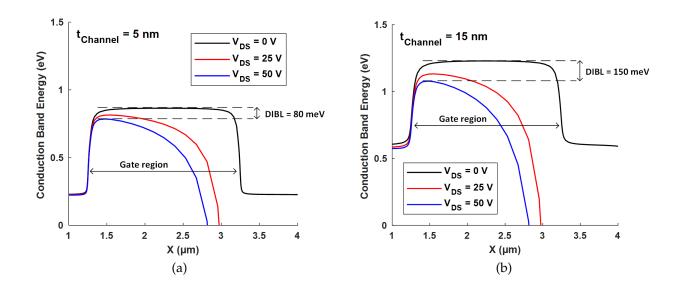

| 4.4  | Drain-induced-barrier-lowering increases as the channel thickness in-                  |    |

|      | creases showing (a) $t_{Channel} = 5 \text{ nm}$ and (b) $t_{Channel} = 15 \text{ nm}$ | 65 |

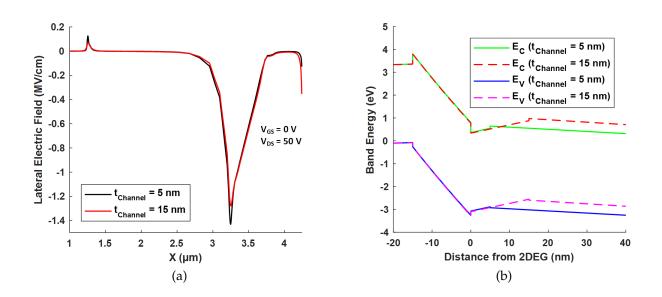

| 4.5  | (a) Lateral electric field calculated along the channel/buffer interface               |    |

|      | with different channel thickness values (5 nm and 15 nm). (b) Energy                   |    |

|      | band diagrams for $t_{Channel}$ = 5 nm and 15 nm in off-state with 50 V                |    |

|      | applied bias                                                                           | 67 |

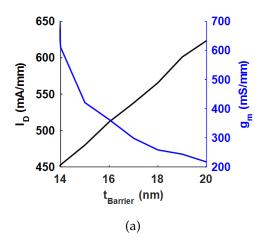

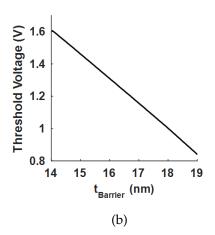

| 4.6  | Simulation results for $t_{Barrier}$ presenting (a) maximum drain current              |    |

|      | and transconductance as well as (b) threshold voltage trends                           | 69 |

| 4.7  | Simulation results for $t_{Barrier}$ presenting (a) breakdown voltage and      |    |

|------|--------------------------------------------------------------------------------|----|

|      | FOM trends as well as (b) on-state resistance and gate charge trends           | 70 |

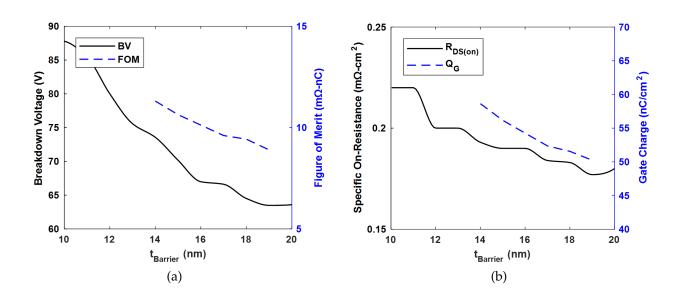

| 4.8  | Simulation results for $x_{AlGaN}$ presenting (a) breakdown voltage and        |    |

|      | FOM trends as well as (b) on-state resistance and gate charge trends           | 71 |

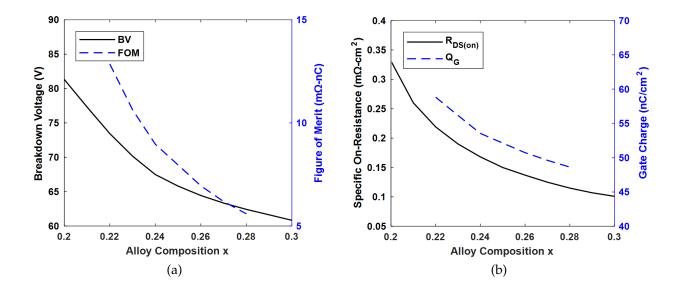

| 4.9  | Simulation results for $t_{AlN}$ presenting (a) breakdown voltage and FOM      |    |

|      | trends as well as (b) on-state resistance and gate charge trends               | 72 |

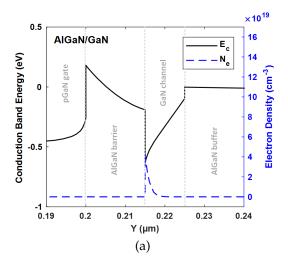

| 4.10 | Simulation results showing conduction band energy and electron den-            |    |

|      | sity in the on-state for devices with (a) no AlN interlayer and (b) with       |    |

|      | a 1.5 nm AlN interlayer                                                        | 73 |

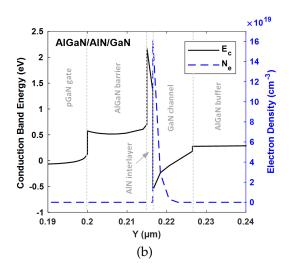

| 5.1  | A simplified fabrication process flow for the UCF Schottky-gate GaN            |    |

|      | HEMTs                                                                          | 78 |

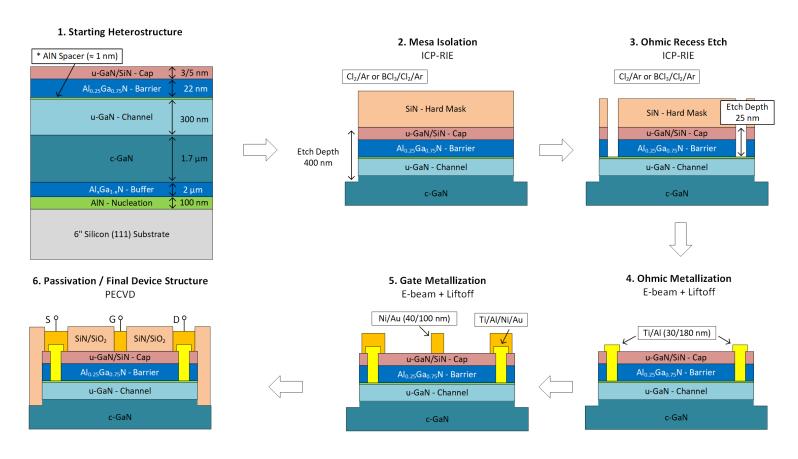

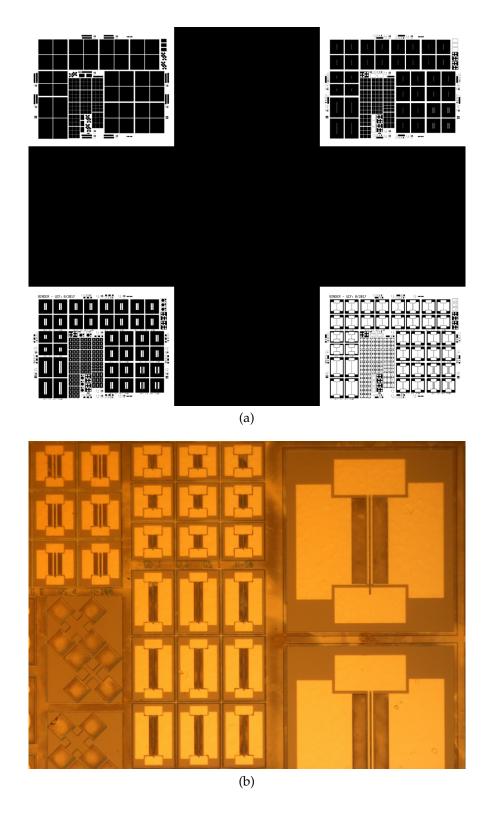

| 5.2  | (a) Double finger mask design for UCF HEMTs, (b) mask legend for               |    |

|      | the UCF HEMT four layer mask, and (c) UCF GaN HEMT photomask                   |    |

|      | on 4" quartz plate                                                             | 79 |

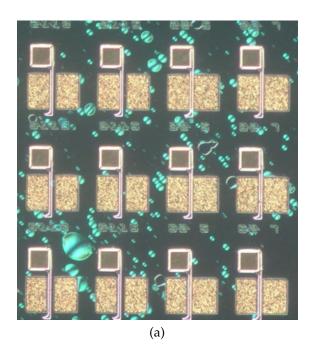

| 5.3  | (a) Actual four layer mask design image and (b) microscope image of            |    |

|      | UCF devices after all fabrication steps are complete                           | 80 |

| 5.4  | (a) Hall-effect test structure and (b) Schottky junction diode test structure. | 81 |

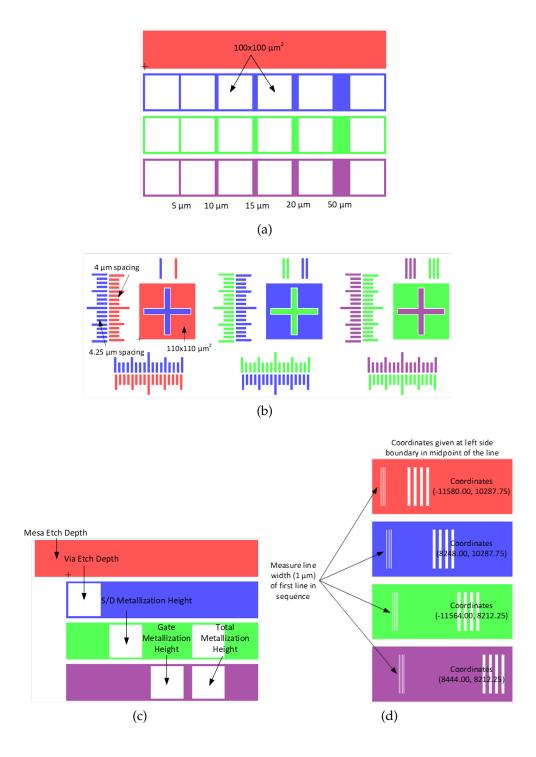

| 5.5  | (a) TLM test structure, (b) alignment test structure, (c) profile/height       |    |

|      | test structure, and (d) linewidth test structure                               | 82 |

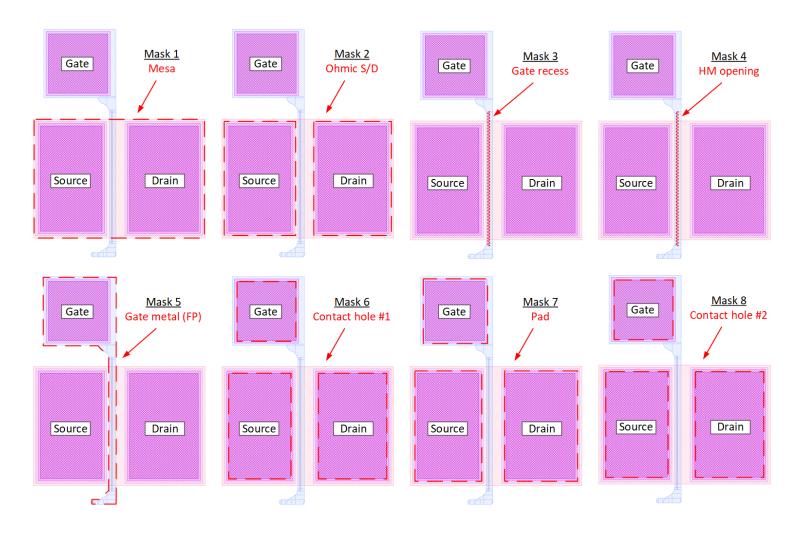

| 5.6  | The 8-layer mask used at NDL for HEMT fabrication                              | 85 |

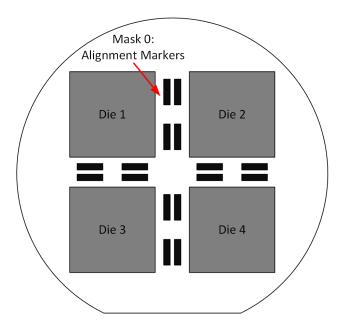

| 5.7  | Example drawing of mask 0 with sample alignment marker blocks                  | 86 |

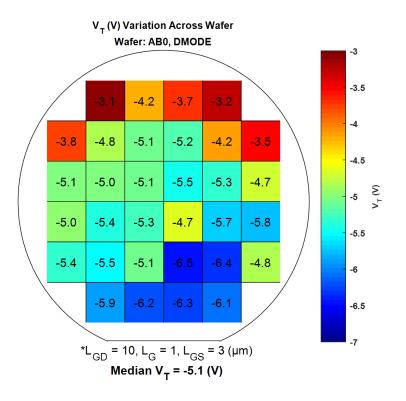

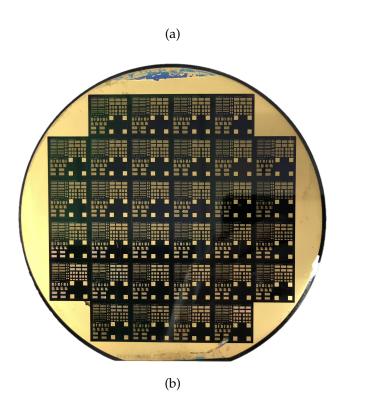

| 5.8  | (a) Threshold voltage mapping of NDL wafer "AB0" for d-mode de-                 |    |

|------|---------------------------------------------------------------------------------|----|

|      | vices and (b) wafer image of AB0                                                | 37 |

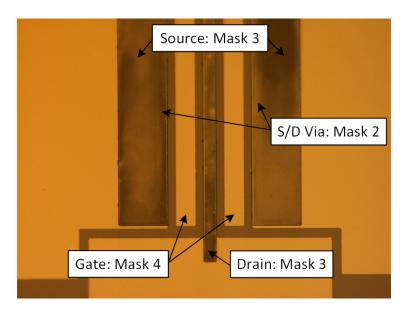

| 5.9  | UCF GaN HEMT before high temperature annealing, showing features                |    |

|      | from each mask layer                                                            | 38 |

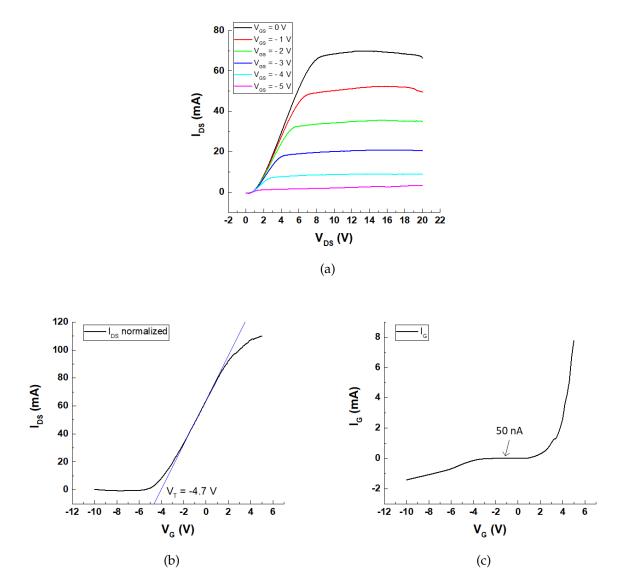

| 5.10 | Curves for UCF d-mode MIS-HEMT devices showing (a) normalized                   |    |

|      | drain current versus drain voltage curves, (b) normalized drain current         |    |

|      | versus gate voltage plot, and (c) gate current versus gate voltage plot   8     | 39 |

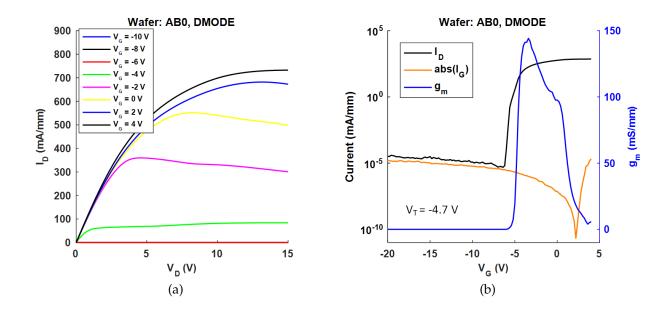

| 5.11 | Curves for NDL d-mode MIS-HEMT devices showing (a) plot of drain                |    |

|      | current versus drain voltage, and (b) plot of drain and gate current and        |    |

|      | transconductance versus gate voltage                                            | €  |

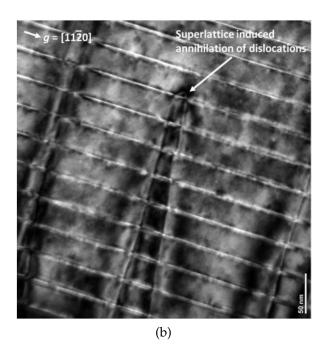

| 5.12 | (a) NDL devices showing passivation layer pitting and peeling on the            |    |

|      | surface and (b) superlattice induced annihilation of dislocations 9             | 91 |

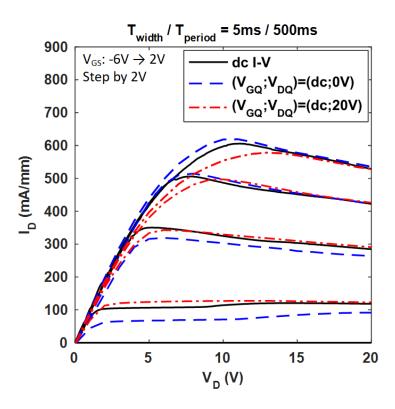

| 6.1  | Pulse versus dc I-V characteristics for AlGaN/GaN HEMT: showing                 |    |

|      | degradation due to trapping effects                                             | 97 |

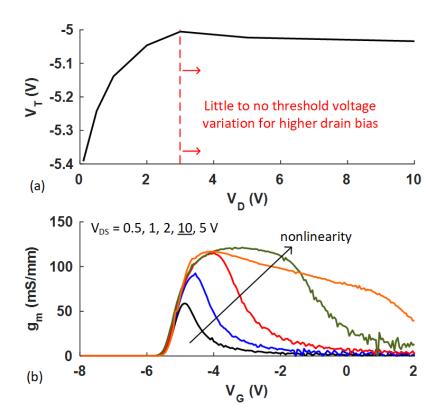

| 6.2  | (a) Threshold voltage variation due to drain voltage bias. (b) Non-             |    |

|      | linear transconductance profiles due to velocity reduction in the chan-         |    |

|      | nel                                                                             | 98 |

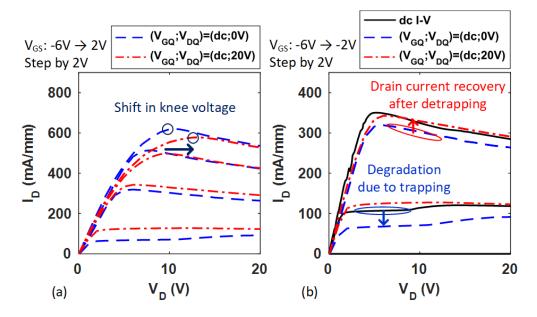

| 6.3  | (a) Pulse $I_D$ - $V_D$ characterization showing a shift in knee voltage due    |    |

|      | to starting drain bias. (b) Trapping and recovery phenomena due to              |    |

|      | drain current pulse polarity                                                    | )0 |

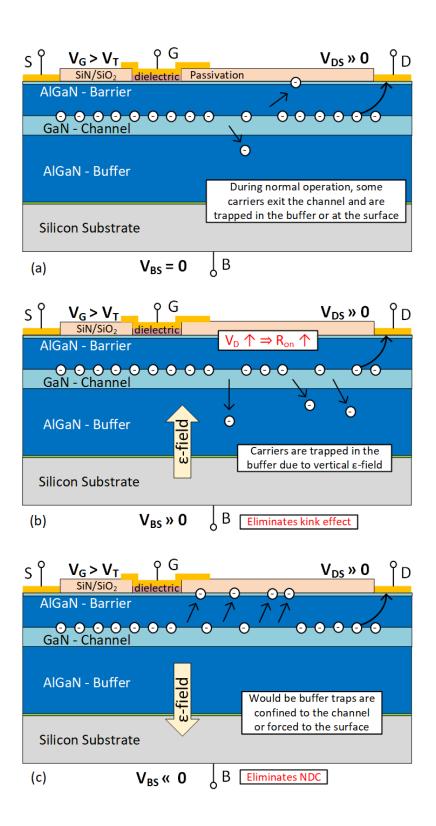

| 6.4  | Effect of substrate bias on trap distribution within the device at (a) $V_{BS}$ |    |

|      | = 0 V, (b) $V_{BS} \gg 0$ V, and (c) $V_{BS} \ll 0$ V                           | )2 |

| 6.5 | (a) Reverse drain voltage sweep showing eliminated NDC with $V_{BS}$ =           |

|-----|----------------------------------------------------------------------------------|

|     | -50V. Forward and reverse DC I-V characteristics with $V_{BS}$ biased at (b)     |

|     | 0V, (c) 50V, and (d) -50V                                                        |

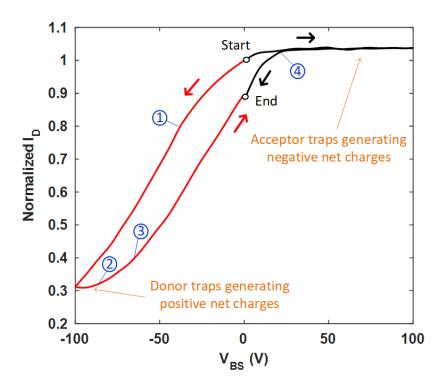

| 6.6 | Substrate bias sweep with $I_D$ normalized to the value at $V_{GS}=0V$ ,         |

|     | $V_{DS} = 10V$ , and $V_{BS} = 0V$ . Red line represents the reverse bias sweep, |

|     | followed by 12 hour rest for trap recovery and then the forward sweep            |

|     | shown in black                                                                   |

## LIST OF TABLES

| 2.1 | Design Parameters for Lateral Layer Stack-Up                                             | 19 |

|-----|------------------------------------------------------------------------------------------|----|

| 3.1 | Doping Concentration and Specified Impurity Species                                      | 32 |

| 3.2 | Properties of Specified Traps in Simulated Structure                                     | 32 |

| 3.3 | Physics Models for Sentaurus Simulation                                                  | 33 |

| 3.4 | Default Benchmark Values for Simulation Trials                                           | 38 |

| 4.1 | Default Benchmark Values for Simulation Trials and Varied Dimensions for Each Experiment | 60 |

| 4.2 | Doping Concentration and Specified Impurity Species                                      | 61 |

| 4.3 | Properties of Specified Traps in the Simulated Structure                                 | 62 |

| 4.4 | Influence of Individual Components on Breakdown as Channel Thickness Increases           | 67 |

| 4.5 | Summary of Factors Influenced by AlGaN Barrier Thickness                                 | 68 |

#### **CHAPTER 1: INTRODUCTION**

The power electronics industry is driven by device miniaturization and system power density improvements, both of which are enabled by wide bandgap (WBG) device technology. When evaluating WBG technology, Gallium Nitride (GaN) heterojunction devices have superior material characteristics compared to Silicon Carbide (SiC) devices: although both enable higher operating frequency and higher voltage operation than silicon-based electronics [1]. According to a market report by P&S Market Research [2], GaN is expected to be the major wide bandgap competitor for silicon for device ratings less than 600 V. This is due in part to the miniaturization enabled by wide bandgap technology, and also due to the higher performance and lower figure of merit ( $R_{DS(on)} \times Q_G$ ) of GaN devices compared to silicon. Despite these advantages, GaN devices still have extensive hurdles to overcome before they can replace silicon: chiefly including a comparative manufacturing cost and significant long-term reliability concerns.

This chapter presents an overview of GaN materials advantages, heterostructure design, a synopsis of modern device structures, and introduces some prominent failure mechanisms for GaN HEMTs. In addition, an outline of this work is presented at the end of the chapter.

#### 1.1 GaN Overview and Materials Advantages

As mentioned, compared to silicon, GaN has superior material characteristics which allow for higher frequency operation, and higher breakdown voltage. This is due to reduced switching loss from the higher mobility and saturation velocity, and reduced conduction losses since the device length can be reduced for the same given breakdown voltage due to a higher critical electric field. Figure 1.1 presents an overview of the merits of using GaN compared to silicon with the graph normalized to the properties of GaN to show scale.

Figure 1.1: Merits of using GaN compared to silicon from a materials perspective.

The channel in AlGaN/GaN devices is composed of a two dimensional electron gas (2DEG) which is created by spontaneous and piezoelectric polarization due to lattice mismatch between the two respective layers. This 2DEG has a higher mobility than that of bulk GaN. Compared to silicon devices in which the channel is formed by doping a region, in GaN the channel is naturally formed and requires no doping. This means there is no impact on carrier mobility and velocity due to impurity scattering resulting from doping: leading to a very high channel electron mobility.

Figure 1.2: GaN heterostructure types showing (a) the single heterostructure (Al-GaN/GaN), (b) the double heterostructure (AlGaN/GaN/AlGaN), and (c) an advanced double heterostructure design.

#### 1.2 Heterostructure Design

Lateral GaN transistors require a multi-layer heterostructure design which is highly dependent on the starting wafer used for growth. GaN is most commonly grown on silicon but also can be grown on silicon carbide or sapphire. Due to the lack of availability, the high cost, and small wafer size, GaN wafers are very rarely used in GaN processing, especially for lateral transistors. GaN is most commonly grown by metal organic chemical vapor deposition (MOCVD). Concerning heterostructure design, a standard baseline structure is shown in Figure 1.2(a); this structure is typical for GaN-on-Si wafers. Silicon substrates give cost and availability advantages compared to SiC or sapphire substrates, although GaN-on-silicon has a larger lattice mismatch compared to SiC or sapphire. The large lattice mismatch will cause poor quality GaN growth on Si, so to facilitate better bonding, a nucleation (seed) layer is needed. For GaN-on-Si wafers, AlN is typically used as the

nucleation layer. On top of the nucleation layer, the channel/buffer region is grown, with a typical defect density of  $10^9$  cm<sup>-3</sup>. The interface between the channel and barrier layer is where the 2DEG forms, which lies on the channel side of the interface.

Concerning heterostructure design, Figure 1.2(b) depicts a double heterostructure (Al-GaN/GaN/AlGaN). The double heterostructure results in better breakdown voltage and on-state resistance performance compared to the single heterostructure. This is due to improved channel carrier confinement, decreasing buffer leakage, and a higher critical electric field of the buffer layer which improves breakdown voltage.

Finally, there are some advanced structure design considerations which can result in improved reliability and performance (Figure 1.2(c)). Typically a carbon doped GaN layer is used below the channel region. Carbon doping makes the region more semi-insulating, which prevents current punch-through at high electric fields, and also helps to confine the 2DEG. A carbon doped "back barrier" will improve breakdown voltage at the expense of increased dynamic on-state resistance. Doping with carbon creates trap sites in GaN, which can act as acceptor- or donor-like traps depending on whether carbon serves as an interstitial for gallium or nitrogen in the GaN lattice. These traps can lead to current collapse and will adversely impact reliability and breakdown performance. Carbon doping can be done by modifying the temperature of the growth process, where a low temperature process results in more carbon in the GaN lattice, and a high temperature process results in better quality GaN with less carbon.

In addition to carbon doping, another way to improve electrical characteristics is to add an AlN spacer between the AlGaN barrier and GaN channel. The AlN interlayer will increase electron density in the channel, and can improve interface roughness, leading to an increase in mobility. The thickness of the AlN interlayer is critical however, as a thick layer can cause structural degradation due to partial strain relaxation.

Lastly, a superlattice buffer can be used to reduce defect and mismatch compared to a typical graded AlGaN buffer structure. These layers are intended for stress relief, which also can improve passivation adhesion, resulting in fewer surface states. The trade-off for a superlattice buffer is a reduced thermal performance compared to a graded buffer structure.

#### 1.3 Device Structures

Figure 1.3: Energy band diagram for an enhancement-mode AlGaN/GaN HEMT.

AlGaN/GaN devices are naturally depletion-mode, meaning they are normally on devices. These devices require structure changes to make them enhancement-mode, or normally off devices. For power electronics, it is necessary to use enhancement-mode devices so that if there is a circuit failure the system will fail in the off-state rather than in the on-state which can be dangerous and destructive when under load. An enhancement-mode device has a band diagram like the one seen in Figure 1.3, where the 2DEG quantum-well formed

at the barrier/channel interface is above the Fermi level, and thus depleted. In this section we will discuss enhancement-mode structures, and present some more modern device structures used in GaN power device design.

#### 1.3.1 Enhancement-Mode Structures

Figure 1.4: Enhancement-mode structures for AlGaN/GaN devices showing (a) recessed gate, (b) implanted gate, and (c) pGaN gate technologies.

There are three common techniques for create an enhancement-mode device: recessed gate, implanted gate, and pGaN gate. These structures are shown in Figure 1.4. The pGaN gate enhancement-mode structure is by far the most common of the three. From a fabrication perspective it is the most reliable, as recess gate has threshold voltage instability

issues and implanted gate can contribute to trapping issues leading to reliability concerns. However, pGaN gate devices suffer from more gate leakage than recessed or implanted gate structures.

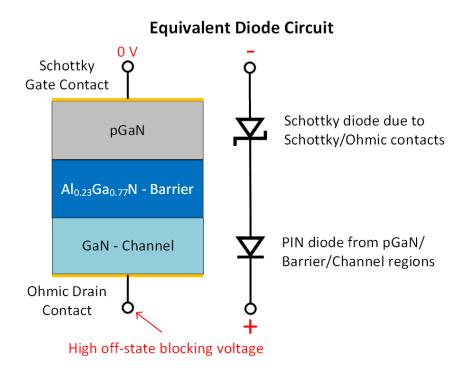

Figure 1.5: (a) Device structure for a pGaN gate HEMT and (b) equivalent circuit model of series diodes for off-state operation.

In the pGaN gate structure (shown in Figure 1.5(a)), a p-doped GaN layer is grown on top of the AlGaN barrier which serves to deplete the channel under the gate. This p-doped GaN layer along with the AlGaN barrier and GaN channel together forms a pin-diode, which can add about 10  $\mu$ A/mm of gate current. Replacing the ohmic gate contact with a Schottky contact will significantly reduce the on-state gate current as the Schottky-diode

is now in series with the *pin*-diode (Figure 1.5(b)), thereby increasing the diode forward voltage and reducing the gate current. The Schottky-gate pGaN HEMT is a popular method for achieving low off-state leakage currents and normally-off operation. A combination of gate recess and pGaN (or pAlGaN) doping can be used to further improve threshold voltage.

#### 1.3.2 Modern Device Structures

Figure 1.6: Gate injection transistor (GIT) operating with (a) zero gate voltage, (b) in the on-state but below the forward voltage, and (c) in the on-state in injection condition.

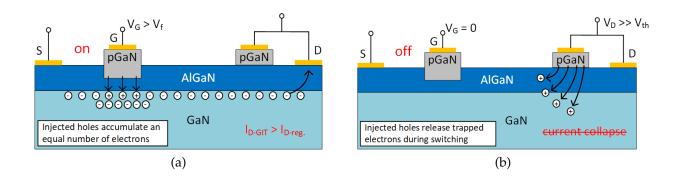

Two spin-offs of the pGaN gate structure are the gate injection transistor (GIT) and the hybrid-drain gate injection transistor (HD-GIT). Both build on the principles of pGaN gate operation, but provide unique advantages to aid in device operation and reliability. The gate injection transistor (Figure 1.6) provides the benefit of conductivity modulation (higher  $I_{DS}$ ), but comes at the cost of a larger gate current compared to the conventional pGaN gate device. The GIT has three modes of operation: the off-state at  $V_G = 0V$ , the on-state at  $V_{th} < V_G < V_f$ , and the injection state at  $V_G > V_f$ . In the off-state and on-state, the device operates just as a conventional pGaN gated device. However, if the gate voltage exceeds the series diodes forward voltage the gate will inject holes into the device. Due to charge neutrality, the injected holes accumulate an equal number of electrons in the channel, which increases  $I_{DS}$ . The accumulated electrons increase current density, but the injected holes mostly stay around the gate area and do not significantly contribute to the drain current. This is due to a large mobility imbalance between holes and electrons: hole mobility is at least two orders of magnitude lower than electron mobility.

The HD-GIT is designed to eliminate current collapse by adding an additional pGaN region near the drain. This hybrid drain serves to inject holes under the drain in the off-state condition with a high drain bias, effectively releasing trapped electrons during the process of switching. This solves the current collapse issue and can be used for high voltage (600V) devices. One drawback of this approach is that it uses both pGaN gate and gate recess technology to make the device enhancement-mode. For the HD-GIT structure, the AlGaN barrier layer needs to be roughly twice as thick compared to a normal pGaN gate structure. This is so that the pGaN hybrid drain does not deplete the channel and act as a second gate. From a fabrication perspective this complicates things, as it requires etching and regrowth of a pGaN layer, and it also introduces possible threshold voltage variation issues as are seen with gate recess devices. The HD-GIT structure can be seen in Figure 1.7.

Figure 1.7: HD-GIT device operating in the off-state.

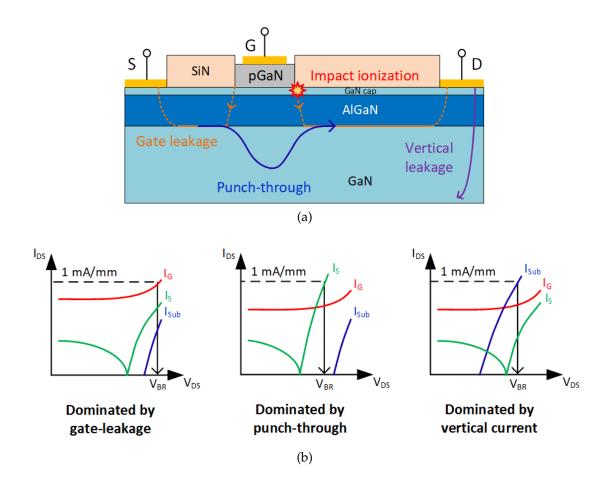

#### 1.4 Failure Mechanisms

As a significant portion of this work covers device optimization in regards to performance and breakdown, it is prudent to cover some prominent failure mechanisms in the introduction. GaN devices primarily suffer from a few dominant failure mechanisms, although each of these mechanisms may contribute to other failure modes. Failure mechanisms can be isolated by the dominant leakage current path: whether gate-leakage, drain- or source-leakage, or substrate-leakage. This leakage can be due to punch-through, impact ionization, gate leakage, or vertical leakage paths within the device. These failure mechanisms are depicted in Figure 1.8(a). To evaluate the source of the failure mechanisms the leakage current can be examined, and the dominate leakage path can point towards impact ionization, punch-though, or vertical leakage current depending on the source. An example of this is given in Figure 1.8(b).

Vertical leakage current is due to breakdown at the silicon substrate, as silicon has a much lower critical electric field than GaN. This can be avoided by proper buffer thickness optimization. This tends to be a dominant breakdown factor for high voltage devices, thus buffer thickness is a critical factor to high voltage design.

Figure 1.8: (a) Failure mechanisms in GaN HEMTs and (b) leakage current evaluation of breakdown mechanisms.

Punch-through occurs in off-state at a high drain bias, where electrons travel through the bulk underneath the turned-off gate and "punch-though" what should be a depleted region below the gate. This buffer leakage current can be a large contributor to off-state  $I_{DS}$ . Solutions to reduce punch-through include increasing the gate length, making the buffer more semi-insulating (e.g. carbon doping), or reducing the trap density in the buffer. This issue will be discussed in more detail in Chapter 3.

Impact ionization occurs at the drain-side gate edge, or at the edge of the gate-fieldplate. A high electric field causes high-energy electrons to knock other electrons out of the valence band into the conduction band: creating electron-hole pairs and raising the current (depicted in Figure 1.9(a)). This may continue to avalanche condition, resulting in unrecoverable breakdown. To reduce impaction ionization, electric-field peaks and hotspots must be reduced. This can be done by multiple field-plate structures. An example of impact ionization occurring in a high-voltage device is shown in Figure 1.9(b).

Figure 1.9: (a) Simplified impact ionization model and (b) impact ionization occurring in a high voltage device.

#### 1.5 Dissertation Organization

The outline of this work is as follows:

Chapter 2 covers lateral optimization trends for high voltage (> 600V) GaN HEMTs. Drift length and length of the gate field plate are scaled to exhibit the influence of these terms on the on-state resistance, gate charge, and breakdown voltage. Novelty of this study comes from a comprehensive look at drift length and field plate optimization for high voltage and low figure of merit designs. This optimization maps out  $R_{DS(on)}$  and  $Q_G$  to suggest designs which optimize

conduction losses versus switching losses for specificity in power electronics system design.

- Chapter 3 presents a fabless design approach for lateral optimization of low voltage GaN power HEMTs. This optimization covers lateral scaling terms including gate-to-drain, gate, and gate-to-source lengths to minimize figure of merit for a target breakdown voltage. Low voltage design optimization showed heavy influence of buffer trap density and thickness on breakdown performance.

- Chapter 4 gives insight into heterostructure design and the impact on performance for low voltage GaN power HEMTs. Low voltage simulations reveal less dependence on vertical leakage current and substrate breakdown compared to high voltage designs, and more reliance on buffer leakage and punch-through as the dominant factors leading to breakdown. Optimization curves are presented for breakdown voltage, on-state resistance, and gate charge. Trends are presented for the optimization of the channel layer thickness, barrier layer thickness and molar fraction, impact of an AlN interlayer, and optimization of buffer layer thickness.

- Chapter 5 covers the fabrication strategy for Schottky-gate and MIS-HEMT device fabrication in the UCF CREOL cleanroom. This chapter also covers the fabrication effort through collaboration at the National Nano Device Laboratories in Hsinchu, Taiwan.

- Chapter 6 introduces a new phenomenon discovered during testing of our fabricated devices: trap induced negative differential conductance. Negative differential conductance (NDC) seen in the drain current saturation region is typically attributed to selfheating effects in GaN HEMTs. In this chapter, it is demonstrated that NDC is due to trap states in the buffer resulting from poor carrier confinement in the channel during saturation which leads to stray electrons

exiting the channel and becoming trapped. Lastly, this chapter presents an overview of defect induced performance degradation.

**Chapter 7** concludes the results obtained in this work, and presents an outlook for future work on GaN power HEMTs.

# CHAPTER 2: LATERAL SCALING AND OPTIMIZATION FOR HIGH-VOLTAGE GAN HEMTS

GaN power devices are typically used in the 600 V market, for high efficiency, high power-density systems. For these devices, the lateral optimization of gate-to-drain, gate, and gate-to-source lengths, as well as gate field-plate length are critical for optimizing breakdown voltage and performance. This work presents a systematic study of lateral scaling optimization for high voltage devices to minimize figure of merit ( $R_{DS(on)} \times Q_G$ ) and maximize breakdown voltage.

This chapter demonstrates the effects of lateral scaling on the figure of merit for a high-voltage pGaN, enhancement-mode HEMT. To this end, the drift length ( $L_{drift}$ ) and the length of the gate field plate ( $L_{GFP}$ ) have been scaled to exhibit the influence of these terms on the on-state resistance ( $R_{DS(on)}$ ), gate charge ( $Q_G$ ), and breakdown voltage ( $V_{BR}$ ). Results conclude that for a given field plate length, the increase in breakdown voltage as  $L_{GD}$  increases, saturates when  $L_{GD}$  is greater than  $L_{GD(sat)}$ . For this design, with  $L_{GFP}$  at 5  $\mu$ m, the saturation length  $L_{GD(sat)}$  was 6  $\mu$ m. Novelty of this study comes from a comprehensive look at drift length and field plate optimization for high voltage and low figure of merit designs, specifically for the enhancement-mode pGaN structure. Taking this optimization one step further, we have mapped out  $R_{DS(on)}$  and  $Q_G$  to suggest designs which optimize conduction losses versus switching losses for specificity in power electronics system design.

A. Binder and J. S. Yuan, "Optimization of an enhancement-mode AlGaN/GaN/AlGaN DHFET towards a high breakdown voltage and low figure of merit," in 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2017, pp. 122–126.

#### 2.1 Introduction

Fueled by the desire for higher performance devices, designers have investigated various GaN device structures and methods to improve breakdown voltage, FOM, and reliability. Power electronics systems almost exclusively employ enhancement-mode (e-mode) devices; however, most studies have been conducted on the effects of employing a gate field plate on GaN depletion-mode (d-mode) devices. This is due to the relative ease of fabrication in comparison to E-mode devices. For this study we present a comprehensive look at FOM optimization and it is imperative not to limit these device studies to D-mode devices. Towards this end, we investigate the effect of drift length and field plate scaling on breakdown voltage and FOM for a pGaN, E-mode, double heterostructure field effect transistor (DHFET). The purpose of this work is to demonstrate how to optimize the lateral design of a pGaN HEMT towards a high breakdown voltage and low figure of merit. This is accomplished by showing how the drift length ( $L_{drift}$ ) and length of the gate field plate ( $L_{GFP}$ ) effect on-state resistance ( $R_{DS(on)}$ ), gate charge ( $Q_G$ ), and breakdown voltage ( $V_{BR}$ ). The results of this work are an aid to device designers for the purpose of enabling application specific power electronics design.

#### 2.2 Device Design and Simulation Model

#### 2.2.1 Theoretical Analysis

For device modeling, it is well understood that increasing the drift length or length of the gate field plate results in an increase in breakdown voltage (eq. 2.1). The relationship between breakdown voltage and drift length holds true when  $L_{GD} < L_{GD(sat)}$ , a point at which increasing  $L_{GD}$  further no longer increases the breakdown voltage (as is well

detailed in [3]).

$$BV \propto L_{drift}, L_{GFP}$$

(2.1)

Since the focus of this paper is, in part, on examining device FOM variation as lateral dimensions scale, it is necessary to first understand the general relationship between  $R_{DS(on)}$ ,  $Q_G$ , and the lateral dimensions at the center of this study,  $L_{drift}$  and  $L_{GFP}$ . The relationship between drift resistance and drift length is given by eq. 2.2 where the drift resistance is directly proportional to drift length, while  $R_{drift}$  remains independent from  $L_{GFP}$  (eq. 2.3). Finally, concerning gate charge, it should be noted that gate charge is directly proportional to the length of the gate field plate, but is independent from the drift length (eq. 2.4).

$$R_{drift} = \frac{L_{drift}}{q \cdot \mu_{drift} \cdot N_{drift}}$$

(2.2)

$$R_{drift} \propto L_{drift} \tag{2.3}$$

$$Q_G \propto L_{GFP}$$

(2.4)

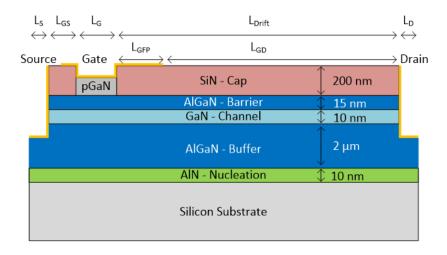

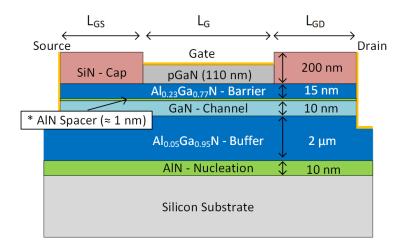

#### 2.2.2 Device Description

The cross section of the device as simulated, shown in Fig. 2.1, displays the vertical device dimensions. As mentioned, this study focuses on the lateral dimensions to optimize breakdown voltage and FOM. The simulated structure is an AlGaN/GaN/AlGaN double

heterostructure field effect transistor (DHFET) which results in better breakdown voltage and on-state resistance performance compared to the single heterostructure device [3]. This device is made enhancement-mode by the incorporation of the pGaN region above the AlGaN barrier and under the gate. Doping the GaN layer above the channel prevents the polarization of the AlGaN/GaN interface, which stops the channel from forming under the gate resulting in shifting the threshold voltage positive [4].

Figure 2.1: Cross-section representation of proposed AlGaN/GaN/AlGaN enhancement-mode DHFET with gate field plate.

For simulation purposes, the device cross-section excludes the silicon substrate as this layer does not affect the on-state resistance, gate charge, or electric field distribution near the surface. The effects of the inclusion or exclusion of the substrate on simulation results can be seen elsewhere in [5]. Simulations of the GaN HEMT were performed using Sentaurus TCAD (Synopsys) [6].

The basic lateral device dimensions for the following simulation trials are shown in Table 2.1 where  $L_{GFP}$  and  $L_{GD}$  are varied while all other parameters are held constant.

Table 2.1: Design Parameters for Lateral Layer Stack-Up.

| Region    | $L_S$  | $L_{GS}$ | $L_G$  | $L_{GFP}$ | $L_{GD}$ | $L_D$  |

|-----------|--------|----------|--------|-----------|----------|--------|

| Thickness | 0.5 μm | 1 μm     | 1.4 μm | 1-5 μm    | 1-20 μm  | 0.5 μm |

#### 2.3 Results and Discussion

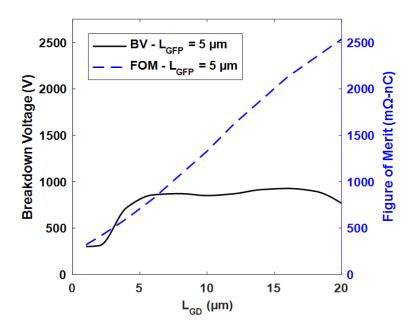

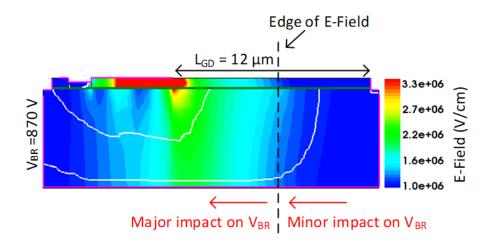

It is generally understood that the breakdown voltage of a lateral FET is proportional to the drift length, however, as mentioned previously, it is also known that this relationship tends to saturate once the drift length is increased beyond a certain threshold [3]. For this simulated structure, when  $L_{GFP}$  is 5  $\mu$ m, the correlation between breakdown voltage and  $L_{drift}$  disappears after  $L_{GD}$  increases beyond 6  $\mu$ m as seen in Fig. 2.2. This phenomenon can be explained intuitively by looking at the electric field distribution within the device.

Figure 2.2: Breakdown voltage and FOM analysis for DHFET-based device at  $L_{GFP}$  = 5  $\mu$ m.

This saturation of the breakdown voltage is in part due to the thickness of the buffer

region. Notice in Fig. 2.3 that the electric field distribution extends uniformly through the buffer region in a vertical fashion, rather than staying contained near the channel. When investigating breakdown at the substrate interface, considering the lower critical electric field of Si compared to GaN, increasing the buffer region thickness would also increase the breakdown limit, however there are ultimately limitations to how thick the buffer region can be grown [7]. Alternatively, considering breakdown to be due to leakage current in the buffer, using the space-charge-limited current (SCLC) conduction mechanism, a thinner buffer layer results in a higher breakdown voltage [8]. Both methods show a strong dependence of breakdown voltage on buffer layer thickness.

Figure 2.3: Electric field profiles of proposed DHFET with gate field plate for  $L_{GFP} = 5 \mu m$ .

From the electric field distribution plot, an intuitive understanding of how scaling  $L_{GD}$  affects  $V_{BR}$  can be obtained. For a given field plate length, the impact of scaling  $L_{GD}$  is broken down by dividing the device into two regions that are separated by the edge of the electric field as shown in Fig. 2.3. Scaling up to the edge of the E-field will have very little effect on  $V_{BR}$ ; scaling beyond this will result in a significant reduction in breakdown voltage.

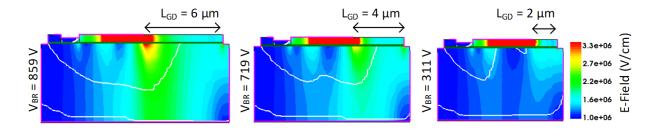

Looking at the cross-sectional plots for  $L_{GD}$  = 6, 4, and 2  $\mu$ m we see the trend demonstrated (Fig. 2.4). At  $L_{GD}$  = 6  $\mu$ m (the length corresponding to the edge of the E-field shown in

Fig. 2.3), the breakdown voltage is at a comparable level to before any scaling. As  $L_{GD}$  is reduced beyond the edge of the E-field, the breakdown voltage drops off sharply.

Figure 2.4: Electric field profiles as  $L_{GD}$  is reduced.

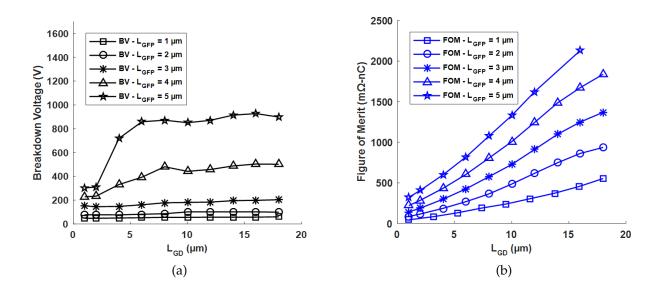

Figure 2.5: Breakdown voltage and FOM as a function of  $L_{GD}$  and  $L_{GFP}$ .

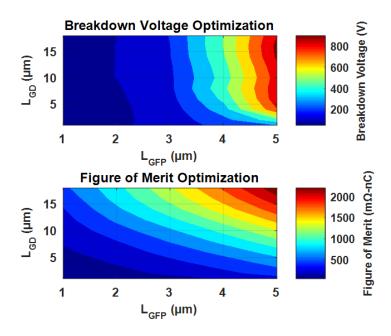

To understand the effect of varying  $L_{GD}$  and  $L_{GFP}$  on breakdown voltage and FOM, a series of simulations were run, the results of which can be seen in Fig. 2.5. A contour plot was generated for both breakdown voltage and FOM optimization to better aid in the interpretation of these results. The top subplot in Fig. 2.6 represents a breakdown voltage optimization for any given combination of  $L_{GFP}$  and  $L_{GD}$ , where blue represents low voltage and red areas designate high voltage. The bottom subplot displays a FOM

optimization which follows a very basic principle: smaller devices with a shorter field plate will have a lower figure of merit.

Figure 2.6: Optimization plots for breakdown voltage and figure of merit.

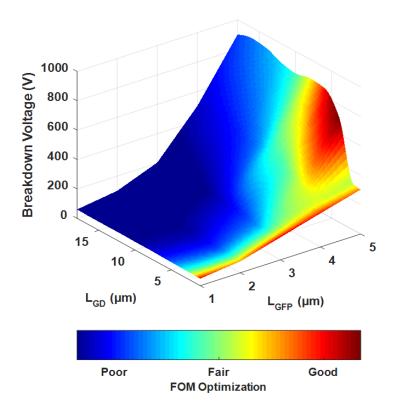

To help designers better understand how to design for high breakdown voltage and low figure of merit, another visual aid has been created. Combinating the previous two subplots (Fig. 2.6) results in the 3D plot shown in Fig. 2.7, which shows the breakdown voltage as a function of  $L_{GD}$  and  $L_{GFP}$  where the color bar represents various levels of FOM optimization. In this case, red regions are optimized well towards FOM (low FOM) while blue regions have high FOM for any given breakdown voltage level. Simply put, high peaks that are red in color are optimum designs for high voltage devices.

The specific trade-off between  $R_{DS(on)}$  and  $Q_G$ , when targeting a certain breakdown voltage threshold, allows for the optimization of a device towards higher current operation or higher switching frequency operation (lower conduction loss or lower switching loss). To understand how the individual components of FOM are affected, namely  $R_{DS(on)}$  and  $Q_G$ , they must be individually examined.

Figure 2.7: 3D optimization of breakdown voltage as a function of FOM,  $L_{GFP}$ , and  $L_{GD}$  for proposed DHFET.

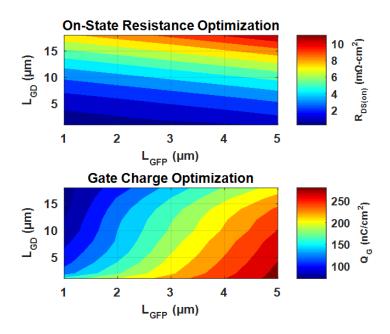

Looking at the  $R_{DS(on)}$  optimization plot in Fig. 2.8, it shows an expected trend where the smallest size device produces the lowest resistance. One thing to note is that  $R_{DS(on)}$  increases with  $L_{GFP}$  because the drift length here is defined as  $L_{GD} + L_{GFP}$ . So when  $L_{GFP}$  increases,  $L_{GD}$  is held constant and the entire device length increases. Drift length increases proportionally with  $L_{GFP}$ . Examining the  $Q_G$  optimization plot shows that the smallest field plate length results in the lowest  $Q_G$ , however, it also shows that as  $L_{GD}$  increases,  $Q_G$  decreases. This is because both  $Q_G$  and  $R_{DS(on)}$  have been normalized to the device size. So, as  $L_{GD}$  increases,  $Q_G$  stays the same, but normalized  $Q_G$  will decrease. Ultimately, this analysis represents a comprehensive look at the optimization of an E-mode pGaN HEMT from the perspective of a power electronics designer.

Figure 2.8: Optimization of on-state resistance and gate charge as a function of  $L_{GD}$  and  $L_{GFP}$ .

### 2.4 Conclusion

This chapter demonstrates a full optimization process to target optimum gate-to-drain length and gate field plate length for a normally on, high voltage, pGaN HEMT. To optimize field plate geometry and drift length scaling, device simulations were performed using Sentaurus TCAD. Based on this optimization, a device can be designed for a specific breakdown voltage, targeting the minimum figure of merit. For this simulated structure, when  $L_{GFP}$  is 5  $\mu$ m, the correlation between breakdown voltage and  $L_{drift}$  disappears after  $L_{GD}$  increases beyond 6  $\mu$ m. This phenomenon was explained intuitively by looking at the electric field distribution within the device where it was shown that scaling up to the edge of the E-field has very little effect on  $V_{BR}$  where-as scaling beyond this results in a significant reduction in breakdown voltage. From these simulation results, a 3D optimization plot was generated to show the breakdown voltage and FOM optimization as

a function of  $L_{GD}$  and  $L_{GFP}$ . Additionally, the specific trade-off between  $R_{DS(on)}$  and  $Q_G$  is presented when targeting a certain breakdown voltage threshold. This trade-off allows for the optimization of a device towards higher current operation or higher switching frequency operation (lower conduction loss versus lower switching loss).

Finally, this work demonstrated the semi-independence of breakdown voltage from drift length given that the drift length is scaled past  $L_{GD(sat)}$  at the edge of the E-field. Observing the electric field for the cross-sectional plot of the device validates this finding. In total, these results represent a comprehensive look at the optimization of  $L_{GFP}$  and  $L_{GD}$  for a high-voltage, e-mode, pGaN DHFET as an aid to device designers for the purpose of enabling application specific power electronics design.

# CHAPTER 3: FABLESS DESIGN APPROACH FOR LATERAL OPTIMIZATION OF LOW VOLTAGE GAN POWER HEMTS

As mentioned previously, GaN power devices are typically used in the 600 V market, and the adoption of GaN in the low voltage sector has had limited success. This is in part due to the GaN FOM not being competitive yet compared to Si for these low voltage devices. To address why, we present a simulation work to demonstrate a fabless design approach for the lateral optimization of a low voltage GaN power HEMT. Optimization of lateral scaling terms such as gate-to-drain, gate, and gate-to-source lengths allows for minimization of the figure-of-merit ( $R_{DS(on)} \times Q_G$ ) for a targeted breakdown voltage. Results show a FOM of 11 m $\Omega$ -nC for a device with a breakdown voltage > 50 V. These results are for a given heterostructure design and estimated trap densities, and the effects of changing these estimated trap densities have been demonstrated to heavily influence breakdown behavior. As such, the focus of this study is on the relative difference between results rather than the absolute numbers. For this given design, results suggest that by shrinking  $L_{GD}$  further the FOM can be reduced to 6.68 m $\Omega$ -nC with a breakdown of 71 V: representing a 74% decrease in FOM compared to the EPC 2023 device (30 V device) [9].

#### 3.1 Introduction

High electron mobility transistors (HEMTs) designed from wide bandgap materials have advantages over silicon transistors for both high switching frequency and low loss opera-

A. Binder, J.-S. Yuan, B. Krishnan, and P. M. Shea, "Fabless design approach for lateral optimization of low voltage GaN power HEMTs," Superlattices and Microstructures, vol. 121, pp. 92–106, Sep. 2018.

tion [10], giving GaN a materials based advantage over Si. However, this advantage in materials so far has not translated well to better device performance for low voltage power devices. GaN benefits from a higher critical electric field than Si, that combined with the large bandgap means that for any given breakdown voltage the total device length can be reduced compared with Si devices. Reducing the device length results in lower on-state resistance, and a higher power density, both critical elements to power electronics design [1]. Additionally, the high electron mobility of the two-dimensional-electron-gas (2DEG) that constitutes the device channel, a unique feature of GaN HEMTs, allows high switching frequency operation at low losses. However, if the device is not optimized well, then it will perform poorly.

As technology advances, simulation tools for semiconductor device modeling have become more numerous and have increased in popularity. With the availability of these simulation and modeling programs, such as Silvaco or Sentarus TCAD, comes the option for more robust fabless design of high performance semiconductors. Earlier fabless designs relied on analytical equations for predicting breakdown voltage and performance metrics before fabrication, then required iterations after fabrication to improve on these designs. A fabless design approach based on simulation modeling has the potential to reduce the required iterations after initial fabrication, especially if the simulation model is well calibrated to previous fabricated device results [11]. Reducing the required fabrication iterations drastically lessens the cost of getting a product from concept to market.

The drawback of a fabless design approach is that in order to generate true predictions, each structure simulated will need a fabricated benchmark device to calibrate the simulation to experimental results. However, even without a benchmark, while there is some questionable accuracy in exact numbers reported, it can be verified that trends seen in simulation are correct. Based on this knowledge, a comparative study can be done, looking for relative difference and not exact accuracy. From this study, accurate predictions can be

made to suggest design improvements that will improve breakdown voltage, performance, and perhaps reliability of devices. This paper aims to demonstrate a design optimization and simulation approach for low voltage GaN power HEMTs. The simulation results shown focus on the comparative difference between results, rather than exact numbers reported, to generate trends that will optimize the device performance.

# 3.2 Device Structure and Simulation Methodology

#### 3.2.1 Gan HEMT Device Structures

For GaN HEMTs, fabless design has three critical components: device structure, vertical layer thickness optimization, and lateral feature length optimization. Examination of the downselect process for device structures is as follows. Device structure covers two principal areas: device types and heterostructure layer selection. For power devices, the HEMT must be enhancement-mode rather than depletion-mode; this ensures that failure of the device results in an open circuit rather than a short circuit. Following this thought, enhancement-mode HEMTs employ the following methods to provide normally-off operation: recessing of AlGaN barrier layer (known as gate recess technique) [12–14], and adding a p-GaN material under the gate (known as p-GaN gate) [15–17]. Additionally, there is a method whereby fluorine implantation under the gate results in negative trap sites in the barrier layer that deplete the 2DEG channel under zero bias [17]. Of these methods, the p-GaN gate is the most popular and is used by several institutions leading to commercial devices available on the market [18] (pp. 24). The p-GaN gate, enhancement mode device is the chosen device for the focus of this paper.

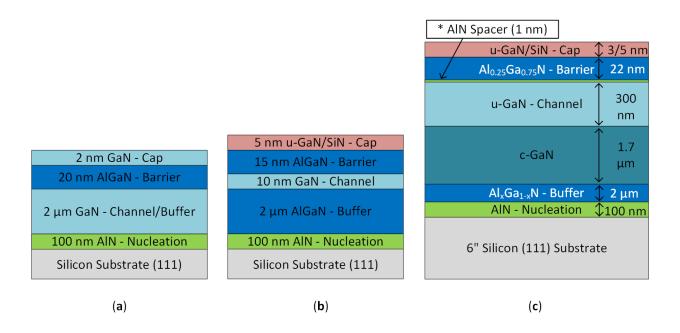

Figure 3.1: (a) Single heterostructure: the most basic design; (b) double heterostructure: has improved breakdown voltage and on-state resistance performance compared to single heterostructure design; (c) advanced heterostructure design builds off the double heterostructure and includes a carbon doped semi-insulating layer and thicker channel region to reduce defect density near channel.

Concerning heterostructure design given p-GaN gate type device, there are several considerations for improving device performance further beyond the single heterostructure layer stack-up. The single heterostructure design, shown in Figure 3.1 (a), makes use of an AlGaN/GaN barrier/channel interface to form the 2DEG. This is the most basic design type. Following the single heterostructure is the double heterostructure field effect transistor (DHFET) shown in Figure 3.1 (b). This design makes use of an AlGaN/GaN/AlGaN barrier/channel/buffer region which results in better  $R_{DS(on)}$  performance and higher breakdown voltage than the single heterostructure design due to improved carrier confinement in the channel and higher critical electric field of the AlGaN buffer layer [3]. Finally, improvements can be made on DHFET structure such as adding a semi-insulating carbon doped c-GaN region between the buffer and channel to reduce buffer leakage current [19], or increasing the channel thickness to reduce the defect density near the the channel as

shown in Figure 3.1 (c). In addition, other improvements can be made such as adding an AlN spacer to block leakage current through the cap layer or gate and enhance transport properties [20], or using a super-lattice buffer to further reduce defects and mismatch compared to a typical graded AlGaN buffer [21].

## 3.2.2 Simulation Methodology and Simulation Parameters

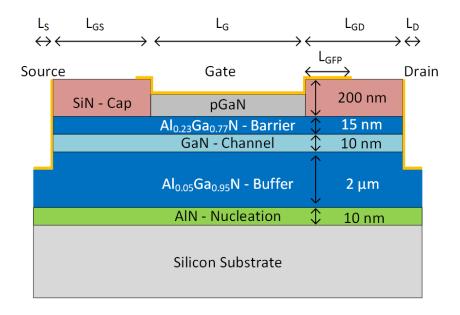

For this paper, simulation results will focus on the p-GaN gate, DHFET structure shown in Figure 3.2. From the previous downselect, it is clear that the p-GaN gate double heterostructure provides a good baseline for optimization upon which further experimentenhanced simulation work can be later compared to.

Figure 3.2: Enhancement mode, p-GaN gate, DHFET structure used in simulations.

Concerning device design, the gate electrode is Schottky type (barrier height = 0.6 eV). For this device design (pGaN, Schottky gate), gate current will not significantly contribute to device breakdown. Gate current is negligible for these off-state breakdown simulations as the device is normally off and thus the gate voltage is held at 0 V. With a high drain voltage

and zero gate voltage, the Schottky gate diode remains reverse biased and turned off. The intrinsic pin diode and the added Schottky diode due to the gate metal are in series, thus raising the forward voltage and significantly reducing on-state gate leakage (Figure 3.3). In addition, the Schottky type gate also serves to extend the reverse breakdown voltage of the gate due to high drain bias in the off-state condition.

Figure 3.3: Equivalent circuit model of series diodes for off-state operation.

Details on the specified doping levels within the device are given in Table 3.1. For simulation purposes the impurity species are specified as boron for p-type and arsenic for n-type as that is how Sentaurus requires them to be defined (due to limited doping species availability). The dopants specified in the channel and buffer are intended to reflect N-doping as is natural for an unintentionally doped GaN material due to nitrogen vacancies, gallium interstitials, or oxygen incorporation [22].

Trap formation within GaN devices has a significant impact on device performance. As such, accurate specification of trap location, concentration, and energy level within GaN

HEMTs is critical to robust simulation design. Details on trap concentration specified for the following simulation work are given in Table 3.2. The surface traps are specified as donor traps and are set conservatively a small margin higher than our experimental results. Additionally, surface traps are reported for a similar concentration and energy level in several sources [23,24]. Bulk GaN traps have been reported for a similar concentration in [8] and since the AlGaN buffer is very low molar fraction, the trap density set for the simulation has been estimated to be similar to bulk GaN trap levels. A brief review on reported trap energy levels in GaN devices is given in [22]. Additionally, other simulation reports have assumed similar values for trap concentrations and energy levels [22,25–27].

Table 3.1: Doping Concentration and Specified Impurity Species.

| Layer                       | pGaN gate                  | Barrier                 | Channel                 | Buffer                     |  |

|-----------------------------|----------------------------|-------------------------|-------------------------|----------------------------|--|

| <b>Doping Concentration</b> | $3 \times 10^{17} cm^{-3}$ | $1\times10^{18}cm^{-3}$ | $1\times10^{15}cm^{-3}$ | $1 \times 10^{14} cm^{-3}$ |  |

| <b>Impurity Species</b>     | Boron                      | Arsenic                 | Arsenic                 | Arsenic                    |  |

Physics based simulators such as Sentaurus use mathematical models to describe the simulated device. These models consist of a set of fundamental equations which are derived from Maxwells laws and consist of Poissons Equation, the continuity equations, and the transport equations. Of these equations, Poissons equation and the carrier continuity equations provide the baseline, or general framework for device simulation, however, further secondary equations are needed to show certain unique device characteristics [28].

Table 3.2: Properties of Specified Traps in Simulated Structure.

| Interface/Region           | Type     | Concentration              | Energy Level             |

|----------------------------|----------|----------------------------|--------------------------|

| SiN/AlGaN (cap/barrier)    | Donor    | $5 \times 10^{13} cm^{-2}$ | 0.6 eV above midband     |

| GaN/AlGaN (channel/buffer) | Acceptor | $6 \times 10^{12} cm^{-2}$ | 0.23 eV below cond. band |

| AlGaN (buffer)             | Acceptor | $1 \times 10^{15} cm^{-3}$ | 0.45 eV below cond. band |

| AlGaN/AlN (buffer/nucl.)   | Acceptor | $5\times10^{13}cm^{-2}$    | 0.6 eV above midband     |

The models used for the simulation results shown in this work, are presented in Table 3.3 and detailed below.

Table 3.3: Physics Models for Sentaurus Simulation.

| Model Type                                  | Model Used                                |  |  |

|---------------------------------------------|-------------------------------------------|--|--|

| Transport model for heterostructure devices | Thermionic emission model                 |  |  |

| Carrier transport                           | Drift-diffusion model                     |  |  |

| Mobility models                             | Doping dependence & High field saturation |  |  |

| Charge distribution model                   | Fermi-Dirac statistics                    |  |  |

| Band structure                              | No bandgap narrowing                      |  |  |

| Generation-Recombination                    | Shockley-Read-Hall (SRH)                  |  |  |

| Piezoelectric polarization                  | Strain model                              |  |  |

| Traps and fixed charges                     | eBarrierTunneling                         |  |  |

The thermionic emission model is required for heterojunctions as the conventional transport equations are not valid at heterojunction interfaces. An interface-specific model must be used for carrier transport, of these models, the thermionic current model is set for both electron and hole current at a material-interface heterojunction. For modeling carrier transport, the drift-diffusion model is used which is also the default model for Sentaurus simulations. Carrier transport models are usually established as some form of simplification to the Boltzmann Transport Equations. Different assumptions result in models such as the drift-diffusion model or the hydrodynamic model. In most cases, the drift-diffusion model is the simplest and is quite adequate for most devices. This model falls short for nano-scale devices, however, since GaN power devices are on a much larger scale, the drift-diffusion model is sufficiently accurate for simulation purposes [7]. For mobility models, doping dependence incorporates degredation due to impurity scattering. Also, adding high field saturation includes the effect of velocity saturation for high electric fields. Sentaurus allows for different models to be used in calculating band structure and bandgap narrowing. The main difference between models available is how they handle bandgap narrowing. For these results, no bandgap narrowing is chosen so as not to unnecessarily

complicate the simulation. In terms of charge distribution models, Fermi-Dirac statistics are used instead of Boltzmann statistics as it is a more accurate model especially for high values of carrier densities [6]. Generation and recombination processes are modeled by the Shockley-Read-Hall (SRH) recombination model, which is recombination through deep defect levels in the gap. For computing polarization effects, Sentaurus provides two models (strain and stress). The strain model in this case uses a simplified model by Ambacher. Using this, the piezoelectric polarization vector P can be expressed as a function of the local strain tensor. The statement eBarrierTunneling allows traps to be coupled to nearby interfaces by tunneling. eBarrierTunneling allows coupling to the conduction band.

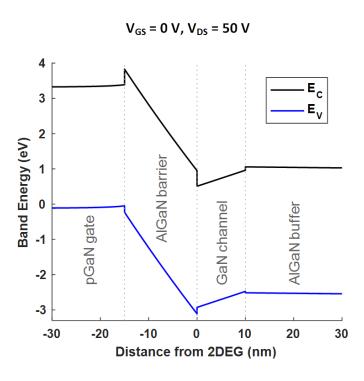

For clarity, a band diagram of the DHFET structure has been included (Figure 3.4) with the band energy calculated through a vertical cut in the center of the device (under the gate), in the off-state, at  $V_{DS} = 50$  V.

Figure 3.4: Energy band diagram of DHFET structure in the off-state with 50 V applied bias.

## 3.2.3 Definitions for Parameter Extraction

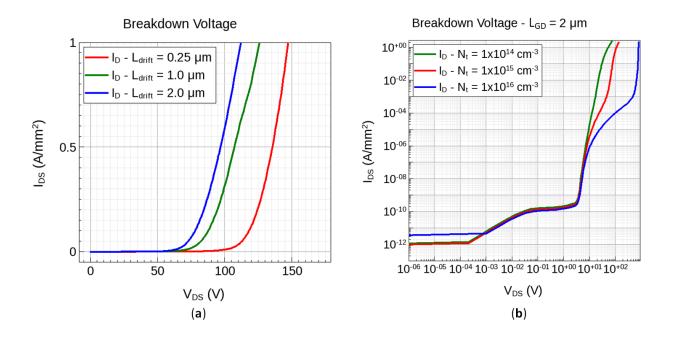

As the results presented in this work center around breakdown voltage, on-state resistance, and gate charge, the definitions for those parameters must be explicitly stated. Breakdown voltage is often defined in industry as the off-state voltage at which the drain leakage current exceeds 250 A [29,30], however, this definition does not account for scale of design: specifically the device width. Another definition that is commonly used which incorporates device width is to define breakdown at 1 mA/mm of leakage current [28,31,32]. This definition is much improved compared to the other, however, in our simulations, even with this definition, depending on the device size and the shape of the breakdown curve, this definition did not produce comparable breakdown results across all simulations. Therefore, the breakdown definition was expanded to include an area factor normalization parameter, and the definition for breakdown used in our simulation results has been modified to 10 mA/mm². Breakdown voltage plots are given in Figure 3.5 showing both linear and log scales.

Concerning on-state resistance,  $R_{DS(on)}$  is extracted from an  $I_D - V_D$  curve when the device is operating in the linear region. The voltage is sampled at  $I_D = 0.1$  A/mm and the resistance is calculated as the inverse of the slope at that point. This extraction method is one of the frequently used industry standard methods. Gate charge has been extracted at  $V_G = 6$  V with the drain voltage at 30 V bias.

This method of extraction is in line with the industry standard. An example of the curves used to extract  $R_{DS(on)}$  and  $Q_G$  are shown in Figure 3.6.

Figure 3.5: Breakdown voltage shown both in linear (a) and log (b) scales.

Figure 3.6: Curves used to extract  $R_{DS(on)}$  (a) and  $Q_G$  (b).

#### 3.3 Results and Discussion

### 3.3.1 Sentaurus Simulation: Design of Experiment

The simulation results presented here are from Sentaurus TCAD. Sentaurus software enables device design and simulation to extract critical semiconductor device parameters and to study device operation. Low voltage device design has a distinct set of design challenges compared to high voltage device design [33]. High voltage devices typically have a long gate-to-drain region, and shorter gate and gate-to-source lengths, while low voltage devices are much more laterally balanced. As GaN is typically used for the 100-650 V range, most publications focus on the design of high voltage GaN devices and not on low voltage design. This provides a unique opportunity for research on the challenges of low voltage design.

The simulation data reported is from a three terminal device (drain/gate/source) with a floating body contact. Other simulation data (not shown in the paper) shows negligible difference between the three terminal and four terminal results. From our simulation results for this device (comparing three terminal results to four terminal results), there is no known influence on breakdown characteristics resulting from the substrate electrode. Note however that the influence of a substrate electrode will be dependent on the device setup; and a different device design may result in different results. As vertical leakage current is not a significant breakdown factor in our simulation results, it should be expected that a substrate electrode would not have much impact on this device.

For these simulations, benchmark values were set for both lateral and vertical dimensions, then results were compared against the benchmark. The test setup was organized such that one parameter was varied at a time while the rest were held at a constant value. From this, a series of curves can be generated to show relative difference in results when varying

only one parameter. The baseline dimensions (both lateral and vertical) are shown in Table 3.4. These values should be used for reference throughout this document.

The simulation data presented throughout is from 2D simulations, however, in Sentaurus an area factor is set for 2D simulations which gives devices a specified width. The width specified for these simulations is 1 mm.

Table 3.4: Default Benchmark Values for Simulation Trials.

| <b>Lateral Dimensions</b> | $L_{GD}$ | $L_{GFP}$        | $L_G$ | $L_{GS}$ | $L_D$                       | $L_S$                            |

|---------------------------|----------|------------------|-------|----------|-----------------------------|----------------------------------|

|                           | 1 μm     | 0 μm             | 2 μm  | 1 μm     | 0.25 μm                     | 0.25 μm                          |

| Vertical Dimensions       | •        | $t_{cap}$ 200 nm |       |          | t <sub>buffer</sub><br>2 μm | t <sub>nucleation</sub><br>10 nm |

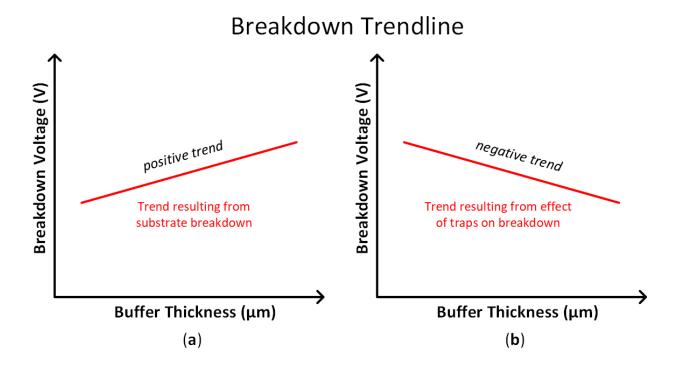

<sup>\*</sup>W = 1 mm.