# AUTOMATIC EXTRACTION OF BEHAVIORAL MODELS FROM SIMULATIONS OF ANALOG/MIXED-SIGNAL (AMS) CIRCUITS

by

Satish Batchu

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

The University of Utah

May 2011

Copyright © Satish Batchu 2011

All Rights Reserved

## The University of Utah Graduate School

## STATEMENT OF THESIS APPROVAL

| This thesis of           | Satish Batchu                                      |                             |        |

|--------------------------|----------------------------------------------------|-----------------------------|--------|

| has been approved by the | following supervisory committee members:           |                             |        |

| Chris J. Myers           | , Chair                                            | 12/17/2010<br>Date Approved |        |

| Kenneth S. Stevens       | , Member                                           | 12/17/2010<br>Date Approved | _      |

| Scott R. Little          | , Member                                           | 12/17/2010<br>Date Approved | -      |

| <i>.</i>                 | ianluca Lazzi<br>ectrical and Computer Engineering | _, Chair of                 | and by |

Charles A. Wight, Dean of the Graduate School.

## ABSTRACT

Verification of analog circuits is becoming a bottle-neck for the verification of complex analog/mixed-signal (AMS) circuits. In order to assist functional verification of complex AMS system-on-chips (SoCs), there is a need to represent the transistor-level circuits in the form of abstract models. The ability to represent the analog circuits as behavioral models is necessary, but not sufficient. Though there exist languages like Verilog-AMS and VHDL-AMS for modeling AMS circuits, there is no easy method for generating these models directly from the transistor-level descriptions. This thesis presents an improved method for extracting behavioral models from the simulations of AMS circuits. This method generates labeled Petri net (LPN) models that can be used in the formal verification of circuits, and SystemVerilog models that can be used in the system-level simulations. To my advisor, Chris

# CONTENTS

| AB            | STRACT                                                                                                                                                                                                                                                                                                                                                             | iii                                                                                           |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| LIS           | T OF FIGURES                                                                                                                                                                                                                                                                                                                                                       | vii                                                                                           |

| LIS           | T OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                    | ix                                                                                            |

| AC            | KNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                     | x                                                                                             |

| $\mathbf{CH}$ | APTERS                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |

| 1.            | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                             |

|               | 1.1Motivation1.2Related Work1.3Contributions1.4Thesis Overview                                                                                                                                                                                                                                                                                                     | $     \begin{array}{c}       1 \\       3 \\       6 \\       7     \end{array} $             |

| 2.            | BACKGROUND                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                             |

|               | <ul> <li>2.1 Tool Flow.</li> <li>2.2 Motivating Example</li> <li>2.3 Simulation Data.</li> <li>2.4 Labeled Petri Net (LPN)</li> <li>2.4.1 LPN Syntax.</li> <li>2.4.2 LPN Semantics</li> <li>2.5 Verification Property</li> <li>2.6 SystemVerilog</li> </ul>                                                                                                        | 9<br>12<br>14<br>14<br>16<br>20<br>21<br>23                                                   |

| 3.            | MODEL GENERATION                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                            |

|               | <ul> <li>3.1 Motivation</li> <li>3.2 Overview</li> <li>3.3 Generation of an LPN Process</li> <li>3.4 Dealing with Transient Behavior</li> <li>3.4.1 Initial Transient</li> <li>3.4.2 Intermediate Transient</li> <li>3.5 Generalizing the Extracted LPN</li> <li>3.5.1 Functional Approach</li> <li>3.5.2 Pseudo-Transitions</li> <li>3.5.3 Limitations</li> </ul> | $\begin{array}{c} 26 \\ 29 \\ 32 \\ 39 \\ 39 \\ 43 \\ 46 \\ 48 \\ 55 \\ 58 \\ 59 \end{array}$ |

|               | 3.5.1Functional Approach3.5.2Pseudo-Transitions                                                                                                                                                                                                                                                                                                                    | · · · ·                                                                                       |

| 4. | CASE STUDIES                                                  | 63                                      |

|----|---------------------------------------------------------------|-----------------------------------------|

|    | <ul><li>4.1 Phase Interpolator</li></ul>                      | $\begin{array}{c} 63 \\ 68 \end{array}$ |

| 5. | CONCLUSIONS                                                   | 79                                      |

|    | 5.1 Summary                                                   | 79                                      |

|    | 5.2 Future Work                                               | 80                                      |

|    | 5.2.1 Linear Interpolation of Assignments                     | 80                                      |

|    | 5.2.2 Generation of <i>stable</i> Using a Functional Approach | 81                                      |

|    | 5.2.3 Embedding Limitations Within the Model                  | 81                                      |

|    | 5.2.4 Guidance for Additional Simulations                     | 81                                      |

|    | 5.2.5 Equivalence Checking                                    | 82                                      |

|    | 5.2.6 Extension of LPNs to Express Temporal Properties        | 82                                      |

|    | 5.2.7 Application to Other Hybrid System Models               | 83                                      |

| RE | FERENCES                                                      | 84                                      |

# LIST OF FIGURES

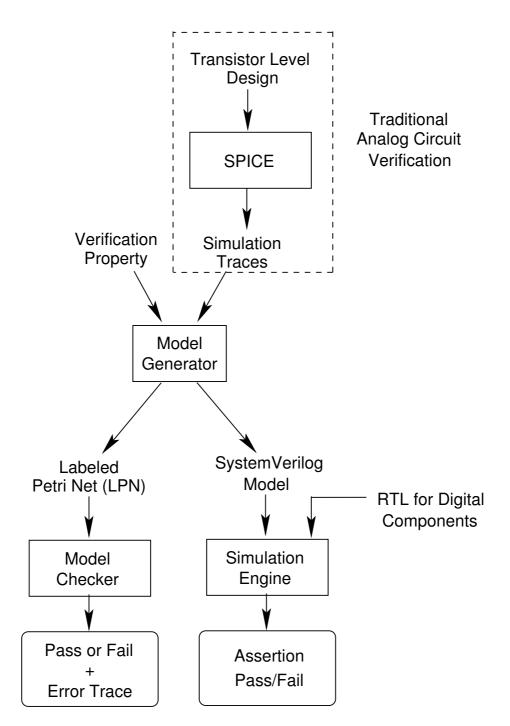

| 2.1  | Tool flow.                                                                                           | 11 |

|------|------------------------------------------------------------------------------------------------------|----|

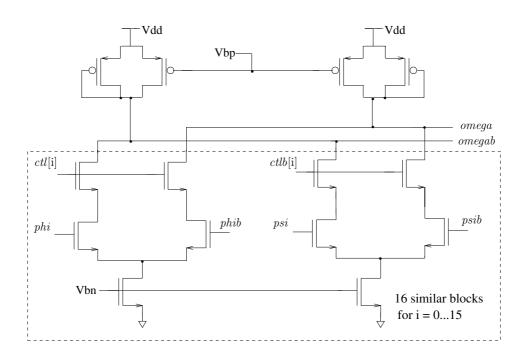

| 2.2  | Schematic of a phase interpolator.                                                                   | 12 |

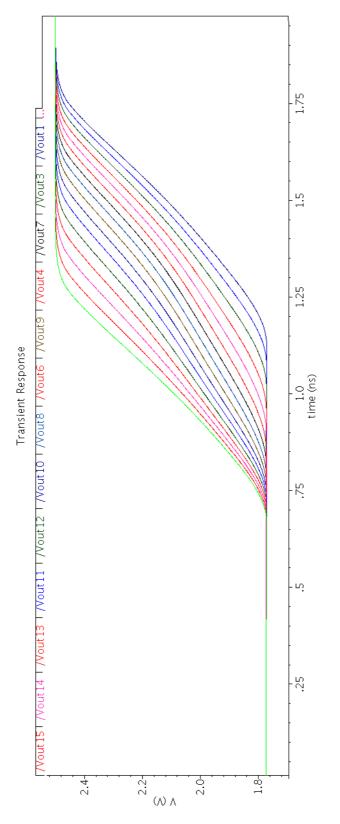

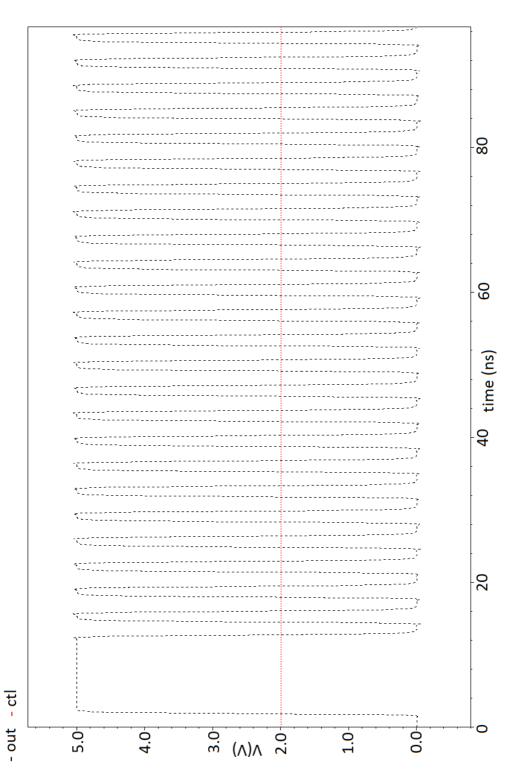

| 2.3  | SPICE simulation showing phase interpolation.                                                        | 13 |

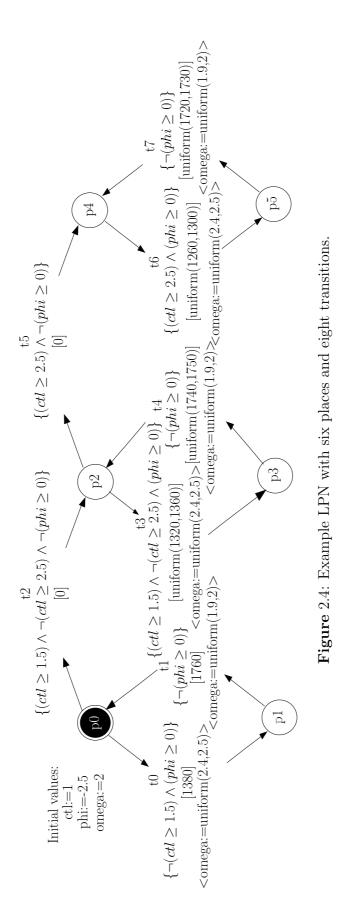

| 2.4  | Example LPN                                                                                          | 18 |

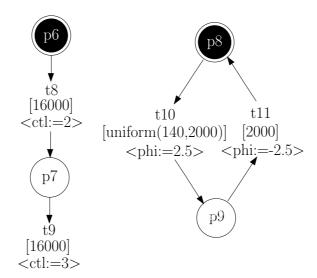

| 2.5  | Environment model                                                                                    | 19 |

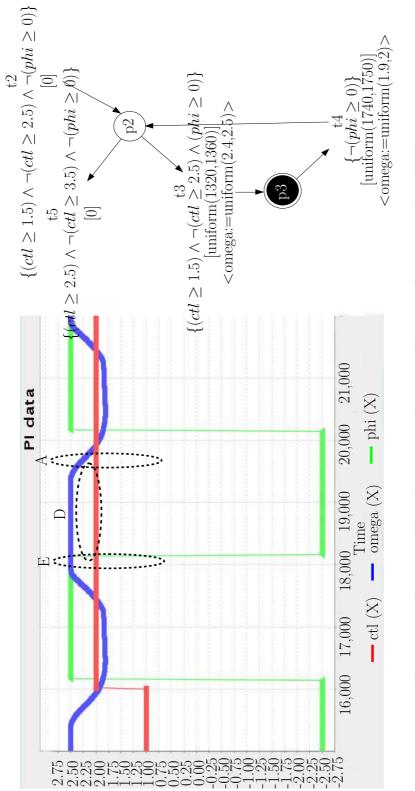

| 2.6  | Portion of the phase interpolator simulation and corresponding LPN                                   | 22 |

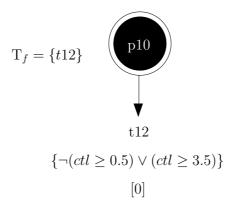

| 2.7  | An example property LPN                                                                              | 23 |

| 2.8  | An example SystemVerilog model                                                                       | 25 |

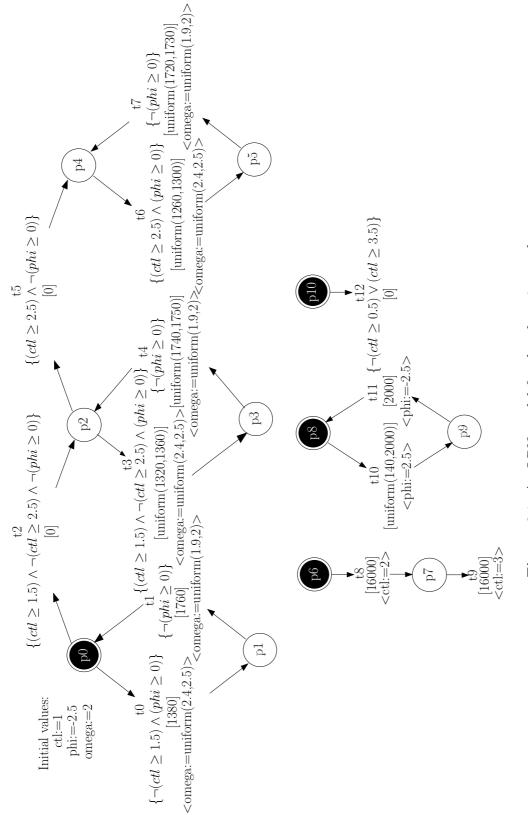

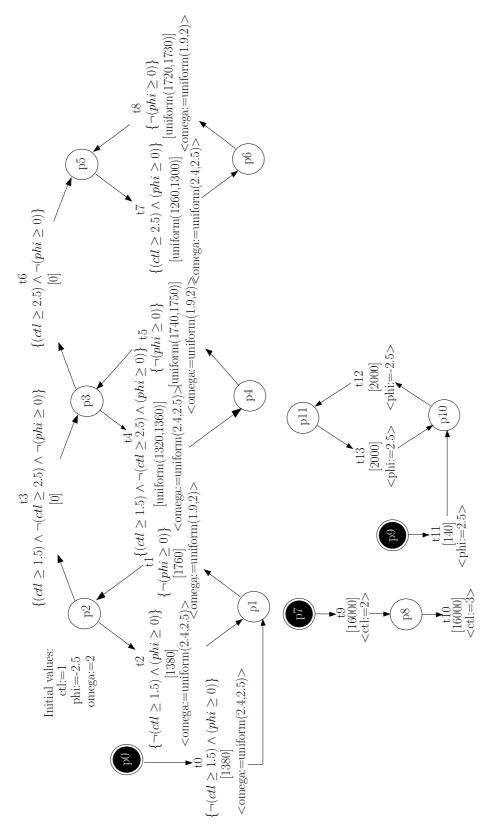

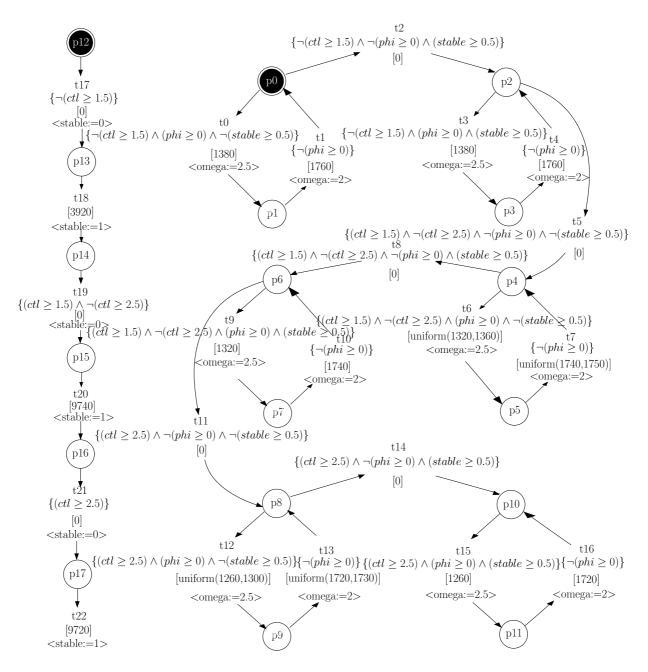

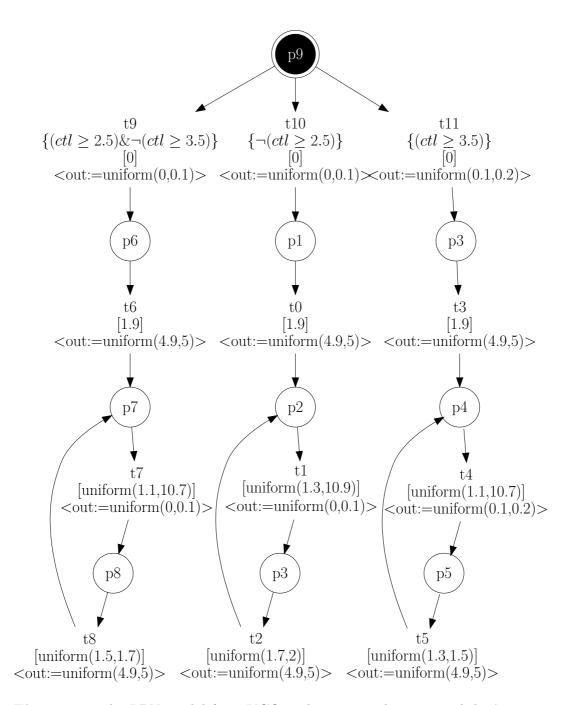

| 3.1  | An LPN model for the phase interpolator                                                              | 27 |

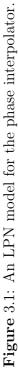

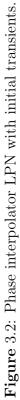

| 3.2  | Phase interpolator LPN with initial transients                                                       | 42 |

| 3.3  | Phase interpolator LPN with intermediate transients                                                  | 47 |

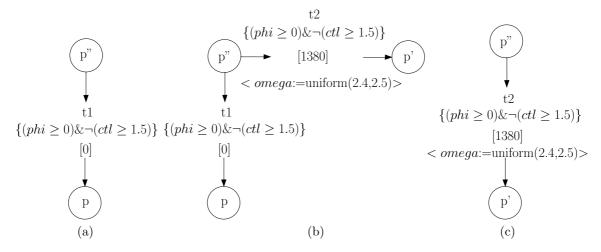

| 3.4  | Example illustrating the addition of a transition to an LPN                                          | 52 |

| 3.5  | Example illustrating the mergeTransitions operation                                                  | 54 |

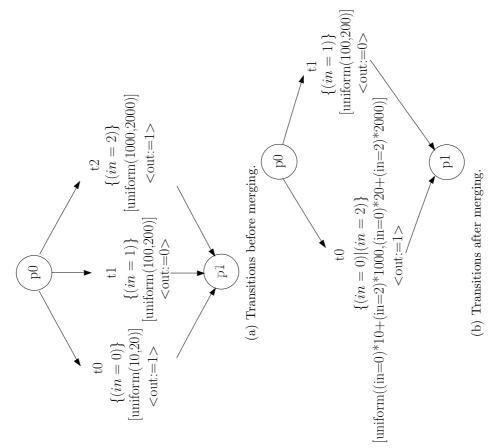

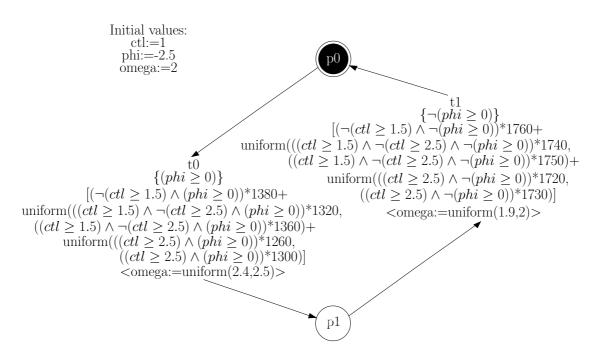

| 3.6  | Phase interpolator LPN generated using a functional approach                                         | 55 |

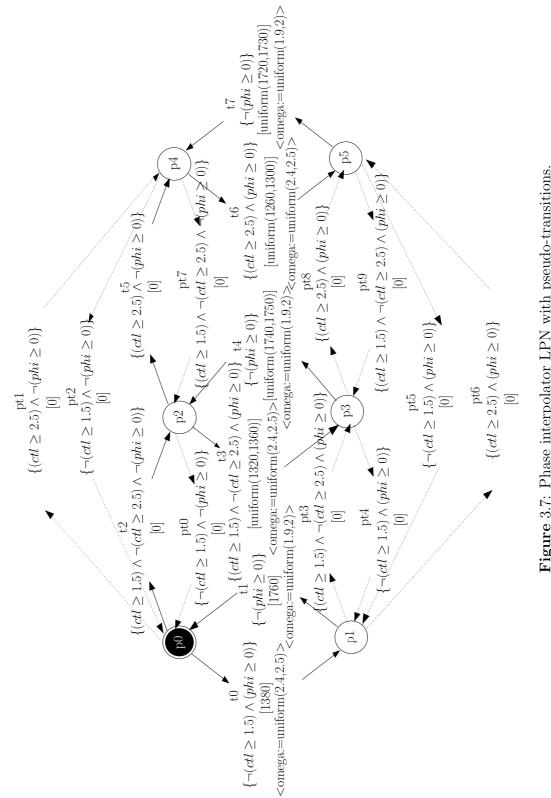

| 3.7  | Phase interpolator LPN with pseudo-transitions                                                       | 57 |

| 3.8  | The delay function.                                                                                  | 61 |

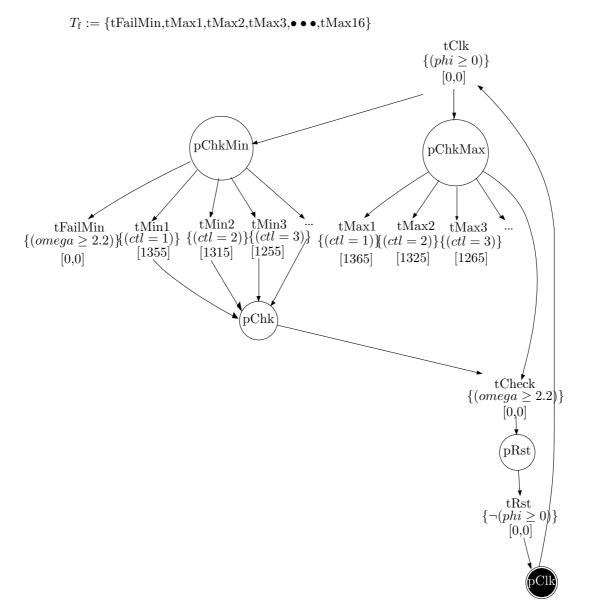

| 3.9  | Part of the SystemVerilog model for the phase interpolator                                           | 62 |

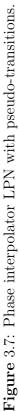

| 4.1  | An LPN model for the 16 division phase interpolator                                                  | 64 |

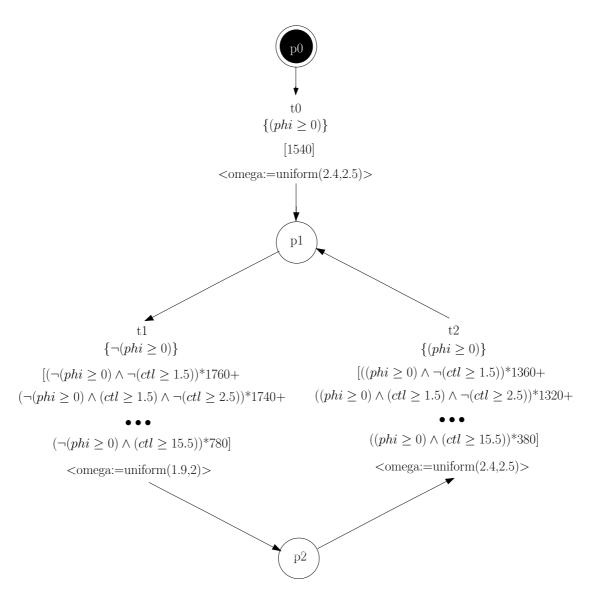

| 4.2  | Property LPN for a phase interpolator.                                                               | 66 |

| 4.3  | SystemVerilog model for a phase interpolator.                                                        | 67 |

| 4.4  | A part of the simulation of a SystemVerilog model for a phase interpolator.                          | 69 |

| 4.5  | SPICE simulation of a VCO                                                                            | 70 |

| 4.6  | The LPN model for a VCO without control inputs and don't cares                                       | 72 |

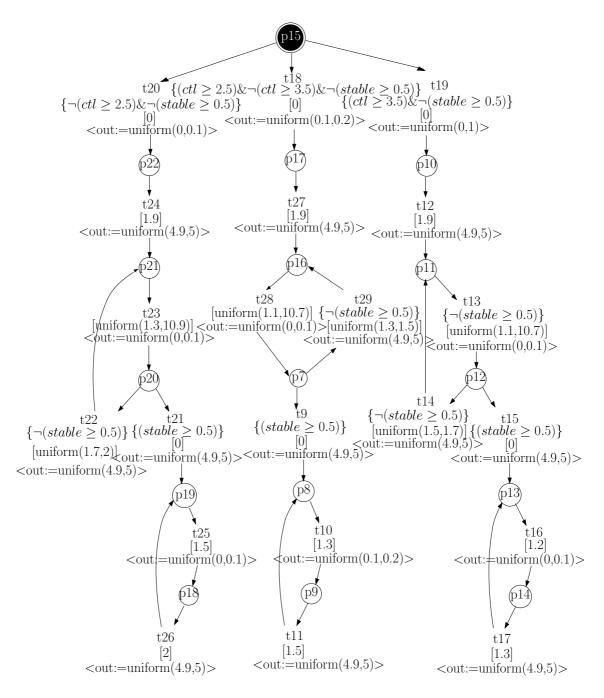

| 4.7  | The LPN process for a VCO with a control input                                                       | 73 |

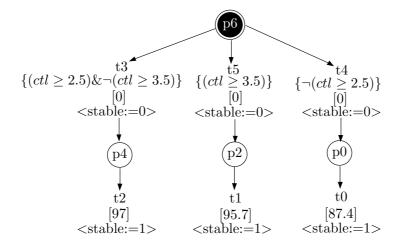

| 4.8  | The LPN process for assigning the <i>stable</i> variable                                             | 74 |

| 4.9  | The LPN process for a VCO demonstrating the transients, functional approach, and pseudo-transitions. | 75 |

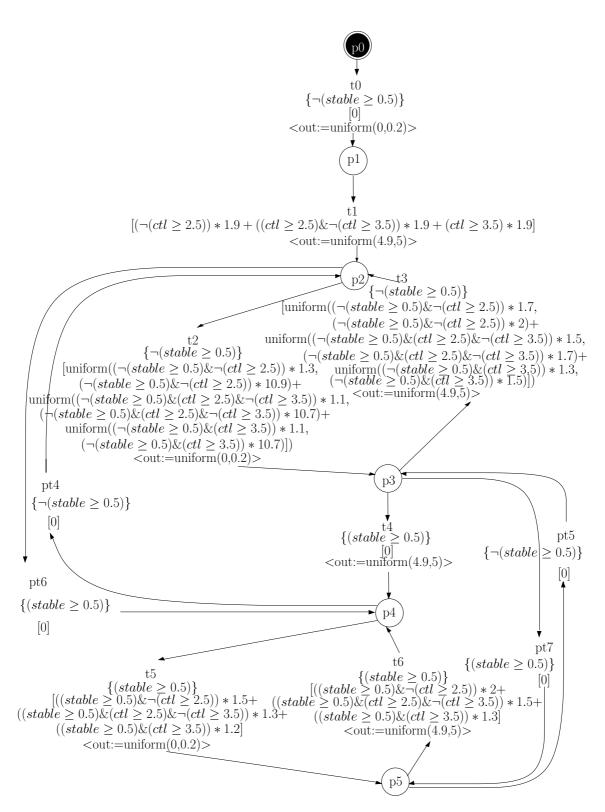

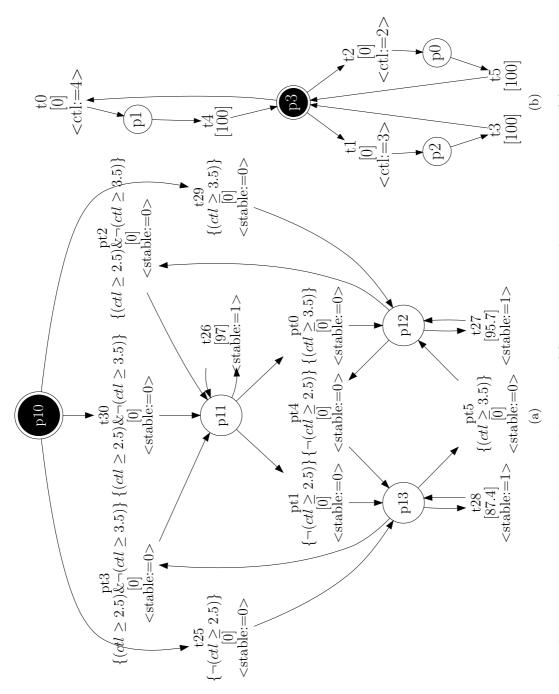

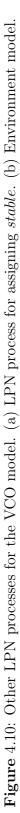

| 4.10 | Other LPN processes for the VCO model                                                                | 76 |

| 4.11 | Part of the SystemVerilog model for a VCO       | 77 |

|------|-------------------------------------------------|----|

| 4.12 | Simulation of the SystemVerilog model for a VCO | 78 |

## LIST OF ALGORITHMS

| 3.1 | $\texttt{genModel}(N,C,\Sigma,par)\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 30 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | $\texttt{genProcess}(N,c,\Sigma,\theta,par)\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$                            | 33 |

| 3.3 | $\texttt{addStableVariable}(N,c,\Sigma,\theta)  \dots $                                                                                               | 34 |

| 3.4 | $\texttt{calculateDurations}(\sigma, In, Out, reg) \dots \dots$                                                                                       | 36 |

| 3.5 | $\texttt{addInitialTransient}(N, p_0, \sigma, reg, c, dur, rate, val, \theta) \dots \dots \dots \dots$                                                                                                                                                      | 41 |

| 3.6 | $\texttt{addStableToData}(\sigma, c, \mathit{reg}, \mathit{dur}, \mathit{pre}, \mathit{par})$                                                                                                                                                               | 45 |

| 3.7 | $updateLPN(N, \sigma, i, reg, c, dur, pre, rate, val, \theta) \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                    | 50 |

| 3.8 | $mergeTransitions(N) \dots \dots$                                                                                                                     | 53 |

| 3.9 | insertPseudoTransitions(N,c,region,	heta)                                                                                                                                                                                                                   | 56 |

## ACKNOWLEDGEMENTS

The past two years at the University of Utah has been an exciting journey for me. Apart from the technical knowledge gained through regular coursework, I got an exposure to different aspects of research through this thesis. This page will not be sufficient to express my gratitude to my advisor, Chris Myers. From my experience, Chris is the ideal advisor one can expect to have. Apart from giving me proper guidance and encouragement throughout this process, he was very helpful and patient in improving my writing skills. The most important of all are his great personal qualities that I picked up in this course of time.

I would like to thank Ken Stevens and Scott Little for serving as my committee members, and for providing valuable comments and suggestions. Scott in particular was very co-operative and helpful by giving his thoughtful feedback at various phases of this research. My summer internship at Intel was very useful in shaping this research work. Thanks to Chris for his frequent visits and meetings that were very helpful. I am very thankful to Chandramouli Kashyap, Murali Talupur, Chirayu Amin, John O'Leary, Carl Seger, and Noel Menezes of Intel Corporation for their valuable comments and discussions.

Thanks to the Semiconductor Research Corporation (SRC) for having faith in this research and supporting this research for several years. SRC is very helpful in supporting its students and in opening a number of opportunities to its students. I thank Chris for giving me an opportunity to be a student member of SRC.

I thank my parents for providing constant encouragement and motivation without having any clue about what I was up to. I do not think that I would have completed my graduate studies successfully without their blessings and support. Lastly, I would like to thank my labmates Kevin Jones, Robert Thacker, Curtis Madsen, and Zhen Zhang for making our lab a wonderful place to work. Special thanks to my friend Santosh Varanasi for helping me take the right decisions with his valuable insights.

### CHAPTER 1

## INTRODUCTION

Given a choice between having a car whose operation is completely mechanical and one that relies on today's advanced electronic circuits, many of us would opt for a mechanical car. This is because most of the *integrated circuits* (ICs) which are present in the products today are not tested exhaustively. The primary reason for this is that there is no answer to the question, "When can we say that a chip, comprising millions of transistors, has been verified thoroughly?" The only thing that can be done is to ensure that the chip has been verified for as many test-cases as possible before it reaches the end-product. With the ever-increasing complexity of system-on-chips (SoCs) and the rapidly decreasing time-to-market, many SoC designs reach the market or at least end up as first silicon without being tested adequately. Thus, verification plays a key role in today's industrial design flow, be it analog or digital. The cost of a bug in the design grows exponentially with the time for which it stays in the design without being caught. If a bug is found during the postsilicon validation or later stages, then the chip has to be re-spun and it incurs a huge cost in terms of time and money. So, it is important that a chip is tested adequately before it is taped-out.

#### 1.1 Motivation

The last few years have witnessed an increasing interest in integrating analog/ mixed-signal (AMS) circuits with application specific integrated circuit (ASIC) designs. This is evident from the wide adoption of serial-signalling interfaces like Serial-ATA, PCI-Express<sup>TM</sup>, and Ethernet. The primary intention of this integration is to improve the turn-around time of ASICs by adopting SoC design approaches [1]. Verification of these ICs turned out to be a very challenging task due to this integration. This challenge can be attributed to the disparity between the conventional verification methods of digital circuits and analog circuits. The techniques used for verifying digital circuits are quite advanced while those used for analog circuits are ad-hoc. Formal methods like equivalence checking and model checking are proving to be very successful for the validation of digital designs. Advanced tools and languages, which support techniques like constrained random stimulus generation and assertion-based functional coverage analysis, have enabled the verification of extremely complex digital designs [2, 3]. On the contrary, analog validation still relies heavily on transistor-level simulations done using accurate differential equation models and SPICE simulators. AMS circuits have been evolving rapidly over the past few years. As these circuits evolve and tend to grow into larger components within a chip, verifying the system adequately using traditional techniques becomes tedious. Improving the verification quality of these complex SoCs comprising both digital and AMS circuits requires either an impractical increase in the number of resources or the usage of advanced verification methodologies.

Functional verification ensures that a circuit performs its intended function correctly. Functional verification is meant for catching functional bugs at early stages of the design. Functional bugs can occur due to simple mistakes like incorrect connection of the wires of a bus and connecting active high signals to active low inputs at an interface. While SPICE is an efficient tool for performance verification, it is not a very effective tool for functional verification of complex mixed-signal SoCs because of its poor performance owing to high accuracy. As the complexity or size of a circuit being simulated increases, the time required for SPICE simulation becomes a showstopper for verifying the circuit adequately. Compromising the accuracy of the simulations to a certain extent is tolerable while performing functional verification. This has been a tradition followed for digital circuits since the invention of *hardware description languages* (HDLs) and it has proved to be very successful in catching functional bugs in the initial stages of the design. To bridge the gap between design and verification, analog designers have to adopt a consistent verification methodology. Verification of analog designs is complicated not only because analog signals are continuous in time and value, but also due to the increasing process variability, number of parameters, and physical effects which have to be considered.

Analog circuits can be verified using either formal methods or simulation methods. Formal methods verify a system under all possible combinations of input signals and for all possible states. This process is accomplished by finding the state-space of the mixed-signal system. Simulation methods aim at simulating the whole system, which is possible only by modeling the system components at various levels of abstraction [4]. High-level modeling languages like Verilog-AMS and SystemVerilog are gaining importance as abstract models tend to be a lot faster than transistor-level schematics for simulation purposes. Recently, researchers have begun exploring the application of formal methods to these circuits [5]. Various tools which have been developed to explore the continuous state-space of AMS systems have showed some promising results [6, 7, 8]. But a major challenge being faced by these tools is that the designer has to model every system being verified, at an appropriate level of abstraction [9]. Given the complexity of mixed-signal circuits and the analog designers' addiction to the high accuracy SPICE simulations, creating accurate models can take a lot of designers' time and effort.

While having abstract models that are as accurate as the device-level transistor models is desirable for the block-level designers, such an accuracy slows down systemlevel verification. It is difficult to use a single abstract model for both circuit analysis purposes of the designer and system-level verification purposes. Thus, a verification methodology has to be compatible with the circuit analysis methods that an AMS designer uses and at the same time be very efficient for system-level verification if it has to be adopted widely [1]. Hence, tools capable of automatically generating models at the appropriate level of abstraction can prove to be very useful to the AMS community.

#### 1.2 Related Work

Functional verification of complex mixed-signal SoCs is complicated by the fact that the performance of a circuit analysis engine degrades exponentially with the size of the circuit being analyzed. Though the *FastSpice* solvers [10, 11] perform better than traditional SPICE on large circuits, they do that at the cost of reduced accuracy and a large dependence on the nature of the circuit [1]. Other disadvantages with relying on FastSpice for functional verification are that it is utilized too late in the design cycle when the complete transistor-level design of the system is available and it is too slow for simulating the whole system in all the modes of operation. There exist advanced simulation techniques for *periodic steady state* (PSS) analysis of analog circuits [12], but they do not apply to large mixed-signal circuits, which generally do not provide those basic periodic conditions. Transient simulation is an option for verification of such circuits, especially radio-frequency (RF) front-ends with very high carrier frequencies, but it requires a lot of simulation time and computational power [13]. Methods for generating coverage-guided test cases and for generating input stimuli which cover every possible state that a continuous system can adopt have been discussed in [14, 15]. In [16], the authors describe a way of finding the test cases that characterize an AMS circuit and its application for evaluating the equivalence between a circuit and its behavioral model. However, simulating an SoC such that all these stimuli are applied to the AMS circuit for every unique input to the rest of the system takes a prohibitively large amount of time. Abstract modeling of subsystems and circuits using HDLs can solve these problems because HDLs are capable of modeling just the circuit behavior by ignoring the lower-level details. The improvement in the simulation performance is a result of the loss in accuracy.

In [17], the authors develop behavioral models which specify custom memory structures as interacting state machines. However, this method is applicable only to memory designs with regular components. Various techniques for abstracting linear systems have shown promising results [18, 19], but there are not many successful methods for accurately modeling nonlinearities of AMS circuits. The approaches used for modeling nonlinear systems rely on approximating them as either *piecewise linear* or *picewise polynomial* and then applying the abstract modeling techniques of the linear or weakly nonlinear systems [20, 21]. The piecewise linear approximation leads to difficulties in modeling the higher order systems while the piecewise polynomial approximation necessitates complex ways of selecting the inputs [22]. Since analog designers simulate their circuits for a variety of inputs which when applied to the circuit is expected to work properly, generating abstract models from simulation data does not require significant additional work by the designer. This has created an increasing interest in *simulation-aided verification* (SAV) techniques. One of the approaches to verify AMS circuits proves the correctness of a circuit by finding a finite number of simulation traces that are sufficient to represent all trajectories of the system [23]. Other approaches include verification of formal properties on simulation traces directly [24, 25], and generation of a formal model from simulation traces, which can be analyzed using state space exploration techniques [26]. Dastidar et al. generate a *finite state machine* (FSM) from a set of simulation traces [26]. An acyclic FSM is generated using currents, voltages, and time as state variables. The state space of the system is divided symmetrically into state divisions. The state of the appropriate state division. The simulator is then started from here and run for the next delta time step. This process is done until the global time reaches a user specified maximum.

LPN Embedded/Mixed-signal Analyser (LEMA) is a tool that takes simulation traces of AMS circuits and generates formal models in the form of *labeled petri nets* (LPNs) and AMS HDL models in the form of Verilog-AMS and VHDL-AMS [22]. The LPN models are meant to be verified formally using various model checking techniques [27]. The AMS HDL models can be integrated with the behavioral models of the rest of the ASIC for performing fast system-level simulations which verify the functionality of the system as a whole. The approach used in LEMA is similar to that of Dastidar et al. The state space is divided into regions based on thresholds on signal values, which can either be provided by the user or generated automatically. The obtained graphs may be cyclic because a global timer is not one of the state variables. Since the information from simulation traces is captured from start to finish without stopping anywhere, the models generated by LEMA preserve the original simulation traces. Using this approach, the model allows for dynamic variation of parameters. Standard simulationbased methods allow for changes in initial conditions and parameters, but these values are then fixed for the duration of the simulation run. Simulation of an LPN model allows the system to be explored under ranges of initial conditions as well as ranges of dynamically changing parameter values. This additional behavior helps in discovering errors caused by variations [9]. However, using this method, the number of simulations required for generating a model that produces reasonably good results in all the test conditions can be very high.

#### **1.3** Contributions

This thesis presents an improved method for extracting behavioral models from simulations of AMS circuits. This method allows the extracted behavioral models to replace the original transistor-level circuits in the complex mixed-signal SoCs, thus improving the performance of system-level simulations. The abstract models generated by this method are LPNs which can be verified formally and HDL models which can be simulated for correctness. The new method has been implemented in the tool LEMA such that LPN and SystemVerilog models can be extracted automatically from the simulation traces of AMS circuits. The method presented here enables the extraction of models which have different levels of accuracy and generality based on the algorithms used. The three major contributions of this research are :

- A method to represent transient behavior, present in simulation traces, in the LPN models.

- Generalization while extracting the LPN models so that they can be subjected to arbitrary stimuli for simulation purposes.

- A generic way of representing the extracted LPN models in HDLs like SystemVerilog and automatic translation of LPNs to SystemVerilog accurately.

A real analog circuit always has a finite settling time before it attains a steady-state frequency, voltage, etc. If this is not taken into consideration while extracting models from the simulations, the generated models are not accurate representations of the actual circuits. These transients can be present at the start of the simulation or whenever there is a change in the mode of operation. The first contribution of this research is a solution to the above problem in which a binary state variable is added when a circuit has transient effects. The addition of binary variable isolates the transient behavior from the steady-state behavior of the model. An LPN model generated from a set of simulation traces is just as good as the simulation traces from which it is generated. In other words, it produces correct results only when it is subjected to sequences of stimuli which are exactly the same as those used for generating it. For any other sequence of stimuli, the results are unpredictable and there is a possibility of deadlock. The second contribution of this thesis is the extension of the applicability of these models by generalizing them during model generation. Two methods for doing this are discussed.

- Addition of pseudo-transitions.

- A functional approach.

The LPN models generated from simulations cannot be simulated with any of the standard tools used in industry. Also, if they cannot be integrated with the HDL models of other digital blocks in the system, then their practical use is very limited. In order to apply this model generation approach to real world examples, the LPN models have to be represented accurately in industry-standard HDLs. Though they can be represented in Verilog-AMS, the simulation performance is limited by by the continuous-time kernel of the mixed-signal simulator. For this reason, the LPN models are being represented in SystemVerilog which runs on the discrete-event kernel. The third contribution of this thesis is an approach for accurate translation of LPNs in SystemVerilog while complying with the LPN semantics.

#### 1.4 Thesis Overview

The rest of this thesis is organized as four chapters which give a detailed description of the contributions of this research. Chapter 2 gives an overview of the LEMA tool's model generator. It also provides the mathematical definition of an LPN along with its graphical description, and shows how the LPNs are capable of modeling AMS circuits. A brief introduction to SystemVerilog is given and the reason for choosing SystemVerilog as the HDL is detailed.

Chapter 3 describes the model generation algorithm in detail. The approach used to distinguish the steady-state behavior from the transient behavior present in the simulation traces is discussed. It is also shown how the same method applies for separating the initial portion of the simulations, which does not account for the actual circuit's functionality, from the relevant portion of the circuit's simulation. Different methods of generalizing the model such that it can be simulated with arbitrary stimuli are discussed. The advantages and disadvantages of these approaches are mentioned so that one knows when to choose a particular method. This chapter also describes the method used to translate an LPN to SystemVerilog. A number of subtleties in the LPN semantics are shown and the way in which this method allows correct translation of the LPN semantics to SystemVerilog is demonstrated.

Chapter 4 presents industrial examples like a *phase interpolator* and a *voltage controlled oscillator* (VCO). The LPN models generated using the improved model generation approach are shown which demonstrate the importance of the methods presented in Chapter 3. Property LPNs which are used to formally verify the functionality of these models are also shown. The same property LPNs get translated to assertions upon converting the LPN model to SystemVerilog. The SystemVerilog models are simulated and the functionality is verified by means of assertions. These examples also show how the methods presented here are directly applicable to the accurate and generalized modeling of industrial circuits.

Chapter 5 summarizes the research work detailed in this thesis. The scope and results of this research are also presented. This chapter also describes a number of interesting areas where this research is applicable directly or indirectly. While this work solves some of the problems related to model extraction, there are numerous interesting problems that still need to be addressed. The future work section of this chapter describes some such problems which need to be addressed.

### CHAPTER 2

## BACKGROUND

The first section of this chapter introduces a tool flow that is easy to integrate with the current industrial design and verification flows of AMS circuits. Then, it is shown how the method of model generation described in Chapter 3 fits into this tool flow without any extra burden on the designers. The later sections provide the background information that is useful in understanding the model generation method described in the following chapters. A *phase interpolator* example circuit, which served as a motivation for many improvements in the model generation method, is presented. The LPNs are explained mathematically and their graphical representation is shown. A brief introduction to SystemVerilog, which is the HDL into which the LPNs get translated, is provided.

#### 2.1 Tool Flow

The complexity of digital circuits that are being shipped as ASICs has increased tremendously over the past two decades. This advancement has been possible primarily due to the improvements in the *design automation* tools which deal with Boolean logic. For instance, today's design automation tools for digital circuits are capable of synthesizing multimillion gate circuits from high-level HDL descriptions of the desired functionality, checking the equivalence of the HDL model and synthesized circuit, verifying the generated circuit for arbitrary test cases which a human brain may not even think of, etc. Many of these tools are capable of dealing with different models of the same circuit that differ just in the level of abstraction. Digital circuits are typically represented at RTL, gate-level, transistor-level, and layout-level abstractions only. On the contrary, analog circuits are generally represented at circuit-level and layout-level abstractions. Though they can be represented in HDLs like Verilog-AMS and VHDL-AMS, they can neither be synthesized to transistor-level designs nor be verified as an equivalent description of an already designed transistor-level schematic.

State machines are the ubiquitous representation for digital circuits, and most tools utilize them. It is important that AMS circuits have a similar formal model that can be analyzed easily by design automation tools. It is not just sufficient to have a model that is an accurate abstract representation of an AMS circuit. The model should be easily obtainable by leveraging the existing design methodologies. In other words, modeling the circuit should require minimal efforts of the designer because the designers are not expected to model the circuits manually. If they have to do that, then the same design exists at two places and every small change in the design needs to be ported manually to the model and vice versa. This is not a good practice because of the high probability for inconsistencies between the model and the circuit. For simulation purposes, the model should also be representable in the industry-standard HDLs.

SAV [22] is a methodology developed with the above requirements in mind. Fig. 2.1 shows the verification flow using the SAV methodology that can be integrated with the current industrial design and verification flows. The top portion of the figure shows the traditional AMS verification process where the designer simulates the design for a number of test configurations and ensures that the performance and functionality requirements are met by observing the simulation traces. This is an iterative process. The model generator shown in the figure takes the set of simulation data that the designer used to verify the circuit and an optional verification property and generates an LPN model and a SystemVerilog model. The LPN models can be verified using model checking approaches. The SystemVerilog model generated for the AMS circuit can be integrated with the RTL models of the digital logic and simulated using the traditional techniques used for functional verification of digital logic. The model generator also translates the verification properties to SystemVerilog assertions which can be used to analyze the functional coverage of the test-bench. The remainder of this chapter describes the inputs accepted and the outputs produced by LEMA which is a tool that implements the verification flow mentioned above.

Figure 2.1: Tool flow.

### 2.2 Motivating Example

A phase interpolator example is used in Chapter 3 to illustrate the improved method for generating models from simulation traces. Phase interpolating circuits are commonly used in the receivers of serial communication links for adjusting the phase of the sampling clocks in fine increments. Fig. 2.2 shows the transistor-level schematic of one block of the phase interpolator with symmetric load [28]. This block has two unit cells, each clocked by differential clocks *phi* and *psi*.

A typical phase interpolator has 16 such blocks connected to the differential output, *omega* and *omegab*. Thermometer encoded control lines, ctl[15:0], are used to control the phase of the output signal *omega* by mixing the phases of *phi* and *psi* in an appropriate ratio. Fig. 2.3 shows 16 SPICE simulations of such a phase interpolator, each for a different value of ctl. It can be observed that the phase of the output is different in all the simulations, and hence is adjusted as the value of ctl is changed.

Figure 2.2: Schematic of a phase interpolator.

#### 2.3 Simulation Data

Our SAV methodology generates abstract models using the data obtained by simulating a circuit in a simulator like SPICE. Simulation data is a tuple of the form  $\langle S, \Sigma \rangle$ , where S is the set of all design variables in the circuit being modeled, and  $\Sigma$  is the set of time series simulation traces. Each trace  $\sigma \in \Sigma$  is an n-tuple  $\langle \tau, \nu_0, \ldots, \nu_{n-1} \rangle$ where  $\tau \in \mathbb{R}$  is the timestamp for the data points  $(\nu_0, \ldots, \nu_{n-1}) \in \mathbb{R}^n$  where n is |S|.

Table 2.1 is an example which shows the type of simulation data that can be obtained by simulating circuits in SPICE. The data in this table correspond to a phase interpolator simulation in which *ctl* is varied sequentially through the thermometer code sequence 1 to 3, and is used to generate the LPN models described in Chapter 3. For the sake of simplicity, the differential signals have been replaced by single-ended signals. The two clock inputs, *phi* and *psi*, have equal frequencies and are separated in phase by 90 degrees.

These data show the voltages of the signals, *ctl*, *phi*, and *omega*, which are recorded at a timestep of 20 ps for a duration of 48 ns. To access the timestamp for data point *i*, the notation  $\sigma_i(\tau)$  is used. Similarly, to access the data value *i* for variable  $\nu$ , the notation  $\sigma_i(\nu)$  is used. In Table 2.1,  $\sigma_1(\tau)$  is 20 ps and  $\sigma_1(phi)$  is -2.5 V.

## 2.4 Labeled Petri Net (LPN)

LPNs are the formal models used to represent AMS circuits in LEMA. They are a variant of Petri Nets which have extended semantics that allow modeling of hybrid systems and embedded systems. *Hybrid Petri nets* (HPN) and *hybrid automata* were developed to represent systems which have continuously varying signals [29, 30, 31, 32]. As these formalisms are not easily compiled from high-level languages, *labeled hybrid Petri nets* (LHPNs) were developed [33, 34]. LHPNs have been generalized as LPNs due to the recent extensions which enable them to model embedded systems which typically contain software, digital systems, and analog circuitry [35].

The LPNs generated using the methods presented in Chapter 3 are the simplest forms of LPNs because the individual processes of these LPNs do not have concurrency. In other words, each process has exactly one token at any instant and hence the generated LPNs are essentially extended state machines. LPNs differ

| · · · · · |      | -   |         |

|-----------|------|-----|---------|

| Time      | phi  | ctl | omega   |

| (ps)      | (V)  |     | (V)     |

| 0         | -2.5 | 1   | 1.77387 |

| 20        | -2.5 | 1   | 1.77306 |

| ÷         | :    | •   | ÷       |

| 120       | -2.5 | 1   | 1.77349 |

| 140       | 2.5  | 1   | 1.77411 |

| 160       | 2.5  | 1   | 1.77436 |

| :         | ÷    | :   | ÷       |

| 1500      | 2.5  | 1   | 1.99551 |

| 1520      | 2.5  | 1   | 1.02016 |

| :         | ÷    | :   | ÷       |

| 2120      | 2.5  | 1   | 2.49981 |

| 2140      | -2.5 | 1   | 2.49979 |

| 2160      | -2.5 | 1   | 2.49981 |

| :         | :    | •   | :       |

| 3880      | -2.5 | 1   | 2.02190 |

| 3900      | -2.5 | 1   | 2.00266 |

| ÷         | :    | :   | :       |

| 4120      | -2.5 | 1   | 1.86098 |

| 4140      | 2.5  | 1   | 1.85366 |

| 4160      | 2.5  | 1   | 1.84671 |

| :         | ÷    | •   | ÷       |

| 15980     | -2.5 | 1   | 1.94194 |

| 16000     | -2.5 | 2   | 1.92845 |

| 16020     | -2.5 | 2   | 1.91594 |

| :         | •    | •   | :       |

| 16120     | -2.5 | 2   | 1.86734 |

| 16140     | 2.5  | 2   | 1.86030 |

| 16160     | 2.5  | 2   | 1.85361 |

|           | :    | :   | :       |

| 31980     | -2.5 | 2   | 1.93301 |

| 32000     | -2.5 | 3   | 1.92046 |

|           | :    | :   | :       |

| 47980     | -2.5 | 3   | 1.92376 |

Table 2.1: Part of the simulation data of a phase interpolator.

from standard state machines in that they contain rates, real values, delays, etc. which allow modeling of continuous and asynchronous signals. LPNs also allow for nondeterminism in all the above parameters. The syntax of the LPNs that are generated from simulation traces is described in Section 2.4.1. Section 2.4.2 gives a brief explanation of LPN semantics which is essential to understand the model generation procedure described in Chapter 3. A detailed description of the complete syntax and semantics of general LPNs is given in [33, 34, 35].

#### 2.4.1 LPN Syntax

An LPN is a tuple  $N = \langle P, T, T_f, X, V, \Delta, \dot{V}, F, L, M_0, Y_0, Q_0, R_0 \rangle^1$

- P: is a finite set of places;

- T: is a finite set of transitions;

- $T_f \subseteq T$ : is a finite set of failure transitions;

- X : is a finite set of discrete integer variables  $(X = X_i \cup X_o \cup X_n)$ ;

- V: is a finite set of continuous variables  $(V = V_i \cup V_o \cup V_n);$

- $\Delta$  : is a finite set of rate variables;

- $\dot{V}: V \to \Delta$  is the mapping of variables to their rates;

- $F \subseteq (P \times T) \cup (T \times P)$  is the flow relation;

- L : is a tuple of labels defined below;

- $M_0 \subseteq P$  is the set of initially marked places;

- Y<sub>0</sub>: X → (ℤ∪{-∞})×(ℤ∪{∞}) is the initial range of values for each discrete variable;

- Q<sub>0</sub> : V → (Q ∪ {−∞}) × (Q ∪ {∞}) is the initial range of values for each continuous variable;

- R<sub>0</sub>: Δ → (ℚ ∪ {−∞}) × (ℚ ∪ {∞}) is the initial range of rates of change for each continuous variable.

$<sup>^1\</sup>mathrm{A}$  somewhat simplified version of LPNs is used in this thesis which is sufficient for AMS circuit models.

where  $X_i, X_o$ , and  $X_n$  are the discrete integer input, output, and internal variables, respectively, and  $V_i, V_o$ , and  $V_n$  are continuous input, output, and internal variables, respectively.

Fig. 2.4 is a graphical representation of an example LPN that is generated from simulation traces for the phase interpolator. Circles labeled  $p_0$  to  $p_5$  are places which represent the states of the LPN (i.e.,  $P = \{p_0, \ldots, p_5\}$ ). The tokens in the LPN move between places by the firing of transitions, which are named  $t_0$  to  $t_7$  in the figure (i.e.,  $T = \{t_0, \ldots, t_7\}$ ). The figure shows that  $p_0$  has a token indicating that this place is initially marked (i.e.,  $M_0 = \{p_0\}$ ). The arcs connecting the places and the transitions represent the flow relation, F. This example LPN only has discrete variables, ctl, phi, and omega (i.e.,  $X = \{ctl, phi, omega\}$ ). The variables ctl and phi are input variables, and omega is an output variable for this LPN (i.e.,  $X_i =$  $\{ctl, phi\}, X_o = \{omega\}, X_n = \emptyset$ . The general LPN would also have continuous variables. The lack of continuous variables in this LPN implies that there are no rate variables (i.e.,  $V = \Delta = \emptyset$ ). Though the simulation data in Table 2.1 show that phi and *omega* are continuously varying signals, they have been abstracted by the SAV method as discrete variables. The initial values of ctl, phi, and omega are 1, -2.5, and 2, respectively. An LPN with continuously-varying variables would have initial rates of change for the same.

A process is a connected set of places and transitions in an LPN. Every transition  $t \in T$  has a preset denoted by  $\bullet t = \{p \mid (p,t) \in F\}$  and a postset denoted by  $t\bullet = \{p \mid (t,p) \in F\}$ . Similarly, every place has a preset denoted by  $\bullet p = \{t \mid (t,p) \in F\}$  and a postset denoted by  $p\bullet = \{t \mid (p,t) \in F\}$ . Fig. 2.5 shows the environment model that is generated from simulation traces for the phase interpolator. It comprises of two processes — the first comprising transitions  $t_8$  and  $t_9$  models a phase interpolation selector, and the second process comprising transitions  $t_{10}$  and  $t_{11}$  models a clock generator.

Each transition in an LPN may have one or more labels, each of which is either an enabling condition or an assignment. The numerical portion of the grammar,  $\chi$ , used by these labels is described below:

$$\chi ::= c_i \mid \infty \mid x_i \mid v_i \mid \dot{v}_i \mid (\chi) \mid -\chi \mid \chi + \chi \mid \chi * \chi \mid \text{INT}(\phi) \mid \text{uniform}(\chi, \chi)$$

Figure 2.5: Environment model.

where  $c_i$  is a rational constant from  $\mathbb{Q}$ ,  $x_i$  is a discrete variable,  $v_i$  is a continuous variable, and  $\dot{v}_i$  the rate of change of a continuous variable  $v_i$ . The function INT converts the Boolean **true** or **false** value to an integer 1 or 0, respectively. The function uniform(l, u) returns a uniform random value between the lower and upper bounds obtained by evaluating the expressions l and u. The set  $\mathcal{P}_{\chi}$  is defined as the set of all formulae that can be constructed using the grammar  $\chi$ . The Boolean part of the grammar,  $\phi$ , that the labels are allowed to use is as follows:

$$\phi \quad ::= \quad \mathbf{true} \mid \mathbf{false} \mid \neg \phi \mid \phi \land \phi \mid \phi \lor \phi \mid \chi \ge \chi$$

where  $\neg$ ,  $\land$ , and  $\lor$  are Boolean negation, conjunction, and disjunction operators, respectively. The set  $\mathcal{P}_{\phi}$  is defined as the set of all formulae that can be constructed using the grammar  $\phi$ .

The labels used as enabling conditions can only use a restricted subset of the  $\chi$  and  $\phi$  grammars which are  $\chi_e$  and  $\phi_e$ , respectively. The numerical part  $\chi_e$  does not allow the usage of continuous variables. In other words, enabling conditions are allowed to have continuous variables only on the left side of the inequalities to ensure that the right side of these relations is constant when time advances between transition firings. The sets  $\mathcal{P}_{\chi_e}$  and  $\mathcal{P}_{\phi_e}$  are defined as the set of all formulae that can be constructed from the  $\chi_e$  grammar and  $\phi_e$  grammar, respectively.

The formal definition for the labels on a transition in an LPN is a tuple  $L = \langle En, D, XA, VA, RA \rangle$ :

- $En: T \to \mathcal{P}_{\phi_e}$  labels each transition  $t \in T$  with an enabling condition.

- D: T → P<sub>χ</sub> labels each transition t ∈ T with a delay for which t has to be enabled, before it can fire.

- $XA: T \times X \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  and discrete variable  $x \in X$  with the discrete variable assignment that is made to x when t fires.

- $VA: T \times V \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  and continuous variable  $v \in V$  with the continuous variable assignment that is made to v when t fires.

- $RA: T \times \Delta \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  and continuous rate variable  $\dot{v} \in \Delta$  with the rate assignment that is made to  $\dot{v}$  when t fires.

Note that vacuous assignments, which reassign the existing value, are not shown in the graphical representation for simplicity. In the example LPN shown in Fig. 2.4, transition  $t_0$  has an enabling condition of  $\{\neg(ctl \ge 1.5) \land (phi \ge 0)\}$ , a delay assignment of 1380 time units, a discrete variable assignment  $\langle omega := uniform(2.4, 2.5) \rangle$ . This LPN does not have rate assignments on any of the transitions because it does not have continuous variables.

#### 2.4.2 LPN Semantics

The state of an LPN is defined by the set of marked places, the values and rates of the variables, the Boolean values of the continuous inequalities, and the values of all transitions' clocks. The current state of an LPN changes either when a transition fires or as time advances. A transition  $t \in T$  is said to be enabled when all the places in its preset are marked (i.e.,  $\bullet t \subseteq M$ ), and the enabling condition on t evaluates to true. At the instant when a transition t is enabled, its clock is initialized to zero, and its delay assignment, D(t), is evaluated. Transition t which is enabled at time  $\tau$  is scheduled to fire at time  $\tau + D(t)$ . However, if t gets disabled at any time during this period, then the scheduled firing event does not occur. A transition is disabled when any of the places in its preset become unmarked or its enabling condition evaluates to false. In the time duration  $\tau$  to  $\tau + D(t)$ , simulation continues as usual and other transitions can be enabled or disabled due to the fact that the inequalities can change at any instant. When a transition fires, the marking is updated by deleting the tokens from the places in its preset and adding tokens to the places in its postset. Also, the discrete, continuous value, and continuous rate assignments associated with the transition are performed, the state of the continuous inequalities are updated, and the clocks associated with newly enabled transitions are initialized to zero.

The semantics of LPNs and its correlation with simulation traces are illustrated using Fig. 2.6, which shows a portion of the phase interpolator simulation and the corresponding portion of the LPN model. In the initial state, place  $p_3$  is marked. Because the preset of transition  $t_4$  contains  $p_3$  alone, which is marked, it is enabled when its enabling condition,  $\neg(phi \ge 0)$ , evaluates to true. The time at which this condition evaluates to true is circled and marked as E in the simulation trace. At that instant,  $t_4$  is enabled and hence a uniform random value is chosen from its delay assignment range of 1740 to 1750 time units and  $t_4$  is scheduled to fire after that time. The circled portion of the simulation trace marked as D shows that the enabling condition of  $t_4$  holds true for that duration. Hence,  $t_4$  fires at the circled portion marked as A, when the chosen random delay is reached. At this instant, *omega* is assigned a uniform random value between the bounds 1.9 and 2. The marking is then updated by deleting the token from  $t_4$ 's preset place,  $p_3$ , and adding token to  $t_4$ 's postset place,  $p_2$ . From the simulation trace, it can be seen that transition  $t_3$  fires next. This process continues until the value of ctl changes such that transition  $t_5$  can fire.

### 2.5 Verification Property

The LEMA tool accepts a verification property in the form of an LPN. The LPNs produced by the model generation tool have these properties embedded in them so that a model checker can verify them formally. The properties in LPNs are specified using the failure transitions and the SystemVerilog models produced by the model generation tool have these properties embedded in the form of *assertions*. Fig. 2.7 shows an LPN which verifies a simple property of the phase interpolator model generated from the simulation data shown in Table 2.1. It asserts that the generated

Figure 2.7: An example property LPN.

model is functional only when the value of ctl is within the range [0.5,3.5). In this LPN, the set of failure transitions,  $T_f$ , includes the single transition  $t_{12}$ .

## 2.6 SystemVerilog

SystemVerilog is a language developed with the intent of being useful both as an HDL and as a hardware verification language (HVL). It is based on IEEE  $1364^{\text{TM}}$ Verilog language and has extensions which make it easy to write test-benches and allow for reuse of verification intellectual property (IP) [2]. While there are dedicated languages like Verilog-AMS and VHDL-AMS which are capable of modeling AMS circuits, SystemVerilog is chosen for several reasons the primary reason being SystemVerilog models simulate only on a discrete-event kernel whereas the models described in the AMS HDLs mentioned above need a mixed-signal simulator which has a continuous-time kernel and a discrete-event kernel. Though simulation of models written in HDLs like Verilog-AMS is faster when compared to SPICE simulation, the improvement in performance degrades as the amount of code in the *analog* block, which uses the continuous-time kernel, of the Verilog-AMS model increases [36]. For system-level verification where performance of the simulations is critical, it is better to have models which are very efficient if they have sufficient accuracy. The LPN models extracted from the simulation traces can be described in SystemVerilog with a slight compromise in accuracy. Instead of Verilog, SystemVerilog is chosen because SystemVerilog allows real-valued ports for its modules which can be used to model continuously varying signals of analog circuits.

Fig. 2.8 shows an example SystemVerilog model that is equivalent to the LPN shown in Fig. 2.4. The code within the *module* and *endmodule* statements describes a hierarchical block in a design. Modules enforce hierarchy by communicating through a set of input, output, and bidirectional ports. The block of code within the begin and end statements that follow an *initial* statement is called an initial block and is used to set the initial state of the internal and output signals in the block. The assign statement in SystemVerilog is a continuous assignment statement which evaluates the expression on the right hand side whenever there is a change on any of the variables of the expression. The result of the evaluation is assigned to the variable on the left hand side after waiting for an *inertial delay* which follows the # symbol. The block of code within the *begin* and *end* statements that follow an *always* statement is called an always block. The list of signals or events that follow the always @ statement is called a sensitivity list. The assignments inside the always block are procedural assignments and are executed whenever an event is triggered by a change in any of the signals of the sensitivity list. assert statements are generally used to describe properties of the design that are meant to be satisfied always. In other words, assertions can be used to verify properties on the design for a given set of simulations.

```

'timescale 1ps/1fs

module phaseint(omega, phi, ctl);

input real phi, ctl;

output real omega;

logic p_0, p_1, p_2, p_3, p_4, p_5, p_6, p_7, p_8, p_9, p_{10};

wire t_0, t_1, t_2, t_3, t_4, t_5, t_6, t_7, t_8, t_9, t_{10}, t_{11}, t_{12};

initial begin

omega = 2.0;

p_0 = 1'b0; p_1 = 1'b0; ...; p_{10} = 1'b0;

#1 p_0 = 1'b1; p_{10} = 1'b1;

end

assign #delay(\sim t_0,1380) t_0 = \sim (\texttt{ctl}\geq 1.5)\&(\texttt{phi}\geq 0)\&p_0;

assign #delay(\sim t_1,1760) t_1 = \sim(phi\geq0)&p<sub>1</sub>;

assign #delay(\sim t_2,0) t_2 = \sim(ctl\geq2.5)&(ctl\geq1.5)&\sim(phi\geq0)&p<sub>0</sub>;

...

assign #delay(\sim t_{12},0) t_{12} = (\sim (ct1 \ge 0.5) || (ct1 \ge 3.5)) \& p_{10};

always O(posedge t_0) begin

p_0 = 1'b0;

p_1 = 1'b1;

omega = 2.5;

end

always O(posedge t_1) begin

p_1 = 1'b0;

p_0 = 1'b1;

omega = 2.0;

end

always O(posedge t_2) begin

p_0 = 1'b0;

p_2 = 1'b1;

end

. . .

always O(t_{12})

assert(!t_{12})

else $error("Error! Assertion failure");

endmodule

```

Figure 2.8: An example SystemVerilog model.

## CHAPTER 3

# MODEL GENERATION

This chapter describes an improved method for generating LPN and SystemVerilog models from simulations of analog circuits. Section 3.1 shows an LPN model that is generated for a phase interpolator using the model generation method described in [22]. This example is used to illustrate some of the problems that exist in this approach. Sections 3.2 and 3.3 present an improved algorithm for generating models from circuit simulations. In Section 3.4, the techniques used for solving problems faced by the model generator when circuits have transient behavior are presented. Another problem that is addressed is the limited applicability of the generated models. Section 3.5 describes two techniques — insertion of pseudo-transitions and a functional approach — to solve this problem and discusses their limitations. Section 3.6 describes a new method for translating a general LPN to SystemVerilog while retaining the original semantics of the LPN.

## 3.1 Motivation

It is customary for analog designers to simulate their circuits using a variety of test-cases during the process of their design and verification. Little et al. developed the tool LEMA which leverages the designer's simulations to extract the circuit's behavior and represent it in the form of an abstract model [22]. Thus, this tool does not require any additional work from the designer for getting behavioral models required for system-level verification. At the same time, the designers are not required to change their existing block-level verification methodologies for using this method. Fig. 3.1 shows an LPN model generated from the simulation data of a phase interpolator using the method described in [22]. This model is supposed to describe the behavior of the phase interpolator for three different values of ctl as observed in the given simulation

trace. Though the abstract model need not be as accurate as a SPICE model, it still has to represent the circuit's behavior correctly.

Analog circuits typically need a finite response time before attaining a steadystate. Generally, it is the steady state behavior which is of primary interest for functional validation. The method described by Little et al. in [9] does not distinguish the transient behavior from the steady-state behavior, and as a result of the conservative approximations, the steady-state behavior includes the transient behavior as well. This approach can potentially produce uninteresting models which show a combined behavior from the circuit's different operating modes when its operation is expected to be distinct. For instance, transition  $t_3$  in the LPN shown in Fig. 3.1 has a delay ranging from 1320 to 1360 ps. In reality, the circuit's phase delay is changing from 1360 to 1320 ps for a short duration and after that, the delay is precisely 1320 ps. In other words, though the circuit exhibits the properties of two different modes only for a short duration when it switches from one mode to another, the generated model includes the behavior of both the modes of operation for the complete duration because the steady-state behavior is not distinguished from the transient behavior.

The models generated using Little's method describe just the simulation traces from which they are generated. Thus, these models are functional only when the inputs change in the sequence that occurred in the given simulation traces. The model's behavior is not correct for any other input combination. In a phase interpolator, the value of *ctl* decides the phase offset of the output *omega* with respect to the input *phi*, thus defining the mode of operation. The simulation trace used for generating the model shown in Fig. 3.1 had *ctl* switching monotonically from 1 to 3 in steps of 1 and hence transitions  $t_2$  and  $t_5$  are the only transitions that can change the mode of operation for this model. Consequently, this model deadlocks when the value of *ctl* is changed from 2 to 1. This deadlock does not occur if the circuit's simulation trace has a situation where the value of *ctl* changes from 2 to 1. Simulating an analog circuit for different modes of operation is possible, but it is not feasible to exercise all possible permutations of the modes of operation. So, the models generated using this method show a potential incorrect behavior even for the input combinations that are present in the given simulations depending on the sequence of the input changes in the simulation traces.

### 3.2 Overview

This chapter describes the function genModel which takes an initial LPN, N, a set of components, C, a set of simulation traces,  $\Sigma$ , and a set of user-specified parameters, *par*, and generates an LPN and a SystemVerilog model for the system. The given initial LPN model, N, must contain all the design variables at a minimum, and is included as part of the final LPN. Additionally, the initial LPN may also contain a verification property. This feature is particularly useful for embedding verification properties into the models of the circuit, much like the assertions embedded in today's *register transfer level* (RTL) designs. An application of property LPNs is demonstrated in Chapter 4.

A component  $c = \langle In, Out, Care, Ctl \rangle$  is a tuple comprising various subsets of the system variables, S. Each component defines the interface of an LPN process that is being constructed. In component c, In and Out are the inputs and the outputs of an LPN process that is being constructed; Care and Ctl are the set of care variables and control inputs for the process, respectively. For simplicity, it is assumed that the outputs are a subset of care variables (i.e., Out  $\subseteq$  Care). The user-specified parameters, par, that are used in generating the models include  $\tau_{\min}$ ,  $\epsilon$ , ratio, ws, tol, sig, and sep. The parameters,  $\tau_{\min}$ ,  $\epsilon$ , and ratio, are used in the detection of DMV variables. Calculation of rates for continuous variables is done using the window size parameter, ws. Isolation of transient portions from the steady-state portions of the simulations is done using the tolerance parameter, tol. The parameters, sig and sep, are used in the normalization of the LPN model.

Algorithm 3.1 presents the genModel function which is an improved method for extracting behavioral models from simulation traces. This function creates an LPN process for each component  $c \in C$ , and then converts the generated LPN model to SystemVerilog. A component is primarily used to describe the interface of a process in the LPN that is being generated. Each process in the LPN is constructed based on the interface described by its corresponding component. The user can specify the

Algorithm 3.1: genModel $(N, C, \Sigma, par)$

$(X, V) := \text{detectDMV}(V, \Sigma, par)$  $\theta := \text{genThresholds}(X, V, \Sigma, par)$ 3 forall  $c = \langle In, Out, Care, Ctl \rangle \in C$  do  $N := \text{genProcess}(N, c, \Sigma, \theta, par)$ SV := convertToSystemVerilog(N)N := normalizeLPN(N, par)7 return (SV, N)

circuit's input/output interface or a system's block-level connections in the form of a set of components, C. Intuitively, each component,  $c = \langle In, Out, Care, Ctl \rangle$ , can be thought of as a block in a system where In and Out are the inputs and the outputs of the specific block that the component is representing; Care and Ctl are the set of care variables and control inputs of the block, respectively. A variable is said to be a care variable if the sequence in which it changes its region with respect to the changes of other variables is an important aspect that needs to be encapsulated in the generated model. The *Care* is the subset of continuous and DMV variables that includes all the care variables in the circuit being modeled (i.e.,  $Care \subseteq V \cup X$ ). This classification of variables is used in the functional approach described in Section 3.5.1. The inputs of a circuit which when triggered cause the circuit to show a transient behavior that is different from the steady-state behavior for a finite time duration are called control inputs. The notion of control inputs is used to encapsulate the transient and the steady-state behaviors separately in the generated models as described in Section 3.4.2. As the name implies, control inputs, Ctl, are a subset of the input variables, In.

In this method, all the signals in a circuit are classified as either *continuous* or *discrete multi-valued* (DMV) variables. DMV variables are the variables which are stable most of the time. They are useful in abstracting the continuous-time continuous-valued signals that are stable most of the time as continuous-time discrete-valued signals. DMV variables are also useful in modeling buses comprised of multiple data lines as a single variable. Combining the individual lines of a bus in this way reduces the number of state-variables and hence the complexity of the model. Fig. 3.1 shows that ctl[2:0], which are 3 individual thermometer-encoded inputs to the circuit,

are being combined and treated as a single DMV variable, *ctl*, in the generated model. The improved method presented here is illustrated using example circuits which only have DMV variables though the new techniques are directly applicable to circuits with both types of signals.

The first step is to find the subset of the design variables, V, which are DMV. The function detectDMV detects the DMV variables from the set of all variables, V, using the given simulation traces,  $\Sigma$ , and the configurable parameters,  $\tau_{\min}$ ,  $\epsilon$ , and ratio (line 1). The  $\tau_{\min}$  parameter specifies the minimum time duration for which a variable has to be stable if this time has to count towards the total ratio of the waveform duration for which it is stable. The  $\epsilon$  parameter specifies the amount of tolerance allowed for a variable to be treated as having a stable value. The ratio parameter determines the minimum ratio of the waveform duration for which a DMV variable has to be stable. A detailed description of the DMV variable detection method is given in [22]. The above parameters can be configured such that continuous-valued signals like clocks, which are stable most of the time, are abstracted as DMV variables. At the end of this step, the disjoint sets X and V are updated such that the detected DMV variables are moved from V to X.

To generate models, waveforms are split into regions which in turn are depicted as places in the generated LPN. Splitting the waveform into regions is done using the threshold values,  $\theta$ , of the design variables. The  $i^{th}$  region for variable  $\nu$  is defined as  $\xi_i(\nu) = [\theta_i(\nu), \theta_{i+1}(\nu))$  and the thresholds,  $\theta$ , for each variable  $\nu$  are  $\langle \theta_0(\nu), \ldots, \theta_m(\nu) \rangle$  where  $\theta_1(\nu)$  and  $\theta_{m-1}(\nu)$  are the lowest and highest real-valued thresholds, respectively.  $\theta_0(\nu)$  and  $\theta_m(\nu)$  are virtual and are set to  $-\infty$  and  $\infty$ , respectively. Thus, the lowest region for variable  $\nu$  is  $\xi_0(\nu)$  and the highest region is  $\xi_{m-1}(\nu)$ . The function **genThresholds** generates the threshold values for all the variables from the given set of simulation traces (line 2). Greedy algorithms are used to auto-generate thresholds for continuous variables [22]. To generate the thresholds for the DMV variables, the stable values that each DMV variable has in all the simulation traces are extracted. Thresholds for each DMV variable are then determined as the medians of every two adjacent values from the detected set of values of each variable.

The genProcess method generates an LPN process for every component using its interface, simulation data, threshold values, and the user-specified parameters (lines 3-4). The LPN model, N, is updated by integrating the LPN process generated for each component. When a component with exactly the same input/output interface as the actual circuit's is used, it generates an LPN process that represents the circuit's behavior. A user can optionally provide other components that represent the blocks that drive the circuit's inputs. The resultant LPN model can be simulated as a stand-alone system. The convertToSystemVerilog function converts the generated LPN model to a SystemVerilog model that can be integrated with the HDL models of the other digital blocks of the system for system-level simulations. A detailed description of this function is given in Section 3.6. Finally, the normalizeLPN function scales the values, delays, and rates on the transitions in the generated LPN using the parameters, siq and sep, as described in [22]. The normalization step is intended to add precision which aids the formal verification tool described in [22]. Thus, the generated SystemVerilog model can be used with the simulation tools and the normalized LPN model can be used with formal verification tools.

## 3.3 Generation of an LPN Process

Algorithm 3.2 presents the genProcess method which generates an LPN process that it adds to N for a component c, from a set of simulation traces,  $\Sigma$ , using the thresholds,  $\theta$ , and user-specified parameters, *par*. The generation of every LPN process begins by the addition of an initial place, whose postset transitions set the initial states corresponding to each simulation trace. These transitions allow the model to choose an initial state from any of the given simulation traces dynamically based on the applied inputs. The addInitialPlace function adds this initial place to the LPN (line 2). Control inputs are those inputs which can cause the circuit to display a transient behavior that is different from its steady-state behavior for considerable amount of time. To isolate such transient behavior from the steady-state behavior of the model, the addStableVariable function adds a Boolean state variable, *stable*, to the LPN and the simulation data if the circuit has any control inputs (lines 3-4).

**Algorithm 3.2**: genProcess $(N, c, \Sigma, \theta, par)$

```

1 let c = \langle In, Out, Care, Ctl \rangle

2 (N, p_0) := addInitialPlace(N)

3 if Ctl \neq \emptyset then

(N, c, \Sigma, \theta, stable) := addStableVariable(N, c, \Sigma, \theta)

\mathbf{4}

\mathbf{5}

forall \sigma \in \Sigma do

reg := assignRegions(\sigma, In, Out, \theta)

6

rate := calculateRates(\sigma, Out, Care, reg, par)

7

val := calculateValues(\sigma, Out, Care, reg, par)

8

(dur, pre) := calculateDurations(\sigma, In, Out, req)

9

(N, i) := addInitialTransient(N, p_0, \sigma, req, c, dur, rate, val, \theta)

10

if Ctl \neq \emptyset then

11

(\sigma, reg) := addStableToData(\sigma, c, reg, dur, pre, par)

\mathbf{12}

rate := calculateRates(\sigma, Out, Care, req, par)

13

val := calculateValues(\sigma, Out, Care, reg, par)

14

(dur, pre) := calculateDurations(\sigma, In, Out, reg)

15

(N, region) := updateLPN(N, \sigma, i, reg, c, dur, pre, rate, val, \theta)

16

17 if Ctl \neq \emptyset then

c_{stable} := \langle Ctl, \{stable\}, Ctl, \emptyset \rangle

18

N := genProcess(N, c_{stable}, \Sigma, \theta, par)

19

20 N := \text{insertPseudoTransitions}(N, c, region, \theta)

21 return N

```

Algorithm 3.3 describes the steps involved in the addition of the *stable* variable and initialization of the data values for *stable*. The **createStableVariable** function creates a unique variable, *stable*, for each process having a nonempty set of control inputs. Since this variable is Boolean, it is included in the set of DMV variables, X, of the LPN. As the *stable* variable affects the behavior of the LPN process, it is added to its input set, In, and the set of care variables, *Care*. The *stable* variable being a Boolean has a single real threshold of 0.5. The variable *stable* is inserted in the given set of simulation data and its value is initialized as 0 at all the data points. Its actual value at each data point is determined as 0 or 1 depending on whether the circuit is displaying transient behavior or steady-state behavior, respectively at that point. A detailed description of this step is given in the addStableToData function described in Section 3.4.2.

After the initialization of the *stable* variable, the **genProcess** function traverses each of the given simulation traces and updates the LPN process incrementally with

Algorithm 3.3: addStableVariable( $N, c, \Sigma, \theta$ )

| 1        | stable := createStableVariable(N)              |

|----------|------------------------------------------------|

| 2        | $X := X \cup \{stable\}$                       |

| 3        | $In := In \cup \{stable\}$                     |

| 4        | $Care := Care \cup \{stable\}$                 |

| <b>5</b> | $\theta_0(stable) := -\infty$                  |

| 6        | $\theta_1(stable) := 0.5$                      |

| 7        | $\theta_2(stable) := \infty$                   |

| 8        | forall $\sigma \in \Sigma$ do                  |

| 9        | for $i \leftarrow 0$ to $( \sigma  - 1)$ do    |

| 10       | $\sigma_i(stable) := 0$                        |

| 11       | <b>return</b> $(N, c, \Sigma, \theta, stable)$ |