# EFFICIENT, SOUND FORMAL VERIFICATION FOR ANALOG/MIXED-SIGNAL CIRCUITS

by

Andrew N. Fisher

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

August 2015

Copyright © Andrew N. Fisher 2015

All Rights Reserved

# The University of Utah Graduate School

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                                                 | Andrew N. Fisher            |               |

|---------------------------------------------------------------------|-----------------------------|---------------|

| has been approved by the following                                  | supervisory committee membe | ers:          |

| Chris J. Myers                                                      | , Chair                     | May 29, 2015  |

|                                                                     |                             | Date Approved |

| Kenneth Stevens                                                     | s, Member                   | May 29, 2015  |

|                                                                     |                             | Date Approved |

| Priyank Kalla                                                       | , Member                    | May 29, 2015  |

|                                                                     |                             | Date Approved |

| Scott Little                                                        | , Member                    | June 2, 2015  |

|                                                                     |                             | Date Approved |

| Eric Mercer                                                         | , Member                    | May 29, 2015  |

|                                                                     |                             | Date Approved |

|                                                                     |                             |               |

| and byGi                                                            | anluca Lazzi                | , Chair of    |

| the Department of Department of Electrical and Computer Engineering |                             |               |

|                                                                     |                             |               |

| and by David Kieda, Dean of The O                                   | Graduate School.            |               |

## **ABSTRACT**

The increasing demand for smaller, more efficient circuits has created a need for both digital and analog designs to scale down. Digital technologies have been successful in meeting this challenge, but analog circuits have lagged behind due to smaller transistor sizes having a disproportionate negative affect. Since many applications require small, low-power analog circuits, the trend has been to take advantage of digital's ability to scale by replacing as much of the analog circuitry as possible with digital counterparts. The results are known as digitally-intensive analog/mixed-signal (AMS) circuits. Though such circuits have helped the scaling problem, they have further complicated verification. This dissertation improves on techniques for AMS property specifications, as well as, develops sound, efficient extensions to formal AMS verification methods.

With the language for analog/mixed-signal properties (LAMP), one has a simple intuitive language for specifying AMS properties. LAMP provides a more procedural method for describing properties that is more straightforward than temporal logic-like languages. However, LAMP is still a nascent language and is limited in the types of properties it is capable of describing. This dissertation extends LAMP by adding statements to ignore transient periods and be able to reset the property check when the environment conditions change.

After specifying a property, one needs to verify that the circuit satisfies the property. An efficient method for formally verifying AMS circuits is to use the restricted polyhedral class of zones. Zones have simple operations for exploring the reachable state space, but they are only applicable to circuit models that utilize constant rates. To extend zones to more general models, this dissertation provides the theory and implementation needed to soundly handle models with ranges of rates.

As a second improvement to the state representation, this dissertation describes how octagons can be adapted to model checking AMS circuit models. Though zones have efficient algorithms, it comes at a cost of over-approximating the reachable state space. Octagons have similarly efficient algorithms while adding additional flexibility to reduce the necessary over-approximations.

Finally, the full methodology described in this dissertation is demonstrated on two

examples. The first example is a switched capacitor integrator that has been studied in the context of transforming the original formal model to use only single rate assignments. The property of not saturating is written in LAMP, the circuit is learned, and the property is checked against a faulty and correct circuit. In addition, it is shown that the zone extension, and its implementation with octagons, recovers all previous conclusions with the switched capacitor integrator without the need to translate the model. In particular, the method applies generally to all the models produced and does not require the soundness check needed by the translational approach to accept positive verification results. As a second example, the full tool flow is demonstrated on a digital C-element that is driven by a pair of RC networks, creating an AMS circuit. The RC networks are chosen so that the inputs to the C-element are ordered. LAMP is used to codify this behavior and it is verified that the input signals change in the correct order for the provided SPICE simulation traces.

# CONTENTS

| $\mathbf{AB}$ | STRACT                                                                                                                                                                                                                                                                     | iii                                                       |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| LIS           | ST OF FIGURES                                                                                                                                                                                                                                                              | viii                                                      |

| LIS           | ST OF TABLES                                                                                                                                                                                                                                                               | xi                                                        |

| LIS           | ST OF ALGORITHMS                                                                                                                                                                                                                                                           | xi                                                        |

| AC            | CKNOWLEDGMENTS                                                                                                                                                                                                                                                             | xii                                                       |

| СН            | IAPTERS                                                                                                                                                                                                                                                                    |                                                           |

| 1.            | INTRODUCTION                                                                                                                                                                                                                                                               | 1                                                         |

| 2.            | 1.1 Survey of AMS Circuit Verification  1.1.1 Simulation-Based  1.1.2 Equivalence Checking  1.1.3 Theorem Proving  1.1.4 Model Checking  1.2 Contributions  1.3 Dissertation Overview  BACKGROUND  2.1 Labeled Petri Nets  2.1.1 LPN Syntax  2.1.2 LPN Semantics  2.2 LEMA | 22<br>33<br>55<br>66<br>88<br>100<br>13<br>13<br>16<br>22 |

|               | 2.2.1 Model Generator          2.2.2 Translator          2.2.3 Model Checkers                                                                                                                                                                                              | 22<br>25<br>25                                            |

| <b>3.</b>     | LAMP                                                                                                                                                                                                                                                                       | 28                                                        |

|               | 3.1 Related Work 3.2 Motivating Examples 3.2.1 Models 3.2.2 Properties 3.3 LAMP 3.4 Results                                                                                                                                                                                | 28<br>29<br>30<br>32<br>37<br>40                          |

|               | 3.5 TA Translations                                                                                                                                                                                                                                                        | 44<br>48                                                  |

| <b>4.</b>     | RANGES OF RATES                                                                                                                                                                                                            | <b>52</b>                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|               | 4.1 Motivating Example 4.2 Theory 4.3 Reachability Algorithm 4.4 Correctness 4.5 Related Work 4.6 Experimental Results 4.7 Conclusion                                                                                      | 54<br>58<br>61<br>63<br>64             |

| <b>5.</b>     | OCTAGONS                                                                                                                                                                                                                   | 70                                     |

|               | 5.1 Motivating Example 5.2 Theory 5.2.1 DBM Representation 5.2.2 Adding A New Variable 5.2.3 Time Advancement 5.2.4 Warping 5.3 Reachability Algorithm 5.4 Experimental Results 5.5 Conclusion                             | 74<br>75<br>79<br>80<br>84<br>88<br>92 |

| 6.            | CASE STUDIES                                                                                                                                                                                                               | 98                                     |

|               | 6.1 Switched Capacitor Integrator 6.2 C-element 6.3 Conclusion                                                                                                                                                             | 102                                    |

| 7.            | CONCLUSION                                                                                                                                                                                                                 | 115                                    |

|               | 7.1 Summary 7.2 Future Work 7.2.1 Extensions To LAMP 7.2.2 Improving Range of Rate Efficiency 7.2.3 Improving the Octagon Representation 7.2.4 Counter-Example Guided Abstraction Refinement 7.2.5 Real World Case Studies | 117<br>118<br>118<br>119<br>120        |

| $\mathbf{AP}$ | PPENDICES                                                                                                                                                                                                                  |                                        |

| Α.            | TRACES AND RANGES OF RATES                                                                                                                                                                                                 | 122                                    |

| в.            | ADDITIONAL REACHABILITY COMPONENTS                                                                                                                                                                                         | 143                                    |

| C.            | DERIVING THE WARPING EQUATIONS                                                                                                                                                                                             | 153                                    |

| ВĒ            | PEFBENCES                                                                                                                                                                                                                  | 166                                    |

# LIST OF FIGURES

| 2.1  | A model of a capacitor whose charging is turned on by $sw_1$                    | 16 |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | A property LPN for a capacitor stage in Fig. 2.1                                | 17 |

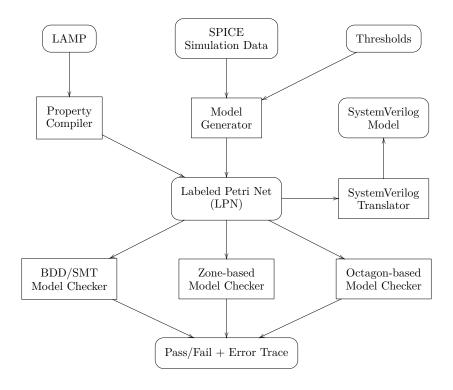

| 2.3  | LEMA's tool flow                                                                | 23 |

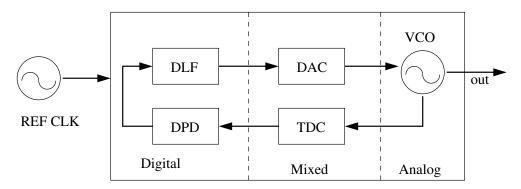

| 2.4  | Digitally-intensive AMS design of a PLL                                         | 23 |

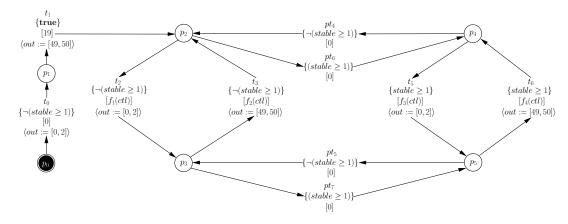

| 2.5  | LPN model for a VCO                                                             | 24 |

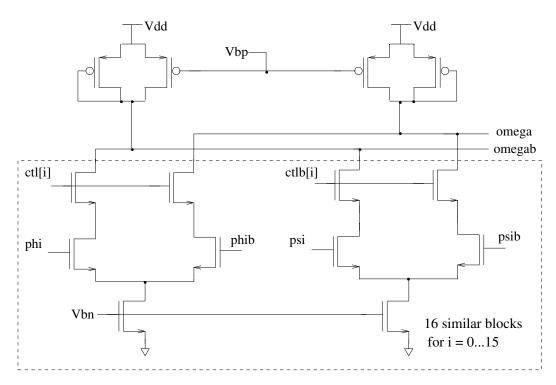

| 3.1  | Phase interpolator circuit implementation                                       | 30 |

| 3.2  | Generated LPN model of a PI circuit                                             | 31 |

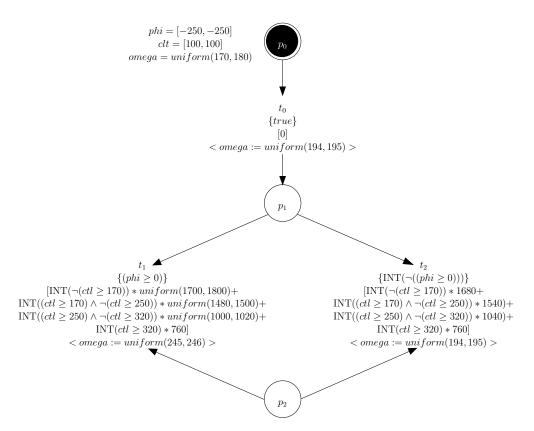

| 3.3  | Model of a VCO with a stable and unstable phase                                 | 32 |

| 3.4  | Model for the process that changes the stable and unstable phases for Fig. 3.3. | 33 |

| 3.5  | Typical simulation trace for a VCO                                              | 34 |

| 3.6  | An LPN for the phase interpolator verification property                         | 35 |

| 3.7  | Format for a LAMP property                                                      | 37 |

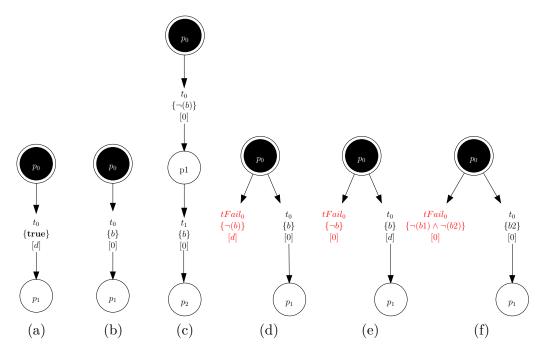

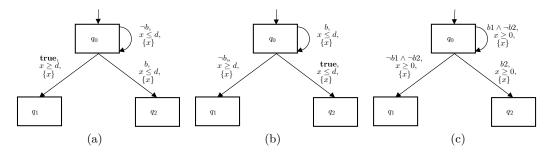

| 3.8  | LPN translations for LAMP statements                                            | 38 |

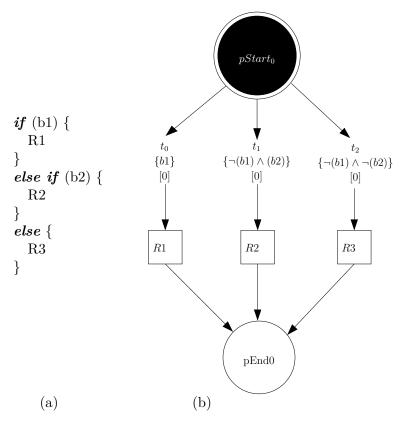

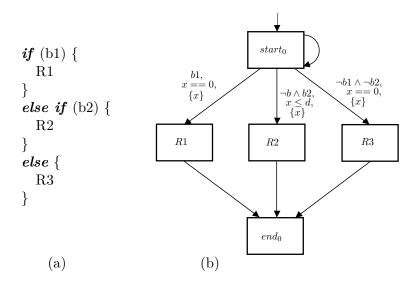

| 3.9  | LPN translation for the $\it if\text{-}else$ statement                          | 39 |

| 3.10 | LPN for an <b>always</b> statement with condition list $\{a, b, \ldots\}$       | 40 |

| 3.11 | PI circuit property using LAMP                                                  | 41 |

| 3.12 | The LPN generated for the LAMP property in Fig. 3.11                            | 42 |

| 3.13 | VCO circuit property using LAMP                                                 | 44 |

| 3.14 | The LPN generated for the LAMP property expressed in Fig. 3.11                  | 45 |

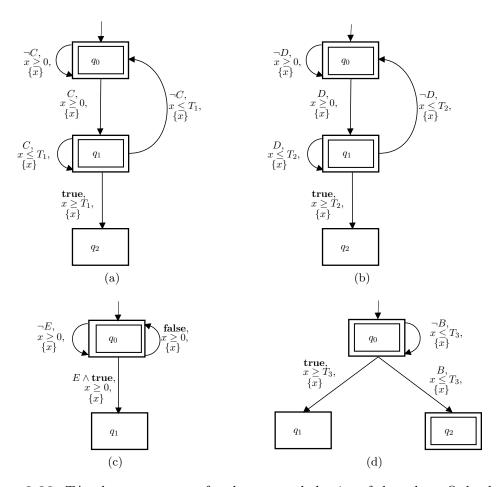

| 3.15 | TA translations for single argument LAMP statements                             | 47 |

| 3.16 | TA translations for binary argument LAMP statements                             | 47 |

| 3.17 | TA translation for the <i>if-else</i> statement                                 | 48 |

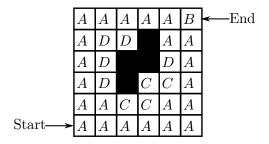

| 3.18 | Robot grid                                                                      | 48 |

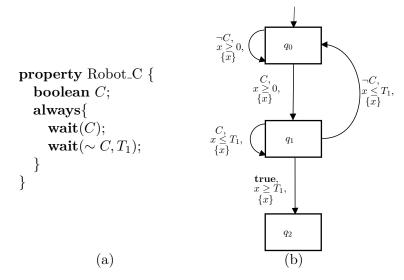

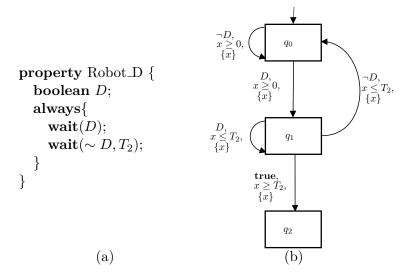

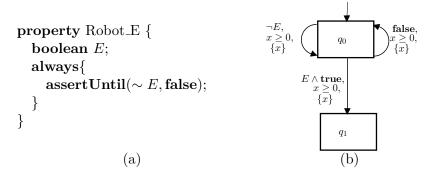

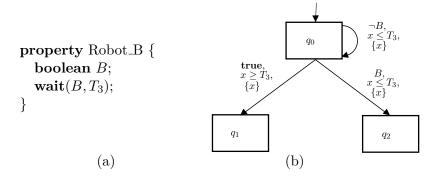

| 3.19 | Property and TA translation for staying in state $C$ for a limited time         | 49 |

| 3.20 | Property for staying in state $D$ for a limited time                            | 50 |

| 3.21 | Property for prohibiting entering $E$                                           | 50 |

| 3.22 | Property for asserting $B$ must be reached                                      | 51 |

| 3.23 | TAs that accept runs for the correct behavior of the robot                      | 51 |

| 4.1  | Capacitor stages $i$ and $i+1, \ldots, \ldots$                                  | 54 |

| 4.2  | A model of a capacitor whose charging is turned on by $sw_i$                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 4.3  | Time advancement of a zone                                                                                                        |

| 4.4  | Warping a zone                                                                                                                    |

| 4.5  | A property LPN for a capacitor stage in Fig. 4.2                                                                                  |

| 4.6  | An example of translating an LPN model into single rates 65                                                                       |

| 4.7  | Modified capacitor properties                                                                                                     |

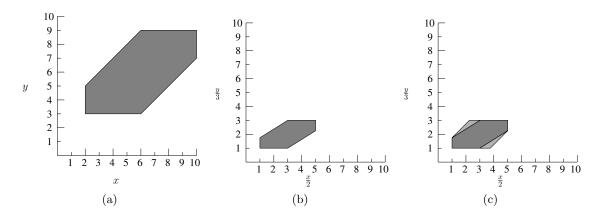

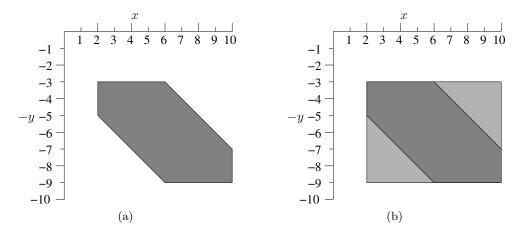

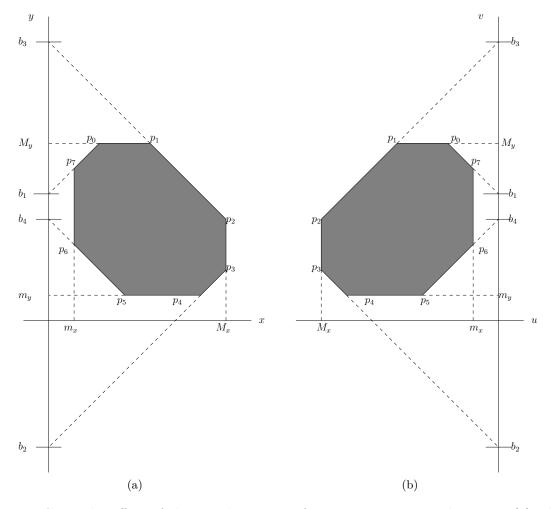

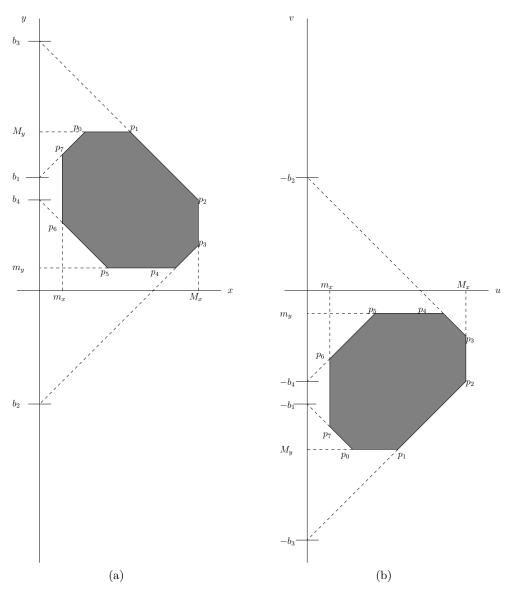

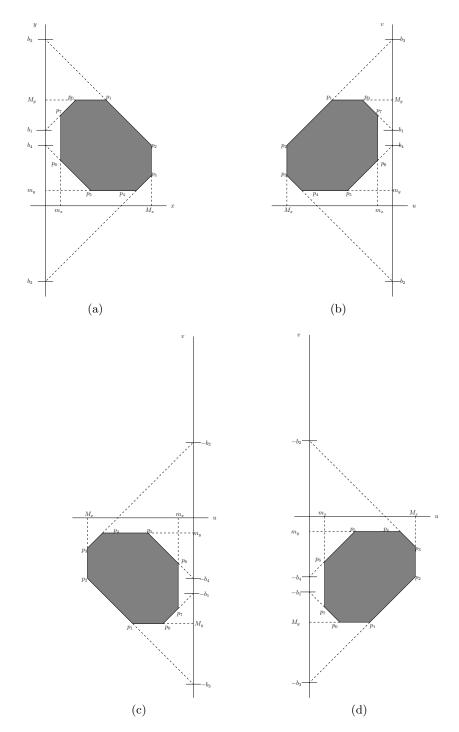

| 5.1  | Warping a zone. 71                                                                                                                |

| 5.2  | Negative warping                                                                                                                  |

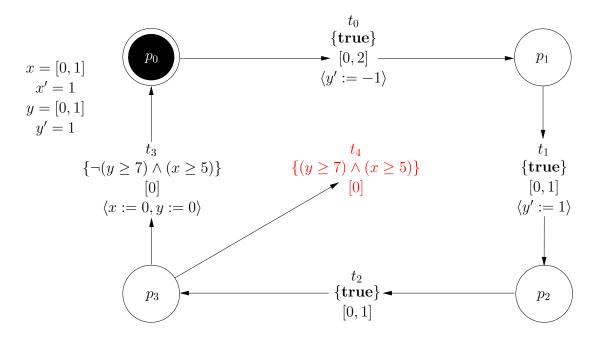

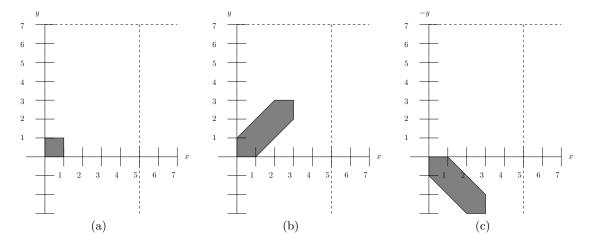

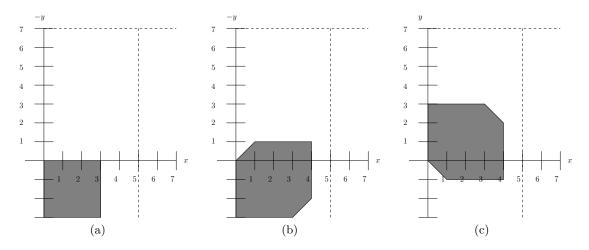

| 5.3  | A model where zones leads to a false negative result                                                                              |

| 5.4  | The first sequence of zones for Fig. 5.3                                                                                          |

| 5.5  | The second sequence of zones for Fig. 5.3                                                                                         |

| 5.6  | The third sequence of zones for Fig. 5.3                                                                                          |

| 5.7  | The initial sequence of octagons for Fig. 5.3                                                                                     |

| 5.8  | The second sequence of octagons for Fig. 5.3                                                                                      |

| 5.9  | The third sequence of octagons for Fig. 5.3                                                                                       |

| 5.10 | A generic octagon                                                                                                                 |

| 5.11 | Exact space obtained by advancing the octagon consisting of the line joining $(1,0,0)$ and $(0,1,0)$ forward 4 time units         |

| 5.12 | Over-approximation required for advancing the octagon consisting of the line joining $(1,0,0)$ and $(0,1,0)$ forward 4 time units |

| 5.13 | Two dimensional time advancement of an octagon                                                                                    |

| 5.14 | Labeled octagon                                                                                                                   |

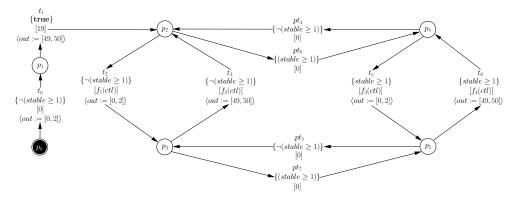

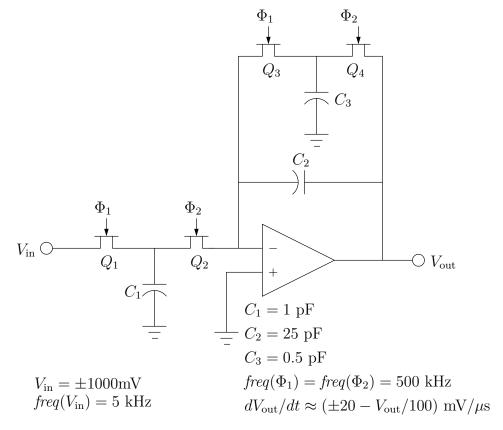

| 6.1  | A schematic drawing of a switched capacitor integrator 99                                                                         |

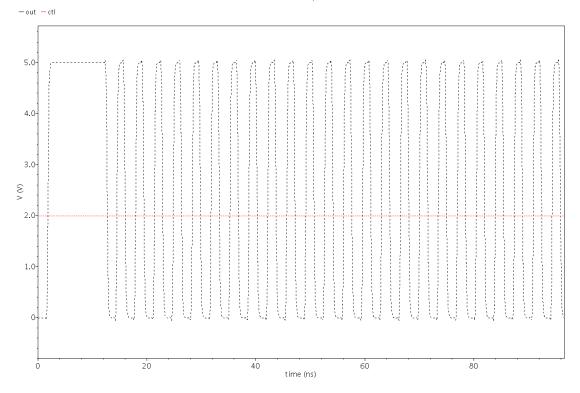

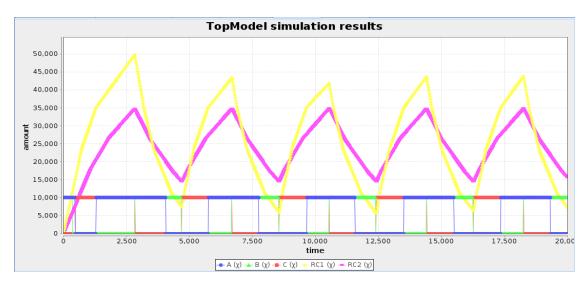

| 6.2  | SPICE simulation of the switched capacitor integrator with $C_2=23~\mathrm{pF.}$ 100                                              |

| 6.3  | SPICE simulation of the switched capacitor integrator with $C_2=27~\mathrm{pF.}$ 101                                              |

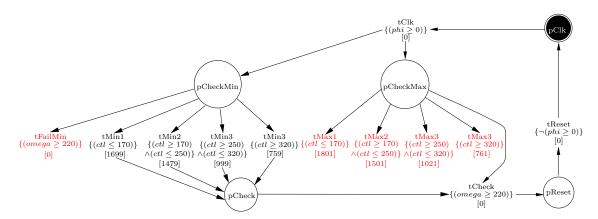

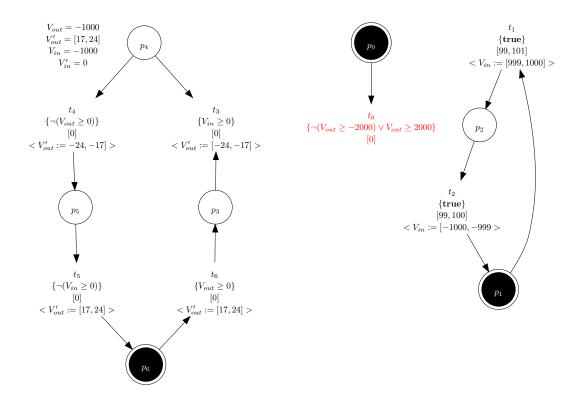

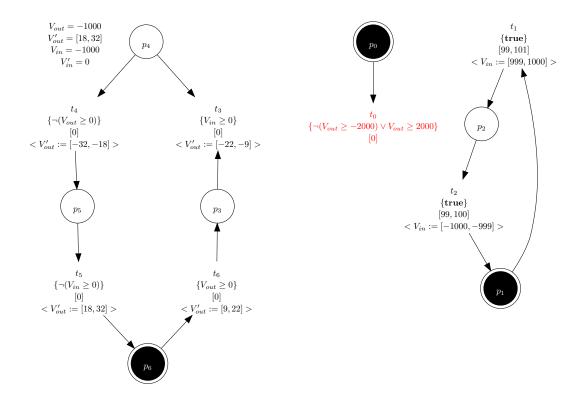

| 6.4  | Generated LPN model of a switched capacitor integrator                                                                            |

| 6.5  | Saturation property for switched capacitor integrator                                                                             |

| 6.6  | The switch capacitor integrator of Fig. 6.1 with a feedback resistor $103$                                                        |

| 6.7  | SPICE simulations traces for the corrected switched capacitor circuit of Fig. $6.6.104$                                           |

| 6.8  | Generated LPN model of a switched capacitor integrator with feedback resistor. $105$                                              |

| 6.9  | Generated LPN model of a switched capacitor integrator with more thresholds $106$                                                 |

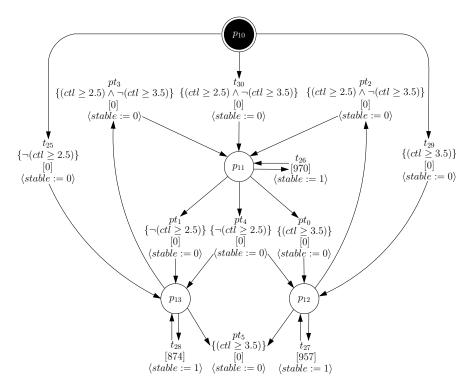

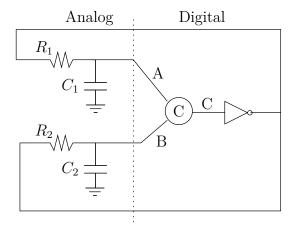

| 6.10 | Digital C-element with inputs driven by RC circuits                                                                               |

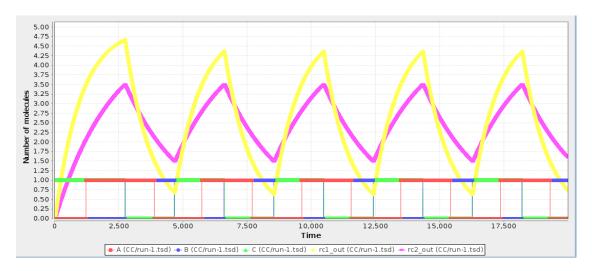

| 6.11 | SPICE simulation data for Fig. 6.10                                                                                               |

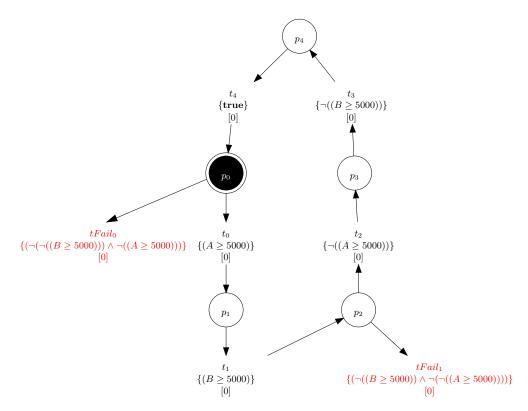

| 6.12 | Property for the circuit in Fig. 6.10 requiring that $A$ changes before $B$ 108                                                   |

| 6.13 | The property LPN associated with Fig. 6.12                                                                                        |

| 6.14 | An LPN model of a C-element                                                                                                                            | 110 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.15 | An LPN model of the $R_1C_1$ network                                                                                                                   | 111 |

| 6.16 | LEMA screenshot of a top-level model connecting the LPNs for each RC-network, the C-element, and the property LPN                                      | 112 |

| 6.17 | An LPN model of the $R_2C_2$ network                                                                                                                   | 113 |

| 6.18 | Simulation of the C-element models                                                                                                                     | 114 |

| A.1  | Example LPN illustrating that resetting a rate once per assignment is not enough to capture all behavior                                               | 123 |

| A.2  | Piecewise approximation of a ranges of rates                                                                                                           | 124 |

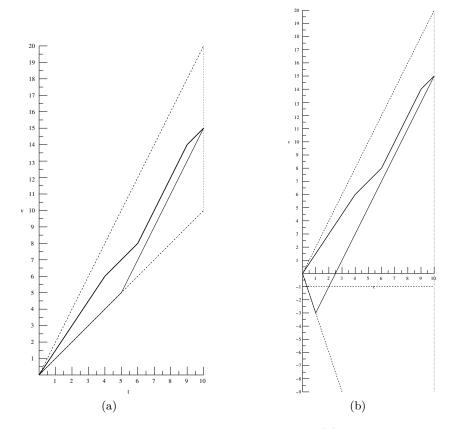

| A.3  | Example trajectories for the continuous variables $t$ and $v$ in Fig. A.1 starting from when transition $t_7$ fires                                    | 128 |

| A.4  | Translation of Fig. A.1a inspired by [25]                                                                                                              | 129 |

| A.5  | Fig. A.1a model transformed to only allow a single resetting of the rate for $v$ .                                                                     | 137 |

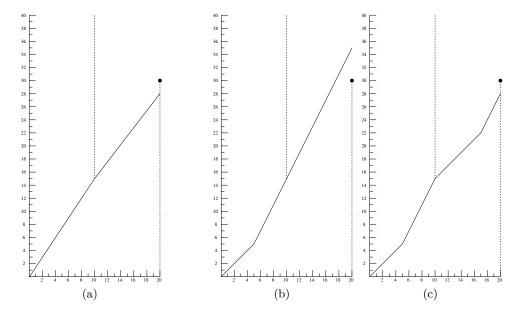

| A.6  | The set of inequality equivalent traces for Fig. A.1 starting at $(v,t) = (0,0)$ , $v' \in [1,2]$ , and $t' = [1,1]$                                   | 140 |

| A.7  | Comparison of rate change event with exact polyhedra                                                                                                   | 141 |

| A.8  | Zone after starting with Fig. A.7c, firing the inequality events $v \ge 15$ , $t \ge 10$ (as well as transitions $t_0$ and $t_1$ ), and advancing time | 141 |

| C.1  | Labeled octagon                                                                                                                                        | 154 |

| C.2  | Warping when $\frac{\beta}{\alpha} > 1$                                                                                                                | 157 |

| C.3  | Warping when $\frac{\beta}{\alpha} < 1$                                                                                                                | 158 |

| C.4  | Warping in the yx-plane when $\frac{\beta}{\alpha} < 1$                                                                                                | 160 |

| C.5  | The effect of the coordinate transformation $u = -x$ and $v = y$                                                                                       | 162 |

| C.6  | The effect of the coordinate transformation $u = x$ and $v = -y$                                                                                       | 163 |

| C.7  | The effect of the coordinate transformation $u = -x$ and $v = -y$                                                                                      | 165 |

# LIST OF TABLES

| 3.1 | Verification results for a PI circuit                                                                                                                                                 | 42  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Verification results for a VCO circuit                                                                                                                                                | 46  |

| 4.1 | Comparison of translational approach [74] to our algorithmic approach with a tFail enabling condition of $\neg(V_i \ge 18)$                                                           | 67  |

| 4.2 | The total number of event firings for the property with tFail $V_i \geq 18$                                                                                                           | 67  |

| 4.3 | Comparison of translational approach [74] to our algorithmic approach with a tFail enabling condition of $V_i \geq 30$ that should not verify to be correct                           | 68  |

| 4.4 | The total number of event firings for the property with tFail $V_i \geq 30.\dots$                                                                                                     | 68  |

| 4.5 | Comparison of translational approach in [74] to our algorithmic approach for the property shown in Fig. 4.5 that should not verify to be correct                                      | 69  |

| 4.6 | The total number of event firings for the property with tFail $\neg (V_i \ge 30)$                                                                                                     | 69  |

| 5.1 | Results of running LEMA on the LPN in Fig. 5.3                                                                                                                                        | 93  |

| 5.2 | Comparison of zones and octagons with a tFail enabling condition of $\neg (V_i \ge 18)$ .                                                                                             | 94  |

| 5.3 | Comparison of zones and octagons with a tFail enabling condition of $\neg(V_i \ge 18)$ . All cases verify as correct                                                                  | 94  |

| 5.4 | The total number of event firings for the property with tFail $V_i \geq 18$                                                                                                           | 94  |

| 5.5 | Comparison of zones and octagons with a tFail enabling condition of $V_i \geq 30$ that should not verify to be correct                                                                | 95  |

| 5.6 | The total number of event firings for the property with tFail $V_i \geq 30$                                                                                                           | 95  |

| 5.7 | Comparison of zones and octagons for the property shown in Fig. 4.5 that should not verify to be correct                                                                              | 96  |

| 5.8 | The total number of event firings for the property with tFail $\neg (V_i \ge 30)$                                                                                                     | 96  |

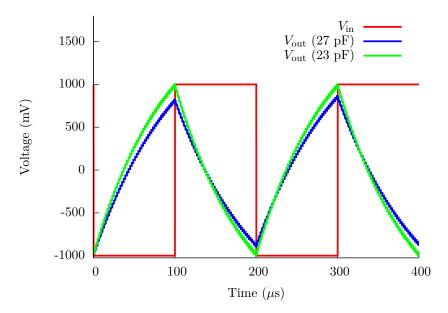

| 6.1 | Comparison of the verification results. for a switched capacitor integrator using the approach of [74], the zone-based approach of Chapter 4, the octagon-based approach of Chapter 5 | 105 |

| 6.2 | Results for verifying the C-element network                                                                                                                                           | 114 |

| A.1 | Collected verification results                                                                                                                                                        | 137 |

# LIST OF ALGORITHMS

| 4.1  | $\mathtt{reach}(N,T_{\mathrm{fail}})$                                                                                                                                                                                 | 60  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | ${\tt findPossibleEvents}(T, En, D, R, RR, I, Z) \ \ldots \ldots \ldots \ldots \ldots$                                                                                                                                | 61  |

| 4.3  | ${\tt updateState}(P,T,V,F,En,D,DA,VA,RA,RR,Z,e,\psi)\ldots\ldots\ldots\ldots\ldots$                                                                                                                                  | 62  |

| 5.1  | $\mathtt{addT}(O,En_{new})$                                                                                                                                                                                           | 89  |

| 5.2  | $\operatorname{addV}(Q,R,O,v)\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$         | 90  |

| 5.3  | ${\tt advanceTime}(En,D,R,I,O)\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$        | 90  |

| 5.4  | ${\tt dbmWarp}(R,R',O)\ \dots \dots$                                                                            | 91  |

| 5.5  | ${\tt recanonicalize}(O)\ \ldots \ldots \ldots \ldots$                                                                                                                                                                | 92  |

| B.1  | $intitialStateSet(T, V, En, DA, M_0, Q_0, RR_0) \dots$                                                                                                                                                                | 144 |

| B.2  | $\operatorname{addV}(Q,R,Z,v) \dots \dots$                                                                      | 145 |

| В.3  | $\operatorname{addT}(Z,t) \ \dots $                                                                             | 145 |

| B.4  | $\operatorname{addSetItem}(T, En, D, R, Z, \mathcal{E}, e_{\text{new}}) \dots $                                 | 146 |

| B.5  | ${\tt happensFirstII}(R,Z,i_{\rm new},i,E)\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$                                                                                                         | 147 |

| B.6  | ${\tt happensFirstIT}(D,R,Z,i_{\rm new},E) \dots \dots$                                                         | 147 |

| B.7  | happensFirstTI $(D, R, Z, t_{\text{new}}, i, E)$                                                                                                                                                                      | 147 |

| B.8  | $\texttt{compareSameV}(i_{\text{new}}, i, E, \texttt{restrictVal}_{\text{new}}, \texttt{restrictVal}) \ \dots $ | 148 |

| B.9  | $\texttt{compareDifferentV}(Z, i_{\text{new}}, i, E, \texttt{restrictVal}_{\text{new}}, \texttt{restrictVal}) \ \dots \dots \dots \dots$                                                                              | 148 |

| B.10 | ${\tt ineqCanChange}(R,I,Z,i)\$                                                                                                                                                                                       | 149 |

| B.11 | $\operatorname{restrict}(T,D,Z,E)\dots$                                                                                                                                                                               | 150 |

| B.12 | ${\tt recanonicalize}(Z)\ \dots \dots$                                                                          | 150 |

| B.13 | $\texttt{fireTransition}(M,F,Q,V,VA,RA,Z,\psi,t)~\dots \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                      | 151 |

| B.14 | $\operatorname{doVarAsgn}(Q,R,Z,VA,t) \dots \dots$                                                              | 151 |

| B.15 | ${\tt advanceTime}(En,D,R,I,Z)\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$        | 151 |

| B.16 | checkIneq(En, R, I, Z, v)                                                                                                                                                                                             | 152 |

## ACKNOWLEDGMENTS

Doing a second Ph.D. was not much easier than doing a first. I learned many new skills, not only in my new field, but also in how to do research in general. I would like to thank my advisor, Chris Myers, for his contributions to this new knowledge. Chris taught me a lot about how to write papers, create presentations, and do reviews. His support in rounding out my academic experience has been invaluable.

Next, I would like to thank my family. They have been a great source of love and support for all things not academic. They have been there through the highs and the lows that come from endeavoring on a difficult course. I would like to especially thank my parents, Kevin and Rhonda Fisher, whose unfailing support has enabled me to finish this degree.

I would also like to thank my labmates, Curtis Madsen, Nick Roehner, and Zhen Zhang. They each helped me to really become part of the group. Curtis taught me a lot about how to be an admin for the lab and was a great companion for discussing computer related topics. Nick provided conversations on the more general topics of philosophy, music, and culture and was over all a very positive force in the lab. Zhen has been my sounding board for numerous topics related to my work and helped me to get my thoughts straight. He was also a willing participant in conversations with me regardless of whether they were closely related to the topic at hand or were something that just occurred to me. In addition, I would like to thank the rest of my labmates, Dhanashree Kulkarni, Leandro Watanabe, Tramy Nguyen, Scott Glass, and Tim Pruss for putting up with me for these few years.

I would like to thank my committee, Ken Stevens, Priyank Kalla, Eric Mercer, and Scott Little. They have been great in helping me throughout the degree. They gave me several ideas for current and future work and have been there whenever I asked for help.

I would like to thank my friends who were not directly related to my research, including Neil Cotter, Derek Crane, Derek Moore, and Jason Parkin. Neil and I both have an interest in mathematics and our chats have provided much needed distractions and have helped me keep in touch with my math background. Derek Crane introduced me to the topic of cybersecurity and fired my interest in that direction. Derek Moore and Jason Parkin have helped to make the long train rides to the university more enjoyable and have been fun to talk to about computer engineering related topics.

Finally, I would like to thank all the past members of the lab who contributed to LEMA. Without their work, this work would not be possible. In particular, I would like to thank Satish Batchu, Kevin Jones, Dhanashree Kulkarni, Scott Little, and David Walter for their contributions to LEMA.

This material is based upon work supported by the National Science Foundation (NSF) under Grant No. CCF-1117515 and an ARCS fellowship. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the NSF.

# CHAPTER 1

#### INTRODUCTION

As embedded systems become more popular, it is increasingly difficult to meet the challenge of creating higher performance circuits within smaller sizes and lower power constraints. Digital devices have been successful in meeting this demand. As one example, in 1971 the Intel 4004 processor had 2,300 transistor and in 2012 the number had grown to over 1.4 billion transistors in the 3rd Generation Intel Core I7 [60]. In the same time frame, the process node decreased from  $10\mu m$  to 22nm. However, shrinking transistor sizes and increasing transistor counts are not enough to create useful designs, especially when the number of transistors is in the billions. Abstraction is necessary to handle such complex designs. Here too, the simplicity of digital circuits has met the challenge by introducing computer-aided design (CAD) tools that support a wide range of abstraction levels and automate large portions of the design process. In particular, several methods have been successfully applied to verifying the correctness of designs [13, 23, 24, 26, 27, 47, 63, 65].

In contrast, analog circuits have not been able to keep pace. Performance doubles about every two years for digital circuits while it takes four to five years for analog performance to double [83]. In particular, scaling is not as favorable to analog circuits. Noise is more prevalent, gains are harder to achieve, and the lower power requirement only exacerbate these concerns. However, analog circuits are necessary in any application that interacts with the real world, such as cell phones and sensors. To cope with this challenge, analog designers have turned to digital alternatives as much as possible resulting in analog/mixed-signal circuits (AMS). In fact, some designs have reached the point of essentially adding a processor and are more accurately described as digitally-intensive AMS circuits. Of course, adding this additional circuitry increases the complexity, making errors more likely, especially when designs are still being done by hand. Although CAD tools have made some strides in areas like sizing and layout [28], the verification problem is particularly difficult to handle in the AMS setting. The traditional simulation methodology is difficult to adapt to the large transistor counts resulting from the digital portions while digital techniques do not support the continuous nature of the analog portion. Even so, strides have been made to

adapt simulation-based verification and convert digital verification methodologies to the AMS domain. These methods are briefly surveyed in Section 1.1. Section 1.2 details this dissertation's contribution to these methods. Finally, Section 1.3 concludes the chapter with an outline of the rest of the dissertation.

# 1.1 Survey of AMS Circuit Verification

Since AMS circuits combine both the analog and digital domains, it is natural to start with either and attempt to extend the techniques to the entire AMS design. Indeed, most AMS verification techniques have been developed in this way and fall into one of four categories: simulation-based, equivalence checking, theorem proving, and model checking. Each of these categories is explored in greater detail in the following subsections. For additional information, one can consult recent survey papers [6, 103, 117].

#### 1.1.1 Simulation-Based

Traditional simulation-based verification utilizes some variant of the Simulation Program with Integrated Circuit Emphasis (SPICE). SPICE [85] simulation does not require any additional work to apply to AMS designs, since, after all, the digital circuits are nothing more than transistors with a convenient abstraction. The difficulty comes when handling the large number of transistors introduced by the digital portion. For example, a digitally-intensive phase locked loop (PLL) can take days or even weeks to verify due to the large number of transistors. Longer simulation time naturally leads to less simulation runs and severely slows down the design process. In turn, functional bugs are more likely to be missed. Simulation is also plagued by the need for a designer to check simulations by hand to determine whether the circuit is functioning correctly, which becomes more difficult as the designs become more complex.

Instead of having a designer check all the simulations by hand, an alternative is to use monitors [5, 22, 31–33, 36, 42, 44, 75–79, 99, 106, 107, 113, 114, 119]. The first step in automatization is to develop a language for describing correct behaviors. Such descriptions are usually written in a type of formal language like *linear temporal logic* (LTL) [13, 97] or the *property specification language* (PSL) [1], which can be parsed algorithmically. Once the property language is chosen, it is used to create assertions that are checked against the traces. This check is performed in one of two ways: online or offline. Online monitoring usually relies on constructing a sequence recognizer that continually checks or monitors the signal. As soon as a trace violates the property, an error is raised. In offline monitoring, the whole set of simulations is constructed beforehand and then checked against the property.

Without having a runtime constraint, offline monitoring is more flexible and can use more complicated algorithms. Though offline and online monitors have made advances towards automation, they remain susceptible to missing errors due to incomplete simulations.

To mitigate the concerns with simulation, one can determine the *robustness* [32, 36] of the property. With robustness, one attempts to determine how sensitive a property is to changes in the simulation traces. Tolerances are provided to indicate how far traces can drift before a property is violated. So robust properties allow traces to vary widely before they are violated. The tolerances allow one to reduce the number of simulations since only one trace needs to be tested in the region defined by the tolerance. Though robustness helps to ensure that all necessary regions are tested, all traces have to be recalculated if any parameters change and sensitive properties still require a large number of simulations.

Another method to reduce the number of required simulations is *event-driven* (ED) simulation. ED simulation attempts to make the cost of creating simulations cheaper by using triggers to determine when to solve differential equations and which equations need to be solved. Like the online methods, however, these approaches ultimately cannot guarantee the correct functioning of a circuit and could miss important behaviors not being simulated.

If the cost of simulations is not a concern, one can use Monte Carlo simulation [113] to determine a properties sensitivity to changes in parameters. With Monte Carlo methods, one runs randomly chosen simulations and aggregates the data to determine the possible distribution of solutions. Confidence intervals are provided to determine the likelihood of failure when conditions change. Of course, the downside is that even more simulations need to be calculated compounding the problem when simulations are expensive.

In contrast to the above methods, which still calculate individual traces, symbolic simulation [108, 111] gathers several traces together in an abstract representation. The simulation is then calculated by manipulating the whole collection. The method of [108] uses a first-order language to describe the state space. The states are formally manipulated to determine how the collection evolves. In [111], the authors use a similar approach by representing states as conjunctions involving interval constraints. Symbolic solution techniques are then used to determine how the state evolves. Though several traces are simulated together, there is still no guarantee that all behaviors are explored and the describing formulas can experience exponential blow-up.

#### 1.1.2 Equivalence Checking

A related notion to verifying circuit correctness is *equivalence checking* where one verifies two circuits perform the same task. In fact, a method of equivalence checking can often

be used as a method of verification by using one circuit description as the specification and the other as the circuit to verify. Then, determining the circuits are equivalent is the same as determining that the circuit matches the specification. In the digital context, equivalence checking is simply the process of determining if two descriptions perform the same function. This ability enables digital circuits to be designed at different levels of abstraction by ensuring that each level is equivalent to the others. For example, one can ensure that a register-transfer level (RTL) description is the same as the synthesized transistor implementation.

With all the benefits equivalence checking brings to digital circuits, it would be advantageous to have this ability for AMS designs. Although it is straightforward to define the equivalence of two digital circuits, AMS circuits are not as simple. Equivalences have been based on frequency domain characteristics [15, 56, 101] and time domain characteristics [55, 59]. In addition, methods have utilized hardware description languages (HDL). Specifically, the AMS extension of the very high speed integrated circuit hardware description language (VHDL), called VHDL-AMS [100]. In each case, equivalence checking is used to determine if descriptions on different levels of abstraction or different implementations on the same level are equivalent.

The methods based on frequency domain characteristics define two descriptions to be equivalent if their transfer functions are equivalent. In [15], the authors map the transfer function to the Z-domain and utilize a digital representation using adders, multipliers, and delay elements. Staying in the s-domain, [56] uses interval arithmetic and tolerances to establish that the transfer functions describe essentially the same behavior. Finally, [101] turns the check into an optimization where one optimizes the conformation of the magnitude and phase response of the implementation to a tolerance around the specification. Though this is useful for analog circuits, it does not extend well to the full range of behavior for AMS circuits since not all behavior needed is frequency based.

Staying in the time domain, instead of mapping to the frequency domain, [55] establishes equivalence by creating a correspondence between solutions of the respective governing differential equations. To identify this correspondence, local linearizations are employed so that the problem reduces to finding transformation matrices. Thus, for a given pair of systems, the local vector fields are computed for a point, then the transformation matrix is found, and a new point along the solution curve is selected. The process of finding local linearization and stepping along the solution curves is equivalent to numerically integrating

the differential equation, so the method is as costly as jointly solving two sets of differential equations and is similar to the calculations needed for SPICE.

Instead of looking at local linearizations, [59] restricts the problem to circuits that have a global linear behavior. Thus, two circuits are equivalent if they exhibit the same linear behavior within a specified tolerance. To determine this linear behavior, a set of random inputs is applied to each system, the output responses are recorded, and the results of linear regression are compared. For general circuits, the design must first be partitioned into appropriate sized blocks and each of these blocks must be verified separately.

On a higher level of abstraction, [100] establishes equivalence based on VHDL-AMS circuit descriptions. The check is split into identifying the digital and analog pieces separately. The digital pieces are compared by creating a mitre and then using Boolean satisfiability (SAT) and binary decision diagram (BDD) [3, 21] techniques to verify equivalence. For the analog portion, the corresponding analog pieces are tied together with a comparator and are equated using a combination of rewriting rules and simulation to determine equivalence. Since the digital and analog portions are handled separately, their interaction is not taken into account.

## 1.1.3 Theorem Proving

Theorem proving verifies circuit correctness by mapping the circuit and specification to a formal description and establishing a proof that the circuit satisfies the property. Formal descriptions include combinations of linear constraints [46, 48–50], systems of recurrence relations (SRE) [4, 5], and the differential temporal logic (dTL) [61, 82, 88–95].

In [48–50], the linear or piecewise linear nature of many analog components is exploited to map the behavior of voltages and currents to a conjunction of linear constraints. After also giving the specification in terms of linear constraints, a decision procedure is applied to determine if the circuit description implies the specification. As a variant of this idea, [46] maps a circuit netlist together with a VHDL-AMS specification to the prototype verification language (PVS) [86] and applies the PVS decision procedures to prove that the netlist satisfies the property. In this context, the circuit description is again based around linear constraints and is thus applicable to analog circuits that can be described by linear or piecewise linear functions. Since these methods are based on intervals and linearizations, they are approximate; however, steps are taken to ensure that the results are conservative.

SREs are a more general class of equations than linear constraints. They allow for more arbitrary combinations of additions and multiplication, as well as allowing for division, logical expressions, and if-then-else constructs. The work of [4] maps AMS circuits and

corresponding properties to SREs by using a set of rewriting rules. After obtaining the SRE description, the proof proceeds by an induction argument. In [4], the properties are written almost directly in terms of SREs; however, [5] extends the property descriptions to PSL [1, 45].

Instead of extending the the class of equations, one can build on the logic specification idea. The series of papers [61, 82, 88–95] directly incorporate differential equations into the logic semantics creating the differential dynamic logic ( $d\mathcal{L}$ ) and its extensions differential temporal dynamic logic (dTL) and  $dTL^2$ . With  $d\mathcal{L}$ , dTL, and  $dTL^2$ , one can directly translate a hybrid automata model into a hybrid program that is a description of the circuit in the formal language. Once the model is constructed, one can then proceed to prove properties about the system using formal proofs in  $d\mathcal{L}$ , dTL, or  $dTL^2$ . In particular, one can write properties for the correct operation of the circuit and prove whether the system satisfies them. In all cases, the proofs can be partially automated. When running the automation, one of three cases occurs: a proof that the property is satisfied, a proof that the property is not satisfied, or the theorem prover cannot produce a proof either way. When the theorem prover cannot produce a proof, it is necessary that additional information be found (by hand) to give to the theorem prover so it can make progress.

#### 1.1.4 Model Checking

Model checking, also known as reachability analysis, is the process of finding all the possible states a system can reach from the initial conditions. Properties are translated into forbidden states and are checked by determining if these states are in the reachable set. Model checking is a well established methodology in the digital domain [26, 27, 63]. Though digital model checking has to contend with large state counts, the state space is computable and the basic process is straightforward. AMS model checking, on the other hand, has an infinite state space that is usually not computable [58, 96]. Even still, progress has been made with approaches ranging from discretizing the state space [51–53, 105], performing numeric next state calculations [39, 70, 71, 73, 109, 110, 118], manipulating symbolic next states [112], and combining different methods [116].

One of the earliest ideas for model checking AMS designs stems from the already available digital model checking tools. If the AMS problem is turned into a digital problem, then the rest of the checking can be done utilizing already existing tools. In [51–53], the authors attempt to turn the AMS model checking problem into a digital one by cutting the continuous space into hyper-cubes thereby discretizing the space. The hyper-cubes are formed by selecting a finite set of discrete points for each coordinate direction. Each

hyper-cube becomes a state and transitions are added between any two states for which there is a local linear solution that starts in one state and ends in the other. In this approach, trajectories are best approximated when they move perpendicular to the face of the hyper-cubes; however, the hyper-cubes are fixed regardless of the direction of the dynamics. To achieve a better approximation, [105] extends the hyper-cube construction so they follow the path of the trajectories. To verify properties of interest, it is often necessary to pick fine-grained partitions which result in a large state space for the digital checker. Hence, the state space limit of digital model checking is often reached.

To avoid a complete discretization, one usually adopts a model formalism that has both discrete and continuous parts such as linear hybrid automata (LHAs) [7] or labeled Petri nets (LPNs) [74]. Due the presence of continuous variables, the state space is infinite, so equivalence classes of states are formed to produce a finite representation. These equivalence classes are usually some subclass of polyhedra. The choice of which subset is a trade-off between accuracy and complexity of representation. After selecting the subclass, the next challenge is to determine how the state space evolves. In [70], the authors allow time to flow forwards until a constraint on the continuous variables is violated. SPICE simulations are run to determine which constraints are reachable from the current state. Avoiding SPICE calculations, [118] uses a more symbolic approach. The state space is represented as a formula on intervals and interval arithmetic together with Taylor series approximations to find estimates on the solutions to the differential equations that start in the given state. Allowing for even more general sets of solutions, [39, 71] introduce a class of polyhedra defined by a fixed set of prechosen unit vectors. The next states are found by essentially incorporating a linear numerical integrator that is lifted to sets. By using set representation, these methods have the advantage of collecting together multiple solutions, though the complexity of finding these solutions is still high.

In an effort to simplify these calculations, [73] chooses a more restrictive polyhedra set. By reducing the complexity of the representing space, they are able to reduce the complexity of the next state calculations to essentially setting the upper bound variable constraint to their maximum values allowed by any constraints defined on the variables. Though the method reduces the calculation overhead, the restrictive nature of the polyhedral class leads to large over-approximations of the exact state space.

An even more symbolic approach to constructing next states is to encode the behavior as a BDD or SAT formula. In [112], the authors present two methods: the first is based on BDDs and the second on SAT. In both cases the states are represented symbolically as constraints on the system. In the BDD version, the method starts with the set of failure states and then iteratively calculates which states could have reached the current collection of states. The process continues until a fixed point is reached, which is then intersected with the initial states to determine if any of the initial states can lead to the failure. The SAT method starts with a symbolic representation for the initial state and then iteratively adds constraints that represent the next states reachable from the current states. This process is similar to the unrolling of a programming loop with each stage indicating what states are reachable after n iterations. Though these methods avoid performing numerical integration, the BDDs are difficult to maintain as the state space increases while the SAT method is only able to perform bounded model checking, that is modeling checking that is bounded in either time or number of iterations.

Recently, [116] has proposed a hybrid approach combining SPICE simulations and SAT solvers. Since SAT solvers can have an exponential runtime, [116] first uses SPICE simulations to reduce give an initial estimate of the state space and then runs a SAT solver to provide soundness. Running too many SPICE simulations follows the law of diminishing returns where the extra run-time needed to calculate the SPICE traces does not significantly reduce the run-time for the SAT solver. To find an optimal point, [116] uses a Bayesian estimate to determine how many SPICE simulations should be run.

## 1.2 Contributions

This dissertation presents improvements in the tools and algorithms used to specify and verify properties for AMS circuits. The four contributions of this dissertation are the following.

- An extension to the language for analog/mixed signal properties (LAMP).

- Developing the necessary theory for soundly exploring LPNs with ranges of rates and applying it to extending zones.

- Implementing a state exploration algorithm based on octagons.

- Demonstrating the new verification flow for LEMA.

The first contribution is to extend the AMS property language LAMP. The goal of LAMP [37, 66, 67] is to be a simple, intuitive language that is easier for nonexperts to use. The LAMP language is written more like a programming language and describes properties that are checked procedurally. Thus, LAMP avoids the need for analog designers

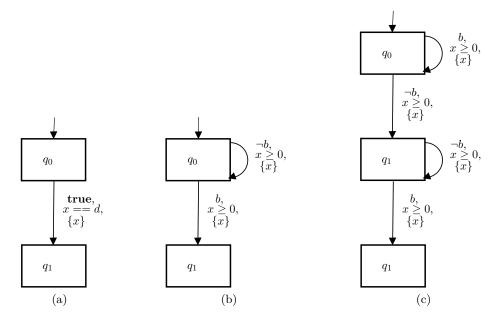

to learn and understand temporal logics. In addition, LAMP is easy to translate into LPNs, making model checking simpler. However, LAMP is still at a nascent stage and does not support many constructs. Two new constructs are added to LAMP: a delay statement and a generalized always block. The delay statement allows LAMP to ignore transient periods without performing a check. The always block is given a sensitivity list that allows the property check to break out of the loop when the signal changes. This change allows the property to handle more general environments since checks can be aborted when the conditions change.

The second contribution is to provide the underlying theory necessary to perform zone-based state exploration for LPNs with ranges of rates. Part of the flexibility of the LPN semantics is to allow a continuous variable to be assigned a range of possible rates. Such generality aids in doing linear approximations to nonlinear dynamics and is built into the automatically generated LPNs in [73]. While some versions of state exploration can handle these ranges of rates, methods like zones are designed around having a single rate. Though zones are less accurate than other methods, they are easier to implement and have efficient algorithms, so it would be useful to apply them to LPNs with ranges of rates. It is shown that it is enough to consider only the extremal and zero rates. Using this fact, the zone based model checker algorithm of [72] is extended to handle ranges of rates.

The third contribution is to implement an octagon-based model checker. While zones have the advantage of having a simple representation and efficient algorithms, they lead to large over-approximations of the state space, especially in the presence of negative rates. Octagons add a symmetry that reduces the negative-rate over-approximations to the same level as positive rates, thus creating a more accurate state space representation. Moreover, the representation requires only a minor adjustment to the zonal version while the algorithms maintain the same level of complexity.

The fourth contribution is to demonstrate the complete new verification flow for LEMA. This dissertation adds additions to LAMP, extends the zone-based method to ranges of rates, and adds the new octagon-based model checker. With these additions, LEMA's tool flow has been altered some from previous versions. Now, it is possible to learn models, create properties, and directly verify the properties against the models with the zone-based model checker and a new octagon-based model checker. These new changes are illustrated with the aid of a few small examples.

## 1.3 Dissertation Overview

The rest of the dissertation is divided into six chapters. The basic outline is a background chapter, a chapter per contribution, and a final concluding chapter.

Chapter 2 provides the background material for the dissertation. This chapter introduces the formal syntax and semantics for LPNs, and introduces the *LPN embedded mixed-signal analyzer* (LEMA) tool. It is critical to introduce LPNs since they are the formalism used by the work in this dissertation for modeling AMS circuits, as well as representing properties. In fact, the most relevant verification flow for this dissertation is the following. Start with an LPN model of the circuit. Combine this model with an LPN for the property. Finally, use a state exploration algorithm to determine whether a failure transition can ever fire. Every chapter that follows relates back to some aspect of this flow. Since this is the case, Chapter 2 also provides a brief overview of the tool LEMA.

Chapter 3 introduces the LAMP language. Before giving the formal definition of LAMP, this chapter provides an overview of other property languages used in specifying AMS properties. Some of these languages are illustrated by creating a property for a phase interpolator (PI). LAMP is then formally defined and used to specify the same PI property for comparison. The extensions to LAMP are folded into the definition of LAMP and are further illustrated by means of an example property for a voltage controlled oscillator (VCO). Specifically, the previous LAMP statements could not handle the transient behavior of the VCO that is present before the oscillation stabilizes. This behavior can now be ignored by using a delay statement. In addition, the always block is extended to allow breakouts when the environment changes. Previously, properties would incorrectly signal a failure if the environment changed in the middle of the check. The new always block allows the property to reset the check when the environment changes. This ability is illustrated using the the VCO. The always block is written to use the voltage so the correct oscillation can be checked after the voltage changes.

Chapter 4 provides the theory and implementation for handling ranges of rates. This chapter is comprised of 3 stages. It starts with a discussion of previous attempts to handle ranges of rates. In particular, two translational methods are discussed that both seek to solve the problem by changing the LPNs involved. It is already known that one of the approaches does not solve the problem; however, it is shown that the second approach does not work either. It may be possible to adapt these methods, but this approach leads to generating a new LPN model per LPN property. Following this discussion, some additional terminology for LPNs is introduced and then the general theory for handling ranges of rates

is presented. Using the theory as inspiration, LEMA's zone-based model checker is modified to handle ranges of rates.

Chapter 5 presents the use of octagons for AMS verification. This chapter starts by presenting an example where LEMA's zone-based model checker falsely declares that an LPN fires a failure transition. It is also shown that by tightening the over-approximation for negative rates with the use of octagons, the false negative can be eliminated. Octagons are then formally defined and the zone-based model checker is modified to implement octagons. The new octagon model checker is then run on the example to show that indeed, the false negative is eliminated. This chapter concludes by indicating how much of an over-approximation is introduced by the operations on octagons.

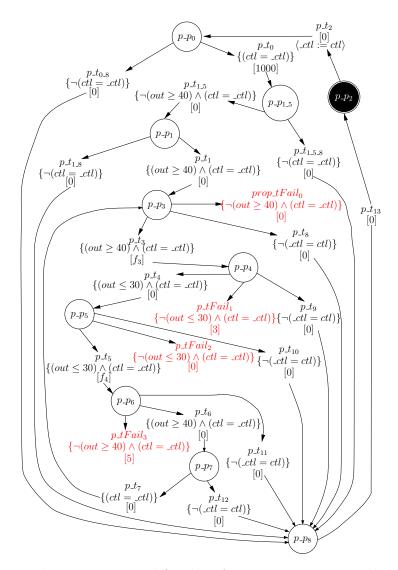

Chapter 6 demonstrates LEMA's full tool flow starting with properties and SPICE traces and ending with the extensions to the zone-based model checker and using the new octagon-based model checker. The first case study is a switched capacitor integrator. It is shown that the previous property of nonsaturation can be codified in LAMP and that all the previous results for this circuit can be recovered with less of a state count and without needing to translate the model or check additional conditions to ensure correctness. The second example is a digital C-element that is driven by two RC networks. The property provided is to ensure an ordering on the inputs for the C-element. It is shown how the property can be written in LAMP and the circuit is verified.

Chapter 6 demonstrates the complete new verification flow for LEMA with the the aid of two examples. In each case, a model is learned using the model generator, a property is written in LAMP, and the zone-based and octagon-based model checkers are applied. The first example is a switched capacitor integrator. This circuit has been studied before in [74]. The main changes to the previous demonstration are the addition of using LAMP, the removal of the model translation steps, the removal of any additional checks in order to accept positive verification results, and the use of octagons. The second example is a digital C-element whose inputs are driven by a pair of RC networks. The SPICE simulation traces were provided by a third party along with the property that the one input signal to the C-element changes before the other. This property is codified in LAMP, a model is learned from the SPICE traces, and the property is verified.

Chapter 7 provides a summary of the contributions of this dissertation. It recaps how LAMP is extended and what additional flexibility this provides. Then, it discusses how the theory for handling ranges of rates lays the foundation for implementations based on single rates. Next, the utility of using octagons is summarized followed by a brief discussion of how

the case studies indicate where octagons and zones fit in view of more general polyhedral methods. This chapter concludes with future work.

# CHAPTER 2

## BACKGROUND

This dissertation utilizes LPNs [17, 66, 68, 73] as the chosen formal model for both modeling the behavior of circuits and for creating properties that check this behavior. As such, nearly every chapter depends on a knowledge of them. Furthermore, the work presented has been incorporated into LEMA. This chapter presents this necessary background. Section 2.1 introduces LPNs and Section 2.2 describes LEMA.

#### 2.1 Labeled Petri Nets

This section provides an overview of the LPN formalism used in this dissertation. LPNs are a type of Petri net that add the ability to reason with continuous variables in addition to the discrete events supported by LPNs. LPNs are a culmination of a few iterations of extensions to Petri nets, a formalism introduced in [87]. The basic Petri net structure provides a framework for discrete events and naturally supports concurrent events. On this foundation, several variants have been developed including timed Petri nets (TPNs) [80], timed event/level (TEL) structures [18], first-order Petri nets (FOPN) [14], and many others. LPNs are a type of hybrid Petri (HPN), which incorporate timing, discrete events, and continuous variables. The formal definition is provided in Sections 2.1.1 and 2.1.2.

#### 2.1.1 LPN Syntax

An LPN is a type of Petri net that has been augmented with a set of labels for modeling continuous variables and their rates of change. This does not preclude the use of discrete (or Boolean) variables since they can be modeled using a continuous variable with a rate of zero. LPNs are assumed to be safe and, in general, continuous variables are allowed to nondeterministically choose a rate from an interval of possible rates. Formally, an LPN is a tuple  $N = \langle P, T, T_f, V, F, M_0, Q_0, R_0, L \rangle$  where:

- P is a finite set of places:

- T is a finite set of transitions:

- $T_f \subseteq T$  is a finite set of failure transitions;

- V is a finite set of continuous variables;

- $F \subseteq (P \times T) \cup (T \times P)$  is the flow relation;

- $M_0 \subseteq P$  is the set of initially marked places;

- $Q_0: V \to \mathbb{Q}$  is the initial value of each continuous variable;

- $R_0: V \to \mathbb{Q} \times \mathbb{Q}$  is the initial range of rates for each continuous variable;

- L is a tuple of labels defined below.

Failure transitions are used by LPNs to signal when a failure has occurred, and the *flow* relation, F, is used to describe how the places and transitions are connected. Every transition  $t \in T$  has a preset denoted by  $\bullet t = \{p \mid (p,t) \in F\}$  and a postset denoted by  $t \bullet = \{p \mid (t,p) \in F\}$ . The set  $\mathbb{Q} \times \mathbb{Q}$  is identified with the set of intervals so that  $(a,b) \in \mathbb{Q} \times \mathbb{Q}$  corresponds to the interval [a,b] with  $a \leq b$ . Furthermore, the intervals are restricted to either be nonnegative (that is,  $a \geq 0$ ) or negative (that is, b < 0). The labels, L, for an LPN are defined by the tuple  $L = \langle En, DA, VA, RA \rangle$ :

- $En: T \to \mathcal{P}_{\phi}$  labels each transition  $t \in T$  with an enabling condition;

- $DA: T \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  with an expression for the delay before a transition t can fire;

- $VA: T \times V \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  and continuous variable  $v \in V$  with an expression for the continuous variable assignment that is made to v when t fires;

- $RA: T \times V \to \mathcal{P}_{\chi}$  labels each transition  $t \in T$  and continuous variable  $v \in V$  with an expression for the rate assignment that is made to v when t fires.

The enabling conditions are Boolean expressions,  $\mathcal{P}_{\phi}$ , that satisfy the grammar:

$$\phi ::= \mathbf{true} \mid \neg \phi \mid \phi \land \phi \mid v \ge c$$

where  $\neg$  is negation,  $\wedge$  is conjunction, v is a continuous variable, and c is a rational constant. The expressions **false** and  $\vee$  are defined from these. In addition, the negation of  $v \geq c$  is defined as  $v \leq c$  since strict inequalities are not supported in the zone-based verification that is extended in this dissertation. The assignments are numerical formulae,  $\mathcal{P}_{\chi}$ , that satisfy the following grammar:

$$\chi ::= c \mid \infty \mid v \mid (\chi) \mid -\chi \mid \chi + \chi \mid \chi * \chi \mid INT(\phi) \mid rate(v) \mid [\chi_i, \chi_j]$$

where the function INT( $\phi$ ) converts a Boolean expression that evaluates to **true** or **false** to 1 or 0, respectively, the function rate(v) returns the current range of rates for the continuous variable v, and  $[\chi_i, \chi_j]$  defines an interval of values that depends on the values of  $\chi_i$  and  $\chi_j$  when evaluated.

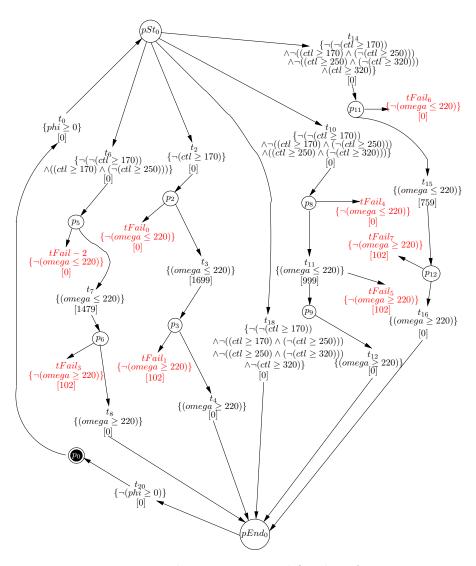

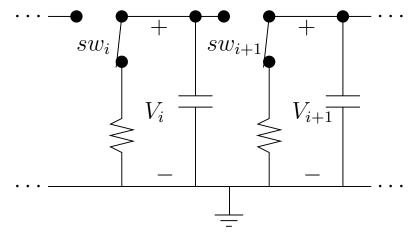

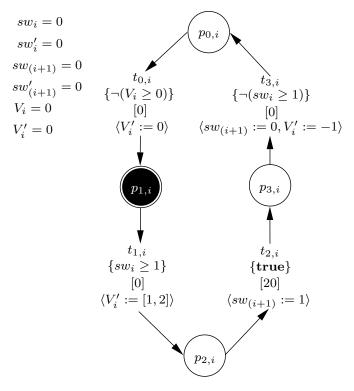

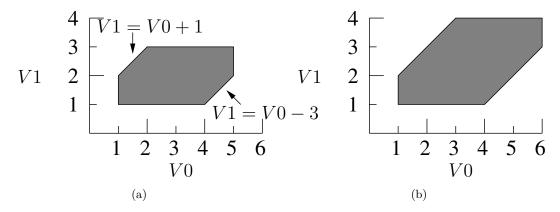

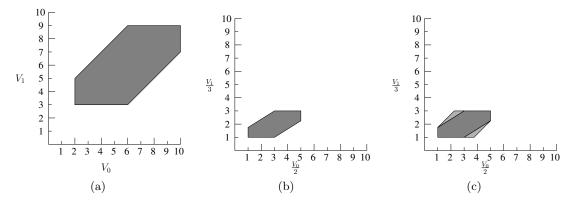

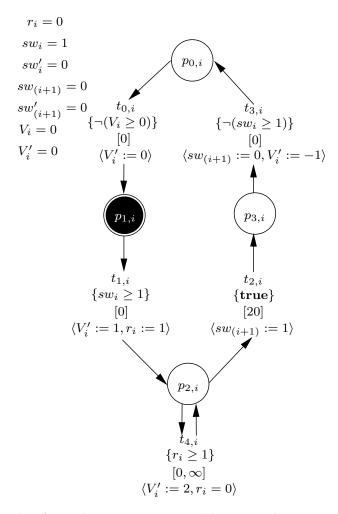

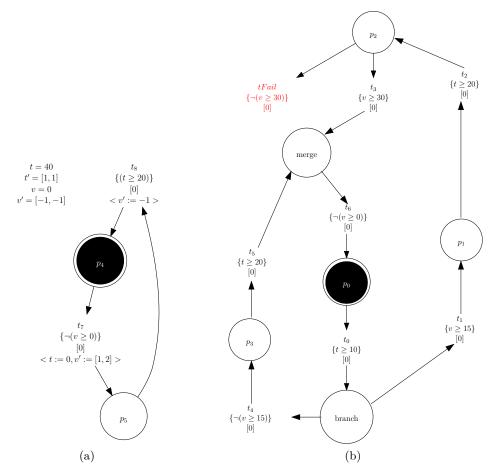

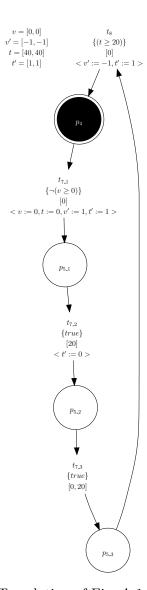

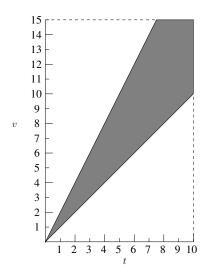

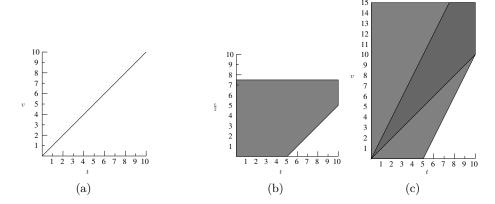

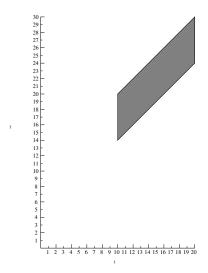

As a running example, consider a sequence of capacitors that are charged sequentially. The charging phase of the first capacitor is initiated by a switch  $sw_0$ . After  $20\mu s$  of charging, a switch  $sw_1$  is turned on, initiating the second capacitor's charging phase, and so on. When the switch  $sw_0$  is turned off, the first capacitor starts discharging and the switch  $sw_1$  is turned off, starting the second capacitor to discharge, and so on. Fig. 2.1 shows an LPN model of the i-th capacitor where the charging is some uncertain rate between  $1\text{mV}/\mu\text{s}$  and  $2\text{mV}/\mu\text{s}$ . The initial marking is  $M_0 = \{p_{1,i}\}$  and is represented by the filled in circle. The values  $V_i = 0$  and  $V'_i = 0$  are the initial conditions for the voltage  $V_i$ . The variables  $sw_i$ and  $sw_{(i+1)}$  are essentially Boolean variables with initial values of 0, representing false. The enabling conditions, delays, and variable assignments are in the curly braces, square brackets, and angle brackets, respectively. In this example, the delays are constants rather than bounds. Initially, the capacitor is not charging. When the signal  $sw_i$  is set to 1, charging is initiated by assigning the interval [1,2] to  $V_i'$ , which indicates the rate of  $V_i$ can be any rate between  $1 \text{mV}/\mu \text{s}$  and  $2 \text{mV}/\mu \text{s}$ . The capacitor is allowed to charge for  $20 \mu \text{s}$ (given as a delay on the transition  $t_{2,i}$ ) before setting the variable  $sw_{(i+1)}$  to 1. Once the charging is turned off, that is, when  $sw_i$  is set to 0, the capacitor begins to discharge at a rate of  $-1\text{mV}/\mu\text{s}$ . Finally, when the capacitor is fully discharged, the  $t_{0,i}$  transition fires, setting the rate to zero.

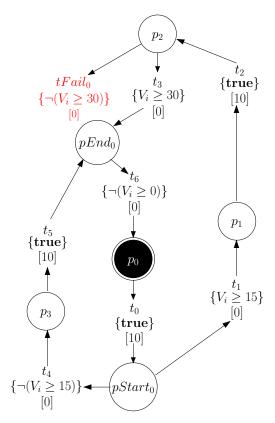

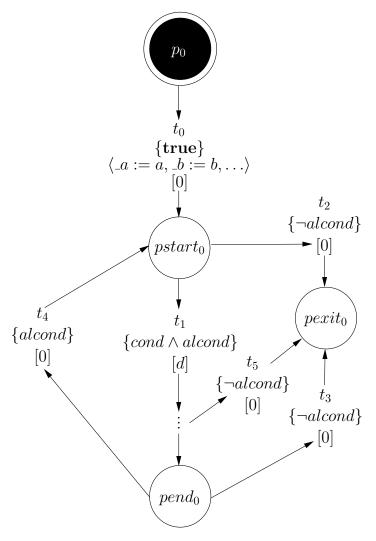

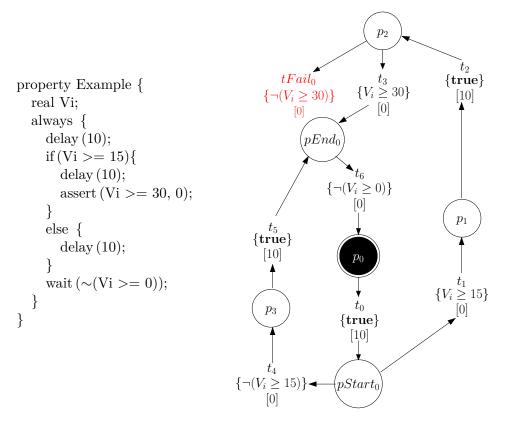

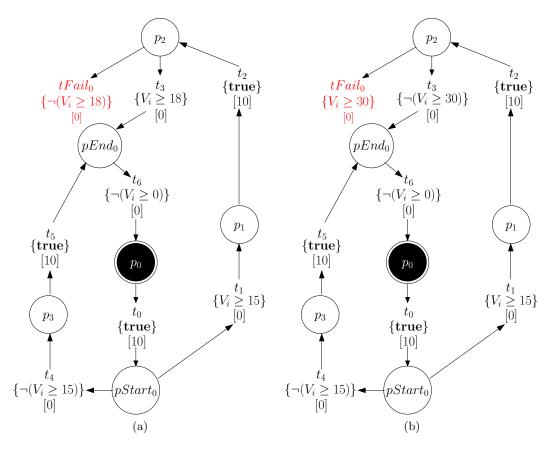

Property checks are added to an LPN model by adding failure transitions  $T_f$ . Failure transitions are specialty transitions that, when fired, indicate a failure. The red transition, tFail, in Fig. 2.2 is an example of a failure transition. This transition checks the property that, when  $sw_i \geq 1$  is **true**, if  $V_i$  is greater than 15 after 10 time units, then  $V_i$  is greater than 30 after an additional 10 time units. Failure transitions can be added directly to a model or to a separate LPN as in Fig. 2.2. When the failure transition is in a separate LPN, the LPN with the failure transition is called a property LPN. For example, the LPN in Fig. 2.2 is a property LPN that checks a property for Fig. 2.1.

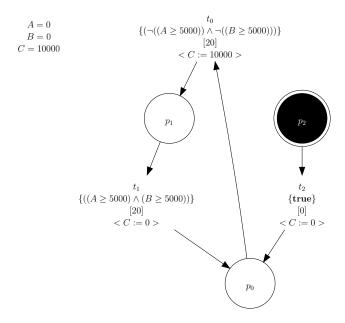

**Figure 2.1**: A model of a capacitor whose charging is turned on by  $sw_i$ . After a time delay of  $20\mu$ s, the switch  $sw_{(i+1)}$  is turned on (i.e., set to 1), initiating the charging of the next capacitor. Note that [d] is used when  $d_l(t) = d_u(t) = d$ .

#### 2.1.2 LPN Semantics

The state of an LPN consists of the set of marked places, the time each transition has been enabled, the delay range for each transition, the values of the continuous variables, the rate for each continuous variable, and the range of rates for each continuous variable. To determine which transitions can fire, the state also includes the truth value of each predicate,  $v_i \geq c_i$ . The set of all inequalities is denoted by  $\mathcal{I}$ . The state of an LPN is formally defined as a tuple  $\sigma = \langle M, C, D, Q, R, RR, I \rangle$  where:

- $M \subseteq P$  is the set of marked places;

- $C: T \to \mathbb{Q}$  is the value of each transition's clock;

- $D: T \to \mathbb{Q} \times \mathbb{Q}$  is the delay range for each enabled transition;

- $Q: V \to \mathbb{Q}$  is the value of each continuous variable;

- $R: V \to \mathbb{Q}$  is the rate of each continuous variable;

- $RR: V \to \mathbb{Q} \times \mathbb{Q}$  is the range of rates for each continuous variable;

- $I: \mathcal{I} \to \{ \mathbf{false}, \mathbf{true} \}$  is the value of each inequality.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Recording the inequality values is not strictly necessary. It is included as a matter of convenience so that an implementation does not need to calculate it repeatedly.

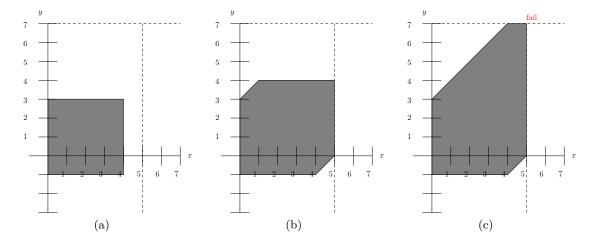

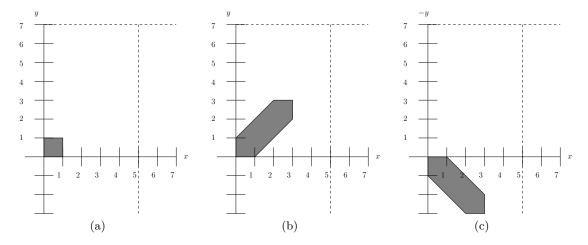

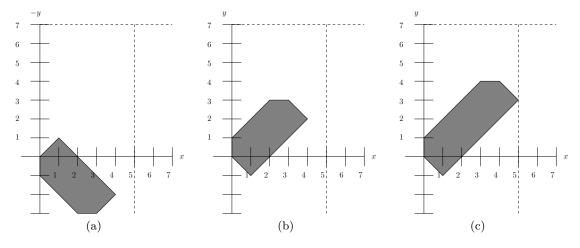

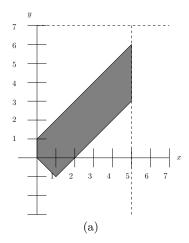

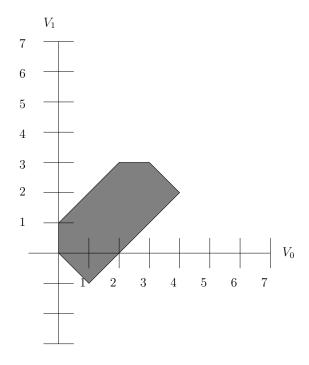

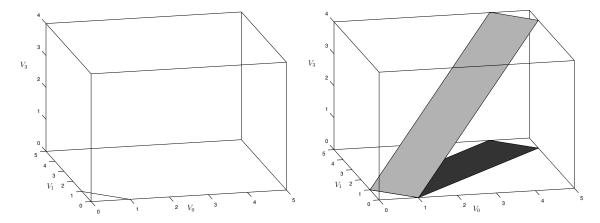

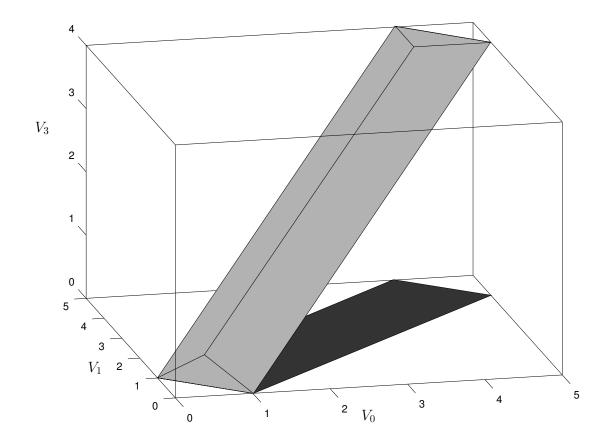

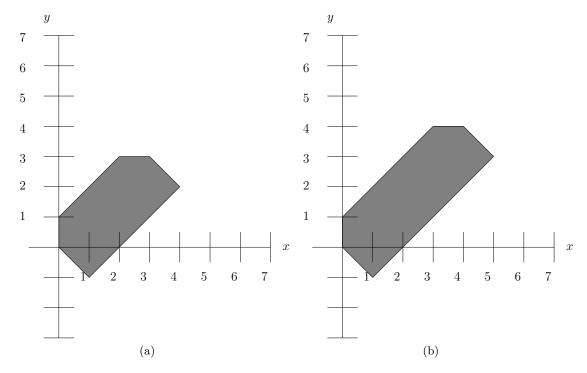

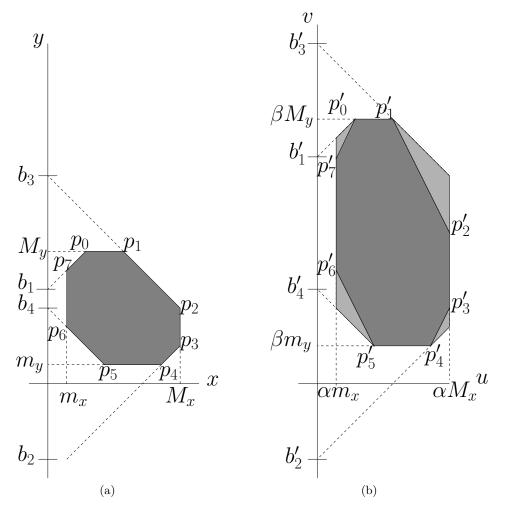

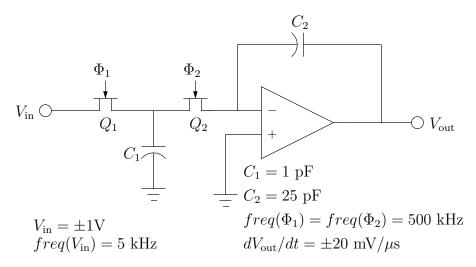

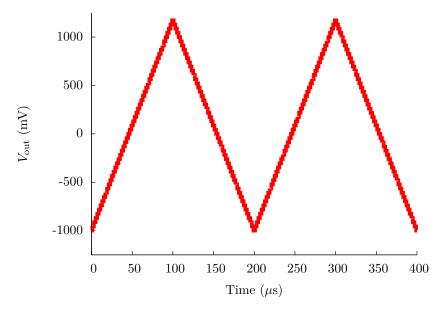

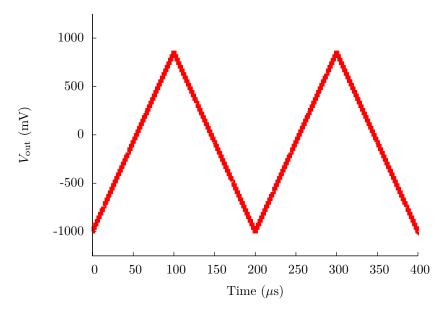

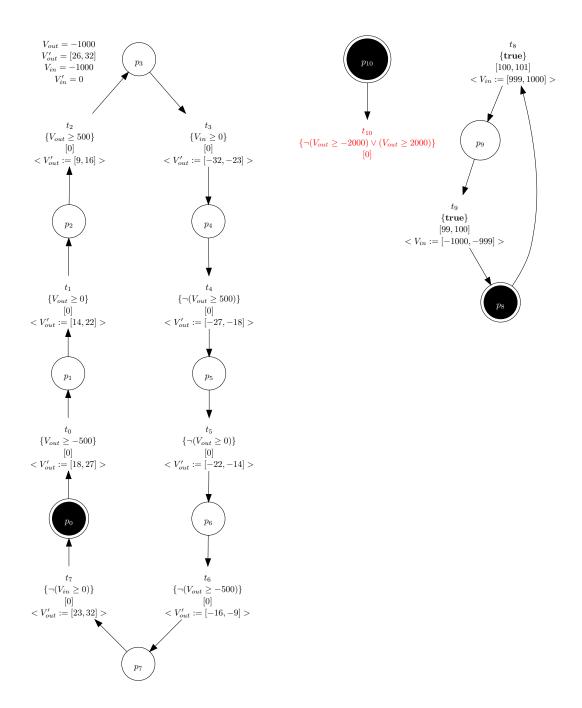

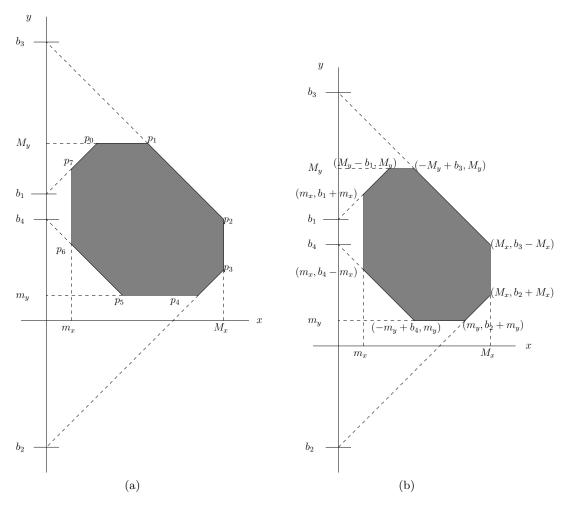

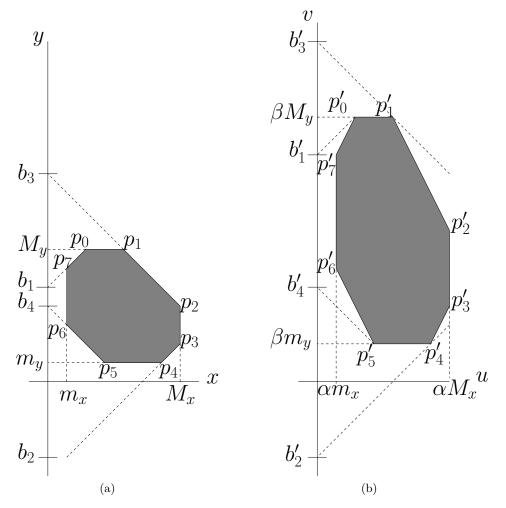

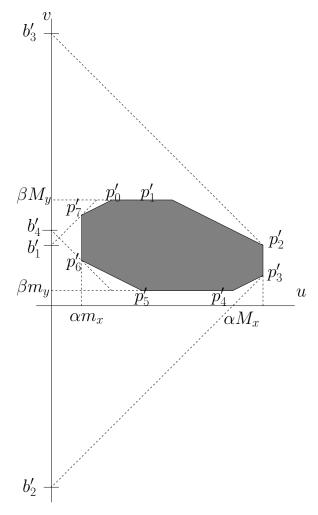

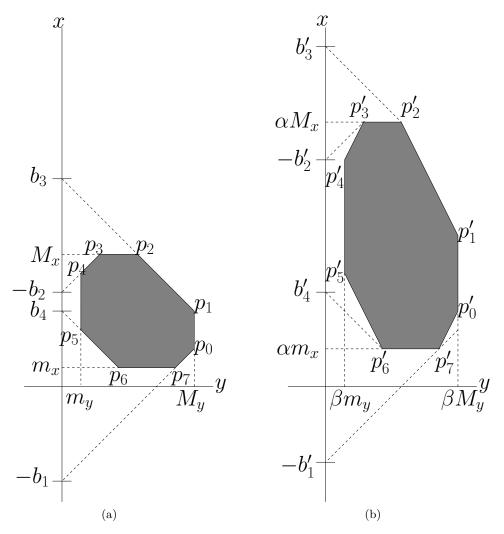

**Figure 2.2**: A property LPN for a capacitor stage in Fig. 2.1. When  $sw_i$  is 1, the property checks that  $V_i$  is above 15mV after  $10\mu s$ , and then that  $V_i$  is more than 30mV after an additional  $10\mu s$ . The property is violated if the fail transition, tFail, fires.